Page 1

QCPUQCPU

(Function Explanation,

Program Fundamentals)

Mitsubishi Programmable

Logic Controller

Q00JCPU

Q00CPU

Q01CPU

Q02CPU

Q02HCPU

Q06HCPU

Q12HCPU

Q25HCPU

Q12PHCPU

Q25PHCPU

Q12PRHCPU

Q25PRHCPU

Page 2

Page 3

SAFETY PRECAUTIONS

(Always read these instructions before using this equipment.)

Before using this product, please read this manual and the relevant manuals int roduced in this manual

carefully and pay full attention to safety to handle the product correctly.

In this manual, t h e safety instructions are ranked as "DA NGER" and "CAUTION".

DANGER

CAUTION

Note that the CAUTION level may lead to a serious consequence according to the circumstances.

Always follow the instructions of both levels because they are important to personal safety.

Please save this ma nual to make it accessible when required and alwa ys forward it to the end user.

Indicates that incorrect handling may cause hazardous conditions,

resulting in death or severe injury.

Indicates that incorrect handling may cause hazardous conditions,

resulting in medium or slight personal injury or physical damage.

A

- 1

Page 4

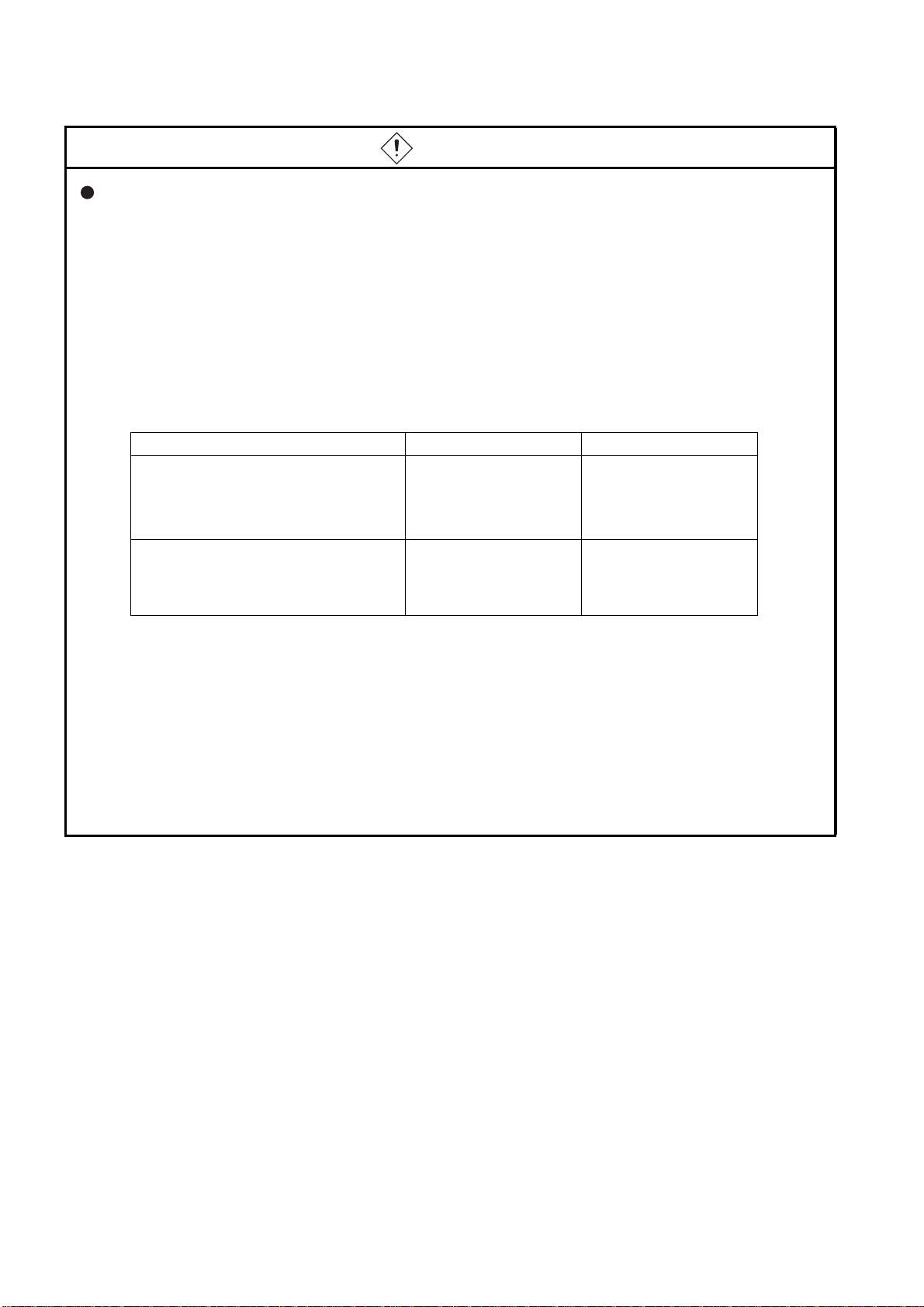

[Design Precautions]

DANGER

Install a safety circuit external to the PLC that keeps the entire system safe even when there are

problems with the external power suppl y or the PLC module. Otherwise, trouble could result from

erroneous output or er roneous operation.

(1) Outside the PLC, constru ct mech anica l damag e prevent ing i nterl ock circu its su ch as eme rgency

stop, protective circuits, posit ioning upper and lower limits switches and interlocking for ward/

reverse operations.

(2) When the PLC detects the following problems,

it will stop calc ulation and turn off all output in the case of (a).

In the case of (b), it will hold or turn off all output according to the parameter setting.

Note that the An S series module wi ll turn off the output in either of cases (a) and (b).

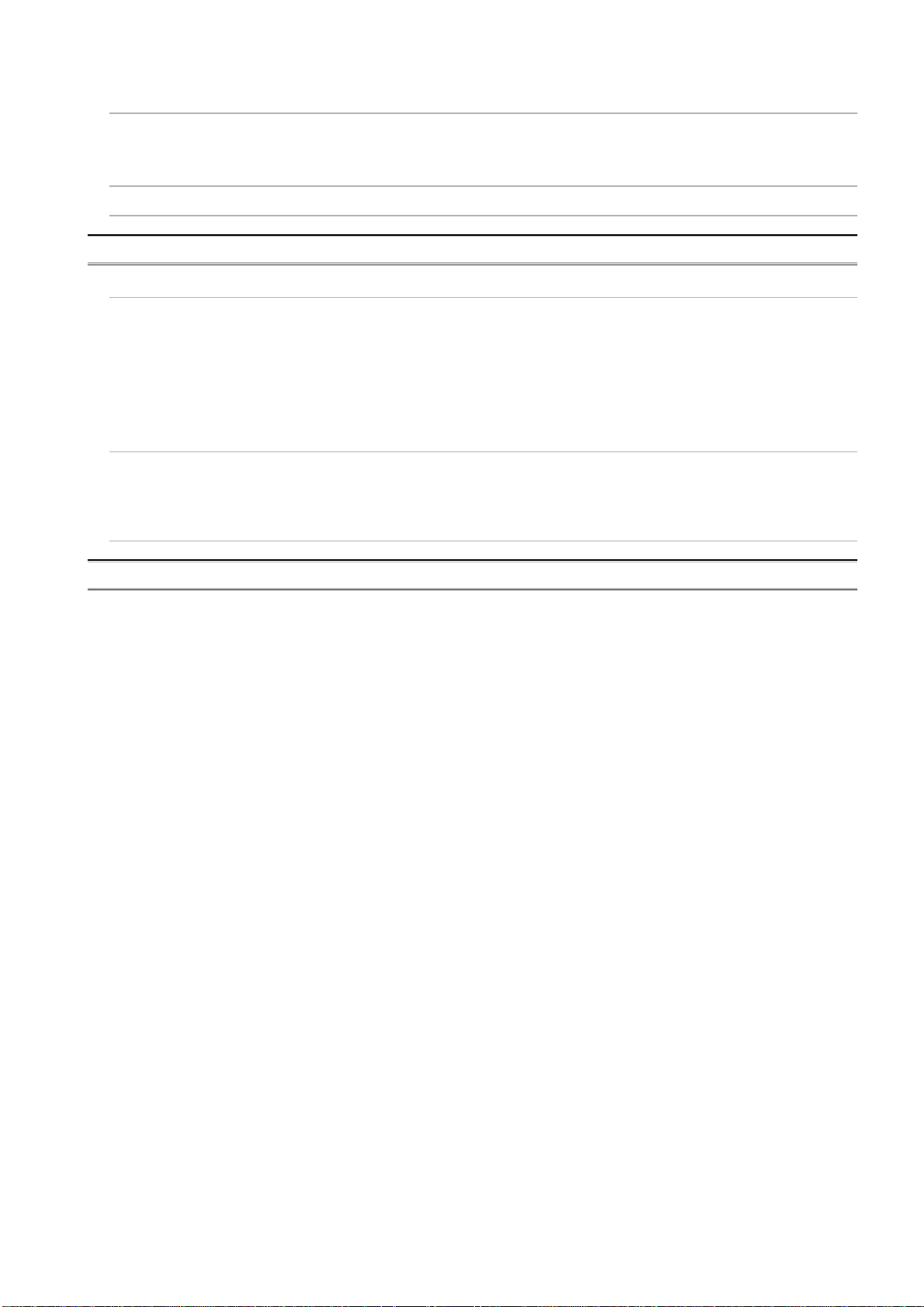

Q series module AnS series module

(a) The power supply module has

over currentprotection equipment

and over voltage protection

equipment.

(b) The CPU module self-diagnosis

functions, such as the watchdog

timer error, detect problems.

Output OFF Output OFF

Hold or turn off all

output according to

the parameter setting.

Output OFF

In addition, all output will be turned on when there are pro blems that the PLC CPU cannot

detect, such as in th e I/O control ler. Buil d a fail safe ci rcuit ex terior t o the PLC that will make sure

the equipment operates safely at such times.

Refer to " LOADING AND INSTALLATION" in QCPU User's Manual (Hardware Design,

Maintenance and Inspection) for example fail safe circuits.

(3) Output could be left on or off when t here is trouble in the outputs module rel ay or transistor. So

build an external monitoring circuit that will monitor any single outputs that could cause serious

trouble.

A

- 2

Page 5

[Design Precautions]

DANGER

When overcurrent which exceeds the rating or caused by short-circuited load flows in the output

module for a long time, it may cause smoke or fire. To prevent this, configure an external safety

circuit, such as fuse.

Build a circuit that turns on the external power supp ly when the PLC main module power is turned

on.

If the external power supply is turned on first, it could result in erroneous output or erroneous

operation.

When there are communication problems with the data link , refer to the corresponding data link

manual for the operating status of each station.

Not doing so could result in erroneous output or erroneous operation.

When connecting a peripheral device to the CPU module or connecting a personal computer or the

like to the intelligent function module / special function module to exercise control (data change) on

the running PLC, configure up an int erlock circuit in the sequence program to ensure that the whole

system will always operate safely.

Also before exercising other control (program change, operating status c hange (status control)) on

the running PLC, read the manual carefully and fully conf irm safety.

Especially for the above control on the remote PLC from an external device, an immediate action

may not be taken for PLC trouble due to a data communication fault.

In addition to configuring up the interlock circuit in the sequence program, corrective and other

actions to be taken as a system for the occurrence of a data communication fault should be

predetermined between the external device and PLC CPU.

CAUTION

Do not bunch the control wires or communication cables with the main circuit or power wires, or

install them close to each other.

They should be installed 100 mm (3.94 inch) or more from each other.

Not doing so could result in noise that would cause erroneous ope ration.

When controlling items li ke lamp l oad, heate r or sole noid val ve using a n output module, l arge curr ent

(approximately ten times greater than that present in normal circumstances) may flow when the

output is turned OFF to ON.

Take measures such as replacing the module with one having sufficient rated current.

A

- 3

Page 6

[Installation Precautions]

CAUTION

Use the PLC in an environment that meets the general specifications contained in QCPU User's

Manual (Hardware Design, Maintenance and Inspect ion).

Using this PLC in an environment outside the range of the gen eral specifications could result in

electric shock, fire, erroneous operation, and damage to or deterioration of the product.

While pressing th e inst alla tion lever l ocate d at the bott om of module , ins ert th e modul e fixi ng tab into

the fixing hole in the base unit until it stops. Then, securely mount the mo dule with the fixing hole as

a supporting poin t.

Incorrect loading of the module can cause a malfunction, failure or drop.

When using the PL C in the en vi ro nm e nt of mu c h vi bra t i o n, ti gh te n th e m od ul e wit h a sc re w.

Tighten the screw in the specified torque range.

Undertightening can cause a drop, shor t circuit or malfunction.

Overtightening can cause a drop, short circuit or malfunction due to damage to the screw or mo dule.

When installing extension cables, be sure that the base unit and the extension module connectors

are installed correctly.

After installation, check them for looseness.

Poor connections c ould cause an input or out put failure.

Securely load the memory card into the memory card loading connector.

After installation, check for lifting.

Poor connections c ould cause an operation fault.

Completely turn off the external ly supplied power used in the system before mounting or removing

the module. Not doing so could result in damage to the product.N ote that the module can be

changed online (while power is on) in the system that uses the CPU module compatible with online

module change or on the MELSECNET/H remote I/O station.

Note that there are restrictions on the modules that can be changed online(while power is on), and

each module has its predetermined changing procedure.

For details, refer to QCPU User's Manual (Hardware Design, Maintenance and Inspection) and the

online module change section in the manual of the module compatible with online module change.

Do not directly touch the module's conductive parts or elect ronic components.

Touching the conductive parts could cause an operation failure or give damage to the mo dule.

A

- 4

Page 7

[Wiring Precautions]

DANGER

Completely turn off the externally supplied pow er used in the system when installing or placing

wiring.

Not completely turning off all po wer could result in electric shock or damage to the product.

When turning on the power supply or opera ting the module after installation or wiring work, be sure

that the module's terminal covers are correctly attached.

Not attaching the terminal cover could result in electric shock.

DANGER

Be sure to ground the FG terminals and LG terminals to the prote c tive ground conductor.

Not doing so could result in electric shock or erroneous operation.

When wiring in the PLC, be sure tha t it is d one corr ectl y by che cki ng t he pr od uct' s ra te d vol tage and

the terminal layout.

Connecting a power supply that is diff erent from the rating or incorrectly wiring the product coul d

result in fire or damage.

External connections shall be crimped or pressure welded with the specified tools, or correctly

soldered.

Imperfect connections could result in short circuit, fi res, or erroneous operation.

Tighten the terminal screws with the specified torque.

If the terminal sc rews are loose, it could result in short cir c uits, fire, or erroneous operation.

Tighte ning the terminal screw s too far may cause damages to the screws and/or the module,

resulting in fallout, short circuits, or malfunction.

Be sure there are no foreign substances such as sawdust or wiring debris inside the module.

Such debris could cause fires, damage, or erroneous operation.

The module has an ing ress pr eventio n la bel o n its t op t o preve nt for eign matter, such as wire offcuts ,

from entering th e module during wir ing.

Do not peel this la be l du ri ng wi rin g .

Before starting system operation, be sure to peel this label because of hea t dissipation.

A

- 5

Page 8

[Startup and Maintenance Precautions]

DANGER

Do not touch the terminals while power is on.

Doing so could cause shock or erroneous operation.

Correctly connect the battery.

Also, do not charge, disassemble, heat, place in fire, sho rt circuit, or solder the battery.

Mishandling of bat tery can cause overheating or cracks which could result in injury and fires.

Switch off all phases of the externally supplied power used in the system when cleaning the module

or retightening the terminal or module mounting scr ews.

Not doing so could resu lt in electric shock.

Undertightening of terminal screws can cause a short ci rcuit or malfunction.

Overtightening of screws can cause damages to the screws and/or the module, resulting in fallout,

short circuits, or malfunction.

A

- 6

Page 9

[Startup and Maintenance Precautions]

CAUTION

The online operations conducted for the CPU module being operated, connecting the peripheral

device (especiall y, when changing data or operation s tatus) , shall b e conduc ted af ter th e manual has

been carefully read and a sufficien t check of safety has been conducted.

Operation mistakes could cause damage or problems with of the module.

Do not disassemble or mod ify the modules.

Doing so could cause trouble, erroneous operation, injur y, or fire.

Use any radio communication device such as a cellular phone or a PHS phone more than 25cm

(9.85 inch) away in all direction s of the PLC.

Not doing so can cause a mal function.

Completely turn off the externall y supplied power used in the system before mount ing or removing

the module. Not doing so could result in damage to the product.

Note that the module can be changed online (while power is on) in the system that uses the CPU

module compatible with online module change or on the MELSECNET/H remote I/O station.

Note that there are restrictions on the modules that can be changed online (while power is on) , and

each module has its predetermined changing procedure.

For details, refer to QCPU User's Manual (Hardware Design, Maintenance and Inspection) and the

online module change section in the manual of the module compatible with online module change.

Do not mount/remove the module onto/from base unit more than 50 t imes (IEC61131-2-compliant),

after the first use of the product.Failure to do so may cause the module to malfunction due to poor

contact of connector.

Do not drop or give an impact to the battery mounted to the module.

Doing so may damage the battery, causing the battery fluid to leak inside the battery.

If the battery is dropped or given an impact, dispose of it without using.

Before touching the module, always touch grounded metal, etc. to discharge static electricity from

human body, etc.

Not doing so can cause the module to fail or malfunction.

A

- 7

Page 10

[Disposal Precautions]

CAUTION

When disposing of this product, treat it as industrial waste.

[Transportation Precautions]

CAUTION

When transporting lithium batteries, make sure to trea t them based on the transp ort regulations.

(Refer to Appendix4 for details of the controlled models.)

A

- 8

Page 11

REVISIONS

The manual number is given on the bottom left of the back cover.

Print Date Manual Number Revision

Jun., 2004 SH(NA)-080484ENG-A First edition

Japanese Manual Version SH-080473 -A

This manual confers no industrial property rights or any rights of any other kind, nor does it confer any patent licenses.

Mitsubishi Electric Corporation cannot be held responsible for any problems involving industrial property rights which may

occur as a result of using the contents noted in this manual.

C

2004 MITSUBISHI ELECTRIC CORPORATION

A

- 9

Page 12

INTRODUCTION

Thank you for choo sing t he Mits ubis hi MELSE C-Q Se ries of Gene ral Pu rpose Prog rammabl e Contr oll ers.

Before using the equipment, please read this manual carefully to develop full familiarity with the functions

and performance of the Q series PLC you have purchased, so as to ensure correct use.

CONTENTS

SAFETY PRECAUTIONS•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• A - 1

REVISIONS•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 9

INTRODUCTION ••••••••••••••••••••••••••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• ••A - 10

CONTENTS••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 10

ABOUT MANUALS•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 20

HOW TO SEE THIS MANUAL IS ORGANIZED••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 23

HOW TO USE THIS MANUAL•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 25

GENERIC TERMS AND ABBREVIATIONS•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••A - 26

CHAPTER1 OVERVIEW 1 - 1 to 1 - 28

1.1 Features •••••••••••••••••••••••••••••••••••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• ••••••••••••••• 1 - 10

1.1.1 Features of Basic model QCPU•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 10

1.1.2 Features of High Performance model QCPU •••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 11

1.1.3 Features of Process CPU•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 13

1.1.4 Features of Redundant CPU•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 15

1.2 Program Storage and Operation••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 17

1.3 Devices and Instructions Convenient for Programming ••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 23

1.4 How to Check the Serial No. and Function Version•••••••••••••••••••••••••••••••••••••••••••••••••••••••• 1 - 28

CHAPTER2 PERFORMANCE SPECIFICATION 2 - 1 to 2 - 8

CHAPTER3 SEQUENCE PROGRAM CONFIGURATION AND EXECUTION CONDITIONS

3 - 1 to 3 - 83

3.1 Sequence Program•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••3 - 3

3.1.1 Main routine programs •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••3 - 7

3.1.2 Subroutine programs •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••3 - 9

3.1.3 Interrupt programs •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 12

3.2 Settings for Execution of Only One Sequence Program •••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 22

3.3 Settings for Creation and Execution of Multiple Sequence Programs •••••••••••••••••••••••••••••••••• 3 - 24

3.3.1 Initial execution type program••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 26

3.3.2 Scan execution type program••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 30

3.3.3 Low speed execution type program ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 33

3.3.4 Stand-by type program••••••••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• •••••••••••••••••••••• 3 - 41

3.3.5 Fixed scan execution type program ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 46

3.3.6 Execution type setting and example of type changing••••••••••••••••••••••••••••••••••••••••••••••• 3 - 52

3.4 Operation Processing •••••••••••••••••••••••• •••••• ••••••• ••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• •• 3 - 58

A

- 10

Page 13

3.4.1 Initial processing••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 58

3.4.2 I/O refresh (I/O module refresh processing) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 59

3.4.3 Automatic refresh of the intelligent functi on modu le•••• ••••••• •••••• ••••••••••••••••••••••••••••••••• 3 - 59

3.4.4 END processing ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 60

3.5 RUN, STOP, PAUSE Operation Processing •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 61

3.6 Operation Processing during Momentary Power Failure•••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 63

3.7 Data Clear Processing••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 64

3.8 I/O Processing and Response Lag•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 66

3.8.1 Refresh mode•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 67

3.8.2 Direct mode •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 70

3.9 Numeric Values which can be Used in Sequence Programs••••••••••••••••••••••••••••••••••••••••••••• 3 - 73

3.9.1 BIN (Binary Code)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 76

3.9.2 HEX (Hexadecimal)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 77

3.9.3 BCD (Binary Coded Decimal)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 78

3.9.4 Real numbers (floating decimal point data) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 79

3.10 Character String Data•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 3 - 83

CHAPTER4 I/O NUMBER ASSIGNMENT 4 - 1 to 4 - 34

4.1 Relationship between Number of Slots and Main Base Unit •••••••••••••••••••••••••••••••••••••••••••••••4 - 1

4.2 Relationship between No. of Extension Stages and No. of Slots••••••••••••••••••••••••••••••••••••••••••4 - 2

4.3 Installing Extension Base Units and Setting the Number of Stages ••••••••••••••••••••••••••••••••••••••4 - 4

4.4 Base Unit Assignment (Base Mode) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 10

4.5 Definition of I/O Number••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 17

4.6 Concept of I/O Number Assignment •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 18

4.6.1 I/O numbers of base unit••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 18

4.6.2 I/O numbers of remote station•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 21

4.7 I/O Assignment by GX Developer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 23

4.7.1 Purpose of I/O assignment by GX Developer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 23

4.7.2 Concept of I/O assignment using GX Developer•••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 25

4.8 Examples of I/O Number Assignment••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 30

4.9 Checking the I/O Numbers•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 4 - 34

CHAPTER5 MEMORIES AND FILES HANDLED BY CPU MODULE 5 - 1 to 5 - 59

5.1 Basic Model QCPU••••••••••••••••••••••••••••• ••••••• ••••••• •••••• •••••••••••••••••••••••••••••••••••••••• •••••• ••5 - 1

5.1.1 Memory configuration and storable data••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••5 - 1

5.1.2 Program memory••••••••••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••5 - 3

5.1.3 Standard ROM•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••5 - 7

5.1.4 Standard RAM •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••5 - 9

5.1.5 Standard ROM program execution (boot run) and writing••••••••••••••••••••••••••••••••••••••••••• 5 - 12

5.2 High Performance Model QCPU, Process CPU and Redundant CPU••••••••••••••••••••••••••••••••• 5 - 16

5.2.1 Memory configuration and storable data•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 16

5.2.2 Program memory•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 20

5.2.3 Standard ROM••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 24

5.2.4 Standard RAM ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 26

A

- 11

Page 14

5.2.5 Memory card ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 29

5.2.6 Write to standard ROM and Flash card by GX Developer •••••••••••••••••••••••••••••••••••••••••• 5 - 34

5.2.7 Automatic all data write from memory card to standard ROM•••••••••••••••••••••••••••••••••••••• 5 - 39

5.2.8 Execution of standard ROM/memory card programs (boot run) ••••••••••••••••••••••••••••••••••• 5 - 43

5.2.9 Details of written files••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 48

5.3 Program File Structure••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••••••••••••••••••••••••• 5 - 50

5.4 File Operation by GX Developer and Handling Precautions•••••••••••••••••••••••••••••••••••••••••••••• 5 - 52

5.4.1 File operation••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 52

5.4.2 Precautions for handling files ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 53

5.4.3 Memory capacities of files ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 5 - 54

5.4.4 File size units••••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• •••••••••••••••••••••••••••••••••••••••• •• 5 - 56

CHAPTER6 FUNCTIONS 6 - 1 to 6 - 163

6.1 Function List •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 1

6.2 Constant scan •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 5

6.3 Latch Function•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 9

6.4 Setting of Output (Y) Status when Changing between STOP and RUN ••••••••••••••••••••••••••••••• 6 - 12

6.5 Clock Function••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 15

6.6 Remote Operation •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 20

6.6.1 Remote RUN/STOP •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 20

6.6.2 Remote PAUSE ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 24

6.6.3 Remote RESET•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 27

6.6.4 Remote latch clear •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 31

6.6.5 Relationship of remote operation and CPU's RUN/STOP status •••••••••••••••••••••••••••••••••• 6 - 33

6.7 Input Response Time Selection of Q Series Modules ••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 34

6.8 Error Time Output Mode Setting ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 37

6.9 Hardware Error Time PLC Operation Settings•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 38

6.10 Intelligent Function Module Switch Setting••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 39

6.11 Monitor Function •••••••••••••••••••••••••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •• 6 - 42

6.11.1 Monitor condition setting ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 44

6.11.2 Local device monitor/test •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 50

6.11.3 Enforced ON/OFF of external I/O •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 53

6.12 Writing in Program during CPU Module RUN ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 61

6.12.1 Write during RUN in ladder mode•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 61

6.12.2 File-write during RUN•••••••••••• ••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •• 6 - 67

6.13 Execution Time Measurement•••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••••• 6 - 70

6.13.1 Program list monitor •••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••••••••••••••••••••••••• 6 - 70

6.13.2 Interrupt program monitor list ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 76

6.13.3 Scan time measurement••••••••••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •• 6 - 77

6.14 Sampling Trace Function•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 80

6.15 Debug Execution by Multiple Users ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 91

6.15.1 Simultaneous monitoring execution by multiple users ••••••••••••••••••••••••••••••••••••••••••••••• 6 - 92

6.15.2 Simultaneous write during RUN by multiple users•••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 95

6.16 Watchdog Timer (WDT) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 6 - 97

A

- 12

Page 15

6.17 Self-diagnostics Function•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 100

6.17.1 Interrupt due to error occurrence••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 111

6.17.2 LED display at the time of error occurrence•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 113

6.17.3 Error Clear•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 113

6.18 Error History ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 115

6.18.1 Basic model QCPU ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 115

6.18.2 High Performance model QCPU, Process CPU, Redundant CPU •••••••••••••••••••••••••••••••6 - 116

6.19 System Protect •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 117

6.19.1 Password registration •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 118

6.19.2 Remote password••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 121

6.20 CPU Module System Display by GX Developer •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 127

6.21 LED Display•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 131

6.21.1 Method to turn off the LED •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 132

6.21.2 Priority setting•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 133

6.22 High Speed Interrupt Function ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 136

6.22.1 High speed interrupt program execu tio n•••••••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••••••••••••••• 6 - 138

6.22.2 High speed I/O refresh, high speed buffer transfer••••••••••••••••••••••••••••••••••••••••••••••••••6 - 140

6.22.3 Processing times •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 143

6.22.4 Restrictions••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 145

6.23 Interrupt from the Intelligent Function Module••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 148

6.24 Serial Communication Function•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 149

6.25 Reading the Module Service Interval Time •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 157

6.26 Device Initial Value ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••6 - 159

CHAPTER7 COMMUNICATION WITH INTELLIGENT FUNCTION MODULE 7 - 1 to 7 - 10

7.1 Communication Between CPU Module and Intelligent Function Modules•••••••••••••••••••••••••••••••7 - 2

7.1.1 Initial setting and auto refresh setting by GX Configurator••••••••••••••••••••••••••••••••••••••••••••7 - 3

7.1.2 Initial setting by device initial value ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••7 - 5

7.1.3 Communication by FROM/TO instruction ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••7 - 5

7.1.4 Communication by intelligent function module device •••••••••••••••••••••••••••••••••••••••••••••••••7 - 6

7.1.5 Communication by instructions for Intelli. function modules ••••••••••••••••••••••••••••••••••••••••••7 - 8

7.2 Access to AnS Series Corresponding Special Function Module •••••••••••••••••••••••••••••••••••••••• 7 - 10

CHAPTER8 PARAMETERS 8 - 1 to 8 - 37

8.1 PLC Parameters ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••8 - 2

8.1.1 Basic model QCPU •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••8 - 2

8.1.2 High Performance model QCPU, Process CPU, Redundant CPU •••••••••••••••••••••••••••••••• 8 - 14

8.2 Redundant Parameter ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 8 - 30

8.3 Network Parameters ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 8 - 32

8.4 Remote Password •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 8 - 37

CHAPTER9 DEVICE EXPLANATION 9 - 1 to 9 - 107

9.1 Device List••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••9 - 1

A

- 13

Page 16

9.2 Internal User Devices ••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• •••••••••••9 - 5

9.2.1 Input (X)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••9 - 8

9.2.2 Output (Y)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 10

9.2.3 Internal relay (M) ••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• •••••• ••••••• •••••••••••••••••••••• 9 - 11

9.2.4 Latch relay (L)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 12

9.2.5 Annunciator (F) ••••••••••••• •••••• ••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •• 9 - 14

9.2.6 Edge relay (V)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 20

9.2.7 Link relay (B)••• •••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• •••••••••••••••••••••• 9 - 21

9.2.8 Link special relay (SB) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 23

9.2.9 Step relay (S) •••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••••••••••••••••••••••••• 9 - 24

9.2.10 Timer (T) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 25

9.2.11 Counter (C)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 32

9.2.12 Data register (D)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 38

9.2.13 Link register (W)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 39

9.2.14 Link special register (SW) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 41

9.3 Internal System Devices• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• •••••••••••••••••••••••••••••••••••••••• •• 9 - 42

9.3.1 Function devices (FX, FY, FD) ••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• ••••••• •••••• ••••••• •• 9 - 42

9.3.2 Special relay (SM)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 45

9.3.3 Special register (SD)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 46

9.4 Link direct device •••••••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• ••••••••••••••••••••••••••••••••••• 9 - 48

9.5 Intelligent Function Module Device•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 53

9.6 Index Register (Z) ••• •••••• ••••••• ••••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •• 9 - 55

9.6.1 Switching between scan execution and low speed execution types •••••••••••••••••••••••••••••• 9 - 57

9.6.2 Switching scan/low speed exec. to Interrupt/fixed scan exec.•••••••••••••••••••••••••••••••••••••• 9 - 58

9.7 File Register (R)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 62

9.7.1 File register data storage location•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 63

9.7.2 File register capacity•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 64

9.7.3 Differences in access methods by storage destination memory ••••••••••••••••••••••••••••••••••• 9 - 65

9.7.4 File register registration procedure •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 66

9.7.5 File register designation method ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 71

9.7.6 Precautions for using file registers••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 72

9.8 Nesting (N) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 76

9.9 Pointer (P)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 77

9.9.1 Local pointer•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 79

9.9.2 Common pointer •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 81

9.10 Interrupt pointer (I)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 84

9.10.1 List of interrupt pointer Nos and interrupt factors ••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 86

9.11 Other Devices ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 92

9.11.1 SFC block device (BL) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 92

9.11.2 SFC transition device (TR) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 92

9.11.3 Network No. designation device (J)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 92

9.11.4 I/O No. designation device (U)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 93

9.11.5 Macro instruction argument device (VD)•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 94

9.12 Constants•••••••••••••••••••••••••• •••••• ••••••• •••••• •••••••••••••••••••••••••••••••••••••••• ••••••• •••••• ••••••• •• 9 - 96

9.12.1 Decimal constant (K) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 96

9.12.2 Hexadecimal constant (H) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• ••••••• •• 9 - 96

9.12.3 Real number (E)••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 97

9.12.4 Character string (" ") •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 97

A

- 14

Page 17

9.13 Convenient Usage of Devices•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 98

9.13.1 Global devices and local devices •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 9 - 98

CHAPTER10 CPU MODULE PROCESSING TIME 10 - 1 to 10 - 21

10.1 Scan Time•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 10 - 1

10.1.1 Scan time structure ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 10 - 1

10.1.2 Time required for each processing included in scan time ••••••••••••••••••••••••••••••••••••••••••• 10 - 4

10.1.3 Factors that increase the scan time ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••10 - 12

10.1.4 Factors that can shorten scan time by changing the settings •••••••••••••••••••••••••••••••••••••10 - 17

10.2 Other Processing Times••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••10 - 21

CHAPTER11 PROCEDURE FOR WRITING PROGRAM TO CPU MODULE 11 - 1 to 11 - 16

11.1 Basic Model QCPU••••••••••••••••••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• •••••• 11 - 1

11.1.1 Items to be examined for program creation•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 1

11.1.2 Hardware check ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 2

11.1.3 Procedure for writing program •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 4

11.1.4 Boot run procedure ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 6

11.2 High Performance Model QCPU, Process CPU, Redundant CPU•••••••••••••••••••••••••••••••••••••• 11 - 7

11.2.1 Items to be examined for program creation•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 7

11.2.2 Hardware check ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 11 - 8

11.2.3 Procedure for writing one program •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••11 - 10

11.2.4 Procedure for writing multiple programs•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••11 - 13

11.2.5 Boot run procedure ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••11 - 16

APPENDICES App- 1 to App - 90

Appendix 1 Special Relay List••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• App- 1

Appendix 2 Special Register List•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••App- 28

Appendix 3 Comparison ••••••••••••••••••••••••••••••••••••••••••• •••••• ••••••• •••••• ••••••• ••••••• •••••• ••••••• ••••App - 80

Appendix 3.1 Basic model QCPU Upgrade•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••App- 80

Appendix 3.2 High Performance model QCPU Upgrade•••••••••••••••••••••••••••••••••••••••••••••••••••App- 84

Appendix 4 Precautions for Battery Transport••••••••••••••••••••••• •••••••••••••••••••••••••••••••••••••••• ••••App - 88

Appendix 5 Device Point Assignment Sheet•••••••••••••••••••••••••••••••• •••••••••••••••••••••••••••••••••••••App - 89

INDEX INDEX- 1 to INDEX- 4

A

- 15

Page 18

(Related manual).................QCPU User's Manual (Hardware Design, Maintenance and Inspection)

CONTENTS

CHAPTER1 OVERVIEW

1.1 Features

CHAPTER2 SYSTEM CONFIGURATION

2.1 System Configuration

2.1.1 System Configuration for Single CPU System

2.1.2 System Configuration for Bus connection of GOT

2.1.3 Configuration of peripher al devic es

2.1.4 Applicable Devices and Software

2.1.5 Precaution on system configuration

2.2 Confirming Serial No. and Function Version

CHAPTER3 GENERAL SPECIFICATIONS

CHAPTER4 HARDWARE SPECIFICATIONS OF THE CPU MODULE

4.1 Performance Specifications

4.2 Basic Model QCPU

4.2.1 Part Names

4.2.2 Switch Operation After Writing Program

4.2.3 Reset Operation

4.2.4 Latch Clear Operation

4.3 High Performance Model QCPU, Process CPU and Redundant CPU

4.3.1 Part Names

4.3.2 Switch Operation After Writing Program

4.3.3 Reset Operation

4.3.4 Latch Clear Operation

4.3.5 Automatic Writing to Standard ROM

CHAPTER5 POWER SUPPLY MODULE

5.1 Base Units and CPU Modules Used with Power Sup pl y Modu le

5.2 Specifications

5.2.1 Power supply module specifications

5.2.2 Selecting the power supply module

5.2.3 Precaution when connecting the uninterruptive power supply

5.2.4 Cautions on power supply cap ac ity

5.3 Names of Parts and Settings

CHAPTER6 BASE UNIT AND EXTENSION CABLE

6.1 Base Unit

A

- 16

Page 19

6.1.1 Specification Table

6.1.2 Part Names

6.1.3 Setting the Extension Base Unit

6.1.4 Guideline for Use of Extension Base Units

6.2 Extension Cable

6.2.1 Specification Table

CHAPTER7 MEMORY CARD AND BATTERY

7.1 Memory Card

7.1.1 List of Usable Memory Cards

7.1.2 Memory Card Specifications

7.1.3 The Part Names of the Memory Card

7.1.4 Handling the Memory Card

7.1.5 Memory Card Loading/Unloading Procedures

7.1.6 Specifications of the Battery for Memory Card

7.1.7 Battery Installation into the Memory Card

7.2 Battery (Q6BAT, Q7BAT)

7.2.1 Battery Specifications

7.2.2 Installation of Battery

CHAPTER8 CPU MODULE START-UP PROCEDURES

CHAPTER9 EMC AND LOW VOLTAGE DIRECTIVES

9.1 Requirements for Conformance to EMC Directive

9.1.1 Standards relevant to the EMC Directive

9.1.2 Installation instructions for EMC Directive

9.1.3 Cables

9.1.4 Power Supply Module and Q00JCPU's Power Supply Part

9.1.5 When Using MELSEC-A Series Modules

9.1.6 Others

9.2 Requirement to Conform to the Low Voltage Directive

9.2.1 Standard applied for MELSEC-Q series PLC

9.2.2 MELSEC-Q series PLC selection

9.2.3 Power supply

9.2.4 Control panel

9.2.5 Grounding

9.2.6 External wiring

CHAPTER10 LOADING AND INSTALLATION

10.1 General Safety Requirements

10.2 Calculating Heat Generation of PLC

10.3 Module Installation

10.3.1 Precaution on in stallation

10.3.2 Instructions for mounting the base unit

10.3.3 Installation and removal of module

10.4 How to Set Stage Numbers for the Extension Base Unit

A

- 17

Page 20

10.5 Connection and Disconnection of Extension Cable

10.6 Wiring

10.6.1 The precautions on the wiring

10.6.2 Connecting to the power supply module

CHAPTER11 MAINTENANCE AND INSPECTION

11.1 Daily Inspection

11.2 Periodic Inspection

11.3 Battery Life and Replacement Procedure

11.3.1 Battery lives of CPU modules

11.3.2 Replacement Procedure of the CPU Module Battery

11.3.3 SRAM card battery life

11.3.4 SRAM card CPU module battery replacement procedure

11.4 When PLC Has Been Stored Without Battery

11.5 When Battery Has Gone Flat During Storage of PLC

CHAPTER12 TROUBLESHOOTING

12.1 Troubleshooting Basics

12.2 Troubleshooting

12.2.1 Troubleshooting flowchart

12.2.2 Flowchart for when the ERR terminal (negative logic) is turns off (opened)

12.2.3 Flowchart for when the "MODE" LED does not turn on

12.2.4 Flowchart for when the "MODE" LED is flickering

12.2.5 Flowchart for when the "POWER" LED turns off

12.2.6 Flowchart for when the "POWER" LED turns on (red)

12.2.7 Flowchart for when the "RUN" LED turned off

12.2.8 When the "RUN" LED is flickering

12.2.9 Flowchart for when the "ERR." LED is on/flickering

12.2.10 When the "USER" LED is turned on

12.2.11 When the "BAT." LED is turned on

12.2.12 Flowchart for when the "BOOT" LED is flickering

12.2.13 Flowchart for when output module LED does not turn on

12.2.14 Flowchart for when output load of output module does not turn on

12.2.15 Flowchart for when a program cannot be read

12.2.16 Flowchart for when write a program cannot be written

12.2.17 Flowchart for when program is rewritten unintentionally

12.2.18 Flowchart for when boot operation cannot be performed from memory card

12.2.19 Flowchart for when UNIT VERIFY ERR. occurs

12.2.20 Flowchart for when CONTROL BUS ERR. occurs

12.3 Error Code List

12.3.1 Error codes

12.3.2 CPU module errors

12.3.3 Error codes returned to request source during communication with CPU module

12.4 Module Change during System Operation

12.4.1 Online module change

12.4.2 Change of redundant power supply module (Q64RP)

A

- 18

Page 21

12.5 I/O Module Troubleshooting

12.5.1 Input circuit troubleshoot ing

12.5.2 Output Circuit Troubleshooting

12.6 Special Relay List

12.7 Special Register List

APPENDICES

Appendix 1 External Dimensions

Appendix 1.1CPU module

Appendix 1.2Power supply module

Appendix 1.3Main base unit

Appendix 1.4Extension base unit

Appendix 1.5Extension cable

Appendix 1.6Tracking cable

Appendix 2 Comparison

Appendix 2.1Functions Improvement of Basic Model QCPU

Appendix 2.2Upgraded Functions of High Performance Model QCPU

Appendix 2.3Precautions for Using the High Performance Model QCPU of Older Versions

Appendix 3 Precautions for Battery Transportation

INDEX

A

- 19

Page 22

ABOUT MANUALS

Related Manuals

The following manuals are also related to this product.

In necessary, order them by quoting the details in the tables below.

(1) Common to CPU modules

The following table indicates the related manuals common to the Basic model QCPU,

High Performance model QCPU, Process CPU and Redundant CPU.

Manual Name

QCPU User's Manual (Hardware Design, Maintenance and Inspection)

This manual provides the specifications of the CPU modules, power supply modules, base units,

extension cables, memory cards and others.

(Sold separately)

QCPU (Q Mode)/QnACPU Programming Manual (Common Instructions)

This manual describes how to use the sequence instructions and application instructions.

(Sold separately)

QCPU (Q Mode)/QnACPU Programming Manual (SFC)

This manual explains the system configuration, performance specifications, functions, programming, debugging,

error codes and others of MELSAP3.

(Sold separately)

QCPU (Q Mode) Programming Manual (MELSAP-L)

This manual describes the programming methods, specifications functions, and so on that are necessary to

create the MELSAP-L type SFC program.

(Sold separately)

QCPU (Q Mode) Programming Manual (Structured Text)

This manual describes the structured text language programming methods.

(Sold separately)

Manual Number

(Model Code)

SH-080483ENG

(13JR73)

SH-080039

(13JF58)

SH-080041

(13JF60)

SH-080076

(13JF61)

SH-080366E

(13JF68)

A

- 20

Page 23

(2) Basic model QCPU

The following table indicates the related manuals of the Basic model QCPU other than

the manuals indicated in "(1) Common to CPU modules".

Manual Name

QCPU (Q Mode)/QnACPU Programming Manual (PID Control Instructions)

This manual describes the dedicated instructions used to exercise PID control.

(Sold separately)

QCPU User’s Manual (Multiple CPU System)

This manual explains the multiple CPU system overview, system configuration, I/O numbers, communication

between CPU modules, and communication with the I/O modules or intelligent function modules.

(Sold separately)

Q Corresponding MELSEC Communication Protocol Reference Manual

This manual explains the communication methods and control procedures through the MC protocol for the

external devices to read and write data from/to the CPU module using the serial communication module/

Ethernet module.

(Sold separately)

(3) High Performance model QCPU

The following table indicates the related manuals of the High Performance model

QCPU other than the manuals indicated in "(1) Common to CPU modules".

Manual Name

QCPU (Q Mode)/QnACPU Programming Manual (PID Control Instructions)

This manual describes the dedicated instructions used to exercise PID control.

(Sold separately)

QCPU User’s Manual (Multiple CPU System)

This manual explains the multiple CPU system overview, system configuration, I/O numbers, communication

between CPU modules, and communication with the I/O modules or intelligent function modules.

(Sold separately)

Manual Number

(Model Code)

SH-080040

(13JF59)

SH-080485ENG

(13JR75)

SH-080008

(13JF89)

Manual Number

(Model Code)

SH-080040

(13JF59)

SH-080485ENG

(13JR75)

A

- 21

Page 24

(4) Process CPU

The following table indicates the related manuals of the Process CPU other than the

manuals indicated in "(1) Common to CPU modules".

Manual Name

QnPHCPU/QnPRHCPU Programming Manual (Process Control Instructions)

This manual describes the programming procedures, device names, and other items necessary to implement

PID control using process control instructions.

(Sold separately)

QCPU User’s Manual (Multiple CPU System)

This manual explains the multiple CPU system overview, system configuration, I/O numbers, communication

between CPU modules, and communication with the I/O modules or intelligent function modules.

(Sold separately)

(5) Redundant CPU

The following table indicates the related manuals of the Redundant CPU other than

the manuals indicated in "(1) Common to CPU modules".

Manual Name

QnPRHCPU User's Manual (Redundant System)

This manual explains the redundant system configuration, functions, communication with external devices, and

troubleshooting for redundant system construction using the Redundant CPU.

(Sold separately)

QCPU (Q Mode)/QnACPU Programming Manual (PID Control Instructions)

This manual describes the dedicated instructions used to exercise PID control.

(Sold separately)

QnPHCPU/QnPRHCPU Programming Manual (Process Control Instructions)

This manual describes the programming procedures, device names, and other items necessary to implement

PID control using process control instructions.

(Sold separately)

Manual Number

(Model Code)

SH-080316E

(13JF67)

SH-080485ENG

(13JR75)

Manual Number

(Model Code)

SH-080486ENG

(13JR76)

SH-080040

(13JF59)

SH-080316E

(13JF67)

A

- 22

Page 25

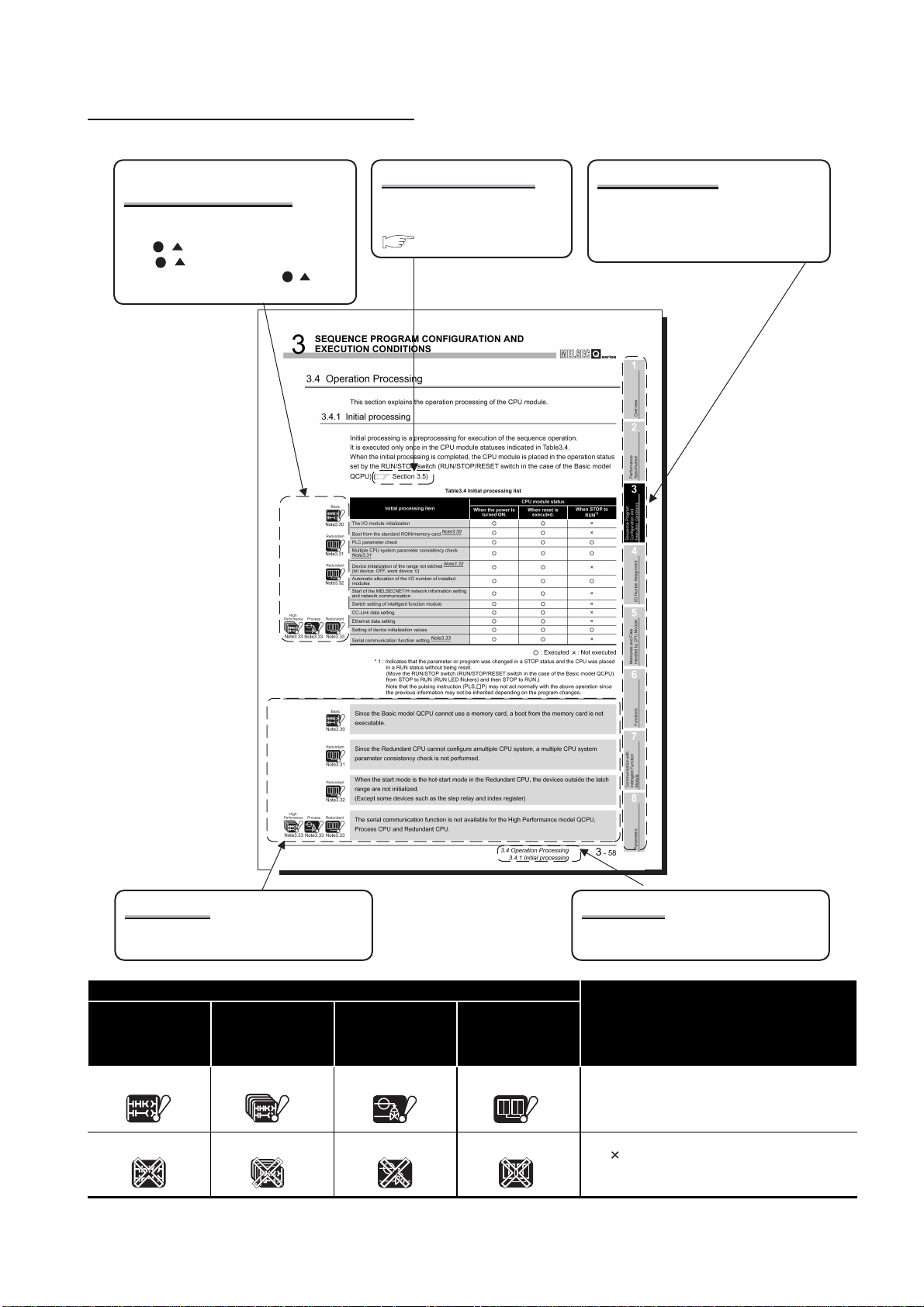

HOW TO SEE THIS MANUAL IS ORGANIZED

CPU modules requiring

precautions

The CPU modules requiring precautions

are shown as icons.

"Note . " under the icon corresponds to

"Note . " in the sentences and at the

page bottom. However, "Note . " is not

described in the section title.

Reference destination

A reference destination or

reference manual is marked

.

Chapter heading

The index on the right side of the page

shows the chapter of the open page at a

glance.

Precautions

Precautions corresponding to the icons are

provided.

Icon

High

QCPU

Basic

Basic

Performance

model QCPU

High

Performance

High

Performance

Process CPU Redundant CPU

Process Redundant

Process

Redundant

Section title

The section of the open page is shown at a

glance.

DescriptionBasic model

The ! marked icon indicates the CPU module

does not support a part of the described

functions.

The marked icon indicates the CPU module

does not support all of the described functions.

A

- 23

Page 26

In addition, this manual provides the foll owi ng exp la nati ons.

POINT

Explains the matters to be especially noted, the functions and others related to the

description.

Remark

Provides the reference destination related to the description on that page and the

convenient information.

A

- 24

Page 27

HOW TO USE THIS MANUAL

This manual is prepared for users to understand memory map, functions, programs and

devices of the CPU module when you use Q Series PLCs.

The manual is classified roughly into three sections as shown below.

1) Chapters 1 Describe the outline of the CPU module.

2) Chapters 2 to 5 Describe the perform ance spe cificat ions, executab le pr ogram, I/O

3) Chapter 6 Describes the functions of the CPU modules.

4) Chapter 7 Describes communication with intelligent function modules.

5) Chapters 8 and 9 Describe parameters and devices used in the CPU modules.

6) Chapter 10 Describes the CPU module processing time.

7) Chapter 11 Describes the procedure for writing parameters and programs

Remark

No. and memory of the CPU module.

created at the GX Developer to the CPU module.

This manual does not explain the functi ons of power sup pl y modu le s, bas e units,

extension cables, memory cards and batteries of CPU module.

For these details, refer to the manual shown below.

QCPU User's Manual (Hardware Design, Maintenance and Inspection)

Refer to the following manual for the multiple CPU system.

QCPU User's Manual (Multiple CPU Syst em)

Refer to the following manual for the redundant system.

QnPRHCPU User's Manual (Redundant System)

A

- 25

Page 28

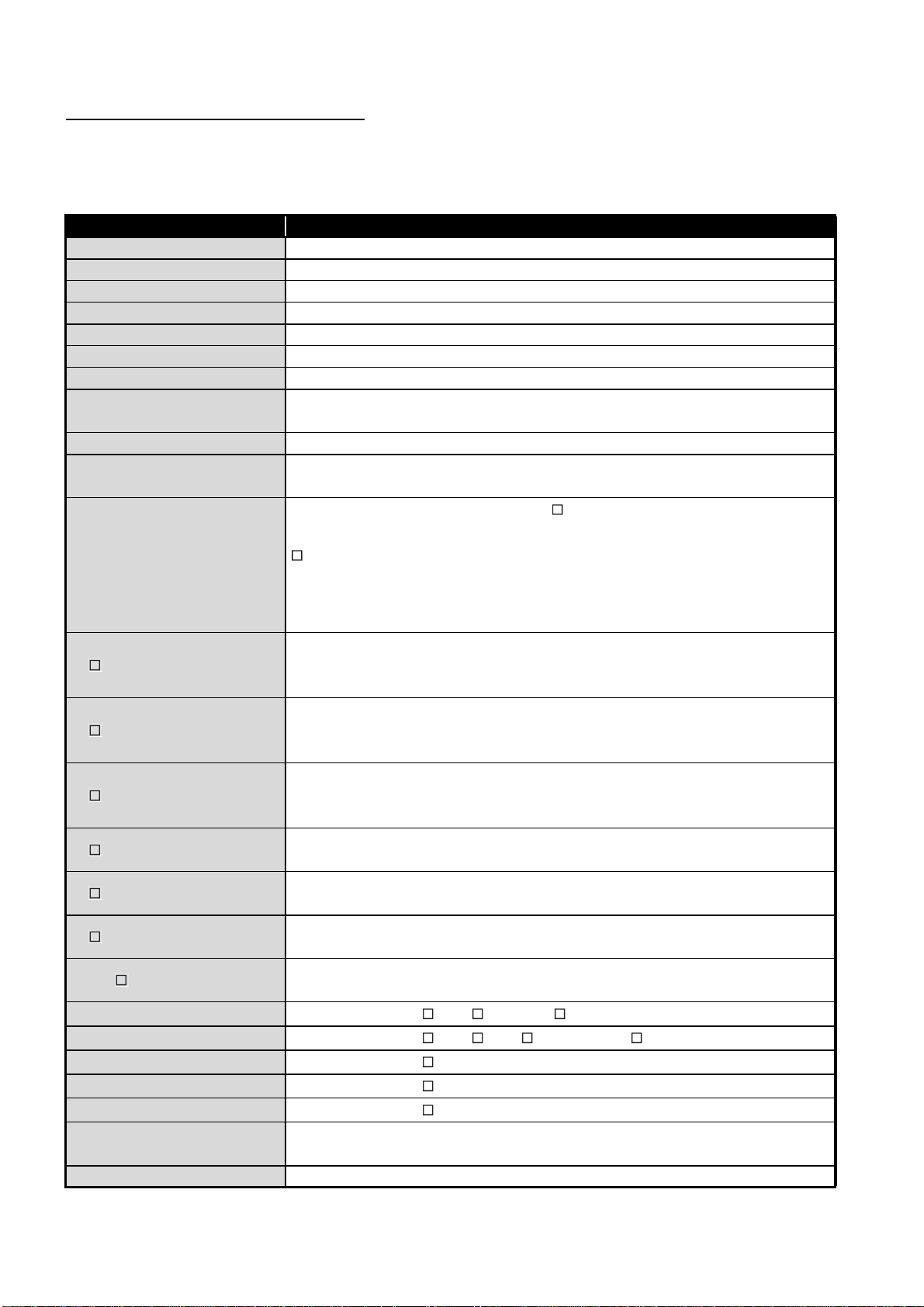

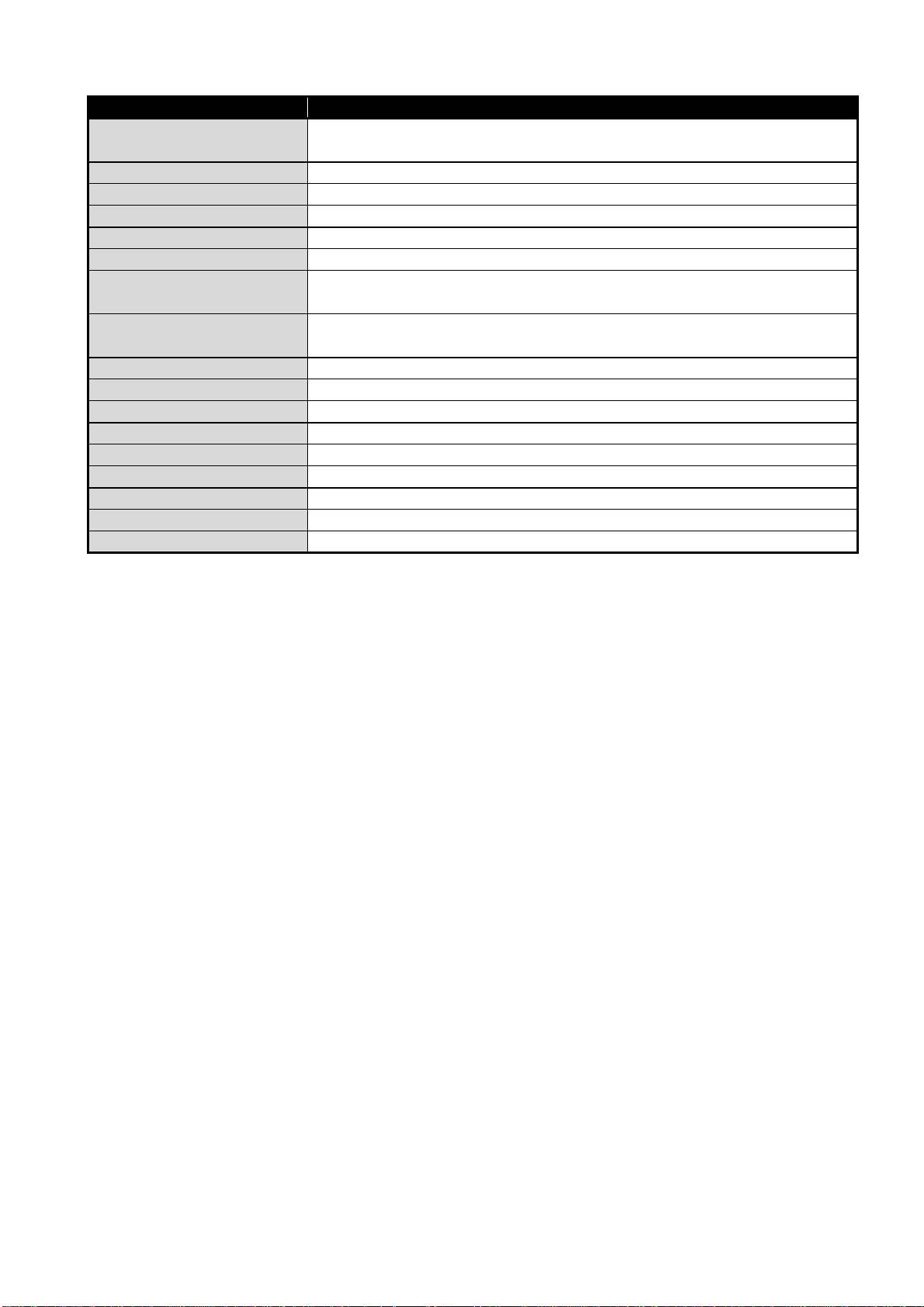

GENERIC TERMS AND ABBREVIATIONS

Unless otherwise specified, this manual uses the following generic terms and

abbreviations to explain the Q series CPU modules.

Generic Term/Abbreviation Description

Basic model QCPU General name for Q00JCPU, Q00CPU and Q01CPU modules.

High Performance model QCPU General name for Q02CPU, Q02HCPU, Q06HCPU Q12HC PU and Q25HCPU mo dules .

Process CPU General name for Q12PHCPU and Q25PHCPU

Redundant CPU General name for Q12PRHCPU and Q25PRHCPU.

QnHCPU General name for Q02HCPU, Q06HCPU Q12HCPU and Q25HCPU

QnPHCPU General name for Q12PHCPU and Q25PHCPU

QnPRHCPU General name for Q12PRHCPU and Q25PRHCPU.

CPU module

Q series Abbreviation for Mitsubishi MEL SEC-Q Series Programmable Logic Controller.

AnS series

GX Developer

Q3 B

Q3 SB

Q3 RB

Q5 B

Q6 B

Q6 RB

QA1S6 B

Main base unit

Extension base unit

Slim type main base unit

Redundant main base unit

Redundant extension base unit

Base unit

Redundant base unit General name for redundant main base unit and redundant extension base unit.

General name for Basic model QCPU, High performance model QCPU, Process CPU

and Redundant CPU.

Abbreviation for compact types of Mitsubishi MELSEC-A Series Programmable Logic

Controller.

Product name for Q series compatible SW D5C-GPPW-E type GPP function software

package.

indicates the version.

For the GX Developer versions applicable for each CPU module, refer to "System

configuration" in the QCPU User's Manual (Hardware Design, Maintenance and

Inspection).

General name for Q33B, Q35B, Q38B and Q312B main base units on which CPU

module (except Q00JCPU), Q series power supply module, I/O module and intelligent

function module can be mounte d.

General name for Q32SB, Q33SB an d Q35SB slim ty pe main base uni ts on which Basic

model QCPU (except Q00JCPU) High Performance model QCPU, slim type power

supply module, I/O module and intelligent function module can be mounted.

General name for Q38RB redundant power supply base unit on which CPU module

(except Q00JCPU), redundant power supply module, Q series I/O module and

intelligent function module can be mounted.

General name for Q52B and Q55B extension base unit on which the Q Series I/O and

intelligent function module can be mounted.

General name for Q63B, Q65B, Q68B and Q612B extension base unit on which Q

Series power supply module, I/O module, intelligent function module can be mounted.

General name for Q68R B re dun dan t power supply base unit on w h ic h red und an t po we r

supply module, Q series I/O modules and intelligent function module can be mounted.

General name for QA1S65B and QA1S68B extension base units on which with AnS

Series power supply module, I/O module, special function module can be mounted.

General name for Q3 B, Q3 SB and Q3 RB.

General name for Q5 B, Q6 B, Q6 RB and QA1S6 B.

General name for Q3 SB.

General name for Q3 RB.

General name for Q6 RB.

General name for main base unit, extension base unit, slim type main base unit,

redundant main base unit and redundant extension base unit.

A

- 26

Page 29

Generic Te rm/Abbreviation Description

Extension cable

Tracking cable General name for QC10TR and QC30TR tracking cable for Redundant CPU.

Q series power supply module General name for Q61P-A1, Q61P-A2, Q62P, Q63P and Q64P power supply modules.

Slim type power supply module General name for Q61SP slim type power supply module.

Redundant power supply module General name for Q64RP redundant power supply module.

AnS series power supply module General name for A1S61PN, A1S62PN and A1S63P power supply modules.

Power supply module

Battery

SRAM card Abbreviation for Q2MEM-1MBS and Q2MEM-2MBS type SRAM card.

Flash card General name for Q2MEM-2MBF and Q2MEM-4MBF type Flash card.

ATA card General name for Q2MEM- 8MBA, Q 2M EM -16 MBA a nd Q 2M EM -32 MBA ty pe ATA card.

Memory card General name for SRAM card, Flash card and ATA card.

PC CPU module MELSEC-Q series compatible PC CPU module of Contec makes.

Control system Abbreviation for Redundant CPU specified as control system.

Standby system Abbreviation for Redundant CPU specified as standby system.

System A Abbreviation for Redundant CPU specified as System A.

System B Abbreviation for Redundant CPU specified as System B.

General name for QC05B, QC06B, QC12B, QC30B, QC50B, QC100B extension

cables.

General name for Q series power supply modules, AnS series power supply modules,

slim type power supply module and redundant power supply module.

General name for Q6BAT and Q7BAT CPU module batteries and Q2MEM-BAT SRAM

card battery.

A

- 27

Page 30

1

OVERVIEW

CHAPTER1 OVERVIEW

This manual describes the programs, I/O number assignment method, functions and

devices of the Q Series CPU Modules ( (1) below).

For the power supply modules, base units, extension cables, memory cards and batteries,

refer to the manual below.

QCPU User's Manual (Hardware Design, Maintenance and Inspection)

(1) CPU modules corresponding to the description of this manual

The CPU modules described in this manual are as shown in Table1.1.

Table1.1 List of CPU modules corresponding to the description of this manual

CPU module Model name

Basic model QCPU Q00JCPU, Q00CPU, Q01CPU

High Performance model QCPU

Process CPU Q12PHCPU, Q25PHCPU

Redundant CPU Q 12PRHCPU, Q25PRHCPU

Q02CPU, Q02HCPU, Q06HCPU, Q12HCPU,

Q25HCPU

1

- 1

Page 31

1

OVERVIEW

1

(2) List of Q Series CPU Module manuals

The Q series CPU module manuals are as shown below.

For details such as manual numbers, refer to "About Manuals" in this manual.

Overview

(a) Basic model QCPU

2

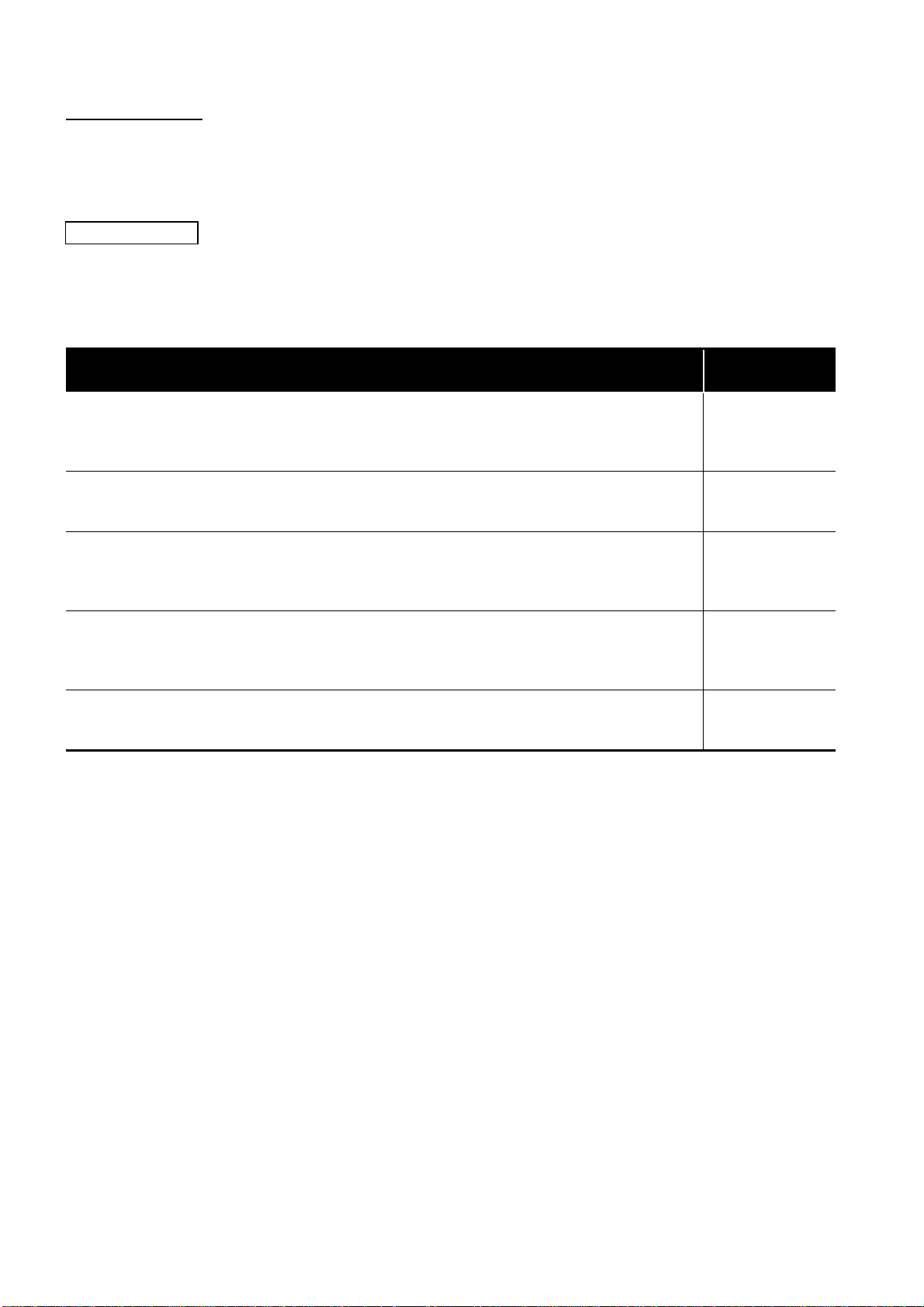

T able1.2 List of user's manuals of basic model QCPU

Purpose

Confirmation of part names and

specifications of the CPU module

Confirmation of connection methods

for the power supply module, base

unit and I/O module

Construction of the single CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Construction of the multiple CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Hardware

(Packed)

QCPU (Q mode)

CPU Module User's

Manual (Hardware)

Outline

Outline

Maintenance

and

Inspection

QCPU User's

Manual (Hardware

Design,

Maintenance and

inspection)

Details

Details

Details

Program

Fundamentals

QCPU User's

Manual (Fun ction

Explanation,

Program

Fundamentals)

Outline

Multi CPU

System

QCPU User's

Manual (Multiple

CPU System)

Details

Redundant

System

QnPRHCPU User's

Manual (Redundant

System)

Sequence Program

3

4

5

Performance

Configuration and

Specification

Execution Conditions

I/O Nunber Assignment

Confirmation of the sequence program

configuration and memory

Confirmation of the functions,

parameters, and devices of the CPU

module

Confirmation of the troubleshooting

and error codes

Details

Details

Details

1

- 2

Memories and Files

Handled by CPU Module

6

Functions

7

Communication with

Intelligent Function

Module

8

Parameters

Page 32

1

OVERVIEW

Table1.3 List of progra m mi ng m a nuals of basic model QCPU

Purpose

Confirmation of usage of

sequence instructions, basic

instructions, application

instructions, etc.

Confirmation of dedicated

instructions for PID control

Confirmation of MELSAP3's

system configuration,

performance specifications,

functions, programming,

debugging, and error codes

Confirmation of the

programming method,

specifications, functions, etc.

required for SFC programming

of the MELSAP-L type

Common

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual

(Common

Instruction)

Details

PID Control

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual (PID

Control

Instruction)

Details

Process

Control

Instruction

QnPHCPU/

QnPRHCPU

Programming

Manual (Process

Control

Instruction)

SFC

QCPU (Q mode)/

QnACPU

Programming

Manual (SFC)

Details

MELSAP-L

QCPU (Q mode)

Programming

Manual

(MELSAP-L)

Details

Structured

Text

QCPU (Q mode)

Programming

Manual

(Structured Text)

Confirmation of the

programming method of the

structured text language

Details

1

- 3

Page 33

1

OVERVIEW

1

(b) High Performance Model QCPU

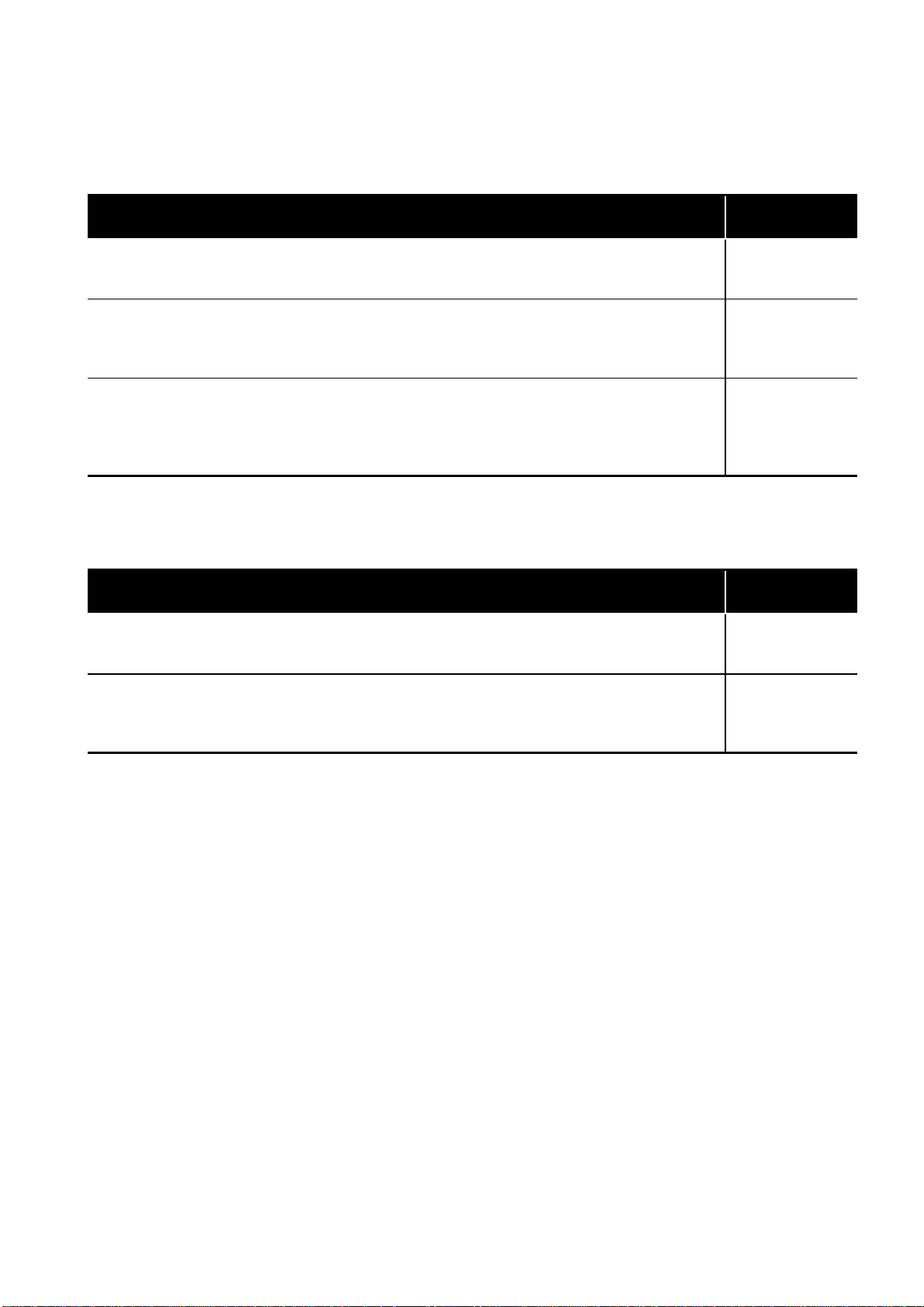

Table1.4 List of user's manuals of high performance model QCPU

Purpose

Confirmation of part names and

specifications of the CPU module

Confirmation of connection methods

for power supply module, base unit

and I/O module

Construction of the single CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Construction of the multiple CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Hardware

(Packed)

QCPU (Q mode)

CPU Module User's

Manual (Hardware)

Outline

Outline

Maintenance

and

Inspection

QCPU User's

Manual (Hardware

Design,

Maintenance and

inspection)

Details

Details

Details

Program

Fundamentals

QCPU User's

Manual (Fun ction

Explanation,

Program

Fundamentals)

Outline

Multi CPU

System

QCPU User's

Manual (Multiple

CPU System)

Details

Redundant

System

QnPRHCPU User's

Manual (Redundant

System)

Sequence Program

2

3

4

Performance

Configuration and

Overview

Specification

Execution Conditions

I/O Nunber Assignment

Confirmation of the sequence program

configuration and memory

Confirmation of the functions,

parameters, and devices of CPU

module

Confirmation of the troubleshooting

and error codes

Details

Details

Details

5

Memories and Files

Handled by CPU Module

6

Functions

7

Communication with

Intelligent Function

Module

8

1

- 4

Parameters

Page 34

1

OVERVIEW

Table1.5 List of programming manuals of high performance model QCPU

Purpose

Confirmation of usage of

sequence instructions, basic

instructions, application

instructions, etc.

Confirmation of dedicated

instructions for PID control

Confirmation of MELSAP3's

system configuration,

performance specifications,

functions, programming,

debugging, and error codes

Confirmation of the

programming method,

specifications, functions, etc.

required for SFC programming

of the MELSAP-L type

Common

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual

(Common

Instruction)

Details

PID Control

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual (PID

Control

Instruction)

Details

Process

Control

Instruction

QnPHCPU/

QnPRHCPU

Programming

Manual (Process

Control

Instruction)

SFC

QCPU (Q mode)/

QnACPU

Programming

Manual (SFC)

Details

MELSAP-L

QCPU (Q mode)

Programming

Manual

(MELSAP-L)

Details

Structured

Text

QCPU (Q mode)

Programming

Manual

(Structured Text)

Confirmation of the

programming method of the

structured text language

Details

1

- 5

Page 35

1

OVERVIEW

1

(c) Process CPU

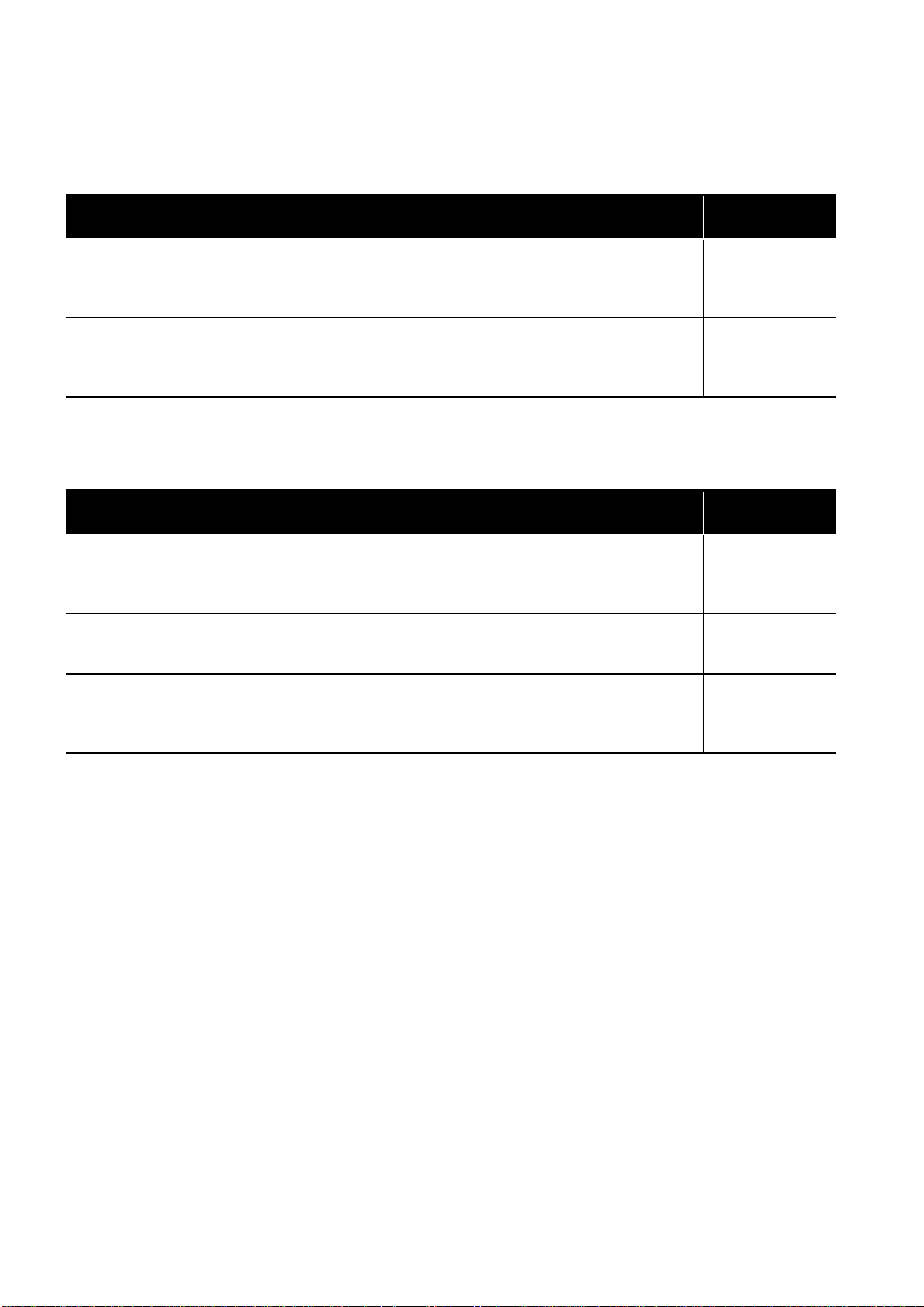

Table1.6 List of user's manuals of process CPU

Purpose

Confirmation of part names and

specifications of the CPU module

Confirmation of connection methods

for power supply module, base unit

and I/O module

Construction of the single CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Construction of the multiple CPU

system (confirmation of start-up

procedure and I/O number

assignment)

Hardware

(Packed)

QCPU (Q mode)

CPU Module User's

Manual (Hardware)

Outline

Outline

Maintenance

and

Inspection

QCPU User's

Manual (Hardware

Design,

Maintenance and

inspection)

Details

Details

Details

Program

Fundamentals

QCPU User's

Manual (Fun ction

Explanation,

Program

Fundamentals)

Outline

Multi CPU

System

QCPU User's

Manual (Multiple

CPU System)

Details

Redundant

System

QnPRHCPU User's

Manual (Redundant

System)

Sequence Program

2

3

4

Performance

Configuration and

Overview

Specification

Execution Conditions

I/O Nunber Assignment

Confirmation of sequence program

configuration and memory

Confirmation of the functions,

parameters, and devices of the CPU

module

Confirmation of the troubleshooting

and error codes

Details

Details

Details

5

Memories and Files

Handled by CPU Module

6

Functions

7

Communication with

Intelligent Function

Module

8

1

- 6

Parameters

Page 36

1

OVERVIEW

Table1.7 List of programming manuals of process CPU

Purpose

Confirmation of usage of

sequence instructions, basic

instructions, application

instructions, etc.

Confirmation of dedicated

instructions for process control

Confirmation of MELSAP3's

system configuration,

performance specifications,

functions, programming,

debugging and error codes

Confirmation of the

programming method,

specifications, functions etc.

required for SFC programming

of the MELSAP-L type

Common

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual

(Common

Instruction)

Details

PID Control

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual (PID

Control

Instruction)

Process

Control

Instruction

QnPHCPU/

QnPRHCPU

Programming

Manual (Process

Control

Instruction)

Details

SFC

QCPU (Q mode)/

QnACPU

Programming

Manual (SFC)

Details

MELSAP-L

QCPU (Q mode)

Programming

Manual

(MELSAP-L)

Details

Structured

Text

QCPU (Q mode)

Programming

Manual

(Structured Text)

Confirmation of the

programming method of the

structured text language

Details

1

- 7

Page 37

1

OVERVIEW

1

(d) Redundant CPU

Table1.8 List of user's manual of redundant CPU

Purpose

Confirmation of part names and

specifications of the CPU module

Confirmation of connection methods

for power supply module, base unit

and I/O module

Construction of redundant system

(confirmation of start-up procedure

and I/O number assignment)

Confirmation of the configuration and

memory of sequence programs

Confirmation of the functions,

parameters, devices, etc. of the CPU

module

Hardware

(Packed)

QCPU (Q mode)

CPU Module User's

Manual (Hardware)

Outline

Outline

Maintenance

and

Inspection

QCPU User's

Manual (Hardware

Design,

Maintenance and

inspection)

Details

Details

Program

Fundamentals

QCPU User's

Manual (Fun ction

Explanation,

Program

Fundamentals)

Outline

Details

Details

Multi CPU

System

QCPU User's

Manual (Multiple

CPU System)

Redundant

System

QnPRHCPU User's

Manual (Redundant

System)

Details

Sequence Program

2

3

4

5

Performance

Configuration and

Overview

Specification

Execution Conditions

I/O Nunber Assignment

Confirmation of the troubleshooting

Confirmation of the error codes

Details

Details

Memories and Files

Handled by CPU Module

6

Functions

7

Communication with

Intelligent Function

Module

8

1

- 8

Parameters

Page 38

1

OVERVIEW

Table1.9 List of programming manuals of redundant CPU

Purpose

Confirmation of usage of

sequence instructions, basic

instructions, application

instructions, etc.

Confirmation of dedicated

instructions for PID control

Confirmation of dedicated

instructions for process control

Confirmation of MELSAP3's

system configuration,

performance specifications,

functions, programming,

debugging and error codes

Confirmation of the

programming method,

specifications, functions, etc.

required for SFC programming

of the MELSAP-L type

Common

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual

(Common

Instruction)

Details

PID Control

Instructions

QCPU (Q mode)/

QnACPU

Programming

Manual (PID

Control

Instruction)

Details

Process

Control

Instruction

QnPHCPU/

QnPRHCPU

Programming

Manual (Process

Control

Instruction)

Details

SFC

QCPU (Q mode)/

QnACPU

Programming

Manual (SFC)

Details

MELSAP-L

QCPU (Q mode)

Programming

Manual

(MELSAP-L)

Details

Structured

Text

QCPU (Q mode)

Programming

Manual

(Structured Text

Edition)

Confirmation of the

programming method of the

structured text language

Details

1

- 9

Page 39

1

OVERVIEW

1.1 Features

1.1.1 Features of Basic model QCPU

Basic model QCPU

This section explains the features of the CPU modules.

The features specific to the Basic model QCPU are described below.

(1) Cost performance optimum for small-scaled system

The Basic model QCPU is a module targeted for a small-scaled system and optimum

for controlling a simple, compact system.

The Basic model QCPU realizes the cost performance optimum for a small-scaled

system.

GX Developer

Ethernet

Sequence Program

1

2

3

4

Performance

Configuration and

Overview

Specification

Execution Conditions

CC-Link remote

I/O station

MELSECNET/H PLC to PLC network

Diagram 1.1 System example using the Basic model QCPU

CC-Link remote

device station

(2) Communications with personal computer or display by serial

communication function ( Section 6.23)

The Q00CPU or Q01CPU can communicate with a personal computer/display other