Mitsubishi M37207MF-XXXSP, M37207MF-XXXFP, M37207M8-XXXSP, M37207EFSP, M37207EFFP Datasheet

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

DESCRIPTION

The M37207MF-XXXSP/FP and M37207M8-XXXSP are single-chip

microcomputers designed with CMOS silicon gate technology. It is

housed in a 64-pin shrink plastic molded DIP or a 80-pin plastic molded

QFP.

In addition to their simple instruction sets, the ROM, RAM and I/O

addresses are placed on the same memory map to enable easy programming.

The M37207MF-XXXSP/FP has a PWM function and an OSD function, so it is useful for a channel selection system for TV. The features of the M37207EFSP/FP are similar to those of the M37207MFXXXSP/FP except that these chips have a built-in PROM which can

be written electrically. The difference between M37207MF-XXXSP/

FP and M37207M8-XXXSP are the ROM size, RAM size, ROM size

for display and kinds of character. Accordingly, the following descriptions will be for the M37207MF-XXXSP/FP unless otherwise noted.

FEATURES

Number of basic instructions .................................................... 71

•

Memory size .................................................................................

•

Minimum instruction execution time

•

........................................ 0.5 µs (at 8 MHz oscillation frequency)

Power source voltage.................................................. 5 V ± 10 %

•

Subroutine nesting ............................................128 levels (Max.)

•

Interrupts ...................................................... 15 types, 14 vectors

•

8-bit timers ................................................................................. 6

•

Programmable I/O ports

•

(Ports P0, P1, P2, P30–P36, P4, P6) ....................................... 47

Input ports (Ports P70, P71) ....................................................... 2

•

Output ports (Ports P52–P56)..................................................... 5

•

12 V withstand ports................................................................. 10

•

LED drive ports .......................................................................... 4

•

Serial I/O ....................................... 8-bit ✕ 1 channel (2 systems)

•

ROM ......................32K bytes (M37207M8-XXXSP)

62K bytes (M37207MF-XXXSP/FP,

M37207EFSP/FP)

RAM ...................... 512 bytes (M37207M8-XXXSP)

960 bytes (M37207MF-XXXSP/FP,

M37207EFSP/FP)

ROM correction memory ............................ 64 bytes

ROM for display.......8K bytes (M37207M8-XXXSP)

12K bytes (M37207MF-XXXSP/FP,

M37207EFSP/FP)

RAM for display ........................................144 bytes

Multi-master I2C-BUS interface ...............................1 (3 systems)

•

Power dissipation

•

In high-speed mode ........................................................165 mW

CC = 5.5 V, 8 MHz oscillation frequency, CRT on)

(at V

In low-speed mode.........................................................0.33 mW

(at V

CC = 5.5 V, 32 kHz oscillation frequency)

A-D comparator (6-bit resolution)................................8 channels

•

PWM output circuit ...................................... 14-bit ✕ 1, 8-bit ✕ 10

•

Interrupt interval determination circuit ........................................ 1

•

ROM correction function ..........................................32 bytes ✕ 2

•

CRT display function

•

Number of display characters ............... 24 characters ✕ 3 lines

(16 lines maximum)

Kinds of characters .................. 256 kinds (M37207M8-XXXSP)

384 kinds (M37207MF-XXXSP/FP,

M37207EFSP/FP)

Character display area ..........................................12 ✕ 16 dots

Kinds of character sizes .................................................4 kinds

Kinds of character colors (It can be specified by the character)

maximum 15 kinds (R, G, B, I)

Kinds of character background colors (It can be specified by the character)

maximum 7 kinds (R, G, B)

1/2-character unit color specification is possible.

Kinds of raster colors (maximum 15 kinds)

Display position

Horizontal .................................................................. 64 levels

Vertical ....................................................................128 levels

Bordering (horizontal and vertical)

Wipe function

Scanning line double count mode display is possible.

APPLICATION

TV

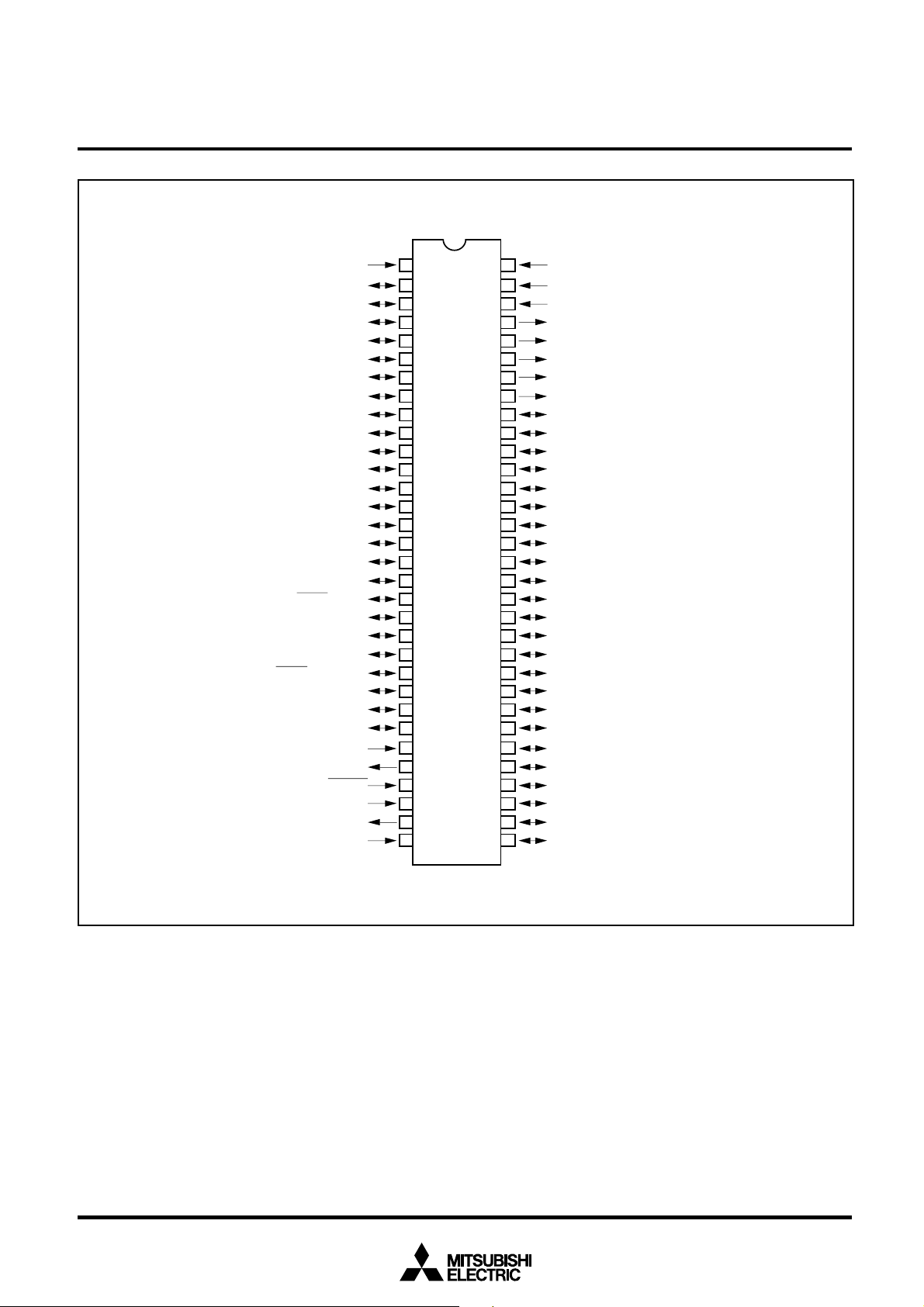

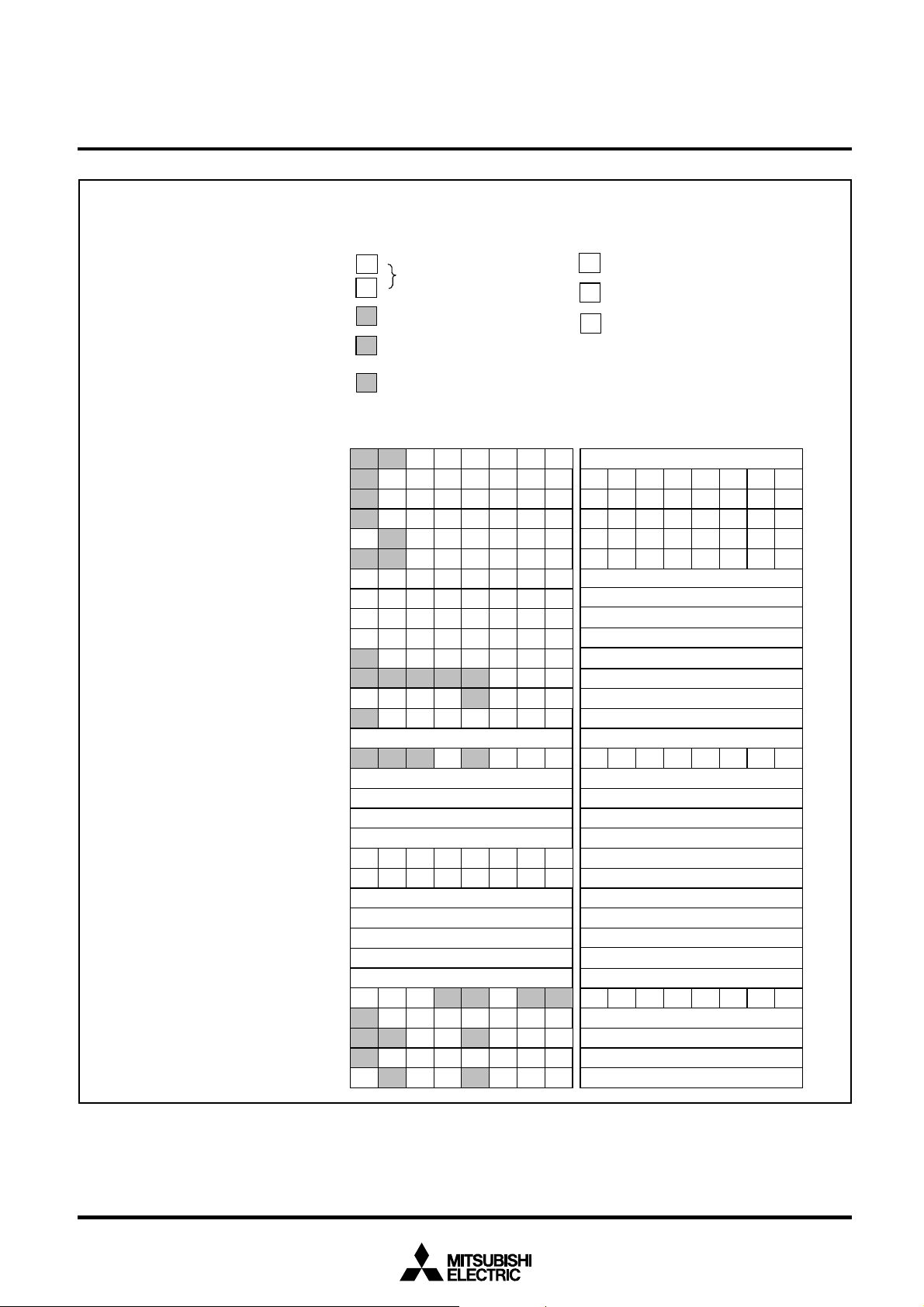

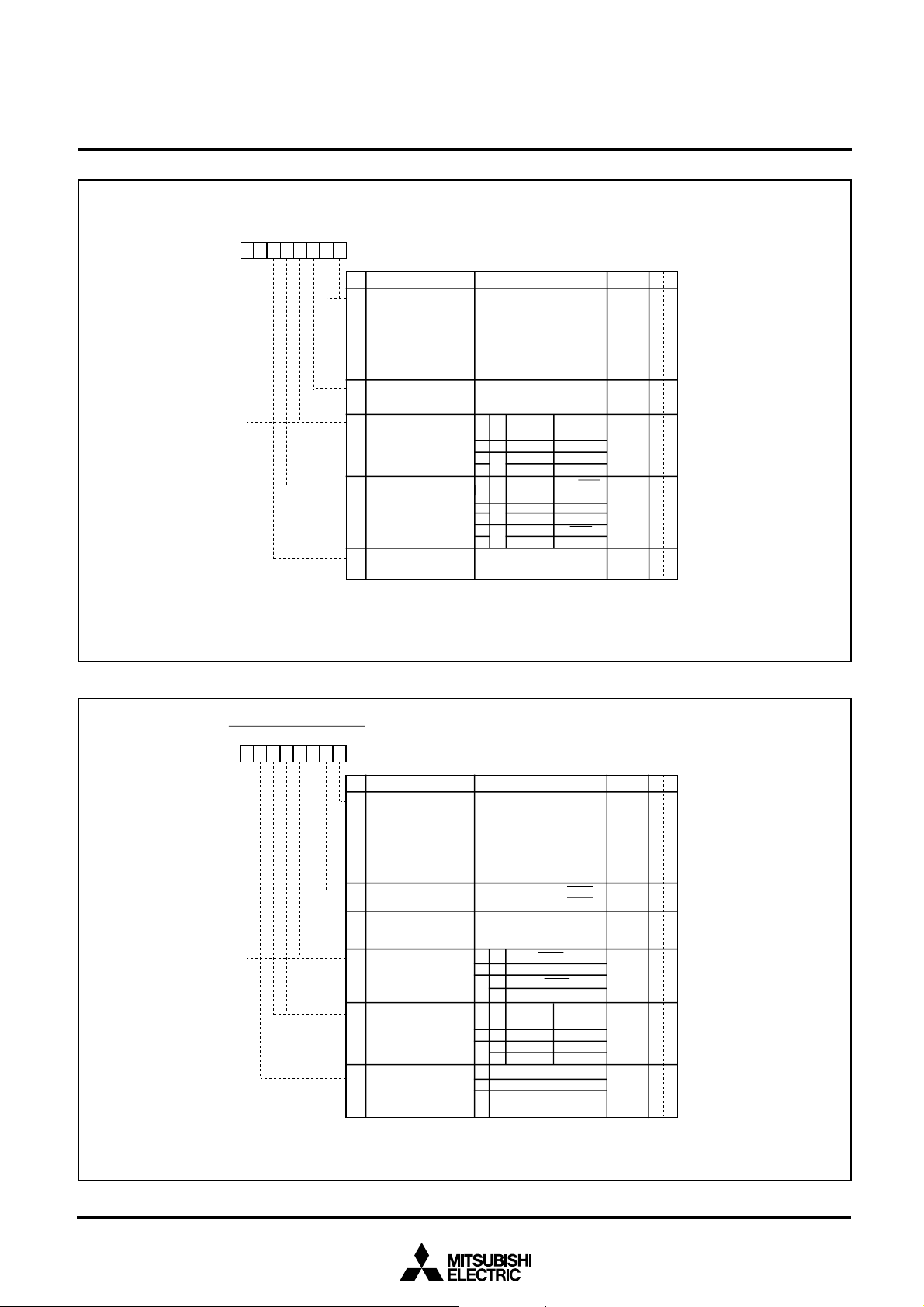

PIN CONFIGURATION (TOP VIEW)

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

P4

P4

P4

3

P4

1/SCLK2

0/SOUT2

OSC1/P70/AD4

OSC2/P7

P3

6

/INT2/AD2

P3

P3

4

D-A/AD3

0

/PWM0

P6

1

/PWM1

P6

P62/PWM2

P6

3

/PWM3

4

/PWM4

P6

P65/PWM5

6

/PWM6

P6

7

/PWM7

P6

P3

3

2

/TIM2/AD6

P3

P47/

S

RDY1

/PWM8

6/SIN1

5/SCLK1

4/SOUT1

RDY2

/SCL2/AD7

/SDA2/AD8

/PWM9

/SCL1

/SDA1

P4

P4

P4

/

S

2/SIN2

/SCL3/X

/SDA3/X

CNV

RESET

1

/AD5

5

/AD1

/INT1

/TIM3

P3

P3

COUT

CIN

X

X

OUT

V

SS

SS

1

2

3

4

5

6

7

8

9

M37207EFSP

10

11

12

13

14

15

16

17

1

18

0

19

20

21

22

23

24

25

26

27

28

φ

29

30

IN

31

32

64

V

CC

63

H

SYNC

62

V

SYNC

61

R/P5

2

60

G/P5

3

59

B/P5

4

58

I/P55/TIM1 OVERFLOW

57

OUT/P5

6

56

P0

M37207MF-XXXSP, M37207M8-XXXSP

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P0

P0

P0

P0

P0

P0

P0

P1

P1

P1

P1

P1

P1

P1

P1

P2

P2

P2

P2

P2

P2

P2

P2

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

Outline 64P4B

2

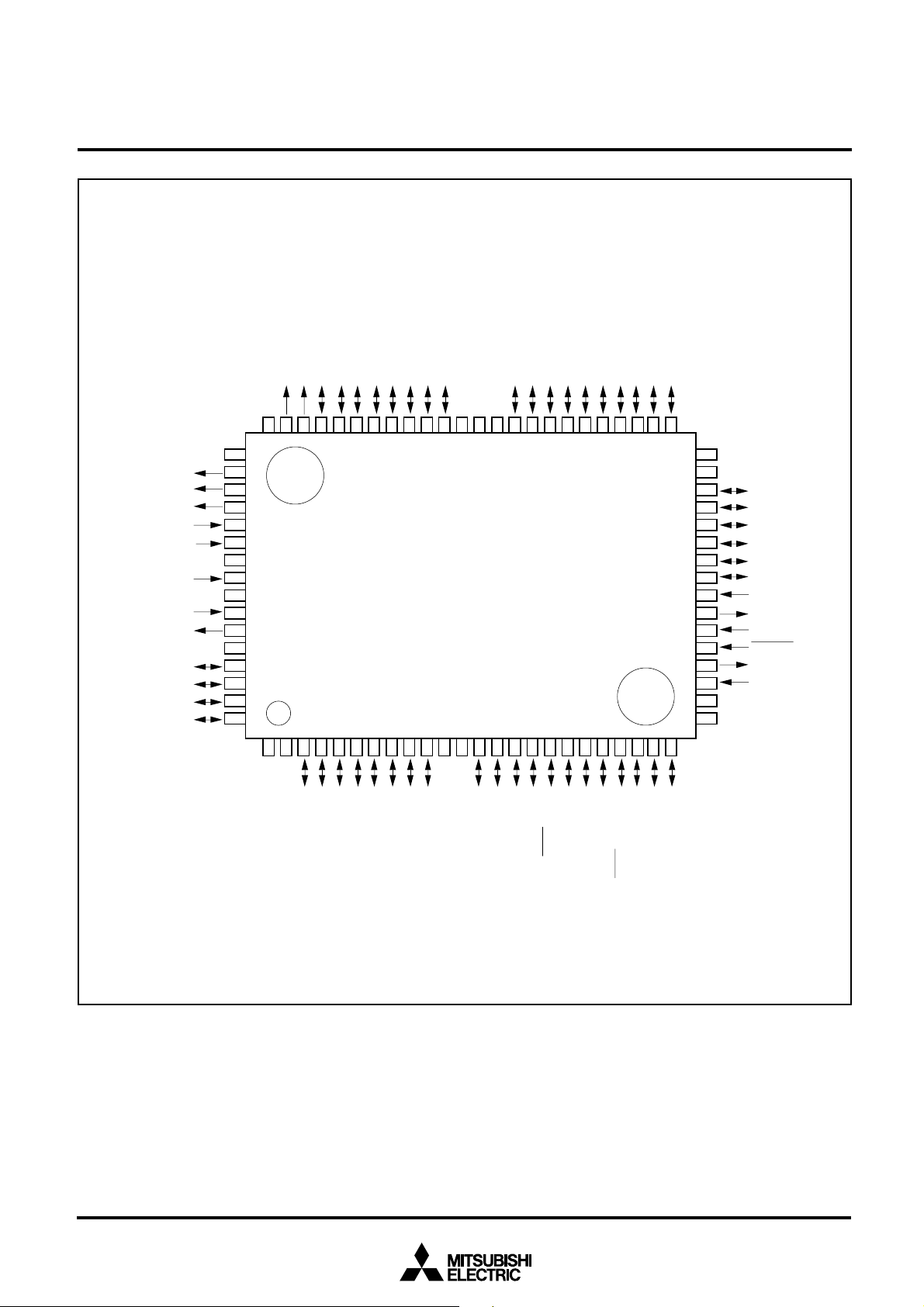

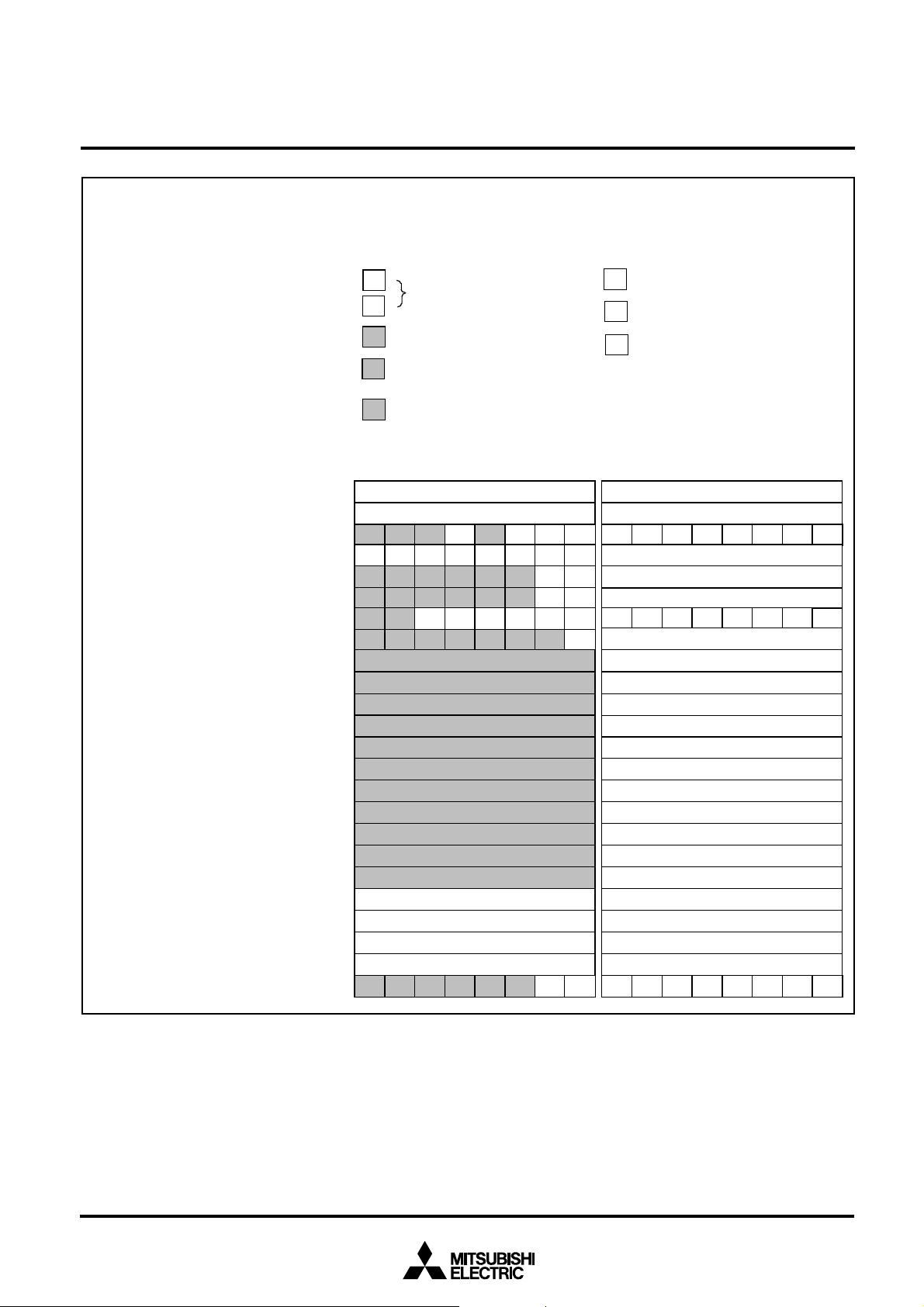

PIN CONFIGURATION (TOP VIEW)

6

/TIM1 OVERFLOW

5

0

1

P0

I/P5

OUT/P5

NC

B/P5

G/P5

R/P5

V

SYNC

H

SYNC

NC

V

NC

OSC1/P70/AD4

OSC2/P7

1

/AD5

NC

6

/INT2/AD2

P3

5

/AD1

P3

P3

4

/INT1

D-A/AD3

CC

NC

63

64

65

4

66

67

3

68

2

69

70

71

72

73

74

75

76

77

78

79

80

2

1

P0

62

60

61

4

5

3

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

4

P0

57

8

56

9

5

P0

6

7

NC

P0

P0

55

53

54

12

10

11

NC

52

13

NC

51

14

0

1

P1

P1

50

49

151617

2

P1

48

3

P1

47

18

4

P1

46

19

5

P1

45

20

6

P1

44

21

7

P1

43

22

42

23

0

P2

41

24

1

P2

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

NC

NC

P2

2

P2

3

P2

4

P2

5

P2

6

P2

7

V

SS

OUT

X

X

IN

RESET

φ

CNV

SS

NC

NC

3

2

P0

P0

59

58

M37207MF-XXXFP, M37207EFFP

7

6

NC

NC

/PWM0

/PWM1

0

1

P6

P6

/PWM2

/PWM3

2

3

P6

P6

NC

NC

/PWM6

/PWM4

4

P6

/PWM5

6

5

P6

P6

/PWM7

7

P6

Outline 80P6N-A

/TIM3

3

P3

/TIM2/AD6

2

P3

1

P3

0

P3

/PWM9

IN1

/S

6

/SRDY1/PWM8

7

P4

P4

/SCL1

/SDA1

CLK1

OUT1

/S

/S

5

4

P4

P4

COUT

/SDA2/AD8

/SCL3/X

IN2

/S

/SRDY2/SCL2/AD7

2

CLK2

3

/S

P4

1

P4

P4

CIN

/SDA3/X

OUT2

P4φ/S

NC: Unconnected

3

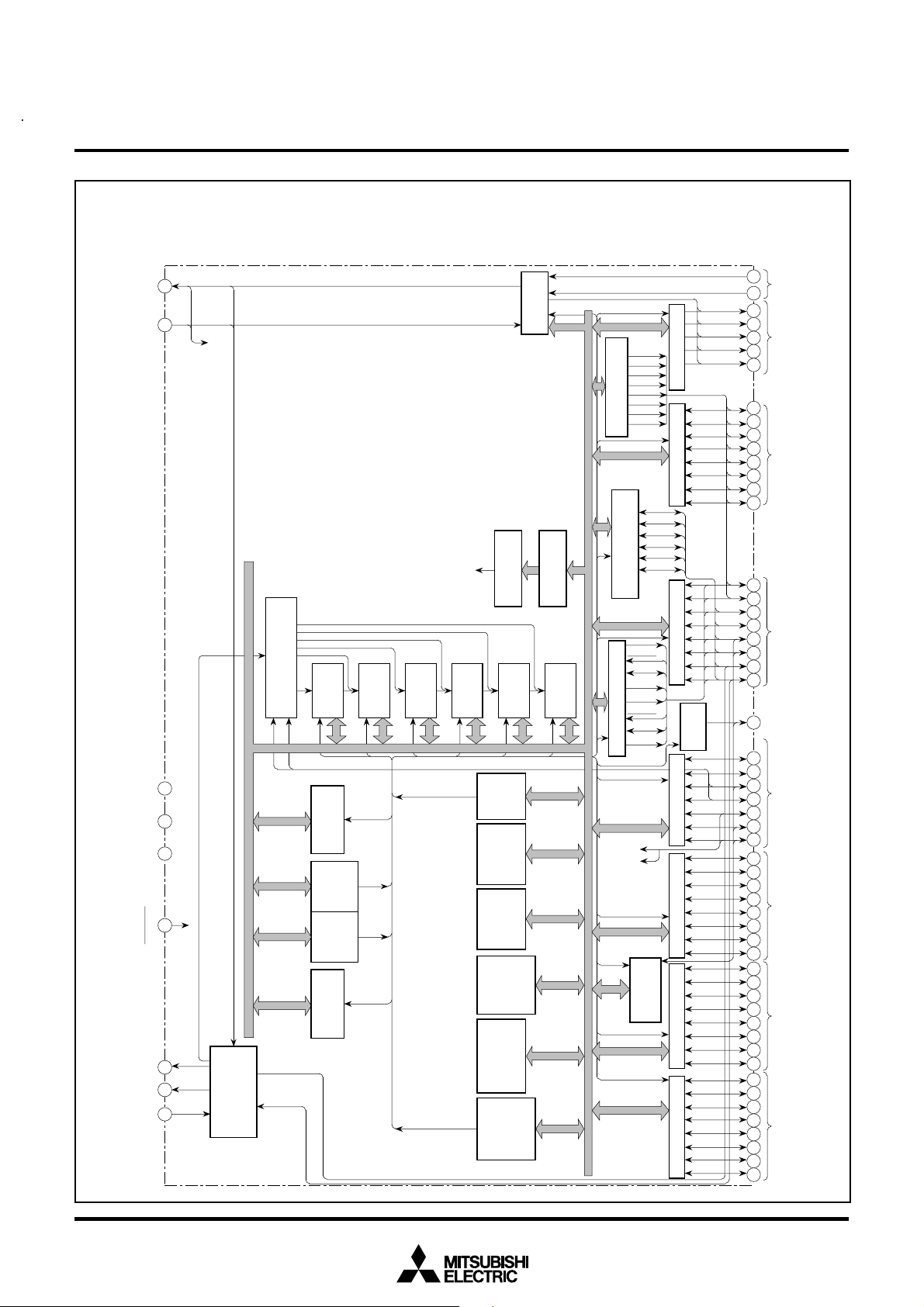

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

1

, P7

0

Input ports P7

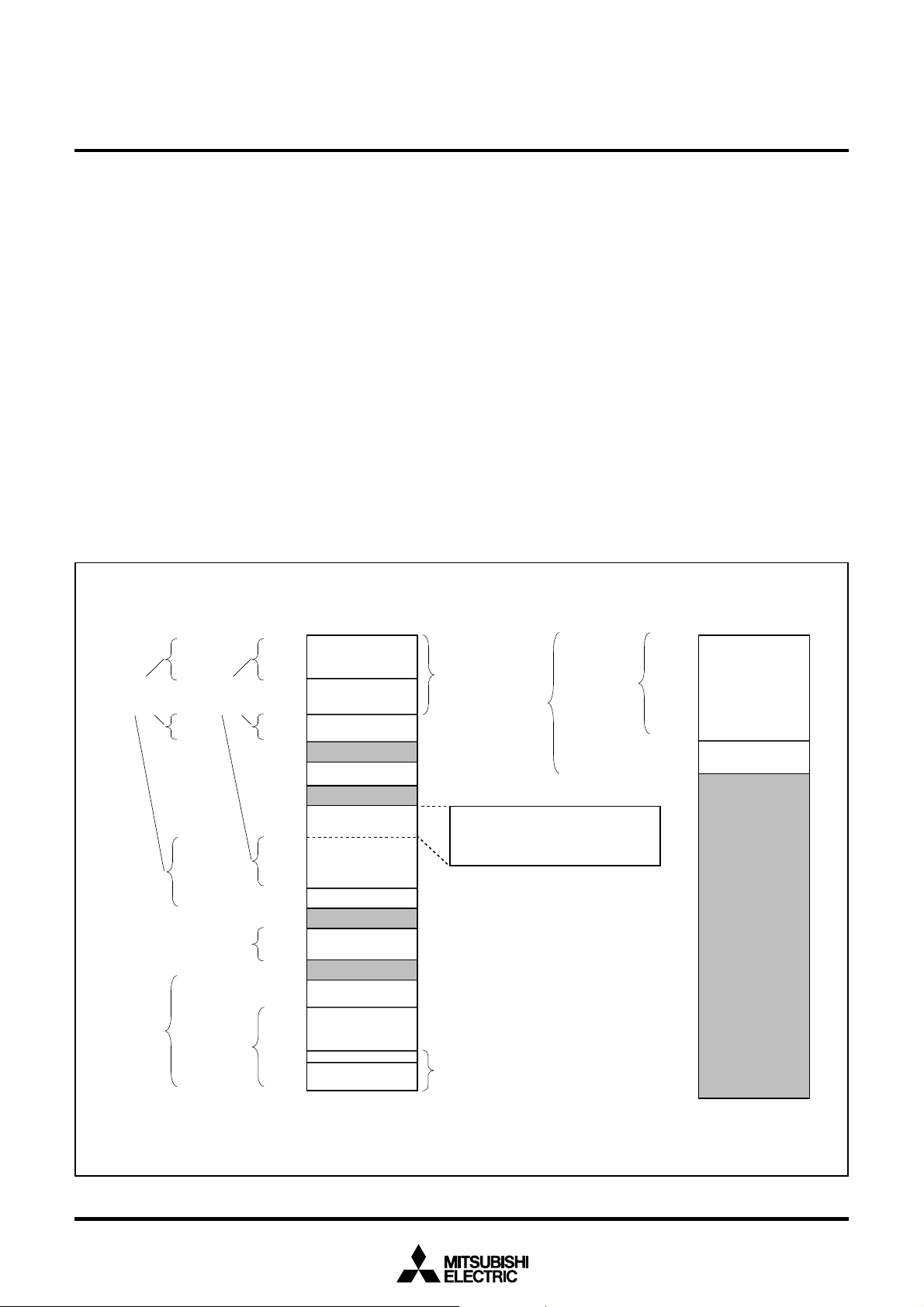

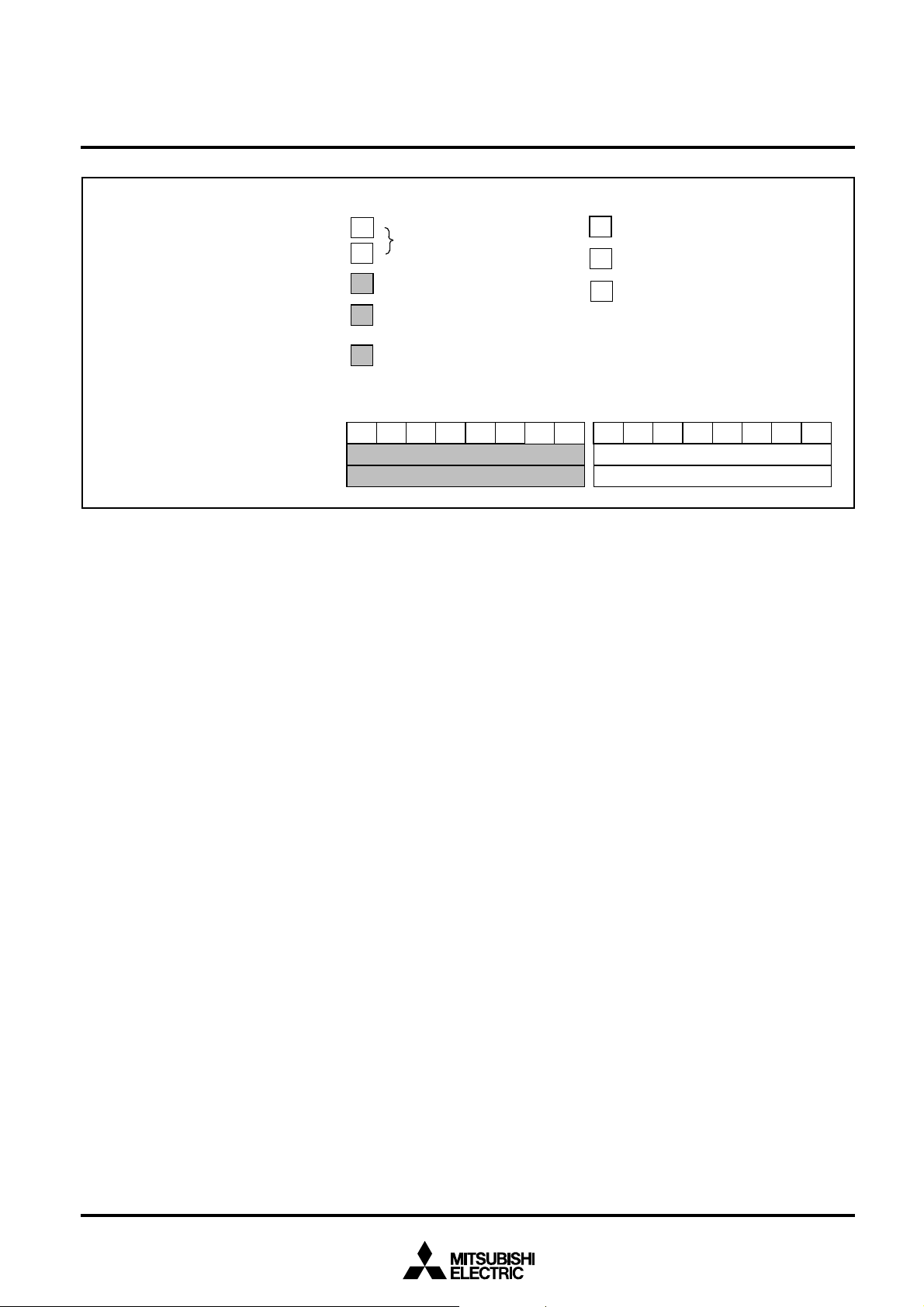

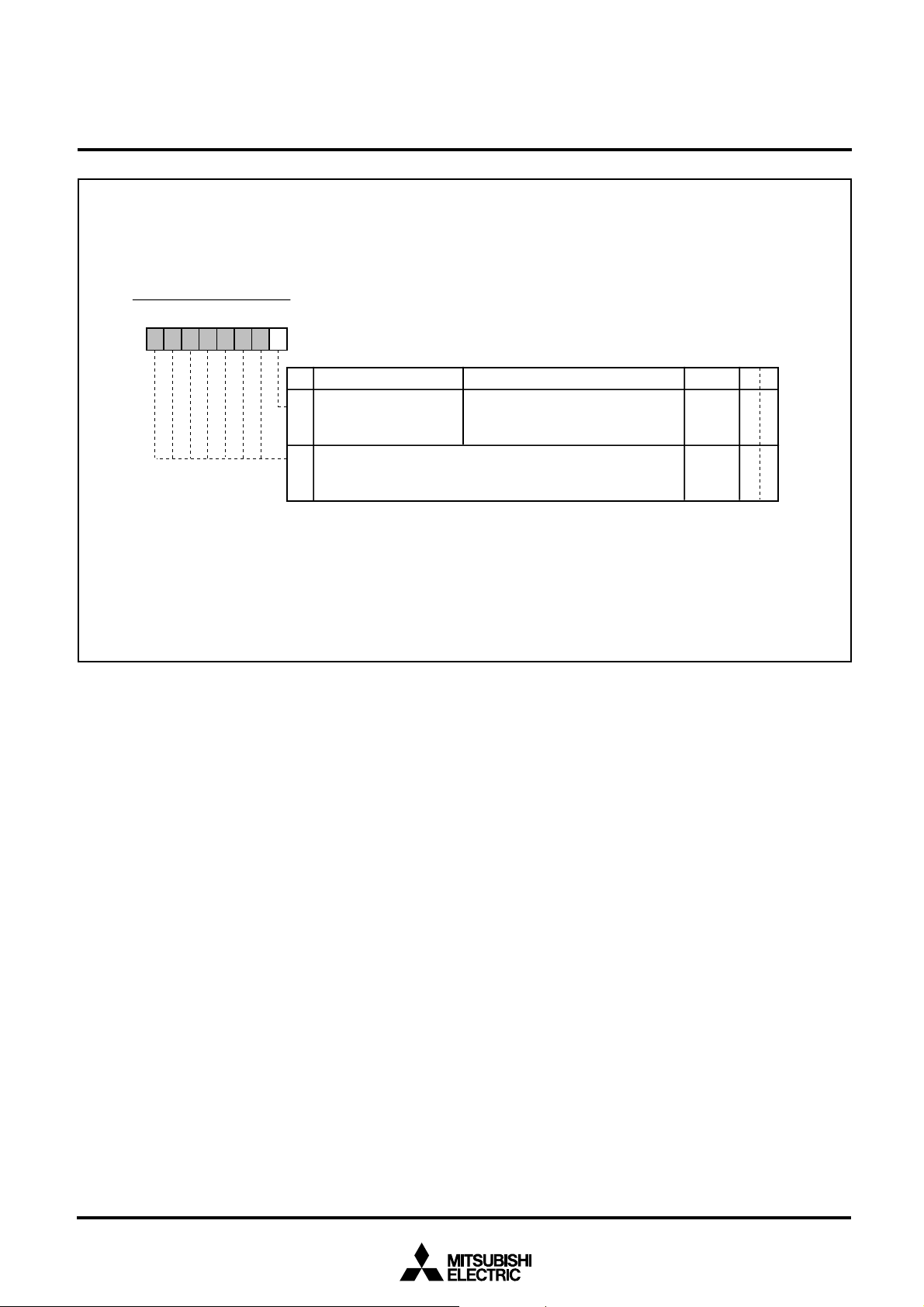

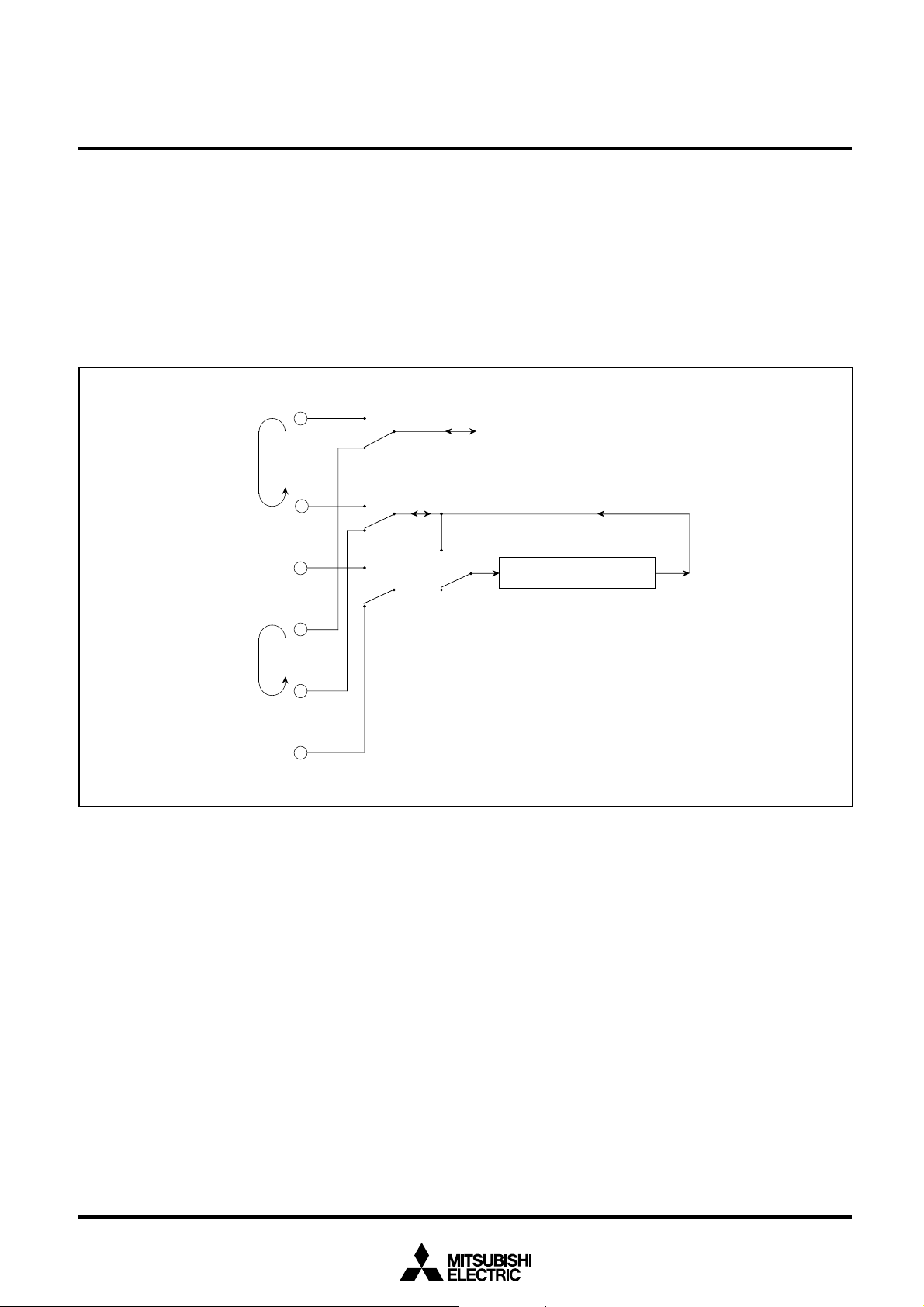

FUNCTIONAL BLOCK DIAGRAM of M37207M8-XXXSP

2

OSC2

Clock output for CRT/

Sub-clock output

1

OSC1

Sub-clock input

Clock input for CRT/

SS

27

CNV

SS

32

V

CC

64

V

29

RESET

Reset input

Timing output

φ

28

OUT

31

X

Clock

output

IN

30

X

input

Clock

A-D comparator

Timer count source

TIM2

Data bus

Clock

circuit

generating

selection circuit

T1 (8)

Timer 1

TIM3

ROM

64 K bytes

(Note 2)

counter

Program

counter

Program

RAM

960 bytes

(Note 1)

COUT

X

CIN

X

(8)

L

PC

(8)

H

PC

T2 (8)

Timer 2

Address bus

T3 (8)

Timer 3

Instruction

Control signal

T4 (8)

Timer 4

Stack

pointer

Index

register

Index

register

status

processor

A (8)

Accumulator

8-bit

arithmetic

decoder

Timer 5

S (8)

Y (8)

X (8)

register

and

CRT circuit

instruction

T5 (8)

PS (8)

logical unit

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

H

SYNC

63

V

SYNC

62

input

Sync

61

60

59

58

57

Output ports

7

87

–P6

0

9

10

11

12

I/O ports P6

13

14

19

20

7

21

–P4

0

22

24 23

25

26

I/O ports P4

6

D-A

18

17

16

15

5

I/O ports

34

40

39

38

37

I/O ports

35 36

34

33

48

47

46

45

44

I/O ports

43

42

41

56

55

54

53

52

I/O ports

51

50

49

6

–P5

2

P5

6

–P3

0

P3

7

–P2

0

P2

7

–P1

0

P1

7

–P0

0

P0

register (8)

T6 (8)

Timer 6

PWM0

P5 (5)

PWM1

PWM2

PWM3

PWM4

PWM5

PWM6

PWM7

8-bit PWM circuit

P6 (8)

SCL1

SDA1

SCL2

SDA2

SCL3

SDA3

C-BUS Interface

2

Multi-master

I

S

RDY1

P4 (8)

S

IN1

S

CLK1

S

OUT1

S

RDY2

SI/O (8)

S

IN2

S

CLK2

S

OUT2

P3 (7)

INT2

INT1

P2 (8)

A-D

comparator

P1 (8)

P0(8)

14-bit

PWM circuit

R

G

B

I

OUT

Note 1: M37207M8-XXXSP has a 512 bytes RAM.

Note 2: M37207M8-XXXSP has a 32 K bytes ROM.

4

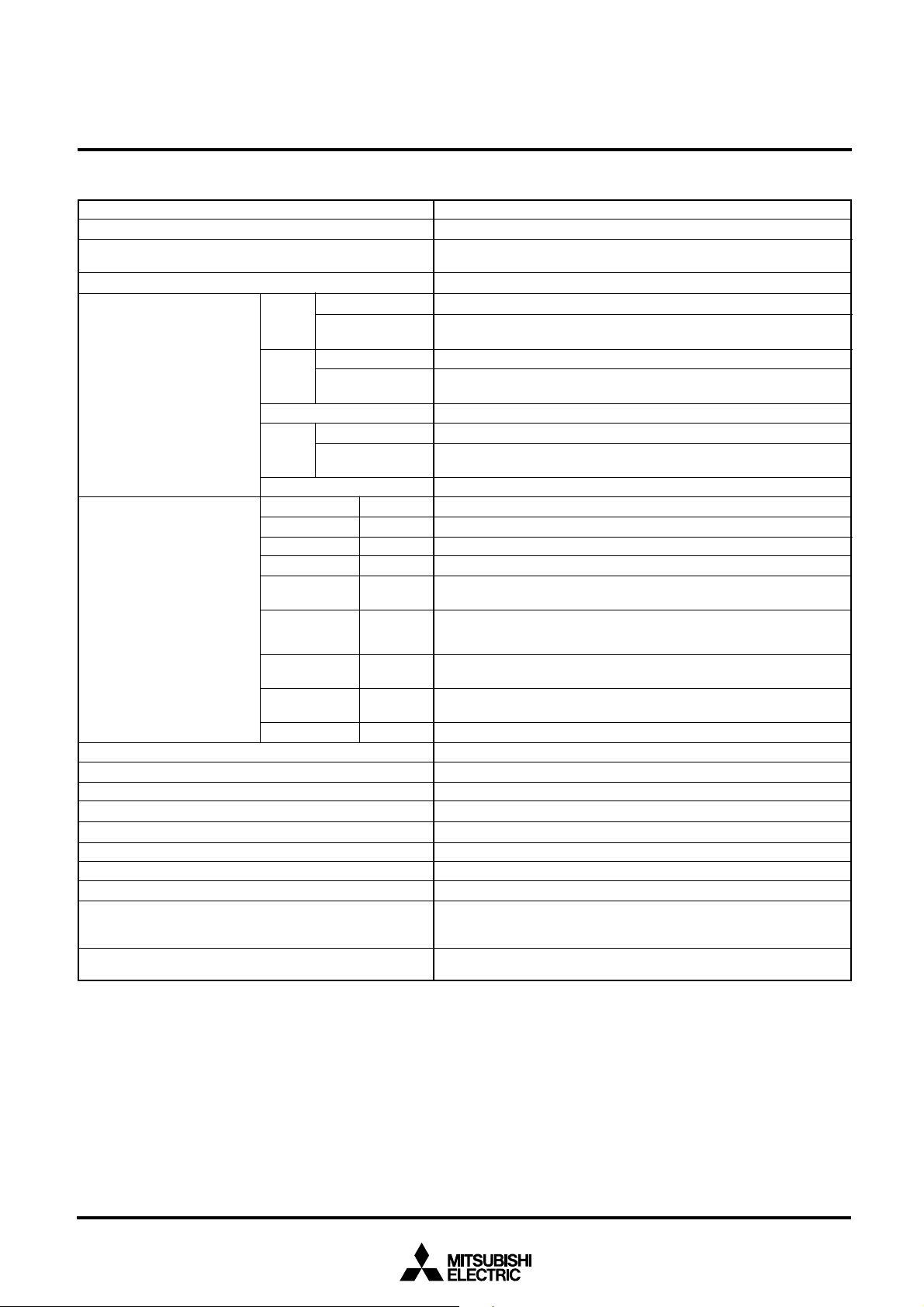

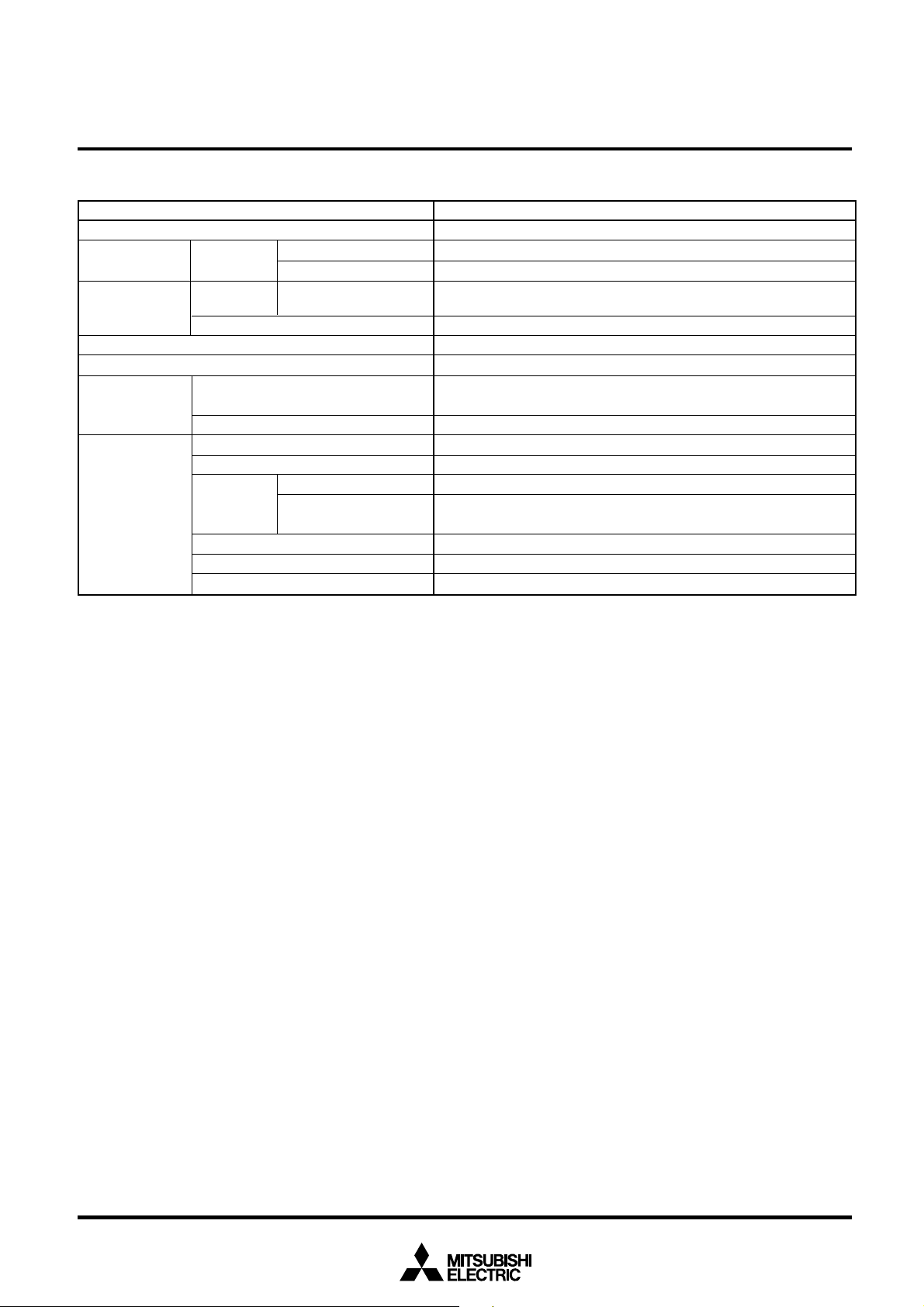

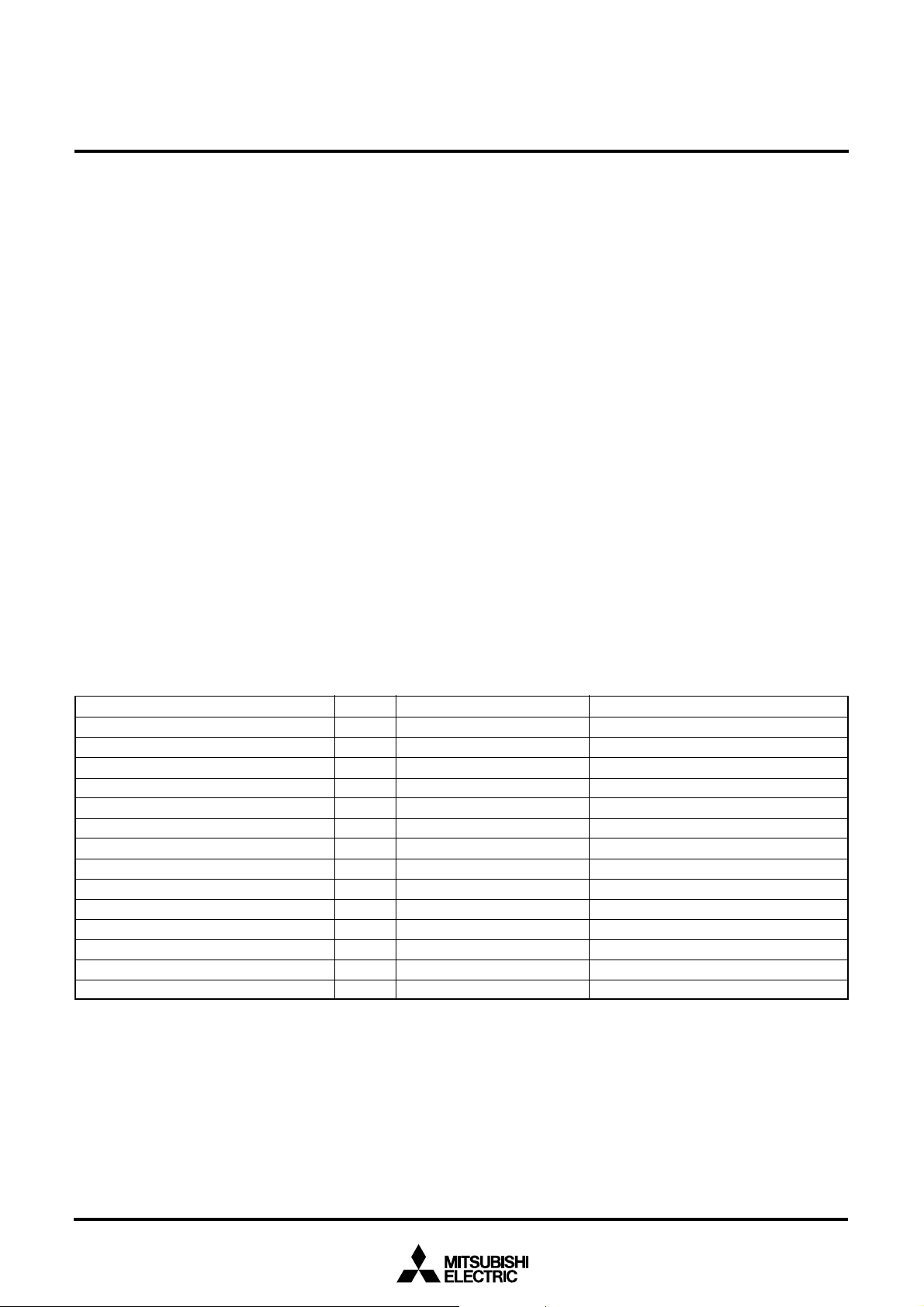

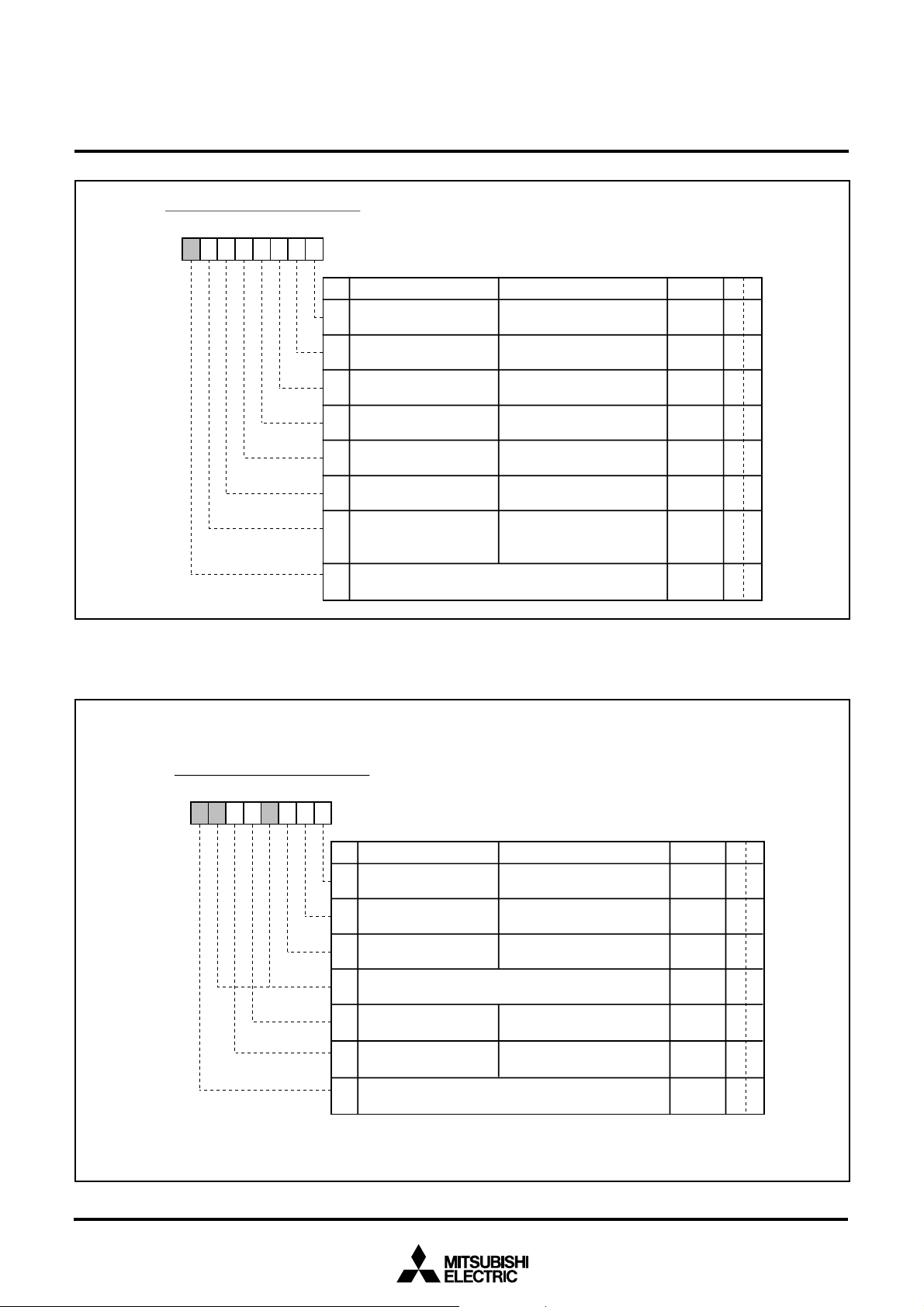

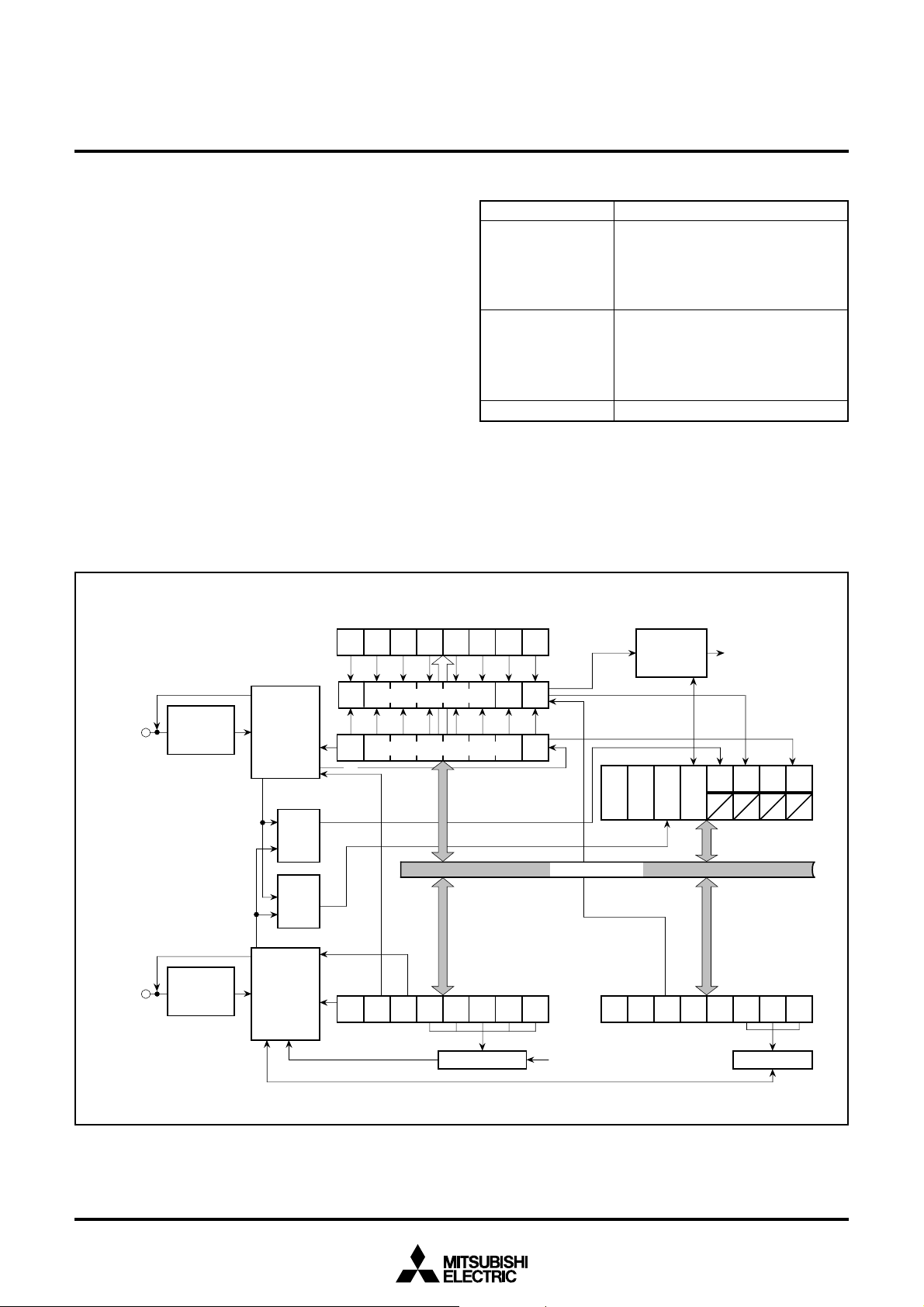

FUNCTIONS

Parameter

Number of basic instructions

Instruction execution time

Clock frequency

Memory size

Input/Output ports

Serial I/O

Multi-master I2C-BUS interface

A-D comparator

PWM output circuit

Timers

ROM correction function

Subroutine nesting

Interrupt interval determination circuit

Interrupt

Clock generating circuit

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

ROM

RAM

ROM correction memory

CRT ROM

CRT RAM

P00–P07

P10–P17

P20–P27

P30, P31

P32–P36

P40–P47

P52–P56

P60–P67

P70, P70

M37207M8-XXXSP

M37207MF-XXXSP/FP

M37207EFSP/FP

M37207M8-XXXSP

M37207MF-XXXSP/FP

M37207EFSP/FP

M37207M8-XXXSP

M37207MF-XXXSP/FP

M37207EFSP/FP

I/O

I/O

I/O

I/O

I/O

I/O

Output

I/O

Input

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

Functions

71

0.5 ms (the minimum instruction execution time, at 8 MHz oscillation frequency)

8 MHz (maximum)

32 K bytes

,

64 K bytes

512 bytes

960 bytes

,

64 bytes

8K bytes

,

12K bytes

144 bytes

8-bit ✕ 1 (CMOS input/output structure)

8-bit ✕ 1 (CMOS input/output structure)

8-bit ✕ 1 (CMOS input/output structure)

2-bit ✕ 1 (CMOS input/output structure)

5-bit ✕ 1 (N-channel open-drain output structure, can be used as external

clock input pins, A-D input pins, INT input pins)

8-bit ✕ 1 (N-channel open-drain output structure, can be used as serial I/O

pins, A-D input pins, PWM output pins, multi-master I2C-BUS interface,

sub-clock I/O pins)

5-bit ✕ 1 (CMOS output structure, can be used as CRT output pins, an

external clock output pin)

8-bit ✕ 1 (N-channel open-drain output structure, can be used as PWM

output)

2-bit ✕ 1 (can be used as CRT display clock I/O pins, analog input pins)

8-bit ✕ 1 (2 systems)

1 (3 systems)

8 channels (6-bit resolution)

14-bit ✕ 1, 8-bit ✕ 10

8-bit timer ✕ 6

32 bytes ✕ 2

128 levels (maximum)

1

External interrupt ✕ 2, Internal timer interrupt ✕ 6, Serial I/O interrupt ✕ 1,

CRT interrupt ✕ 1, Multi-master I2C-BUS interface interrupt ✕ 1,

f(XIN)/4096 interrupt ✕ 1, VSYNC interrupt ✕ 1, BRK interrupt ✕ 1

2 built-in circuits (externally connected to a ceramic resonator or a quartzcrystal oscillator)

5

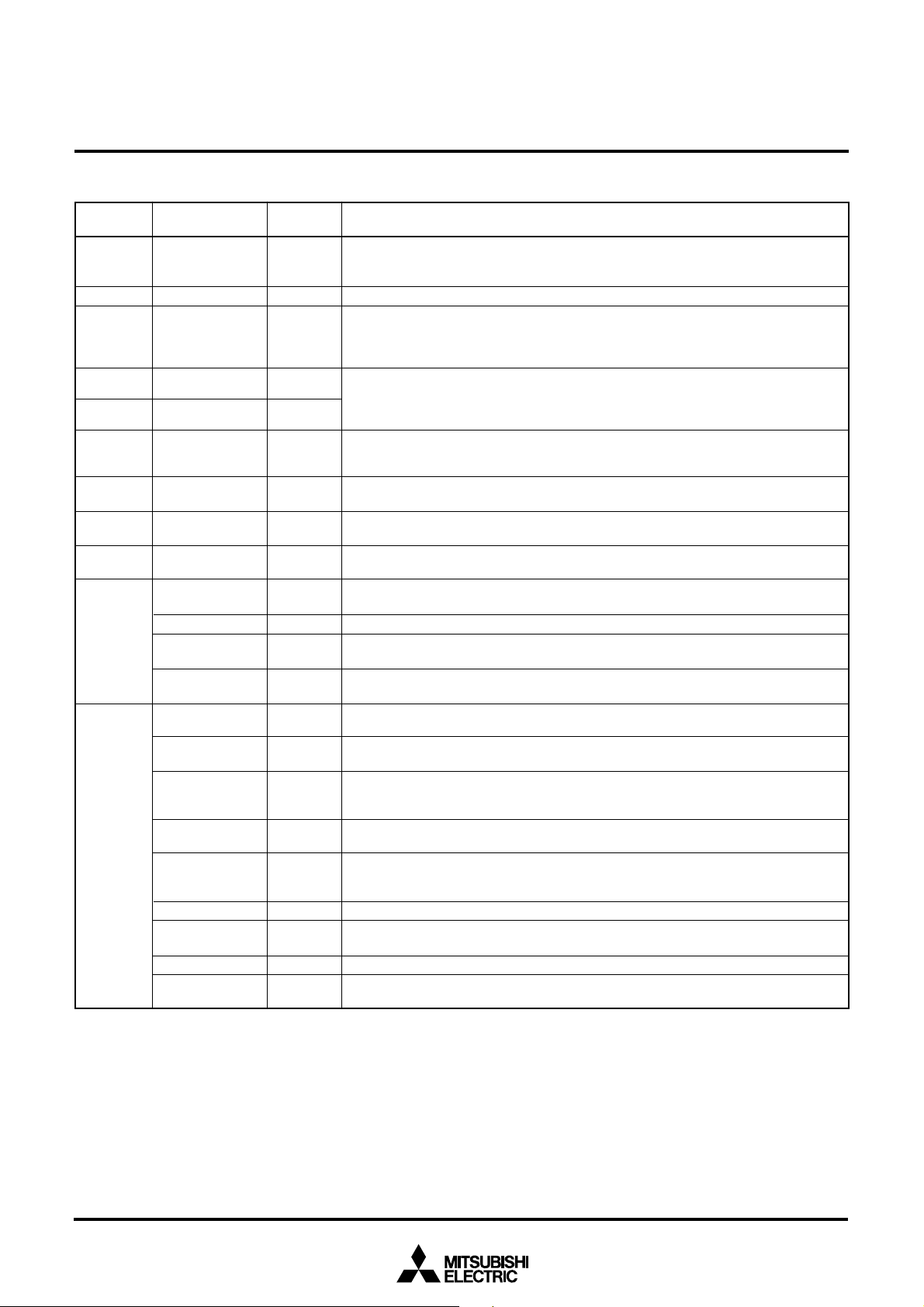

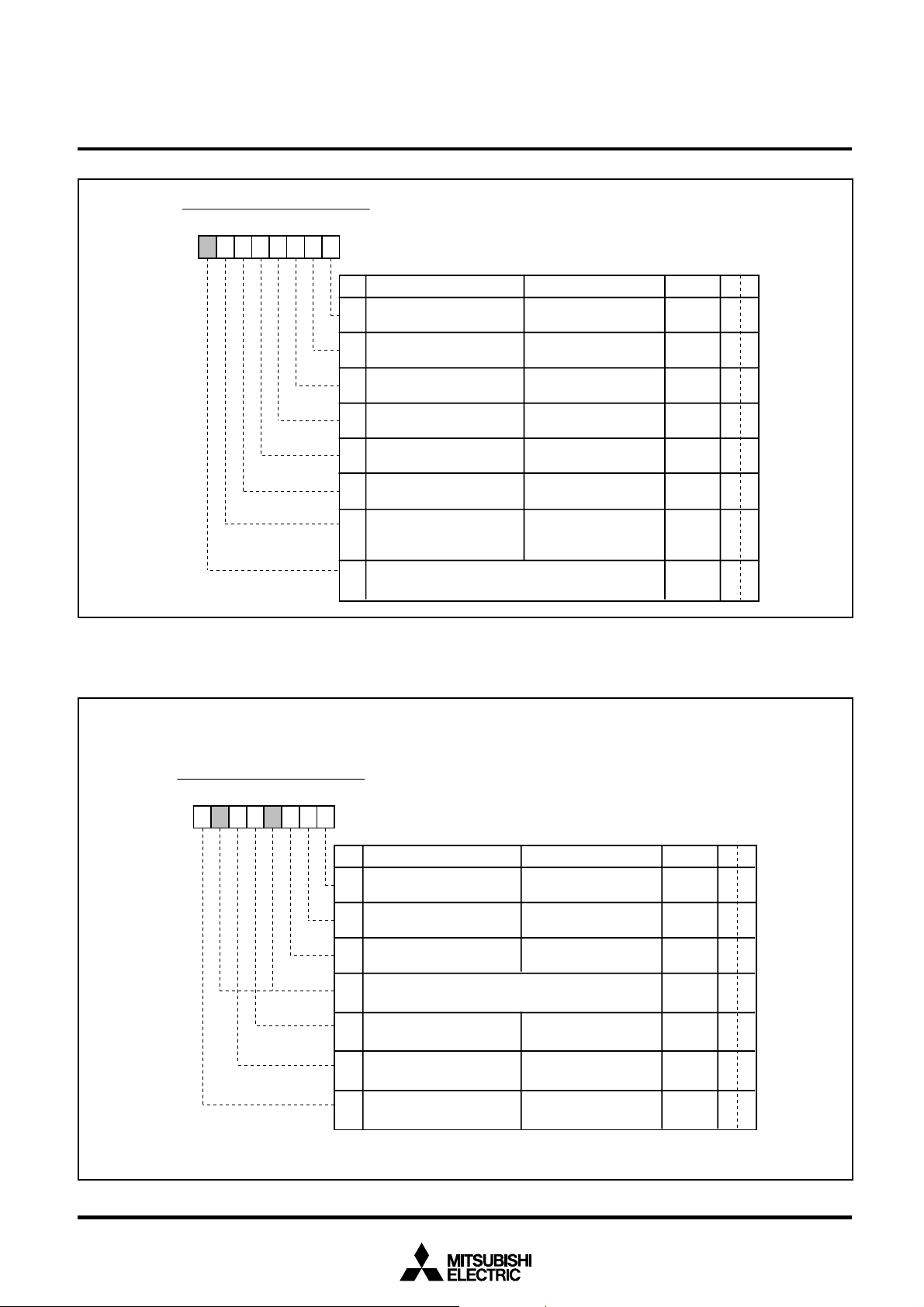

FUNCTIONS (continued)

Parameter

Power source voltage

Power dissipation

Operating temperature range

Device structure

Package

CRT display

function

In high-speed

mode

In low-speed

mode

In stop mode

M37207MF-XXXSP, M37207M8-XXXSP

M37207EFSP

M37207MF-XXXFP, M37207EFFP

Number of display characters

Character display area

Kinds of

characters

Kinds of character sizes

Kinds of character colors

Display position (horizontal, vertical)

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

CRT ON

CRT OFF

CRT OFF

M37207M8-XXXSP

M37207MF-XXXSP/FP,

M37207EFSP/FP

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

Functions

5 V ± 10 %

165 mW typ. (at oscillation frequency f(XIN) = 8 MHz, fOSC = 8 MHz)

82.5 mW typ. (at oscillation frequency f(XIN) = 8 MHz)

0.33 mW typ. (at oscillation frequency fCLK = 32 kHz, f(XIN) = stopped)

1.1 mW (maximum)

–10 °C to 70 °C

CMOS silicon gate process

64-pin shrink plastic molded DIP

80-pin plastic molded QFP

24 characters ✕ 3 lines (maximum 16 lines by software)

12 ✕ 16 dots

256 Kinds

384 Kinds

4 kinds

Maximum 15 kinds (R, G, B, I); can be specified by the character

64 levels (horizontal) ✕ 128 levels (vertical)

6

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

PIN DESCRIPTION

Pin Functions

VCC, VSS

Name

Power source

Input/

Output

Apply voltage of 5 V ± 10 % (typical) to VCC and AVCC, and 0 V to VSS.

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

CNVSS

______

RESET

XIN

XOUT

P00–P07

P10–P17

P20–P27

P30, P31

P32/TIM2/

AD6,

P33/TIM3,

P34/INT1,

P35/AD1,

P36/INT2/

AD2

P40/SOUT2/

SDA3/XCIN,

P41/SCLK2/

SCL3/

XCOUT, P42/

SIN2/SDA2/

AD8,

_____

P43/SRDY2/

SCL2/AD7,

P44/SOUT1/

SDA1,

P45/SCLK1/

SCL1,

P46/SIN1/

PWM9,

_____

P47/SRDY1/

PWM8

CNVSS

Reset input

Clock input

Clock output

I/O port P0

I/O port P1

I/O port P2

I/O port P3

I/O port P3

Analog input

External clock

input

External interrupt

input

I/O port P4

Serial I/O data

input/output

Serial I/O synchronous clock input/

output

Serial I/O receive

enable signal output

Multi-master I2CBUS interface

Sub-clock input

Sub-clock output

Analog input

PWM output

Input

Input

Output

I/O

I/O

I/O

I/O

I/O

Input

Input

Input

I/O

I/O

I/O

Output

I/O

Input

Output

Input

Output

Connected to VSS.

To enter the reset state, the reset input pin must be kept at a “L” for 2 ms or more (under

normal VCC conditions).

If more time is needed for the quartz-crystal oscillator to stabilize, this “L” condition should

be maintained for the required time.

This chip has an internal clock generating circuit. To control generating frequency, an

external ceramic resonator or a quartz-crystal oscillator is connected between pins XIN and

XOUT. If an external clock is used, the clock source should be connected to the XIN pin and

the XOUT pin should be left open.

Port P0 is an 8-bit I/O port with direction register allowing each I/O bit to be individually

programmed as input or output. At reset, this port is set to input mode. The output structure

is CMOS output. See notes at end of table for full details of port P0 functions.

Port P1 is an 8-bit I/O port and has basically the same functions as port P0. The output

structure is CMOS output.

Port P2 is an 8-bit I/O port and has basically the same functions as port P0. The output

structure is CMOS output.

Ports P30, P31 are 2-bit I/O ports and have basically the same functions as port P0. The

output structure is CMOS output.

Ports P32–P36 are 5-bit I/O ports and have basically the same functions as port P0. The

output structure is N-channel open-drain output.

Pins P32, P35, P36 are also used as analog input pins AD6, AD1 and AD2 respectively.

Pins P32, P33 are also used as external clock input pins TIM2, TIM3 respectively.

Pins P34, P36 are also used as external interrupt input pins INT1, INT2.

Port P4 is an 8-bit I/O port and has basically the same functions as port P0. The output

structure is N-channel open-drain output.

Pins P40, P42, P44, P46 are also used as serial I/O data input/output pins SOUT2, SIN2,

SOUT1, SIN1 respectively. The output structure is N-channel open-drain output.

Pins P41, P45 are also used as serial I/O synchronous clock input/output pins SCLK2, SCLK1

respectively.

Pins P43, P47 are also used as serial I/O receive enable signal output pins SRDY2, SRDY1

respectively. The output structure is N-channel open-drain output.

Pins P40–P45 are also used as SDA3, SCL3, SDA2, SCL2, SDA1, SCL1 respectively

when multi-master I2C-BUS interface is used. The output structure is N-channel opendrain output.

Pin P40 is also used as sub-clock input pin XCIN.

Pin P41 is also used as sub-clock output pin XCOUT. The output structure is N-channel

open-drain output.

Pins P42, P43 are also used as analog input pins AD8, AD7 respectively.

Pins P46, P47 are also used as PWM output pins PWM9, PWM8 respectively. The output

structure is N-channel open-drain output.

_____ _____

7

PIN DESCRIPTION (continued)

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

Pin Name

R/P52,

G/P53,

B/P54,

I/P55/TIM1

OVERFLOW,

OUT/P56

P60/PWM–

P67/PWM7

OSC1/P70/

AD4,

OSC2/P71/

AD5

HSYNC

VSYNC

f

D-A/AD3

Note : As shown in the memory map (Figure 5), port P0 is accessed as a memory at address 00C016 of zero page. Port P0 has the port P0

direction register (address 00C116 of zero page) which can be used to program each bit as an input (“0”) or an output (“1”). The pins

programmed as “1” in the direction register are output pins. When pins are programmed as “0,” they are input pins. When pins are

programmed as output pins, the output data are written into the port latch and then output. When data is read from the output pins, the

output pin level is not read but the data of the port latch is read. This allows a previously-output value to be read correctly even if the

output “L” voltage has risen, for example, because a light emitting diode was directly driven. The input pins float, so the values of the pins

can be read. When data is written into the input pin, it is written only into the port latch, while the pin remains in the floating state.

Output port

P5

CRT output

Timer 1 overflow

signal output

I/O port P6

PWM output

Input port P7

Clock input

for CRT

display

Clock output

for CRT

display

Analog input

HSYNC input

VSYNC input

Timing

output

DA output

Analog input

Input/

Output

Output

Output

Output

I/O

Output

Input

Input

Output

Input

Input

Input

Output

Output

Input

Ports P52–P56 are 5-bit output ports. The output structure is CMOS output.

Pins P52–P56 are also used as CRT output pins R, G, B, I, OUT respectively. The output structure

is CMOS output.

Pin P55 is also used as timer 1 overflow signal output pin TIM1 OVERFLOW. The output structure is

CMOS output.

Port P6 is an 8-bit I/O port and has basically the same functions as port P0. The output structure is

N-channel open-drain output.

Pins P60–P67 are also used as PWM output pins PWM0–PWM7. The output structure is CMOS

output.

Ports P70, P71 are 2-bit input port.

Pin P70 is also used as CRT display clock input pin OSC1.

Pin P71 is also used as CRT display clock output pin OSC2. The output structure is CMOS output.

Pins P70, P71 are also used as analog input pins AD4, AD5 respectively.

This is a horizontal synchronous signal input for CRT display.

This is a vertical synchronous signal input for CRT display.

This is a timing output pin. This pin has reset-out output function. The output structure is CMOS

output.

This is an output pin for 14-bit PWM.

The D-A pin is also used as analog input pin AD3.

Functions

8

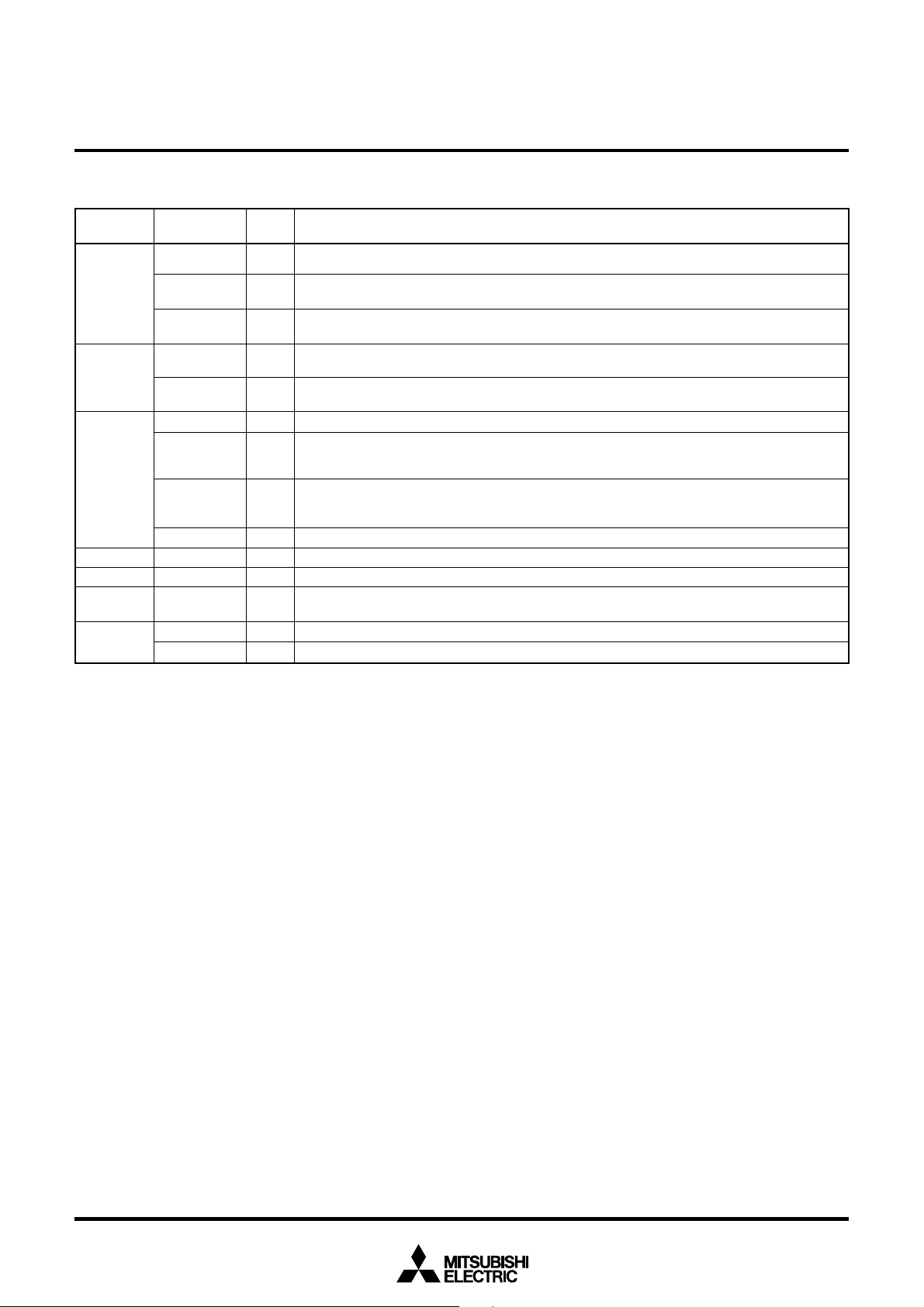

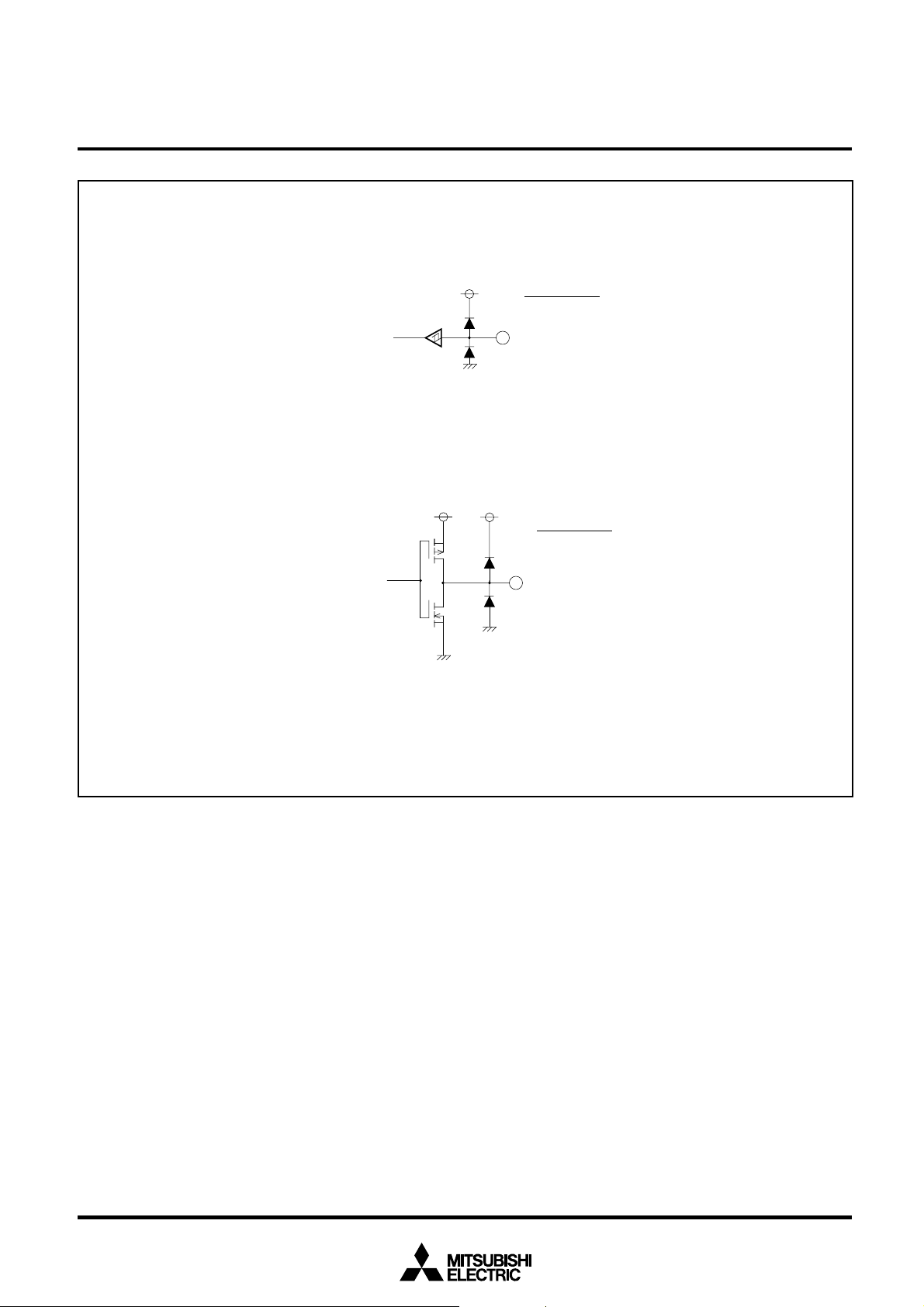

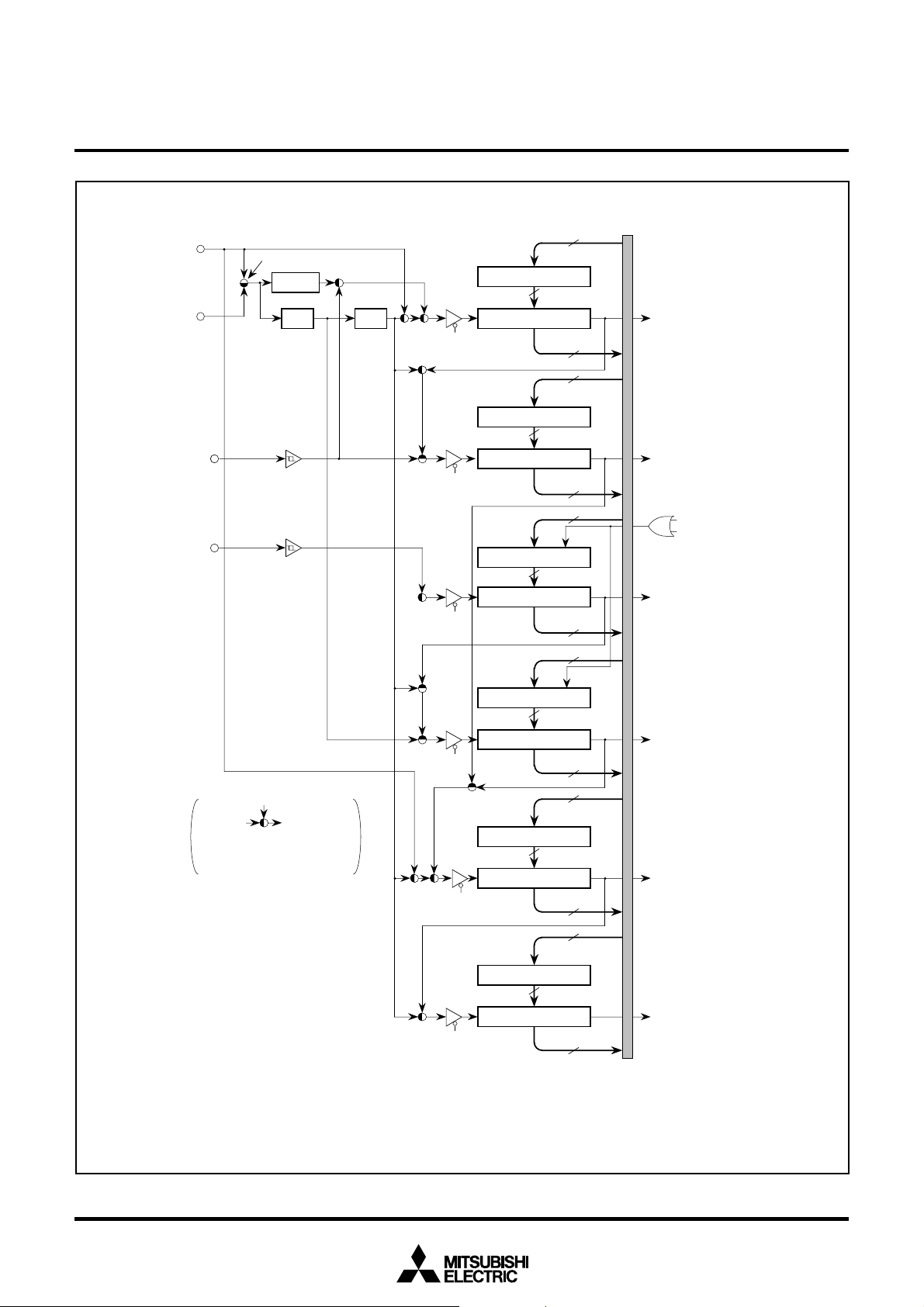

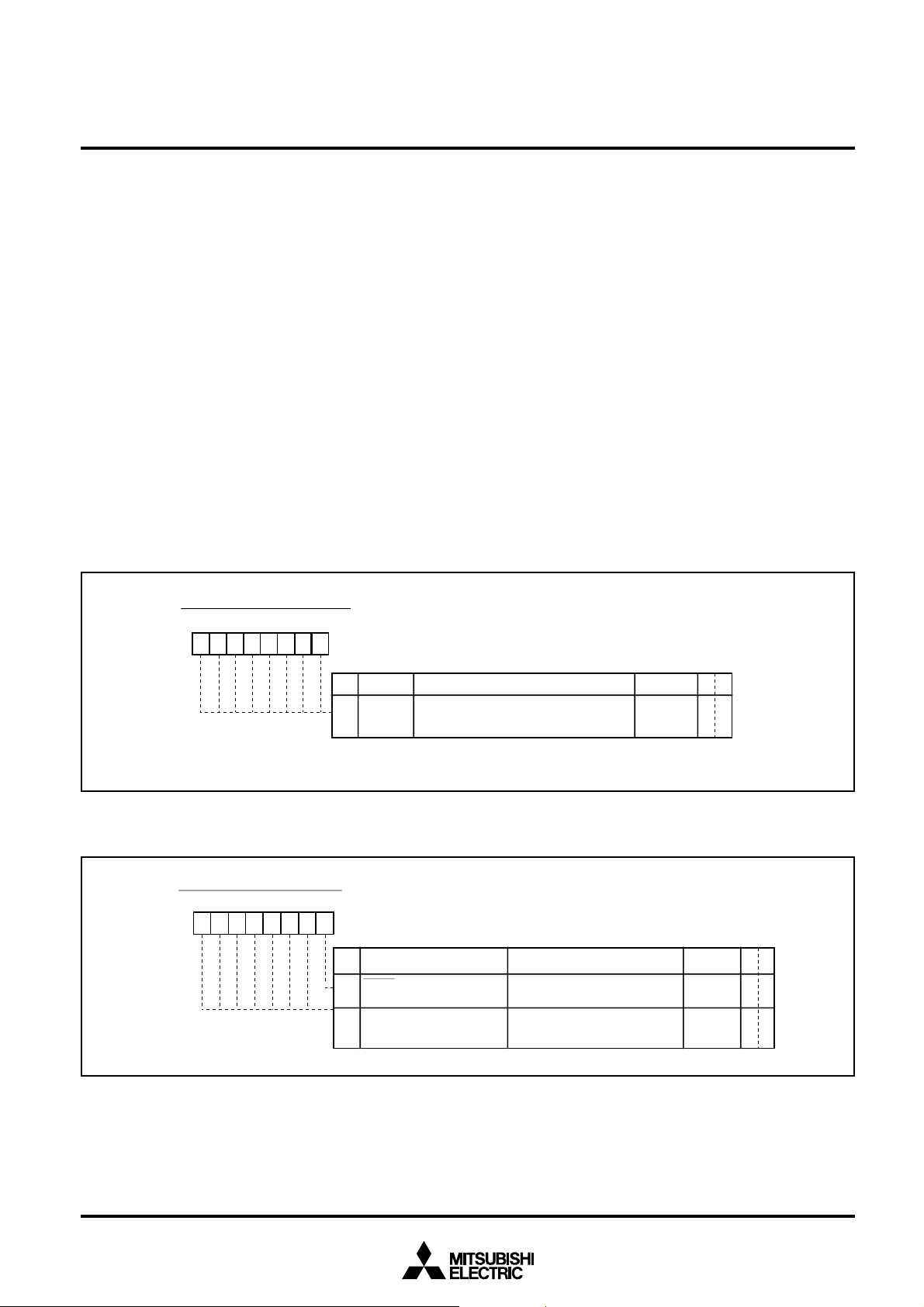

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

Ports P00–P07, P10–P17, P20–P27, P30, P31, D-A

Direction register

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

CMOS output

Data bus

Ports P4

6, P47, P60–P67

Data bus

Ports P32–P36, P42–P45

Port latch

Direction register

Port latch

Direction register

Ports P00–P07, P10–P17,

P20–P27, P30, P31, D-A

Note : D-A pin is also used as

AD3.

N-channel open-drain output

Ports P46, P47, P60–P67

Note : Each port is also used as

follows:

P46 : SIN1/PWM9

_____

P47 : SRDY1/PWM8

P60–P67 : PWM0–PWM7

N-channel open-drain output

Data bus

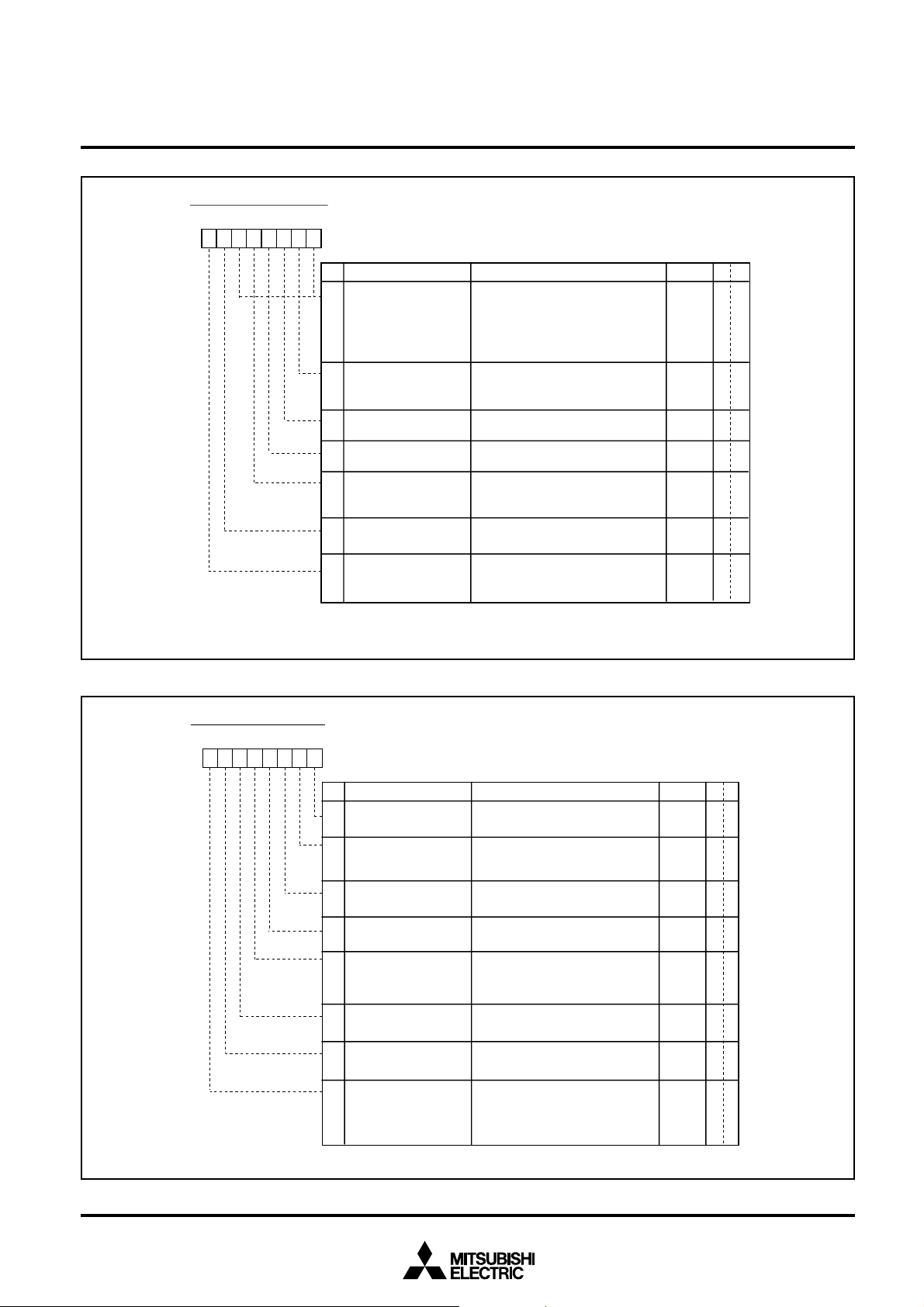

Fig. 1. I/O Pin Block Diagram (1)

Port latch

Ports P32–P36, P42–P45

Note : Each port is also used as

follows:

P32 : TIM2/AD6

P33 : TIM3

P34 : INT1

P35 : AD1

P36 : INT2/AD2

P42 : SIN2/SDA2/AD8

_____

P43 : SRDY2/SCL2/AD7

P44 : SOUT1/SDA1

P45 : SCLK1/SCL1

9

SYNC, VSYNC

H

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

Schmidt input

Internal circuit

R, G, B, I, OUT,

P52–P55, φ

Internal circuit

HSYNC, VSYNC

CMOS output

P52–P55, φ

Note : Each port is also used as follows:

P52 : R

P53 : G

P54 : B

P55 : I/TIM1

P56 : OUT

Fig. 2. I/O Pin Block Diagram (2)

10

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

FUNCTIONAL DESCRIPTION

Central Processing Unit (CPU)

This microcomputer uses the standard 740 Family instruction set.

Refer to the table of 740 Family addressing modes and machine

instructions or the SERIES 740 <Software> User’s Manual for details on the instruction set.

Machine-resident 740 Family instructions are as follows:

The FST, SLW instruction cannot be used.

The MUL, DIV, WIT and STP instructions can be used.

CPU Mode Register

b7b6 b5b4b3 b2b1b0

1

00

CPU mode register (CPUM) (CM) [Address 00FB16]

B

0, 1

Name Functions

Processor mode bits

(CM0, CM1)

Stack page selection

2

bit (CM2) (See note 1)

CPU Mode Register

The CPU mode register contains the stack page selection bit and

internal system clock selection bit. The CPU mode register is allocated at address 00FB16.

After reset

b1 b0

0 0: Single-chip mode

0 1:

1 0: Not available

1 1:

0: 0 page

1: 1 page

RW

RW

0

RW

1

Fig. 3. CPU Mode Register

3

Fix these bits to “1.”

Internal system clock

41

output selection bit

(CM4) (See note 2)

X

COUT

51

drivability

selection bit (CM5)

Main Clock (X

60

IN–XOUT

stop bit

(CM6)

Internal system clock

70

selection bit

(CM7)

0: Output is stopped

1: Internal system

clock

φ

output

0: LOW drive

1: HIGH drive

)

0: Oscillating

1: Stopped

0: X

IN–XOUT

selected

(high-speed mode)

1: X

CIN–XCOUT

selected

RW

1

RW

RW

RW

RW

(high-speed mode)

Notes 1: This bit is set to “1” after the reset release.

φ

2: The internal system clock

stops at HIGH.

11

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

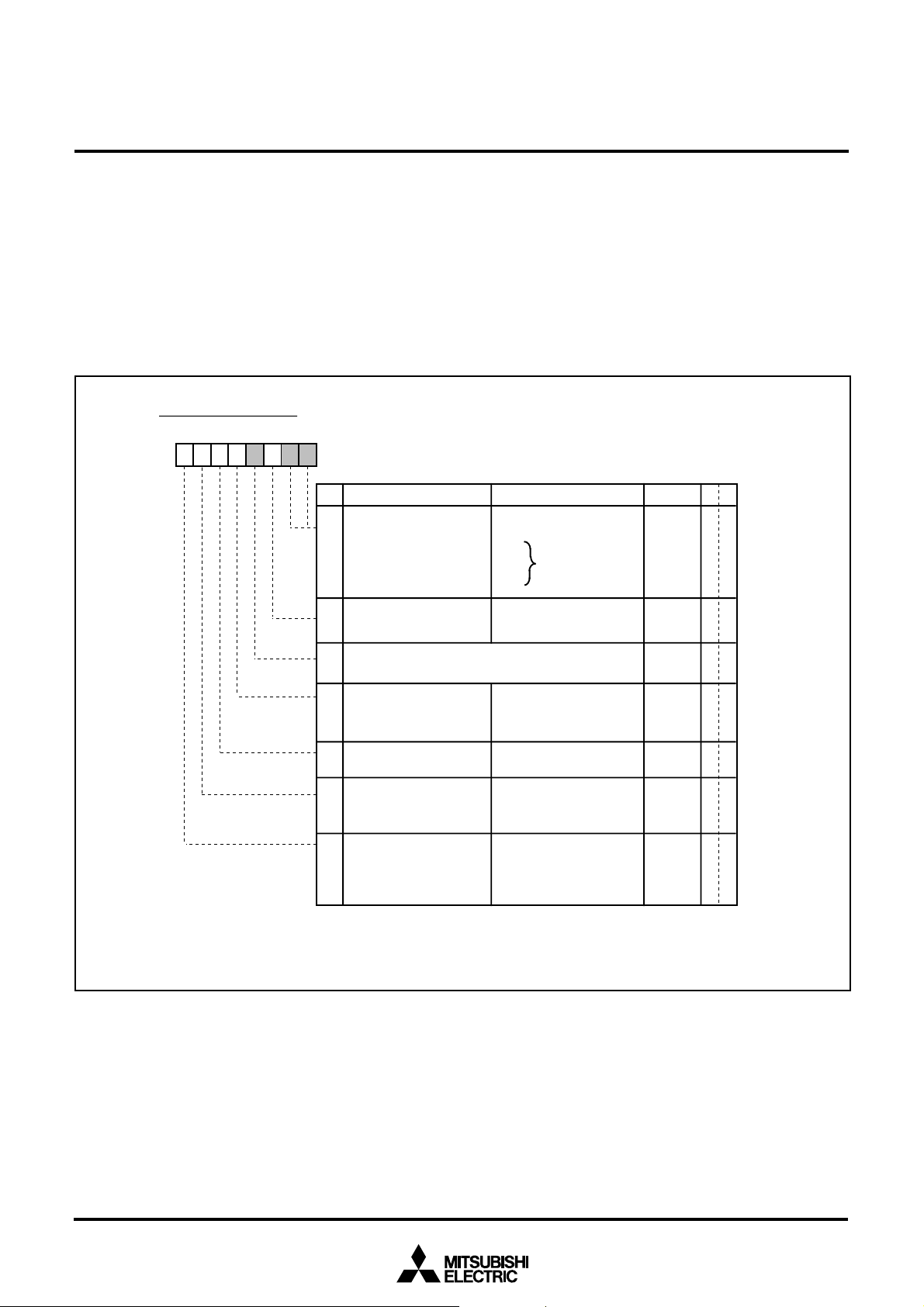

MEMORY

Special Function Register (SFR) Area

The special function register (SFR) area in the zero page contains

control registers such as I/O ports and timers.

RAM

RAM is used for data storage and for stack area of subroutine calls

and interrupts.

ROM

ROM is used for storing user programs as well as the interrupt vector

area.

RAM for Display

RAM for display is used for specifying the character codes and colors to display.

ROM for Display

ROM for display is used for storing character data.

000016

Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

Zero Page

The 256 bytes from addresses 000016 to 00FF16 are called the zero

page area. The internal RAM and the special function registers (SFR)

are allocated to this area.

The zero page addressing mode can be used to specify memory and

register addresses in the zero page area. Access to this area with

only 2 bytes is possible in the zero page addressing mode.

Special Page

The 256 bytes from addresses FF0016 to FFFF16 are called the special page area. The special page addressing mode can be used to

specify memory addresses in the special page area. Access to this

area with only 2 bytes is possible in the special page addressing

mode.

ROM Correction Memory (RAM)

This is used as the program area for ROM correction.

10000

16

RAM

(960 bytes)

for M37207MF

ROM

(62 K bytes)

for M37207MF

RAM

(512 bytes)

for M37207M8

RAM

for display

(144 bytes)

(See note)

ROM

(32 K bytes)

for M37207M8

00C016

00FF16

01FF16

020416

021B16

02C016

02FF16

030016

033F16

04FF16

060016

06D716

080016

800016

FF0016

FFDE16

FFFF

SFR area

Not used

2 page register

Not used

Not used

Not used

Interrupt vector area

16

Zero page

ROM

for display

(12 K bytes)

for M37207MF

ROM correction memory (64 bytes)

Block 1: addresses 02C0

Block 2: addresses 02E016 to 02FF16

Special page

for display

(8 K bytes)

for M37207M8

Note: Refer to Table 9. Contents of CRT display RAM.

ROM

11FFF16

12FFF16

16 to 02DF16

Not used

1FFFF16

Fig. 4. Memory Map

12

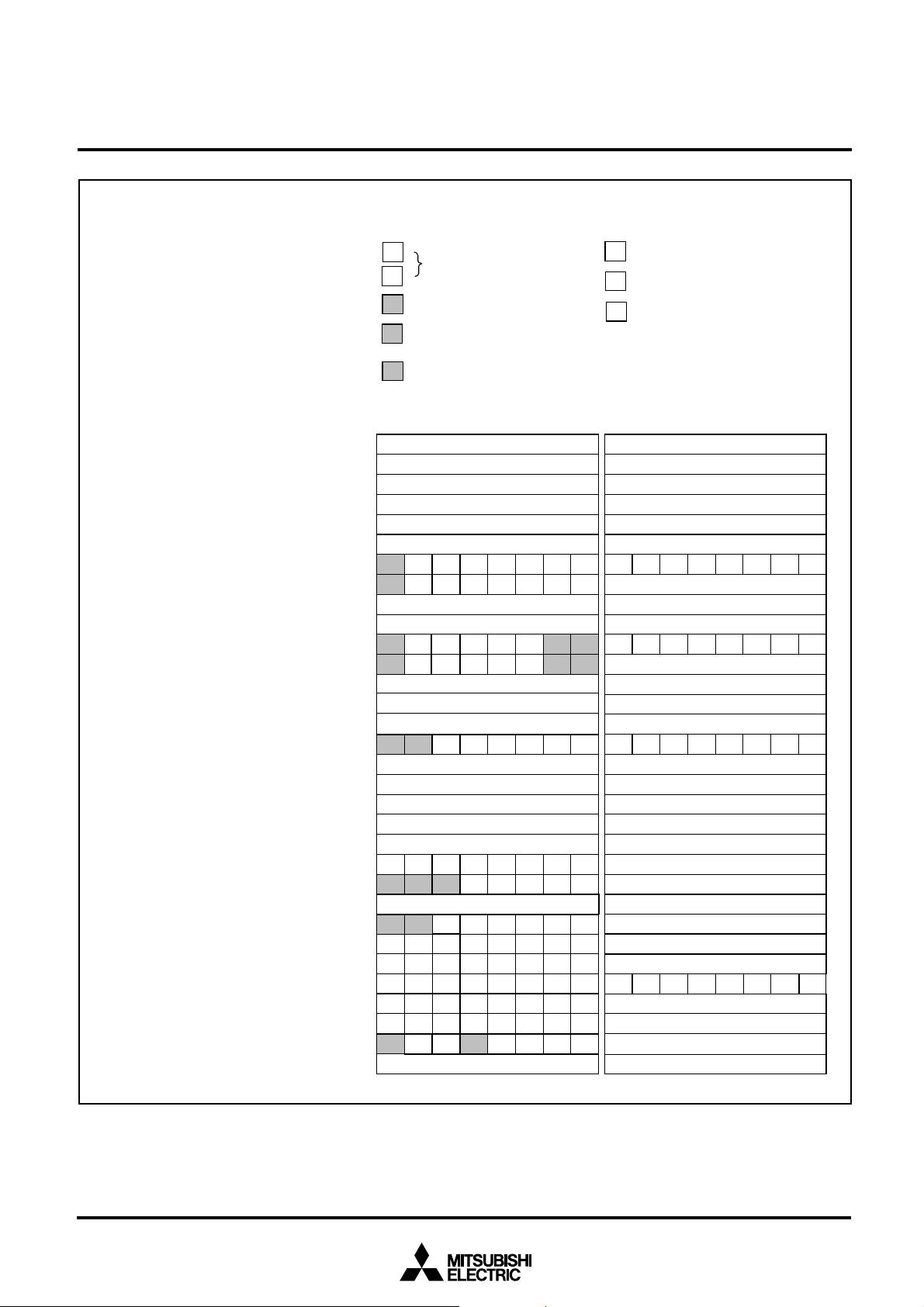

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

■SFR Area (addresses C016 to DF16)

<Bit allocation>

:

Name

:

: No function bit

: Fix this bit to “0”

0

(do not write “1”)

: Fix this bit to “1”

1

(do not write “0”)

Function bit

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

<State immediately after reset>

: “0” immediately after reset

0

1

: “1” immediately after reset

: Undefined immediately

?

after reset

Address

Port P0 (P0)

C0

16

Port P0 direction register (D0)

C1

16

Port P1 (P1)

C2

16

Port P1 direction register (D1)

C3

16

Port P2 (P2)

C4

16

Port P2 direction register (D2)

C5

16

Port P3 (P3)

C6

16

Port P3 direction register (D3)

C7

16

C8

16

Port P4 (P4)

Port P4 direction register (D4)

C9

16

Port P5 (P5)

CA

16

Port P5 control register (D5)

CB

16

CC

16

Port P6 (P6)

Port P6 direction register (D6)

CD

16

DA-H register (DA-H)

CE

16

DA-L register (DA-L)

CF

16

PWM0 register (PWM0)

D0

16

PWM1 register (PWM1)

D1

16

PWM2 register (PWM2)

D2

16

PWM3 register (PWM3)

D3

16

PWM4 register (PWM4)

D4

16

PWM output control register 1 (PW)

D5

16

PWM output control register 2 (PN)

D6

16

Interrupt interval determination register (??)

D7

16

Interrupt interval determination control register (RE)

D8

16

D9

DA

DB

DC

DD

DE

DF

2

16

C data shift register (S0)

I

16

I2C address register (S0D)

16

I2C status register (S1)

16

I2C control register (S1D)

16

I2C clock control register (S2)

16

Serial I/O mode register (SM)

16

Serial I/O regsiter (SIO)

Register

b7 b0

ACK

Bit allocation State immediately after reset

PW0PW1PW2PW3PW4PW5PW6PW7

PN2PN3PN4

PN1 PN0

RE1RE2RE3RE4RE5 RE0

D1D2D3D4D5D6D7 D0

SAD0SAD1SAD2SAD3SAD4SAD5SAD6

RBW

LRBAD0AASALPINBBTRXMST

BC0BC1BC2ESOALS

CCR0CCR1CCR2CCR3CCR4

SM0SM1SM2SM3SM5SM6

BSEL0BSEL1

ACK

BIT

10BIT

SAD

FAST

MODE

0

b7 b0

?

16

00

?

16

00

?

16

00

??0

00

16

?????

?

?

0

?

00

????

16

?

?

?

00

16

?

00

??????

?

?

?

?

?

16

00

16

00

?

00

16

?

00

16

00 0 010 0?

00

16

00

16

00

16

?

Fig. 5. Memory Map of Special Function Register (SFR)

13

■

SFR Area (addresses E0

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

16

to FF16)

Address

E0

16

E1

16

E2

16

E3

16

E4

16

E5

16

E6

16

E7

16

E8

16

E9

16

EA

16

EB

16

EC

16

ED

16

EE

16

EF

16

F0

16

F1

16

F2

16

F3

16

F4

16

F5

16

F6

16

F7

16

F8

16

F9

16

FA

16

FB

16

FC

16

FD

16

FE

16

FF

16

Register

Horizontal register (HR)

Vertical register 1 (CV1)

Vertical register 2 (CV2)

Vertical register 3 (CV3)

Character size register (CS)

Border selection register (MD)

Color register 0 (CO0)

Color register 1 (CO1)

Color register 2 (CO2)

Color register 3 (CO3)

CRT control register 1 (CC)

Display block counter (CBC)

CRT port control register (CRTP)

Wipe mode register (SL)

Wipe start register (??)

A-D control register 1 (ADM)

Timer 1 (TM1)

Timer 2 (TM2)

Timer 3 (TM3)

Timer 4 (TM4)

Timer mode register 1 (TMR1)

Timer mode register 2 (TMR2)

PWM5 register (PWM5)

PWM6 register (PWM6)

PWM7 register (PWM7)

PWM8 register (PWM8)

PWM9 register (PWM9)

CPU mode register (CPUM)

Interrupt request register 1 (IREQ1)

Interrupt request register 2 (IREQ2)

Interrupt control register 1 (ICON1)

Interrupt control register 2 (ICON2)

<Bit allocation>

:

Function bit

Name

:

: No function bit

: Fix this bit to “0”

0

(do not write “1”)

: Fix this bit to “1”

1

(do not write “0”)

b7 b0

0

CS7

CO07

CO17

CO27

CO37

0

CM7 CM6 CM5

0

Bit allocation State immediately after reset

HR0HR1HR2HR3HR4HR5

CV10CV11CV12CV13CV14CV15CV16

CV20CV21CV22CV23CV24CV25CV26

CV30CV31CV32CV33CV34CV35CV36

CS10CS11CS20CS21

MD11MD21MD31MD30

MD10MD20

CO00

CO01CO02CO03CO05

CO11

CO11CO12CO13CO15

CO22

CO21CO22CO23CO25

CO33

CO31CO32CO33CO35

CC0CC1CC2

VSYC

HSYC

SL0SL1

ADM0ADM1ADM2ADM4

TMR10TMR11TMR12TMR13TMR14

TMR20TMR21TMR22TMR23TMR24TMR25TMR26TMR27

00

TM1RTM2RTM3RTM4RCRTRVSCRIICR

IT1RIT2R

TM1ETM2ETM3ETM4ECRTEVSCEIICE

IT1EIT2E

CO06

CO16

CO26

CO36

TMR15TMR16TMR17

TM56R

TM56ETM56C

CS30CS31

CO04

CO14

CO24

CO34

CC3CC4CC5CC6

IRGB

11

CK0MSR

R/G/B

SL2SL3SL4SL5SL6

CM2

S1R

SIEMSE

00

<State immediately after reset >

: “0” immediately after reset

0

: “1” immediately after reset

1

: Undefined immediately

?

after reset

b7 b0

00

16

0

??????

?

?0??????

?0??????

00??

00??? ?

00 000 00

????

??

00

16

00

16

00

16

00

16

00

16

00

16

00

16

00

16

00

16

?

FF

16

07

16

FF

16

07

16

00

16

00

16

?

?

?

?

?

0111 0010

CK0

00

00

00

00

16

16

16

16

Fig. 6. Memory Map of Special Function Register (SFR)

14

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

■SFR Area (addresses 20416 to 21B16)

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

Address

16

204

205

16

206

16

207

16

208

16

209

16

20A

16

20B

16

20C

16

20D

16

20E

16

20F

16

210

16

211

16

212

16

213

16

214

16

215

16

216

16

217

16

218

16

219

16

21A

16

21B

16

<Bit allocation>

Name

0

1

Register

b7

Timer 5 (T5)

Timer 6 (T6)

Port control register (P7D)

Serial I/O control register (SIC)

CRT control register 2 (CBR)

CRT clock selection register (OP)

A-D control register (ADC)

Timer mode register (TMR3)

ROM correction address 1 (high-order)

ROM correction address 1 (low-order)

ROM correction address 2 (high-order)

ROM correction address 2 (low-order)

ROM correction enable register (RCR)

0

<State immediately after reset>

: “0” immediately after reset

b0

P7D0

SIC0SIC1SIC2SIC3SIC4SIC5SIC8SIC7

CBR0CBR1

ADC0ADC1ADC2ADC3ADC4ADC5

TMR30

0

: “1” immediately after reset

1

: Undefined immediately

?

after reset

b7

00

16

00

16

0000

00

16

00

16

00

16

00??

00

16

:

Function bit

:

: No function bit

: Fix this bit to “0”

(do not write “1”)

: Fix this bit to “1”

(do not write “0”)

Bit allocation State immediately after reset

P7D1P7D2P7D4

OP1OP0

?

?

?

?

?

?

?

?

?

?

?

00

16

00

16

00

16

00

16

0000

RC1RC0

????

00

??

b0

??

??

00

Fig. 7. Memory Map of 2 Page Register

15

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

<Bit allocation>

:

Function bit

Name

:

: No function bit

: Fix this bit to “0”

0

(do not write “1”)

: Fix this bit to “1”

1

(do not write “0”)

Register

b7

Processor status register (PS)

Program counter (PCH)

Program counter (PCL)

Fig. 8. Internal State of Processor Status Register and Program Counter at Reset

Bit allocation State immediately after reset

I ZCDBTVN???????

<State immediately after reset>

: “0” immediately after reset

0

1

: “1” immediately after reset

: Undefined immediately

?

after reset

b0

b7

Contents of address FFFF

Contents of address FFFE16

b0

1

16

16

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

INTERRUPTS

Interrupts can be caused by 15 different sources consisting of 3 external, 10 internal, 1 software, and reset. Interrupts are vectored interrupts with priorities as shown in Table 1. Reset is also included in

the table because its operation is similar to an interrupt.

When an interrupt is accepted,

(1) The contents of the program counter and processor status

register are automatically stored into the stack.

(2) The interrupt disable flag I is set to “1” and the corresponding

interrupt request bit is set to “0.”

(3) The jump destination address stored in the vector address enters

the program counter.

Other interrupts are disabled when the interrupt disable flag is set to

“1.”

All interrupts except the BRK instruction interrupt have an interrupt

request bit and an interrupt enable bit. The interrupt request bits are

in interrupt request registers 1 and 2 and the interrupt enable bits are

in interrupt control registers 1 and 2. Figures 10 to 13 show the interrupt-related registers.

Interrupts other than the BRK instruction interrupt and reset are accepted when the interrupt enable bit is “1,” interrupt request bit is “1,”

and the interrupt disable flag is “0.” The interrupt request bit can be

set to “0” by a program, but not set to “1.” The interrupt enable bit can

be set to “0” and “1” by a program.

Reset is treated as a non-maskable interrupt with the highest priority.

Figure 9 shows interrupt control.

Interrupt Causes

(1) VSYNC and CRT interrupts

The VSYNC interrupt is an interrupt request synchronized with

the vertical sync signal.

The CRT interrupt occurs after character block display to the CRT

is completed.

(2) INT1, INT2 interrupts

With an external interrupt input, the system detects that the level

of a pin changes from “L” to “H” or from “H” to “L,” and generates

an interrupt request. The input active edge can be selected by

bits 3 and 4 of the interrupt interval determination control register

(address 00D816) : when this bit is “0,” a change from “L” to “H” is

detected; when it is “1,” a change from “H” to “L” is detected.

Note that all bits are cleared to “0” at reset.

(3) Timer 1, 2, 3 and 4 interrupts

An interrupt is generated by an overflow of timer 1, 2, 3 or 4.

(4) Serial I/O interrupt

This is an interrupt request from the clock synchronous serial

I/O function.

Table 1. Interrupt Vector Addresses and Priority

Interrupt Source

Reset

CRT interrupt

INT1 interrupt

INT2 interrupt

Timer 4 interrupt

f(XIN)/4096 interrupt

VSYNC interrupt

Timer 3 interrupt

Timer 2 interrupt

Timer 1 interrupt

Serial I/O interrupt

Multi-master I2C-BUS interface interrupt

Timer 5 · 6 interrupt

BRK instruction interrupt

Note : Switching a source during a program causes an unnecessary interrupt. Therefore, set a source at initializing of program.

Priority

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Vector Addresses

FFFF16, FFFE16

FFFD16, FFFC16

FFFB16, FFFA16

FFF916, FFF816

FFF716, FFF616

FFF516, FFF416

FFF316, FFF216

FFF116, FFF016

FFEF16, FFEE16

FFED16, FFEC16

FFEB16, FFEA16

FFE716, FFE616

FFE316, FFE216

FFDF16, FFDE16

Remarks

Non-maskable

Active edge selectable

Active edge selectable

Active edge selectable

Source switch by software (See note)

Non-maskable (software interrupt)

17

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

(5) f(XIN)/4096 interrupt

This interrupt occurs regularly with a f(XIN)/4096 period. Set bit 0

of the PWM output control register 1 to “0.”

(6) Multi-master I2C-BUS interface interrupt

This is an interrupt request related to the multi-master I2C-BUS

interface.

(7) Timer 5 · 6 interrupt

An interrupt is generated by an overflow of timer 5 or 6. Their

priorities are same, and can be switched by software.

(8) BRK instruction interrupt

This software interrupt has the least significant priority. It does

not have a corresponding interrupt enable bit, and it is not affected by the interrupt disable flag I (non-maskable).

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

Interrupt request bit

Interrupt enable bit

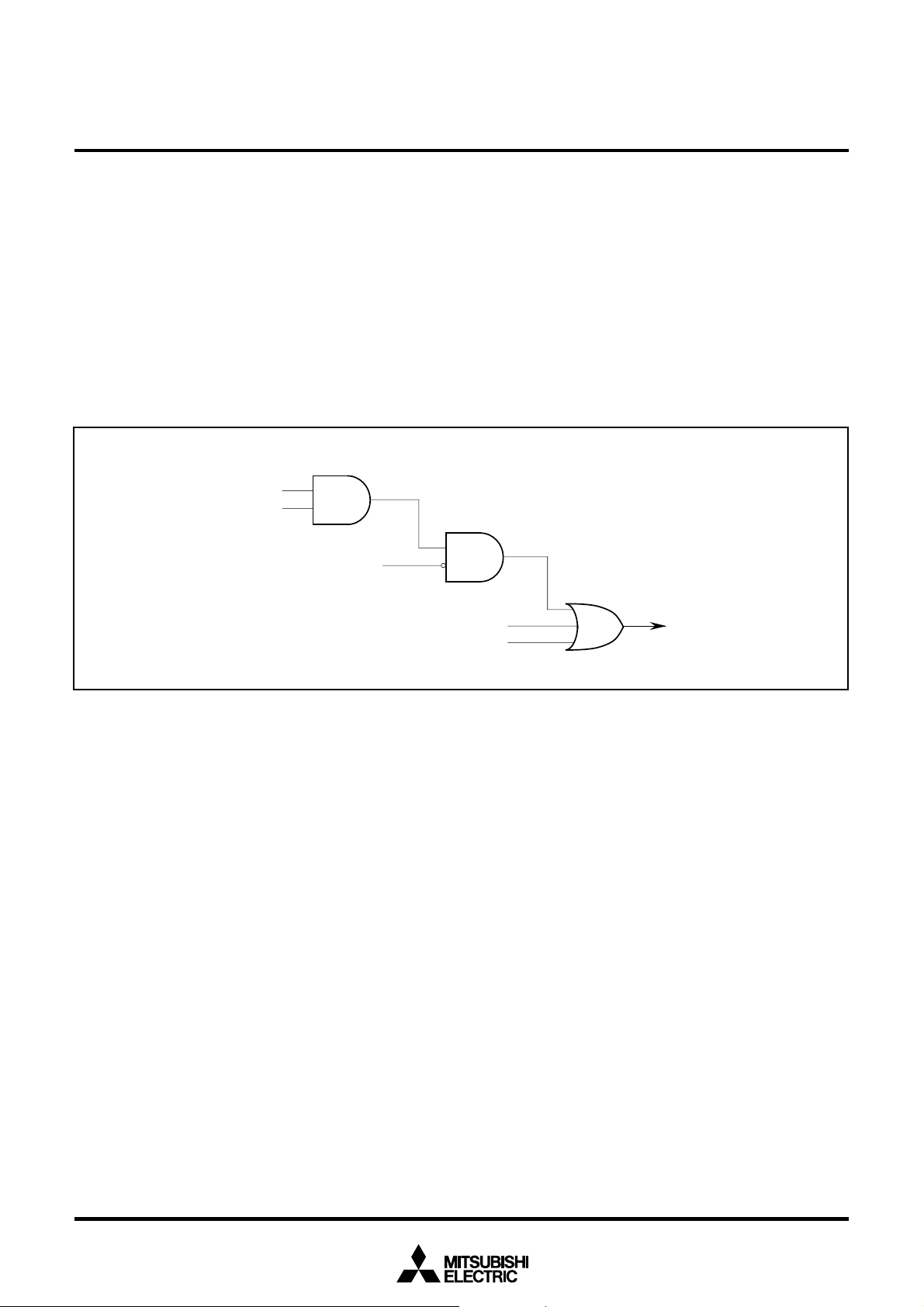

Fig. 9. Interrupt Control

Interrupt disable flag I

BRK instruction

Reset

Interrupt request

18

Interrupt Request Register 1

b7b6 b5b4b3 b2b1b0

Interrupt request register 1 (IREQ1) [Address 00FC

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

16

]

Fig. 10. Interrupt Request Register 1

B Name Functions

0

Timer 1 interrupt

request bit (TM1R)

1 Timer 2 interrupt

request bit (TM2R)

2 Timer 3 interrupt

request bit (TM3R)

Timer 4 interrupt

3

request bit (TM4R)

4 CRT interrupt

request bit (CRTR)

5V

SYNC

interrupt

request bit (VSCR)

Multi-master I

6

interface interrupt

request bit (IICR)

7 Nothing is assigned. This bit is a write disable bit.

When this bit is read out, the value is “0.”

2

C-BUS

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

After reset

0 ✽

0 ✽

0 ✽

0 ✽

0 ✽

0 ✽

0

0

RW

R

R

R

R

R

R

✽

R

—

R

Interrupt Request Register 2

b7b6 b5b4b3 b2b1b0

0

Fig. 11. Interrupt Request Register 2

Interrupt request register 2 (IREQ2) [Address 00FD

B Name Functions

INT1 interrupt

0

request bit (ITIR)

INT2 interrupt

1

request bit (IT2R)

Serial I/O interrupt

2

request bit (SIR)

3,6

Nothing is assigned. These bits are write disable bits.

When these bits are read out, the values are “0.”

IN

)/4096 interrupt

f(X

4

request bit (MSR)

Timer 5 • 6 interrupt

5

request bit (TM56R)

7

Fix this bit to “0.”

✽: “0” can be set by software, but “1” cannot be set.

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

0 : No interrupt request issued

1 : Interrupt request issued

16

]

After reset

0 ✽

0 ✽

0 ✽

0

0 ✽

0 ✽R

0

RW

R

R

R

R—

R

RW

19

Interrupt Control Register 1

b7b6 b5b4b3 b2b1b0

Interrupt control register 1 (ICON1) [Address 00FE

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

16

]

Fig. 12. Interrupt Control Register 1

B Name Functions

Timer 1 interrupt

0

enable bit (TM1E)

Timer 2 interrupt

1

enable bit (TM2E)

Timer 3 interrupt

2

enable bit (TM3E)

Timer 4 interrupt

3

enable bit (TM4E)

CRT interrupt enable

4

bit (CRTE)

SYNC

interrupt enable

V

5

bit (VSCE)

6

Multi-master I

interface interrupt

enable bit (IICE)

7

Nothing is assigned. This bit is a write disable

bit. When this bit is read out, the value is “0.”

2

C-BUS

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

After reset

0

0

0

0

0

0RW

0

0

RW

RW

RW

RW

RW

RW

R

W

—

R

Interrupt Control Register 2

b7b6 b5b4b3 b2b1b0

0

Fig. 13. Interrupt Control Register 2

0

Interrupt control register 2 (ICON2) [Address 00FF

B Name Functions

INT1 interrupt

0

enable bit (IT1E)

INT2 interrupt enable

1

bit (IT2E)

Serial I/O interrupt

2

enable bit (SIE)

Fix these bits to “0.”

3, 6

4

f(X

IN

)/4096 interrupt

enable bit (MSE)

5

Timer 5 • 6 interrupt

enable bit (TM56E)

7

Timer 5 • 6 interrupt

switch bit (TM56C)

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

0 : Timer 5

1 : Timer 6

16

]

After reset

0

0

0

0

0RW

0RW

0RW

RW

RW

RW

RW

RW

20

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

TIMERS

The M37267M6-XXXSP has 6 timers: timer 1, timer 2, timer 3, timer

4, timer 5 and timer 6. All timers are 8-bit timers with the 8-bit timer

latch. The timer block diagram is shown in Figure 17 .

0 .

All of the timers count down and their divide ratio is 1/(n+1), where n

is the value of timer latch. By writing a count value to the corresponding timer latch (addresses 00F016 to 00F316 : timers 1 to 4, addresses

020C16 and 020D16 : timers 5 and 6), the value is also set to a timer,

simultaneously.

The count value is decremented by 1. The timer interrupt request bit

is set to “1” by a timer overflow at the next count pulse after the count

value reaches “0016.”

(1) Timer 1

Timer 1 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

f(XIN)/4096 or f(XCIN)/4096

•

f(XCIN)

•

External clock from the TIM2 pin

•

The count source of timer 1 is selected by setting bits 5 and 0 of

timer mode register 1 (address 00F416). Either f(XIN) or f(XCIN) is

selected by bit 7 of the CPU mode register.

Timer 1 interrupt request occurs at timer 1 overflow.

(2) Timer 2

Timer 2 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

Timer 1 overflow signal

•

External clock from the TIM2 pin

•

The count source of timer 2 is selected by setting bits 4 and 1 of

timer mode register 1 (address 00F416). Either f(XIN) or f(XCIN) is

selected by bit 7 of the CPU mode register. When timer 1 overflow

signal is a count source for timer 2, timer 1 functions as an 8-bit

prescaler.

Timer 2 interrupt request occurs at timer 2 overflow.

(3) Timer 3

Timer 3 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

External clock from the TIM3 pin

•

The count source of timer 3 is selected by setting bit 0 of timer mode

register 2 (address 00F516). Either f(XIN) or f(XCIN) is selected by bit

7 of the CPU mode register.

Timer 3 interrupt request occurs at timer 3 overflow.

(5) Timer 5

Timer 5 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

f(XCIN)

•

Timer 4 overflow signal

•

The count source of timer 3 is selected by setting bit 6 of timer mode

register 1 (address 00F416) and bit 7 of timer mode register 2 (address 00F516). Either f(XIN) or f(XCIN) is selected by bit 7 of the CPU

mode register.

Timer 5 interrupt request occurs at timer 5 overflow.

(6) Timer 6

Timer 6 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

Timer 5 overflow signal

•

The count source of timer 6 is selected by setting bit 7 of timer mode

register 1 (address 00F416). Either f(XIN) or f(XCIN) is selected by bit

7 of the CPU mode register. When timer 5 overflow signal is a count

source for timer 6, timer 5 functions as an 8-bit prescaler.

Timer 6 interrupt request occurs at timer 6 overflow.

At reset, timers 3 and 4 are connected by hardware and “FF16” is

automatically set in timer 3; “0716” in timer 4. The f(XIN) ✽ /16 is selected as the timer 3 count source. The internal reset is released by

timer 4 overflow in this state and the internal clock is connected.

At execution of the STP instruction, timers 3 and 4 are connected by

hardware and “FF16” is automatically set in timer 3; “0716” in timer 4.

However, the f(XIN) ✽ /16 is not selected as the timer 3 count source.

So set bit 0 of timer mode register 2 (address 00F516) to “0” before

execution of the STP instruction (f(XIN) ✽ /16 is selected as

timer 3 count source). The internal STP state is released by timer 4

overflow in this state and the internal clock is connected.

As a result of the above procedure, the program can start under a

stable clock.

✽ : When bit 7 of the CPU mode register (CM7 ) is “1,” f(XIN) be-

comes f(XCIN).

The timer-related registers is shown in Figures 14 to 16.

(4) Timer 4

Timer 4 can select one of the following count sources:

f(XIN)/16 or f(XCIN)/16

•

f(XIN)/2 or f(XCIN)/2

•

Timer 3 overflow signal

•

The count source of timer 3 is selected by setting bits 1 and 4 of

timer mode register 2 (address 00F516). Either f(XIN) or f(XCIN) is

selected by bit 7 of the CPU mode register. When timer 3 overflow

signal is a count source for timer 4, the timer 3 functions as an 8-bit

prescaler.

Timer 4 interrupt request occurs at timer 4 overflow.

21

Timer Mode Register 1

b7b6 b5b4b3b2b1b0

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

Timer mode register 1 (TMR1) [Address 00F4

16

]

Fig. 14. Timer Mode Register 1

Timer Mode Register 2

b7b6 b5b4b3b2b1b0

B

0

Name Functions

Timer 1 count source

selection bit 1

(TMR10, TMR15)

b5 b0

0 0: f(XIN)/16 or f(X

0 1: f(X

1 0: f(Xc

IN

)/4096 or f(X

IN

)

1 1: External clock from TIM2 pin

Count source selected by bit 4 of TM1

1

Timer 2 count source

selection bit 1

0:

1:

External clock from TIM2 pin

(TMR11)

Timer 1 count

2

stop bit (TMR12)

Timer 2 count stop

3

bit (TMR13)

4

Timer 2 count source

selection bit 2

0: Count start

1: Count stop

0: Count start

1: Count stop

0: f(XIN)/16 or f(X

1: Timer 1 overflow

(TMR14)

6

Timer 5 count source

selection bit 2 (TMR16)

7 Timer 6 internal count

source selection bit

0: Timer 2 overflow

1: Timer 4 overflow

0: f(XIN)/16 or f(X

1: Timer 5 overflow

(TMR17)

Note: Either f(XIN) or f(X

CIN

) is selected by bit 7 of the CPU mode register.

Timer mode register 2 (TMR2) [Address 00F5

CIN

)/16 (See note)

CIN

)/4096 (See note)

CIN

)/16 (See note)

CIN

)/16 (See note)

16

]

After reset

0

0

0

0

0

0WR

0WR

R

W

WR

WR

WR

WR

WR

Fig. 15. Timer Mode Register 2

B

0

Name Functions

Timer 3 count source

selection bit (TMR20)

1 Timer 4 count source

selection bit 2

(TMR21)

Timer 3 count

2

stop bit (TMR22)

Timer 4 count stop bit

3

(TMR23)

4

Timer 4 count source

selection bit 1

(TMR24)

Timer 5 count stop bit

5

(TMR25)

Timer 6 count stop bit

6

(TMR26)

Timer 5 count source

7

selection bit 1

(TMR27)

Note: Either f(XIN) or f(X

After reset

0 : f(X

IN

)/16 or f(X

CIN

)/16 (See note)

1 : External clock from TIM3 pin

0 : Timer 3 overflow signal

1 : f(X

IN

)/16 or f(X

CIN

)/16 (See note)

0: Count start

1: Count stop

0: Count start

1: Count stop

0: Count source selected by bit 1

of TMR2

1 : f(X

IN

)/2 or f(X

CIN

)/2 (See note)

0: Count start

1: Count stop

0: Count start

1: Count stop

0: Count source selected by bit 0

of TMR3

1: Count source selected by bit 6

of TMR1

CIN

) is selected by bit 7 of the CPU mode register.

RW

0 RW

0RW

0

RW

0

RW

0RW

0

RW

0

RW

0

RW

22

Timer Mode Register 3

b7b6 b5b4b3 b2b1b0

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

Timer mode register 3 (TMR3) [Address 020B

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

16

]

Fig. 16. Timer Mode Register 3

B

0

Timer 5 count source

selection bit 3

(TMR30)

1

Nothing is assigned. These bits are write disable bits.

to

When these bits are read out, the values are “0.”

7

Note: Either f(XIN) or f(X

Name Functions

0 : f(XIN)/16 or f(X

1 : f(X

CIN

CIN

) is selected by bit 7 of the CPU mode register.

CIN

)

)/16 (See note)

After reset

RW

0RW

0R—

23

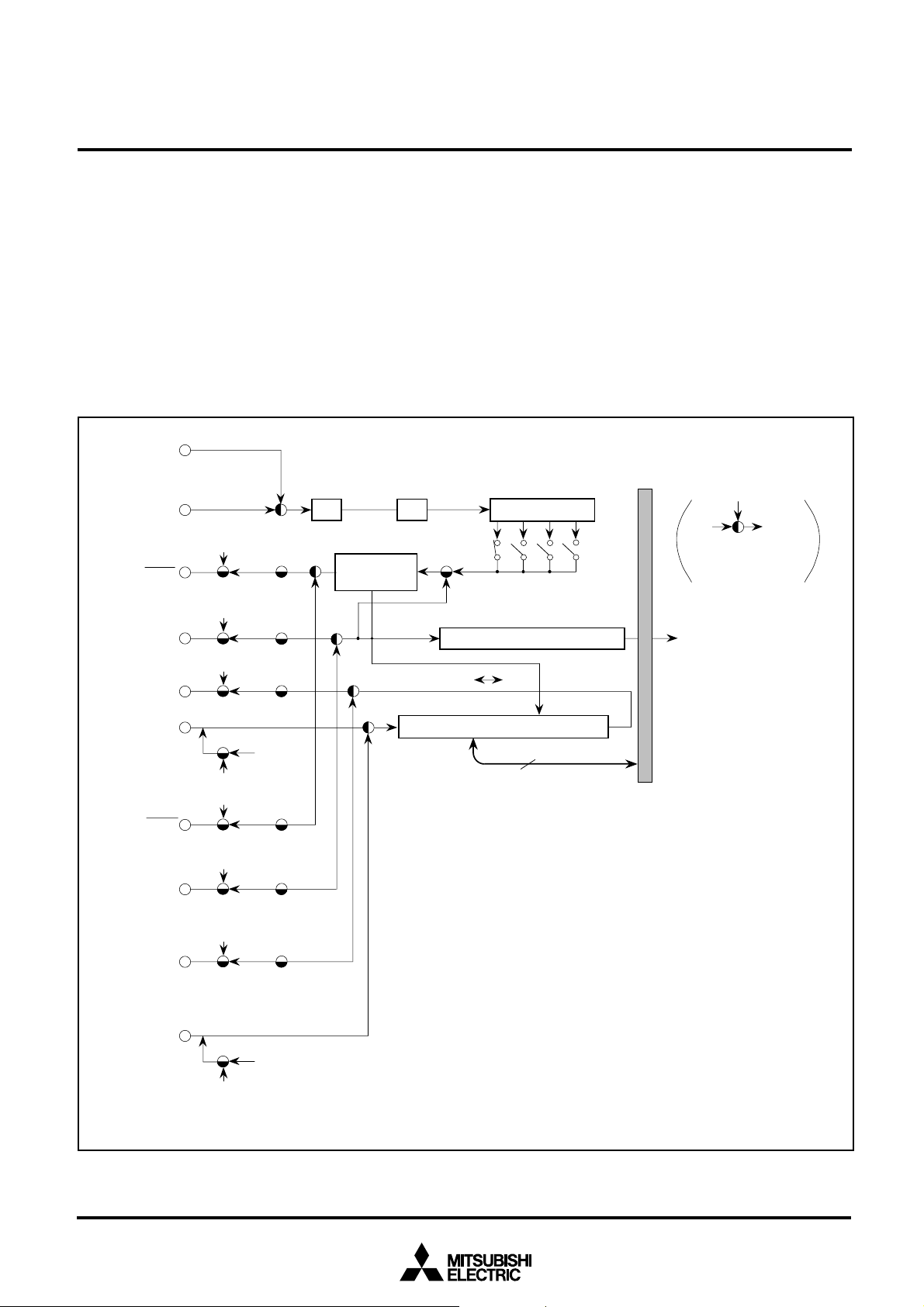

X

CIN

X

IN

TIM2

TIM3

CM

7

1/4096

1/2

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

Data bus

8

TMR1

5

TMR1

1/8

5

TMR1

TMR1

TMR1

TMR2

0

TMR1

4

1

TMR1

0

TMR2

Timer 1 latch (8)

2

Timer 2 latch (8)

3

Timer 3 latch(8)

2

8

Timer 1 (8)

8

Timer 2 (8)

8

Timer 3 (8)

Timer 1

interrupt request

8

8

Timer 2

interrupt request

8

8

FF

16

Reset

STP instruction

Timer 3

interrupt request

8

8

07

16

8

8

Selection gate : Connected to

black side at

reset.

TMR2

TMR2

4

TMR2

1

Timer 4 latch (8)

3

TMR1

6

Timer 5 latch (8)

8

Timer 4 (8)

8

Timer 5 (8)

7

TMR1 : Timer mode register 1

TMR2 : Timer mode register 2

TMR3 : Timer mode register 3

CM : CPU mode register

TMR2

TMR3

TMR2

0

5

8

8

Timer 6 latch (8)

8

TMR1

7

TMR2

Timer 6 (8)

6

8

Notes 1: HIGH pulse width of external clock inputs TIM2 and TIM3 needs 4 machine cycles or more.

2: When the external clock source is selected, timers 1, 2, and 3 are counted at a rising edge of input signal.

3: In the stop mode or the wait mode, external clock inputs TIM2 and TIM3 cannot be used.

Timer 4

interrupt request

Timer 5

interrupt request

Timer 6

interrupt request

Fig. 17. Timer Block Diagram

24

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

SERIAL I/O

This microcomputer has a built-in serial I/O which can either transmit

or receive 8-bit data serially in clock synchronous mode.

The serial I/O block diagram is shown in Figure 18. The synchronous

clock I/O pin (SCLK), and data I/O pins (SOUT, SIN), receive enable

signal output pin (SRDY) also function as port P4.

Bit 2 of the serial I/O mode register (address 00DE16) selects whether

the synchronous clock is supplied internally or externally (from the

pins SCLK1, SCLK2). When an internal clock is selected, bits 1 and 0

select whether f(XIN) or f(XCIN) is divided by 8, 16, 32, or 64. To use

pins for serial I/O, set the corresponding bits of the port P4 direction

register (address 00C916) to “0.”

S

S

S

S

S

X

CIN

X

RDY2

CLK2

OUT2

IN2

S

RDY1

CLK1

IN

____

P43 latch

SM4

P41 latch

SM3

P40 latch

SM3

SM6

0

latch

P4

P47 latch

SIC7

P45 latch

SIC5

CM7

SCL2 CSIO

SM6

SCL3

SM7

SDA3

SM7

SDA2

PWM8

SIC3

SCL1

SIC4

1/2

CSIO

CSIO

Synchronous

circuit

CSIO

1/2

SM5

Serial I/O shift register (8)

CM : CPU mode register

SM : Serial I/O mode register

SIC : Serial I/O control register

CSIO : Bit 1 of serial I/O control register

The operation of the serial I/O is described below. The operation

differs depending on the clock source; external clock or internal clock.

Frequency divider

1/2

SM2

S

Serial I/O counter (8)

: LSB MSB

1/81/4 1/16

SM

SM

(Note)

(Address 00DF16)

8

Data bus

1

0

Selection gate : Connected to

black side at

reset.

Serial I/O

interrupt request

P44 latch

S

OUT1

S

IN1

SIC5

SIC6

PWM9

6

latch

P4

Note : When the data is set in the serial I/O register (address 00DF

Fig. 18. Serial I/O Block Diagram

SDA1

SIC4

16

), the register functions as the serial I/O shift register.

25

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

Internal clock : The SRDY signal goes to HIGH during the write cycle

by writing data into the serial I/O register (address 00DD16). After the

write cycle, the SRDY signal goes to “L” (receive enable state). The

____

SRDY signal goes to “H” at the next falling edge of the transfer clock

____

____

for the serial I/O register.

The serial I/O counter is set to “7” during write cycle into the serial I/

O register (address 00DD16), and transfer clock goes HIGH forcibly.

At each falling edge of the transfer clock after the write cycle, serial

data is output from the SOUT pin. Transfer direction can be selected

by bit 5 of the serial I/O mode register. At each rising edge of the

transfer clock, data is input from the SIN pin and data in the serial I/O

register is shifted 1 bit.

After the transfer clock has counted 8 times, the serial I/O counter

becomes “0” and the transfer clock stops at HIGH. At this time the

interrupt request bit is set to “1.”

External clock : When an external clock is selected as the clock source,

the interrupt request is set to “1” after the transfer clock has counted

8 counts. However, transfer operation does not stop, so the clock

should be controlled externally. Use the external clock of 1 MHz or

less with a duty cycle of 50%.

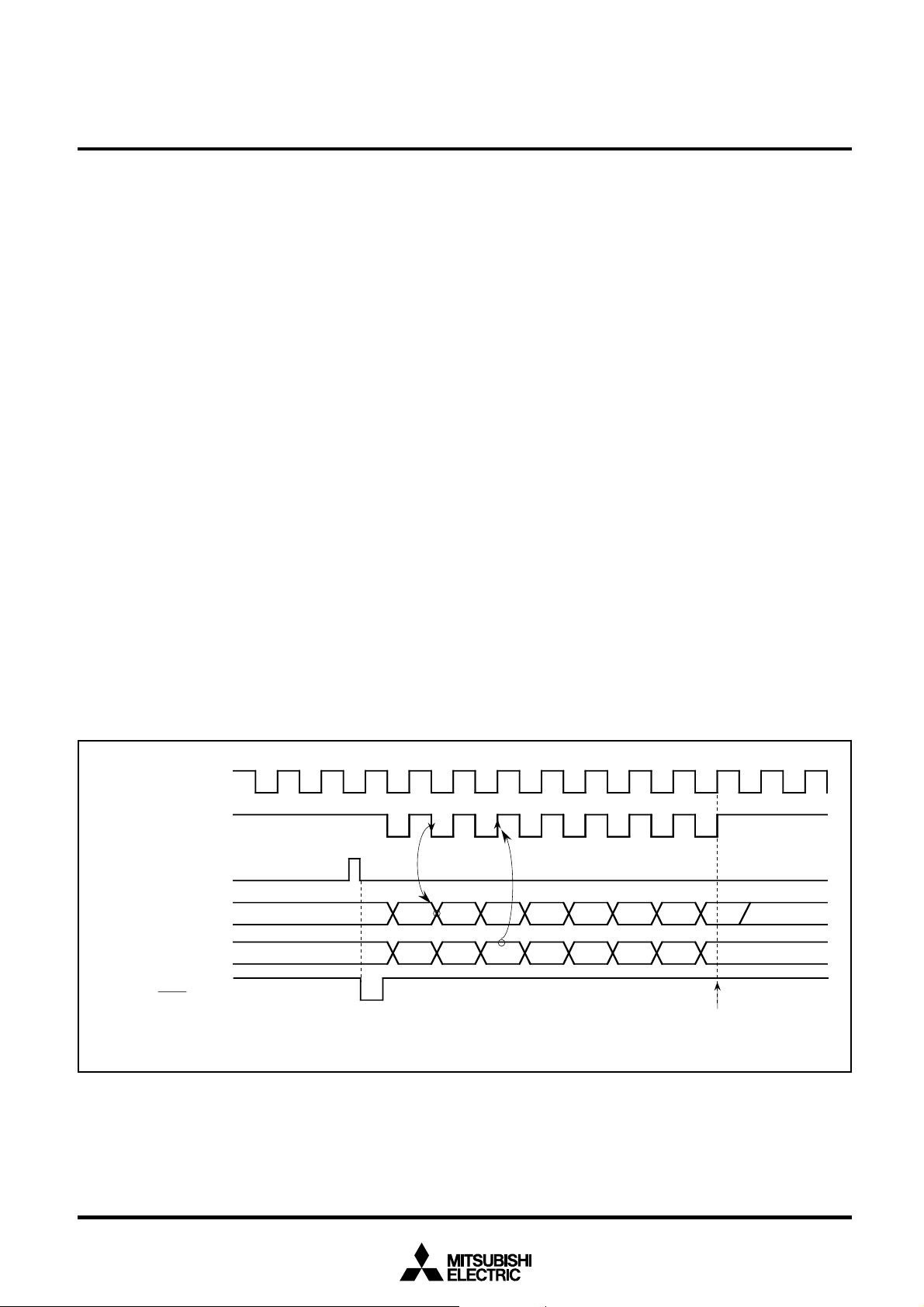

The serial I/O timing is shown in Figure 19. When using an external

clock for transfer, the external clock must be held at “H” for initializing

the serial I/O counter. When switching between an internal clock and

an external clock, do not switch during transfer. Also, be sure to initialize the serial I/O counter after switching.

Notes 1: On programming, note that the serial I/O counter is set by

writing to the serial I/O register with the bit managing instructions such as SEB and CLB.

2: When an external clock is used as the synchronous clock,

write transmit data to the serial I/O register when the transfer clock input level is HIGH.

Synchronous clock

Transfer clock

Serial I/O register

write signal

Serial I/O output

S

OUT

Serial I/O input

S

IN

Receive

signal

enable

RDY

S

Note : When an internal clock is selected, the S

Fig. 19. Serial I/O Timing (for LSB first)

D

0

D

1

D

2

D

3

D

4

D

OUT

pin is at high-impedance after transfer is completed.

(See note)

5

D

6

D

7

Interrupt request bit is set to “1”

26

Serial I/O Mode Register

b7b6 b5b4b3 b2b1b0

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

)/4 or f(X

)/16 or f(X

)/32 or f(X

)/64 or f(X

CIN

CIN

CIN

CIN

16]

)/4

)/16

)/32

)/64

After reset

0

RW

RW

Serial I/O mode register (SM) [Address 00DE

B Name Functions

Internal synchronous

0, 1

clock selection bits

(SM0, SM1)

(See note 1)

b1 b0

0 0: f(X

0 1: f(X

1 0: f(X

1 1: f(X

IN

IN

IN

IN

Fig. 20. Serial I/O Mode Register

Serial I/O Control Register

b7b6 b5b4b3 b2b1b0

Synchronous clock

2

selection bit (SM2)

0, P41

Ports P4

3, 7

function selection

bits (SM3, SM7)

(See note 2)

4, 6

Ports P4

2, P43

function selection bits

(SM4, SM6)

(See note 2)

Transfer direction

5

selection bit (SM5)

Notes 1: Either f(XIN) or f(XCIN) is selected by bit 7 of the CPU

mode register.

2: When using ports P4

the serial control register to “1.”

Serial I/O control register (SIC) [Address 0207

B Name Functions

Input signal to sift

0

register selection bit

(SIC0)

Serial I/O pin switch

1

bit (CSIO)

2

C-BUS connection

I

2

ports switch bit

(SIC2)

7

function

Ports P4

3, 7

selection bits

(SM3, SM7)

(See note 2)

4, 5

Ports P4

4

, P45

function selection bits

(SM4, SM6)

(See note 2)

6

function

Ports P4

6

selection bits

(SIC6)

(See note 2)

Notes 1: When inputting data from the S

I/O register.

2: When using ports P4

serial I/O control register to “0.”

0: External clock

1: Internal clock

b7

b3

P40/S

OUT2

/

P41/S

CLK2

CIN

SDA3/X

0

P4

✕

0

1

b6

0

1

0

1

0: LSB first

1: MSB first

0

1

S

OUT2

SDA3

b4

P42/S

IN2

/

SDA2/AD8

0

P4

2

SDA2

1

P4

2

SDA2

0–P43 as serial I/O pins, set bit 1 of

COUT

SCL3/X

P4

1

S

CLK2

SCL3

P43/S

RDY2

SCL2/AD7

P4

3

S

RDY2

SDA2

16

]

/

/

After reset

CSIO b0

0 0: Input signal from S

0 1: Input signal from S

1 0: Input signal from S

1 1: Input signal from S

0:

S

OUT1

,

S

CLK1

1:

S

OUT2

,

S

CLK2

0:

SDA2, SCL2, SDA1, SCL1

1:

SDA3, SCL3

P47/S

b7

b3

0

✕

1

0

1

b5

b4

P44/S

OUT1

SDA1

0

P4

4

✕

1

S

OUT1

0

1

SDA1

b6

P46/S

0

1

out

4

–P47 as serial I/O pins, set bit 1 of the

IN1

OUT1

(See note 1)

IN2

OUT2

(See note 1)

,

S

IN1

,

S

RDY1

,

S

IN2

,

S

RDY2

RDY1

/PWM8

P4

7

S

RDY1

PWM8

/

P45/S

CLK1

/

SCL1

P4

5

S

CLK1

SCL1

IN1

/PWM9

P4

6

PWM9

pin, set “FF16” to the serial

0

RW

0

RW

0RW

0RW

RW

RW

0

RW

0

0RW

0RW

0RW

0RW

Fig. 21. Serial I/O Control Register

27

M37207MF-XXXSP/FP, M37207M8-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

Serial I/O Common Transmission/Reception Mode

By writing “1” to bit 0 of the serial I/O control register, signals SIN and

SOUT are switched internally to be able to transmit or receive the

serial data.

Figure 22 shows signals on serial I/O common transmission/reception mode.

Note : When receiving the serial data after writing “FF16” to the serial

I/O register.

MITSUBISHI MICROCOMPUTERS

M37207EFSP/FP

and ON-SCREEN DISPLAY CONTROLLER

S

CLK2

S

OUT2

S

IN2

S

CLK1

S

OUT1

S

IN1

Fig. 22. Signals on Serial I/O Common Transmission/Reception Mode

“1”

“0”

CSIO

“1”

“0”

“1”

“0”

CSIO

“1”

“0”

SIC0

SIC0

: Bit 0 of serialI/O control register

CSIO : Bit 1 of serial I/O control register

Clock

Serial I/O shift register (8)

28

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

MULTI-MASTER I2C-BUS INTERFACE

The multi-master I2C-BUS interface is a serial communications circuit, conforming to the Philips I2C-BUS data transfer format. This

interface, offering both arbitration lost detection and a synchronous

functions, is useful for the multi-master serial communications.

Figure 23 shows a block diagram of the multi-master I2C-BUS interface and Table 2 shows multi-master I2C-BUS interface functions.

This multi-master I2C-BUS interface consists of the I2C address register, the I2C data shift register, the I2C clock control register, the I2C

control register, the I2C status register and other control circuits.

I2C address register (S0D)

b7 b0

SAD6 SAD5 SAD4 SAD3 SAD2 SAD1 SAD0 RBW

Table 2. Multi-master I2C-BUS Interface Functions

Item

Function

In conformity with Philips I2C-BUS

standard:

Format

10-bit addressing format

7-bit addressing format

High-speed clock mode

Standard clock mode

In conformity with Philips I2C-BUS

standard:

Communication mode

Master transmission

Master reception

Slave transmission

Slave reception

SCL clock frequency

16.1 kHz to 400 kHz (at φ = 4 MHz)

φ : System clock = f(XIN)/2

Note: We are not responsible for any third party’s infringement of

patent rights or other rights attributable to the use of the control function (bits 6 and 7 of the I2C control register at address

00F916) for connections between the I2C-BUS interface and

ports (SCL1, SCL2, SDA1, SDA2).

Interrupt

generating

circuit

Interrupt

request signal

(IICIRQ)

Address comparator

Serial

data

(SDA)

Noise

elimination

circuit

Data

control

circuit

b7

I C data shift register

S0

AL

circuit

BB

circuit

Serial

clock

(SCL)

Noise

elimination

circuit

Clock

control

circuit

b7 b0

FAST

ACK

ACK

I2C clock control register (S2)

BIT

MODE

Fig. 23. Block Diagram of Multi-master I2C-BUS Interface

2

CCR4 CCR3 CCR2 CCR1 CCR0

Clock division

b0

Internal data bus

System clock

b7

MST TRX BB PIN

AL AAS AD0 LRB

2

I C status

(S1)

register

b7 b0

BSEL1 BSEL0

10BIT

ALS

SAD

I2C clock control register (S1D)

(φ)

BC2 BC1 BC0

ESO

Bit counter

b0

29

MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

(1) I2C Data Shift Register