Mitsubishi M30222FGGP, M30222FGFP Datasheet

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

Description

The M30222 single-chip microcomputers are built using the high-performance silicon gate CMOS process

using a M16C/60 Series CPU core and are packaged in a 100-pin plastic molded QFP. These single-chip

microcomputers operate using sophisticated instructions featuring a high-level of instruction efficiency and

are capable of executing instructions at high speed. They also feature a built-in multiplier and DMAC,

making them ideal for controlling office, communications, industrial equipment, and other high-speed pro-

cessing applications.

The M30222 group includes a range of products with various package types.

Features

• Memory capacity ......................................... Flash ROM 260 Kbytes

...................................................................... RAM 20 Kbytes

• Shortest instruction execution time ............. 62.5ns (f(XIN)=16MHZ)

• Supply voltage ............................................ 2.7 to 5.5V

• Low power consumption ............................. TBD

• Interrupts ..................................................... 25 internal and 8 external interrupt sources

4 software interrupt sources

7 levels (including key input interrupt)

• Multifunction 16-bit timer .............................

• Serial I/O ..................................................... 5 channel

• DMAC........................................................... 2 channels (trigger: 24 sources)

• A-D converter ............................................... 10 bits X 8 channels (expandable up to 10 channels)

• D-A converter ...............................................8 bits X 2 channels

• CRC calculation circuit .................................1 circuit

• Watchdog timer ............................................ 1 timer

• Key-on Wake up ...........................................8 inputs

• Programmable I/O ........................................ 54 lines

• Input port ......................................................1 line (P8

• Clock generating circuit ............................... 2 built-in clock generation circuits

•LCD Drive ...................................................... 1/2, 1/3 bias

5 output timers, 6 input timers, three phase motor control, real-time port

3 for UART or clock synchronous (1 channel for I

2 for clock synchronous

(built-in feedback resistor, and external ceramic or quartz oscillator)

4 common outputs

40 segment outputs

Built-in charge pump

1/2, 1/3, 1/4 duty

Expansion CLK output

Static/direct drive mode

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

2

C or SPI)

3 shared with NMI pin)

Specifications written in this manual

are believed to be accurate but are

not guaranteed to be entirely error

free. They may be changed for func-

tional or performance improvements.

Please make sure your manual is the

latest version.

Applications

Audio, cameras, office, industrial, communications and, portable equipment

1-2

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

Table of Contents

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Description ............................................................ 1-2

Operation of Functional Blocks ............................ 1-10

Memory ............................................................... 1-10

Central Processing Unit (CPU) ............................ 1-11

Reset ................................................................... 1-14

Special function registers..................................... 1-15

Software Reset .................................................... 1-20

Clock generating Circuit ...................................... 1-21

Clock Output ........................................................ 1-25

Wait Mode ........................................................... 1-26

Stop Mode ........................................................... 1-27

Status Transition Of BCLK ................................... 1-28

Voltage Down Converter ...................................... 1-30

Power control....................................................... 1-32

Protection ............................................................ 1-34

Software wait ....................................................... 1-35

Overview of Interrupts.......................................... 1-36

Watchdog Timer .................................................. 1-57

DMAC .................................................................. 1-59

Timers ................................................................. 1-69

Timer A ................................................................ 1-71

Timer B ................................................................ 1-85

Timer functions for three-phase motor control ..... 1-93

Serial Communications ...................................... 1-105

(1) Clock synchronous serial I/O mode .............. 1-114

(2) Clock Asynchronous Serial I/O (UART) Mode1-120

UART2 in I2C Mode .......................................... 1-130

UART2 in SPI mode .......................................... 1-138

S I/O 3, 4 ........................................................... 1-143

LCD Drive Control Circuit .................................. 1-147

A-D Converter ................................................... 1-157

D-A Converter .................................................... 1-168

CRC Calculation Circuit ..................................... 1-170

Programmable I/O Ports .................................... 1-172

Electrical Characteristics ................................... 1-179

Flash Memory .................................................... 1-186

CPU Rewrite Mode ............................................ 1-188

Parallel I/O Mode ............................................... 1-202

Standard serial I/O mode 1 ................................ 1-206

Standard serial I/O mode 2 ................................ 1-226

1-3

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

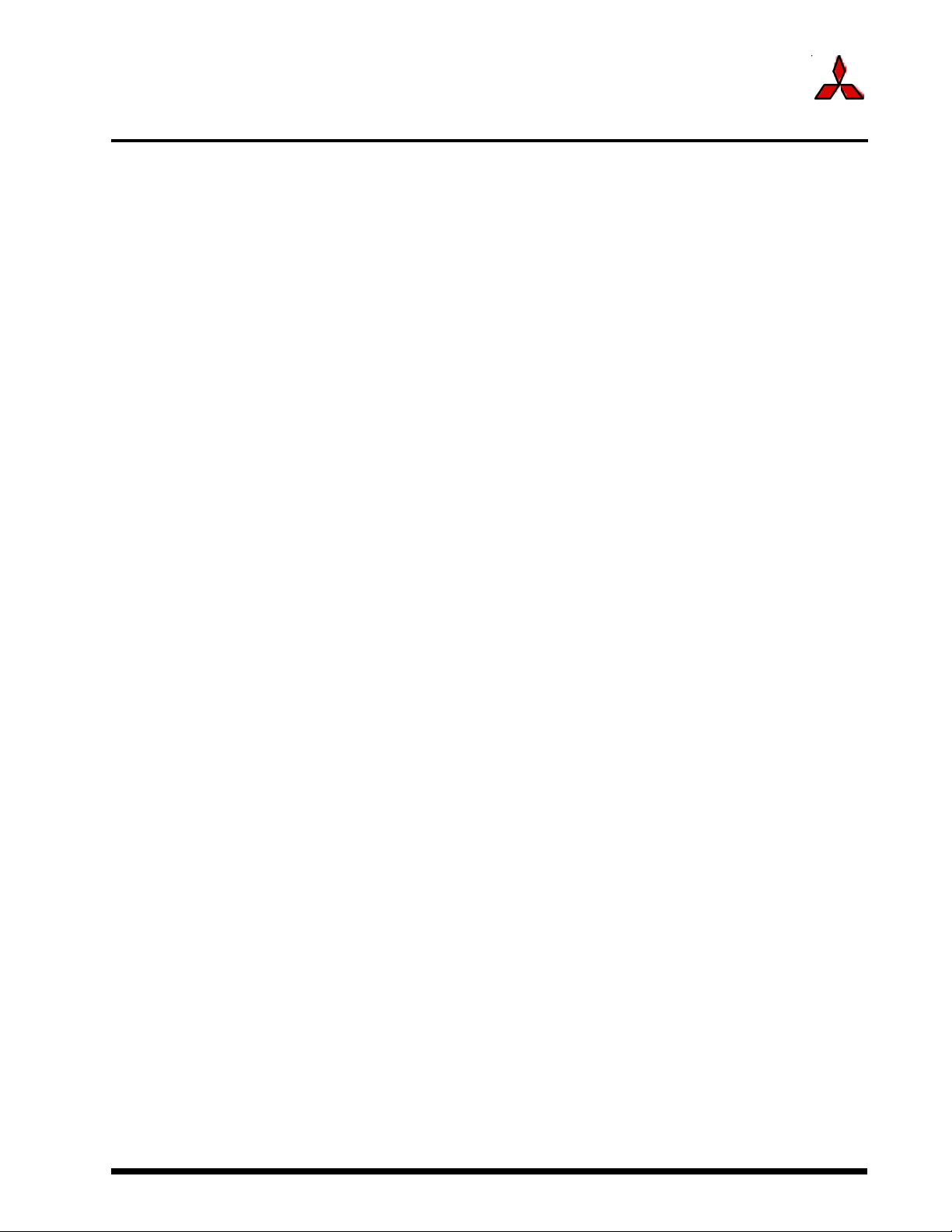

Pin Configuration

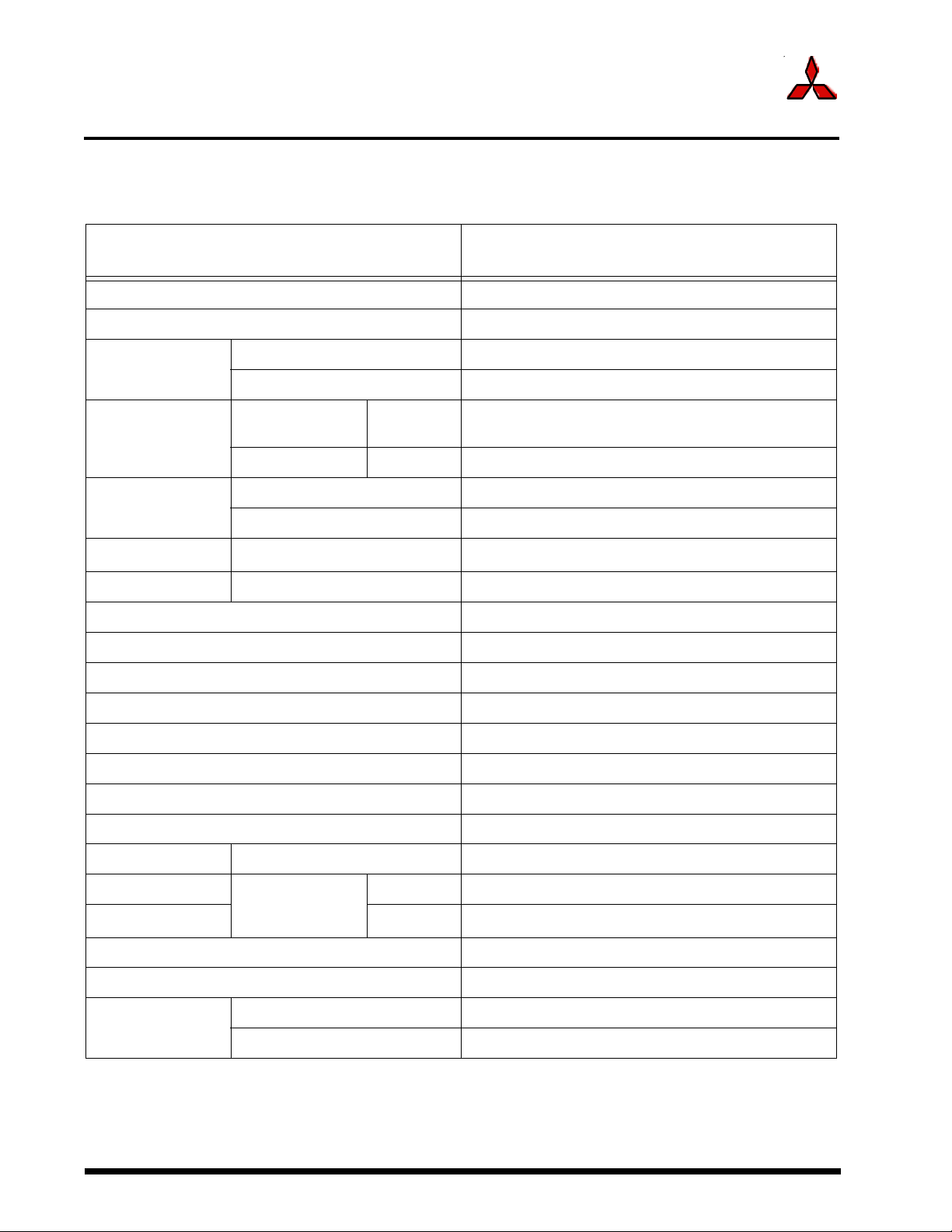

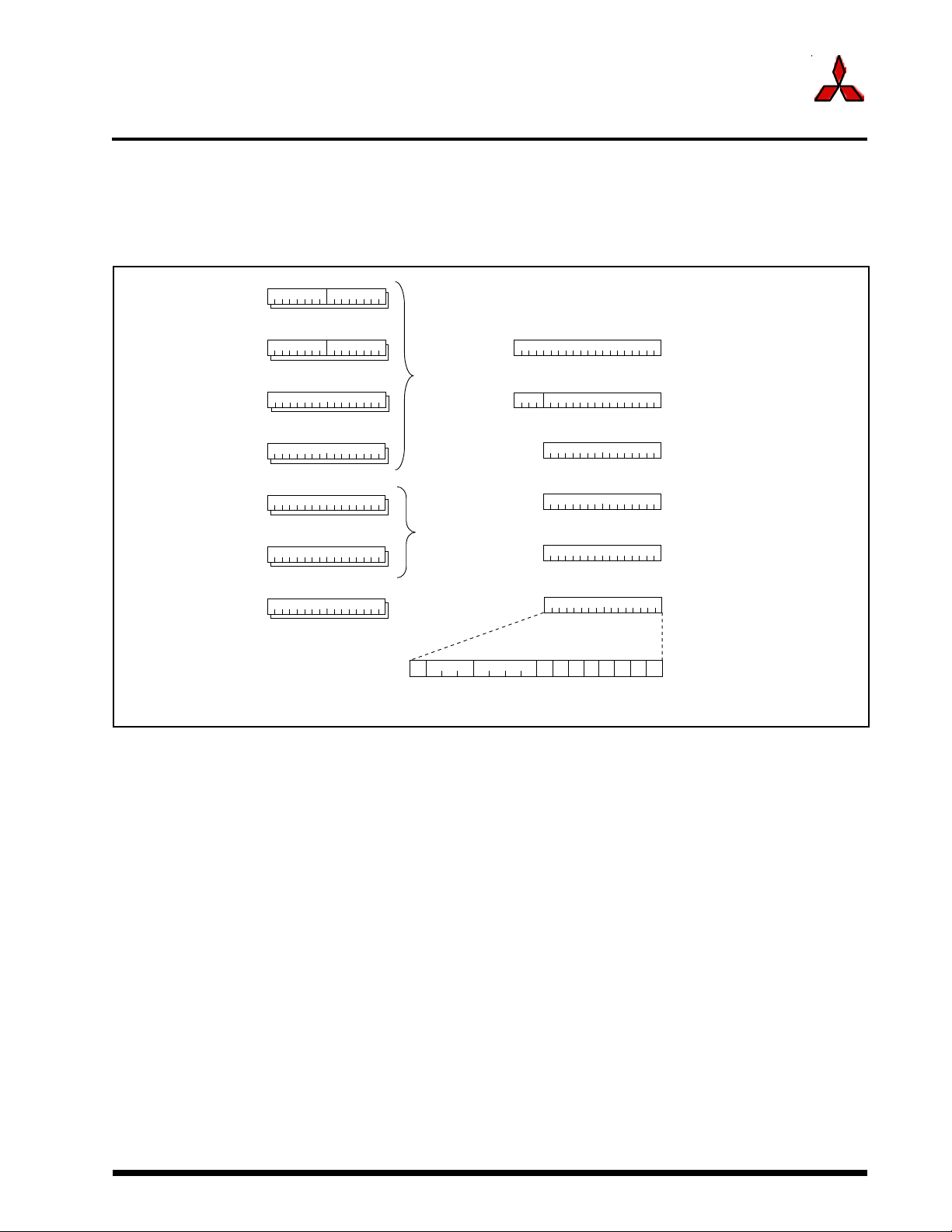

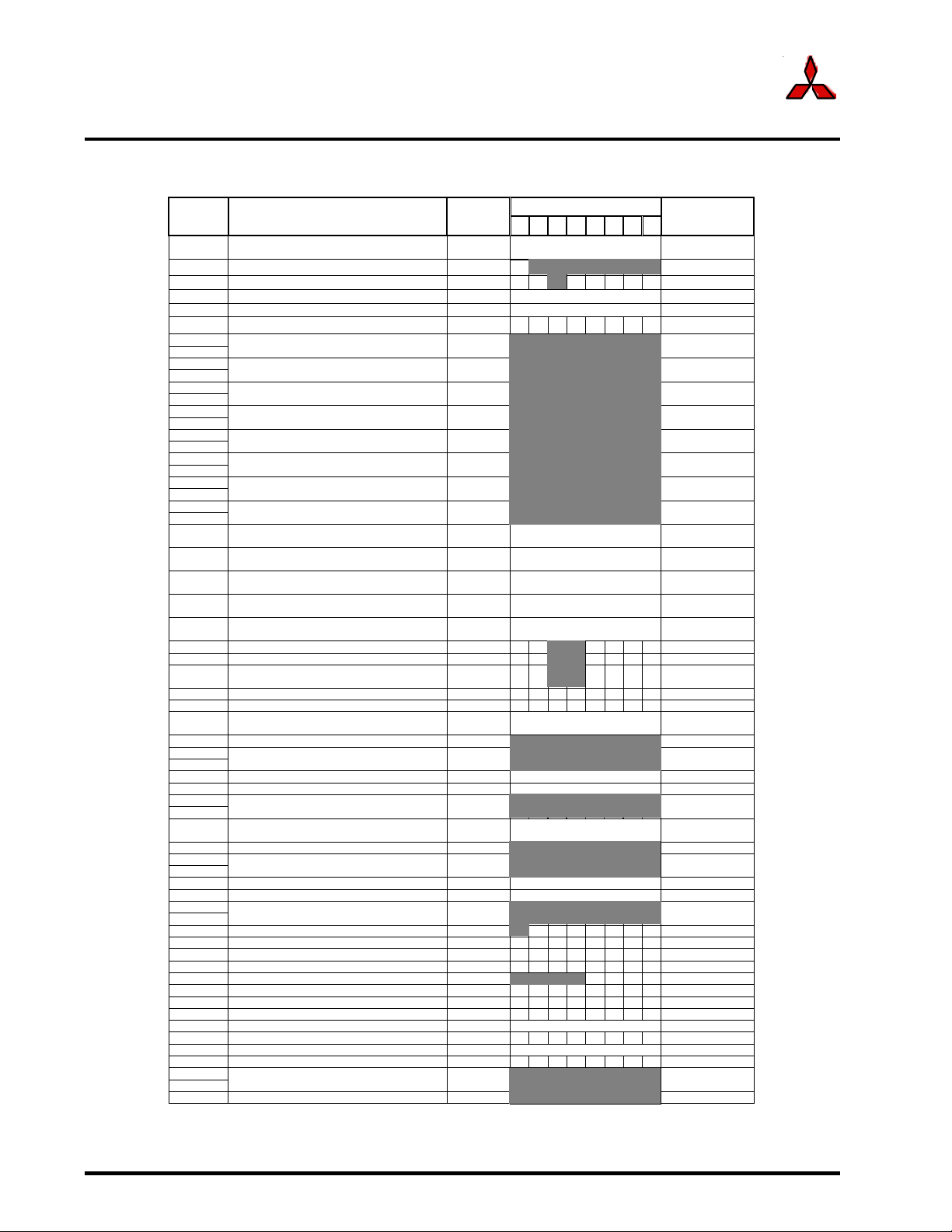

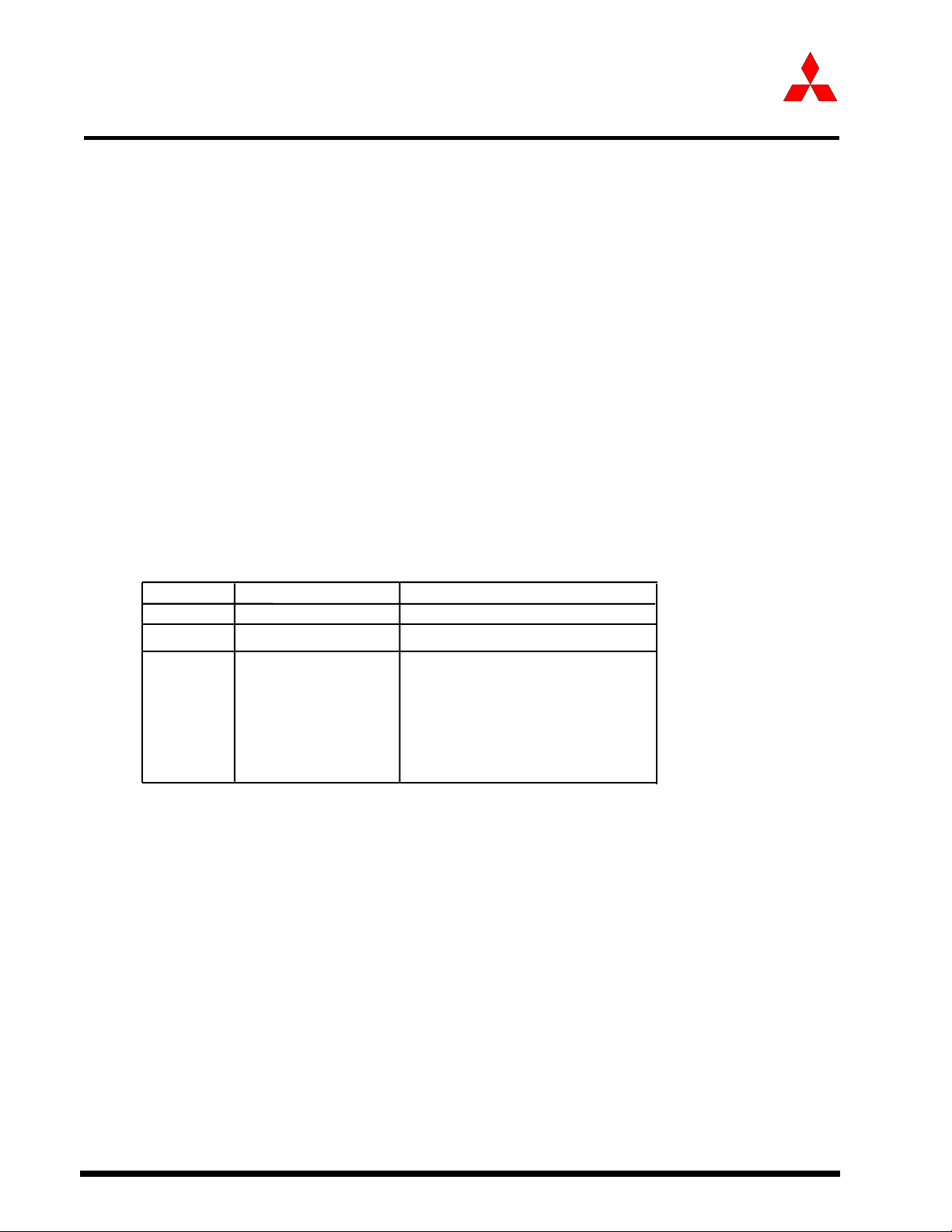

Figure 1.1 shows the pin configurations for M30222 group.

P97/ADtrg/LED7/Sin4/INT3

P100/AN0

P101/AN1

AVcc

Vref

AVss

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

P106/AN6/INT6

P107/AN7/INT7

P103/AN3

P102/AN2

P104/AN4

P105/AN5

VL1

VL2

VL3

COM2

COM0

COM1

C2

C1

P96/ANEX1/Sout4

P95/ANEX0/CLK4

P94/DA1/TB4in

P93/DA0/TB3in

P92/TB2in/Sout3

P91/TB1in/Sin3

P90/TB0in/INT2/CLK3

P86/INT1

CNVss

P85/Xcin

P84/Xcout

RESET

P83/NMI

P82/INT0

P81/TA4IN/INT5/U

P80/TA4OUT/INT5/U

P77/TA3IN/INT4

P76/TA3OUT/INT4

P75/TA2IN/W

P74/TA2OUT/W

P73/CTS2/RTS2/TA1IN/V

P72/CLK2/TA1OUT/V

P71/RxD2/SCL/TA0IN/TB5IN

P70/TxD2/SDA/TA0OUT

P67/TxD1/KI7

P66/RxD1/KI6

Xout

Vss

100

98

99

1

2

3

4

5

6

7

8

9

10

1211

13

14

Xin

V

cc

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

33

31

95

96

97

M30222FG

36

35

34

92

91

93

94

40

38

37

39

88

89

90

43

42

85

86

87

44

84

45

46

47

81

82

83

80

79

78

77

5758596061626364656667686970717273747576

53545556

52

51

49

48

50

COM3

SEG00

SEG01

SEG02

SEG03

SEG04

SEG05

SEG06

SEG07

SEG08

SEG09

SEG10

SEG11

SEG12

SEG13

SEG14

Vss

SEG15

VDC

Vcc

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24/P30

SEG25/P31

P65/CLK1/KI5

P64/CTS1/RTS1/CTS0/CLKS1/KI432

Fig. 1.1. Pin configuration (top view)

P61/CLK0/KI1

P63/TxD0/KI3

P62/RxD0/KI2

P60/CTS0/RTS0/KI0

SEG39/P47/RTP1

SEG37/P45

SEG38/P46/RTP0

SEG33/P41

SEG35/P4341SEG36/P44

SEG34/P42

SEG32/P40

SEG30/P36

SEG31/P37

SEG29/P35

SEG27/P33

SEG28/P34

SEG26/P32

1-4

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

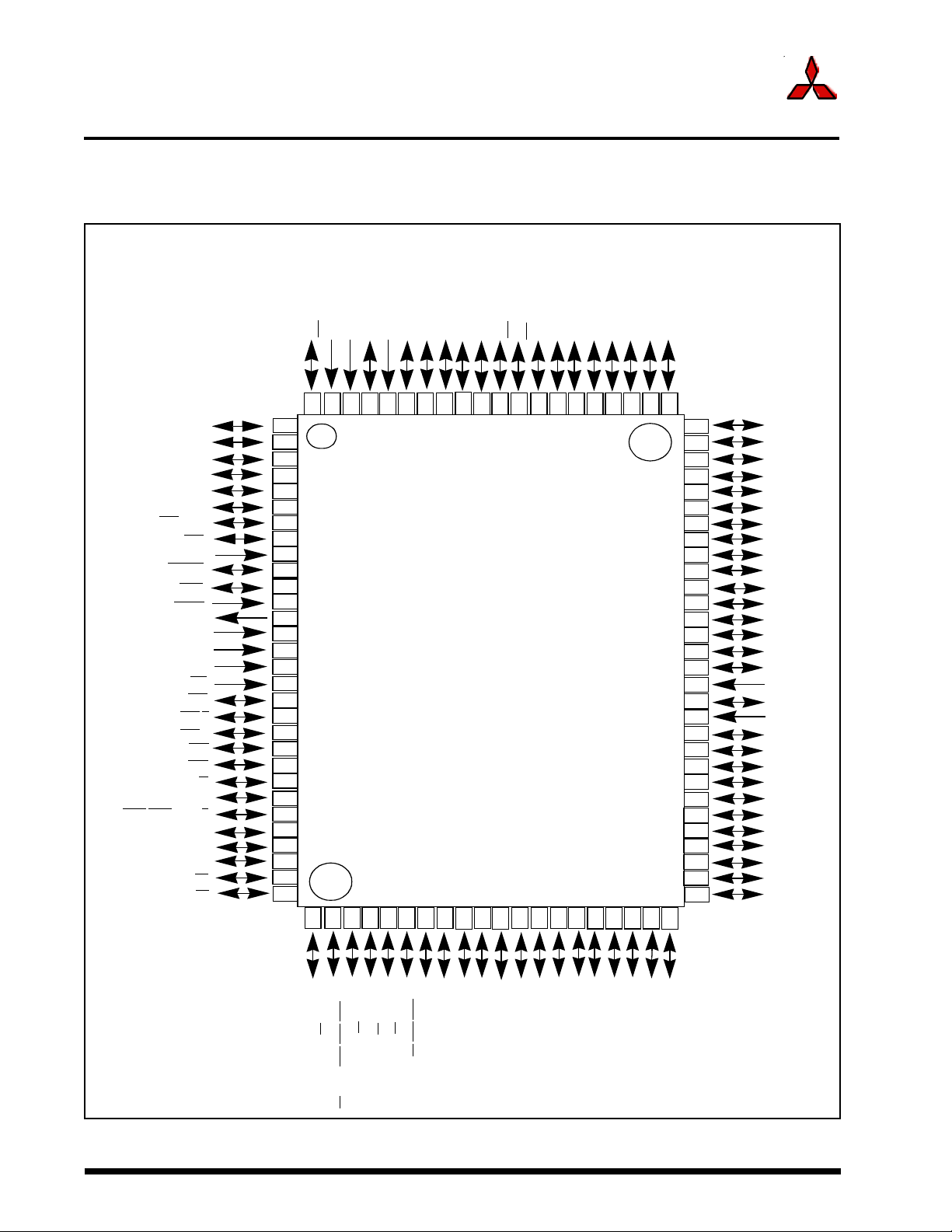

Block Diagram

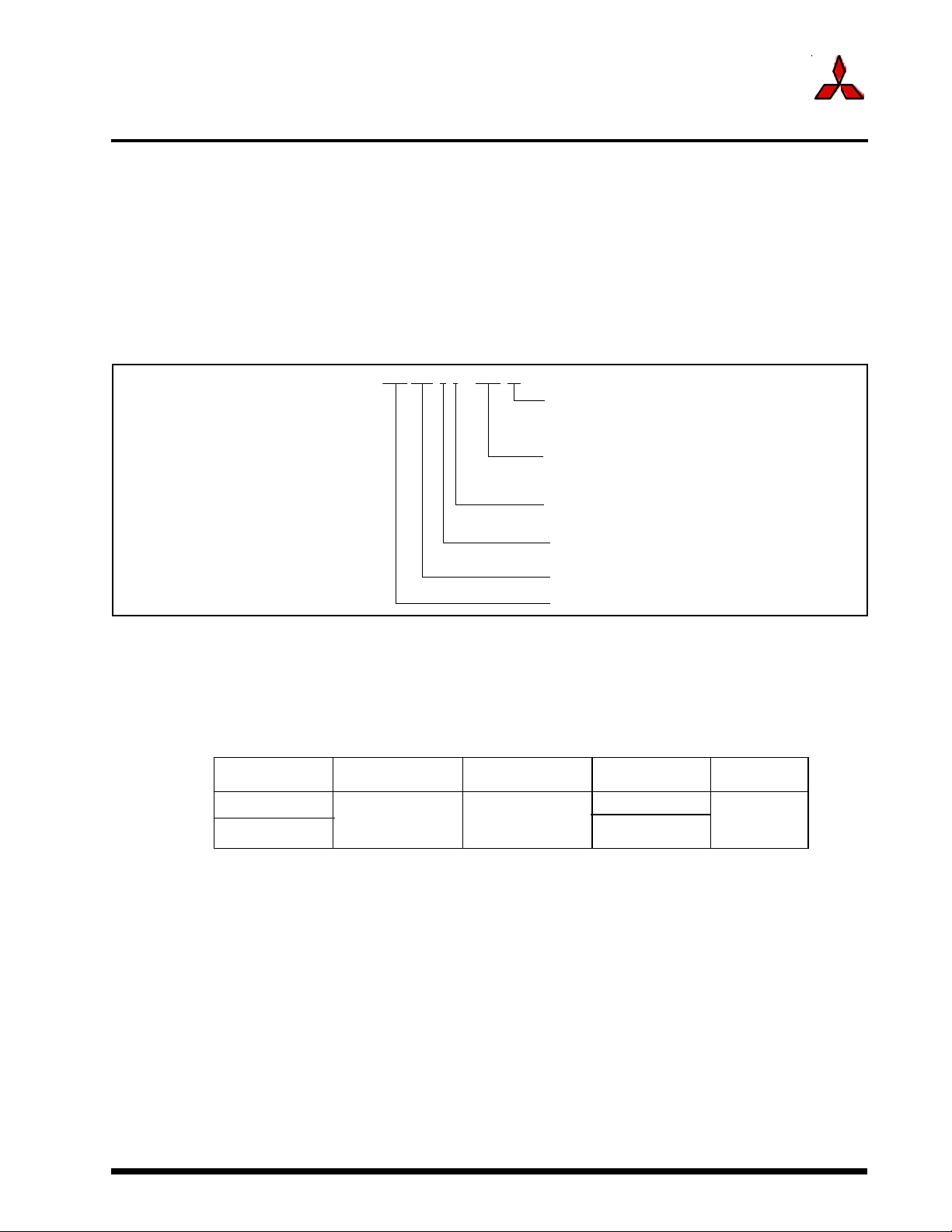

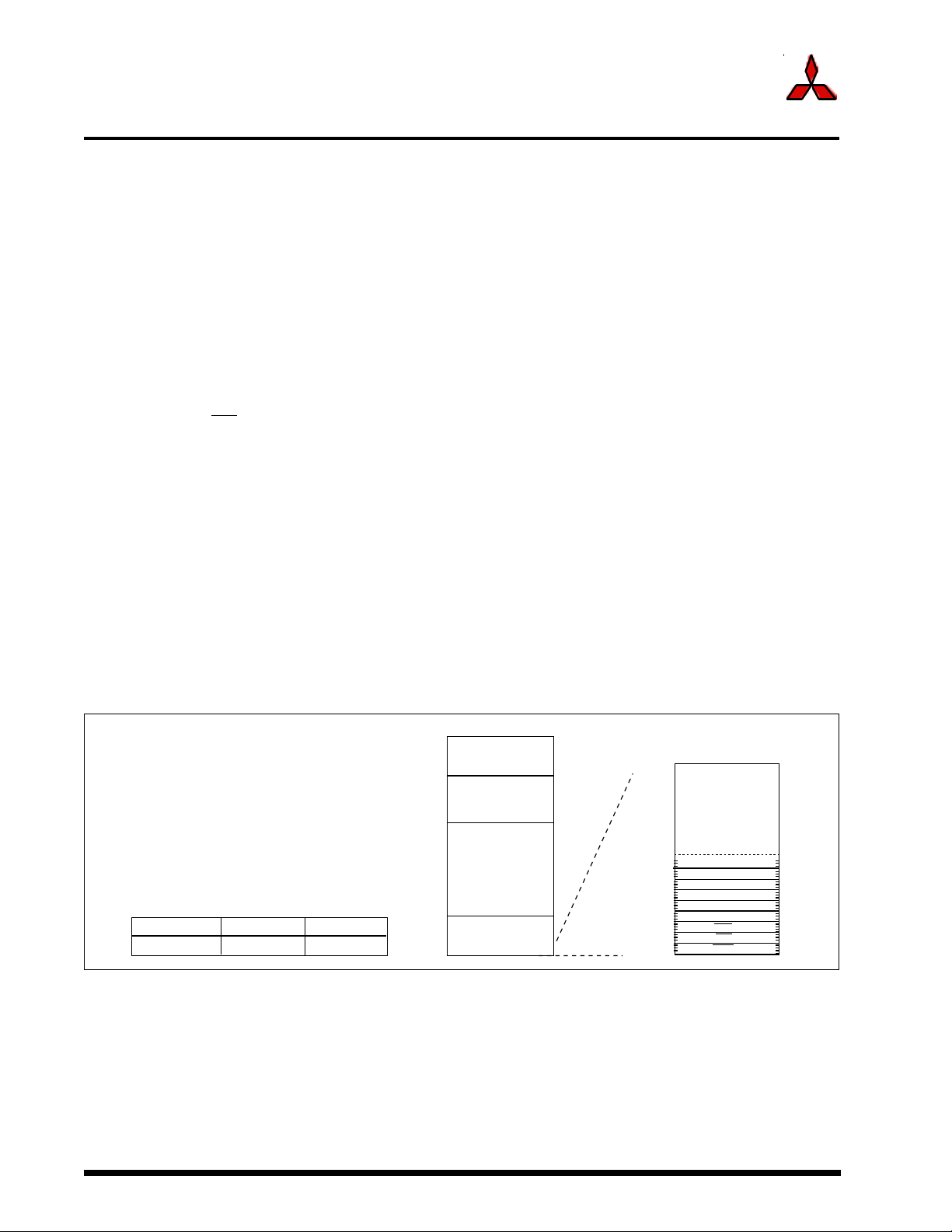

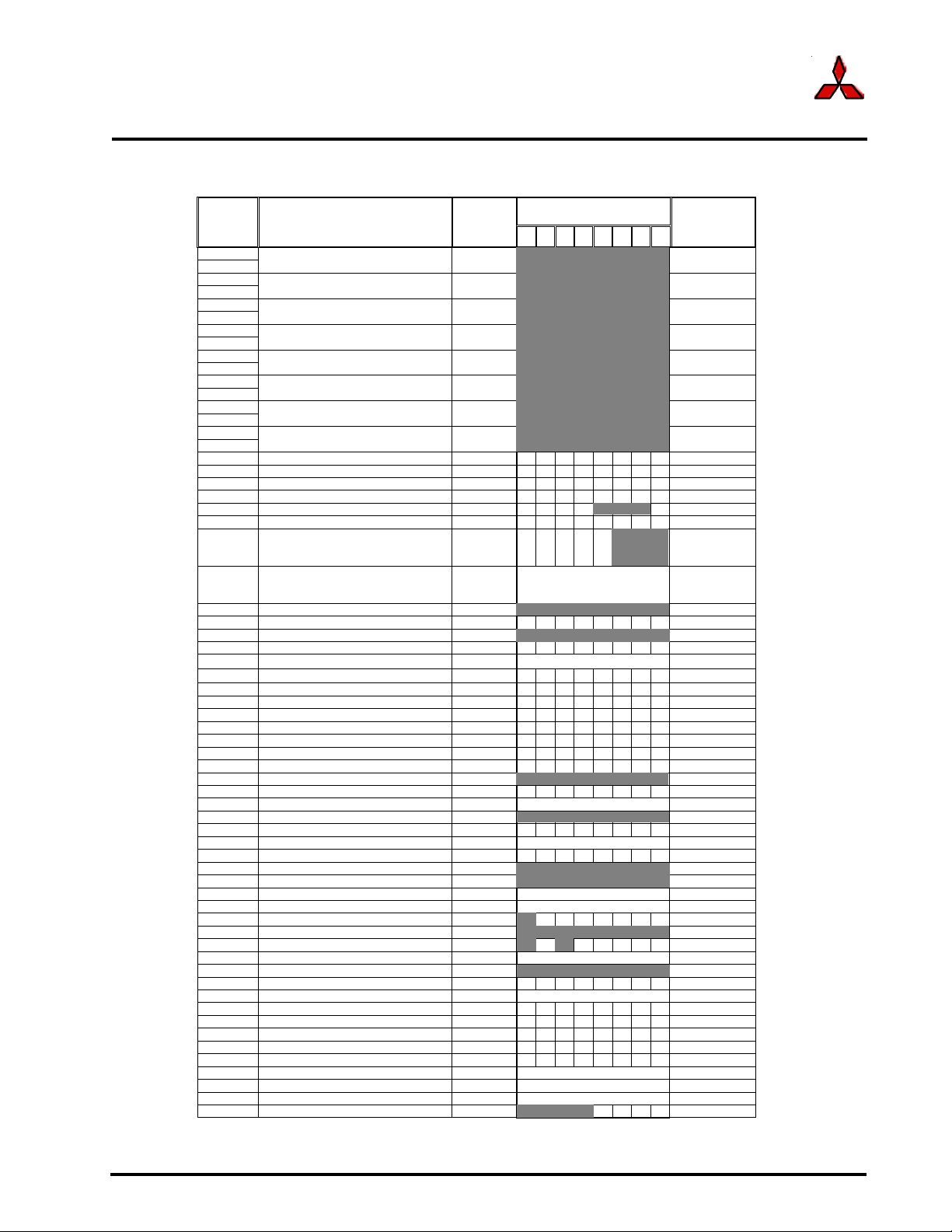

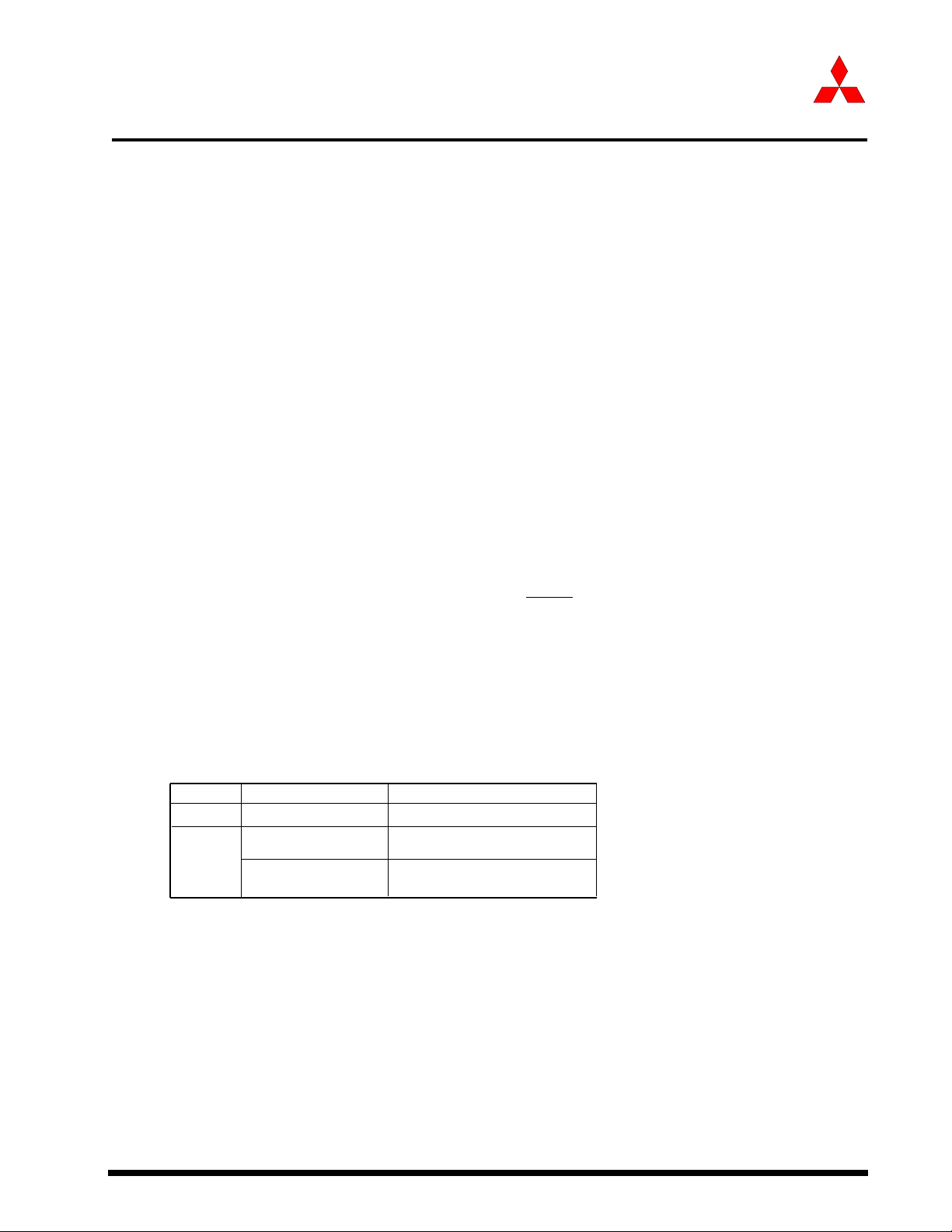

Figure 1.2 is a block diagram of the M30222 group.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

I/O ports

COM 0-3

Internal peripheral functions

Timer

Timer TA0 (16 bits)

Expandable up to 10 channels)

Timer TA1 (16 bits)

Timer TA2 (16 bits)

Timer TA3 (16 bits)

UART/clock synchronous SI/O

Timer TA4 (16 bits)

Timer TB0 (16 bits)

Timer TB1 (16 bits)

CRC

Timer TB2 (16 bits)

Timer TB3 (16 bits)

Timer TB4 (16 bits)

Timer TB5 (16 bits)

Watchdog timer

(15 bits)

DMAC

(2 channels)

D-A converter

(8 bits X 2 channels)

Note 1: ROM size depends on MCU type.

Note 2: RAM size depends on MCU type.

4

A-D converter

SEG 0-23

24

Port P3

SEG 24-31

(10 bits X 8 channels

(8 bits X 3 channels)

arithmetic circuit (CCITT

(Polynomial : X

16

+X

)

5

12

+1)

+X

M16C/60 series16-bit CPU core

Registers

R0LR0H

R0LR0H

R1H R1L

R1H R1L

R2

R2

R3

R3

A0

A0

A1

A1

FB

FB

SB FLG

Program counter

PC

Vector table

INTB

Stack pointer

ISP

USP

8

8

Port P4

SEG 32-39

System clock generator

IN-XOUT

X

X

CIN-XCOUT

Clock synchronous SI/O

(8 bits X 2 channels)

LCD Controller

VDC

Memory

ROM

(Note 1)

RAM

(Note 2)

Multiplier

Port P6

8

Port P7

8

Port P8

6

Port P8

3

Port P9

1

8

Port P10

8

Fig. 1.2. Block diagram of M30222 group

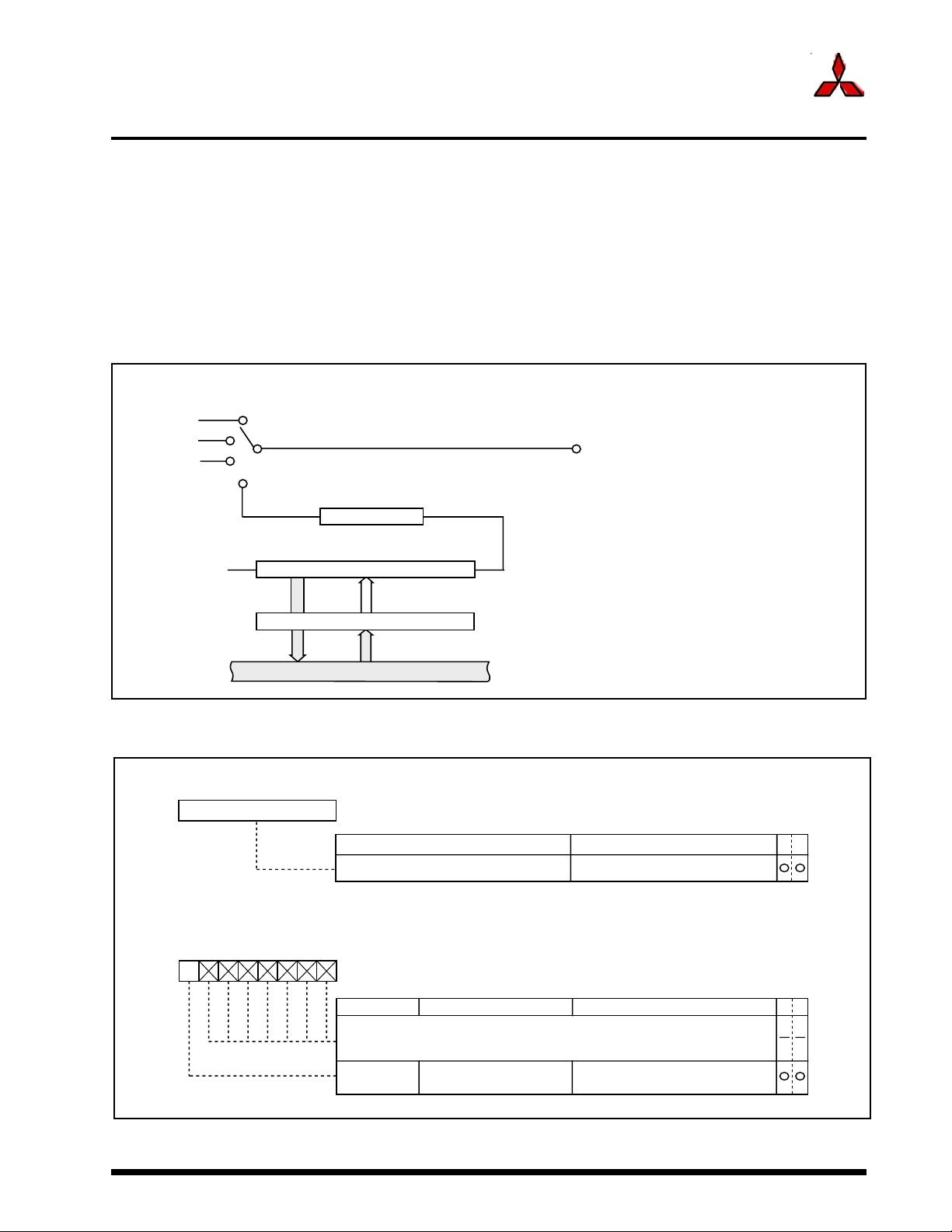

Memory Expansion

Figure 1.3 shows the Memory expansion for the M30222 group.

ROM size

(Bytes)

260K

128K

96K

64K

32K

M30222FC/FP/GP

20K SRAM

Flash Memory Version

Fig. 1.3. Memory Expansion

1-5

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

Performance Outline

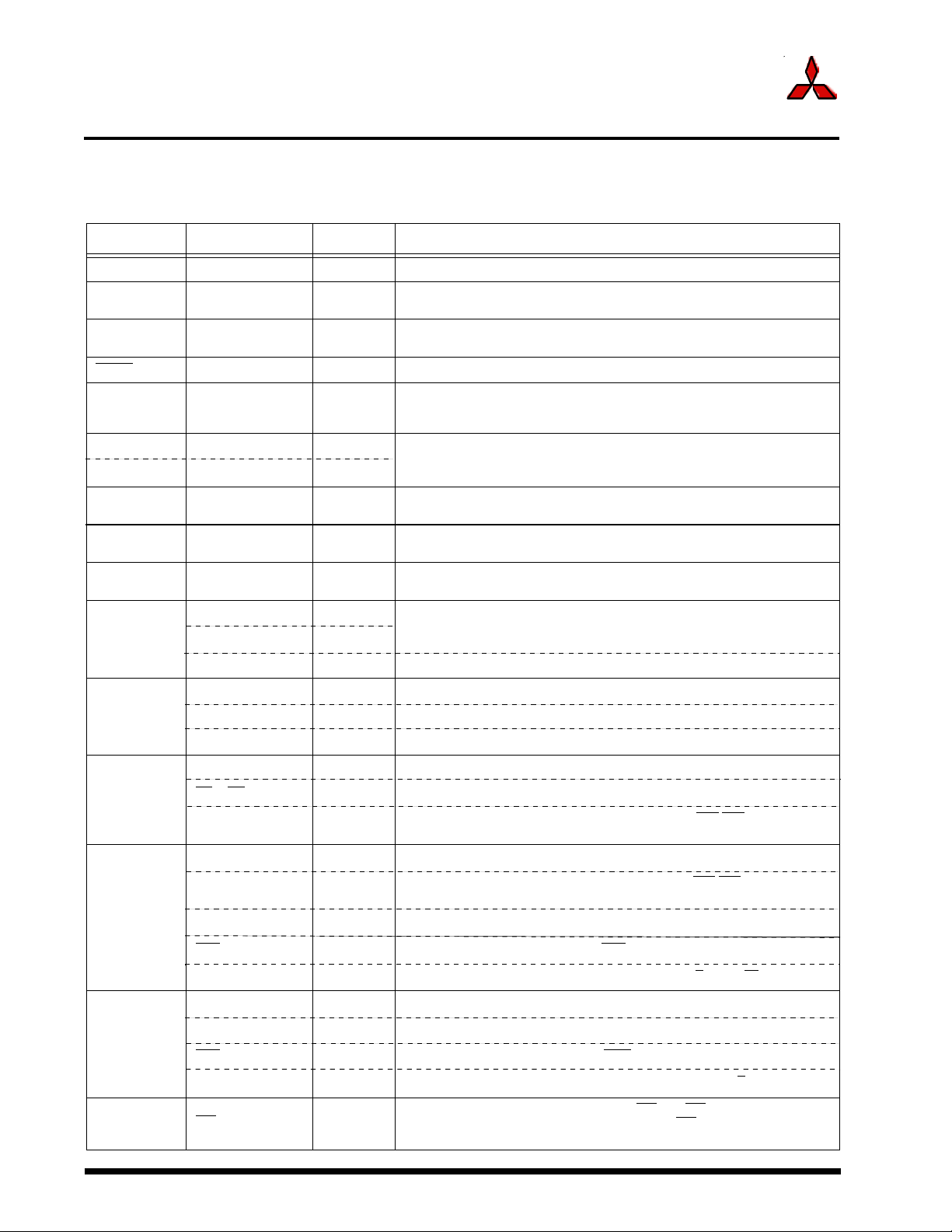

Table 1.1. Performance outline of the M30222 group

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Parameters

Number of basic instructions 91

Shortest instruction execution time 62.5ns f(Xin) = 16MHz

ROM 260K bytes

Memory size

Input/Output

Multifunctional

timer

Serial I/O UART0, UART1, UART2

A-D converter 10 bits x (8 + 2) channels

D-A converter 8 bits x 2

CRC calculation circuit CRC-CCITT

RAM 20K bytes

P3-P4, P6-P10

except P83

P83 I 1 bit x 1

TA0, TA1, TA2, TA3, TA4 16 bits x 5

TB0, TB1, TB2, TB3, TB4, TB5 16 bits x 6, three-phase motor control

SIO3, SIO4 (Clock synchronous) x 2

I/O 8 bits x 6, 7 bits x 1

(UART or clock synchronous) x 3, or I

Functions

2

C x 1

Watchdog timer 15 bits x 1 (with prescaler)

Interrupts 25 external, 8 internal sources, 4 software, 7 levels

Clock generating circuit 2 built-in clock generation circuits

Supply voltage 2.7 to 5.5V f(Xin) = 16 MHz, without software wait

Power consumption TBD

I/O characteristics I/O withstand voltage 5.5V

P3, P4 0.1 mA (high output), 2.5 mA (low output)

Output current

P6-P10 5 mA at 5V (excluding pins P7

Device configuration CMOS high performance silicon gate

Package 100-pin plastic mold QFP

COM0 to COM3 4 lines

LCD

SEG0 to SEG39 40 lines (16 lines shared with I/O ports)

, P71, P83)

0

1-6

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

Mitsubishi plans to release the following products in the M30222 group:

(1) Support for Flash memory version and mask ROM versions

(2) ROM capacity: 260 K bytes

(3) Package

100P6S-A : Plastic molded QFP (mask ROM version)

100P6Q-A: Plastic molded QFP

M16C Family Group

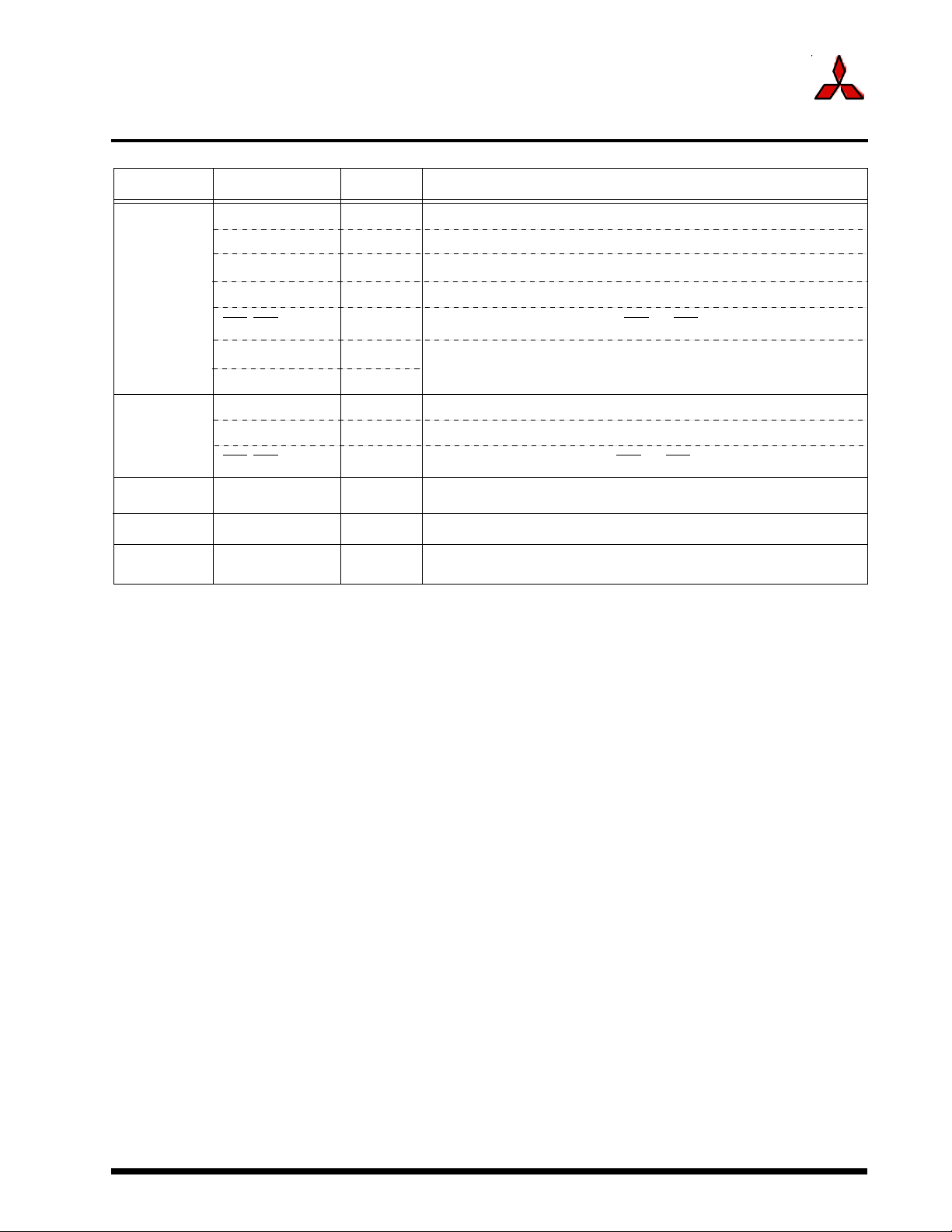

Figure 1.4 shows the M30222 family.

Type No. M 3 0 2 2 2 F G – X X X F P

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Package type:

FP: Package 100P6S-A

GP: 100P6Q-A

ROM No.

Omitted for flash memory version

ROM capacity:

G: 260K bytes

Memory type:

F : Flash memory version

M30222 Group

Fig. 1.4. Type No., memory size, and package

Table 1.2 shows the product list for the M30222 family.

Table 1.2. Product list

Type No. ROM Capacity RAM Capacity Package Type Remarks

M30222FGFP 100P6S-A

M30222FGGP 100P6Q-A

260 Kbytes

20 Kbytes

M16C Family

Flash

1-7

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Pin Description

Table 1.3. Pin Description for M30222 group

Pin name Signal name I/O type Function

Vcc, Vss Power supply Input Supply 2.7 to 5.5V to the Vcc pin and 0V to Vss

VDC Voltage Down

CNVss CNVss

RESET

Xin, Xout Main Clock Input/Output These pins are provided for the main clock generating circuit. Connect a ceramic reso-

/P8

P8

4

5

Xcout/Xcin Subclock Input/Output

AVcc

AVss

Vref

P3

to P3

0

7

to P4

P4

0

7

to P6

P6

0

7

to P7

P7

0

7

Converter

Reset input Input An “L” on this input resets the microcomputer.

I/O Port Input/Output These pins are provided for the subclock generating circuit. Connect a ceramic reso-

Analog power

supply + reference

Analog power

supply + reference

Reference voltage

input

I/O Port P3 Input/Output This is an 8-bit CMOS I/O port. It has an input/output direction register that allows the

RTP0_0 to RTP3_1 Output

SEG24 to SEG31 Output Pins in this port also function as SEG output for LCD and output for Real-time port.

I/O Port P4 Input/Output This is an 8-bit I/O port equivalent to P3.

SEG32 to SEG39 Output Pins in Port 4 also function as SEG outputs for LCD.

RTP4_0 to RTP7_1 Output Pins in Port 4 also function as Real-time port.

I/O Port P6 Input/Output This is an 8-bit I/O port equivalent to P3.

to KI7 Input Pins in Port 6 also function as key-input interrupts.

KI0

UART0, UART1 Input/Output Pins in Port 6 also function as transmit, receive, clock, and CTS

I/O Port P7 Input/Output This is an 8-bit I/O port equivalent to P3.

UART2

Timer A/B Input/Output Some pins in Port 7 serve as input/output for Timer A and Timer B.

INT4

Input Connects capacitor from VDC to Vss; or if not using VDC, connect 3.3V to VDC pin.

This pin is used to enable flash programming. Connect the pull-down resistor from

CNVss to Vss. Connect CNVss to enable flash programming.

nator or crystal between the Xin and the Xout pins. To use an externally derived clock,

input it to the Xin.

nator or crystal between the Xcin pin and leave the Xcout pin open. These pins also

function as CMOS I/O ports.

Input

Input This pin is a power supply input for A-D converter. Connect this pin to Vss.

Input This pin is a reference voltage input for the A-D converter.

Input/Output Some pins in Port 7 serve as transmit, receive, clock, and CTS

Input Pins P76 and P77 function as inputs for INT4.

This pin is a power supply input for the A-D converter. Connect this pin to Vcc.

user to set each pin for input or output individually. When used for input, the port can

be set by software to have or not have a pull resistor in units of four bits.

UART1.

UART2 provides I

2

C serial communications.

/RTS pins for UART0,

/RTS for UART2.

to P82, P8

P8

0

P8

3

Three-phase Output Some pins in Port 7 function as three-phase outputs for V, V

I/O Port P8 Input/Output P80 to P82, P86 are I/O ports equivalent to P3.

Timer A Input/Output Some pins in Port 8 serve as input/output for Timer A and Timer B.

6

INT5

Three-phase Output Pins P80 and P81 function as inputs three-phase outputs for U and U.

NMI Input

Input Pins P80 and P81 function as inputs for INT5.

P8

is an input only port that also functions for NMI. The NMI interrupt is generated

3

when the input at this pin changes from “H” to “L”. The NMI

celled using software. The pull-up resistor cannot be set for this pin.

1-8

, W, and W.

function cannot be can-

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Description

Pin name Signal name I/O type Function

I/O Port P9 Input/Output This is an 8-bit I/O equivalent to P3.

SIO 3/4 Input/Output Pins in Port 9 function as transmit, receive and clock for SIO3 and SIO4.

Timer B Input Some pins in Port 9 serve as TB3 and TB4 pins.

P9

to P9

0

7

D-A Output P9

, INT3 Input Pin P90 and P97 can be configured as INT2 and INT3.

INT2

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

and P94 can be configured to function as a digital to analog output.

3

ANEX0 Output

ANEX1 Input

I/O Port 10 Input/Output This is an 8-bit I/O port equivalent to P3.

to P10

P10

0

SEG23

SEG0 to

COM0 to COM3 COM ports Pins in this port function as COM output for LCD drive circuit.

VL1 to VL3 Power supply for

AN0 to AN7 Input Pins in Port 10 function as analog inputs.

7

INT6

, INT7 Input P106 and P107 function as inputs for INT6 and INT7.

SEG drive pins Pins in this port function as SEG output for LCD drive circuit.

LCD driver

These pins are used to connect to an optional external op amp.

Power supply input for LCD drive circuit.

1-9

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Memory

Operation of Functional Blocks

The M30222 group accommodates certain units in a single chip. These units include ROM and RAM to

store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations.

Also included are peripheral units such as timers, serial I/O, D-A converter, DMAC, CRC calculation

circuit, A-D converter, LCD, and I/O ports. The following explains each unit.

Memory

Figure 1.5 is a memory map of the M30222 group. The linear address space of 1M bytes extends from

address 0000016 to FFFFF16. From FFFFF16 down is ROM. For example, in the M30222FG-XXXFP, there

is 256K bytes of internal ROM from C000016 to FFFFF16. The vector table for fixed interrupts such as the

reset and NMI are mapped to FFFDC16 to FFFFF16. The starting address of the interrupt routine is stored

here. The address of the vector table for timer interrupts, etc., can be set as desired using the internal

register (INTB). See the section on interrupts for details.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

From 0040016 up is RAM. For example, in the M30222FG-XXXFP, 20K bytes of internal RAM is mapped

to the space from 0040016 to 053FF16. In addition to storing data, the RAM also stores the stack used

when calling subroutines and when interrupts are generated.

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for periph-

eral devices such as I/O ports, A-D converter, serial I/O, and timers, etc. Tables 1.5 to 1.9 show the

location of peripheral unit control registers. Any part of the SFR area that is not occupied is reserved and

cannot be used for other purposes.

00000

16

SFR area

053FF

16

16

Type No. Address YYYYY

M30222MG/FG/GP

Address XXXXX

C0000

For details, see Tables

16

00400

XXXXX

16

D0000

16

YYYYY16

16

16

FFFFF

16

1.5-1.9

Internal RAM area

Internal reserved

area

Internal ROM area

FFE0016

FFFDC

FFFFF

Undefined instruction

16

BRK instruction

Address match

Watchdog timer

16

Special page

vector table

Overflow

Single step

DBC

NMI

Reset

Fig. 1.5. Memory Map

1-10

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

CPU

Central Processing Unit (CPU)

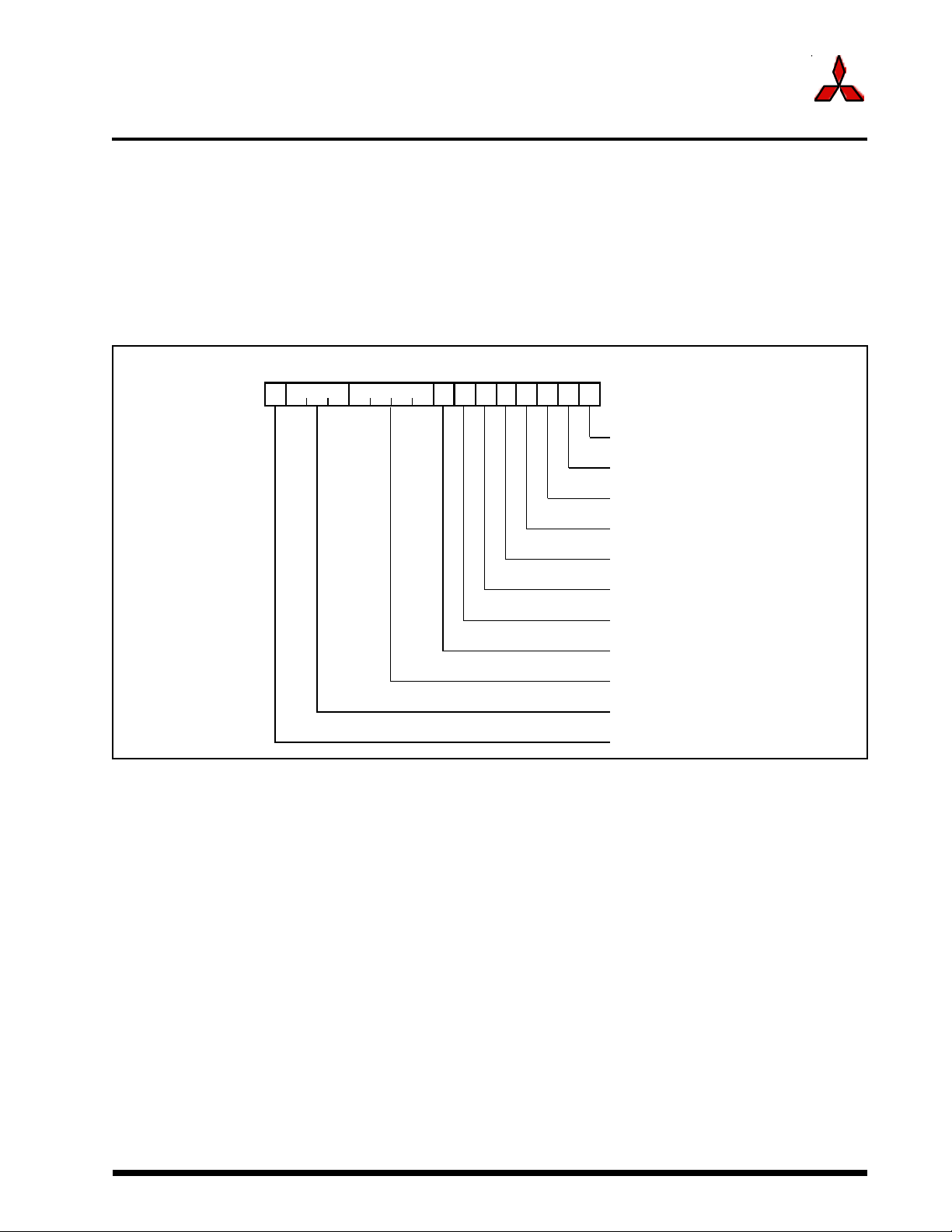

The CPU has a total of 13 registers shown in Figure 1.6. Seven of these registers (R0, R1, R2, R3, A0, A1,

and FB) come in two sets; therefore, these have two register banks.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

b15

(Note)

R0

(Note)

R1

(Note)

R2

(Note)

R3

(Note)

A0

(Note)

A1

(Note)

FB

H

b15 b8 b7 b0

H

b15 b0

b15

b15

b15 b0

b15 b0

These registers consist of two register banks.

Note:

b8 b7 b0

L

L

b0

b0

Data

registers

Address

registers

Frame base

registers

IPL

PC

b19

INTB

HL

b15

USP

b15

ISP

b15 b0

SB

b15

FLG

b0 b19

Program counter

b0

Interrupt table

register

b0

User stack pointer

b0

Interrupt stack

pointer

Static base

register

b0

Flag register

CDZSBOIU

Fig. 1.6. Central Processing Unit Register

(1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and

arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H),

and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can

use as 32-bit data registers (R2R0/R3R1).

(2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data

registers. These registers can also be used for address register indirect addressing and address register

relative addressing. In some instructions, registers A1 and A0 can be combined for use as a 32-bit

address register (A1A0).

(3) Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

1-11

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

CPU

(4) Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

(5) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector

table.

(6) Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each

configured with 16 bits. Your desired type of stack pointer (USP or ISP) can be selected by a stack

pointer select flag (U flag). This flag is located at the position of bit 7 in the flag register (FLG).

(7) Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

(8) Flag register (FLG)

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.7 shows the flag

register (FLG). The following explains the function of each flag:

• Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

• Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is “1”, a single-step interrupt is generated after instruction execution. This flag is cleared to

“0” when the interrupt is acknowledged.

• Bit 2: Zero flag (Z flag)

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, cleared to “0”.

• Bit 3: Sign flag (S flag)

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, cleared to “0”.

• Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is “0” ; register bank 1 is

selected when this flag is “1”.

• Bit 5: Overflow flag (O flag)

This flag is set to “1” when an arithmetic operation resulted in overflow; otherwise, cleared to “0”.

• Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is “0”, and is enabled when this flag is “1”. This flag is cleared to “0”

when the interrupt is acknowledged.

• Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is “0” ; user stack pointer (USP) is selected when this

flag is “1”.

This flag is cleared to “0” when a hardware interrupt is acknowledged or an INT instruction of software

interrupt Nos. 0 to 31 is executed.

1-12

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

CPU

• Bits 8 to 11: Reserved area

• Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor

interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is

enabled.

• Bit 15: Reserved area.

IPL

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

b0b15

CDZSBOIU

Flag register (FLG)

Carry flag

Debug flag

Zero flag

Fig. 1.7. Flag Register

Sign flag

Register bank select flag

Overflow flag

Interrupt enable flag

Stack pointer select flag

Reserved area

Processor interrupt priorit

Reserved area

1-13

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Reset

Reset

There are two kinds of resets; hardware and software. In both cases, operation is the same after the

reset. (See “Software Reset” for details.) This section explains on hardware resets.

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the

reset pin level “L” (0.2VCC max.) for at least 20 cycles. When the reset pin level is then returned to the

“H” level while main clock is stable, the reset status is cancelled and program execution resumes from

the address in the reset vector table.

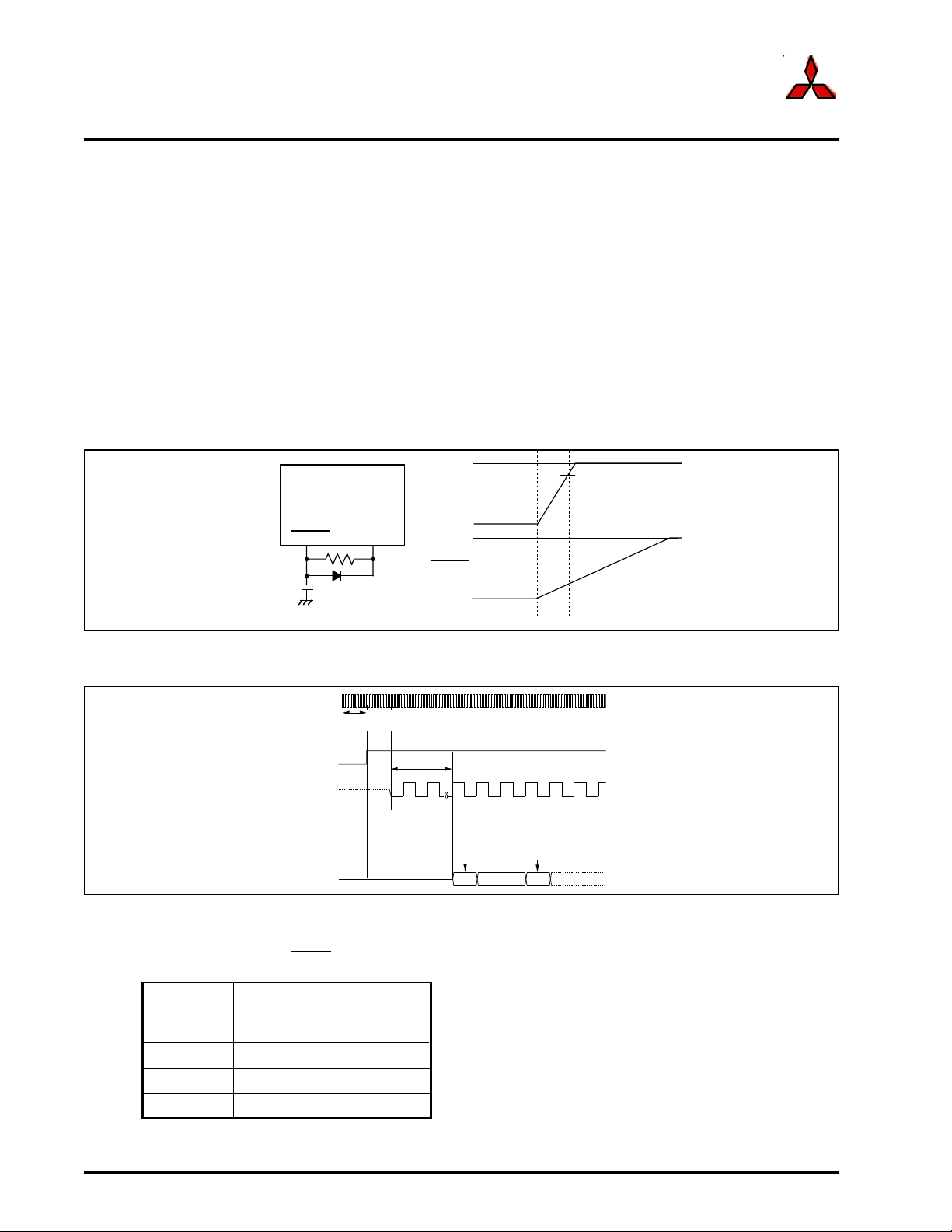

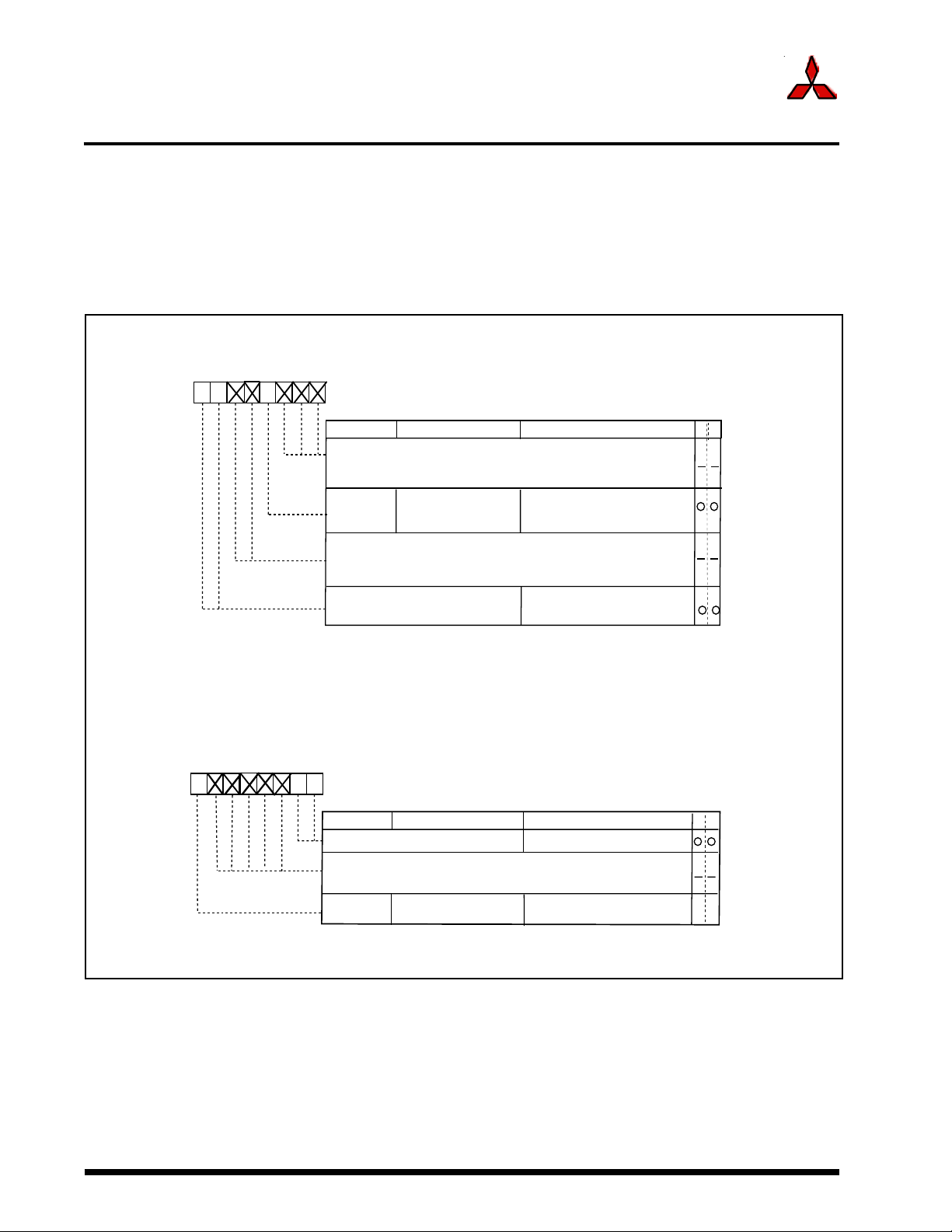

Figure 1.8 shows an example reset circuit. Figure 1.9 shows a reset sequence. Table 1.4 shows the pin

status when reset pin level is "L".

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

RESET

Example when Vcc = 5V

Fig. 1.8. Example of Reset Circuit

in

X

RESET

BCLK

Address

Fig. 1.9. Reset sequence

V

CC

More than 20

cycles are

BCLK

24cycles

5V

V

CC

0V

5V

RESET

0V

needed

FFFFC

16

FFFFE

Content of reset

vector

16

4.0V

0.8V

Table 1.4. Pin status when Reset pin level is "L"

level

Status

is

output

Pin name

P3, P4

P6 to P10

SEG0 to SEG23

COM0 to COM3

Input port (with a pull-up resistor)

Input port (floating)

"H" level is output

"H"

1-14

Under

development

MITSUBISHI MICROCOMPUTERS

Specifications in this manual are tentative and subject to change

Rev. G

Special function registers

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Special function registers

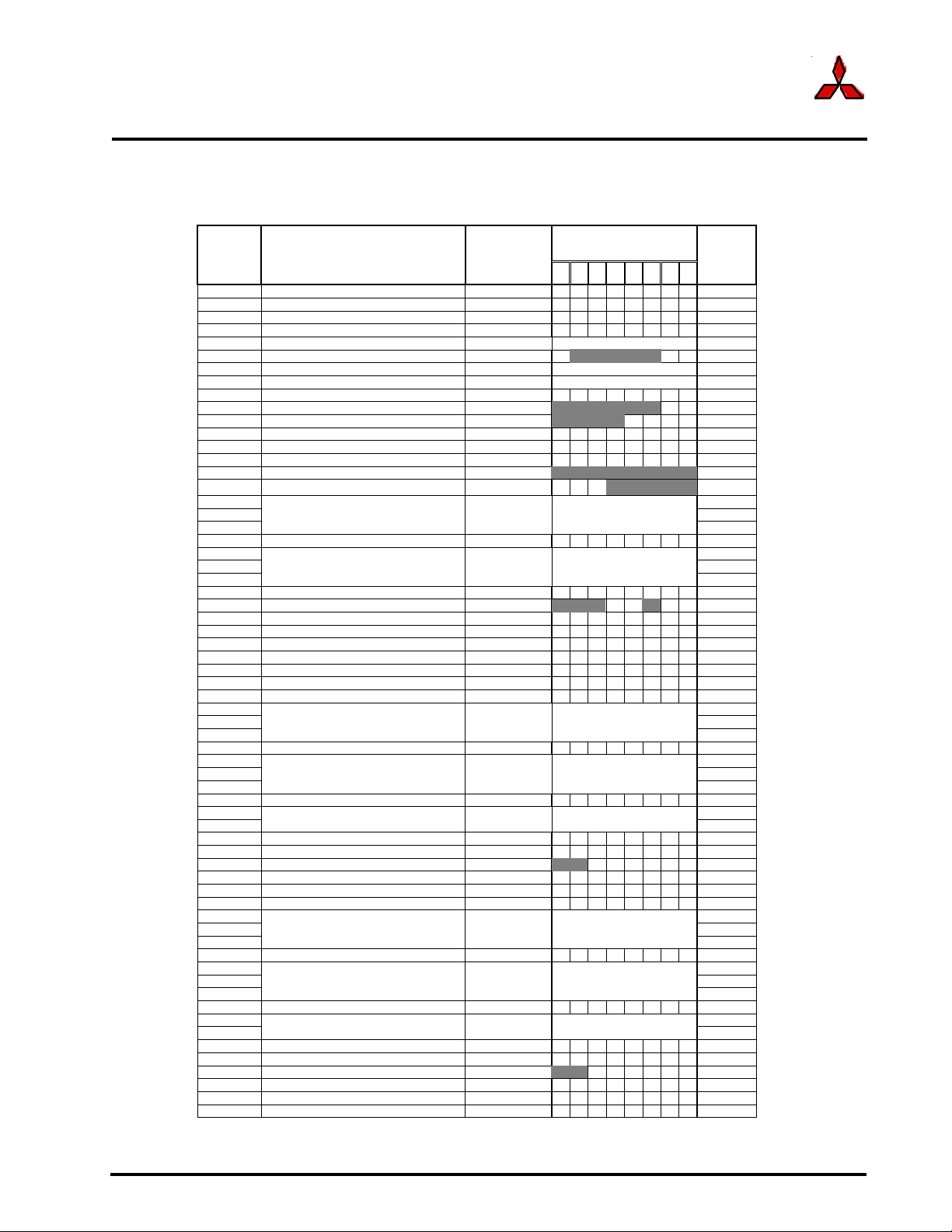

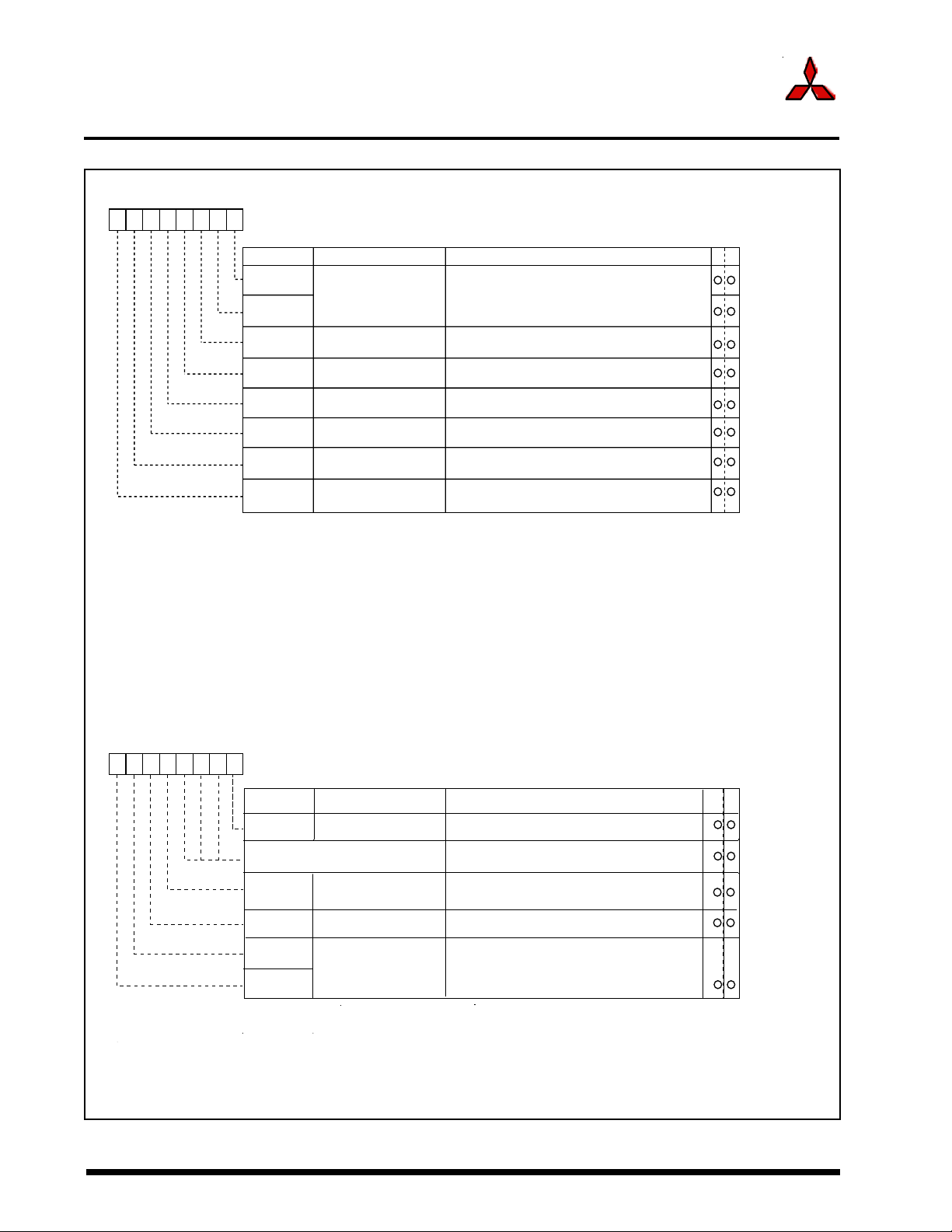

Table 1.5. Location and value after reset of peripheral unit control registers (1)

M30222 Group

Address Register Name Acronym

0000

16

0001

16

0002

16

0003

16

000416Processor mode register 0 PM0

000516Processor mode register 1 PM1

000616System clock control register 0 CM0

000716System clock control register 1 CM1

0008

16

000916Address match interrupt enable register AIER

000A16Protect register PRCR

000B

16

000C

16

000D

16

000E16Watchdog timer start register WDTS 1.57

000F16Watchdog timer control register WDC

0010

16

0011

0012

0013

0014

0015

0016

0017

001816VDC control register VDCC

0019

001A

001B

001C

001D

001E

001F

0020

0021

0022

0023

0024

0025

0026

0027

0028

0029

002A

002B

002C16DMA0 control register DM0CON

002D

002E

002F

0030

0031

0032

0033

0034

0035

0036

0037

0038

0039

003A

003B

003C16DMA1 control register DM1CON

003D

003E

003F

Address match interrupt register 0 RMAD0

16

16

16

16

Address match interrupt register 1 RMAD1

16

16

16

16

16

16

16

16

16

16

16

DMA0 source pointer SAR0

16

16

16

16

DMA0 destination pointer DAR0

16

16

16

DMA0 transfer counter TRC0

16

16

16

16

16

16

16

16

DMA1 source pointer SAR1

16

16

16

16

DMA1 destination pointer DAR1

16

16

16

DMA1 transfer counter TCR1

16

16

16

16

16

16

16

Value after ResetSFR

b7 b6 b5 b4 b3 b2 b1 b0

00

000

000

16

48

16

20

16

0000

00

16

00

16

00 00

?

?

?

000000

?

?

?

000000

Number

00

? = Undefined

Page

1.19

1.19

1.23

1.23

1.53

1.34

1.57

1.53

1.53

1.53

1.53

1.53

1.53

1.29

1.62

1.62

1.62

1.62

1.62

1.62

1.62

1.62

1.61

1.62

1.62

1.62

1.62

1.62

1.62

1.62

1.62

1.61

1-15

Under

development

MITSUBISHI MICROCOMPUTERS

Specifications in this manual are tentative and subject to change

Rev. G

Special function registers

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

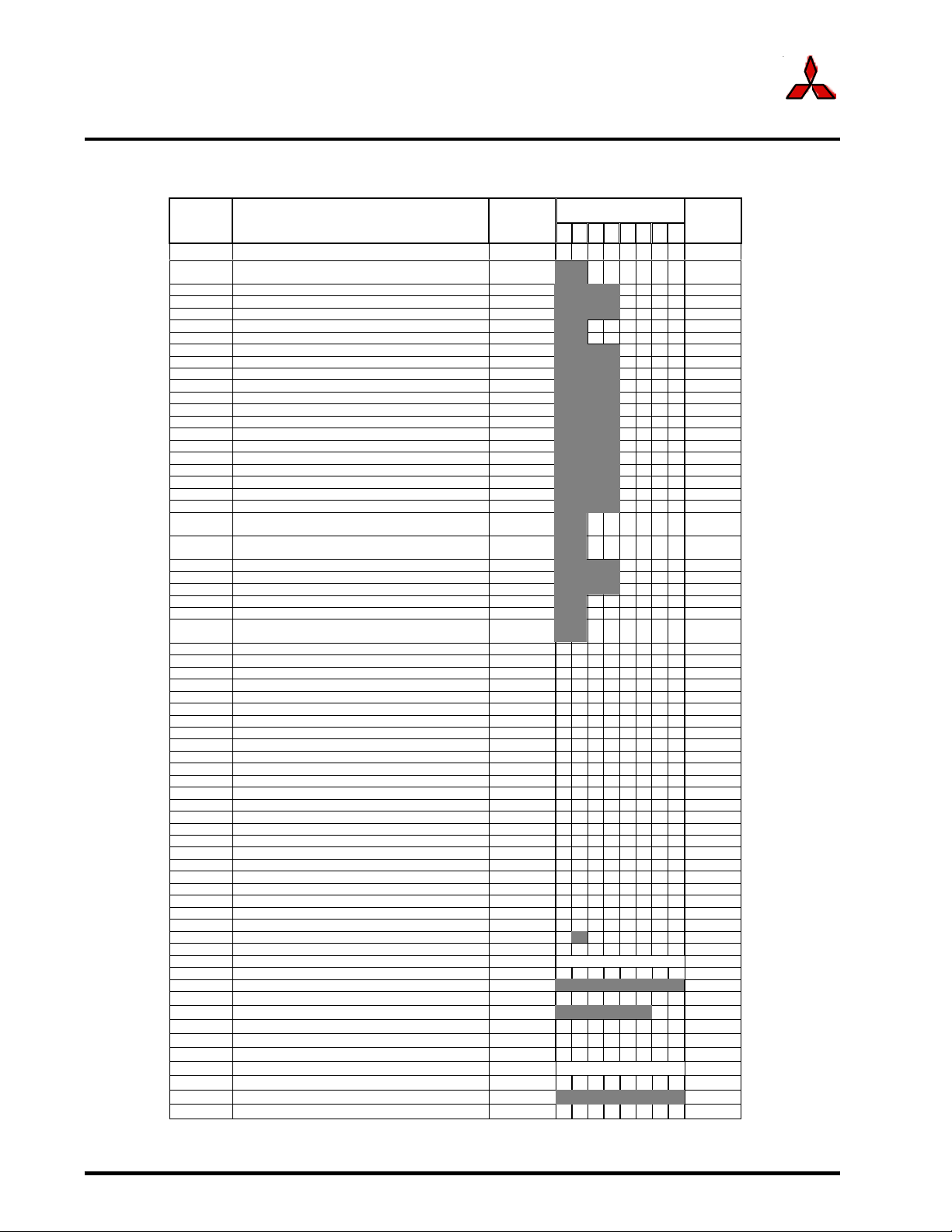

Table 1.6. Location and value after reset of peripheral unit control registers (2)

M30222 Group

Address

0044

0045

0046

0047

0048

0049

004A

004B

004C

004D

004E

004F

0050

0051

0052

0053

0054

0055

0056

0057

0058

0059

005A

005B

005C

005D

005E

005F

Register Name Acronym

INT3 interrupt control register

16

SI/O4 interrupt control register

Timer B5 interrupt control register TB5IC

16

Timer B4 interrupt control register TB 4IC

16

Timer B3 interrupt control register TB3IC

16

INT7 interrupt control register INT7IC

16

INT6 interrupt control register INT6IC

16

Bus collision detection interrupt control register BCNIC

16

DMA0 interrupt control register DM0IC

16

DMA1 interrupt control register DM1IC

16

Key input interrupt control register KUPIC

16

A-D conversion interrupt control register ADIC

16

UART2 transmit interrupt control register S2TIC

16

UART2 receive interrupt control register S2RIC

16

UART0 transmit interrupt control register S0TIC

16

UART0 receive interrupt control register S0RIC

16

UART1 transmit interrupt control register S1TIC

16

UART1 receive interrupt control register S1RIC

16

Timer A0 interrupt control register TA0IC

16

Timer A1 interrupt control register TA1IC

16

Timer A2 interrupt control register TA2IC

16

Timer A3 interrupt control register

16

INT4 interrupt control register

Timer A4 interrupt control register

16

INT5 interrupt control register

Timer B0 interrupt control register TB0IC

16

Timer B1 interrupt control register TB1IC

16

Timer B2 interrupt control register TB2IC

16

INT0 interrupt control register INT0IC

16

INT1 interrupt control register INT1IC

16

INT2 interrupt control register

16

SI/O3 interrupt control register

INT3IC

S4IC

TA3IC

INT4IC

TA4IC

INT5IC

INT2IC

S3IC

Value after ResetSFR

b7 b6 b5 b4 b3 b2 b1 b0

000000

0000

0000

0000

000000

000000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

000000

000000

0000

0000

0000

000000

000000

000000

Page

Number

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

1.39

0100

0101

0102

0103

0104

0105

0106

0107

0108

0109

010A

010B

010C

010D

010E

010F

0110

0111

0112

0113

0120

0121

0122

0123

0124

0125

0126

0127

0128

0129

0130

0131

0132

0133

LCD RAM0 LRAM0

16

LCD RAM1 LRAM1

16

LCD RAM2 LRAM2

16

LCD RAM3 LRAM3

16

LCD RAM4 LRAM4

16

LCD RAM5 LRAM5

16

LCD RAM6 LRAM6

16

LCD RAM7 LRAM7

16

LCD RAM8 LRAM8

16

LCD RAM9 LRAM9

16

LCD RAM10 LRAM10

16

LCD RAM11 LRAM11

16

LCD RAM12 LRAM12

16

LCD RAM13 LRAM13

16

LCD RAM14 LRAM14

16

LCD RAM15 LRAM15

16

LCD RAM16 LRAM16

16

LCD RAM17 LRAM17

16

LCD RAM18 LRAM18

16

LCD RAM19 LRAM19

16

LCD mode register LCDM

16

16

Segment output enable register SEG

16

16

LCD frame frequency counter LCDTIM 1.143

16

16

Key input mode register KUPM

16

16

16

16

LCD expansion register LEXP

16

16

LCD clock divide counter LCDC 1.144

16

16

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

????????

0 000000

00

16

00

16

? = Undefined

00

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.146

1.143

1.143

1.52

1.144

1-16

Under

development

MITSUBISHI MICROCOMPUTERS

Specifications in this manual are tentative and subject to change

Rev. G

Special function registers

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Table 1.7. Location and value after reset of peripheral unit control registers (3)

M30222 Group

Address

Register Name Acronym

034016Timer B3, 4, 5 count start flag TBSR

0341

16

0342

0343

0344

0345

0346

0347

Timer A1-1 register TA11 1.94

16

16

Timer A2-1 register TA21 1.94

16

16

Timer A4-1 register TA41 1.94

16

16

034816Three-phase PWM control register 0 INVC0

034916Three-phase PWM control register 1 INVC1

034A16Three-phase output buffer register 0 IDB0

034B16Three-phase output buffer register 1 IDB1

Value after ResetSFR

b7 b6 b5 b4 b3 b2 b1 b0

000

00

16

00

16

3F

16

3F

16

Page

Number

1.85

1.92

1.92

1.93

1.93

034C16Dead time timer DTT 1.93

034D16Timer B2 interrupt occurrence frequency set counter ICTB2 1.93

034E

16

034F

16

0350

16

0351

0352

0353

0354

0355

035B16Timer B3 mode register TB3MR

Timer B3 register TB3 1.85

16

16

Timer B4 register TB4 1.85

16

16

Timer B5 register TB5 1.85

16

00 0000

1.87

1.88,

1.90

035C16Timer B4 mode register TB4MR

00 0000

1.87

1.88,

1.90

035D16Timer B5 mode register TB5MR

035E16Interrupt cause select register 0 IFSR0

035F16Interrupt cause select register 1 IFSR1

00 0000

00

16

00

16

1.87

1.88,

1.90

1.49

1.49

036016SI/O3 transmit/receive register S3TRR 1.138

0361

16

036216SI/O3 control register S3C

40

16

1.138

036316SI/O3 bit rate generator S3BRG 1.138

036416SI/O4 transmit/receive register S4TRR 1.138

0365

16

036616SI/O4 control register S4C

40

16

1.138

036716SI/O4 bit rate generator S4BRG 1.138

036C16Clock divided control register CDCC

036D

16

0

1.24

036E16Clock divided counter CDC 1.24

037516UART2 special mode register 3 U2SMR3

037616UART2 special mode register 2 U2SMR2

037716UART2 special mode register U2SMR

037816UART2 transmit/receive mode register U2MR

00

16

00

16

00

16

00

16

1.112

1.130

1.112,

1.134

1.111,

1.130

1.108,

1.114,

1.120

037916UART2 bit rate generator U2BRG 1.107

037A

16

037B

037C16UART2 transmit/receive control register 0 U2C0

037D16UART2 transmit/receive control register 1 U2C1

037E

037F

UART2 transmit buffer register U2TB 1.107

16

16

UART2 receive buffer register U2RB 1.102

16

08

16

02

16

1.110

? = Undefined

1-17

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Special function registers

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

SFR

Address

038016Count start flag TABSR

038116Clock prescaler reset flag CPSRF

Register Name Acronym

038216One-shot start flag ONSF

038316Trigger select register TRGSR

038416Up-down flag UDF

0385

16

0386

0387

0388

0389

038A

038B

038C

038D

038E

038F

0390

0391

0392

0393

0394

0395

039616Timer A0 mode register TA0MR

Timer A0 TA0

16

16

Timer A1 TA1

16

16

Timer A2 TA2

16

16

Timer A3 TA3

16

16

Timer A4 TA4

16

16

Timer B0 TB0

16

16

Timer B1 TB1

16

16

Timer B2 TB2

16

16

039716Timer A1 mode register TA1MR

039816Timer A2 mode register TA2MR

039916Timer A3 mode register TA3MR

039A16Timer A4 mode register TA4MR

039B16Timer B0 mode register TB0MR

039C16Timer B1 mode register TB1MR

039D16Timer B2 mode register TB2MR

039E

16

039F

16

03A016UART0 transmit/receive mode register U0MR

03A116UART0 bit rate generator U0BRG 1.107

03A2

03A3

03A416UART0 transmit/receive control register 0 U0C0

03A516UART0 transmit/receive control register 1 U0C1

03A6

03A7

03A816UART1 transmit/receive mode register U1MR

03A916UART1 bit rate generator U1BRG 1.107

03AA

03AB

03AC16UART1 transmit/receive control register 0 U1C0

03AD16UART1 transmit/receive control register 1 U1C1

03AE

03AF

03B016UART transmit/receive control register 2 UCON

03B1

03B2

03B3

03B416Flash memory control register (Note) FMCR

03B5

03B6

03B7

03B816DMA0 request cause select register DM0SL

03B9

03BA16DMA1 DM1SL

03BB

03BC

03BD

03BE16CRC input register CRCIN 1.164

UART0 transmit buffer register U0TB 1.107

16

16

UART0 receive buffer register U0RB 1.107

16

16

16

UART1 transmit buffer register U1TB 1.107

16

16

UART1 receive buffer register U1RB 1.107

16

16

16

16

16

16

16

16

16

16

CRC data register

16

CRCD

Value after Reset

b7 b6 b5 b4 b3 b2 b1 b0

00

0

00 00000

00 0000

00 0000

00 0000

0000000

16

00

16

00

16

00

16

00

16

00

16

00

16

00

16

00

16

08

16

02

16

00

16

08

16

02

16

0001

00

16

00

16

1.71, 1.85, 1.94

1.72, 1.85

1.72

1.72, 1.94

1.71

1.71

1.71, 1.90

1.71, 1.90

1.71

1.71, 1.90

1.83

1.83

1.83, 1.90

1.70, 1.73, 1.74,

1.77, 1.78

1.70, 1.73, 1.74,

1.77, 1.78, 1.95

1.70, 1.73, 1.74,

1.77, 1.78, 1.95

1.70, 1.72, 1.73,

1.77, 1.78

1.70, 1.73, 1.74,

1.77, 1.78, 1.95

1.84, 1.87, 1.90

1.84, 1.87, 1.90

1.84, 1.87, 1.90,

1.95

1.108, 1.114,

1.120

1.109

1.110

1.108, 1.114,

1.120

1.109

1.110

1.111

1.176

1.60

1.61

1.164

Note: This register only exists in flash memory version

? = Undefined

Page Number

1-18

Under

development

MITSUBISHI MICROCOMPUTERS

Specifications in this manual are tentative and subject to change

Rev. G

Special function registers

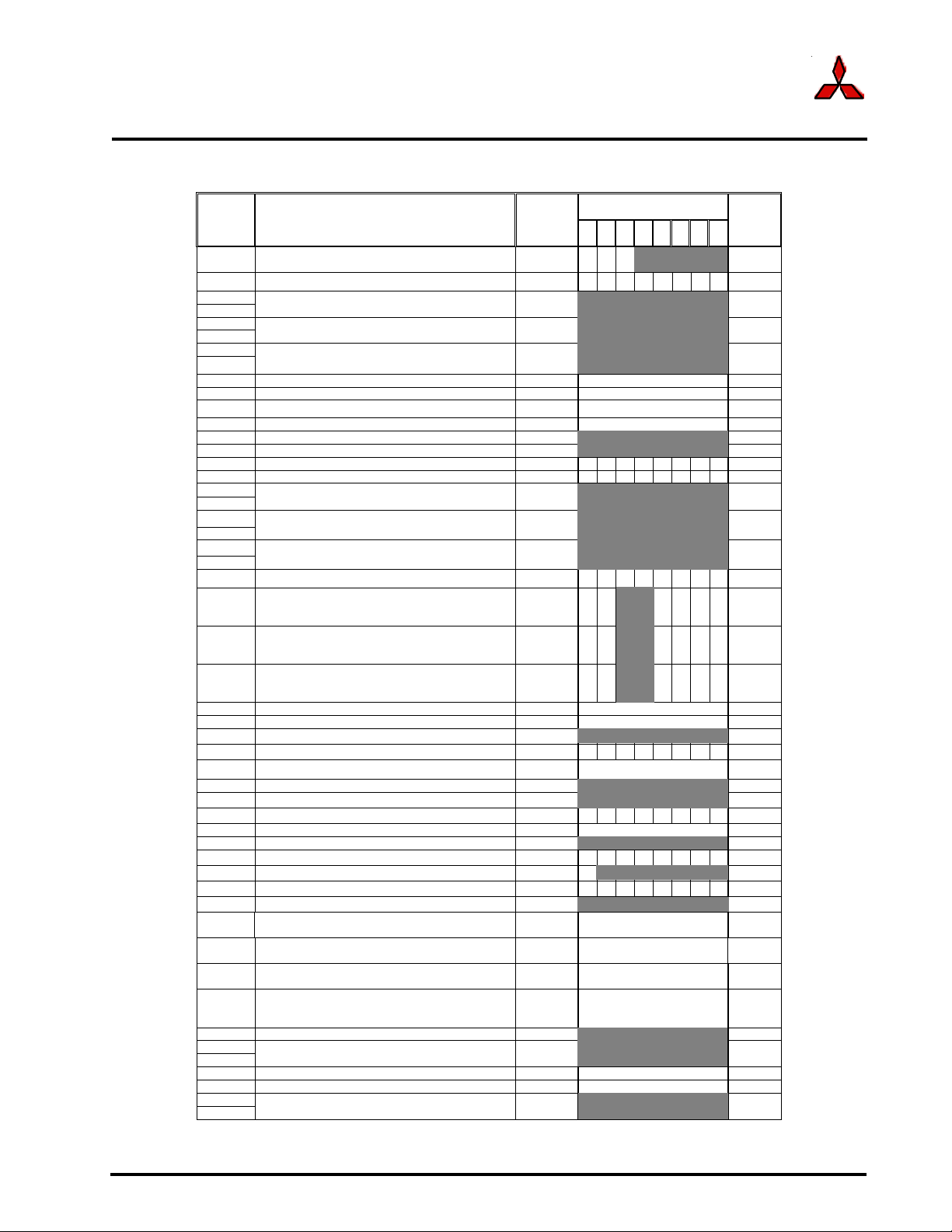

Table 1.8. Location and value after reset of peripheral unit control registers (4)

Table 1.9. Location and value after reset of peripheral unit control registers (5)

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30222 Group

Address

03C0

16

03C1

03C2

03C3

03C4

03C5

03C6

03C7

03C8

03C9

03CA

03CB

03CC

03CD

03CE

03CF

03D0

03D1

03D2

03D3

03D416A-D control register 2 ADCON2

03D5

A-D register 0 AD0

16

16

A-D register 1 AD1

16

16

A-D register 2 AD2

16

16

A-D register 3 AD3

16

16

A-D register 4 AD4

16

16

A-D register 5 AD5

16

16

A-D register 6 AD6

16

16

A-D register 7 AD7

16

16

16

16

16

16

Register Name Acronym

03D616A-D control register 0 ADCON0

03D716A-D control register 1 ADCON1

Value after ResetSFR

b7 b6 b5 b4 b3 b2 b1 b0

0000

00000

00

16

Page Number

0

1.153, 1.155,

1.156, 1.157,

1.158, 1.159

1.153, 1.155,

1.156, 1.157,

1.158, 1.159

1.154

1.154

1.154

1.154

1.154

1.154

1.154

1.154

1.154

03D816D-A register 0 DA0 1.163

03D9

16

03DA16D-A register 1 DA1 1.163

03DB

16

03DC16D-A control register DACON

03DD

16

03DE

16

03DF

16

03E0

16

03E1

16

03E2

16

03E3

16

03E4

16

03E516Port P3 P3 1.170

03E6

16

03E716Port P3 direction register PD3

00

16

00

16

1.163

1.170

03E816Port P4 P4 1.170

03E9

16

03EA16Port P4 direction register PD4

03EB

16

03EC16Port P6 P6 1.170

03ED16Port P7 P7 1.170

03EE16Port P6 direction register PD6

03EF16Port P7 direction register PD7

03F016Port P8 P8

03F116Port P9 P9 1.170

03F216Port P8 direction register PD8

03F316Port P9 direction register PD9

00

16

00

16

00

000000

0 0000

16

00

16

1.170

1.170

1.170

0

1.170

0

1.170

1.170

03F416Port P10 P10 1.170

03F5

16

03F616Port P10 direction register PD10

03F7

16

03F8

16

03F9

16

03FA

16

03FB

16

03FC16Pull-up control register 0 PUR0

03FD16Pull-up control register 1 PUR1

03FE16Pull-up control register 2 PUR2

03FF16Real-time port control register RTP

00

16

00

16

00

16

00

16

000

1.170

1.171

1.171

1.171

0

1.83

? = Undefined

1-19

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Software Reset

Software Reset

Writing “1” to bit 3 of the processor mode register 0 (address 000416) applies a (software) reset to the

microcomputer. A software reset has the same effect as a hardware reset. The contents of internal RAM

are preserved.

Figure 1.10 shows processor mode register 0 and 1.

Processor mode register 0 (Note)

b7 b6 b5 b4 b3 b2 b1 b0

0

0

0

Symbol Address When reset

PM0 0004

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

16

00

16

Nothing is assigned.

Write "0" when writing to this these bits. If read, the value is indeterminate.

PM03

Nothing is assigned.

Write "0" when writing to this these bits. If read, the value is indeterminate.

Reserved bit Must always be set to "0"

Note : Set bit 1 of the protect register (address 000A

values to this register.

Processor mode register 1 (Note )

b7 b6 b5 b4 b3 b2 b1 b0

0

0

0

Note : Set bit 1 of the protect register (address 000A16) to “1” when writing new values

Symbol

PM1

Reserved bit

Nothing is assigned.

Write "0" when writing to this these bits. If read, the value is indeterminate.

PM17

to this register.

Bit name FunctionBit symbol

Software reset

Bit name FunctionBit symbol

Wait bit

bit

Address

0005

16

The device is reset when this bit is set

to “1”. The value of this bit is “0” when

read.

16

) to “1” when writing new

Must always be set to “0”

0 : No wait state

1 : Wait state inserted

When reset

0XXXXX00

2

WR

WR

O O

Fig. 1.10. Processor mode register 0 and 1

1-20

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Clock Generating Circuit

Clock generating Circuit

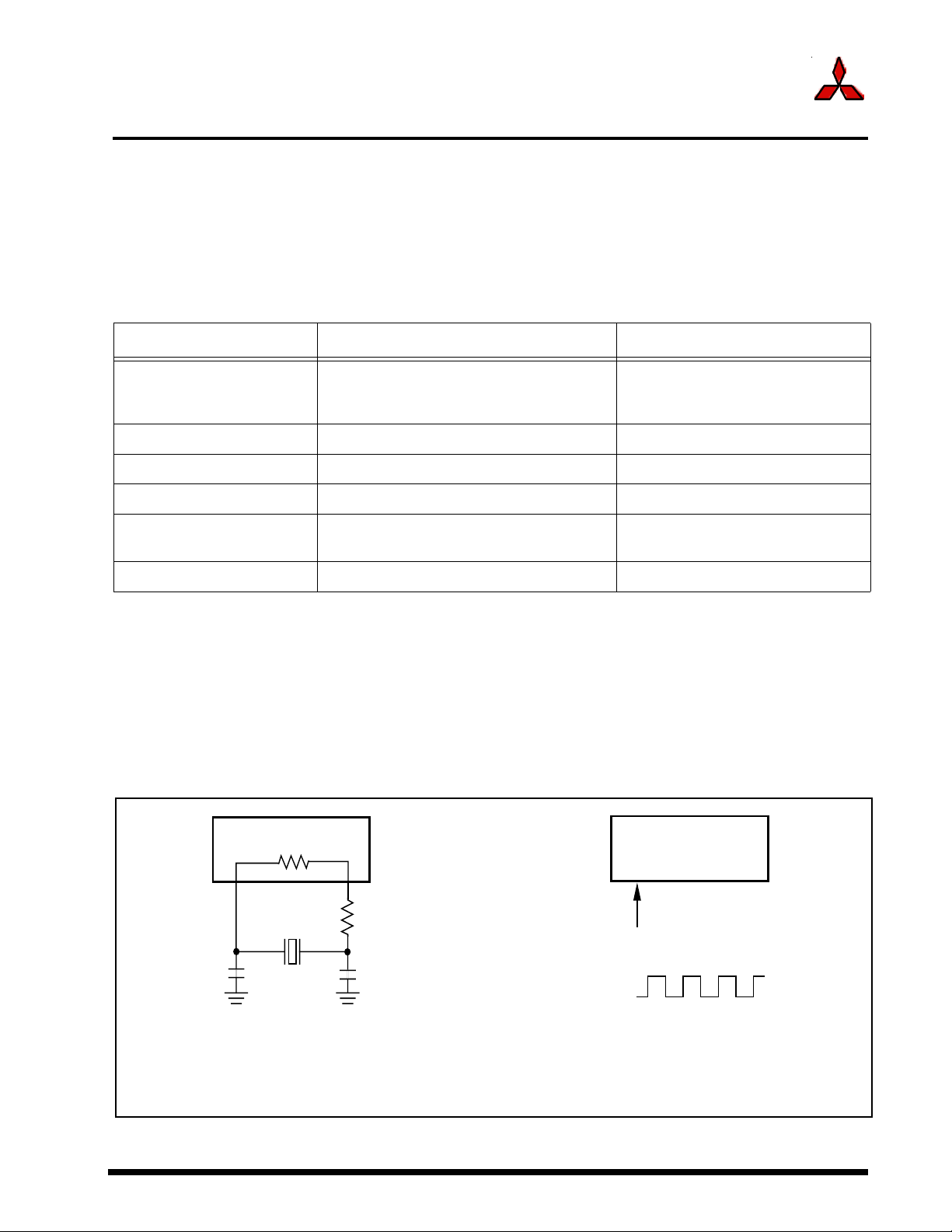

The clock generating circuit contains two oscillator circuits that supply the operating clock sources to

the CPU and internal peripheral units. Table 1.10 shows some examples of the main clock and

subclock generating circuits.

Table 1.10. Main clock and sub-clock generating circuits

Main clock generating circuit Sub-clock generating circuit

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Use of clock Operating clock source for CPU

Operating clock source for Internal

peripheral

Usable oscillator Ceramic or crystal oscillator Crystal oscillator

Pins to connect oscillator Xin, Xout Xcin, Xcout

Oscillation stop/restart function Available Available

Oscillator status immediately

after Reset

Other Externally derived clock can be input (Note)

Note: Max. voltage is the same as VDC

Oscillating Stopped

Operating clock source

Count clock source for Timers A/B

Operating clock source for LCD

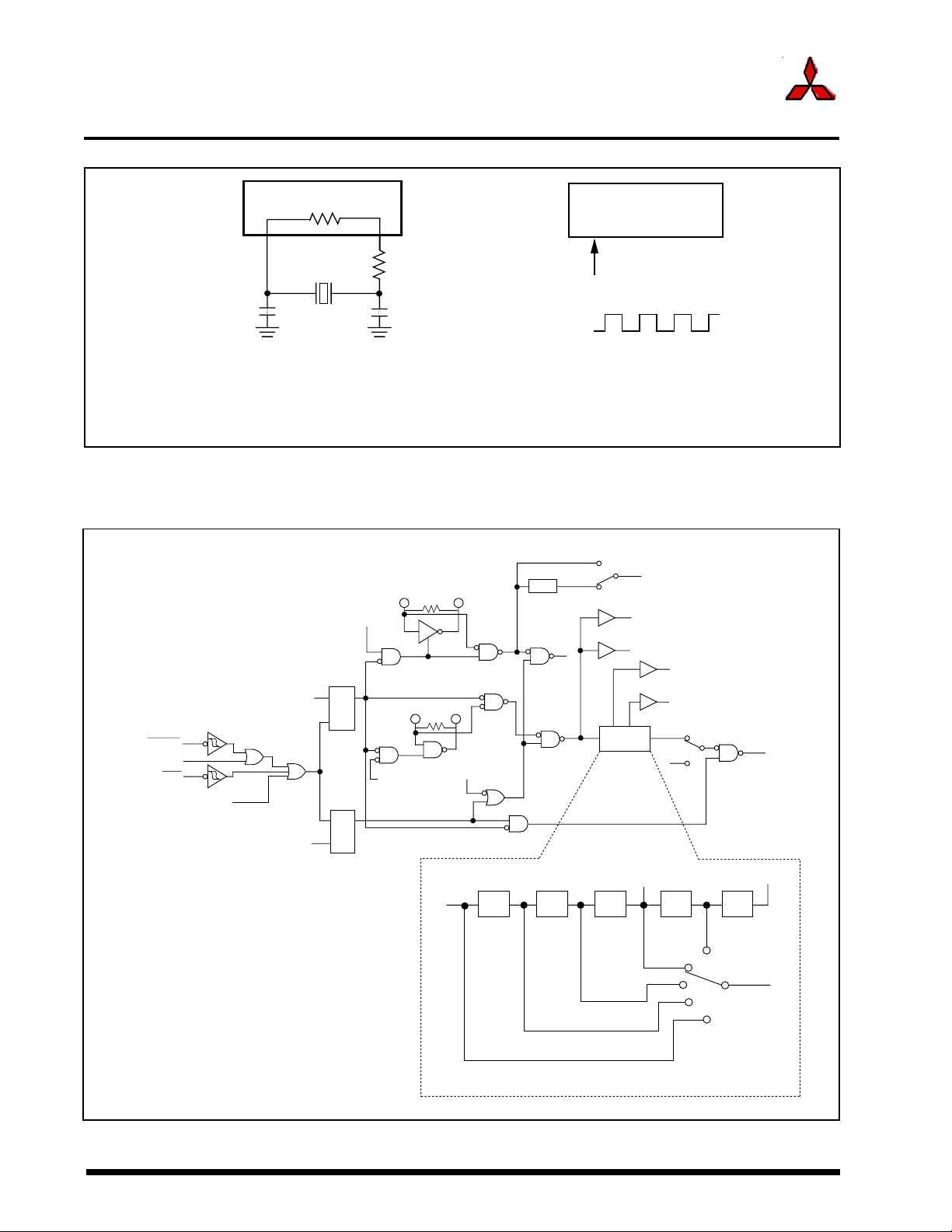

Figure 1.11 shows some examples of the main clock circuit, one using an oscillator connected to the

circuit, and the other one using an externally derived clock for input. Figure 1.12 shows some ex-

amples of sub-clock circuits, one using an oscillator connected to the circuit, and the other one using

an externally derived clock for input. Circuit constants in Figures 1.11 and 1.12 vary with each oscil-

lator used. Use the values recommended by the manufacturer of your oscillator.

Microcomputer

(Built-in feedback resistor)

Xin

Cin

Note: Insert a damping resistor if required. The resistance will vary depending on the oscillator and the oscillation drive

capacity setting. Use the value recommended by the maker of the oscillator.

When the oscillation drive capacity is set to low, check that oscillation is stable. Also, if the oscillator manufacturer's

data sheet specifies that a feedback resistor be added external to the chip, insert a feedback resistor between X

and X

Fig. 1.11. Examples of main clock

Xout

(Note)

Rd

out

following the instruction.

Cout

Microcomputer

Xin Xout

Open

Externally derived clock

Vcc

Vss

in

1-21

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Clock Generating Circuit

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Microcomputer

(Built-in feedback resistor)

X

cin

X

cout

(Note 1)

R

C

cin

Note 1: Insert a damping resistor if required. The resistance will vary depending on the oscillator and the oscillation drive

capacity setting. Use the value recommended by the maker of the oscillator.

When the oscillation drive capacity is set to low, check that oscillation is stable. Also, if the oscillator manufacturer's

data sheet specifies that a feedback resistor be added external to the chip, insert a feedback resistor between X

and X

cout

following the instruction.

Note 2: Reference XCin to VDC supply.

C

cout

Fig. 1.12. Examples of sub-clock

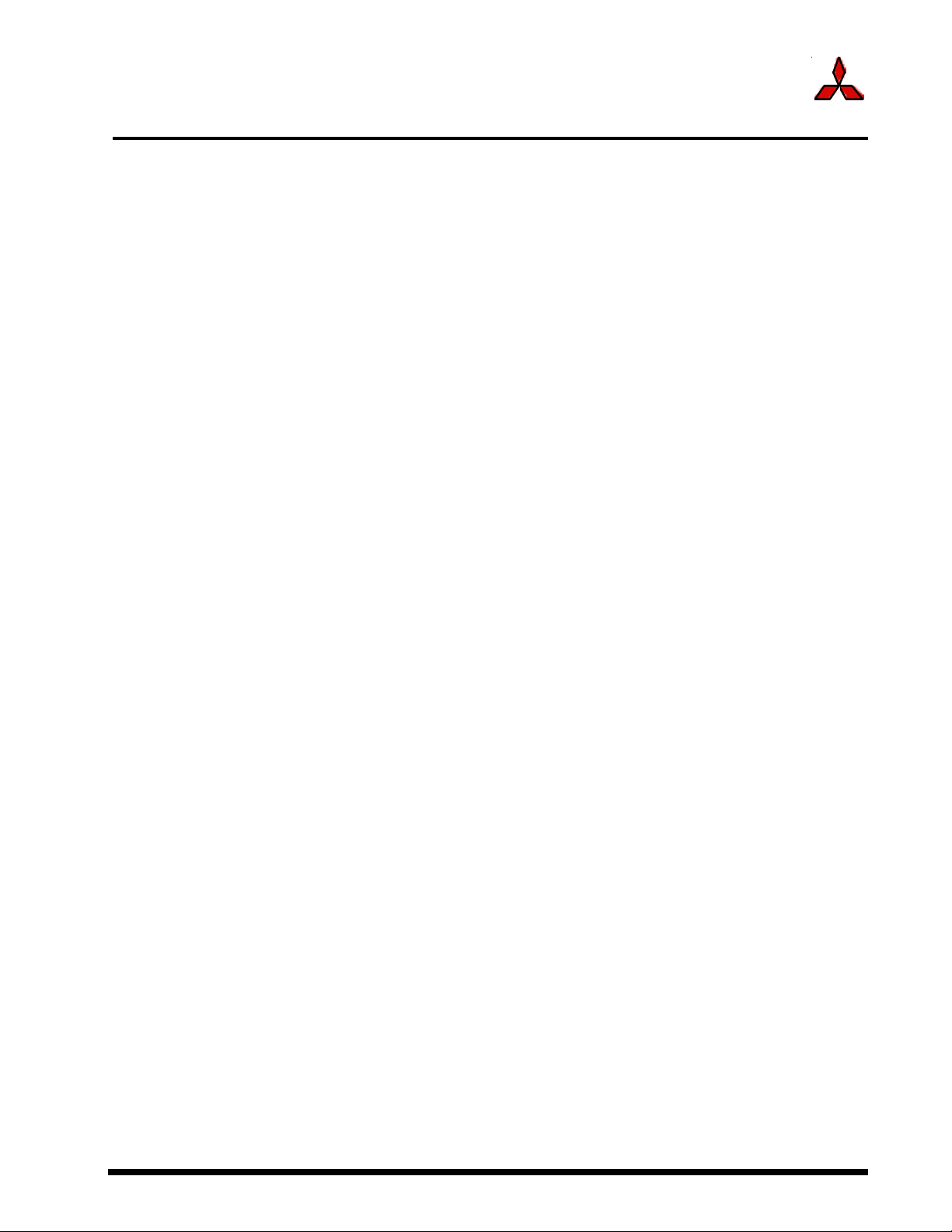

Figure 1.13 shows a block diagram of the clock generating circuit.

X

CIN

X

COUT

CM04

Sub clock

RESET

Software reset

NMI

Interrupt request

level judgment

output

CM10 "1"

Write signal

WAIT instruction

Q

S

R

QS

R

CM05

X

IN

Main clock

X

OUT

CM02

VDC

1/32

Microcomputer

X

cin

Externally derived clock

(Note 2)

Vss

CM14=1

f

C1

C32

f

f

C

a

CM14=0

f

1

f

AD

c

b

Divider

f

C132

f

f

32

d

f

C

X

cout

Open

8

CM07=0

CM07=1

cin

BCLK

CM0i : Bit i at address 0006

CM1i : Bit i at address 0007

WDCi : Bit i at address 000F

Fig. 1.13. Clock generating circuit

b

a

16

16

16

1/2 1/2 1/2 1/2

CM06=1

CM06=0

CM17,CM16=01

CM06=0

CM17,CM16=00

CM06=0

CM17,CM16=10

CM06=0

CM17,CM16=11

Details of divider

c

1/2

d

1-22

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Clock Generating Circuit

The following paragraphs describes the clocks generated by the clock generating circuit.

(1) Main clock

The main clock is generated by the main clock oscillation circuit. After a reset, the clock is divided by 8 to

the BCLK. The clock can be stopped using the main clock stop bit (bit 5 at address 0006

clock, after switching the operating clock source of CPU to the sub-clock, reduces the power dissipation.

After the oscillation of the main clock oscillation circuit has stabilized, the drive capacity of the main clock

oscillation circuit can be reduced using the X

Reducing the drive capacity of the main clock oscillation circuit reduces the power dissipation. This bit

changes to “1” when shifting from high-speed/medium-speed mode to stop mode and at a reset. When

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

(2) Sub-clock

The sub-clock is generated by the sub-clock oscillation circuit. No sub-clock is generated after a reset. After

oscillation is started using the port Xc select bit (bit 4 at address 0006

the BCLK by using the system clock select bit (bit 7 at address 0006

oscillation has fully stabilized before switching.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

16). Stopping the

IN-XOUT drive capacity select bit (bit 5 at address 000716).

16), the sub-clock can be selected as

16). However, be sure that the sub-clock

After the oscillation of the sub-clock oscillation circuit has stabilized, the drive capacity of the sub-clock

oscillation circuit can be reduced using the XCIN-XCOUT drive capacity select bit (bit 3 at address 000616).

Reducing the drive capacity of the sub-clock oscillation circuit reduces the power dissipation. This bit changes

to “1” when shifting to stop mode and at a reset.

(3) BCLK

The BCLK is the clock that drives the CPU, and is fc or the clock is derived by dividing the main clock by 1, 2,

4, 8, or 16. The BCLK is derived by dividing the main clock by 8 after a reset.

The main clock division select bit 0(bit 6 at address 0006

medium-speed to stop mode and at reset. When shifting from low-speed/low power dissipation mode to stop

mode, the value before stop mode is retained.

16) changes to “1” when shifting from high-speed/

(4) Peripheral function clock (f1, f8, f32, fAD)

The clock for the peripheral devices is derived from the main clock or by dividing it by 1, 8, or 32. The periph-

eral function clock is stopped by stopping the main clock or by setting the WAIT peripheral function clock stop

bit (bit 2 at 000616) to “1” and then executing a WAIT instruction.

(5) fC132

This clock is derived by dividing the sub-clock by 1 or 32. The clock is selected by fC132 clock select bit (bit4

at address 0007

16). It is used for the Timer A and Timer B counts, intermittent pull up operation of key input.

(6) fC

This clock has the same frequency as the sub-clock. It is used for the BCLK and for the Watchdog timer.

Figure 1.14 shows the system clock control registers 0 and 1.

1-23

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Clock Generating Circuit

System clock control register 0 (Note 1)

b7 b6 b5 b4 b3 b2 b1 b0

Symbol Address When reset

CM0 0006

16

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

48

16

CM00

CM01

CM02

CM03

CM04

CM05

CM06

CM07

Bit name FunctionBit symbol

Clock output function

select bits

WAIT peripheral function

clock stop bit

Xcin-Xout drive capacity

select bit (Note 2)

Port Xc Select Bit

Main clock (Xin-X

stop bit (Note 3, 4)

Main clock division select

bit 0 (Note 6)

System clock select bit

(Note 5)

out

)

b1 b0

0 0 : I/O port P7

0 1 : fC1 output

1 0 : f

1

1 1 : Clock divide counter output

0 : Do not stop peripheral function clock in wait mode

1 : Stop peripheral function clock in wait mode (Note 7)

0 : LOW

1 : HIGH

0 : I/O port

1 : Xcin - Xcout generation

0 : Main clock on

1 : Main clock off

0 : CM16 and CM17 valid

1 : Division by 8 mode

Xin, Xout

0 :

Xcin, Xcout1 :

5

output

WR

Note 1: Set bit 0 of the protect register (address 000A16) to "1" before writing to this register.

Note 2: Changes to "1" when shifting to stop mode and at a reset.

Note 3: When inputting external clock, only clock oscillation buffer is stopped and clock input is acceptable.

Note 4: If this bit is set to "1", X

pulled up to X

Note 5: Set subclock (X

from "0" to "1". Do not write to both bits at the same time. Likewise, set the main clock stop bit (CM05) to "0" and

out

out

("H") via the feedback resistor.

cin

turns "H". The built-in feedback resistor remains being connected, so XIN turns

- X

) enable bit (CM04) to "1" and allow the subclock to stabilize before setting CM07 from

cout

allow the subclock to stabilize before settng CM07 bit from "1" to "0".

Note 6: This bit changes to "1" when shifting from high-speed/medium-speed mode to stop mode and at a reset. When

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

C

, f

C132

, fC1, f

C32

Note 7: f

is not included.

System clock control register 1 (Note 1)

b7 b6 b5 b4 b3 b2 b1 b0

0

00

Note 1: Set bit 0 of the protect register (address 000A16) to "1" before writing to this register.

Note 2: This bit changes to "1" when shifting from high-speed/medium-speed mode to stop mode and at a reset. When

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

Note 3: Can be selected when bit 6 of the system clock control register 0 (address 0006

fixed at 8.

Note 4: If this bit is set to "1", X

impedance state.

Symbol Address When reset

CM1 0007

16

20

16

Bit name FunctionBit symbol

CM10

Reserved bit

CM14

CM15

CM16

CM17

out

All clock stop control bit

(Note 4)

C132

clock select bit 0 : f

f

in-Xout

drive capacity

X

select bit (Note 2)

Main clock division

select bit 1 (Note 3)

goes "H", and the built-in feedback resistor is cut off. Xcin and Xcout goes into high

0 : Clock on

1 : All clocks off (stop mode)

Always set to

C32

1 : f

C1

0 : LOW

1 : HIGH

b7 b6

0 0 : No division mode

0 1 : Division by 2 mode

1 0 : Division by 4 mode

1 1 : Division by 16 mode

"0"

16

) is "0". If "1", division mode is

Fig. 1.14. Clock control registers 0 and 1

WR

1-24

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Clock output

Clock Output

The M30222 provides for a clock output signal (P73/CLKOUT pin) of user defined frequency. The clock

output function select bit (CM00, CM01) allows you to choose the clock source from f1, fC1, or a divide-by-

n clock for output to the P73/CLKOUT pin. The clock divide counter is an 8-bit counter whose count source

is f32, and its divide ratio can be set in the range of 0016 to FF16. Also, the clock divided counter can be

controlled for start or stop by the clock divide counter start flag. Figure 1.15 shows a block diagram of

clock output. Figure 1.16 shows a clock divided counter related register.

Clock source

selection

P7

5

f

1

f

C1

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

P75/CLK

OUT

1/2

f

32

Clock divided counter (8)

Reload register (8)

Data bus low-order bits

Fig. 1.15. Block diagram of clock output

Clock divided counter

b7 b0

8-bit timer 0016 to FF

Clock divided counter control register

b7 b6 b5 b4 b3 b2 b1 b0

Symbol

CDCC 036C

Division n+1 n=0016 to FF

Address 036E

Low-order 8 bits

Symbol Address

CDC

036E

16

16

16

Example:

When f(X

n=07

16 :

16

n=26

16

n=4D

n=9B

16

IN

:

:

:

Function Values that can be set

Address When reset

16

)=10MHz, count source = f

approx. 19.5kHz

approx. 4.0kHz

approx. 2.0kHz

approx. 1.0kHz

When reset

XX

16

16

0XXXXXXX

2

32

WR

Nothing is assigned. Write "0" when writing to these bits.

When read, the value is indeterminate.

CDCS

Clock divided counter

start flg

Fig. 1.16. Clock divided counter related register

Bit name

1-25

0 : Stop

1 : Start

FunctionBit symbol WR

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Wait Mode

Wait Mode

When a WAIT instruction is executed, the BCLK stops and the microcomputer enters the wait mode. In

this mode, oscillation continues but the BCLK and Watchdog timer stop. Writing “1” to the WAIT periph-

eral function clock stop bit and executing a WAIT instruction stops the clock being supplied to the

internal peripheral functions, allowing power dissipation to be reduced. Table 1.11 shows the status of

the ports in wait mode.

Wait mode is cancelled by a hardware reset or an interrupt. If an interrupt is used to cancel wait mode,

the microcomputer restarts from the interrupt routine using as BCLK, the clock that had been selected

when the WAIT instruction was executed.

Usage Precautions

When switching to either wait mode or stop mode, instructions occupying four bytes either from the WAIT

instruction or from the instruction that sets the every-clock stop bit to “1” within the instruction queue are

prefetched and then the program stops. So put at least four NOPs in succession either to the WAIT instruc-

tion or to the instruction that sets the every-clock stop bit to “1”.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Table 1.11. Port Status during wait mode

Pin

Port

CLKOUT/

P7

5

Mode

C

When f

When f1, clock divided

counter output selected

1 selected

Single-chip mode

Retainsstatus before wait mode

Does not stop

Retains status before stop mode.

Does not stop when the WAIT

peripheral function clock stop bit is "0".

When the WAIT peripheral function

clock stop bit is "1", the status immediately prior to entering wait mode

is maintained.

1-26

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Stop Mode

Stop Mode

Writing "1" to all-clock stop control bit (bit 0 at address 000716) stops all oscillation and the microcom-

puter enters stop mode. In stop mode, the content of the internal RAM is retained provided that VCC

remains above 2V.

Because the oscillation , BCLK, f1 to f32, fC, fC132, fC1, fC32 and fAD stops in stop mode, peripheral

functions such as the A-D converter and watchdog timer do not function. However, Timer A and Timer

B operate provided that the event counter mode is set to an external pulse, and UART0 to UART2

functions provided an external clock is selected. Table 1.12 shows the status of the ports in stop mode.

Stop mode is cancelled by a hardware reset or an interrupt. If an interrupt is to be used to cancel stop

mode, that interrupt must first have been enabled. If coming out of stop mode is caused by an interrupt,

that interrupt routine is executed.

When shifting from high-speed/medium-speed mode to stop mode and at a reset, the main clock divi-

sion select bit 0 (bit 6 at address 000616) is set to “1”. When shifting from low-speed/low power dissipa-

tion mode to stop mode, the value before stop mode is retained.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Usage Precautions

(1) When returning from stop mode by hardware reset, RESET pin must be set to “L” level until main clock

oscillation is stabilized.

(2) When switching to either wait mode or stop mode, instructions occupying four bytes either from the WAIT

instruction or from the instruction that sets the every-clock stop bit to “1” within the instruction queue are

prefetched and then the program stops. Put at least four NOPs in succession either to the WAIT instruction or

to the instruction that sets the every-clock stop bit to “1”.

Table 1.12 Port status during stop mode

Pin Status

Port

CLKOUT/

P7

5

Mode

selected

fc1

When

When f1, clock divided

output selected

Retains status before stop mode

"H"

Retains

status before

stop

mode

1-27

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Status Transition of BCLK

Status Transition Of BCLK

Power dissipation can be reduced and low-voltage operation achieved by changing the count source for

BCLK. Table 1.13 shows the operating modes corresponding to the settings of system clock control

registers 0 and 1.

When reset, the device starts in division by 8 mode. The main clock division select bit 0(bit 6 at address

16) changes to “1” when shifting from high-speed/medium-speed to stop mode and at a reset. When

0006

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

The following shows the operational modes of BCLK.

(1) Division by 2 mode

The main clock is divided by 2 to obtain the BCLK.

(2) Division by 4 mode

The main clock is divided by 4 to obtain the BCLK.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

(3) Division by 8 mode

The main clock is divided by 8 to obtain the BCLK. When reset, the device starts operating from this

mode. Before the user can go from this mode to no division mode, division by 2 mode, or division by 4

mode, the main clock must be oscillating stably. When going to low-speed or lower power consumption

mode, make sure the sub-clock is oscillating stably.

(4) Division by 16 mode

The main clock is divided by 16 to obtain the BCLK.

(5) No-division mode

The main clock is divided by 1 to obtain the BCLK.

(6) Low-speed mode

fC is used as the BCLK. Note that oscillation of both the main and sub-clocks must have stabilized before

transferring from this mode to another or vice versa. At least 2 to 3 seconds are required after the sub-

clock starts. Therefore, the program must be written to wait until this clock has stabilized immediately

after powering up and after stop mode is cancelled.

(7) Low power dissipation mode

fC is the BCLK and the main clock is stopped.

Note : Before the count source for BCLK can be changed from XIN to XCIN or vice versa, the clock to which

the count source is going to be switched must be oscillating stably. Allow time in software for

the source to stabilize before switching over the clock.

1-28

Under

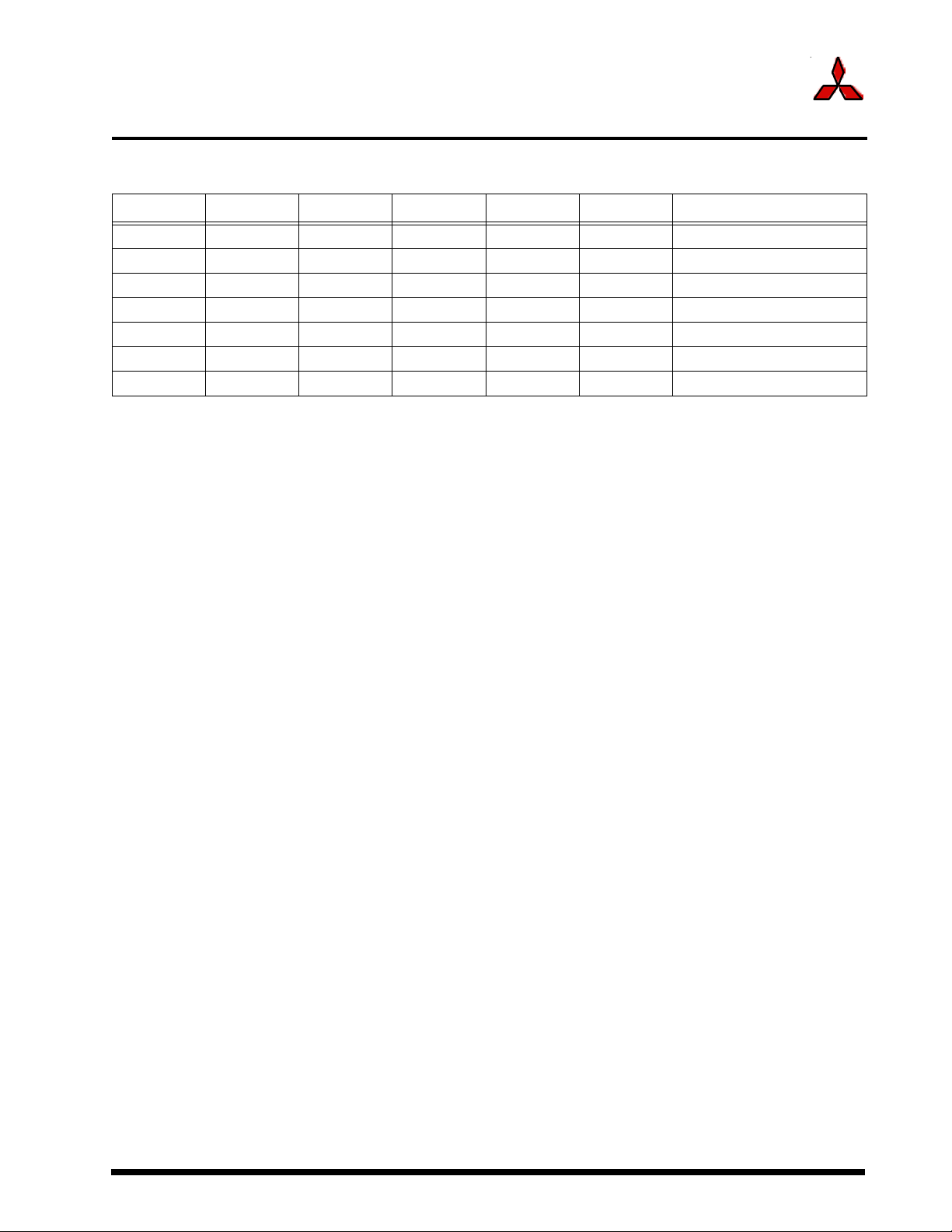

CM17 CM16 CM07 CM06 CM05 CM04 BCLK operating mode

01000Invalid Divide by 2

10000Invalid Divide by 4

Invalid Invalid 0 1 0 Invalid Divide by 8

11000Invalid Divide by 16

01000Invalid None

Invalid Invalid 1 Invalid 0 1 Low-speed

Invalid Invalid 1 Invalid 1 1 Low power dissipation

development

Specifications in this manual are tentative and subject to change

Rev. G

Status Transition of BCLK

Table 1.13. Operating modes dictated by settings of system clock control registers 0 and 1

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

1-29

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Voltage Down Converter

Voltage Down Converter

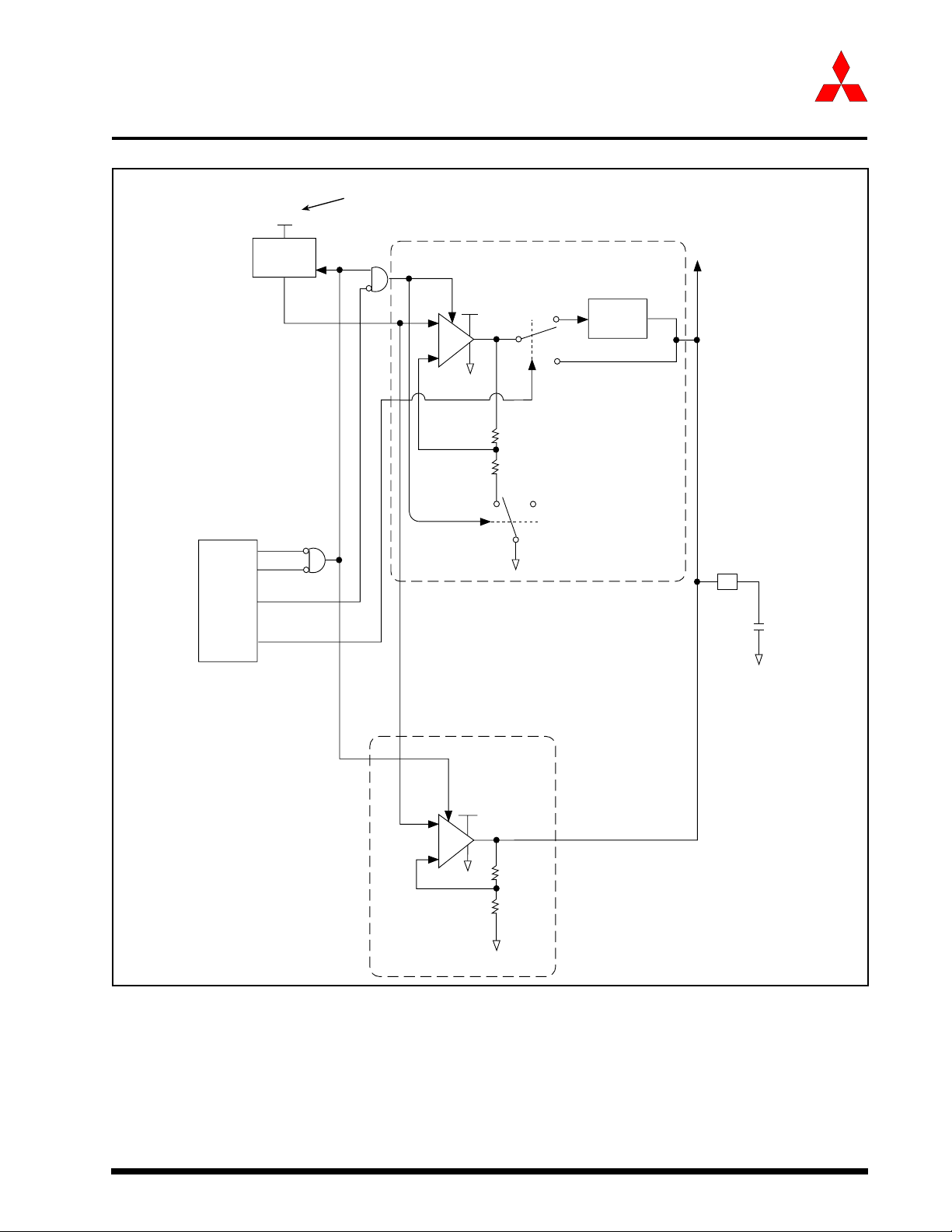

The Voltage Down Converter (VDC) is a bandgap reference based voltage regulator used for generating

a low-voltage supply. The VDC block inputs the external supply VCC (up to 5.5 volts) and generates a 3.3-

volt (nominal) supply (VDD). Table 1.14 describes the specified voltage regulation. The VDC is pro-

grammable in terms of drive limit and power level. In low power mode, the VDC can source up to 20mA

and uses less than 10uA bias current. In high-power mode, the VDC can source up to 200mA. There is

a programmable option to limit the current of the VDC in high-power mode to about 80mA. The VDC

default state (from reset) is high-power mode with current limiting enabled. The current limiting is en-

abled at reset in order to avoid a large in-rush current to an external hold capacitor (required) on the

VDC pin. Once the external hold capacitor is charged, the current limiter can be disabled in software.

Figures 1.17 and 1.18 describe the programmable features of the VDC. The external hold capacitor is

required to stabilize the VDC and to minimize voltage ripple on the 3.3 volt supply during operation.

Table 1.15 describes the external hold capacitor requirements.

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Table 1.14. VDC voltage regulations

Signal Description

Package Supply (Vcc) Range: 2.7v to 5.5v (input to VDC)

Internal Supply (Vdd) 3.3v (nominal) +/- 10% (output from VDC) OR

Note: Whichever is smaller

Voltage Down Converter control

b7 b6 b5 b4 b3 b2 b1 b0

Vcc - 200mV @ Icc

register

Symbol Address When reset

VDCC 0018

Bit symbol WR

VDCC0

VDCC1

Nothing is assigned. Write "0" when writing to this bit. If read, the

value is indeterminate.

HPOWER

ILIMEN

Nothing is assigned. Write "0" when writing to these bits. If read, the

value is indeterminate.

b1 b0

0 0 : VDC enabled

0 1 : Reserved

1 0 : Reserved

1 1 : VDC disabled

0 : High power

1 :

0 : Current limit enabled

1 : Current limit disabled

<15 mA (Note)

(AVG)

Low power

16

XXX00X00

Function

2

_

_

_ _

Figure 1.17. VDC Control/Status Register

Table 1.15. Required External Components

Component Value Material

External Hold Capacitor 0.1µF +/- 20% Ceramic

1-30

Under

development

Specifications in this manual are tentative and subject to change

Rev. G

Voltage Down Converter

EXTERNAL

SUPPLY (5 V)

Vcc

BANDGAP

REFERENCE

MITSUBISHI MICROCOMPUTERS

M30222 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

HIGH POWER REGULATOR

3.3 V SUPPLY

VDC

Control

Status

Register

VDCC0

VDCC1

HPOWER

ILIMEN

(1.22V)

Vcc

EN

(1)

LOW POWER REGULATOR

(0)

CURRENT

LIMIT

(1)

(0)

VDC Pin

0.1 µ F

EXTERNAL

HOLD CAPACIT

OR

Fig. 1.18. VDC Functional block diagram

Vcc

EN

1-31

Loading...

Loading...