Page 1

5

Table of Contents

4

3

2

1

Page

01

D D

02

03

04

05

06

07

08

09

Title

TABLE OF CONTENTS

Build Options

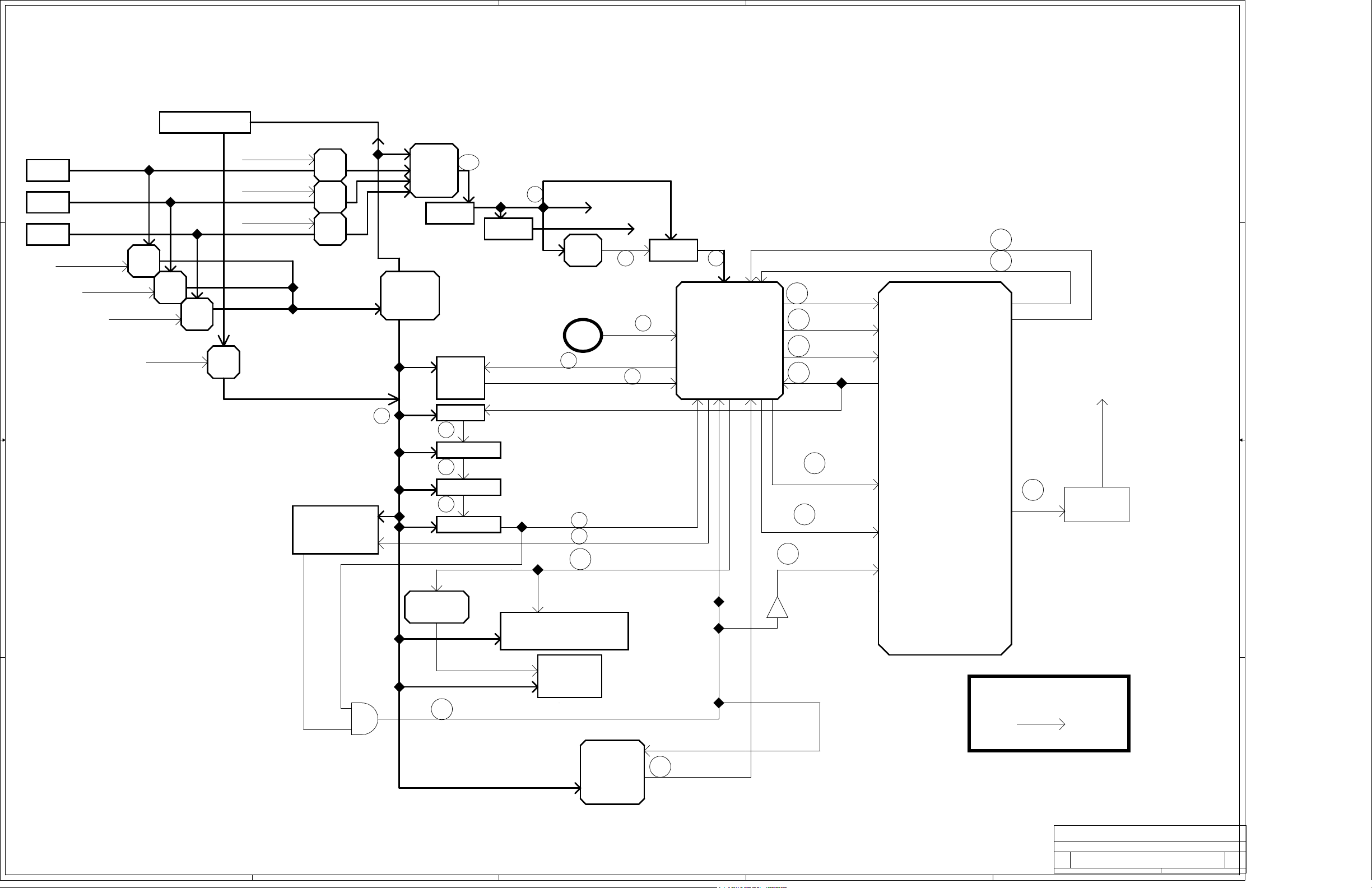

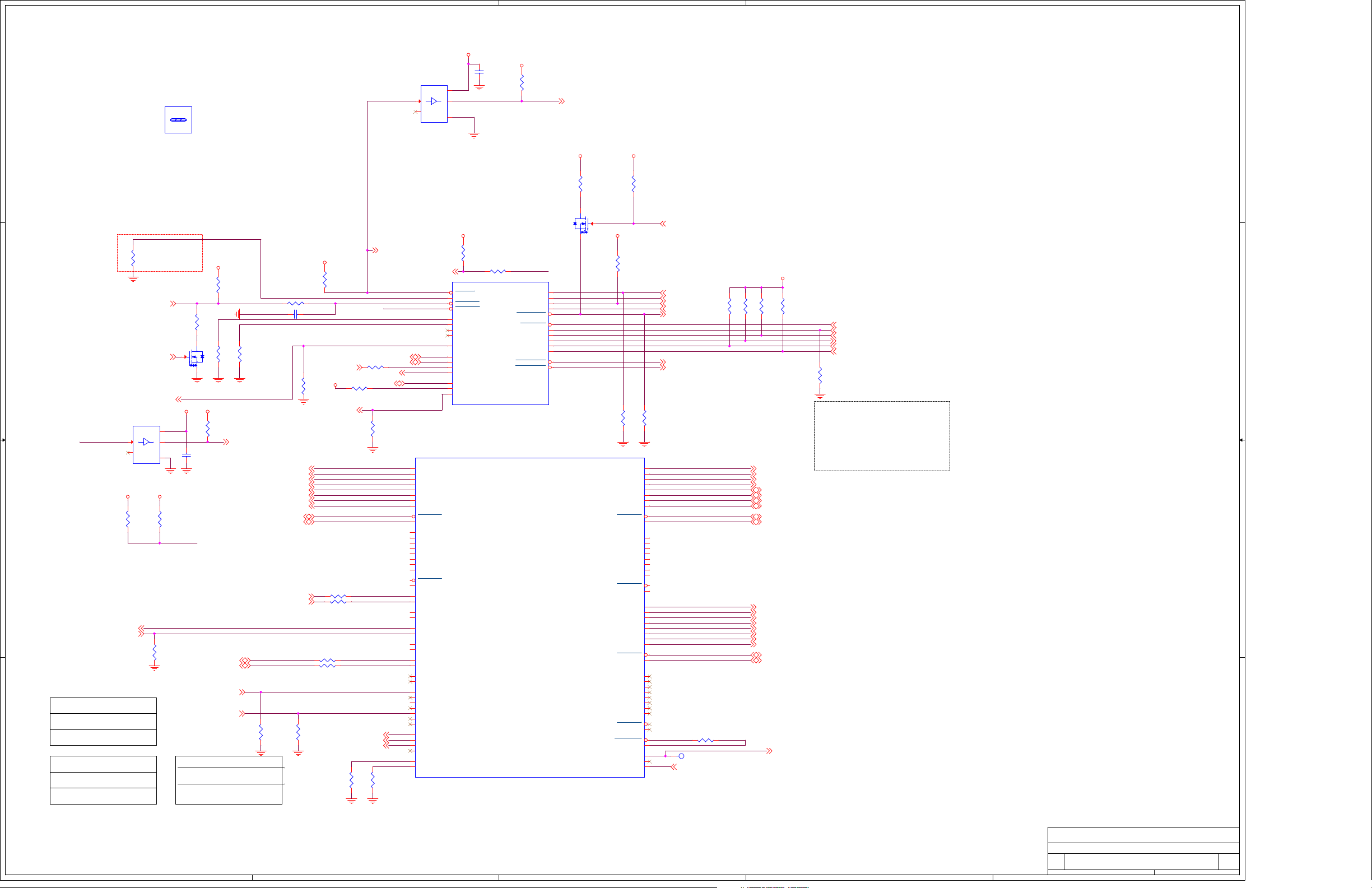

BLOCK DIAGRAM

CLOCK DISTRIBUTION

SIGNAL & RESET MAP

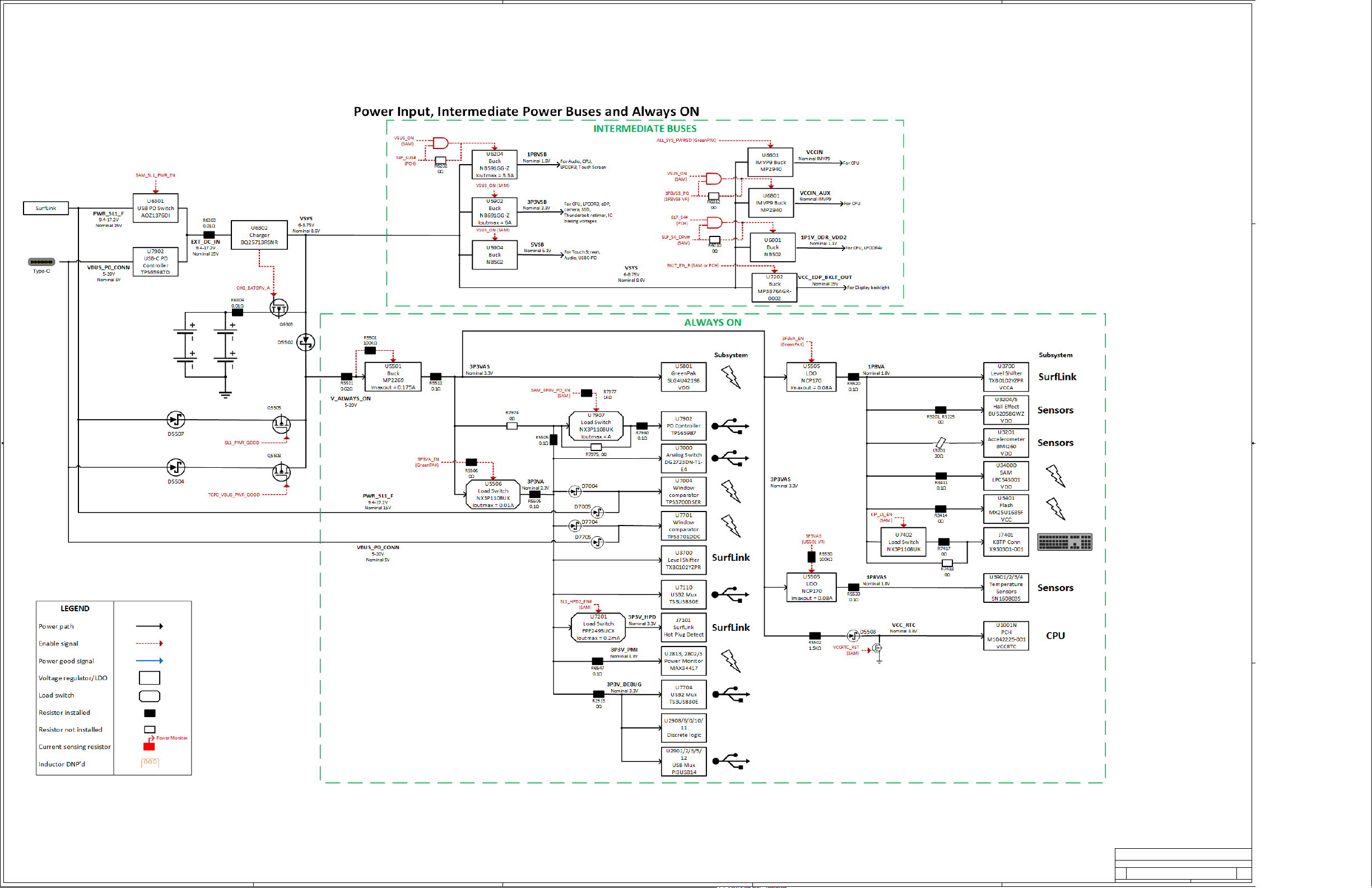

POWER FLOW 1 of 3

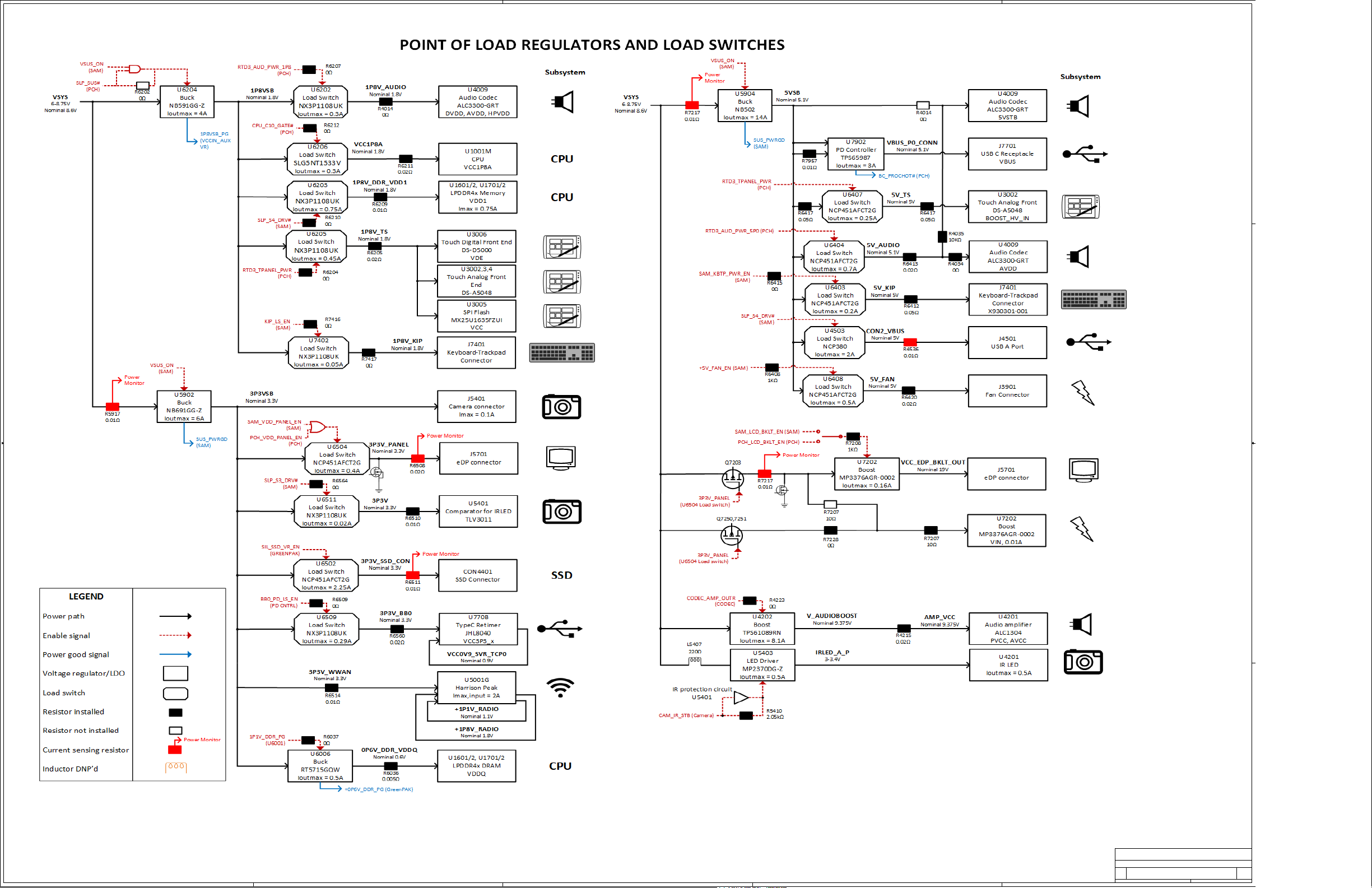

POWER FLOW 2 of 3

POWER FLOW 3 of 3

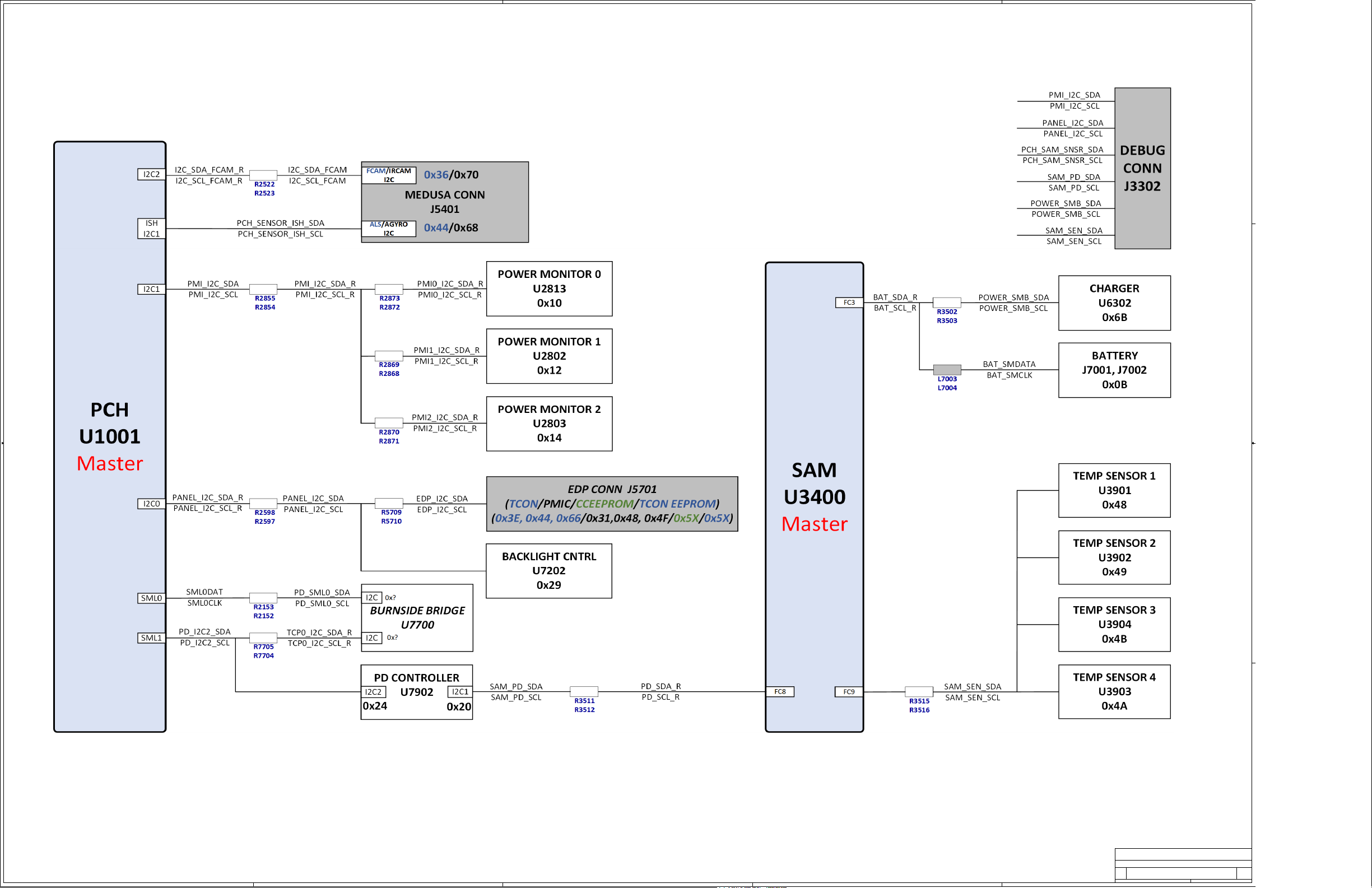

I2C MAP

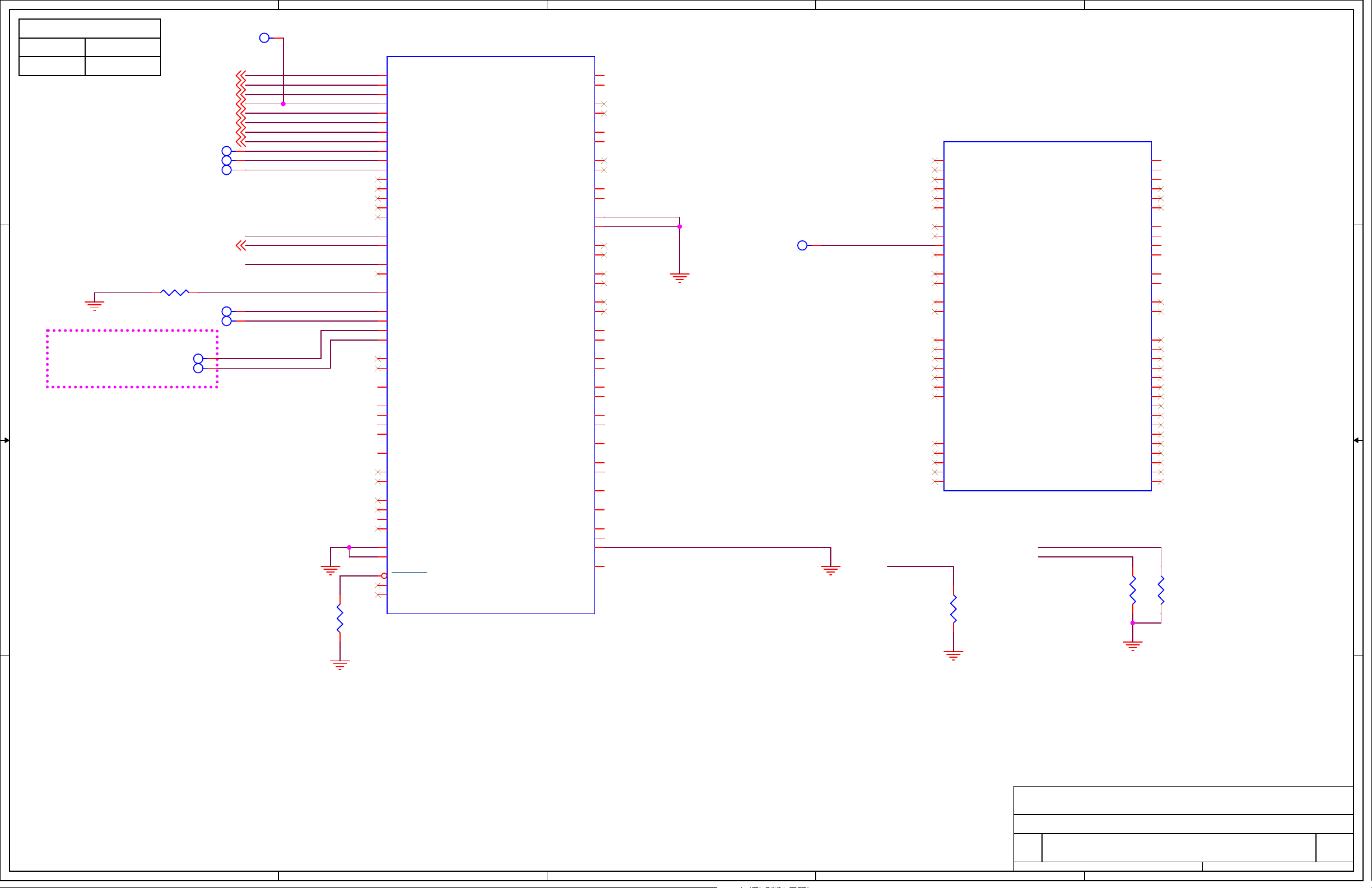

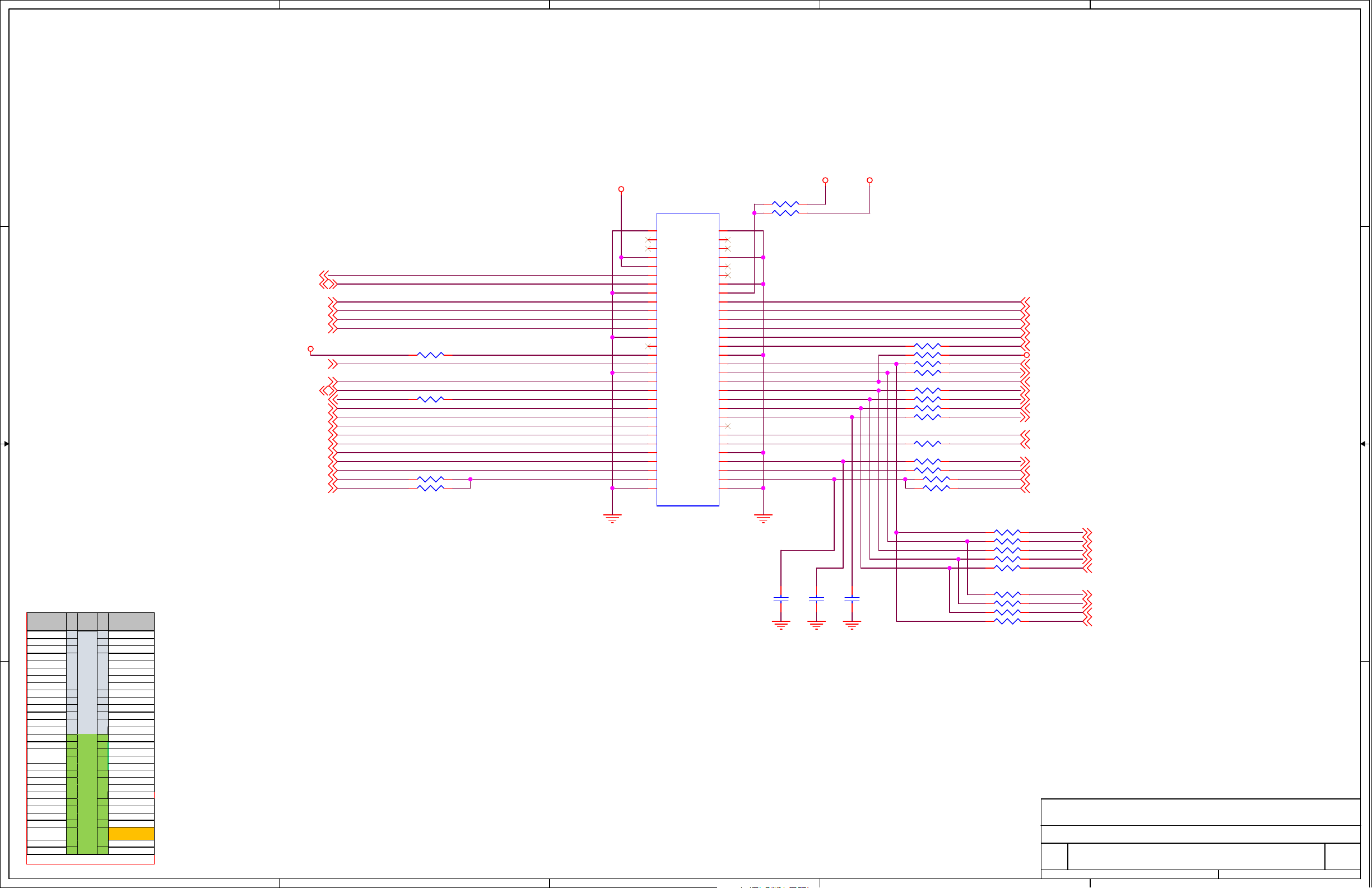

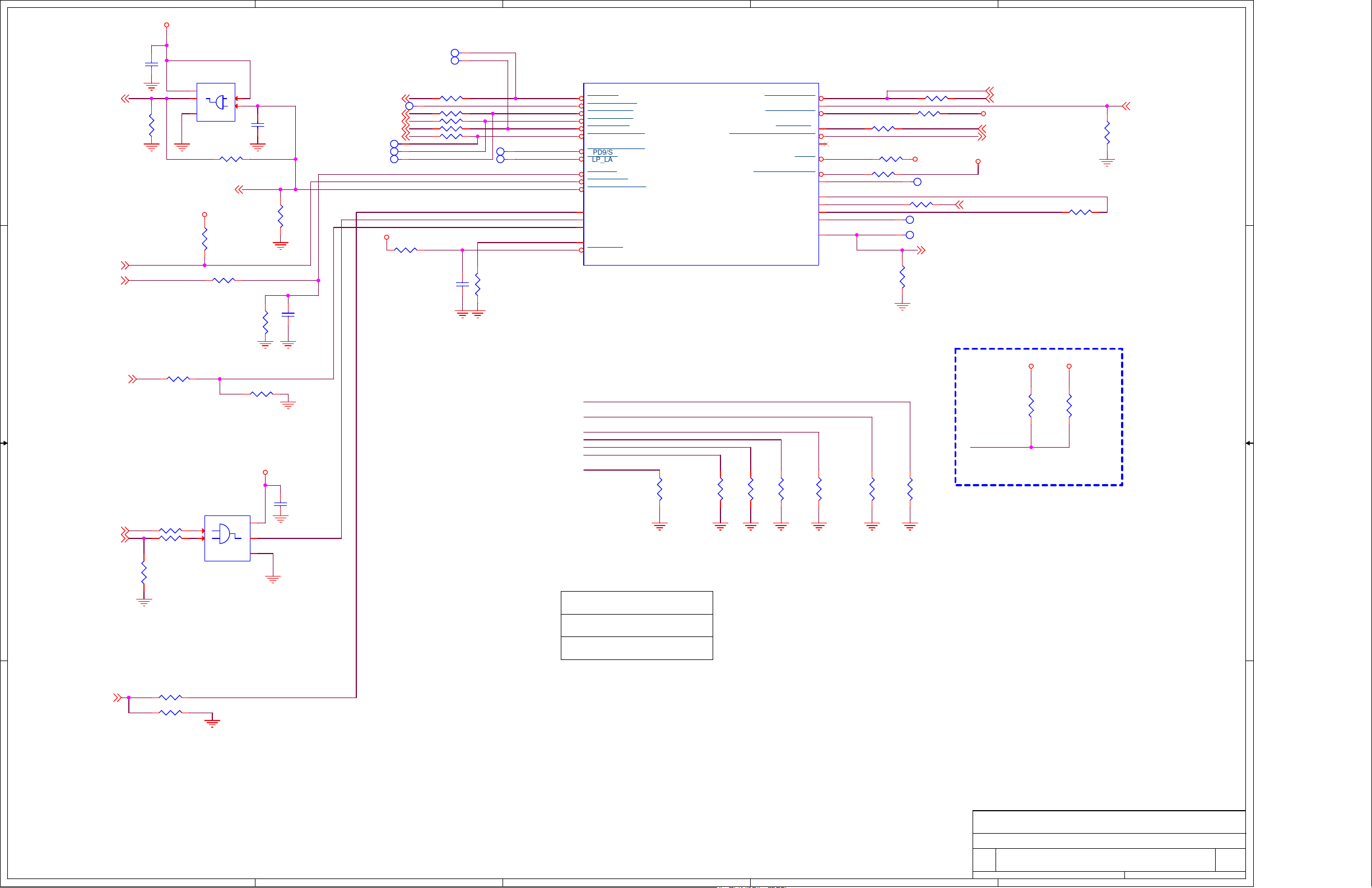

CPU(1)_Disp,Type-C,MISC

11

C C

12

13

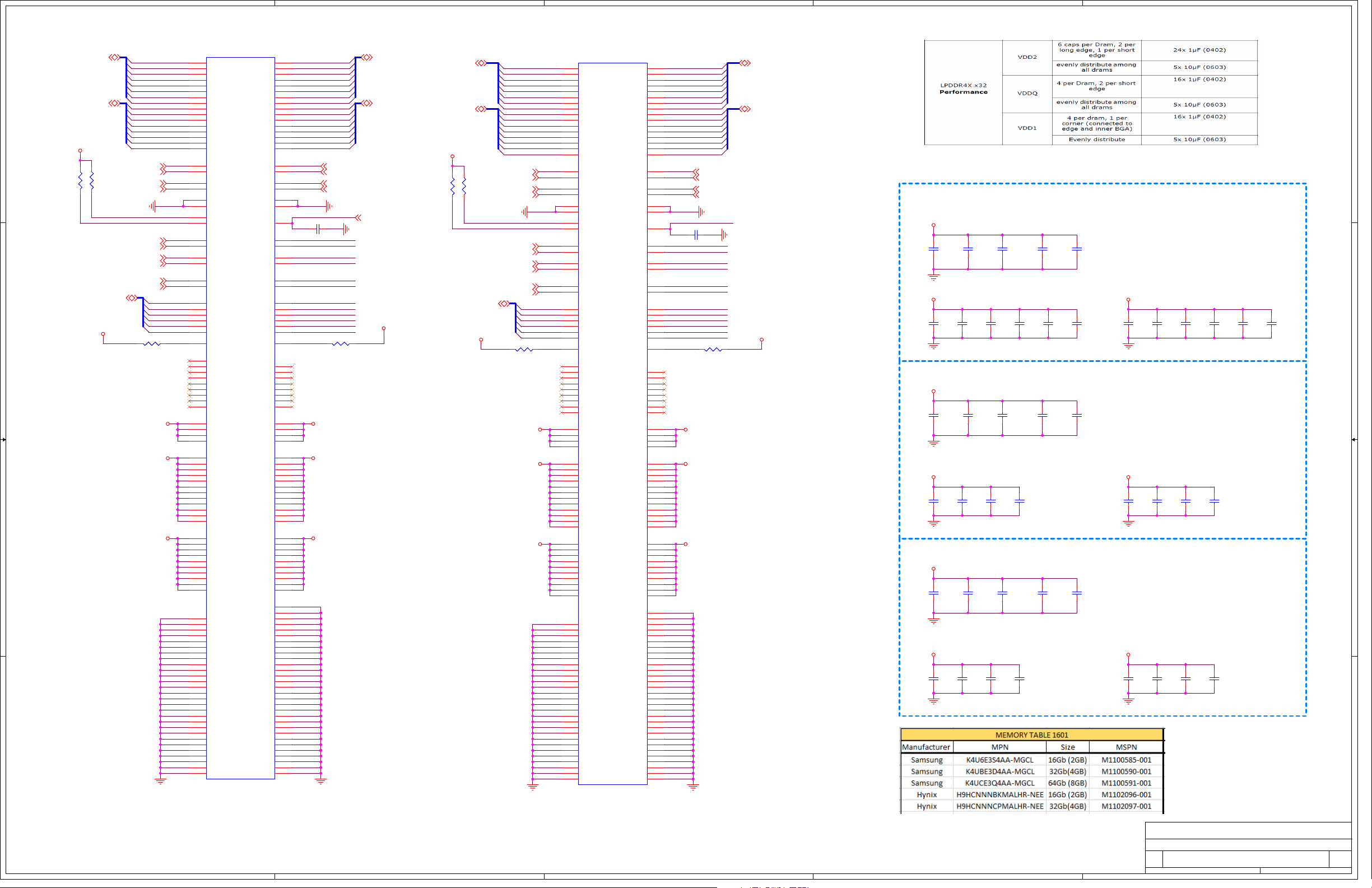

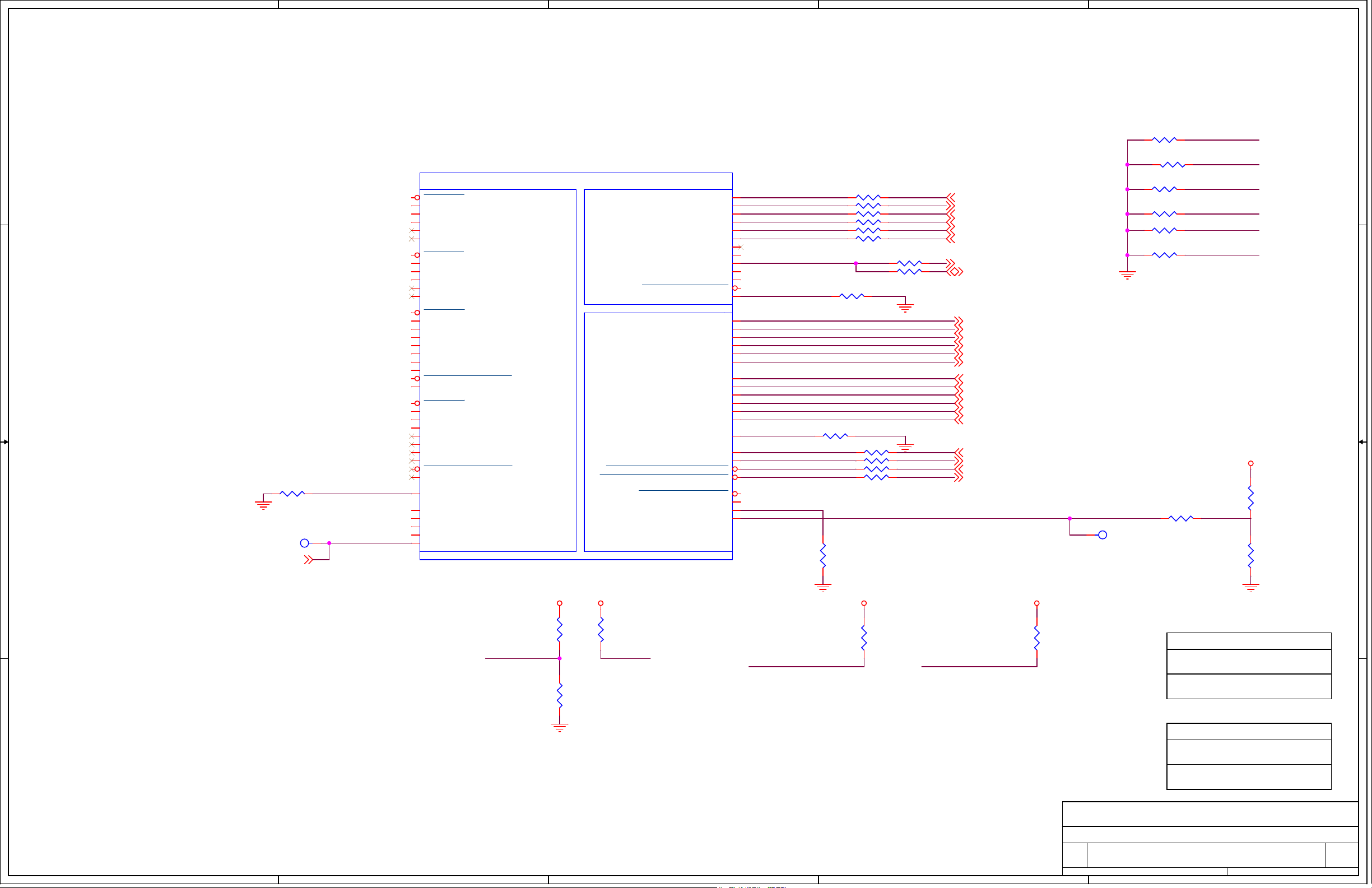

CPU(2)_LPDDR

CPU(3)_ICL POWER1_DDR_VCCSTG

CPU(4)_ICL_POWER2_VCCIN

Page

31

32

33

34

35

36

37

38

39

40

41

42

43

Title

Power/Volume Button Debug

Sensors

Debug Conn

SAM_1_PWR_ADC_Debug

SAM_2

X

Level Shifters

TPM

Temp Sensor

REALTEK ALC3269C-GRT CODEC

Headphone/Speaker Connector

Audio Smart Amp

X

Page

61

62

63

64

65

66

67

68

69

70

71

72

73

Title

X

+1.8VSB & Load SW

CHARGER

+5V Load SW

+3P3V Load SW

VCCIN Coontroller

VCCIN DRMOS

VCCINAUX Controller

VCCINAUX DRMOS

SL1 PWR/ BATT CONN.10

SL1 SIGNALS

+3P3V_HPD/LCD backlight

X

14

15

16

17

18

19

20

21

B B

22

23

24

25

26

27

28

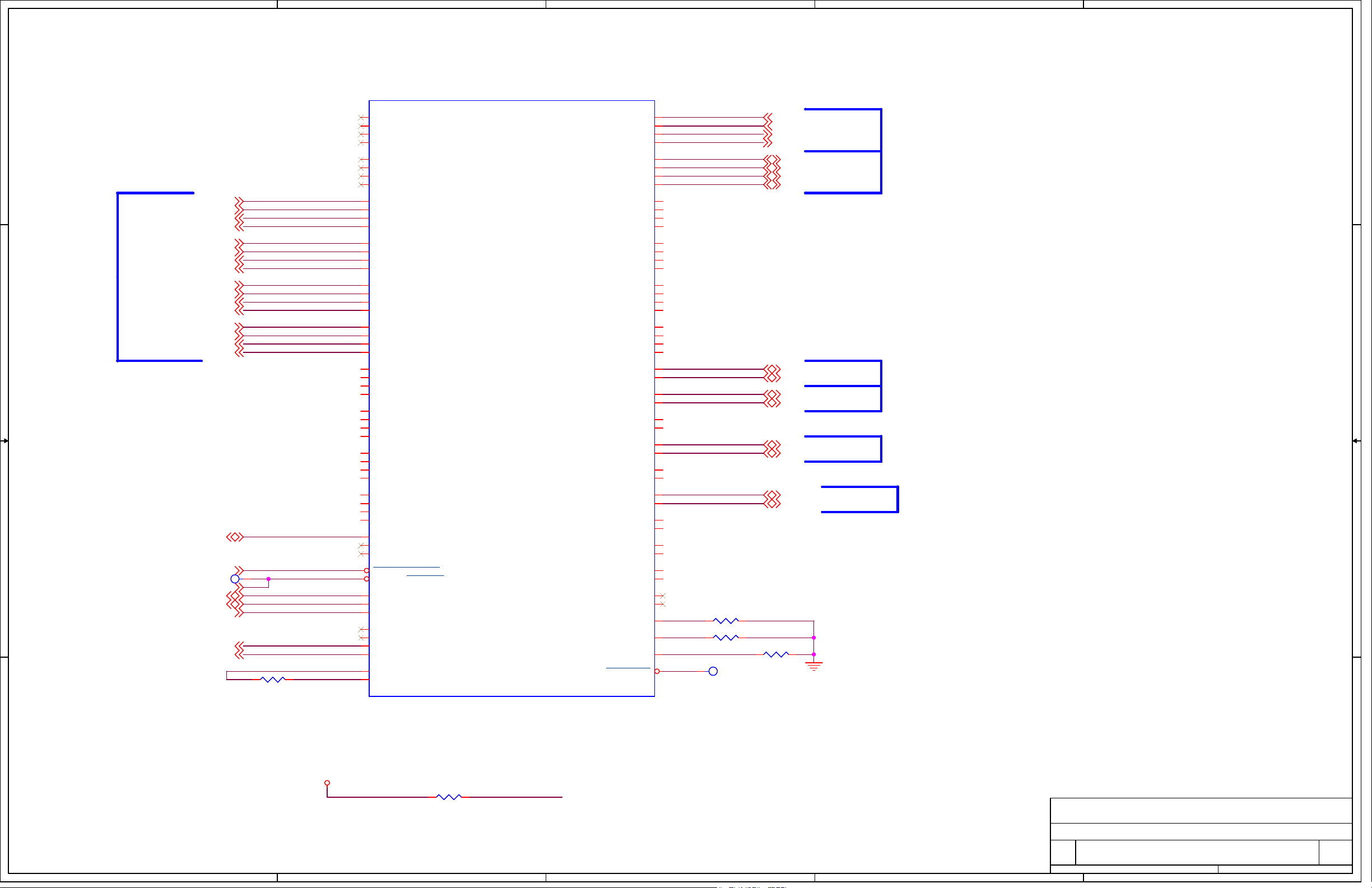

CPU(5)_GND

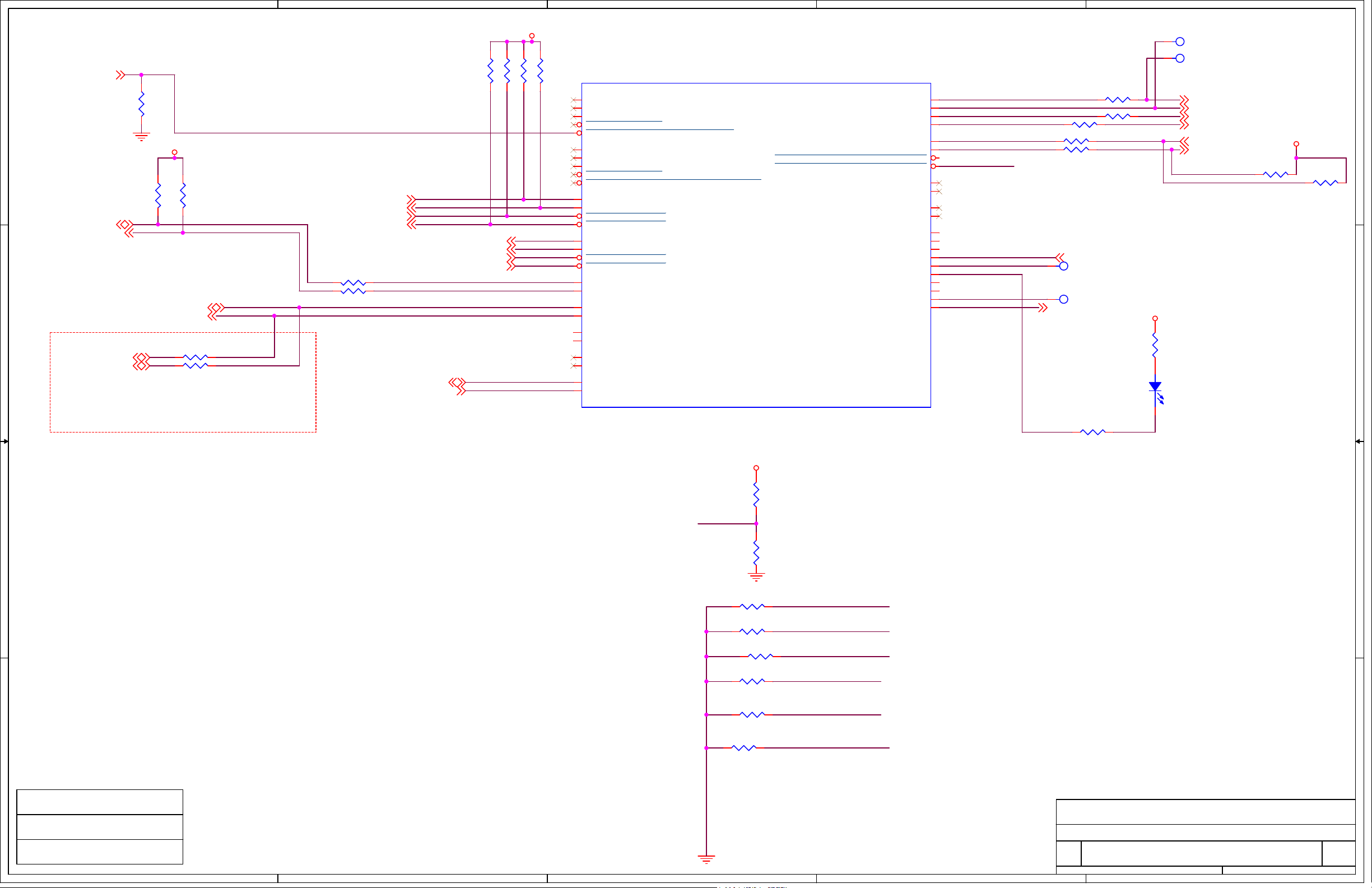

CPU(6)_CFG_RESERVED

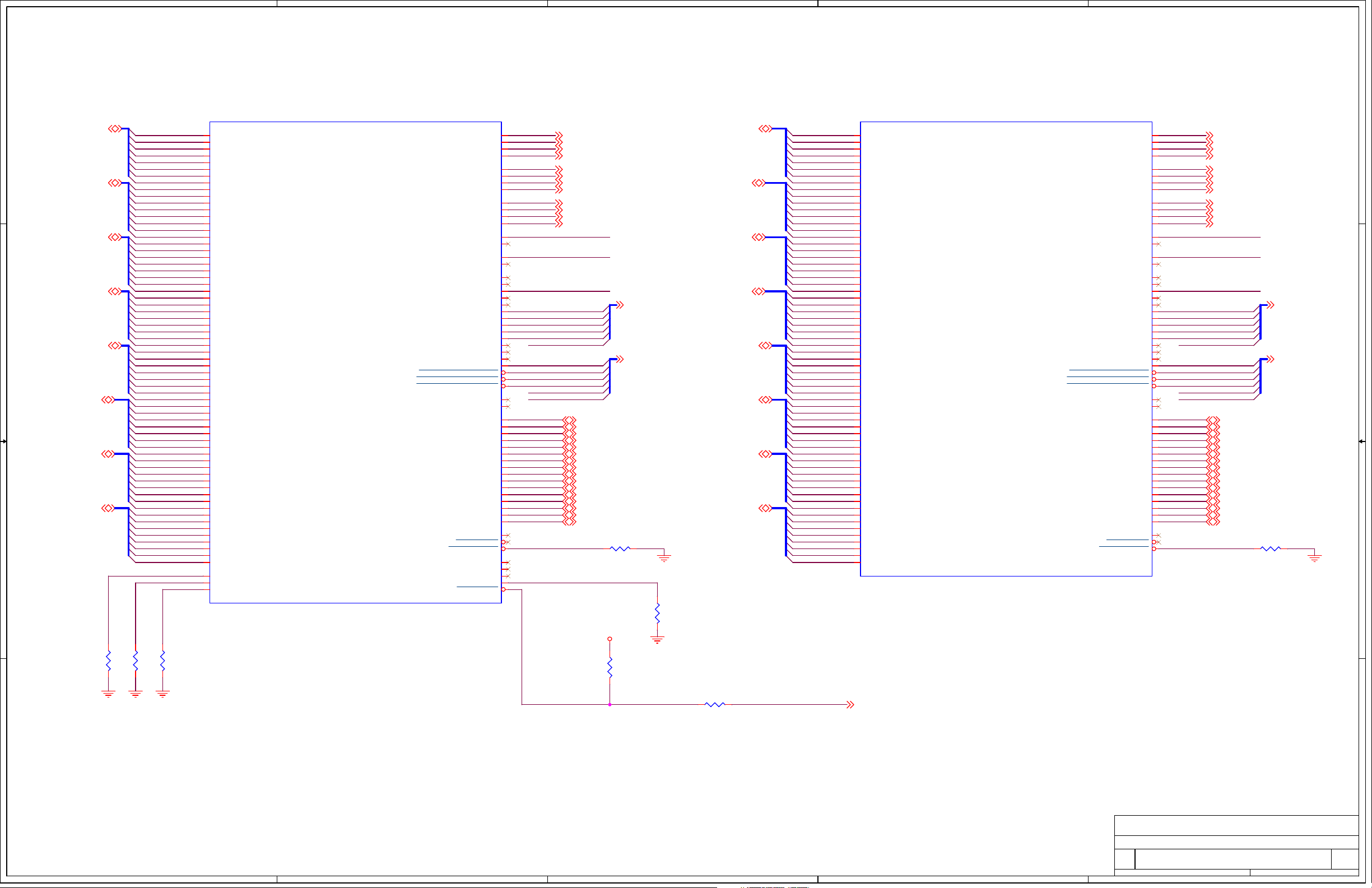

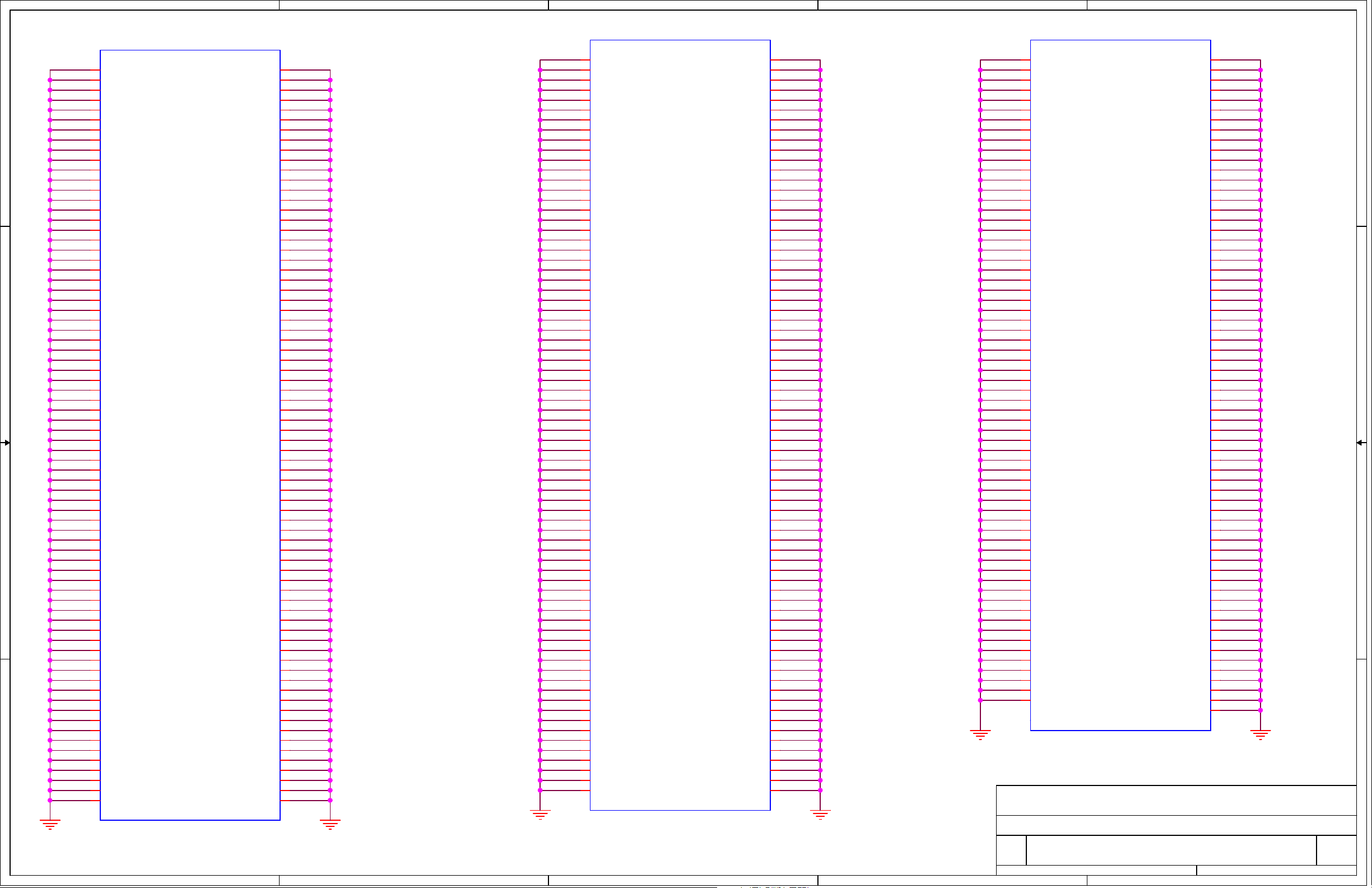

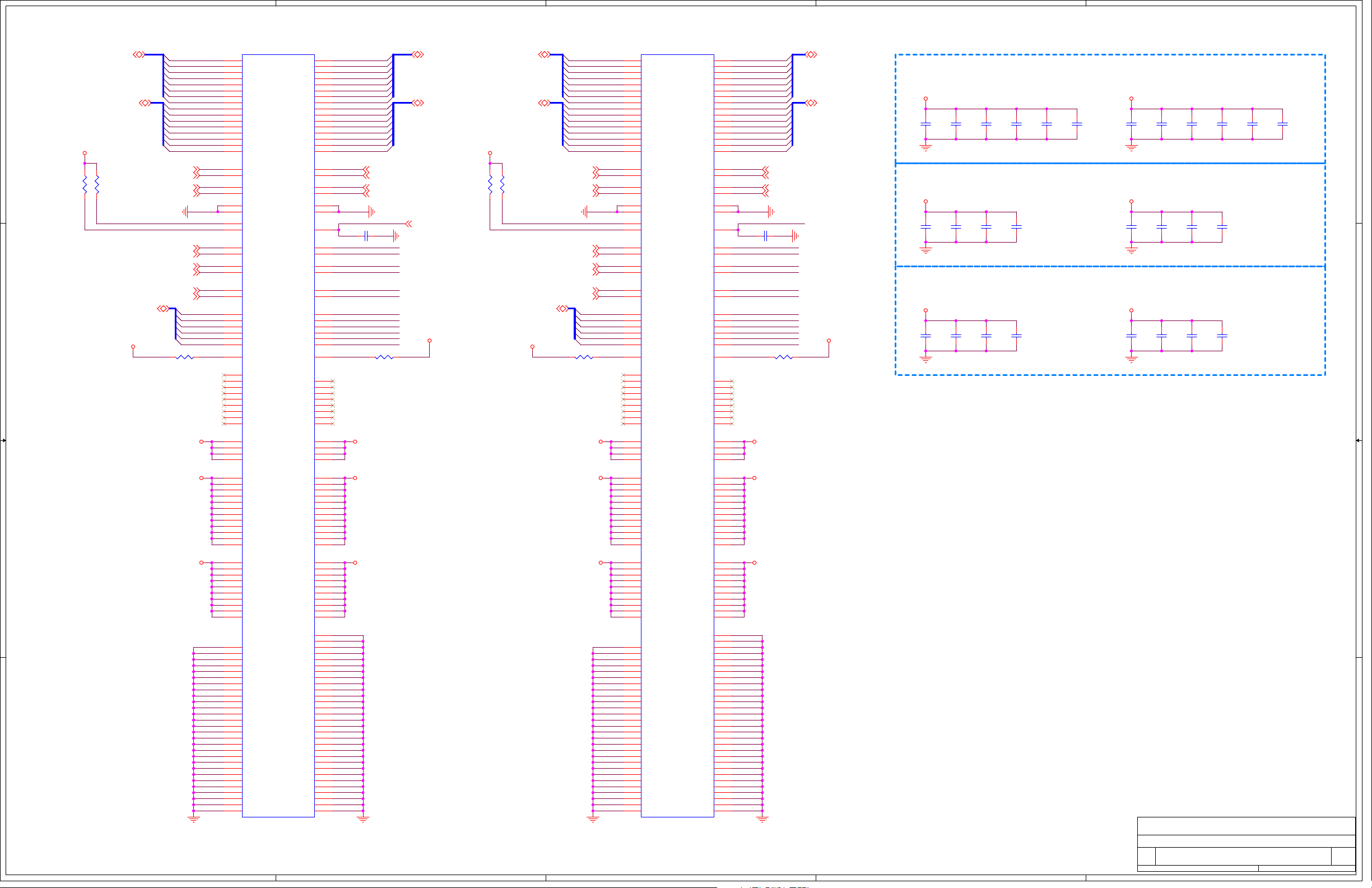

LPDDR3(1)_MEMORY DOWN

LPDDR3(2)_MEMORY DOWN

SFF

Mechanical Parts

PCH(1)_SD,HDA,RTC, CLK

PCH(2)_CLK,SMB,LPC, SPI

PCH(3)_SYS PWR CONTR

PCH(4)_CSI,eMMC,CNVi

PCH(5)_PCIE,USB

PCH(6)_CPU,GPIO,MISC

PCH(7)_POWER

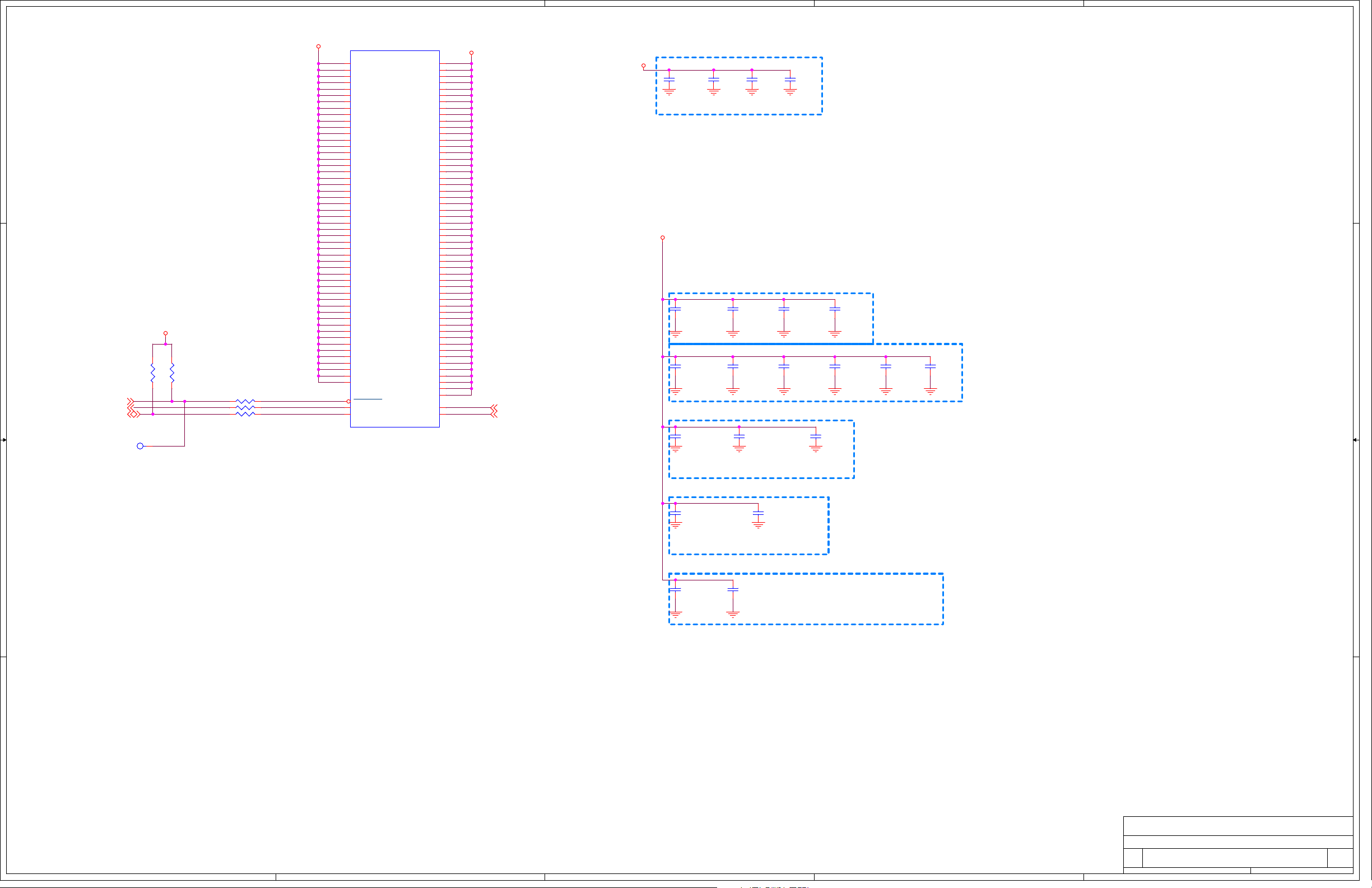

PCH(8)_VCCIN_AUX_Decoupling

Power Monitor

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

M.2 SSD Connector

USB A 3.0 Port

DP Dongle Control

X

uSD Card B2B

X

Wi-Fi_BT

X

X

X

Camera Front/IR Connector

VA and VCCRTC

+VCCSTG

eDP connector

Silego Controller

74

75

76

77

78

80

81

82

KBTP Connector

X

X

USB Type-C Port

X

USB Type-C PD79

X

X

X

29

30

A A

Type-C Debug

Touch Con & Key

59

60

+5VSB & +3P3VSB

+1P2V_DUAL&++0P6V_DDR_VDDQ

DBG_S - Replace with board short for MP

CAD Note:

Property: BUILD-OPT

DNP = Do Not Place

5

DBG_R - Replace with lower cost component for MP

DBG_N - Install for Non-Debug Builds

DBG_D - Remove from BOM (Depopulate) for MP

DBG_T - Used for Telemetry in MP as needed

DBG_TS - Used for Telemetry in MP as needed. This part needs to be

replaced with a short if telemetry is not needed.

4

3

<Variant Name>

<Variant Name>

<Variant Name>

Table of Contents

Table of Contents

Title:

Title:

Title:

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

Table of Contents

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

1 82Tuesday, May 21, 2019

1 82Tuesday, May 21, 2019

1

1 82Tuesday, May 21, 2019

<RevCode>

<RevCode>

<RevCode>

Page 2

5

D D

4

3

2

1

C C

B B

A A

Build Options

Build Options

Build Options

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

1

1.00

1.00

1.00

2 82Tuesday, May 21, 2019

2 82Tuesday, May 21, 2019

2 82Tuesday, May 21, 2019

CAD Note:

Defaults: Footprint SMD 0201, Cap tmp Coeff X5R, 1% resistors

5

4

3

Title:

Title:

Title:

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

Page 3

5

4

3

2

1

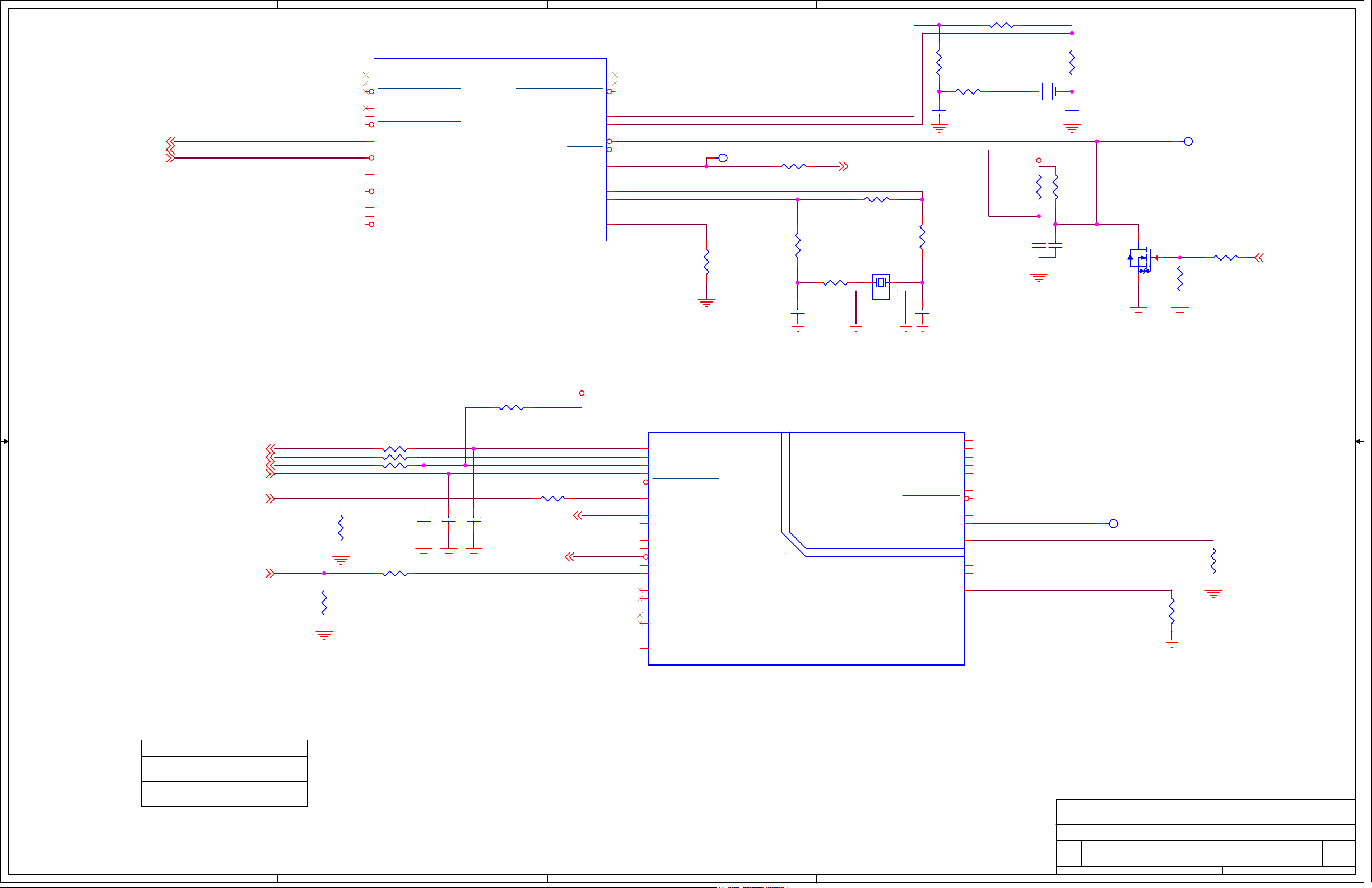

LAST UPDATE - Oct 25 2018

D D

EDAN-A

Dragonfly

Debug connector

Multiple MB

interfaces

IR Camera

IR

OV7251

LED

MIPI

Power Monitors

MIPI MIPI

RTS5849D-GR ISP

Firefly

USB-C

conn

Type C Debug

Multiple MB

interfaces

Chimera

SSD M.2

128GB, 256GB

C C

512GB, 1TB

LPDDR4X x32

LPDDR3 x32

LPDDR3 x32

LPDDR3 x32

8,16,32 GB

128-bit (32b x 4) – 2 Chl -64 bit each

I2C

4x PCIe

USB2

USB2

USB2

I2C

PCIe

DDR

Front RGB Camera

OV9734

MIPI

ALS

TCS3430

Chimera FPC

I2C

SPI

HDA

PDM

USB3

USB2

TPM

Nuvoton

NationZ

I2C

SPI

Chimera FPC

I2C

HD Audio

Digital

Mic

Digital

Mic

USB3.1

USB2

SPI ROM

ALC 3300

Codec

PDM

16MB

R

ALC1304M

L

AMP

Analog audio combo jack

Right

Left

USB A Port

Block Diagram 1.6

USB3

USB2

CNVi

USB3.1

USB2

DP

DP

SL40

PWR_SL

Wifi

CNVi

Harrison Peak

Thermal

Sensors

Hall

Sensor

BU52072

Chimera

LCD

13.5"

15"

eDP

CONN

I2C

eDP

NTRIG G5

SPI

I2C

eDP

SPI

Ice Lake

U 4+2

IO

IOx

Backlight

Controller

AND

PWM_EN

PWM

BT

Greenpak

B B

KBTP CONN

Battery

Connector

IOx

GPIO

UART

16Mb SPI

Flash

I2C

SPI

I2C

SAM

eSPI

UART

PWM

eSPI

UART

FAN

I2C

SML1

USBC

USB2

I2C

8Mb SPI

Flash

USBC

PD Controller

Retimer

SPI

USB2

USBC

CC1/CC2

TCP_VBUS

USB C Port

BQ25713

+5VSB

SPI

8Mb SPI

Flash

LEGEND

Edan-A specific

Common to Foxburg

I2C

VBAT

VBATI2C

Battery

Charger

VBAT

EXT_DC_IN

Charging

FET’s

A A

Fuel

Gauge

5

2S3P batt

49.4 WHr

PWR_SL

IMVP9

4

3

VCCIN

AUX

ROP

Power

Debug feature

BLOCK DIAGRAM

BLOCK DIAGRAM

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A1

A1

A1

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Title:

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

BLOCK DIAGRAM

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

3 82Tuesday, May 21, 2019

3 82Tuesday, May 21, 2019

3 82Tuesday, May 21, 2019

1.00

1.00

1.00

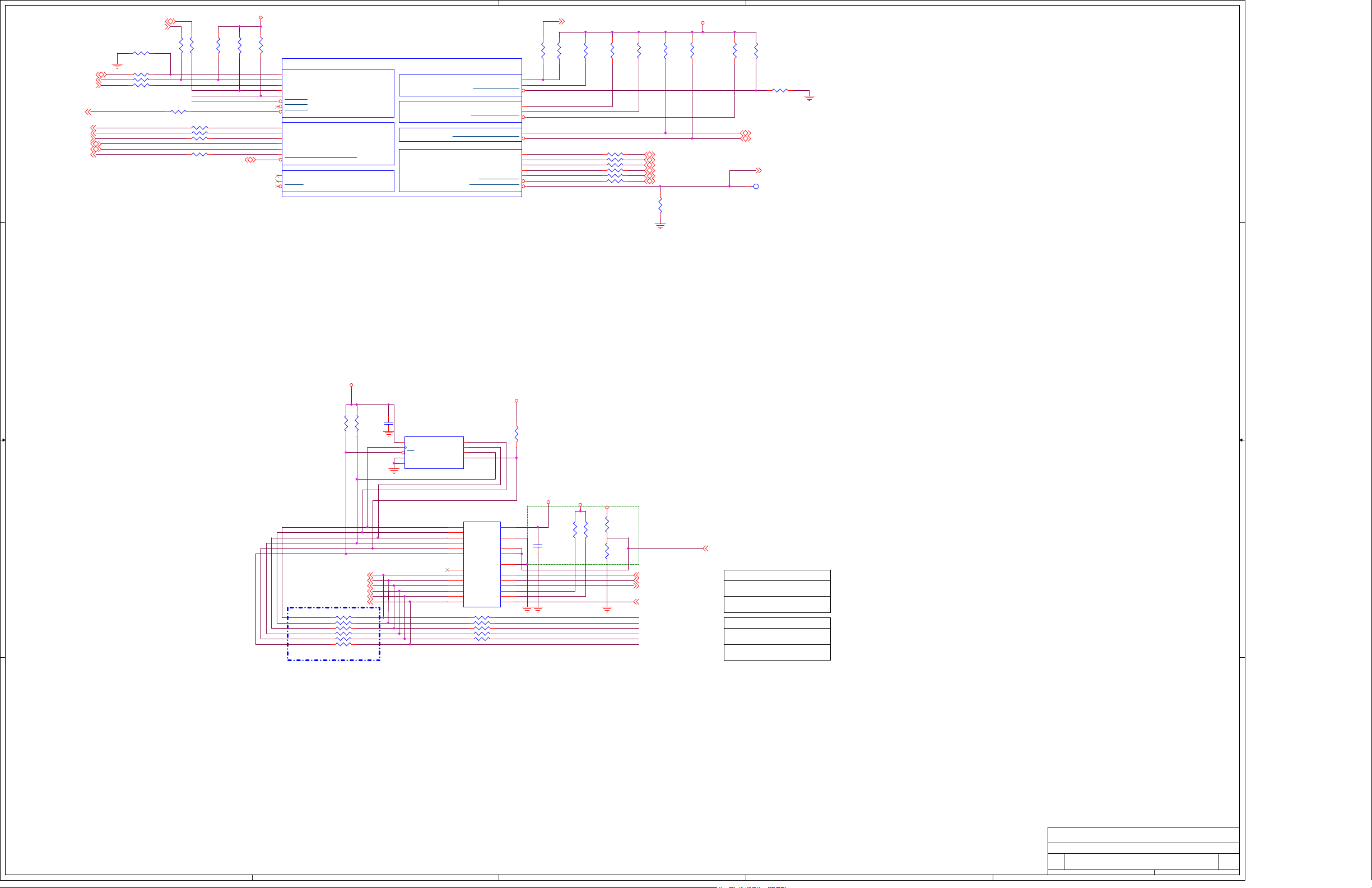

Page 4

5

D D

4

3

2

1

C C

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

CLCOK DISTRIBUTION

CLCOK DISTRIBUTION

Title:

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

CLCOK DISTRIBUTION

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

4 82Tuesday, May 21, 2019

4 82Tuesday, May 21, 2019

1

4 82Tuesday, May 21, 2019

2.89.6

2.89.6

2.89.6

Page 5

5

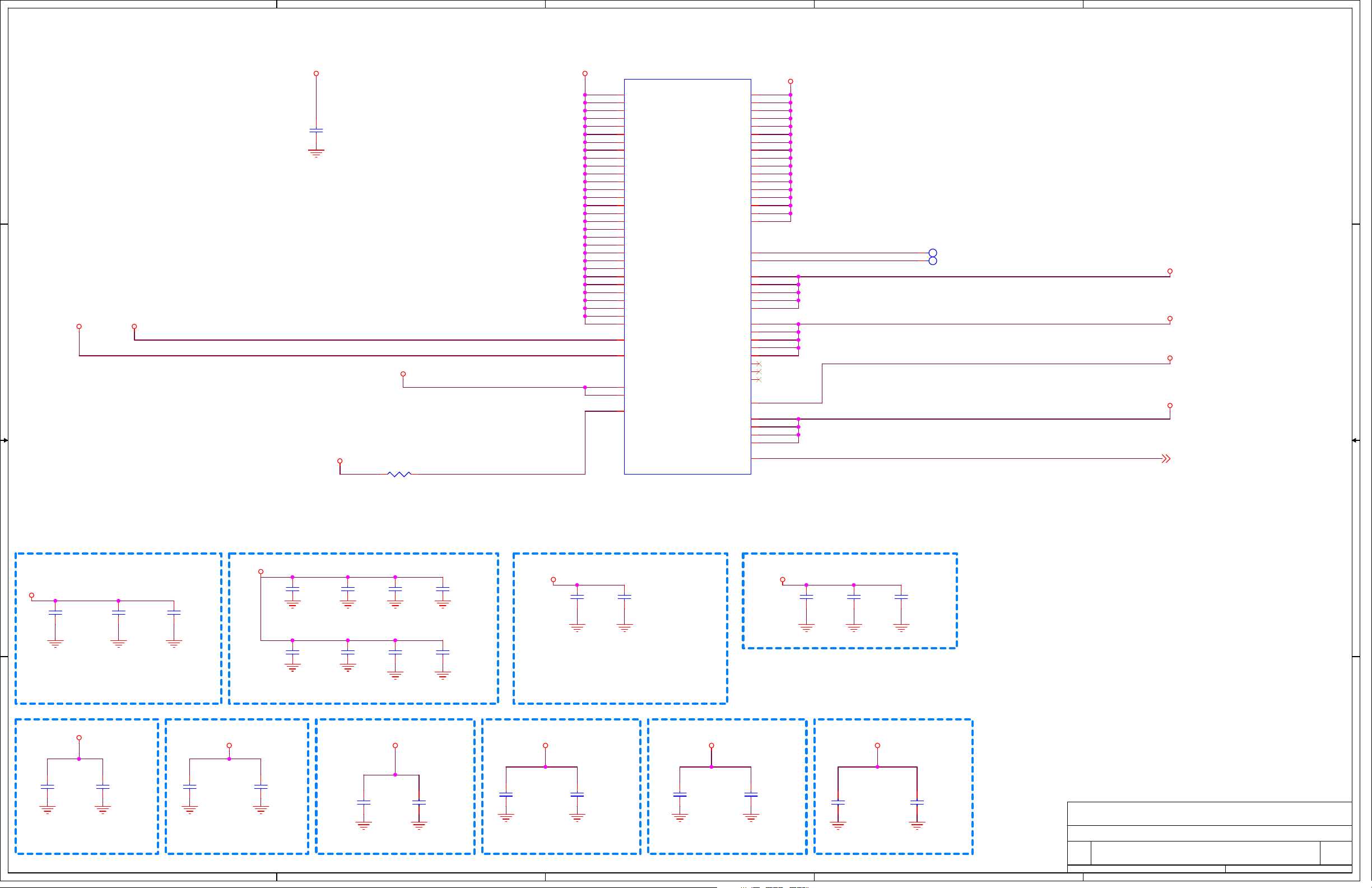

SIGNAL & RESET MAP

4

3

2

1

Last Update - Feb 13 2018

D D

Battery

+VDD_BATA_PACK

SL1_PWR_GOOD

SL1

PWR_SL1_F

SW

Switch

(Diode)

1-1

+V_ALWAYS_ON

TCP0_VBUS_PWR_GOOD

USB-C

+VBUS_P0_CONN

TCP1_VBUS_PWR_GOOD

USB-C

C C

+VBUS_P1_CONN

SAM_SL1_PWR_EN

TCP0_LS_EN_N

TCP1_LS_EN_N

LS

LS

CHG_BATDRV_A

LS

FET

SW

SW

EXT_DC_IN

Step Down

LDO

Charging

circuit

& Switch

+3P3VSB

+5VSB

+5VSB2

1-2

+VSYS

+1P8VSB

10

1P8VSB_PG

+VCCIN_AUX

11

VCCIN_AUX_READY

+VNN_BYP

12

+V1P05_BYP_EN

+1P8V_DDR_VDD1

+V1P05_BYP

+1P1V_DDR_VDD2

B B

+3P3VAS

2

+VCC_RTC

Silego

1 of 2

Power

Button

6

SUS_PWRGD

+1P8VAS

3P3VA_EN

PWRBTN#_1V8

VSUS_ON

13

VCCIN_AUX_PG

17

SLP_S4_DRV#

19

SLP_S3_DRV#

3 4

LDO

+1P8V_SAM

5

7

SAM

LPC

15

SAM_PCH_PWRBT N#

14

RSMRST#

8

PCH_DPWROK

9

SLP_SUS#

23

PM_PCH_PWROK

24

SYS_PWROK

21

VCCST_PWRGD

PWRBTN#

RSMRST#

DSW_PWROK

SLP_SUS#

PCH_PWROK

SYS_PWROK

VCCST_PWRGD

Intel

PCH

16

18

SLP_S3#

SLP_S4#

PLTRST#

SLP_S4#

SLP_S3#

25

PLTRST#

SAM

TPM

SSD/M.2

PLTRST_BUF#

AND Gate

Buffer

Silego

2 of 2

+1P1V_DDR_PG

3P3V/5V

3P3V_SSD_M2

ML_3P3V_PWR_FUSE (MDP)

OD

page 75

+3P3V_SSD

Power On Sequence

20

ALL_SYS_PWRGD

1

VRDY

3

EN

22

VRM_PWRGD

2

A A

VCCIN

5

4

25

<Core Design>

<Core Design>

<Core Design>

SIGNAL&RESET MAP

SIGNAL&RESET MAP

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Title:

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

1

SIGNAL&RESET MAP

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

5 82Tuesday, May 21, 2019

5 82Tuesday, May 21, 2019

5 82Tuesday, May 21, 2019

1.00

1.00

1.00

Page 6

5

4

3

2

1

LAST UPDATE - Sept 13 2018

EDAN/HOOK Power Flow EV1

D D

C C

B B

A A

<Core Design>

<Core Design>

<Core Design>

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A1

A1

A1

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Title:

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

POWER FLOW (1 OF 3)

POWER FLOW (1 OF 3)

POWER FLOW (1 OF 3)

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

1.00

1.00

1.00

6 82Tuesday, May 21, 2019

6 82Tuesday, May 21, 2019

6 82Tuesday, May 21, 2019

Page 7

5

4

3

2

1

LAST UPDATE - SEPT. 13 2018

D D

C C

B B

A A

<Core Design>

<Core Design>

<Core Design>

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A1

A1

A1

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Title:

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

POWER FLOW (2 OF 3)

POWER FLOW (2 OF 3)

POWER FLOW (2 OF 3)

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

1.00

1.00

1.00

7 82Tuesday, May 21, 2019

7 82Tuesday, May 21, 2019

7 82Tuesday, May 21, 2019

Page 8

5

4

3

2

1

LAST UPDATE - SEPT. 13 2018

D D

C C

B B

A A

<Core Design>

<Core Design>

<Core Design>

POWER FLOW (3 OF 3)

POWER FLOW (3 OF 3)

Title:

Title:

Title:

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

POWER FLOW (3 OF 3)

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

8 82Tuesday, May 21, 2019

8 82Tuesday, May 21, 2019

1

8 82Tuesday, May 21, 2019

1.00

1.00

1.00

Page 9

5

4

3

2

1

LAST UPDATE - APR.2018 (OUTDATED)

D D

C C

B B

A A

09. I2C MAP

09. I2C MAP

09. I2C MAP

Title:

Title:

Title:

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A1

A1

A1

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

1.00

1.00

1.00

9 82Tuesday, May 21, 2019

9 82Tuesday, May 21, 2019

9 82Tuesday, May 21, 2019

Page 10

5

4

3

2

1

+VCCST_CPU

U1003

5

VCC

4

PCB1001

D D

ALL

H_PROCHOT#[26,63,66,76]

C C

SAM_PROCHOT[35]

Q1001

SOT-VMT3_1P2XP8XP55_P4MM-1

U1002

H_PROCHOT#

B B

TBT_LSX0_TXD[77]

TBT_LSX0_RXD[77]

I2O

1

NC1

74AUP1G07GX

+3P3VSB

R1011

100K

ALL

HIGH: JTAG ODT ENABLED

Pull up or down straps required

DDP1 I2C/TBT LSX #0/BSSB-LS#0 VCC

GPP_E19/DDP1_CTRLDATA

0 1.8V

1

3.3V

DDP2 I2C/TBT LSX #1/BSSB-LS#1 VCC

A A

GPP_E21/DDP2_CTRLDATA

0 1.8V

1

3.3V

TOP

Bottom

M1098028-005

R1001

330

Added terminatio n when PECI trans is DNP

Intel recommend ed 200-400 Ohm PD

R1037

100

0402S_P4

G

DBG_PMODE[18,29]

+VCCST_CPU

5

VCC

4

3

GND

+1P8VSB

R1042

75K

DNP

GPP_E6

R1091

20K

eSPI Flash Sharing Mode

+VCCSTG_TERM

R1008

1K

0201S_P28-W 35

H_PROCHOT#

D

R1023 49.9

R1022 49.9

0201S_P28-W35

0201S_P28-W35

S

+1P8VSB

R1039

10K

C1009

0.1u 10V

H_PROCHOT_1P8V# [33,34]

eDP

mDP

+3P3V_PANEL_EN_R[65]

SLDP_CTRL_CLK[46]

SLDP_CTRL_DATA[46]

LOW: 1.8V FOR BSSB SINGAL THROUGH LS

EDP_HPD[57]

SL1_DP_HPD[71]

R1017 100K

GPP_H2

0 DEFAULT Master Attached

1

Slave Attached

R1002 499

0201S_P28-W 35

C1008 47pDNP

0201S_P33

EDP_TX0_DN[57]

EDP_TX0_DP[57]

EDP_TX1_DN[57]

EDP_TX1_DP[57]

EDP_TX2_DN[57]

EDP_TX2_DP[57]

EDP_TX3_DN[57]

EDP_TX3_DP[57]

EDP_AUX_DN[57]

EDP_AUX_DP[57]

PCH_SERIRQ[38]

+VCCST_CPU

R1016

49.9

0201S_P28-W 35

H_PROCHOT#_R

PROC_POPIRCOMP

PCH_OPIRCOMP

DBG_PMODE

SAM_PCH_PW RBTN#[22,37]

R1010

DNP

1K

PCIE_SSD_PERST#[44]

R1015 15

R1034 0

R1014 0

R1006 0

GPP_E17 reserved for GPU_EVENT# for SB

R1033 1M

+3P3VSB

PCH_VDD_PANEL_EN[30,65]

PCH_LCD_BKLT_EN[34,72]

PCH_BKLT_CTRL_PW M[72]

BB_FORCE_PW R[77,79]

R1007 1K

DNP

GPP_E22_SERIRQ

GPP_E23_3P3_PNL

EDP_DISP_UTIL

DNP

R1019

0

GPP_E6[18]

DP_RCOMP

TP_CATERR#_R [ 76]

GPP_E3[18]

GPP_E7[18]

R10430

R1040

49.9K

0201S_P28-W 35

R1003

150

I2O

1

NC1

3

GND

74AUP1G07GX

+VCCST_CPU

R1020

1K

0201S_P28-W 35

H_THERMTRIP#[58]

TP_CATERR#_R

PM_THRMTRIP#

PCH_PW RBTN#

GPP_H2

Y5

Y3

Y1

Y2

V2

V1

V3

V5

W4

W3

AE3

AE5

AE2

AE1

AC5

AC3

AC1

AC2

AD3

AD4

DP15

DJ17

DL40

DP42

DL17

DK17

DN17

DP17

DK34

DL34

DN33

DL33

DW11

CV42

CV39

CY43

CR41

CT41

DV14

DN21

DL19

DU19

J3

D2

R2

J4

CD5

PECI

C3

E3

CJ41

DU3

A14

B14

INT. PU

DL15

DV11

DT11

CR38

CR39

DT12

INT. PD

DJ38

DL38

U1001A

DDIA_TXN_0

DDIA_TXP_0

DDIA_TXN_1

DDIA_TXP_1

DDIA_TXN_2

DDIA_TXP_2

DDIA_TXN_3

DDIA_TXP_3

DDIA_AUX

DDIA_AUX_P

DDIB_TXN_0

DDIB_TXP_0

DDIB_TXN_1

DDIB_TXP_1

DDIB_TXN_2

DDIB_TXP_2

DDIB_TXN_3

DDIB_TXP_3

DDIB_AUX

DDIB_AUX_P

GPP_E22/DDPA_CTRLCLK/PCIE_LNK_DOWN

GPP_E23/DDPA_CTRLDATA/BK4/SBK4

GPP_H16/DDPB_CTRLCLK

GPP_H17/DDPB_CTRLDATA

GPP_E18/DDP1_CTRLCLK/TBT_LSX0_TXD

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD

GPP_E20/DDP2_CTRLCLK/TBT_LSX1_TXD

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD

GPP_D9/ISH_SPI_CS_N/DDP3_CTRLCLK/GSPI2_CS0_N/TBT_LSX2_TXD

GPP_D10/ISH_SPI_CLK/DDP3_CTRLDATA/GSPI2_CLK/TBT_LSX2_RXD

GPP_D11/ISH_SPI_MISO/DDP4_CTRLCLK/GSPI2_MISO/TBT_LSX3_TXD

GPP_D12/ISH_SPI_MOSI/DDP4_CTRLDATA/GSPI2_MOSI/TBT_LSX3_RXD

GPP_E14/DPPE_HPDA/DISP_MISCA

GPP_A18/DDSP_HPDB/DISP_MISCB

GPP_A19/DDSP_HPD1/DISP_MISC1

GPP_A20/DDSP_HPD2/DISP_MISC2

GPP_A14/USB_OC1_N/DDSP_HPD3/DISP_MISC3

GPP_A15/USB_OC2_N/DDSP_HPD4/DISP_MISC4

GPP_E17

EDP_VDDEN

EDP_BKLTEN

EDP_BKLTCTL

RSVD_1

DISP_UTILS

DISP_RCOMP

M1042225-001

R1018 0

U1001D

CATERR

PECI

PROCHOT

THRMTRIP

PROC_POPIRCOMP

PCH_OPIRCOMP

RSVD_A14

RSVD_B14

DBG_PMODE

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

GPP_E6

GPP_H2/CNV_BT_I2S_SDO

GPP_H19/TIME_SYNC0

M1042225-001

C1001

0.1u 6.3V

0201S_P28-W 35

4 OF 19

+1P8VSB

R1012

10K

PM_THRMTRIP#

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_JTAGX

PROC_PRDY

PROC_PREQ

1 OF 19

PCH_CATERR#_1V8 [33,34 ]

+VCCSTG_TERM +3P3VSB

R1021

5.1

DBG_D

D

Q1002

DBG_D

P3

K5

K3

P4

N1

N5

R5

K1

K2

N3

N2

P6

M6

G

+VCCSTG_TERM

S

GPP_A17/DISP_MISCC

R1038 100

R1004 49.9

TCP0_TX_N0

TCP0_TX_P0

TCP0_TX_N1

TCP0_TX_P1

TCP0_TXRX_N0

TCP0_TXRX_P0

TCP0_TXRX_N1

TCP0_TXRX_P1

TCP0_AUX

TCP0_AUX_P

TCP1_TX_N0

TCP1_TX_P0

TCP1_TX_N1

TCP1_TX_P1

TCP1_TXRX_N0

TCP1_TXRX_P0

TCP1_TXRX_N1

TCP1_TXRX_P1

TCP1_AUX

TCP1_AUX_P

TCP2_TX_N0

TCP2_TX_P0

TCP2_TX_N1

TCP2_TX_P1

TCP2_TXRX_N0

TCP2_TXRX_P0

TCP2_TXRX_N1

TCP2_TXRX_P1

TCP2_AUX

TCP2_AUX_P

TCP3_TX_N0

TCP3_TX_P0

TCP3_TX_N1

TCP3_TX_P1

TCP3_TXRX_N0

TCP3_TXRX_P0

TCP3_TXRX_N1

TCP3_TXRX_P1

TCP3_AUX

TCP3_AUX_P

TC_RCOMP

TC_RCOMP_P

GPP_A21

GPP_A22

DBG_D

R1013 100K

DNP

SAM_SOC_JTAG_T RST# [35]

XDP_TCK [18,76]

XDP_TDI [18,76]

XDP_TDO [18,76]

XDP_TMS [18,76]

XDP_TRST# [18,76]

PROC_PRDY# [18]

PROC_PREQ# [18]

R1005 49.9

BB5

BB6

AV6

AV5

BH2

BH1

BF1

BF2

AY5

AY6

AR5

AR6

AL5

AL3

BD2

BD1

BB1

BB2

AN3

AN5

BF6

BF5

BJ5

BJ6

BL1

BL2

BM2

BM1

BG6

BG5

BP6

BP5

BV5

BV6

BR1

BR2

BT2

BT1

BT6

BT5

TCRCOMP_DN

AY1

TCRCOMP_DP

AY2

CT38

CV43

CV41

R1009

150

TP1001

EDP_I2C_INT [57,76]

+VCCSTG_TERM

100

R1028

R1027 49.9

R1030 1K

DNP

R1026 49.9

PCH_TRST# [18,76]

PCH_JTAG_TCK [ 18,76]

PCH_JTAG_TDI [18,76]

PCH_JTAG_TDO [18,76]

PCH_JTAG_TMS [18,76]

PCH_JTAGX [18, 76]

DNP

R1029

49.9

0201S_P28-W 35

TBL1001

Table is not avaliable now.

TCP0_TX_N0 [77]

TCP0_TX_P0 [77]

TCP0_TX_N1 [77]

TCP0_TX_P1 [77]

TCP0_TXRX_N0 [77]

TCP0_TXRX_P0 [77]

TCP0_TXRX_N1 [77]

TCP0_TXRX_P1 [77]

TCP0_AUX_DN [77]

TCP0_AUX_DP [77]

SL_DATA0_DN [71]

SL_DATA0_DP [71]

SL_DATA2_DN [71]

SL_DATA2_DP [71]

SL_DATA1_DN [71]

SL_DATA1_DP [71]

SL_DATA3_DN [71]

SL_DATA3_DP [71]

SLDP_AUX_DN [46]

SLDP_AUX_DP [46]

USBA_EN [45]

USB-C

USB-C

SL40

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

W x H 437 x 328 mm

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

CPU(1)_Disp,Type-C,MISC

CPU(1)_Disp,Type-C,MISC

CPU(1)_Disp,Type-C,MISC

Title:

Title:

Title:

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

Engineer:

1

0.23

0.23

10 82Tuesday, May 21, 2019

10 82Tuesday, May 21, 2019

10 82Tuesday, May 21, 2019

0.23

Page 11

5

4

3

2

1

D D

C C

B B

M_A_0_DQ_[7:0][16]

M_A_1_DQ_[7:0][16]

M_A_2_DQ_[7:0][16]

M_A_3_DQ_[7:0][16]

M_B_0_DQ_[7:0][16]

M_B_1_DQ_[7:0][16]

M_B_2_DQ_[7:0][16]

M_B_3_DQ_[7:0][16]

M_A_0_DQ_0

M_A_0_DQ_1

M_A_0_DQ_2

M_A_0_DQ_3

M_A_0_DQ_4

M_A_0_DQ_5

M_A_0_DQ_6

M_A_0_DQ_7

M_A_1_DQ_0

M_A_1_DQ_1

M_A_1_DQ_2

M_A_1_DQ_3

M_A_1_DQ_4

M_A_1_DQ_5

M_A_1_DQ_6

M_A_1_DQ_7

M_A_2_DQ_0

M_A_2_DQ_1

M_A_2_DQ_2

M_A_2_DQ_3

M_A_2_DQ_4

M_A_2_DQ_5

M_A_2_DQ_6

M_A_2_DQ_7

M_A_3_DQ_0

M_A_3_DQ_1

M_A_3_DQ_2

M_A_3_DQ_3

M_A_3_DQ_4

M_A_3_DQ_5

M_A_3_DQ_6

M_A_3_DQ_7

M_B_0_DQ_0

M_B_0_DQ_1

M_B_0_DQ_2

M_B_0_DQ_3

M_B_0_DQ_4

M_B_0_DQ_5

M_B_0_DQ_6

M_B_0_DQ_7

M_B_1_DQ_0

M_B_1_DQ_1

M_B_1_DQ_2

M_B_1_DQ_3

M_B_1_DQ_4

M_B_1_DQ_5

M_B_1_DQ_6

M_B_1_DQ_7

M_B_2_DQ_0

M_B_2_DQ_1

M_B_2_DQ_2

M_B_2_DQ_3

M_B_2_DQ_4

M_B_2_DQ_5

M_B_2_DQ_6

M_B_2_DQ_7

M_B_3_DQ_0

M_B_3_DQ_1

M_B_3_DQ_2

M_B_3_DQ_3

M_B_3_DQ_4

M_B_3_DQ_5

M_B_3_DQ_6

M_B_3_DQ_7

U1001B

CA48

DDRA_DQ0_0/DDR0_DQ0_0/DDR0_DQ0_0

CA47

DDRA_DQ0_1/DDR0_DQ0_1/DDR0_DQ0_1

CA49

DDRA_DQ0_2/DDR0_DQ0_2/DDR0_DQ0_2

BV49

DDRA_DQ0_3/DDR0_DQ0_3/DDR0_DQ0_3

CA45

DDRA_DQ0_4/DDR0_DQ0_4/DDR0_DQ0_4

BV47

DDRA_DQ0_5/DDR0_DQ0_5/DDR0_DQ0_5

BV45

DDRA_DQ0_6/DDR0_DQ0_6/DDR0_DQ0_6

BV48

DDRA_DQ0_7/DDR0_DQ0_7/DDR0_DQ0_7

CC42

DDRA_DQ1_0/DDR0_DQ1_0/DDR1_DQ0_0

CC39

DDRA_DQ1_1/DDR0_DQ1_1/DDR1_DQ0_1

CC43

DDRA_DQ1_2/DDR0_DQ1_2/DDR1_DQ0_2

CE38

DDRA_DQ1_3/DDR0_DQ1_3/DDR1_DQ0_3

CC38

DDRA_DQ1_4/DDR0_DQ1_4/DDR1_DQ0_4

CE39

DDRA_DQ1_5/DDR0_DQ1_5/DDR1_DQ0_5

CE42

DDRA_DQ1_6/DDR0_DQ1_6/DDR1_DQ0_6

CE43

DDRA_DQ1_7/DDR0_DQ1_7/DDR1_DQ0_7

BT48

DDRA_DQ2_0/DDR0_DQ2_0/DDR0_DQ1_0

BT47

DDRA_DQ2_1/DDR0_DQ2_1/DDR0_DQ1_1

BT49

DDRA_DQ2_2/DDR0_DQ2_2/DDR0_DQ1_2

BN49

DDRA_DQ2_3/DDR0_DQ2_3/DDR0_DQ1_3

BT45

DDRA_DQ2_4/DDR0_DQ2_4/DDR0_DQ1_4

BN47

DDRA_DQ2_5/DDR0_DQ2_5/DDR0_DQ1_5

BN45

DDRA_DQ2_6/DDR0_DQ2_6/DDR0_DQ1_6

BN48

DDRA_DQ2_7/DDR0_DQ2_7/DDR0_DQ1_7

BV42

DDRA_DQ3_0/DDR0_DQ3_0/DDR1_DQ1_0

BV39

DDRA_DQ3_1/DDR0_DQ3_1/DDR1_DQ1_1

BV43

DDRA_DQ3_2/DDR0_DQ3_2/DDR1_DQ1_2

BW38

DDRA_DQ3_3/DDR0_DQ3_3/DDR1_DQ1_3

BV38

DDRA_DQ3_4/DDR0_DQ3_4/DDR1_DQ1_4

BW39

DDRA_DQ3_5/DDR0_DQ3_5/DDR1_DQ1_5

BW42

DDRA_DQ3_6/DDR0_DQ3_6/DDR1_DQ1_6

BW43

DDRA_DQ3_7/DDR0_DQ3_7/DDR1_DQ1_7

AY48

DDRB_DQ0_0/DDR0_DQ4_0/DDR0_DQ2_0

AY47

DDRB_DQ0_1/DDR0_DQ4_1/DDR0_DQ2_1

AY49

DDRB_DQ0_2/DDR0_DQ4_2/DDR0_DQ2_2

AU45

DDRB_DQ0_3/DDR0_DQ4_3/DDR0_DQ2_3

AY45

DDRB_DQ0_4/DDR0_DQ4_4/DDR0_DQ2_4

AU47

DDRB_DQ0_5/DDR0_DQ4_5/DDR0_DQ2_5

AU48

DDRB_DQ0_6/DDR0_DQ4_6/DDR0_DQ2_6

AU49

DDRB_DQ0_7/DDR0_DQ4_7/DDR0_DQ2_7

AY42

DDRB_DQ1_0/DDR0_DQ5_0/DDR1_DQ2_0

AY38

DDRB_DQ1_1/DDR0_DQ5_1/DDR1_DQ2_1

AY43

DDRB_DQ1_2/DDR0_DQ5_2/DDR1_DQ2_2

BB39

DDRB_DQ1_3/DDR0_DQ5_3/DDR1_DQ2_3

AY39

DDRB_DQ1_4/DDR0_DQ5_4/DDR1_DQ2_4

BB38

DDRB_DQ1_5/DDR0_DQ5_5/DDR1_DQ2_5

BB42

DDRB_DQ1_6/DDR0_DQ5_6/DDR1_DQ2_6

BB43

DDRB_DQ1_7/DDR0_DQ5_7/DDR1_DQ2_7

AR48

DDRB_DQ2_0/DDR0_DQ6_0/DDR0_DQ3_0

AR47

DDRB_DQ2_1/DDR0_DQ6_1/DDR0_DQ3_1

AR49

DDRB_DQ2_2/DDR0_DQ6_2/DDR0_DQ3_2

AM45

DDRB_DQ2_3/DDR0_DQ6_3/DDR0_DQ3_3

AR45

DDRB_DQ2_4/DDR0_DQ6_4/DDR0_DQ3_4

AM47

DDRB_DQ2_5/DDR0_DQ6_5/DDR0_DQ3_5

AM48

DDRB_DQ2_6/DDR0_DQ6_6/DDR0_DQ3_6

AM49

DDRB_DQ2_7/DDR0_DQ6_7/DDR0_DQ3_7

AT42

DDRB_DQ3_0/DDR0_DQ7_0/DDR1_DQ3_0

AT39

DDRB_DQ3_1/DDR0_DQ7_1/DDR1_DQ3_1

AR43

DDRB_DQ3_2/DDR0_DQ7_2/DDR1_DQ3_2

AT38

DDRB_DQ3_3/DDR0_DQ7_3/DDR1_DQ3_3

AR38

DDRB_DQ3_4/DDR0_DQ7_4/DDR1_DQ3_4

AR39

DDRB_DQ3_5/DDR0_DQ7_5/DDR1_DQ3_5

AR42

DDRB_DQ3_6/DDR0_DQ7_6/DDR1_DQ3_6

AT43

DDRB_DQ3_7/DDR0_DQ7_7/DDR1_DQ3_7

D47

DDR_RCOMP_0

E46

DDR_RCOMP_1

C47

DDR_RCOMP_2

M1042225-001

2 OF 19

DDRA_CLK_N/DDR0_CLK_N_0

DDRA_CLK_P/DDR0_CLK_P_0

DDRB_CLK_N/DDR0_CLK_N_1

DDRB_CLK_P/DDR0_CLK_P_1

DDRA_CKE0/DDR0_CKE0

DDRA_CKE1/NC

DDRB_CKE0/NC

DDRB_CKE1/DDR0_CKE1

DDRA_CS_0/DDR0_CS_N_0

DDRB_CS_1/DDR0_CS_N_1

DDRB_CA1/DDR0_MA15CAS

DDRB_CA3/DDR0_MA16RAS

DDRA_DQSN_0/DDR0_DQSN_0/DDR0_DQSN_0

DDRA_DQSP_0/DDR0_DQSP_0/DDR0_DQSP_0

DDRA_DQSN_1/DDR0_DQSN_1/DDR1_DQSN_0

DDRA_DQSP_1/DDR0_DQSP_1/DDR1_DQSP_0

DDRA_DQSN_2/DDR0_DQSN_2/DDR0_DQSN_1

DDRA_DQSP_2/DDR0_DQSP_2/DDR0_DQSP_1

DDRA_DQSN_3/DDR0_DQSN_3/DDR1_DQSN_1

DDRA_DQSP_3/DDR0_DQSP_3/DDR1_DQSP_1

DDRB_DQSN_0/DDR0_DQSN_4/DDR0_DQSN_2

DDRB_DQSP_0/DDR0_DQSP_4/DDR0_DQSP_2

DDRB_DQSN_1/DDR0_DQSN_5/DDR1_DQSN_2

DDRB_DQSP_1/DDR0_DQSP_5/DDR1_DQSP_2

DDRB_DQSN_2/DDR0_DQSN_6/DDR0_DQSN_3

DDRB_DQSP_2/DDR0_DQSP_6/DDR0_DQSP_3

DDRB_DQSN_3/DDR0_DQSN_7/DDR1_DQSN_3

DDRB_DQSP_3/DDR0_DQSP_7/DDR1_DQSP_3

DDRA_CS_1/NC

DDRB_CS_0/NC

DDRB_CA4/DDR0_BA0

NC/DDR0_BA1

DDRA_CA5/DDR0_BG0

NC/DDR0_BG1

NC/DDR0_MA0

NC/DDR0_MA1

DDRB_CA5/DDR0_MA2

NC/DDR0_MA3

NC/DDR0_MA4

DDRA_CA0/DDR0_MA5

DDRA_CA2/DDR0_MA6

DDRA_CA4/DDR0_MA7

DDRA_CA3/DDR0_MA8

DDRA_CA1/DDR0_MA9

NC/DDR0_MA10

NC/DDR0_MA11

NC/DDR0_MA12

DDRB_CA0/DDR0_MA13

DDRB_CA2/DDR0_MA14WE

NC/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_PAR

NC/DDR0_ACT

NC/DDR0_ALERT

RSVD_M38

DDR0_VREF_CA

DDR1_VREF_CA

DDR_VTT_CTL

DRAM_RESET

BL48

BL47

BF42

BF43

BG49

BJ47

BF38

BF41

BM38

BM42

BP42

BG42

BM43

BG39

BB49

BD47

BB48

BL49

BG38

BL45

BJ46

BG48

BE45

BG45

BG47

BE47

BJ38

BB47

BE48

BM39

BG43

BJ42

BM41

BJ39

BB45

BY47

BY46

CC41

CE41

BR47

BR46

BV41

BW41

AV46

AV47

AY41

BB41

AN46

AN47

AR41

AT41

BF39

BE49

BD46

M38

C44

B45

M39

DK47

M_A_LP4_CLK_N [16]

M_A_LP4_CLK_P [16]

M_B_LP4_CLK_N [16]

M_B_LP4_CLK_P [16]

M_A_LP4_CKE0 [16]

M_A_LP4_CKE1 [16]

M_B_LP4_CKE0 [16]

M_B_LP4_CKE1 [16]

M_A_LP4_CS#0 [16]

M_A_LP4_CS#1 [16]

M_B_LP4_CS#0 [16]

M_B_LP4_CS#1 [16]

M_B_CA4

M_A_CA5

M_B_CA5

M_A_CA0

M_A_CA2

M_A_CA4

M_A_CA3

M_A_CA1

M_A_CA5

M_B_CA0

M_B_CA2

M_B_CA1

M_B_CA3

M_B_CA4

M_B_CA5

DDR0_ALERT#

DDR_VTT_CTRL

M_A_CA[5:0] [16]

M_B_CA[5:0] [16]

M_A_DQS_0_DN [16]

M_A_DQS_0_DP [16]

M_A_DQS_1_DN [16]

M_A_DQS_1_DP [16]

M_A_DQS_2_DN [16]

M_A_DQS_2_DP [16]

M_A_DQS_3_DN [16]

M_A_DQS_3_DP [16]

M_B_DQS_0_DN [16]

M_B_DQS_0_DP [16]

M_B_DQS_1_DN [16]

M_B_DQS_1_DP [16]

M_B_DQS_2_DN [16]

M_B_DQS_2_DP [16]

M_B_DQS_3_DN [16]

M_B_DQS_3_DP [16]

R1135 0

0201S_P28-W35

+1P1V_DDR_VDD2

M_C_1_DQ_[7:0][17]

M_C_2_DQ_[7:0][17]

M_C_3_DQ_[7:0][17]

M_D_1_DQ_[7:0][17]

DNP

R1117

10K

0201S_P28-W35

M_C_0_DQ_[7:0][17]

M_D_0_DQ_[7:0][17]

M_D_2_DQ_[7:0][17]

M_D_3_DQ_[7:0][17]

M_C_0_DQ_0

M_C_0_DQ_1

M_C_0_DQ_2

M_C_0_DQ_3

M_C_0_DQ_4

M_C_0_DQ_5

M_C_0_DQ_6

M_C_0_DQ_7

M_C_1_DQ_0

M_C_1_DQ_1

M_C_1_DQ_2

M_C_1_DQ_3

M_C_1_DQ_4

M_C_1_DQ_5

M_C_1_DQ_6

M_C_1_DQ_7

M_C_2_DQ_0

M_C_2_DQ_1

M_C_2_DQ_2

M_C_2_DQ_3

M_C_2_DQ_4

M_C_2_DQ_5

M_C_2_DQ_6

M_C_2_DQ_7

M_C_3_DQ_0

M_C_3_DQ_1

M_C_3_DQ_2

M_C_3_DQ_3

M_C_3_DQ_4

M_C_3_DQ_5

M_C_3_DQ_6

M_C_3_DQ_7

M_D_0_DQ_0

M_D_0_DQ_1

M_D_0_DQ_2

M_D_0_DQ_3

M_D_0_DQ_4

M_D_0_DQ_5

M_D_0_DQ_6

M_D_0_DQ_7

M_D_1_DQ_0

M_D_1_DQ_1

M_D_1_DQ_2

M_D_1_DQ_3

M_D_1_DQ_4

M_D_1_DQ_5

M_D_1_DQ_6

M_D_1_DQ_7

M_D_2_DQ_0

M_D_2_DQ_1

M_D_2_DQ_2

M_D_2_DQ_3

M_D_2_DQ_4

M_D_2_DQ_5

M_D_2_DQ_6

M_D_2_DQ_7

M_D_3_DQ_0

M_D_3_DQ_1

M_D_3_DQ_2

M_D_3_DQ_3

M_D_3_DQ_4

M_D_3_DQ_5

M_D_3_DQ_6

M_D_3_DQ_7

U1001C

AK48

DDRC_DQ0_0/DDR1_DQ0_0/DDR0_DQ4_0

AK45

DDRC_DQ0_1/DDR1_DQ0_1/DDR0_DQ4_1

AK49

DDRC_DQ0_2/DDR1_DQ0_2/DDR0_DQ4_2

AG47

DDRC_DQ0_3/DDR1_DQ0_3/DDR0_DQ4_3

AK47

DDRC_DQ0_4/DDR1_DQ0_4/DDR0_DQ4_4

AG45

DDRC_DQ0_5/DDR1_DQ0_5/DDR0_DQ4_5

AG48

DDRC_DQ0_6/DDR1_DQ0_6/DDR0_DQ4_6

AG49

DDRC_DQ0_7/DDR1_DQ0_7/DDR0_DQ4_7

AJ38

DDRC_DQ1_0/DDR1_DQ1_0/DDR1_DQ4_0

AL39

DDRC_DQ1_1/DDR1_DQ1_1/DDR1_DQ4_1

AJ39

DDRC_DQ1_2/DDR1_DQ1_2/DDR1_DQ4_2

AL43

DDRC_DQ1_3/DDR1_DQ1_3/DDR1_DQ4_3

AL38

DDRC_DQ1_4/DDR1_DQ1_4/DDR1_DQ4_4

AJ42

DDRC_DQ1_5/DDR1_DQ1_5/DDR1_DQ4_5

AL42

DDRC_DQ1_6/DDR1_DQ1_6/DDR1_DQ4_6

AJ43

DDRC_DQ1_7/DDR1_DQ1_7/DDR1_DQ4_7

AB49

DDRC_DQ2_0/DDR1_DQ2_0/DDR0_DQ5_0

AB48

DDRC_DQ2_1/DDR1_DQ2_1/DDR0_DQ5_1

AE49

DDRC_DQ2_2/DDR1_DQ2_2/DDR0_DQ5_2

AE47

DDRC_DQ2_3/DDR1_DQ2_3/DDR0_DQ5_3

AE48

DDRC_DQ2_4/DDR1_DQ2_4/DDR0_DQ5_4

AB47

DDRC_DQ2_5/DDR1_DQ2_5/DDR0_DQ5_5

AB45

DDRC_DQ2_6/DDR1_DQ2_6/DDR0_DQ5_6

AE45

DDRC_DQ2_7/DDR1_DQ2_7/DDR0_DQ5_7

AD38

DDRC_DQ3_0/DDR1_DQ3_0/DDR1_DQ5_0

AD39

DDRC_DQ3_1/DDR1_DQ3_1/DDR1_DQ5_1

AE39

DDRC_DQ3_2/DDR1_DQ3_2/DDR1_DQ5_2

AE43

DDRC_DQ3_3/DDR1_DQ3_3/DDR1_DQ5_3

AE38

DDRC_DQ3_4/DDR1_DQ3_4/DDR1_DQ5_4

AD43

DDRC_DQ3_5/DDR1_DQ3_5/DDR1_DQ5_5

AD42

DDRC_DQ3_6/DDR1_DQ3_6/DDR1_DQ5_6

AE42

DDRC_DQ3_7/DDR1_DQ3_7/DDR1_DQ5_7

J48

DDRD_DQ0_0/DDR1_DQ4_0/DDR0_DQ6_0

J45

DDRD_DQ0_1/DDR1_DQ4_1/DDR0_DQ6_1

J49

DDRD_DQ0_2/DDR1_DQ4_2/DDR0_DQ6_2

G47

DDRD_DQ0_3/DDR1_DQ4_3/DDR0_DQ6_3

J47

DDRD_DQ0_4/DDR1_DQ4_4/DDR0_DQ6_4

G45

DDRD_DQ0_5/DDR1_DQ4_5/DDR0_DQ6_5

G48

DDRD_DQ0_6/DDR1_DQ4_6/DDR0_DQ6_6

E48

DDRD_DQ0_7/DDR1_DQ4_7/DDR0_DQ6_7

J38

DDRD_DQ1_0/DDR1_DQ5_0/DDR1_DQ6_0

G39

DDRD_DQ1_1/DDR1_DQ5_1/DDR1_DQ6_1

G38

DDRD_DQ1_2/DDR1_DQ5_2/DDR1_DQ6_2

G42

DDRD_DQ1_3/DDR1_DQ5_3/DDR1_DQ6_3

J39

DDRD_DQ1_4/DDR1_DQ5_4/DDR1_DQ6_4

J42

DDRD_DQ1_5/DDR1_DQ5_5/DDR1_DQ6_5

G43

DDRD_DQ1_6/DDR1_DQ5_6/DDR1_DQ6_6

J43

DDRD_DQ1_7/DDR1_DQ5_7/DDR1_DQ6_7

B43

DDRD_DQ2_0/DDR1_DQ6_0/DDR0_DQ7_0

D43

DDRD_DQ2_1/DDR1_DQ6_1/DDR0_DQ7_1

A43

DDRD_DQ2_2/DDR1_DQ6_2/DDR0_DQ7_2

C40

DDRD_DQ2_3/DDR1_DQ6_3/DDR0_DQ7_3

C43

DDRD_DQ2_4/DDR1_DQ6_4/DDR0_DQ7_4

D40

DDRD_DQ2_5/DDR1_DQ6_5/DDR0_DQ7_5

B40

DDRD_DQ2_6/DDR1_DQ6_6/DDR0_DQ7_6

A40

DDRD_DQ2_7/DDR1_DQ6_7/DDR0_DQ7_7

B35

DDRD_DQ3_0/DDR1_DQ7_0/DDR1_DQ7_0

D35

DDRD_DQ3_1/DDR1_DQ7_1/DDR1_DQ7_1

A35

DDRD_DQ3_2/DDR1_DQ7_2/DDR1_DQ7_2

D38

DDRD_DQ3_3/DDR1_DQ7_3/DDR1_DQ7_3

C35

DDRD_DQ3_4/DDR1_DQ7_4/DDR1_DQ7_4

C38

DDRD_DQ3_5/DDR1_DQ7_5/DDR1_DQ7_5

B38

DDRD_DQ3_6/DDR1_DQ7_6/DDR1_DQ7_6

A38

DDRD_DQ3_7/DDR1_DQ7_7/DDR1_DQ7_7

M1042225-001

3 OF 19

DDRC_CLK_N/DDR1_CLK_N_0

DDRC_CLK_P/DDR1_CLK_P_0

DDRD_CLK_N/DDR1_CLK_N_1

DDRD_CLK_P/DDR1_CLK_P_1

DDRC_CKE0/DDR1_CKE0

DDRC_CKE1/NC

DDRD_CKE0/NC

DDRD_CKE1/DDR1_CKE1

DDRC_CS_0/DDR1_CS_N_0

DDRC_CS_1/NC

DDRD_CS_0/NC

DDRD_CS_1/DDR1_CS_N_1

DDRD_CA4/DDR1_BA0

DDRC_CA5/DDR1_BG0

DDRD_CA5/DDR1_MA2

DDRC_CA0/DDR1_MA5

DDRC_CA2/DDR1_MA6

DDRC_CA4/DDR1_MA7

DDRC_CA3/DDR1_MA8

DDRC_CA1/DDR1_MA9

NC/DDR1_MA10

NC/DDR1_MA11

NC/DDR1_MA12

DDRD_CA0/DDR1_MA13

DDRD_CA2/DDR1_MA14WE

DDRD_CA1/DDR1_MA15CAS

DDRD_CA3/DDR1_MA16RAS

NC/DDR1_ODT_0

NC/DDR1_ODT_1

DDRC_DQSN_0/DDR1_DQSN_0/DDR0_DQSN_4

DDRC_DQSP_0/DDR1_DQSP_0/DDR0_DQSP_4

DDRC_DQSN_1/DDR1_DQSN_1/DDR1_DQSN_4

DDRC_DQSP_1/DDR1_DQSP_1/DDR1_DQSP_4

DDRC_DQSN_2/DDR1_DQSN_2/DDR0_DQSN_5

DDRC_DQSP_2/DDR1_DQSP_2/DDR0_DQSP_5

DDRC_DQSN_3/DDR1_DQSN_3/DDR1_DQSN_5

DDRC_DQSP_3/DDR1_DQSP_3/DDR1_DQSP_5

DDRD_DQSN_0/DDR1_DQSN_4/DDR0_DQSN_6

DDRD_DQSP_0/DDR1_DQSP_4/DDR0_DQSP_6

DDRD_DQSN_1/DDR1_DQSN_5/DDR1_DQSN_6

DDRD_DQSP_1/DDR1_DQSP_5/DDR1_DQSP_6

DDRD_DQSN_2/DDR1_DQSN_6/DDR0_DQSN_7

DDRD_DQSP_2/DDR1_DQSP_6/DDR0_DQSP_7

DDRD_DQSN_3/DDR1_DQSN_7/DDR1_DQSN_7

DDRD_DQSP_3/DDR1_DQSP_7/DDR1_DQSP_7

NC/DDR1_ALERT

NC/DDR1_BA1

NC/DDR1_BG1

NC/DDR1_MA0

NC/DDR1_MA1

NC/DDR1_MA3

NC/DDR1_MA4

NC/DDR1_PAR

NC/DDR1_ACT

Y48

Y47

M43

M42

U45

V46

M41

P43

V42

V39

Y39

T39

T38

T42

R45

N47

P42

Y49

U48

Y45

U47

R49

U49

M47

M45

R47

P39

N46

R48

Y41

V41

Y42

V47

V43

V38

AH46

AH47

AJ41

AL41

AC47

AC46

AE41

AD41

H47

H46

G41

J41

C42

D42

D36

C36

P38

M48

M49

M_C_LP4_CLK_N [17]

M_C_LP4_CLK_P [17]

M_D_LP4_CLK_N [17]

M_D_LP4_CLK_P [17]

M_C_LP4_CKE0 [17]

M_C_LP4_CKE1 [17]

M_D_LP4_CKE0 [17]

M_D_LP4_CKE1 [17]

M_C_LP4_CS#0 [17]

M_C_LP4_CS#1 [17]

M_D_LP4_CS#0 [17]

M_D_LP4_CS#1 [17]

M_D_CA4

M_C_CA5

M_D_CA5

M_C_CA0

M_C_CA2

M_C_CA4

M_C_CA3

M_C_CA1

M_C_CA5

M_D_CA0

M_D_CA2

M_D_CA1

M_D_CA3

M_D_CA4

M_D_CA5

DDR1_ALERT#

M_C_DQS_0_DN [ 17]

M_C_DQS_0_DP [17]

M_C_DQS_1_DN [ 17]

M_C_DQS_1_DP [17]

M_C_DQS_2_DN [ 17]

M_C_DQS_2_DP [17]

M_C_DQS_3_DN [ 17]

M_C_DQS_3_DP [17]

M_D_DQS_0_DN [ 17]

M_D_DQS_0_DP [17]

M_D_DQS_1_DN [ 17]

M_D_DQS_1_DP [17]

M_D_DQS_2_DN [ 17]

M_D_DQS_2_DP [17]

M_D_DQS_3_DN [ 17]

M_D_DQS_3_DP [17]

R1136 0

0201S_P28-W35

M_C_CA[5:0] [17]

M_D_CA[5:0] [17]

R1103

R1105

100

5

R1102

100

470

DRAM_RESET_N_R

4

R1101

0

3

DRAM_RESET# [16,17]

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

W x H 512 x 331 mm

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

CPU(2)_LPDDR4

CPU(2)_LPDDR4

CPU(2)_LPDDR4

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

1

1.00

1.00

11 82Tuesday, May 21, 2019

11 82Tuesday, May 21, 2019

11 82Tuesday, May 21, 2019

1.00

100 R1104

Use Seperated Via To GND

A A

Page 12

5

4

3

2

1

+VCCSTG_OUT

D D

+VCCSTG +VCCST_CPU

C C

C1204

1u

6.3V

0201S_P35-W35

+VCCSTG_TERM

+VCCSTG_OUT

R1201

0

5%

1/10W

0603S_P6-W95

+VCCSTG_OUT_LGC

+1P1V_DDR_VDD2

AA37

AG36

AJ36

AL36

AL49

AN36

AP37

AR36

AR37

AT36

AT49

AA49

AV36

AW37

AY36

BA37

BA49

BB36

BD36

BE37

BF36

BF37

AB36

BF49

BG36

BJ36

BL37

BM49

BN37

BP38

CB1

BY1

F33

G33

E5

U1001M

M1042225-001

VDDQ_1

13 OF 19

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_24

VDDQ_25

VDDQ_26

VDDQ_27

VDDQ_28

VDDQ_29

VDDQ_30

VCCST

VCCSTG

VCCSTG_OUT_F33

VCCSTG_OUT_G33

VCCSTG_OUT_LGC

VCCSTG_OUT_R35

VCCSTG_OUT_V34

VCCSTG_OUT_T34

VCCSTG_OUT_U35

VCCSTG_OUT_AB34

VDDQ_31

VDDQ_32

VDDQ_33

VDDQ_34

VDDQ_35

VDDQ_36

VDDQ_37

VDDQ_38

VDDQ_39

VDDQ_40

VDDQ_41

VDDQ_42

VDDQ_43

VDDQ_44

VDDQ_45

VDDQ_46

VDDQ_47

RSVD_2

RSVD_3

VCC1P8A_1

VCC1P8A_2

VCC1P8A_3

VCC1P8A_4

VCC1P8A_5

RSVD_W35

RSVD_AA35

RSVD_Y34

VCCPLL

VCCPLL_OC_1

VCCPLL_OC_2

VCCPLL_OC_3

VCCPLL_OC_4

VCCIO_OUT

+1P1V_DDR_VDD2

BP39

BR37

BT38

AC35

BU37

BU49

CA39

CB49

L38

L49

N36

T49

AC37

AD35

AD36

AE36

AF49

VCCIN_AUX0_R

A33

VCCIN_AUX1_R

B33

BG9

BJ9

BM9

BW1

BW2

R35

V34

T34

U35

AB34

W35

AA35

Y34

CD2

CG38

CG41

CG42

CG49

AD7

TP1201 SP_TP_SMDP58

TP1202 SP_TP_SMDP58

+VCC1P8A

+VCCSTG_OUT

+VCC1.05_OUT_SFR

+VCCPLL_OC

VCCIO_OUT [18]

B B

TOP SIDE BOTTOM SIDE TOP SIDE SOCKET

+1P1V_DDR_VDD2

C1211

22u

0603

20%

10V

+VCCSTG

A A

C1203

1u

0201S_P35-W35

6.3V

DNP

Place close to U1001M Place close to U1001M

C1220

22u

0603

20%

10V

C1247

1u

0201S_P35-W35

6.3V

5

C1228

22u

0603

20%

10V

DNP

+VCCST_CPU

C1205

1u

0201S_P35-W35

6.3V

DNP

+1P1V_DDR_VDD2

C1222

1u

6.3V

20%

0201

C1218

1u

6.3V

20%

0201

C1202

1u

6.3V C1252

0201S_P35-W35

C1206

1u

6.3V

20%

0201

C1238

1u

6.3V

20%

0201

C1233

1u

6.3V

20%

0201

C1207

1u

6.3V

20%

0201

C1250

1u

0201S_P35-W35

6.3V

DNP

4

C1221

1u

6.3V

20%

0201

C1208

1u

6.3V

20%

0201

C1249

1u

0201S_P35-W35

6.3V

+1P1V_DDR_VDD2 +1P1V_DDR_VDD2

C1253

1u

0201S_P35-W35

6.3V

C1214

10u

20%

6.3V

0402

C1254

1u

0201S_P35-W35

6.3V

DNP

C1224

10u

20%

6.3V

0402

1u

0201S_P35-W35

6.3V

3

C1251

1u

0201S_P35-W35

6.3V

DNP

DNP

C1213

10u

20%

6.3V

0402

C1225

10u

20%

6.3V

0402

DNP

+VCC1P8A+VCC1.05_OUT_FET+VCCPLL_OC+VCCSTG_OUT

C1248

10u

6.3V

0402S_P7-W70

Place close to U1001MPlace close to U1001MPlace close to U1001MPlace close to U1001M

DNP

C1215

10u

20%

6.3V

0402

C1201

22u

0603S_1-W100

20%

10V

DNP

2

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

W x H 437 x 328 mm

Date: Sheet of

Date: Sheet of

Date: Sheet of

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

CPU(3)_ICL_POWER1

CPU(3)_ICL_POWER1

CPU(3)_ICL_POWER1

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

12 82Tuesday, May 21, 2019

12 82Tuesday, May 21, 2019

1

12 82Tuesday, May 21, 2019

1.00

1.00

1.00

Page 13

5

4

3

2

1

+VCCIN

D D

TODO: Update rail

C C

SVID_ALERT#[66]

VIDSCLK[66]

VIDSOUT[66]

+VCCST_CPU

0201S_P28-W35

0201S_P28-W35

R1303 56

R1304 100

TP1303SP_TP_SMDP58

R130200201S_P28-W35

R130500201S_P28-W35

R130100201S_P28-W35

H_CPU_SVIDALERT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

A19

AC12

V13

W12

Y13

K29

K31

B19

B23

B27

B29

BN10

BP11

BP9

BR10

BT11

A21

BT9

BU10

BV36

BV9

BW10

BW36

BW9

BY10

C19

C23

A23

C27

C29

CA36

CA9

CB10

CC11

CC36

CC9

CD10

CE11

A24

CE34

CE35

CF10

CF33

CG11

CG34

CG35

CH10

J30

CJ11

A27

CJ34

U1001L

VCCIN_1

VCCIN_2

VCCIN_3

VCCIN_4

VCCIN_5

VCCIN_6

VCCIN_7

VCCIN_8

VCCIN_9

VCCIN_10

VCCIN_11

VCCIN_12

VCCIN_13

VCCIN_14

VCCIN_15

VCCIN_16

VCCIN_17

VCCIN_18

VCCIN_19

VCCIN_20

VCCIN_21

VCCIN_22

VCCIN_23

VCCIN_24

VCCIN_25

VCCIN_26

VCCIN_27

VCCIN_28

VCCIN_29

VCCIN_30

VCCIN_31

VCCIN_32

VCCIN_33

VCCIN_34

VCCIN_35

VCCIN_36

VCCIN_37

VCCIN_38

VCCIN_39

VCCIN_40

VCCIN_41

VCCIN_42

VCCIN_43

VCCIN_44

VCCIN_45

VCCIN_46

VCCIN_47

VCCIN_48

VCCIN_49

VCCIN_50

VCCIN_51

H1

VIDALERT

H2

VIDSCK

H3

VIDSOUT

M1042225-001

12 OF 19

VCCIN_100

VCCIN_101

VCCIN_102

VCCIN_103

VCCIN_104

VCCIN_SENSE

VSSIN_SENSE

VCCIN_52

VCCIN_53

VCCIN_54

VCCIN_55

VCCIN_56

VCCIN_57

VCCIN_58

VCCIN_59

VCCIN_60

VCCIN_61

VCCIN_62

VCCIN_63

VCCIN_64

VCCIN_65

VCCIN_66

VCCIN_67

VCCIN_68

VCCIN_69

VCCIN_70

VCCIN_71

VCCIN_72

VCCIN_73

VCCIN_74

VCCIN_75

VCCIN_76

VCCIN_77

VCCIN_78

VCCIN_79

VCCIN_80

VCCIN_81

VCCIN_82

VCCIN_83

VCCIN_84

VCCIN_85

VCCIN_86

VCCIN_87

VCCIN_88

VCCIN_89

VCCIN_90

VCCIN_91

VCCIN_92

VCCIN_93

VCCIN_94

VCCIN_95

VCCIN_96

VCCIN_97

VCCIN_98

VCCIN_99

CJ35

CK10

J32

CL34

CL35

CN34

CN35

CP33

CR34

A29

CR35

CT33

CT34

CT35

CU33

D19

D21

D23

D24

D27

AA12

D29

F19

F21

F23

F24

F27

F29

G1

G19

G23

AB1

G27

G29

H19

H23

H27

H29

J18

J20

J22

J23

AB13

J26

J28

K17

K19

K21

K23

K24

K27

M1

U1

F17

G17

+VCCIN

VCCIN_VIN_SENSE [66]

VCCIN_VSS_SENSE [66]

BACKSIDE CAP

+VCCIN

C1322

1u

6.3V

20%

0201

PRIMARY SIDE

+VCCIN

C1320

22u

0603

20%

10V

C1313

22u

0603

20%

10V

C1316

22u

0603

20%

10V

C1301

1u

6.3V

20%

0201

C1311

22u

0603

20%

10V

C1323

22u

0603

20%

10V

C1309

22u

0603

20%

10V

C1325

1u

6.3V

20%

0201

C1310

1u

6.3V

20%

0201

C1321

22u

0603

20%

10V

C1326

22u

0603

20%

10V

Place close as possible to A29

C1318

22u

0603

20%

10V

C1307

22u

0603

20%

10V

C1324

22u

0603

20%

10V

C1303

22u

0603

20%

10V

C1314

22u

0603

20%

10V

C1327

22u

0603

20%

DNP

10V

C1364

22u

0603

20%

10V

3

DNP

B B

A A

5

4

C1360

22u

0603

20%

10V

C1306

22u

0603

20%

10V

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

W x H 512 x 331 mm

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

CPU(4)_ICL_POWER2

CPU(4)_ICL_POWER2

CPU(4)_ICL_POWER2

Title:

Title:

Title:

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

Engineer:

1

1.00

1.00

13 82Tuesday, May 21, 2019

13 82Tuesday, May 21, 2019

13 82Tuesday, May 21, 2019

1.00

Page 14

5

4

3

2

1

BT3

BT39

BT41

BT42

BT43

BT7

BU45

BU47

BV1

BV11

BV2

BV3

BV7

BW3

BW37

BW5

BW6

BW7

BY37

BY45

BY49

C11

C13

C14

C17

C21

C24

C31

C34

C39

C48

C49

C6

CA3

CA38

CA41

CA42

CA43

CA7

CB37

CB45

CB47

CC3

CC7

CE37

CE45

CE49

CE9

CG37

CG39

CG43

CG45

CG47

CG9

CH3

CH5

CJ37

CJ42

CJ9

CK45

CK49

CK9

CL37

CL42

CL49

CM45

CM47

CM9

CN3

CN37

CN39

CN5

CP9

CR32

U1001P

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

M1042225-001

16 OF 19

3

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

CR37

CR45

CR49

CT37

CT39

CT42

CT9

CU45

CU47

CU49

CV3

CV34

CV35

CV5

CV9

CY41

CY45

CY49

CY9

D13

D17

D31

D44

D49

DA10

DA33

DA9

DB32

DB35

DB38

DB45

DB47

DB49

DC3

DC49

DC5

DC6

DD37

DD42

DE10

DE13

DE17

DE18

DE20

DE22

DE23

DE26

DE28

DE29

DE33

DE45

DE6

DF13

DF22

DF28

DF33

DF35

DF39

DG10

DG12

DG13

DG15

DG22

DG23

DG47

DG6

DH1

DH3

DH45

DH5

DJ19

DJ21

DJ27

DJ31

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

W x H 347 x 225 mm

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

U1001O

A11

VSS_1

A46

BB3

BB7

BD3

A48

BD5

BD6

BD7

BE1

BE2

BF3

A49

BF45

BF47

BF7

BG3

BG7

BJ1

BJ2

BJ3

BJ41

BJ43

BJ45

BJ49

BJ7

BM3

BM5

BM6

BM7

BP1

BP2

BP3

BP7

AB3

A17

AB5

AB6

A3

AE6

AF37

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

M1042225-001

BA45

BA47

BB11

D D

BC37

BD38

BD39

BD41

BD42

BD43

BD45

BD49

C C

B B

A A

BG41

BH37

AA45

BM11

BM45

BM47

AA47

BP43

BR45

BR49

AB11

AB38

AB39

AB41

AB42

AB43

AC45

AC49

AD10

AD11

AD34

AD37

15 OF 19

5

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

AF45

AF47

AG1

AG11

AG3

AG38

AG39

AG41

A31

AG42

AG43

AG5

AG9

AH2

AH37

AH45

AH49

AJ2

AJ3

A34

AK37

AL2

AL45

AL47

AL6

AM2

AM37

AN2

AN38

AN39

A36

AN41

AN42

AN43

AN45

AN49

AN6

AR1

AR11

AR2

AR3

A39

AR7

AR9

AT3

AT45

AT47

AT5

AT6

AT7

AU37

AV11

A42

AV3

AV38

AV39

AV41

AV42

AV43

AV45

AV49

AV7

AY3

A44

AY7

B17

B2

B21

B24

B3

B31

B48

BA1

BA2

4

U1001Q

DJ33

VSS_297

DJ36

VSS_298

DJ42

VSS_299

DK3

VSS_300

DK4

DK49

DL10

DL13

DL44

DL47

DM47

DN15

DN19

DN24

DN31

DN36

DN42

DP45

DR49

DT10

DT15

DT20

DT27

DT32

DT37

DT42

DT49

DU10

DU15

DU20

DU27

DU32

DU37

DU48

DU49

DV44

DV48

DW10

DW20

DW27

DW44

DW46

DW48

DW49

VSS_301

VSS_302

DK6

VSS_303

DK8

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

DT1

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

DT3

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

DT6

VSS_328

DT7

VSS_329

DT8

VSS_330

DU1

VSS_331

VSS_332

VSS_333

DU2

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

DU7

VSS_341

DV2

VSS_342

VSS_343

VSS_344

DV8

VSS_345

DW1

VSS_346

VSS_347

DW2

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

DW7

VSS_355

E11

VSS_356

E34

VSS_357

E36

VSS_358

E39

VSS_359

E42

VSS_360

E6

VSS_361

M1042225-001

<OrgName>

<OrgName>

<OrgName>

Custom

Custom

Custom

17 OF 19

VSS_362

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

VSS_396

VSS_397

VSS_398

VSS_399

VSS_400

VSS_401

VSS_402

VSS_403

VSS_404

VSS_405

VSS_406

VSS_407

VSS_408

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

F11

F31

F45

F47

F8

G21

G24

G3

G31

G36

G49

G5

H17

H21

H24

H31

H33

H36

H45

H49

J10

J13

J16

J36

J6

K11

K33

K8

L36

L39

L41

L42

L43

L45

L47

M10

M3

M36

M5

N45

N49

P11

P41

P8

R3

R37

T11

T36

T41

T43

T45

T47

U3

U37

U5

V11

V36

V45

V49

V9

W37

Y36

Y38

Y43

Y9

DE15

CPU(5)_GND

CPU(5)_GND

CPU(5)_GND

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

14 82Tuesday, May 21, 2019

14 82Tuesday, May 21, 2019

14 82Tuesday, May 21, 2019

1

1.00

1.00

1.00

Page 15

5

4

3

2

1

CFG4

0

Default

1

D D

C C

B B

enable eDP

Disable eDP

TP1519

TP1520

TP1521

R1507 49.9

0201S_P28-W35

TP1528

TP1529

TP1518SP_TP_SMDP58

TP1514SP_TP_SMDP58

Place outside of thermal module

TP1516

U1001S

CFG0[18]

CFG1[18]

CFG2[18]

CFG3[18]

CFG4[18]

CFG5[18]

CFG6[18]

CFG7[18]

CFG16

CFG17[18]

CFG18

CFG_RCOMP

BPM_N_2

BPM_N_3

CFG8

CFG9

CFG10

BPM_N_0

BPM_N_1

AG6

AE7

AG7

AD9

AE9

AB9

AJ6

AB7

V10

AJ5

Y10

AJ7

AB10

AL7

AL9

AJ9

V6

V7

Y6

Y7

AD6

T9

T7

T10

T6

BJ11

BL10

AV1

AT2

AT1

AU1

AU2

AV2

DP3

DT2

AR10

AP10

BP36

BM36

J15

K15

C5

D4

A5

R1502

0

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_RCOMP

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

RSVD_68

RSVD_69

RSVD_TP_AV1

RSVD_TP_AT2

RSVD_TP_AT1

RSVD_TP_AU1

RSVD_TP_AU2

RSVD_TP_AV2

RSVD_83

RSVD_84

RSVD_85

RSVD_87

RSVD_86

RSVD_88

VSS_430

VSS_431

SKTOCC

RSVD_D4

RSVD_70

M1042225-001

19 OF 19

RSVD_TP_1

RSVD_TP_2

RSVD_60

RSVD_61

RSVD_TP_CT32

RSVD_TP_CV32

RSVD_G15

RSVD_F15

RSVD_TP_BW11

RSVD_TP_CA11

VSS_428

VSS_429

RSVD_58

RSVD_59

RSVD_71

RSVD_72

RSVD_65

RSVD_66

RSVD_TP_DV6

RSVD_TP_DW6

RSVD_TP_DP2

RSVD_TP_DP1

RSVD_TP_DW4

RSVD_TP_DV4

RSVD_TP_R1

RSVD_TP_DW3

RSVD_TP_DV3

RSVD_TP_DH49

RSVD_TP_DL8

VSS_432

RSVD_TP_P10

TP_3

TP_4

TP_1

TP_2

A47

B47

C1

E1

CT32

CV32

G15

F15

BW11

CA11

C16

A16

C2

A4

DP5

DR5

D14

E16

DV6

DW6

DP2

DP1

DW4

DV4

CM33

DB10

R1

DW3

DV3

DH49

DL8

DW47

DV47

DU47

P10

TP1501

FIVR_VLOAD_TCSS

CFG4

N34

AK10

BT36

AH10

BC10

CH33

CJ32

AM10

BH10

J34

Y11

L34

AJ11

CG32

CK33

BP41

AL11

BG11

AN11

M13

M34

DU42

DW42

D33

L13

K13

U1001R

RSVD_TP_N34

RSVD_TP_AK10

RSVD_7

RSVD_TP_AH10

RSVD_TP_BC10

RSVD_TP_CH33

RSVD_12

RSVD_TP_AM10

RSVD_TP_BH10

RSVD_TP_J34

RSVD_9

RSVD_10

RSVD_17

RSVD_21

RSVD_22

RSVD_20

RSVD_23

RSVD_24

RSVD_16

RSVD_18

RSVD_19

RSVD_42

RSVD_43

RSVD_44

RSVD_45

RSVD_47

M1042225-001

R1501

1K

0201S_P28-W35

18 OF 19

CFG16

CFG18

RSVD_TP_DA11

RSVD_TP_CL32

RSVD_TP_CN32

RSVD_32

RSVD_33

RSVD_34

IST_TP_0

IST_TP_1

IST_TRIG_0

IST_TRIG_1

PCH_IST_TP0

PCH_IST_TP1

RSVD_27

RSVD_28

VCCIN_AUX_OUT

RSVD_35

RSVD_46

RSVD_48

RSVD_49

RSVD_50

RSVD_51

RSVD_52

RSVD_53

RSVD_54

RSVD_36

RSVD_37

RSVD_38

RSVD_39

RSVD_40

RSVD_41

R1503 49.9

DA11

CL32

CN32

CY35

DB37

DF37

BF11

BD11

BE10

BF10

CW33

CY32

CY37

CV37

C33

G34

H34

DJ34

DK31

DK15

CP3

CP5

AN9

AN7

AF10

AE11

H5

D1

DJ40

DK40

R1504 49.9

A A

<OrgName>

<OrgName>

<OrgName>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

W x H 367 x 237 mm

EDAN_A_EV1

EDAN_A_EV1

EDAN_A_EV1

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

CPU(6)_CFG,RESERVED

CPU(6)_CFG,RESERVED

CPU(6)_CFG,RESERVED

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

15 82Tuesday, May 21, 2019

15 82Tuesday, May 21, 2019

15 82Tuesday, May 21, 2019

1

1.00

1.00

1.00

Page 16

5

4

3

2

1

M_A_2_DQ_[7:0][11]

M_A_3_DQ_[7:0][11]

D D

+0P6V_DDR_VDDQ

1%

1%

R1601 240

R1602 240

M_A_CA[5:0][11]

C C

B B

A A

+1P1V_DDR_VDD2

LPDDR4X ODT_CA is not used.

M_A_2_DQ_4

M_A_2_DQ_1

M_A_2_DQ_7

M_A_2_DQ_6

M_A_2_DQ_3

M_A_2_DQ_5

M_A_2_DQ_2 M_A_0_DQ_4

M_A_2_DQ_0

M_A_3_DQ_2

M_A_3_DQ_0

M_A_3_DQ_1

M_A_3_DQ_4

M_A_3_DQ_3

M_A_3_DQ_5

M_A_3_DQ_6

M_A_3_DQ_7

M_A_DQS_2_DP[11]

M_A_DQS_2_DN[11]

M_A_DQS_3_DP[11]

M_A_DQS_3_DN[11]

GND GND

ZQ0_1601

ZQ1_1601

M_A_LP4_CKE0[11]

M_A_LP4_CKE1[11]

M_A_LP4_CS#0[11]

M_A_LP4_CS#1[11]

M_A_LP4_CLK_P[11]

M_A_LP4_CLK_N[11]

M_A_CA0

M_A_CA1

M_A_CA2

M_A_CA3

M_A_CA4

M_A_CA5

R1606 0

+1P8V_DDR_VDD1

+1P1V_DDR_VDD2

+0P6V_DDR_VDDQ

GND

U1601

B2

DQ0_A

C2

DQ1_A

E2

DQ2_A

F2

DQ3_A

F4

DQ4_A

E4

DQ5_A

C4

DQ6_A

B4

DQ7_A

B11

DQ8_A

C11

DQ9_A

E11

DQ10_A

F11

DQ11_A

F9

DQ12_A

E9

DQ13_A

C9

DQ14_A

B9

DQ15_A

D3

DQS0_A_t

E3

DQS0_A_c

D10

DQS1_A_t

E10

DQS1_A_c

C3

DMI0_A

C10

DMI1_A

A5

ZQ0

A8

NC/ZQ1

J4

CKE0_A

J5

NC/CKE1_A

H4

CS0_A

H3

NC/CS1_A

J8

CK_A_t

J9

CK_A_c

H2

CA0_A

J2

CA1_A

H9

CA2_A

H10

CA3_A

H11

CA4_A

J11

CA5_A

G2

ODT_CA_A

A1

DNU_A1

A2

DNU_A2

A11

DNU_A11

A12

DNU_A12

B1

DNU_B1

B12

DNU_B12

G11

NC_G11

K5

NC_K5

K8

NC_K8

F1

VDD1_F1

F12

VDD1_F12

G4

VDD1_G4

G9

VDD1_G9

A4

VDD2_A4

A9

VDD2_A9

F5

VDD2_F5

F8

VDD2_F8

H1

VDD2_H1

H5

VDD2_H5

H8

VDD2_H8

H12

VDD2_H12

K1

VDD2_K1

K3

VDD2_K3

K10

VDD2_K10

K12

VDD2_K12

B3

VDDQ_B3

B5

VDDQ_B5

B8

VDDQ_B8

B10

VDDQ_B10

D1

VDDQ_D1

D5

VDDQ_D5

D8

VDDQ_D8

D12

VDDQ_D12

F3

VDDQ_F3

F10

VDDQ_F10

A10

VSS_A10

A3

VSS_A3

C1

VSS_C1

C12

VSS_C12

C5

VSS_C5

C8

VSS_C8

D11

VSS_D11

D2

VSS_D2

D4

VSS_D4

D9

VSS_D9

E1

VSS_E1

E12

VSS_E12

E5

VSS_E5

E8

VSS_E8

G12

VSS_G12

G1

VSS_G1

G10

VSS_G10

G3

VSS_G3

G5

VSS_G5

G8

VSS_G8

J1

VSS_J1

J10

VSS_J10

J12

VSS_J12

J3

VSS_J3

K11

VSS_K11

K2

VSS_K2

K4

VSS_K4

K9

VSS_K9

32GB

BGA200_15P1X10P1X1_P65XP8-2

TBL1601

DQS0_B_t

DQS0_B_c

DQS1_B_t

DQS1_B_c

RESET_n

CKE1_B/NC

CS1_B/NC

ODT_CA_B

DNU_AA1

DNU_AA12

DNU_AB1

DNU_AB2

DNU_AB11

DNU_AB12

VDD1_T4

VDD1_T9

VDD1_U1

VDD1_U12

VDD2_N1

VDD2_N3

VDD2_N10

VDD2_N12

VDD2_R1

VDD2_R5

VDD2_R8

VDD2_R12

VDD2_U5

VDD2_U8

VDD2_AB4

VDD2_AB9

VDDQ_U3

VDDQ_U10

VDDQ_W1

VDDQ_W5

VDDQ_W8

VDDQ_W12

VDDQ_AA3

VDDQ_AA5

VDDQ_AA8

VDDQ_AA10

VSS_N11

VSS_P10

VSS_P12

VSS_T10

VSS_T12

VSS_V12

VSS_W2

VSS_W4

VSS_W9

VSS_W11

VSS_Y12

VSS_AB10

VSS_AB3

VSS_AB5

VSS_AB8

DQ0_B

DQ1_B

DQ2_B

DQ3_B

DQ4_B

DQ5_B

DQ6_B

DQ7_B

DQ8_B

DQ9_B

DQ10_B

DQ11_B

DQ12_B

DQ13_B

DQ14_B

DQ15_B

DMI0_B

DMI1_B

CKE0_B

CS0_B

CK_B_t

CK_B_c

CA0_B

CA1_B

CA2_B

CA3_B

CA4_B

CA5_B

NC_N5

NC_N8

VSS_N2

VSS_N4

VSS_N9

VSS_P1

VSS_P3

VSS_T1

VSS_T3

VSS_T5

VSS_T8

VSS_V1

VSS_V5

VSS_V8

VSS_Y1

VSS_Y5

VSS_Y8

AA2

Y2

V2

U2

U4

V4

Y4

AA4

AA11

Y11

V11

U11

U9

V9

Y9

AA9

W3

V3

W10

V10

Y3

Y10

T11

P4

P5

R4

R3

P8

P9

R2

P2

R9

R10

R11

P11

T2

N5

N8

AA1

AA12

AB1

AB2

AB11

AB12

T4

T9

U1

U12

N1

N3

N10

N12

R1

R5

R8

R12

U5

U8

AB4

AB9

U3

U10

W1

W5

W8

W12

AA3

AA5

AA8

AA10

N2

N4

N9

N11

P1

P3

P10

P12

T1

T3

T5

T8

T10

T12

V1

V5

V8

V12

W2

W4

W9

W11

Y1

Y5

Y8

Y12

AB10

AB3

AB5

AB8

M_A_0_DQ_1

M_A_0_DQ_0

M_A_0_DQ_2

M_A_0_DQ_7

M_A_0_DQ_3

M_A_0_DQ_5

M_A_0_DQ_6

M_A_1_DQ_7

M_A_1_DQ_3

M_A_1_DQ_2

M_A_1_DQ_0

M_A_1_DQ_4

M_A_1_DQ_1

M_A_1_DQ_6

M_A_1_DQ_5

DRAM_RESET#

C1615 0.1u

10VDNP

M_A_LP4_CKE0

M_A_LP4_CKE1

M_A_LP4_CS#0

M_A_LP4_CS#1

M_A_LP4_CLK_P

M_A_LP4_CLK_N

M_A_CA0

M_A_CA1

M_A_CA2

M_A_CA3

M_A_CA4

M_A_CA5

R1605 0

+1P8V_DDR_VDD1

+1P1V_DDR_VDD2

+0P6V_DDR_VDDQ

GND

M_A_DQS_0_DP [11]

M_A_DQS_0_DN [11]

M_A_DQS_1_DP [11]

M_A_DQS_1_DN [11]

DRAM_RESET# [11,17]

GND

+1P1V_DDR_VDD2

M_A_0_DQ_[7:0] [11]

M_A_1_DQ_[7:0] [11]

M_B_2_DQ_[7:0][11]

M_B_3_DQ_[7:0][11]

+0P6V_DDR_VDDQ

1%

1%

R1603 240

R1604 240

M_B_CA[5:0][11]

+1P1V_DDR_VDD2 +1P1V_DDR_VDD2

M_B_2_DQ_4

M_B_2_DQ_1

M_B_2_DQ_6

M_B_2_DQ_5

M_B_2_DQ_7

M_B_2_DQ_3

M_B_2_DQ_2

M_B_2_DQ_0

M_B_3_DQ_2

M_B_3_DQ_6

M_B_3_DQ_5

M_B_3_DQ_4

M_B_3_DQ_3

M_B_3_DQ_1

M_B_3_DQ_0

M_B_3_DQ_7

M_B_DQS_2_DP[11]

M_B_DQS_2_DN[11]

M_B_DQS_3_DP[11]

M_B_DQS_3_DN[11]

GND

M_B_LP4_CKE0[11]

M_B_LP4_CKE1[11]

M_B_LP4_CS#0[11]

M_B_LP4_CS#1[11]

M_B_LP4_CLK_P[11]

M_B_LP4_CLK_N[11]

R1607 0

+1P8V_DDR_VDD1

+1P1V_DDR_VDD2

+0P6V_DDR_VDDQ

ZQ0_1602

ZQ1_1602

M_B_CA0

M_B_CA1

M_B_CA2

M_B_CA3

M_B_CA4

M_B_CA5

GND

U1602

B2

DQ0_A

C2

DQ1_A

E2

DQ2_A

F2

DQ3_A

F4

DQ4_A

E4

DQ5_A

C4

DQ6_A

B4

DQ7_A

B11

DQ8_A

C11

DQ9_A

E11

DQ10_A

F11

DQ11_A

F9

DQ12_A

E9

DQ13_A

C9

DQ14_A

B9

DQ15_A

D3

DQS0_A_t

E3

DQS0_A_c

D10

DQS1_A_t

E10

DQS1_A_c

C3

DMI0_A

C10

DMI1_A

A5

ZQ0

A8

NC/ZQ1

J4

CKE0_A

J5

NC/CKE1_A

H4

CS0_A

H3

NC/CS1_A

J8

CK_A_t

J9

CK_A_c

H2

CA0_A

J2

CA1_A

H9

CA2_A

H10

CA3_A

H11

CA4_A

J11

CA5_A

G2

ODT_CA_A

A1

DNU_A1

A2

DNU_A2

A11

DNU_A11

A12

DNU_A12

B1

DNU_B1

B12

DNU_B12

G11

NC_G11

K5

NC_K5

K8

NC_K8

F1

VDD1_F1

F12

VDD1_F12

G4

VDD1_G4

G9

VDD1_G9

A4

VDD2_A4

A9

VDD2_A9

F5

VDD2_F5

F8

VDD2_F8

H1

VDD2_H1

H5

VDD2_H5

H8

VDD2_H8

H12

VDD2_H12

K1

VDD2_K1

K3

VDD2_K3

K10

VDD2_K10

K12

VDD2_K12

B3

VDDQ_B3

B5

VDDQ_B5

B8

VDDQ_B8

B10

VDDQ_B10

D1

VDDQ_D1

D5

VDDQ_D5

D8

VDDQ_D8

D12

VDDQ_D12

F3

VDDQ_F3

F10

VDDQ_F10

A10

VSS_A10

A3

VSS_A3

C1

VSS_C1

C12

VSS_C12

C5

VSS_C5

C8

VSS_C8

D11

VSS_D11

D2

VSS_D2

D4

VSS_D4

D9

VSS_D9

E1

VSS_E1

E12

VSS_E12

E5

VSS_E5

E8

VSS_E8

G12

VSS_G12

G1

VSS_G1

G10

VSS_G10

G3

VSS_G3

G5

VSS_G5

G8

VSS_G8

J1

VSS_J1

J10

VSS_J10

J12

VSS_J12

J3

VSS_J3

K11

VSS_K11

K2

VSS_K2

K4

VSS_K4