MCP3201

2.7V 12-Bit A/D Converter with SPI® Serial Interface

FEATURES

• 12-bit resolution

• ±1 LSB max DNL

• ±1 LSB max INL (MCP3201-B)

• ±2 LSB max INL (MCP3201-C)

• On-chip sample and hold

®

• SPI

serial interface (modes 0,0 and 1,1)

• Single supply operation: 2.7V - 5.5V

• 100ksps max. sampling rate at VDD = 5V

• 50ksps max. sa mpling rate at V

= 2.7V

DD

• Low power CMOS technology

- 500nA typical standby current, 2µA max.

- 400µA max. active current at 5V

• Industrial temp range: -40°C to +85°C

• 8-pin PDIP, SOIC and TSSOP packages

APPLICATIONS

• Sensor Interface

• Process Control

• Data Acquisition

• Battery Operated Systems

DESCRIPTION

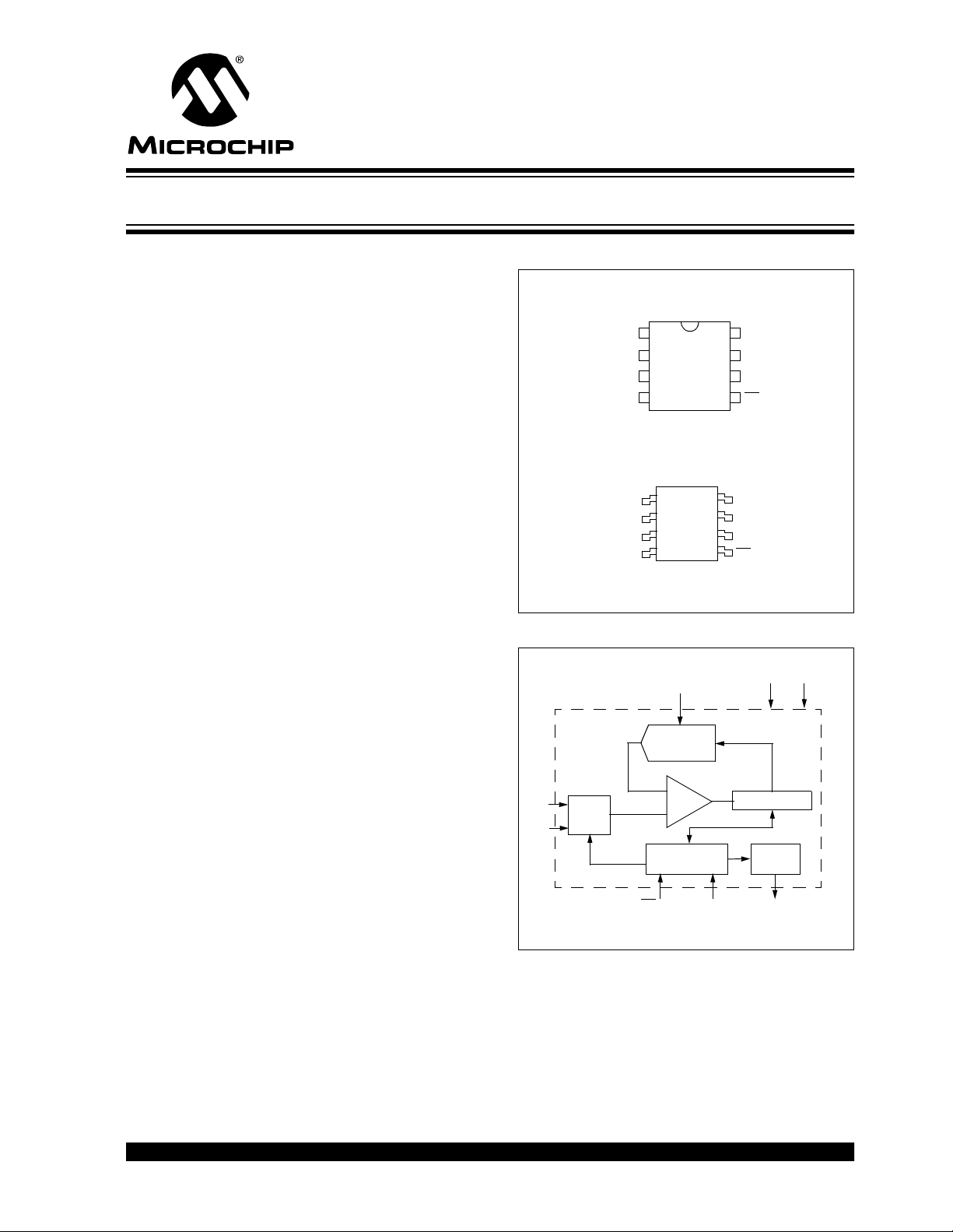

PAC K AGE TYPES

PDIP

SOIC, TSSOP

V

REF

IN+

IN–

V

V

SS

REF

IN+

IN–

V

SS

MCP3201

1

2

3

4

1

2

3

4

8

V

DD

7

CLK

6

D

OUT

CS/SHDN

5

MCP3201

8

V

DD

7

CLK

6

D

OUT

5

CS/SHDN

FUNCTIONAL BLOCK DIAGRAM

V

V

REF

DD

V

SS

The Microchip Technology Inc. MCP3201 is a succes-

DAC

sive approximation 12-bit Analog-to-Digital (A/D) Converter with on-board sample and hold circuitry. The

device provides a single pseudo-differential input. Differential Nonlinearity (DNL) is specified at ±1 LSB, and

Integral Nonlinearity (INL) is offered in ±1 LSB

(MCP3201-B) and ±2 LSB (MCP3201-C) versions.

Communication with the device is done using a simple

serial interface compatible with the SPI protocol. The

device is capable of sample rates of up to 100ksps at a

clock rate of 1.6MHz. The MCP3201 operates over a

IN+

IN-

Sample

and

Hold

Control Logic

CS/SHDN

Comparator

CLK

12-Bit SAR

Shift

Register

D

OUT

broad voltage range (2.7V - 5.5V). Low current design

permits operation with typical standby and active currents of only 500nA and 300µA, respectively. The

device is offered in 8-pin PDIP, TSSOP and 150mil

SOIC packages.

1999 Microchip Technology Inc. Preliminary DS21290B-page 1

MCP3201

1.0 ELECTRICAL

PIN FUNCTION TABLE

CHARACTERISTICS

1.1 Maximum Ratings*

VDD.........................................................................7.0V

All inputs and outputs w.r.t. V

Storage temperature..........................-65°C to +150°C

Ambient temp. with power applied......-65°C to +125°C

Soldering temperature of leads (10 seconds)..+300°C

ESD protection on all pins...................................> 4kV

*Notice: Stresses above those listed under “Maximum ratings” may

cause permanent damage to the device. This is a stress rating only and

functional operation of the device at those or any other conditions

above those indicated in the operational listin gs of this spe cificat ion is

not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

...... -0.6V to VDD +0.6V

SS

NAME FUNCTION

V

DD

V

SS

IN+

INCLK

D

OUT

CS/SHDN

V

REF

+2.7V to 5.5V Power Supply

Ground

Positive Analog Input

Negative Analog Input

Serial Clock

Serial Data Out

Chip select/Shutdown Input

Reference Voltage Input

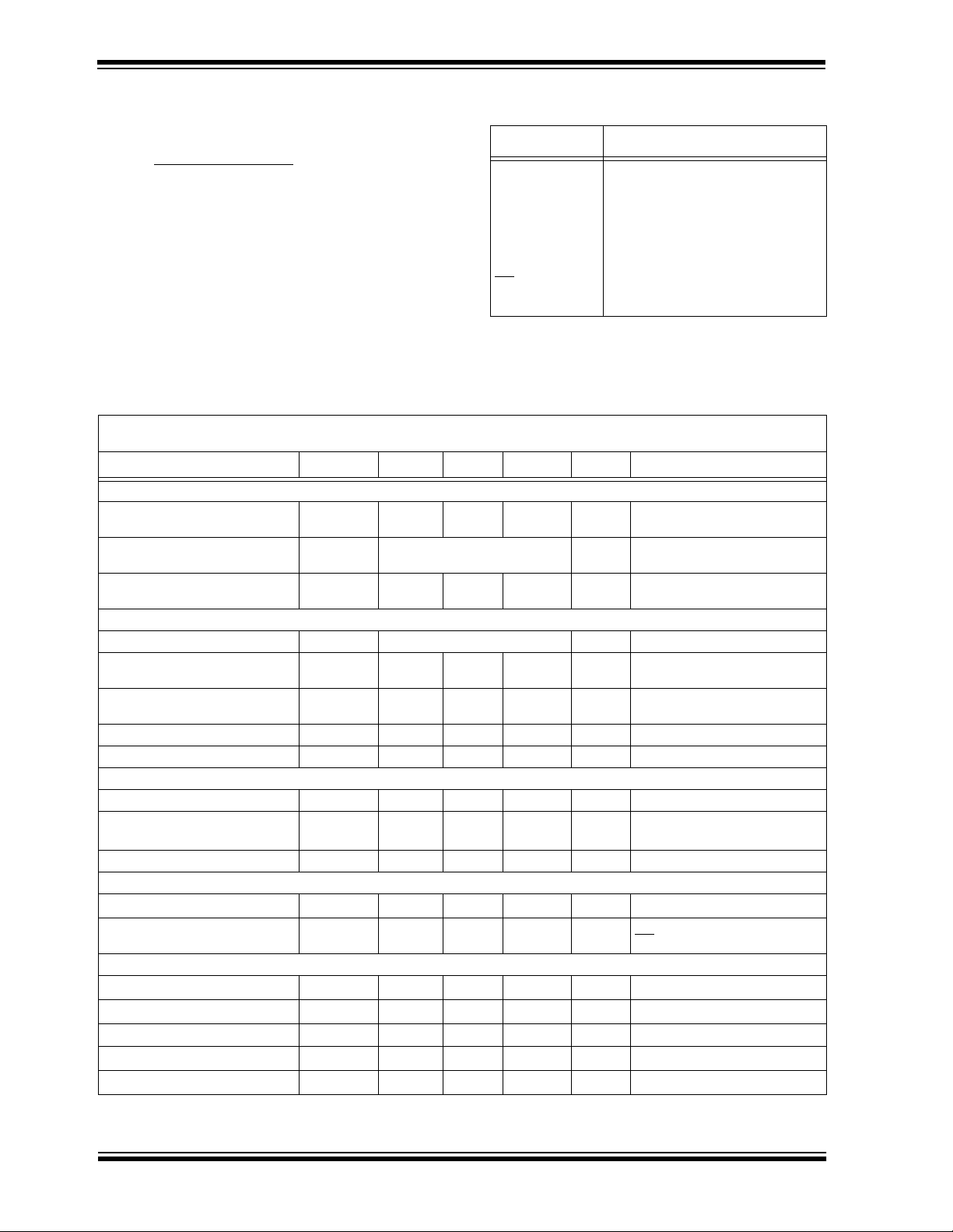

ELECTRICAL CHARACTERISTICS

All parameters apply at VDD = 5V, VSS = 0V, V

and f

CLK

= 16*f

unless otherwise noted.

SAMPLE

PARAMETER SYMBOL MIN. TYP. MAX. UNITS CONDITIONS

Convers ion Rate

Conversion Time t

Analog Input Sample Time t

Throughput Rate f

CONV

SAMPLE

SAMPLE

DC Accuracy

Resolution 12 bits

Integral Nonlinearity INL ±0.75

Different ial Nonlinea rity DNL ±0.5 ±1 LSB No missing codes over tem-

Offset Error ±1.25 ±3 LSB

Gain Error ±1.25 ±5 LSB

Dynamic Performance

Total Harmonic Distortion -82 dB V

Signal to Noise and Distortion

(SINAD)

Spurious Free Dynamic Range 86 dB V

Reference Input

Voltage Range 0.25 V

Current Drain 100

Analog Inputs

Input Voltage Range (IN+) IN- V

Input Voltage Range (IN-) V

Leakage Current 0.001 ±1 µA

Switch Resistance R

Sample Capacitor C

SS

SAMPLE

REF

= 5V, T

= -40°C to +85°C, f

AMB

12 clock

1.5 clock

100

50

±1

±1

±2

72 dB V

DD

150

.001

-100 VSS+100 mV

SS

3

+IN- V

REF

1K Ω See Figure 4-1

20 pF See Figure 4-1

= 100ksps

SAMPLE

cycles

cycles

ksps

ksps

LSB

LSB

V

= V

DD

REF

V

= V

DD

REF

MCP3201-B

MCP3201-C

perature

= 0.1V to 4.9V@1kHz

IN

= 0.1V to 4.9V@1kHz

IN

= 0.1V to 4.9V@1kHz

IN

VNote2

µA

µA CS

= VDD = 5V

= 5V

= 2.7V

DS21290B-page 2 Preliminary 1999 Microchip Technology Inc.

MCP3201

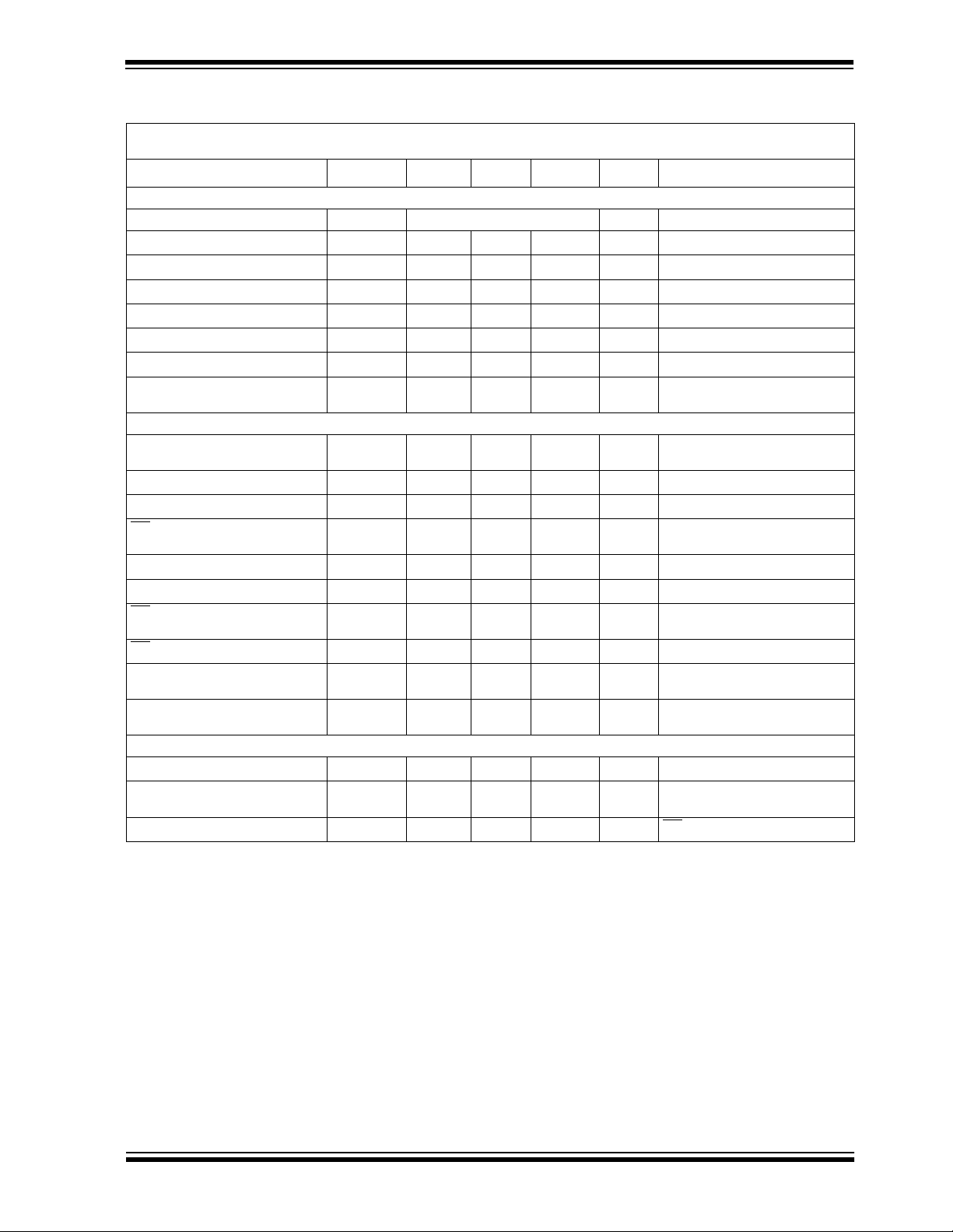

ELECTRICAL CHARACTERISTICS (CONTINUED)

All parameters apply at VDD = 5V, VSS = 0V, V

and f

CLK

= 16*f

unless otherwise noted.

SAMPLE

PARAMETER SYMBOL MIN. TYP. MAX. UNITS CONDITIONS

Digital Input/Output

Data Coding Format Straight Binary

High Level Input Voltage V

Low Level Input Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Input Leakage Current I

Output Leakage Current I

Pin Capacitance (all

inputs/outputs)

LO

CIN, C

IH

IL

OH

OL

LI

OUT

Timing Parameters

Clock Frequency f

Clock High Time t

Clock Low Tim e t

Fall To First Rising CLK

CS

Edge

CLK Fall To Output Data Valid t

CLK Fall To Output Enable t

CS

Rise To Output Disable t

CS Disable Time t

D

Rise Time t

OUT

D

Fall Time t

OUT

CLK

t

SUCS

DIS

CSH

HI

LO

DO

EN

R

F

Power Requirements

Operating Voltage V

Operating Current

Standby Current I

I

DDS

DD

DD

Note 1: This parameter is guaranteed by characterization and not 100% tested.

2: See graph that relates linearity performance to V

3: Because the sample cap will eventually lose charge, effective clock rates below 10kHz can affect linearity

performance, especially at elevated temperatures. See Section 6.2 for more informatio n.

REF

0.7 V

= 5V, T

= -40°C to +85°C, f

AMB

DD

0.3 V

DD

SAMPLE

V

V

= 100ksps

4.1 V IOH = -1mA, VDD = 4.5V

0.4 V IOL = 1mA, VDD = 4.5V

-10 10 µA VIN = VSS or V

-10 10 µA V

= VSS or V

OUT

DD

10 pF VDD = 5.0V (Note 1)

T

= 25°C, f = 1 MHz

AMB

1.6

0.8

MHz

MHz

VDD = 5V (Note 3)

VDD = 2.7V (Note 3)

312 ns

312 ns

100 ns

200 ns See Test Circuits, Figure 1-2

200 ns See Test C i rcuits, Figu re 1-2

100 ns See Test C i rcuits, Figu re 1-2

(Note 1)

625 ns

100 ns See Test C i rcuits, Figu re 1-2

(Note 1)

100 ns See Test C i rcuits, Figu re 1-2

(Note 1)

2.7 5.5 V

300

210

400 µAµAVDD = 5.0V, D

VDD = 2.7V, D

OUT

OUT

0.5 2 µA CS = VDD = 5.0V

level.

REF

DD

unloaded

unloaded

1999 Microchip Technology Inc. Preliminary DS21290B-page 3

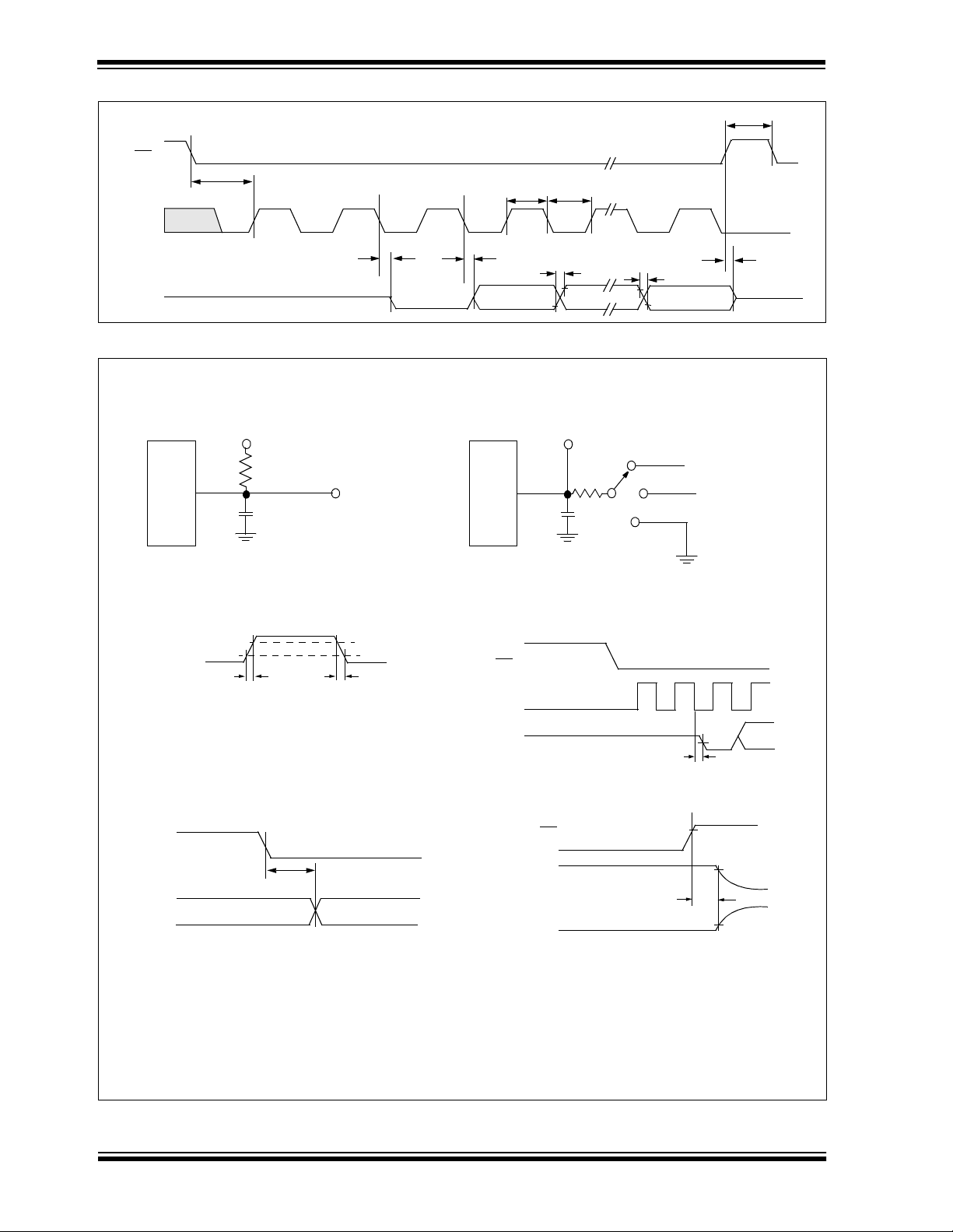

MCP3201

t

CSH

CS

t

SUCS

CLK

D

OUT

HI-Z

FIGURE 1-1: Serial Timing.

Load circuit for tR, t

1.4V

3K

D

OUT

C

Voltage Waveforms for tR, t

F, tDO

= 100pF

L

Test Point

F

t

t

HI

LO

t

EN

t

DO

NULL BIT

MSB OUT

t

R

Load circuit for

t

t

DIS

F

and t

LSB

EN

t

DIS

HI-Z

Test Point

V

DD

3K

D

OUT

100pF

V

SS

Voltage Waveforms for t

VDD/2

t

Waveform 2

DIS

tEN Waveform

t

Waveform 1

DIS

EN

CLK

D

D

OUT

Voltage Waveforms for t

OUT

V

OH

V

OL

t

R

t

DO

t

F

DO

CS

CLK

D

OUT

CS

D

OUT

Waveform 1*

D

OUT

Waveform 2

12

t

Voltage Waveforms for t

V

IH

T

DIS

†

EN

DIS

3

10%

4

B11

90%

* Waveform 1 is for an output with internal condi-

tions such that the output is high, unless disabled by the output control.

† Waveform 2 is for an output with internal condi-

tions such that the output is low, unless disabled

by the output control.

FIGURE 1-2: Test Circuits.

DS21290B-page 4 Preliminary 1999 Microchip Technology Inc.

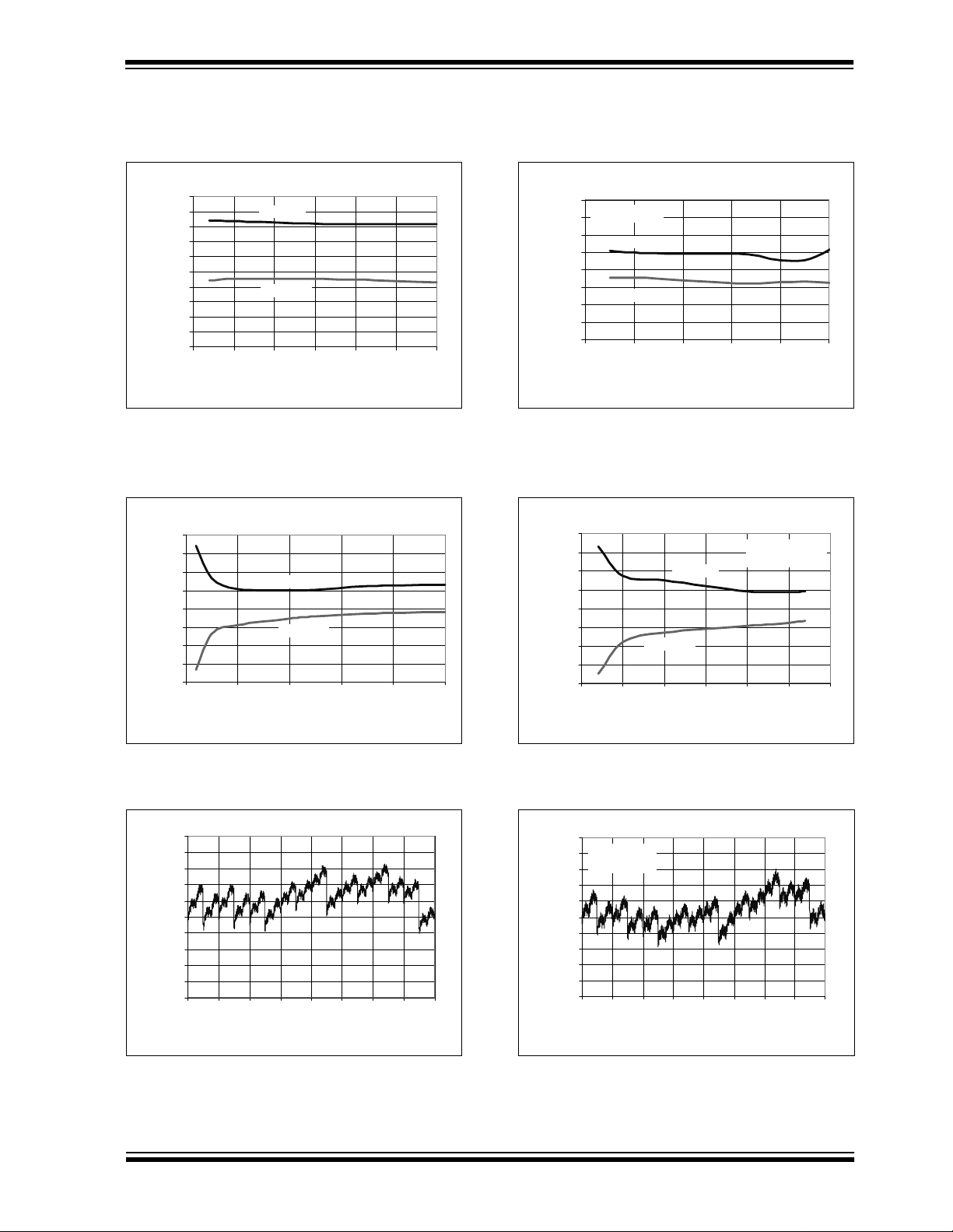

2.0 TYPICAL PERFORMANCE CHARACTERISTICS

)

Note: Unless otherwise indicated, VDD = V

= 5V, VSS = 0V, f

REF

SAMPLE

= 100ksps, f

CLK

= 16*f

MCP3201

SAMPLE,TA

= 25°C

1.0

0.8

Positive INL

0.6

0.4

0.2

0.0

-0.2

INL (LSB)

-0.4

Negative INL

-0.6

-0.8

-1.0

0 25 50 75 100 125 150

Sample Rat e (ksps)

FIGURE 2-1: Integral Nonlinearity (INL) vs. Sample

Rate.

2.0

1.5

1.0

0.5

0.0

-0.5

INL (LSB)

-1.0

-1.5

-2.0

012345

Positive INL

Negative INL

V

(V)

REF

2.0

VDD = V

= 2.7V

1.5

1.0

REF

Posi tive INL

0.5

0.0

-0.5

INL (LSB)

Negative INL

-1.0

-1.5

-2.0

0 20406080100

Sample Rate (ksps)

FIGURE 2-4: Integral Nonl inearity (INL) vs. Sample

Rate (V

= 2.7V).

DD

2.0

1.5

1.0

0.5

0.0

-0.5

INL (LSB

-1.0

-1.5

-2.0

0.0 0.5 1.0 1.5 2.0 2.5 3.0

Positive INL

Negative INL

V

REF

(V)

VDD = 2.7V

F

SAMPLE

= 50ksps

FIGURE 2-2: Integral Nonlinearity (INL) vs. V

REF

.

FIGURE 2-5: Integral Nonlinearity (INL) vs. V

REF

(VDD = 2.7V).

1.0

0.8

0.6

0.4

0.2

0.0

-0.2

INL (LSB)

-0.4

-0.6

-0.8

-1.0

0 512 1024 1536 2048 2560 3072 3584 4096

Digital Code

FIGURE 2-3: Integral Nonlinearity (INL) vs. Code

(Representative Part).

1999 Microchip Technology Inc. Preliminary DS21290B-page 5

1.0

VDD = V

= 2.7V

REF

= 50ksps

F

SAMPLE

0 512 1024 1536 2048 2560 3072 3584 4096

INL (LSB)

0.8

0.6

0.4

0.2

0.0

-0.2

-0.4

-0.6

-0.8

-1.0

Digit a l Code

FIGURE 2-6: Integral Nonlinearity (INL) vs. Code

(Representative Part, V

= 2.7V).

DD

MCP3201

Note: Unless otherwise indicated, VDD = V

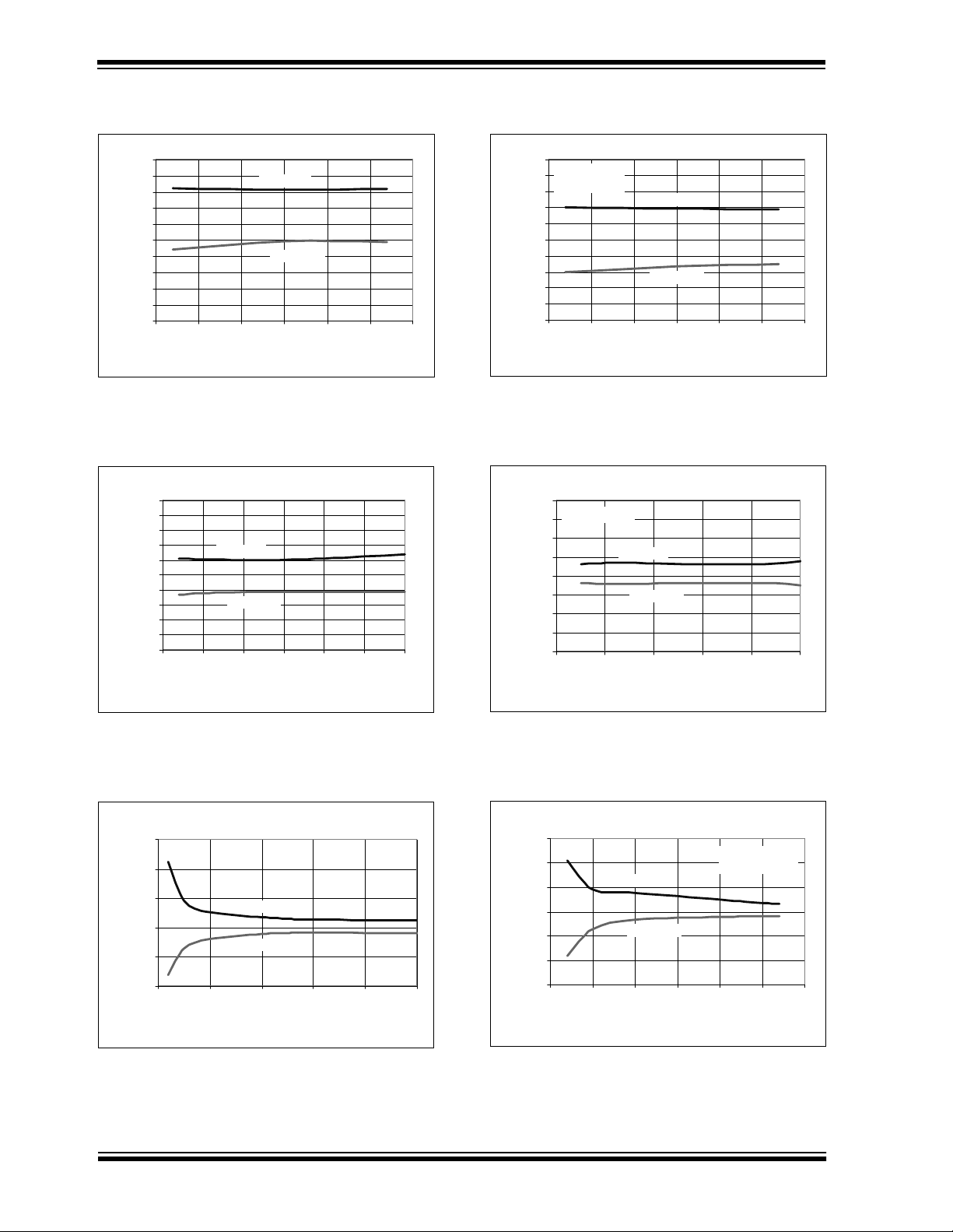

1.0

0.8

0.6

0.4

0.2

0.0

-0.2

INL (LSB)

-0.4

-0.6

-0.8

-1.0

-50 -25 0 25 50 75 100

Positive INL

Negative INL

= 5V, VSS = 0V, f

REF

Tem perature ( °C)

FIGURE 2-7: Integral Nonlinearity (INL) vs.

Temperature.

1.0

0.8

0.6

0.4

0.2

0.0

-0.2

DNL (LSB)

-0.4

-0.6

-0.8

-1.0

0 25 50 75 100 125 150

Positive DNL

Negative DNL

Sampl e Rat e (ksps)

SAMPLE

= 100ksps, f

1.0

VDD = V

0.8

F

SAMPLE

0.6

0.4

0.2

0.0

-0.2

INL (LSB)

-0.4

-0.6

-0.8

-1.0

-50 -25 0 25 50 75 100

CLK

= 2.7V

REF

= 50ksps

= 16*f

SAMPLE,TA

Positive INL

Negative INL

= 25°C

Tem perature ( °C)

FIGURE 2-10: Integral Nonlinearity (INL) vs.

Temperature (V

2.0

1.5

1.0

0.5

0.0

-0.5

DNL (LSB)

-1.0

-1.5

-2.0

VDD = V

= 2.7V)

DD

= 2.7V

REF

.

Positive DNL

Negative DNL

0 20 40 60 80 100

Sample Rate (ksps)

FIGURE 2-8: Differential Nonlinearity (DNL) vs.

Sample Rate.

3.0

2.0

1.0

0.0

DNL (LSB)

-1.0

-2.0

012345

Positive DNL

Negative DNL

V

REF

(V)

FIGURE 2-9: Differential Nonlinearity (DNL) vs.

V

REF

.

FIGURE 2-11: Differential Nonlinearity (DNL) vs.

Sample Rate (V

3.0

2.0

1.0

0.0

DNL (LSB)

-1.0

-2.0

-3.0

0.0 0.5 1.0 1.5 2.0 2.5 3.0

FIGURE 2-12: Differe nti al N onl ine arity (DNL) vs . V

= 2.7V)

DD

Positive DNL

Negative DNL

.

VDD = 2.7V

= 50ksps

F

SAMPLE

V

(V)

REF

REF

(VDD = 2.7V).

DS21290B-page 6 Preliminary 1999 Microchip Technology Inc.

MCP3201

)

)

Note: Unless otherwise indicated, VDD = V

1.0

0.8

0.6

0.4

0.2

0.0

-0.2

DNL (LSB)

-0.4

-0.6

-0.8

-1.0

0 512 1024 1536 2048 2560 3072 3584 4096

= 5V, VSS = 0V, f

REF

Digital Code

FIGURE 2-13: Differential Nonlinearity (DNL) vs.

Code (Representative Part).

1.0

0.8

0.6

0.4

0.2

0.0

-0.2

DNL (LSB)

-0.4

-0.6

-0.8

-1.0

-50 -25 0 25 50 75 100

Positive DNL

Negative DNL

Tem per ature (°C)

SAMPLE

= 100ksps, f

1.0

VDD = V

0.8

F

SAMPLE

0.6

0.4

0.2

0.0

-0.2

DNL (LSB)

-0.4

-0.6

-0.8

-1.0

0 512 1024 1536 2048 2560 3072 3584 4096

CLK

= 2.7V

REF

= 50ksps

= 16*f

SAMPLE,TA

= 25°C

Digital Code

FIGURE 2-16: Differential Nonlinearity (DNL) vs.

Code (Representative Part, V

1.0

VDD = V

= 2.7V

0.8

0.6

0.4

0.2

0.0

-0.2

DNL (LSB)

-0.4

-0.6

-0.8

-1.0

REF

F

= 50ksps

SAMPLE

-50 -25 0 25 50 75 100

Temp er at ur e ( ° C)

DD

Positive DNL

Negative DNL

= 2.7V).

FIGURE 2-14: Differential Nonlinearity (DNL) vs.

Temperature.

5

4

VDD = 5V

F

SAMPLE

VDD = 2.7V

F

SAMPLE

= 100ksps

= 50ksps

V

(V)

REF

REF

.

3

2

1

0

Gain Error (LSB

-1

-2

012345

FIGURE 2-15: Gain Error vs. V

FIGURE 2-17: Differential Nonlinearity (DNL) vs.

Temperature (V

20

18

16

14

12

10

8

6

Offset Error (LSB

4

2

0

012345

FIGURE 2-18: Offset Error vs. V

= 2.7V).

DD

VDD = 5V

F

SAMPLE

= 100ksps

VDD = 2.7V

F

SAMPLE

= 50ksps

V

REF

(V)

REF

.

1999 Microchip Technology Inc. Preliminary DS21290B-page 7

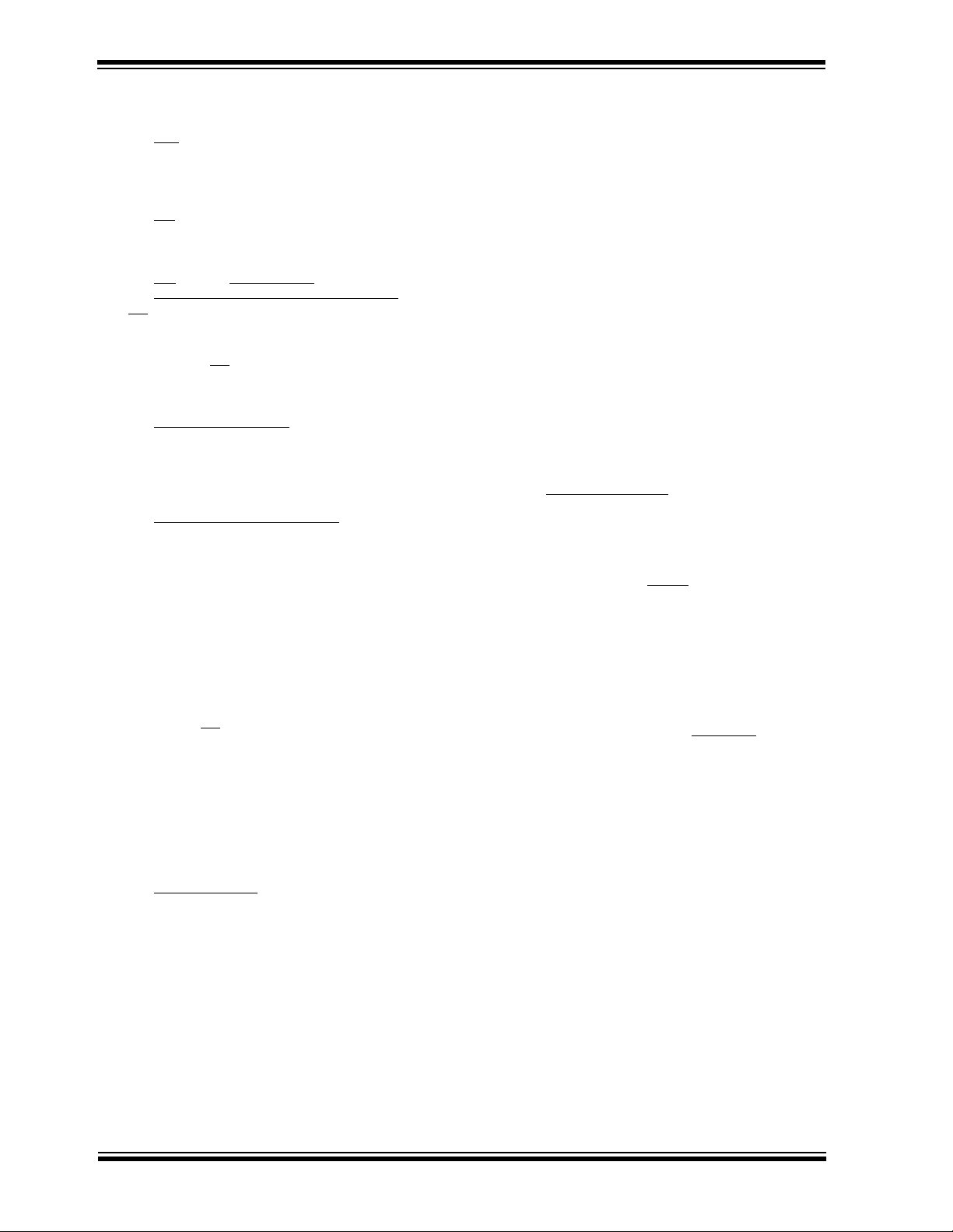

MCP3201

)

)

)

Input S i gnal Level ( dB )

)

Note: Unless otherwise indicated, VDD = V

1.0

0.8

0.6

VDD = V

= 2.7V

REF

F

0.4

SAMPLE

= 50ksps

0.2

0.0

-0.2

-0.4

Gain Error (LSB

-0.6

-0.8

-1.0

VDD = V

F

SAMPLE

= 5V

REF

= 100ksps

-50 -25 0 25 50 75 100

Tem per a t ur e ( °C)

FIGURE 2-19: Gain Error vs. Temperature.

100

90

80

70

60

50

40

SNR (dB)

30

VDD = V

F

SAMPLE

= 2.7V

REF

= 50ksps

20

10

0

1 10 100

Input Frequency (kHz)

VDD = V

F

SAMPLE

REF

= 100ksps

= 5V, VSS = 0V, f

REF

= 5V

SAMPLE

= 100ksps, f

CLK

= 16*f

SAMPLE,TA

= 25°C

2.0

1.8

1.6

1.4

VDD = V

F

SAMPLE

= 5V

REF

= 100ksps

1.2

1.0

0.8

0.6

Offset Error (LSB

0.4

VDD = V

F

SAMPLE

= 2.7V

REF

= 50ksps

0.2

0.0

-50-250255075100

Tempe r at ur e ( °C)

FIGURE 2-22: Offset Error vs. Temperature.

100

90

80

70

60

VDD = V

50

40

SINAD (dB

30

F

SAMPLE

= 2.7V

REF

= 50ksps

20

10

0

1 10 100

Input Frequency (kH z)

VDD = V

F

SAMPLE

= 5V

REF

= 100ksps

FIGURE 2-20: Signal to Nois e Rat io (SNR ) vs. In put

Frequency.

0

-10

-20

-30

-40

-50

-60

THD (dB)

-70

-80

-90

-100

VDD = V

= 2.7V

REF

F

= 50ksps

SAMPLE

VDD = V

= 5V

REF

F

= 100ksps

SAMPLE

1 10 100

FIGURE 2-23: Signal to Noise and Distortion

(SINAD) vs. Input Frequency.

80

70

60

50

40

30

SINAD (dB

20

10

0

-40 -35 -30 -25 -20 -15 -10 -5 0

VDD = 5V

F

SAMPLE

= 100ksps

VDD = 2.7V

F

SAMPLE

= 50ksps

Input Frequency (kHz)

FIGURE 2-21: Total Harmonic Distortion (THD) vs.

Input Frequency.

DS21290B-page 8 Preliminary 1999 Microchip Technology Inc.

FIGURE 2-24: Signal to Noise and Distortion

(SINAD) vs. Input Signal Level.

MCP3201

)

)

Note: Unless otherwise indicated, VDD = V

12.00

11.75

11.50

11.25

11.00

10.75

10.50

10.25

10.00

ENOB (rms)

9.75

9.50

9.25

9.00

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

VDD = V

F

SAMPLE

= 2.7V

REF

= 50ksps

V

REF

(V)

= 5V, VSS = 0V, f

REF

VDD = V

= 5V

REF

=100ksps

F

SAMPLE

FIGURE 2-25: Effective Number of Bits (ENOB) vs.

V

REF

.

100

90

80

70

60

50

40

SFDR (dB

30

VDD = V

F

SAMPLE

= 2.7V

REF

= 50ksps

20

10

0

110100

Input F r eque ncy (kHz)

VDD = V

F

SAMPLE

= 5V

REF

= 100ksps

SAMPLE

= 100ksps, f

12.0

11.5

CLK

= 16*f

SAMPLE,TA

= 25°C

VDD = 5V

F

SAMPLE

= 100ksps

11.0

10.5

10.0

9.5

ENOB (rms)

9.0

8.5

VDD = 2.7V

F

SAMPLE

= 50ksps

8.0

110100

Input Frequency (kHz)

FIGURE 2-28: Effective Number of Bits (ENOB) vs.

Input Frequency.

0

-10

-20

-30

-40

-50

-60

-70

Power Supply Rejection (dB

-80

1 10 100 1000 10000

Ripple Frequency (kHz)

FIGURE 2-26: Spurious Free Dynamic Range

(SFDR) vs. Input Frequency.

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

Amplitude (dB)

-100

-110

-120

-130

0 10000 20000 30000 40000 500 00

Fr equenc y ( H z )

FIGURE 2-27: Frequency Spectrum of 10kHz input

(Representative Part).

1999 Microchip Technology Inc. Preliminary DS21290B-page 9

VDD = V

REF

= 100ksps

F

SAMPLE

= 9.985kHz

F

INPUT

4096 points

= 5V

FIGURE 2-29: Power Supply Rejection (PSR) vs.

Ripple Frequency.

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

Amplitude (dB)

-100

-110

-120

-130

0 5000 10000 15000 20000 25000

Fr eq uenc y ( Hz)

VDD = V

REF

F

= 50ksps

SAMPLE

F

= 998.76Hz

INPUT

4096 points

= 2.7V

FIGURE 2-30: Frequency Spectrum of 1kHz input

(Representative Part, V

= 2.7V).

DD

MCP3201

Note: Unless otherwise indicated, VDD = V

500

V

= V

REF

450

400

350

300

250

(µA)

DD

I

200

150

100

50

0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

FIGURE 2-31: IDD vs. V

400

350

300

250

200

(µA)

DD

I

150

100

50

0

10 100 1000 10000

DD

All points at F

at V

= VDD = 2.5V, F

REF

= 1.6MHz except

CLK

= 800kHz

CLK

VDD (V)

DD.

VDD = V

= 5V

REF

VDD = V

= 2.7V

REF

Cloc k Frequency (kH z)

= 5V, VSS = 0V, f

REF

= 100ksps, f

SAMPLE

100

90

80

70

60

(µA)

50

REF

40

I

30

20

10

0

2.02.53.03.54.04.55.05.56.0

FIGURE 2-34: I

100

90

80

70

60

(µA)

50

REF

40

I

30

20

10

0

10 100 1000 10000

CLK

V

REF = VDD

All points at F

at V

= VDD = 2.5V, F

REF

REF

= 16*f

= 1.6MHz except

CLK

CLK

SAMPLE,TA

= 800kHz

= 25°C

VDD (V)

vs. V

DD

.

VDD = V

= 5V

REF

VDD = V

= 2.7V

REF

Cl oc k Frequency ( kHz)

FIGURE 2-32: IDD vs. Clock Frequency.

400

350

VDD = V

= 5V

REF

F

= 1.6MHz

CLK

300

250

200

(µA)

DD

I

150

100

50

0

FIGURE 2-33: I

VDD = V

= 2.7V

REF

F

= 800kHz

CLK

-50-250 255075100

Temperat ur e (°C)

vs. Temperature.

DD

FIGURE 2-35: I

100

90

80

70

60

(µA)

50

REF

40

I

30

20

10

0

-50-250 255075100

FIGURE 2-36: I

vs. Clock Frequency.

REF

VDD = V

= 5V

REF

F

= 1.6MHz

CLK

VDD = V

= 2.7V

REF

F

= 800kHz

CLK

Tem perat ur e ( °C )

vs. Temperature.

REF

DS21290B-page 10 Preliminary 1999 Microchip Technology Inc.

MCP3201

)

Note: Unless otherwise indicated, VDD = V

80

V

= CS = V

REF

VDD = V

DD

DDS

REF

vs. V

= CS = 5V

VDD (V)

DD.

70

60

50

(pA)

40

DDS

I

30

20

10

0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

FIGURE 2-37: I

100.00

10.00

= 5V, VSS = 0V, f

REF

SAMPLE

= 100ksps, f

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

Analog Input Leakage (nA

0.0

-50-250 255075100

CLK

= 16*f

SAMPLE,TA

= 25°C

VDD = V

F

CLK

= 5V

REF

= 1.6Mhz

Temper atur e ( ° C)

FIGURE 2-39: Analog Input Leakage Current vs.

Temperature.

(nA)

1.00

DDS

I

0.10

0.01

-50 -25 0 25 50 75 100

FIGURE 2-38: I

Tem p er ature (° C)

vs. Temperature.

DDS

1999 Microchip Technology Inc. Preliminary DS21290B-page 11

MCP3201

3.0 PIN DESCRIPTIONS

3.1 IN+

Positive analog input. This input can vary from IN- to

+ IN-.

V

REF

3.2 IN-

Negative analog input. This input can vary ±100mV

from V

3.3 CS/SHDN(Chip Select/Shutdown)

The CS/SHDN pin is used to initiate communication

with the device when pulled low and will end a conversion and put the device in low power standby when

pulled high. The CS

between conversions.

3.4 CLK (Serial Clock)

The SPI clock pin is used to initiate a conversion and to

clock out each bit of the conversion as it takes place.

See Section 6.2 for constraints on clock speed.

3.5 DOUT (Serial Data output)

The SPI serial data output pin is used to shift out the

results of the A/D conversion. Data will always change

on the falling edge of each clock as the conversion

takes place.

.

SS

/SHDN pin must be pulled high

In this diagram, it is shown that the source impedance

) adds to the internal sampling switch (RSS) imped-

(R

S

ance, directly affecting the time that is required to

charge the c apa citor (C

). Consequently, a larger

SAMPLE

source impedance increases the offset, gain, and integral linearity errors of the conversion.

Ideally, the impedance of the signal source should be

near zero. This is achievable with an operational amplifier such as the MCP601 , whic h has a closed loop output impedance of tens of ohms. The adverse affects of

higher source impedances are shown in Figure4-2.

If the volt age lev el o f IN+ is equ al to or less than IN -, the

resultant code wi ll be 000h. If t he voltag e at IN+ is e qual

to or greater than {[V

+ (IN-)] - 1 LSB}, then the out-

REF

put code will be FFFh . If the v olta ge level at IN- is more

than 1 LSB below V

input will have to go below V

, then the v olt age level at the IN+

SS

to see the 000h output

SS

code. Conv ersely, if IN- is more than 1 LSB above Vss,

then the FFFh code wil l not be seen unless the IN+

input level goes above V

REF

level .

4.2 Reference Input

The reference input (V

voltage range and the LSB size, as shown below.

LSB Size = V

) determines the analog i nput

REF

REF

4096

4.0 DEVICE OPERATION

The MCP3201 A/D Converter employs a conventional

SAR architecture. With this architecture, a sample is

acquired on an internal sample/hold capacitor for

1.5 clock cycles starting on the first rising edge of the

serial clock after CS

sample time, the input switch of t he converter op ens

and the device uses the collected charge on the internal sample and hold cap acitor to produce a serial 12-b it

digital output code. Conversion rates of 100ksps are

possible on the MC P3201. See Section 6.2 for information on minimum clock rates. Communication with the

device is do ne using a 3-wire SPI-com patible in terface.

4.1 Analog Inputs

The MCP3201 provides a single pseudo-differential

input. The IN+ input can range from IN- to V

(V

+IN-). The IN- input is limi ted to ±10 0mV from th e

REF

rail. The IN- input can be used to cancel small sig-

V

SS

nal common-mode noise which is present on both the

IN+ and IN- inputs.

For the A/D Con verter to meet speci fication, the charg e

holding capacitor (C

to acquire a 12-bit accurate voltage level during the

1.5 clock cycle sampling period. The analog input

model is shown in Figure 4-1.

has been pulled low. Following this

REF

) must be given enough time

SAMPLE

As the reference input is reduced, the LSB size is

reduced according ly . The th eoretical dig ital output code

produced by the A/D Con v erter is a functio n of the analog input signal and the reference input as shown

below.

Digital Output Code = 4096 * V

IN

V

REF

where:

VIN = analog input voltage = V(IN+) - V(IN-)

= reference volta ge

V

REF

When using an external voltage reference device, the

system designer should always refer to the manufacturer’s recommendations for c ircuit la you t. Any instabi lity in the operation of the reference device will have a

direct effect on the operation of the A/D Converter.

DS21290B-page 12 Preliminary 1999 Microchip Technology Inc.

VA

Legend

I

LEAKAGE

C

SAMPLE

CHx

R

S

VA

= Signal Source

R

= Source Impedance

S

CHx

= Input Channel Pad

C

= Input Capacitance

PIN

V

= Threshold Voltage

T

= Leakage Current at the pin

due to various junctions

SS

= Sampling Switch

R

= Sampling Switch Resistor

SS

= Sample/Hold Capacitance

C

PIN

7pF

MCP3201

V

DD

= 0.6V

V

T

= 0.6V

V

T

I

LEAKAGE

±1nA

Sampling

Switch

R

SS

SS

= 1kΩ

C

SAMPLE

= DAC capacitance

= 20 pF

V

SS

FIGURE 4-1: Analog Input Model.

1.8

VDD = V

1.6

1.4

1.2

1.0

0.8

0.6

0.4

Clock Frequency (MHz)

0.2

0.0

100 1000 10000

Input R esi s t ance ( O hm s)

VDD = V

REF

= 2.7V

= 5V

REF

FIGURE 4-2: Maximum Clock Frequency vs. Input

Resistance (R

) to maintain less than a 0.1 LSB

S

deviation in INL from nominal conditions.

1999 Microchip Technology Inc. Preliminary DS21290B-page 13

MCP3201

5.0 SERIAL COMMUNICATIONS

Communication with the device is done using a standard SPI-compatible serial interface. Initiating communication with the MCP3201 begins with the CS going

low. If the device was powered up with the CS

it must be brough t high and ba ck lo w to ini tiate comm unication. The device will begin to sample the analog

input on the first rising edge after CS

sample period will e nd in t he fall ing ed ge of the se cond

clock, at whic h tim e the device will o utp ut a l o w null bit.

The next 12 clocks will output the result of the conver-

CS

t

SUCS

CLK

t

SAMPLE

D

OUT

HI-Z

* After completing the data transfer, if further clocks are applied with CS

by zeros indefinitely. See Figure below.

: during this time, the bia s curr en t and the co mp arato r power down and the reference input beco me s a high im pe da nce

** t

DATA

node, leaving the CLK running to clock out the LSB-first data or zeros.

NULL

B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

BIT

pin low,

goes low. The

t

CYC

t

CONV

sion with MSB first, as shown in Figure 5-1. Data is

always output from th e de vice on the falling edg e of the

clock. If all 12 data bits have been transmitted and the

device cont inues to receive clock s whil e the CS

is held

low, the device will output the conversion result LSB

first, as shown in Figure 5-2. If more clocks are provided to the device while CS

is still low (after the LSB

first data has been transmitted), the device will clock

out zeros indefinitely.

t

CSH

Power

Down

t

**

DATA

HI-Z

*

low, the A/D Converter will output LSB first data, followed

NULL

B11 B10 B9 B8

BIT

FIGURE 5-1: Communication with MCP3201 using MSB first Format.

t

CYC

CS

t

SUCS

CLK

t

SAMPLE

D

OUT

HI-Z

* After completing the data transfer, if further clocks are applied with CS

** t

node, leaving the CLK running to clock out the LSB-first data or zeros.

NULL

B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

BIT

: during this time, the bia s curr en t and the co mp arato r power dow n an d the ref ere nce input beco me s a hi gh impe da nce

DATA

t

CONV

B1 B2 B3

low, the A/D Converter will output zeros indefinitely.

FIGURE 5-2: Communication with MCP3201 using LSB first Format.

Power Down

t

**

DATA

B4

B5 B6 B7 B8 B9 B10 B11*

t

CSH

HI-Z

DS21290B-page 14 Preliminary 1999 Microchip Technology Inc.

MCP3201

6.0 APPLICATIONS INFORMATION

6.1 Using the MCP3201 with

Microcontroller SPI Ports

With most microcontroller SPI ports, it is required to

clock out eigh t bits at a time . If t his is the c ase, it will b e

necessary to provide more clocks than are required for

the MCP3201. As an example, Figure 6-1 and

Figure 6-2 show how the MCP3201 can be interfaced

to a microcontroller with a st andard SPI po rt. Since the

MCP3201 always clocks data out on the falling edge of

clock, the MCU SPI po r t must be conf igured t o match

this operati on. SPI Mod e 0,0 (cl ock id les low) a nd S PI

Mode 1,1 (clock idles high) are both compatible with the

MCP3201. Figure 6-1 depicts the operation shown in

SPI Mode 0,0, which requires that the CLK from the

microcontroller idles in the ‘low’ state. As shown in the

diagram, the MSB is clocked out of the A/D Converter

on the falling edge of the third clock pulse. After the first

eight clocks have been sent to the device, the microcontroller’s receive buffer will contain two unknown bits

CS

CLK 910111213141516

D

OUT

12345678

HI-Z

NULL

BIT

??0

B11 B10 B9 B8

B11 B10 B9 B8

B7

B7

(the output is at high impedance for the f irst two cloc ks),

the null bit and the highe st order fi v e bits of the con v ersion. After the second eight clocks have been sent to

the device, the MCU receive register will contain the

lowest order seven bits and the B1 bit repeated as the

A/D Converter has begun to shift out LSB first data with

the extra clock. Typical procedure would then call for

the lower orde r byte of data to be shif ted right by one bit

to remove the extra B1 bit. The B7 bit is then transferred from the high order byte to the lower order byte,

and then the higher order byte is shifted one bit to the

right as well. Eas ier m anipu lation of th e con v erted data

can be obtained by using this method.

Figure 6-2 shows the same thing in SPI Mode 1,1

which requires that the clock idles in the high state. As

with mode 0,0, the A/D Converter outputs data on the

falling edge of the c lock a nd the MCU la tches data from

the A/D Converter in on the rising edge of the clock.

B6 B5 B4 B3 B2 B1 B0

B6 B5 B4 B3 B2 B1 B0

MCU latches data from A/D Converter

on rising edges of SCLK

Data is clocked out of

A/D Converter on falling edges

HI-Z

B2

B1

LSB first data begins

to come out

B1

Data stored into MCU receive re gister

after transmission of first 8 bits

Data stored into MCU receive reg ister

after transmission of second 8 bits

FIGURE 6-1: SPI Communication using 8-bit segments (Mode 0,0: SCLK idles low).

CS

CLK

D

OUT

1234567

HI-Z

NULL

B11 B10 B9 B8

BIT

??0

Data stored into MCU receive register

B11 B10 B9 B8

after transmission of first 8 bits

8

9 10111213 1415 16

B6 B5 B4 B3 B2 B1 B0

B7

B7

B6 B5 B4 B3 B2 B1 B0

Data stored into MCU receive r egister

after transmission of second 8 bits

B1

B1

FIGURE 6-2: SPI Communication using 8-bit segments (Mode 1,1: SCLK idles high).

MCU latches data from A/D Converter

on rising edges of SCLK

Data is clocked out of

A/D Converter on falling edges

HI-Z

LSB first data begins

to come out

1999 Microchip Technology Inc. Preliminary DS21290B-page 15

MCP3201

6.2 Maintaining Minimum Clock Speed

When the MCP3201 initiates the sample period,

charge is stored on the sample capacitor. When the

sample period is complete, the device converts one bit

for each clock that is received. It is impor tant for the

user to note that a slow clock rate will allow charge to

bleed off the sample cap while the conversion is taking

place. At 85°C (worst case condition), the part will

maintain proper charge on the sample capacitor for at

least 1.2ms after the sample period has ended. This

means that the time between the end of the sample

period and the time that all 12 data bits have been

clocked o ut must n ot e xc eed 1.2 ms (effect iv e cl oc k frequency of 10kHz). Failure to meet this criteria may

induce linearity errors into the conversion outside the

rated specif icat ions. It sh ould b e note d that du ri ng the

entire conversion cycle, the A/D Converter does not

require a constant cloc k speed or du ty cycle, as long as

all timing specification s are met .

6.3 Buffering/Filtering the Analog Inputs

If the signal source for the A/D Converter is not a low

impedance source , it will ha v e to be b uffered or inaccurate conversion results may occur. See Figure 4-2. It is

also recommended that a fil ter be used to eliminate an y

signals th at may be aliased back in to the conversion

results. This is illustrated in Figure 6-3 where an op

amp is used to drive the analog input of the MCP3201.

This amplifier pro v ide s a low impedance source for the

conver ter input and a low pass filter, which eliminates

unwanted high frequency noise.

Low pass (anti-aliasing) filters can be designed using

Microchip’s interactive FilterLab™ software. FilterL ab

will calcul ate capaci tor and res istor values, as we ll as

determine the number of poles that are required for the

application. For more information on filtering signals,

see the application note AN699

Filters for Data Acqu is iti on Sys tem s.”

“Anti-Aliasing Analog

6.4 Layout Considerations

When layi ng out a printed ci rcuit board for u se with analog components, care should be taken to reduce noise

wherever possible. A bypas s capacitor sh ould always

be used with th is device and should be plac ed as clos e

as possibl e to the d evice pin. A bypass c apa ci tor value

of 1µF is recommended.

Digital and analo g trace s should be sepa rated a s muc h

as possible on the board and no traces should run

underneath the device or the bypass capacitor. Extra

precautions should be taken to keep traces with high

frequency signals (such as clock lines) as far as possible from analog traces.

Use of an analog ground plane is recommended in

order to keep the ground potential the same for all

devices on the board. Providing V

devices in a “star” conf igurat ion can al so re duc e nois e

by eliminating current return paths and associated

errors. See Figure 6-4. For more information on layout

tips when using A/D Converter, refer to AN688

Tips for 12-Bit A/D Converter Applications”

V

DD

Connection

Device 1

Device 2

connections to

DD

Device 4

Device 3

“Layout

.

V

4.096V

Reference

0.1µF

ADI

REF198

1µF

Tant.

0.1µF

IN+

DD

10µF

V

REF

1µF

FIGURE 6-4: VDD traces arranged in a ‘Star’

configuration in order to reduce errors caused by

current return paths.

MCP3201

C

1

R

1

V

IN

R

MCP601

2

C

2

+

-

R

4

R

3

IN-

FIGURE 6-3: The MCP601 Operational Amplifier is

used to implement a 2nd order anti-aliasing filter for

the signal being converted by the MCP3201.

DS21290B-page 16 Preliminary 1999 Microchip Technology Inc.

FilterLab is a tra demark of Microchip Technology Inc. in

the U.S.A and other countries. All rights reserved.

MCP3201

MCP3201 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

MCP3201 - G T /P

Package: P = PDIP (8 lead)

Temperature I=–40°C to +85°C

Range:

Performance B = ±1 LSB INL (TSSOP not available in this grade)

Grade: C=±2 LSB INL

Device: MCP3201

SN = SOIC (150 mil Body), 8 lead

ST = TSSOP, 8 lead (C Grade only)

12-Bit Serial A/D Converter

=

MCP3201T

12-Bit Serial A/D Converter on tape and reel

=

(SOIC and TSSOP packages only)

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Cor porate Literature Center U.S. FAX: (602) 786-7277. After September 1, 1999, (480) 786-7277

3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

1999 Microchip Technology Inc. Preliminary DS21290B-page 17

MCP3201

NOTES:

DS21290B-page 18 Preliminary 1999 Microchip Technology Inc.

NOTES:

MCP3201

1999 Microchip Technology Inc. Preliminary DS21290B-page 19

WORLDWIDE SALES AND SERVICE

AMERICAS

Corporate Office

Microchip Technology Inc.

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-786-7200 Fax: 480-786-7277

Technical Support: 480-786-7627

Web Address: http://www.microchip.com

Atlanta

Microchip Technology Inc.

500 Sugar Mill Road, Suite 200B

Atlanta, GA 30350

Tel: 770-640-0034 Fax: 770-640-0307

Boston

Microchip Technology Inc.

5 Mount Royal Avenue

Marlborough, MA 01752

Tel: 508-480-9990 Fax: 508-480-8575

Chicago

Microchip Technology Inc.

333 Pierce Road, Suite 180

Itasca, IL 60143

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Microchip Technology Inc.

4570 Westgrove Drive, Suite 160

Addison, TX 75248

Tel: 972-818-7423 Fax: 972-818-2924

Dayton

Microchip Technology Inc.

Two Prestige Place, Suite 150

Miamisburg, OH 45342

Tel: 937-291-1654 Fax: 937-291-9175

Detroit

Microchip Technology Inc.

Tri-Atria Office Building

32255 Northwestern Highway, Suite 190

Farmington Hills, MI 48334

Tel: 248-538-2250 Fax: 248-538-2260

Los Angeles

Microchip Technology Inc.

18201 Von Karman, Suite 1090

Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338

New York

Microchip Technology Inc.

150 Motor Parkway, Suite 202

Hauppauge, NY 11788

Tel: 631-273-5305 Fax: 631-273-5335

San Jose

Microchip Technology Inc.

2107 North First Street, Suite 590

San Jose, CA 95131

Tel: 408-436-7950 Fax: 408-436-7955

AMERICAS (continued)

Toro nt o

Microchip Technology Inc.

5925 Airpor t Road, Suite 200

Mississauga, Ontario L4V 1W1, Canada

Tel: 905-405-6279 Fax: 905-405-6253

ASIA/PACIFIC

Hong Kong

Microchip Asia Pacific

Unit 2101, Tower 2

Metroplaza

223 Hing Fong Road

Kwai Fong, N.T., Hong Kong

Tel: 852-2-401-1200 Fax: 852-2-401-3431

Beijing

Microchip Technology, Beijing

Unit 915, 6 Chaoyangmen Bei Dajie

Dong Erhuan Road, Dongcheng District

New China Hong Kong Manhattan Building

Beijing 100027 PRC

Tel: 86-10-85282100 Fax: 86-10-85282104

India

Microchip Technology Inc.

India Liaison Office

No. 6, Legacy, Convent Road

Bangalore 560 025, India

Tel: 91-80-229-0061 Fax: 91-80-229-0062

Japan

Microchip Technology Intl. Inc.

Benex S-1 6F

3-18-20, Shinyokohama

Kohoku-Ku, Yokohama-shi

Kanagawa 222-0033 Japan

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea

Microchip Technology Korea

168-1, Youngbo Bldg. 3 Floor

Samsung-Dong, Kangnam-Ku

Seoul, Korea

Tel: 82-2-554-7200 Fax: 82-2-558-5934

Shanghai

Microchip Technology

RM 406 Shanghai Golden Bridge Bldg.

2077 Yan’an Road West, Hong Qiao District

Shanghai, PRC 200335

Tel: 86-21-6275-5700 Fax: 86 21-6275-5060

ASIA/PACIFIC (continued)

Singapore

Microchip Technology Singapore Pte Ltd.

200 Middle Road

#07-02 Prime Centre

Singapore 188980

Tel: 65-334-8870 Fax: 65-334-8850

Taiwan, R.O.C

Microchip Technology Taiwan

10F-1C 207

Tung Hua North Road

Taip e i , Ta i w a n , R O C

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

EUROPE

United Kingdom

Arizona Microchip Technology Ltd.

505 Eskdale Road

Winnersh Triangle

Wokingham

Berkshire, England RG41 5TU

Tel: 44 118 921 5858 Fax: 44-118 921-5835

Denmark

Microchip Technology Denmark ApS

Regus Business Centre

Lautrup hoj 1-3

Ballerup DK-2750 Denmark

Tel: 45 4420 9895 Fax: 45 4420 9910

France

Arizona Microchip Technology SARL

Parc d’Activite du Moulin de Massy

43 Rue du Saule Trapu

Batiment A - ler Etage

91300 Massy, France

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany

Arizona Microchip Technology GmbH

Gustav-Heinemann-Ring 125

D-81739 München, Germany

Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

Italy

Arizona Microchip Technology SRL

Centro Direzionale Colleoni

Palazzo Taurus 1 V. Le Colleoni 1

20041 Agrate Brianza

Milan, Italy

Tel: 39-039-65791-1 Fax: 39-039-6899883

11/15/99

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999. The

Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 cer tified.

®

8-bit MCUs, KEELOQ

®

code hopping

All rights reserved. © 1999 Microchip Technology Incorporated. Printed in the USA. 11/99 Printed on recycled paper.

Information contained in this publi c ation regarding device applications and the like is i nte nded for suggestion only and may be superseded by updates . No repr esentation or warranty is given and no liability is assumed

by Microchip T echnology Incorpora ted with respect to the accuracy or use of such information, or infringe ment of patents or othe r intellec tual property rights arising from such use or otherwis e. Use of Microchi p’s produc ts

as critical components in life s upport systems is not authorized except with expres s w ri t ten approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellect ual property rights. The Microchip

logo and name are registered trademarks of Mi crochip Technology Inc. in the U.S. A. and other countries. All rights reserved. All other tradem arks mentioned herein are the property of their respective comp ani es .

1999 Microchip Technology Inc.

Loading...

Loading...