PIC18CXX8

High-Performance Microcontrollers with CAN Module

High Performance RISC CPU:

• C-compiler optimized architecture instruction set

• Linear program memory addressi ng to 32 Kbytes

• Linear data memory addressing to 4 Kbytes

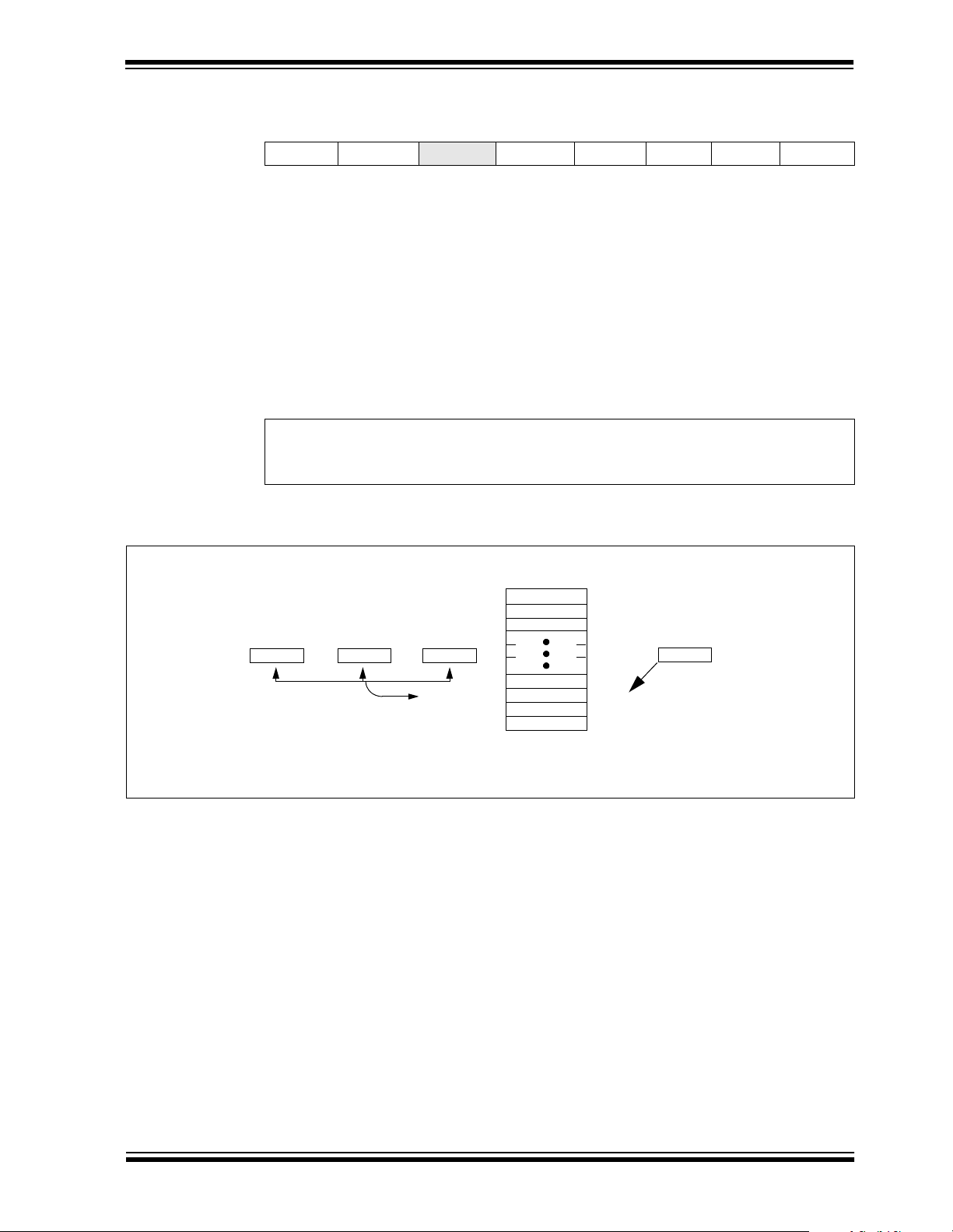

Program Memory

On-Chip Off-Chip

Device

EPROM

(bytes)

PIC18C658 32 K 16384 N/A 1536

PIC18C858 32 K 16384 N/A 1536

• Up to 10 MIPS operation:

- DC - 40 MHz clock input

- 4 MHz - 10 MHz osc./clock input with PLL active

• 16-bit wide instructions, 8-bit wide data path

• Priority levels for interrupts

• 8 x 8 Single Cycle Hardware Multiplier

# Single

Word

Instructions

Maximum

Addressing

(bytes)

On-Chip

RAM

(bytes)

Peripheral Features:

• High current sink/source 25 mA/25 mA

• Up to 76 I/O with individual direction contro l

• Four ext ernal interrupt pins

•Timer0 module: 8-bit/16-bit timer/counter with

8-bit programmable prescaler

•Timer1 module: 16-bit timer/counter

•Timer2 module: 8-bit timer/counter with 8-bit

period register (time base for PWM)

•Timer3 module: 16-bit timer/counter

• Secondary oscillator clock option - Timer1/Timer3

• Two Capture/Compa re/PWM (CCP) modules

CCP pins can be configured as:

- Capture input: 16-bit, max resolution 6.25 ns

- Compare is 16-bit, max resolution 100 ns (T

- PWM output: PWM resolution is 1- to 10-bit.

Max. PWM freq. @:8-bit resolution = 156 kHz

10-bit resolution = 39kHz

• Master Synchronous Serial Port (MSSP) with two

modes of operation:

- 3-wire SPI™ (Supports all 4 SPI modes)

2

C™ Master and Slave mode

-I

• Addressable USART module: Supports Interrupt

on Address bit

CY)

Advanced Analog Features:

• 10-bit Analog-to-Digital Converter module (A/D)

with:

- Fast sampling rate

- Conversion available during SLEEP

- DNL = ±1 LSb, INL = ±1 LSb

- Up to 16 channels available

• Analog Comparator Module:

- 2 Comparators

- Programmable input and output multiplexing

• Comparator Voltage Reference Module

• Programmable Low Voltage Detection (LVD)

module

- Supports interrupt on low voltage detection

• Programmable Brown-out Reset (BOR)

CAN BUS Module Features:

• Message bit rates up to 1 Mbps

• Conforms to CAN 2.0B ACTIVE Spec with:

- 29-bit Identifier Fields

- 8 byte message length

• 3 Transmit Message Buffers with prioritization

• 2 Receive Message Buf fers

• 6 full 29-bit Acceptance Filters

• Prioritization of Acceptance Filters

• Multiple Receive Buffers for High Priority

Messages to prevent loss due to overflow

• Advanced Error Management Features

Special Microcontroller Features:

• Power-on Reset (POR), Power-up T imer (PWRT),

and Oscillator Start-up Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator

• Programmable code protection

• Power saving SLEEP mode

• Selectable oscillator options, including:

- 4X Phase Lock Loop (of primary oscillator)

- Secondary Oscillator (32 kHz) clock input

• In-Circuit Serial Programming (ICSP™) via two pins

CMOS Technology:

• Low power, high speed EPROM technology

• Fully static design

• Wide operating voltage range (2.5V to 5.5V)

• Industrial and Extended temperature ranges

• Low power consumption

2000 Microchip Technology Inc. Advanced Information DS30475A-page 1

PIC18CXX8

Pin Diagrams

64-Pin TQFP

RE1/WR

RE0/RD

RG0/CANTX1

RG1/CANTX2

RG2/CANRX

RG3

/VPP

MCLR

RG4

V

SS

VDD

RF7

RF6/AN11

RF5/AN10/CV

RF2/AN7/C1OUT

REF

RF4/AN9

RF3/AN8

RE2/CS

RE3

RE4

RE5

RE6

RE7/CCP2

RD0/PSP0

VDDVSSRD1/PSP1

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PIC18C658

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3

RB4

RB5

RB6

SS

V

OSC2/CLKO/RA6

OSC1/CLKI

V

DD

RB7

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

-

+

SS

DD

AV

RF0/AN5

RF1/AN6/C2OUT

AV

REF

REF

RA2/AN2/V

RA3/AN3/V

SS

DD

V

V

RA1/AN1

RA0/AN0

/AN4/LVDIN

RA5/SS

RA4/T0CKI

RC1/T1OSI

RC6/TX/CK

RC0/T1OSO/T13CKI

RC7/RX/DT

DS30475A-page 2 Advanced Information 2000 Microchip Technology Inc.

Pin Diagrams (Cont.’d)

68-Pin PLCC

PIC18CXX8

RE1/WR

RE0/RD

RG0/CANTX1

RG1/CANTX2

RG2/CANRX

RG3

MCLR

/VPP

RG4

NC

V

VDD

RF7

RF6/AN11

RF5/AN10/CV

RF2/AN7/C1OUT

REF

RF4/AN9

RF3/AN8

SS

RE2/CS

RE3

RE4

RE5

RE6

RE7/CCP2

9 8 7 6 5 4 3 2 1 6867666564636261

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

2728 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

DD

AV

RF0/AN5

RF1/AN6/C2OUT

PIC18C658

-

+

SS

REF

REF

AV

RA2/AN2/V

RA3/AN3/V

RD0/PSP0

VDDVSSRD1/PSP1

RA1/AN1

RA0/AN0

NC

NC

SS

V

DD

V

RD2/PSP2

RD3/PSP3

RA4/T0CKI

/AN4/LVDIN

RA5/SS

RD4/PSP4

RC1/T1OSI

RD5/PSP5

RD6/PSP6

RC6/TX/CK

RC0/T1OSO/T13CKI

RD7/PSP7

RC7/RX/DT

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3

RB4

RB5

RB6

V

SS

NC

OSC2/CLKO/RA6

OSC1/CLKI

DD

V

RB7

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1

2000 Microchip Technology Inc. Advanced Information DS30475A-page 3

PIC18CXX8

Pin Diagrams (Cont.’d)

80-Pin TQFP

RH2

RH3

RE1/WR

RE0/RD

RG0/CANTX1

RG1/CANTX2

RG2/CANRX

RG3

MCLR

/VPP

RG4

V

VDD

RF7

RF6/AN11

RF5/AN10/CV

RF2/AN7/C1OUT

REF

RF4/AN9

RF3/AN8

RH7/AN15

RH6/AN14

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

80

RH1

79

RH0

78

RE2/CS

RE3

77 76 75

RE4

RE5

RE6

RE7/CCP2

RD0/PSP0

VDDVSSRD1/PSP1

PIC18C858

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

RJ0

RJ1

68 67 66 6572 71 70 6974 73

64 63 62 61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

RJ2

RJ3

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3

RB4

RB5

RB6

SS

V

OSC2/CLKO/RA6

OSC1/CLKI

DD

V

RB7

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1

RK3

RK2

21 22 23 24 25 26 27 28 29 30 31 32

-

+

SS

DD

AV

RH5/AN13

RF0/AN5

RH4/AN12

RF1/AN6/C2OUT

AV

REF

REF

RA2/AN2/V

RA3/AN3/V

SS

V

RA1/AN1

RA0/AN0

33 34

DD

V

/AN4/LVDIN

RA5/SS

35 36

RA4/T0CKI

40

39

37

38

RK1

RK0

RC1/T1OSI

RC6/TX/CK

RC7/RX/DT

RC0/T1OSO/T13CKI

DS30475A-page 4 Advanced Information 2000 Microchip Technology Inc.

Pin Diagrams (Cont.’d)

84-Pin PLCC

RH1

PIC18CXX8

DDVSS

V

RE2/CS

RE3

RE4

RH0

RE5

RD0/PSP0

RE6

RE7/CCP2

NC

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

RJ0

RJ1

RH2

RH3

RE1/WR

RE0/RD

RG0/CANTX1

RG1/CANTX2

RG2/CANRX

RG3

MCLR

/VPP

RG4

NC

V

VDD

RF7

RF6/AN11

RF5/AN10/CV

RF2/AN7/C1OUT

REF

RF4/AN9

RF3/AN8

RH7/AN15

RH6/AN14

SS

11

987654321

10

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

3435 36 37 38 39 40 41 42 43

33

SS

DD

AV

AV

RH4/AN12

RF0/AN5

RF1/AN6/C2OUT

RH5/AN13

PIC18C858

-

+

REF

REF

RA2/AN2/V

RA3/AN3/V

NC

RA1/AN1

RA0/AN0

83 82 81

84 75

44

45

SS

V

DD

V

/AN4/LVDIN

RA5/SS

80

797877

4948

4746

RA4/T0CKI

RC1/T1OSI

50

RC6/TX/CK

RC0/T1OSO/T13CKI

76

51

RK0

RC7/RX/DT

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

5352

RK1

RJ2

RJ3

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3

RB4

RB5

RB6

V

SS

NC

OSC2/CLKO/RA6

OSC1/CLKI

DD

V

RB7

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1

RK3

RK2

2000 Microchip Technology Inc. Advanced Information DS30475A-page 5

PIC18CXX8

Table of Contents

1.0 Device Overview ..........................................................................................................................................................................9

2.0 Oscillator Configurations ............................................................................................................................................................21

3.0 Reset.......................................................................................................................................................................................... 29

4.0 Memory Organization .................................................................................................................................................................41

5.0 Table Reads/Table Writes.......................................................................................................................................................... 65

6.0 8 X 8 Hardware Multiplier................... ........................................................................................................................................71

7.0 Interrupts.................................................................................................................................................................................... 75

8.0 I/O Ports ........................................... ......................... ......................... ........................................................................................89

9.0 Parallel Slave Port.......................................................................... .......................................................................................... 109

10.0 Timer0 Module ......................................................................................................................................................................... 113

11.0 Timer1 Module ......................................................................................................................................................................... 117

12.0 Timer2 Module ......................................................................................................................................................................... 121

13.0 Timer3 Module ......................................................................................................................................................................... 123

14.0 Capture/Compare/PWM (CCP) Modules ................................................................................................................................. 127

15.0 Master Synchronous Serial Port (MSSP) Module .................................................................................................................... 135

16.0 Addressable Universal Synchronous Asynchronous Receiv er Transmitter (USA RT )..............................................................167

17.0 CAN Module.............................................................................................................................................................................183

18.0 10-bit Analog-to-Digital Converter (A/D) Module......................................................................................................................227

19.0 Comparator Module.............................................................................. .. .... ....... .... .. .... .... .........................................................237

20.0 Comparator Voltage Reference Module........... .. ....... .... .. .... .. .. ......... .. .... .. .. ......... .. .. .... .. .... ....... .. .............................................. 243

21.0 Low Voltage Detect .................................................................................................................................................................. 247

22.0 Special Features of the CPU......................................................................................... ...........................................................251

23.0 Instruction Set Summary.......................................................................................................................................................... 261

24.0 Development Support. .............................................................................................................................................................. 305

25.0 Electrical Characteristics..........................................................................................................................................................311

26.0 DC and AC Characteristics Graphs and Tables.......................................................................................................................341

27.0 Packaging Information........................................... ..................................... .............................................................................. 343

Appendix A: Data Sheet Revision History......................................................................................................................................349

Appendix B: Device Differences.....................................................................................................................................................349

Appendix C: Device Migrations ............................................... .... ......... .... .. .... .... ......... .. .... .... .........................................................350

Appendix D: Migrating from other PICmicro Devices................................... .... .. ......... .... .. .... ....... .... .... .. .. ......................................350

Appendix E: Development Tool Version Requirements.................................................................................................................351

Index ..................................................................................................................................................................................................353

On-Line Support.................................................................... .. .... .... .. ......... .. .... .... .. ......... ................................................................... 361

Reader Response.............................................................................................................................................................................. 362

PIC18CXX8 Product Identification System ........................................................................................................................................363

DS30475A-page 6 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers wit h the best docume ntation possible to ensure successf ul use of your Mic rochip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined

and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department

via E-mail at docerrors@mail.m ic rochip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-

4150. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

2000 Microchip Technology Inc. Advanced Information DS30475A-page 7

PIC18CXX8

NOTES:

DS30475A-page 8 Advanced Information 2000 Microchip Technology Inc.

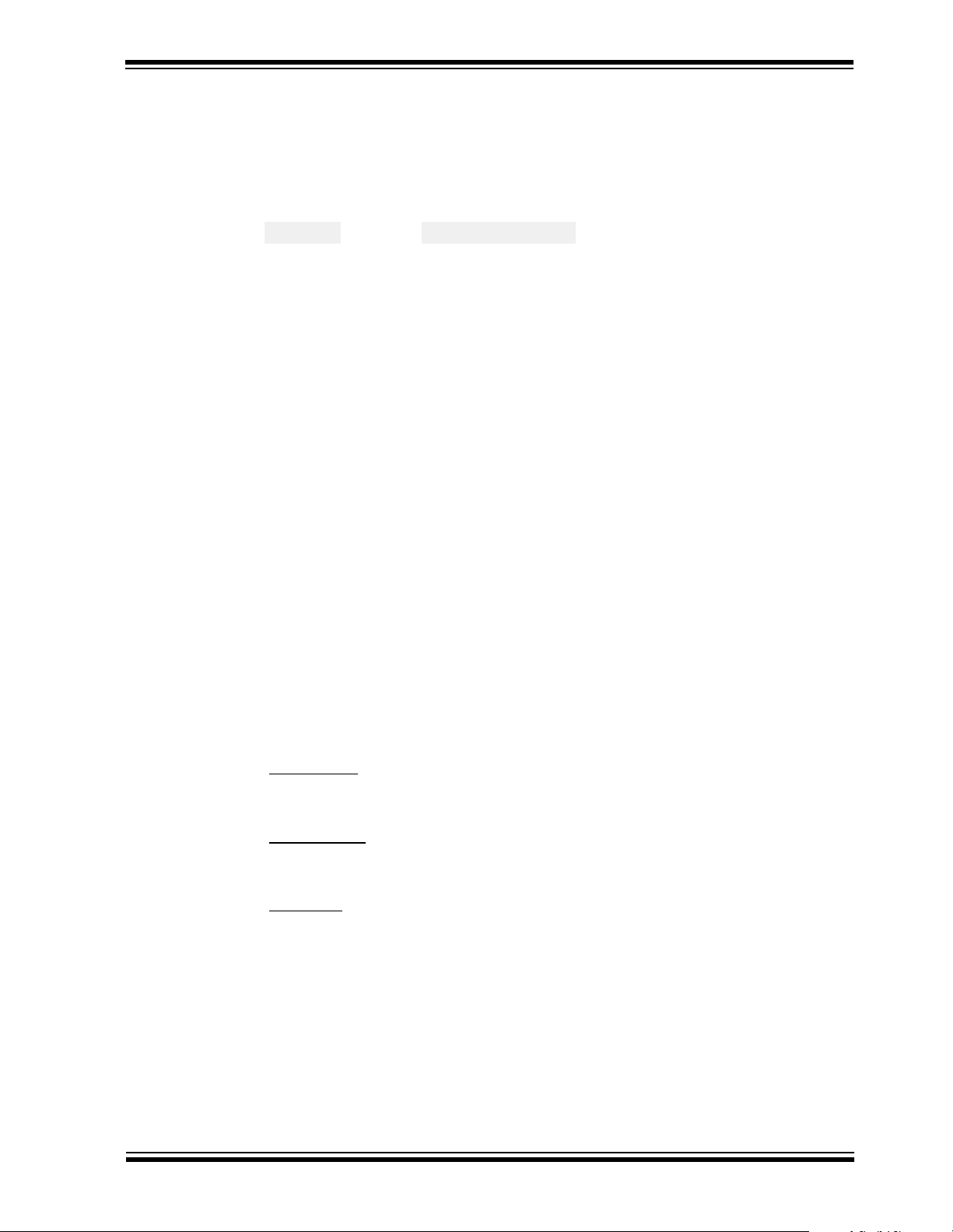

PIC18CXX8

1.0 DEVICE OVERVIEW

This document contains device specific information for

the following three devices:

1. PIC18C658

2. PIC18C858

The PIC18C658 is ava ilable in 64- pin TQFP and 6 8-pin

PLCC packages. The PIC18C858 is available in 80-pin

TQFP and 84-pin PLCC packages.

An overview of features is shown in Table 1-1.

The following two figures are device block diagrams

sorted by pin count; 64/68-pin for Figure 1-1 and

80/84-pin for Figure 1-2. The 64/68-pin and 80/84-pin

pinouts are listed in Table 1-2.

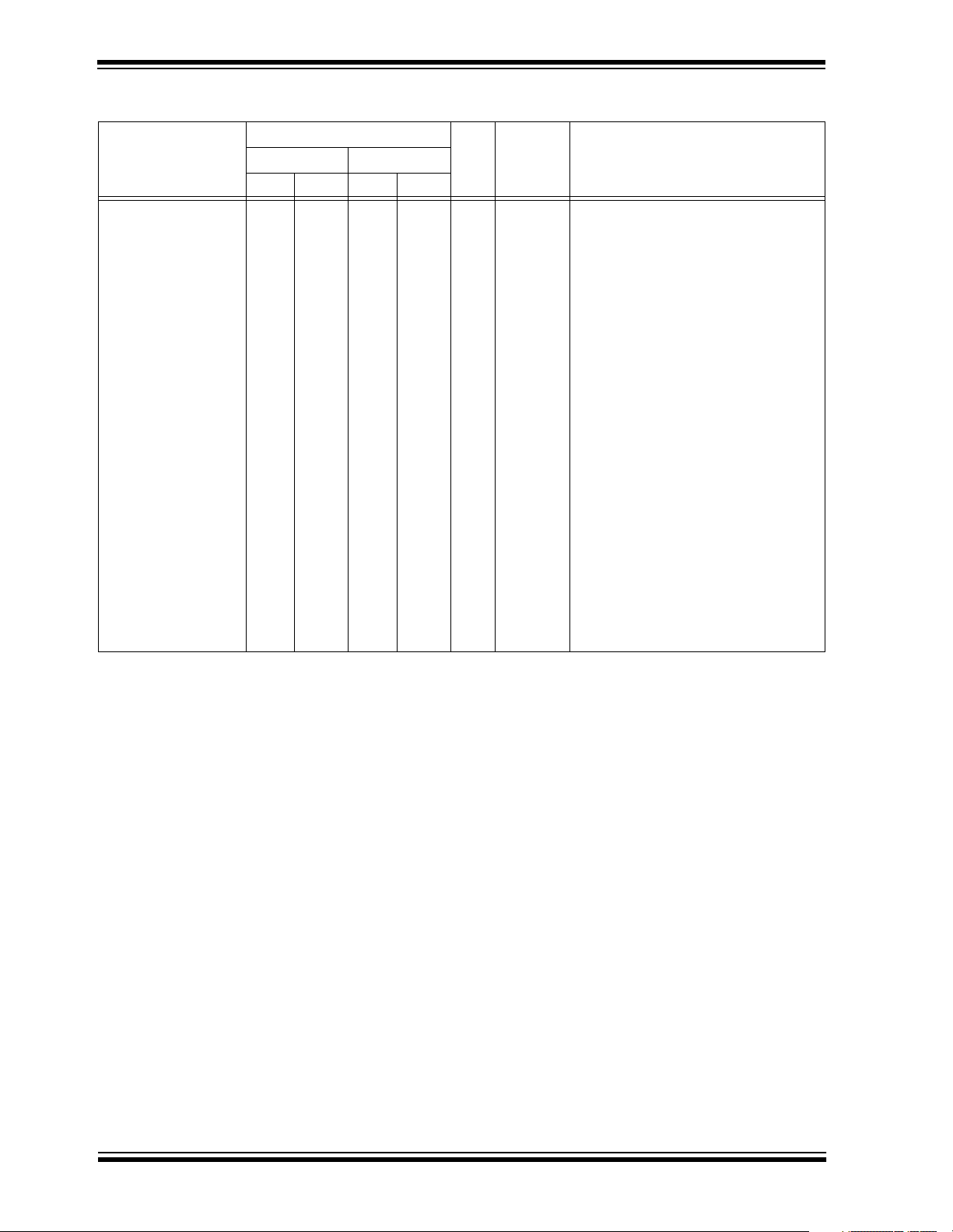

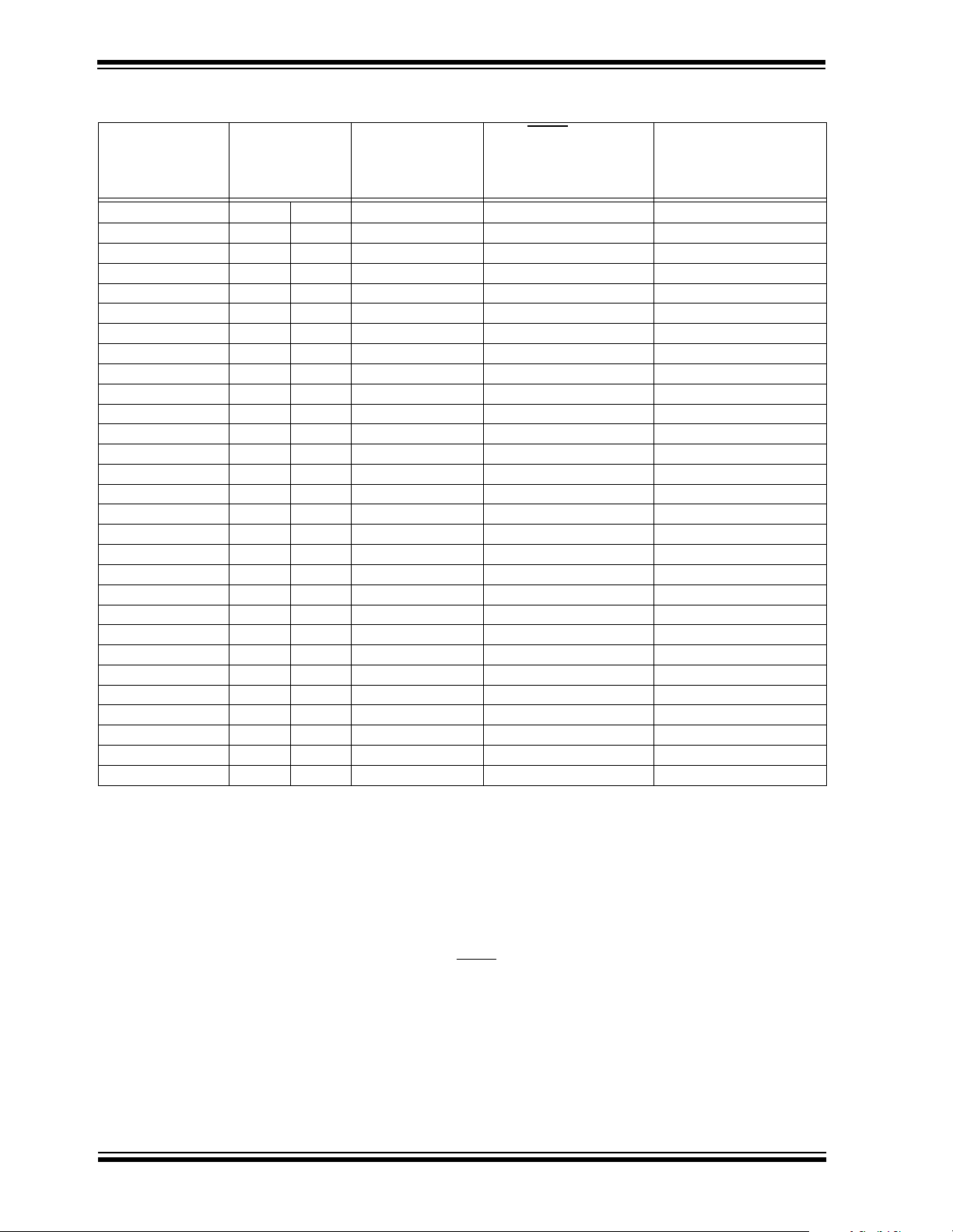

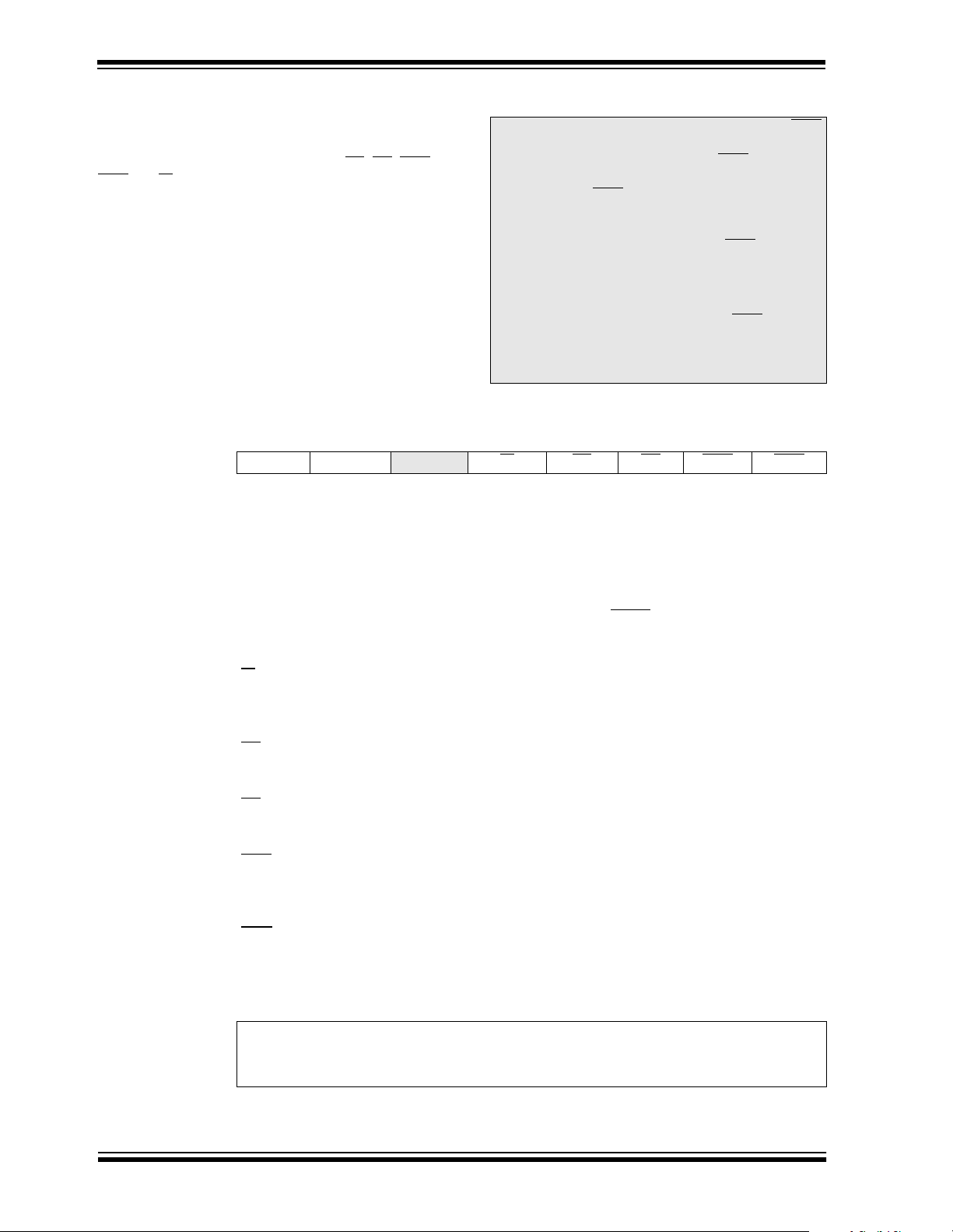

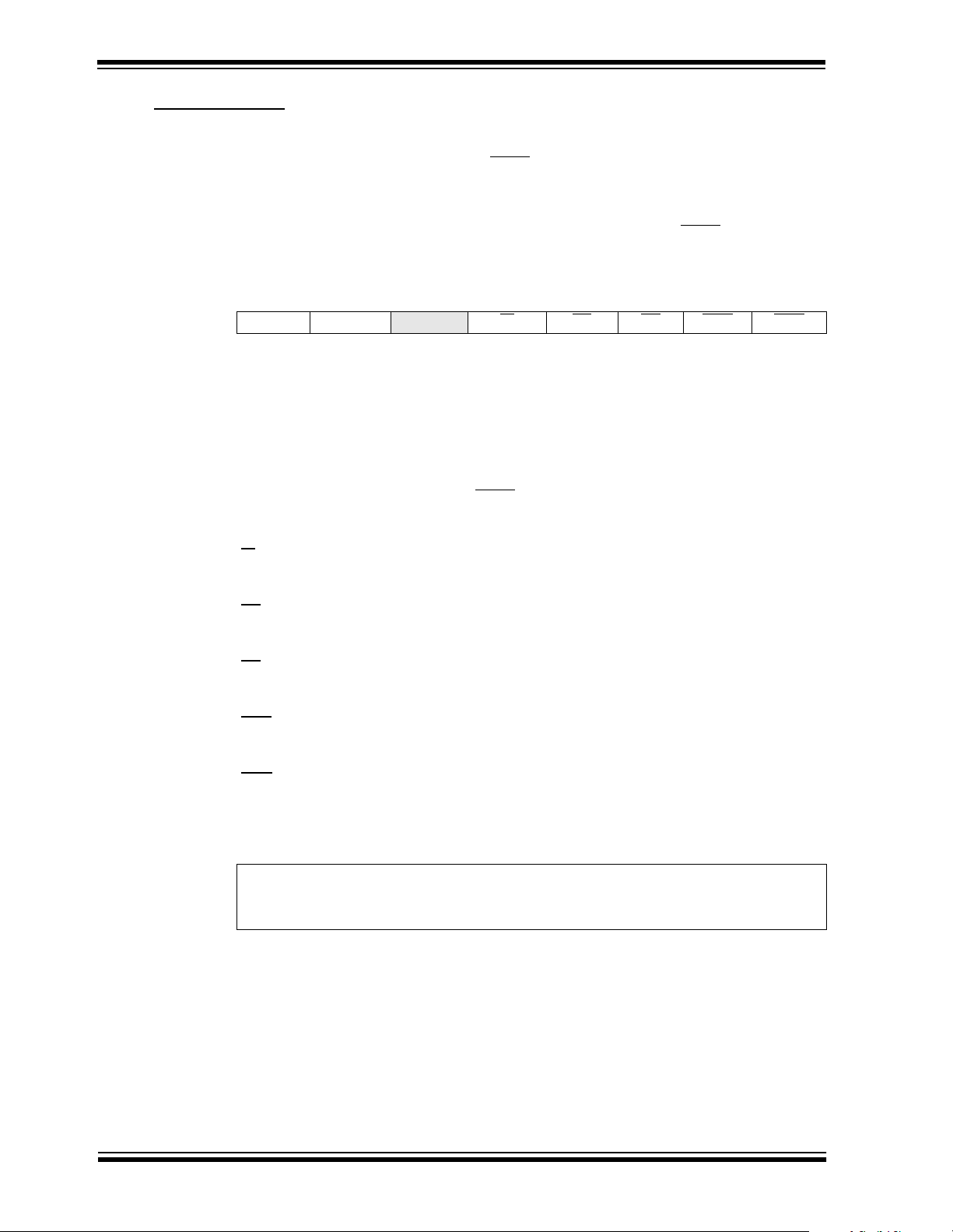

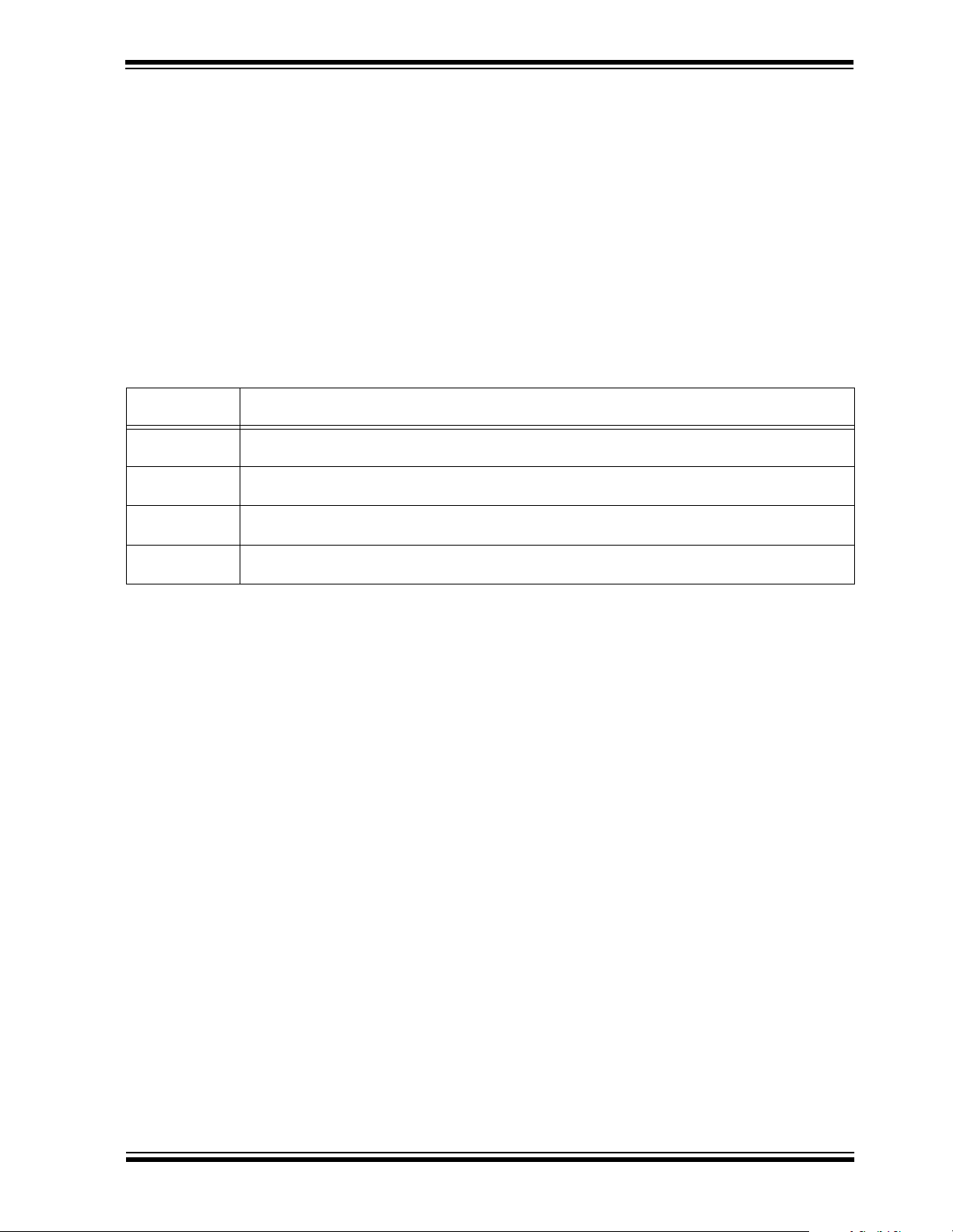

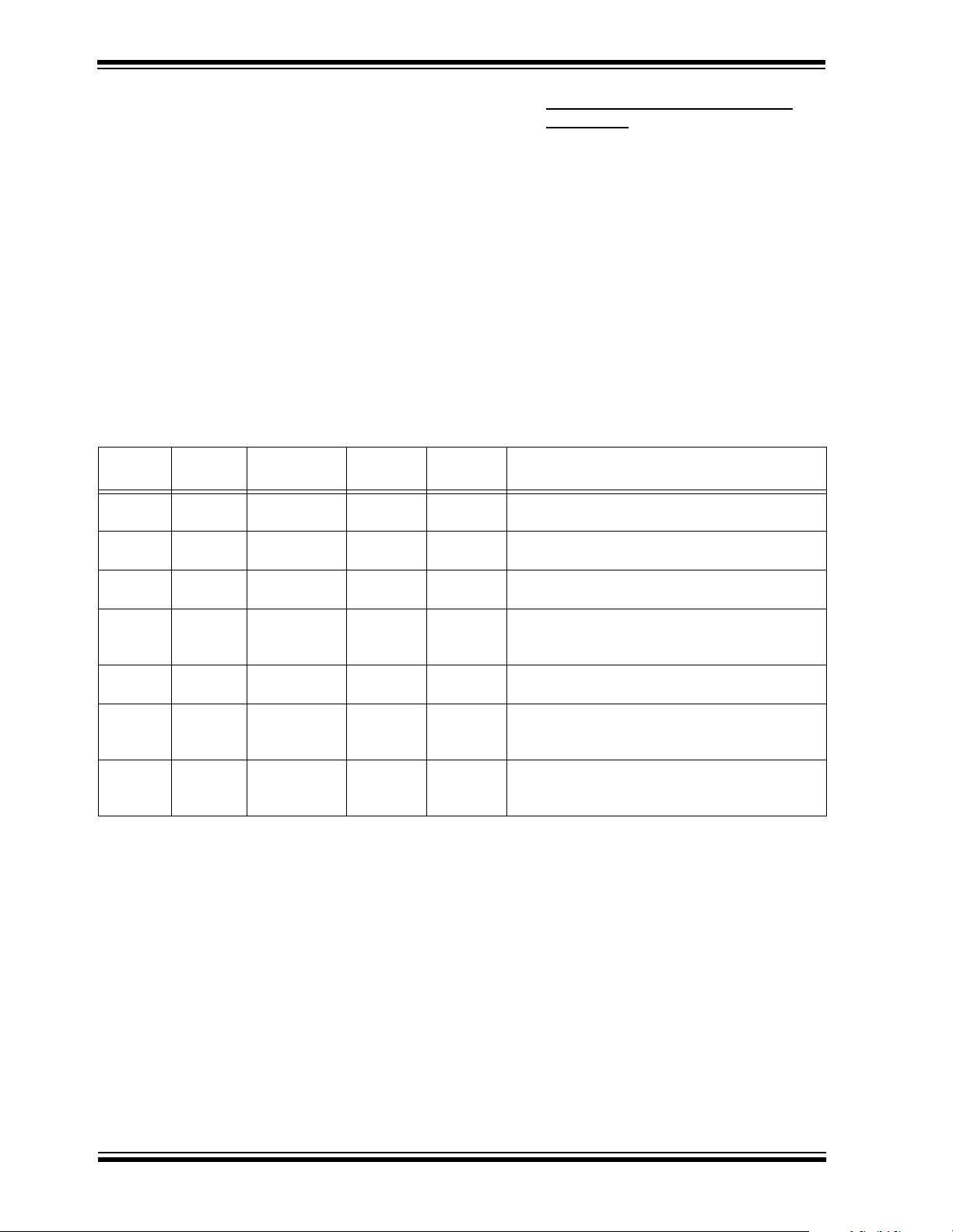

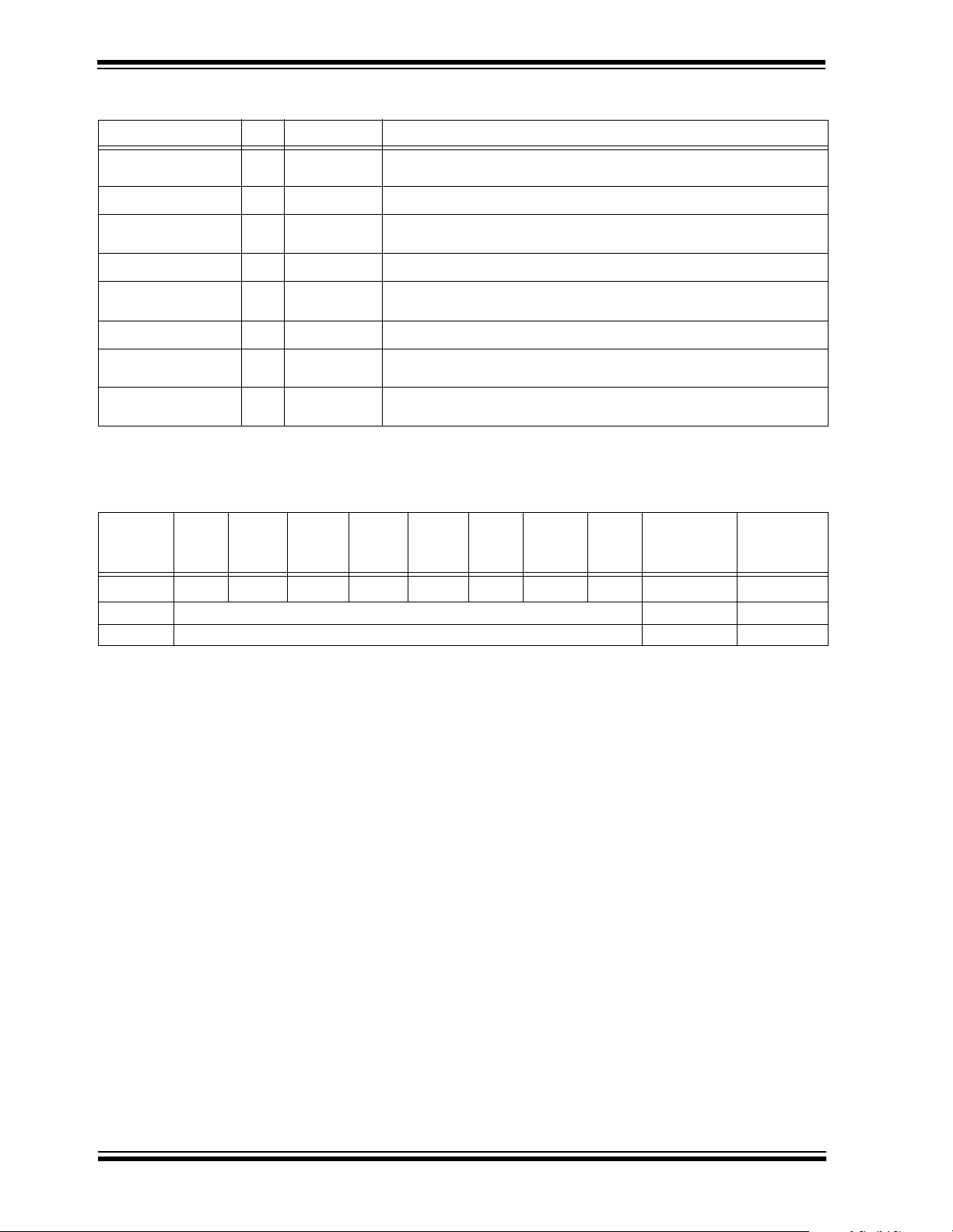

TABLE 1-1: DEVICE FEATURES

Features PIC18C658 PIC18C858

Operating Frequency DC - 40 MHz DC - 40 MHz

Bytes 32 K 32 K

Program Memory Internal

Data Memory (Bytes) 1536 1536

Interrupt sources 21 21

I/O Ports Ports A – G Ports A – H, J, K

Timers 4 4

Capture/Compare/PWM modules 2 2

Serial Communications

Parallel Communications PSP PSP

10-bit Analog-to-Digital Module 12 input channels 16 input channels

Analog Comparators 2 2

RESETS (and Delays)

Programmable Low Voltage Detect Yes Yes

Programmable Brown-out Reset Yes Yes

CAN Module Y es Yes

In-Circuit Serial Programming (ICSP™)YesYes

Instruction Set 75 Instructions 75 Instructions

Packages

# of Single word

Instructions

16384 16384

MSSP, CAN

Addressable USART

POR, BOR,

RESET Instruction, Stack Ful l,

Stack Underflow

(PWRT, OST)

64-pin TQFP

68-pin CERQUAD

(Windowed)

68-pin PLCC

MSSP, CAN

Addressable USART

POR, BOR,

RESET Instruction, Stack Full,

Stack Underflow

(PWRT, OST)

80-pin TQFP

84-pin CERQUAD

(Windowed)

84-pin PLCC

2000 Microchip Technology Inc. Advanced Information DS30475A-page 9

PIC18CXX8

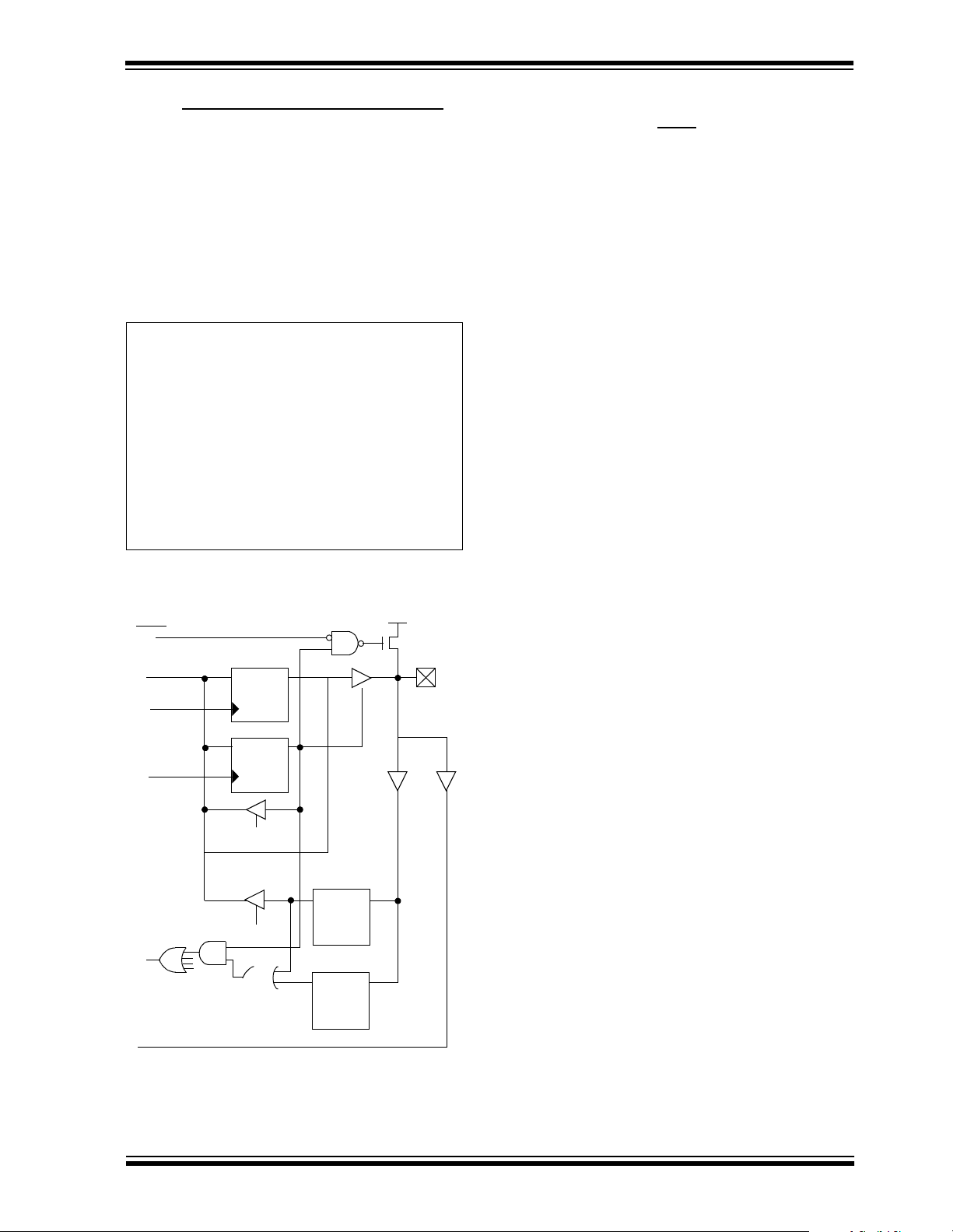

FIGURE 1-1: PIC18C658 BLOCK DIAGRAM

PORTA

PORTB

RA0/AN0

RA1/AN1

RA2/AN2/VREFRA3/AN3/VREF+

RA4/T0CKI

RA5/AN4/SS

RB0/INT0

RB7:RB4

/LV DIN

OSC2/CLKO

OSC1/CLKI

Instruction

Decode &

Control

Timing

Generation

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

MCLR

VDD, VSS

PORTC

RC0/T1OSO/T13CKI

RC1/T1OSI

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

BOR

Comparator

Timer1

Timer2

Synchronous

Serial Port

USART

CAN Module

DS30475A-page 10 Advanced Information 2000 Microchip Technology Inc.

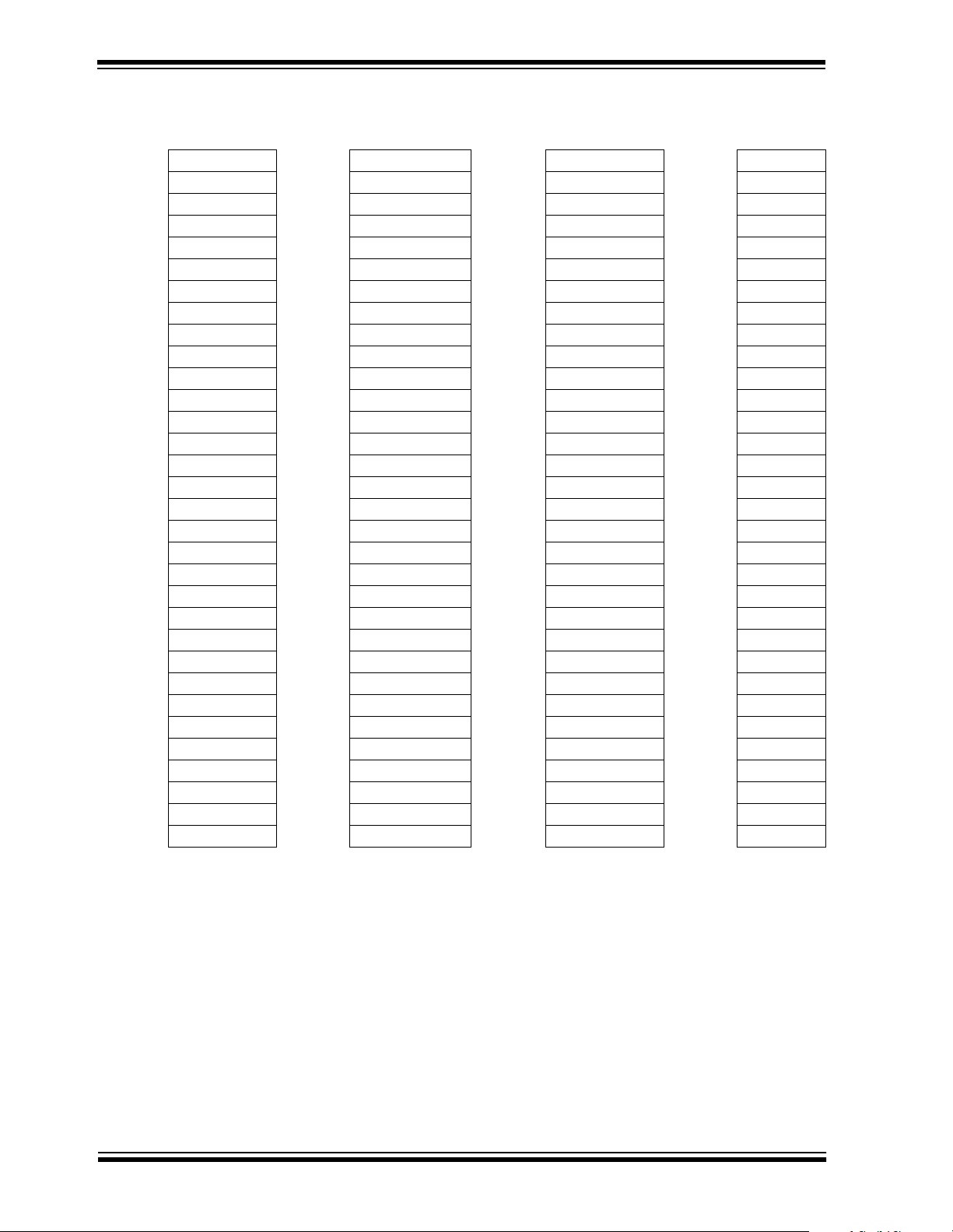

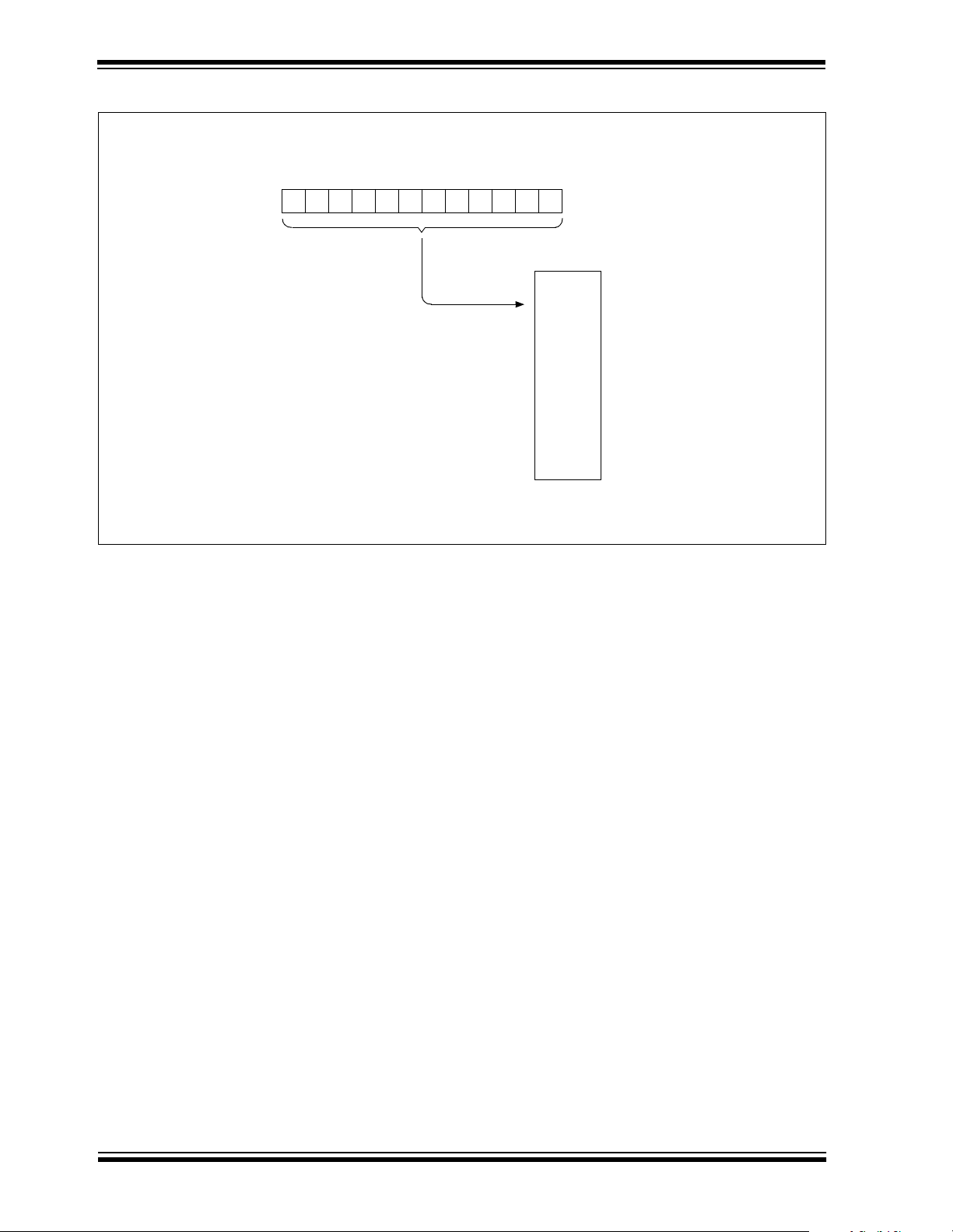

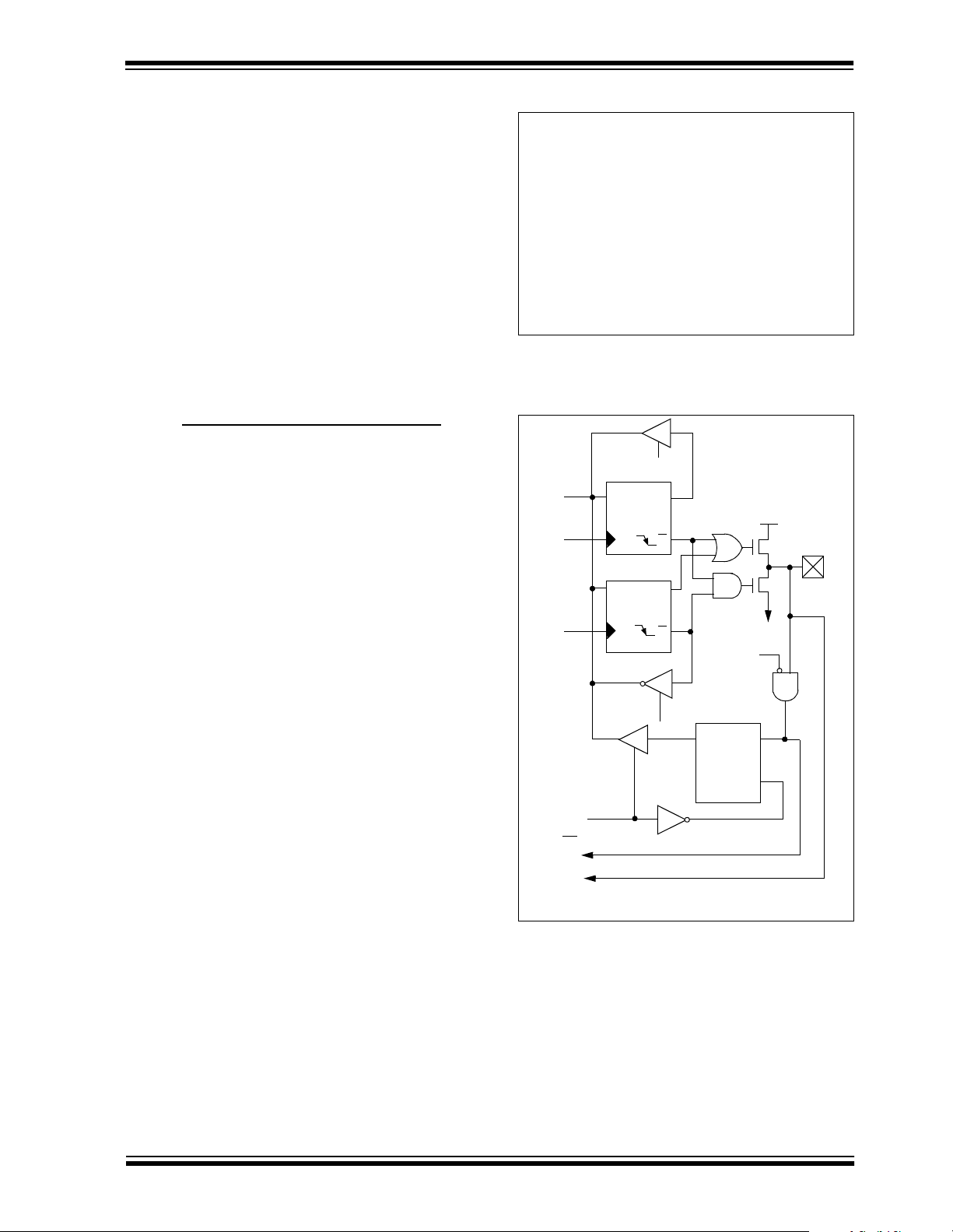

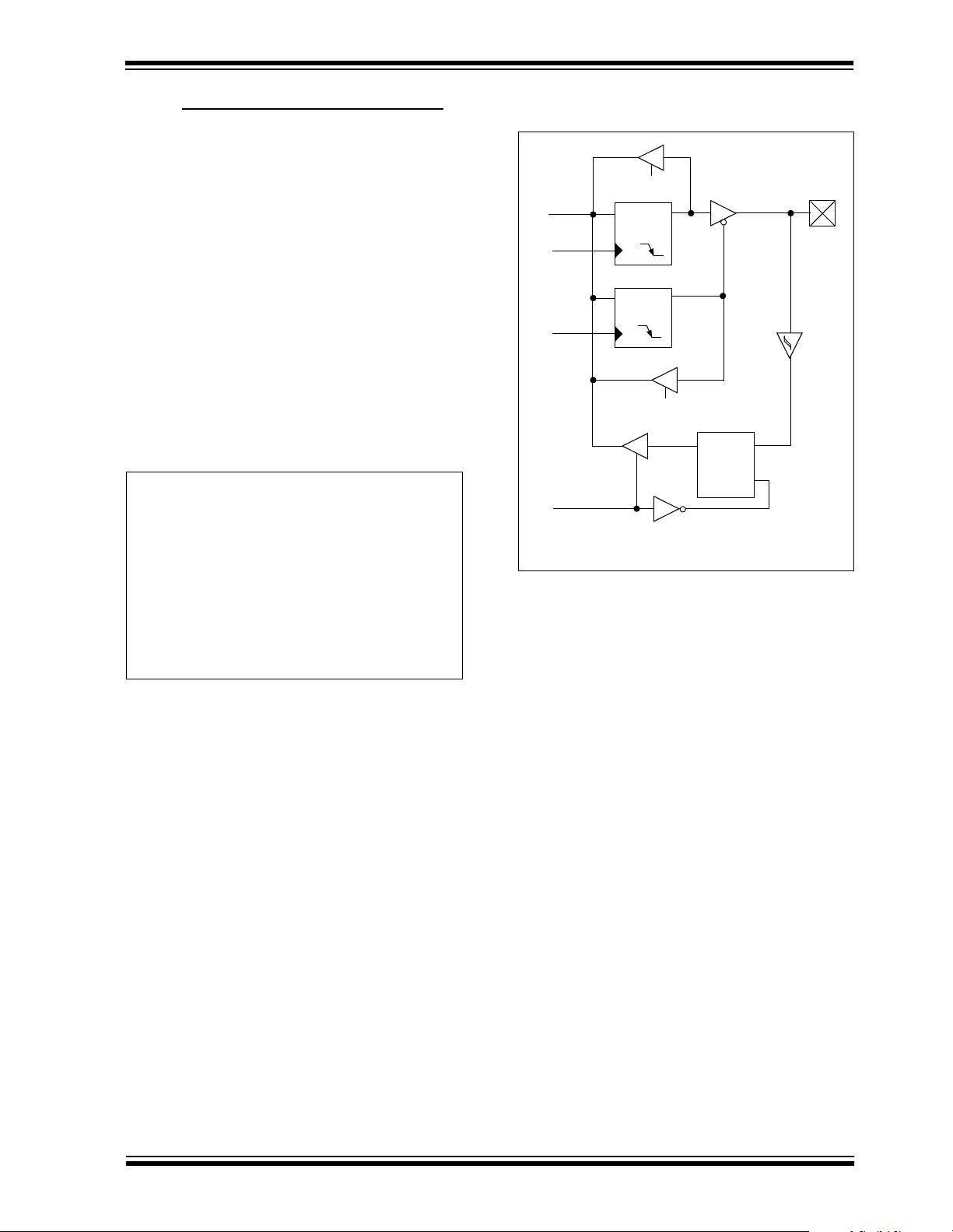

FIGURE 1-2: PIC18C858 BLOCK DIAGRAM

8

PCLATH

PCH PCL

Program Counter

31 Level Stack

4

BSR

Data Latch

Data RAM

( 1.5 K )

Address Latc h

12

Address<12>

12 4

Bank0, F

FSR0

FSR1

FSR2

PIC18CXX8

PORTA

RA0/AN0

RA1/AN1

RA2/AN2/VREFRA3/AN3/VREF+

RA4/T0CKI

RA5/AN4/SS

PORTB

RB0/INT0

RB1/INT1

RB7:RB4

/LV DIN

OSC2/CLKO

OSC1/CLKI

Instruction

Decode &

Control

Timing

Generation

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

MCLR

VDD, VSS

Decode

inc/dec

logic

PRODLPRODH

8 x 8 Multiply

WREG

PORTC

RC0/T1OSO/T13CKI

RC1/T1OSI

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

BOR

Comparator

Timer1

Timer2

Synchronous

Serial Port

USART

10-bit

ADC

CAN Module

2000 Microchip Technology Inc. Advanced Information DS30475A-page 11

PIC18CXX8

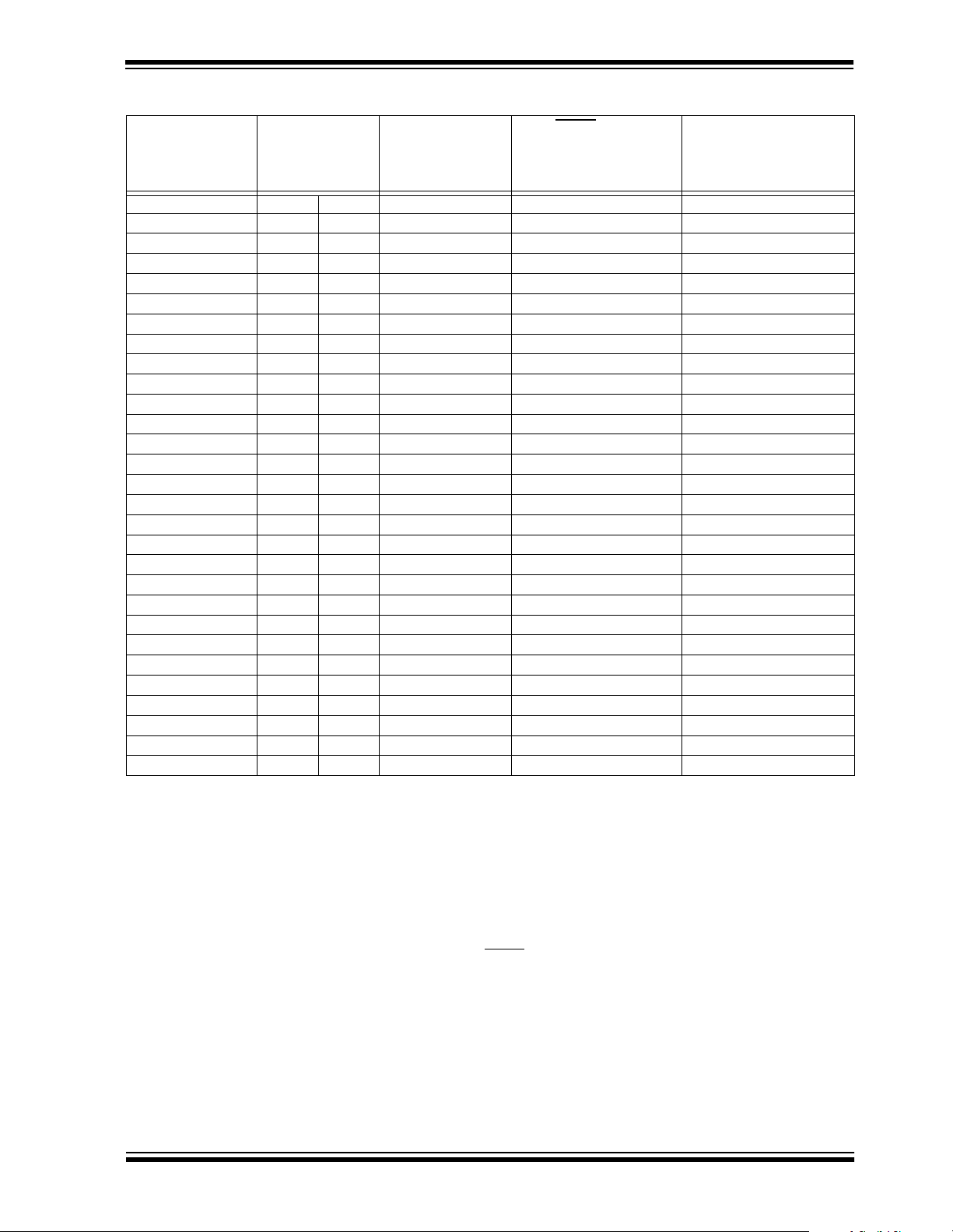

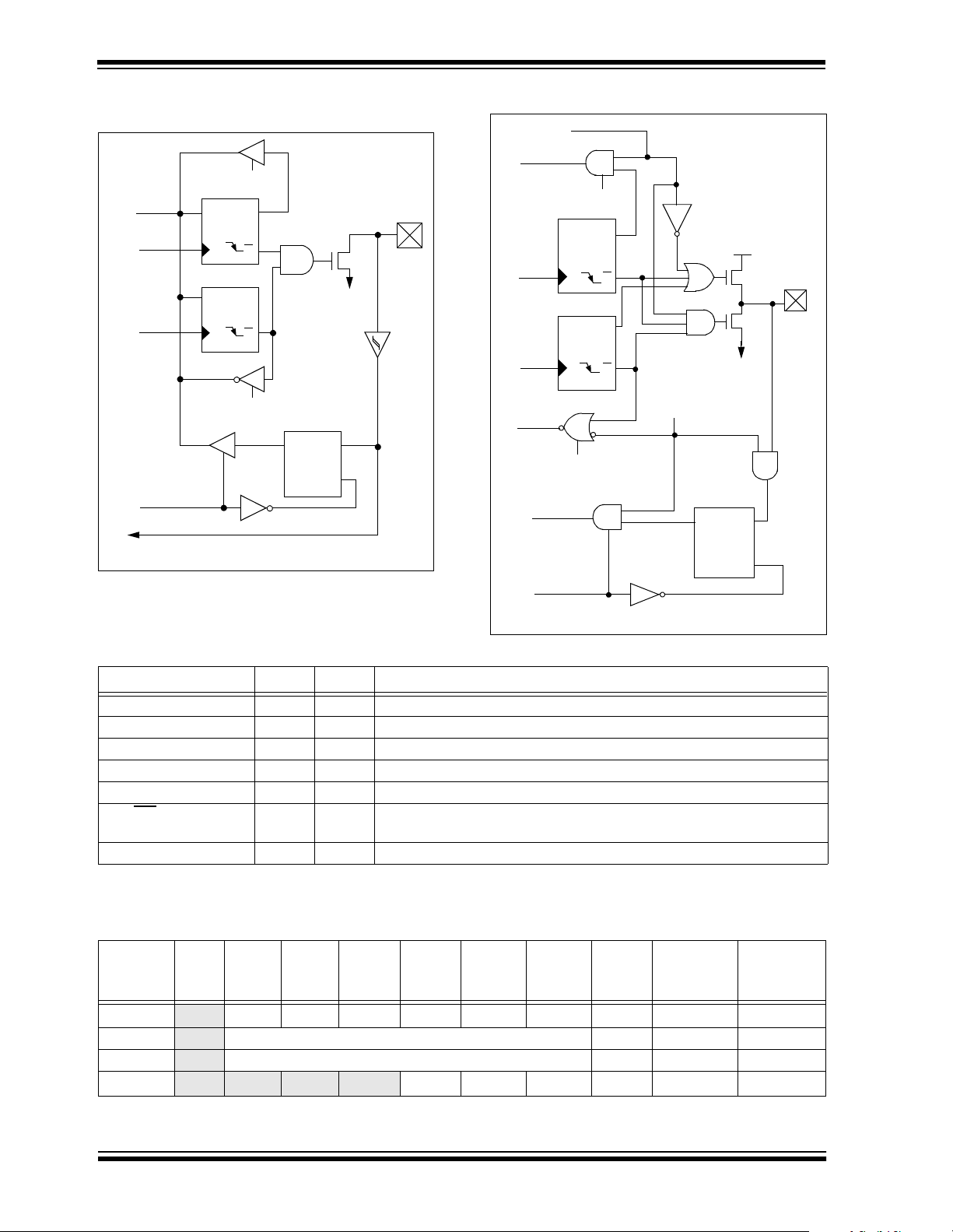

TABLE 1-2: PINOUT I/O DESCRIPTIONS

Pin Number

Pin Name

MCLR

/VPP

MCLR

VPP

NC — 1, 18,

OSC1/CLKI

OSC1

CLKI

OSC2/CLKO/RA6

OSC2

CLKO

RA6

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to VDD)

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

716920

— 1, 22,

35, 52

39 50 49 62

40 51 50 63

43, 64

Pin

Type

I/O

Buffer

Type

I

P

——These pins should be left

IICMOS/ST

O

O

ST Master clear (RESET) input. This pin is

an active low RESET to th e device.

Programming voltage i nput

unconnected

Oscillator crystal input or external

clock source input. ST buffer when

configured in RC mode. O th er w i se

CMOS.

CMOS

—

—

TTL

External clock source input. Always

associated with pin function OSC1

(see OSC1/CLKI, OSC2/CLKO pins).

Oscillator crystal output.

Connects to crystal or resonator in

Crystal Oscillator mode.

In RC mode, OSC2 pin outputs CLKO,

which has 1/4 the freque ncy of OSC1

and denotes the instruct i on cycle rate

General purpose I/O pin

DS30475A-page 12 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RA0/AN0

RA0

AN0

RA1/AN1

RA1

AN1

RA2/AN2/V

RA3/AN3/V

RA4/T0CKI

RA5/AN4/SS

RA6 See the OSC2/CLKO/RA6 pin

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

REF-

RA2

AN2

V

REF-

REF+

RA3

AN3

REF+

V

RA4

T0CKI

/LVDIN

RA5

AN4

SS

LVDIN

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

24 34 30 42

23 33 29 41

22 32 28 40

21 31 27 39

28 39 34 47

27 38 33 46

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTA is a bi-directional I/O port

TTL

I

Analog

TTL

I

Analog

TTL

I

Analog

I

Analog

TTL

I

Analog

I

Analog

ST/OD

I

I

I

I

ST

TTL

Analog

ST

Analog

Digital I/O

Analog input 0

Digital I/O

Analog input 1

Digital I/O

Analog input 2

A/D reference voltage (L ow) in put

Digital I/O

Analog input 3

A/D reference voltage (High) input

Digital I/O – Open drain when

configured as output

Timer0 external clock input

Digital I/O

Analog input 4

SPI slave select input

Low voltage detect input

DD)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 13

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RB0/INT0

RB0

INT0

RB1/INT1

RB1

INT1

RB2/INT2

RB2

INT2

RB3/INT3

RB3

INT3

RB4 44 56 54 68 I/O TTL Digital I/O

RB5 43 55 53 67 I/O TTL Digital I/O

RB6 42 54 52 66 I/O

RB7 37 48 47 60 I/O

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

48 60 58 72

47 59 57 71

46 58 56 70

45 57 55 69

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTB is a bi-directional I/O p ort.

PORTB can be software

programmed for internal weak pull-ups on

all inputs.

TTL

I

I

I

I

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

Digital I/O

External interrupt 0

Digital I/O

External interrupt 1

Digital I/O

External interrupt 2

Digital I/O

External interrupt 3

Interrupt on change pin

Interrupt-on-chang e pi n

Digital I/O

Interrupt-on-chang e pi n

ICSP programming clock

Digital I/O

Interrupt-on-chang e pi n

ICSP programming data

DD)

DS30475A-page 14 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RC0/T1OSO/T13CKI

RC0

T1OSO

T13CKI

RC1/T1OSI

RC1

T1OSI

RC2/CCP1

RC2

CCP1

RC3/SCK/SCL

RC3

SCK

SCL

RC4/SDI/SDA

RC4

SDI

SDA

RC5/SDO

RC5

SDO

RC6/TX/CK

RC6

TX

CK

RC7/RX/DT

RC7

RX

DT

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

30 41 36 49

29 40 35 48

33 44 43 56

34 45 44 57

35 46 45 58

36 47 46 59

31 42 37 50

32 43 38 51

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTC is a bi-directional I/O port

ST

O

I

I

I

O

O

I

—

ST

ST

CMOS

ST

ST

ST

ST

ST

ST

ST

ST

ST

—

ST

—

ST

ST

ST

ST

Digital I/O

Timer1 oscillator output

Timer1/Timer3 external clock input

Digital I/O

Timer1 oscilla to r i npu t

Digital I/O

Capture1 input/Com pare1

output/PWM1 output

Digital I/O

Synchronous serial clock

input/output for SPI mode

Synchronous serial clock

input/output for I

Digital I/O

SPI data in

2

I

C data I/O

Digital I/O

SPI data out

Digital I/O

USART asynchronous transmit

USART synchronous clock

(See RX/DT)

Digital I/O

USART asynchronous receive

USART synchronous data

(See TX/CK)

2

C mode

DD)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 15

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RD0/PSP0

RD0

PSP0

RD1/PSP1

RD1

PSP1

RD2/PSP2

RD2

PSP2

RD3/PSP3

RD3

PSP3

RD4/PSP4

RD4

PSP4

RD5/PSP5

RD5

PSP5

RD6/PSP6

RD6

PSP6

RD7/PSP7

RD7

PSP7

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

583723

55 67 69 83

54 66 68 82

53 65 67 81

52 64 66 80

51 63 65 79

50 62 64 78

49 61 63 77

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

TTL

PORTD is a bi-directional I/O port. These

pins have TTL input buffers when external

memory is enabled.

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

Digital I/O

Parallel slave port data

DD)

DS30475A-page 16 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RE0/RD

RE0

R

D

RE1/WR

RE1

W

R

RE2/CS

RE2

S

C

RE3 63 8 77 8 I/O ST Digital I/O

RE4 62 7 76 7 I/O ST Digital I/O

RE5 61 6 75 6 I/O ST Digital I/O

RE6 60 5 74 5 I/O ST Digital I/O

RE7/CCP2

RE7

CCP2

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

211415

110314

649789

594734

Pin

Type

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTE is a bi-directional I/O p ort

ST

I

I

I

TTL

ST

TTL

ST

TTL

ST

ST

Digital I/O

Read control for parall el sl ave port

(See WR

Digital I/O

Write co nt rol for parallel slave port

(See CS

Digital I/O

Chip select control for parallel slave

port (See RD

Digital I/O

Capture2 input, Comp ar e2 output,

PWM2 output

and CS pins)

and RD pins)

and WR)

DD)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 17

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RF0/AN5

RF0

AN5

RF1/AN6/C2OUT

RF1

AN6

C2OUT

RF2/AN7/C1OUT

RF2

AN7

C1OUT

RF3/AN8

RF1

AN8

RF4/AN9

RF1

AN9

RF5/AN10/CV

RF1

AN10

CVREF

RF6/AN11

RF6

AN11

RF7 11 21 13 25 I/O ST Digital I/O

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

REF

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

18 28 24 36

17 27 23 35

16 26 18 30

15 25 17 29

14 24 16 28

13 23 15 27

12 22 14 26

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTF is a bi-directional I/O port

ST

I

Analog

ST

I

Analog

O

I

O

I

I

I

O

I

ST

ST

Analog

ST

ST

Analog

ST

Analog

ST

Analog

Analog

ST

Analog

Digital I/O

Analog input 5

Digital I/O

Analog input 6

Comparator 2 output

Digital I/O

Analog input 7

Comparator 1 output

Digital I/O

Analog input 8

Digital I/O

Analog input 9

Digital I/O

Analog input 10

Comparator V

Digital I/O

Analog input 11

REF output

DD)

DS30475A-page 18 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RG0/CANTX1

RG0

CANTX1

RG1/CANTX2

RG1

CANTX2

RG2/CANRX

RG2

CANRX

RG3 6 15 8 19 I/O ST Digital I/O

RG4 8 17 10 21 I/O ST Digital I/O

RH0 ——79 10 I/O ST Digital I/O

RH1 ——80 11 I/O ST Digital I/O

RH2 —— 1 12 I/O ST Digital I/O

RH3 —— 2 13 I/O ST Digital I/O

RH4/AN12

RH4

AN12

RH5/AN13

RH5

AN13

RH6/AN14

RH6

AN14

RH7/AN15

RH7

AN15

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

312516

413617

514718

——22 34

——21 33

——20 32

——19 31

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

OSTCAN Bus

OSTCAN Bus

ISTCAN Bus

ST

I

Analog

ST

I

Analog

ST

I

Analog

ST

I

Analog

PORTG is a bi-directional I/O port

Digital I/O

CAN bus output

Digital I/O

Complimentary CAN bus output

or CAN bus bit time cloc k

Digital I/O

CAN bus input

PORTH is a bi-directional I/O port.

Digital I/O

Analog input 12

Digital I/O

Analog input 13

Digital I/O

Analog input 14

Digital I/O

Analog input 15

DD)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 19

PIC18CXX8

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

RJ0

RJ0

RJ0

RJ1

RJ1

RJ1

RJ2

RJ2

RJ2

RJ3

RJ3

RJ3

RK0 ——39 52 I/O ST Digital I/O

RK1 ——40 53 I/O ST Digital I/O

RK2 ——41 54 I/O ST Digital I/O

RK3 ——42 55 I/O ST Digital I/O

V

SS 9, 25,

DD 10, 26,

V

VSS 20 30 26 38 P — Gro und reference for analog mod ul es

A

AVDD 19 29 25 37 P — Positive supply for analog modules

Legend: TTL = TTL com pat ibl e i nput CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

PIC18C658 PIC18C85 8

TQFP PLCC TQFP PLCC Description

—

—

—

—

—

—

—

—

41, 56

38, 57

—

—

—

—

—

—

—

—

19, 36,

53, 68

2, 20,

37, 49

62

—

61

—

60

—

59

—

11, 31,

51, 70

12, 32,

48, 71

23, 44,

65, 84

2, 24,

45, 61

Pin

Type

76

—

I/O ST Digital I/O

75

—

I/O ST Digital I/O

74

—

I/O ST Digital I/O

73

—

I/O ST Digital I/O

Buffer

Type

PORTJ is a bi-directional I/O port

PORTK is a bi-directional I/O p ort

P — Ground re fe re nce for logic and I/O pins

P — Positive supply for logic and I/O pins

DD)

DS30475A-page 20 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

2.0 OSCILLATOR CONFIGURATIONS

2.1 Oscillator Types

The PIC18CXX8 can be operated in one of eight oscillator modes, programmable by three configuration bits

(FOSC2, FOSC1, and FOSC0).

1. LP Low Power Crystal

2. XT Crystal/Resonator

3. HS High Speed Crystal/Resonator

4. HS4 High Speed Crystal/Resonator with

PLL enabled

5. RC External Resistor/Capac ito r

6. R CIO External Resisto r/Capac itor wi th I/O

pin enabled

7. EC External Clock

8. ECIO External Clock with I/O pin enabled

2.2 Crystal Oscillator/Ceramic

Resonators

In XT, LP, HS or HS4 (PLL) oscillator modes, a crystal

or ceramic resonator is connected to the OSC1 and

OSC2 pins to establish oscillation. Figure2-1 shows

the pin connections . An external cloc k source may also

be connected to the OSC1 pin, as shown in Figure 2-3

and Figure 2-4.

The PIC18CXX8 oscillat or desi gn requ ires th e use o f a

parallel cut crystal.

Note: Use of a series cut crystal may give a fre-

quency out of the crystal manufacturer’s

specifications.

FIGURE 2-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

(1)

C1

(1)

C2

Note 1: See Table 2-1 and Table 2-2 for recom-

2: A series resisto r (RS) may be required

3: R

OSC1

XTAL

(2)

RS

OSC2

mended values of C1 and C2.

for AT strip cut crystals.

F varies with the crystal chosen.

RF

(3)

SLEEP

PIC18CXX8

To

internal

logic

2000 Microchip Technology Inc. Advanced Information DS30475A-page 21

PIC18CXX8

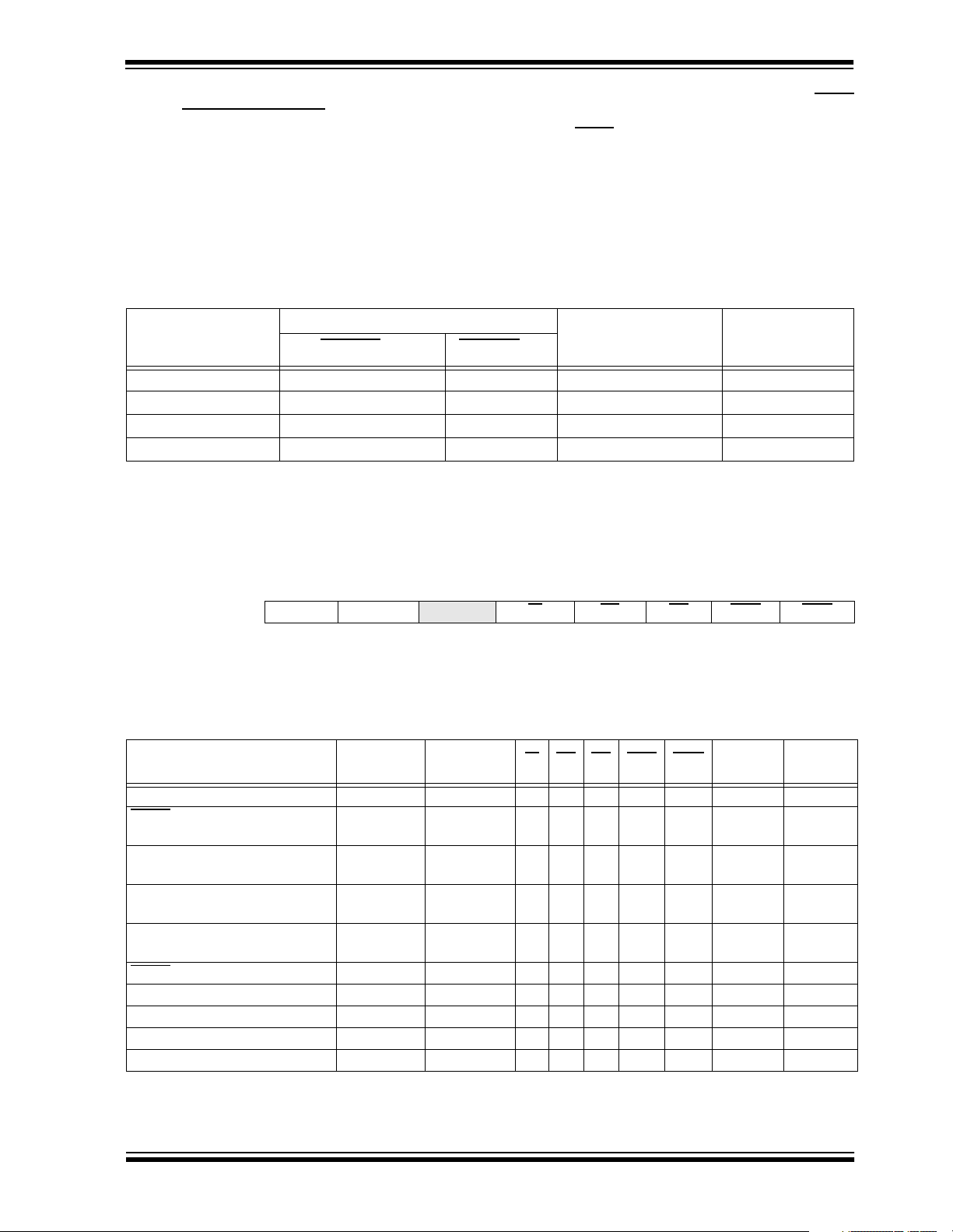

TABLE 2-1: CERAMIC RESONATORS

Ranges Tested:

Mode Freq OSC1 OSC2

XT 455 kHz

2.0 MHz

4.0 MHz

HS 8.0 MHz

16.0 MHz

20.0 MHz

25.0 MHz

HS+PLL 4.0 MHz

8.0 MHz

10.0 MHz

These values are for design guidance only. See

notes on this page.

68 - 100 pF

15 - 68 pF

15 - 68 pF

10 - 68 pF

10 - 22 pF

TBD

TBD

TBD

10 - 68 pF

TBD

68 - 100 pF

15 - 68 pF

15 - 68 pF

10 - 68 pF

10 - 22 pF

TBD

TBD

TBD

10 - 68 pF

TBD

Resonators Used:

455 kHz Panasonic EFO-A455K04B ± 0.3%

2.0 MHz Murata Erie CSA2.00MG

4.0 MHz Murata Erie CSA4.00MG

8.0 MHz Murata Erie CSA8.00MT

16.0 MHz Murata Erie CSA16.00MX

All resonators used did not have built-in capacitors.

± 0.5%

± 0.5%

± 0.5%

± 0.5%

TABLE 2-2: CAPACITOR SELECTION FOR

Osc Type

CRYSTAL OSCILLATOR

Crystal

Freq

DS30475A-page 22 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

2.3 RC Oscillator

For timing insensitive applications, the “RC” and

"RCIO" device options offer additional cost savings.

The RC oscillator frequency is a function of the supply

voltage, the resistor (R

EXT) and capacitor (CEXT) v al-

ues and the operating temperature. In addition to this,

the oscillator frequency will vary from unit to unit due

to normal process parameter variation. Furthermore,

the difference in lead frame capacitance between

package types will also affect the oscillation frequency ,

especially for low C

EXT values. The user also needs to

take into account variation due to tolerance of external

R and C components used. Figure 2-2 shows how the

R/C combination is connected.

In the RC oscillator mode, the oscillator frequency

divided by 4 is available on the OSC2 pin. This signal

may be used f or t e st pu r pos es or t o sy nc hr o n iz e ot he r

logic.

FIGURE 2-2: RC OSCILLATOR MODE

VDD

REXT

OSC1

CEXT

VSS

F

OSC/4

or I/O

Recommended values: 3 kΩ ≤ REXT ≤ 100 kΩ

OSC2/CLKO/RA6

CEXT > 20pF

Internal

clock

PIC18CXX8

2.4 External Clock Input

The EC and ECIO os c ill ato r m ode s req uire a n e xt erna l

clock source to be connected to the OSC1 pin. The

feedback device between OSC1 and OSC2 is turned

off in these mode s to save c urrent. The re is no os cill ator start-up time required after a Power-on Reset or

after a recovery from SLEEP mode.

In the EC oscillator mode, the oscillator frequency

divided by 4 is available on the OSC2 pin. This signal

may be used f or t e st pu r pos es or t o sy nc hr o n iz e ot he r

logic. Figure 2-3 shows the pin connecti ons for the EC

oscillator mode.

FIGURE 2-3: EXTERNAL CLOCK INPUT

OPERATION

(EC OSC CONFIGURATION)

Clock from

ext. system

F

OSC/4

The ECIO oscillator mode functions like the EC mode,

except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of

PORTA (RA6). Figure 2-4 shows the pin connections

for the ECIO oscillator mode.

OSC1

PIC18CXX8

OSC2

FIGURE 2-4: EXTERNAL CLOCK INPUT

OPERATION

(ECIO CONFIGURATION)

The RCIO oscillator mode functions like the RC mode,

except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of

PORTA (RA6).

Clock from

ext. system

RA6

OSC1

PIC18CXX8

I/O (OSC2)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 23

PIC18CXX8

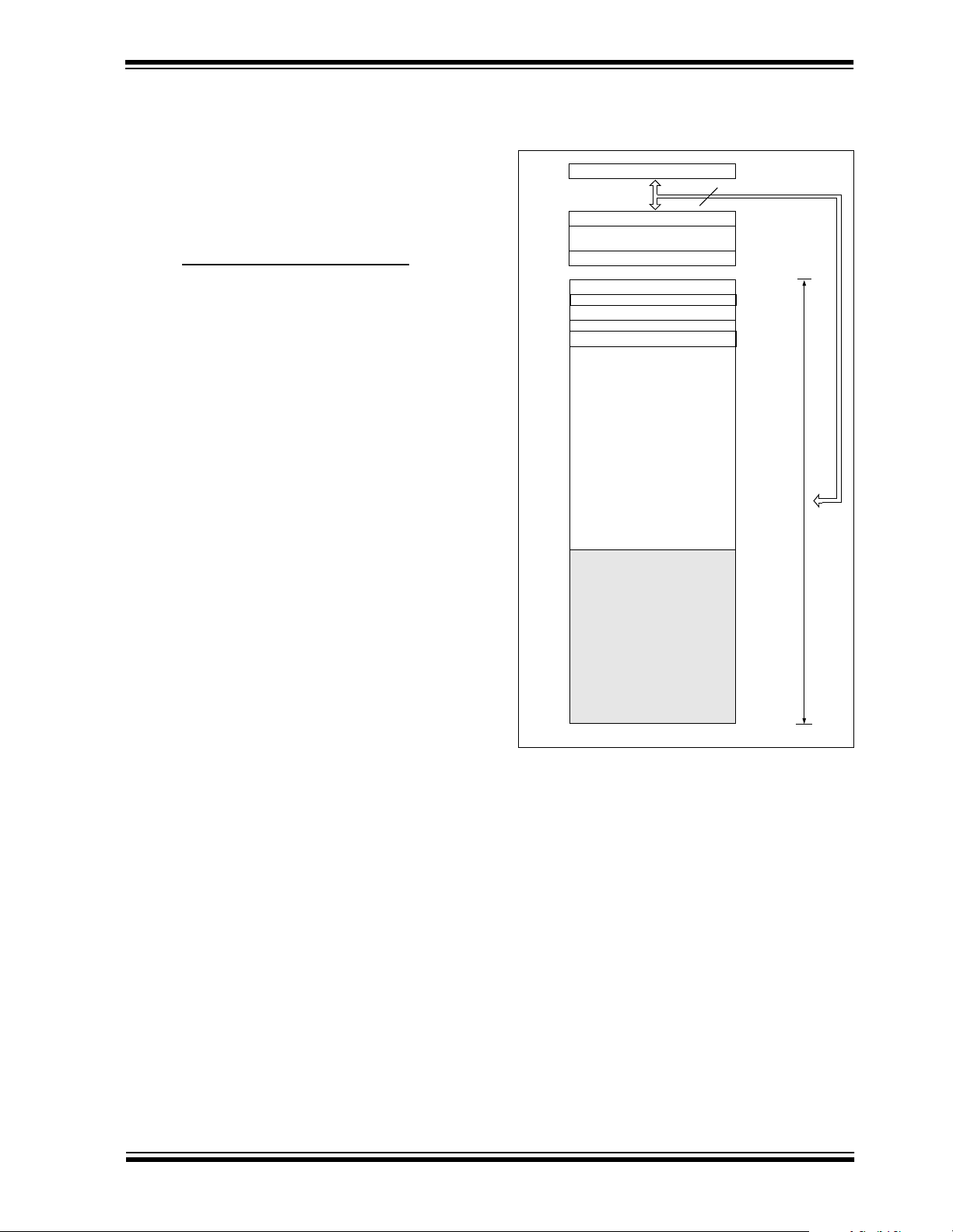

2.5 HS4 (PLL)

A Phase Locked Loop circuit is provided as a programmable option for users that want to multiply the

frequency of the i nc om ing c rys tal o sc ill ato r s ig nal b y 4.

For an input clock frequency of 10 MHz, the internal

clock frequency will be multiplied to 40 MHz. This is

useful for customers who are concerned with EMI due

to high frequency crystals.

FIGURE 2-5: PLL BLOCK DIAGRAM

OSC2

Crystal

Osc

Phase

Comparator

IN

F

FOUT

The PLL can only be enabled when the oscillator configuration bits are programmed for HS mode. If they

are programmed for any other mode, the PLL is not

enabled and the system clock will come directly from

OSC1.

The PLL is one of the modes of the FOSC2:FOSC0

configuration bits . Th e o sc ill ato r mode is specified during device programming.

A PLL lock timer is used to ensure that the PLL has

locked before device execution starts. The PLL lock

timer has a time-out referred to as T

FOSC2:FOSC0 = ‘110’

Loop

Filter

PLL.

VCO

SYSCLK

OSC1

Divide by 4

MUX

DS30475A-page 24 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

2.6 Oscillator Switching Feature

The PIC18CXX8 devices include a feature that allows

the system clock source to be switched from the main

oscillator t o an alternate lo w frequency clock s ource.

For the PIC18CXX8 devices, this alternate clock

source is the Timer1 oscillator. If a l ow freque ncy c rystal (32 kHz, for example) has been attached to the

Timer1 oscillator pins and the Timer1 oscillator has

been enabled, the device can switch to a low power

execution mode. Figure 2-6 shows a block diagram of

the system clock so urc es. The clock switching feature

is enabled by programming the Oscillator Switching

Enable (OSCSEN

CONFIG1H to a ’0’. Clock switching is disabled in an

erased device. See Section 9 for further details of the

Timer1 oscillator. See Section 22.0 for Configuration

Register details.

) bit in Configuration register

FIGURE 2-6: DEVICE CLOCK SOURCES

2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock source switching is performed under

software control. The system clock switch bit, SCS

(OSCCON register), controls the clock switching. When

the SCS bit is ’0’, the system clock source comes from

the main oscillator selected by the FOSC2:FOSC0 configuration bits. When the SCS bit is set, the system clock

source will come from the T imer1 oscilla tor . The SCS bit

is cleared on all forms of RESET.

Note: The Timer 1 oscillator mu st be enabl ed to

switch the system clock source. The

Timer1 oscillator is enabled by setting the

T1OSCEN bit in the T imer1 cont rol register

(T1CON). If the Timer1 oscillator is not

enabled, any write to the SCS bit will be

ignored (SCS bit forced cleared) and the

main oscillator will continue to be the system clock source.

REGISTER 2-1: OSCCON REGISTER

U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-1

— — — — — — — SCS

bit 7 bit 0

bit 7-1 Unimplemented: Read a s '0'

bit 0 SCS: System Clock Switch bit

OSCSEN configuration bit = ’0’ and T1OSCEN bit is set:

when

1 = Switch to Timer1 Oscillator/Clock pin

0 = Use primary Oscillator/Clock input pin

OSCSEN is clear or T1OSCEN is clear:

when

2000 Microchip Technology Inc. Advanced Information DS30475A-page 25

PIC18CXX8

2.6.2 OSCILLATOR TRANSITIONS

The PIC18CXX8 devices contain circuitry to prevent

"glitches" when switching between oscillator sources.

Essentially, the circuitry waits for eight rising edges of

the clock source that the processor is switching to.

This ensures that the new clock source is stable and

that its pulse width will not be less than the shortest

pulse width of the two clock sources.

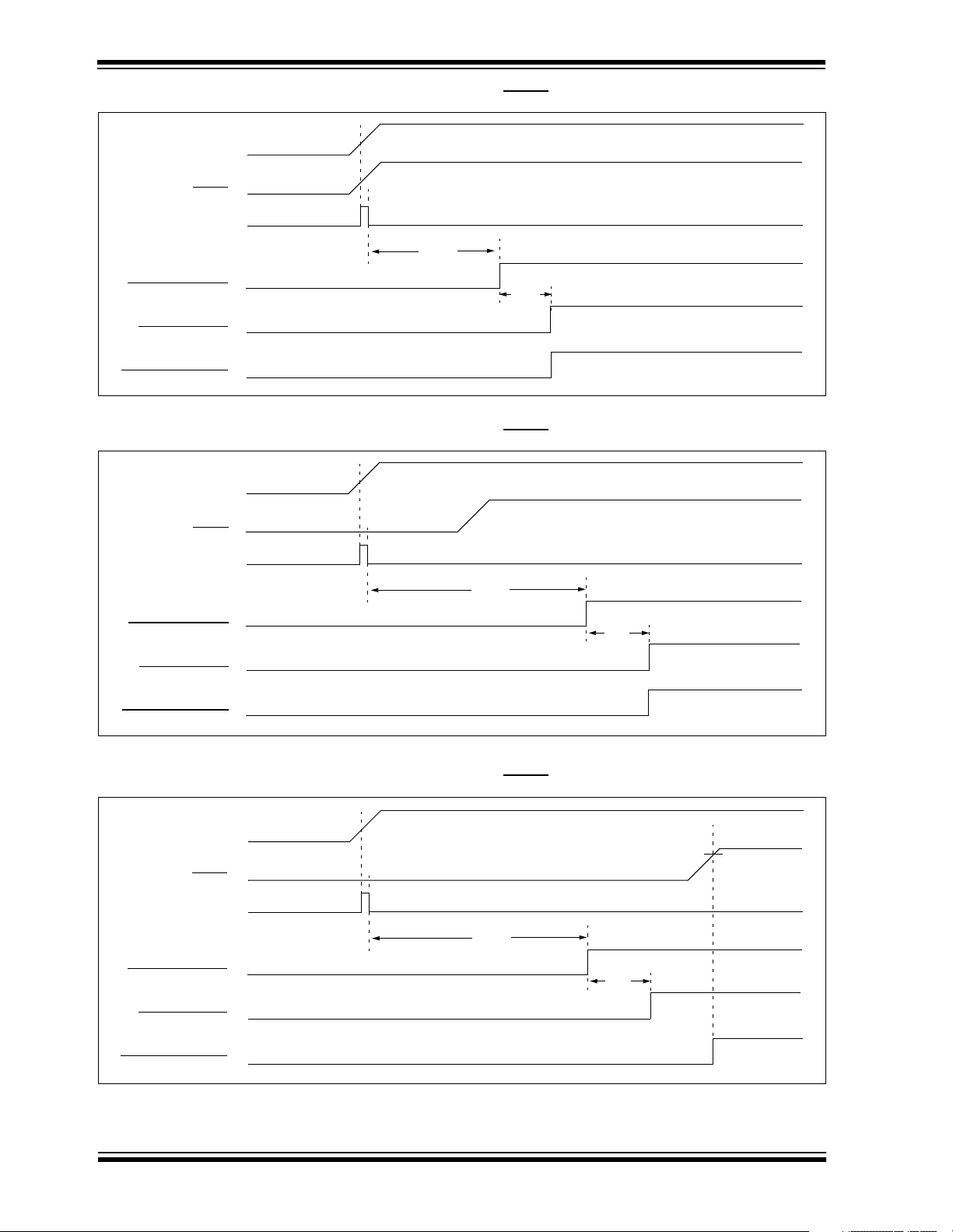

A timing diagram indicating the transition from the

main oscillator to the Timer1 oscillator is shown in

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will

depend on the mode of the main oscillator. In addition

to eight clock cycles of the main oscillator, additional

delays may take place.

If the main oscillator is configured for an external crystal (HS, XT, LP), the transition will take place after an

oscillator start-up time (T

OST) has occurred. A timing

diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes is

shown in Figure 2-8.

Figure 2-7. The Timer1 oscillator is assumed to be

running all the time. After the SCS bit is set, the processor is frozen at the next occurring Q1 cycle. After

eight synchronization cycles are counted from the

Timer1 oscillator, operation resumes. No additional

delays are required after the synchronization cycles.

FIGURE 2-7: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

Q1

T1OSI

OSC1

Internal

System

Clock

SCS

(OSCCON<0>)

Program

Counter

TOSC

Q1

TDLY

TT1P

21 345678

Tscs

PC + 2PC

Q3Q2Q1Q4Q3Q2

Q4 Q1

Q2 Q3 Q4 Q1

PC + 4

Note 1: Delay on internal system clock is eight oscillator cycles for synchronization.

FIGURE 2-8: TIMING DIAGRAM FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS,XT,LP)

Q3 Q4

T1OSI

OSC1

OSC2

Internal System

Clock

SCS

(OSCCON<0>)

Program Counter

Note 1: TOST = 1024TOSC (drawing not to scale).

PC PC + 2

Q1

TOST

TOSC

TT1P

12345678

TSCS

Q1 Q2 Q3 Q4 Q1 Q2

Q3

PC + 4

DS30475A-page 26 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

If the main oscill ator is confi gured for HS4 (PLL) m ode,

an oscillator start-up tim e (T

time-out (T

PLL) will occur. The PLL time-out is typicall y

OST) plus an additional PLL

2 ms and allows the PLL to lock to the main oscillator

frequency. A timing diagram indicating the transition

from the Timer1 oscilla tor to the main os cillator f or HS4

mode is shown in Figure 2-9.

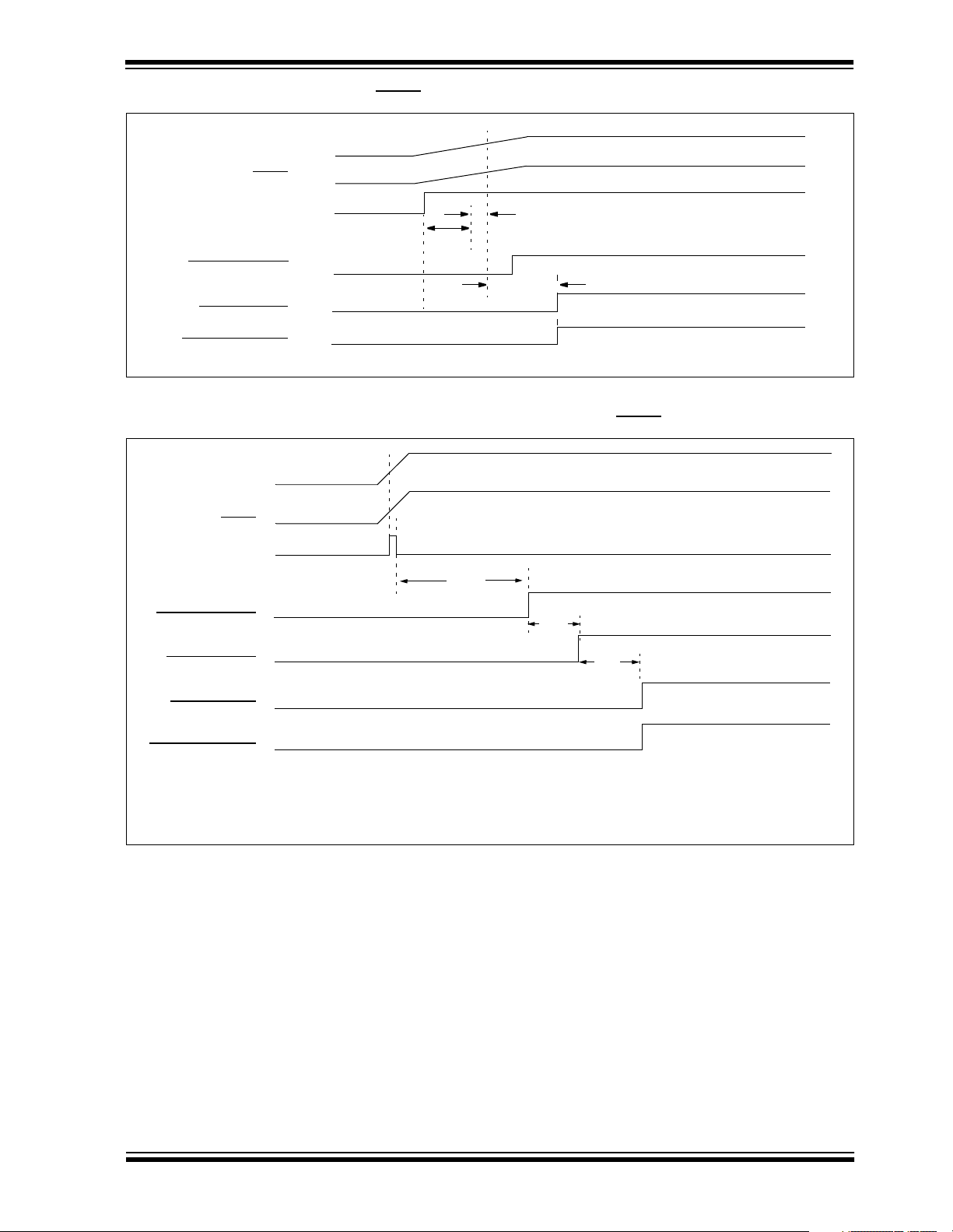

If the main oscillato r is co nfigure d in th e RC, R CIO, EC

or ECIO modes, t here i s no os ci lla tor st art-u p time-out.

Operation will resume after eight cycles of the main

oscillator have been counted. A t iming diagram ind icating the transition from the Timer1 oscillator to the main

oscillator for RC, RCIO, EC and ECIO modes is shown

in Figure 2-10.

FIGURE 2-9: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS WITH PLL)

Q4 Q1

T1OSI

OSC1

TOST

Internal System

Clock

(OSCCON<0>)

Program Counter

Note 1: TOST = 1024TOSC (drawing not to scale).

SCS

PC PC + 2

Q1 Q2 Q3 Q4 Q1 Q2

FIGURE 2-10: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

2000 Microchip Technology Inc. Advanced Information DS30475A-page 27

PIC18CXX8

2.7 Effects of SLEEP Mode on the

On-chip Oscillator

When the device executes a SLEEP instruction, the

on-chip clocks and oscillator are turned off and the

device is held at the beginning of an instruction cycle

(Q1 state). With th e o scill ato r off, the OSC1 and OSC2

signals will stop oscillating. Since all the transistor

switching currents have been removed, SLEEP mode

achieves the lowest current consumption of the device

(only leakage currents). Enabling any on-chi p feature

that will operate duri ng SLEEP will i ncrease th e current

consumed during SLEEP. The user can wake from

SLEEP through external RESET, Watchdog Timer

Reset or through an interrupt.

2.8 Power-up Delays

Power up del ays are contr olled by t wo timers, so that

no external RESET circuitry is required for most applications. The delays ensure that the device is kept in

RESET until the device powe r supply and clock ar e stable. For additional information on RESET operation,

see Section 3.0 RESET .

The first timer is the Power-up Timer (PWRT), which

optionally provides a fixed delay of T

#33) on power-up only (POR and BOR). The second

timer is the Osci llator Start-up T ime r (OST), intended to

keep the chip in RESET until the crystal oscillator is

stable.

With the PLL enabled (HS4 oscillator mode), the

time-out sequenc e following a Power-on Reset is diff erent from other oscil lator modes. The time-out se quence

is as follows: th e PWRT time-ou t is invoked a fter a POR

time delay has expired, then the Oscillator Start-up

Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high

frequencies. The PWRT timer is used to provide an

additional time -out. Th is ti me is called T

#7) to allow the PLL ample time to lo ck to the incom ing

clock frequency.

PWRT (parameter

PLL (parameter

TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

OSC Mode OSC1 Pin OSC2 Pin

RC Floating, external resistor should pull high At logic low

RCIO Floating, external resistor should pull high Configured as PORTA, bit 6

ECIO Floating Configured as PORTA, bit 6

EC Floating At logic low

LP, XT, and HS Feedback inverter disabled, at quiescent

voltage level

Note: See Table 3-1 in Section 3.0 RESET, for time-outs due to SLEEP and MCLR

Feedback inverter disabled, at quiescent

voltage level

Reset.

DS30475A-page 28 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

3.0 RESET

The PIC18CXX8 differentiates between various kinds

of RESET:

a) Power-on Reset (POR)

b) MCLR

c) MCLR

d) Watchdog Timer (WDT) Reset (during normal

e) Programmable Brown-out Reset (PBOR)

f) RESET Instruction

g) Stack Ful l Reset

h) Stack Underflow Reset

Most registers are unaff ected by a RESET. Their status

is unknown on POR and unchanged by all other

RESETs. The other registers are forced to a “RESET”

Reset during normal operation

Reset during SLEEP

operation)

state on Power-on Reset, MCLR

Brown-out Reset, MCLR

Reset during SLEEP and by

the RESET instruction.

Most registers are not affected by a WDT wake-up,

since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI

and BOR are set or cleared differently in different

POR

RESET situations, as indicated i n Table 3-2. These bits

are used in software to determine the nature of the

RESET. See Table 3-3 for a full description of the

RESET states of all registers.

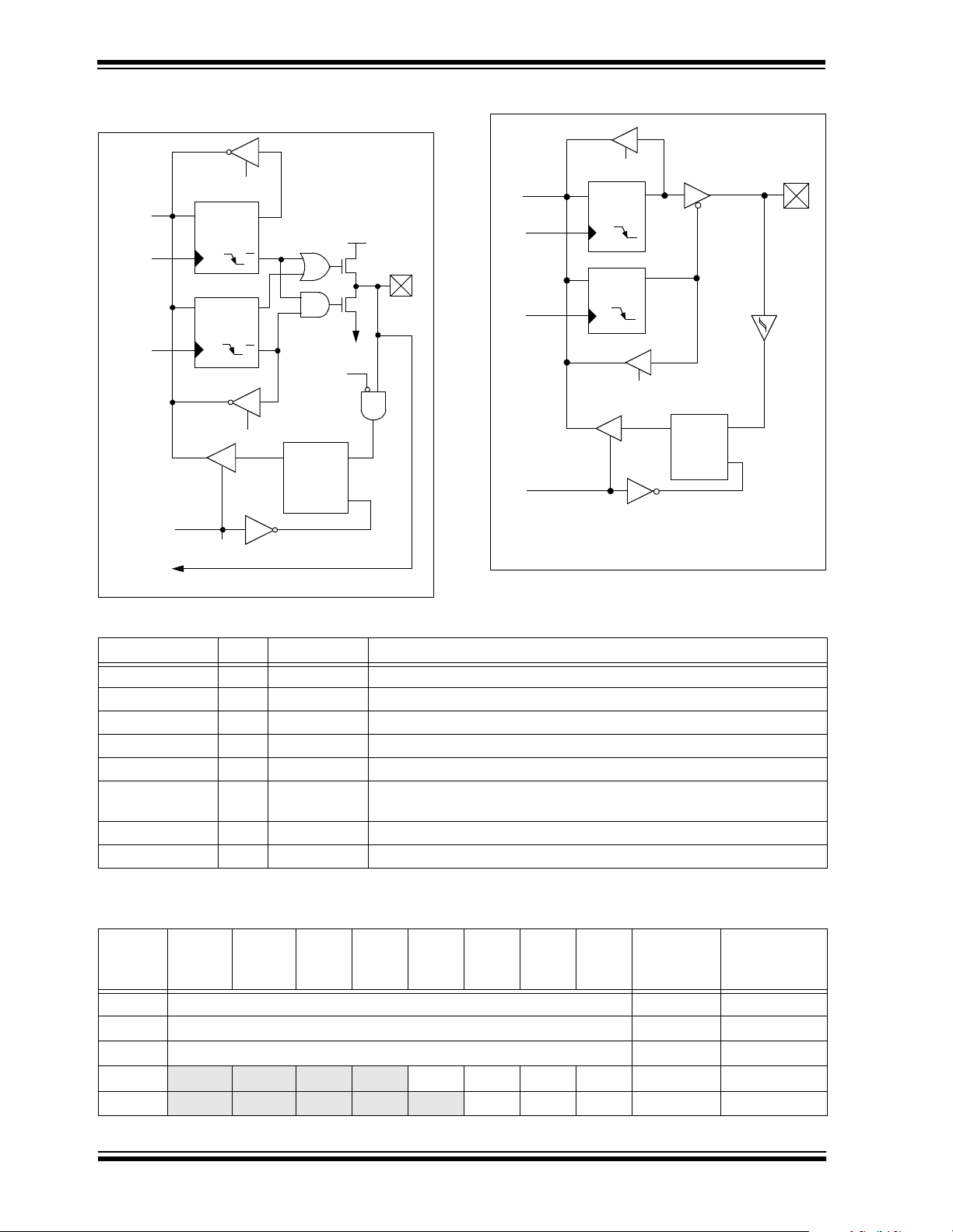

A simplified block diagram of the on-chip RESET circuit

is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR

in the MCLR

Reset path. The filter will detect and

ignore small pulses.

A WDT Reset does not drive MCLR

FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

RESET

Instruction

Stack

Pointer

Stack Full/Underflow Reset

External Reset

, WDT Reset,

, TO, PD,

noise filter

pin low.

MCLR

WDT

Module

DD Rise

V

Detect

VDD

Brown-out

Reset

OST/PWRT

OST

OSC1

On-chip

RC OSC

Note 1: This is a separate oscillator from the RC oscillator of the CLKI pin.

2: See Table 3-1 for time-out situations.

(1)

SLEEP

WDT

Time-out

Reset

Power-on Reset

BOREN

10-bit Ripple Counter

PWRT

10-bit Ripple Counter

Enable PWRT

Enable OST

(2)

S

Chip_Reset

R

Q

2000 Microchip Technology Inc. Advanced Information DS30475A-page 29

PIC18CXX8

3.1 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when a

V

DD rise is detected. To take advan tage of th e POR cir-

cuitry, connect the MCLR

resistor) to V

DD. This will eliminate ext ernal RC compo-

pin directly (or through a

nents usually needed to create a Power-on Reset

delay . A minimum ris e rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (exits the

RESET condition), device operating parameters (voltage, frequency, temperature,...) must be m et to en su re

operation. If these cond itions are not met, the d evice

must be held in RESET until the operating conditions

are met. Brown-out Reset may be used to meet the

voltage start-up condition.

FIGURE 3-2: EXTERNAL POWER-ON

RESET CIRCUIT (FOR SLOW

DD POWER-UP)

V

DD

V

D

R

R1

MCLR

C

Note 1: External Power-on Reset circuit is required

only if the V

DD power-up slope is too slow.

The diode D hel ps d isch arge th e ca pacito r

quickly when V

DD powers down.

2: R < 40 kΩ is recommended to make sure

that the voltage drop across R does not

violate the device’s electrical specification.

3: R1 = 100Ω to 1 kΩ will limit any current

flowing into MCLR

C in the even t of MCLR/

down due to Electrostatic Discharge

(ESD) or Electrical Overstress (EOS).

PIC18CXX8

from external capacitor

VPP pin break-

3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out

(parameter #33), only on power-up from the POR. The

Power-up Timer operates on an internal RC oscillator.

The chip is kept in RESET as long as the PWRT is

active. The PWRT ’s time delay allows V

acceptable level. A configuration bit (PWRTEN

DD to rise to an

in

CONFIG2L register) is provided to enable/disable the

PWRT.

The power-up time dela y will vary f rom chip to c hip due

DD, temperature and process variation. See DC

to V

parameter #33 for details.

3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024

oscillator cycle (from OSC1 input) delay after the

PWRT delay is over (parameter #32). This ensures that

the crystal oscilla tor or res onator has started an d stabilized.

The OST time-out is invoked only for XT, LP, HS and

HS4 modes and only on Power-on Reset or wake-up

from SLEEP.

3.4 PLL Lock Time-out

With the PLL enabled, the time-ou t sequen ce foll owin g

a Power-on Reset is different from other oscillator

modes. A portion of the Pow er-up T imer is used to provide a fixed time-out th at is suff icient for the PLL to lock

to the main oscillato r frequency. This PLL lock time-out

PLL) is typically 2 ms and follows the oscillator

(T

start-up time-out (OST).

3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if

clear/programmed) or enable (if set) the Brown-out

Reset circuitry. If VDD falls below parameter D005 for

greater than parameter #35, the brown-out situation

resets the chip. A RESET may not occur if VDD falls

below parameter D005 for less than parameter #35.

The chip will remain in Bro wn-out Re set unt il V

above BV

DD. The Power-up T im er w ill th en be invoked

and will keep the chip in RESET an additional time

delay (parameter #33). If V

DD drops below BVDD while

the Power-up Timer is running, the chip will go back

into a Brown-out Reset and the Power-up Timer will be

initialized . Once V

DD rises above BVDD, the Power-up

Timer will execute the additional time delay.

DD rises

DS30475A-page 30 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

3.6 Time-out Sequence

On power-up, the time-out sequence is as follows:

First, PWRT time-out is invoked after the POR time

delay has expired, then OST is activated. The total

time-out will vary based on oscillator configuration and

the status of the PWRT. For example, in RC mode with

the PWRT disabled, there will be no time-out at all.

Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and

Figure 3-7 depict time-out sequences on power-up.

Since the time-outs oc cur from the POR pulse, if MCLR

is kept low long enough, the time-outs will expire.

Bringing MCLR

(Figure 3-5). This is useful for testing purposes or to

synchronize more th an one PIC18C XX8 device opera ting in para llel.

Table 3-2 shows the RESET conditions for some Special Function Registers, while Table 3-3 shows the

RESET conditions for all registers.

high will begin execution immediately

TABLE 3-1: TIME-OUT IN VARIOUS SITUATIONS

Oscillator

Configuration

HS with PLL enabled

HS, XT, LP 72 ms + 1024Tosc 1024Tosc 72 ms + 1024Tosc 1024Tosc

EC 72 ms — 72 ms —

External RC 72 ms — 72 ms —

Note 1: 2 ms = Nominal time required for the 4X PLL to lock.

2: 72 ms is the nominal power-up timer delay.

(1)

PWRTE

72 ms + 1024Tosc + 2 ms 1024Tosc + 2 ms 72 ms + 1024Tosc + 2 ms 1 02 4Tosc + 2 ms

Power-up

N = 0 PWRTEN = 1

(2)

Brown-out

(2)

Wake-up from

SLEEP or

Oscillator Switch

REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

R/W-0 R/W-0 U-0 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

IPEN LWRT

bit 7 bit 0

— RI TO PD POR BOR

TABLE 3-2: STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR

RCON REGISTER

Condition

Power-on Reset 0000h 00-1 1100 1 1 1 0 0 u u

Reset during normal

MCLR

operation

Software Reset during normal

operation

Stack Full Reset during normal

operation

Stack Underflow Reset during

normal operation

MCLR

Reset during SLEEP 0000h 00-u 10uu u 1 0 u u u u

WDT Reset 0000h 0u-u 01uu u 0 1 u u u u

WDT Wake-up PC + 2 uu-u 00uu u 0 0 u u u u

Brown-out Reset 0000h 0u-1 11u0 1 1 1 u 0 u u

Interrupt wake-up from SLEEP PC + 2

Legend: u = unchanged, x = unknown,- = unimplemented bit, read as '0'

Note 1: When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the

interrupt vector (0x000008h or 0x000018h).

Program

Counter

0000h 00-u uuuu u u u u u u u

0000h 0u-0 uuuu 0 u u u u u u

0000h 0u-u uu11 u u u 1 1 u 1

0000h 0u-u uu11 u u u 1 1 1 u

(1)

RCON

Register

uu-u 00uu u 0 0 u u u u

TO PD POR BOR STKFUL STKUNF

RI

2000 Microchip Technology Inc. Advanced Information DS30475A-page 31

PIC18CXX8

FIGURE 3-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

VDD

MCLR

INTERNAL POR

TPWRT

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

TOST

FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR

VDD

MCLR

INTERNAL POR

TPWRT

PWRT TI ME-OUT

OST TIME-OUT

INTERNAL RESET

NOT TIED TO VDD): CASE 1

TOST

FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR

VDD

MCLR

INTERNAL POR

TPWRT

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

DS30475A-page 32 Advanced Information 2000 Microchip Technology Inc.

NOT TIED TO VDD): CASE 2

TOST

FIGURE 3-6: SLOW RISE TIME (MCLR TIED TO VDD)

VDD

MCLR

0V

1V

PIC18CXX8

5V

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RES ET

T

PWRT

TDEADTIME

TOST

FIGURE 3-7: TIME-OUT SEQUENCE ON POR W/ PLL ENABLED (MCLR

VDD

MCLR

IINTERNAL POR

TPWRT

PWRT TIME-OUT

TOST

TIED TO VDD)

OST TIME-OUT

PLL TIME-OUT

INTERNAL RESET

TOST = 1024 clock cycles.

PLL ≈ 2 ms max. First three stages of the PWRT timer.

T

TPLL

2000 Microchip Technology Inc. Advanced Information DS30475A-page 33

PIC18CXX8

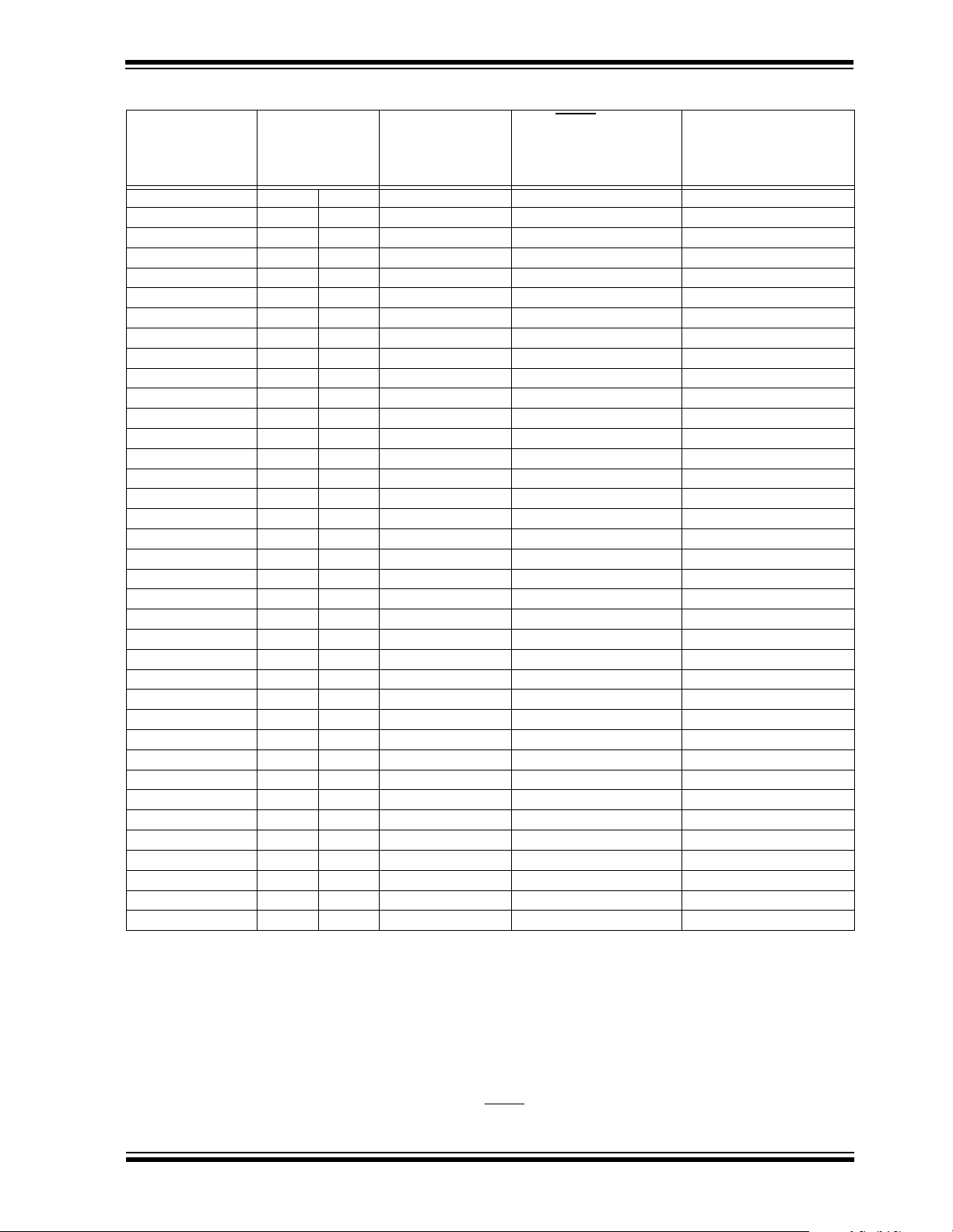

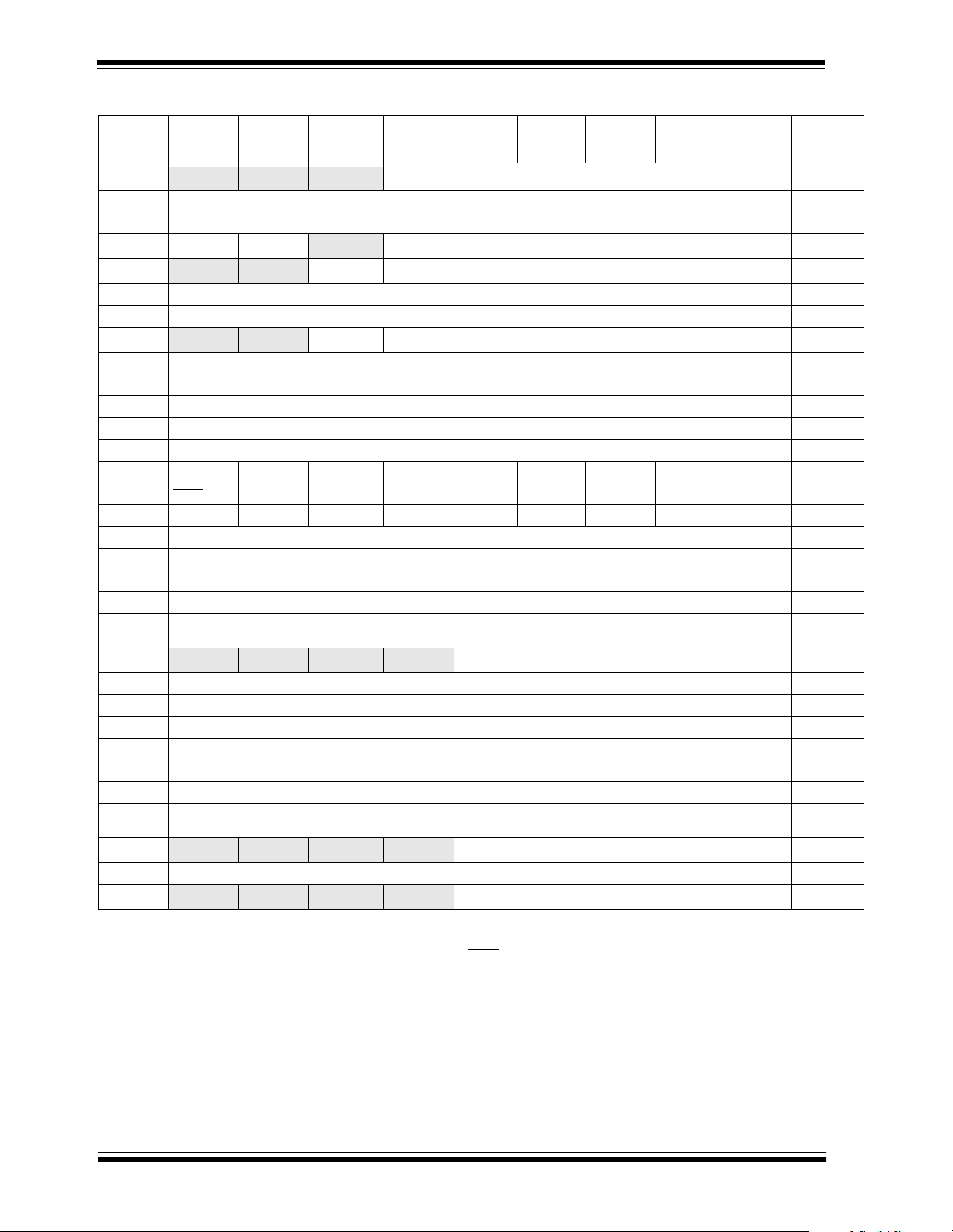

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Reset

MCLR

Register

Applicable

Devices

TOSU 658 858 ---0 0000 ---0 0000 ---0 uuuu

TOSH 658 858 0000 0000 0000 0000 uuuu uuuu

TOSL 658 858 0000 0000 0000 0000 uuuu uuuu

STKPTR 658 858 00-0 0000 00-0 0000 uu-u uuuu

PCLATU 658 858 ---0 0000 ---0 0000 ---u uuuu

PCLATH 658 858 0000 0000 0000 0000 uuuu uuuu

PCL 658 858 0000 0000 0000 0000 PC + 2

TBLPTRU 658 858 --00 0000 --00 0000 --uu uuuu

TBLPTRH 658 858 0000 0000 0000 0000 uuuu uuuu

TBLPTRL 658 858 0000 0000 0000 0000 uuuu uuuu

TABLAT 658 858 0000 0000 0000 0000 uuuu uuuu

PRODH 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PRODL 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

INTCON 658 858 0000 000x 0000 000u uuuu uuuu

INTCON2 658 858 1111 1111 1111 1111 uuuu uuuu

INTCON3 658 858 1100 0000 1100 0000 uuuu uuuu

INDF0 658 858 N/A N/A N/A

POSTINC0 658 858 N/A N/A N/A

POSTDEC0 658 858 N/A N/A N/A

PREINC0 658 858 N/A N/A N/A

PLUSW0 658 858 N/A N/A N/A

FSR0H 658 858 ---- 0000 ---- 0000 ---- uuuu

FSR0L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

WREG 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

INDF1 658 858 N/A N/A N/A

POSTINC1 658 858 N/A N/A N/A

POSTDEC1 658 858 N/A N/A N/A

PREINC1 658 858 N/A N/A N/A

PLUSW1 658 858 N/A N/A N/A

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrup t and th e GIEL or GIEH bit is set, the PC is loaded with the interrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware

stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other

oscillator modes, they are disabled and read ’0’.

6: The long write enable is only reset on a POR or MCLR

7: Available on PIC18C858 only.

Power-on Reset,

Brown-out Reset

WDT Reset

RESET Instruction

Stack Resets

.

Wake-up via WDT

or Interrupt

(3)

(3)

(3)

(3)

(2)

(1)

(1)

(1)

DS30475A-page 34 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Reset

MCLR

Register

FSR1H 658 858 ---- 0000 ---- 0000 ---- uuuu

FSR1L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

BSR 658 858 ---- 0000 ---- 0000 ---- uuuu

INDF2 658 858 N/A N/A N/A

POSTINC2 658 858 N/A N/A N/A

POSTDEC2 658 858 N/A N/A N/A

PREINC2 658 858 N/A N/A N/A

PLUSW2 658 858 N/A N/A N/A

FSR2H 658 858 ---- 0000 ---- 0000 ---- uuuu

FSR2L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

STATUS 658 858 ---x xxxx ---u uuuu ---u uuuu

TMR0H 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TMR0L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

T0CON 658 858 1111 1111 1111 1111 uuuu uuuu

OSCCON 658 858 ---- ---0 ---- ---0 ---- ---u

LVDCON 658 858 --00 0101 --00 0101 --uu uuuu

WDTCON 658 858 ---- ---0 ---- ---0 ---- ---u

(4, 6)

RCON

TMR1H 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TMR1L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

T1CON 658 858 0-00 0000 u-uu uuuu u-uu uuuu

TMR2 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PR2 658 858 1111 1111 1111 1111 1111 1111

T2CON 658 858 -000 0000 -000 0000 -uuu uuuu

SSPBUF 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

SSPADD 658 858 0000 0000 0000 0000 uuuu uuuu

SSPSTAT 658 858 0000 0000 0000 0000 uuuu uuuu

SSPCON1 658 858 0000 0000 0000 0000 uuuu uuuu

SSPCON2 658 858 0000 0000 0000 0000 uuuu uuuu

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrup t and th e GIEL or GIEH bit is set, the PC is loaded with the interrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware

stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other

oscillator modes, they are disabled and read ’0’.

6: The long write enable is only reset on a POR or MCLR

7: Available on PIC18C858 only.

Applicable

Devices

658 858 00-1 11q0 00-1 qquu uu-u qquu

Power-on Reset,

Brown-out Reset

WDT Reset

RESET Instruction

Stack Resets

.

Wake-up via WDT

or Interrupt

2000 Microchip Technology Inc. Advanced Information DS30475A-page 35

PIC18CXX8

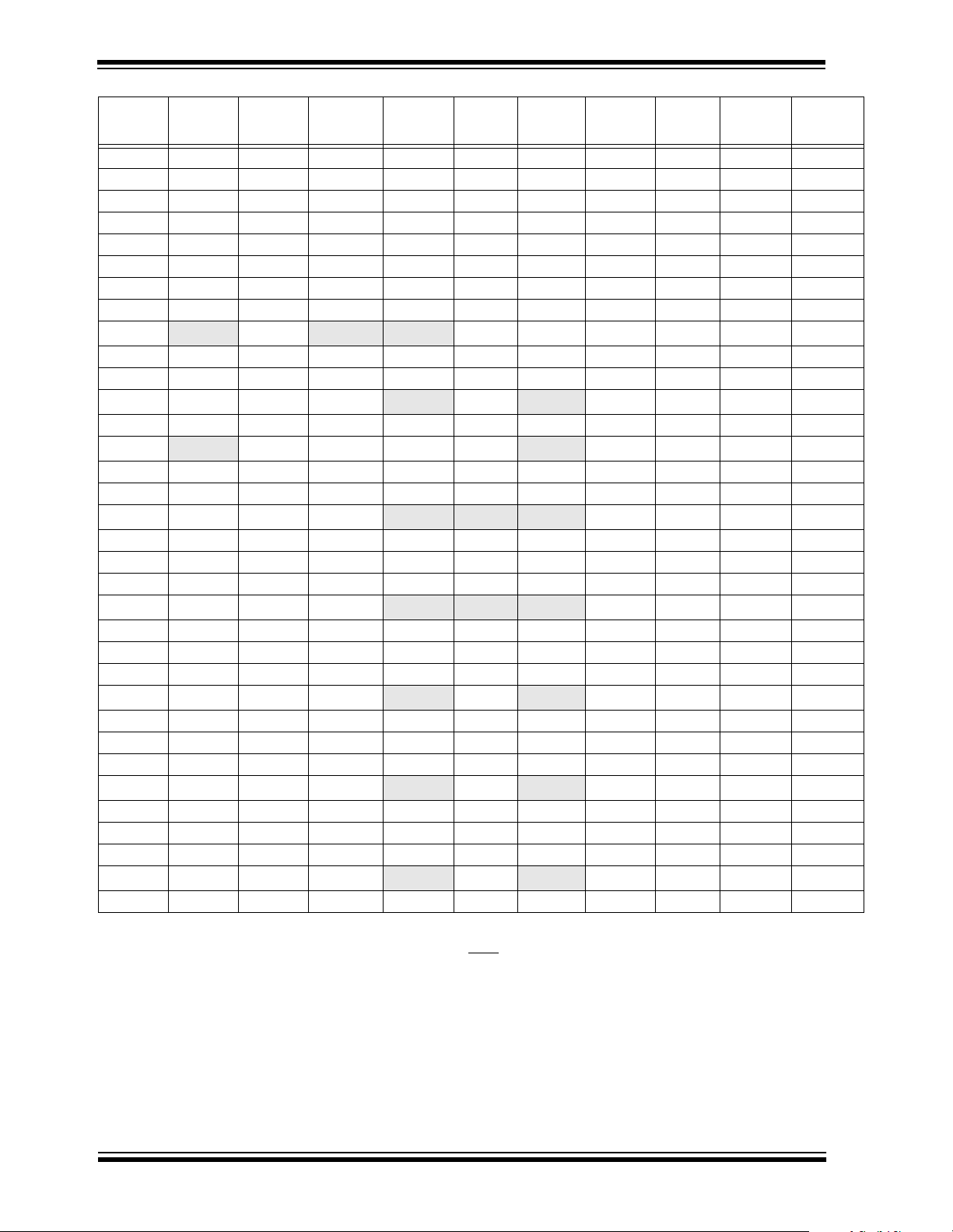

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

MCLR Reset

Register

ADRESH 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

ADRESL 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

ADCON0 658 858 --00 0000 --00 0000 --uu uuuu

ADCON1 658 858 --00 0000 --00 0000 --uu uuuu

ADCON2 658 858 0--- -000 0--- -000 u--- -uuu

CCPR1H 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

CCPR1L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

CCP1CON 658 858 --00 0000 --00 0000 --uu uuuu

CCPR2H 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

CCPR2L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

CCP2CON 658 858 --00 0000 --00 0000 --uu uuuu

CVRCON 658 858 0000 0000 0000 0000 uuuu uuuu

CMCON 658 858 0000 0000 0000 0000 uuuu uuuu

TMR3H 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TMR3L 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

T3CON 658 858 0000 0000 uuuu uuuu uuuu uuuu

PSPCON 658 858 0000 ---- 0000 ---- uuuu ----

SPBRG 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RCREG 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TXREG 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TXSTA 658 858 0000 -01x 0000 -01u uuuu -uuu

RCSTA 658 858 0000 000x 0000 000u uuuu uuuu

IPR3 658 858 1111 1111 1111 1111 uuuu uuuu

PIR3 658 858 0000 0000 0000 0000 uuuu uuuu

PIE3 658 858 0000 0000 0000 0000 uuuu uuuu

IPR2 658 858 -1-- 1111 -1-- 1111 -u-- uuuu

PIR2 658 858 -0-- 0000 -0-- 0000 -u-- uuuu

PIE2 658 858 -0-- 0000 -0-- 0000 -u-- uuuu

IPR1 658 858 1111 1111 1111 1111 uuuu uuuu

PIR1 658 858 0000 0000 0000 0000 uuuu uuuu

PIE1 658 858 0000 0000 0000 0000 uuuu uuuu

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrup t and th e GIEL or GIEH bit is set, the PC is loaded with the interrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware

stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other

oscillator modes, they are disabled and read ’0’.

6: The long write enable is only reset on a POR or MCLR

7: Available on PIC18C858 only.

Applicable

Devices

658 858 -111 1111 -111 1111 -uuu uuuu

658 858 -000 0000 -000 0000 -uuu uuuu

658 858 -000 0000 -000 0000 -uuu uuuu

Power-on Reset,

Brown-out Reset

WDT Reset

RESET Instruction

Stack Resets

.

Wake-up via WDT

or Interrupt

(1)

(1)

(1)

DS30475A-page 36 Advanced Information 2000 Microchip Technology Inc.

PIC18CXX8

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Reset

MCLR

WDT Reset

RESET Instruction

Stack Resets

-111 1111

-uuu uuuu

-u0u 0000

.

(5)

(5)

(5)

Wake-up via WDT

or Interrupt

-uuu uuuu

-uuu uuuu

-uuu uuuu

(5)

(5)

(5)

TRISJ

TRISH

Register

(7)

(7)

Applicable

Devices

-8581111 1111 1111 1111 uuuu uuuu

-8581111 1111 1111 1111 uuuu uuuu

Power-on Reset,

Brown-out Reset

TRISG 658 858 ---1 1111 ---1 1111 ---u uuuu

TRISF 658 858 1111 1111 1111 1111 uuuu uuuu

TRISE 658 858 1111 1111 1111 1111 uuuu uuuu

TRISD 658 858 1111 1111 1111 1111 uuuu uuuu

TRISC 658 858 1111 1111 1111 1111 uuuu uuuu

TRISB 658 858 1111 1111 1111 1111 uuuu uuuu

TRISA

LATJ

LATH

(7)

(7)

(5)

658 858 -111 1111

-858xxxx xxxx uuuu uuuu uuuu uuuu

-858xxxx xxxx uuuu uuuu uuuu uuuu

(5)

LATG 658 858 ---x xxxx ---u uuuu ---u uuuu

LATF 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

LATE 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

LATD 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

LATC 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

LATB 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

(5)

LATA

PORTJ

PORTH

(7)

(7)

658 858 -xxx xxxx

-858xxxx xxxx uuuu uuuu uuuu uuuu

-8580000 xxxx 0000 uuuu uuuu uuuu

(5)

PORTG 658 858 ---x xxxx ---u uuuu ---u uuuu

PORTF 658 858 x000 0000 u000 0000 uuuu uuuu

PORTE 658 858 --00 xxxx uuuu u000 uuuu uuuu

PORTD 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PORTC 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PORTB 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PORTA

(5)

658 858 -x0x 0000

(5)

TRISK 658 858 1111 1111 1111 1111 uuuu uuuu

LATK 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

PORTK 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

TXERRCNT 658 858 0000 0000 0000 0000 uuuu uuuu

RXERRCNT 658 858 0000 0000 0000 0000 uuuu uuuu

COMSTAT 658 858 0000 0000 0000 0000 uuuu uuuu

CIOCON 658 858 1000 ---- 1000 ---- uuuu ----

BRGCON3 658 858 -0-- -000 -0-- -000 -u-- -uuu

BRGCON2 658 858 0000 0000 0000 0000 uuuu uuuu

BRGCON1 658 858 0000 0000 0000 0000 uuuu uuuu

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrup t and th e GIEL or GIEH bit is set, the PC is loaded with the interrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware

stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other

oscillator modes, they are disabled and read ’0’.

6: The long write enable is only reset on a POR or MCLR

7: Available on PIC18C858 only.

2000 Microchip Technology Inc. Advanced Information DS30475A-page 37

PIC18CXX8

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Reset

MCLR

Register

CANCON 658 858 xxxx xxx- uuuu uuu- uuuu uuu-

CANSTAT 658 858 xxx- xxx- uuu- uuu- uuu- uuu-

RXB0D7 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RXB0D6 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RXB0D5 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RXB0D4 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RXB0D3 658 858 xxxx xxxx uuuu uuuu uuuu uuuu

RXB0D2 658 858 xxxx xxxx uuuu uuuu uuuu uuuu