Page 1

查询16F872供应商

PIC16F872

28-Pin, 8-Bit CMOS FLASH Microcontroller

Devices Included in this Data Sheet:

•PIC16F872

Microcontroller Core Features:

• High-performance RISC CPU

• Only 35 single word instructions to learn

• All single cycle instructions except for program

branches which are two cycle

• Operating speed: DC - 20 MHz clock input

DC - 200 ns instruction cycle

• 2K x 14 words of FLASH Program Memory

128 x 8 bytes of Data Memory (RAM)

64 x 8 bytes of EEPROM Data Memory

• Pinout compatible to the PIC16C72A

• Interrupt capability (up to 10 sources)

• Eight level deep hardware stack

• Direct, indirect and relative addressing modes

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator for reliable operation

• Programmable code-protection

• Power saving SLEEP mode

• Selectable oscillator options

• Low-power, high-speed CMOS FLASH/EEPROM

technology

• Fully static design

• In-Circuit Serial Programming (ICSP) via two

pins

• Single 5V In-Circ uit Serial Prog ramming capabi lity

• In-Circuit Debugging via two pins

• Processor read/write access to program memory

• Wide operating voltage range: 2.0V to 5.5V

• High Sink/Source Current: 25 mA

• Commercial and Industrial temperature ranges

• Low-power consumption:

- < 2 mA typical @ 5V, 4 MHz

-20 µA typical @ 3V, 32 kHz

-< 1 µA typical standby current

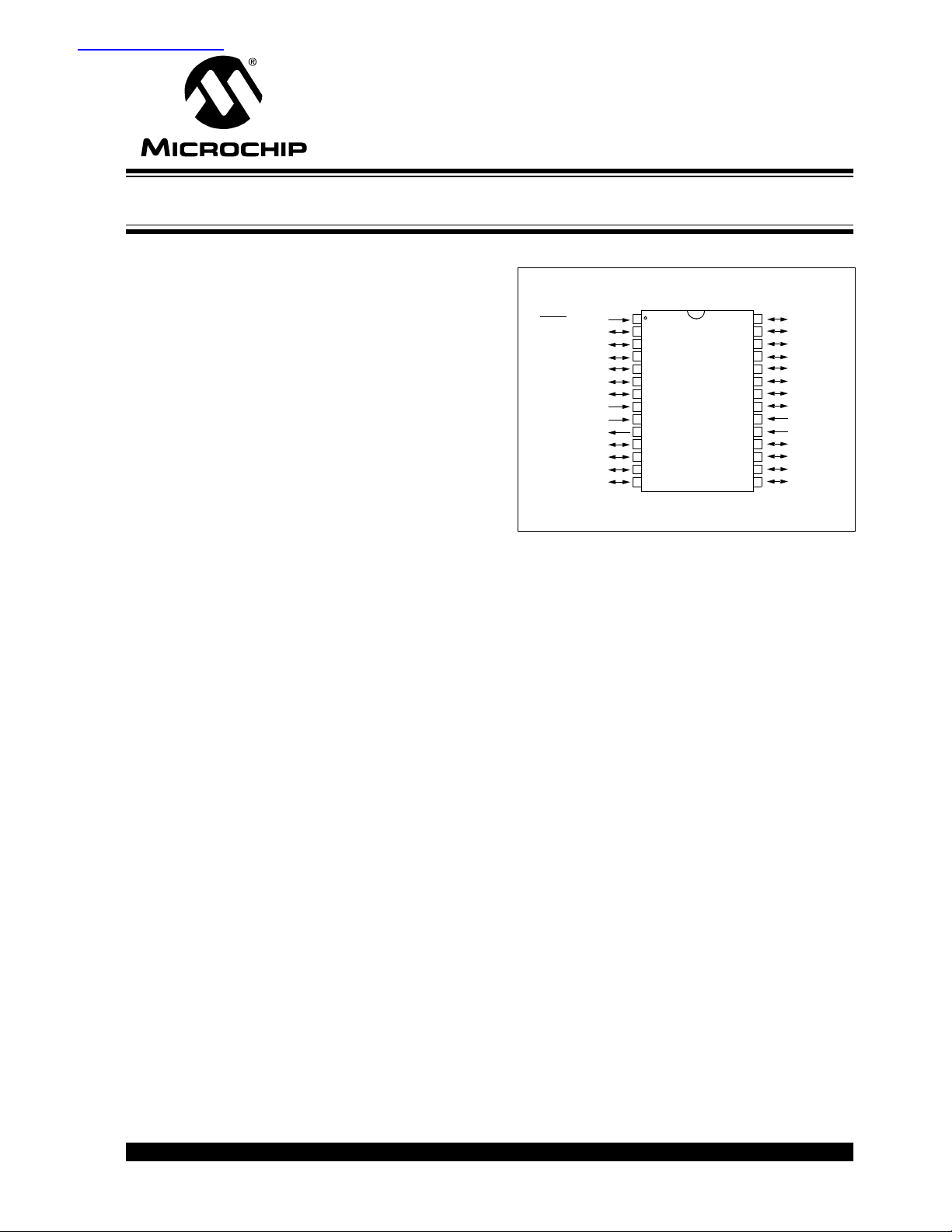

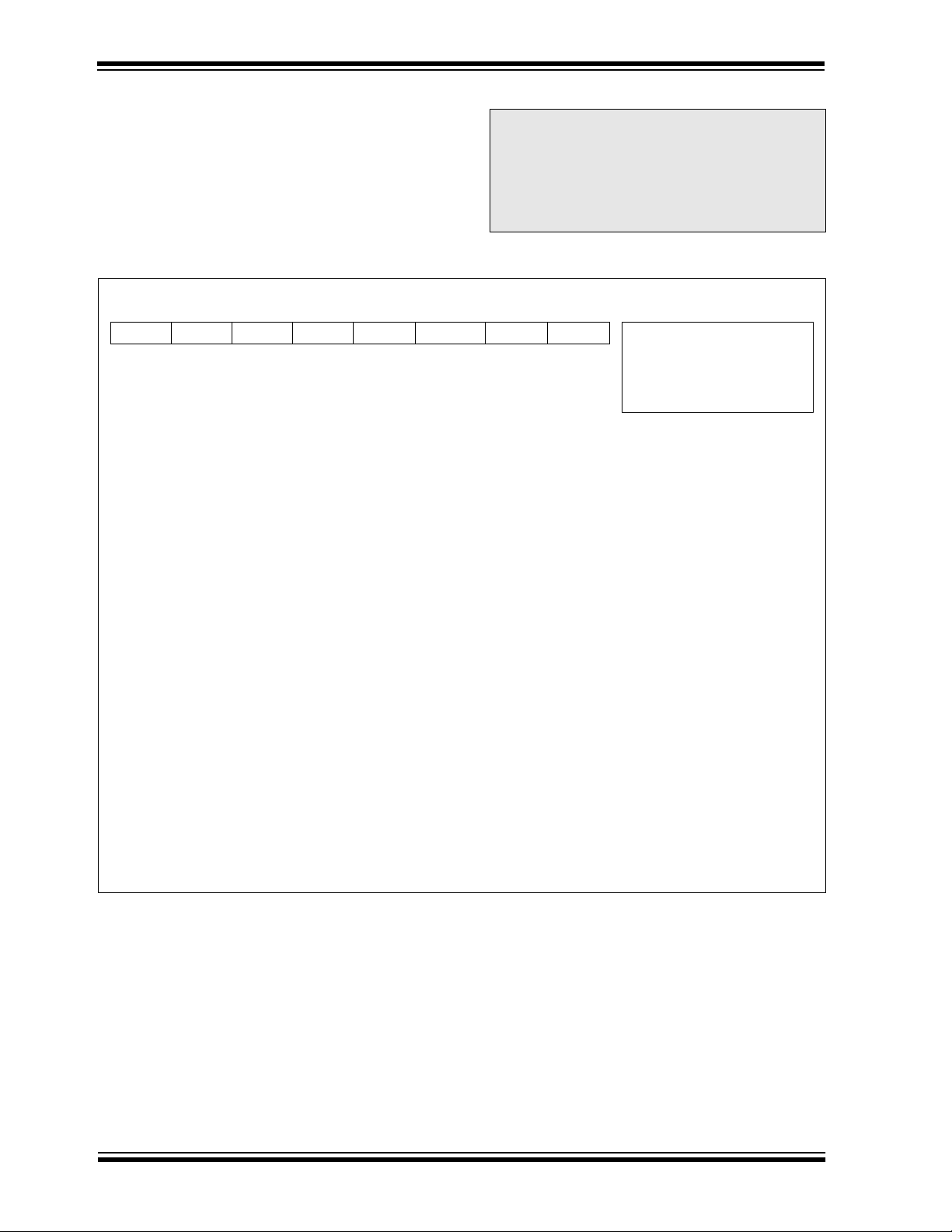

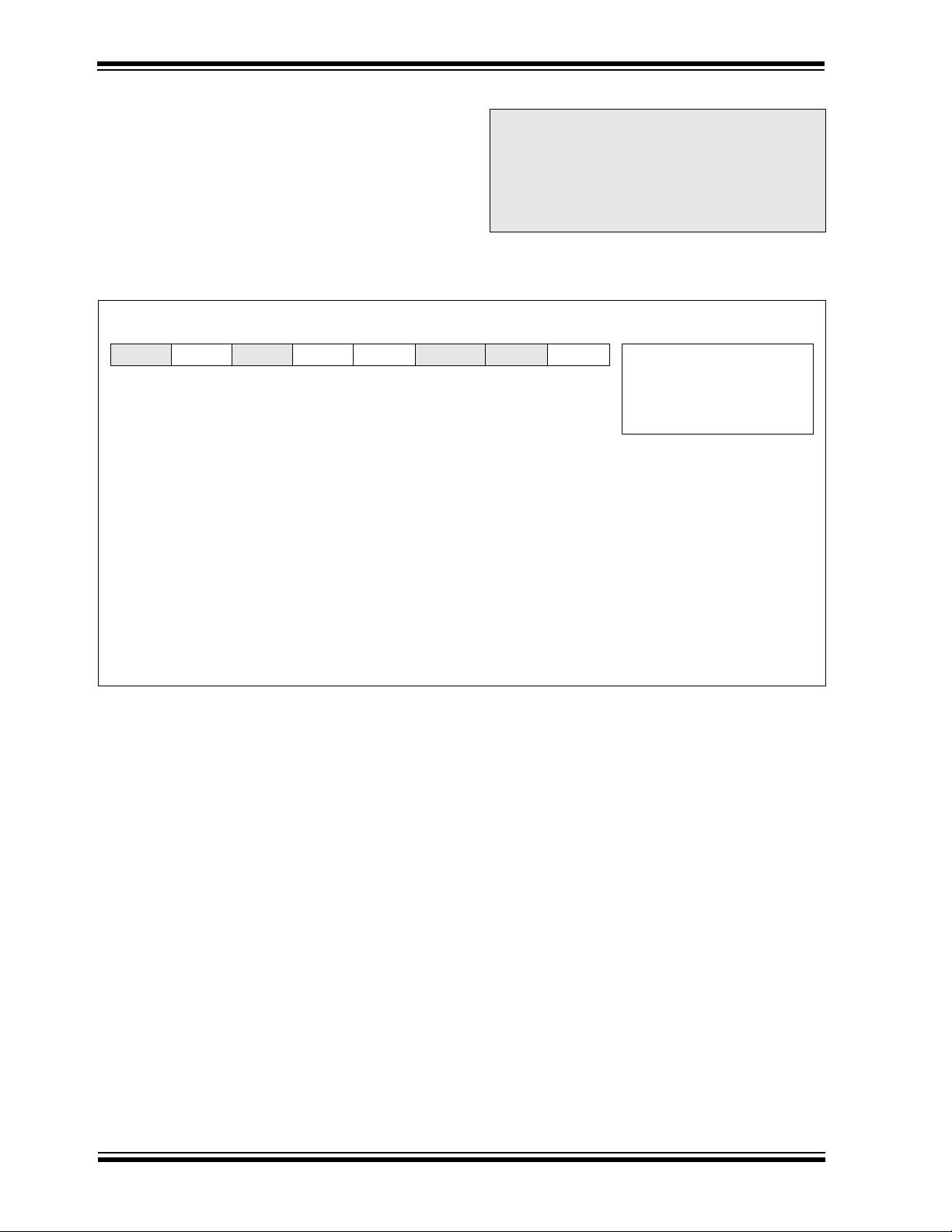

Pin Diagram

DIP, SOIC, SSOP

PIC16F872

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RB7/PGD

RB6/PGC

RB5

RB4

RB3/PGM

RB2

RB1

RB0/INT

V

DD

V

SS

RC7

RC6

RC5/SDO

RC4/SD I/SDA

MCLR/VPP/TH V

RA0/AN0

RA1/AN1

RA2/AN2/V

RA3/AN3/V

OSC2/CLKOUT

RC0/T1OS O/T1CKI

REF

REF

RA4/T0CKI

RA5/AN4/SS

V

OSC1/C L KIN

RC1/T1OSI

RC2/CCP1

RC3/SCK/SCL

1

2

3

4

-

+

SS

5

6

7

8

9

10

11

12

13

14

Peripheral Features:

• Timer0: 8-bit timer/counter with 8-bit prescaler

• Timer1: 16-bit timer/counter with prescaler,

can be incremented during sleep via external

crystal/clock

• Timer2: 8-bit timer/counter with 8-bit period

register, prescaler and postscaler

• One Capture, Compare, PWM module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

• 10-bit multi-channel Analog-to-Digital converter

• Synchronous Serial Port (SSP) with SPI

Mode) and I

2C

(Master/Slave)

• Brown-out detection circuitry for Brown-out Reset

(BOR)

(Master

1999 Microchip Technology Inc.

Preliminary DS30221A-page 1

Page 2

PIC16F872

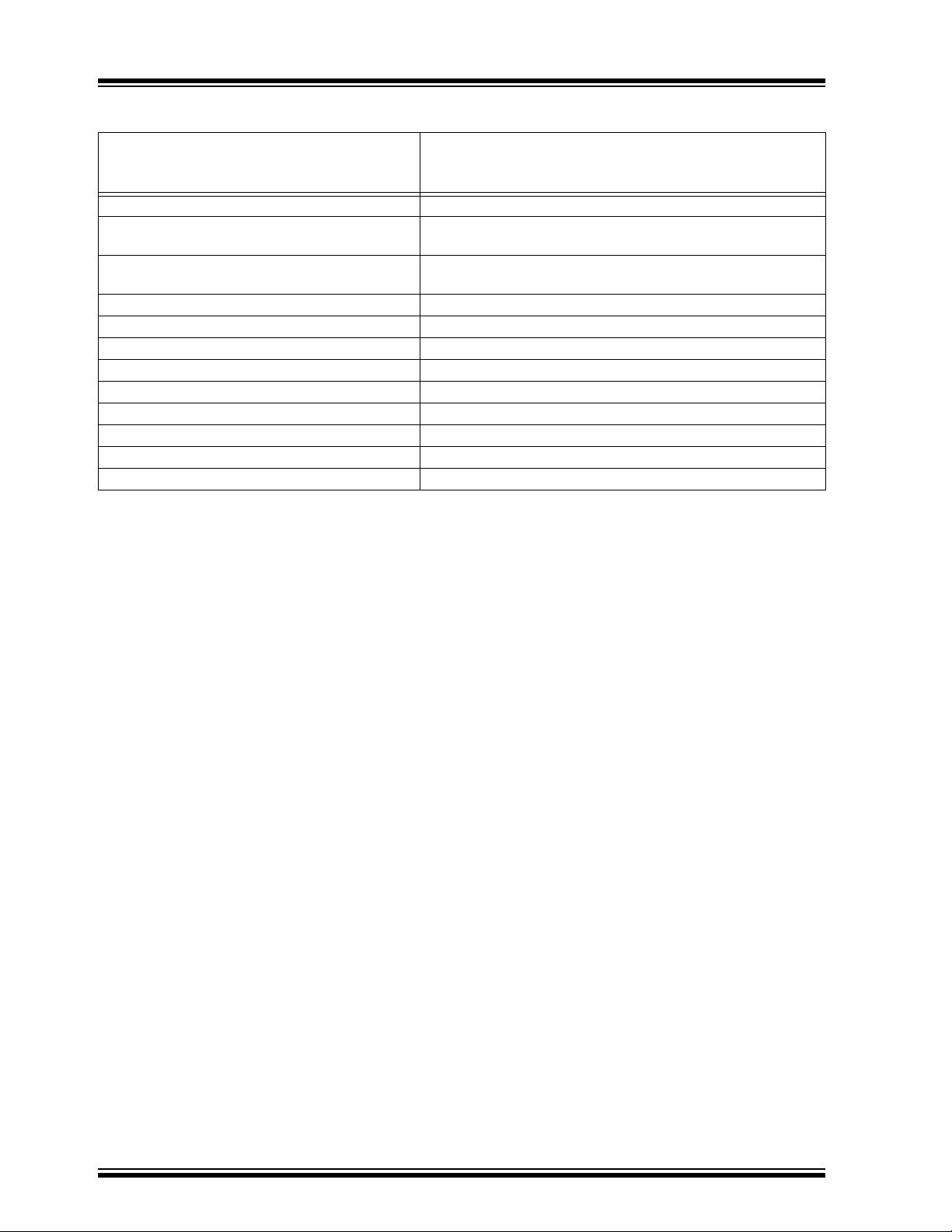

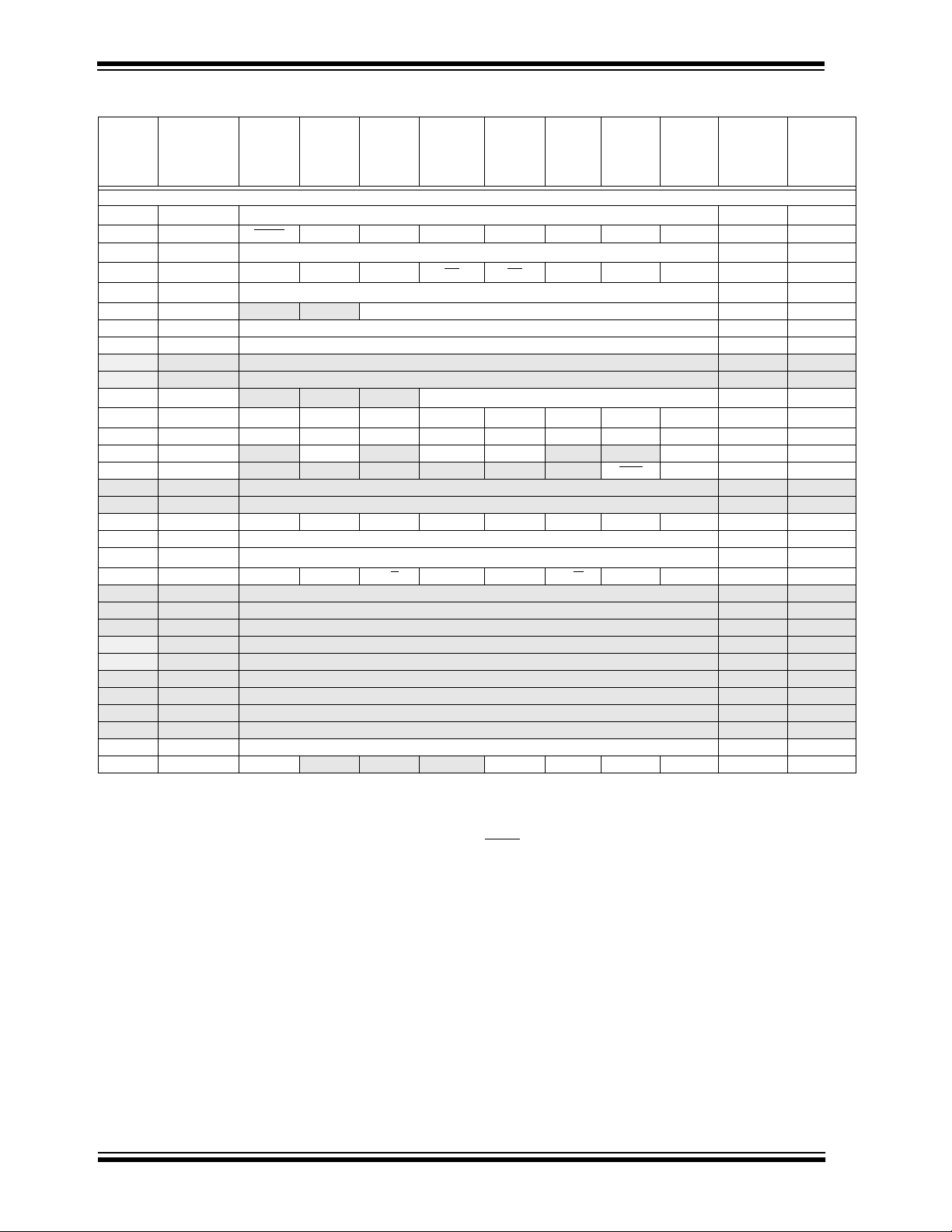

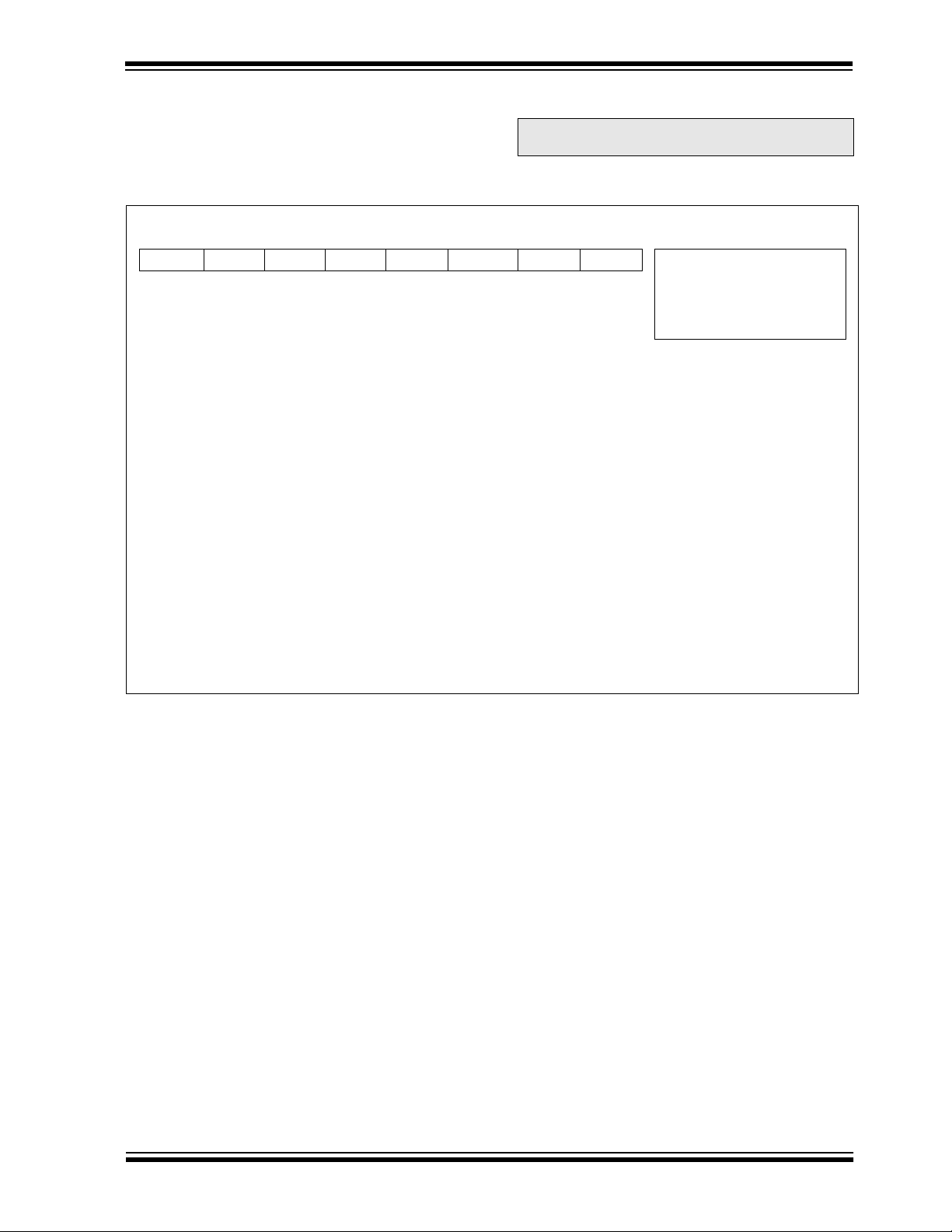

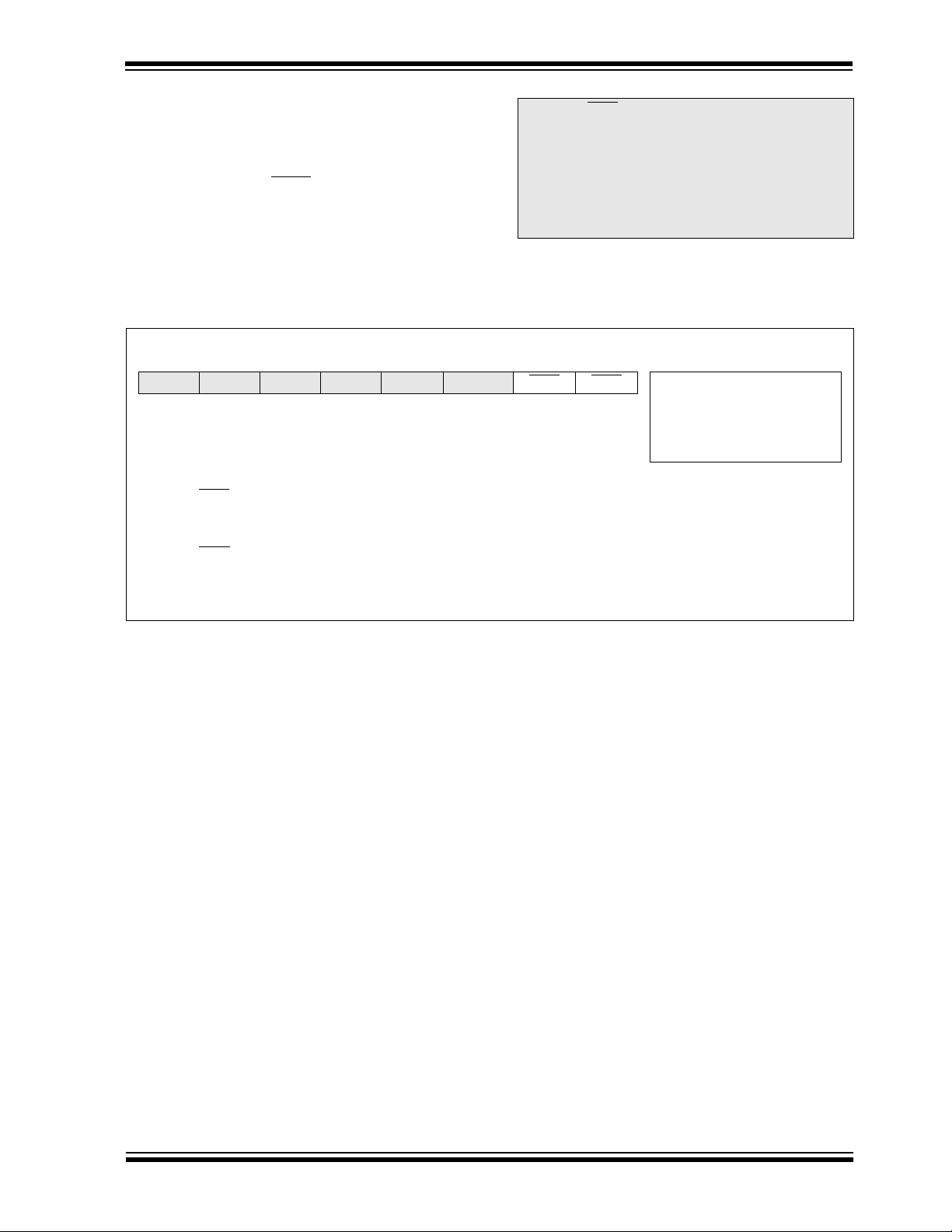

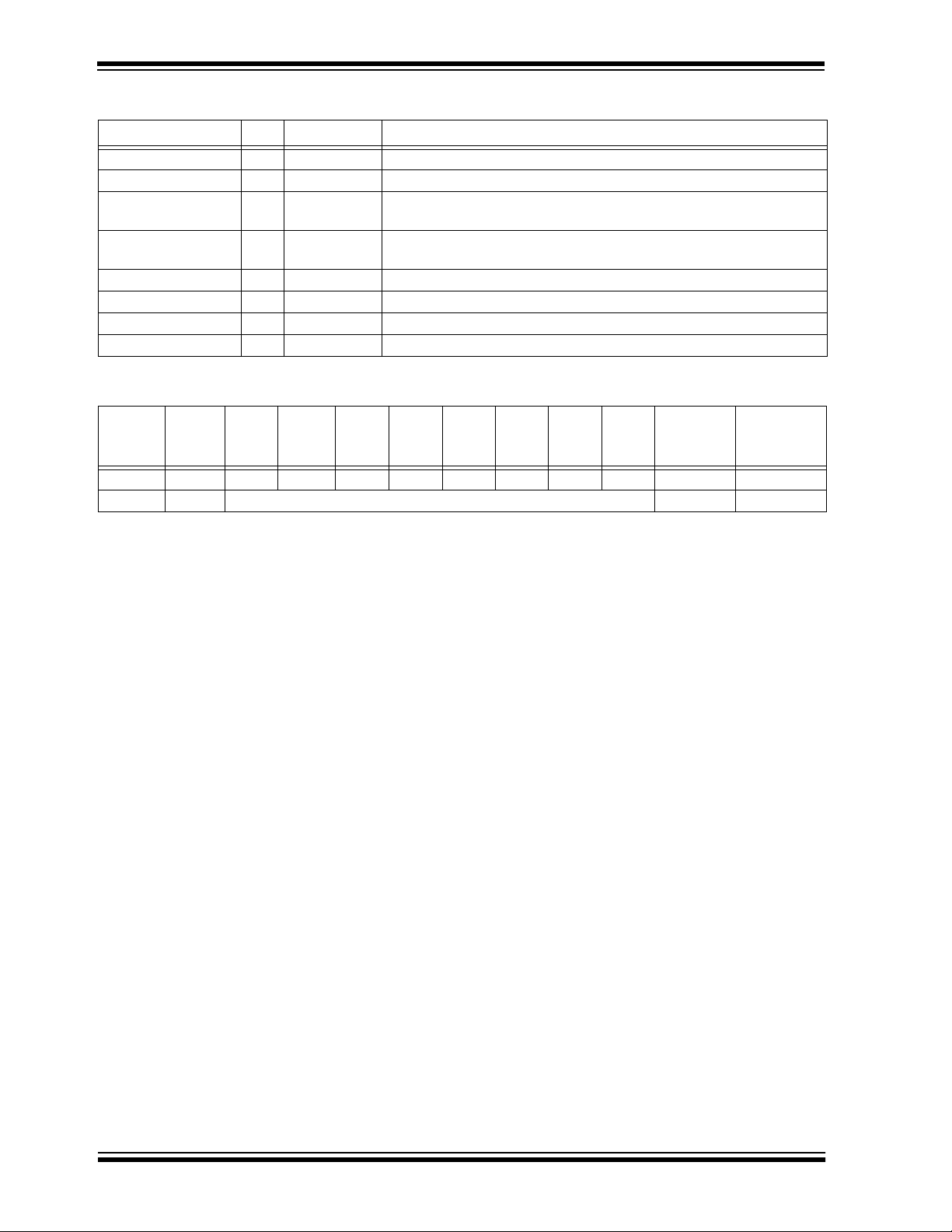

Key Features

PICmicro™ Mid-Range Reference Manual

(DS33023)

Operating Frequency DC - 20 MHz

Resets (and Delays) POR, BOR

FLASH Program Memory

(14-bit words)

Data Memory (bytes) 128

EEPROM Data Memory 64

Interrupts 10

I/O Ports Ports A,B,C

Timers 3

Capture/Compare/PWM module 1

Serial Communications MSSP

10-bit Analog-to-Digital Module 5 input channels

Instruction Set 35 Instructions

PIC16F872

(PWRT, OST)

2K

DS30221A-page 2 Preliminary

1999 Microchip Technology Inc.

Page 3

PIC16F872

Table of Contents

1.0 Device Overview........................................................................................................................................................................... 5

2.0 Memory Organization.................................................................................................................................................................... 7

3.0 I/O Ports................. ................................... .................................... ............................................................. ............. ............ ........ 23

4.0 Data EEPROM and FLASH Program Memory .......................................................................................................................... 29

5.0 Timer0 Module. ........................................................................................................................................................................... 37

6.0 Timer1 Module. ........................................................................................................................................................................... 41

7.0 Timer2 Module. .......................................................................................................................................................................... 45

8.0 Capture/Compare/PWM (CCP) Module(s).................................................................................................................................. 47

9.0 Master Synchronous Serial Port (MSSP) Module........................................................ ............................................................... 53

10.0 Analog-to-Digital Converter (A/D) Module ..................................................................................................................................85

11.0 Special Features of the CPU......................................................................................................................................................95

12.0 Instruction Set Summary........................................................................................................................................................... 111

13.0 Development Support............................................................................................................................................................... 119

14.0 Electrical Characteristics........................................................................................................................................................... 125

15.0 DC and AC Characteristics Graphs and Tables .......................................................................................................................143

16.0 Packaging Infor mation...................... ............. ................................... ............. ........................................................... ............ .... 145

Appendix A: Revision History......................................................................................................................................................... 149

Appendix B: Conversion Considerations................................................................................ .... .. .... .............................................. 149

Index ......................................... .. .. .. .. .. .. ....... .. .. .. .. .. .. .. ..... .. .. .. .. .... .. .. ..... .. .. .. .. .. .. .. .. ...............................................................151

On-Line Support................................................................................................................................................................................. 157

Product Identification System............................................................................................................................................................ 159

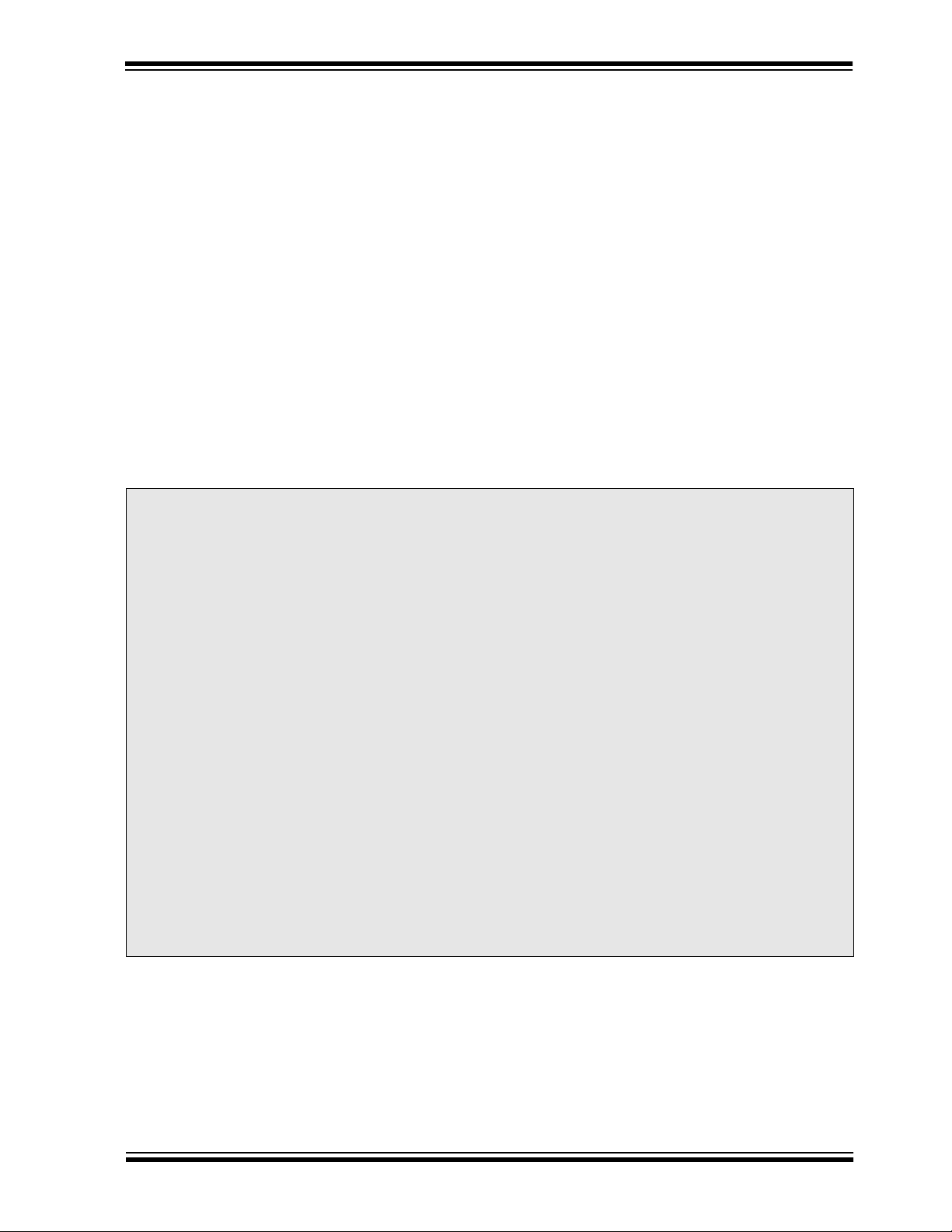

To Our Valued Customers

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended

workarounds. As device/documentation issues become known to us, w e will pub lish an errata sheet. The errata will specify the re vision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include liter-

ature number) you are using.

Corrections to this Data Sheet

We constantly strive to improve the quality of all our products and documentation. W e hav e spent a great deal of time to ensure that

this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or

appears in error, please:

• Fill out and mail in the reader response form in the back of this data sheet.

• E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

1999 Microchip Technology Inc.

Preliminary DS30221A-page 3

Page 4

PIC16F872

NOTES:

DS30221A-page 4 Preliminary

1999 Microchip Technology Inc.

Page 5

PIC16F872

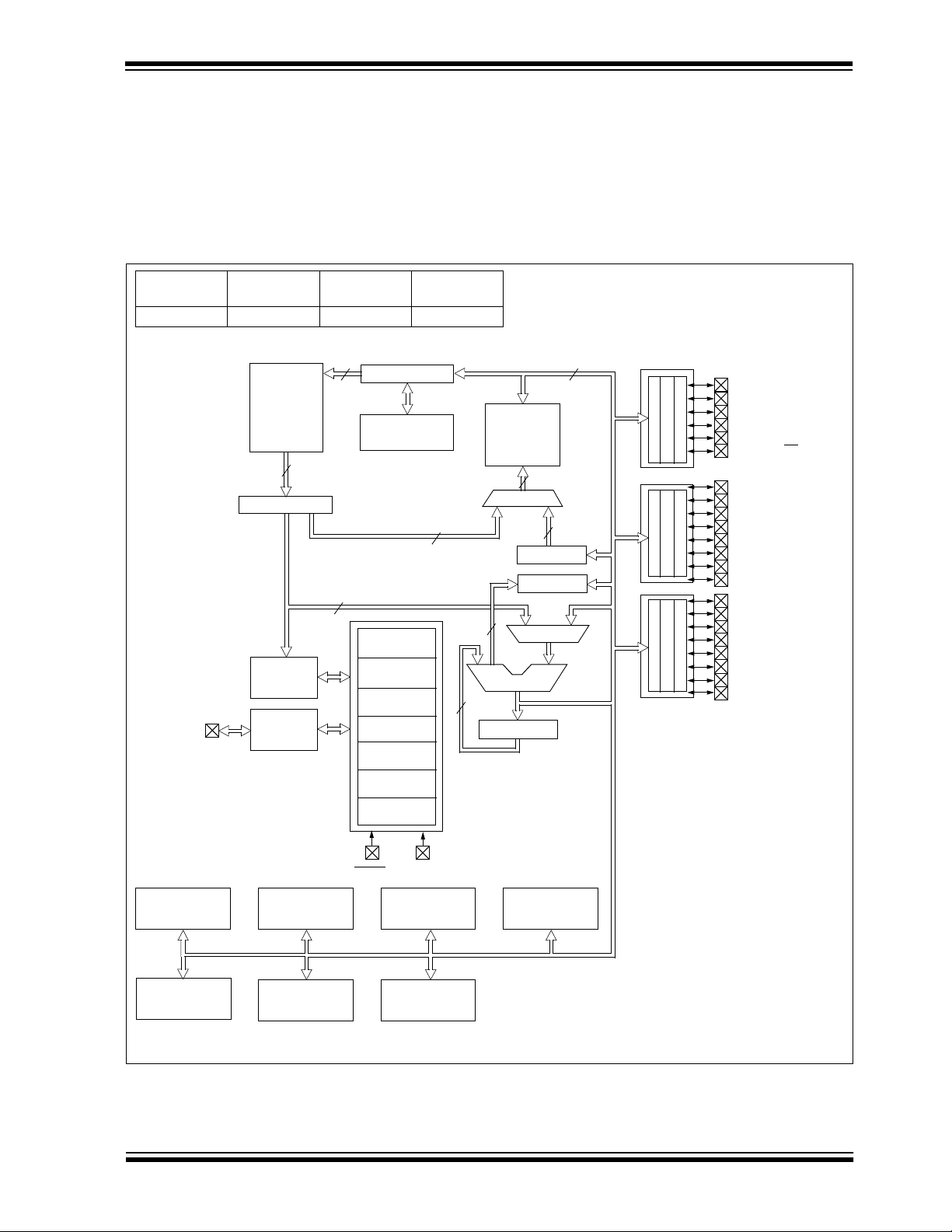

1.0 DEVICE OVERVIEW

This document contains device-specific information.

Additional information may be found in the PICmicro™

Mid-Range Reference Manual, (DS33023), which may

be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The

Reference Manual should be considered a comple-

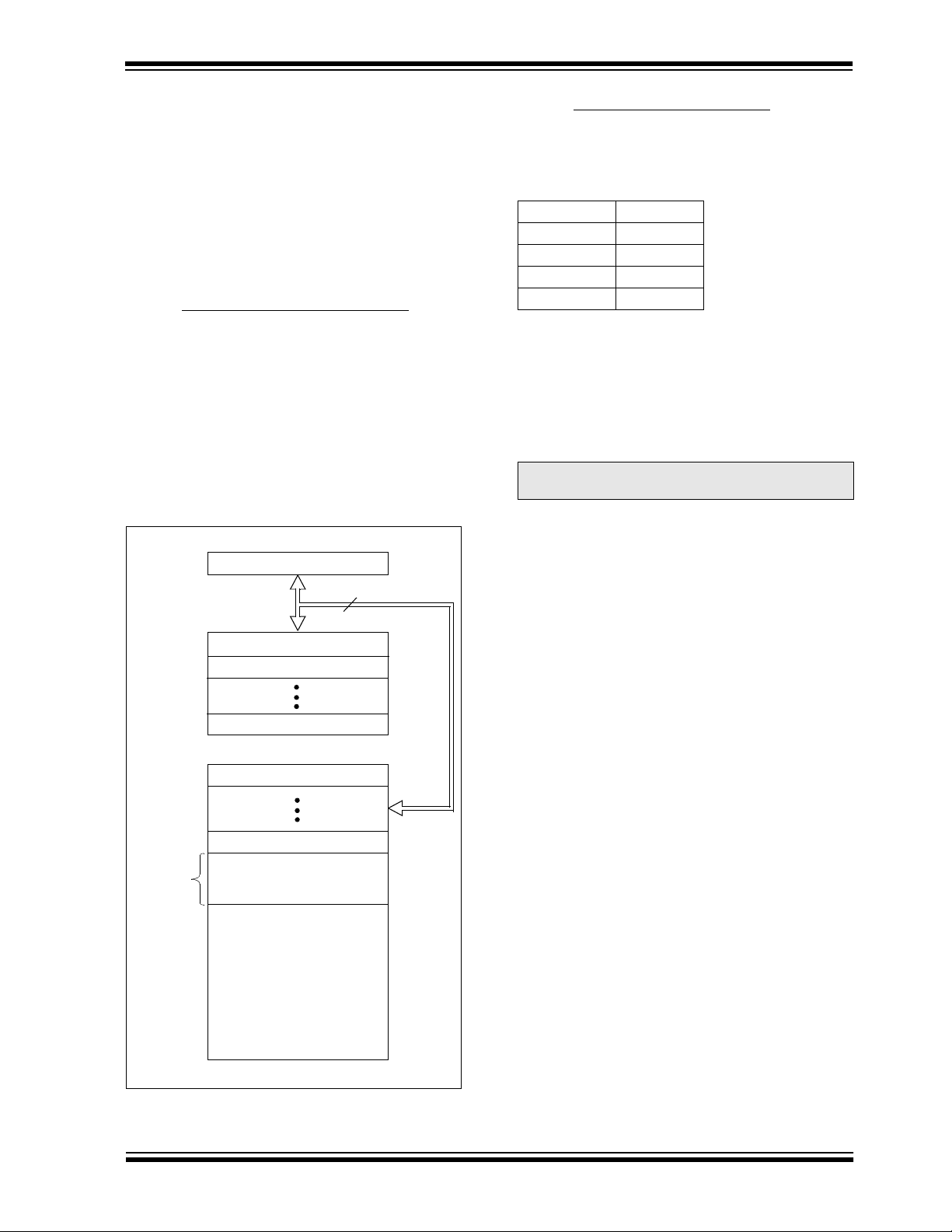

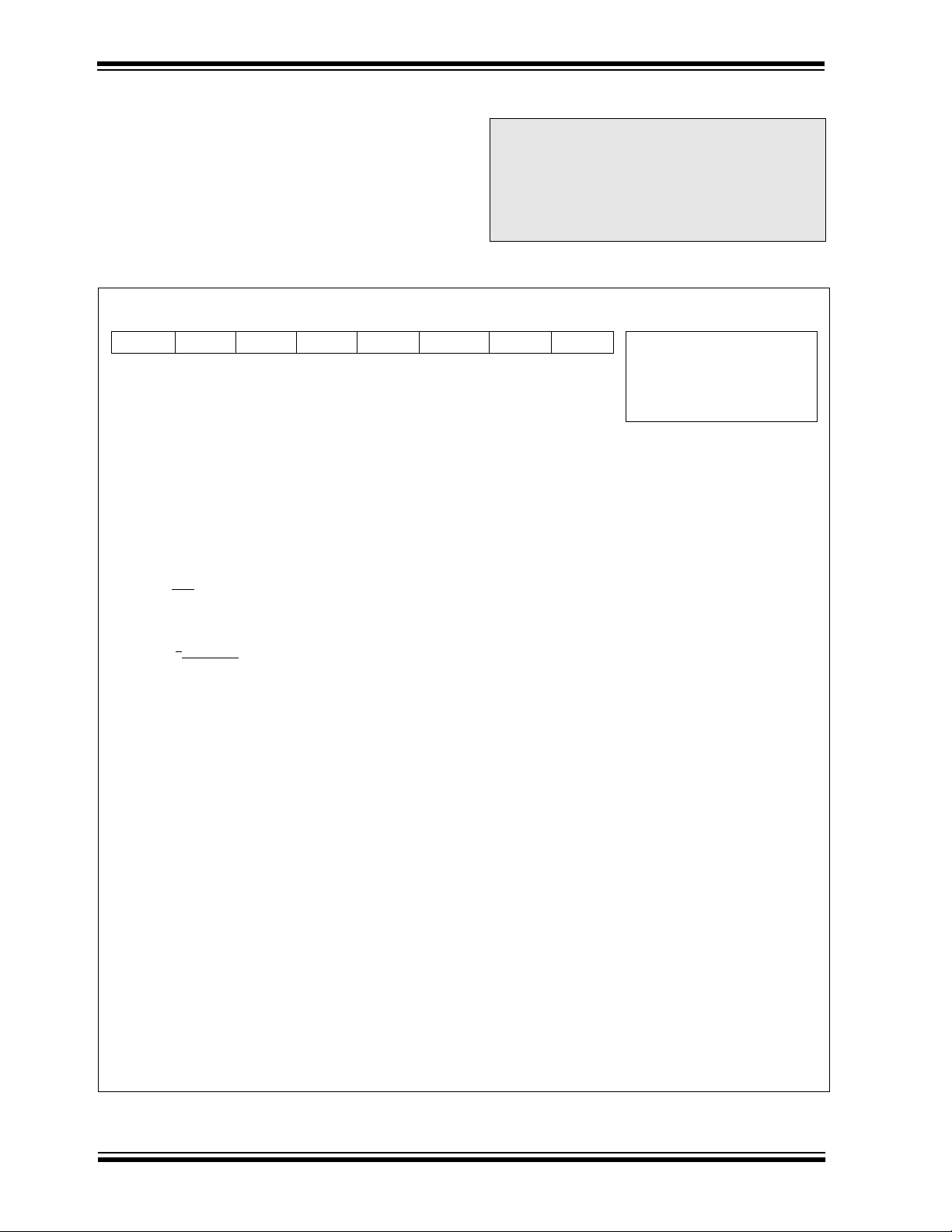

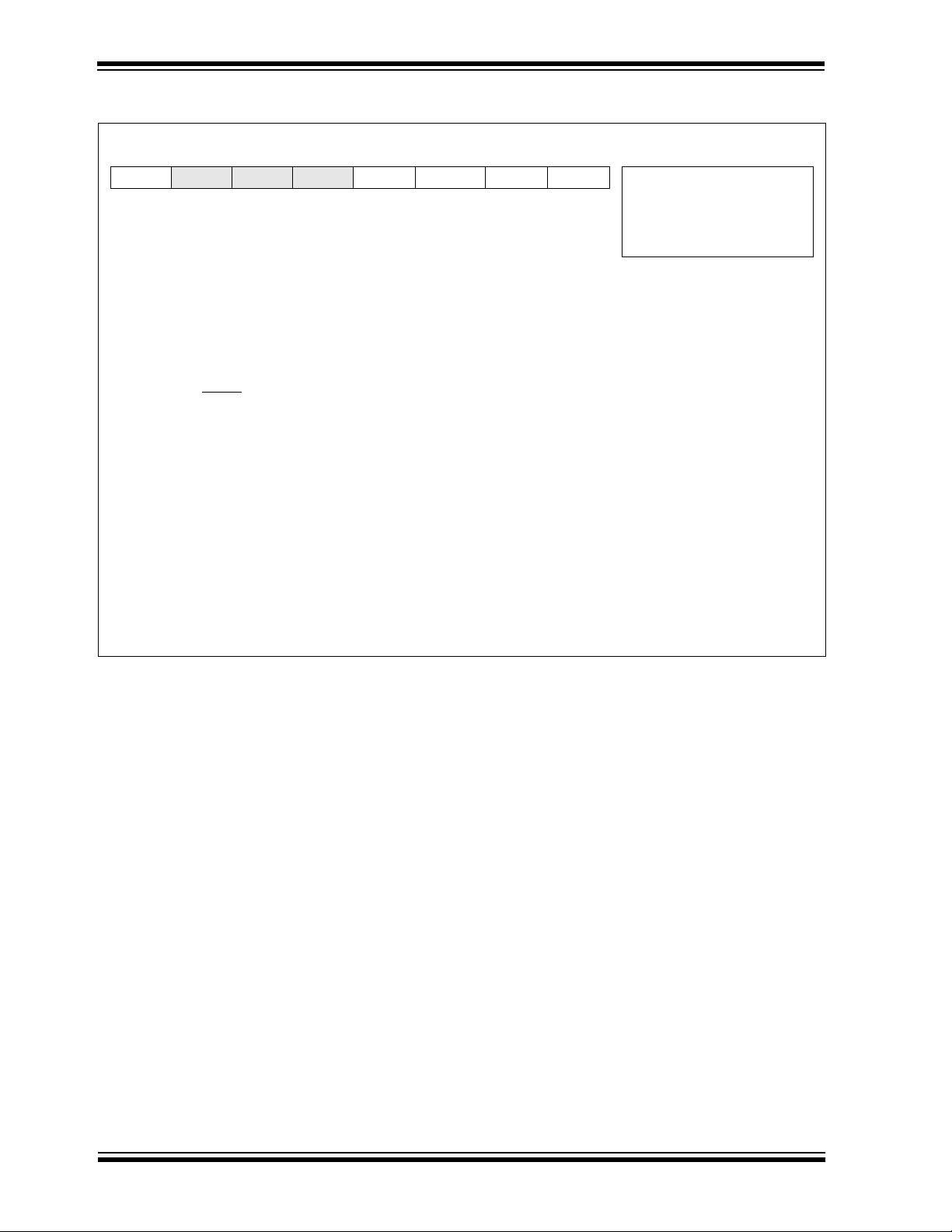

FIGURE 1-1: PIC16F872 BLOCK DIAGRAM

Device Program

FLASH

PIC16F872 2K 128 Bytes 64 Bytes

FLASH

Program

Memory

Program

OSC1/CLKIN

OSC2/CLKOUT

Bus

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

Data Memory Data

EEPROM

13

Program Counter

8 Level Stack

(13-bit)

RAM Addr (1)

Direct Addr

8

Start-up Timer

Power-up

Timer

Oscillator

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

In-Circuit

Debugger

Low-Voltage

Programming

7

mentary document to this data she et, and is high ly recommended reading for a better understanding of the

device architecture and operation of the peripheral

modules.

This data sheet covers the PIC16F872 device. The

PIC16F872 is a 28-pin device and its block diagram is

shown in Figure 1-1.

3

8

Data Bus

RAM

File

Registers

Addr MUX

FSR reg

STATUS reg

ALU

W reg

9

8

MUX

8

Indirect

Addr

PORTA

PORTB

PORTC

RA0/AN0

RA1/AN1

RA2/AN2/VREFRA3/AN3/VREF+

RA4/T0CKI

RA5/AN4/SS

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RC0/T1OSO/T1CKI

RC1/T1OSI

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6

RC7

VDD, VSS

MCLR

Data EEPROM

CCP1

Synchronous

Serial Port

Note 1: Higher order bits are from the STATUS register.

1999 Microchip Technology Inc.

10-bit A/DTimer0 Timer1 Timer2

Preliminary DS30221A-page 5

Page 6

PIC16F872

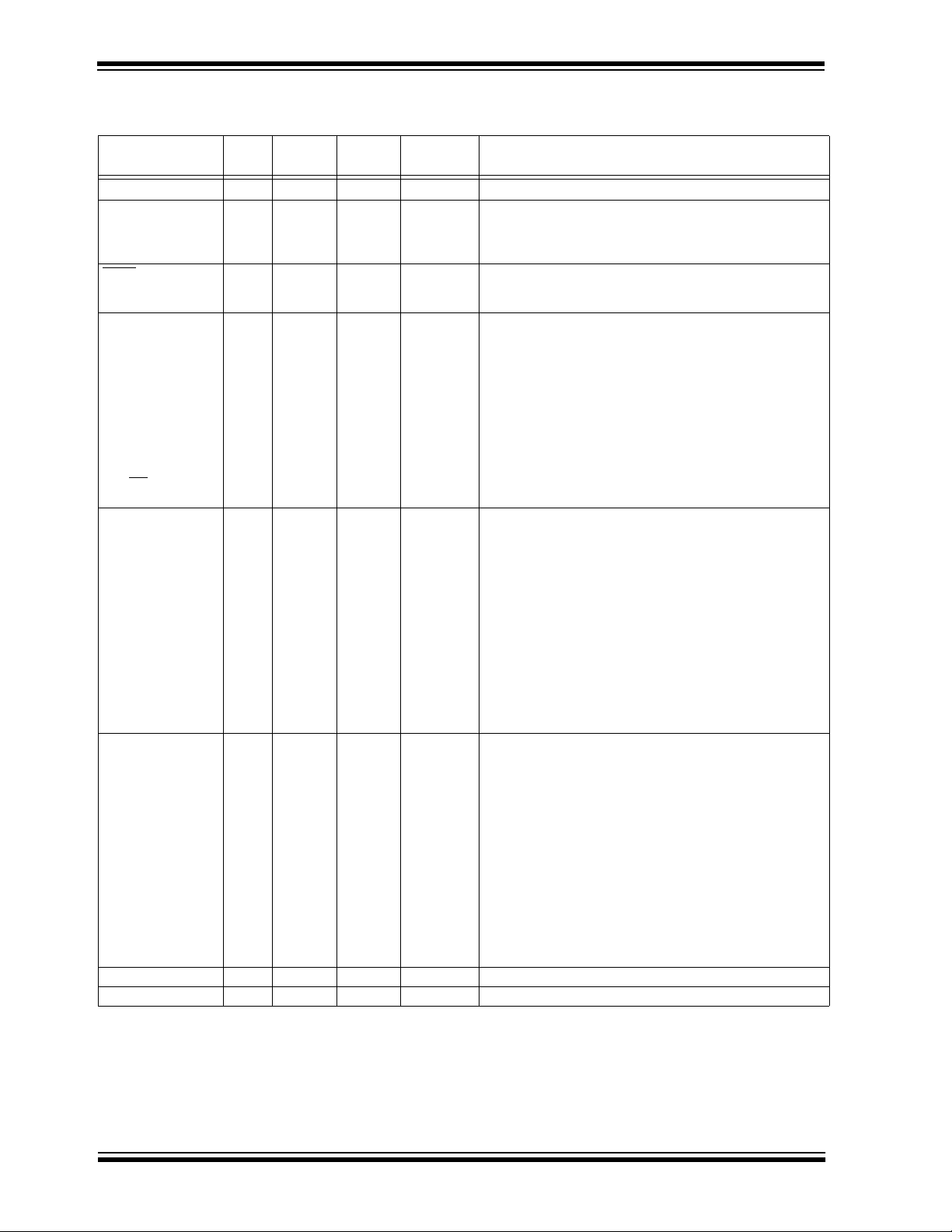

TABLE 1-1: PIC16F872 PINOUT DESCRIPTION

Pin Name

OSC1/CLKIN 9 9 I

OSC2/CLKOUT 10 10 O — Oscillator crystal output. Connects to crystal or resonator in crystal

/VPP/THV 1 1 I/P ST Master clear (reset) input or programming voltage input or high

MCLR

RA0/AN0 2 2 I/O TTL RA 0 c a n al so be analog inpu t0.

RA1/AN1 3 3 I/O TTL RA 1 c a n al so be analog inpu t1.

RA2/AN2/V

RA3/AN3/V

RA4/T0CKI 6 6 I/O ST RA4 can also be the cloc k inp ut to the Timer0 module . Outp ut

RA5/SS/

RB0/INT 21 21 I/O

RB1 22 22 I/O TTL

RB2 23 23 I/O TTL

RB3/PGM 24 24 I/O

RB4 25 2 5 I/O TTL Interrupt on cha n g e pi n .

RB5 26 2 6 I/O TTL Interrupt on cha n g e pi n .

RB6/PGC 27 27 I/O

RB7/PGD 28 28 I/O

RC0/T1OSO /T 1 C K I 11 11 I/O ST RC0 can also be the Timer1 oscillator output or Timer1 cl ock

RC1/T1OSI 12 12 I/O ST RC1 can also be the Timer1 oscillator input.

RC2/CCP1 13 13 I/O ST RC2 can also be the Capture1 input/Compare1 outpu t/PWM1

RC3/SCK/SCL 14 14 I/O ST RC3 can also be the synchronous serial clo ck input /output for

RC4/SDI/SDA 15 15 I/O ST RC4 can also be the SPI Data In (SPI mode) or

RC5/SDO 16 16 I/O ST RC5 can also be the SPI Data Out (SPI mode).

RC6 17 17 I/O ST

RC7 18 18 I/O ST

SS 8, 19 8, 19 P — Ground reference for logic and I/O pins.

V

DD 20 20 P — Positive supply for logic and I/O pins.

V

Legend: I = input O = output I/O = input/output P = power

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP.

REF- 4 4 I/O TTL RA2 can also be analog input2 or negative analog reference

REF+ 5 5 I/O TTL RA3 can also be analog input3 or positive analog reference

AN4 7 7 I/O TTL RA 5 c a n al so be analog in pu t 4 or t h e s lave sel ect for the

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

DIP

Pin#

— = Not used TTL = TTL input ST = Schmitt Trigger input

SOIC

Pin#

I/O/P

Type

Buffer

Type

ST/CMOS

TTL/ST

TTL/ST

TTL/ST

TTL/ST

Description

(3)

Oscillator crystal input/external clock source input.

oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT,

which has 1/4 the frequency of OSC1 and denotes the instruction

cycle rate.

voltage test mode control. This pin is an active low reset to the

device.

PORTA is a bi-directional I/O port.

voltage.

voltage.

is open drain type.

synchronous serial port.

PORTB is a bi-directi onal I/O port. PORTB can be sof tware

programmed f or internal weak pull-up on all inputs.

(1)

(1)

(2)

(2)

RB0 can also be the external int er rupt pin.

RB3 can als o be the low voltage pro gra m m i ng input.

Interrupt on change pin or In-Circuit Debugger pin. Serial

programming clock.

Interrupt on change pin or In-Circuit Debugger pin. Serial

programming data.

PORTC is a bi-directional I/O port.

input.

output.

2

both SPI and I

data I/O (I

C modes.

2

C mode).

DS30221A-page 6 Preliminary

1999 Microchip Technology Inc.

Page 7

PIC16F872

2.0 MEMORY ORGANIZATION

There are three memory blocks in each of these

PICmicro

Memory have separate buses, so that concurrent

access can occur, and is detailed in this section. The

EEPROM data memory block is detailed in

Section 4.0.

Additional inf ormation on de vice m emory may be f ound

in the PICmicro Mid-Range Reference Manual,

(DS33023).

2.1 Program Memory Organization

The PIC16F872 dev ices ha v e a 13-b it prog ram co unter

capable of addressing an 8K x 14 program memory

space. The PIC16F872 device has 2K x 14 words of

FLASH program me mory. Accessing a locati on above

the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is

at 0004h.

FIGURE 2-1: PIC16F872 PROGRAM

®

MCUs. The Program Memory and Data

MEMORY MAP AND STACK

PC<12:0>

CALL, RETURN

RETFIE, RETLW

13

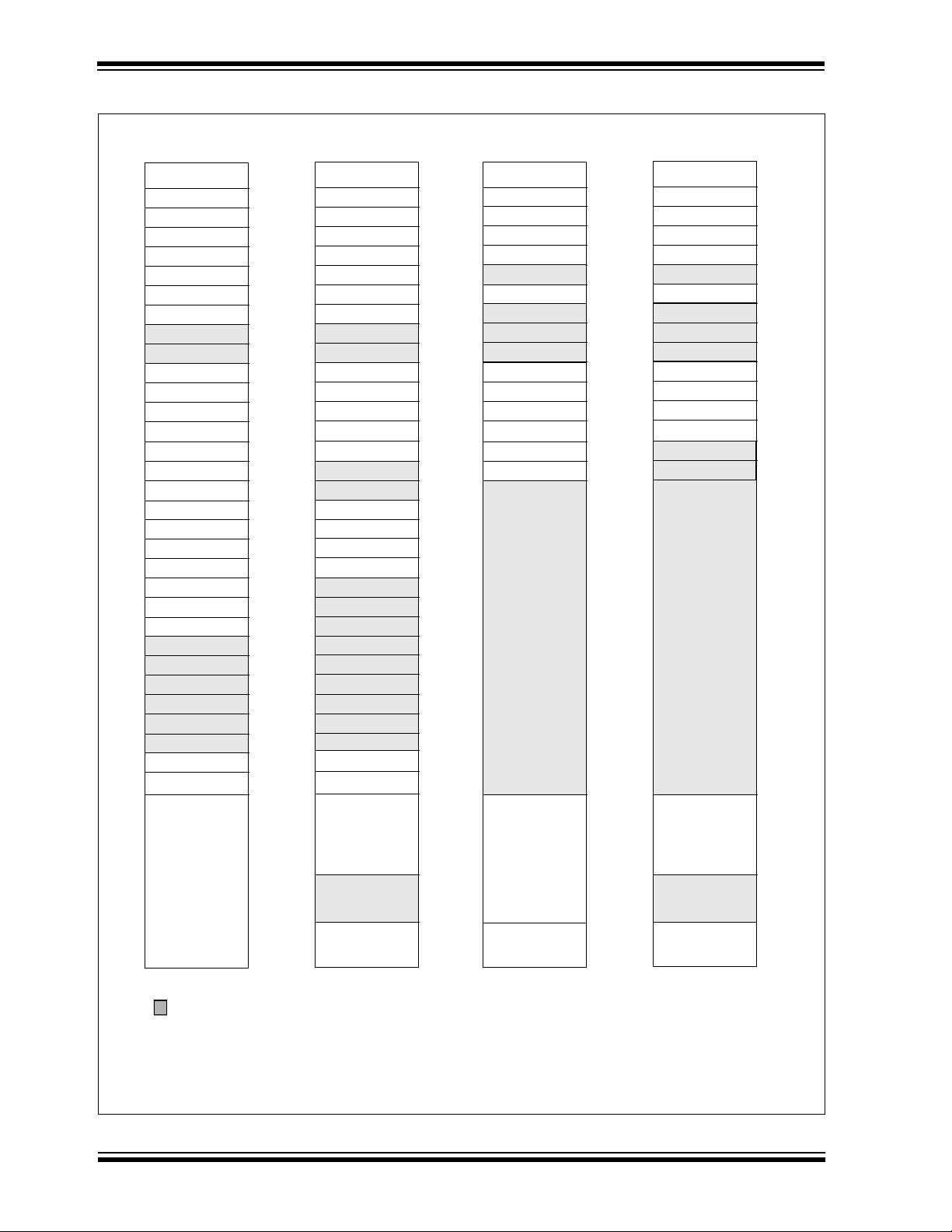

2.2 Data Memory Organization

The data memory is partitioned into multiple banks

which contain the General Purpose Registers and the

Special Function Registers. Bits RP1(STATUS<6>)

and RP0 (STATUS<5>) are the bank select bits.

RP<1:0> Bank

00 0

01 1

10 2

11 3

Each bank extends up to 7Fh (128 bytes). The lower

locations of each bank are reserved for the Special

Function Registers . Abo v e the Spec ial Fun ction Re gisters are General Purpose Registers, implemented as

static RAM. All implemented banks contain Special

Function Registers. Some “high use” Special Function

Registers from one bank may be mirrored in another

bank for code reduction and quicker access.

Note: EEPROM Data Memory description can b e

found in Section 4.0 of this Data Sheet

2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be a ccessed ei ther direc tly, or indi-

rectly through the File Select Register FSR.

On-Chip

Program

Memory

Stack Level 1

Stack Level 2

Stack Level 8

Reset Vector

Interrupt Vector

Page 0

0000h

0004h

0005h

07FFh

0800h

1FFFh

1999 Microchip Technology Inc.

Preliminary DS30221A-page 7

Page 8

PIC16F872

FIGURE 2-2: PIC16F872 REGISTER FILE MAP

PCL

FSR

PR2

(*)

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

BFh

C0h

EFh

F0h

FFh

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PORTC

(*)

00h

01h

02h

03h

04h

05h

06h

07h

Indirect addr .

OPTION_REG

STATUS

08h

09h

PCLATH

INTCON

PIR1

PIR2

TMR1L

TMR1H

T1CON

TMR2

T2CON

SSPBUF

SSPCON

CCPR1L

CCPR1H

CCP1CON

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

PCLATH

INTCON

SSPCON2

SSPADD

SSPSTAT

18h

19h

1Ah

1Bh

1Ch

1Dh

ADRESH

ADCON0 ADCON1

1Eh

1Fh

20h

ADRESL

General

Purpose

Register

General

Purpose

32 Bytes

Register

96 Bytes

accesses

Bank 0

7Fh

70h-7Fh

Bank 1

TRISA

TRISB

TRISC

PIE1

PIE2

PCON

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTB

PCLATH

INTCON

EEDATA

EEADR

EEDATH

EEADRH

accesses

20h-7Fh

accesses

70h-7Fh

Bank 2

File

Address

(*)

100h

101h

102h

103h

104h

Indirect addr.

OPTION_REG

PCL

STATUS

FSR

105h

106h

TRISB

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

PCLATH

INTCON

EECON1

EECON2

Reserved

Reserved

110h

120h

(*)

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

(1)

18Eh

(1)

18Fh

190h

1A0h

accesses

A0h - BFh

1BFh

1C0h

16Fh

170h

17Fh

accesses

70h-7Fh

1EFh

1F0h

1FFh

Bank 3

Unimplemented data memory locations, read as ’0’.

* Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

DS30221A-page 8 Preliminary

1999 Microchip Technology Inc.

Page 9

PIC16F872

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers can be classified into

two sets: core (CPU) and peripheral. Those registers

The Special Function Registers are registers used by

the CPU and peripheral modules for controlling the

desired operation of the device. These registers are

implemented as static RAM. A list of these registers is

given in Table 2-1.

associated with the core functions are described in

detail in this section. Those related to the operation of

the peripheral features are described in detail in the

peripheral feature section.

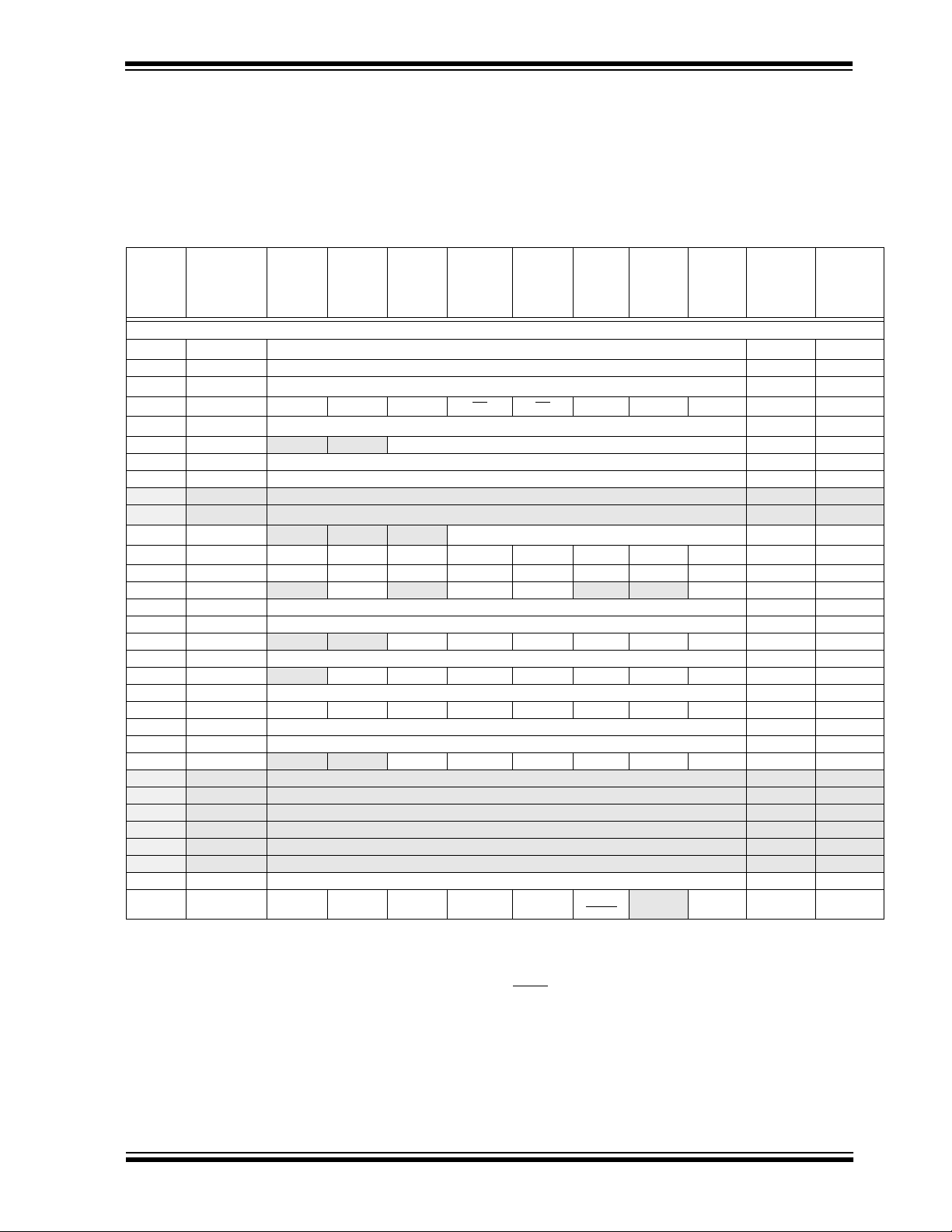

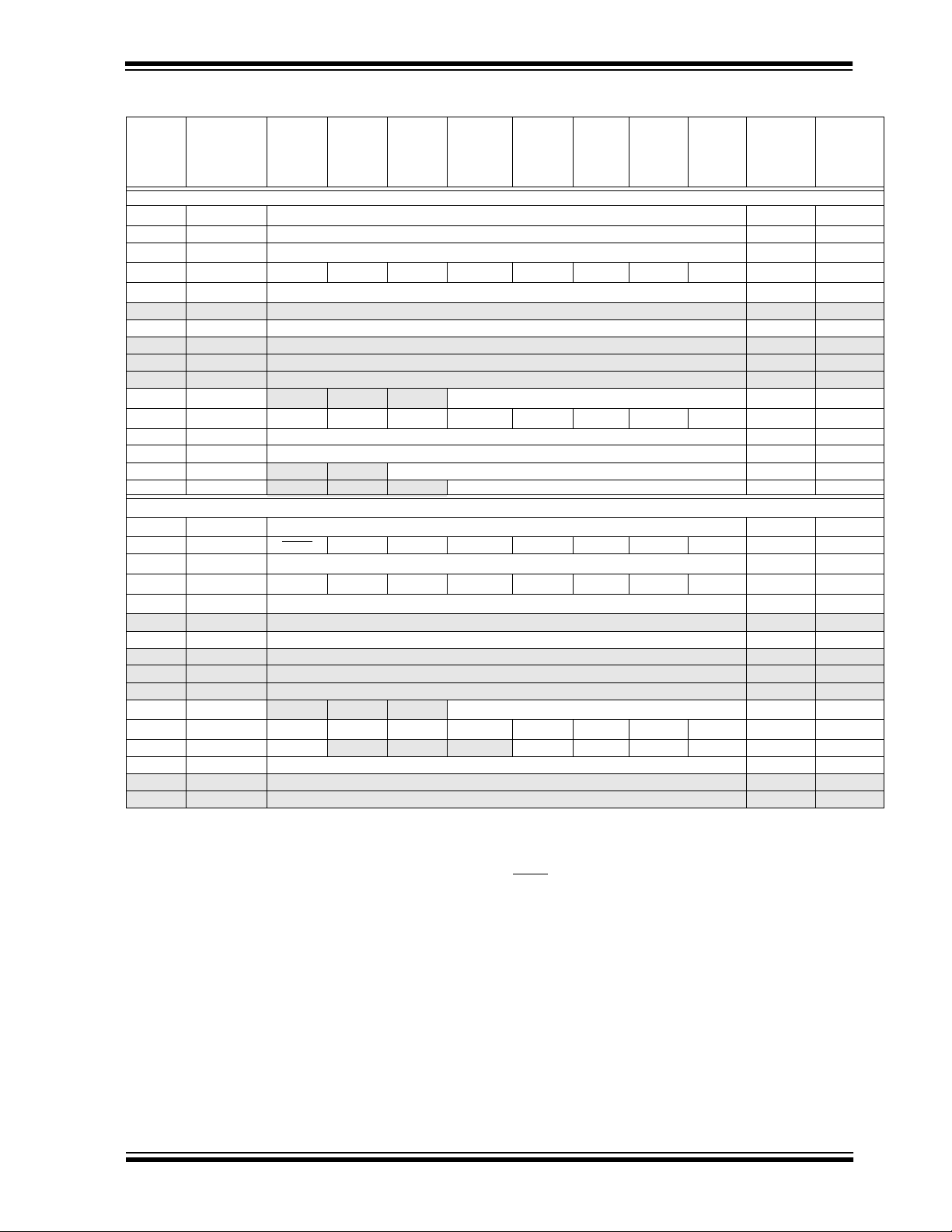

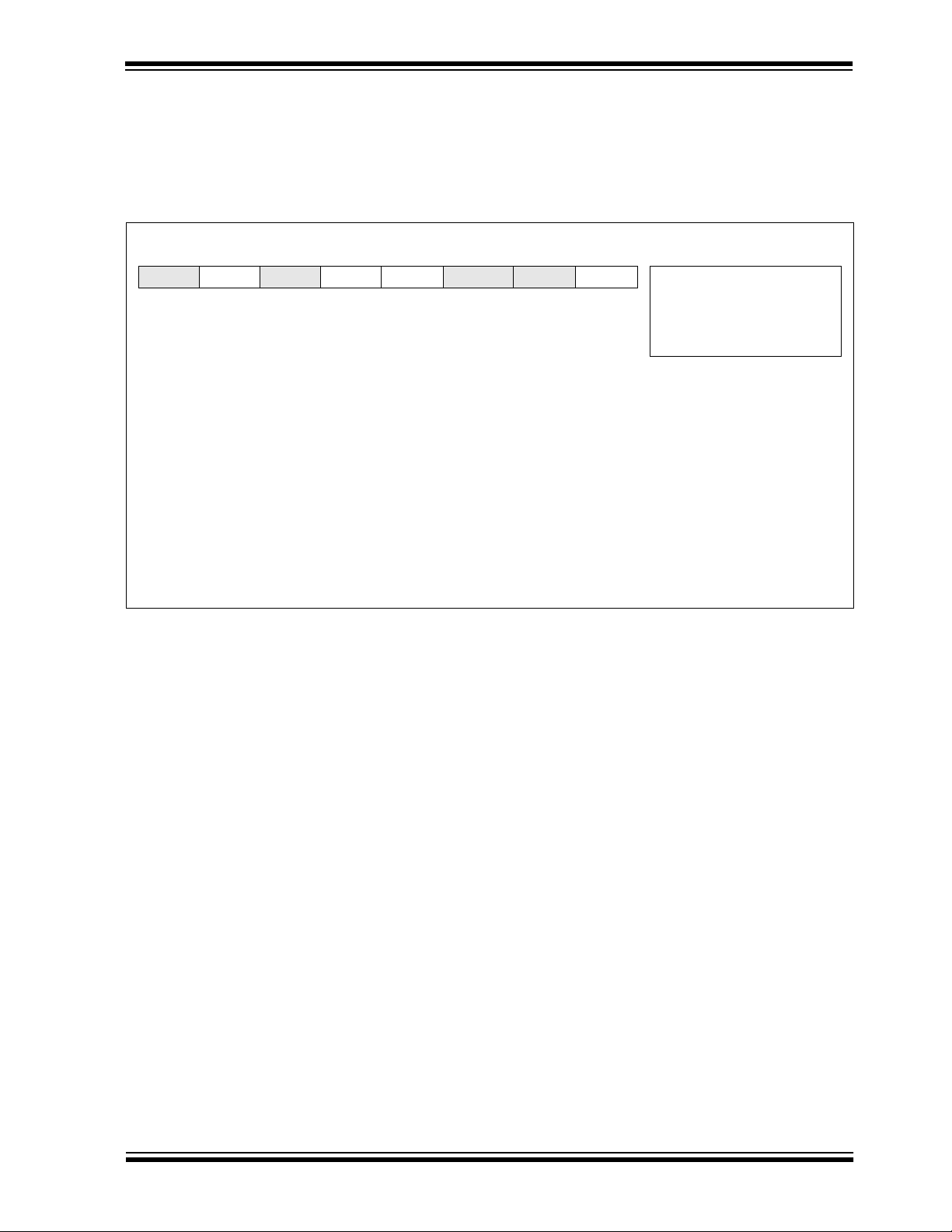

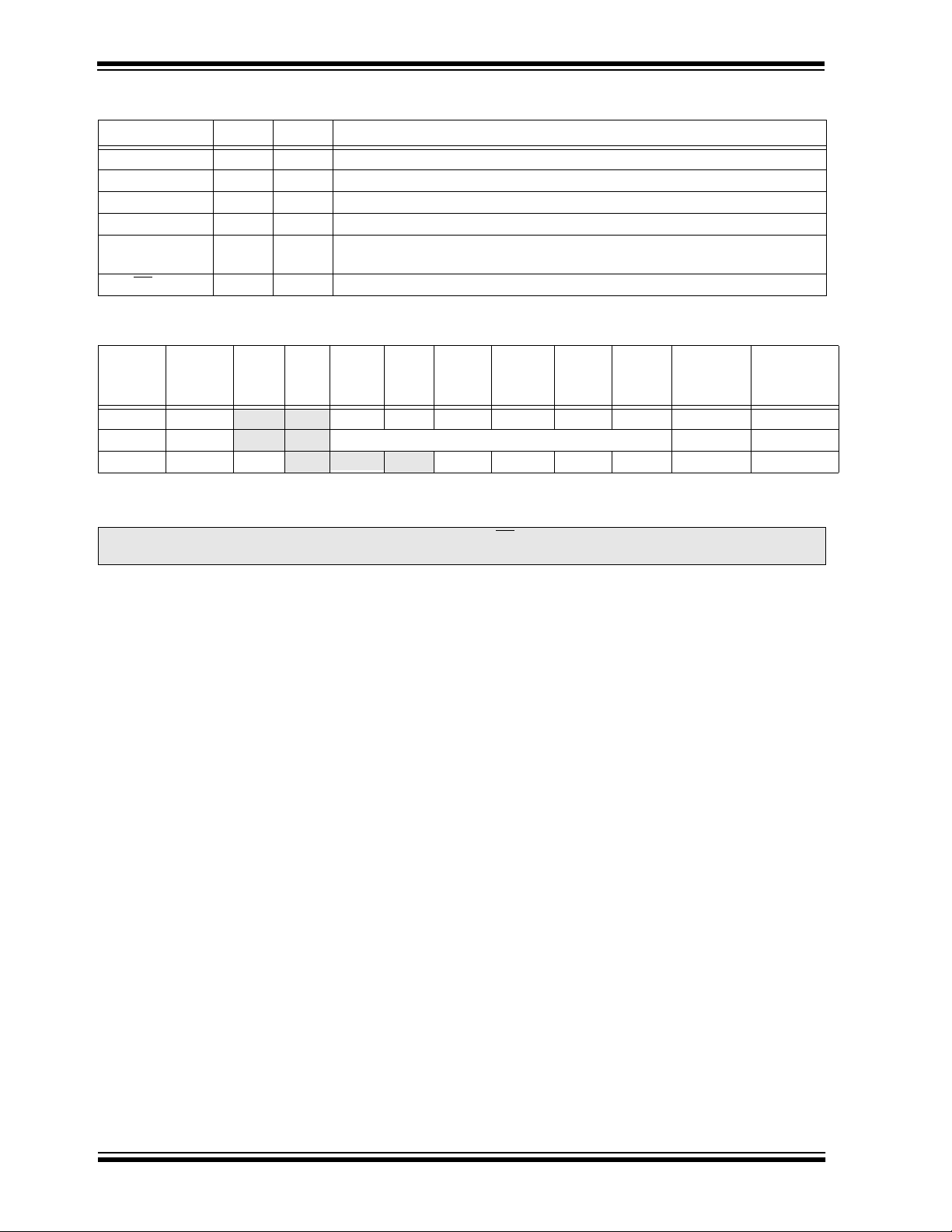

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR,

BOR

Bank 0

(3)

00h

01h TMR0 Timer0 module’s register xxxx xxxx uuuu uuuu

02h

03h

04h

05h POR TA

06h POR TB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

07h PORTC PORTC Data Latch when written: PORTC pins when read xxxx xxxx uuuu uuuu

08h — Unimplemented — —

09h

0Ah

0Bh

0Ch PIR1 (4) ADIF (4) (4) SSPIF CCP1IF TMR2IF TMR1IF r0rr 0000 r0rr 0000

0Dh PIR2

0Eh TMR1L Holding register for the Least Significant Byte of the 16-bit TMR1 register xxxx xxxx uuuu uuuu

0Fh TMR1H Holding register for the Most Significant Byte of the 16-bit TMR1 register xxxx xxxx uuuu uuuu

10h T1CON

11h TMR2 Timer2 module’s register 0000 0000 0000 0000

12h T2CON

13h SSPBUF Synchronous Serial Port Receive Buffer/Transmit Register xxxx xxxx uuuu uuuu

14h SSPCON WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0 0000 0000 0000 0000

15h CCPR1L Capture/Compare/PWM Register1 (LSB) xxxx xxxx uuuu uuuu

16h CCPR1H Capture/Compare/PWM Register1 (MSB) xxxx xxxx uuuu uuuu

17h CCP1CON

18h — Unimplemented — —

19h — Unimplemented — —

1Ah — Unimplemented — —

1Bh — Unimplemented — —

1Ch — Unimplemented — —

1Dh — Unimplemented — —

1Eh ADRESH A/D Result Register High Byte xxxx xxxx uuuu uuuu

1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’, r = reserved.

Note 1: The upper byte of the program counter is not directly accessible. PCLA TH is a holding register for the PC<12:8> whose

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

(3)

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

(3)

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

(3)

FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu

— — PORTA Data Latch when written: PORTA pins when read --0x 0000 --0u 0000

— Unimpleme nted — —

(1,3)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(3)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— (4) — EEIF BCLIF — — (4) -r-0 0--r -r-0 0--r

— — T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON --00 0000 --uu uuuu

— TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 -000 0000

— — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 --00 0000 --00 0000

GO/

DONE

—ADON0000 00-0 0000 00-0

Shaded locations are unimplemented, read as ‘0’.

contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from any bank.

4: These bits are reserved; always maintain these bits clear.

Value on

all other

resets

(2)

1999 Microchip Technology Inc.

Preliminary DS30221A-page 9

Page 10

PIC16F872

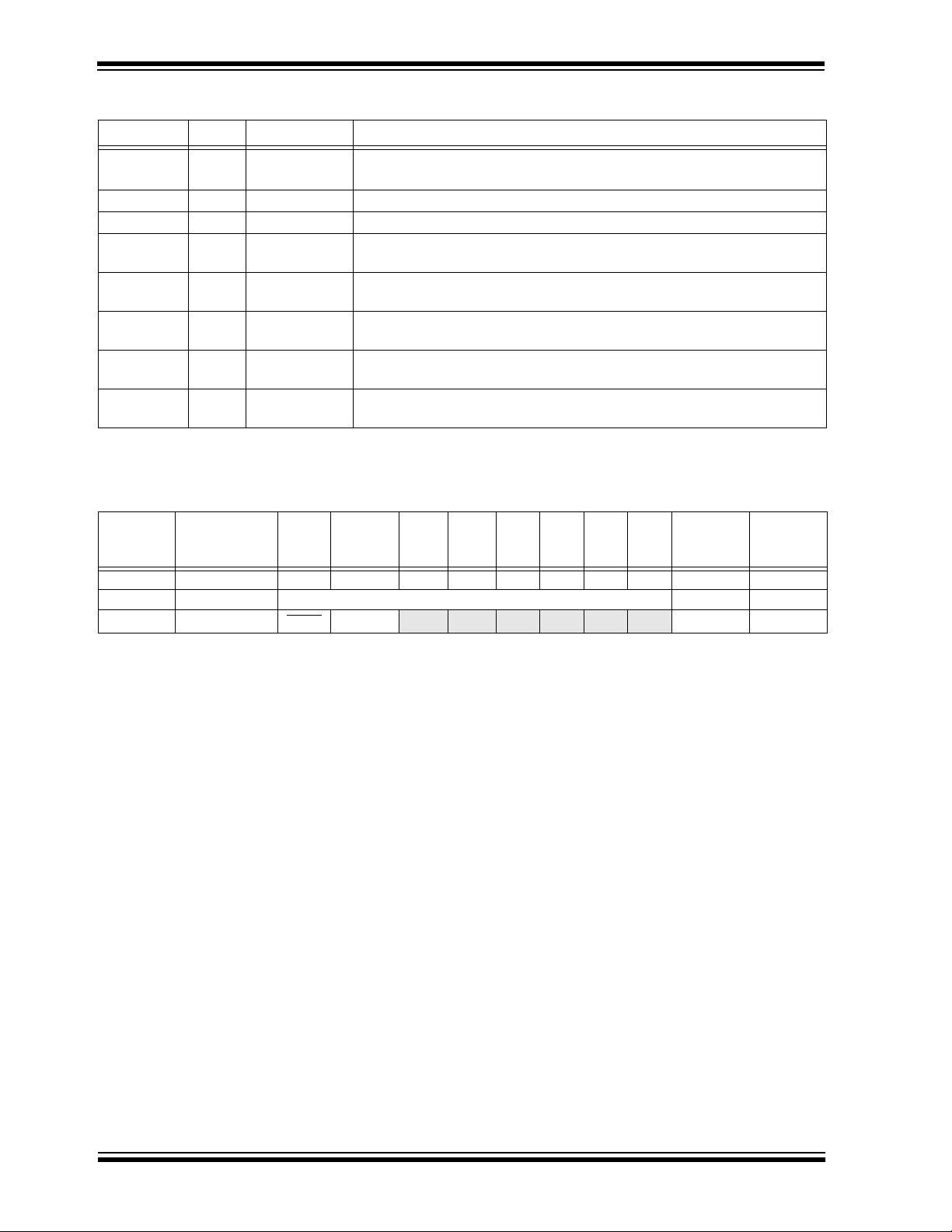

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR,

BOR

Value on:

Bank 1

(3)

80h

81h OPTION_REG RBPU

82h

83h

84h

85h TRISA

86h TRISB PORTB Data Direction Register 1111 1111 1111 1111

87h TRISC PORTC Data Direction Register 1111 1111 1111 1111

88h — Unimplemented — —

89h — Unimplemented — —

8Ah

8Bh

8Ch PIE1 (4) ADIE (4) (4) SSPIE CCP1IE TMR2IE TMR1IE r0rr 0000 r0rr 0000

8Dh PIE2

8Eh PCON

8Fh — Unimplemented — —

90h — Unimplemented — —

91h SSPCON2 GCEN ACKSTAT ACKDT ACKEN RCEN PEN RSEN SEN 0000 0000 0000 0000

92h PR2 Timer2 Period Register 1111 1111 1111 1111

93h SSPADD

94h SSPSTAT SMP CKE D/A

95h — Unimplemented — —

96h — Unimplemented — —

97h — Unimplemented — —

98h — Unimplemented — —

99h — Unimplemented — —

9Ah — Unimplemented — —

9Bh — Unimplemented — —

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh ADRESL A/D Result Register Low Byte xxxx xxxx uuuu uuuu

9Fh ADCON1 ADFM

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

(3)

PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

(3)

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

(3)

FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu

— — PORTA Data Direction Register --11 1111 --11 1111

(1,3)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(3)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— (4) — EEIE BCLIE — — (4) -r-0 0--r -r-0 0--r

— — — — — —PORBOR ---- --qq ---- --uu

Synchronous Serial Port (I

— — — PCFG3 PCFG2 PCFG1 PCFG0 0--- 0000 0--- 0000

2

C mode) Address Register

PSR/WUA BF 0000 0000 0000 0000

0000 0000 0000 0000

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’, r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose

contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from any bank.

4: These bits are reserved; always maintain these bits clear.

Value on

all other

resets

(2)

DS30221A-page 10 Preliminary

1999 Microchip Technology Inc.

Page 11

PIC16F872

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR,

BOR

Bank 2

(3)

100h

101h TMR0 Timer0 module’s register xxxx xxxx uuuu uuuu

102h

103h

104h

105h — Unimplemented — —

106h PORTB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

107h — Unimplemented — —

108h — Unimplemented — —

109h — Unimplemented — —

10Ah

10Bh

10Ch EEDATA EEPROM data register xxxx xxxx uuuu uuuu

10Dh EEADR EEPROM address register xxxx xxxx uuuu uuuu

10Eh EEDATH

10Fh EEADRH

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

(3)

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

(3)

STAT US IRP RP1 RP0 TO PD Z DC C 0001 1xxx 000q quuu

(3)

FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu

(1,3)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(3)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— — EEPROM data register high byte xxxx xxxx uuuu uuuu

— — — EEPROM address register high byte xxxx xxxx uuuu uuuu

Bank 3

(3)

180h

181h OPTION_REG RBPU

182h

183h

184h

185h — Unimplemented — —

186h TRISB PORTB Data Direction Register 1111 1111 1111 1111

187h — Unimplemented — —

188h — Unimplemented — —

189h — Unimplemented — —

18Ah

18Bh

18Ch EECON1 EEPGD

18Dh EECON2 EEPROM control register2 (not a physical register) ---- ---- ---- ---18Eh — Reserved maintain clear 0000 0000 0000 0000

18Fh — Reserved maintain clear 0000 0000 0000 0000

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’, r = reserved.

Note 1: The upper byte of the program counter is not directly accessible. PCLA TH is a holding register for the PC<12:8> whose

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

(3)

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

(3)

STAT US IRP RP1 RP0 TO PD Z DC C 0001 1xxx 000q quuu

(3)

FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu

(1,3)

PCLATH — — —

(3)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— — — WRERR WREN WR RD x--- x000 x--- u000

Write Buffer for the upper 5 bits of the Program Counter

---0 0000 ---0 0000

Shaded locations are unimplemented, read as ‘0’.

contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from any bank.

4: These bits are reserved; always maintain these bits clear.

Value on

all other

resets

(2)

1999 Microchip Technology Inc.

Preliminary DS30221A-page 11

Page 12

PIC16F872

2.2.2.1 STATUS REGISTER

The STATUS register contains the arithmetic status of

the ALU, the R ESET st atus an d the ba nk sel ect bi ts f or

data memory.

The STATUS register can be the destination for any

instruction, as with any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. The se bi ts ar e set or c leared accordi ng to the

device logic. Fur th er more, the TO

writable, therefore, the result of an instruction with the

STATUS re gister as desti nation may be different t han

intended.

and PD bits are not

For example, CLRF STATUS will clear the up p er- t h ree

bits and set th e Z bi t. T his l ea v es the STATUS register

as 000u u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register, because these instructions do not

affect the Z, C or DC b its from the STA TUS register. For

other instructions not affecting any status bits, see the

"Instruction Set Summary."

Note: The C and DC bits operate as a borrow

and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO PD Z DC C R = Readable bit

bit7 bit0

bit 7: IRP: Register Bank Select bit (used for indirect address in g)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5: RP<1:0>: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4: TO

bit 3: PD

bit 2: Z: Zero bit

bit 1: DC: Digit carry/borrow

bit 0: C: Carry/borrow

: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP in struction

0 = A WDT time-out occurred

: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

(for borrow

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

1 = A carry-out from the most significant bit of the result occurred

0 = No carry-out from the most significant bit of the result occurred

Note: For borrow

the second operand. For rotate (RR F, RLF) instructions, this bit is loaded with ei ther the high or low o rder

bit of the source register.

the polarity is reversed)

bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

the polarity is reversed. A subtraction is executed by adding the two’s complement of

W = Writable bit

U = Unimplemented bit,

read as ‘0’

- n= Value at POR reset

DS30221A-page 12 Preliminary

1999 Microchip Technology Inc.

Page 13

PIC16F872

2.2.2.2 OPTION_REG REGISTER

The OPTION_REG Regis ter is a read ab le and writab le

register , which contai ns various c ontrol bits to c onfigure

the TMR0 prescaler/WDT postscaler (single assignable regist er kno wn also as the prescale r), the Ext ernal

INT Interrupt, TMR0 and the w eak pul l-ups on PO R TB .

REGISTER 2-2: OPTION_REG REGISTER (ADDRESS 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 R = Readable bit

bit7 bit0

bit 7: RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6: INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5: T0CS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4: T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3: PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0: PS<2:0>: Prescaler Rate Select bits

Bit Value T MR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Note: To achieve a 1:1 prescaler assignme nt for

the TMR0 register, assign the prescaler to

the Watchdog Timer.

W = Writable bit

U = Unimplemented bit,

read as ‘0’

- n= Value at POR reset

Note: When using Low Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the

TRISB register must be c leared to disable the pull-up on RB3 and ens ure the proper operat ion of the dev ice.

1999 Microchip Technology Inc.

Preliminary DS30221A-page 13

Page 14

PIC16F872

2.2.2.3 INTCON REGISTER

The INTCON Regi ster i s a rea dab le a nd w ritabl e regi s-

ter, which contains various enable and flag bits for the

TMR0 register overflow, RB Port change and External

RB0/INT pin interrupts.

Note: Interrupt flag bits get set when an in terrupt

condition occurs , regardless of the sta te of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF R = Readable bit

bit7 bit0

bit 7: GIE: Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

bit 6: PEIE: Peripheral Interrupt Enable bit

1 = Enables all un-masked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5: T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4: INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3: RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2: T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1: INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0: RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB<7:4> pins changed state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

W = Writab le bit

U = Unimplemented bit,

read as ‘0’

- n= Value at POR reset

DS30221A-page 14 Preliminary

1999 Microchip Technology Inc.

Page 15

2.2.2.4 PIE1 REGISTER

PIC16F872

The PIE1 register contain s the individual en able bits for

the peri pheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— ADIE — — SSPIE CCP1IE TMR2IE TMR1IE R = Readable bit

bit7 bit0

bit 7: Reserved: Always maintain this bit clear

bit 6: ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D converter interrupt

0 = Disables the A/D converter interrupt

bit 5-4: Reserved: Always maintain this bit clear

bit 3: SSPIE: Synchronous Serial Port Interrupt Enable bit

1 = Enables the SSP interrupt

0 = Disables the SSP interrupt

bit 2: CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 1: TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0: TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

W = Writable bit

U = Unimplemented bit,

- n= Value at POR reset

read as ‘0’

1999 Microchip Technology Inc.

Preliminary DS30221A-page 15

Page 16

PIC16F872

2.2.2.5 PIR1 REGISTER

The PIR1 register contains the individual flag bits for

the peri pheral interrupts.

Note: Interrupt flag bits get set when an in terrupt

condition occurs , regardless of the sta te of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an

interrupt.

REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— ADIF — — SSPIF CCP1IF TMR2IF TMR1IF R = Readable bit

bit7 bit0

bit 7: Reserved: Always maintain this bit clear

bit 6: ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed

0 = The A/D conversion is not complete

bit 5-4: Reserved: Always maintain this bit clear

bit 3: SSPIF: Synchronous Serial Port (SSP) Interrupt Flag

1 = The SSP interrupt condition has oc curred , and mus t be cle ared in s oft w are b efore returning from the

interrupt service routine. The conditions that will set this bit are:

SPI

A transmission/reception has taken place.

2

I

C Slave

A transmission/reception has taken place.

2

C Master

I

A transmission/reception has taken place.

The initiated start condition was completed by the SSP module.

The initiated stop condition was completed by the SSP module.

The initiated restart condition was completed by the SSP module.

The initiated acknowledge condition was completed by the SSP module.

A start condition occurred while the SSP module was idle (Multimaster system).

A stop condition occurred while the SSP module was idle (Multimaster system).

0 = No SSP interrupt condition has occurred.

bit 2: CCP1IF: CCP1 Interrupt Flag bit

Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM Mode

Unused in this mode

bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 regi ster did not overflow

W = Writable bit

U = Unim plemented bit,

- n= Value at POR reset

read as ‘0’

DS30221A-page 16 Preliminary

1999 Microchip Technology Inc.

Page 17

2.2.2.6 PIE2 REGISTER

The PIE2 register contain s the individual en able bits for

the SSP bus collision interrupt and the EEPROM write

operation interrupt.

REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

U-0 R/W-0 U-0 R/W-0 R/W-0 U-0 U-0 R/W-0

——— EEIE BCLIE — — — R = Readable bit

bit7 bit0

bit 7: Unimplemented: Read as '0'

bit 6: Reserved: Always maintain this bit clear

bit 5: Unimplemented: Read as '0'

bit 4: EEIE: EEPROM Write Operation Interrupt Enable

1 = Enable EE Write Interrupt

0 = Disable EE Write Interrupt

bit 3: BCLIE: Bus Collision Interrupt Enable

1 = Enable Bus Collision Interrupt

0 = Disable Bus Collision Interrupt

bit 2-1: Unimplemented: Read as '0'

bit 0: Reserved: Always maintain this bit clear

W = Writable bit

U = Unimplemented bit,

- n= Value at POR reset

PIC16F872

read as ‘0’

1999 Microchip Technology Inc.

Preliminary DS30221A-page 17

Page 18

PIC16F872

2.2.2.7 PIR2 REGISTER

The PIR2 register contains the flag bits for the SSP bus

collision interrupt and the EEPROM write operation

interrupt.

.

Note: Interrupt flag bits get set when an in terrupt

condition occurs , regardless of the sta te of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

U-0 R/W-0 U-0 R/W-0 R/W-0 U-0 U-0 R/W-0

——— EEIF BCLIF — — — R = Readable bit

bit7 bit0

bit 7: Unimplemented: Read as '0'

bit 6: Reserved: Always maintain this bit clear

bit 5: Unimplemented: Read as '0'

bit 4: EEIF: EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation is not complete or has not been started

bit 3: BCLIF: Bus Collision Interrupt Flag

1 = A bus collision has occurred in the SSP, when configured for I

0 = No bus collision has occurred

bit 2-1: Unimplemented: Read as '0'

bit 0: Reserved: Always maintain this bit clear

2

W = Writable bit

U = Unimplemented bit,

- n= Value at POR reset

C master mode

read as ‘0’

DS30221A-page 18 Preliminary

1999 Microchip Technology Inc.

Page 19

PIC16F872

2.2.2.8 PCON REGISTER

The Power Control (PCON) Register contains flag bits

to allow differentiation between a Power-on Reset

(POR), a Brown-o ut Re set (BOR) , a Watch-d og Re set

(WDT) and an external MCLR

Reset.

Note: BOR is unknown on POR. It must be set by

the user and checked on subsequent

resets to see if BOR is clear, indicating a

brown-out ha s occurred. The BO R status

bit is a don’t care and is not predictable if

the brown-out ci rcuit i s disabled (by clea ring the BODEN bit in the configuration

word).

REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-1

— — — — — —PORBOR R = Readable bit

bit7 bit0

bit 7-2: Unimplemented: Read as '0'

bit 1: POR

bit 0: BOR

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in softwar e after a Brown- out Reset occurs)

W = Writable bit

U = Unimplemented bit,

- n= Value at POR reset

read as ‘0’

1999 Microchip Technology Inc.

Preliminary DS30221A-page 19

Page 20

PIC16F872

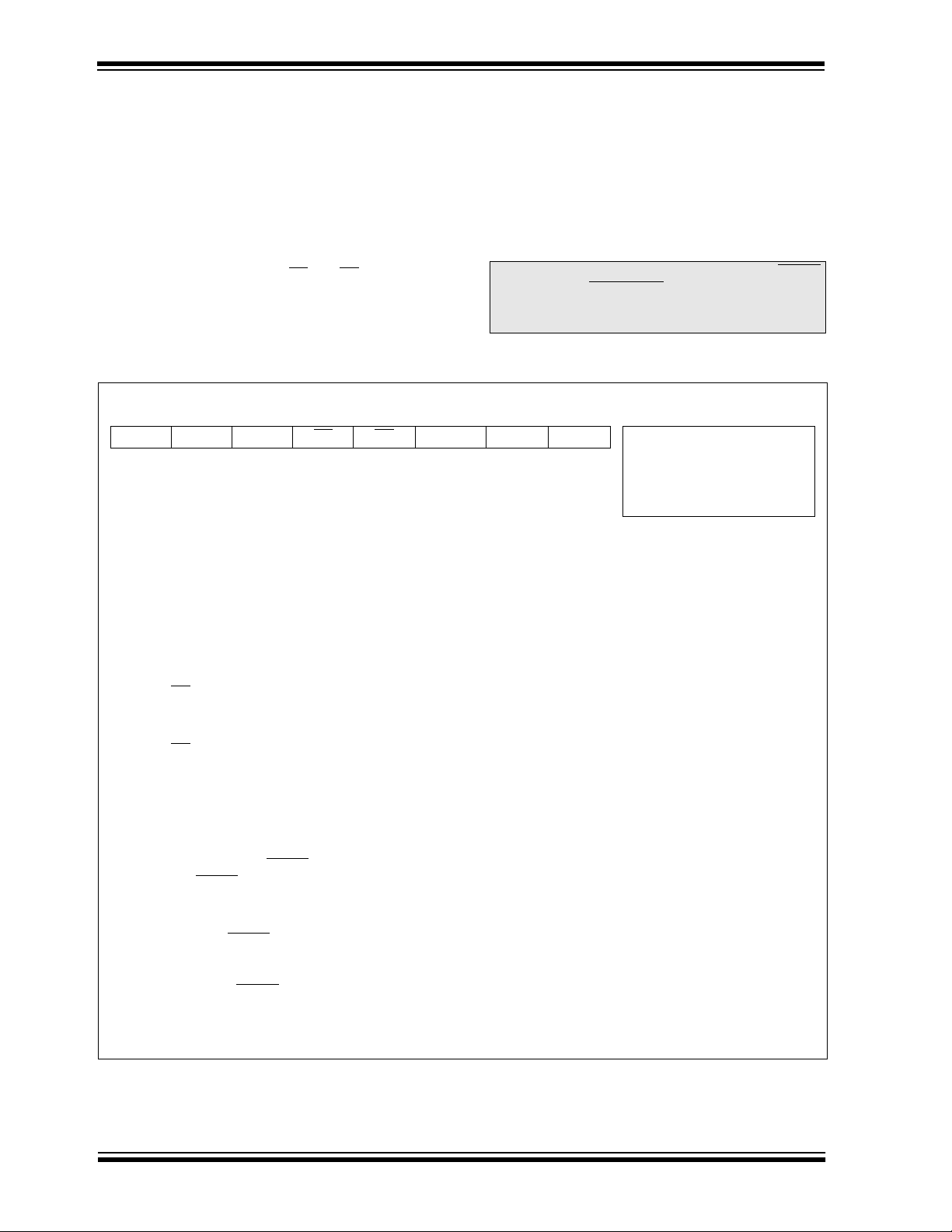

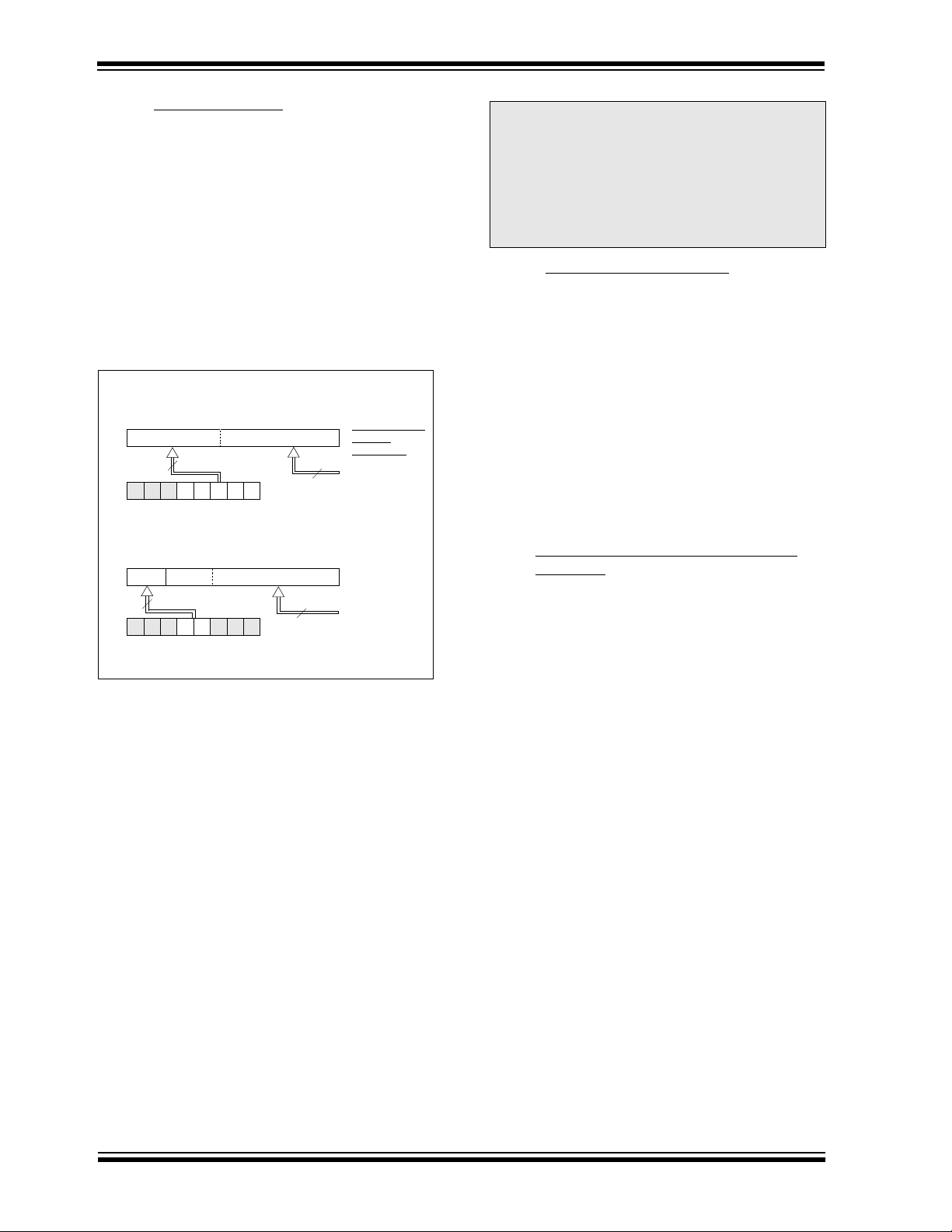

2.3 PCL and PCLATH

The program coun ter (PC) is 13-bits wide . The low b yte

comes from the PCL register, which is a readable and

writable register. The upper bits (PC<12:8>) are not

readable, but are indirectly writable through the

PCLATH register. On any reset, the upper bits of the

PC will be cleared. Figure 2-3 shows the two situations

for the loadin g of the PC . The up per e xa mple in the fi gure shows how the PC is loaded on a write to PCL

(PCLATH<4:0> → PCH). The lower example in the fig-

ure shows ho w the PC is loaded during a CALL or GOTO

instruction (PCLATH<4:3> → PCH).

FIGURE 2-3: LOADING OF PC IN

DIFFERENT SITUATIONS

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

PCLATH

11

2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by add ing an o ffs et

to the progra m counter (ADDWF PCL). When doing a

table read using a computed GOTO method, care

should be exercis ed i f t he table loc at ion c ros se s a PCL

memory boundary (each 256 byte block). Refer to the

application note,

“Implementing a Table Read"

(AN556).

2.3.2 STACK

The PIC16CXX f amily ha s an 8-le ve l deep x 13 -bit wide

hardware stack. T he stack space is not part of either

program or data space and the stack pointer is not

readable or writab le. The PC is PUSHed onto the stac k

when a CALL instruction is executed or an interrupt

causes a branch. The stack is POPed in the event of a

RETURN,RETLW or a RETFIE instruction execution.

PCLATH is not affected by a PUSH or POP operation.

The stack oper ates as a circular b uffer . This means that

after the stack has been PUSHed e ight ti mes , th e nin th

push overw rites th e value that was stored from the firs t

push. The tenth push overwrites the second push (and

so on).

8

Instruction with

PCL as

Destination

ALU

GOTO,CALL

Opcode <10:0>

Note 1: There are no status bits to indicate stack

overflow or stack underflow conditions.

2: There are no instructions/mnemonics

called PUSH or POP. These are actions that

occur from the execution of the CALL,

RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt

address.

2.4 Program Memory Paging

The PIC16CXXX architecture is capabl e of addressing

a continuous 8K word block of program memory. The

CALL and GOTO instructions provide 11 bits of the

address, which al lows br anche s within an y 2K prog ram

memory page. Therefore, the 8K words of program

memory are broken into four pages. Since the

PIC16FC872 has only 2K w ords of progr am memory or

one page, ad ditional code is not requ ired to e nsure th at

the correct page is selected before a CALL or GOTO

instruction is executed. The PCLATH<4:3> bits should

always be maintai ned as z ero s. If a return from a CALL

instruction (or interrupt) is executed, the entire 13-bit

PC is popped off the stack. Manipulation of the

PCLATH is not required for the return instructions.

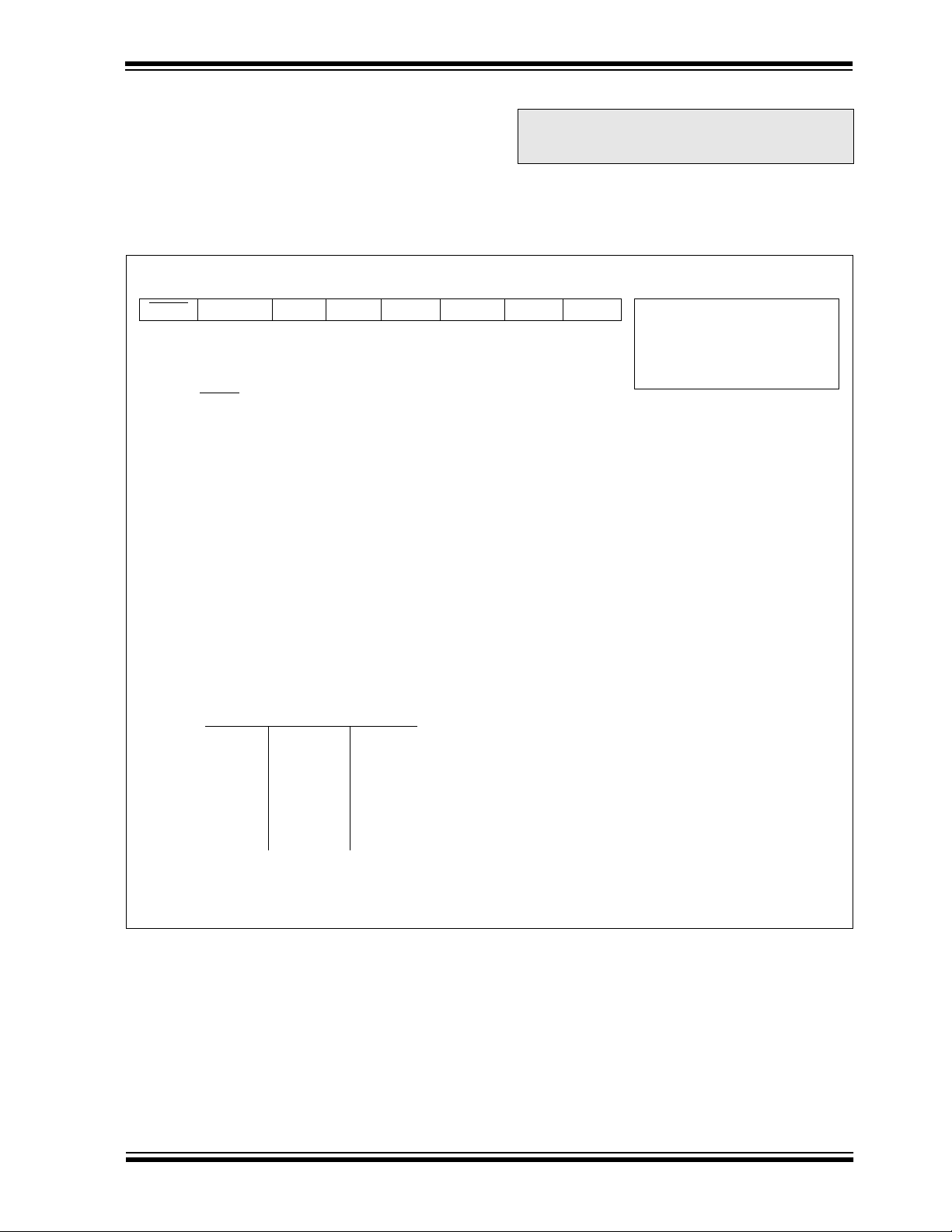

2.5 Indirect Addr essing, INDF and FSR

Registers

The INDF register is not a ph ysic al register . Addr essing

the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually

accesses the regist er pointed to b y the File Select Register, FSR. Reading the INDF register itself indirectly

(FSR = ’0’) will re ad 00h. Wr iting t o the INDF registe r

indirectly resu lts in a no-opera tion (although st atus bits

may be affected). An eff ec tiv e 9-bit addres s is o btaine d

by concatenatin g the 8-bit FSR register an d the IRP b it

(STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM locations 20h-2Fh

using indirect addressing is shown in Example 2-1.

EXAMPLE 2-1: INDIRECT ADDRESSING

movlw 0x20 ;initialize pointer

movwf FSR ;to RAM

NEXT clrf INDF ;clear INDF register

incf FSR,F ;inc pointer

btfss FSR,4 ;all done?

goto NEXT ;no clear next

CONTINUE

: ;yes continue

DS30221A-page 20 Preliminary

1999 Microchip Technology Inc.

Page 21

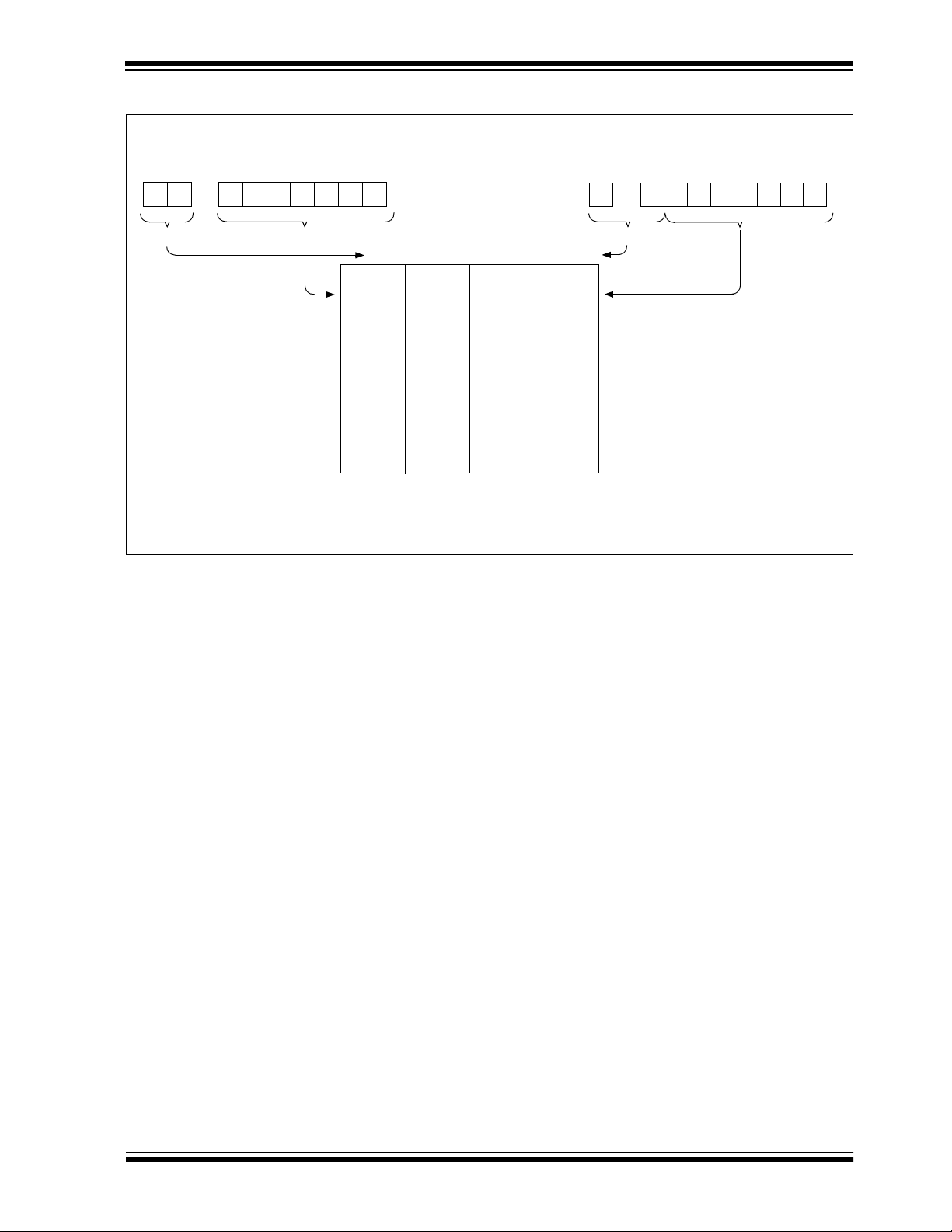

FIGURE 2-4: DIRECT/INDIRECT ADDRESSING

RP1:RP0 6

from opcode

0

PIC16F872

Indirect AddressingDirect Addressing

IRP FSR register

7

0

bank select location select

00 01 10 11

00h

Data

(1)

Memory

7Fh

Bank 0 Bank 1 Bank 2 Bank 3

Note 1: For register file map detail see Figure 2-2.

80h

FFh

100h

17Fh

180h

1FFh

bank select

location select

1999 Microchip Technology Inc.

Preliminary DS30221A-page 21

Page 22

PIC16F872

NOTES:

DS30221A-page 22 Preliminary

1999 Microchip Technology Inc.

Page 23

PIC16F872

3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an

alternate function for the peripheral features on the

device. In general, when a peripheral is enabled, that

pin may not be used as a general purpose I/O pin.

Additional information on I/O ports ma y be found i n th e

PICmicro™ Mid-Range Reference Manual,

(DS33023).

3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a

TRISA bit (=1) will m ake the correspo ndi ng PO RTA pin

an input (i.e., put the corresponding output driver in a

hi-impedance mode). Clearing a TRISA bit (=0) will

make the corresp onding PORTA pin an output (i.e., put

the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the

pins, whereas writing to it will write to th e p ort latch. All

write operations are read-modify-write operations.

Therefore , a write to a port implies that the port pins are

read, the value is modified and then written to the port

data latch.

Pin RA4 is multiplexed with the Timer0 module clock

input to become the RA4/T0CKI pin. The RA4/T0CKI

pin is a Schmitt Trigger input and an open drain output.

All other PORTA pins have TTL input levels and full

CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs

and analog V

selected by clearing/setting the control bits in the

ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are con-

The TRISA register controls the direction of the RA

pins, even when they are being used as analog inputs.

The user must ensure the bits in the TRISA registe r are

maintained set when using them as analog inputs.

EXAMPLE 3-1: INITIALIZING PORTA

BCF STATUS, RP0 ;

BCF STATUS, RP1 ; Bank0

CLRF PORTA ; Initialize PORTA by

BSF STATUS, RP0 ; Select Bank 1

MOVLW 0x06 ; Configure all pins

MOVWF ADCON1 ; as digital inputs

MOVLW 0xCF ; Value used to

MOVWF TRISA ; Set RA<3:0> as inputs

REF input. The operation of each pin is

figured as analog inputs and read as '0'.

; clearing output

; data latches

; initialize data

; direction

; RA<5:4> as outputs

; TRISA<7:6> are always

; read as ’0’.

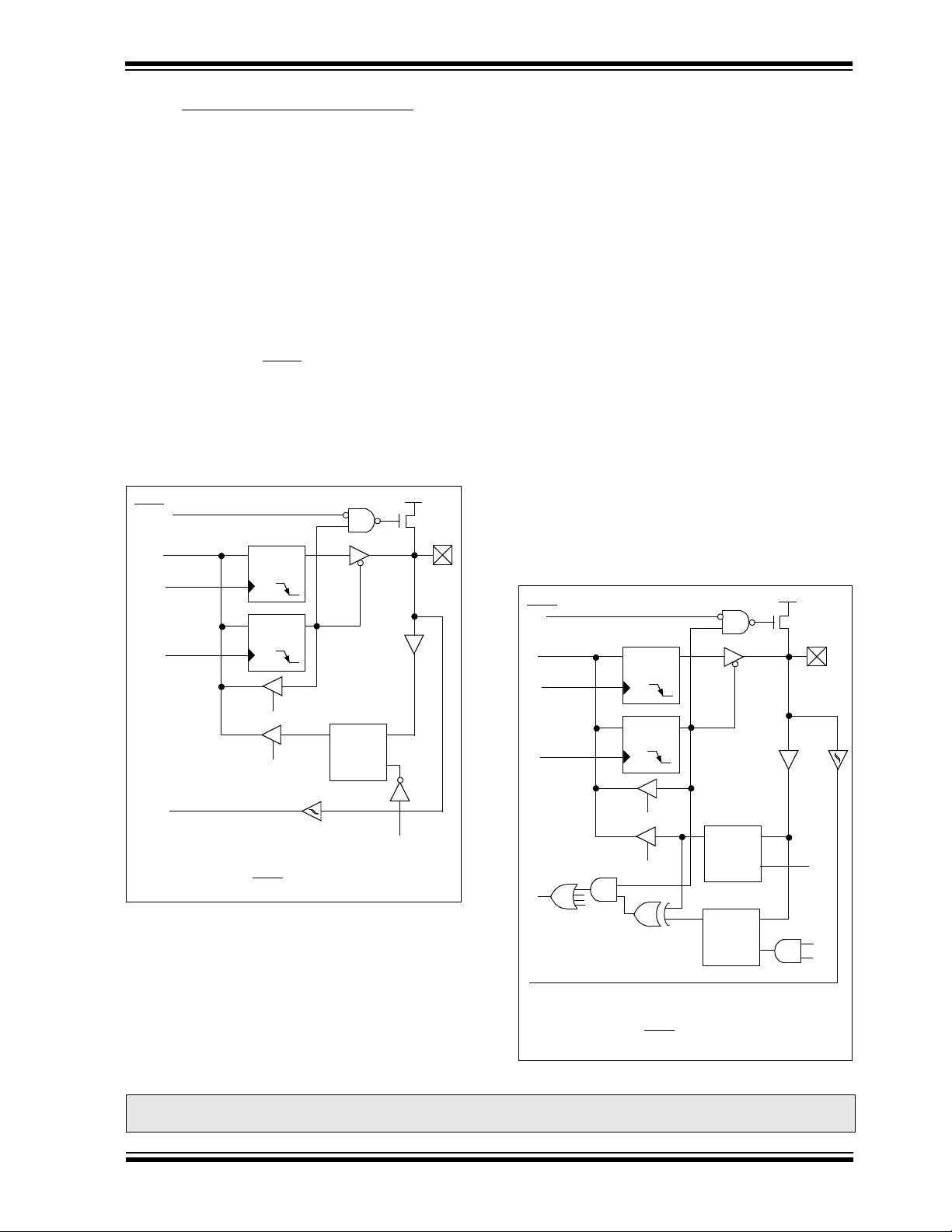

FIGURE 3-1: BLOCK DIAGRAM OF

RA<3:0> AND RA5 PINS

Data

Bus

WR

Port

Data Latch

WR

TRIS

TRIS Latch

RD Port

To A/D Converter

Note 1: I/O pins have protection diodes to VDD and VSS.

CK

CK

QD

Q

QD

Q

RD TRIS

QD

Analog

Input

Mode

EN

VDD

P

N

V

I/O pin

SS

TTL

Input

Buffer

FIGURE 3-2: BLOCK DIAGRAM OF RA4/

T0CKI PIN

Data

Bus

WR

Port

WR

TRIS

RD Port

TMR0 clock input

Note 1: I/O pin has protection diodes to VSS only.

CK

Data Latch

CK

TRIS Latch

RD TRIS

QD

Q

QD

Q

QD

Schmitt

Trigger

Input

Buffer

EN

EN

V

I/O pin

N

SS

(1)

(1)

1999 Microchip Technology Inc.

Preliminary DS30221A-page 23

Page 24

PIC16F872

TABLE 3-1: PORTA FUNCTIONS

Name Bit# Buffer Function

RA0/AN0 bit0 TTL Input/output or analog input

RA1/AN1 bit1 TTL Input/output or analog input

RA2/AN2 bit2 TTL Input/output or analog input

RA3/AN3/VREF bit3 TTL Input/output or analog input or VREF

RA4/T0CKI bit4 ST Input/output or external clock input for Timer0

Output is open drain type

RA5/SS

Legend: TTL = TTL input, ST = Schmitt Trigger input.

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

05h PORTA — — RA5 RA4 RA3 RA2 RA1 RA0

85h TRISA — — PORTA Data Direction Register

9Fh ADCON1 ADFM — — — PCFG3 PCFG2 PCFG1 PCFG0

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

/AN4 bit5 TTL Input/output or slave select input for synchronous serial port or analog input

Value on:

POR,

BOR

--0x 0000 --0u 0000

--11 1111 --11 1111

--0- 0000 --0- 0000

Value on all

other

resets

Note: When using the SSP module in SPI slave mode and SS enabled, the A/D converter must be set to one of

the following modes where PCFG<3:0> = 0100,0101, 011x, 1101, 1110, 1111.

DS30221A-page 24 Preliminary

1999 Microchip Technology Inc.

Page 25

PIC16F872

3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a

TRISB bit (=1) will make the correspon ding POR TB pin

an input (i.e., put the corresponding output driver in a

hi-impedance mode). Clearing a TRISB bit (=0) will

make the corresponding PORTB pin an output (i.e., put

the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the Low

Voltage Programming function; RB3/PGM, RB6/PGC

and RB7/PGD. The alternate functions of these pins

are described in the Special Features Section.

Each of the PORTB pins h as a w ea k in ternal p ull -up. A

single control bit ca n turn on all the pull-u ps. This is performed by clea ring bi t RBPU

(OPTION_REG<7>). The

weak pull-up i s autom atically tur ned off when the po rt

pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

FIGURE 3-3: BLOCK DIAGRAM OF

RB<3:0> PINS

V

TTL

Input

Buffer

EN

DD

weak

P

pull-up

I/O

pin

RD Port

(1)

(2)

RBPU

Data Bus

WR Port

WR TRIS

RB0/INT

RB3/PGM

Note 1: I/O pins have diode protection to V

2: To enable weak pull-ups, set the appropriate TRIS bit(s)

and clear the RBPU

Data Latch

QD

CK

TRIS Latch

QD

CK

RD TRIS

RD Port

Schmitt Trigger

Buffer

bit (OPTION_REG<7>).

QD

DD and VSS.

This interrupt can wake the device from SLEEP. The

user, i n the interrupt service routine , can clea r the interrupt in the following manner:

a) Any read or write of PORTB. This will end the

mismatch condition.

b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF.

Reading PORTB will end the mismatch condition and

allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for

wake-up on key depression operation and opera tions

where PORTB is only used for the interrupt on change

feature. Polling of PORTB is not recommended while

using the interrupt on change feature.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allow

easy interface to a keypad and make it possible for

wake-up on key-depression. Refer to the Embedded

Control Handbook,

(AN552).

Stroke”

“Implementing Wake-Up on Key

RB0/INT is an external interrupt inp ut pin and is confi gured using the INTEDG bit (OPTION_REG<6>).

RB0/INT is discussed in detail in Section 11.10.1.

FIGURE 3-4: BLOCK DIAGRAM OF

RB<7:4> PINS

V

EN

TTL

Input

Buffer

DD

P

weak

pull-up

I/O

pin

Buffer

Q1

(1)

ST

RBPU

Data Bus

WR Port

WR TRIS

Set RBIF

(2)

Data Latch

QD

CK

TRIS Latch

QD

CK

RD TRIS

RD Port

Latch

QD

Four of PORTB’s pins, RB<7:4>, have an interrupt on

change feature. Only pins configured as inputs can

cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on

From other

RB<7:4> pins

RB<7:6> in serial programming mode

QD

RD Port

EN

change comparison). The input pins (of RB<7:4>) are

compared with th e o ld value latche d o n the last read of

PORTB. The “mismatch” outputs of RB<7:4> are

OR’ed together to generate the RB Port Change Inter-

Note 1: I/O pins have diode protection to V

2: To enable weak pull-ups, set the appropriate TRIS bit(s)

and clear the RBPU

bit (OPTION_REG<7>).

DD and VSS.

rupt with flag bit RBIF (INTCON<0>).

Note: When using Low Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the

TRISB register must b e cleared to di sable th e pull-up on RB 3 and ensure the p roper oper ation of the de vice .

1999 Microchip Technology Inc.

Preliminary DS30221A-page 25

Q3

Page 26

PIC16F872

TABLE 3-3: PORTB FUNCTIONS

Name Bit# Buffer Function

RB0/INT bit0 TTL/ST

RB1 bit1 TTL Input/output pin. Internal software programmable weak pull-up.

RB2 bit2 TTL Input/output pin. Internal software programmable weak pull-up.

RB3/PGM bit3 TTL/ST

RB4 bit4 TTL Input/output pin (with interrupt on chang e). Internal so ftw are prog ra mmab l e

RB5 bit5 TTL Input/output pin (with interrupt on chang e). Internal so ftw are prog ra mmab l e

RB6/PGC bit6 TTL/ST

RB7/PGD bit7 TTL/ST

Legend: TTL = TTL input, ST = Schmitt Trigger input.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

06h, 106h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx uuuu uuuu

86h, 186h TRISB PORTB Data Direction Register 1111 1111 1111 1111

81h, 181h OPTION_REG RBPU

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

(1)

Input/output pin or external interrupt input. Internal software

programmable weak pull-up.

(1)

Input/output pin or programming pin in LVP mode. Internal software

programmable weak pull-up.

weak pull-up .

weak pull-up .

(2)

Input/output pin (with interrupt on change) or In-Circuit Debugger pin.

Internal software programmable weak pull-up. Serial programming clock.

(2)

Input/output pin (with interrupt on change) or In-Circuit Debugger pin.

Internal software programmable weak pull-up. Serial programming data.

Value on:

POR,

BOR

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

Value on all

other

resets

DS30221A-page 26 Preliminary

1999 Microchip Technology Inc.

Page 27

PIC16F872

3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a

TRISC bit (=1) will mak e the corres ponding POR TC pin

an input (i.e., put the corresponding output driver in a

hi-impedance mode). Clearing a TRISC bit (=0) will

make the cor respon ding POR T C pin an output (i .e. , put

the contents of the output latch on the selected pin).

PORTC is mul tiple x ed with se v eral peripheral fun ctions

(Table 3-5). PORTC pins have Schmitt Trigger input

buffers.

2

When the I

can be configured with normal I

C module is enab led, the POR TC (3:4) pins

2

C levels or with

SMBUS levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be

taken in defining TRIS bits for each PORTC pin. Some

periphe rals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to

make a pin an input. Since the TRIS bit override is in

effect while the peripheral is enabled, read-modifywrite instructions (BS F, BCF, XORWF) with TRISC as

destination shou ld be a voi ded. The us er should refe r to

the corresponding peripheral section for the correct

TRIS bit settings.

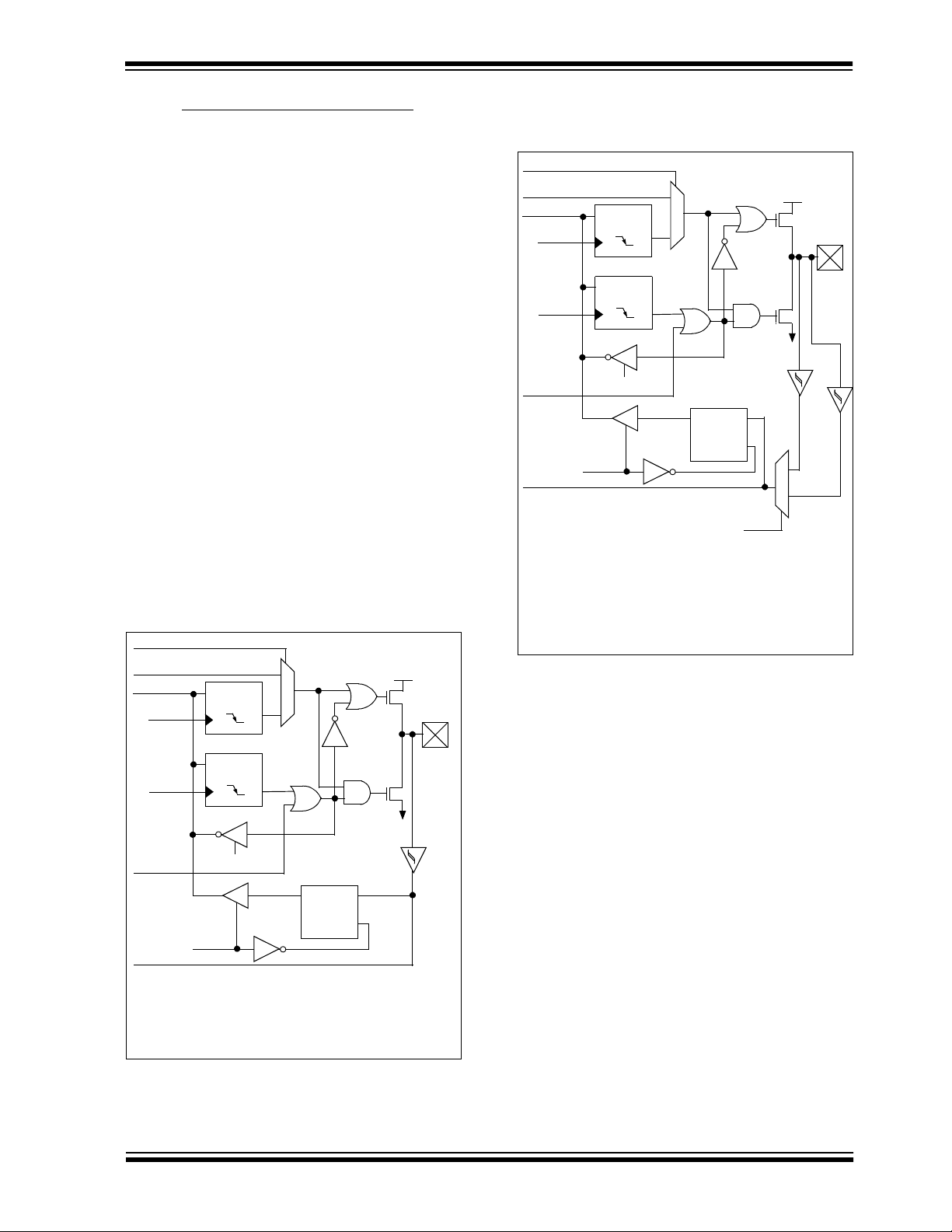

FIGURE 3-5: P ORTC BLOCK DIAGRAM

(PERIPHERAL OUTPUT

OVERRIDE) RC<0:2>

RC<5:7>

Port/Peripheral Select

Peripheral Data Out

Data Bus

WR

Port

WR

TRIS

Peripheral

(3)

OE

(2)

QD

Q

CK

Data Latch

QD

CK

TRIS Latch

RD TRIS

V

Schmitt

Trigger

N

VSS

DD

P

I/O

(1)

pin

0

1

Q

QD

FIGURE 3-6: PORTC BLOCK DIAGRAM

(PERIPHERAL OUTPUT

OVERRIDE) RC<3:4>

CK

Data Latch

CK

TRIS Latch

RD TRIS

RD

Port

(2)

V

Schmitt

Trigger

N

Vss

0

1

DD

P

Schmitt

Trigger

with

SMBus

levels

0

QD

1

Q

QD

Q

QD

EN

CKE

SSPSTAT<6>

Port/Peripheral Select

Peripheral Data Out

Data Bus

WR

Port

WR

TRIS

Peripheral

(3)

OE

SSPl Input

Note 1: I/O pins have diode protection to VDD and VSS.

2: Port/Peripheral select signal selects between port

data and peripheral output.

3: Peripheral OE (output enable) is only activated if

peripheral select is active.

I/O

pin

(1)

RD

Port

Peripheral Input

EN

Note 1: I/O pins have diode protection to VDD and VSS.

2: Port/Peripheral select signal selects between port

data and peripheral output.

3: Peripheral OE (output enable) is only activated if

peripheral select is active.

1999 Microchip Technology Inc.

Preliminary DS30221A-page 27

Page 28

PIC16F872

TABLE 3-5: PORTC FUNCTIONS

Name Bit# Buffer Type Function

RC0/T1OSO/T1CKI bit0 ST Input/output port pin or Timer1 oscillator output/Timer1 clock input.

RC1/T1OSI bit1 ST Input/output port pin or Timer1 oscillator input.

RC2/CCP1 bit2 ST Input/output port pin or Capture1 input/Compare1 output/PWM1

output.

RC3/SCK/SCL bit3 ST RC3 can also be the synchronous serial clock for both SPI and I

modes.

RC4/SDI/SDA bit4 ST RC4 can also be the SPI Data In (SPI mode) or data I/O (I

RC5/SDO bit5 ST Input/output port pin or Synchronous Serial Port data output.

RC6 bit6 ST Input/output port pin.

RC7 bit7 ST Input/output port pin.

Legend: ST = Schmitt Trigger input.

TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0

87h TRISC PORTC Data Direction Register

Legend: x = unknown, u = unchanged.

POR,

BOR

xxxx xxxx uuuu uuuu

1111 1111 1111 1111

2

2

C mode).

Value on all

other resets

C

DS30221A-page 28 Preliminary

1999 Microchip Technology Inc.

Page 29

PIC16F872

4.0 DATA EEPROM AND FLASH

PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are

readable an d writab le during normal oper at ion o v e r the

entire VDD ra nge. A bulk eras e operation may not be

issued from user code (which includes removing code

protection). The data memory is not dire ctly m apped in

the register file space. Instead, it is indirectly

addressed through the Special Function Registers

(SFR).

There are six SFRs used to r ead and w rite the prog ram

and data EEPROM memory. These registers are:

• EECON1

• EECON2

• EEDATA

• EEDATH

• EEADR

• EEADRH

The EEPROM data memory allo ws byte read and write .

When interfacing to the data memory block, EEDATA

holds the 8-bit data f or read/write and EEA DR holds the

address of the EEPROM location being accessed. The

registers EEDATH and EEADRH are not used for data

EEPROM access. The PIC16F 872 de vice has 64 bytes

of data EEPROM with an address range from 0h to

3Fh.

The EEPROM data memory is rated for high erase/

write cycles. The write tim e is co ntro lle d by an on-chi p

timer . The writ e time will v a ry with v oltag e and te mperature, as well as from chip-to-chip. Please refer to the

specifications for exact limits.

The program m emory allows word re ads and writes.

Program memory access allows for checksum calculation and ca libr ation table sto rage. A byt e or wo rd w r ite

automatically erases the location and writes the new

data (erase before write). Writing to program memory

will cease opera tion until the writ e is complete. T he program memory cannot be accessed during the write,

therefore c ode c ann ot execut e . During the write oper ation, the oscillator continues to clock the peripherals,

and therefore, they continue to operate. Interrupt

events will be detected and essentially “queued” until

the write is completed. When the write completes, the

next instruction in the pipeline is executed and the

branch to the interrupt vector address will occur.

When interfacing to the program memory block, the

EEDATH:EEDATA registers form a two byte word,

which holds the 14-bit data for read/write. The

EEADRH:EEADR registers form a two byte word,

which holds the 13-bit address of the FLASH location

being accessed. The PIC16F872 device has 2K w ords

of program FLASH with an address range from 0h to

7FFh. The unused upper bits in both the EEDATH and

EEDATA registers all read as “0’s”.

The value written to pro gram m emory does not need to

be a valid instruction. Therefore, up to 14-bit numbers

can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that

forms an invalid instruction results in a NOP.

4.1 EEADR

The address registers can address up to a maxim um of

256 bytes of data EEPROM or up to a maximum of 8K

words of program FLASH. However, the PIC16F872

has 64 bytes of data EEPROM and 2K words of program FLASH.

When selecting a program address value, the MSByte

of the address is written to the EEADRH register and

the LSByte is written to the EEADR register. When

selecting a data address value, only the LSByte of the

address is written to the EEADR register.

On the PIC16F872 device, the upper two bits of the

EEADR must always be cleared to prevent inadvertent

access to the wrong location in data EEPROM. This

also applies to the program memory. The upper five

MSbits of EEAD RH must always be clear dur ing program FLASH access.

4.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2

will read all '0's. The EECON2 register is used

exclusively in the memory write sequence.

Control bit EEPGD determines if the access will be a

program or a data memory access. When clear, any

subsequent operations will operate on the data memory . Whe n set, any subs equen t oper ations will o per ate

on the program memory.

Control bits RD and WR initiate read and write operations, respectively. These bits cannot be cleared, only

set, in software. They are cleared in hardware at the

completion of the read or write operation. The inability

to clear the WR bit in software prevents the accidental

or premature termination of a write operation.

The WREN bit, when set, will allow a write operation.

On power-up , the WR EN bit is clear . The WRERR bit i s

set when a write operation is interrupted by a MCLR

reset or a WD T ti me-out rese t during n ormal oper atio n.

In these situations, following reset, the user can check

the WRERR bit and rewrite the location. The value of

the data and address registers and the EEPGD bit

remains unchanged.

Interrupt flag bit EEIF, in the PIR2 register, i s set whe n

write is complete. It must be cleared in software.

1999 Microchip Technology Inc.

Preliminary DS30221A-page 29

Page 30

PIC16F872

REGISTER 4-1: EECON1 REGISTER (ADDRESS 18Ch)

R/W-x U-0 U-0 U-0 R/W-x R/W-0 R/S-0 R/S-0

EEPGD — — — WRERR WREN WR RD R = Readable bit

bit7 bit0

bit 7: EEPGD: Program / Data EEPROM Select bit

1 = Accesses Program memory

0 = Accesses data memory

(This bit cannot be changed while a read or write operation is in progress)

bit 6-4: Unimplemented: Read as '0'

bit 3: WRERR: EEPROM Error Flag bit

1 = A write operation is prematurely terminated

(any MCLR

0 = The write operation completed

bit 2: WREN: EEPROM Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1: WR: Write Control bit

1 = initiates a write cycle. (The bit is cleared by hardware once write is complete.) The WR bit can only

be set (not cleared) in software.

0 = Write cycle to the EEPROM is complete

bit 0: RD: Read Control bit

1 = Initiates an EEPROM read RD is cleared in hardware. The RD bit can only be set (not cleared) in

software.

0 = Does not initiate an EEPROM read

reset or any W DT reset during normal operation)

W = Writable bit

U = Unimplemented bit,

read as ‘0’

- n= Value at POR reset

DS30221A-page 30 Preliminary

1999 Microchip Technology Inc.

Page 31

PIC16F872

4.3 Reading the Data EEPROM Memory

T o read a data memory locatio n, the user m ust write the

address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD

(EECON1<0>). The data is available in the very next

instruction cycle of the EEDATA register, therefore it

can be read by the next instruction. EEDATA will hold

this value until another read operation or until it is written to by the user (during a write operation).

4.4 Writing to the Data EEPR OM Memory

To wr ite an EEPROM data location, the address must

first be written to the EEADR register and the data w ritten to the EEDATA register. Then the sequence in

Example 4-2 must be followed to initi ate the write cycle.

EXAMPLE 4-2: DATA EEPROM WRITE

BSF STATUS, RP1 ;

BCF STATUS, RP0 ; Bank 2

MOVLW DATA_EE_ADDR ;

MOVWF EEADR ; Data Memory Address to write

MOVLW DATA_EE_DATA ;

MOVWF EEDATA ; Data Memory Value to write

BSF STATUS, RP0 ; Bank 3

BCF EECON1, EEPGD ; Point to DATA memory

BSF EECON1, WREN ; Enable writes

BCF INTCON, GIE ; Disable Interrupts

MOVLW 55h ;

Required MOVWF EECON2 ; Write 55h

Sequence MOVLW AAh ;

MOVWF EECON2 ; Write AAh

BSF EECON1, WR ; Set WR bit to begin write

BSF INTCON, GIE ; Enable Interrupts

SLEEP ; Wait for interrupt to signal write complete

BCF EECON1, WREN ; Disable writes

The write will not initiate if the above sequence is not

exactly followed (write 55h to EECON2, write AAh to

EECON2, then set WR bit) for each byte. It is strongly

recommended that interrupts be disabled during this

code segment.

Additionally, the WREN bit in EECON1 must be set to

enable writes. This mechanism prevents accidental

writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should

be kept clear at all times, except when updating the

EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the

WREN bit will not aff ect the current write cycle . The WR

bit will be inhibited from be ing set unles s the WREN bit

EXAMPLE 4-1: DATA EEPROM READ

BSF STATUS, RP1 ;

BCF STATUS, RP0 ;Bank 2

MOVLW DATA_EE_ADDR ;

MOVWF EEADR ;Data Memory Address to read

BSF STATUS, RP0 ;Bank 3

BCF EECON1, EEPGD ;Point to DATA memory

BSF EECON1, RD ;EEPROM Read

BCF STATUS, RP0 ;Bank 2

MOVF EEDATA, W ;W = EEDATA

is set. The WREN bit m ust be set on a previous instruction. Both WR and WREN ca nno t be set with the sam e

instruction.

At the completion of the write cycle, the WR bit is

cleared in hardware and the EEPROM Write Compl ete

Interrupt Flag bit (EEIF) is set. EEIF m ust be cl eared by

software.

1999 Microchip Technology Inc.

Preliminary DS30221A-page 31

Page 32

PIC16F872

4.5 Reading the FLASH Program Memory

A program me mory location ma y be rea d by writing tw o

bytes of the address to the EEADR and EEADRH registers, setting the EEPGD control bit (EECON1<7>)

and then setting control bit RD (EECON1<0>). Once

the read control bit is set, the microcontroller will use

the next two instruction cycles to read the data. The

EXAMPLE 4-3: FLASH PROGRAM READ

BSF STATUS, RP1 ;

BCF STATUS, RP0 ; Bank 2

MOVLW ADDRH ;

MOVWF EEADRH ; MSByte of Program Address to read

MOVLW ADDRL ;

MOVWF EEADR ; LSByte of Program Address to read

BSF STATUS, RP0 ; Bank 3

BSF EECON1, EEPGD ; Point to PROGRAM memory

Required BSF EECON1, RD ; EEPROM Read

Sequence

NOP ; memory is read in the next two cycles after BSF EECON1,RD

NOP ;

BCF STATUS, RP0 ; Bank 2

data is available in the EEDATA and EEDATH registers

after the second NOP instruction. Therefore, it can be

read as two bytes in the following instructions. The

EEDATA and EEDATH registers will hold this value

until another read o peration or u ntil it is written to by the

user (during a write operation).