Page 1

PIC16F870/871

Data Sheet

28/40-Pin, 8-Bit CMOS

FLASH Microcontrollers

2003 Microchip Technology Inc. DS30569B

Page 2

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving t he code protect ion features of our

products. Attempts to break microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is intended through suggestion only

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

No representation or warranty is given and no liability is

assumed by Microchip Technology Incorporated with respect

to the accuracy or use of such information, or infringement of

patents or other intellectual property rights arising from such

use or otherwise. Use of Microchip’s products as critical

components in life support systems is not authorized except

with express written approval by Microchip. No licenses are

conveyed, implicitly or otherwise, under any intellectual

property rights.

Trademarks

The Microchip name and logo, the Microchip logo, K

EELOQ,

MPLAB, PIC, PICmicro, PICSTART, PRO MATE and

PowerSmart are registered trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV , MXLAB, PICMASTE R, SEEVAL

and The Embedded Control Solutions Company are

registered trademarks of Microchip Technology Incorporated

in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM,

dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM,

fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC,

microPort, Migratable Memory, MPASM, MPLIB, MPLINK,

MPSIM, PICC, PICkit, PICDEM, PICDEM.net, Powe rCal,

PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select

Mode, SmartSensor, SmartShunt, SmartTel and Total

Endurance are trademarks of Microchip Technology

Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2003, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999

and Mountain View, C a lifornia in March 2002.

The Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

devices, Serial EEPROMs, microperipherals,

non-volatile memory and analog products. In

addition, Microchip’s quality system for the

design and manufacture of development

systems is ISO 9001 certified.

®

8-bit MCUs, KEELOQ

®

code hopping

DS30569B-page ii 2003 Microchip Technology Inc.

Page 3

PIC16F870/871

28/40-Pin, 8-Bit CMOS FLASH Mi crocontrollers

Devices Included in this Data Sheet:

•PIC16F870 •PIC16F871

Microcontroller Core Features:

• High performance RISC CPU

• Only 35 single word instructions to learn

• All single cycle instructions except for program

branches which are two-cycle

• Operating speed: DC - 20 MHz clock input

DC - 200 ns instruction cycle

• 2K x 14 words of FLASH Program Memory

128 x 8 bytes of Data Memory (RAM)

64 x 8 bytes of EEPROM Data Memory

• Pinout compatible to the PIC16CXXX 28 and

40-pin devices

• Interrupt capability (up to 11 sources)

• Eight level deep hardware stack

• Direct, Indirect and Relative Addressing modes

• Power-on Reset (POR)

• Power-up Timer (PWRT) and

Oscillator Start-up Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator for reliable operation

• Programmable code protection

• Power saving SLEEP mode

• Selectable oscillator options

• Low power, high speed CMOS FLASH/EEPROM

technology

• Fully static design

• In-Circuit Serial Programming (ICSP) via

two pins

• Single 5V In-Circu it Seria l P rogramming capability

• In-Circuit Debugging via two pins

• Processor read/write access to program memory

• Wide operating voltage range: 2.0V to 5.5V

• High Sink/Source Current: 25 mA

• Commercial and Industrial temperature ranges

• Low power consumption:

- < 1.6 mA typical @ 5V, 4 MHz

-20 µA typical @ 3V, 32 kHz

-< 1 µA typical standby current

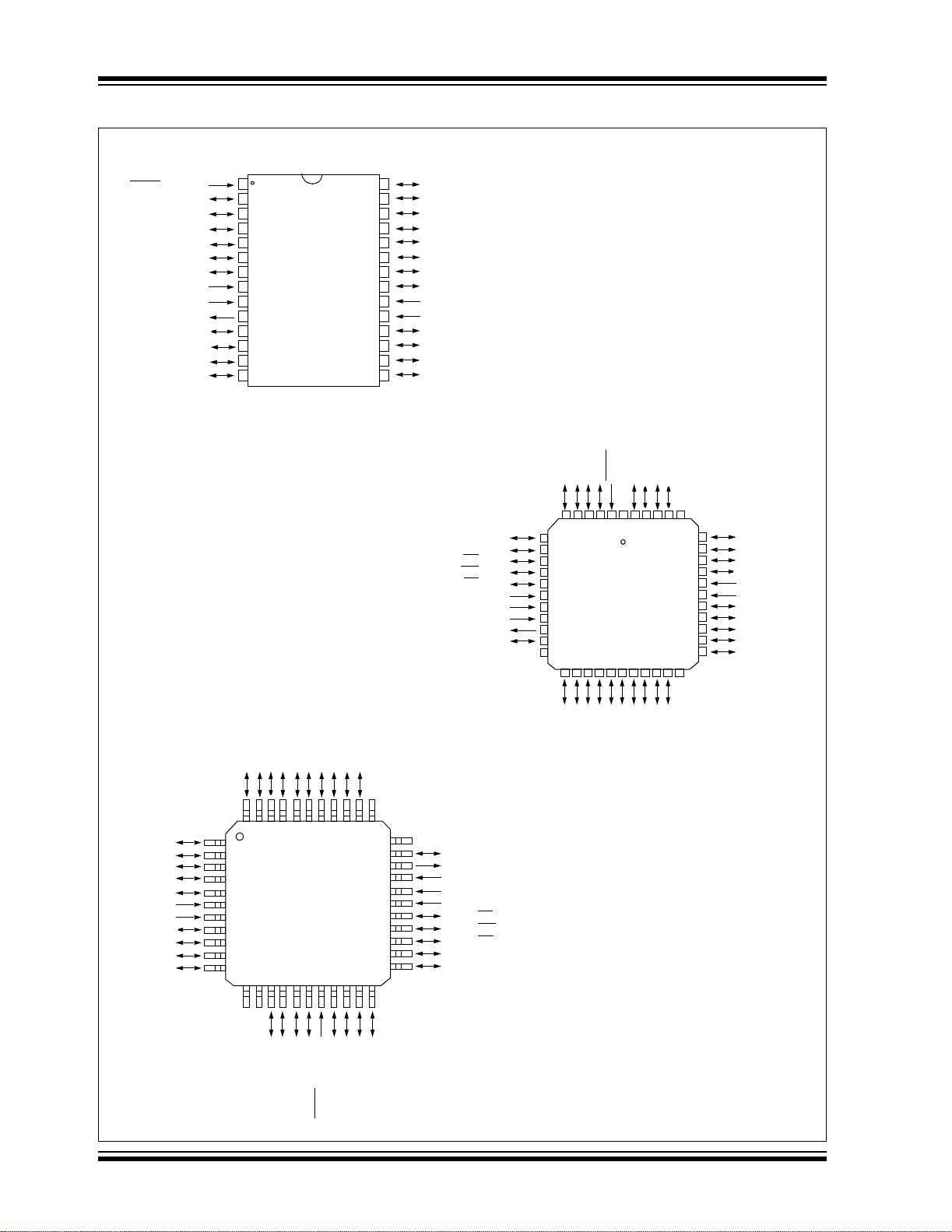

Pin Diagram

PDIP

MCLR/VPP/THV

RA0/AN0

RA1/AN1

RA2/AN2/V

RA3/AN3/V

RC0/T1OSO/T1 CKI

REF+

RA4/T0CKI

RA5/AN4

/AN5

RE0/RD

RE1/WR

/AN6

/AN7

RE2/CS

OSC1/CLKI

OSC2/CLKO

RC1/T1OSI

RC2/CCP1

RD0/PSP0

RD1/PSP1

REF-

V

VSS

RC3

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

PIC16F871

28

27

26

25

24

23

22

21

RB7/PGD

RB6/PGC

RB5

RB4

RB3/PGM

RB2

RB1

RB0/INT

V

DD

VSS

RD7/PSP7

RD6/PSP6

RD5/PSP5

RD4/PSP4

RC7/RX/DT

RC6/TX/CK

RC5

RC4

RD3/PSP3

RD2/PSP2

Peripheral Features:

• Timer0: 8-bit timer/counter with 8-bit prescaler

• Timer1: 16-bit timer/counter with prescaler,

can be incremented during SLEEP via external

crystal/clock

• Timer2: 8-bit timer/counter with 8-bit period

register, prescaler and postscaler

• One Capture, Compare, PWM module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

• 10-bit multi-channel Analog-to-Digital converter

• Universal Synchronous Asynchronous Receiver

Transmitter (USART/SCI) with 9-bit address

detection

• Parallel Slave Port (PSP) 8-bits wide, with

external RD

• Brown-out detection circuitry for

Brown-out Reset (BOR)

, WR and CS controls (40/44-pin only)

2003 Microchip Technology Inc. DS30569B-page 1

Page 4

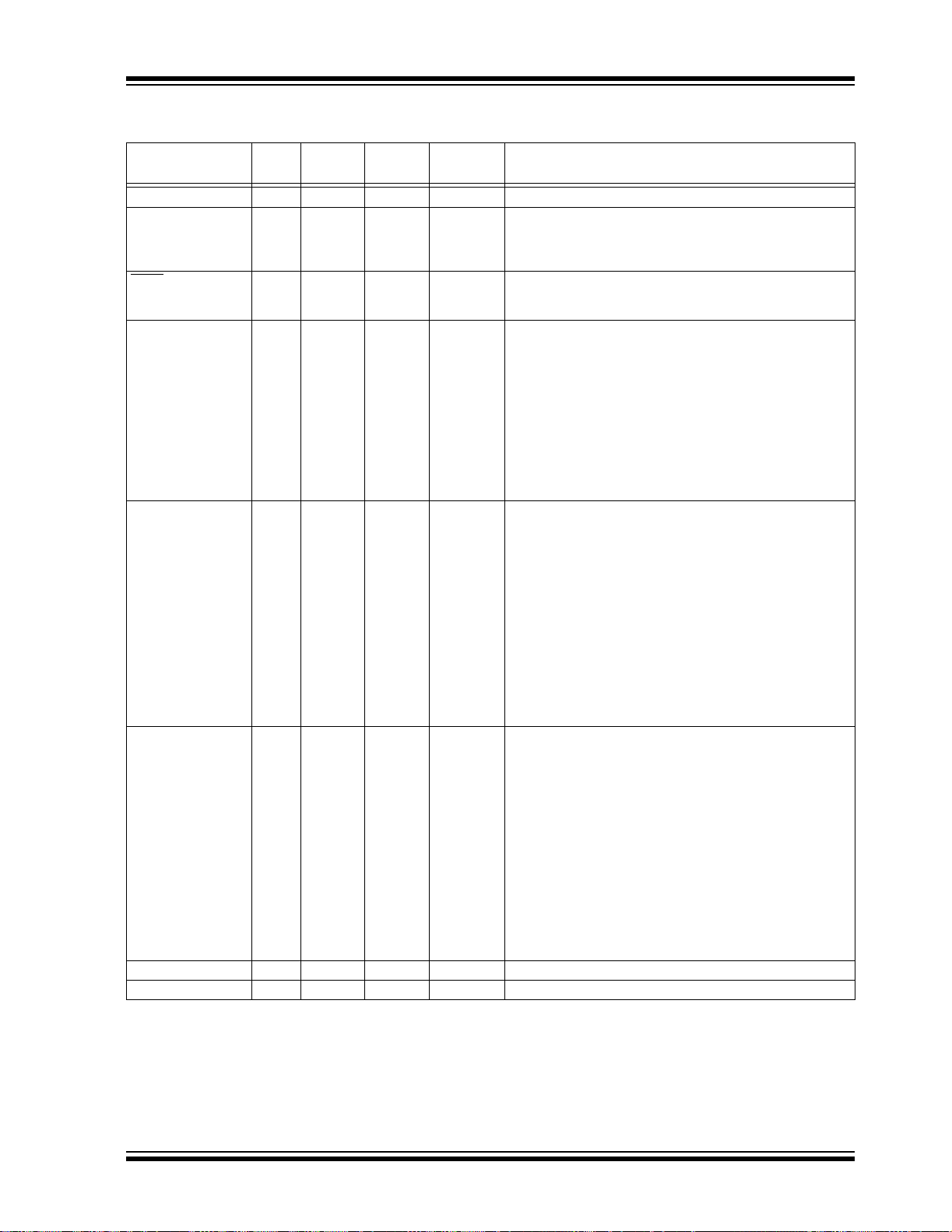

PIC16F870/871

Pin Diagrams

DIP, SOIC, SSOP

MCLR/VPP/THV

RA0/AN0

RA1/AN1

RA2/AN2/V

RA3/AN3/V

RC0/T1OSO/T1CKI

REF-

REF+

RA4/T0CKI

RA5/AN4

V

OSC1/CLKI

OSC2/CLKO

RC1/T1OSI

RC2/CCP1

RC3

1

2

3

4

5

6

7

SS

8

9

10

11

12

13

14

PIC16F870

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RC0/T1OSO/T1CK1

RB7/PGD

RB6/PGC

RB5

RB4

RB3/PGM

RB2

RB1

RB0/INT

V

DD

VSS

RC7/RX/DT

RC6/TX/CK

RC5

RC4

RA4/T0CKI

RA5/AN4

RE0/RD

RE1/WR

RE2/CS

OSC1/CLKI

OSC2/CLKO

PLCC

/AN5

/AN6

/AN7

V

DD

VSS

NC

REF-

/VPP/THV

RA3/AN3/VREF+

65432

7

8

9

10

11

12

13

14

15

16

17

181920212223242526

RA2/AN2/V

RA1/AN1

RA0/AN0

MCLR

PIC16F871

NC

1

RB7/PGD

44

RB6/PGC

43

RB5

RB4

NC

40

41

42

39

38

37

36

35

34

33

32

31

30

29

27

28

RB3/PGM

RB2

RB1

RB0/INT

V

DD

VSS

RD7/PSP7

RD6/PSP6

RD5/PSP5

RD4/PSP4

RC7/RX/DT

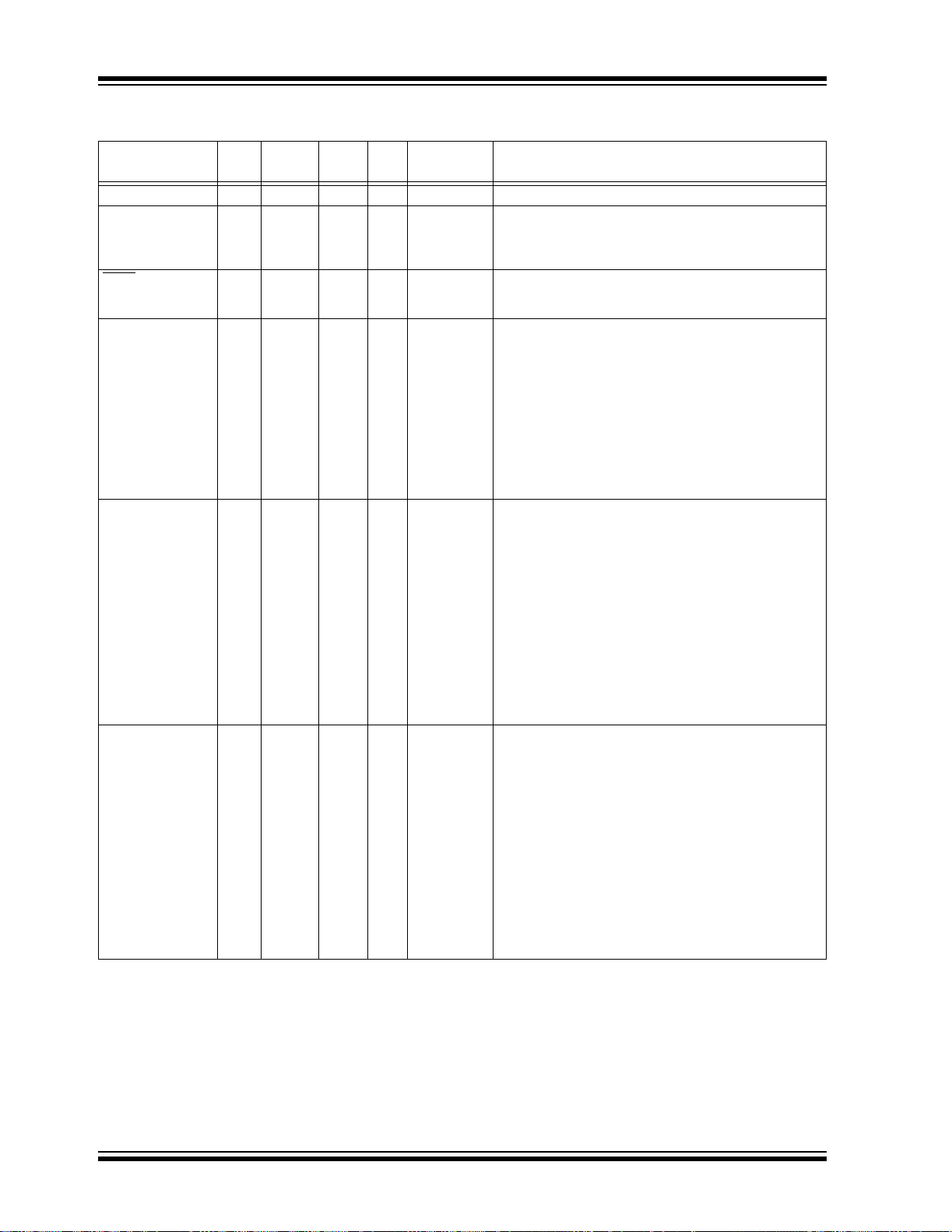

TQFP

RC7/RX/DT

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

V

VDD

RB0/INT

RB1

RB2

RB3/PGM

NC

RC5

RC3

RC6/TX/CK

RC5

RC4

RD3/PSP3

RD2/PSP2

RD1/PSP1

RD0/PSP0

RC3

RC2/CCP1

RC1/T1OSI

NC

4443424140

1

2

3

4

SS

5

6

7

8

9

10

11

121314

NC

NC

39

PIC16F871

16

17

15

RB5

RB4

RB7/PGD

RB6/PGC

363435

37

38

1819202122

REF-

RA1/AN1

RA0/AN0

/VPP/THV

RA2/AN2/V

MCLR

33

32

31

30

29

28

27

26

25

24

23

RA3/AN3/VREF+

NC

RC0/T1OSO/T1CKI

OSC2/CLKO

OSC1/CLKI

SS

V

VDD

RE2/CS/AN7

/AN6

RE1/WR

/AN5

RE0/RD

RA5/AN4

RA4/T0CKI

RC1/T1OSI

RC2/CCP1

RC4

RD3/PSP3

RD2/PSP2

RD1/PSP1

RD0/PSP0

RC6/TX/CK

DS30569B-page 2 2003 Microchip Technology Inc.

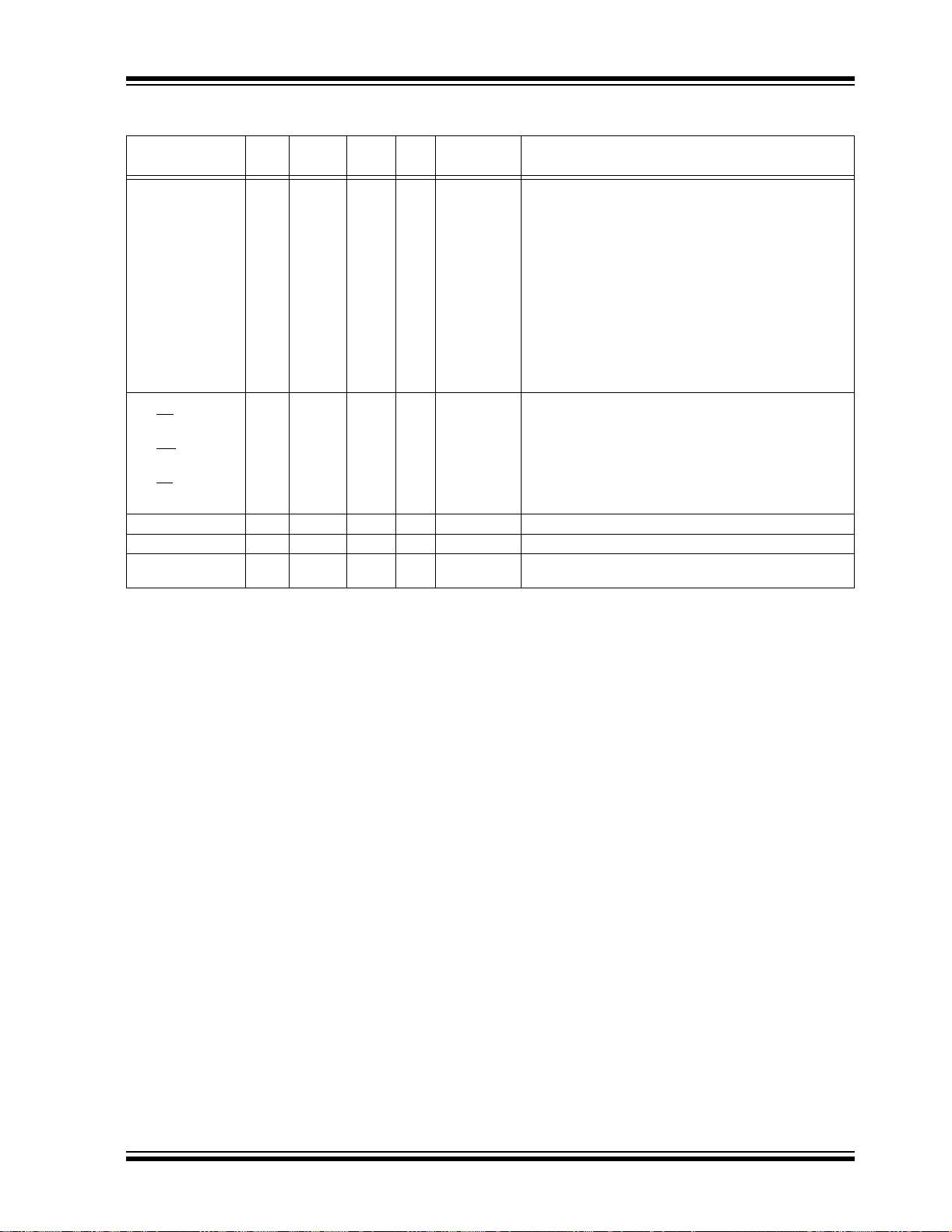

Page 5

PIC16F870/871

TM

PICmicro

Operating Frequency DC - 20 MHz DC - 20 MHz

RESETS (and Delays) POR, BOR (PWRT, OST) POR, BOR (PWRT, OST)

FLASH Program Memory (14-bit words) 2K 2K

Data Memory (bytes) 128 128

EEPROM Data Memory 64 64

Interrupts 10 11

I/O Ports Ports A,B,C Ports A,B,C,D,E

Timers 3 3

Capture/Compare/PWM modules 1 1

Serial Communications USART USART

Parallel Communications — PSP

10-bit Analog-to-Digital Module 5 input channels 8 input channels

Instruction Set 35 Instructions 35 Instructions

Mid-Range MCU Family Reference Manual

Key Features

PIC16F870 PIC16F871

(DS33023)

2003 Microchip Technology Inc. DS30569B-page 3

Page 6

PIC16F870/871

Table of Contents

1.0 Device Overview ..........................................................................................................................................................................5

2.0 Memory Organization. ................................................................................................................................................................ 11

3.0 Data EEPROM and Flash Program Memory.............................................................................................................................. 27

4.0 I/O Ports...................................... ........................................ ....................................................................................................... 33

5.0 Timer0 Module ...........................................................................................................................................................................45

6.0 Timer1 Module ...........................................................................................................................................................................49

7.0 Timer2 Module ...........................................................................................................................................................................53

8.0 Capture/Compare/PWM Modules ....................................................................... .... .. .... .... ....... .... .............................................. 55

9.0 Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART)................................................................ 61

10.0 Analog-to-Digital (A/D) Converter Module..................................................................................................................................79

11.0 Special Features of the CPU................................... ..................... ..............................................................................................87

12.0 Instruction Set Summary.......................................................................................................................................................... 103

13.0 Development Support. ..............................................................................................................................................................111

14.0 Electrical Characteristics.......................................................................................................................................................... 117

15.0 DC and AC Characteristics Graphs and Tables....................................................................................................................... 137

16.0 Packaging Information..............................................................................................................................................................149

Appendix A: Revision History.............................................................................................................................................................157

Appendix B: Device Differences.........................................................................................................................................................157

Appendix C: Conversion Considerations ........................................................... .. ....... .... .. .... .. .... ....................................................... 158

Appendix D: Migration from Mid-Range to Enhanced Devices.......................................................................................................... 158

Appendix E: Migration from High-End to Enhanced Devices.............................................................................................................159

Index .................................................................................................................................................................................................. 161

On-Line Support...................................................................... .... .. .... ....... .... .... .. .... ......... .. ................................................................. 167

Systems Information and Upgrade Hot Line...................................................................................................................................... 167

Reader Response.............................................................................................................................................................................. 168

PIC16F870/871 Product Identification System ..................................................................................................................................169

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding t his publication, p lease c ontact the M arket ing Co mmunications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include

literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

DS30569B-page 4 2003 Microchip Technology Inc.

Page 7

PIC16F870/871

1.0 DEVICE OVERVIEW

This document contains device specific information.

Additional information may be found in the PICmicro

Mid-Range MCU Family Reference Manual

(DS33023), which may be obtained from your local

Microchip Sales Representative or downloaded from

the Microchip web site. The Reference Manual should

be considered a complementary document to this data

sheet, and is highly recommended reading for a better

understanding of the dev ice arc hitecture and oper atio n

of the peripheral modules.

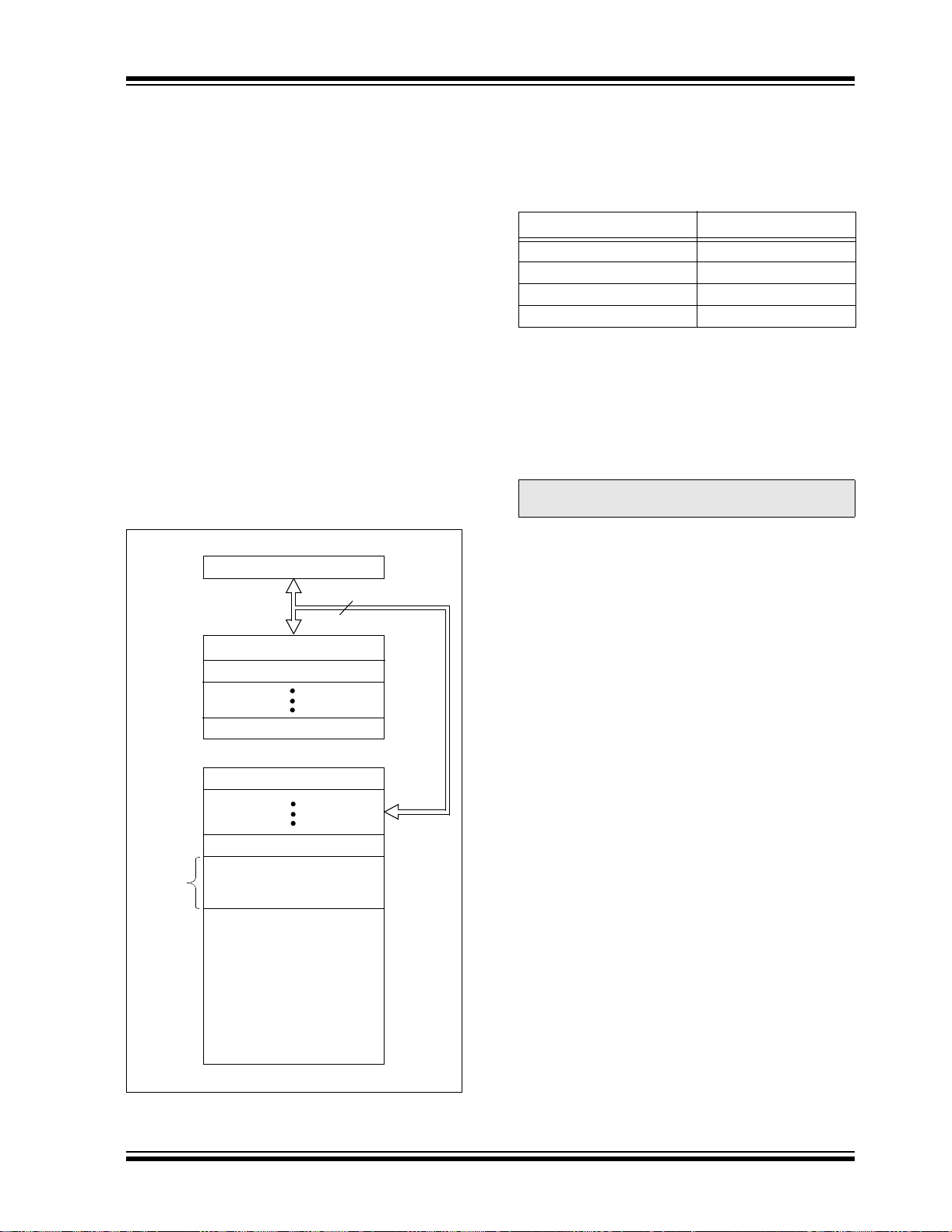

FIGURE 1-1: PIC16F870 BLO CK D IA GRA M

Device Program FLASH Data Memory Data EEPROM

PIC16F870 2K 128 Bytes 64 Bytes

13

Program Counter

8 Level Stack

Direct Addr

8

Power-up

Oscillator

Start-up Timer

Power-on

Watchdog

Brown-out

Debugger

Low-Voltage

Programming

(13-bit)

Timer

Reset

Timer

Reset

In-Circuit

Program

Bus

OSC1/CLKI

OSC2/CLKO

FLASH

Program

Memory

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

TM

RAM Addr (1)

7

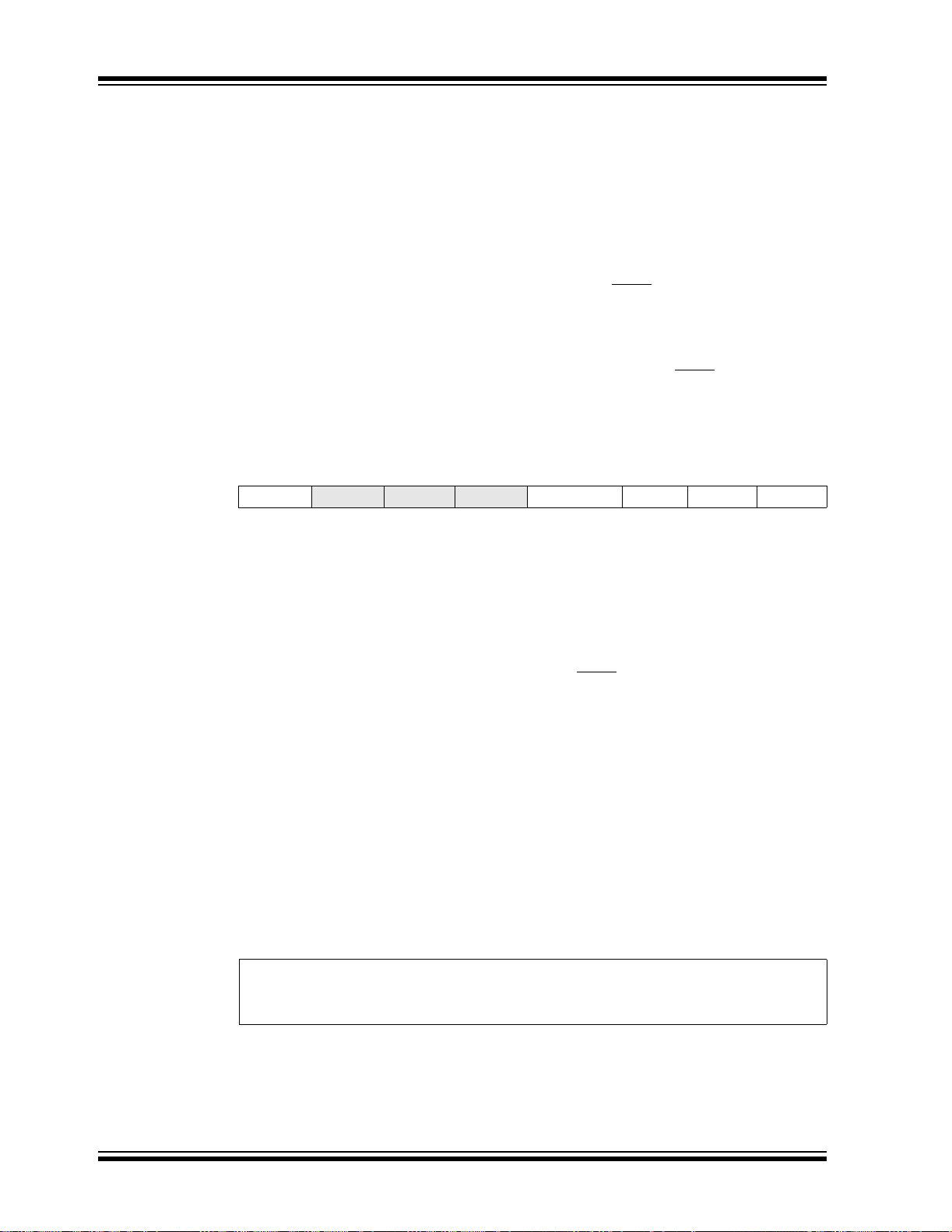

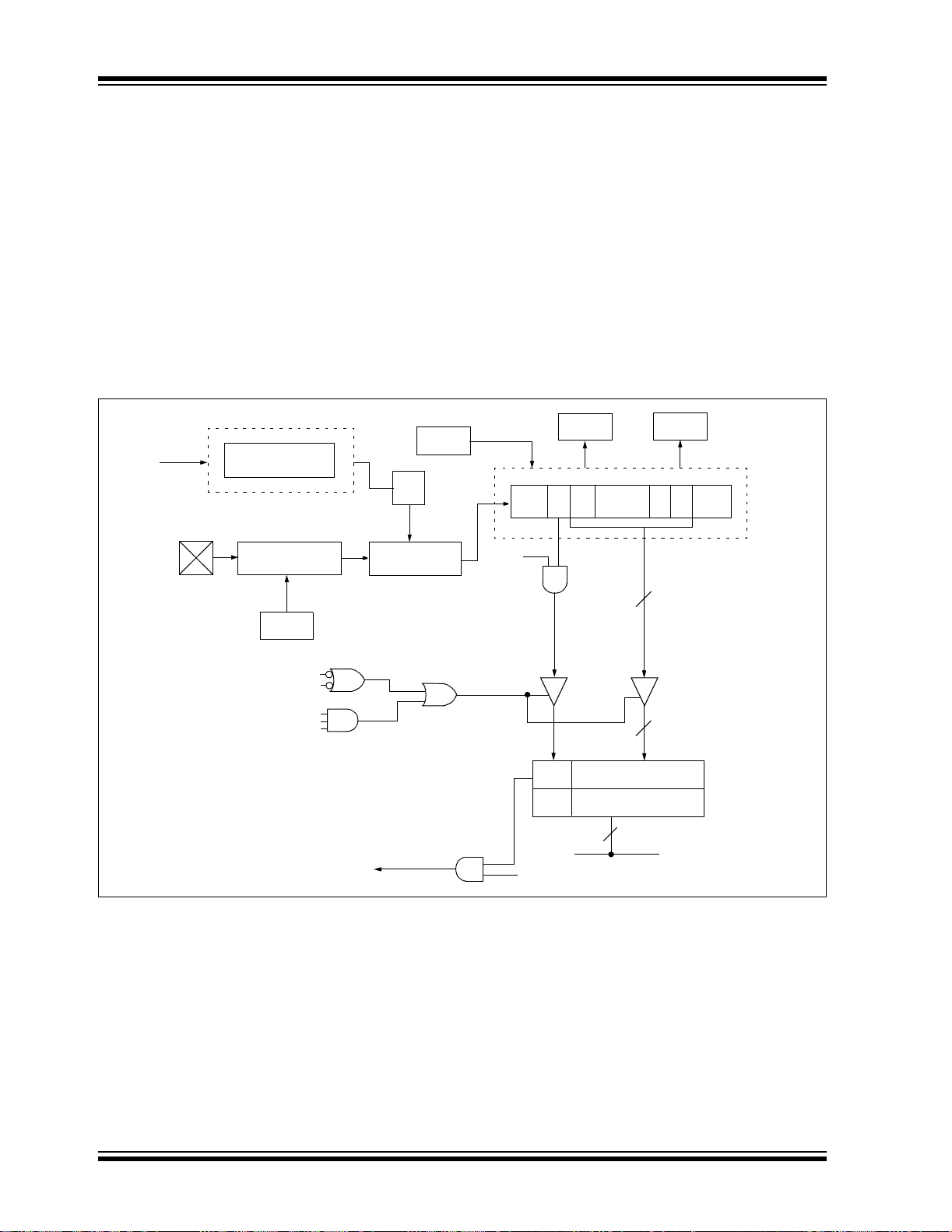

There are two devices (PIC16F870 and PIC16F871)

covered by this data sheet. The PIC16F870 device

comes in a 28-pin package and the PIC16F871 device

comes in a 40-pi n packa ge. The 28-p in devi ce does n ot

have a Parallel Slave Port implemented.

The following two figures are device block diagrams

sorted by pin number: 28-pin for Figure 1-1 and 40-pin

for Figure 1-2. The 28-pin and 40-pin pinouts are li ste d

in Table 1-1 and Table 1-2, respectively.

PORTA

PORTB

PORTC

RA0/AN0

RA1/AN1

RA2/AN2/VREFRA3/AN3/VREF+

RA4/T0CKI

RA5/AN4

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RC0/T1OSO/T1CKI

RC1/T1OSI

RC2/CCP1

RC3

RC4

RC5

RC6/TX/CK

RC7/RX/DT

3

8

Data Bus

RAM

File

Registers

Addr MUX

FSR reg

STATUS reg

ALU

W reg

9

8

MUX

8

Indirect

Addr

MCLR

VDD, VSS

10-bit A/DTimer0 Timer1 Timer2

Data EEPROM

CCP1

USART

Note 1: Higher order bits are from the STATUS register.

2003 Microchip Technology Inc. DS30569B-page 5

Page 8

PIC16F870/871

FIGURE 1-2: PIC16F871 BLO CK D IA GRA M

Device Program FLASH Dat a Memory Data EEPROM

PIC16F871 2K 128 Bytes 64 Bytes

Program

Bus

OSC1/CLKI

OSC2/CLKO

FLASH

Program

Memory

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

13

Program Counter

8 Level Stack

Direct Addr

8

Power-up

Oscillator

Start-up Timer

Power-on

Watchdog

Brown-out

In-Circuit

Debugger

Low-Voltage

Programming

(13-bit)

Timer

Reset

Timer

Reset

RAM Addr (1)

7

8

Data Bus

Addr MUX

3

RAM

File

Registers

FSR reg

STATUS reg

ALU

W reg

9

8

MUX

8

Indirect

Addr

PORTA

PORTB

PORTC

PORTD

PORTE

RA0/AN0

RA1/AN1

RA2/AN2/VREFRA3/AN3/VREF+

RA4/T0CKI

RA5/AN4

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RC0/T1OSO/T1CKI

RC1/T1OSI

RC2/CCP1

RC3

RC4

RC5

RC6/TX/CK

RC7/RX/DT

RD7/PSP7:RD0/PSP0

RE0/RD

/AN5

/AN6

RE1/WR

RE2/CS

/AN7

Data EEPROM

CCP1

MCLR

Parallel Slave Port

VDD, VSS

10-bit A/DTimer0 Timer1 Timer2

USART

Note 1: Higher order bits are from the STATUS register.

DS30569B-page 6 2003 Microchip Technology Inc.

Page 9

TABLE 1-1: PIC16F870 PINOUT DESCRIPTION

PIC16F870/871

Pin Name

OSC1/CLKI 9 9 I

OSC2/CLKO 10 10 O — Oscillator crystal output. Connects to crystal or resonator in

MCLR

/VPP/THV 1 1 I/P ST Master Clear (Reset) input or programming voltage input or High

RA0/AN0 2 2 I/O TTL RA0 can also be analog input 0.

RA1/AN1 3 3 I/O TTL RA1 can also be analog input 1.

RA2/AN2/V

RA3/AN3/V

RA4/T0CKI 6 6 I/O ST/OD RA4 can also be the clock i nput to t he T imer0 mod ule. Outpu t

RA5/AN4 7 7 I/O TTL RA5 can also be analog input 4.

RB0/INT 21 21 I/O

RB1 22 22 I/O TTL

RB2 23 23 I/O TTL

RB3/PGM 24 24 I/O

RB4 25 25 I/O TTL Interrupt-on-change pin.

RB5 26 26 I/O TTL Interrupt-on-change pin.

RB6/PGC 27 27 I/O

RB7/PGD 28 28 I/O

RC0/T1OSO/T1CKI 11 11 I/O ST RC0 can also be the Timer1 oscillator output or Timer1 clock

RC1/T1OSI 12 12 I/O ST RC1 can also be the Timer 1 oscillator input.

RC2/CCP1 13 13 I/O ST RC2 can also be the Capture1 inpu t/Compare1 output/

RC3 14 14 I/O ST

RC4 15 15 I/O ST

RC5 16 16 I/O ST

RC6/TX/CK 17 17 I/O ST RC6 can also be the USART Asynchronous Transmit or

RC7/RX/DT 18 18 I/O ST RC7 can also be the USART Asynchronous Receive or

V

SS 8, 19 8, 19 P — Ground reference for logic and I/O pins.

DD 20 20 P — Positive supply for logic and I/ O pins.

V

REF- 4 4 I/O TTL RA2 can also be analog input 2 or negative analog reference

REF+ 5 5 I/O TTL RA3 can also be analog input 3 or positive analog reference

DIP

Pin#

SOIC

Pin#

I/O/P

Type

Buffer

Type

ST/CMOS

TTL/ST

TTL/ST

TTL/ST

TTL/ST

Description

(3)

Oscillator crystal input/external clock source input.

Crystal Oscillator mode. In RC mode, the OSC2 pin outputs

CLKO, which has 1/4 the frequency of OSC1, and denotes the

instruction cycle rate.

Voltage Test mode cont rol. This pin is an active low RESET to the

device.

PORTA is a bi-directional I/O port.

voltage.

voltage.

is open drain type.

PORTB is a bi-directio nal I/O port. PORTB can be software

programmed for internal weak pull-up on all inputs.

(1)

(1)

(2)

(2)

RB0 can also be the external interrupt pin.

RB3 can also be the low voltage programming input.

Interrupt-on-change pi n or In-Circuit Debugger pin. Serial

programming clock.

Interrupt-on-change pi n or In-Circuit Debugger pin. Serial

programming data.

PORTC is a bi-directional I/O port.

input.

PWM1 output.

Synchronous Clock.

Synchronous Data.

Legend: I = input O = output I/O = input/output P = power

OD = Open Drain — = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

2003 Microchip Technology Inc. DS30569B-page 7

Page 10

PIC16F870/871

TABLE 1-2: PIC16F871 PINOUT DESCRIPTION

DIP

Pin Name

OSC1/CLKI 13 14 30 I

OSC2/CLKO 14 15 31 O — Oscillator crystal output. Connects to crystal or resonator in

MCLR

/VPP/THV 1 2 18 I/P ST Master Clear (Reset) input or programming voltage input or

RA0/AN0 2 3 19 I/O TTL RA0 can also be analog input 0.

RA1/AN1 3 4 20 I/O TTL RA1 can also be analog input 1.

RA2/AN2/V

RA3/AN3/V

RA4/T0CKI 6 7 23 I/O ST RA4 can also be the clock input to t he Timer0

RA5/AN4 7 8 24 I/O TTL RA5 can also be analog input 4.

RB0/INT 33 36 8 I/O

RB1 34 37 9 I/O TTL

RB2 35 38 10 I/O TTL

RB3/PGM 36 39 11 I/O

RB4 37 41 14 I/O TTL Interrupt-on-change pin.

RB5 38 42 15 I/O TTL Interrupt-on-change pin.

RB6/PGC 39 43 16 I/O

RB7/PGD 40 44 17 I/O

RC0/T1OSO/T1CKI 15 16 32 I/O ST RC0 can also be the Timer1 oscillator output or a Timer1

RC1/T1OSI 16 18 35 I/O ST RC1 can also be the Timer1 oscillator input.

RC2/CCP1 17 19 36 I/O ST RC2 can also be the Capture1 input/Compare1 output/

RC3 18 20 37 I/O ST

RC4 23 25 42 I/O ST

RC5 24 26 43 I/O ST

RC6/TX/CK 25 27 44 I/O ST RC6 can also be the USART Asynchronous Transmit or

RC7/RX/DT 26 29 1 I/O ST RC7 can also be the USART Asynchronous Receive or

REF- 4 5 21 I/O TTL RA2 can also be analog input 2 or negative analog

REF+ 5 6 22 I/O TTL RA3 can also be analog input 3 or posit ive analog

Pin#

PLCC

Pin#

Legend: I = input O = output I/O = input/output P = power

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

QFP

Pin#

I/O/P

Type

Buffer

Type

ST/CMOS

TTL/ST

TTL/ST

TTL/ST

TTL/ST

Description

(4)

Oscillator crystal input/external clock source input.

Crystal Oscillator mode. In RC mode, OSC2 pin output s CLKO,

which has 1/4 the frequency of OSC1, and denotes the

instruction cycle rate.

High Voltage Test mode control. This pin is an active low

RESET to the device.

PORTA is a bi-directiona l I/O po r t.

reference v o lta ge.

reference v o lta ge.

timer/counter. Output is open drain type.

PORTB is a bi-directional I/O port. PORTB can be software

programmed for internal weak pull-up on all inputs.

(1)

(1)

(2)

(2)

RB0 can also be the external interrupt pin.

RB3 can also be the low voltage programming input.

Interrupt-on-chan ge pin or In-Circuit Debugger pin.

Serial programming clock.

Interrupt-on-chan ge pin or In-Circuit Debugger pin.

Serial programming data.

PORTC is a bi-dir ec t i onal I/O port.

clock input.

PWM1 output.

Synchronous Clock.

Synchronous Data.

DS30569B-page 8 2003 Microchip Technology Inc.

Page 11

PIC16F870/871

TABLE 1-2: PIC16F871 PINOUT DESCRIPTION (CONTINUED)

DIP

Pin Name

RD0/PSP0 19 21 38 I/O

RD1/PSP1 20 22 39 I/O

RD2/PSP2 21 23 40 I/O

RD3/PSP3 22 24 41 I/O

RD4/PSP4 27 30 2 I/O

RD5/PSP5 28 31 3 I/O

RD6/PSP6 29 32 4 I/O

RD7/PSP7 30 33 5 I/O

RE0/RD

/AN5 8 9 25 I/O

RE1/WR

/AN6 9 10 26 I/O

RE2/CS

/AN7 10 11 27 I/O

V

SS 12,31 13,34 6,29 P — Ground reference for logic and I/O pins.

V

DD 11,32 12,35 7,28 P — Positive supply for logic and I/O pins.

NC — 1,17,28,4012,13,

Pin#

PLCC

Pin#

Legend: I = input O = output I/O = input/output P = power

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

QFP

Pin#

33,34

I/O/P

Type

Buffer

Type

PORTD is a bi-directional I/O port or parallel slave port when

interfacing to a microprocessor bus.

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

PORTE is a bi-directional I/ O port.

(3)

ST/TTL

(3)

ST/TTL

(3)

ST/TTL

— These pins are not internally connected. These pins should be

RE0 can also be read control for the p ar allel slave port, or

analog input 5.

RE1 can also be write cont rol for t he p a ralle l slave por t, or

analog input 6.

RE2 can also be select control for the parallel slave port,

or analog input 7.

left unconnected.

Description

2003 Microchip Technology Inc. DS30569B-page 9

Page 12

PIC16F870/871

NOTES:

DS30569B-page 10 2003 Microchip Technology Inc.

Page 13

PIC16F870/871

2.0 MEMORY ORGANIZATION

The PIC16F870/871 devices have three memory

blocks. The Program Memory and Data Memory have

separate buses, so that concurre nt access can occ ur,

and is detailed in this section. The EEPROM data

memory block is detailed in Section 3.0.

Additional informa tion on devi ce memory may be found

in the PICmic ro

Manual (DS33023).

2.1 Program Memory Organization

The PIC16F870/871 devices have a 13-bit program

counter capable of addressing an 8K x 14 program

memory space. The PIC16F870/871 devices have

2K x 14 words of FLASH program memory. Accessing

a location above the physically implemented address

will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector

is at 0004h.

FIGURE 2-1: PIC16F870/871 PROGRAM

CALL, RETURN

RETFIE, RETLW

TM

Mid-Range MCU Family Reference

MEMORY MAP AND STACK

PC<12:0>

13

2.2 Data Memory Organizati on

The data memory is partitioned into multiple banks

which contain the General Purpose Registers and the

Special Function Registers. Bits RP1 (STATUS<6>)

and RP0 (STATUS<5>) are the bank select bits.

RP<1:0> Bank

00 0

01 1

10 2

11 3

Each bank extends up to 7Fh (128 bytes). The lower

locations of each bank are reserved for the Special

Function Registers. Abo ve the Speci al Function Re gisters are General Purpose Registers, implemented as

static RAM. All implemented banks contain Special

Function Registers. Some “high use” Special Function

Registers from one bank may be mirrored in another

bank for code reduction and quicker access.

Note: EEPROM Data Memory description can

be found in Section 3.0 of this Data Sheet.

2.2.1 GENERAL PURPOSE REGISTER

FILE

The register file can be accessed either directly, or

indirectly through the File Select Register FSR.

On-Chip

Program

Memory

Stack Level 1

Stack Level 2

Stack Level 8

RESET Vector

Interrupt Vector

Page 0

0000h

0004h

0005h

07FFh

0800h

1FFFh

2003 Microchip Technology Inc. DS30569B-page 11

Page 14

PIC16F870/871

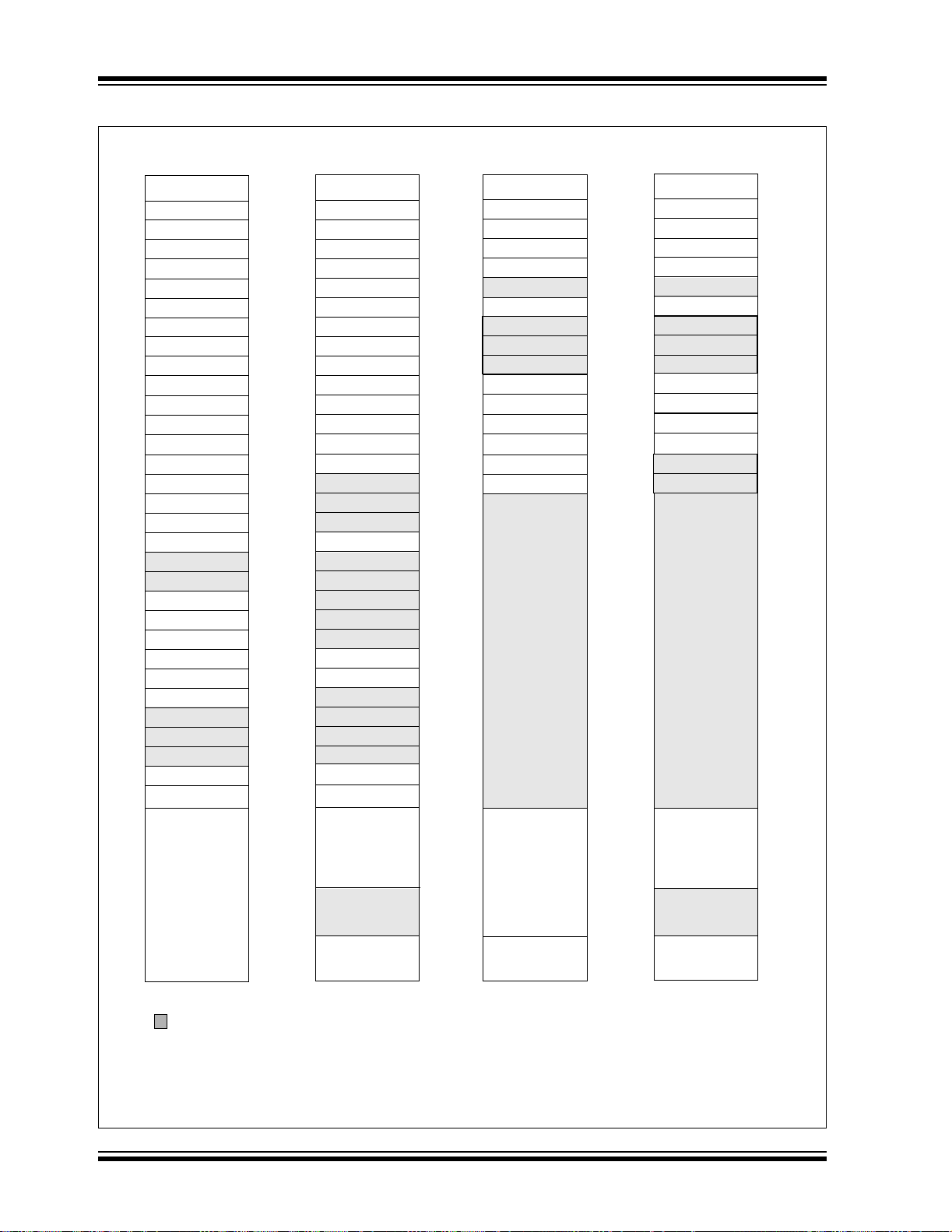

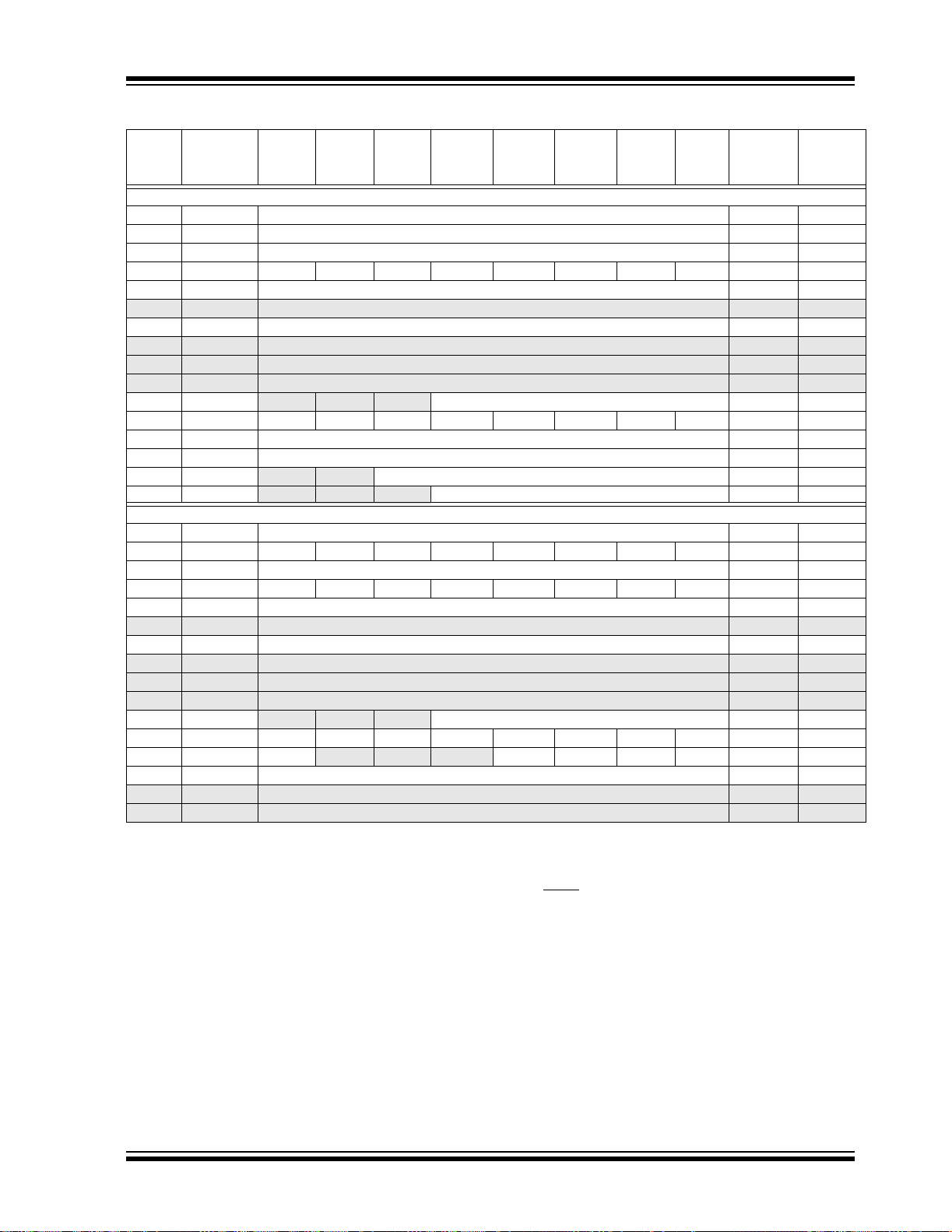

FIGURE 2-2: PIC16F870/871 RE GISTER F ILE MA P

File

Address

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PORTC

PORTD

PORTE

(2)

(2)

PCLATH

INTCON

PIR1

PIR2

TMR1L

TMR1H

T1CON

TMR2

T2CON

(*)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

Indirect addr.

OPTION_REG

STATUS

TRISD

TRISE

PCLATH

INTCON

13h

14h

CCPR1L

CCPR1H

CCP1CON

RCSTA

TXREG

RCREG

15h

16h

17h

18h

19h

1Ah

TXSTA

SPBRG

1Bh

1Ch

1Dh

ADRESH

ADCON0 ADCON1

1Eh

1Fh

20h

ADRESL

General

Purpose

Register

General

Purpose

32 Bytes

Register

96 Bytes

accesses

7Fh

70h-7Fh

Bank 0

PCL

FSR

TRISA

TRISB

TRISC

PIE1

PIE2

PCON

PR2

Bank 1

(2)

(2)

(*)

File

Address

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

BFh

C0h

EFh

F0h

FFh

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTB

PCLATH

INTCON

EEDATA

EEADR

EEDATH

EEADRH

accesses

20h-7Fh

accesses

70h-7Fh

Bank 2

(*)

File

Address

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

110h

120h

16Fh

170h

17Fh

Indirect addr.

OPTION_REG

PCL

STATUS

FSR

TRISB

PCLATH

INTCON

EECON1

EECON2

Reserved

Reserved

(1)

(1)

accesses

A0h - BFh

accesses

70h-7Fh

Bank 3

File

Address

(*)

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

190h

1A0h

1BFh

1C0h

1EFh

1F0h

1FFh

Unimplemented data memory locations, read as '0'.

* Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

2: These registers are not implemented on the PIC16F870.

DS30569B-page 12 2003 Microchip Technology Inc.

Page 15

PIC16F870/871

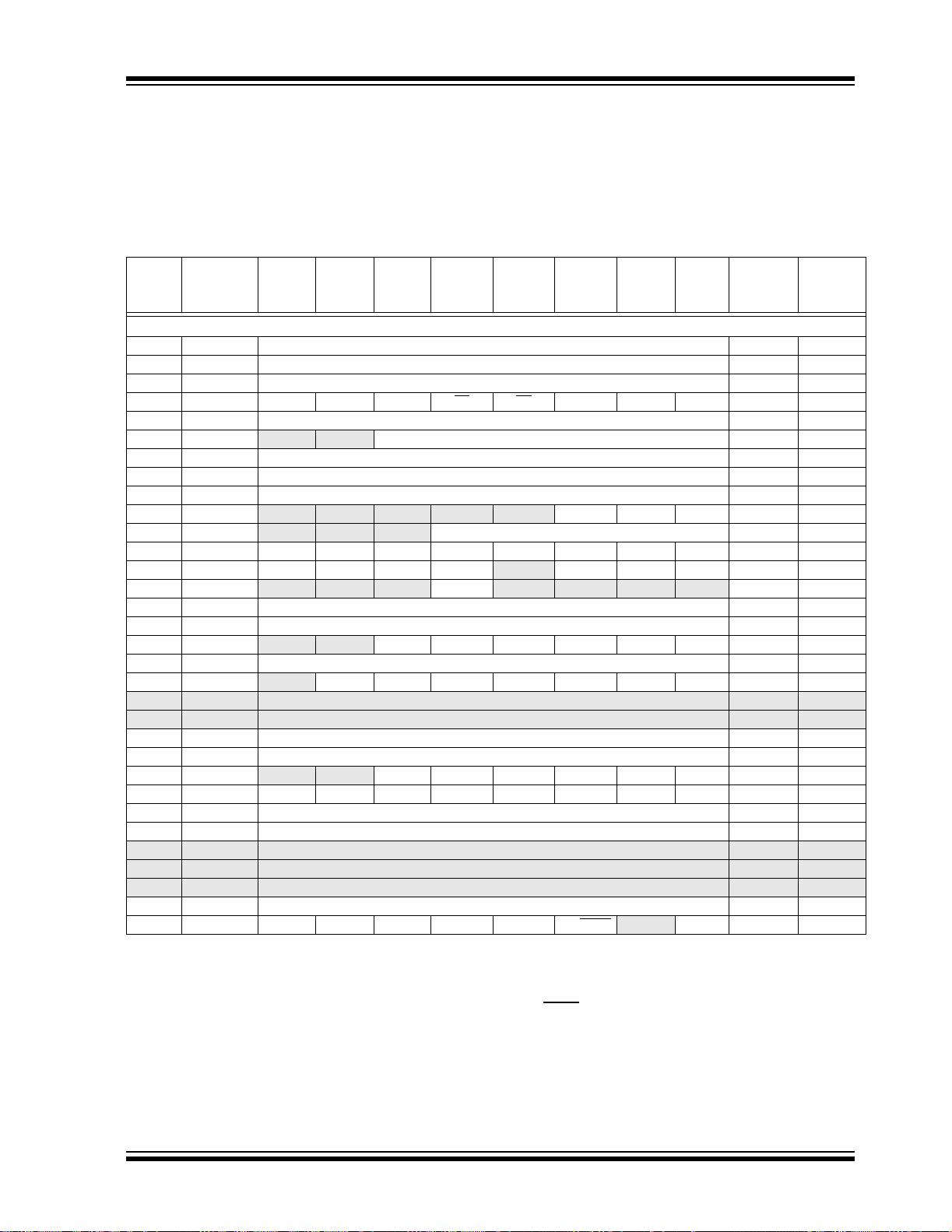

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by

the CPU and peripheral modules for controlling the

desired operation of the device. These registers are

implemented as static RAM. A list of these registers is

given in Table 2-1.

The Special Function Registers can be classified into

two sets: core (CPU) and peripheral. Those registers

associated with the core functions are described in

detail in this section. Those related to the operation of

the peripheral features are described in detail in the

peripheral feature section.

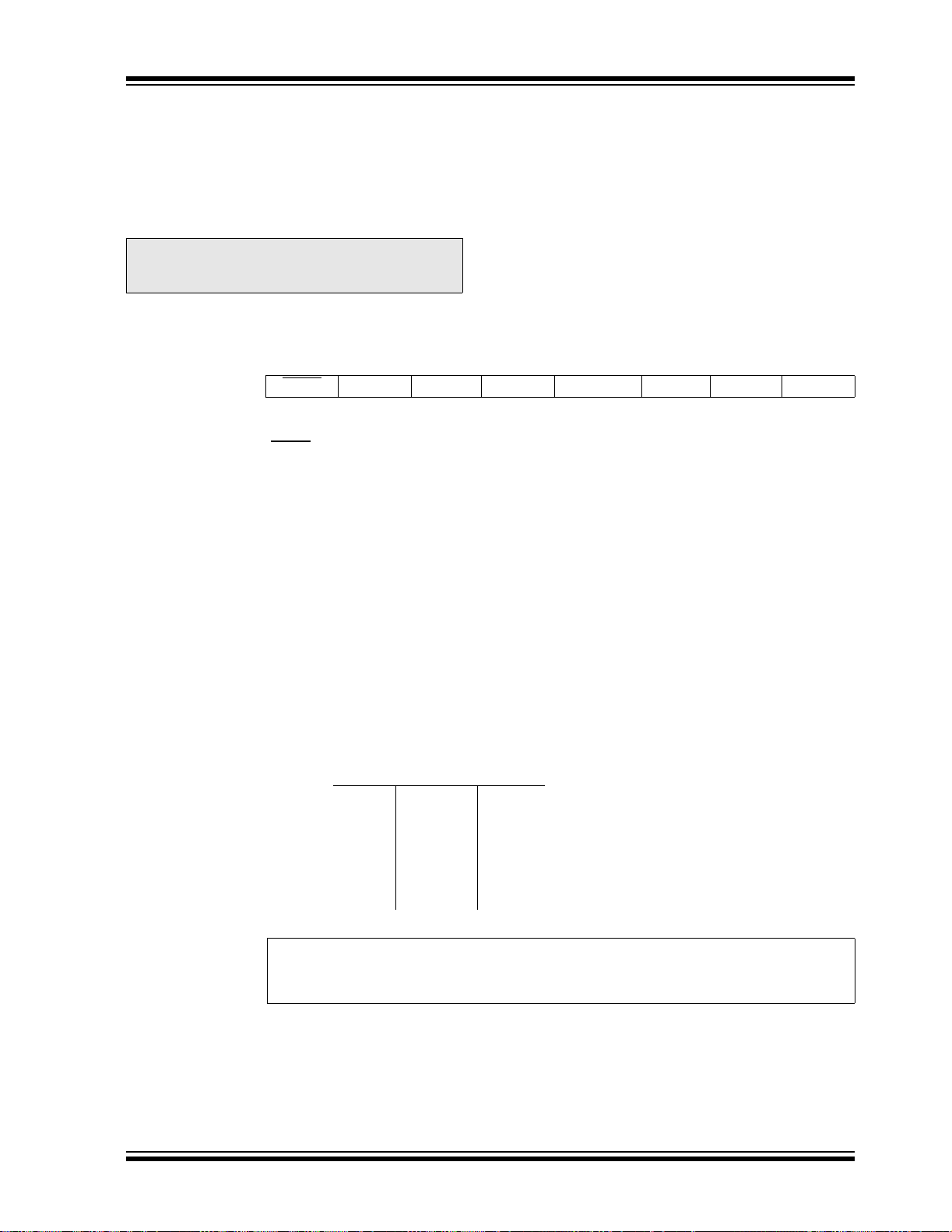

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

Address

Bank 0

(4)

00h

01h TMR0 Timer0 Module’s Register xxxx xxxx uuuu uuuu

(4)

02h

(4)

03h

(4)

04h

05h PORTA

06h PORTB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

07h PORTC PORTC Data Latch when written: PORTC pins when read xxxx xxxx uuuu uuuu

(5)

08h

(5)

09h

(1,4)

0Ah

(4)

0Bh

0Ch PIR1 PSPIF

0Dh PIR2

0Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu

0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu

10h T1CON

11h TMR2 Timer2 Module’s Register 0000 0000 0000 0000

12h T2CON

13h — Unimplemented — —

14h — Unimplemented — —

15h CCPR1L Capture/Compare/PWM Register1 (LSB) xxxx xxxx uuuu uuuu

16h CCPR1H Capture/Compare/PWM Regist er1 (MSB ) xxxx xxxx uuuu uuuu

17h CCP1CON

18h RCSTA SPEN RX9 SREN CREN ADDEN FERR OERR RX9D 0000 000x 0000 000x

19h TXREG USART Transmit Data Register 0000 0000 0000 0000

1Ah RCREG USART Receive Data Register 0000 0000 0000 0000

1Bh — Unimplemented — —

1Ch — Unimplemented — —

1Dh — Unimplemented — —

1Eh ADRESH A/D Result Register High Byte xxxx xxxx uuuu uuuu

1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE

Name

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

PORTD PORTD Data Latch when written: PORTD pins when read xxxx xxxx uuuu uuuu

PORTE — — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

— — PORTA Data Latch when written: PORTA pins when read --0x 0000 --0u 0000

(3)

ADIF RCIF TXIF — CCP1IF TMR2IF TMR1IF 0000 -000 0000 -000

— — —EEIF — — — — ---0 ---- ---0 ----

— — T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON --00 0000 --uu uuuu

— TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 -000 0000

— — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 --00 0000 --00 0000

—ADON0000 00-0 0000 00-0

Value on:

POR, BOR

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose

contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR

and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as ‘0’.

Value on

all other

RESETS

(2)

2003 Microchip Technology Inc. DS30569B-page 13

Page 16

PIC16F870/871

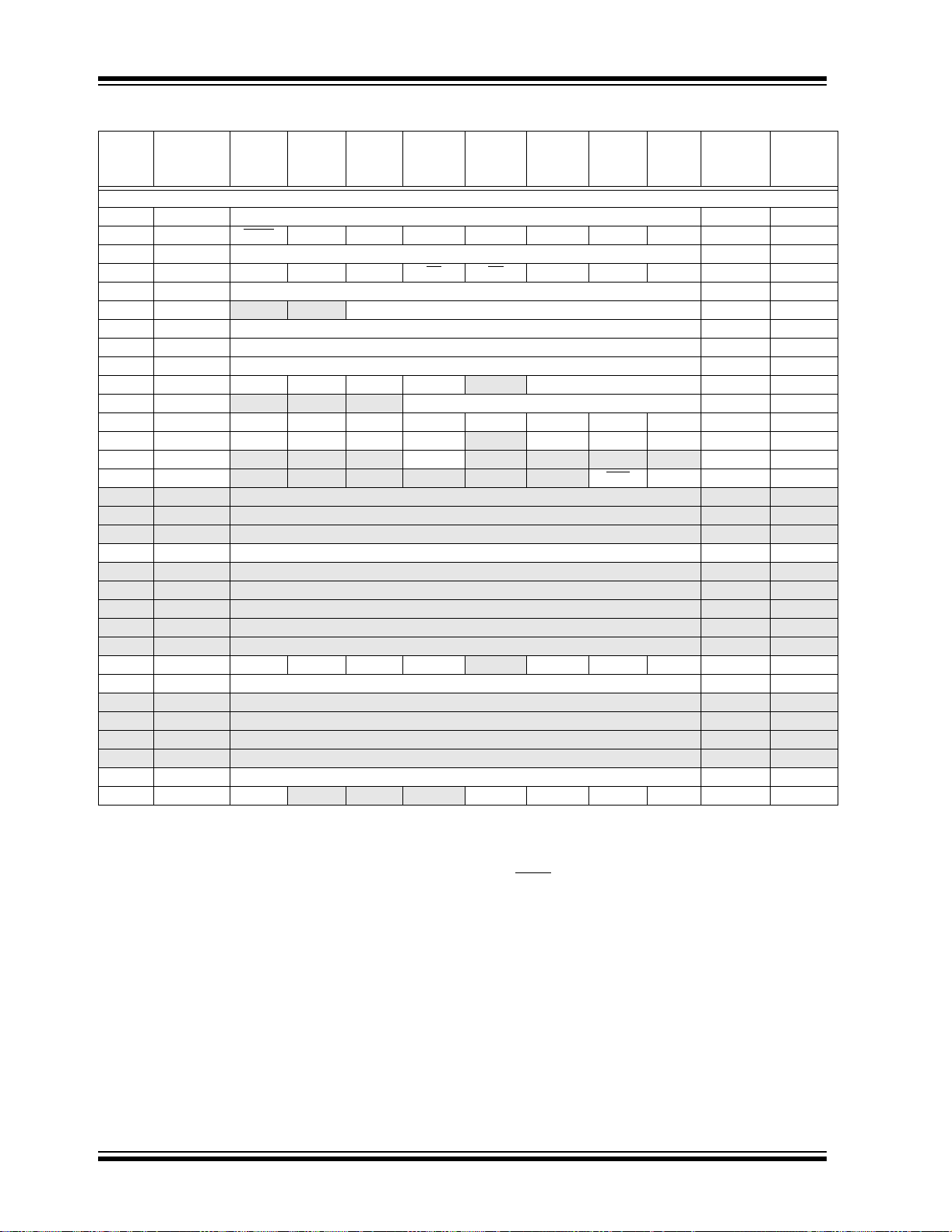

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address

Bank 1

(4)

80h

81h OPTION_REG RBPU

(4)

82h

(4)

83h

(4)

84h

85h TRISA

86h TRISB PORTB Data Direction Register 1111 1111 1111 1111

87h TRISC PORTC Data Direction Register 1111 1111 1111 1111

(5)

88h

(5)

89h

(1,4)

8Ah

(4)

8Bh

8Ch PIE1 PSPIE

8Dh PIE2

8Eh PCON

8Fh — Unimplemented — —

90h — Unimplemented — —

91h — Unimplemented — —

92h PR2 Timer2 Period Register 1111 1111 1111 1111

93h — Unimplemented — —

94h — Unimplemented — —

95h — Unimplemented — —

96h — Unimplemented — —

97h — Unimplemented — —

98h TXSTA CSRC TX9 TXEN SYNC

99h SPBRG Baud Rate Generator Register 0000 0000 0000 0000

9Ah — Unimplemented — —

9Bh — Unimplemented — —

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh ADRESL A/D Result Register Low Byte xxxx xxxx uuuu uuuu

9Fh ADCON1 ADFM

Name

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

TRISD PORTD Data Direction Register 1111 1111 1111 1111

TRISE IBF OBF IBOV PSPMODE — PO RTE Data Direction Bits 0000 -111 0000 -111

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

— — PORTA Data Direction Register --11 1111 --11 1111

(3)

ADIE RCIE TXIE — CCP1IE TMR2IE TMR1IE 0000 -000 0000 -000

— — — EEIE — — — — ---0 ---- ---0 ----

— — — — — —PORBOR ---- --qq ---- --uu

— BRGH TRMT TX9D 0000 -010 0000 -010

— — — PCFG3 PCFG2 PCFG1 PCFG0 0--- 0000 0--- 0000

Value on:

POR, BOR

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose

contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR

and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as ‘0’.

Value on

all other

RESETS

(2)

DS30569B-page 14 2003 Microchip Technology Inc.

Page 17

PIC16F870/871

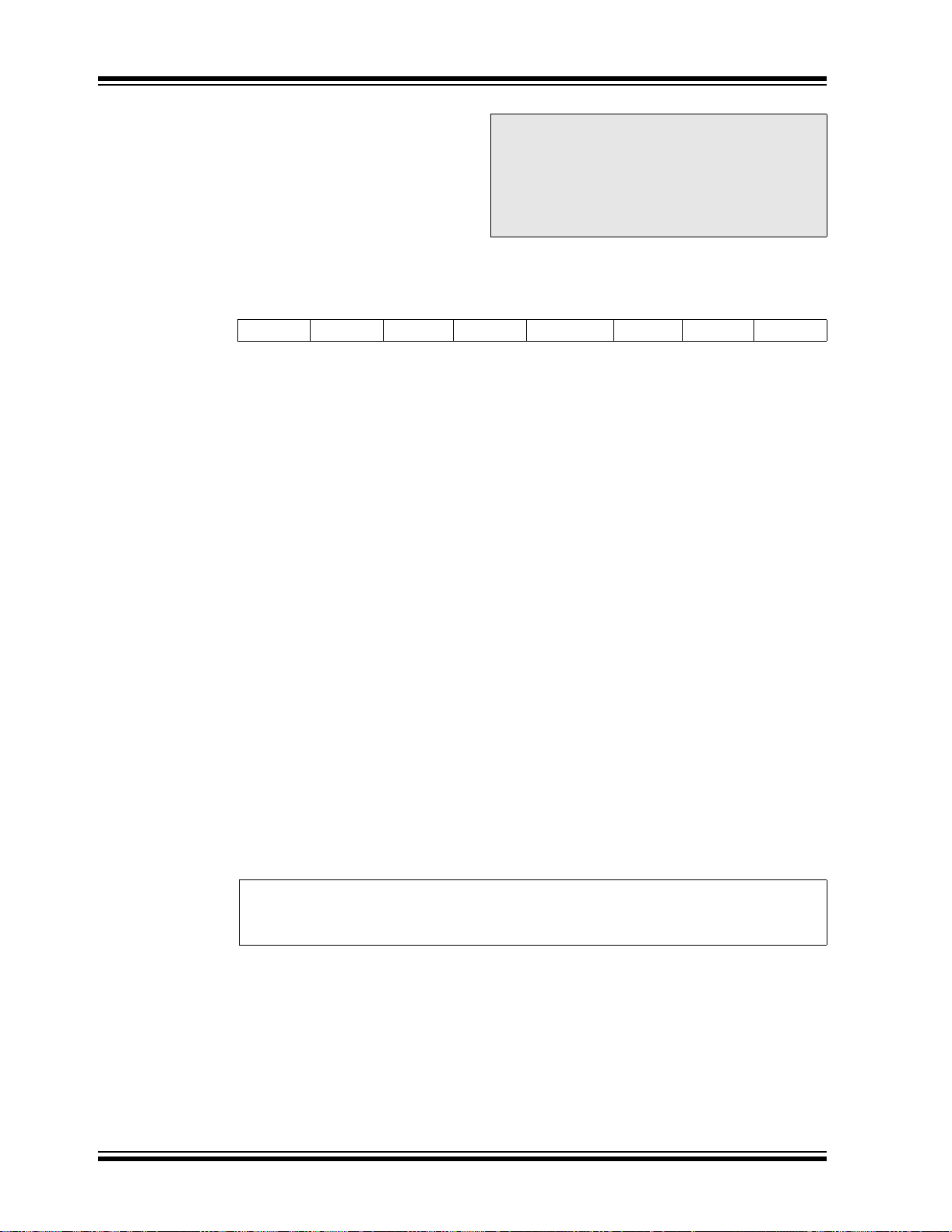

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address

Bank 2

(4)

100h

101h TMR0 Timer0 Module’s Register xxxx xxxx uuuu uuuu

(4)

102h

(4)

103h

(4)

104h

105h — Unimplemented — —

106h PORTB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

107h — Unimplemented — —

108h — Unimplemented — —

109h — Unimplemented — —

(1,4)

10Ah

(4)

10Bh

10Ch EEDATA EEPROM Data Register xxxx xxxx uuuu uuuu

10Dh EEADR EEPROM Address Register xxxx xxxx uuuu uuuu

10Eh EEDATH

10Fh EEADRH

Bank 3

(4)

180h

181h OPTION_REG RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

(4)

182h

(4)

183h

(4)

184h

185h — Unimplemented — —

186h TRISB PORTB Data Direction Register 1111 1111 1111 1111

187h — Unimplemented — —

188h — Unimplemented — —

189h — Unimplemented — —

(1,4)

18Ah

(4)

18Bh

18Ch EECON1 EEPGD

18Dh EECON2 EEPROM Control Register2 (not a physical register) ---- ---- ---- ---18Eh — Reserved maintain clear 0000 0000 0000 0000

18Fh — Reserved maintain clear 0000 0000 0000 0000

Name

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

STATUS IRP RP1 RP0 TO PD Z DC C 0001 1xxx 000q quuu

FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

STATUS IRP RP1 RP0 TO PD Z DC C 0001 1xxx 000q quuu

FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

— — EEPROM Data Register High Byte xxxx xxxx uuuu uuuu

— — — EEPROM Address Register High Byte xxxx xxxx uuuu uuuu

— — — WRERR WREN WR RD x--- x000 x--- u000

Value on:

POR, BOR

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose

contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR

and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as ‘0’.

Value on

all other

RESETS

(2)

2003 Microchip Technology Inc. DS30569B-page 15

Page 18

PIC16F870/871

2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of

the ALU, the RESET statu s and the b ank sele ct bit s for

data memory.

The STATUS register can be the destination for any

instruction, as with any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. These bit s are set or cleared ac cording to the

device logic. Furthermore, the TO

writable, therefore, the result of an instruction with the

STATUS register as destinatio n may be different than

intended.

and PD bits are not

For example, CLRF STATUS will clear the upper three

bits and set the Z bit. This leaves the STATUS register

as 000u u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register, because these instructions do not

affect the Z, C or DC bits from the ST ATUS register . F or

other instructions not affecting any status bits, see the

“Instruction Set Summary”.

Note 1: The C and DC bits operate as a borrow

and digit bo rrow bit, respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO PD ZDCC

bit 7 bit 0

bit 7-6 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP1:RP0: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

11 = Bank 1 (80h - FFh)

10 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes.

bit 4 TO

bit 3 PD

bit 2 Z: Zero bit

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

bit 0 C: Carry/borrow

: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

(for borrow

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note: For borrow

, the polarity is reversed)

bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

, the polarity is reversed. A subtraction is executed by adding the two’s

complement of the second operand. For rotate (RRF, RLF) instructions, this bit is

loaded with either the high or low order bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS30569B-page 16 2003 Microchip Technology Inc.

Page 19

PIC16F870/871

2.2.2.2 OPTION_RE G Regist er

The OPTION_REG register is a readable and writable

register , which cont ains various contr ol bits to conf igure

the TMR0 prescaler/WDT postscaler (single assignable register k nown als o as th e presca ler), t he Externa l

INT interrupt, TMR0 and the weak pull-u ps o n POR TB.

Note: To achieve a 1:1 prescaler assignment for

the TMR0 register, assign the prescaler to

the Watchdog Timer.

REGISTER 2-2: OPTION_REG REGISTER (ADDRESS: 81h,181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

bit 7 RBPU

: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 T0CS: TMR0 Clock Source Select bit

1 = Transition on RA 4/T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS2:PS0: Prescaler Rate Select bits

Bit Value T MR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2003 Microchip Technology Inc. DS30569B-page 17

Page 20

PIC16F870/871

2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the

TMR0 register overflow, RB Port change and External

RB0/INT pin interrupts.

Note: Interrupt flag bits get set when an interrupt

condition occurs, regar dless of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-3: INTCON REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 regis ter has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS30569B-page 18 2003 Microchip Technology Inc.

Page 21

2.2.2.4 PIE1 Regi st er

The PIE1 register cont ains the ind ividual enab le bits for

the periph eral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

REGISTER 2-4: PIE1 REGISTER (ADDRESS: 8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0

(1)

PSPIE

bit 7 bit 0

bit 7 PSPIE

1 = Enables the PSP read/write interrupt

0 = Disables the PSP read/write interrupt

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D converter interrupt

0 = Disables the A/D converter interrupt

bit 5 RCIE: USART Receive Interrupt Enable bit

1 = Enables the USART receive interrupt

0 = Disables the USART receive interrupt

bit 4 TXIE: USART Transmit Interrupt Enable bit

1 = Enables the USART transmit interrupt

0 = Disables the USART transmit interrupt

bit 3 Unimplemented: Read as ‘0’

bit 2 CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 inte rrupt

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

ADIE RCIE TXIE CCP1IE TMR2IE TMR1IE

(1)

: Parallel Slave Port Read/Write Interrupt Enable bit

PIC16F870/871

Note 1: PSPIE is reserved on the PIC16F870; always maintain this bit clear.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2003 Microchip Technology Inc. DS30569B-page 19

Page 22

PIC16F870/871

2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for

the periph eral interrupts.

Note: Interrupt flag bits get set when an interrupt

condition occurs , regardle ss of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an

interrupt.

REGISTER 2-5: PIR1 REGISTER (ADDRESS: 0Ch)

R/W-0 R/W-0 R-0 R-0 U-0 R/W-0 R/W-0 R/W-0

(1)

PSPIF

bit 7 bit 0

bit 7 PSPIF

bit 6 ADIF: A/D Converter Interrupt Flag bit

bit 5 RCIF: USART Receive Interrupt Flag bit

bit 4 TXIF: USART Transmit Interrupt Flag bit

bit 3 Unimplemented: Read as ‘0’

bit 2 CCP1IF: CCP1 Interrupt Flag bit

bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

(1)

1 = A read or a write operation has taken place (must be cleared in software)

0 = No read or write has occurred

1 = An A/D conversion completed

0 = The A/D conversion is not complete

1 = The USART receive buffer is full

0 = The USART receive buffer is empty

1 = The USART transmit buffer is empty

0 = The USART transmit buffer is full

Capture mode:

1 = A TMR1 regist er capture occurred (must be clear ed in software)

0 = No TMR1 regi ster captur e occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode.

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

ADIF RCIF TXIF CCP1IF TMR2IF TMR1IF

: Parallel Slave Port Read/Wri te Interru pt Fla g bit

Note 1: PSPIF is reserved on the PIC16F870; always maintain this bit clear.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS30569B-page 20 2003 Microchip Technology Inc.

Page 23

2.2.2.6 PIE2 Regi st er

The PIE2 register contains the individual enable bit for

the EEPROM write operation interrupt.

REGISTER 2-6: PIE2 REGISTER (ADDRESS: 8Dh)

U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0

— — — EEIE — — — —

bit 7 bit 0

bit 7-5 Unimplemented: Read as '0'

bit 4 EEIE: EEPROM Write Operation Interrupt Enable bit

1 = Enable EE write interrupt

0 = Disable EE w rite interrupt

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

PIC16F870/871

2003 Microchip Technology Inc. DS30569B-page 21

Page 24

PIC16F870/871

2.2.2.7 PIR2 Register

The PIR2 register contains the fla g bit for the EEPROM

write operation interrupt.

.

Note: Interrupt flag bits get set when an interrupt

condition occurs , regardle ss of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-7: PIR2 REGISTER (ADDRESS: 0Dh)

U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0

— — — EEIF — — — —

bit 7 bit 0

bit 7-5 Unimplemented: Read as '0'

bit 4 EEIF: EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation is not complete or has not been started

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS30569B-page 22 2003 Microchip Technology Inc.

Page 25

2.2.2.8 PCON Regist er

The Power Control (PCON) register contains flag bits

to allow differentiation between a Power-on Reset

(POR), a Brown-out Reset (BOR), a Watchdog Reset

(WDT) and an external MCLR

Note: BOR is unknown on POR. It must be set

by the user and checked on subsequent

RESETS to see if BOR is clear, indicating

a brown-out has occurred. The BOR

status bit is a don’t care and is not

predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the

configuration word).

Reset.

REGISTER 2-8: PCON REGISTER (ADDRESS: 8Eh)

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-1

— — — — — —PORBOR

bit 7 bit 0

PIC16F870/871

bit 7-2 Unimplemented: Read as '0'

bit 1 POR

bit 0 BOR

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2003 Microchip Technology Inc. DS30569B-page 23

Page 26

PIC16F870/871

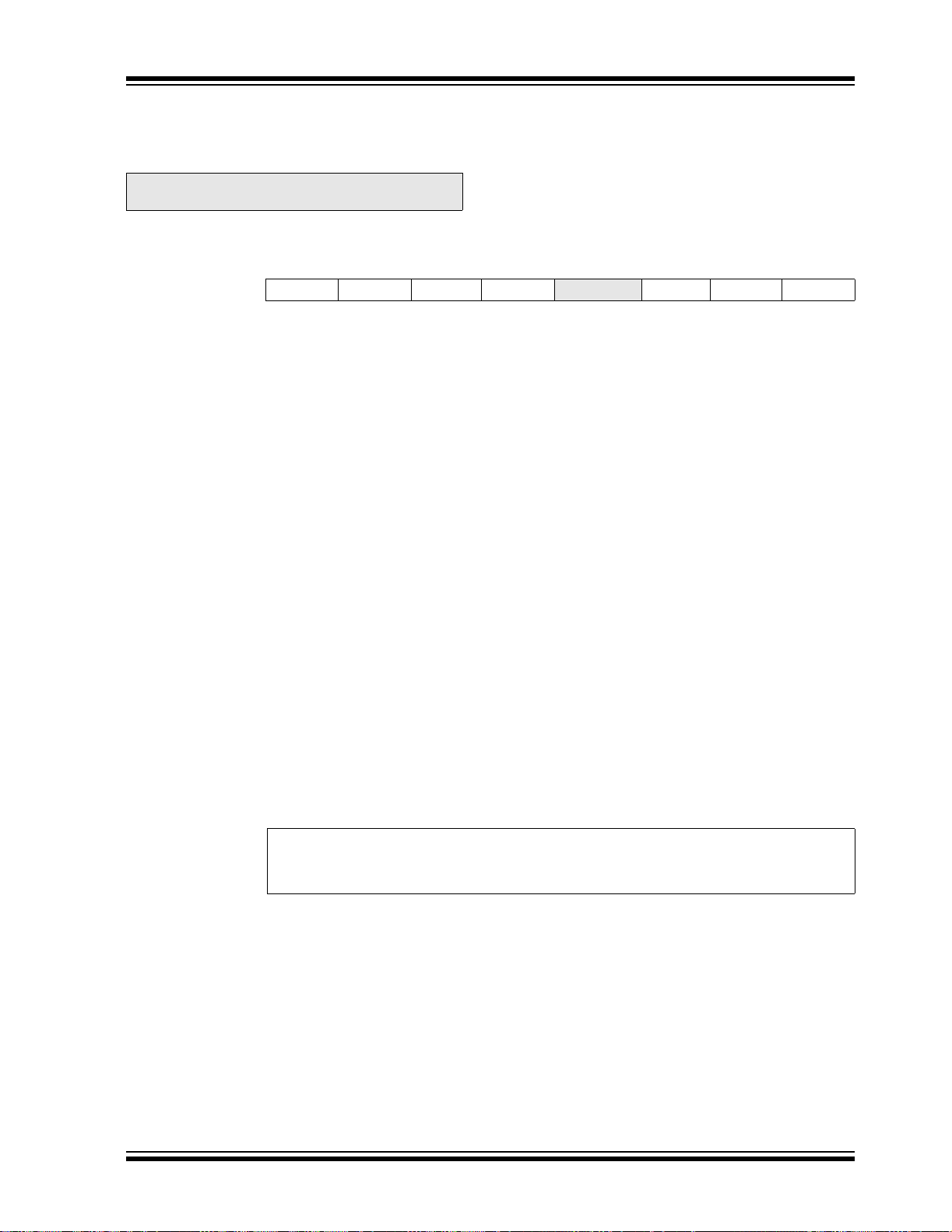

2.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low

byte comes from the PCL register, which is a readable

and writable register. The upper bits (PC<12:8>) are

not readable, but are indirectly writable through the

PCLA TH reg is ter. On any RESET, the upper bits of the

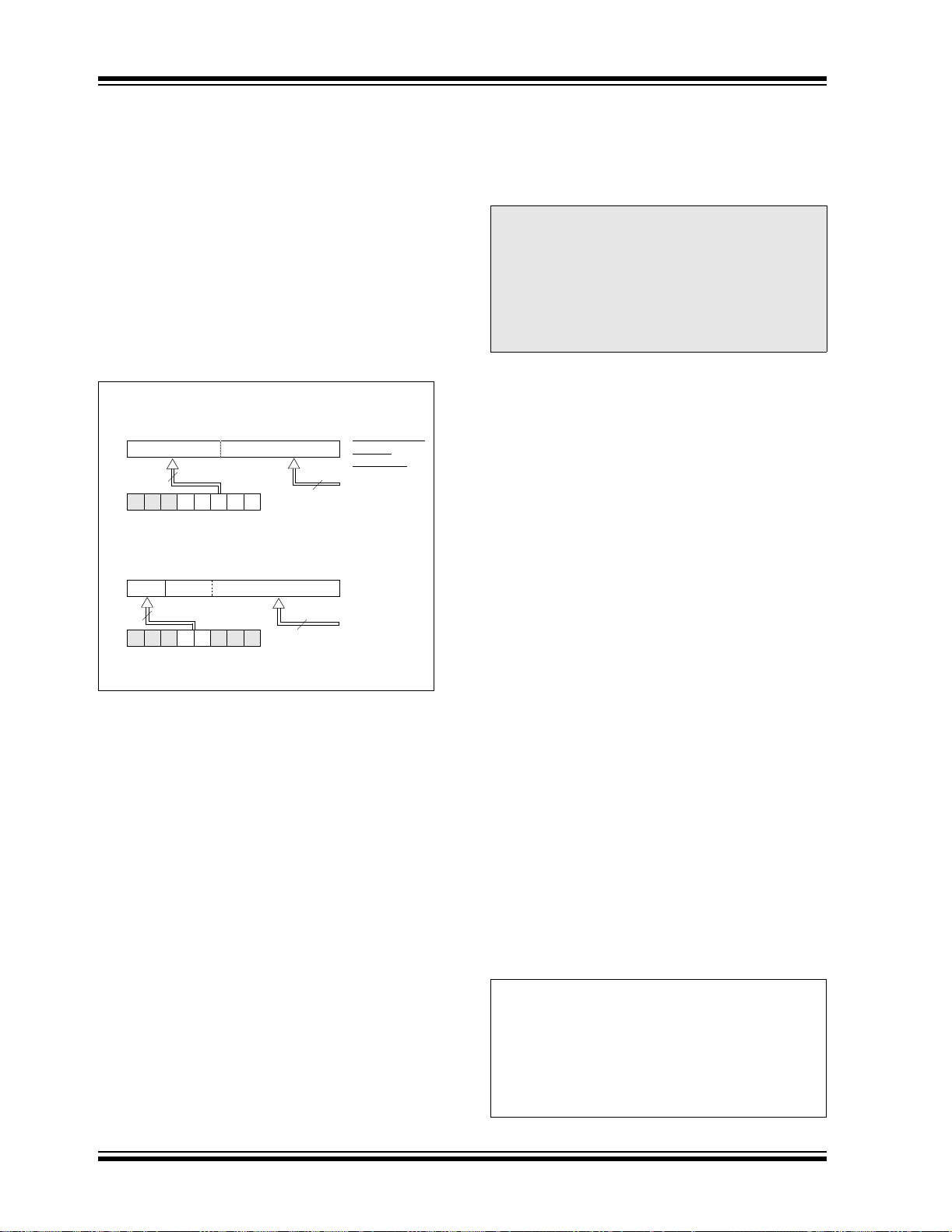

PC will be cleared. Fig ure2-3 shows the two situations

for the loading of the PC. The up per ex ample in th e figure shows how the PC is loaded on a write to PCL

(PCLATH<4:0> → PCH). The lower example in the fi gure shows how the PC is loaded during a CALL or GOTO

instruction (PCLATH<4:3> → PCH).

FIGURE 2-3: LOADING OF P C IN

DIFFERENT SI T UA T IONS

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

11

8

Instruction with

PCL as

Destination

ALU

GOTO,CALL

Opcode <10:0>

The stack operat es as a circular buf fer . This means th at

after the stack has been PUSHed eight times, the ninth

push overwrites the va lue tha t was s tored fro m the first

push. The tenth pus h ov erwr i tes the se co nd push (and

so on).

Note 1: There are no status bits to indicate stack

overflow or stack underflow conditions.

2: There are no instructions/mnemonics

called PUSH or POP. These are actions

that occur from the exec ution of the CALL,

RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt

address.

2.4 Program Memory Paging

The PIC16FXXX architecture is capable of addressing

a continuous 8K word block of program memory. The

CALL and GOTO instructions provide 11 bits of the

address, which all ows branc hes within any 2K program

memory page. Therefore, the 8K words of program

memory are broken into four pages. Since the

PIC16F872 has only 2K words of program memory or

one page, ad ditional code is not requi red to e nsure th at

the correct pag e is selected before a CALL or GOTO

instruction is executed. The PCLATH<4:3> bits should

always be maintained as zeros. If a return from a CALL

instruction (or interrupt) is executed, the entire 13-bit

PC is popped off the stack. Manipulation of the

PCLATH is not required for the return instructions.

PCLATH

2.3.1 COMPUT ED GOTO

A computed GOTO is accomplish ed by adding an offset

to the progr am counter (ADDWF PCL). When doing a

table read using a computed GOTO method, care

should be exercise d i f the t able loca tio n cros ses a PCL

memory boundary (each 256-byte block). Refer to the

application note, “Implementing a Table Read"

(AN556).

2.3.2 STACK

The PIC16FXXX family has an 8-level deep x 13-bit

wide hardware stack. The stack space is not part of

either program or data space and the stack pointer is

not readable or writable. The PC is PUSHed onto the

stack when a CALL instruction is executed, or an interrupt causes a branch . Th e s t ac k is POPed in the event

of a RETURN, RETLW or a RETFIE instruction

execution. PCLATH is not affected by a PUSH or POP

operation.

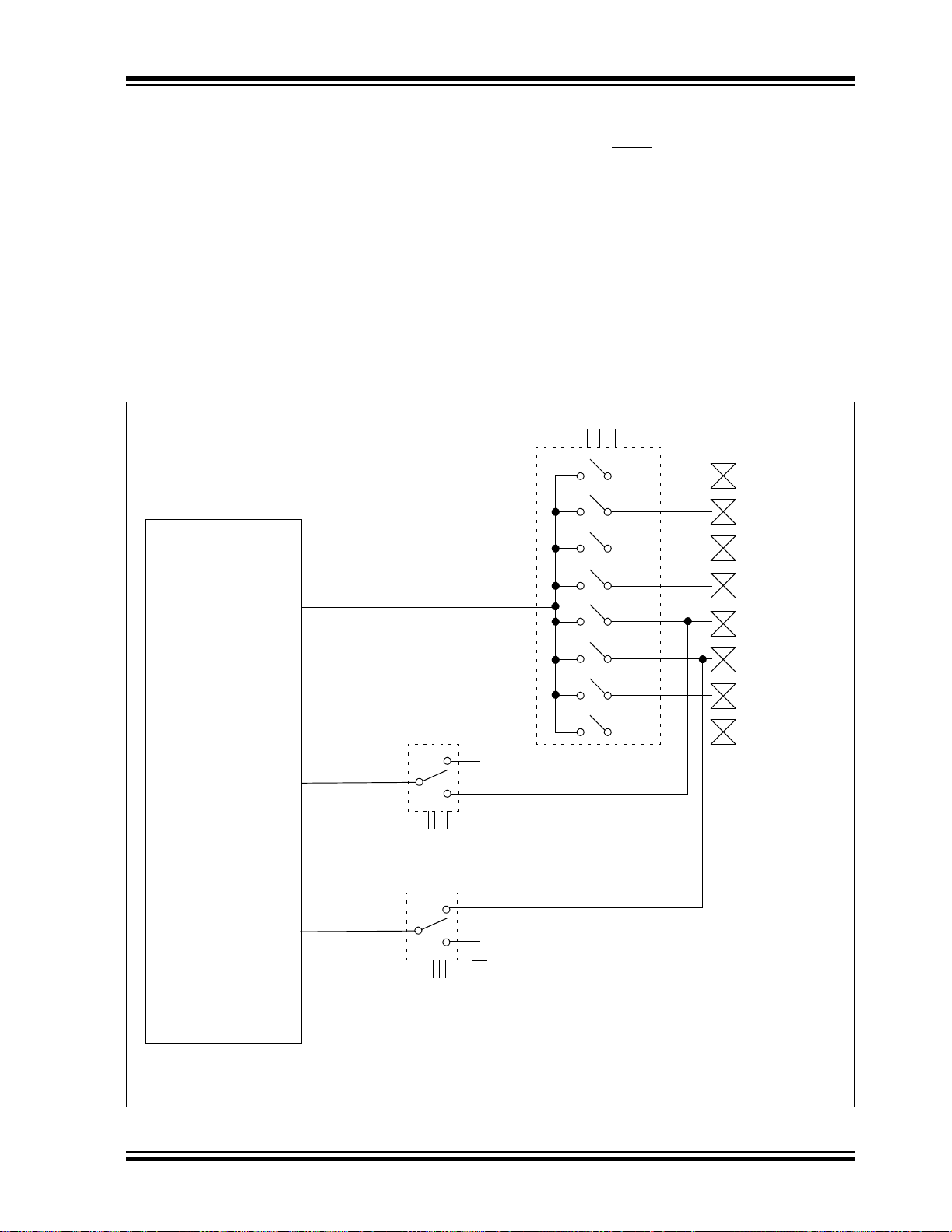

2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physica l register . Addr essing

the INDF register will cause indirect address ing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually

accesses the regist er po int ed to by the File Select register, FSR. Reading the INDF register itself indirectly

(FSR = 0) will read 00h. Writing to the INDF register

indirectly result s in a no op erat ion (alth oug h status bits

may be affected ). An ef fectiv e 9-bit add ress is obt ained

by concatenating the 8 -bit F SR registe r and the IRP bit

(STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM locations 20h-2Fh

using indirect addressing is shown in Example 2-1.

EXAMPLE 2-1: INDIRECT ADDRESSING

movlw 0x20 ;initialize pointer

movwf FSR ;to RAM

NEXT clrf INDF ;clear INDF register

incf FSR,F ;inc pointer

btfss FSR,4 ;all done?

goto NEXT ;no clear next

CONTINUE

: ;yes continue

DS30569B-page 24 2003 Microchip Technology Inc.

Page 27

FIGURE 2-4: DIRECT/INDIRECT ADDRESSING

RP1: RP0 6

from opcode

0

PIC16F870/871

Indirect AddressingDirect Addressing

IRP FSR Register

7

0

Bank Select Location Select

00 01 10 11

00h

Data

(1)

Memory

7Fh

Bank 0 Bank 1 Bank 2 Bank 3

Note 1: For register file map detail see Figure 2-2.

80h

FFh

100h

17Fh

180h

1FFh

Bank Select

Location Select

2003 Microchip Technology Inc. DS30569B-page 25

Page 28

PIC16F870/871

NOTES:

DS30569B-page 26 2003 Microchip Technology Inc.

Page 29

PIC16F870/871

3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are

readable and writab le during no rmal operati on over the

entire V

issued from user code (which includes removing code

protection). The d at a m em ory is n ot d ire ctl y ma pped in

the register file sp ace. Instead , it is indirectly ad dressed

through the Special Function Registers (SFR).

There are six SFRs us ed to read and wr ite the pro gram

and data EEPROM memory. These registers are:

• EECON1

• EECON2

• EEDATA

• EEDATH

• EEADR

• EEADRH

The EEPROM data memory allows byte read and write.

When interfacing to the data memory block, EEDATA

holds the 8-bit data for read/write and EEADR holds the

address of the EEPROM locati on bein g access ed. The

registers EEDATH and EEADRH are not used for data

EEPROM access. The PIC16F870/871 devices have

64 bytes of data EEPROM with an addre ss rang e fro m

0h to 3Fh.

The EEPROM data memory is rated for high erase/

write cycles. The write time is controlled by an on-chip

timer. The write time will vary with voltage and temperature, as well as from chip-to-chip. Please refer to the

specifications for exact limits.

The program memory allows word reads and writes.

Program memory acce ss a llo ws fo r c hec ks um c alc ul ation and calibration table storage. A byte or word write

automatically erases the location and writes the new

data (erase before write). Writing to program memory

will cease operati on until the writ e is complete. T he program memory cannot be accessed during the write,

therefore code ca nnot e xecut e. During the w rite operation, the oscillator continues to clock the peripherals,

and therefore, they continue to operate. Interrupt

events will be detected and essentially “queued” until

the write is completed. When the write completes, the

next instruction in the pipeline is executed and the

branch to the interrupt vector address will occur.

When interfacing to the program memory block, the

EEDATH:EEDATA registers form a two-byte word,

which holds the 14-bit data for read/write. The

EEADRH:EEADR registers form a two-byte word,

which holds the 13-bit address of the FLASH location

being accessed. The PIC16F870/871 devices have

2K words of program FLASH with an address range

from 0h to 7FFh. The unused upper bits in both the

EEDATH and EEDATA registers all read as ‘0’s.

DD range. A bulk erase operation may not be

The value written to pr ogram memory does not need to

be a valid instruction. Therefore, up to 14-bit numbers

can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that

forms an invalid instruction results in a NOP.

3.1 EEADR

The address registers can address up to a maxim um of

256 bytes of data EEPROM or up to a maximum of

8K words of program FLASH. However, the

PIC16F870/871 have 64 bytes of data EEPROM and

2K words of program FLASH.

When selecting a program address value, the MSByte

of the address is written to the EEADRH register and

the LSByte is written to the EEADR register. When

selecting a data address value, only the LSByte of the

address is written to the EEADR register.

On the PIC16F870/871 devices, the upper two bits of

the EEADR must always be cleared to prevent inadvertent access to the wr on g lo ca tion in d ata EEPROM.

This also applies to the program memory. The upper

five MSbits of EEADRH must always be clear during

program FLASH access.

3.2 EECON1 and EECON2 Registers

The EECON1 register is the control register for configuring and initiatin g the access. The EECON2 reg ister is

not a physically implemented register, but is used

exclusively in the memory write sequence to prevent

inadvertent writes.

There are many bits used to control the read and write

operations to EEPROM data and FLASH program

memory. The EEPGD bit determines if the access will

be a program or data memory access. When clear, any

subsequent operations will work on the EEPROM data

memory. When set, all subsequent operations will

operate in the program memory.

Read operations only us e one additio nal bit, RD, whic h

initiates the read operation from the desired memory

location. Once this bit is set, the value of the desired

memory location will be available in the data registers.

This bit cannot be cleared by firmware. It is automatically cleared at the end of the read operation. For

EEPROM data memory reads, the data will be available in the EEDAT A registe r in the v ery ne xt instruc tion

cycle after the RD bit is set. For program memory

reads, the data will be loaded into the

EEDATH:EEDATA registers, following the second

instruction after the RD bit is set.

2003 Microchip Technology Inc. DS30569B-page 27

Page 30

PIC16F870/871

Write operations have two control bit s, WR and WREN,

and two status bits, WRERR and EEIF. The WREN bit

is used to enable or disable the write operation. When

WREN is clear, the write operation will be disabled.

Therefore, the WREN bit must be set befo re ex ec utin g

a write operation. Th e WR bit is used to initi ate the write

operation. It also is automatically cleared at the end of

the write operation. The interrupt flag EEIF is used to

determine when the mem ory write comp letes. This fla g

must be cleared in software before setting the WR bit.

For EEPROM data memory, once the WREN bit and

the WR bit have been set, the desired memory addres s

in EEADR will be erased, followed by a wri te of the data

in EEDATA. This operation takes place in parallel with

the microcontroller continuing to execute normally.

When the write is c omplete, the EEIF flag bit will be set.

For program memory, once the WREN bit and the WR

bit have been set, the m icrocontr oller will cease to ex e-

cute instructions. T he de sired mem ory l ocatio n poi nted

to by EEADRH:EEADR will be erased. Then, the data

value in EEDATH:EEDATA will be programmed. When

complete, the EEIF flag bit will be set and the

microcontroller will continue to execute code.

The WRERR bit is used to indicate when the

PIC16F870/871 devic es have bee n reset during a write

operation. WRERR should be cleared after Power-on

Reset. Thereafter, it should be checked on any other

RESET. The WRERR bit is set when a write operation

is interrupted by a MCLR

Reset, during normal o peration. In these situati ons, following a RESET , the user should check the WRERR bit

and rewrite the memory locati on, if set. The c ontents of

the data registers, address registers and EEPGD bit

are not affected by either MCLR

Time-out Reset, during normal operation.

REGISTER 3-1: EECON1 REGISTER (ADDRESS: 18Ch)

R/W-x U-0 U-0 U-0 R/W-x R/W-0 R/S-0 R/S-0

EEPGD — — — WRERR WREN WR RD

bit 7 bit 0

bit 7 EEPGD: Program/Data EEPROM Select bit

1 = Accesses program memory

0 = Accesses data memory

(This bit cannot be changed while a read or write operati on is in progress.)

bit 6-4 Unimplemented: Read as '0'

bit 3 WRERR: EEPROM Error Flag bit

1 = A write operation is prematurely terminated (any MCLR

normal operation)

0 = The write operation completed

bit 2 WREN: EEPROM Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Wri te Control bit

1 = Initiates a write cycle. (The bit is cleared by hardware once write is complete. The WR bit

can only be set (not cleared) in software.)

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

1 = Initiates an EEPROM read. (RD is cleared in hardware. The RD bit can only be set (not

cleared) in software.)

0 = Does not initiate an EEPROM read

Reset, or a WDT Time-out

Reset, or WDT

Reset or any WDT Reset during

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS30569B-page 28 2003 Microchip Technology Inc.

Page 31

PIC16F870/871

3.3 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the

desired address to access be written to the EEADR

register and clear th e EEPGD bit. Afte r the RD bit is se t,

data will be av ailable in the EEDATA reg ister on the

very next instruction cycle. EEDAT A will hold this value

until another read operation is initiated or until it is

written by firmware.

The steps to reading the EEPROM data memory are:

1. Write the address to EEDATA. Make sure that

the address is not larger than the memory size

of the PIC16F870/871 devices.

2. Clear the EEPGD bit to point to EEPROM data

memory.

3. Set the RD bit to start the read operation.

4. Read the data from the EEDATA register.

EXAMPLE 3-1: EEPROM DATA READ

BSF STATUS, RP1 ;

BCF STATUS, RP0 ;Bank 2

MOVF ADDR, W ;Write address

MOVWF EEADR ;to read from

BSF STATUS, RP0 ;Bank 3

BCF EECON1, EEPGD ;Point to Data memory

BSF EECON1, RD ;Start read operation

BCF STATUS, RP0 ;Bank 2

MOVF EEDATA, W ;W = EEDATA

3.4 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data

memory . Both address and dat a valu es must be writte n

to the SFRs. The EEPGD bit must be cleared, and the

WREN bit must be set, t o enab le w rites. The WREN b it

should be kept clear at all times, ex cept when writi ng to

the EEPROM data. The WR bit can only be set if the

WREN bit was set in a previous operation (i.e., they

both cannot be set in the same opera tio n). The WREN

bit should then be cleared by firmware after the write.

Clearing the WREN bit before the write actually

completes will not terminate the write in progress.