PIC16F685/687/689/690

Data Sheet

20-Pin Flash-Based, 8-Bit

CMOS Microcontrollers with

nanoWatt Technology

© 2005 Microchip Technology Inc. Preliminary DS41262A

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digit al Millennium Copyright Act. If suc h a c t s

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED,

WRITTEN OR ORAL, STATUTORY OR OTHERWISE,

RELATED TO THE INFORMATION, INCLUDING BUT NOT

LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE,

MERCHANTABILITY OR FITNESS FOR PURPOSE.

Microchip disclaims all liability arising from this information and

its use. Use of M icrochip’s prod ucts as critical components in

life support systems is not authorized except with express

written approval by Microchip. No licenses are conveyed,

implicitly or otherwise, under any Microchip intellectual property

rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, K

EELOQ, microID, MPLAB, PIC, PICmicro, PICSTART,

PRO MATE, PowerSmart, rfPIC, and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB,

PICMASTER, SEEVAL, SmartSensor and The Embedded

Control Solutions Company are registered trademarks of

Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM,

dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR,

FanSense, FlexROM, fuzzyLAB, In-Circuit Serial

Programmin g, IC SP, ICEPI C, M PASM, MPLIB, MPLINK,

MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail,

PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB,

rfPICDEM, Select Mode, Smart Serial, SmartTel, Total

Endurance and WiperLock are trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2005, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 quality system certification for

its worldwide headquarters, design and wafer fabrication facilities in

Chandler and Tempe, Arizona and Mountain View, California in

October 2003. The Company’s quality system processes and

procedures are for its PICmicro

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

8-bit MCUs, KEELOQ

®

code hopping

DS41262A-page ii Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

20-Pin Flash-Based, 8-Bit CMOS Microcontrollers with

nanoWatt Technology

High-Performance RISC CPU:

• Only 35 instructions to learn:

- All single-cycle instructions except branches

• Operating speed:

- DC – 20 MHz oscillator/clock input

- DC – 200 n s instruction cycle

• Interrupt capability

• 8-level deep hardware stack

• Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

• Precision Internal Oscillator:

- Factory calibrated to ±1%

- Software selectable frequency range of

8 MHz to 32 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for

power savings

• Power-saving Sleep mode

• Wide operating voltage range (2.0V-5.5V)

• Industrial and Extended Temperature range

• Power-on Reset (PO R)

• Power-up Timer (PWRTE) and Oscillator Start-up

Timer (OST)

• Brown-out Reset (BOR) with software control

option

• Enhanced low-current Watchdog Timer (WDT)

with on-chip oscillator (software selectable

nominal 268 seconds with full prescaler) with

software enable

• Multiplexed Master Clear/Input pin

• Programmable code protection

• High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

• Enhanced USART Module:

- Supports RS-485, RS-232, and LIN 2.0

- Auto-Baud Detect

- Auto-wake-up on Start bit

Low-Power Features:

• Standby Current:

- 1 nA @ 2.0V, typical

• Operating Current:

-20μA @ 32 kHz, 2.0V, typical

- <1 mA @ 4 MHz, 5.5V, typical

• Watchdog Timer Current:

-<1μA @ 2.0V, typical

Peripheral Features:

• 17 I/O pins and 1 input only pin:

- High current source/sink for direct LED drive

- Interrupt-on-pin change

- Individually programmable weak pull-ups

- Ultra Low-Power Wake-up (ULPWU)

• Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference

REF) module (% of VDD)

(CV

- Comparator inputs and outputs externally

accessible

- SR Latch mode

- Timer 1 Gate Sync Latch

• A/D Converter:

- 10-bit resolution and 12 channels

• Timer0: 8-bit timer/counter with 8-bit

programmable prescaler

• Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode

as Timer1 oscillator if INTOSC mode

selected

• Timer2: 8-bit timer/counter with 8-bit period

register, prescaler and postscaler

• Enhanced Capture, Compare, PWM+ module:

- 16-bit Capture, max resolution 12.5 ns

- Compare, max resolution 200 ns

- 10-bit PWM with 1, 2 or 4 output channels,

programmable “dead time”, max frequency

20 kHz

- PWM output steering control

• Synchronous Serial Port (SSP):

- SPI™ mode (Master and Slave)

2

C™ (Master/Slave modes):

•I

2

C™ address mask

-I

• In-Circuit Serial Programming

pins

TM

(ICSPTM) via two

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 1

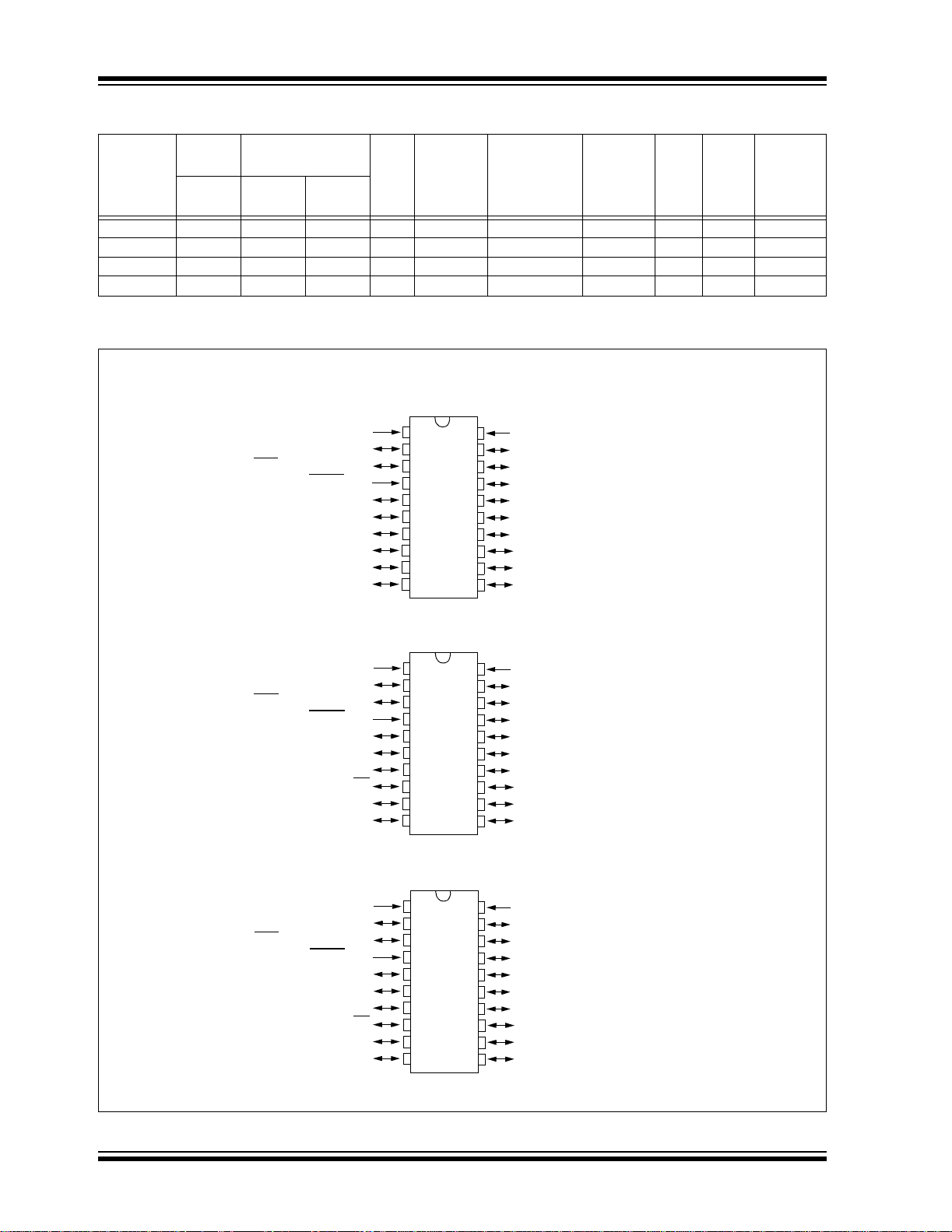

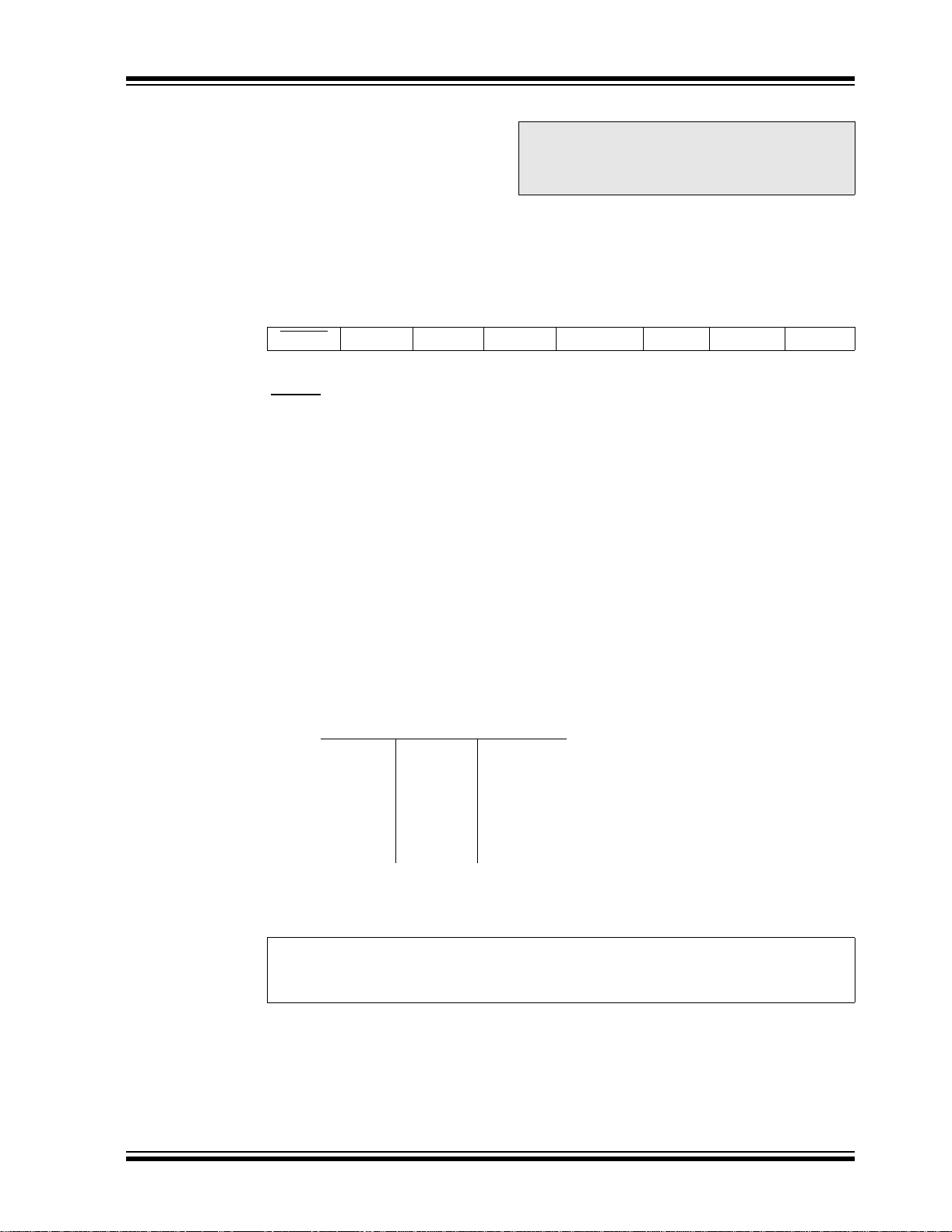

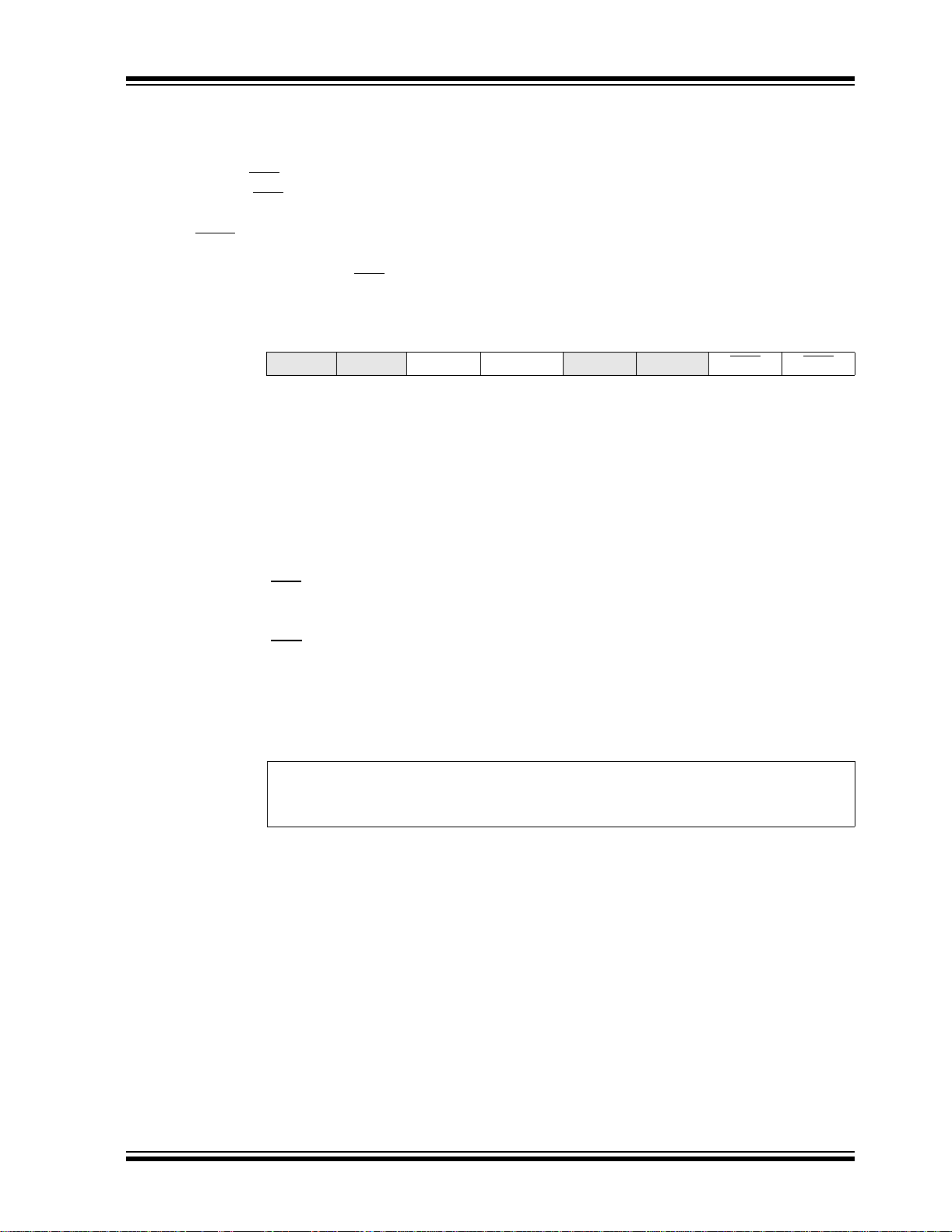

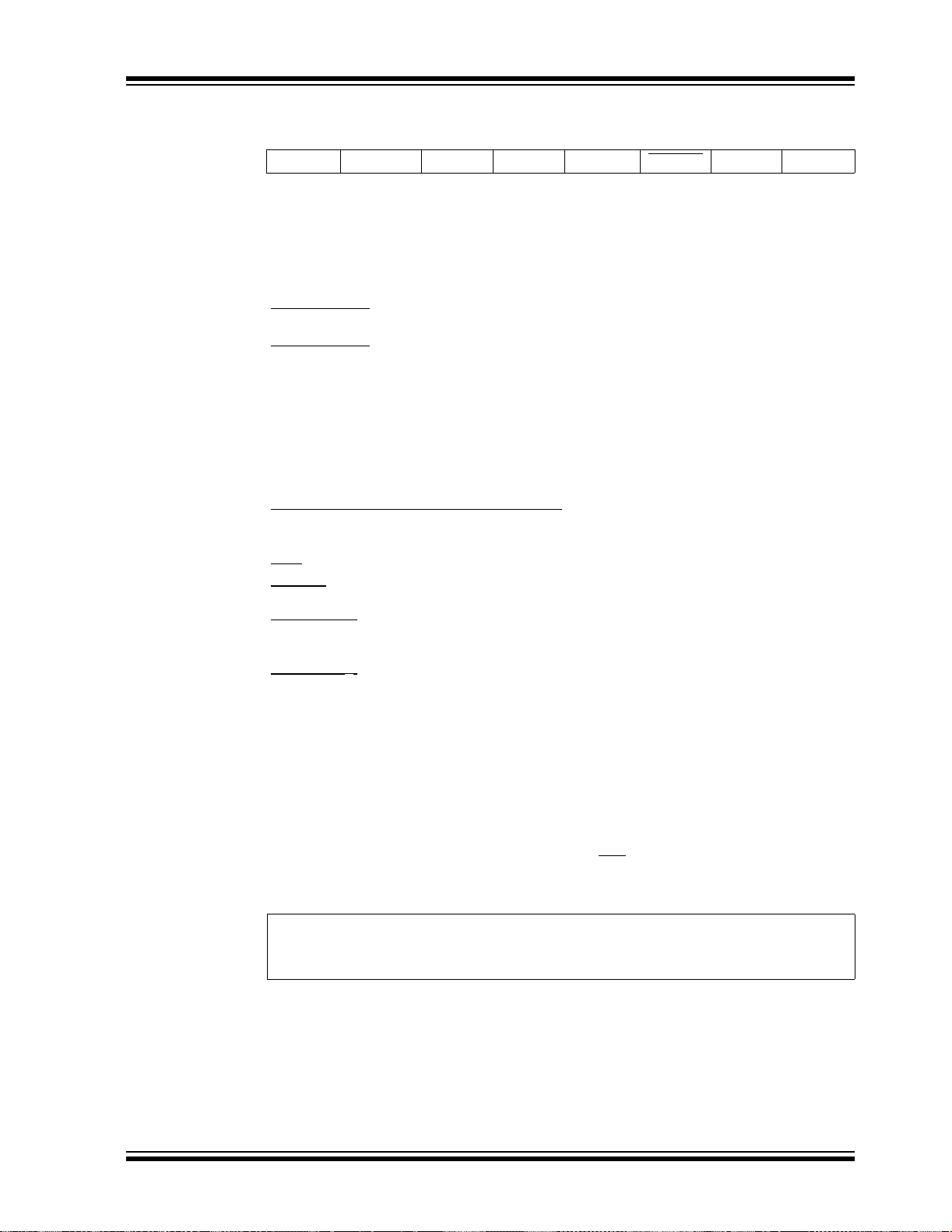

PIC16F685/687/689/690

Program

Memory

Device

Flash

(words)

Data Memory

SRAM

EEPROM

(bytes)

(bytes)

I/O

10-bit A/D

(ch)

Comparators

Timers

8/16-bit

SSP ECCP+ EUSART

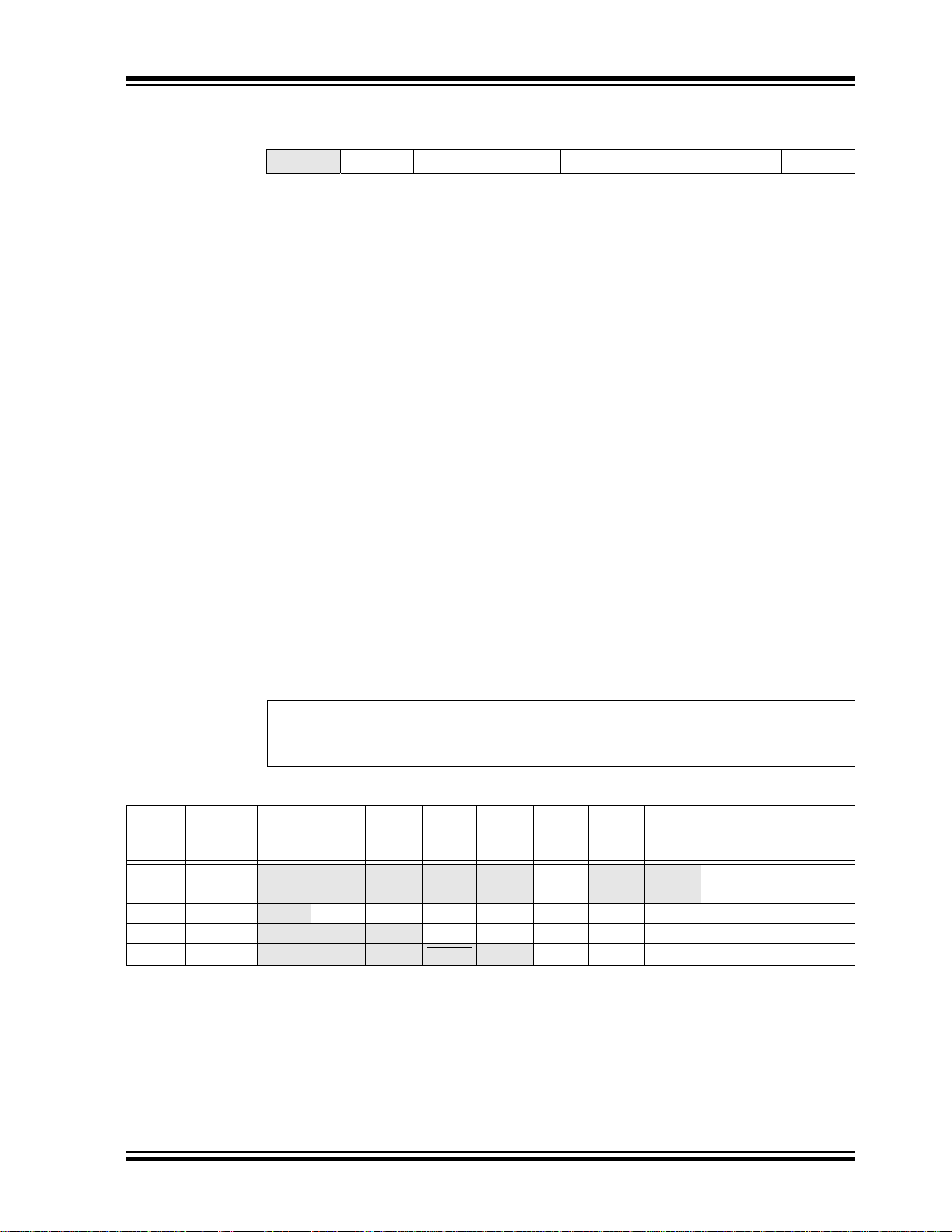

PIC16F685 4096 256 256 18 12 2 2/1 No Yes No

PIC16F687 2048 128 256 18 12 2 1/1 Yes No Yes

PIC16F689 4096 256 256 18 12 2 1/1 Yes No Yes

PIC16F690 4096 256 256 18 12 2 2/1 Yes Yes Yes

Pin Diagrams

20-pin PDIP, SOIC, SSOP

RA5/T1CKI/OSC1/CLKIN

RA4/AN3/T1G

/OSC2/CLKOUT

RA3/MCLR

RC5/CCP1/P1A

RC4/C2OUT/P1B

RC3/AN7/P1C

VDD

/VPP

RC6/AN8

RC7/AN9

RB7

1

2

3

4

5

6

7

8

9

10

PIC16F685

20

19

18

17

16

15

14

13

12

11

VSS

RA0/AN0/C1IN+/ICSPDAT/ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6/P1D

RB4/AN10

RB5/AN11

RB6

REF/ICSPCLK

RA5/T1CKI/OSC1/CLKIN

RA4/AN3/T1G

RA5/T1CKI/OSC1/CLKIN

RA4/AN3/T1G

/OSC2/CLKOUT

RA3/MCLR

RC7/AN9/SDO

/OSC2/CLKOUT

RA3/MCLR

RC5/CCP1/P1A

RC4/C2OUT/P1B

RC3/AN7/P1C

RC7/AN9/SDO

VDD

/VPP

RC5/CPP1

RC4/C2OUT

RC3/AN7

RC6/AN8/SS

RB7/TX/CK

VDD

/VPP

RC6/AN8/SS

RB7/TX/CK

1

2

3

4

5

6

7

8

9

10

1

2

3

4

5

6

7

8

9

10

PIC16F687/689

PIC16F690

20

19

18

17

16

15

14

13

12

11

20

19

18

17

16

15

14

13

12

11

VSS

RA0/AN0/C1IN+/ICSPDAT/ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6

RB4/AN10/SDI/SDA

RB5/AN11/RX/DT

RB6/SCK/SCL

VSS

RA0/AN0/C1IN+/ICSPDAT/ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6/P1D

RB4/AN10/SDI/SDA

RB5/AN11/RX/DT

RB6/SCK/SCL

REF/ICSPCLK

REF/ICSPCLK

DS41262A-page 2 Preliminary © 2005 Microchip Technology Inc.

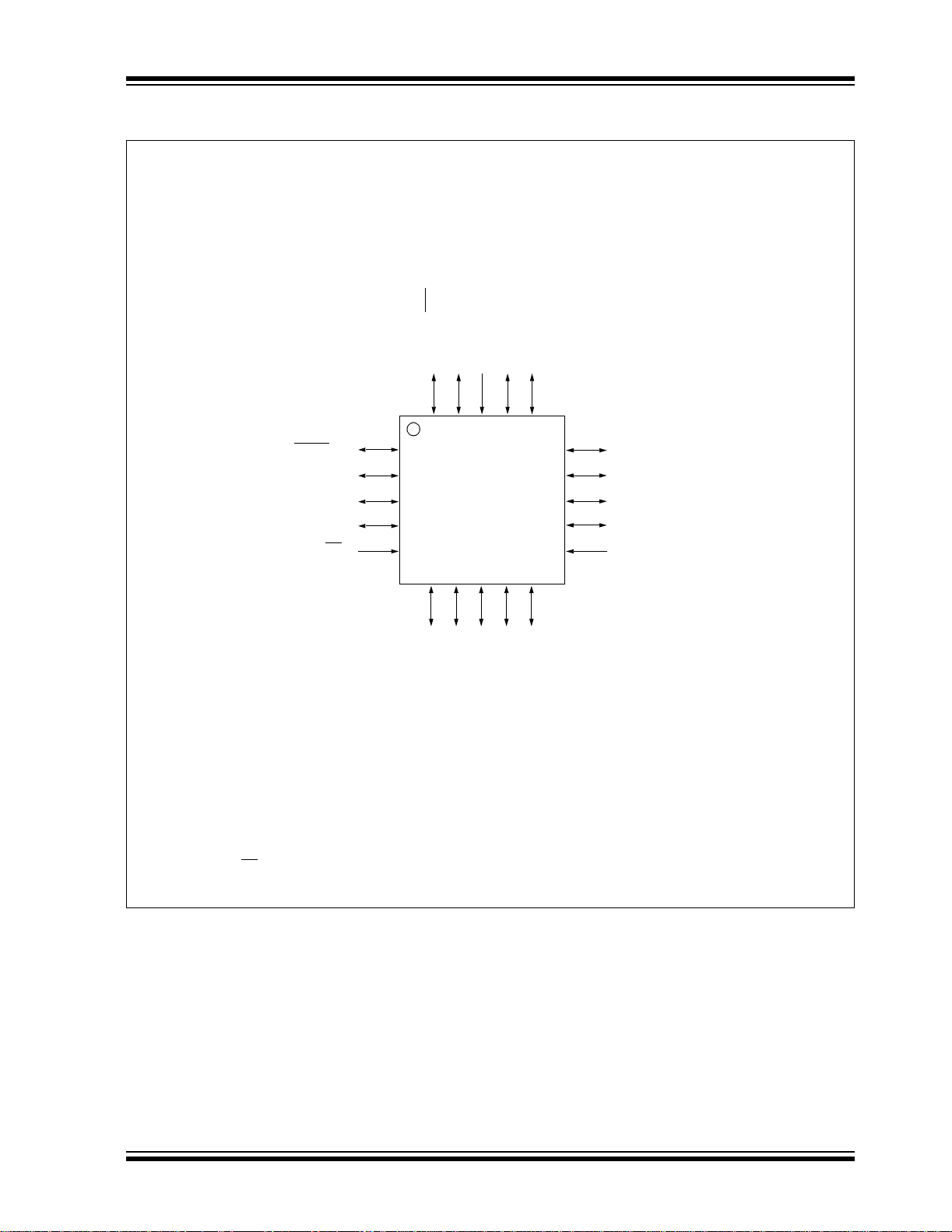

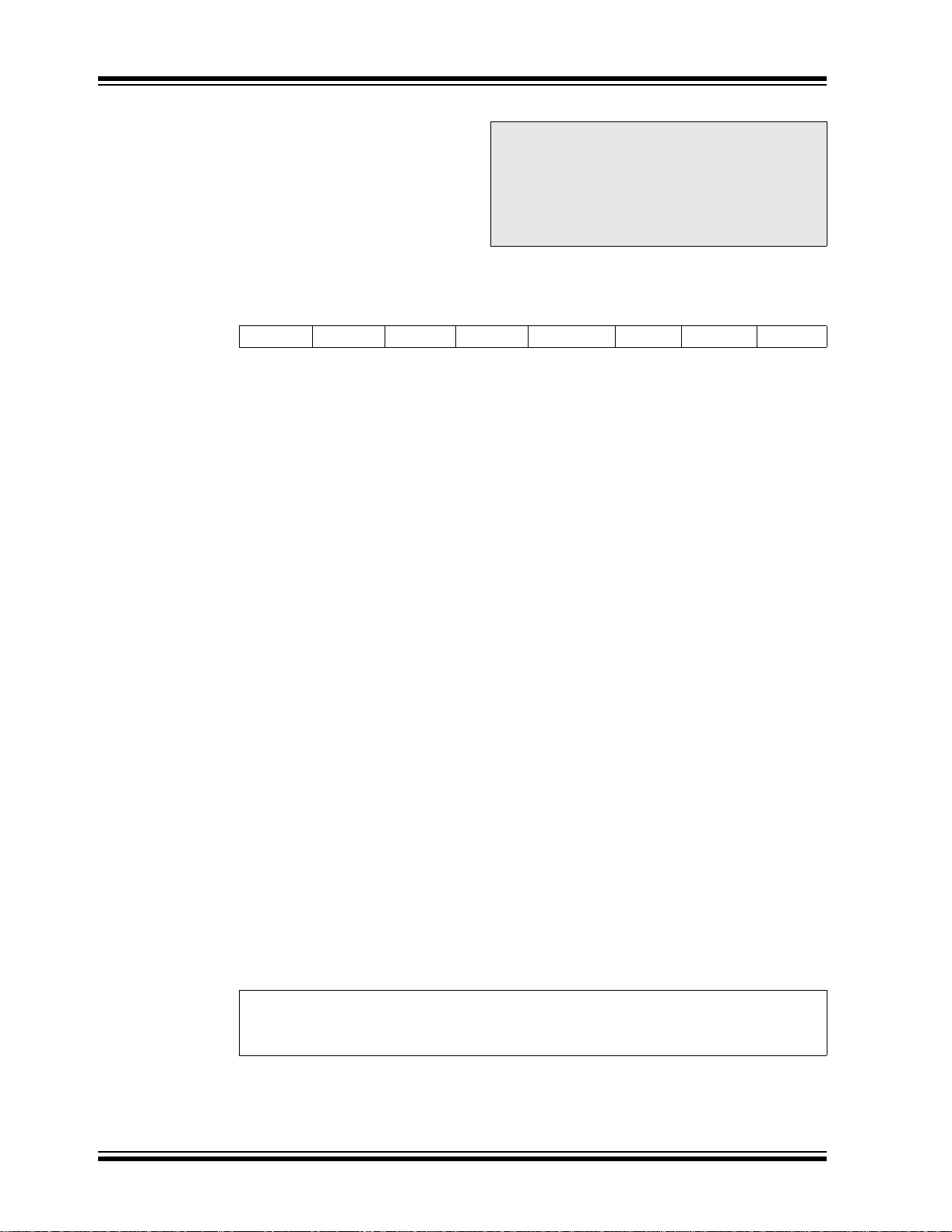

Pin Diagrams (Continued)

20-pin QFN

PIC16F685/687/689/690

RA3/MCLR/VPP

RC5/CCP1/P1A

RC4/C2OUT/P1B

RC3/AN7/P1C

RC6/AN8/SS

RA5/T1CKI/OSC1/CLKIN

19

689/690

7

(2)

(2)

RB7/TX/CK

DD

VSS

V

18

8

RB6/SCK/SCL

RA0/AN0/C1IN+/ICSPDAT/ULPWU

17

16

15

14

13

12

11

9

10

(2)

(2)

RB5/AN11/RX/DT

RB4/AN10/SDI/SDA

RA1/AN1/C12IN-/VREF/ICSPCLK

RA2/AN2/T0CKI/INT/C1OUT

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6/P1D

(1)

RA4/AN3/T1G/OSC2/CLKOUT

20

1

(1)

(1)

(1)

(2)

2

PIC16F685/687/

3

4

5

6

(2)

RC7/AN9/SDO

Note 1: P1A, P1B, P1C and P1D are available on PIC16F685/PIC16F690 only.

2: SS

, SDO, SDA, RX and DT available on PIC16F687/PIC16F689/PIC16F690 only.

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 3

PIC16F685/687/689/690

Table of Contents

1.0 Device Overview..........................................................................................................................................................................5

2.0 Memory Organization.................................................................................................................................................................15

3.0 Clock Sources............................................................................................................................................................................ 35

4.0 I/O Ports....... ............................................................. ..................... ..................... ....................................................................... 47

5.0 Timer0 Module ........................................................................................................................................................................... 69

6.0 Timer1 Module with Gate Control...............................................................................................................................................73

7.0 Timer2 Module ........................................................................................................................................................................... 77

8.0 Comparator Module.............................................................................. .... .... ....... .... .... .. .... .........................................................79

9.0 Analog-to-Digital Converter (A/D) Module..................................................................................................................................93

10.0 Data EEPROM and Flash Program Memory Control ............................................................................................................... 105

11.0 Enhanced Capture/Compare/PWM+ (ECCP+) Module ........................................................................................................... 113

12.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)............................................................... 131

13.0 SSP Module Overview .............................................................................................................................................................155

14.0 Special Features of the CPU........................................................ ..................... ....................................................................... 173

15.0 Instruction Set Summary.......................................................................................................................................................... 193

16.0 Development Support. .............................................................................................................................................................. 203

17.0 Electrical Specifications ............................................................................................................................................................ 209

18.0 DC and AC Characteristics Graphs and Tables....................................................................................................................... 237

19.0 Packaging Information.......................... ..................... .......................................... ..................................................................... 239

Appendix A: Data Sheet Revision History.......................................................................................................................................... 245

Appendix B: Migrating from other PICmicro® Devices ...................................................................................................................... 245

The Microchip Web Site....................................... ............................................................. ................................................................. 253

Customer Change Notification Service ..............................................................................................................................................253

Customer Support.............................................................................................................................................................................. 253

Reader Response.............................................................................................................................................................................. 254

Product Identification System............................................................................................................................................................. 255

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best docum entation possible to ensure s uccessful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of

silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS41262A-page 4 Preliminary © 2005 Microchip Technology Inc.

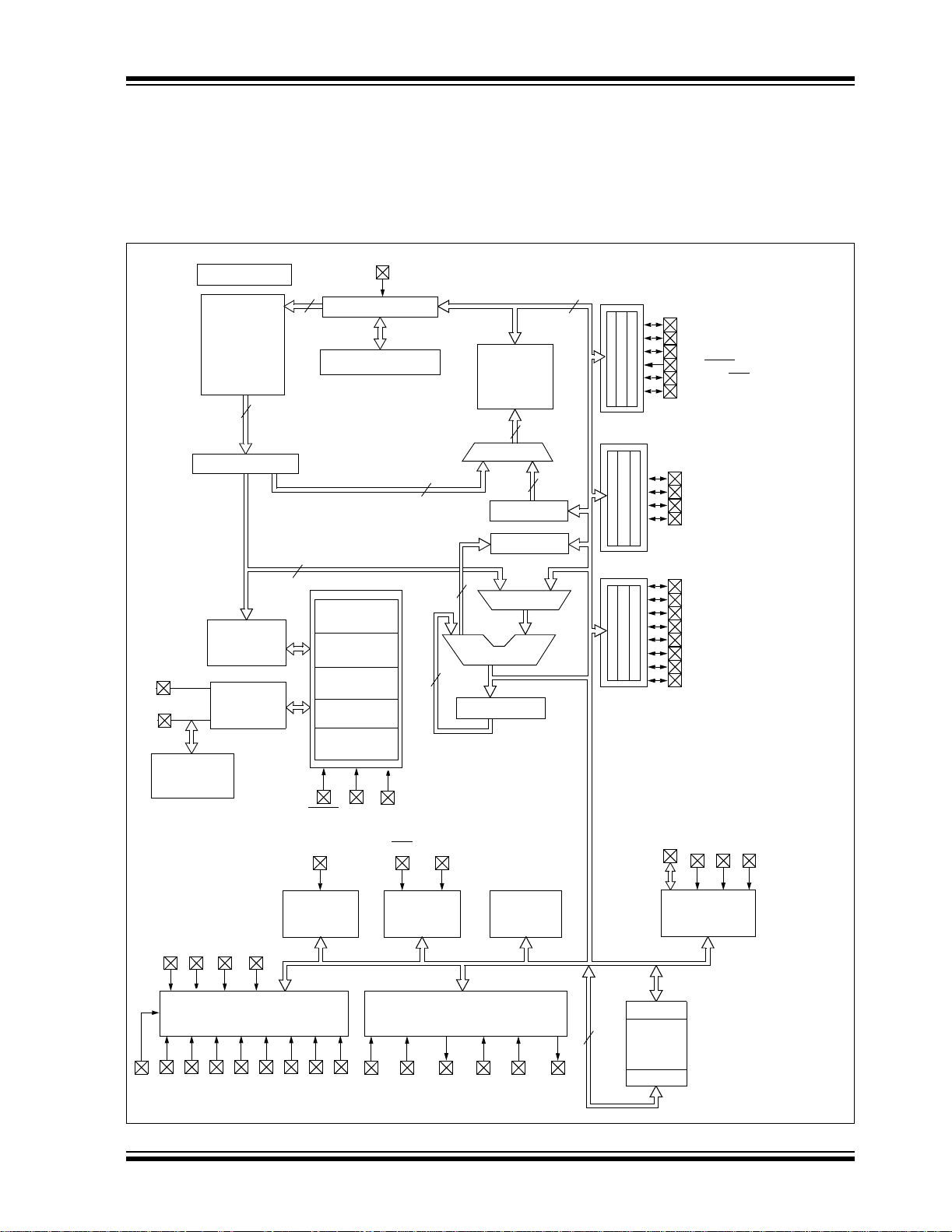

PIC16F685/687/689/690

1.0 DEVICE OVERVIEW

The PIC16F685/687/689/690 devices are covered by

this data sheet. They are available in 20-pin PDIP,

SOIC, TSSOP and QFN packages.

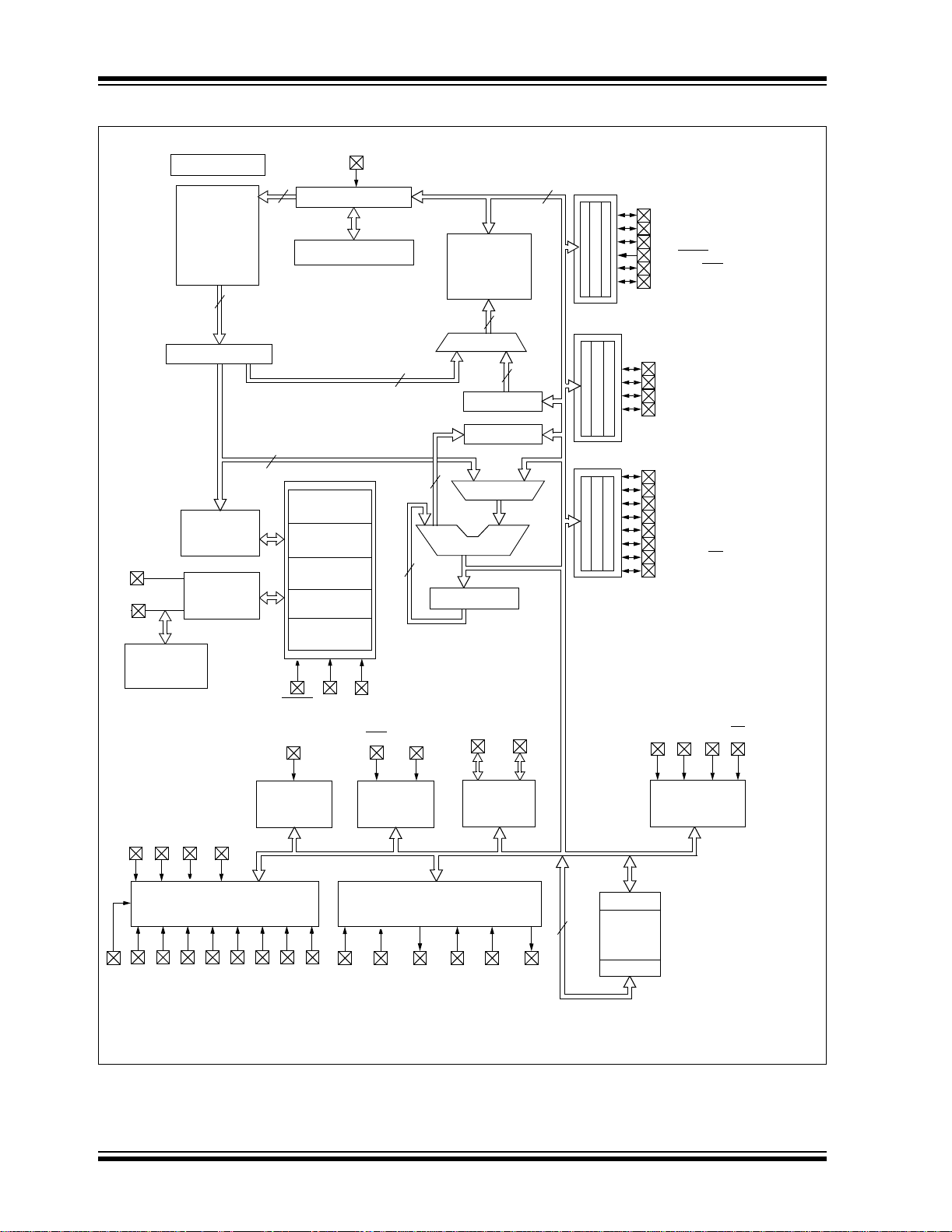

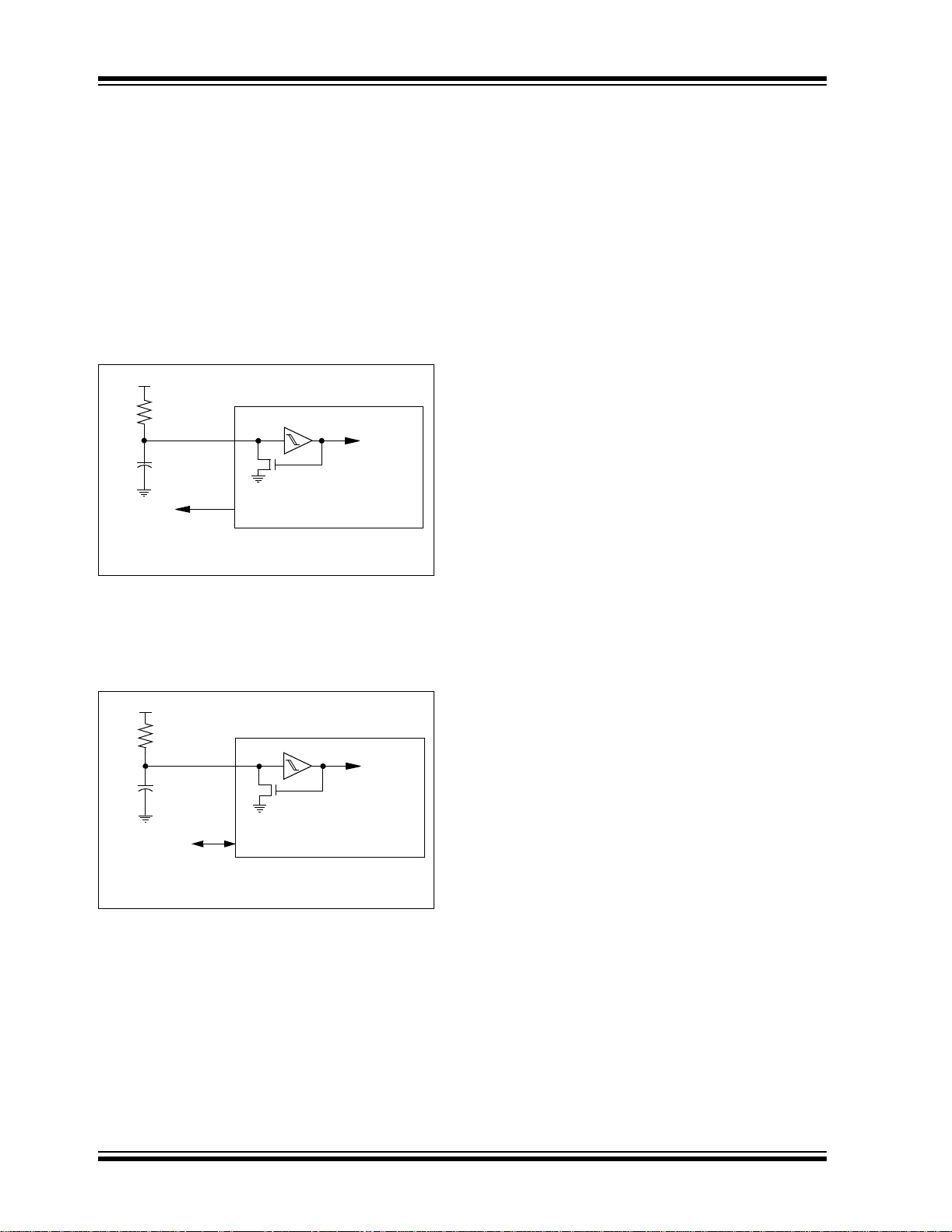

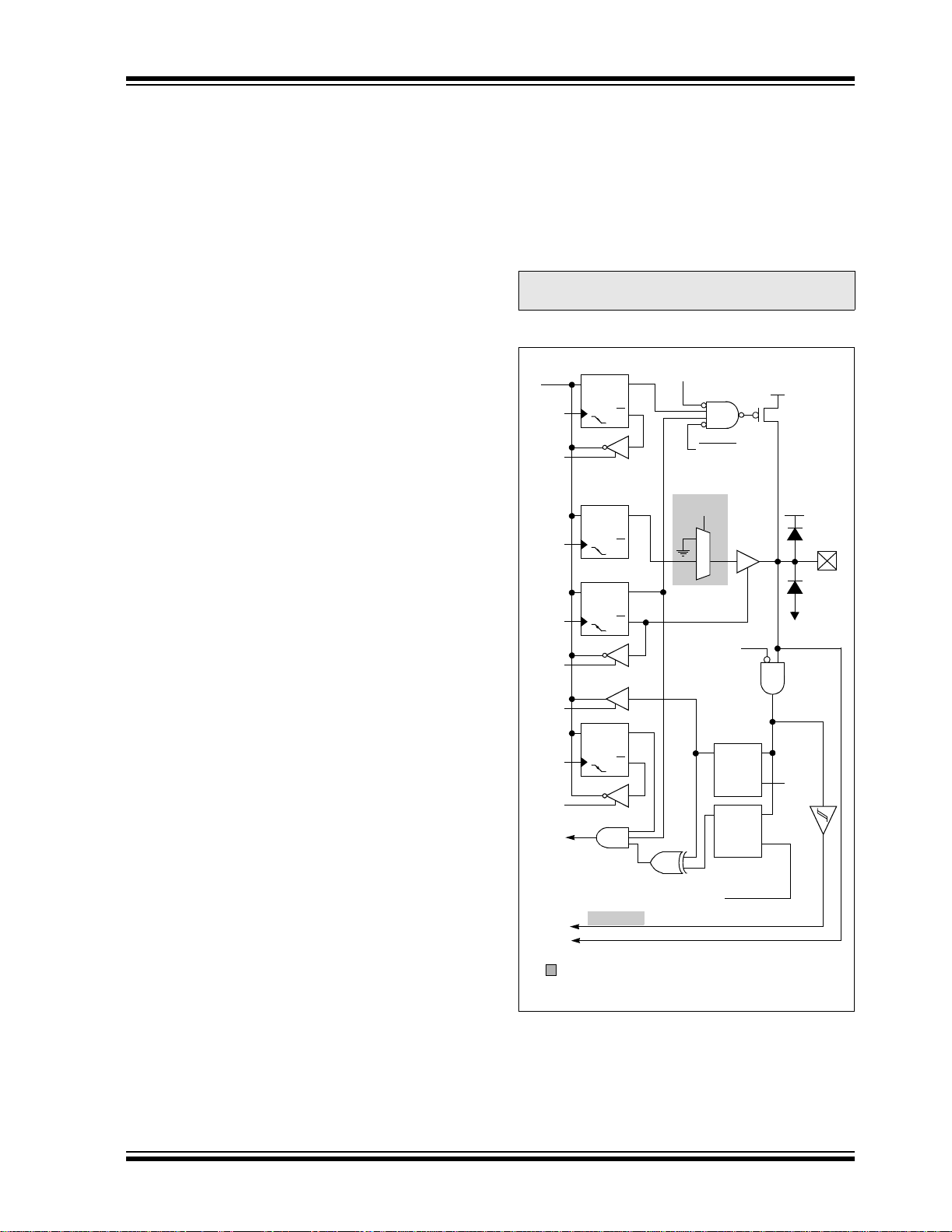

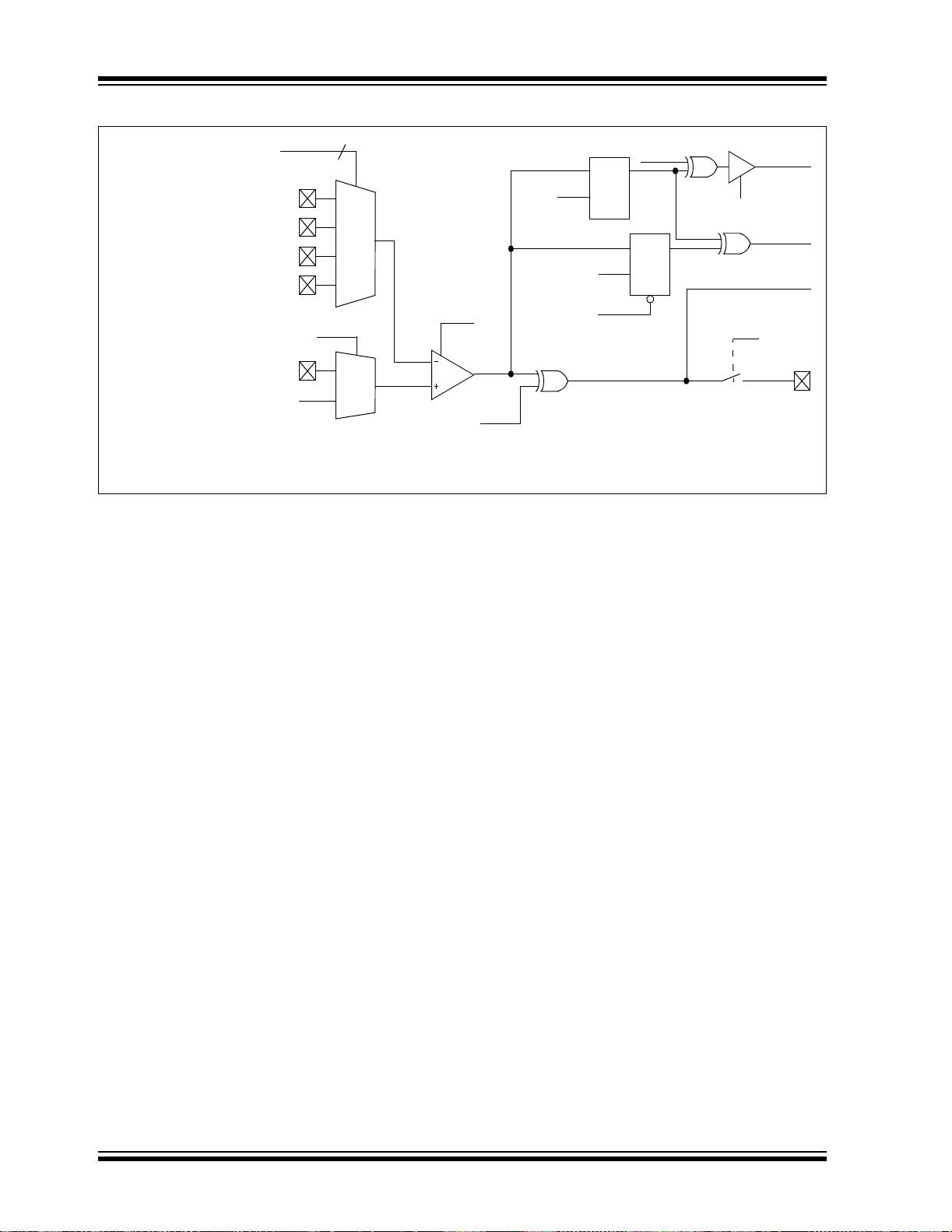

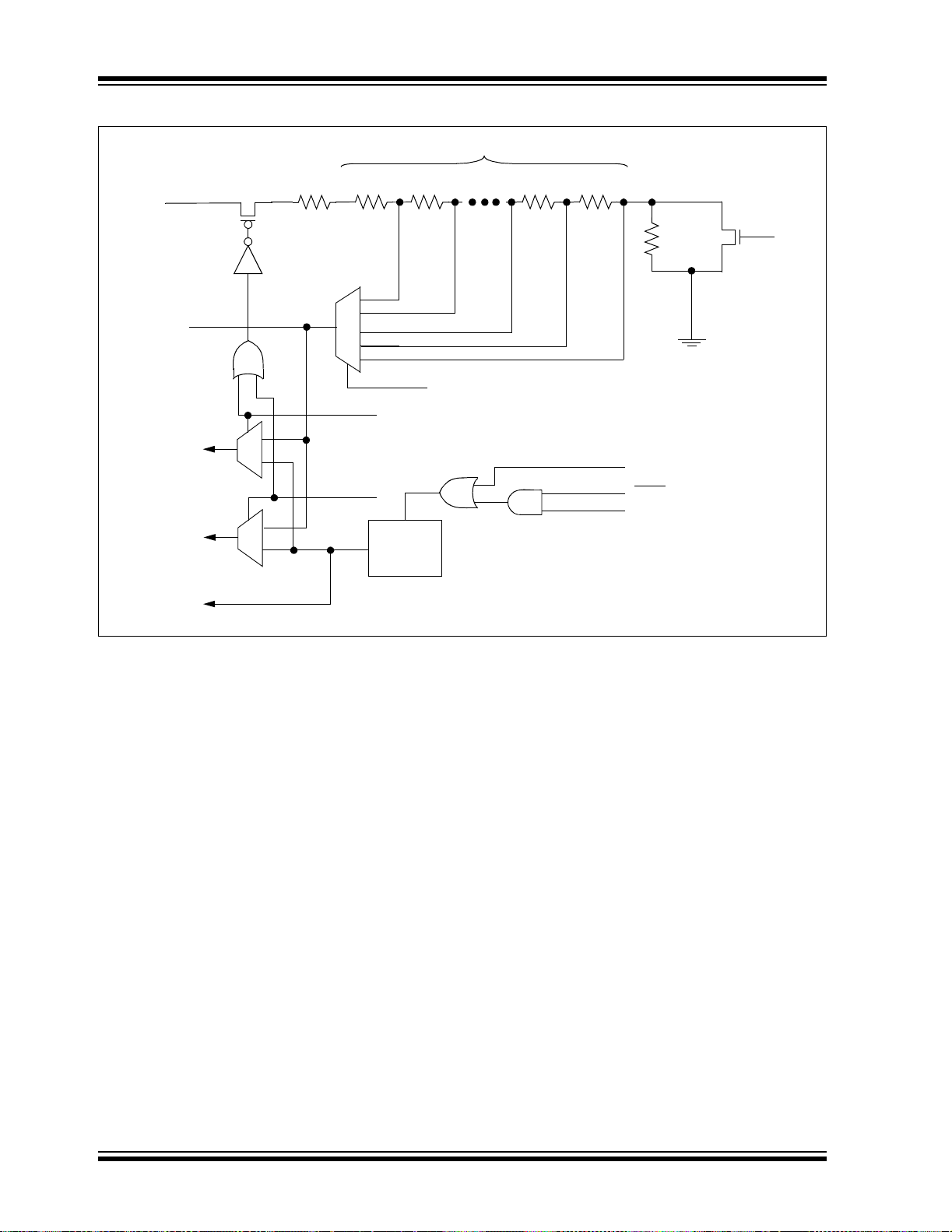

FIGURE 1-1: PIC16F685 BLOCK DIAGRAM

INT

Program

OSC1/CLKI

OSC2/CLKO

Internal

Oscillator

Block

Configuration

Bus

Instruction Reg

Decode and

Flash

4k x 14

Program

Memory

14

Instruction

Control

Timing

Generation

13

Program Counter

8-Level Stack (13-bit)

Direct Addr

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

VDD

MCLR

7

3

8

VSS

T1G T1CKIT0CKI

Block Diagrams and pinout descriptions of the devices

are as follows:

• PIC16F685 (Figure 1-1, Table 1-1)

• PIC16F687/PIC16F689 (Figure 1-2, Table 1-2)

• PIC16F690 (Figure 1-3, Table 1-3)

8

Data Bus

256 bytes

Registers

Addr MUX

ALU

W Reg

RAM

File

RAM Addr

9

8

FSR Reg

Status Reg

MUX

Indirect

Addr

PORTA

PORTB

PORTC

RA0/AN0/C1IN+/ICSPDAT/ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT

RA3/MCLR

RA4/AN3/T1G/OSC2/CLKOUT

RA5/T1CKI/OSC1/CLKIN

RB4/AN10

RB5/AN11

RB6

RB7

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6/P1D

RC3/AN7/P1C

RC4/C2OUT/P1B

RC5/CCP1/P1A

RC6/AN8

RC7/AN9

CCP1/

P1A

P1B P1C P1D

/VPP

REF/ICSPCLK

AN8 AN9 AN10 AN11

Analog-To-Digital Converter

VREF

AN0 AN1 AN2 AN3 AN4 AN5 AN6

Timer0 Timer1

Analog Comparators

AN7

C1IN- C1IN+ C1OUT

2

and Reference

Timer2

C2IN- C2IN+ C2OUT

8

ECCP+

EEDAT

256 Bytes

Data

EEPROM

EEADR

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 5

PIC16F685/687/689/690

U

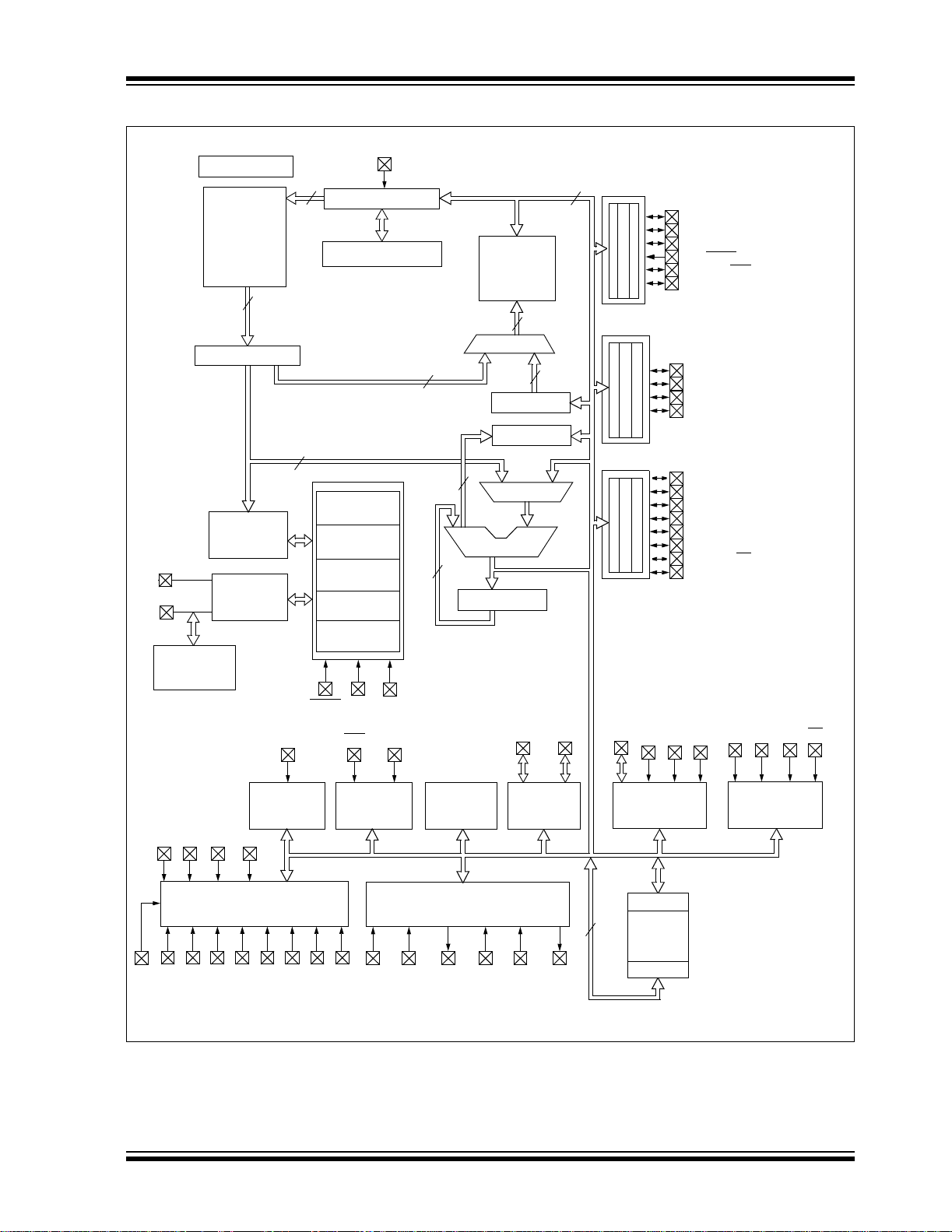

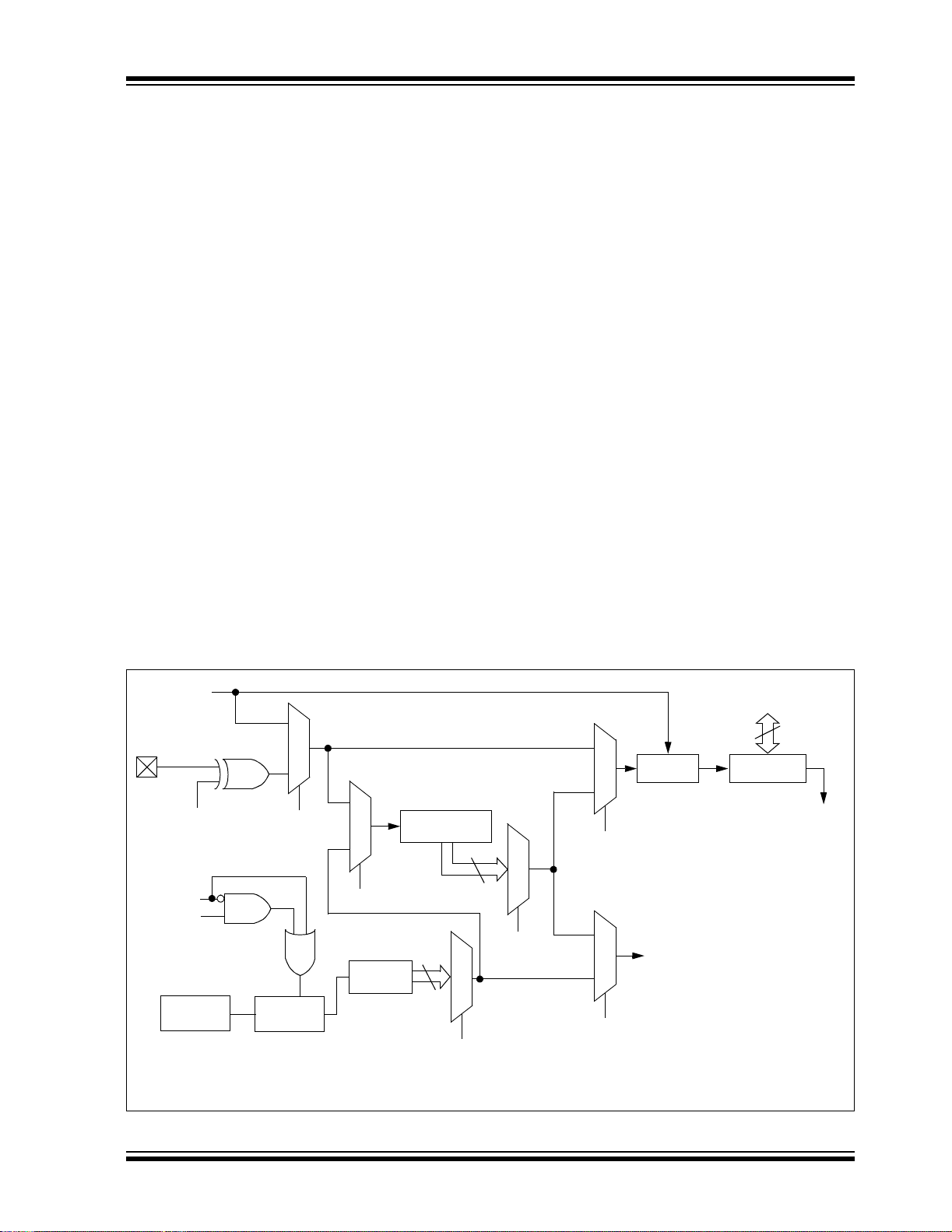

FIGURE 1-2: PIC16F687/PIC16F689 BLOCK DIAGRAM

INT

Program

Bus

OSC1/CLKI

OSC2/CLKO

Internal

Oscillator

Block

Configuration

Flash

(1)

2k

/4k x 14

Program

Memory

14

Instruction Reg

Instruction

Decode and

Control

Timing

Generation

13

Program Counter

8-Level Stack (13-bit)

Direct Addr

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

VDD

MCLR

VSS

T1G

Data Bus

RAM

(1)

/256 bytes

128

File

Registers

RAM Addr

9

Addr MUX

7

3

ALU

8

W Reg

T1CKIT0CKI

TX/CK RX/DT

8

FSR Reg

Status Reg

MUX

Indirect

Addr

8

PORTA

RA0/AN0/C1IN+/ICSPDAT/ULPW

RA1/AN1/C12IN-/VREF/ICSPCLK

RA2/AN2/T0CKI/INT/C1OUT

RA3/MCLR

RA4/AN3/T1G/OSC2/CLKOUT

RA5/T1CKI/OSC1/CLKIN

PORTB

RB4/AN10/SDI/SDA

RB5/AN11/RX/DT

RB6/SCK/SCL

RB7/TX/CK

PORTC

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6

RC3/AN7

RC4/C2OUT

RC5/CCP1

RC6/AN8/SS

RC7/AN9/SDO

SDO

/VPP

SDI/ SCK/

SDA SCL

SS

Timer0 Timer1

AN8 AN9 AN10 AN11

Analog-To-Digital Converter

AN0 AN1 AN2 AN3 AN4 AN5 AN6

AN7

EUSART

2

Analog Comparators

and Reference

C1IN- C1IN+ C1OUTVREF

C2IN- C2IN+ C2OUT

8

EEDAT

256 Bytes

Data

EEPROM

EEADR

Synchronous

Serial Por t

Note 1: PIC16F687 only.

DS41262A-page 6 Preliminary © 2005 Microchip Technology Inc.

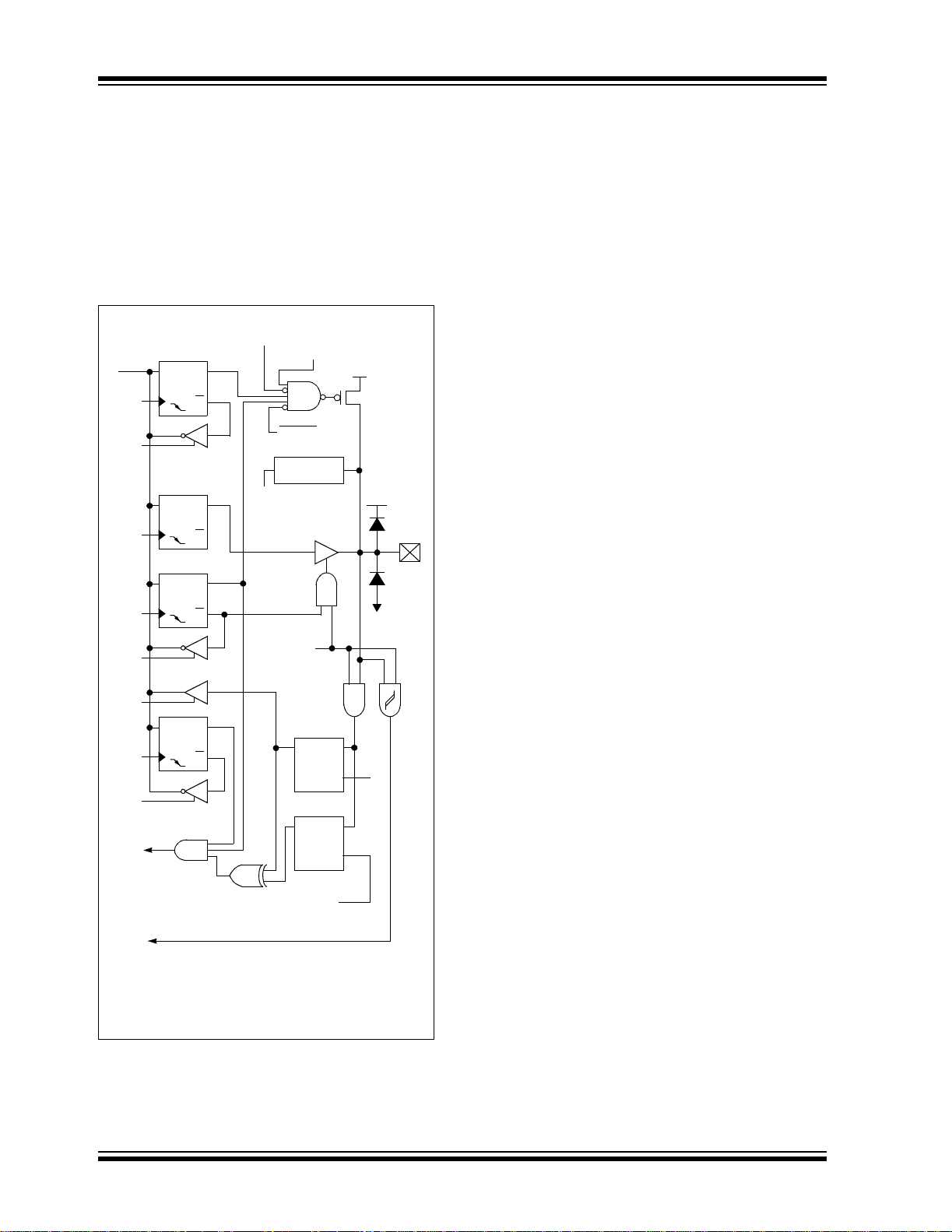

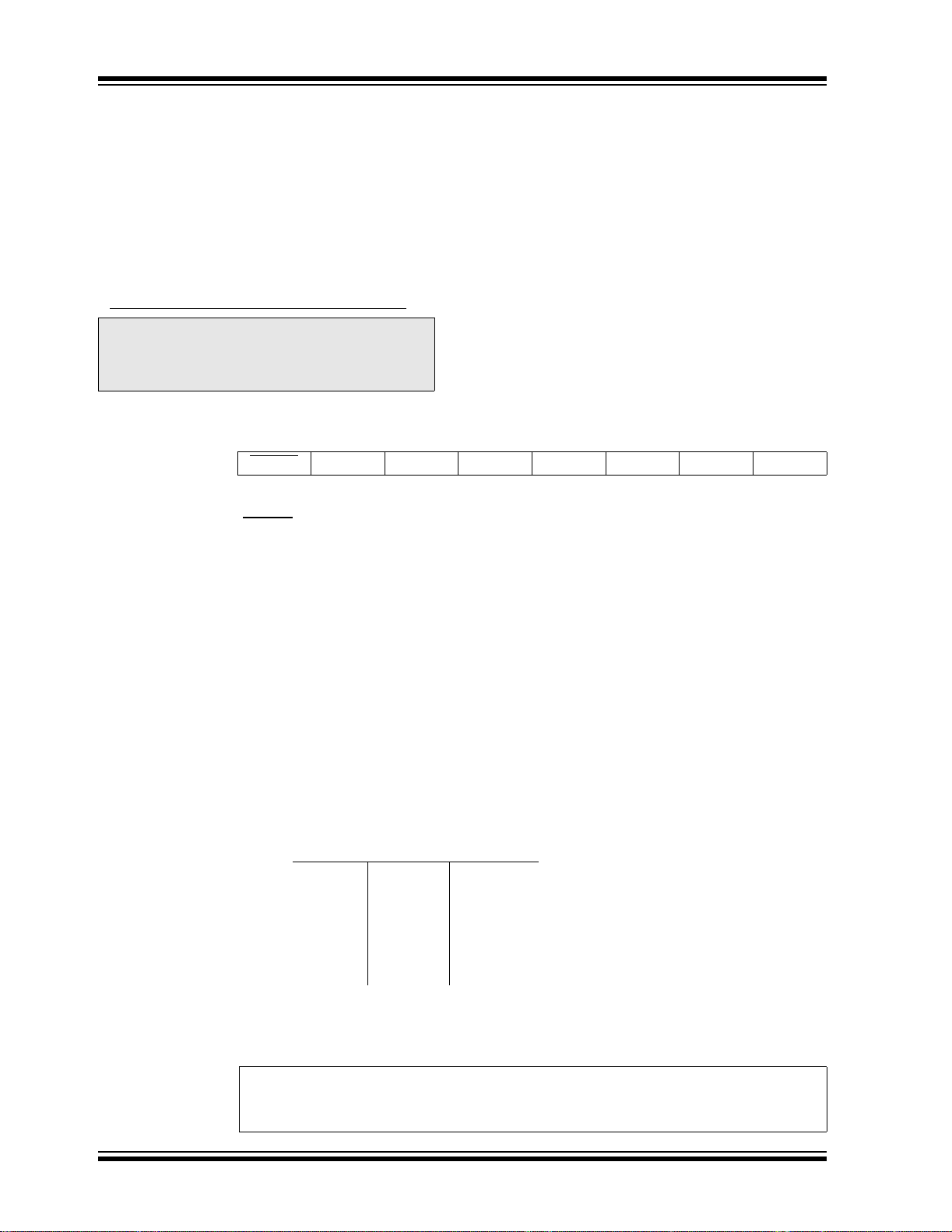

FIGURE 1-3: PIC16F690 BLOCK DIAGRAM

U

INT

Program

OSC1/CLKI

OSC2/CLKO

Internal

Oscillator

Block

Configuration

Bus

Instruction Reg

Decode and

Flash

4k x 14

Program

Memory

14

Instruction

Control

Timing

Generation

13

Program Counter

8-Level Stack (13-bit)

Direct Addr

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

VDD

MCLR

T1G

7

3

8

VSS

T1CKIT0CKI

PIC16F685/687/689/690

8

Data Bus

RAM

256 bytes

Registers

Addr MUX

Status Reg

ALU

W Reg

File

RAM Addr

9

Indirect

Addr

8

FSR Reg

MUX

TX/CK RX/DT

PORTA

PORTB

PORTC

CCP1/

P1A

RA0/AN0/C1IN+/ICSPDAT/ULPW

RA1/AN1/C12IN-/VREF/ICSPCLK

RA2/AN2/T0CKI/INT/C1OUT

RA3/MCLR

RA4/AN3/T1G/OSC2/CLKOUT

RA5/T1CKI/OSC1/CLKIN

RB4/AN10/SDI/SDA

RB5/AN11/RX/DT

RB6/SCK/SCL

RB7/TX/CK

RC0/AN4/C2IN+

RC1/AN5/C12INRC2/AN6/P1D

RC3/AN7/P1C

RC4/C2OUT/P1B

RC5/CCP1/P1A

RC6/AN8/SS

RC7/AN9/SDO

P1B P1C P1D

/VPP

SDO

SDI/ SCK/

SDA SCL

SS

Synchronous

Serial Port

AN8 AN9 AN10 AN11

Analog-To-Digital Converter

VREF

AN0 AN1 AN2 AN3 AN4 AN5 AN6

Timer0 Timer1

AN7

C1IN- C1IN+ C1OUT

Timer2

2

Analog Comparators

and Reference

C2IN- C2IN+ C2OUT

EUSART

8

ECCP+

EEDAT

256 Bytes

Data

EEPROM

EEADR

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 7

PIC16F685/687/689/690

TABLE 1-1: PINOUT DESCRIPTION – PIC16F685

Name Function

RA0/AN0/C1IN+/ICSPDAT/

ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT RA2 ST CMOS General purpose I/O. Individually controlled interrupt-on-

RA3/MCLR

RA4/AN3/T1G

RA5/T1CKI/OSC1/CLKIN RA5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB4/AN10 RB4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB5/AN11 RB5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB6 RB6 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB7 RB7 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RC0/AN4/C2IN+ RC0 ST CMOS General purpose I/O.

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

REF/ICSPCLK RA1 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

/VPP RA3 TTL — General purpose input. Individually controlled interrupt-on-

/OSC2/CLKOUT RA4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

RA0 TTL — General purpose I/O. Individually controlled interrupt-on-

AN0 AN — A/D Channel 0 input.

C1IN+ AN — Comparator 1 positive input.

ICSPDAT TTL CMOS ICSP™ Data I/O.

ULPWU AN — Ultra Low-Power Wake-up input.

AN1 AN — A/D Channel 1 input.

C12IN- AN — Comparator 1 or 2 negative input.

REF AN — External Voltage Reference for A/D.

V

ICSPCLK ST — ICSP™ clock.

AN2 AN — A/D Channel 2 input.

T0CKI ST — Timer0 clock input.

INT ST —

C1OUT — CMOS Comparator 1 output.

MCLR

PP HV — Programming voltage.

V

AN3 AN — A/D Channel 3 input.

T1G

OSC2 — XTAL Crystal/Resonator.

CLKOUT — CMOS F

T1CKI ST — Timer1 clock input.

OSC1 XTAL — Crystal/Resonator.

CLKIN ST — External clock input/RC oscillator connection.

AN10 AN — A/D Channel 10 input.

AN11 AN — A/D Channel 11 input.

AN4 AN — A/D Channel 4 input.

C2IN+ AN — Comparator 2 positive input.

Input

Type

Output

Type

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

Description

External interrupt pin.

change.

ST — Master Clear with internal pull-up.

change. Individually enabled pull-up.

ST — Timer1 gate input.

OSC/4 output.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

DS41262A-page 8 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

TABLE 1-1: PINOUT DESCRIPTION – PIC16F685 (CONTINUED)

Name Function

RC1/AN5/C12IN- RC1 ST CMOS General purpose I/O.

AN5 AN — A/D Channel 5 input.

C12IN- AN — Comparator 1 or 2 negative input.

RC2/AN6/P1D RC2 ST CMOS General purpose I/O.

AN6 AN — A/D Channel 6 input.

P1D — CMOS PWM output.

RC3/AN7/P1C RC3 ST CMOS General purpose I/O.

AN7 AN — A/D Channel 7 input.

P1C — CMOS PWM output.

RC4/C2OUT/P1B RC4 ST CMOS General purpose I/O.

C2OUT — CMOS Comparator 2 output.

P1B — CMOS PWM output.

RC5/CCP1/P1A RC5 ST CMOS General purpose I/O.

CCP1 ST CMOS Capture/Compare input.

P1A ST CMOS PWM output.

RC6/AN8 RC6 ST CMOS General purpose I/O.

AN8 AN — A/D Channel 8 input.

RC7/AN9 RC7 ST CMOS General purpose I/O.

AN9 AN — A/D Channel 9 input.

SS VSS Power — Ground reference.

V

DD VDD Power — Positive supply.

V

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

Input

Type

Output

Type

Description

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 9

PIC16F685/687/689/690

TABLE 1-2: PINOUT DESCRIPTION – PIC16F687/PIC16F689

Name Function

RA0/AN0/C1IN+/ICSPDAT/

ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT RA2 ST CMOS General purpose I/O. Individually controlled interrupt-on-

RA3/MCLR

RA4/AN3/T1G

RA5/T1CKI/OSC1/CLKIN RA5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB4/AN10/SDI/SDA RB4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB5/AN11/RX/DT RB5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

REF/ICSPCLK RA1 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

/VPP RA3 TTL — General purpose input. Individually controlled interrupt-on-

/OSC2/CLKOUT RA4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

RA0 TTL — General purpose I/O. Individually controlled interrupt-on-

AN0 AN — A/D Channel 0 input.

C1IN+ AN — Comparator 1 positive input.

ICSPDAT TTL C MOS ICSP Data I/O.

ULPWU AN — Ultra Low-Power Wake-up input.

AN1 AN — A/D Channel 1 input.

C12IN- AN — Comparator 1 or 2 negative input.

REF AN — External Voltage Reference for A/D.

V

ICSPCLK ST — ICSP™ clock.

AN2 AN — A/D Channel 2 input.

T0CKI ST — Timer0 clock input.

INT ST — External Interrupt.

C1OUT — CMOS Comparator 1 output.

MCLR

PP HV — Programming voltage.

V

AN3 AN — A/D Channel 3 input.

T1G

OSC2 — XTAL Crystal/Resonator.

CLKOUT — CMOS F

T1CKI ST — Timer1 clock input.

OSC1 XTAL — Crystal/Resonator.

CLKIN ST — External clock input/RC oscillator connection.

AN10 AN — A/D Channel 10 input.

SDI ST — SPI™ data input.

SDA ST OD I

AN11 AN — A/D Channel 11 input.

RX ST — EUSART asynchronous input.

DT ST CMOS EUSART synchronous data.

Input

Type

Output

Type

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change.

ST — Master Clear with internal pull-up.

change. Individually enabled pull-up.

ST — Timer1 gate input.

OSC/4 output.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

2

C data input/output.

change. Individually enabled pull-up.

Description

DS41262A-page 10 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

TABLE 1-2: PINOUT DESCRIPTION – PIC16F687/PIC16F689 (CONTINUED)

Name Function

RB6/SCK/SCL RB6 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

SCK ST CMOS SPI™ clock.

SCL ST OD I

RB7/TX/CK RB7 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

TX — CMOS EUSART asynchronous output.

CK ST CMOS EUSART synchronous clock.

RC0/AN4/C2IN+ RC0 ST CMOS General purpose I/O.

AN4 AN — A/D Channel 4 input.

C2IN+ AN — Comparator 2 positive input.

RC1/AN5/C12IN- RC1 ST CMOS General purpose I/O.

AN5 AN — A/D Channel 5 input.

C12IN- AN — Comparator 1 or 2 negative input.

RC2/AN6 RC2 ST CMOS General purpose I/O.

AN6 AN — A/D Channel 6 input.

RC3/AN7 RC3 ST CMOS General purpose I/O.

AN7 AN — A/D Channel 7 input.

RC4/C2OUT RC4 ST CMOS General purpose I/O.

C2OUT — CMOS Comparator 2 output.

RC5/CCP1 RC5 ST CMOS General purpose I/O.

CCP1 ST CMOS Capture/Compare input.

RC6/AN8/SS

RC7/AN9/SDO RC7 ST CMOS General purpose I/O.

SS VSS Power — Ground reference.

V

DD VDD Power — Positive supply.

V

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

RC6 ST CMOS General purpose I/O.

AN8 AN — A/D Channel 8 input.

SS

AN9 AN — A/D Channel 9 input.

SDO — CMOS SPI data output.

Input

Type

Output

Type

change. Individually enabled pull-up.

2

C™ clock.

change. Individually enabled pull-up.

ST — Slave Select input.

Description

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 11

PIC16F685/687/689/690

TABLE 1-3: PINOUT DESCRIPTION – PIC16F690

Name Function

RA0/AN0/C1IN+/ICSPDAT/

ULPWU

RA1/AN1/C12IN-/V

RA2/AN2/T0CKI/INT/C1OUT RA2 ST CMOS General purpose I/O. Individually controlled interrupt-on-

RA3/MCLR

RA4/AN3/T1G

RA5/T1CKI/OSC1/CLKIN RA5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB4/AN10/SDI/SDA RB4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

RB5/AN11/RX/DT RB5 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

REF/ICSPCLK RA1 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

/VPP RA3 TTL — General purpose input. Individually controlled interrupt-on-

/OSC2/CLKOUT RA4 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

RA0 TTL — General purpose I/O. Individually controlled interrupt-on-

AN0 AN — A/D Channel 0 input.

C1IN+ AN — Comparator 1 positive input.

ICSPDAT TTL C MOS ICSP Data I/O.

ULPWU AN — Ultra Low-Power Wake-up input.

AN1 AN — A/D Channel 1 input.

C12IN- AN — Comparator 1 or 2 negative input.

REF AN — External Voltage Reference for A/D.

V

ICSPCLK ST — ICSP™ clock.

AN2 AN — A/D Channel 2 input.

T0CKI ST — Timer0 clock input.

INT ST — External Interrupt.

C1OUT — CMOS Comparator 1 output.

MCLR

PP HV — Programming voltage.

V

AN3 AN — A/D Channel 3 input.

T1G

OSC2 — XTAL Crystal/Resonator.

CLKOUT — CMOS F

T1CKI ST — Timer1 clock input.

OSC1 XTAL — Crystal/Resonator.

CLKIN ST — External clock input/RC oscillator connection.

AN10 AN — A/D Channel 10 input.

SDI ST — SPI data input.

SDA ST OD I

AN11 AN — A/D Channel 11 input.

RX ST — EUSART asynchronous input.

DT ST CMOS EUSART synchronous data.

Input

Type

Output

Type

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

change.

ST — Master Clear with internal pull-up.

change. Individually enabled pull-up.

ST — Timer1 gate input.

OSC/4 output.

change. Individually enabled pull-up.

change. Individually enabled pull-up.

2

C data input/output.

change. Individually enabled pull-up.

Description

DS41262A-page 12 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

TABLE 1-3: PINOUT DESCRIPTION – PIC16F690 (CONTINUED)

Name Function

RB6/SCK/SCL RB6 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

SCK ST CMOS SPI™ clock.

SCL ST OD I

RB7/TX/CK RB7 TTL CMOS General purpose I/O. Individually controlled interrupt-on-

TX — CMOS EUSART asynchronous output.

CK ST CMOS EUSART synchronous clock.

RC0/AN4/C2IN+ RC0 ST CMOS General purpose I/O.

AN4 AN — A/D Channel 4 input.

C2IN+ AN — Comparator 2 positive input.

RC1/AN5/C12IN- RC1 ST CMOS General purpose I/O.

AN5 AN — A/D Channel 5 input.

C12IN- AN — Comparator 1 or 2 negative input.

RC2/AN6/P1D RC2 ST CMOS General purpose I/O.

AN6 AN — A/D Channel 6 input.

P1D — CMOS PWM output.

RC3/AN7/P1C RC3 ST CMOS General purpose I/O.

AN7 AN — A/D Channel 7 input.

P1C — CMOS PWM output.

RC4/C2OUT/P1B RC4 ST CMOS General purpose I/O.

C2OUT — CMOS Comparator 2 output.

P1B — CMOS PWM output.

RC5/CCP1/P1A RC5 ST CMOS General purpose I/O.

CCP1 ST CMOS Capture/Compare input.

P1A ST CMOS PWM output.

RC6/AN8/SS

RC7/AN9/SDO RC7 ST CMOS General purpose I/O.

SS VSS Power — Ground reference.

V

DD VDD Power — Positive supply.

V

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage XTAL = Crystal

RC6 ST CMOS General purpose I/O.

AN8 AN — A/D Channel 8 input.

SS

AN9 AN — A/D Channel 9 input.

SDO — CMOS SPI data output.

Input

Type

Output

Type

change. Individually enabled pull-up.

2

C™ clock.

change. Individually enabled pull-up.

ST — Slave Select input.

Description

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 13

PIC16F685/687/689/690

NOTES:

DS41262A-page 14 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

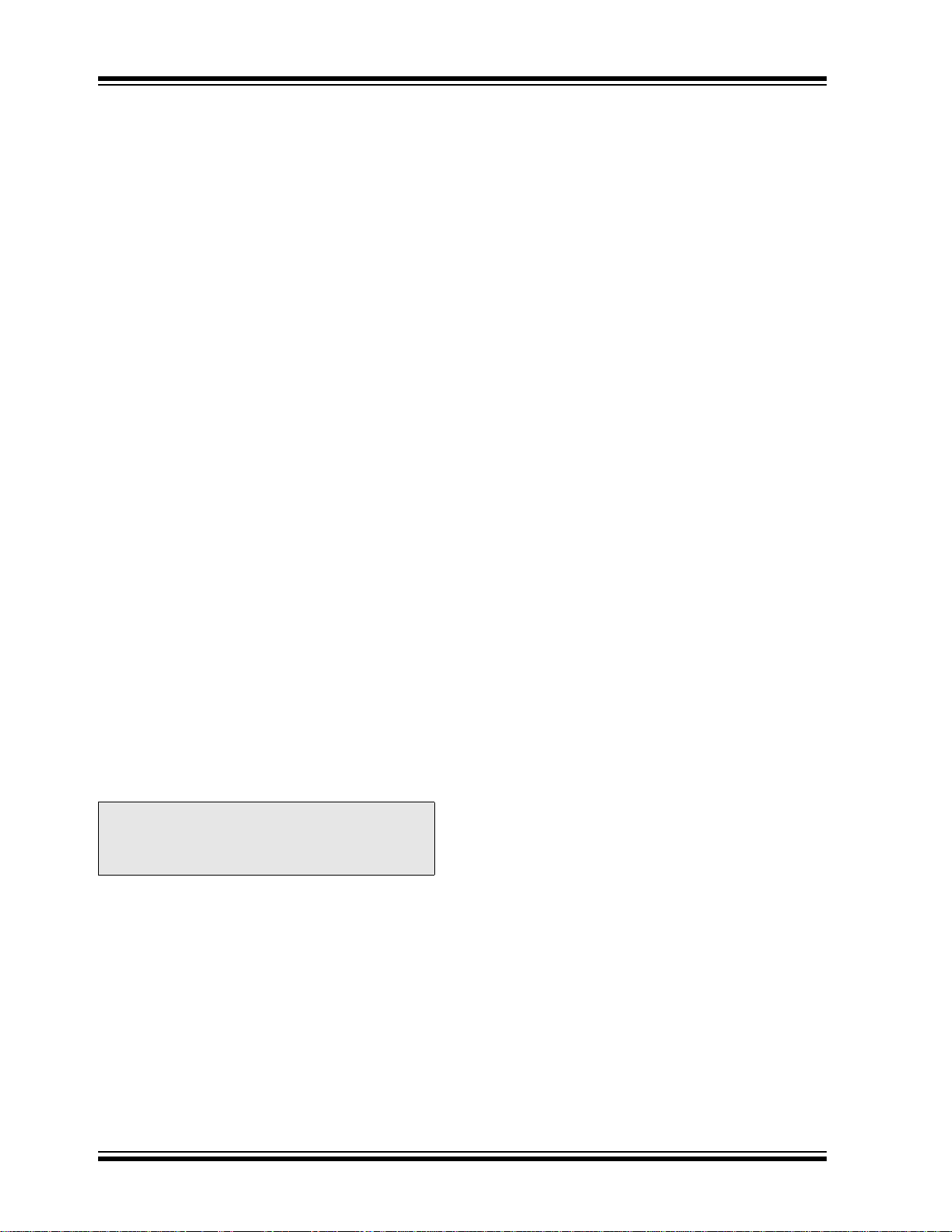

2.0 MEMORY ORGANIZATION

2.1 Program Memory Organization

The PIC16F685/687/689/690 has a 13-bit program

counter capable of addressing an 8k x 14 program

memory space. Onl y the first 2k x 14 (0000h-07 FFh) for

the PIC16F687 is physic ally impleme nted and first 4k x

14 (0000h-0FFFh) for the PIC16F685/PIC16F689/

PIC16F690. Accessing a location above these

boundaries will caus e a wrap around. The Reset vector

is at 0000h and the interrupt vector is at 0004h (see

Figures 2-1 and 2-2).

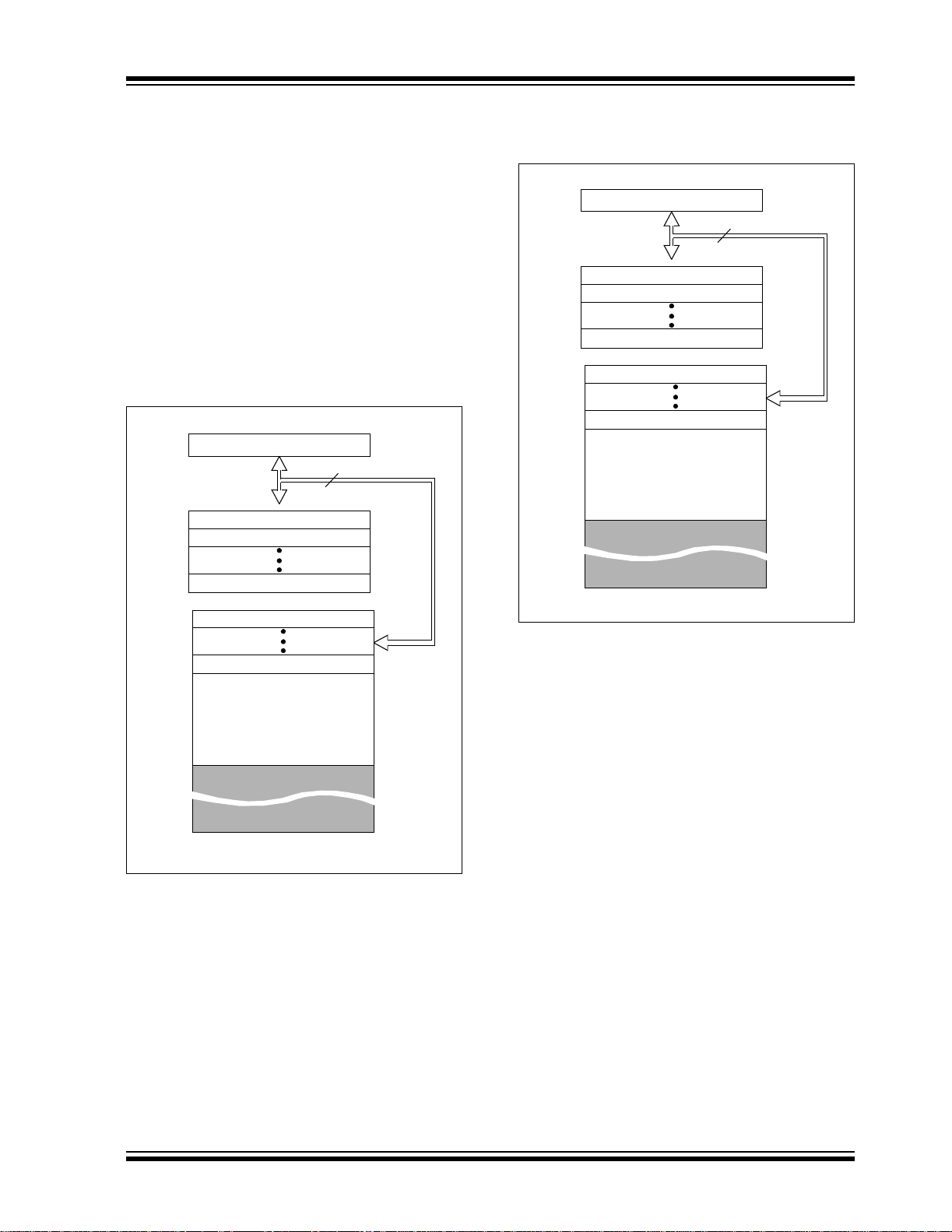

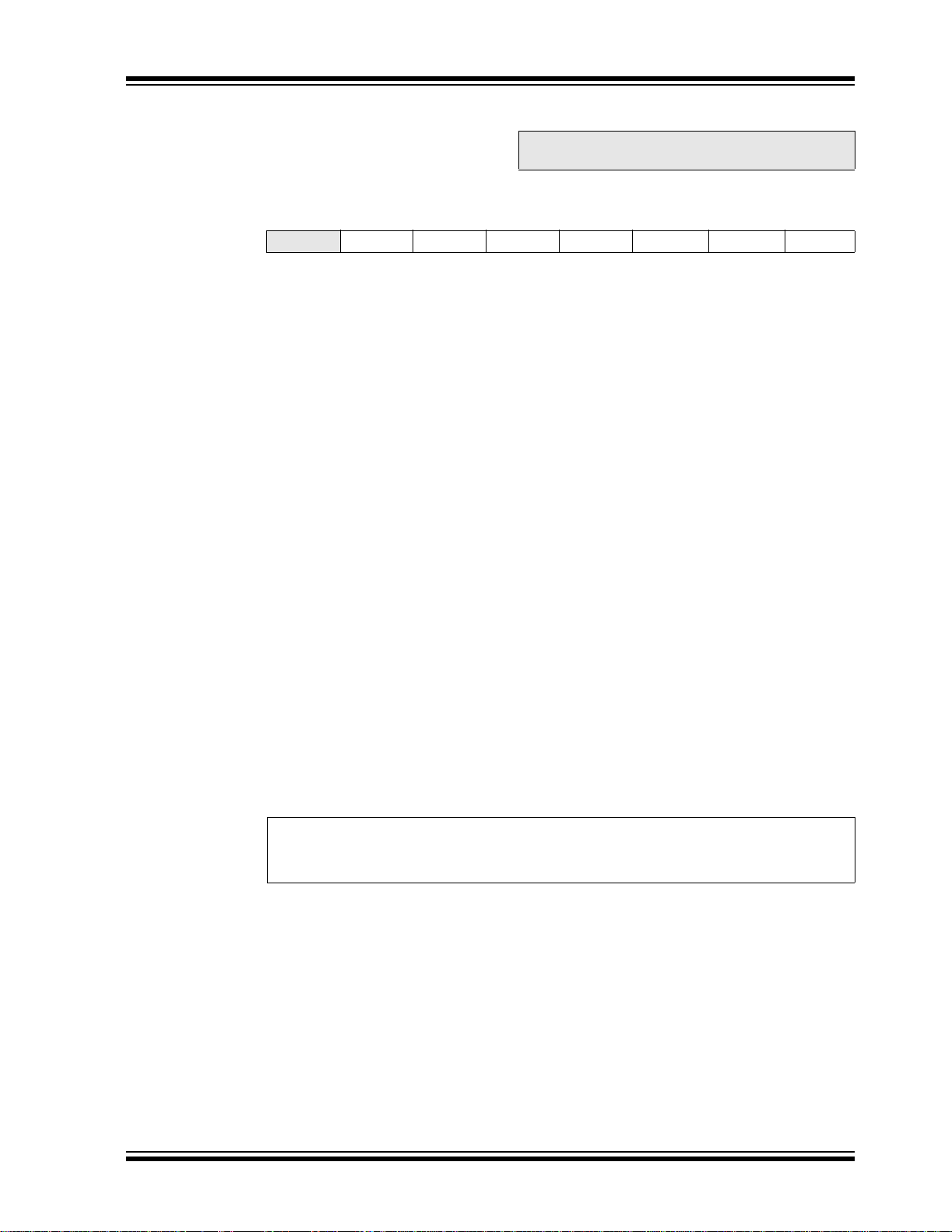

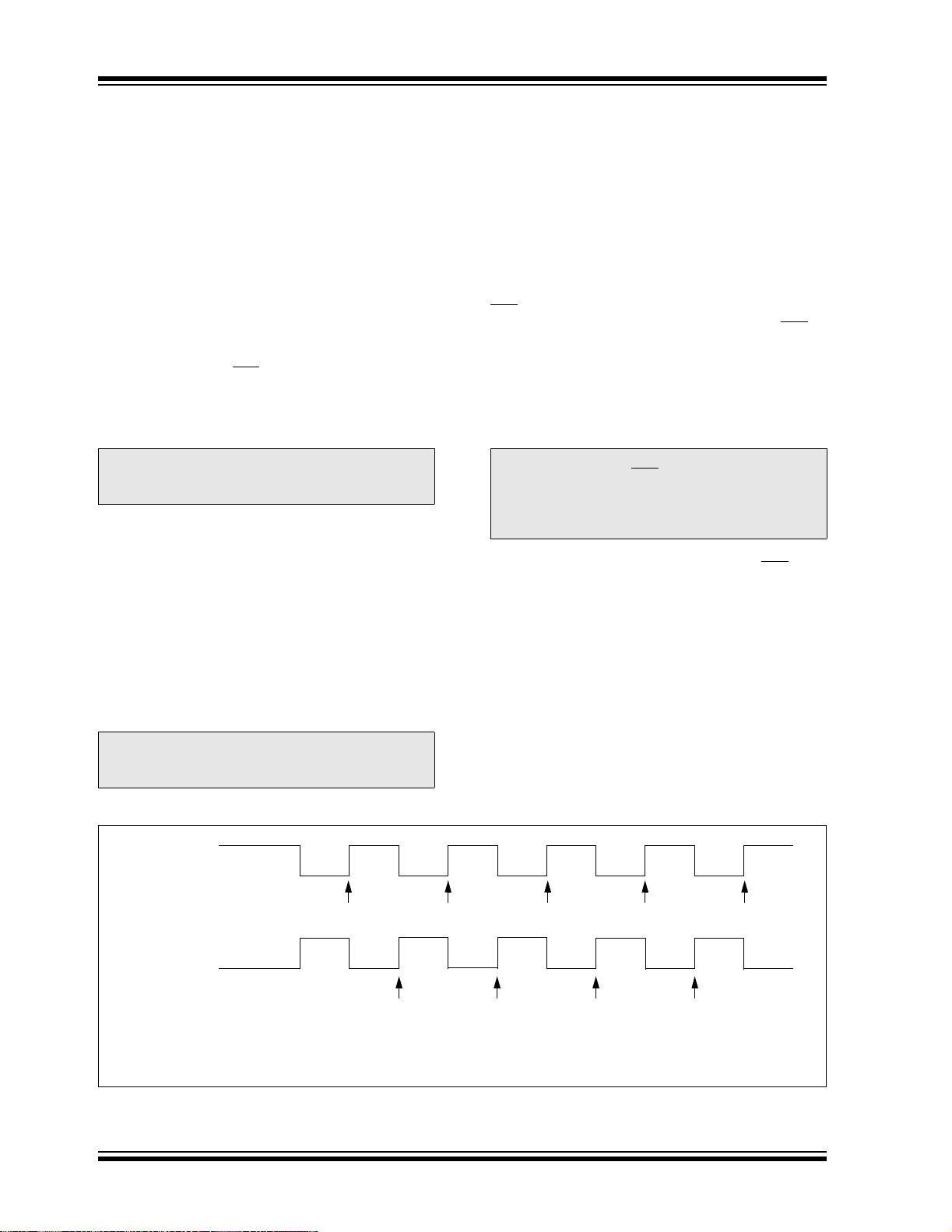

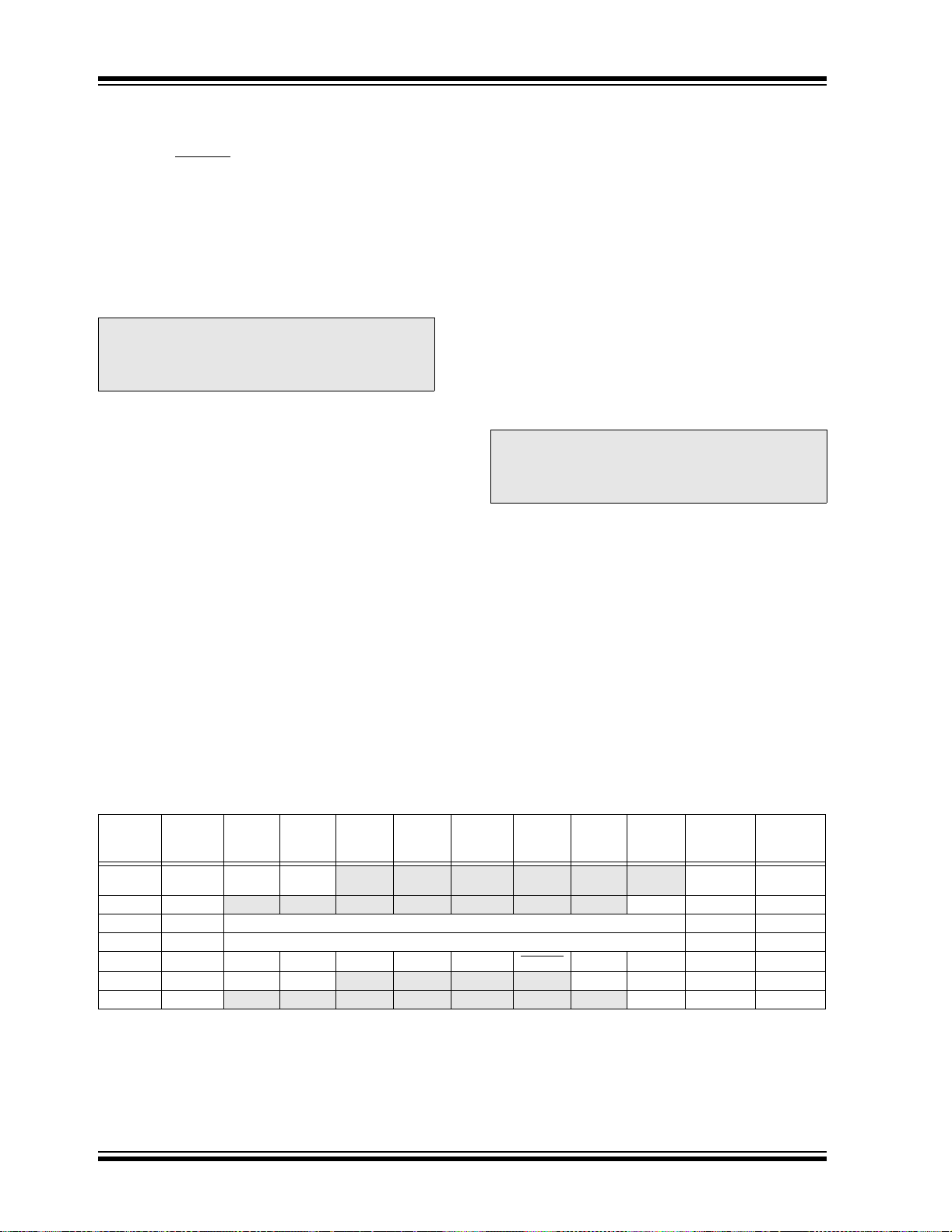

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC16F685/689/690

PC<12:0>

CALL, RETURN

RETFIE, RETLW

Stack Level 1

Stack Level 2

13

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC16F687

PC<12:0>

CALL, RETURN

RETFIE, RETLW

Stack Level 1

Stack Level 2

Stack Level 8

Reset Vector

Interrupt Vector

On-chip Program

Memory

Access 0-7FFh

13

0000h

0004h

0005h

07FFh

0800h

Stack Level 8

Reset Vector

Interrupt Vector

On-chip Program

Memory

Access 0-FFFh

1FFFh

0000h

0004h

0005h

0FFFh

1000h

1FFFh

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 15

PIC16F685/687/689/690

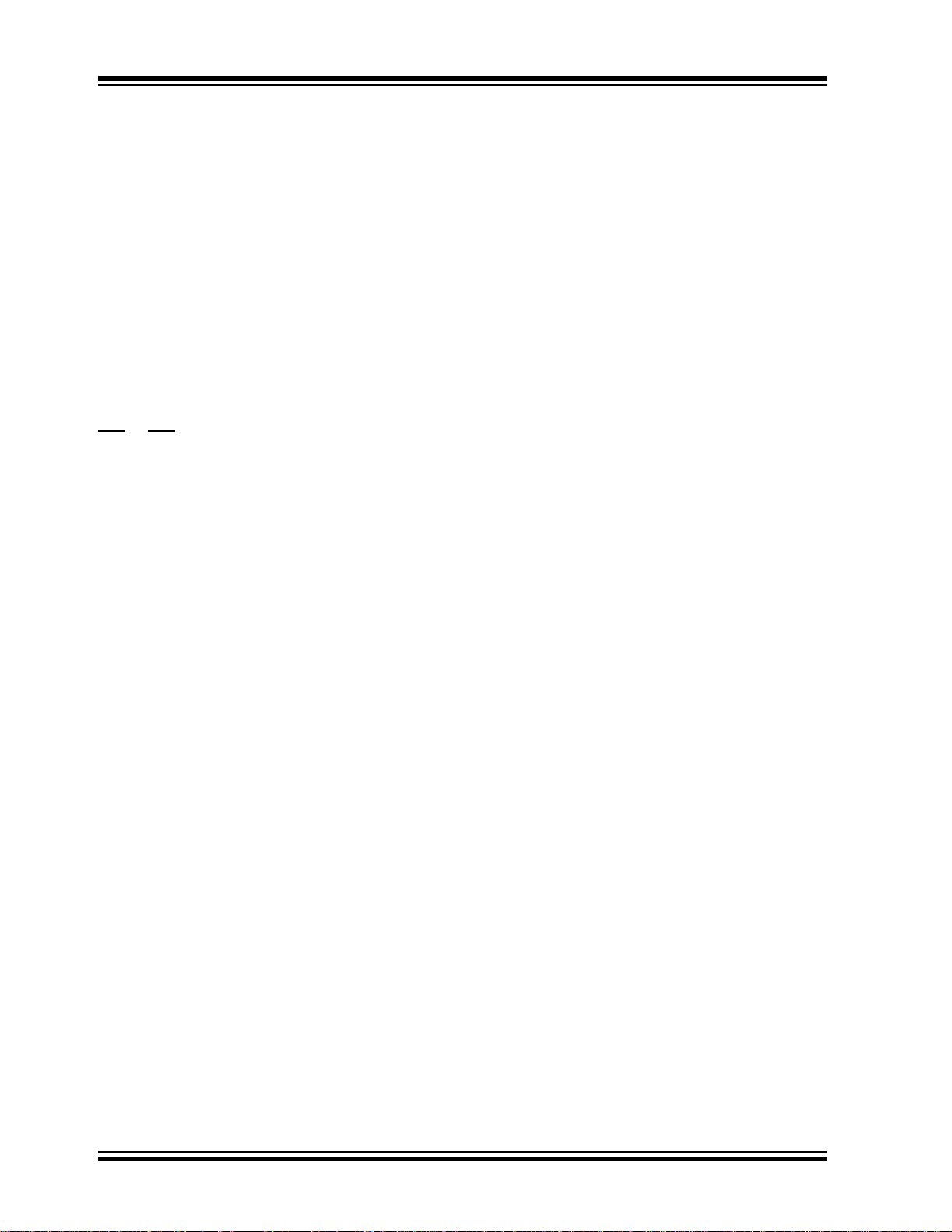

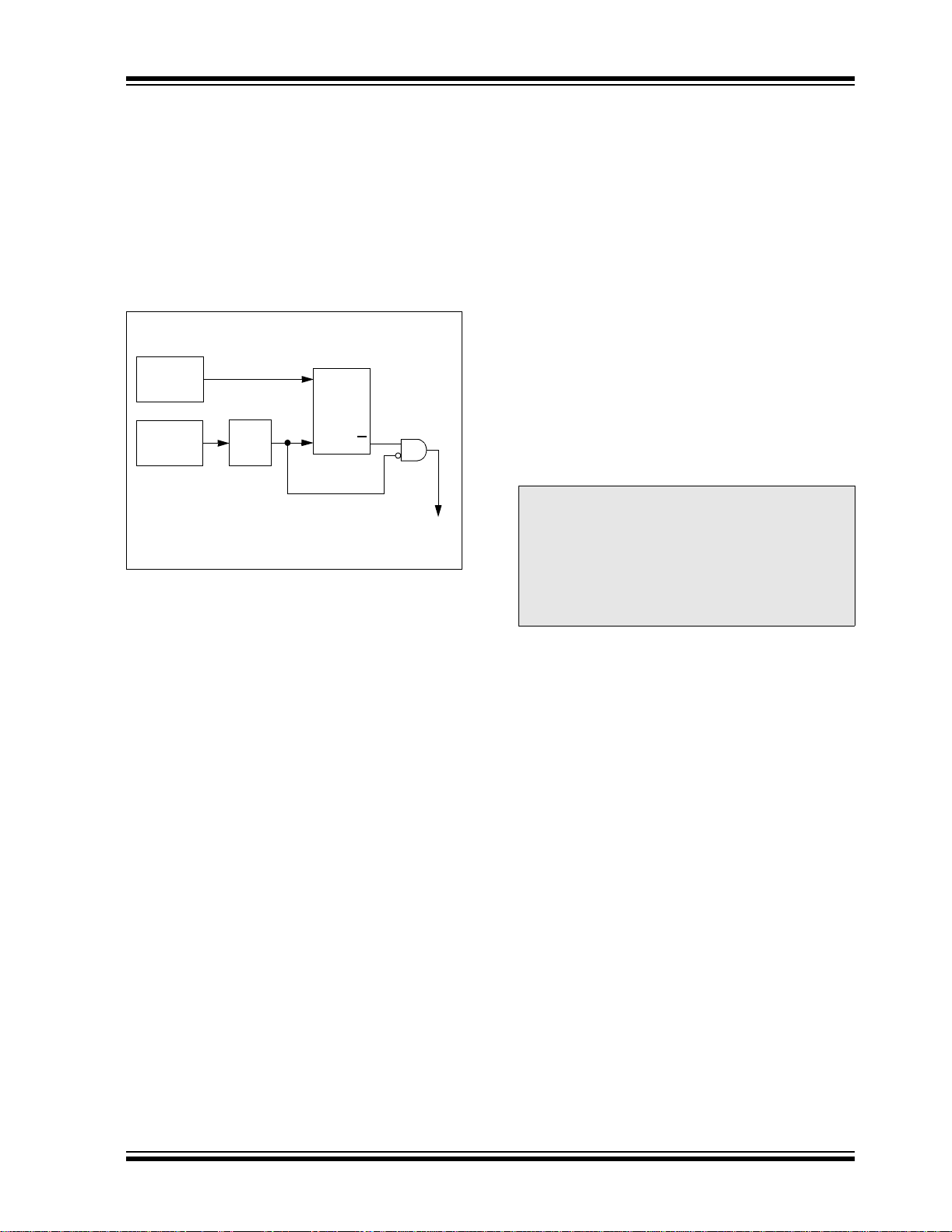

2.2 Data Memory Organization

The data memory (see Figures 2-3, 2-4 and 2-5) is

partitioned into four banks which contain the General

Purpose Registers (GPR) and the Special Function

Registers (SFR). The Special Function Registers are

located in the fir st 32 l oca tio ns o f eac h ba nk. Regi ste r

locations 20h-7Fh in Bank 0 and A0h-EFh (A0-BF,

PIC16F687 only) in Bank 1 are General Purpose

Registers, implemented as static RAM. Register

locations F0h-FFh i n Bank 1, 170 h-17Fh in Ban k 2 an d

1F0h-1FFh in Bank 3 point to addresses 70h-7Fh in

Bank 0. Other General Purpose Resisters (GPR) are

also available in Bank 1 an d Ban k 2 , depending on the

device. Details are shown in Figures 2-3, 2-4 and 2-5.

All other RAM is unimplemented and returns ‘0’ when

read. RP<1:0> (STATUS<6:5>) are the bank select

bits:

RP1

RP0

00→ Bank 0 is selected

01→ Bank 1 is selected

10→ Bank 2 is selected

11→ Bank 3 is selected

2.2.1 GENERAL PURPOSE REGISTER

FILE

The register file is organized as 128 x 8 in the

PIC16F687 and 256 x 8 in the PIC16F685/PIC16F689/

PIC16F690. Each register is accessed, either directly or

indirectly, through the File Select Register (FSR) (see

Section 2.4 “Indirect Addressing, INDF and FSR

Registers”).

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registe rs are registers used by

the CPU and peripheral functions for controlling the

desired operation of the device (see Tables 2-1, 2-2, 2-3

and 2-4). These registers are static RAM.

The special re gisters can be classifi ed into two sets:

core and peripheral. The Special Function Registers

associated with the “c ore” are des cribed in this sect ion.

Registers related to the operati on of peripheral features

are described in the section of that peri phe ral feature .

DS41262A-page 16 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

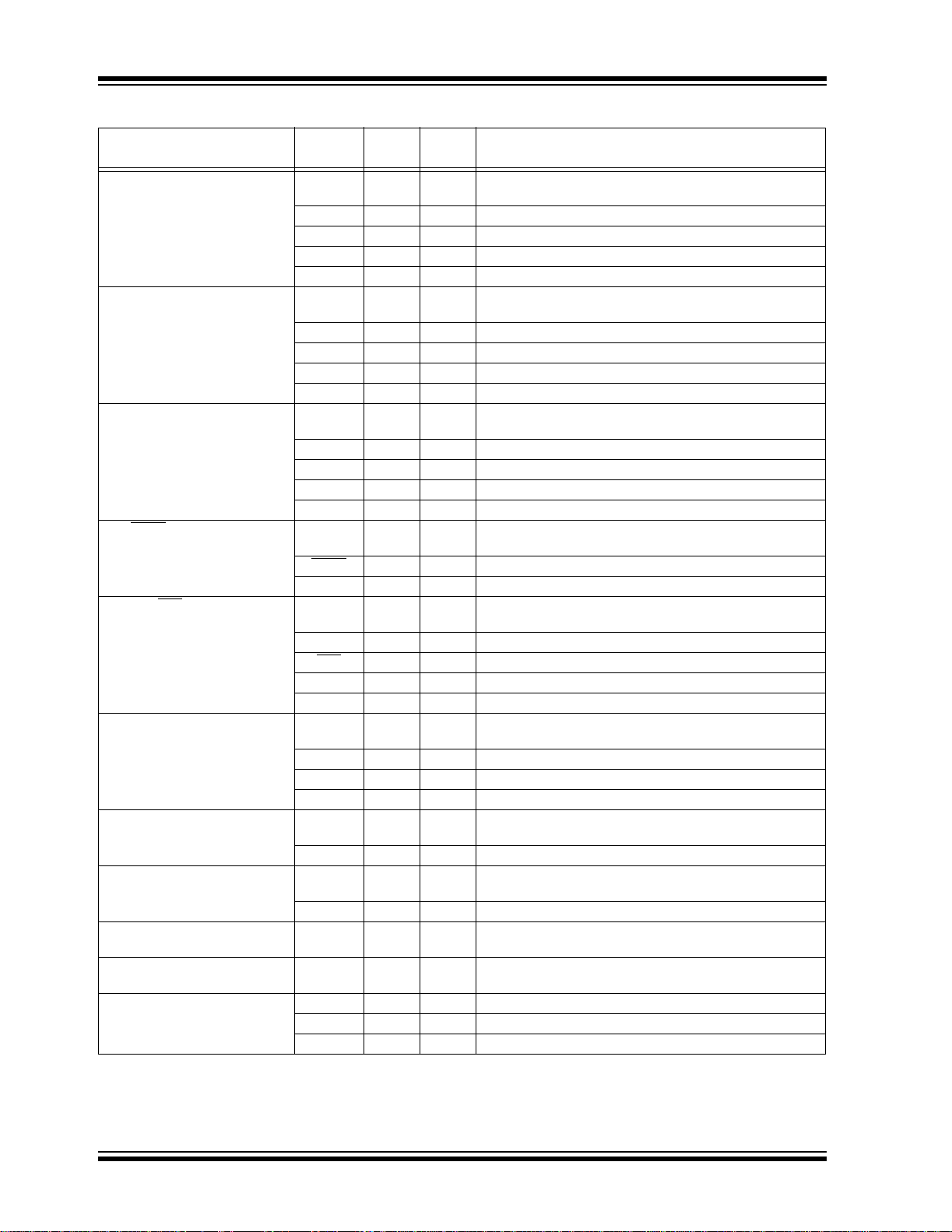

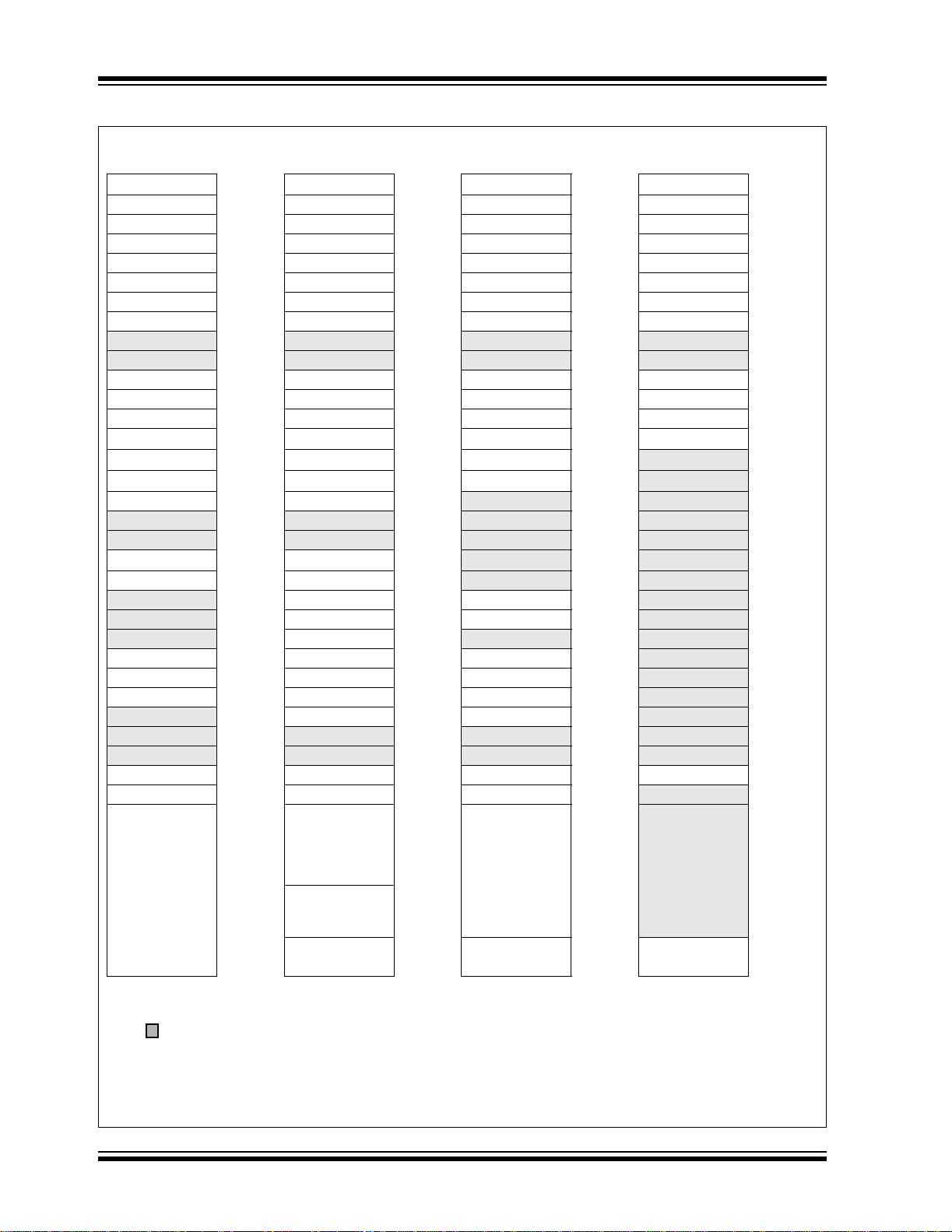

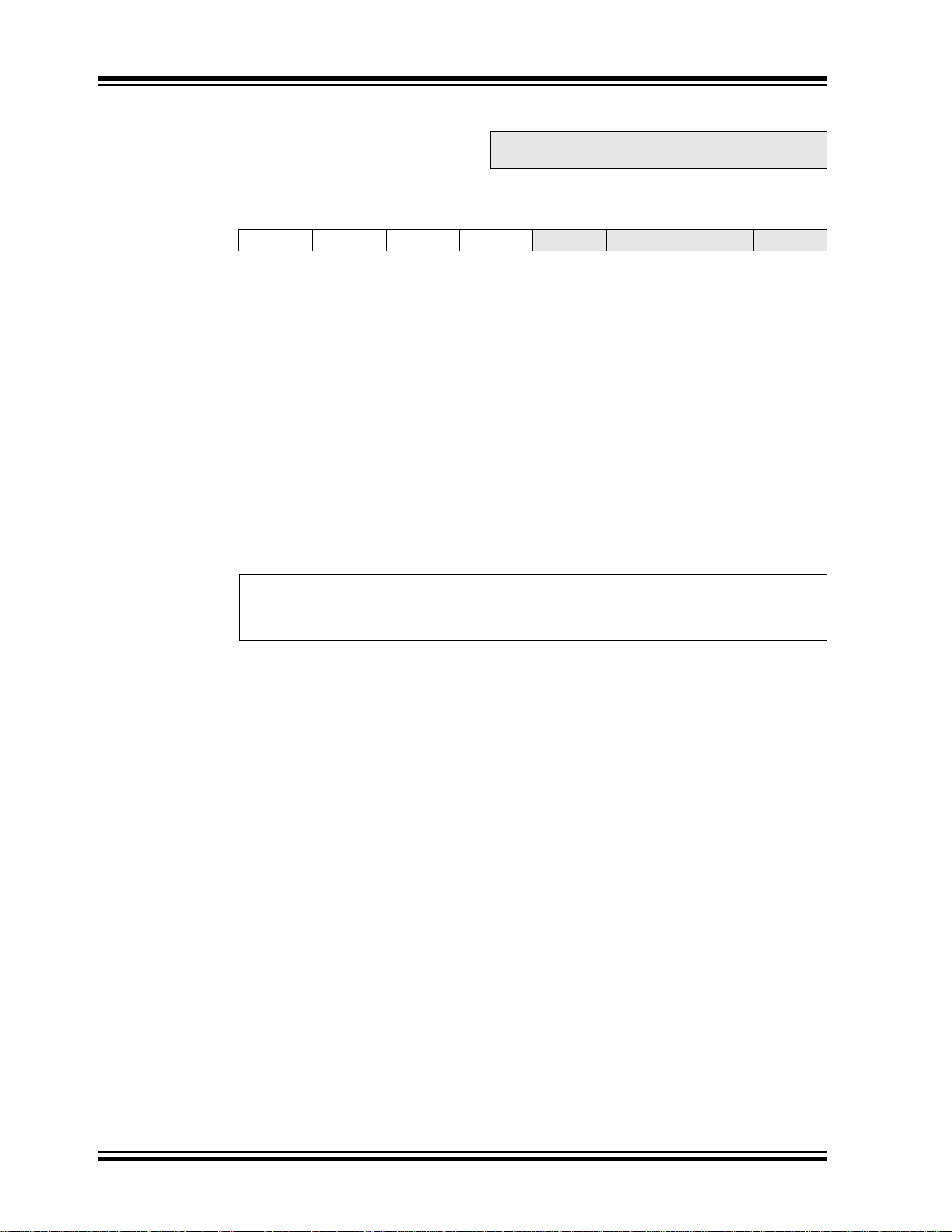

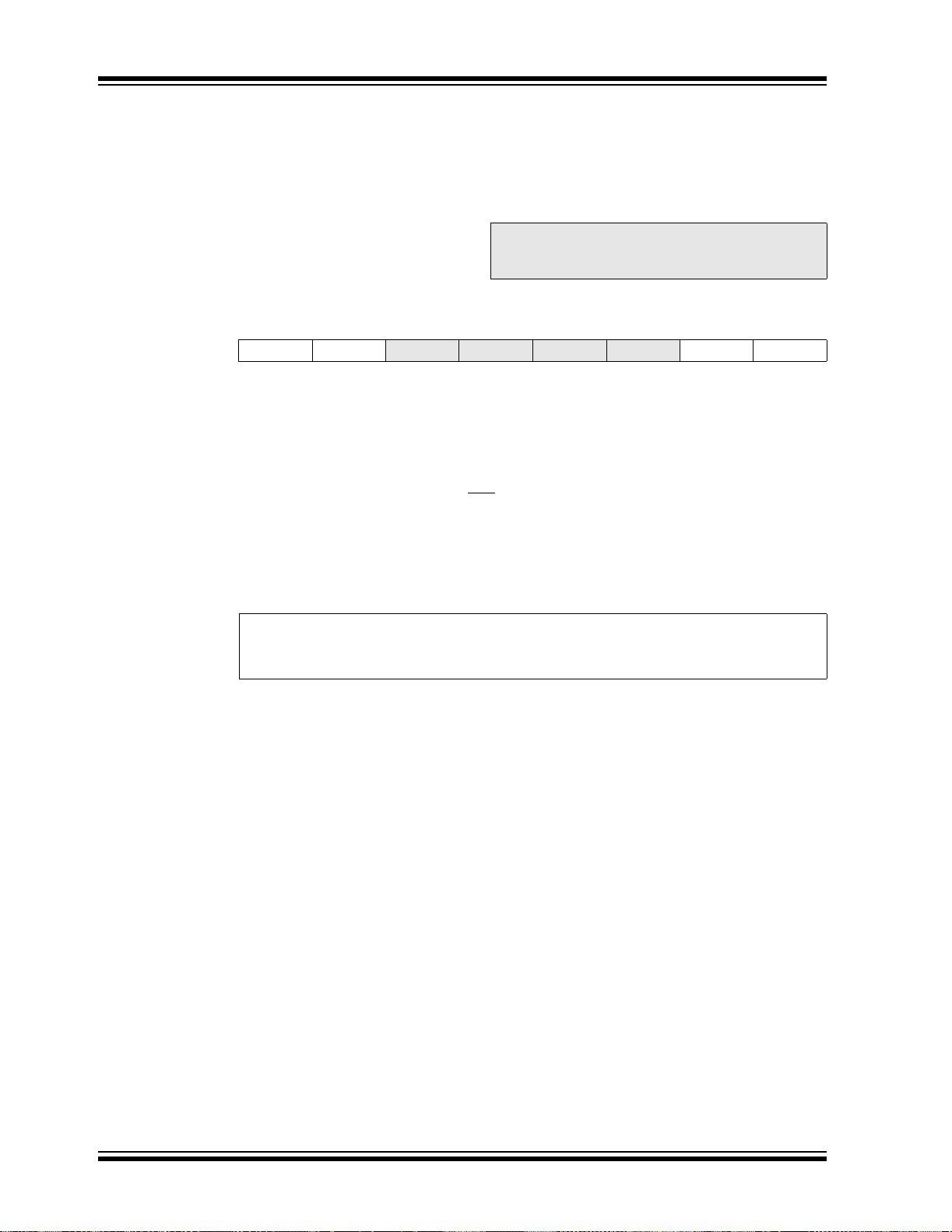

FIGURE 2-3: PIC16F685 SPECIAL FUNCTION REGISTERS

File File File File

Address Address Address Address

Indirect addr.

TMR0 01h OPTION_REG 81h TMR0 101h OPTION_REG 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h PORTA 105h TRISA 185h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

PORTC 07h TRISC 87h PORTC 107h TRISC 187h

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18Bh

PIR1 0Ch PIE1 8Ch EEDAT 10Ch EECON1 18Ch

PIR2 0Dh PIE2 8Dh EEADR 10Dh EECON2

TMR1L 0Eh PCON 8Eh EEDATH 10Eh 18Eh

TMR1H 0Fh OSCCON 8Fh EEADRH 10Fh 18Fh

T1CON 10h OSCTUNE 90h

TMR2 11h 91h 111h 191h

T2CON 12h PR2 92h 112h 192h

CCPR1L 15h WPUA 95h WPUB 115h 195h

CCPR1H 16h IOCA 96h IOCB 116h

CCP1CON 17h WDTCON 97h 117h 197h

PWM1CON 1Ch

ECCPAS 1Dh 9Dh 11Dh PSTRCON 19Dh

ADRESH 1Eh ADRESL 9Eh ANSEL 11Eh SRCON 19Eh

ADCON0 1Fh ADCON1 9Fh ANSELH 11Fh

(1)

00h Indirect addr.

08h 88h 108h 188h

09h 89h 109h 189h

13h 93h 113h 193h

14h 94h 114h 194h

18h 98h VRCON 118h 198h

19h 99h CM1CON0 119h 199h

1Ah 9Ah CM2CON0 11Ah 19Ah

1Bh 9Bh CM2CON1 11Bh 19Bh

20h

(1)

80h Indirect addr.

9Ch 11Ch 19Ch

A0h

(1)

100h Indirect addr.

110h 190h

120h

(1)

(1)

180h

18Dh

196h

19Fh

1A0h

General

General

Purpose

Register

96 Bytes

7Fh FFh 17Fh 1FFh

Bank 0 Bank1 Bank2 Bank3

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 17

Purpose

Register

80 Bytes

accesses

70h-7Fh

EFh 16Fh

F0h accesses

General

Purpose

Register

80 Bytes

70h-7Fh

170h accesses

70h-7Fh

1F0h

PIC16F685/687/689/690

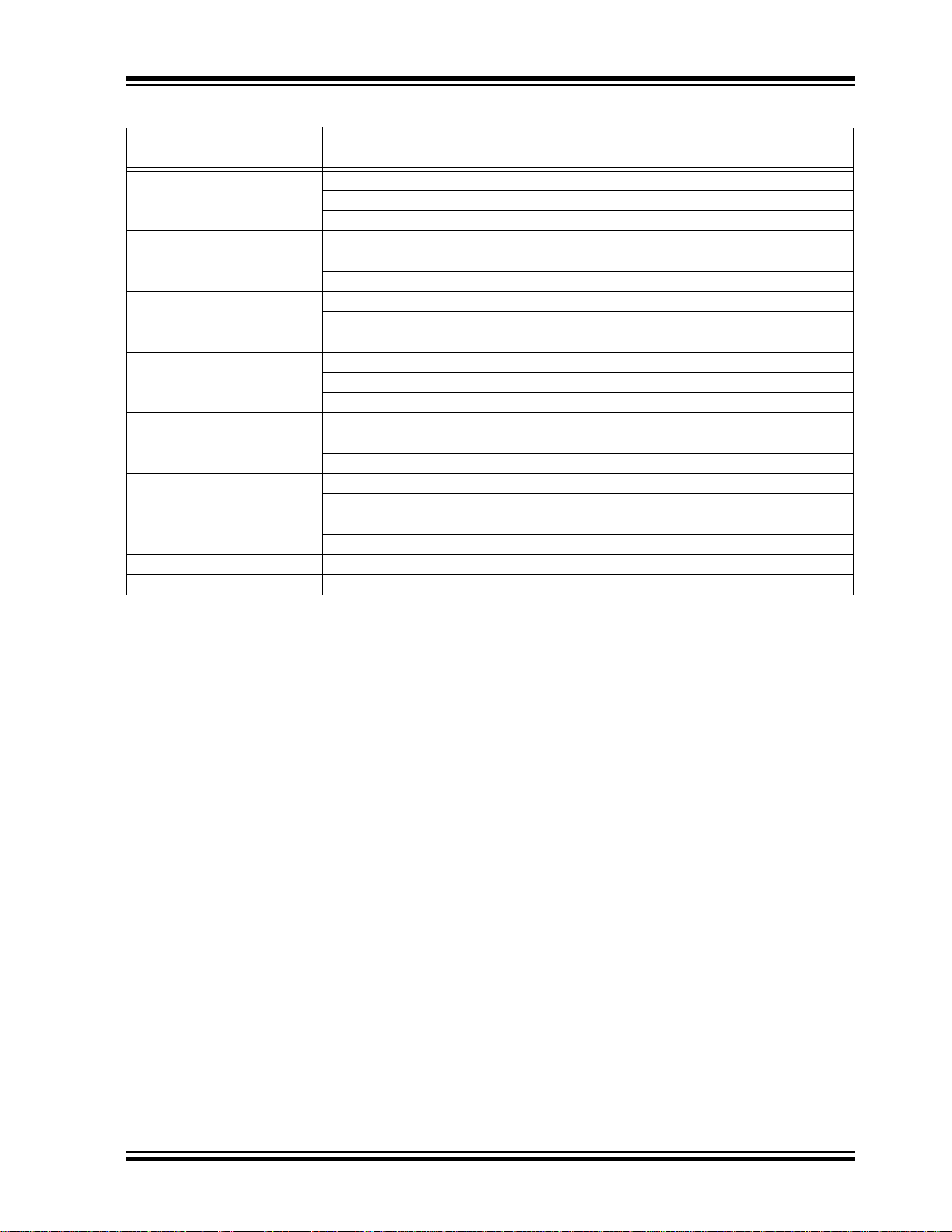

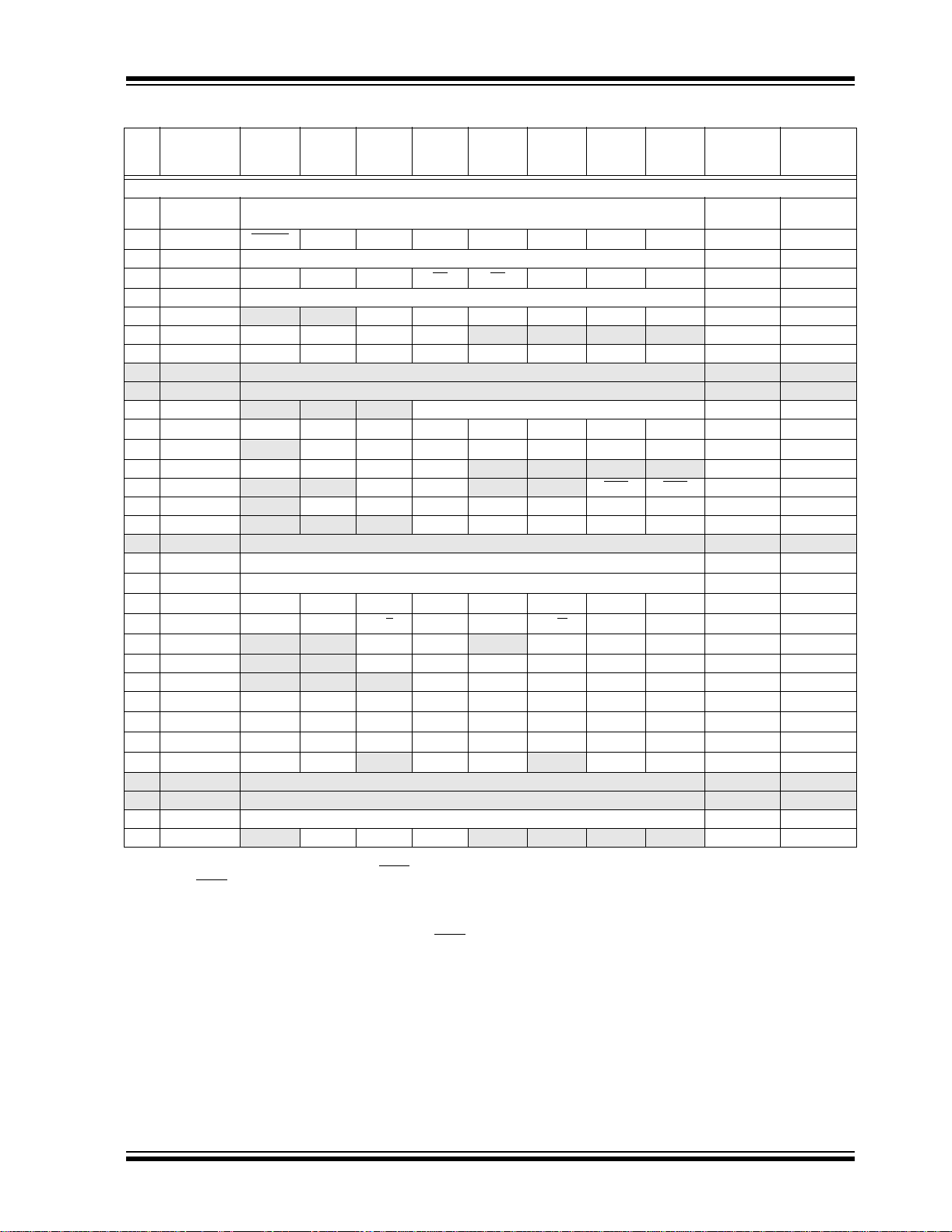

FIGURE 2-4: PIC16F687/P IC16 F689 SPECIAL FUNCTION REGISTERS

File File File File

Address Address Address Address

Indirect addr.

(1)

00h Indirect addr.

TMR0 01h OPTION_REG 81h TMR0 101h OPTION_REG 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h PORTA 105h TRISA 185h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

PORTC 07h TRISC 87h PORTC 107h TRISC 187h

08h 88h 108h 188h

09h 89h 109h 189h

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18Bh

PIR1 0Ch PIE1 8Ch EEDAT 10Ch EECON1 18Ch

PIR2 0Dh PIE2 8Dh EEADR 10Dh EECON2

TMR1L 0Eh PCON 8Eh EEDATH

TMR1H 0Fh OSCCON 8Fh EEADRH

T1CON 10h OSCTUNE 90h 110h 190h

11h 91h 111h 191h

12h 92h 112h 192h

SSPBUF 13h SSPADD

SSPCON 14h SSPSTAT 94h 114h 194h

15h WPUA 95h WPUB 115h 195h

16h IOCA 96h IOCB 116h 196h

17h WDTCON 97h 117h 197h

RCSTA 18h TXSTA 98h VRCON 118h

TXREG 19h SPBRG 99h CM1CON0 119h

RCREG 1Ah SPBRGH 9Ah CM2CON0 11Ah 19Ah

1Bh BAUDCTL 9Bh CM2CON1 11Bh 19Bh

1Ch 9Ch 11Ch 19Ch

1Dh 9Dh 11Dh 19Dh

ADRESH 1Eh ADRESL 9Eh ANSEL 11Eh SRCON 19Eh

ADCON0 1Fh ADCON1 9Fh ANSELH 11Fh

20h

General

Purpose

Register

96 Bytes

General

Purpose

Register

32 Bytes

48 Bytes

(PIC16F689 only)

accesses

7Fh FFh 17Fh 1FFh

70h-7Fh

Bank 0 Bank1 Bank2 Bank3

(1)

80h Indirect addr.

(2)

93h 113h 193h

A0h

General

Purpose

BFh

C0h

EFh

Register

80 Bytes

(PIC16F689 only)

F0h accesses

70h-7Fh

(1)

100h Indirec t addr.

(3)

10Eh 18Eh

(3)

10Fh 18Fh

120h

170h accesses

70h-7Fh

(1)

(1)

180h

18Dh

198h

199h

19Fh

1A0h

1F0h

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

2: Address 93h also access es t he SSP Mask (SSPMSK) regist er under certain conditions.

See Registers 13-2 an d 13-3 for more details.

3: PIC16F689 only.

DS41262A-page 18 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

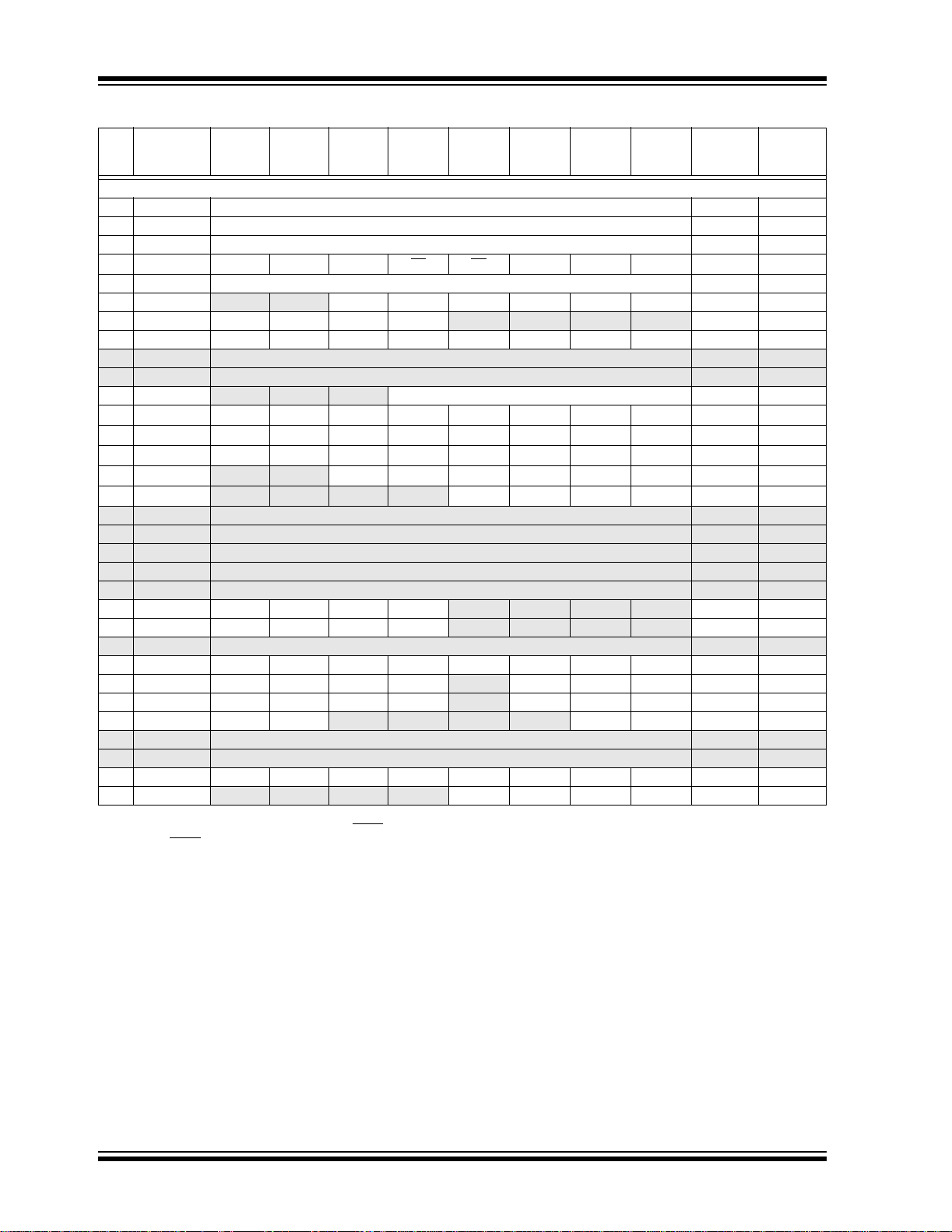

FIGURE 2-5: PIC16F690 SPECIAL FUNCTION REGISTERS

File File File File

Address Address Address Address

Indirect addr.

TMR0 01h OPTION_REG 81h TMR0 101h OPTION_REG 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h PORTA 105h TRISA 185h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

PORTC 07h TRISC 87h PORTC 107h TRISC 187h

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18Bh

PIR1 0Ch PIE1 8Ch EEDAT 10Ch EECON1 18Ch

PIR2 0Dh PIE2 8Dh EEADR 10Dh EECON2

TMR1L 0Eh PCON 8Eh EEDATH 10Eh 18Eh

TMR1H 0Fh OSCCON 8Fh EEADRH 10Fh

T1CON 10h OSCTUNE 90h 110h 190h

TMR2 11h 91h 111h 191h

T2CON 12h PR2 92h

SSPBUF 13h SSPADD

SSPCON 14h SSPSTAT 94h

CCPR1L 15h WPUA 95h WPUB 115h 195h

CCPR1H 16h IOCA 96h IOCB 116h 196h

CCP1CON 17h WDTCON 97h

RCSTA 18h TXSTA 98h VRCON 118h 198h

TXREG 19h SPBRG 99h CM1CON0 119h 199h

RCREG 1Ah SPBRGH 9Ah CM2CON0 11Ah

PWM1CON 1Ch 9Ch 11Ch 19Ch

ECCPAS 1Dh

ADRESH 1Eh ADRESL 9Eh ANSEL 11Eh SRCON 19Eh

ADCON0 1Fh ADCON1 9Fh ANSELH 11Fh 19Fh

(1)

00h Indirect addr.

08h 88h 108h 188h

09h 89h 109h 189h

1Bh BAUDCTL 9Bh CM2CON1 11Bh 19Bh

20h

(1)

80h Indirect addr.

(2)

93h 113h 193h

9Dh 1 1Dh PSTRCON 19Dh

A0h

(1)

100h Indirect addr.

112h 192h

114h 194h

117h 197h

120h

(1)

(1)

180h

18Dh

18Fh

19Ah

1A0h

General

General

Purpose

Register

96 Bytes

7Fh FFh 17Fh 1FFh

Bank 0 Bank1 Bank2 Bank3

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

2: Address 93h also accesses the SSP Mask (SSPMSK) register under certain conditions.

See Registers 13-2 and 13-3 for more details.

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 19

Purpose

Register

80 Bytes

accesses

70h-7Fh

EFh 16Fh

F0h accesses

General

Purpose

Register

80 Bytes

70h-7Fh

170h accesses

70h-7Fh

1F0h

PIC16F685/687/689/690

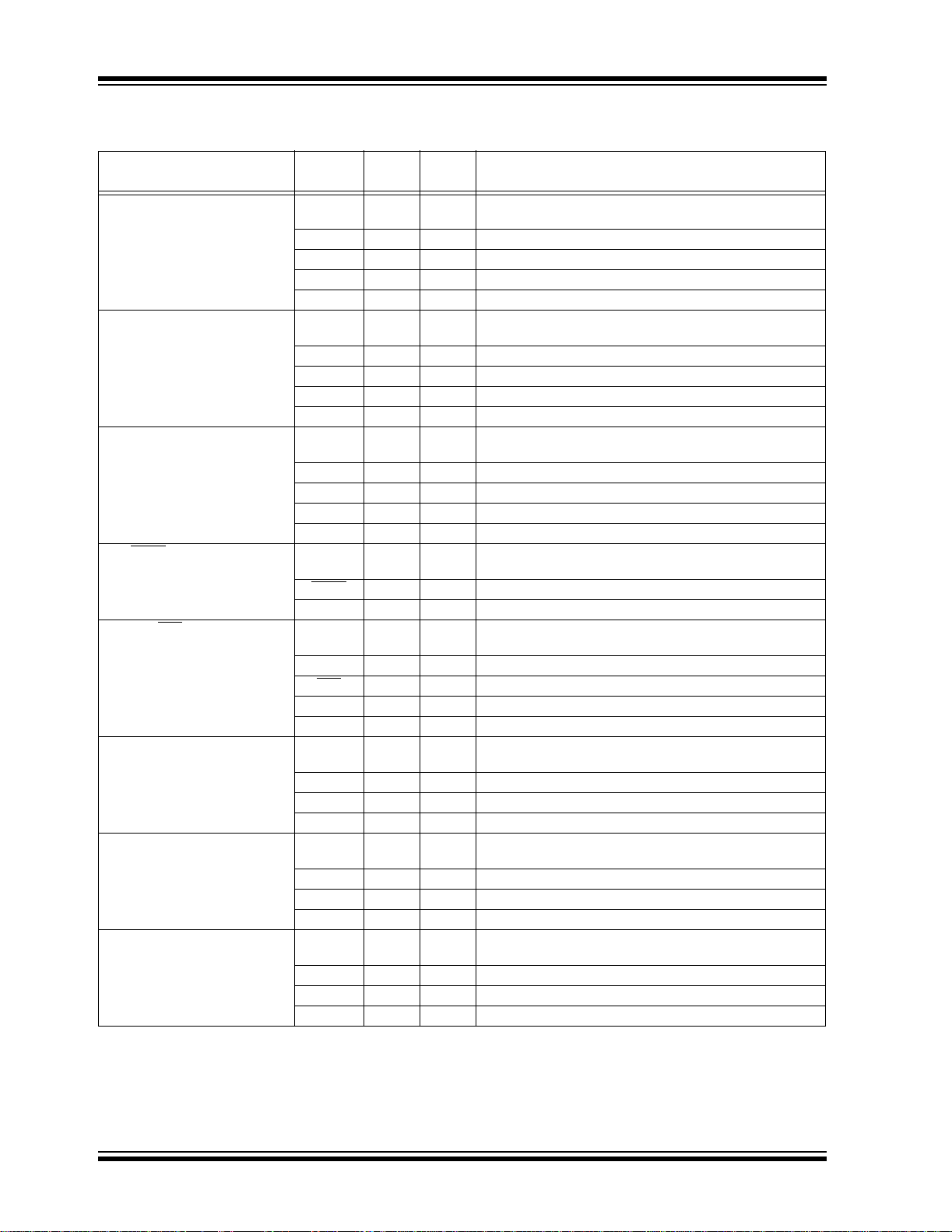

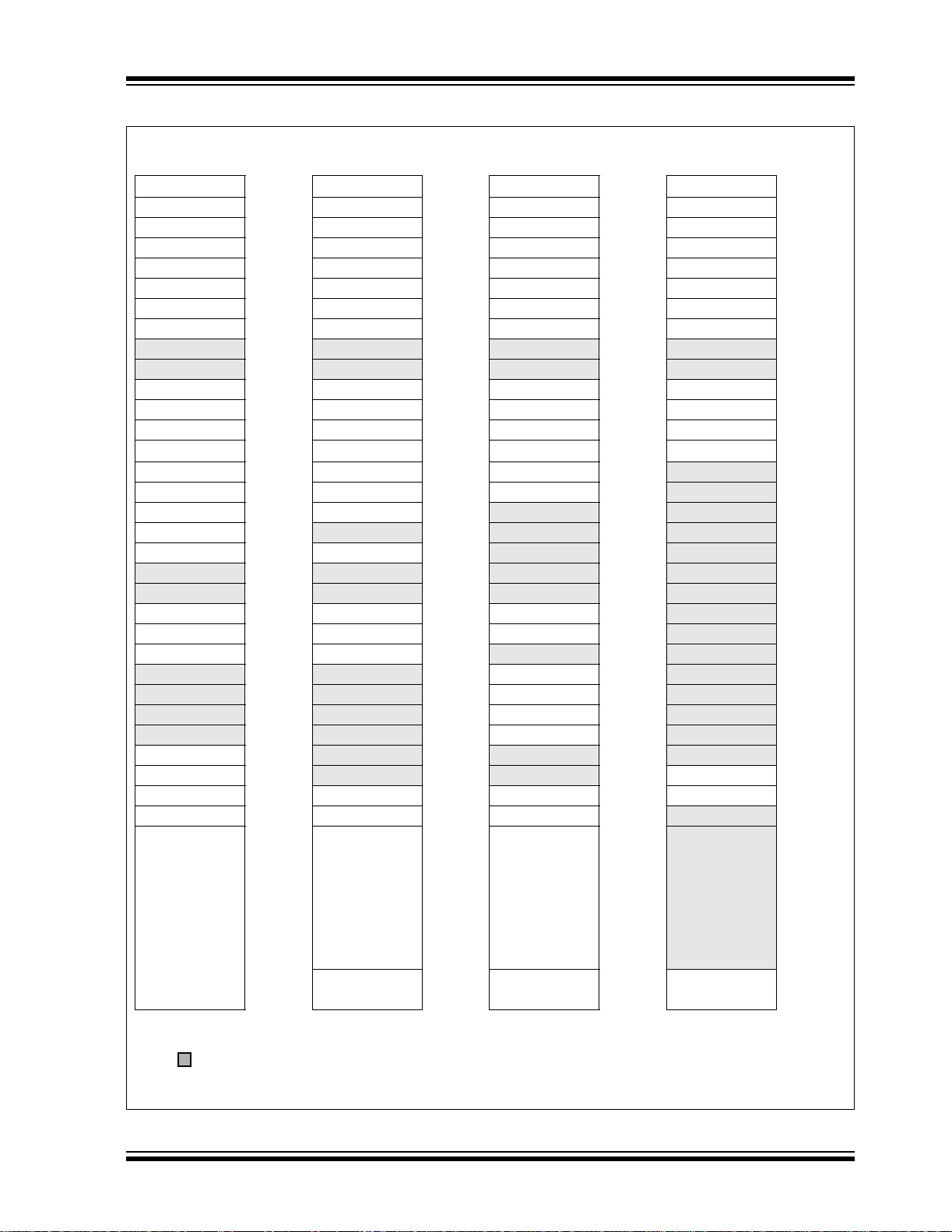

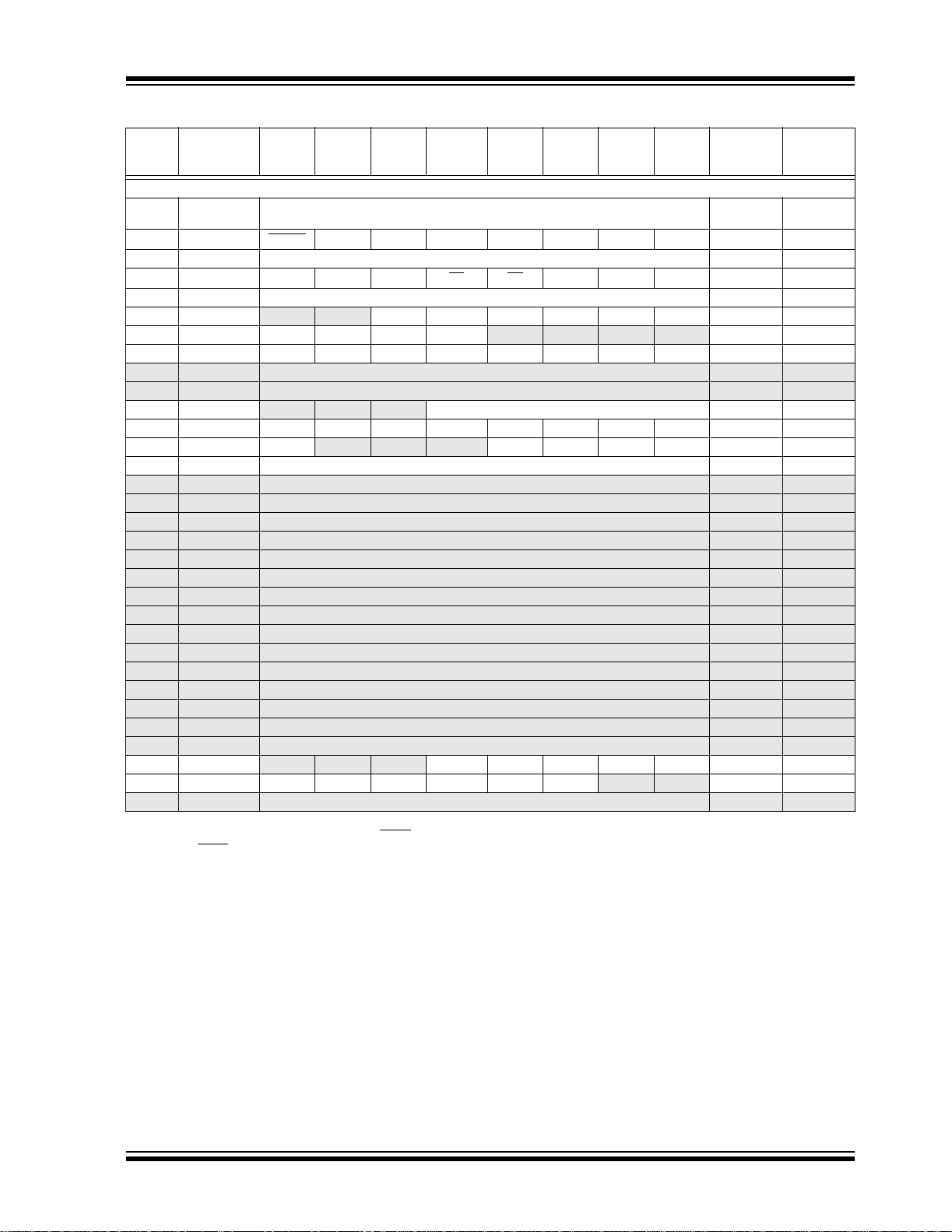

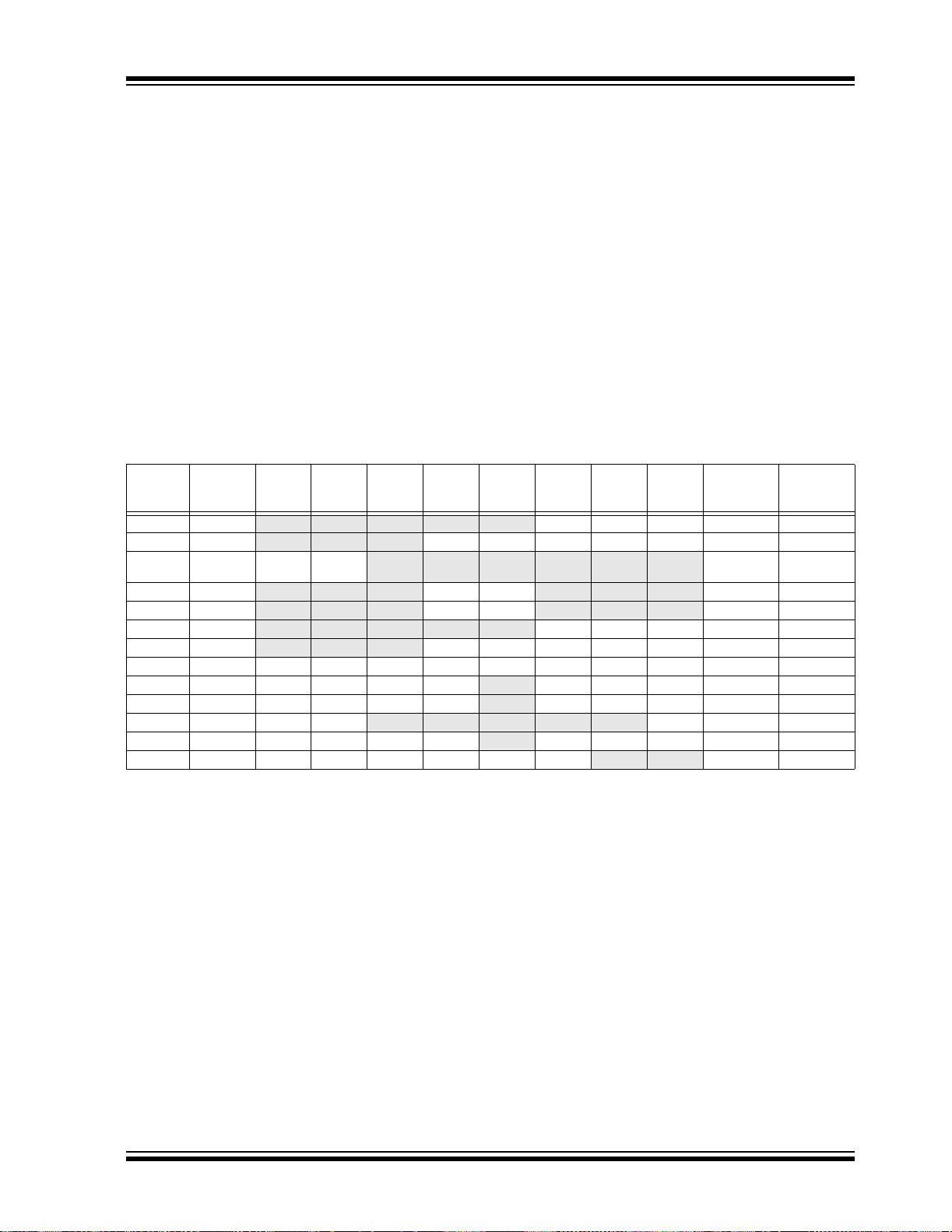

TABLE 2-1: PIC16F685/687/689/690 SPECIAL REGISTERS SUMMARY BANK 0

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR/BOR

Reset

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx xxxx xxxx

01h TMR0 Timer0 Module Register xxxx xxxx uuuu uuuu

02h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

Value on

03h STATUS IRP RP1 RP0 TO

PD ZDCC0001 1xxx 000q quuu

04h FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

05h PORTA

06h PORTB RB7 RB6 RB5 RB4

— — RA5 RA4 RA3 RA2 RA1 RA0 --xx xxxx --uu uuuu

— — — — xxxx ---- uuuu ----

07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 xxxx xxxx uuuu uuuu

08h — Unimplemented — —

09h — Unimplemented — —

0Ah PCLATH

0Bh INTCON GIE PEIE T0IE INTE RABIE T0IF INTF RABIF

0Ch PIR1

0Dh PIR2

— — — Write Buffer for upper 5 bits of Program Counter ---0 0000 ---0 0000

(2)

0000 000x 0000 000x

— ADIF RCIF

(3)

TXIF

(3)

SSPIF

(3)

CCP1IF

(4)

TMR2IF

(4)

TMR1IF -000 0000 -000 0000

OSFIF C2IF C1IF EEIF — — — — 0000 ---- 0000 ----

0Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 xxxx xxxx uuuu uuuu

0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 xxxx xxxx uuuu uuuu

10h T1CON T1GINV TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

TMR1CS TMR1ON 0000 0000 uuuu uuuu

11h TMR2 Timer2 Module Register 0000 0000 0000 0000

12h T2CON

13h SSPBUF

14h SSPCON

15h CCPR1L

16h CCPR1H

17h CCP1CON

18h RCSTA

19h TXREG

1Ah RCREG

(3)

(3)

(3)

(3)

(3, 5)

(4)

(4)

— TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 -000 0000

Synchronous Serial Port Receive Buffer/Transmit Register xxxx xxxx uuuu uuuu

WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0 0000 0000 0000 0000

Capture/Compare/PW M Regi st er 1 (LSB ) xxxx xxxx uuuu uuuu

Capture/Compare/PW M Regi st er 1 (MSB ) xxxx xxxx uuuu uuuu

(4)

P1M1 P1M0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 0000 0000 0000 0000

SPEN RX9 SREN CREN ADDEN FERR OERR RX9D 0000 000x 0000 000x

EUSART Transmit Data Register 0000 0000 0000 0000

EUSART Receive Data Register 0000 0000 0000 0000

1Bh — Unimplemented — —

1Ch

1Dh

PWM1CON

ECCPAS

(4)

PRSEN PDC6 PDC5 PDC4 PDC3 PDC2 PDC1 PDC0 0000 0000 0000 0000

(4)

ECCPASE ECCPAS2 ECCPAS1 ECCPAS0 PSSAC1 PSSAC0 PSSBD1 PSSBD0 0000 0000 0000 0000

1Eh ADRESH A/D Result Register High Byte xxxx xxxx uuuu uuuu

1Fh ADCON0 ADFM VCFG CHS3 CHS2 CHS1 CHS0 GO/DONE

ADON 0000 0000 0000 0000

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR

2: MCLR

and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

Reset and Watchdog Timer Reset dur ing nor mal operation.

mismatched exists.

3: PIC16F687/PIC16F689/PIC16F690 only.

4: PIC16F685/PIC16F690 only.

5: When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register.

See Registers 13-2 and 13 -3 for mo re detail .

Value on

all other

Resets

(1)

DS41262A-page 20 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

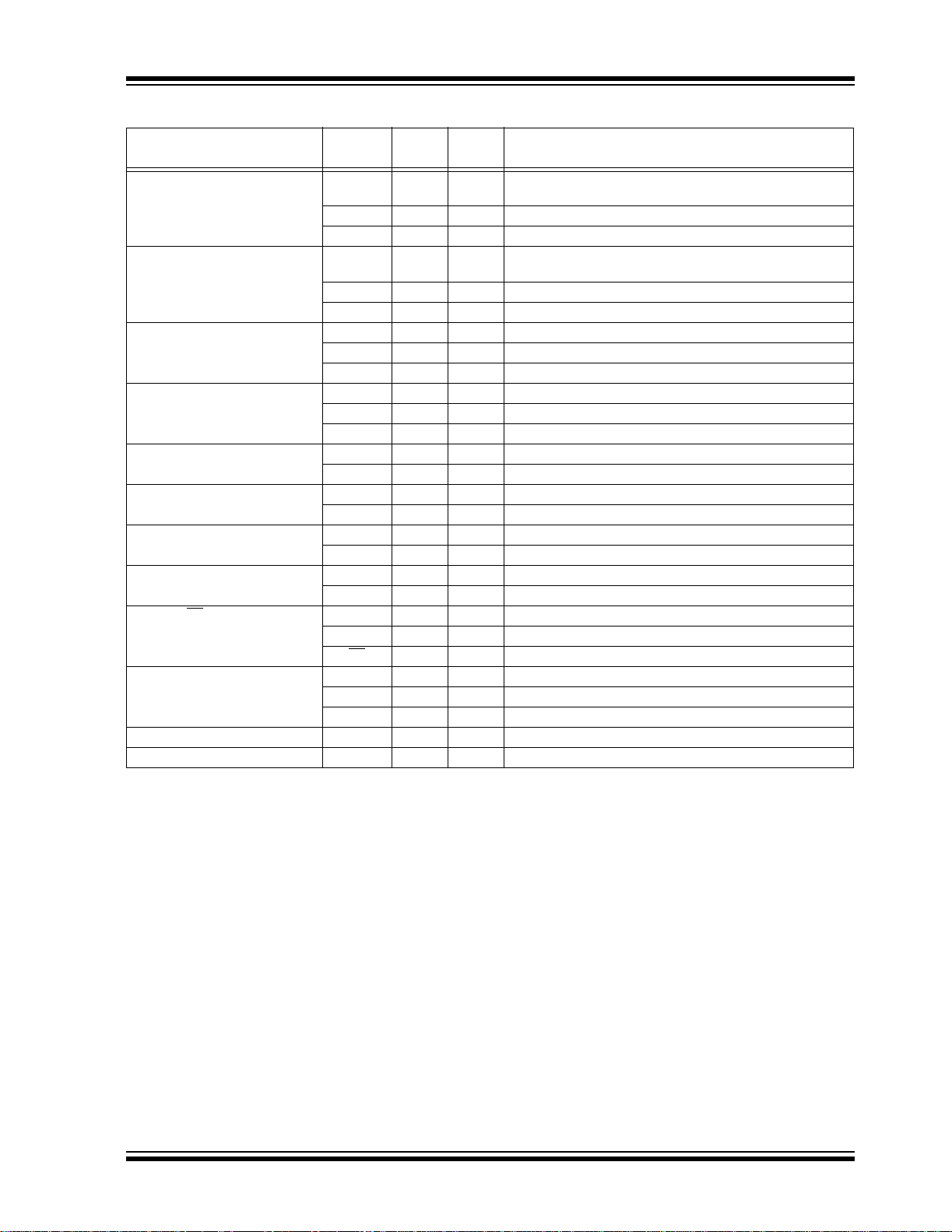

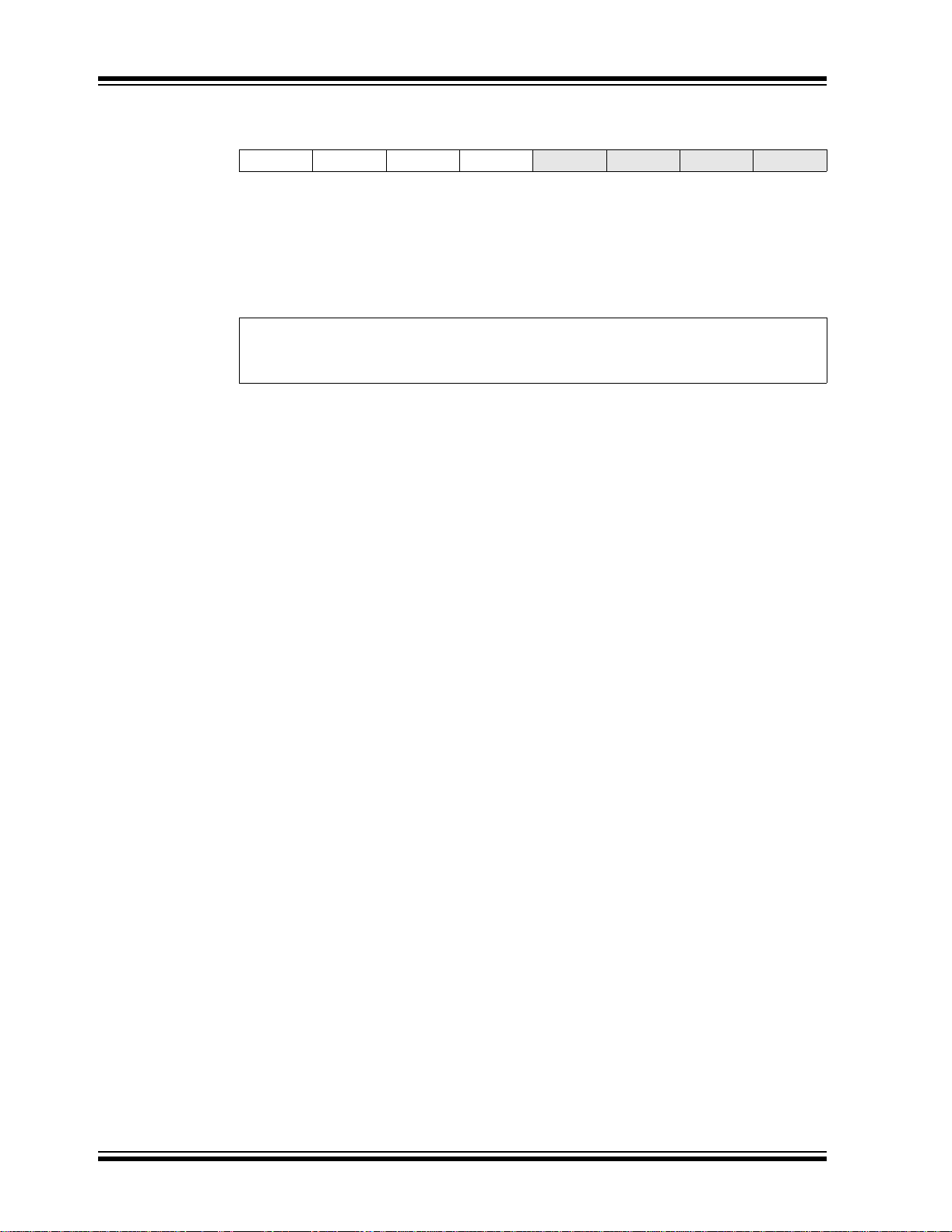

TABLE 2-2: PIC16F685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR/BOR

Reset

Bank 1

Value on

80h INDF Addressing this location uses contents of FSR to address data memory (not a physical

81h OPTION_REG RABPU

register)

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

xxxx xxxx xxxx xxxx

82h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

83h STATUS IRP RP1 RP0 TO

PD ZDCC0001 1xxx 000q quuu

84h FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

85h TRISA

86h TRISB TRISB7 TRISB6 TRISB5 TRISB4

— — TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 --11 1111 --11 1111

— — — — 1111 ---- 1111 ----

87h TRISC TRISC7 TRISC6 TRISC5 TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 1111 1111 1111 1111

88h — Unimplemented — —

89h — Unimplemented — —

8Ah PCLATH

8Bh INTCON GIE PEIE T0IE INTE RABIE T0IF INTF RABIF

8Ch PIE1

8Dh PIE2 OSFIE C2IE C1IE EEIE

8Eh PCON

8Fh OSCCON

90h OSCTUNE

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(2)

0000 000x 0000 000x

— ADIE RCIE

(3)

TXIE

(3)

SSPIE

(3)

CCP1IE

(4)

TMR2IE

(4)

TMR1IE -000 0000 -000 0000

— — — — 0000 ---- 0000 ----

— — ULPWUE SBOREN — —PORBOR --01 --qq --0u --uu

— IRCF2 IRCF1 IRCF0 OSTS HTS LTS SCS -110 q000 -110 x000

— — — TUN4 T UN3 TUN2 TUN1 TUN0 ---0 0000 ---u uuuu

91h — Unimplemented — —

92h PR2

(4)

93h SSPADD

93h SSPMSK

94h SSPSTAT

95h WPUA

(5)

96h IOCA

97h WDTCON

98h TXSTA

99h SPBRG

9Ah SPBRGH

9Bh BAUDCTL

Timer2 Period Register 1111 1111 1111 1111

(3, 6)

Synchronous Serial Port (I2C mode) Address Register 0000 0000 0000 0000

(3, 6)

MSK7 MSK6 MSK5 MSK4 MSK3 MSK2 MSK1 MSK0 1111 1111 1111 1111

(3)

SMP CKE D/A PSR/WUA BF 0000 0000 0000 0000

— —WPUA5WPUA4— WPUA2 WPUA1 WPUA0 --11 -111 --11 -111

— — IOCA5 IOCA4 IOCA3 IOCA2 IOCA1 IOCA0 --00 0000 --00 0000

— — — WDTPS3 WDTPS2 WDTPS1 WDTPS0 SWDTEN ---0 1000 ---0 1000

(3)

(3)

CSRC TX9 TXEN SYNC SENB BRGH TRMT TX9D 0000 0010 0000 0010

BRG7 BRG6 BRG5 BRG4 BRG3 BRG2 BRG1 BRG0 0000 0000 0000 0000

(3)

BRG15 BRG14 BRG13 BRG1 2 BRG11 BRG10 BRG9 BRG8 0000 0000 0000 0000

(3)

ABDOVF RCIDL — SCKP BRG16 — WUE ABDEN 01-0 0-00 01-0 0-00

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh ADRESL A/D Result Register Low Byte xxxx xxxx uuuu uuuu

9Fh ADCON1

— ADCS2 ADCS1 ADCS0 — — — — -000 ---- -000 ---

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR

2: MCLR

and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

Reset and Watchdog Timer Reset during normal operation.

mismatched exists.

3: PIC16F687/PIC16F689/PIC16F690 only.

4: PIC16F685/PIC16F690 only.

5: RA3 pull-up is enabled when pin is configured as MCLR

in Configuration Word.

6: Accessible only when SSPM<3:0> = 1001.

Value on

all other

Resets

(1)

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 21

PIC16F685/687/689/690

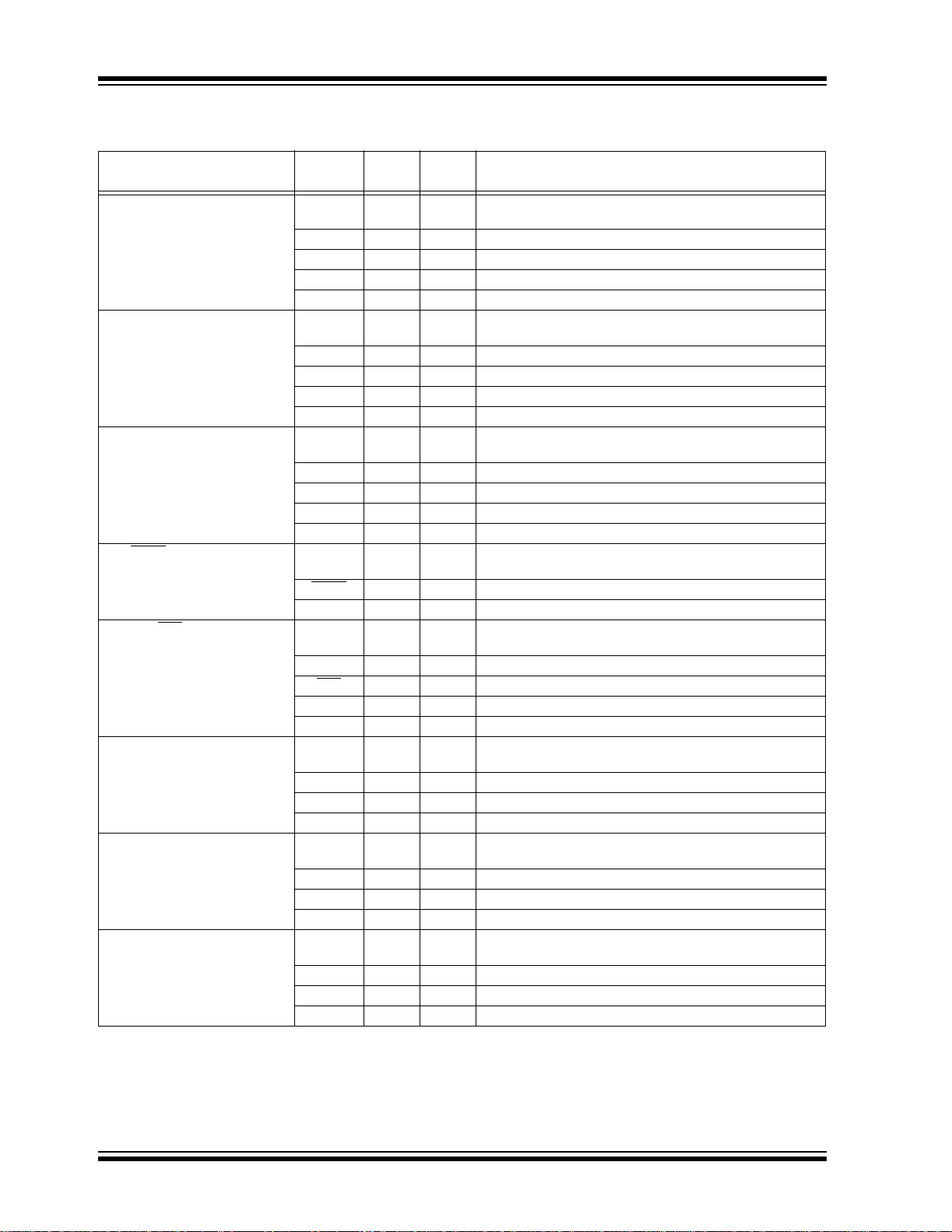

TABLE 2-3: PIC16F685/687/689/690 SPECIAL REGISTERS SUMMARY BANK 2

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 2

100h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx xxxx xxxx

101h TMR0 Timer0 Module Register xxxx xxxx uuuu uuuu

102h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

103h STATUS IRP RP1 RP0 TO

104h FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

105h PORTA

106h PORTB RB7 RB6 RB5 RB4

107h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 xxxx xxxx uuuu uuuu

108h — Unimplemented — —

109h — Unimplemented — —

10Ah PCLA TH

10Bh INTCON GIE PEIE T0IE INTE RABIE T0IF INTF RABIF

EEDAT EEDAT7 EEDAT6 EEDAT5 EEDAT4 EEDAT3 EEDAT2 EEDAT1 EEDAT0 0000 0000 0000 0000

10Ch

EEADR EEADR7 EEADR6 EEADR5 EEADR4 EEADR3 EEADR2 EEADR1 EEADR0 0000 0000 0000 0000

10Dh

10Eh EEDATH

10Fh EEADRH

110h — Unimplemented — —

111h — Unimplemented — —

112h — Unimplemented — —

113h — Unimplemented — —

114h — Unimplemented — —

115h WPUB WPUB7 WPUB6 WPUB5 WPUB4

116h IOCB IOCB7 IOCB6 IOCB5 IOCB4

117h — Unimplemented — —

118h VRCON C1VREN C2VREN VRR VP6EN VR3 V R2 VR1 VR0 0000 0000 0000 0000

119h CM1CON0 C1ON C1OUT

11Ah CM2CON0 C2ON C2OUT

11Bh CM2 CON1 MC1OUT M C2OUT

11Ch — Unimplemented — —

11Dh — Unimplemented — —

11Eh ANSEL ANS7 ANS6 ANS5 ANS4 ANS3 ANS2 ANS1 ANS0 1111 1111 1111 1111

11Fh ANSELH

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR

(3)

(3)

2: MCLR

mismatched exists.

3: PIC16F685/PIC16F689/PIC16F690 only.

— — RA5 RA4 RA3 RA2 RA1 RA0 --xx xxxx --uu uuuu

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

— —

— — — —

— — — — ANS11 ANS10 ANS9 A NS8 ---- 1111 ---- 1111

and WDT Reset does not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

EEDATH5 EEDATH4 EEDATH3 EEDATH2 EEDATH1 EEDATH0

C1OE C1POL — C1R C1CH1 C1CH0 0000 -000 0000 -000

C2OE C2POL — C2R C2CH1 C2CH0 0000 -000 0000 -000

— — — — T1GSS C2SYNC 00-- --10 00-- --10

Reset and Watchdog Timer Reset dur ing nor mal operation.

PD ZDCC0001 1xxx 000q quuu

— — — — xxxx ---- uuuu ----

EEADRH3 EEADRH2 EEADRH1 EEADRH0

— — — — 1111 ---- 1111 ----

— — — — 0000 ---- 0000 ----

Value on

POR/BOR

Reset

(2)

0000 000x 0000 000x

--00 0000 --00 0000

---- 0000 ---- 0000

Value on

all other

Resets

(1)

DS41262A-page 22 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

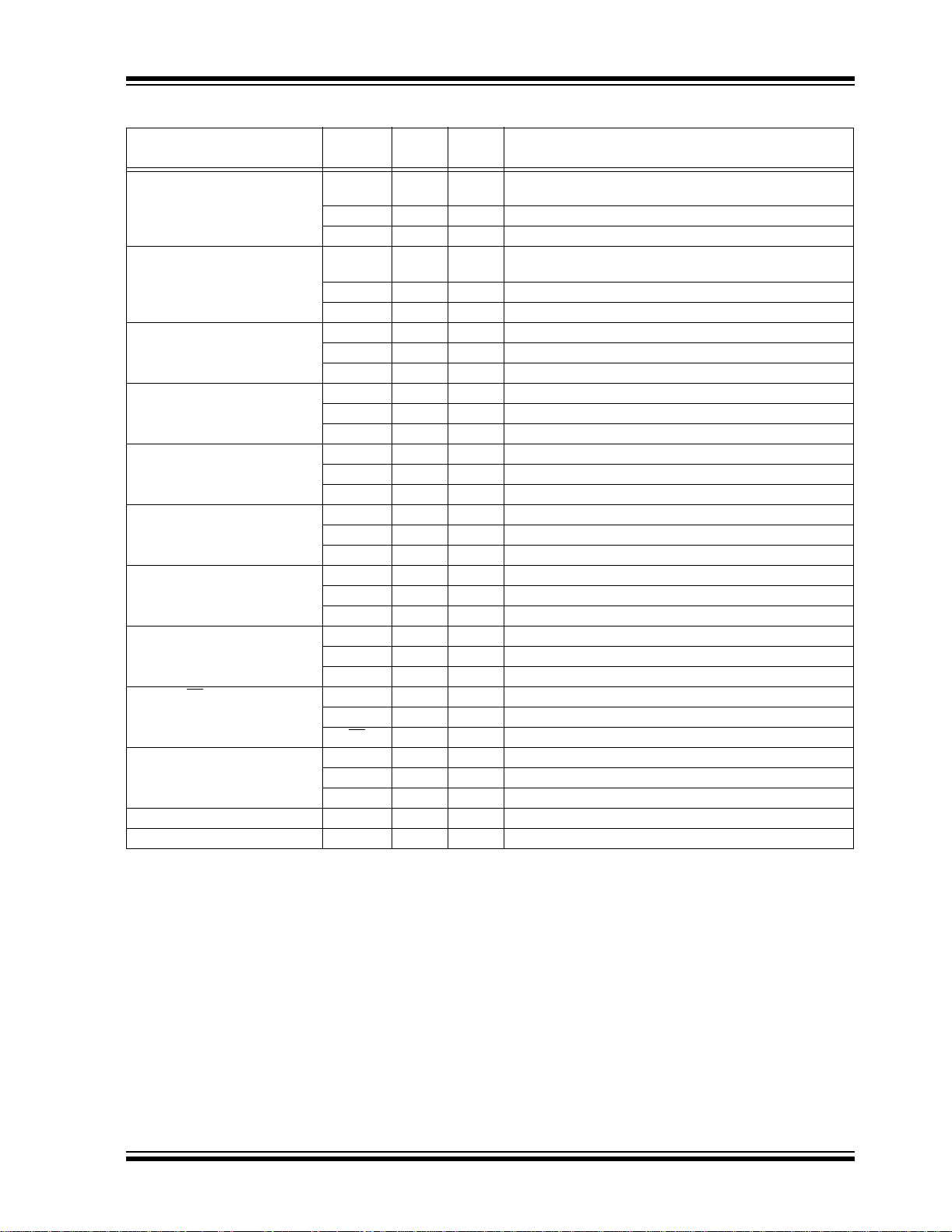

TABLE 2-4: PIC16F685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 3

180h INDF Addressing this location uses contents of FSR to address data memory (not a physical

181h OPTION_REG RABPU

182h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

183h STATUS IRP RP1 RP0 TO

184h FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

185h TRISA

186h TRISB TRISB7 TRISB6 TRISB5 TRISB4

187h TRISC TRISC7 TRISC6 TRISC5 TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 1111 1111 1111 1111

188h — Unimplemented — —

189h — Unimplemented — —

18Ah PCLATH

18Bh INTCON GIE PEIE T0IE INTE RABIE T0IF INTF RABIF

18Ch EECON1 EEPGD

18Dh EECON2 EEPROM Control Register 2 (not a physical register) ---- ---- ---- ---18Eh — Unimplemented — —

18Fh — Unimplemented — —

190h — Unimplemented — —

191h — Unimplemented — —

192h — Unimplemented — —

193h — Unimplemented — —

194h — Unimplemented — —

195h — Unimplemented — —

196h — Unimplemented — —

197h — Unimplemented — —

198h — Unimplemented — —

199h — Unimplemented — —

19Ah — Unimplemented — —

19Bh — Unimplemented — —

19Ch — Unimplemented — —

19Dh PSTRCON

19Eh SRCON SR1 SR0 C1SEN C2REN PULSS PULSR

19Fh — Unimplemented — —

Legend: – = Unimplemented locations read as ‘0’, u = unchange d, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR

2: MCLR

mismatched exists.

3: PIC16F685/PIC16F690 only.

register)

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

PD ZDCC0001 1xxx 000q quuu

— — TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 --11 1111 --11 1111

— — — — 1111 ---- 1111 ----

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

— — — WRERR WREN WR RD x--- x000 0--- q000

(3)

— — — STRSYNC STRD STRC STRB STRA ---0 0001 ---0 0001

— — 0000 00-- 0000 00--

and WDT Reset does not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

Reset and Watchdog Timer Reset during normal operation.

Value on

POR/BOR

Reset

xxxx xxxx xxxx xxxx

(2)

0000 000x 0000 000x

Value on

all other

Resets

(1)

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 23

PIC16F685/687/689/690

2.2.2.1 Status Register

The Status register, shown in Register 2-1, contains:

• the arithmetic status of the ALU

• the Reset status

• the bank select bits for data memory (GPR and

SFR)

The Status register can be the destination for any

instruction, like any other register. If the Status register

is the destination for an instruction that affects the Z,

DC or C bits, then the write to these three bits is

writable. Therefore, the result of an instruction with the

Status register as destination may be different than

intended.

For example, CLRF STATUS, will clear the upper three

bits and set the Z bit. Thi s leaves the Status register as

‘000u u1uu’ (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

Stat us register , beca use these instru ctions do not af fect

any Status bits. For other instructions not affecting any

Status bits, see the “Instruction Set Summary.”

disabled. These bit s are set or cleared ac cording to the

device logic. Furthermore, the TO

and PD bits are not

Note 1: The C and DC bits operate as a Borrow

and Digit Borrow out bit, respectively, in

subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h OR 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

(1)

(1)

bit 7

bit 6-5

bit 4

bit 3

bit 2

bit 1

bit 0

IRP RP1 RP0 TO PD ZDC

bit 7 bit 0

IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h-1FFh)

0 = Bank 0, 1 (00h-FFh)

RP<1:0>: Register Bank Select bits (used for direct addressing)

00 = Bank 0 (00h-7Fh)

01 = Bank 1 (80h-FFh)

10 = Bank 2 (100h-17Fh)

11 = Bank 3 (180h-1FFh)

TO: Time-out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

DC: Digit Carry/Borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

(1)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Bo

rrow, the polarity is reversed. A subtraction is executed by adding the two’s

complement of the second operand. For rotate (RRF, RLF) instructions, this bit is

loaded with either the high or low-order bit of the source register.

(1)

C

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41262A-page 24 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

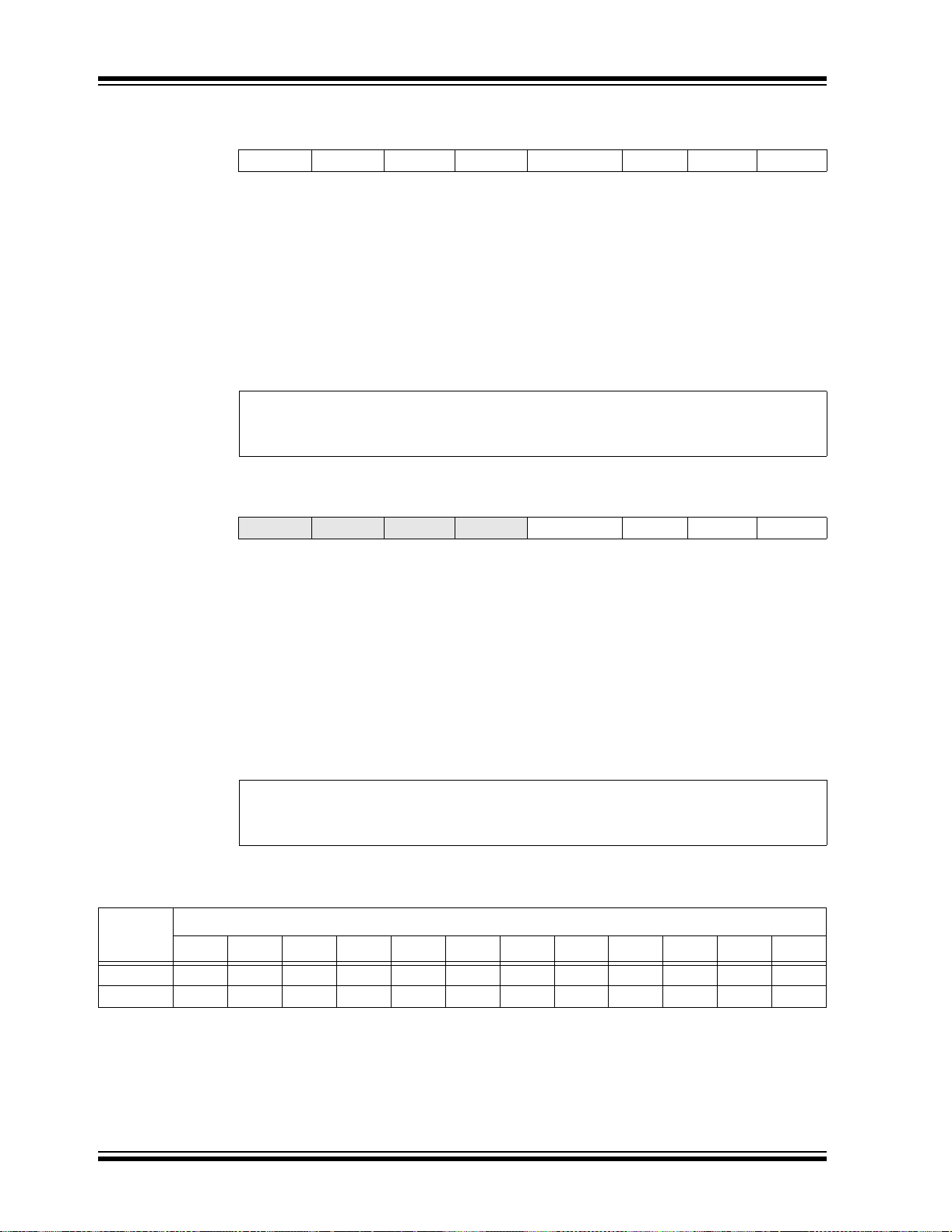

2.2.2.2 OPTION Register

The OPTION register is a readable and writable

register, which contains various control bits to

configure:

• TMR0/WDT prescaler

• External RA2/INT interrupt

•TMR0

• Weak pull-ups on PORTA/PORTB

REGISTER 2-2: OPTION_REG – OPTION REGISTER (ADDRESS: 81h OR 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RABPU

bit 7 bit 0

INTEDG T0CS T0SE PSA PS2 PS1 PS0

Note: To achieve a 1:1 prescaler assignment for

TMR0, assign the prescaler to the WDT by

setting PSA bit to ‘1’ (OPTION_REG<3>).

See Section 5.4 “Prescaler”.

bit 7 RABPU

1 = PORTA/PORTB pull-ups are disabled

0 = PORTA/PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RA2/AN2/T0CKI/INT/C1OUT pin

0 = Interrupt on falling edge of RA2/AN2/T0CKI/INT/C1OUT pin

bit 5 T0CS: TMR0 Clock Source Select bit

1 = Transition on RA2/AN2/T0CKI/INT/C1OUT pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA2/AN2/T0CKI/INT/C1OUT pin

0 = Increment on low-to-high transition on RA2/AN2/T0CKI/INT/C1OUT pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

: PORTA/PORTB Pull-up Enable bit

Bit Va lue TMR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

(1)

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 14.5 “Watchdog

Timer (WDT)” for more information.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 25

PIC16F685/687/689/690

2.2.2.3 INTCON Register

The INTCON register is a readable and writable

register , which c ontains the various en able and fl ag bit s

for TMR0 register overflow, PORTA change and

external RA2/AN2/T0CKI/INT/C1OUT pin interrupts.

Note: Interrupt flag bits are set when an interru pt

condition occurs, regar dless of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User

software should ensure the appropriate

interrupt flag bits are clear prior to

enabling an interrupt.

REGISTER 2-3: INTCON – INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh OR

18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RABIE

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 in terrupt

bit 4 INTE: RA2/INT External Interrupt Enable bit

1 = Enables the RA2/INT external interrupt

0 = Disables the RA2/INT external interrupt

bit 3 RABIE: PORTA/PORTB Change Interrupt Enable bit

1 = Enables the PORTA/PORTB change interrupt

0 = Disables the PORTA/PORTB change interrupt

bit 2 T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 regis ter has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RA2/INT External Interrupt Flag bit

1 = The RA2/INT external interrupt occurred (must be cleared in software)

0 = The RA2/INT external interrupt did not occur

bit 0 RABIF: PORTA/PORTB Change Interrupt Flag bit

1 = When at least o ne of the PORTA or PORTB general purpose I/O p ins cha nge d s tate (must

be cleared in software)

0 = None of the PORTA or PORTB general purpose I/O pins have changed state

(2)

(1,3)

(1, 3)

T0IF

(2)

INTF RABIF

Note 1: IOCA or IOCB register must also be enabled.

2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should

be initialized before clearing T0IF bit.

3: Includes ULPWU interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41262A-page 26 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

2.2.2.4 PIE1 Register

The PIE1 register contai ns th e in terru pt enable bits, as

shown in Register 2-4.

REGISTER 2-4: PIE1 – PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— ADIE RCIE

bit 7 bit 0

bit 7 Unimplemented: Read as ‘0’

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 5 RCIE: EUSART Receive Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 4 TXIE: EUSART Transmit Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 3 SSPIE: Synchronous Serial Port (SSP) Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 CCP1IE: CCP1 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enabled

0 = Disabled

(2)

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

(1)

TXIE

(2)

(2)

(2)

SSPIE

(1)

(2)

CCP1IE

(2)

(1)

TMR2IE

(1)

TMR1IE

Note 1: PIC16F685/PIC16F690 only.

2: PIC16F687/PIC16F689/PI C16F6 90 onl y.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 27

PIC16F685/687/689/690

2.2.2.5 PIE2 Register

The PIE2 register contai ns th e in terru pt enable bits, as

shown in Register 2-5.

REGISTER 2-5: PIE2 – PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS: 8Dh)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0

OSFIE C2IE C1IE EEIE — — — —

bit 7 bit 0

bit 7 OSFIE: Oscillator Fail Interrupt Enable bit

1 = Enabled

0 =Disabled

bit 6 C2IE: Comparator 2 Interrupt Enable bit

1 = Enables Comparator 2 interrupt

0 = Disables Comparator 2 interrupt

bit 5 C1IE: Comparator 1 Interrupt Enable bit

1 = Enables Comparator 1 interrupt

0 = Disables Comparator 1 interrupt

bit 4 EEIE: EE Write Operation Interrupt Enable bit

1 = Enabled

0 =Disabled

bit 3-0 Unimplemented: Read as ‘0’

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41262A-page 28 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

2.2.2.6 PIR1 Register

The PIR1 register contains the interrupt flag bits, as

shown in Register 2-6.

REGISTER 2-6: PIR1 – PERIPHERAL INTERRUPT REQUEST REGISTER 1 (ADDRESS: 0Ch)

U-0 R/W-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0

—

ADIF RCIF

bit 7 bit 0

bit 7 Unimplemented: Read as ‘0’

bit 6 ADIF: A/D Converter Interrupt Flag bit

1 = The A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complete

bit 5 RCIF: EUSART Receive Interrupt Flag bit

1 = The EUSART receive buffer is full (cleared by reading RCREG)

0 = The EUSART receive buffer is not full

bit 4 TXIF: EUSART Transmit Interrupt Flag bit

1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)

0 = The EUSART transmit buffer is full

bit 3 SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit

1 = The Transmission/Reception is complete (must be cleared in software)

0 = Waiting to Transmit/Receive

bit 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode

Unused in this mode

bit 1 TMR2IF: TMR2 to PR2 Interrupt Flag bit

1 = A TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = The TMR1 register overflowed (must be cleared in software)

0 = The TMR1 register did not overflow

(1)

(2)

Note: Interrupt flag bits are set when an interru pt

condition occurs, regar dless of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User

software should ensure the appropriate

interrupt flag bits are clear prior to

enabling an interrupt.

TXIF

(1)

(1)

(1)

(2)

SSPIF

(1)

CCP1IF

(1)

(2)

TMR2IF

(2)

TMR1IF

Note 1: PIC16F687/PIC16F689/PIC16F690 onl y.

2: PIC16F685/PIC16F690 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 29

PIC16F685/687/689/690

2.2.2.7 PIR2 Register

The PIR2 register contains the interrupt flag bits, as

shown in Register 2-7.

REGISTER 2-7: PIR2 – PERIPHERAL INTERRUPT REQUEST REGISTER 2 (ADDRESS: 0Dh)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0

OSFIF C2IF C1IF EEIF — — — —

bit 7 bit 0

bit 7 OSFIF: Oscillator Fail Interrupt Flag bit

1 = System oscillator failed, cloc k input ha s changed to INT OSC (must be c leared in softw are)

0 = System clock operating

bit 6 C2IF: Comparator 2 Interrupt Flag bit

1 = Comparator output (C2OUT bit) has changed (must be cleared in software)

0 = Comparator output (C2OUT bit) has not changed

bit 5 C1IF: Comparator 1 Interrupt Flag bit

1 = Comparator output (C1OUT bit) has changed (must be cleared in software)

0 = Comparator output (C1OUT bit) has not changed

bit 4 EEIF: EE Write Operation Interrupt Flag bit

1 = Write operation completed (must be cleared in software)

0 = Write operation has not completed or has not started

bit 3-0 Unimplemented: Read as ‘0’

Note: Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User

software should ensure the appropriate

interrupt flag bits are clear prior to enabling

an interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41262A-page 30 Preliminary © 2005 Microchip Technology Inc.

PIC16F685/687/689/690

2.2.2.8 PCON Register

The Power Control (PCON) register (see Register 2-8)

contains flag bit s to differentiate between a:

• Power-on Reset (POR

• Brown-out Reset (BOR)

• Watchdog Timer Reset (WDT)

• External MCLR

The PCON register also controls the Ultra Low-Power

Wake-up and software enable of the BO

REGISTER 2-8: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

bit 7-6 Unimplemented: Read as ‘0’

bit 5 ULPWUE: Ultra Low-Power Wake-up Enable bit

bit 4 SBOREN: Software BOR Enable bit

bit 3-2 Unimplemented: Read as ‘0’

bit 1 POR

bit 0 BO

)

Reset

R.

U-0 U-0 R/W-0 R/W-1 U-0 U-0 R/W-0 R/W-x

— — ULPWUE SBOREN

bit 7 bit 0

1 = Ultra Low-Power Wake-up enabled

0 = Ultra Low-Power Wake-up disabled

(1)

1 = BOR enabled

0 = BOR disabled

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

R: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

(1)

— —PORBOR

Note 1: BOREN<1:0> = 01 in the Configuration Word register for this bit to control the BOR.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

© 2005 Microchip Technology Inc. Preliminary DS41262A-page 31

PIC16F685/687/689/690

h

s

n

2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The lo w byte

comes from the PCL register, which is a readable and

writable register . The hig h byte (PC<12:8>) is not directl y

readable or writable and comes from PCLATH. On any

Reset, the PC is cleared. Figure 2-6 shows the two

situatio ns fo r t he l o ad i n g o f t h e PC . The u p pe r e x am pl e