PIC16F684

Data Sheet

14-Pin Flash-Based, 8-Bit

CMOS Microcontrollers with

nanoWatt Technology

2004 Microchip Technology Inc. Preliminary DS41202C

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digit al Millennium Copyright Act. If suc h a c t s

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is intended through suggestion only

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

No representation or warranty is given and no liability is

assumed by Microchip Technology Incorporated with respect

to the accuracy or use of such information, or infringement of

patents or other intellectual property rights arising from such

use or otherwise. Use of Microchip’s products as critical

components in life support systems is not authorized except

with express written approval by Microchip. No licenses are

conveyed, implicitly or otherwise, under any intellectual

property rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, K

EELOQ, microID, MPLAB, PIC, PICmicro, PICSTART,

PRO MATE, PowerSmart, rfPIC, and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, MXDEV, MXLAB, PICMASTER, SEEVAL,

SmartSensor and The Embedded Control Solutions Company

are registered trademarks of Microchip Technology

Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM,

dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR,

FanSense, FlexROM, fuzzyLAB, In-Circuit Serial

Programming, ICSP, ICEPIC, Migratable Memory, MPASM,

MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net,

PICLAB, PICtail, PowerCal, PowerInfo, PowerMate,

PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial,

SmartTel and Tot al Endurance are trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2004, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 quality system certification for

its worldwide headquarters, design and wafer fabrication facilities in

Chandler and Tempe, Arizona and Mountain View, California in

October 2003. The Company’s quality system processes and

procedures are for its PICmicro

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

8-bit MCUs, KEELOQ

®

code hopping

DS41202C-page ii Preliminary 2004 Microchip Technology Inc.

PIC16F684

14-Pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

High-Performance RISC CPU:

• Only 35 instructions to learn:

- All single-cycle instructions except branches

• Operating speed:

- DC – 20 MHz oscillator/clock input

- DC – 200 ns instruction cycle

• Interrupt capability

• 8-level deep hardware stack

• Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

• Precision Internal Oscillator:

- Factory calibrated to ±1%

- Software selectable frequency range of

8 MHz to 31 kHz

- Software tunable

- Two-speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for

power savings

• Power-saving Sleep mode

• Wide operating voltage range (2.0V-5.5V)

• Industrial and Extended Temperature range

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Brown-out Detect (BOD) with software control

option

• Enhanced low-current Watchdog Timer (WDT)

with on-chip oscillator (software selectable

nominal 268 seconds with full prescaler) with

software enable

• Multiplexed Master Clear with pull-up/input pin

• Programmable code protection

• High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

Low-Power Features:

• Standby Current:

- 1 nA @ 2.0V, typical

• Operating Current:

-8.5µA @ 32 kHz, 2.0V, typical

-100µA @ 1 MHz, 2.0V , typical

• Watchdog Timer Current:

-1µA @ 2.0V, typical

Peripheral Features:

• 12 I/O pins with individual direction control:

- High current source/sink for direct LED drive

- Interrupt-on-pin change

- Individually programmable weak pull-ups

- Ultra Low-power Wake-up (ULPWU)

• Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference

(CVREF) module (% of VDD)

- Comparator inputs and outputs externally

accessible

• A/D Converter:

- 10-bit resolution and 8 channels

• Timer0: 8-bit timer/counter with 8-bit

programmable prescaler

• Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode

as Timer1 oscillator if INTOSC mode

selected

• Timer2: 8-bit timer/counter with 8-bit period

register, prescaler and postscaler

• Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max resolution 12.5 ns

- Compare, max resolution 200 ns

- 10-bit PWM with 1, 2 or 4 output channels,

programmable “dead time”, max frequency

20 kHz

• In-Circuit Serial Programming

pins

TM

(ICSPTM) via two

Program

Device

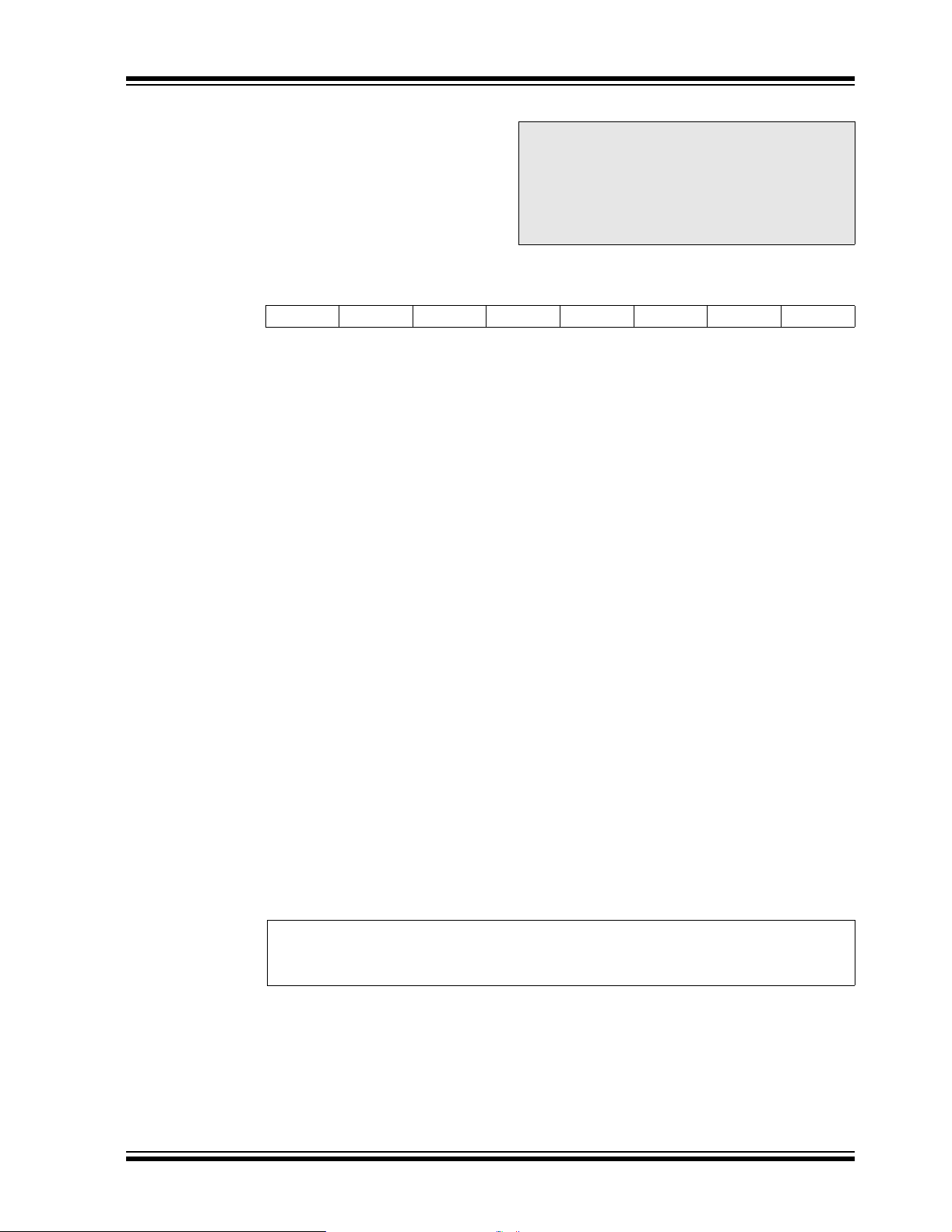

PIC16F684 2048 128 256 12 8 2 2/1

2004 Microchip Technology Inc. Preliminary DS41202C-page 1

Memory

Flash

(words)

Data Memory

SRAM

(bytes)

EEPROM

(bytes)

I/O

10-bit A/D

(ch)

Comparators

Timers

8/16-bit

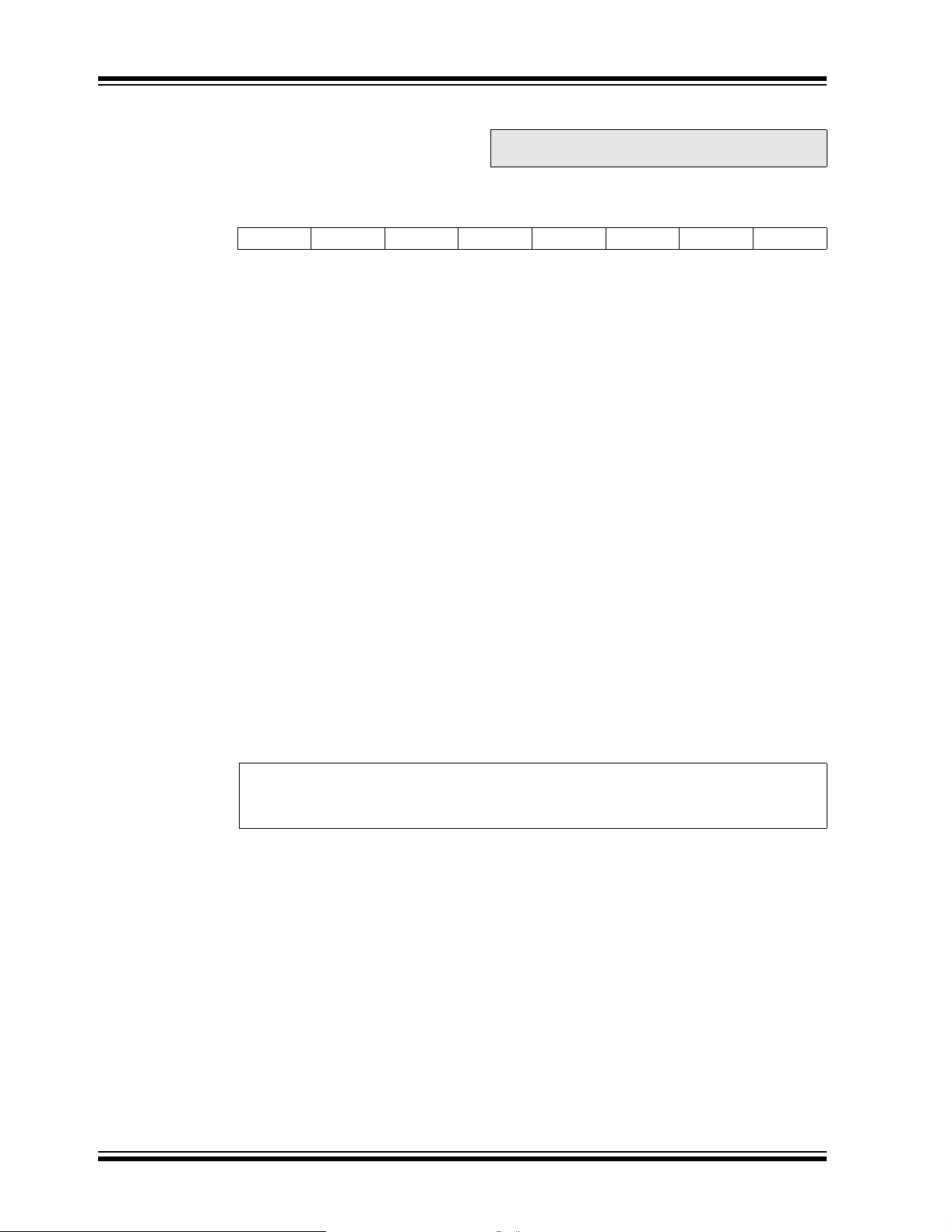

PIC16F684

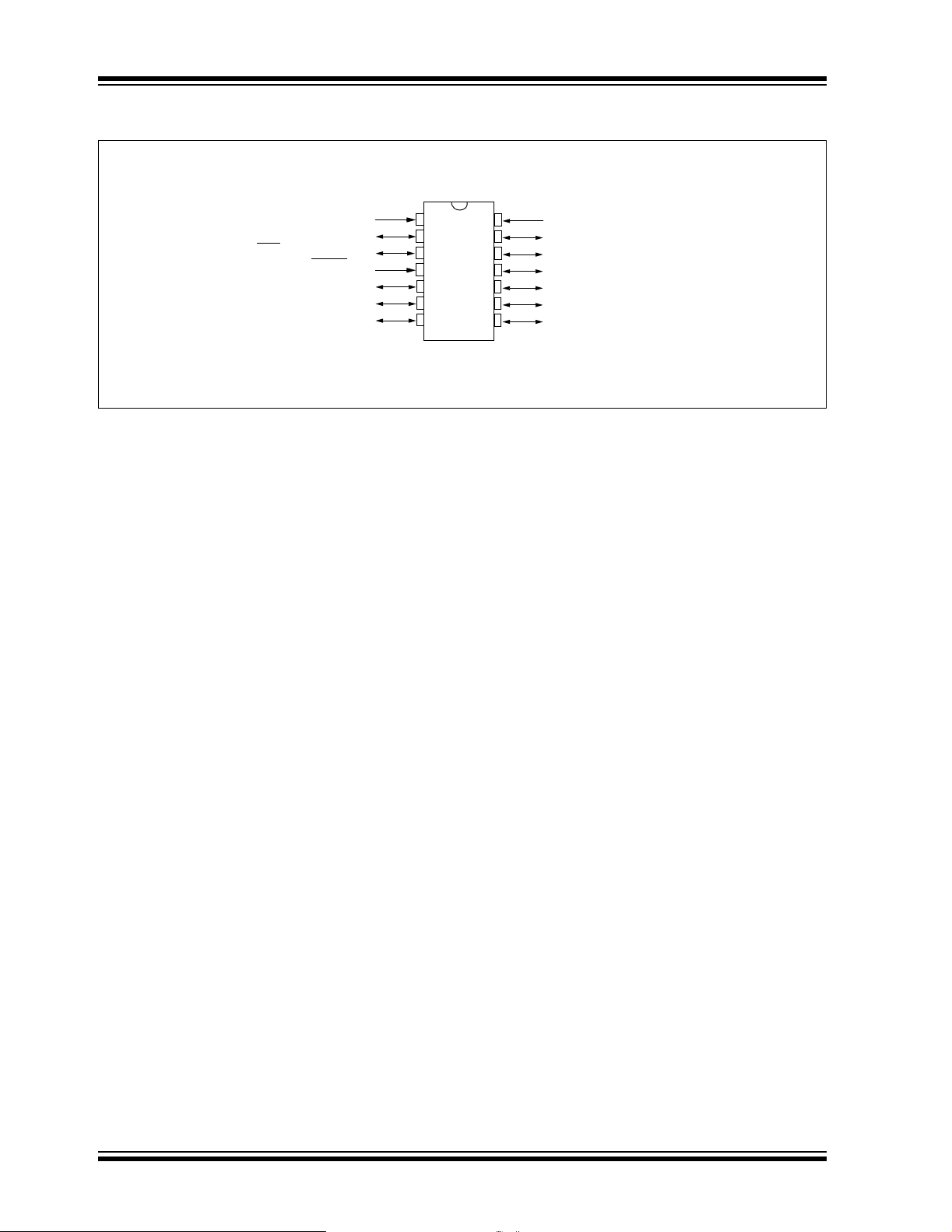

Pin Diagram

14-pin PDIP, SOIC, TSSOP

RA5/T1CKI/OSC1/CLKIN

RA4/AN3/T1G

/OSC2/CLKOUT

RA3/MCLR

RC5/CCP1/P1A

RC4/C2OUT/P1B

RC3/AN7/P1C

VDD

/VPP

1

2

3

4

5

6

7

PIC16F684

14

13

12

11

10

9

8

VSS

RA0/AN0/C1IN+/ICSPDAT/ULPWU

RA1/AN1/C1IN-/V

RA2/AN2/T0CKI/INT/C1OUT

RC0/AN4/C2IN+

RC1/AN5/C2INRC2/AN6/P1D

REF/ICSPCLK

DS41202C-page 2 Preliminary 2004 Microchip Technology Inc.

PIC16F684

Table of Contents

1.0 Device Overview......................................................................................................................................................................... 5

2.0 Memory Organization.................................................................................................................................................................. 7

3.0 Clock Sources........................................................................................................................................................................... 19

4.0 I/O Ports................................................. ................................................. .................................................................................. 31

5.0 Timer0 Module .......................................................................................................................................................................... 45

6.0 Timer1 Module with Gate Control.............................................................................................................................................. 49

7.0 Timer2 Module .......................................................................................................................................................................... 53

8.0 Comparator Module................................................................................................................................................................... 55

9.0 Analog-to-Digital Converter (A/D) Module................................................................................................................................. 63

10.0 Data EEPROM Memory.................................................. ................. ................. ........................................................................ 71

11.0 Enhanced Capture/Compare/PWM (ECCP) Module................................................................................................................. 75

12.0 Special Features of the CPU........................................... ................. ................. ................. ....................................................... 91

13.0 Instruction Set Summary......................................................................................................................................................... 111

14.0 Development Support.............................................................................................................................................................. 121

15.0 Electrical Specifications........................................................................................................................................................... 127

16.0 DC and AC Characteristics Graphs and Tables........................................................................... ........................................... 147

17.0 Packaging Information. ................. ................. ................ ................. ................. ........................................................................ 149

Appendix A: Data Sheet Revision History......................................................................................................................................... 153

Appendix B: Migrating from other PICmicro® Devices ..................................................................................................................... 153

Index ................................................................................................................................................................................................. 155

On-Line Support................................................................................................................................................................................ 159

Systems Information and Upgrade Hot Line..................................................................................................................................... 159

Reader Response............................................................................................................................................................................. 160

Product Identification System ........................................................................................................................................................... 161

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding t his publication, p lease c ontact the M arket ing Co mmunications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include

literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

2004 Microchip Technology Inc. Preliminary DS41202C-page 3

PIC16F684

NOTES:

DS41202C-page 4 Preliminary 2004 Microchip Technology Inc.

PIC16F684

1.0 DEVICE OVERVIEW

This documen t conta i ns dev ic e spec if i c in for m at i on fo r

the PIC16F684. Addition al informa tion may b e found in

the “PICmicro® Mid-Range MCU Family Reference

Manual” (DS33023), which may be obtained from your

local Microchip Sales Representative or downloaded

from the Microchip web site.

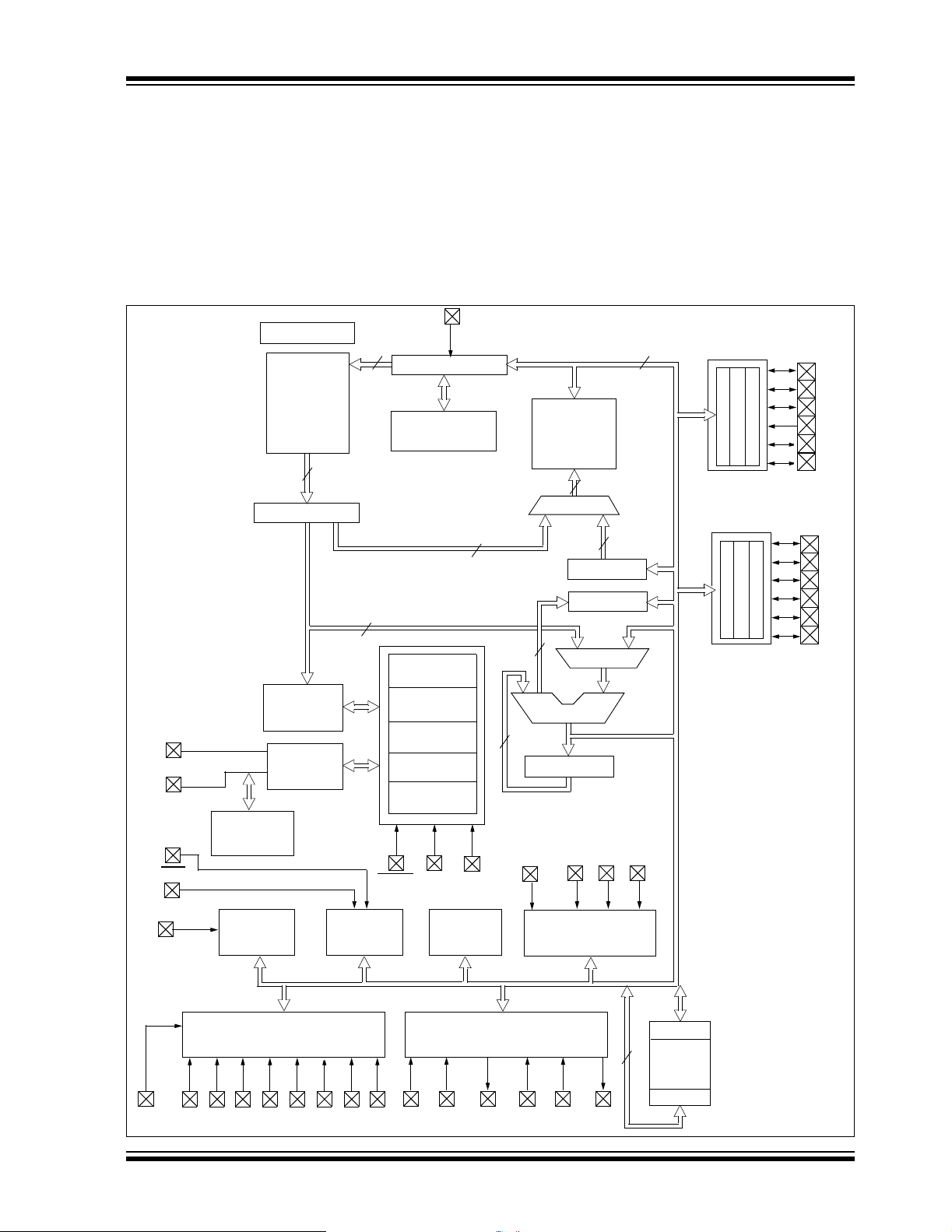

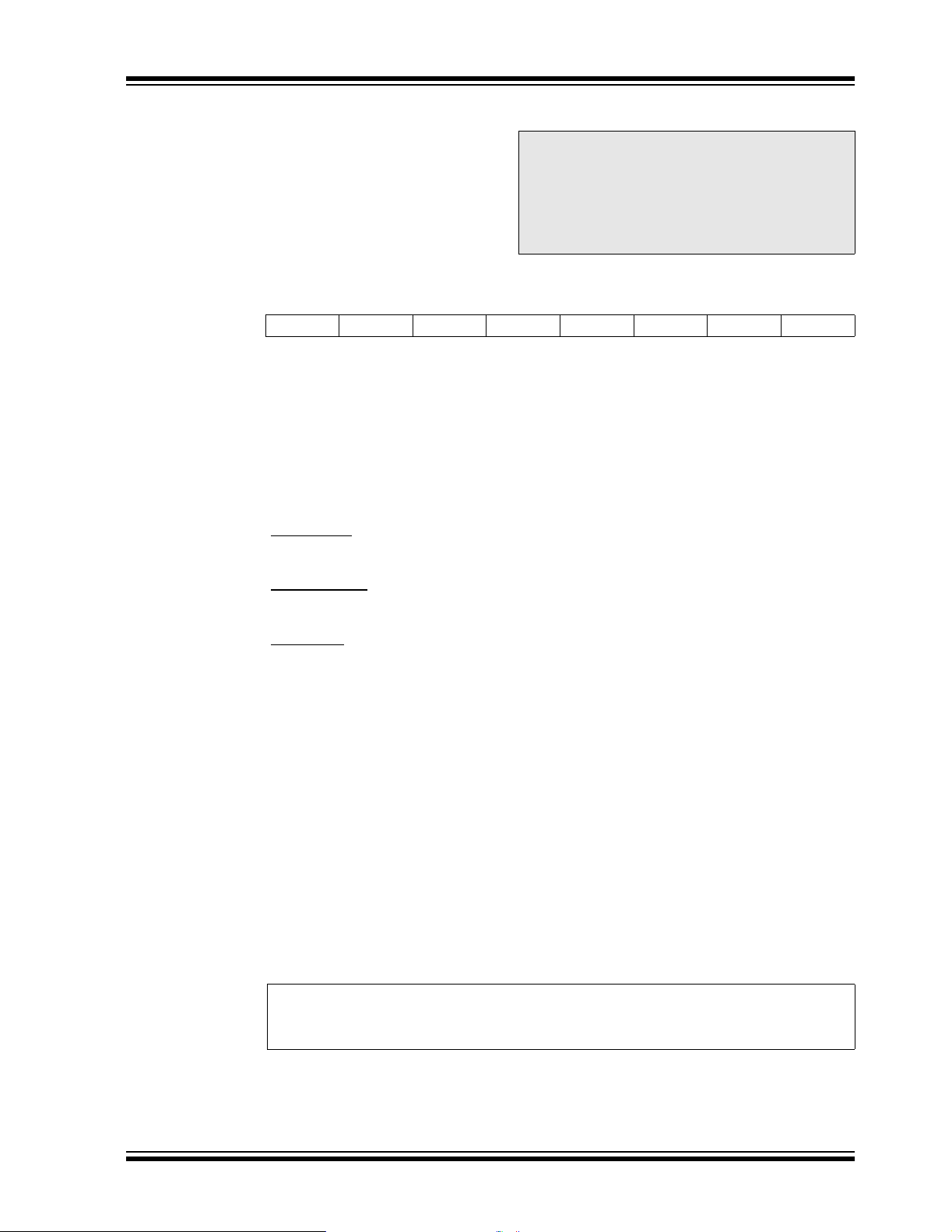

FIGURE 1-1: PIC16F684 BLOCK DIAGRAM

INT

Program Counter

8-Level Stack 128 Bytes

(13-Bit)

Addr

Direct

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Detect

VDD

MCLR

VSS

OSC1/CLKIN

OSC2/CLKOUT

T1G

Program

Bus

Internal

Oscillator

Block

Configuration

Flash

2k X 14

Program

Memory

14

Instruction Reg

Instruction

Decode &

Control

Timing

Generation

13

8

The reference manual shou ld be cons ider ed a com plementary document to this data sheet and is highly

recommended reading for a better unders tanding of the

device architecture and operation of the peripheral

modules.

The PIC16F684 is covered by this data sheet. It is

available in 14-pin PDIP, SOIC and TSSOP packages.

Figure 1-1 shows a block diagram of the PIC16F684

device. Table 1-1 shows the pinout description.

RAM Addr

7

Data Bus

Registers

3

8

CCP1/P1A

RAM

File

9

Addr MUX

8

FSR Reg

Status Reg

MUX

ALU

W Reg

P1B P1C P1D

Indirect

Addr

8

PORTA

PORTC

RA0

RA1

RA2

RA3

RA4

RA5

RC0

RC1

RC2

RC3

RC4

RC5

T1CKI

T0CKI

VREF

2004 Microchip Technology Inc. Preliminary DS41202C-page 5

AN0 AN1 AN2 AN3

Timer0 Timer1

Analog-To-Digital Converter

AN4 AN5 AN6 AN7

C1IN- C1IN+ C1OUT

Timer2

2 Analog Comparators

and Reference

C2IN- C2IN+ C2OUT

ECCP

EEDATA

256 Bytes

8

EEPROM

EEADDR

Data

PIC16F684

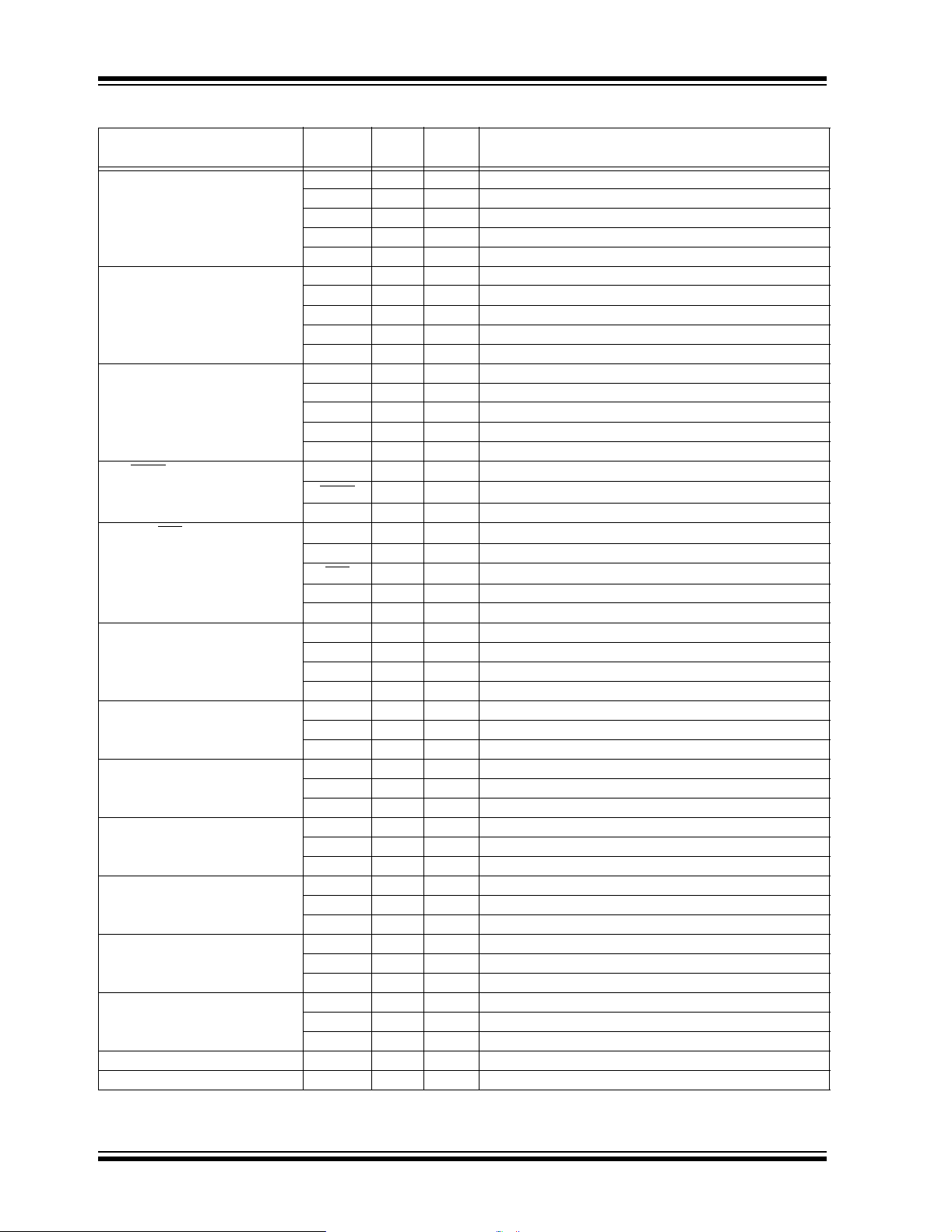

TABLE 1-1: PIC16F684 PINOUT DESCRIPTION

Name Function

RA0/AN0/C1IN+/ICSPDAT/ULPWU RA0 TTL CMOS PORTA I/O w/programmable pull-up and interrupt-on-change

AN0 AN — A/D Channel 0 input

C1IN+ AN — Comparator 1 input

ICSPDAT TTL CMOS Serial Program ming Da ta I/O

ULPWU AN — Ultra Low-power Wake-up input

RA1/AN1/C1IN-/V

RA2/AN2/T0CKI/INT/C1OUT RA2 ST CMOS PORTA I/O w/programmable pull-up and interrupt-on-change

RA3/MCLR

RA4/AN3/T1G

RA5/T1CKI/OSC1/CLKIN RA5 TTL CMOS PORTA I/O w/programmable pull-up and interrupt-on-change

RC0/AN4/C2IN+ RC0 TTL CMOS PORTC I/O

RC1/AN5/C2IN- RC1 TTL CMOS PORTC I/O

RC2/AN6/P1D RC2 TTL CMOS PORTC I/O

RC3/AN7/P1C RC3 TTL CMOS PORTC I/O

RC4/C2OUT/P1B RC4 TTL CMOS PORTC I/O

RC5/CCP1/P1A RC5 TTL CMOS PORTC I/O

SS VSS Power — Ground reference

V

DD VDD Power — Positive supply

V

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, AN = Analog input

REF/ICSPCLK RA1 TTL CMOS PORTA I/O w/programmable pull-up and interrupt-on-change

AN1 AN — A/D Channel 1 input

C1IN- AN — Comparator 1 input

REF AN — External Voltage Reference for A/D

V

ICSPCLK ST — Serial Programming Clock

AN2 AN — A/D Channel 2 input

T0CKI ST — Timer0 clock input

INT ST — External Interru p t

C1OUT — CMOS Comparator 1 output

/VPP RA3 TTL — PORTA input with interrupt-on-change

MCLR

PP HV — Programming voltage

V

/OSC2/CLKOUT RA4 TTL CMOS PORTA I/O w/programmable pull-up and interrupt-on-change

AN3 AN — A/D Channel 3 input

T1G

OSC2 — XTAL Crystal/Resonator

CLKOUT — CMOS F

T1CKI ST — Timer1 clock

OSC1 XTAL — Crystal/Resonator

CLKIN ST — Ex tern al clock input/RC oscillator connection

AN4 AN — A/D Channel 4 input

C2IN+ AN — Comparator 2 input

AN5 AN — A/D Channel 5 input

C2IN- AN — Comparator 2 input

AN6 AN — A/D Channel 6 input

P1D — CMOS PWM output

AN7 AN — A/D Channel 7 input

P1C — CMOS PWM output

C2OUT — CMOS Comparator 2 output

P1B — CMOS PWM output

CCP1 ST CMOS Capture input/Compare output

P1A — CMOS PWM output

Input

Type

Output

Type

ST — Master Clear w/internal pull-up

ST — Timer1 gate

OSC/4 output

Description

DS41202C-page 6 Preliminary 2004 Microchip Technology Inc.

PIC16F684

2.0 MEMORY ORGANIZATION

2.1 Program Memory Organization

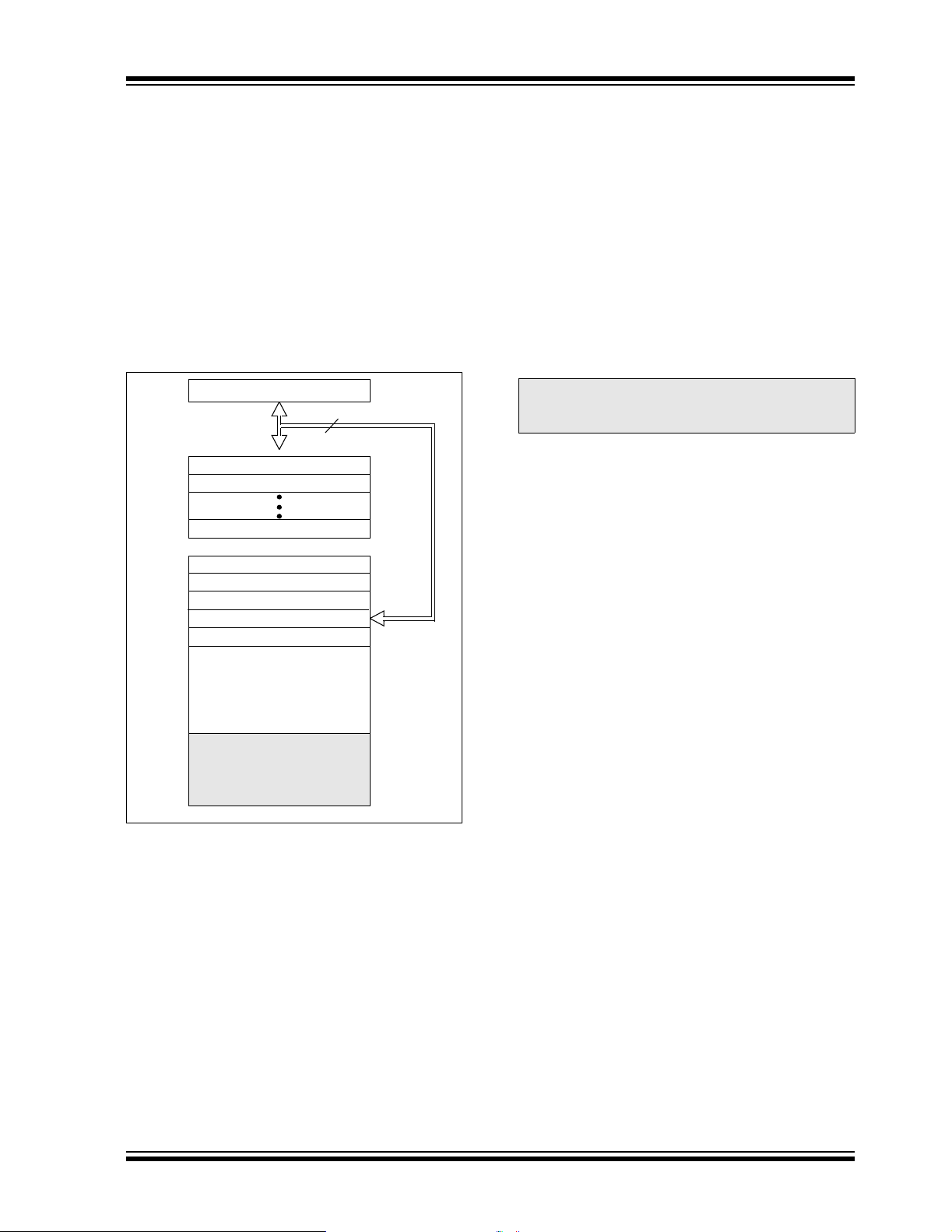

The PIC16F684 has a 13-bit program counter capable

of addressing an 8k x 14 pr ogram mem ory spac e. Only

the first 2k x 14 (0000h-07FFh) for the PIC16F684 is

physically implemented. Accessing a location above

these boundaries will cause a wrap around within the

first 2k x 14 space. The Reset vector is at 0000h and

the interrupt vector is at 0004h (see Figure 2-1).

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC16F684

PC<12:0>

CALL, RETURN

RETFIE, RETLW

Stack Level 1

Stack Level 2

Stack Level 8

Reset Vector

13

000h

2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into

two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR).

The Special Function Registers are located in the first

32 locations of each bank. Register locations 20h-7Fh

in Bank 0 and A0h-BFh in Bank 1 are General Purpose

Registers, implemented as static RAM. Register

locations F0h-FFh in Bank 1 point to addresses

70h-7Fh in Bank 0. All other RAM is unimplemented

and returns ‘0’ when re ad. RP0 (Status<5>) is t he bank

select bit.

RP0 = 0: → Bank 0 is selected

RP0 = 1: → Bank 1 is selected

Note: The IRP and RP1 bits Status<7:6> are

reserved and should always be

maintained as ‘0’s.

Interrupt Vector

On-chip Program

Memory

0004

0005

07FFh

0800h

1FFFh

2004 Microchip Technology Inc. Preliminary DS41202C-page 7

PIC16F684

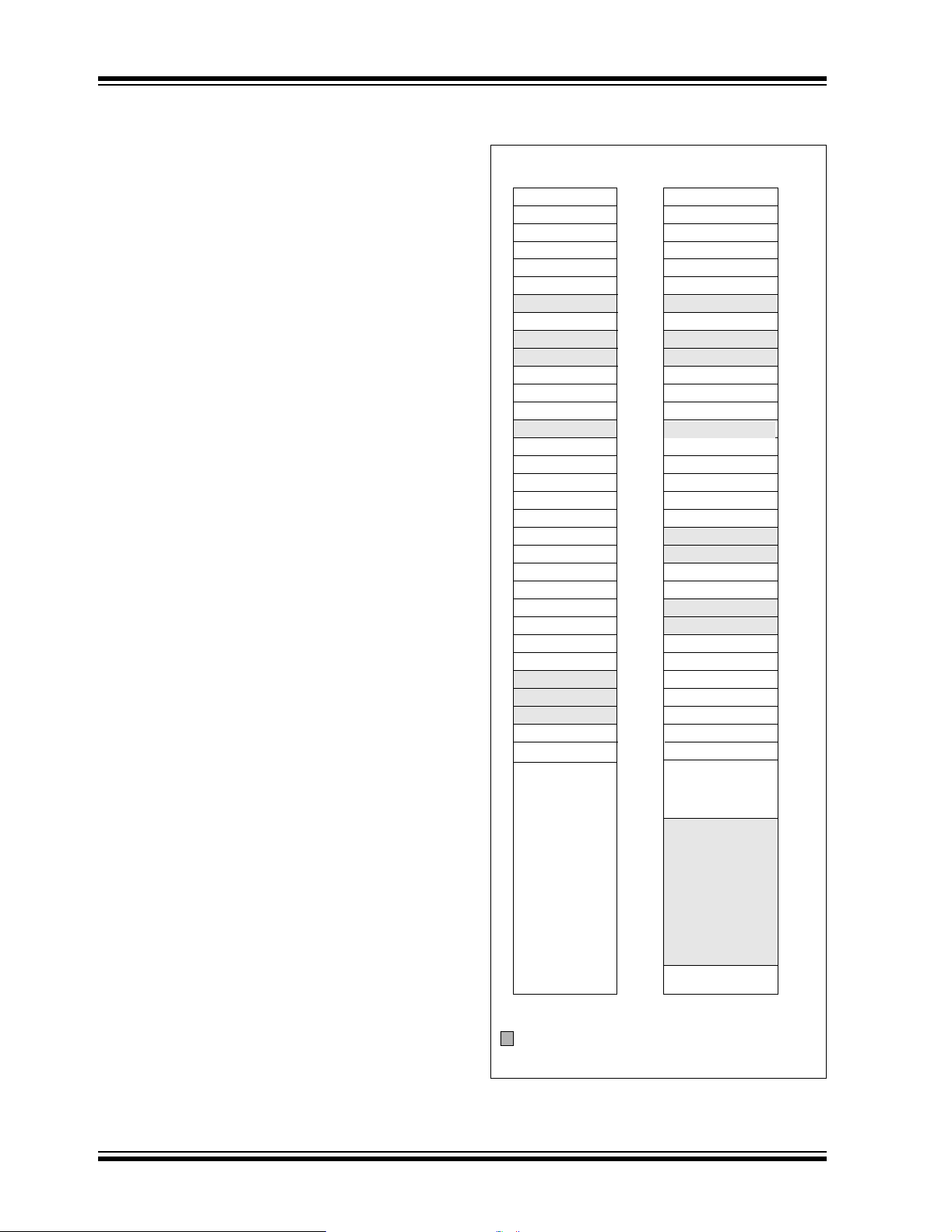

2.2.1 GENERAL PURPOSE REGISTER

FILE

The register file is organized as 128 x 8 in the

PIC16F684. Each register is accessed, either directly

or indirectly, through the File Select Register (FSR)

(see Section 2.4 “Indirect Addressing, INDF and

FSR Registers”).

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by

the CPU and peripheral functions for controlling the

desired operation of the device (see Table 2-1). These

registers are static RAM.

The special re gisters can be classifi ed into two sets:

core and peripheral. The Special Function Registers

associated with the “c ore” are des cribed in this sect ion.

Those related to the operation of the peripheral

features are described in the section of that peripheral

feature.

FIGURE 2-2: DATA MEMORY MAP OF

THE PIC16F684

File

Address

TMR0

PCL

FSR

PIR1

TMR2

(1)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

Indirect Addr.

OPTION_REG

STATUS

TRISA

PCLATH

INTCON

PCON

OSCCON

OSCTUNE

ANSEL

PR2

WPUA

EEDAT

EEADR

EECON1

EECON2

ADRESL

ADCON1

General

Purpose

Registers

32 Bytes

Indirect Addr.

STATUS

PORTA

PORTC

PCLATH

INTCON

TMR1L

TMR1H

T1CON

T2CON

CCPR1L

CCPR1H

CCP1CON

PWM1CON

ECCPAS

WDTCON

CMCON0 VRCON

CMCON1

ADRESH

ADCON0

General

Purpose

Registers

96 Bytes

PCL

FSR

TRISC

PIE1

IOCA

File

Address

(1)

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

(1)

9Dh

9Eh

9Fh

A0h

BFh

F0h

FFh

BANK 0

ACCESSES 70h-7Fh

7Fh

BANK 1

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

DS41202C-page 8 Preliminary 2004 Microchip Technology Inc.

PIC16F684

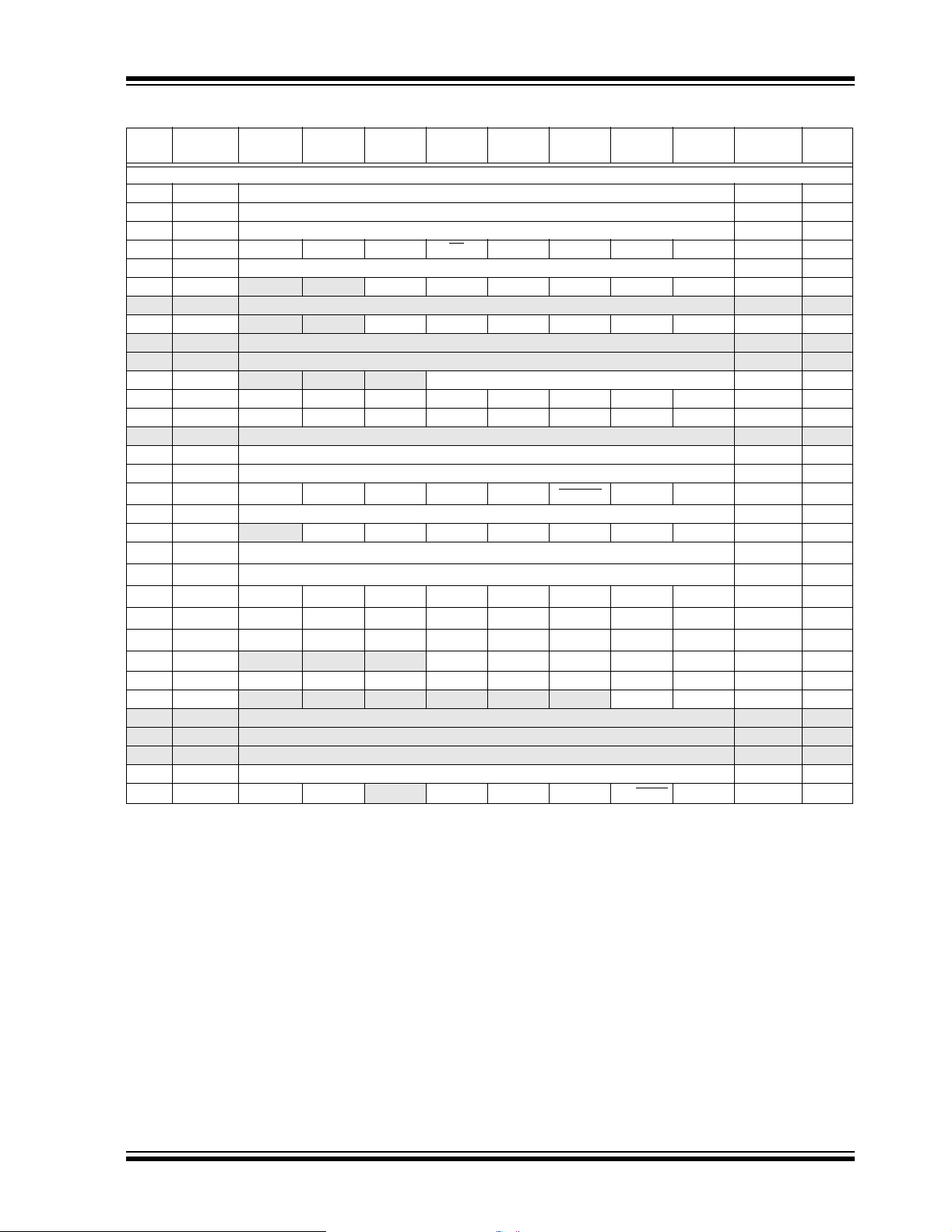

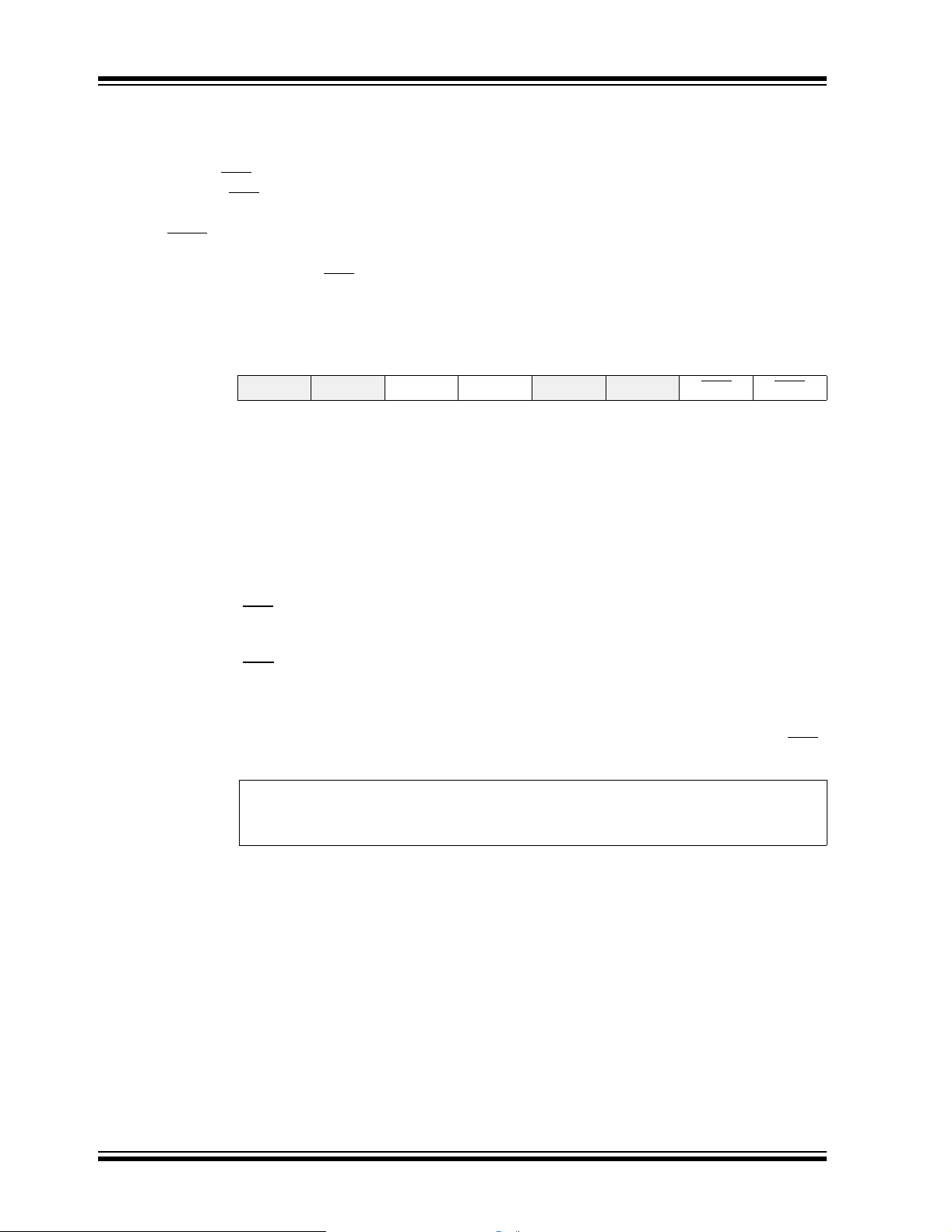

TABLE 2-1: PIC16F684 SPECIAL REGISTERS SUMMARY BANK 0

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 17, 99

01h TMR0 Timer0 Module’s register xxxx xxxx 45, 99

02h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 17, 99

03h STATUS IRP

04h FSR Indirect Data Memory Address Pointer xxxx xxxx 17, 99

05h PORTA

06h — Unimplemented — —

07h PORTC

08h — Unimplemented — —

09h — Unimplemented — —

0Ah PCLATH

0Bh INTCON GIE PEIE T0IE INTE RAIE T0IF INTF RAIF 0000 0000 13, 99

0Ch PIR1

0Dh — Unimplemented — —

0Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 xxxx xxxx 49, 99

0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 xxxx xxxx 49, 99

10h T 1CON T1GINV TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

11h

TMR2 Timer2 Module register 0000 0000 53, 99

12h

T2CON — TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 53, 99

13h

CCPR1L Capture/Compare/PWM Register 1 Low Byte

14h

CCPR1H Capture/Compare/PWM Register 1 High Byte

15h

CCP1CON P1M1 P1M0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0

16h

PWM1CON PRSEN PDC6 PDC5 PDC4 PDC3 PDC2 PDC1 PDC0

17h

ECCPAS ECCPASE ECCPAS2 ECCPAS1 ECCPAS0 PSSAC1 PSSAC0 PSSBD1 PSSBD0

18h WDTCON

19h CMCON0 C2OUT C1OUT

1Ah CMCON1

1Bh — Unimplemented — —

1Ch — Unimplemented — —

1Dh — Unimplemented — —

1Eh ADRESH Most Significant 8 bits of the left shifted A/D result or 2 bits of right shifted result xxxx xxxx 65, 99

1Fh ADCON0 ADFM VCFG

(1)

— — RA5 RA4 RA3 RA2 RA1 RA0 --xx xxxx 31, 99

— — RC5 RC4 RC3 RC2 RC1 RC0 --xx xxxx 40, 99

— — — Write Buffer for upper 5 bits of Program Counter ---0 0000 17, 99

EEIF ADIF CCP1IF C2IF C1IF OSFIF TMR2IF TMR1IF 0000 0000 15, 99

— — —

— — — — — — T1GSS C2SYNC ---- --10 59, 99

RP1

(1)

RP0 TO PD Z DC C 0001 1xxx 11, 99

TMR1CS TMR1ON

WDTPS3 WDTPS2 WDTPS1 WDTPS0 SWDTEN ---0 1000 106, 99

C2INV C1INV CIS CM2 CM1 CM0 0000 0000 55, 99

— CHS2 CHS1 CHS0 GO/DONE ADON

Legend: — = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded =

unimplemented

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

Value on

POR, BOD

0000 0000 51, 99

XXXX XXXX 75, 99

XXXX XXXX 75, 99

0000 0000 75, 99

0000 0000 85, 99

0000 0000 86, 99

00-0 0000 66, 99

Page

2004 Microchip Technology Inc. Preliminary DS41202C-page 9

PIC16F684

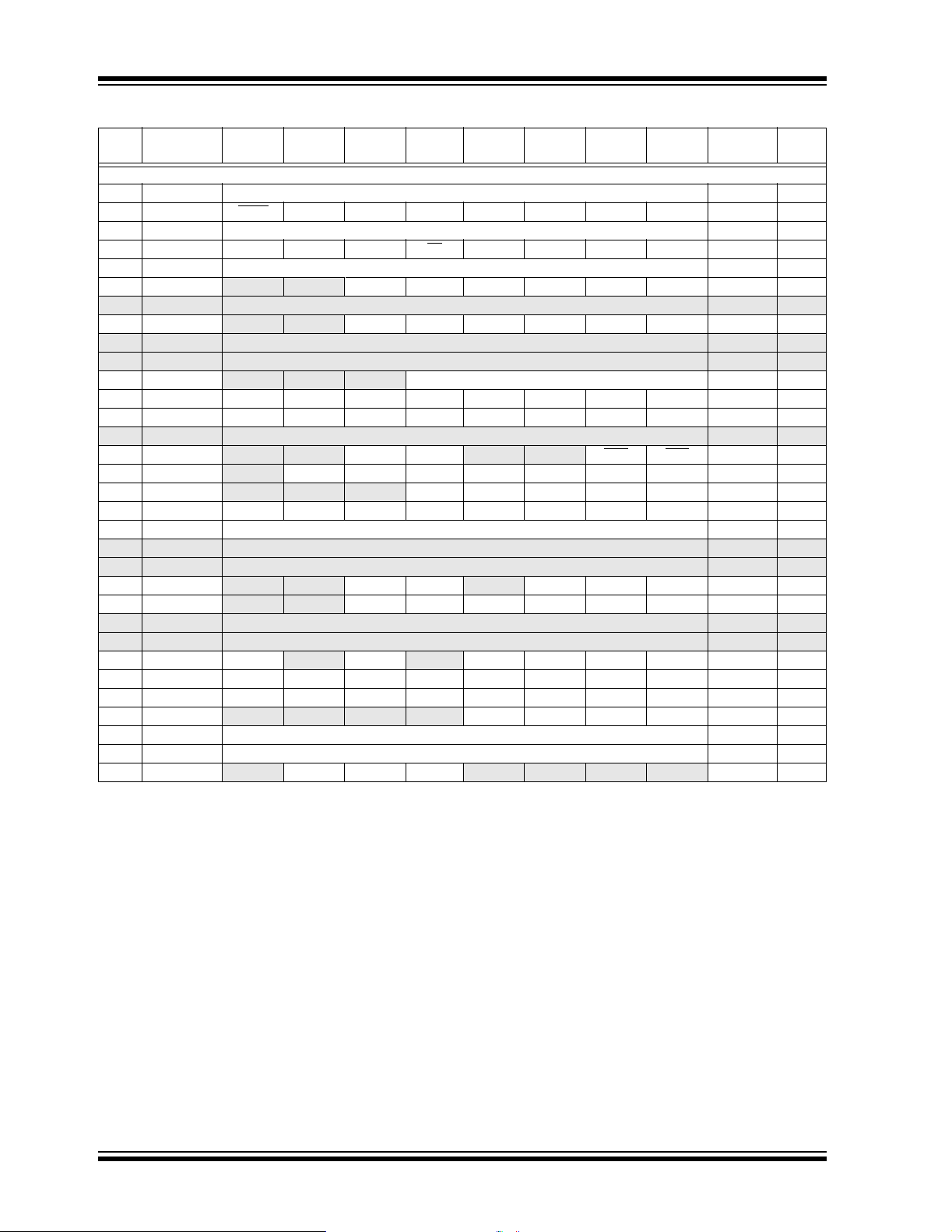

TABLE 2-2: PIC16F684 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 1

80h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 17, 99

81h OPTION_REG RAPU

82h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 17, 99

83h STATUS IRP

84h FSR Indirect Data Memory Address Pointer xxxx xxxx 17, 99

85h TRISA

86h — Unimplemented — —

87h TRISC

88h — Unimplemented — —

89h — Unimplemented — —

8Ah PCLATH

8Bh INTCON GIE PEIE T0IE INTE RAIE T0IF INTF RAIF 0000 0000 13, 99

8Ch PIE1 EEIE ADIE CCP1IE C2IE C1IE OSFIE TMR2IE TMR1IE 0000 0000 14, 99

8Dh — Unimplemented — —

8Eh PCON

8Fh OSCCON

90h OSCTUNE

91h ANSEL ANS7 ANS6 ANS5 ANS4 ANS3 ANS2 ANS1 ANS0 1111 1111 65, 99

92h PR2 Timer2 Module P erio d Re gis te r 1111 1111 53, 99

93h — Unimplemented — —

94h — Unimplemented — —

95h WPUA

96h IOCA

97h — Unimplemented — —

98h — Unimplemented — —

99h VRCON VREN

9Ah EEDAT EEDAT7 EEDAT6 EEDAT5 EEDAT4 EEDAT3 EEDAT2 EEDAT1 EEDAT0 0000 0000 71, 100

9Bh EEADR EEADR7 EEADR6 EEADR5 EEADR4 EEADR3 EEADR2 EEADR1 EEADR0 0000 0000 71, 100

9Ch EECON1

9Dh EECON2 EEPROM Control Register 2 (not a physical register) ---- ---- 72, 100

9Eh ADRESL Least Significant 2 bits of the left shifted result or 8 bits of the right shifted result xxxx xxxx 65, 100

9Fh ADCON1

Legend: — = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

(3)

2: OSTS bit OSCCON <3> reset to ‘0’ with Dual Speed Start-up and LP, HS or XT selected as the oscillator.

3: RA3 pull-up is enabled when MCLRE is ‘1’ in the Configuration Word register.

— — TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 --11 1111 32, 99

— — TRISC5 TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 --11 1111 43, 99

— — — Write Buffer for upper 5 bits of Program Counter ---0 0000 17, 99

— — ULPWUE SBODEN — —PORBOD --01 --qq 16, 99

— IRCF2 IRCF1 IRCF0 OSTS

— — — TUN4 TUN3 T UN2 TUN1 TUN0 ---0 0000 23, 99

— — WPUA5 WPUA4 — WPUA2 WPUA1 WPUA0 --11 -111 32, 100

— — IOCA5 IOCA4 IOCA3 IOCA2 IOCA1 IOCA0 --00 0000 33, 100

— — — — WRERR WREN WR RD ---- x000 72, 100

— ADCS2 ADCS1 ADCS0 — — — — -000 ---- 66, 100

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 12, 99

(1)

(1)

RP1

—VRR— VR3 VR2 VR1 VR0 0-0- 0000 62, 100

RP0 TO PD Z DC C 0001 1xxx 11, 99

(2)

HTS LTS SCS -110 x000 29, 99

Value on

POR, BOD

Page

DS41202C-page 10 Preliminary 2004 Microchip Technology Inc.

PIC16F684

2.2.2.1 Status Register

The Status register, shown in Register2-1, contains:

• the arithmetic status of the ALU

• the Reset status

• the bank select bits for data memory (SRAM)

The Status register can be the destination for any

instruction, like any other register. If the Status register

is the destination for an instruction that affects the Z,

DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the

device logic. Furthermore, the TO

writable. Therefore, the result of an instruction with the

Status register as destination may be different than

intended.

and PD bits are not

For example, CLRF STATUS, will c lea r the up per three

bits and set the Z bit. Thi s leav es the Status register a s

‘000u u1uu’ (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

Stat us register , beca use these instru ctions do not af fect

any Status bits. For other instructions not affecting any

Status bits, see the “Instruction Set Summary”.

Note 1: Bits IRP and RP1 (Status<7:6>) are not

used by the PIC16F684 and should be

maintained as clear. Use of these bits is

not recommended, since this may affect

upward compatibility with future products.

2: The C and DC bits operate as a Borrow

and Digit Borrow out bit, respectively, in

subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS – STATUS REGISTER (ADDRESS: 03h OR 83h)

Reserved Reserved R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO PD Z DC C

bit 7 bit 0

bit 7 IRP: This bit is reserved and should be maintained as ‘0’

bit 6 RP1: This bit is reserved and should be maintained as ‘0’

bit 5 RP0: Register Bank Select bit (used for direct addressing)

1 = Bank 1 (80h – FFh)

0 = Bank 0 (00h – 7Fh)

bit 4 TO

bit 3 PD: Power-down bit

bit 2 Z: Zero bit

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

bit 0 C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

: Time-out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

For borrow ,

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

the polarity is reversed.

Note 1: For borrow,

complement of the second operand. For rotate (RRF, RLF) instructions, this bit is

loaded with either the high-order or low-order bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2004 Microchip Technology Inc. Preliminary DS41202C-page 11

the polarity is reversed. A subtraction is executed by adding the two’s

PIC16F684

2.2.2.2 Option Register

The Option register is a readable and writable register,

which contains various control bits to configure:

• TMR0/WDT prescaler

• External RA2/INT interrupt

•TMR0

• Weak pull-ups on PORTA

REGISTER 2-2: OPTION_REG – OPTION REGISTER (ADDRESS: 81h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RAPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

Note: To achieve a 1:1 prescaler assignment for

TMR0, assign the prescaler to the WDT by

setting PSA bit to ‘1’ (OPTION_REG<3>).

See Section 5.4 “Prescaler”.

bit 7 RAPU

: PORTA Pull-up Enable bit

1 = PORTA pull-ups are disabled

0 = PORTA pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RA2/INT pin

0 = Interrupt on falling edge of RA2/INT pin

bit 5 T0CS: TMR0 Clock Source Sele ct bit

1 = Transition on RA 2/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA2/T0CKI pin

0 = Increment on low-to-high transition on RA2/T0CKI pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

BIT VALUE TMR0 RATE WDT RAT E

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41202C-page 12 Preliminary 2004 Microchip Technology Inc.

PIC16F684

2.2.2.3 INTCON Register

The INTCON register is a readable and writable

register , which c ontains the various en able and fl ag bit s

for TMR0 register overflow, PORTA change and

external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interr upt

condition occurs, regard less of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User

software should ensure the appropriate

interrupt flag bits are clear prior to

enabling an interrupt.

REGISTER 2-3: INTCON – INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh OR 8Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

GIE PEIE T0IE INTE RAIE T0IF INTF RAIF

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interru pts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4 INTE: RA2/INT External Interrupt Enable bit

1 = Enables the RA2/INT external interrupt

0 = Disables the RA2/INT external interrupt

bit 3 RAIE: PORTA Change Interrupt Enable bit

1 = Enables the PORTA change interrupt

0 = Disables the PORTA change interrupt

bit 2 T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 regis ter has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RA2/INT External Interrupt Flag bit

1 = The RA2/INT external interrupt occurred (must be cleared in software)

0 = The RA2/INT external interrupt did not occur

bit 0 RAIF: PORTA Change Interrupt Flag bit

1 = When at least one of the PORTA <5:0> pins changed state (must be cleared in software)

0 = None of the PORTA <5:0> pins have changed state

(1)

(2)

Note 1: IOCA register must also be enabled.

2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should

be initialized before clearing T0IF bit.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2004 Microchip Technology Inc. Preliminary DS41202C-page 13

PIC16F684

2.2.2.4 PIE1 Register

The PIE1 register contai ns th e in terru pt enable bits, as

shown in Register 2-4.

REGISTER 2-4: PIE1 – PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

EEIE ADIE CCP1IE C2IE C1IE OSFIE TMR2IE TMR1IE

bit 7 bit 0

bit 7 EEIE: EE Write Complete Interrupt Enable bit

1 = Enables the EE write complete interrupt

0 = Disables the EE write complete interrupt

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D converter interrupt

0 = Disables the A/D converter interrupt

bit 5 CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 4 C2IE: Comparator 2 Interrupt Enable bit

1 = Enables the Comparator 2 interrupt

0 = Disables the Comparator 2 interrupt

bit 3 C1IE: Comparator 1 Interrupt Enable bit

1 = Enables the Comparator 1 interrupt

0 = Disables the Comparator 1 interrupt

bit 2 OSFIE: Oscillator Fail Interrupt Enable bit

1 = Enables the oscillator fail interrupt

0 = Disables the oscillator fail interr upt

bit 1 TMR2IE: Timer2 to PR2 Match Interrupt Enable bit

1 = Enables the Timer2 to PR2 match interrupt

0 = Disables the Timer2 to PR2 match interrupt

bit 0 TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt

0 = Disables the Timer1 overflow interrupt

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41202C-page 14 Preliminary 2004 Microchip Technology Inc.

PIC16F684

2.2.2.5 PIR1 Register

The PIR1 register contains the interrupt flag bits, as

shown in Register 2-5.

REGISTER 2-5: PIR1 – PERIPHERAL INTERRUPT REQUEST REGISTER 1 (ADDRESS: 0Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

EEIF ADIF CCP1IF C2IF C1IF OSFIF TMR2IF TMR1IF

bit 7 bit 0

bit 7 EEIF: EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation has not completed or has not been started

bit 6 ADIF: A/D Interrupt Flag bit

1 = A/D conversion complete

0 = A/D conversion has not completed or has not been started

bit 5 CCP1IF: CCP1 Interrupt Flag bit

Capture mod

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 regi ster capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode

Unused in this mode

bit 4 C2IF: Comparator 2 Interrupt Flag bit

1 = Comparator 2 output has changed (must be cleared in software)

0 = Comparator 2 output has not changed

bit 3 C1IF: Comparator 1 Interrupt Flag bit

1 = Comparator 1 output has changed (must be cleared in software)

0 = Comparator 1 output has not changed

bit 2 OSFIF: Oscillator Fail Interrupt Flag bit

1 = System oscilla tor failed, clock input h as ch ang ed to INTOSC (must be cle are d i n s oftw a re)

0 = System clock operating

bit 1 TMR2IF: Timer2 to PR2 Match Interrupt Flag bit

1 = Timer2 to PR2 match occurred (must be cleared in software)

0 = Timer2 to PR2 match has not occurred

bit 0 TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = Timer1 register overflowed (must be cleared in software)

0 = Timer1 has not overflowed

e:

:

Note: Interrupt flag bits are set w hen an in terrupt

condition occurs, regar dless of the st ate of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User

software should ensure the appropriate

interrupt flag bits are clear prior to

enabling an interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2004 Microchip Technology Inc. Preliminary DS41202C-page 15

PIC16F684

2.2.2.6 PCON Register

The Power Control (PCON) register (see Table 12-2)

contains flag bit s to differentiate between a:

• Power-on Reset (POR

• Brown-out Detect (BOD)

• Watchdog Timer Reset (WDT)

• External MCLR

The PCON register also controls the ultra low-power

wake-up and software enable of the BOD

The PCON register bits are shown in Register 2-6.

REGISTER 2-6: PCON – POWER CONTROL REGISTER (ADDRESS: 8Eh)

bit 7-6 Unimplemented: Read as ‘0’

bit 5 ULPWUE: Ultra Low-Power Wake-up Enable bit

bit 4 SBODEN: Software BOD Enable bit

bit 3-2 Unimplemented: Read as ‘0’

bit 1 POR

bit 0 BOD

)

Reset

.

U-0 U-0 R/W-0 R/W-1 U-0 U-0 R/W-0 R/W-x

— — ULPWUE SBODEN — —PORBOD

bit 7 bit 0

1 = Ultra low-power wake-up enabled

0 = Ultra low-power wake-up disabled

(1)

1 = BOD enabled

0 = BOD disabled

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

: Brown-out Detect Status bit

1 = No Brown-out Detect occurred

0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

Note 1: BODEN<1:0> = 01 in the Configuration W ord register for this bit to control the BO D

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS41202C-page 16 Preliminary 2004 Microchip Technology Inc.

.

PIC16F684

h

>

s

n

2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte

comes from the PCL register, which is a readable and

writable register. The high byte (PC<12:8>) is not

directly readable or writable and comes from PCLATH .

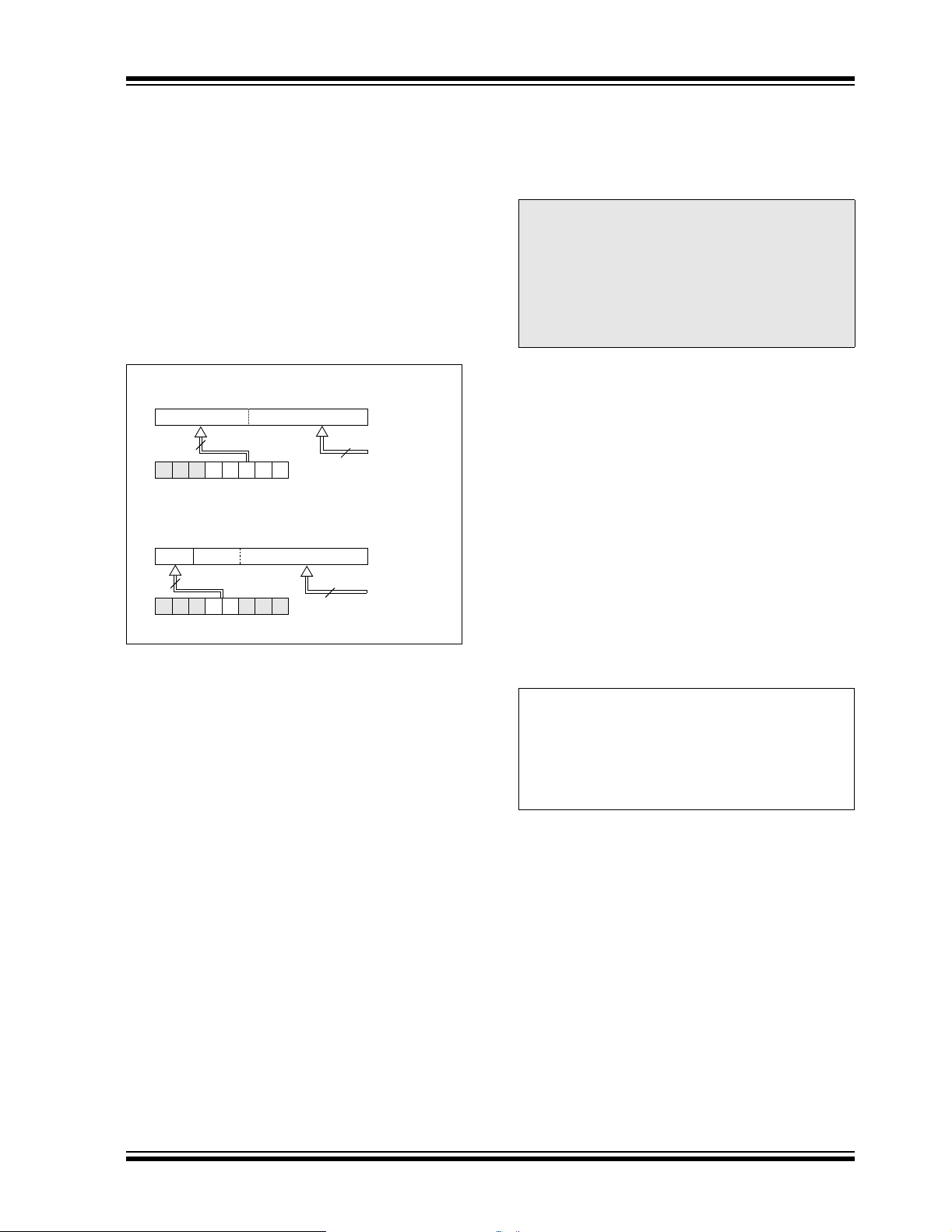

On any Reset, the PC is cleared. Figure 2-3 shows the

two situations for the loading of the PC. The upper

example in Figure 2-3 shows how the PC is loaded on a

write to PCL (PCLATH<4:0> → PCH). The lower example in Figure 2-3 shows how the PC is loaded during a

CALL or GOTO instruction (PCLATH<4:3> → PCH).

FIGURE 2-3: LOADING OF PC IN

DIFFERENT SITUATIONS

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

PCLATH

8

11

2.3.1 COMPUTED GOTO

A computed GOTO is accomplish ed by adding an offset

to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care

should be exercise d i f the t able loca tio n cros ses a PCL

memory boundary (each 256-byte block). Refer to the

Application Note AN556, “Implementing a Table Read”

(DS00556).

Instruction wit

PCL a

Destinatio

ALU Result

GOTO, CALL

OPCODE <10:0

The stack operat es as a circular buf fer . This means th at

after the stack has been PUSHed eight times, the ninth

push overwrites th e valu e that was s tored fro m the firs t

push. The tenth pus h ov erwr i tes the se co nd push (and

so on).

Note 1: There are no Status bits to indicate stack

overflow or stack underflow conditions.

2: There are no instructions/mnemonics

called PUSH or POP. These are actions

that occur from the execution of the

CALL, RETURN, RETLW and RETFIE

instructions or the vectoring to an

interrupt address.

2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physica l register . Addr essing

the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF

register. Any instruction using the INDF register

actually accesses data pointed to by the File Select

Register (FSR). Reading INDF itself indirectly will

produce 00h. Writing to the INDF register indirectly

results in a no operation (although Status bits may be

affected). An effective 9-bit address is obtained by

concatenating the 8-bit FSR and the IRP bit

(Status<7>), as shown in Figure2-4.

A simple program to clear RAM location 20h-2Fh using

indirect addressing is shown in Example 2-1.

EXAMPLE 2-1: INDIRECT ADDRESS ING

MOVLW0x20;initialize pointer

MOVWFFSR ;to RAM

NEXT CLRFINDF ;clear INDF register

INCFFSR ;INC POINTER

BTFSSFSR,4;all done?

GOTONEXT ;no clear next

CONTINUE ;yes continue

2.3.2 STACK

The PIC16F684 Family has an 8-level x 13-bit wide

hardware s tack (see Figure 2-1). The stack space is

not part of either program or data space and the stack

pointer is n ot re ad a bl e or wr i tabl e. T h e P C i s P U SHed

onto the s tack w hen a CALL instruction is executed or

an interrupt causes a branch. The stack is POPed in

the event of a RETURN, RETLW or a RETFIE

instruction execution. PCLATH is not affected by a

PUSH or POP operation.

2004 Microchip Technology Inc. Preliminary DS41202C-page 17

PIC16F684

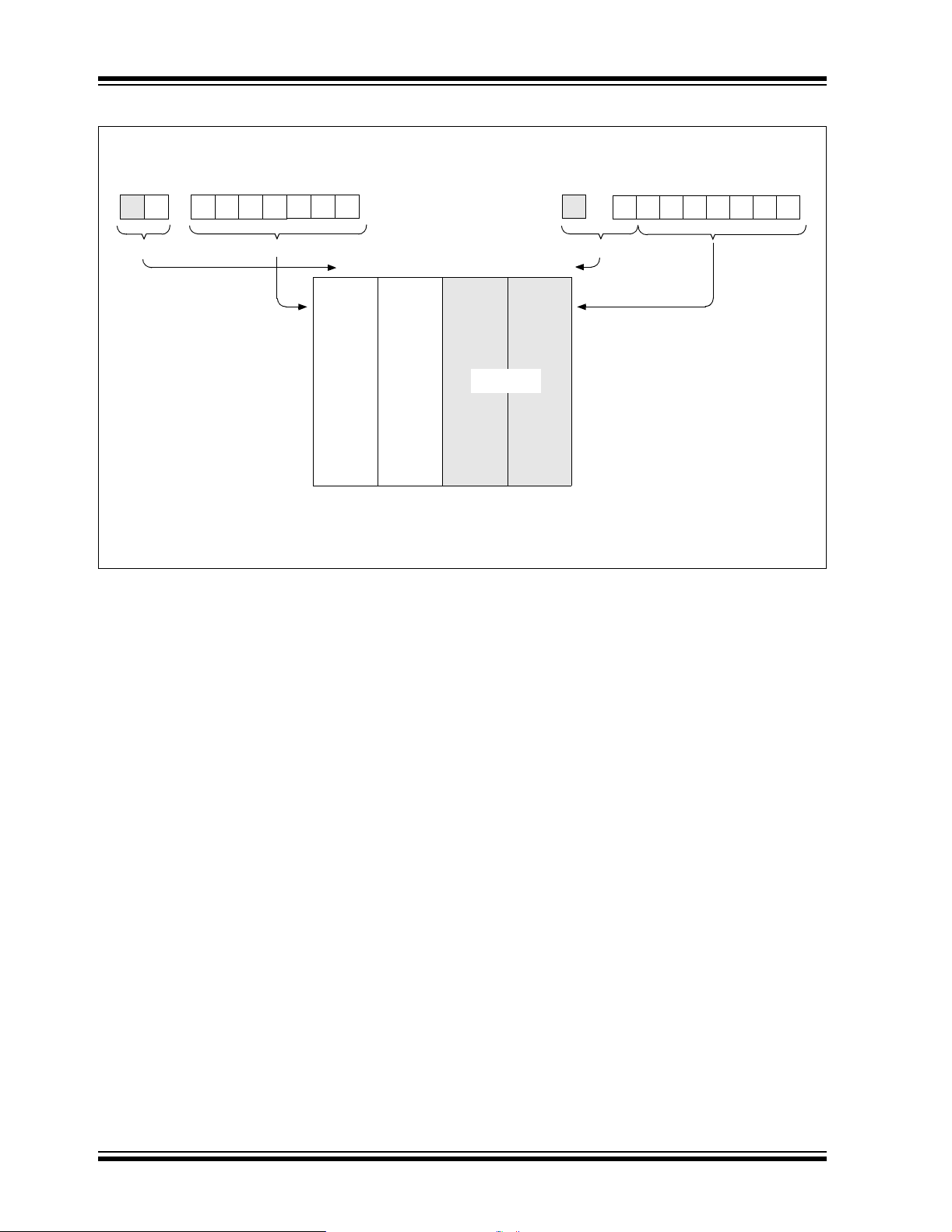

FIGURE 2-4: DIRECT/INDIRECT ADDRESSING PIC16F684

RP1

(1)

RP0 6

From Opcode

0

IRP

Indirect AddressingDirect Addressing

(1)

7

File Select Register

0

Bank Select Location Select

00h

Data

Memory

7Fh

For memory map detail, see Figure 2-2.

Note 1: The RP1 and IRP bits are reserved; always maintain these bits clear.

00 01 10 11

NOT USED

Bank 0 Bank 1 B ank 2 Bank 3

Bank Select

180h

1FFh

Location Select

DS41202C-page 18 Preliminary 2004 Microchip Technology Inc.

PIC16F684

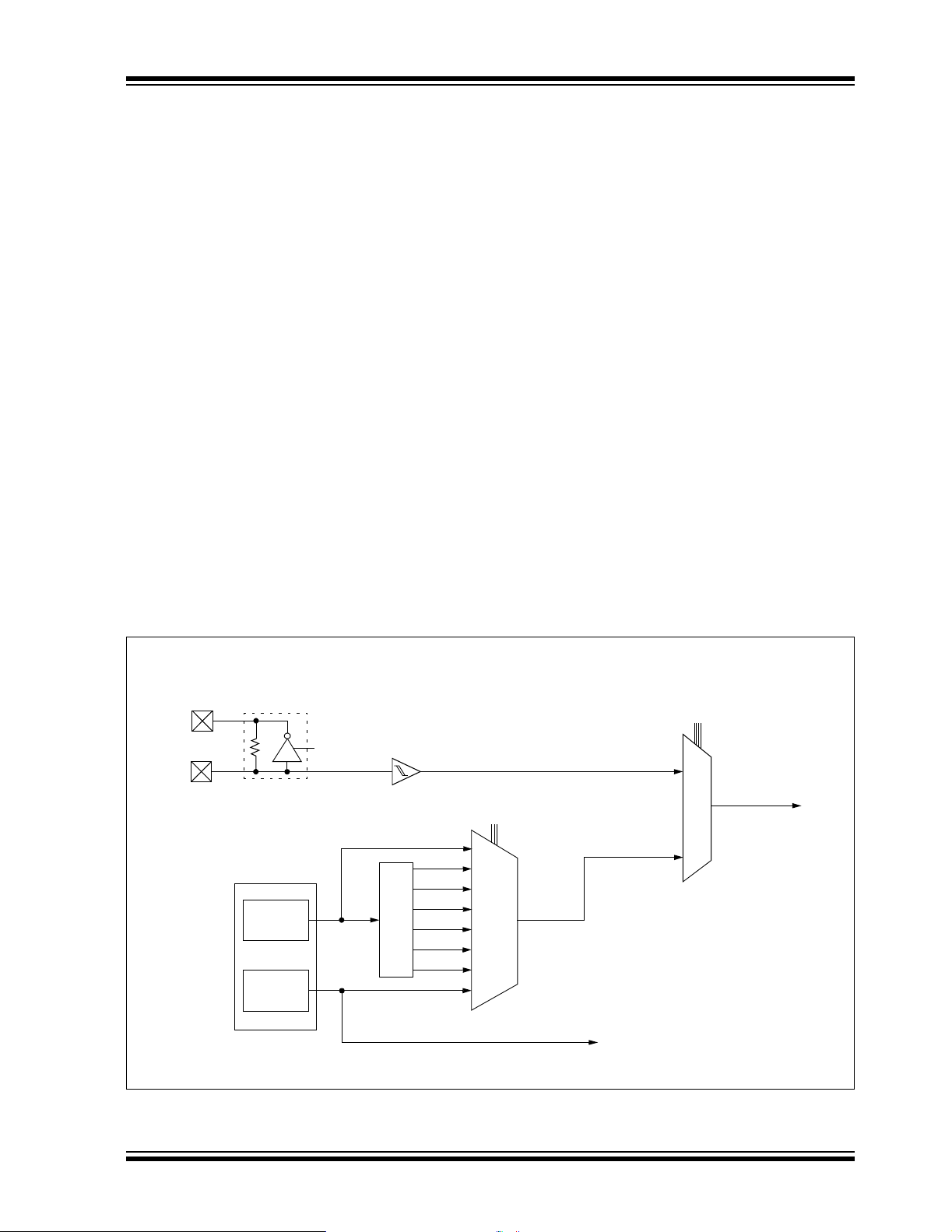

3.0 CLOCK SOURCES

3.1 Overview

The PIC16F684 has a wide variety of clock sources

and selection features to allow it to be used in a wide

range of applications while maximizing performance

and minimizing power consumption. Figure 3-1

illustrates a block diagram of the PIC16F684 clock

sources.

Clock sources can be configured from external

oscillators, quartz crystal resonators, ceramic

resonators and Resistor-Capacitor (RC) circuits. In

addition, the system clock source can be configured

from one of two internal oscillators, with a choice of

speeds selectable via software. Additional clock

features i nclude:

• Selectable system clock source between external

or internal via software.

• Two-Speed Clock Start-up mode, which minimizes latency betw e en ext ernal oscillator start-u p

and code execution.

• Fail-Safe Clock Monitor (FSCM) designed to

detect a failure of the external clock source (LP,

XT, HS, EC or RC modes) and switch to the

internal oscillator.

The PIC16F684 can b e conf igured in one of ei ght cloc k

modes.

1. EC – External clock with I/O on RA4.

2. LP – Low gain Crystal or Ceramic Resonator

Oscillator mode.

3. XT – Medium gain Crystal or Ceramic Resonator Oscillator mode.

4. HS – High gain Crystal or Ceramic Resonator

mode.

5. RC – External Resistor-Capacitor (RC) with

OSC/4 out put on RA4.

F

6. RCIO – External Resistor-Capacitor with I/O on

RA4.

7. INTRC – Internal oscillator with F

OSC/4 output

on RA4 and I/O on RA5.

8. INTRCIO – Internal oscillator with I/O on RA4

and RA5.

Clock source m odes are configu red by t he FOSC<2:0 >

bits in the Configuration Word register (see

Section 12.0 “Special Features of the CPU”). The

internal clock can be generated by two oscillators. The

HFINTOSC is a high-frequency calibrated oscillator.

The LFINTOSC is a low-frequency uncalibrated

oscillator.

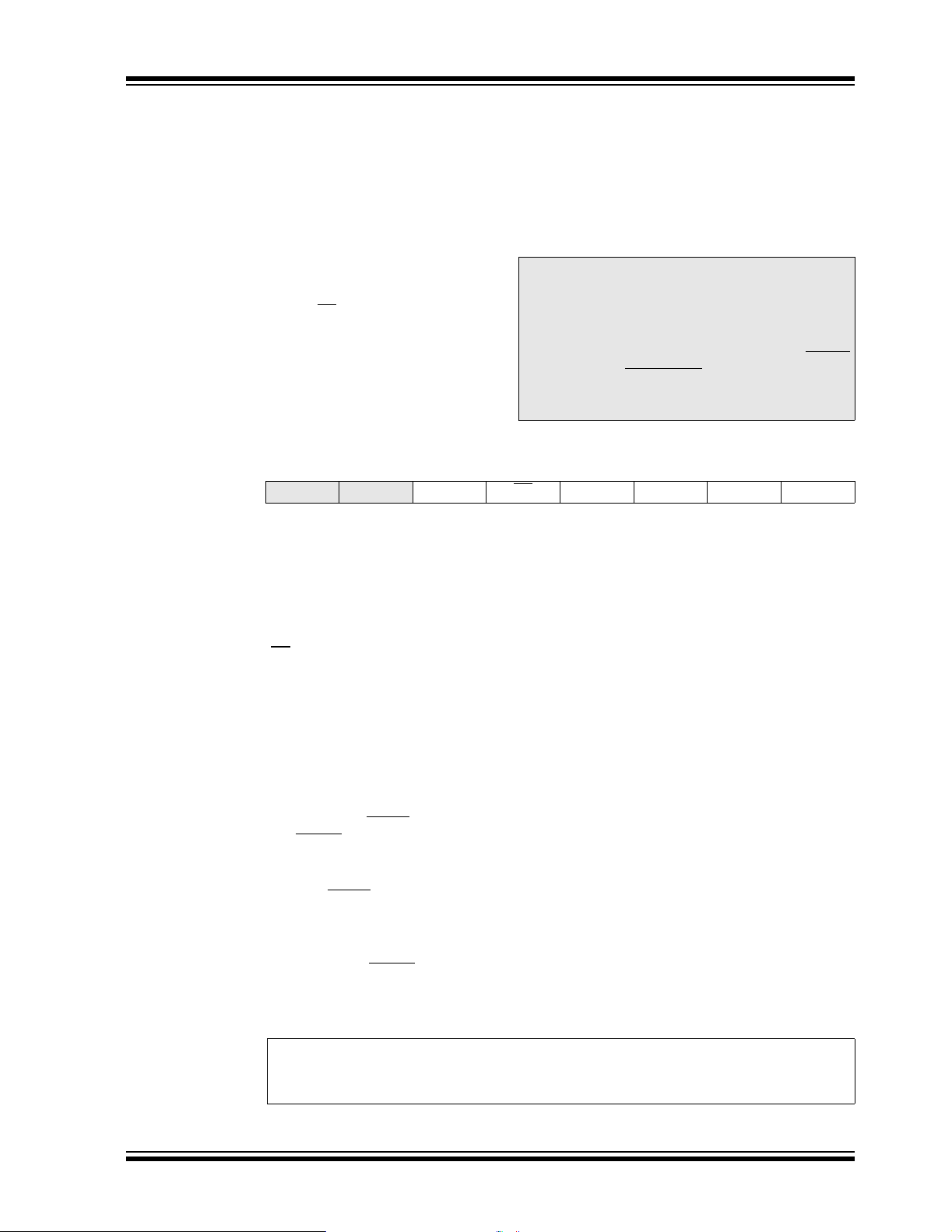

FIGURE 3-1: PIC16F684 CLOCK SOURCE BLOCK DIAGRAM

External Oscillator

OSC2

OSC1

Internal Oscillator

HFINTOSC

8 MHz

LFINTOSC

31 kHz

Sleep

Postscaler

(OSCCON<6:4>)

8 MHz

4 MHz

2 MHz

1 MHz

500 kHz

250 kHz

125 kHz

31 kHz

IRCF<2:0>

111

110

101

100

011

010

001

000

LP, XT, HS, RC, RCIO, EC

MUX

Power-up Timer (PWRT)

Watchdog Timer (WDT)

Fail-Safe Clock Monitor (FSCM)

FOSC<2:0>

(Configuration Word)

SCS

(OSCCON<0>)

MUX

(CPU and Peripherals)

System Clock

2004 Microchip Technology Inc. Preliminary DS41202C-page 19

PIC16F684

3.2 Clock Source Modes

Clock source modes can be classified as external or

internal.

• External clock mode s rely on ext erna l circuitry for

the clock source. Exam ples are oscillator modules

(EC mode), quartz crystal resonators or ceramic

resonators (LP, XT and HS modes), and

Resistor- Capacitor (RC mode) circuits.

• Internal clock sources are contained internally

within the PIC16F684. The PIC16F684 has two

internal oscillators, the 8 MHz High-Frequency

Internal Oscillator (HFINTOSC) and 31 kHz

Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or

internal clock sources via the System Clock Selection

(SCS) bit (see Section 3.5 “Clock Switching”).

3.3 External Clock Modes

3.3.1 OSCILLATOR START-UP TIMER (OST)

If the PIC16F684 is co nfigured for LP, XT or HS modes,

the Oscillator Start-up Timer (OST) counts 1024 oscillations from the OSC1 pin, followi ng a Power-on Res et

(POR) and the Power-up T i mer (PWR T ) has ex pired ( if

configured), or a wake -up from Sleep. D urin g this t ime,

the program counter does not increment and program

execution is suspended. The OST ensures that the

oscillator circuit, using a quartz crystal resonator or

ceramic resonator, has st arted and i s providing a stabl e

system clock to the PIC16F684. When switching

between clock sources a delay is required to allow the

new clock to stabilize. These oscillator delays are

shown in Table 3-1.

In order to minimize laten cy between externa l oscillator

start-up and code execution, the Two-Speed Clock

Start-up mode can be selected (see Section 3.6

“Two-Speed Clock Start-up Mode”).

TABLE 3-1: OSCILLATOR DELAY EXAMPLES

Switch From Switch To Frequency Oscillator Delay

Sleep/POR

Sleep/POR EC, RC DC – 20 MHz

LFINTOSC (31 kHz) EC, RC DC – 20 MHz

Sleep/POR LP, XT, HS 31 kHz to 20 MHz 1024 Clock Cycles (OST)

LFINTOSC (31 kHz) HFINTOSC 125 kHz to 8 MHz 1 µs (approx.)

Note 1: The 5 µs to 10 µs start-up delay is based on a 1MHz system clock.

LFINTOSC

HFINTOSC

31 kHz

125 kHz to 8 MHz

5 µs-10 µs (approx.) CPU Start-up

(1)

3.3.2 EC MODE

The External Clock (EC) mode allows an externally

generated logic level as the system clock source.

When operating in this mode, an external clock source

is connected to the OSC1 pin and the RA5 pin is

available for general purpose I/ O. Figure 3-2 shows the

pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when

EC mode is selected. Therefore, there is no delay in

operation after a Power-on Reset (POR) or wake-up

from Sleep. Because the PIC16F684 design is fully

static, stopping the external clock input will have the

effect of halting the device while leaving all data intact.

Upon restarting the external clock, the device will

resume operation as if no time had elapsed.

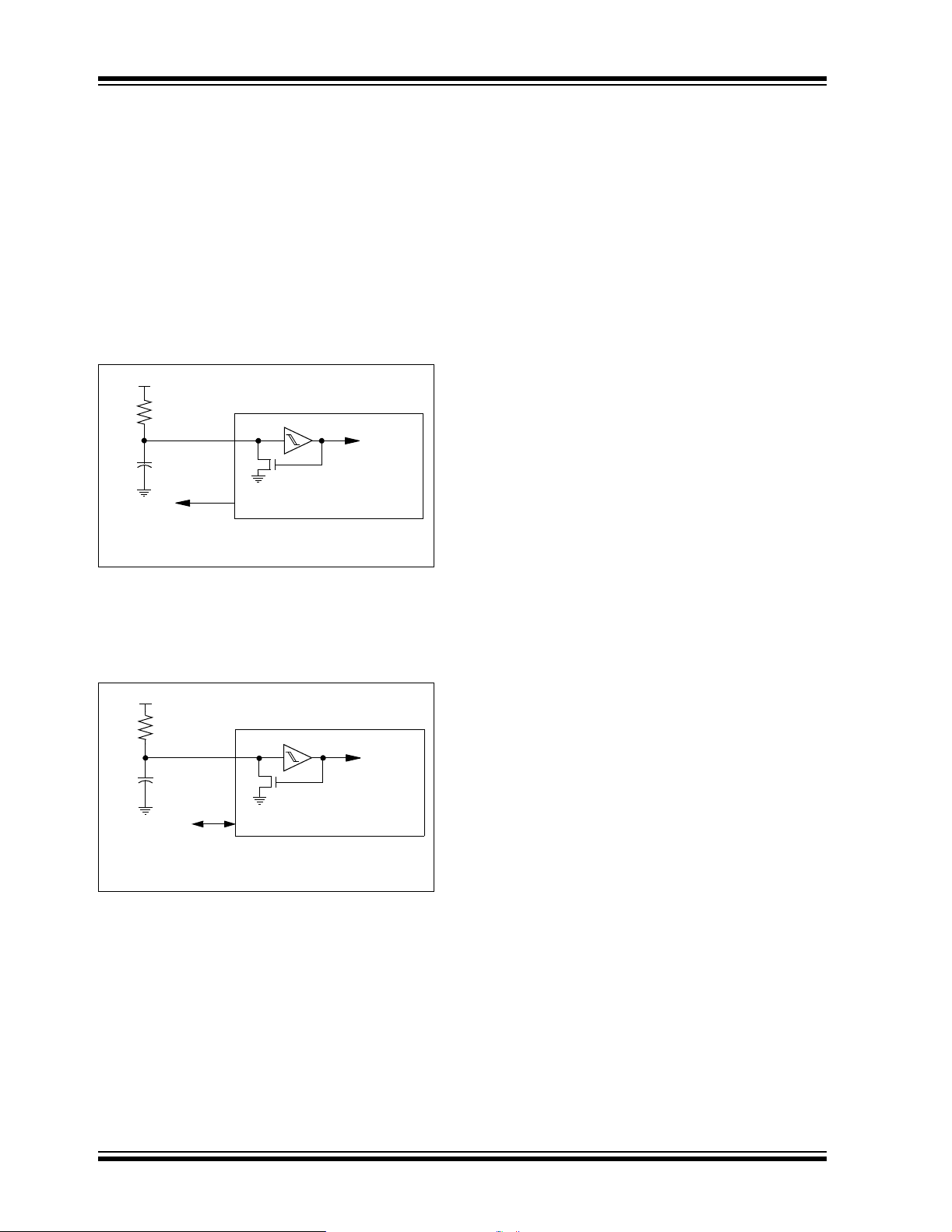

FIGURE 3-2: EXTERNAL CLOCK (EC)

MODE OPERATION

Clock from

Ext. System

RA4

OSC1/CLKIN

PIC16F684

I/O (OSC2)

DS41202C-page 20 Preliminary 2004 Microchip Technology Inc.

PIC16F684

r

r

)

r

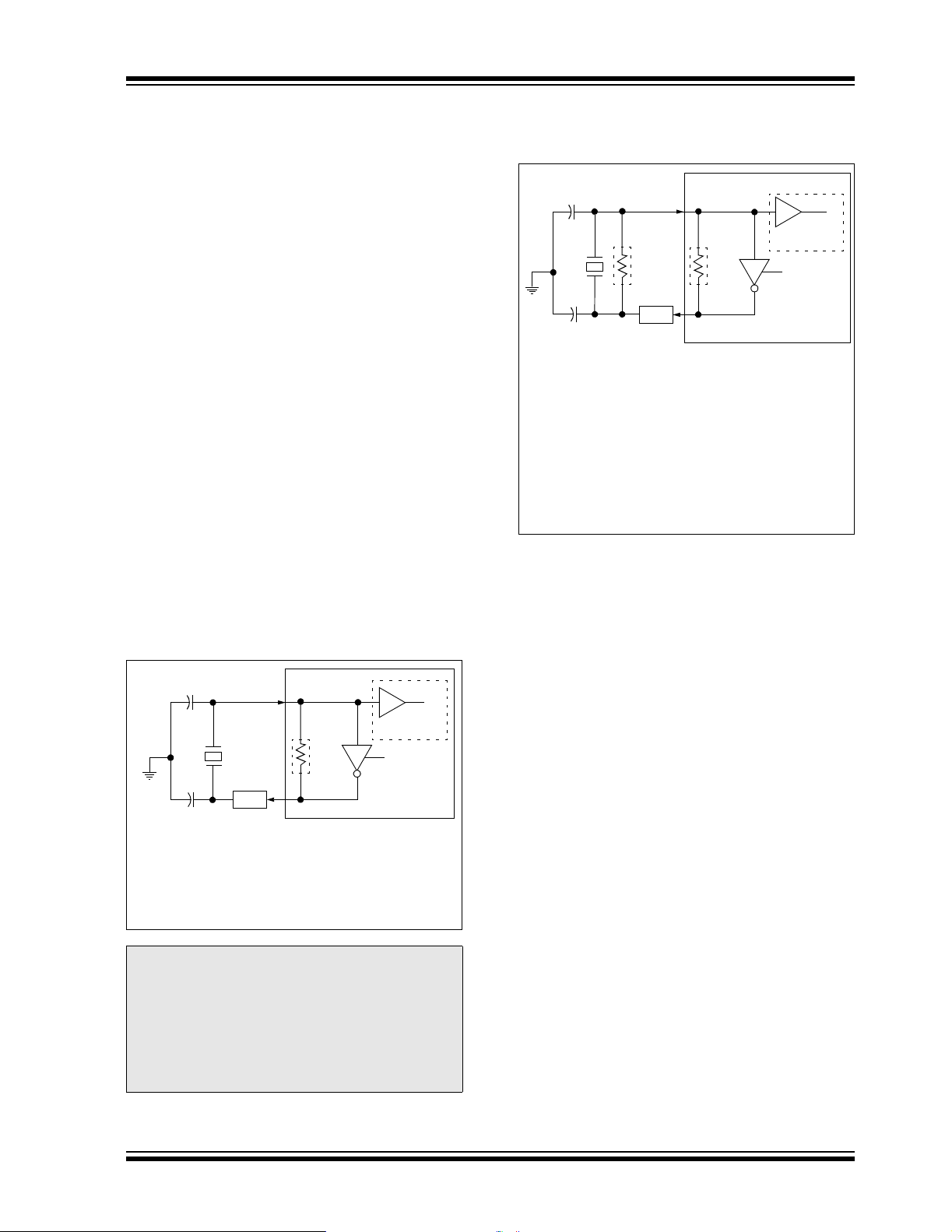

3.3.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz

crystal resonators or ceramic resonators connected to

the OSC1 and OSC2 pins (Figure 3-1). The mode

selects a low, medium or high gain setting of the

internal inverter-amplifier to support various resonator

types and speed.

LP Oscillator mode selects the lowest gain setting of

the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is

best suited to drive resonator s with a low drive lev el

specification, for example, tuning fork type crystals.

XT Oscillator mode selects the intermediate gain

setting of the internal inverter-amplifier. XT mode

current consumption is the medi um of the three modes.

This mode is best suited to drive resonators with a

medium drive level specification, for example,

low-frequency/AT-cut quartz crystal resonators.

HS Oscillator mode selects the highest gain setting of

the internal inverter-amplifier. HS mode current

consumption is the highest of the three modes. This

mode is best suited for resonato rs that req uire a hi gh

drive setting, for example, high-frequency/AT-cut

quartz crystal resonators or ceramic resonators.

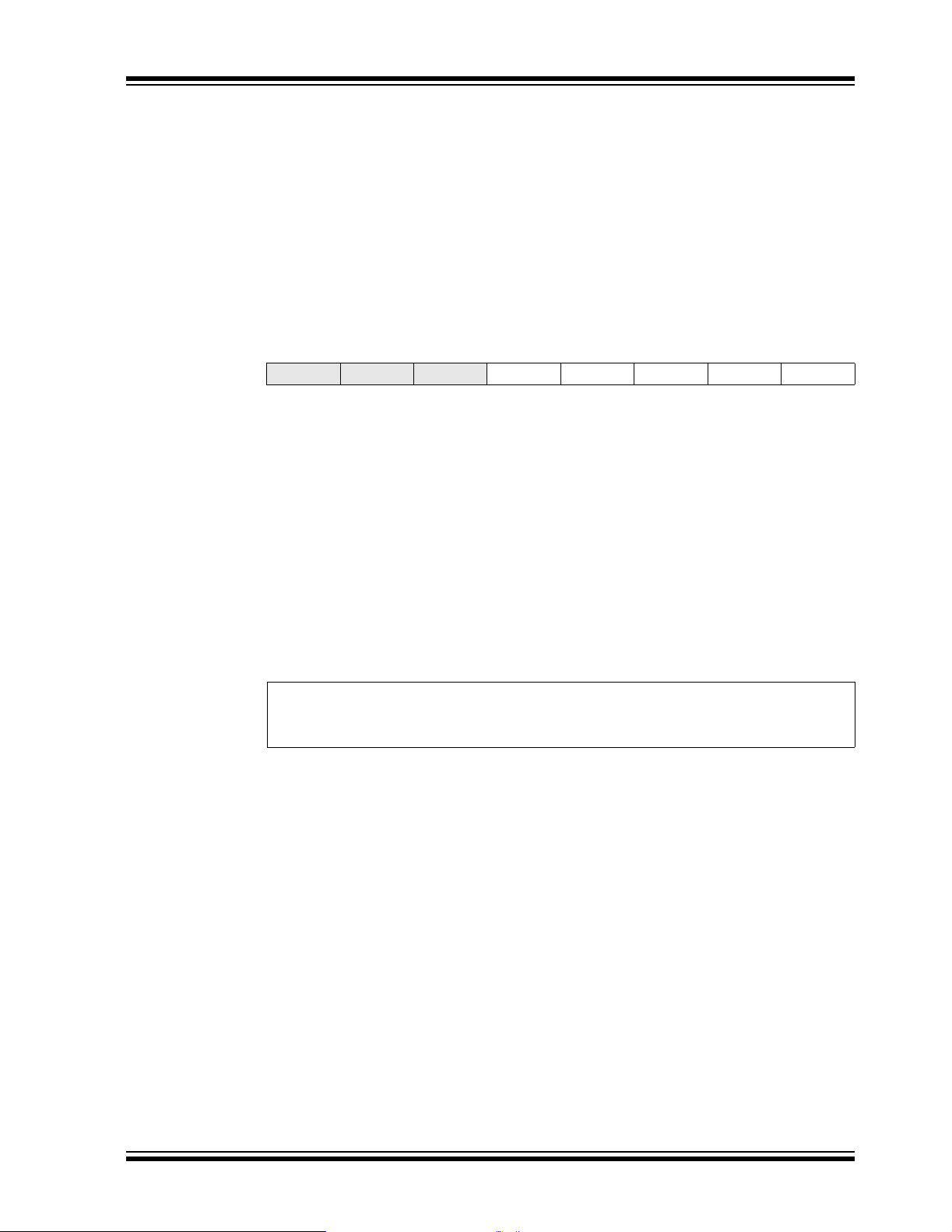

Figure 3-3 and Figure3-4 show typical circuits for

quartz crystal and ceramic resonators, respectively.

FIGURE 3-4: CERAMIC RESONATOR

OPERATION

(XT OR HS MODE)

PIC16F684

OSC1

C1

(3)

RP

OSC2

(1)

R

S

C2

Ceramic

Resonator

Note 1: A series resistor (RS) may be required fo

ceramic resonators with low drive level.

2: The value of R

mode selected (typically between 2 MΩ to

10 MΩ).

3: An additional parallel feedback resistor (R

may be required for proper ceramic resonato

operation (typical value 1 MΩ).

(2)

RF

F varies with the Oscillato

To Internal

Logic

Sleep

P

FIGURE 3-3: QUARTZ CRYSTAL

OPERATION (LP, XT OR

HS MODE)

PIC16F684

OSC1

C1

Quartz

Crystal

OSC2

(1)

R

S

C2

Note 1: A series resistor (RS) may be required for

quartz crystals with low drive level.

2: The value of R

mode selected (typically between 2 MΩ to

10 MΩ).

(2)

RF

F varies with the Oscillator

Note 1: Quartz crystal characteristics vary

according to type, package and manufacturer. The user should consult the manufacturer data sh eets for speci fications and

recommended application.

2: Always verify oscillator perform an ce ov er

DD and temperature range that is

the V

expected for the application.

To Internal

Logic

Sleep

2004 Microchip Technology Inc. Preliminary DS41202C-page 21

PIC16F684

3.3.4 EXTERNAL RC MODES

The External Resistor-Capacitor (RC) modes support

the use of an external RC circuit. This allows the

designer maximum flexibility in frequency choice while

keeping costs to a minimum when clock accuracy is not

required. There are two modes, RC and RCIO.

In RC mode, the RC circuit connects to the OSC1 pin.

The OSC2/CLKOUT pin outputs the RC oscillator

frequency divided by 4. This signal may be used to

provide a clock for external circuitry, synchronization,

calibration, test or other application requirements.

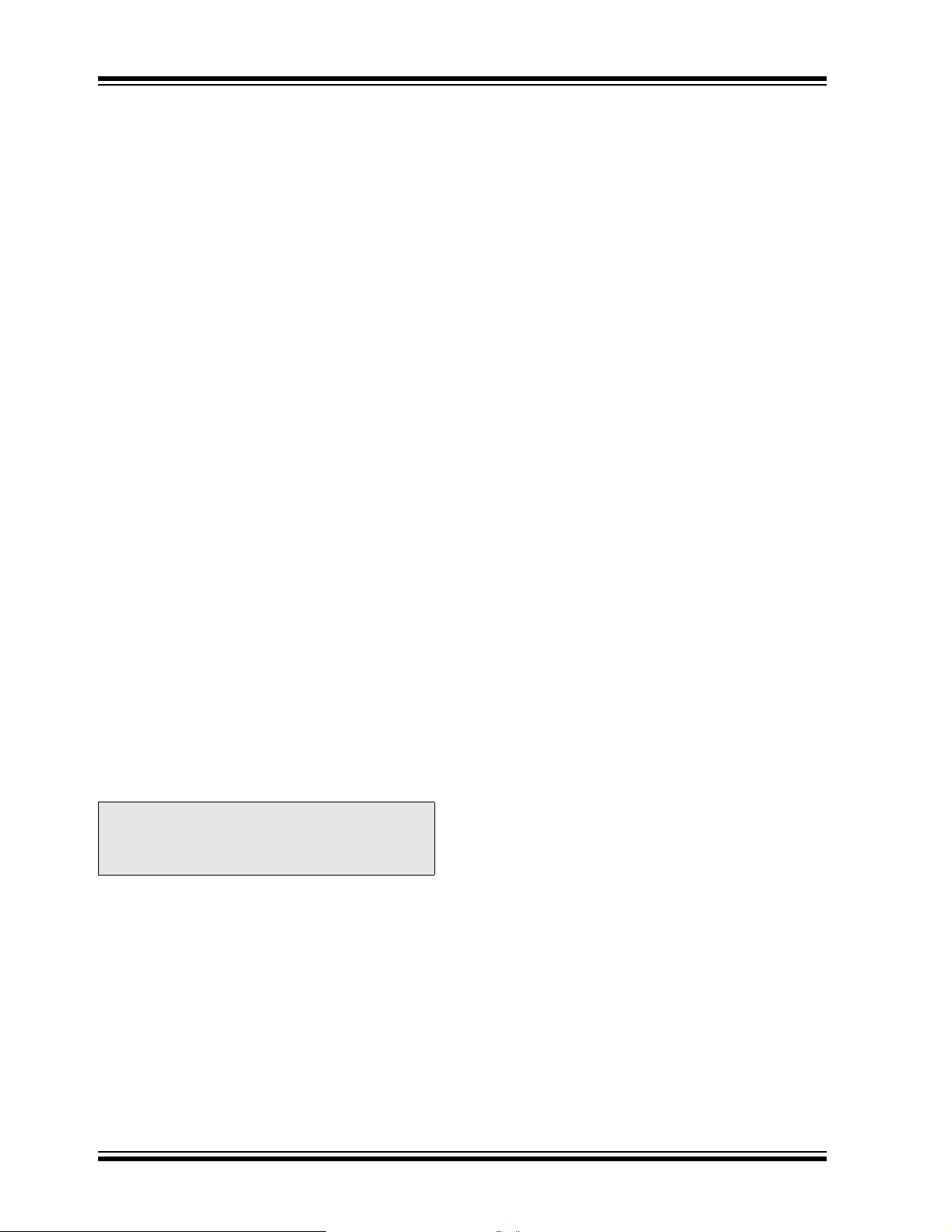

Figure 3-5 shows the RC mode connections.

FIGURE 3-5: RC MODE

VDD

REXT

OSC1

CEXT

VSS

F

Recommended values: 3 kΩ ≤ REXT ≤ 100 kΩ

OSC/4

OSC2/CLKOUT

C

EXT > 20 pF

Internal

Clock

PIC16F684

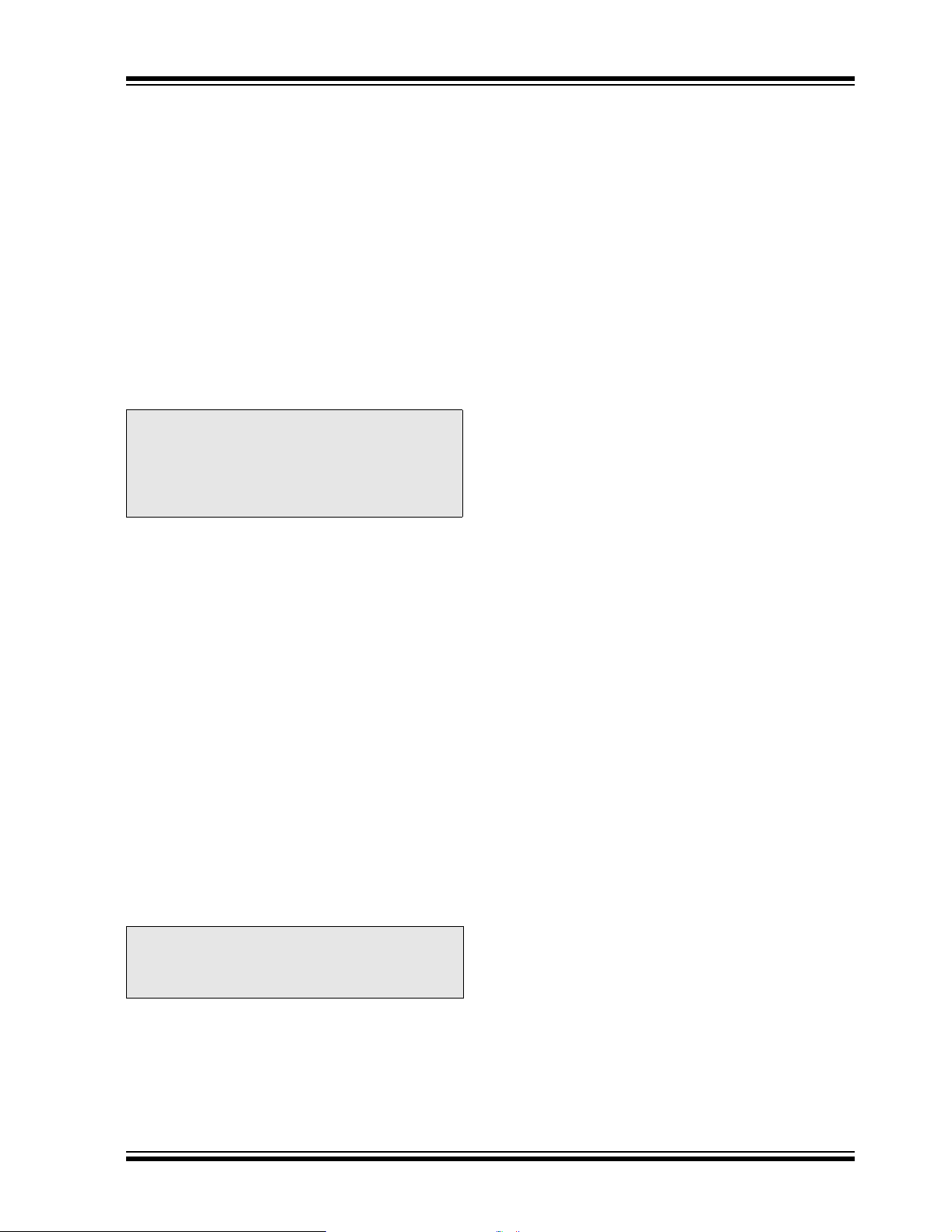

In RCIO mode, the RC circuit is connecte d to the OSC1

pin. The OSC2 pin becomes an additional general

purpose I/O pin. The I/O pin becomes bit 4 of PORTA

(RA4). Figure 3-6 shows the RCIO mode connections.

FIGURE 3-6: RCIO MODE

VDD

3.4 Internal Clock Modes

The PIC16F684 has two independent, internal

oscillators that can be configured or selected as the

system clock source.

1. The HFINTOSC (High-Frequency Internal

Oscillator) is factory calibrated and operates at

8 MHz. The frequency of t he HFINT OSC can be

user adjusted ±12% via software using the

OSCTUNE register (Register 3-1).

2. The LFINTOSC (Low-Frequency Internal

Oscillator) is uncalibrated and operates at

approximately 31 kHz.

The system cloc k speed ca n be selec ted via sof tware

using the Internal Oscillator Frequency Select (IRCF)

bits.

The system clock ca n be se lec ted betw ee n external or

internal clock sources via the System Clock Selection

(SCS) bit (see Section 3.5 “Clock Switching”).

3.4.1 INTRC AND INTRCIO MODES

The INTRC and INTRCIO m odes conf igure the int ernal

oscillators as th e sys tem cl ock so urce when the dev ice

is programmed using the Oscillator Selection (FOSC)

bits in the Configuration Word register (Register 12-1).

In INTRC mode, the OSC1 pin is available for general

purpose I/O. The OSC2/CLKOUT pin outputs the

selected internal os ci lla tor freq uen cy div ide d by 4. The

CLKOUT signal may be used to provide a clock for

external circuitry, synchronization, calibration, test or

other application require me nt s .

In INTRCIO mode, the OSC1 and OSC2 pins are

available for general purpose I/O.

REXT

OSC1

CEXT

VSS

RA4

Recommended values: 3 kΩ ≤ REXT ≤ 100 kΩ

I/O (OSC2)

EXT > 20 pF

C

PIC16F684

Internal

Clock

3.4.2 HFINTOSC

The High-Frequency Int ernal Oscillato r (HFINT OSC) is

a factory calibrated 8 MHz internal clock source. The

frequency of the HFINTOSC can be altered

approximately ±12% via software using the OSCT UNE

register (Register 3-1).

The output of the HFINTOSC connects to a postscaler

and multiplexer (see Figure 3-1). One of seven

frequencies can be selected via software using the

IRCF bits (see Section 3.4.4 “Frequency Select Bits

The RC oscillator frequency is a function of the supply

voltage, the resistor (R

EXT) and capacitor (CEXT)

values and the operating temperature. Other factors

affecting the oscillator frequency are:

• threshold voltage variation

• component tolerances

• packaging variations i n capacitance

(IRCF)”).

The HFINTOSC is enabled by selecting any frequency

between 8 MHz and 125 kHz (IRCF ≠ 000) as the

system clock s ource (SCS = 1), or when Two-Speed

Start-up is enabled (IESO = 1 and IRCF ≠ 000).

The HF Internal Oscillator (HTS) bit (OSCCON<2>)

indicates whether the HFINTOSC is stable or not.

The user also needs to take into account variation due

to tolerance of external RC components used.

DS41202C-page 22 Preliminary 2004 Microchip Technology Inc.

PIC16F684

3.4.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be

adjusted in software by writing to the OSCTUNE

register (Register3-1).

The OSCTUNE register has a tuning range of ±12%.

The default value of the OSCTUNE register is ‘0’. The

value is a 5-bit two’s complement number. Due to

process variatio n, the m onoton icity and freq uency step

cannot be specified.

When the OSCTUNE register is modified, the

HFINTOSC frequency will begin shifting to the new

frequency. The HFINTOSC clock will stabilize within

1 ms. Code execution continues during this shift. There

is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency.

Operation of features that depend on the LFINTOSC

clock source frequency, such as the Power-up Timer

(PWRT), Watchdog Timer (WDT), Fail-Safe Clock

Monitor (FSCM) and peripherals, are not af fected by the

change in frequency.

REGISTER 3-1: OSCTUNE – OSCILLATOR TUNING RESISTOR (ADDRESS: 90h)

U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — — TUN4 TUN3 TUN2 TUN1 TUN0

bit 7 bit 0

bit 7-5 Unimplemented: Read as ‘0’

bit 4-0 TUN<4:0>: Frequency Tuning bits

01111 = Maximum frequency

01110 =

•

•

•

00001 =

00000 = Oscillator module is running at the calibrated frequency.

11111 =

•

•

•

10000 = Minimum frequency

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2004 Microchip Technology Inc. Preliminary DS41202C-page 23

PIC16F684

3.4.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is

an uncalibrated (approximate) 31 kHz internal clock

source.

The output of the LFINTOSC connects to a postscaler

and multiplexer (see Figure3-1). 31 kHz can be

selected via software using the IRCF bits (see

Section 3.4.4 “Frequency Select Bits (IRCF)”). The

LFINTOSC is also the frequency for the Power-up

Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe

Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz

(IRCF = 000) as the system clock sourc e (SCS = 1), or

when any of the following are enabled:

• Two-Speed Start-up (IESO = 1 and IRCF = 000)

• Power-up Timer (PWRT)

• Watchdog Timer (WDT)

• Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit (OSCCON<1>)

indicates whether the LFINTOSC is stable or not.

3.4.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz

LFINTOSC connects to a postscaler and multiplexer

(see Figure 3-1). The Internal Oscillator Frequency

select bits, IRCF<2:0> (OSCCON<6:4>), select the

frequency output of the internal oscillators. One of eight

frequencies can be selected via software:

•8 MHz

• 4 MHz (Default after Reset)

•2 MHz

•1 MHz

• 500 kHz

• 250 kHz

• 125 kHz

•31 kHz

Note: Following any Reset, t he IR CF bit s are set

to ‘110’ and the frequency selection is set

to 4 MHz. The user can modify the IRCF

bits to select a different frequency.

3.4.5 HF AND LF INTOSC CLOCK

SWITCH TIMING

When switching between the LFINTOSC and the

HFINTOSC, the new oscillator may already be shut

down to save power. If this is the case, there is a 10 µs

delay after the IRCF bits are modified before the

frequency selection takes place. The LTS/HTS bits will

reflect the current active status of the LFINTOSC and

the HFINTOSC oscillators. The timing of a frequency

selection is as follows:

1. IRCF bits are modified.

2. If the new clock is shut down, a 10 µs clock

start-up delay is started.

3. Clock switch circuitry waits for a falling edge of

the current clock.

4. CLKOUT is held low and the clock switch

circuitry waits fo r a ris ing edge in the new clock.

5. CLKOUT is now connected with the new clock.

HTS/LTS bits are updated as required.

6. Clock switch is complete.

If the internal oscillator speed selected is between

8 MHz and 125 kHz, there is no start-up delay before

the new frequency is selected. This is because the old

and the new frequencies are derived from the

HFINTOSC via the postscaler and multiplexer.

DS41202C-page 24 Preliminary 2004 Microchip Technology Inc.

PIC16F684

3.5 Clock Switching

The system clock source can be switched between

external and internal clock sources via software using

the System Clock Select (SCS) bit.

3.5.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit (OSCCON<0>)

selects the system clock source that is used for the

CPU and peripherals.

• When SCS = 0, the system clock source is

determined by configuration of the FOSC<2:0>

bits in the Configuration Word register (CONFIG).

• When SCS = 1, the system clock source is

chosen by the internal oscillator frequency

selected by the IRCF bits. After a Reset, SCS is

always cleared.

Note: Any automatic clock switch, which may

occur from Two-Speed Start-up or

Fail-Safe Clock Monitor, does not update

the SCS bit. The user can monitor the

OSTS (OSCCON<3>) to determine the

current system clock source.

3.5.2 OSCILLATOR START-UP TIME-OUT

STATUS BIT

The Oscillator Start-up Time-out Status (OSTS) bit

(OSCCON<3>) indicates whether the system clock is

running from the external clock source, as defined by

the FOSC bits, or from internal clock source. In

particular, OSTS indicates that the Oscillator Start-up

Timer (OST) has timed out for LP, XT or HS modes.

3.6 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power

savings by minimizing the latency between external

oscillator start-up and code execution. In applications

that make heavy us e of the Sleep mode, Two-Speed

Start-up will remove the external oscillator start-up

time from the time spent awake and can reduce the

overall power consumption of the device.

This mode allows the application to wake-up from

Sleep, perform a few instructions using the INTOSC

as the clock source and go back to Sleep without

waiting for the primary oscillator to become stable.

When the PIC16F684 is configured for LP, XT or HS

modes, the Oscillator Start-up Timer (OST) is enabled

(see Section 3.3.1 “Oscillator Start-up Timer

(OST)”). The OST timer will suspend program execution until 1024 oscillations are counted. Two-Speed

Start-up mode minimizes the delay in code execution

by operating from the internal oscillator as the OST is

counting. When the OST count reaches 1024 and the

OSTS bit (OSCCON<3>) is set, program execution

switches to the external oscillator.

3.6.1 TWO-SPEED START-UP MODE

CONFIGURATION

Two-Speed Start-up mode is configured by the

following settings:

• IESO = 1 (CONFIG<10>) Internal/External Switch

Over bit.

•SCS = 0.

• FOSC configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

• Power-on Reset (POR) and, if enabl ed, after

PWRT has expired, or

• Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-Speed

Start-up is disabled. This is because the ex tern al clock

oscillator does not require any stabilization time after

POR or an exit from Sleep.

3.6.2 TWO-SPEED START-UP

SEQUENCE

1. Wake-up from Power-on Reset or Sleep.

2. Instructions begin execution by the internal

oscillator at the frequency set in the IRCF bits

(OSCCON<6:4>).

3. OST enabled to count 1024 clock cycles.

4. OST timed out, wait for falling edge of the

internal oscillator.

5. OSTS is set.

6. System clock held low until the next fal ling edg e

of new clock (LP, XT or HS mode).

7. System clock is switched to external clock

source.

Note: Executing a SLEEP instruction will abort

the oscillator start-up time and will cause

the OSTS bit (OSCCON<3>) to remain

clear.

2004 Microchip Technology Inc. Preliminary DS41202C-page 25

PIC16F684

3.6.3 CHECKING EXTERNAL/INTERNAL

CLOCK STATUS

Checking the state of the OSTS bit (OSCCON<3>) will

confirm if the PIC16F684 is running from the external

clock source as defined by the FOSC bits in the

Configuration Word register (CONFIG) or the internal

oscillator.

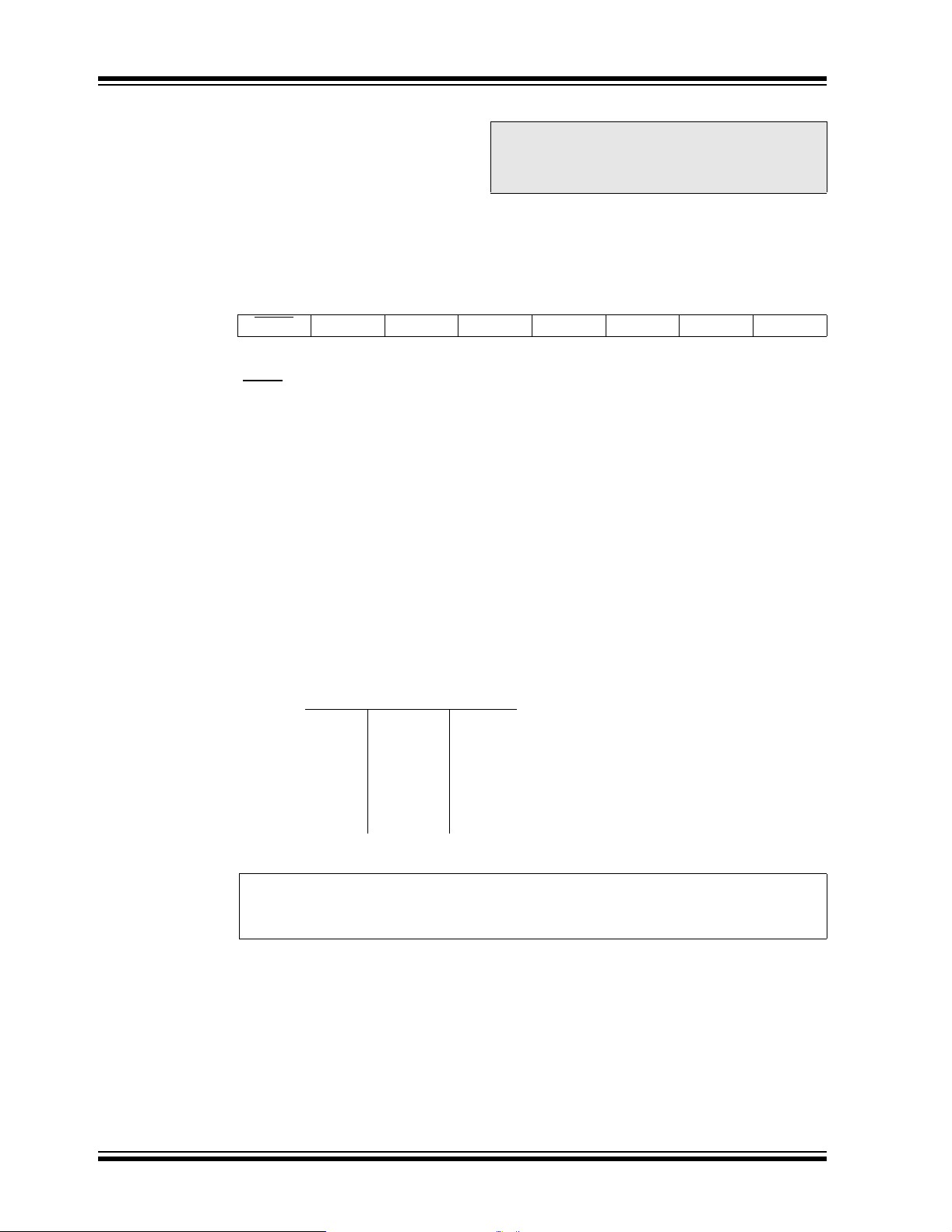

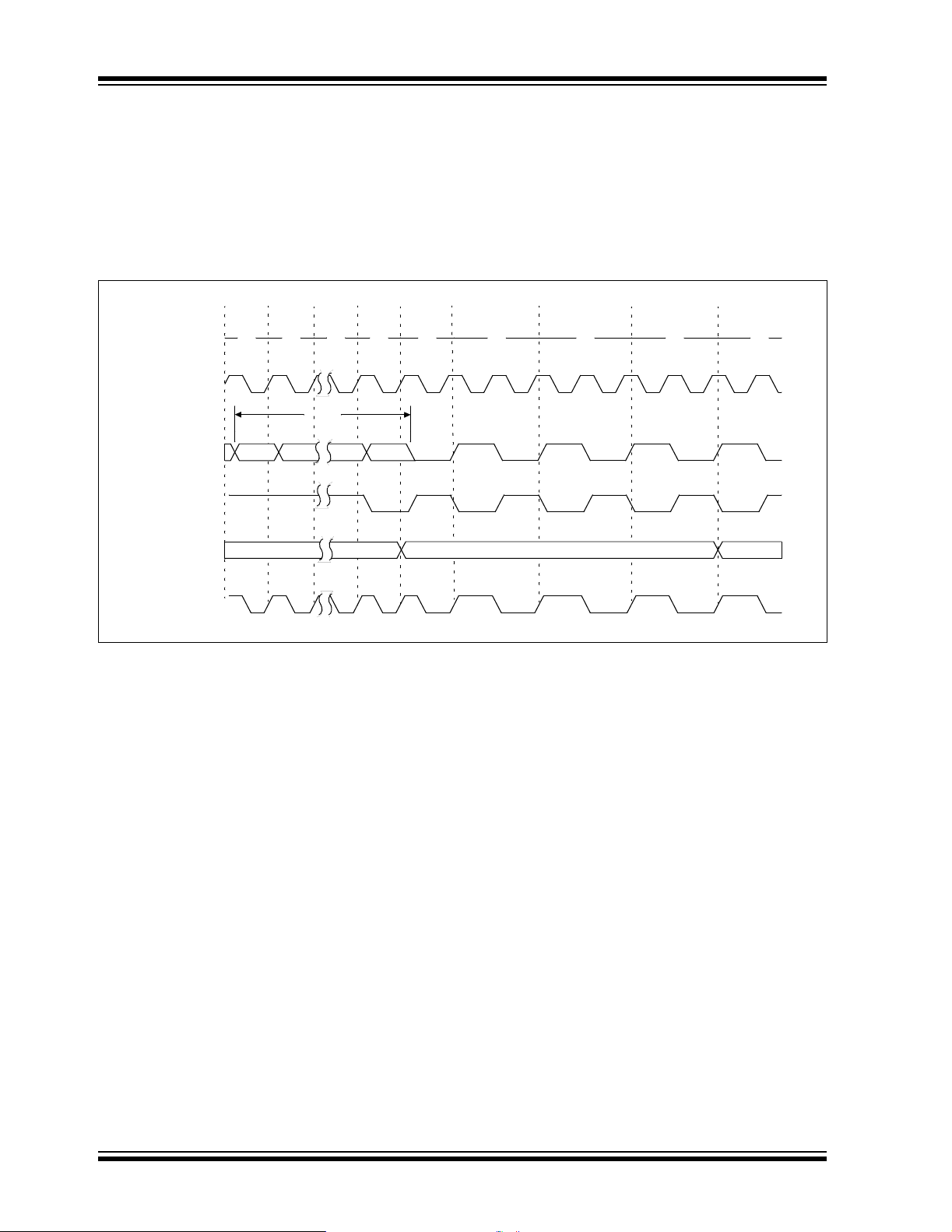

FIGURE 3-7: TWO-SPEED START-UP

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1

INTOSC

TOSTT

OSC1

OSC2

Program Counter

System Clock

0 1 1022 1023

PC PC + 1 PC + 2

DS41202C-page 26 Preliminary 2004 Microchip Technology Inc.

PIC16F684

3.7 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) is designed to

allow the device to continue to operate in the event of

an oscillator failure. The FSCM can detect oscillator

failure at any point after the device has exited a Reset

or Sleep condition and the Oscillator Start-up Timer

(OST) has expired.

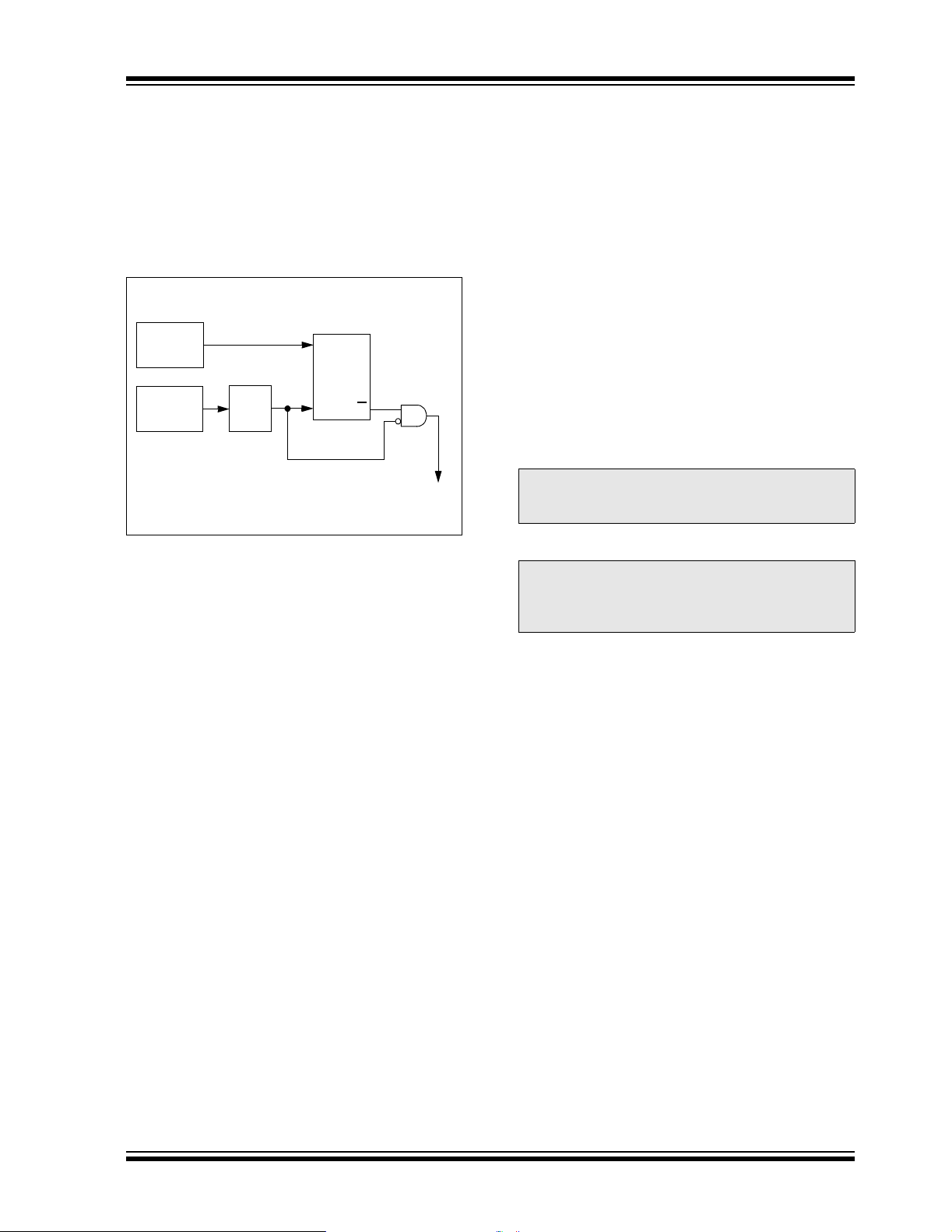

FIGURE 3-8: FSCM BLOCK DIAGRAM

Clock Monitor

Latch (CM)

Primary

Clock

LFINTOSC

Oscillator

31 kHz

(~32 µs)

÷ 64

488 Hz

(~2 ms)

The FSCM function is enabled by setting the FCMEN

bit in the Confi guration Word regist er (CONFIG). It is

applicable to all ex ternal clo ck options (LP, XT , HS, EC,

RC or IO modes).

In the event of an external clock failure, the FSCM will

set the OSFIF bit (PIR1< 2>) and g enerate an os cilla tor

fail interrupt if the OSFIE bit (PIE1<2>) is set. The

device will then switch the system clock to the internal

oscillator. The system clock will continue to come from

the internal oscill ator unless the external clock recovers

and the Fail-Safe condition is exited.

(edge-triggered)

S

Q

C

Q

Clock

Failure

Detected

The frequency of the internal oscillator will depend

upon the value contained in the IRCF bits

(OSCCON<6:4>). Upon entering the Fail-Safe

condition, the OSTS bit (OSCCON<3>) is automatically cleared to reflect that the internal oscillator is

active and the WDT is cleared. The SCS bit

(OSCCON<0 >) is not upda ted. Enabling FSCM does

not affect the LTS bit.

The FSCM sample clock is generated by dividing the

INTRC clock by 64. This will allow enough time

between FSCM sample clocks for a system clock edge

to occur. Figure 3-8 shows the FSCM block diagram.

On the rising edge of the sample clock, the monitoring

latch (CM = 0) will be cleared. On a falling edge of the

primary system clock, the monitoring latch will be set

(CM = 1). In the event that a fal lin g e dge o f th e s am pl e

clock occurs, and the m onitoring latch is n ot set, a clock

failure has been detected. The assigned internal

oscillator is enabled when FSCM is enabled, as

reflected by the IRCF.

Note: Two-Speed Start-up is automatically

enabled when the Fail-Safe Clock Monit or

mode is enabled.

Note: Primary clocks with a frequency ≤ ~488 Hz

will be considered failed by the FSCM. A

slow starting oscillator can cause an

FSCM interrupt.

3.7.1 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, the

execution of a SLEEP instruction, or a modification of

the SCS bit. While in Fail-Safe condition, the

PIC16F684 uses the internal oscillator as the system

clock sourc e. The IRCF bits (OSCCON< 6:4>) can be

modified to adjust the internal oscillator frequency

without exiting the Fail-Safe condition.

The Fail-Safe condition must be cleared before the

OSFIF flag can be cleared.

2004 Microchip Technology Inc. Preliminary DS41202C-page 27

PIC16F684

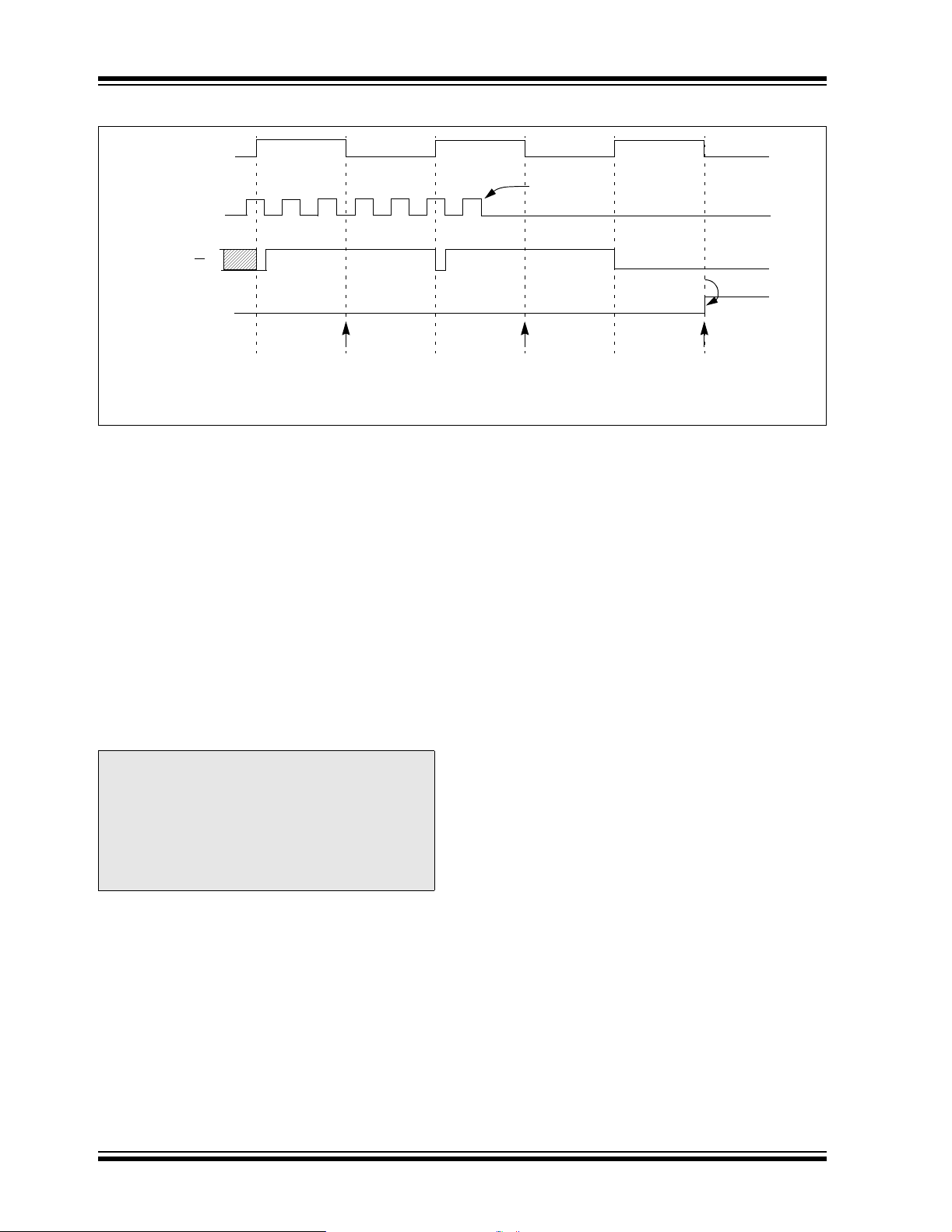

FIGURE 3-9: FSCM TIMING DIAGRAM

Sample Clock

System

Clock

Output

CM Output

(Q)

OSCFIF

CM Test

Note: The system clock is normally at a mu ch higher frequency than the sam ple clock. The relative fr equencies in

this example have been chosen for clarity.

Oscillator

Failure

Failure

Detected

CM Test CM Test

3.7.2 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at

any point after the device has exited a Reset or Sleep

condition and the Oscillator Start-up Timer (OST) has

expired. If the external clock is EC or RC mode,

monitoring will begin immediately following these

events.

For LP, XT or HS mode, the external oscillator may

require a start-up time considerably longer than the

FSCM sample clock time, a false clock failure may be

detected (see Figure 3-9). To prevent this, the internal

oscillator is automatically configured as the system

clock and functions until the external clock is stable

(the OST has timed out). This is identical to

Two-Speed Start-up mode. Once the external oscillator is stable, the LFINTOSC returns to its role as the

FSCM source.

Note: Due to the wide range of oscillato r start-u p

times, the Fail-Safe circuit is not active

during oscillator start-up (i.e., after exiting

Reset or Sleep). After an appropriate

amount of time, the u se r should check the

OSTS bit (OSCCON<3>) to verify the

oscillator start-up and system clock

switchover has successfull y com pl ete d.

DS41202C-page 28 Preliminary 2004 Microchip Technology Inc.

PIC16F684

REGISTER 3-2: OSCCON – OSCILLATOR CONTROL REGISTER (ADDRESS: 8Fh)

U-0 R/W-1 R/W-1 R/W-0 R-1 R-0 R-0 R/W-0

— IRCF2 IRCF1 IRCF0 OSTS

bit 7 bit 0

bit 7 Unimplemented: Read as ‘0’

bit 6-4 IRCF<2:0>: Internal Oscillator Frequency Select bits

000 =31kHz

001 =125kHz

010 =250kHz

011 =500kHz

100 =1MHz

101 =2MHz

110 =4MHz

111 =8MHz

bit 3 OSTS: Oscillator Start-up Time-out Status bit

1 = Device is running from the external system clock defined by FOSC<2:0>

0 = Device is running from the internal system clock (HFINTOSC or LFINTOSC)

bit 2 HTS: HFINTOSC (High Frequency – 8 MHz to 125 kHz) Status bit

1 =HFINTOSC is stable

0 = HFINTOSC is not stable

bit 1 LTS: LFINTOSC (Low Frequency – 31 kHz) Stable bit

1 = LFINTOSC is stable

0 = LFINTOSC is not stable

bit 0 SCS: System Clock Select bit

1 = Internal oscillator is used for system clock

0 = Clock source defined by FOSC<2:0>

(1)

HTS LTS SCS

Note 1: Bit resets to ‘0’ with T wo-Speed S tart-u p and LP, XT or HS selected as the Oscillat or

mode or Fail-Safe mode is enabled.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0Ch PIR1

8Ch PIE1

8Fh OSCCON

90h OSCTUNE

(1)

2007h

Legend: x = unknown, u = unchanged, — = unimplemented locations read as ‘0’. Shaded cells are not used by oscillators.

Note 1: See Register 12-1 for operation of all Configuration Word register bits.

CONFIG CPD CP MCLRE PWRTE WDTE FOSC2 FOSC1 FOSC0 — —

EEIF ADIF CCP1IF C2IF C1IF OSFIF TMR2IF TMR1IF 0000 0000 0000 0000

EEIE ADIE CCP1IE C2IE C1IE OSFIE TMR2IE TMR1IE 0000 0000 0000 0000

— IRCF2 IRCF1 IRCF0 OSTS HTS LTS SCS -110 x000 -110 x000

— — — TUN4 TUN3 TUN2 TUN1 TUN0 ---0 0000 ---u uuuu

Value on:

POR, BOD

Value on

all other

Resets

2004 Microchip Technology Inc. Preliminary DS41202C-page 29

PIC16F684

NOTES:

DS41202C-page 30 Preliminary 2004 Microchip Technology Inc.

PIC16F684

4.0 I/O PORTS

There are as many as twelve general purp ose I/O pins

available. Depending on which peripherals are

enabled, some or all of the pins may not be a vailable a s

general purpose I/O. In general, when a peripheral is

enabled, the associated pin may not be used as a

general purpose I/O pin.