PIC16F627A/628A/648A

深圳市粤原点科技有限公司

(Microchip Authorized Design Partner)指定授权

总部地址:深圳市福田区福虹路世贸广场C座1103座

Add: Room 1103,Block C,World Trade Plaza,

9Fuhong Road,Futian District Shen Zhen City

电话(tel) :86-755-83666321,83666320,83666325

传真(fax) :86-755-83666329

Web: WWW.ORIGIN-GD.COM

E-mail:01@LZmcu.com abc85185@163.com

联系人:马先生,王小姐,汤小姐

在线咨询:QQ:42513912 MSN:action_tech@hotmail.com

7x24小时在线产品咨询:13509674380 13798484366

数据手册

采用纳瓦技术的

8 位 CMOS 闪存单片机

2005 Microchip Technology Inc. DS40044D_CN

请注意以下有关 Microchip 器件代码保护功能的要点:

• Microchip 的产品均达到 Microchip 数据手册中所述的技术指标。

• Microchip 确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的

操作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

• Microchip 愿与那些注重代码完整性的客户合作。

• Microchip 或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了 《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的

软件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

提供本文档的中文版本仅为了便于理解。Microchip

Technology Inc. 及其分公司和相关公司、各级主管与员工及

事务代理机构对译文中可能存在的任何差错不承担任何责任。

建议参考 Microchip Technology Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。未经 Microchip 书面批准,不得

将 Microchip 的产品用作生命维持系统中的关键组件。在

Microchip 知识产权保护下,不得暗中或以其他方式转让任何

许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 Accuron、

dsPIC、 K

EELOQ、 microID、 MPLAB、 PIC、 PICmicro、

PICSTART、 PRO MATE、 PowerSmart、 rfPIC 和

SmartShunt 均为 Microchip Technology Inc. 在美国和其他国

家或地区的注册商标。

AmpLab、 FilterLab、 Migratable Memory、 MXDEV、

MXLAB、 PICMASTER、 SEEVAL、 SmartSensor 和 The

Embedded Control Solutions Company 均为 Microchip

Technology Inc. 在美国的注册商标。

Analog-for-the-Digital Age、 Application Maestro、

dsPICDEM、 dsPICDEM.net、 dsPICworks、 ECAN、

ECONOMONITOR、 FanSense、 FlexROM、 fuzzyLAB、

In-Circuit Serial Programming、 ICSP、 ICEPIC、 Linear

Active Thermistor、 MPASM、 MPLIB、 MPLINK、 MPSIM、

PICkit、 PICDEM、 PICDEM.net、 PICLAB、 PICtail、

PowerCal、 PowerInfo、 PowerMate、 PowerTool、 rfLAB、

rfPICDEM、 Select Mode、 Smart Serial、 SmartTel、 To t al

Endurance 和 WiperLock 均为 Microchip Technology Inc.在

美国和其他国家或地区的商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2005, Microchip Technology Inc.版权所有。

Microchip

州

10

位单片机、

性存储器和模拟产品方面的质量体系流程均符合

16949:2002

系也已通过了

位于美国亚利桑那州

Mountain View

月通过了

ISO/TS-16949:2002

KEELOQ

。此外 ,

ISO 9001:2000

的全球总部、设计中心和晶圆生产厂均于

®

跳码器件、串行

Microchip

Chandler和Tem p e

质量体系认证。公司在

EEPROM

在开发系统的设计和生产方面的质量体

认证。

及位于加利福尼亚

、单片机 外设、非易失

ISO/TS-

2003

PICmicro

年

®

DS40044D_CN 第 ii 页 2005 Microchip Technology Inc.

8

PIC16F627A/628A/648A

采用纳瓦技术的 18 引脚 8 位 CMOS 闪存单片机

高性能 RISC CPU:

• 工作速度可从 DC 到 20 MHz

• 中断能力

• 8 级深度硬件堆栈

• 直接、间接和相对寻址模式

• 35 条单字指令

- 除了转移指令以外,所有指令均为单周期指令

单片机的特殊功能:

• 内部和外部振荡器选择:

- 高精度的内部 4MHz振荡器,出厂时精度校

准为± 1%

- 低功耗内部 48kHz 振荡器

- 可使用晶振和谐振器作为外部振荡器。

• 节能的休眠模式

• PORTB 上有可编程的弱上拉功能

• 主复位 / 输入引脚复用

• 看门狗定时器带有独立的振荡器,能保证可靠的运

行

• 低电压编程

• 在线串行编程 (In-Circuit Serial

Programming™)(通过两个引脚进行)

• 可编程代码保护

• 欠压复位

• 上电复位

• 上电延时定时器和振荡器起振定时器

• 宽工作电压范围 (2.0V 到 5.5V)

• 工业级和扩展级温度范围

• 高耐用性闪存 /EEPROM 单元

- 闪存可经受 10 万次写操作

- EEPROM 可经受 100 万次写操作

- 数据保持期为 40 年

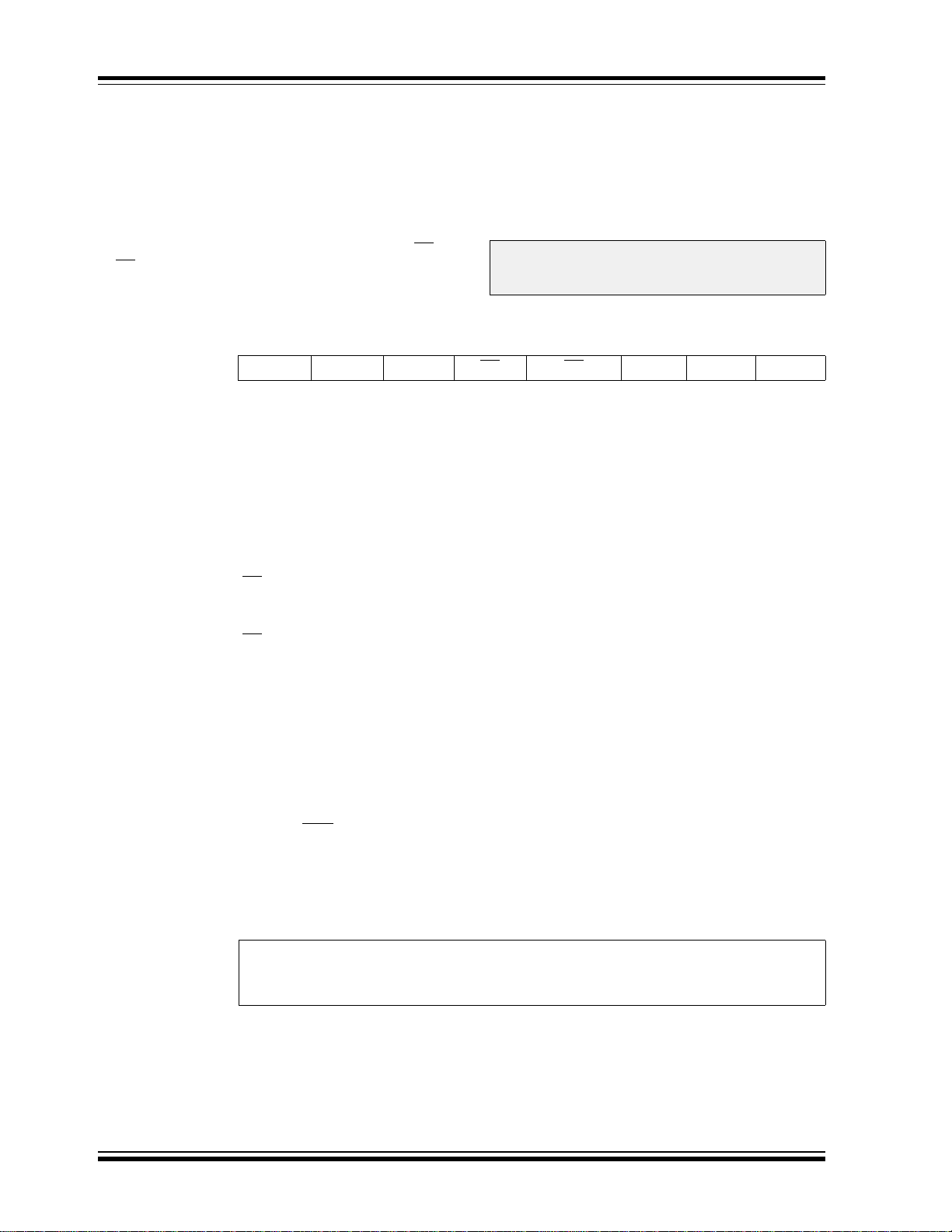

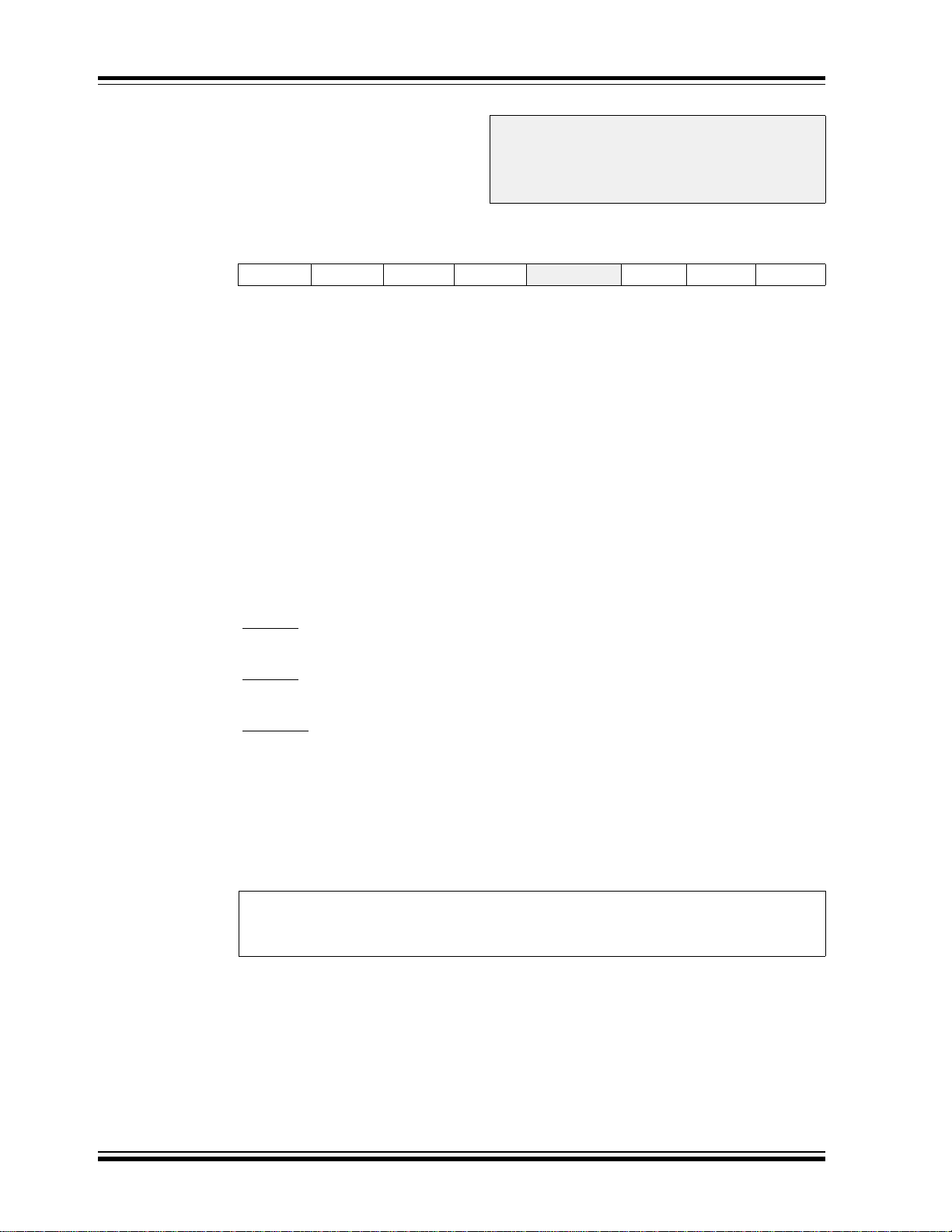

程序存储器 数据存储器

器件

PIC16F627A 1024 224 128 16 1

PIC16F628A 2048 224 128 16 1

PIC16F648A 4096 256 256 16 1

闪存

( 字 )

SRAM ( 字节 )EEPROM (字节 )

低功耗功能:

• 待机电流:

- 当电压为 2.0V 时,典型值为 100 nA

• 工作电流:

- 当频率为 32 kHz,电压为 2.0V 时,典型值为

- 当频率为 1MHz,电压为 2.0V 时,典型值为

• 看门狗定时器电流

- 当电压为 2.0V 时,典型值为 1 µA

• Timer1 振荡器电流:

- 当频率为 32 kHz,电压为 2.0V 时,典型值为

• 双速内部振荡器:

- 有 4MHz和 48kHz 两种频率可供选择

- 从休眠状态唤醒 4 µs, 3.0V,典型值

外设功能:

• 16 个具有独立方向控制的 I/O 引脚

• 较高灌 / 拉电流用于直接驱动 LED

• 模拟比较器模块带有:

- 两个模拟比较器

- 可编程的片上参考电压 (V

- 可选择的内部或外部参考电压

- 可外部访问比较器输出

• Timer0:带 8 位可编程预分频器的 8 位定时器 / 计数

器

• Timer1:带有外部晶振 / 时钟源功能的16 位定时器/

计数器

• Timer2:带 8 位周期寄存器、预分频器和后分频器

的 8 位定时器 / 计数器

• 捕捉、比较、 PWM 模块

-16位捕捉 / 比较

-10位 PWM

• 可寻址的通用同步 / 异步收发器 USART/SCI

I/O

12 µA

120 µA

1.2 µA

CCP

(PWM)

USART

有

有

有

REF)模块。

比较器

22/1

22/1

22/1

定时器

8/16 位

2005 Microchip Technology Inc. DS40044D_CN 第 1 页

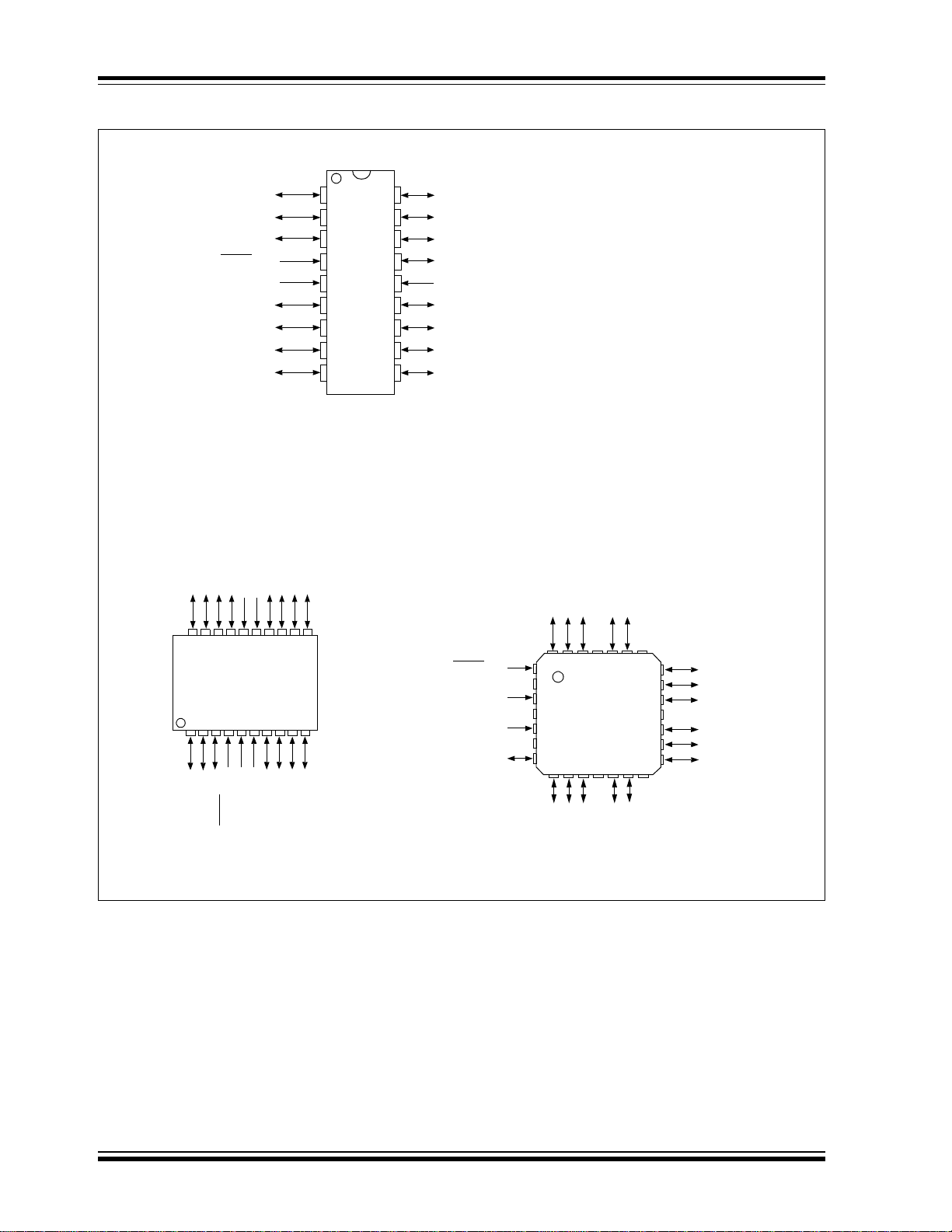

PIC16F627A/628A/648A

引脚图

PDIP 和 SOIC

SSOP

RA2/AN2/V

RA3/AN3/CMP1

RA4/TOCKI/CMP2

RA5/MCLR

RA1/AN1

20

PIC16F627A/628A/648A

1

REF

RA2/AN2/V

RA3/AN3/CMP1

REF

/VPP

VSS

RB0/INT

RB1/RX/DT

RB2/TX/CK

RB3/CCP1

RA6/OSC2/CLKOUT

RA7/OSC1/CLKIN

VDD

RA0/AN0

19181615141312

2 3 4 5 6 7 8 910

VDD

RB6/T1OSO/T1CKI/PGC

RB7/T1OSI/PGD

17

SS

VSS

V

/VPP

RB0/INT

RB1/RX/DT

RA5/MCLR

RA4/TOCKI/CMP2

118

2

3

4

5

6

7

8

9

RB4/PGM

RB5

11

RB3/CCP1

RB2/TX/CK

PIC16F627A/628A/648A

PIC16F627A/628A/648A

17

16

15

14

13

12

11

10

RA1/AN1

RA0/AN0

RA7/OSC1/CLKIN

RA6/OSC2/CLKOUT

DD

V

RB7/T1OSI/PGD

RB6/T1OSO/T1CKI/PGC

RB5

RB4/PGM

28

引脚

QFN

RA5/MCLR/VPP

NC

VSS

NC

VSS

NC

RB0/INT

RA3/AN3/CMP1

RA4/T0CKI/CMP2

RA2/AN2/VREF

NC

2827262524

1

2

3

PIC16F627A/628A

4

PIC16F648A

5

6

7

8

9

10

11

NC

RB3/CCP1

RB2/TX/CK

RB1/RX/DT

RA1/AN1

12

RB4/PGM

RA0/AN0

23

13

RB5

NC

22

21

20

19

18

17

16

15

14

NC

RA7/OSC1/CLKIN

RA6/OSC2/CLKOUT

V

DD

NC

VDD

RB7/T1OSI/PGD

RB6/T1OSO/T1CKI/PGC

DS40044D_CN 第 2 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

目录

1.0 概述 ............................................................................................................................................................................................. 5

2.0 PIC16F627A/628A/648A 器件种类.............................................................................................................................................. 7

3.0 架构综述...................................................................................................................................................................................... 9

4.0 存储器构成 ................................................................................................................................................................................ 15

5.0 I/O 口 ......................................................................................................................................................................................... 31

6.0 Timer0 模块 ............................................................................................................................................................................... 45

7.0 Timer1 模块 ............................................................................................................................................................................... 48

8.0 Timer2 模块 ............................................................................................................................................................................... 52

9.0 捕捉 / 比较 /PWM (CCP)模块 ............................................................................................................................................... 55

10.0 比较器模块 ................................................................................................................................................................................ 61

11.0 参考电压模块 ............................................................................................................................................................................. 67

12.0 通用同步 / 异步收发器 (USART)模块.................................................................................................................................... 71

13.0 数据 EEPROM 存储器 ............................................................................................................................................................... 89

14.0 CPU 的特殊功能 ........................................................................................................................................................................ 95

15.0 指令集综述 .............................................................................................................................................................................. 115

16.0 开发支持.................................................................................................................................................................................. 129

17.0 电气规范 .................................................................................................................................................................................. 135

18.0 直流和交流特性图表................................................................................................................................................................ 151

19.0 封装信息 .................................................................................................................................................................................. 163

附录 A: 数据手册版本历史 ......................................................................................................................................................... 169

附录 B: 器件差异 ....................................................................................................................................................................... 169

附录 C: 器件移植 ....................................................................................................................................................................... 170

附录 D:从其他PICmicro

Microchip 网站 ................................................................................................................................................................................... 171

变更通知客户服务 ............................................................................................................................................................................. 171

客户支持............................................................................................................................................................................................ 171

读者反馈表 ........................................................................................................................................................................................ 172

产品标识体系 .................................................................................................................................................................................... 177

®

器件移植到此系列............................................................................................................................ 170

致 客 户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。 为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。

出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本

数据手册后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号

DS30000 的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到

器件 / 文档存在某些差异时,就会发布勘误表。勘误表上将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

• Microchip 网站 http://www.microchip.com

• 当地 Microchip 销售办事处 (见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统

欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

,例如:DS30000A 是

2005 Microchip Technology Inc. DS40044D_CN 第 3 页

PIC16F627A/628A/648A

注:

DS40044D_CN 第 4 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

1.0 概述

精度双速内部振荡器。 HS 模式是高速晶振。 EC 模式则

是采用外部时钟源。

PIC16F627A/628A/648A 系列单片机是 18 引脚的 8 位

CMOS 闪存单片机,具有多用途、低成本、高性能和全

静态的特点。

®

所有 PICmicro

单片机均采用先进的 RISC 架构。

PIC16F627A/628A/648A 具有增强的内核功能、8 级深

度的堆栈以及多种内部和外部中断源。 哈佛架构独立的

指令总线和数据总线,允许同时取 14 位宽指令字与独

立的 8 位宽数据。 两级指令流水线使得除了程序转移指

令(需要两个周期)以外的所有指令都能在单个周期内

执行。 总共有 35 条指令 (精简指令集)可用,辅之以

大的寄存器组。

PIC16F627A/628A/648A单片机与同类的其他 8 位单片

机相比,通常能实现 2:1 的代码压缩率和 4 倍的速度提

升。

PIC16F627A/628A/648A 器件集成了很多功能部件,从

休眠(断电)模式可以节能。 用户可以通过几种外部中

断、内部中断以及复位将芯片从休眠状态唤醒。

高可靠性的看门狗自带了片上 RC 振荡器,能够避免程

序锁死。

表 1-1 给出了 PIC16F627A/628A/648A 中档单片机系

列的特性。

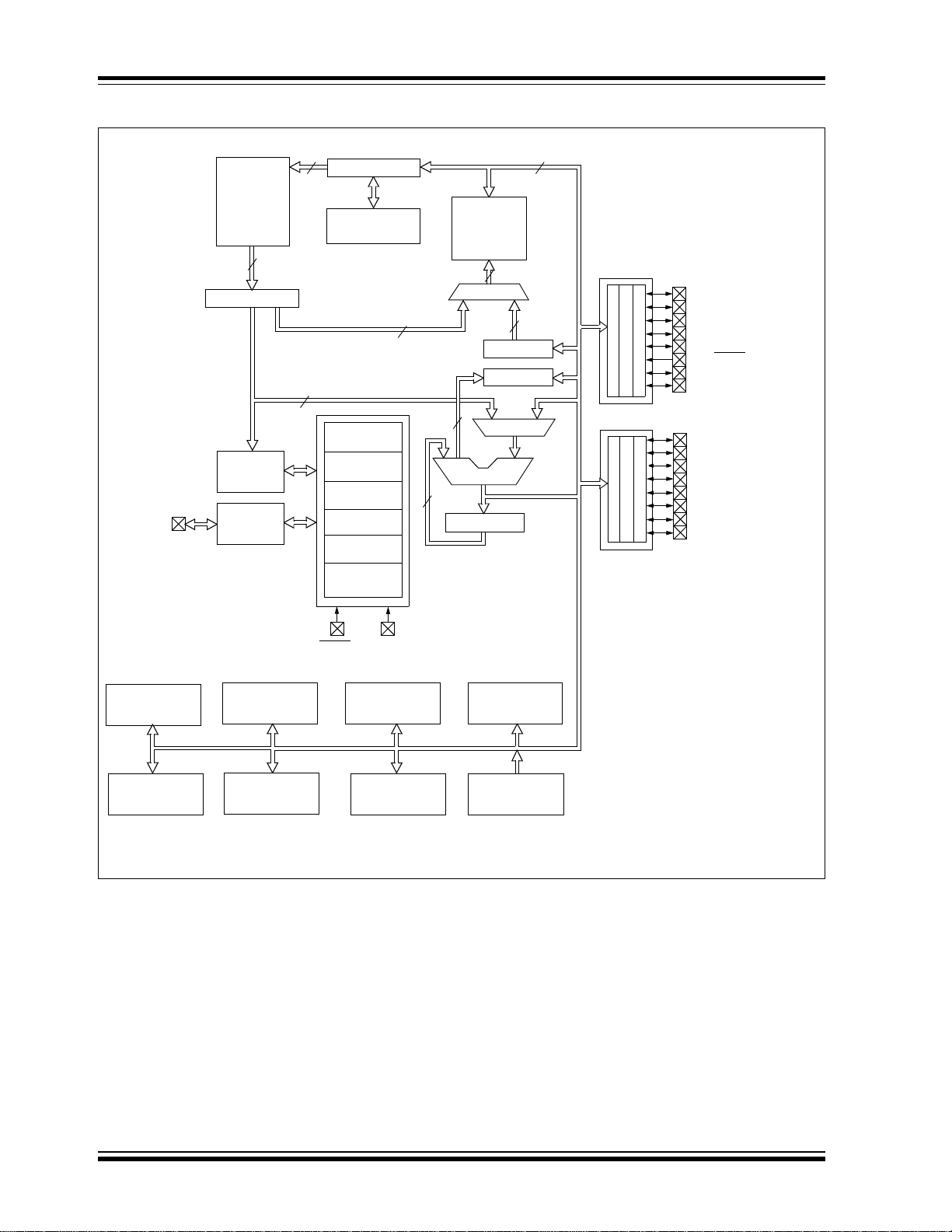

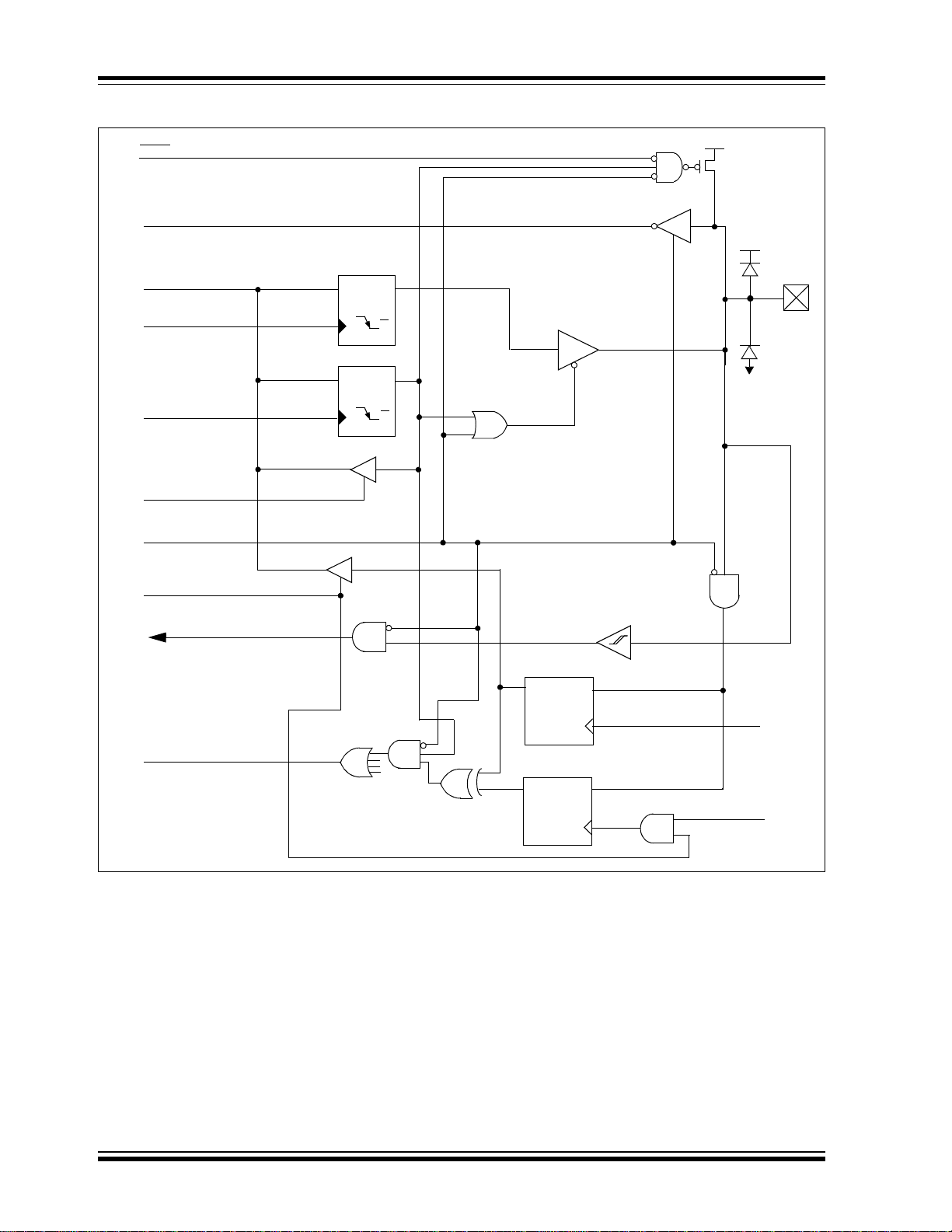

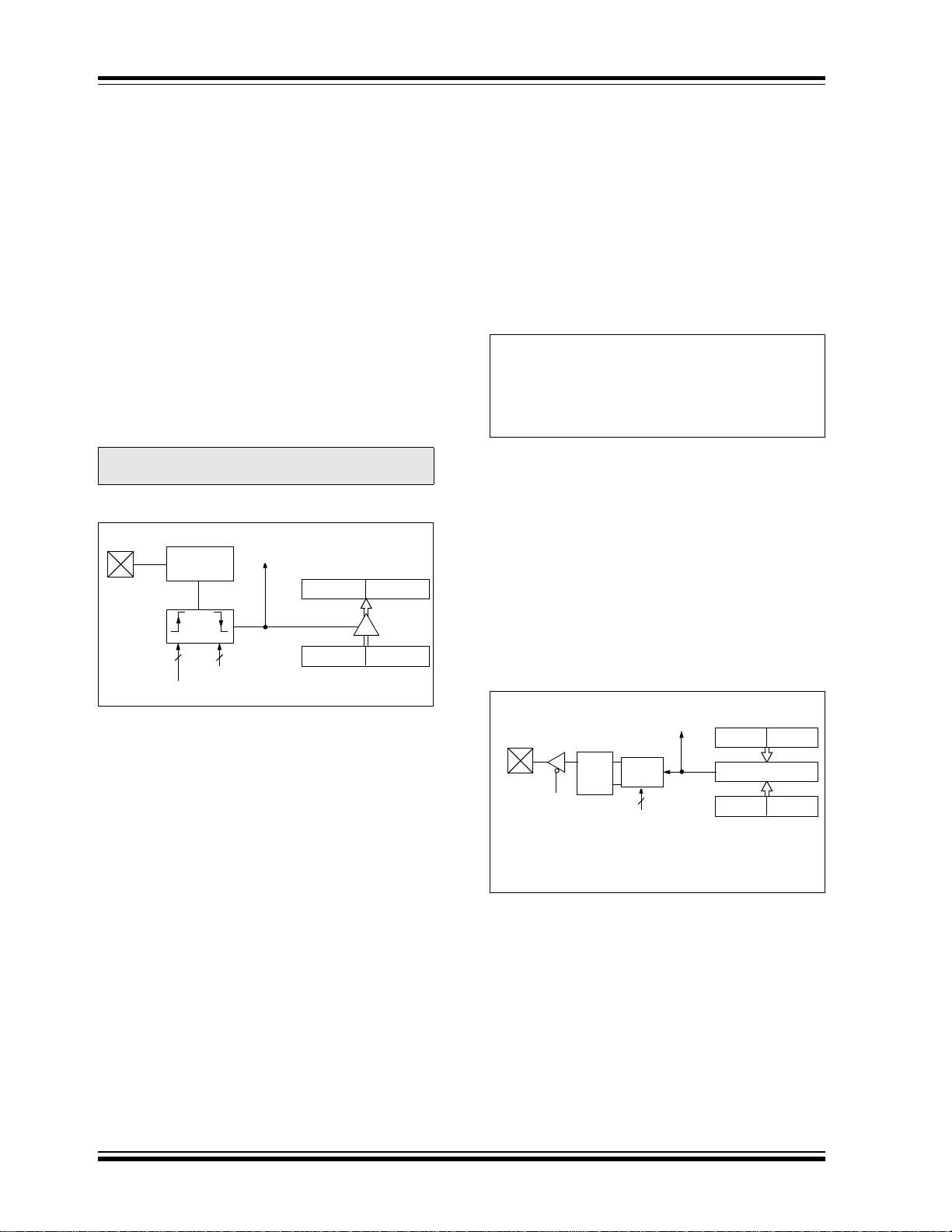

图 3-1 是 PIC16F627A/628A/648A 的简化框图。

PIC16F627A/628A/648A系列适合从电池充电器到低功

耗远程传感器的一系列应用。 闪存技术使得定制应用程

序 (如检测电平、脉冲产生、定时器等)变得十分便

捷。 小尺寸的封装使该系列单片机对于有空间限制的所

有应用都很理想。 低成本、低功耗、高性能、易使用以

及 I/O 的灵活性使得 PIC16F627A/628A/648A 用途非常

广泛。

而减少了外部元件的使用,因此降低了系统成本,提高

了系统可靠性,并降低了功耗。

PIC16F627A/628A/648A有 8 种振荡器配置。 单引脚的

RC 振荡器提供了低成本的解决方案。 LP 振荡器可将功

耗降至最低, XT 是标准晶振,而 INTOSC 是独立的高

1.1 开发支持

支持 PIC16F627A/628A/648A 系列的工具有:功能全面

的宏汇编器、软件模拟器、在线仿真器、低成本在线调

试器、低成本开发编程器和功能前面的编程器。 还可使

用第三方 C 编译器支持工具。

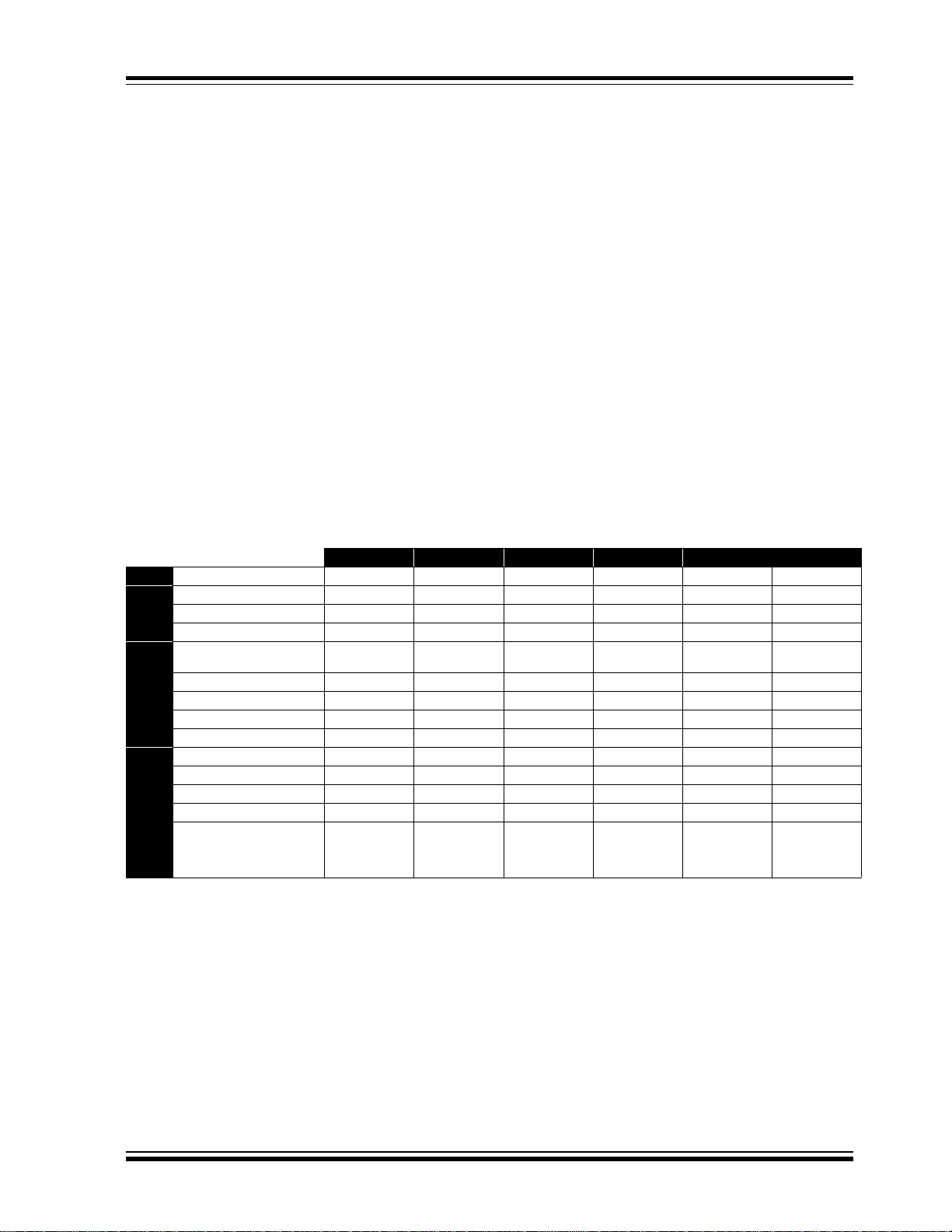

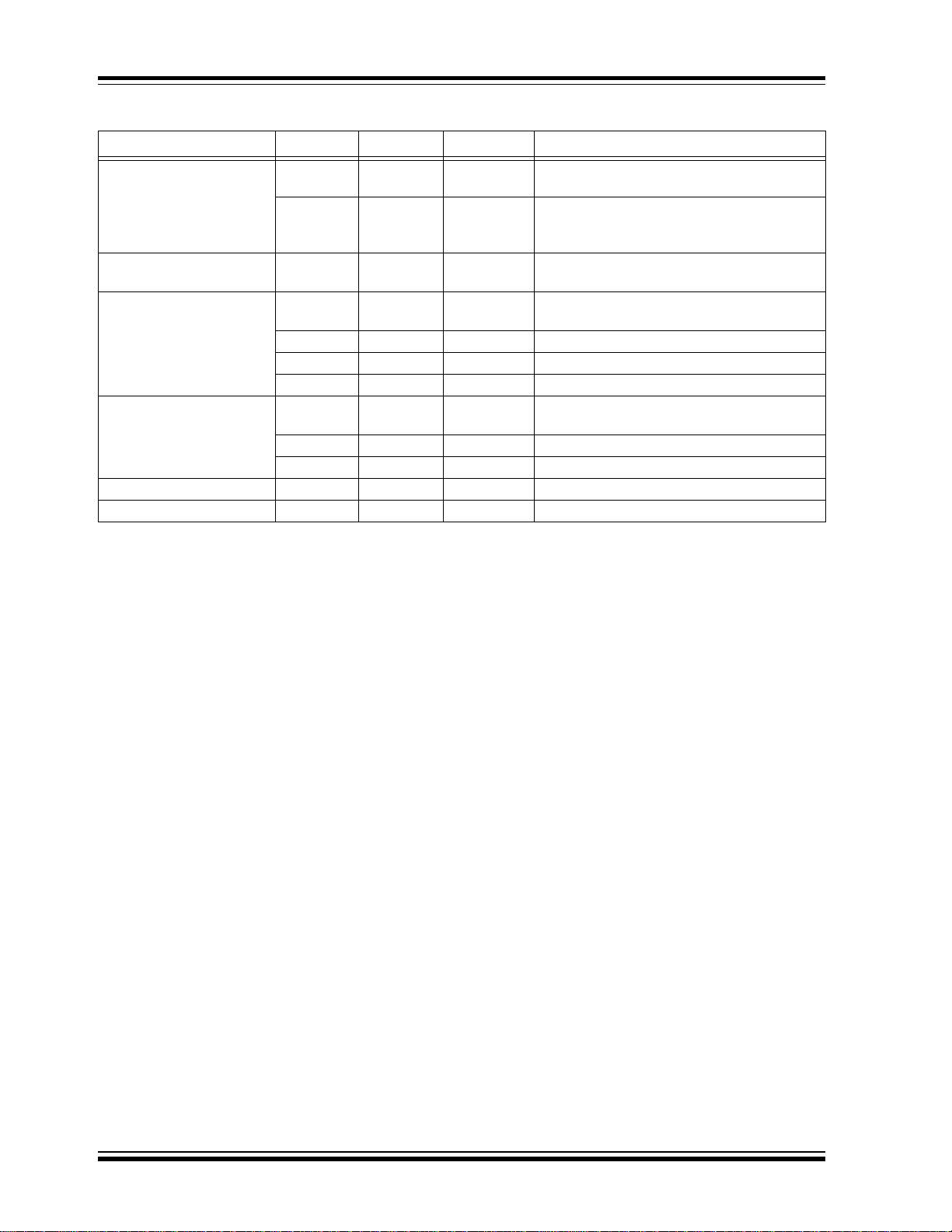

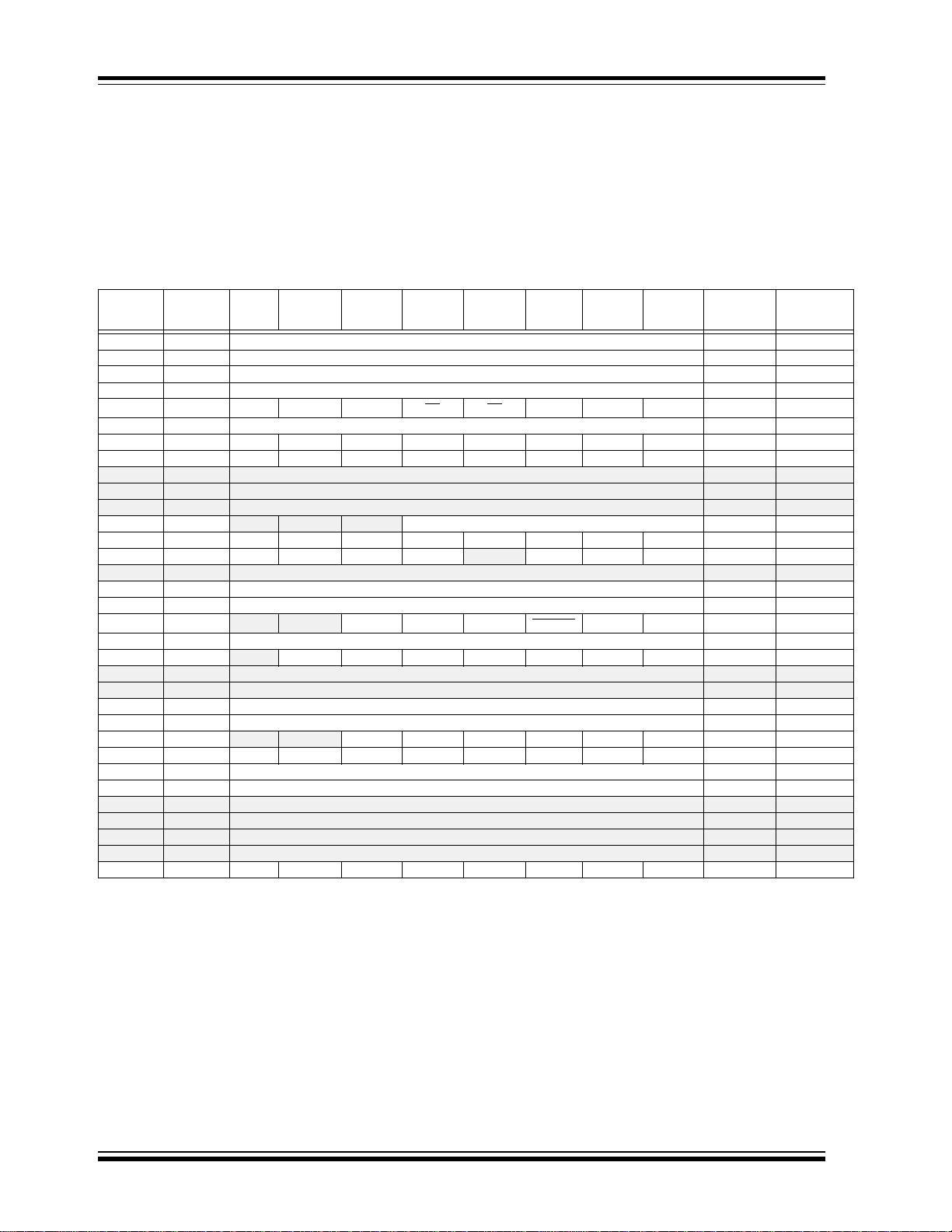

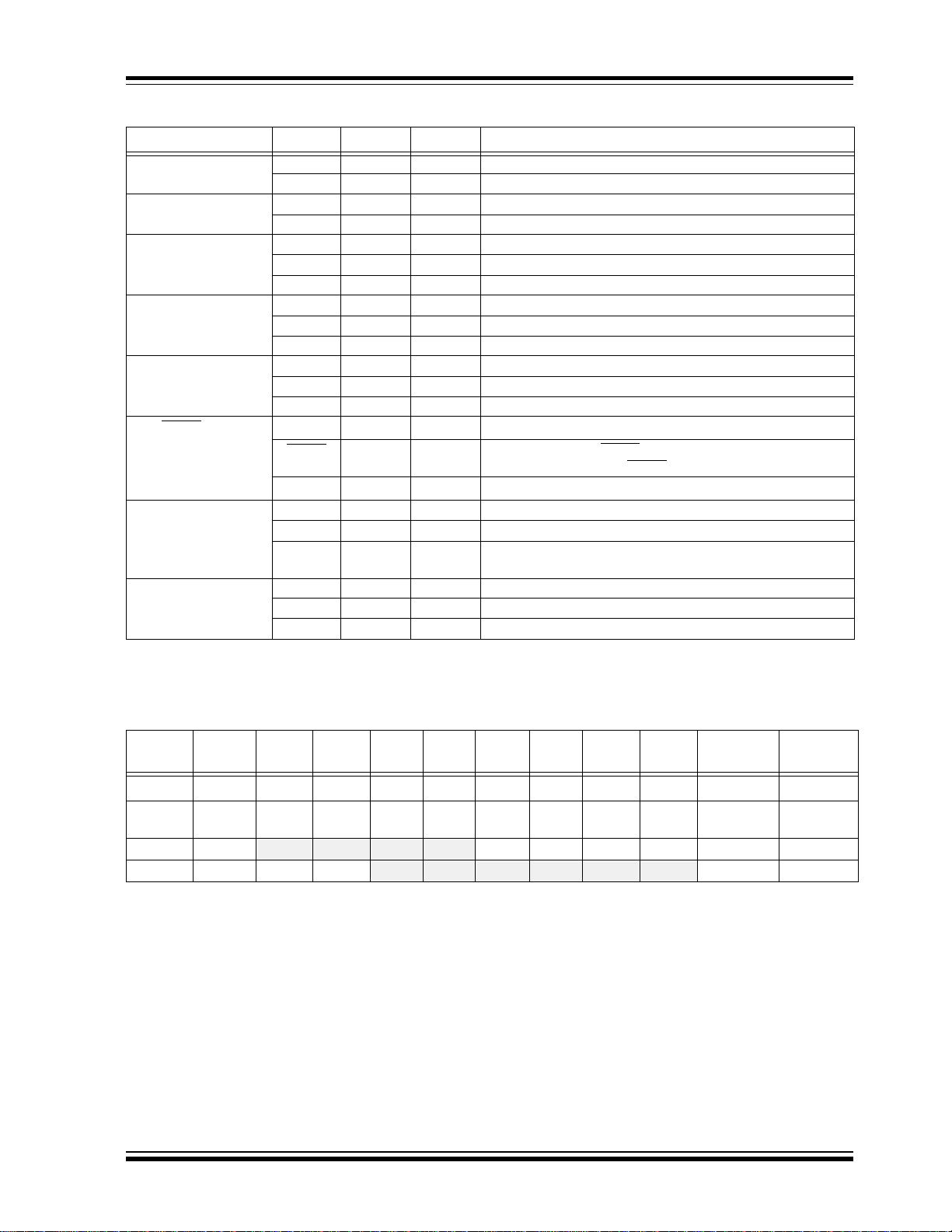

表 1-1: PIC16F627A/628A/648A 系列器件

PIC16F627A PIC16F628A PIC16F648A PIC16LF627A PIC16LF628A PIC16LF648A

时钟 最大工作频率 (MHz)

闪存程序存储器 ( 字 )

存储器 RAM 数据存储器 ( 字节 )

EEPROM 数据存储器 ( 字节 )

定时器模块 TMR0、 TMR1、

比较器

外设 捕捉 / 比较 /PWM 模块

串行通信

内部参考电压 有有有有有有

中断源

I/O 引脚

特性 电压范围 (V)

欠压复位 有有有有有有

封装 18 引脚 DIP 和

PICmicro® 系列的所有器件都有上电复位、可选择的看门狗、可选择的代码保护以及高 I/O 电流性能。

PIC16F627A/628A/648A 系列的所有器件使用时钟引脚 RB6 和数据引脚 RB7 进行串行编程。

20 20 20 20 20 20

1024 2048 4096 1024 2048 4096

224 224 256 224 224 256

128 128 256 128 128 256

TMR2

222222

111111

USART USART USART USART USART USART

10 10 10 10 10 10

16 16 16 16 16 16

3.0-5.5 3.0-5.5 3.0-5.5 2.0-5.5 2.0-5.5 2.0-5.5

SOIC、 20 引脚

SSOP、 28 引脚

QFN

TMR0、 TMR1、

TMR2

18 引脚 DIP 和

SOIC、 20 引脚

SSOP、 28 引脚

QFN

TMR0、 TMR1、

TMR2

18 引脚 DIP 和

SOIC、 20 引脚

SSOP、 28 引脚

QFN

TMR0、 TMR1、

SSOP、 28 引脚

TMR2

18 引脚 DIP 和

SOIC、 20 引脚

QFN

TMR0、 TMR1、

TMR2

18 引脚 DIP 和

SOIC、 20 引脚

SSOP、 28 引脚

QFN

TMR0、 TMR1、

TMR2

18 引脚 DIP 和

SOIC、 20 引脚

SSOP、 28 引脚

QFN

2005 Microchip Technology Inc. DS40044D_CN 第 5 页

PIC16F627A/628A/648A

注:

DS40044D_CN 第 6 页 2005 Microchip Technology Inc.

2.0 PIC16F627A/628A/648A 器件种

类

有多种频率和封装类型可供选择。 根据应用和生产要

求,可以通过器件数据手册最末的“PIC16F627A/

628A/648A 产品识别体系”来选择适当的器件。 在订购

器件的时候,也请使用数据手册的这一页来指定正确的

器件编号。

2.1 闪存器件

闪存器件是电可擦除和再编程的。 这样可以在样片开

发、试用和产品生产中都使用相同的器件。

电可擦除闪存更大的优点是它可以在线或使用器件编程

器(例如 Microchip 的PICSTART

II 编程器)进行擦除或重新编程。

2.2 快速批量生产 (Quick-Turnaround-

Production, QTP)器件

Microchip 为工厂生产订单提供 QTP 编程服务。 这种服

务适用于那些不想对中到大批量单片机编程,并且代码

已经相对稳定的用户。 这些器件是标准的闪存器件,只

是所有的编程单元和配置已在出厂前设定。 Microchip

还在出厂前对某些代码和样片进行了校验。 欲了解更详

细信息,请联系当地 Microchip 销售办事处。

®

Plus 或 PRO MATE

PIC16F627A/628A/648A

®

2.3 带序列号的快速批量生产

(Serialized Quick-Turnaround-

Production, SQTP

Microchip 提供一种独特的编程服务,可用不同的序列

号对每个器件中的几处用户自定义单元进行编程。 这些

序列号可以是随机数、伪随机数或连续数。

这种串行编程使每个器件具有唯一的序列号,可以作为

登录码、口令或用户识别码。

SM

)器件

2005 Microchip Technology Inc. DS40044D_CN 第 7 页

PIC16F627A/628A/648A

注:

DS40044D_CN 第 8 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

3.0 架构综述

PIC16F627A/628A/648A 系列的高性能可以归功于

RISC 微处理器中普遍采用的架构特点。首先,

PIC16F627A/628A/648A 采用了哈佛架构,在这个架构

中,分别使用独立的总线从独立的存储器中存取程序和

数据。 与传统的程序和数据存储器合二为一的冯·诺依

曼架构相比,哈佛架构具有更加优良的总线带宽。 独立

的程序和数据存储器允许指令宽度超过 8 位。 由于指令

操作码为14 位宽,所以所有指令都可以是单字指令。 通

过 14 位宽的程序存储器总线可以在单周期内取一条 14

位的指令。 两级流水线可以使取指和执行指令同时进

行。 因此,除了程序转移指令以外,所有指令(35 条)

都可以在单周期 (时钟频率为 20 MHz 时为 200ns)内

执行。

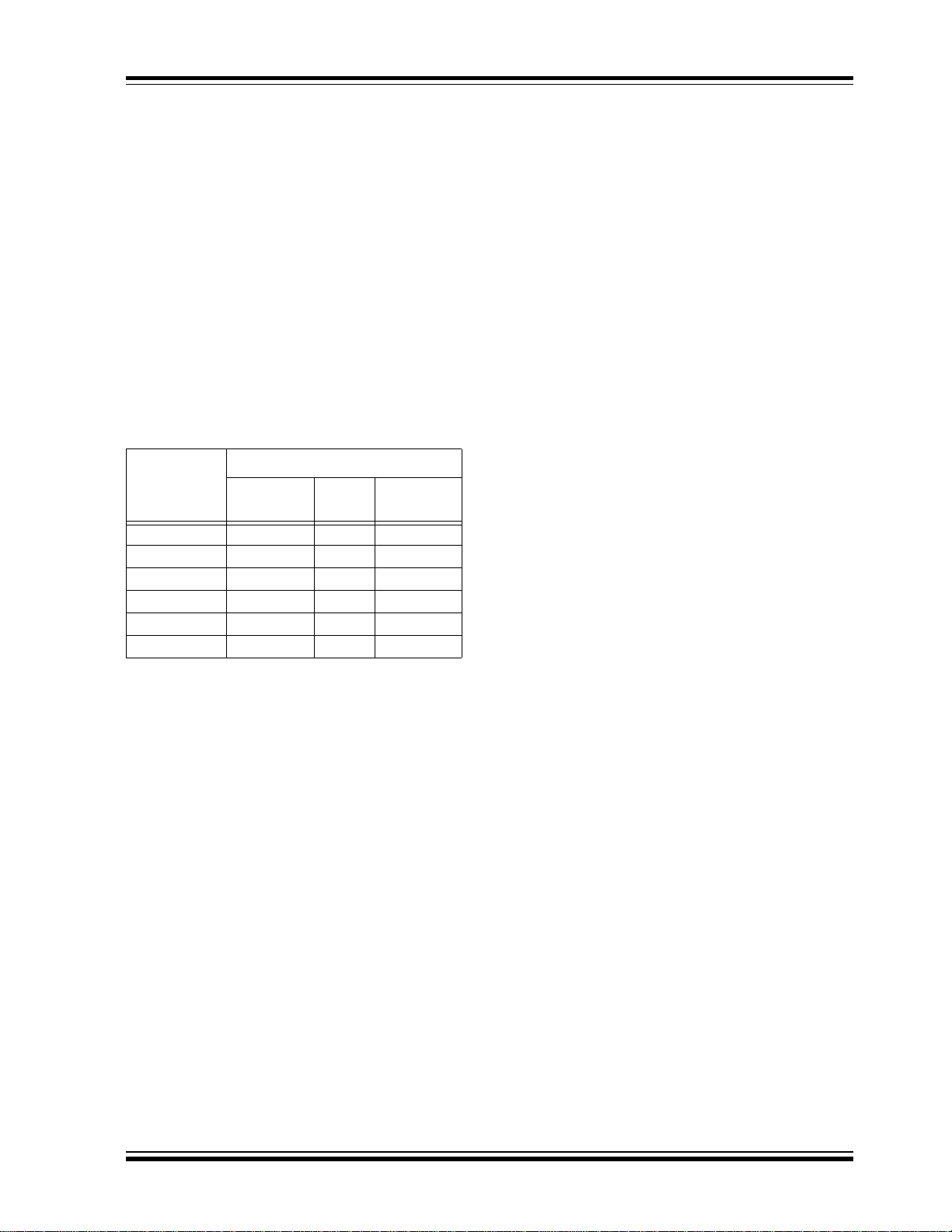

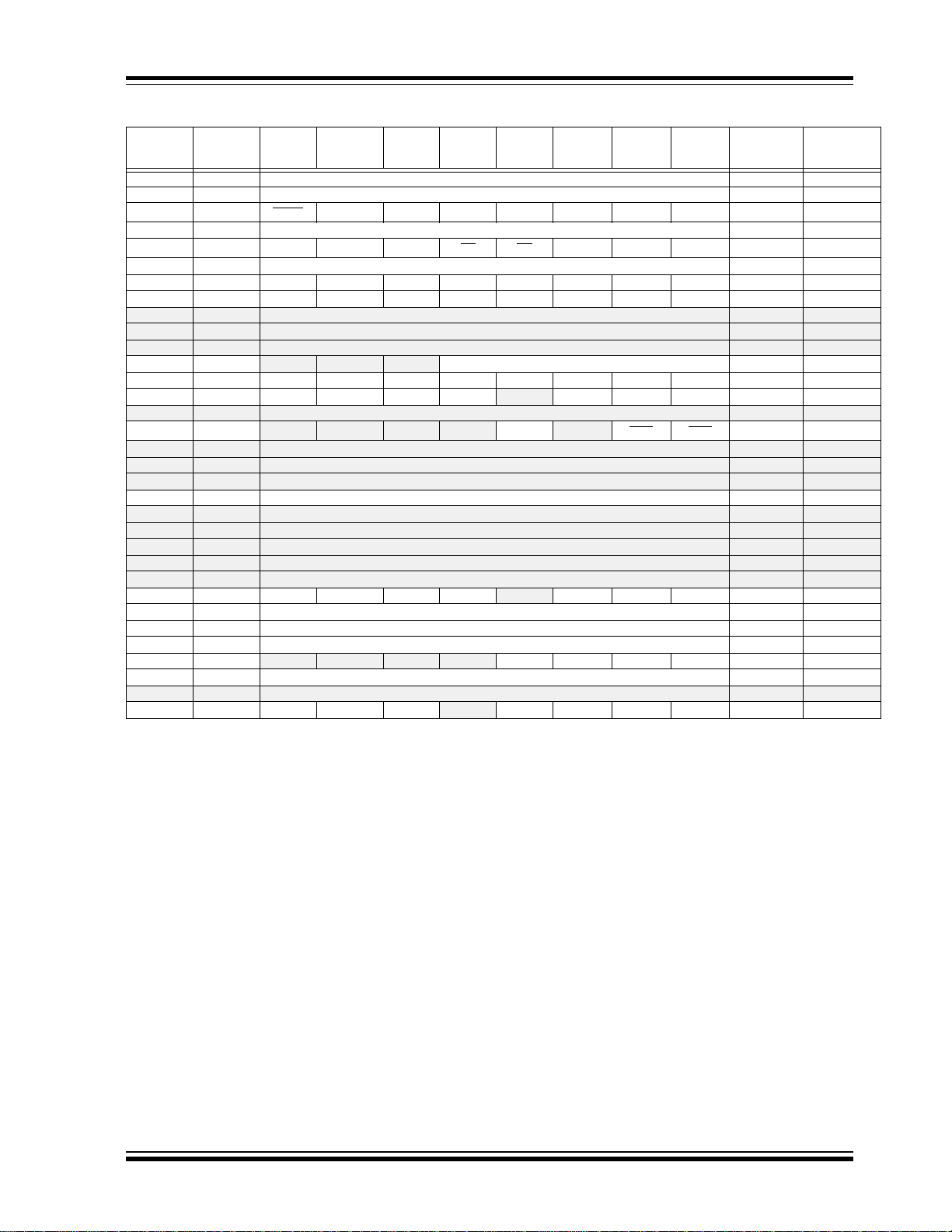

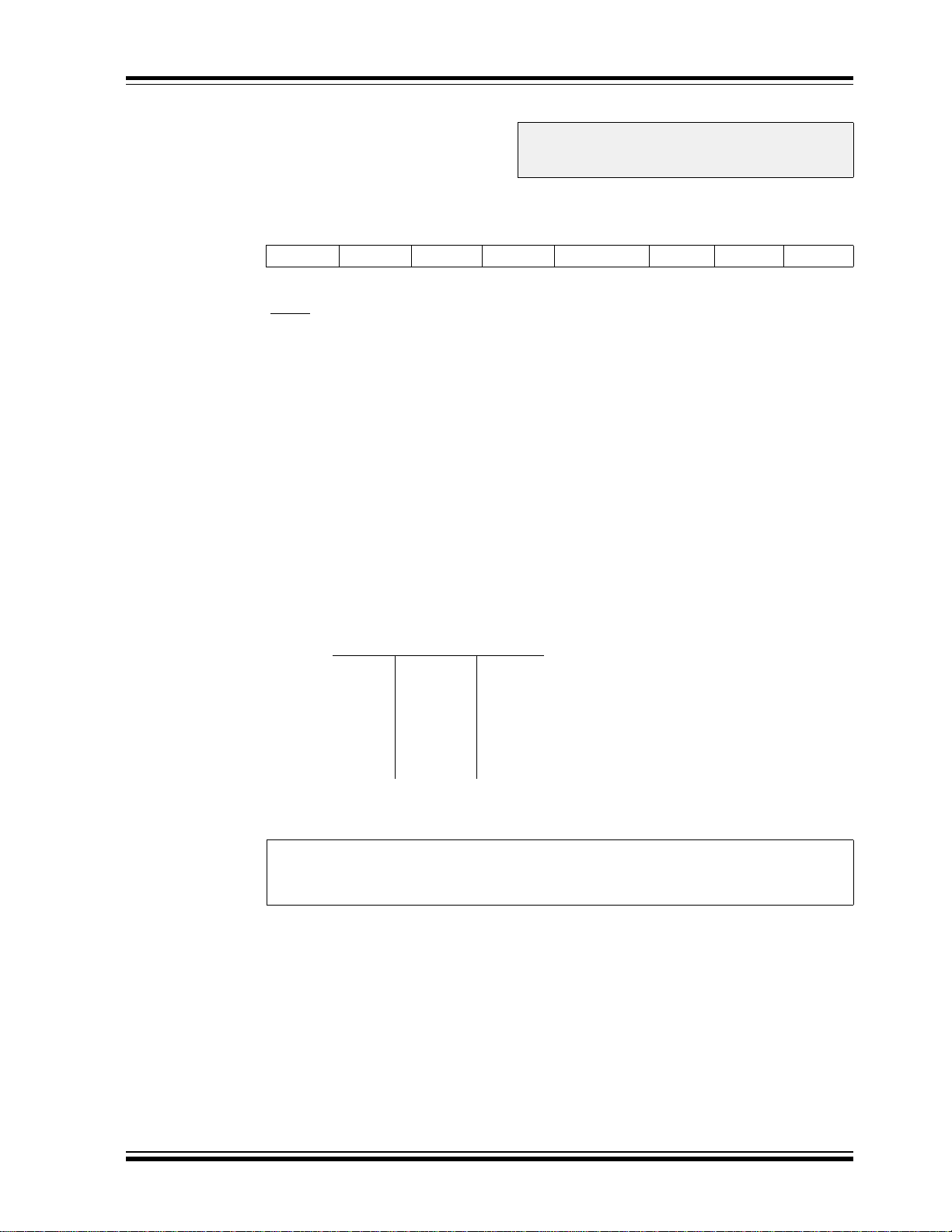

表 3-1 所列为器件的存储器容量(闪存、数据存储器和

EEPROM)。

表 3-1: 器件存储器列表

存储器

器件

PIC16F627A 1024 x 14 224 x 8 128 x 8

PIC16F628A 2048 x 14 224 x 8 128 x 8

PIC16F648A 4096 x 14 256 x 8 256 x 8

PIC16LF627A 1024 x 14 224 x 8 128 x 8

PIC16LF628A 2048 x 14 224 x 8 128 x 8

PIC16LF648A 4096 x 14 256 x 8 256 x 8

闪存

程序

数据

RAM数据EEPROM

PIC16F627A/628A/648A 可以直接或间接的寻址它的文

件寄存器或数据存储器。 所有特殊功能寄存器(Special

Function Register, SFR),包括程序计数器,都映射

到数据存储器空间。 PIC16F627A/628A/648A 有一个正

交 (对称)指令集,因此它可以使用任何寻址模式对任

一寄存器执行任何操作。 指令集的对称特性以及无“特

别理想状态”让使用 PIC16F627A/628A/648A 编程更简

单有效。 此外,所有这些都显著地简化了学习过程。

PIC16F627A/628A/648A 器件包含一个 8 位ALU 和工作

寄存器。 ALU 是一个通用的算术单元。 它对工作寄存器

和任何文件寄存器中的数据进行算术和布尔运算。

ALU 为 8 位宽,能够进行加、减、移位和逻辑操作。 除

非特别指明,否则算术运算一般是以 2 进制补码的形式

进行的。 在双操作数指令中,一般情况下,其中的一个

操作数是在工作寄存器(W 寄存器)中。 另一个操作数

存放在一个文件寄存器中或是立即数。 在单操作数指令

中,操作数放在 W 寄存器中或某个文件寄存器中。

W 寄存器是一个 8 位宽、用于 ALU 运算的工作寄存器。

该寄存器不可寻址。

根据所执行的指令,ALU 可能影响 Status 寄存器中的进

位标志位 C、辅助进位标志位 DC 和全零标志位 Z。 在

减法操作中,C 和 DC 位分别作为借位和辅助借位标志

位。 例如指令 SUBLW 和 SUBWF。

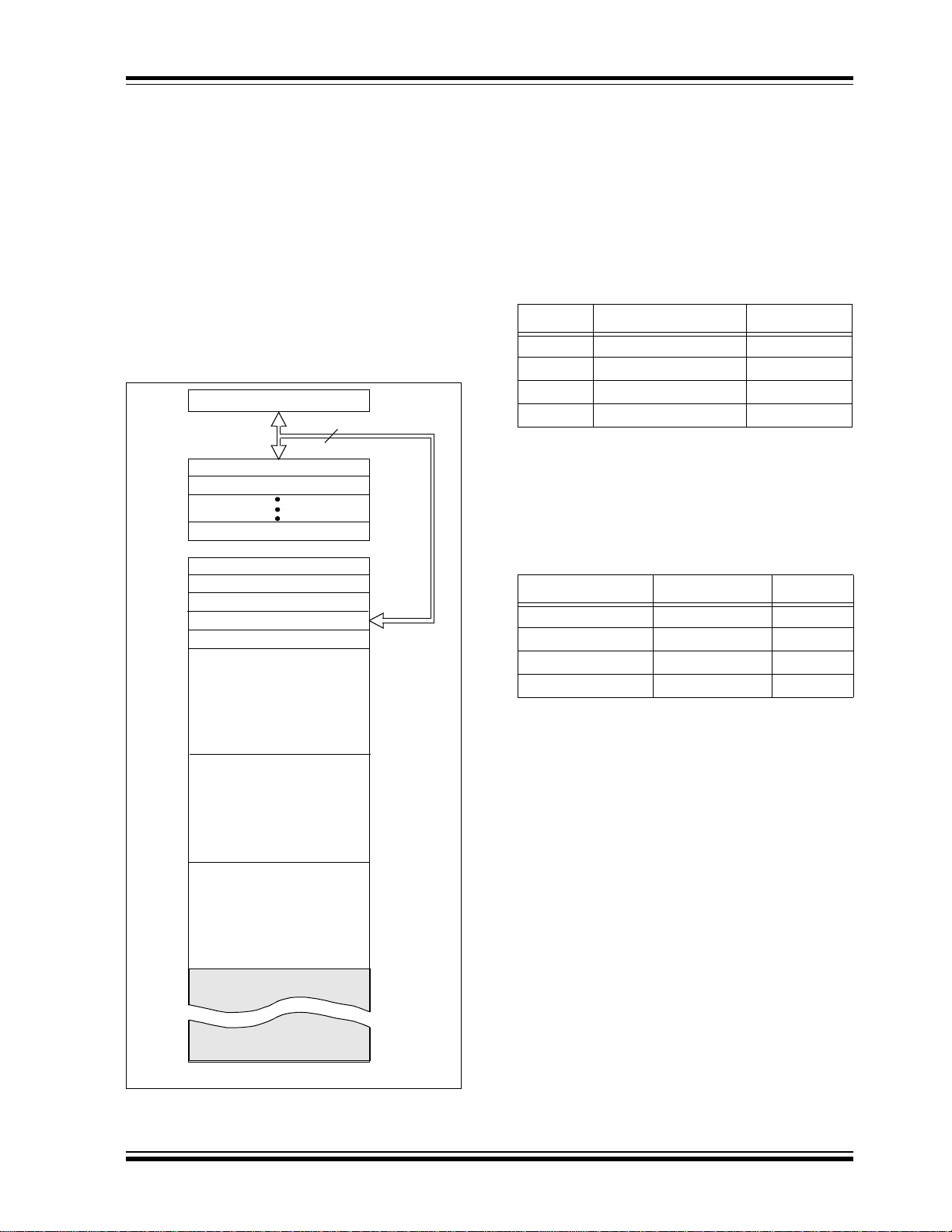

图 3-1 给出了简化框图,表 3-2 对器件引脚作了描述。

PIC16F627A/628A/648A器件上提供了两种类型的数据

存储器。 所提供的非易失性 EEPROM 数据存储器用于

长期存储数据,例如校准值、查表数据以及其他可能需

要现场定期更新的数据。 这些数据类型不会在掉电时丢

失。 所提供的另一个数据存储器是常规的 RAM 数据存

储器。 常规的 RAM 数据存储器用于对正常操作中的数

据进行临时存储。 这些数据会在掉电时丢失。

2005 Microchip Technology Inc. DS40044D_CN 第 9 页

PIC16F627A/628A/648A

图 3-1: 结构框图

程序

总线

OSC1/CLKIN

OSC2/CLKOUT

闪存

程序

存储器

14

指令寄存器

指令

译码与

控制

时序

产生

13

8

程序计数器

8 级堆栈

(13 位)

直接寻址

上电延时

定时器

振荡器

起振定时器

上电

复位

看门狗

定时器

欠压

复位

低电压

编程

RAM 地址(1)

7

3

8

数据总线

RAM

文件

寄存器

9

地址多路开关

8

FSR 寄存器

Stat us 寄存器

MUX

ALU

W 寄存器

8

间接

寻址

PORTA

PORTB

RA0/AN0

RA1/AN1

RA2/AN2/VREF

RA3/AN3/CMP1

RA4/T0CK1/CMP2

RA5/MCLR

RA6/OSC2/CLKOUT

RA7/OSC1/CLKIN

RB0/INT

RB1/RX/DT

RB2/TX/CK

RB3/CCP1

RB4/PGM

RB5

RB6/T1OSO/T1CKI/PGC

RB7/T1OSI/PGD

/VPP

MCLR

比较器

VREF

Timer0 Timer1 Timer2

注: 高位来自 Status 寄存器。

VDD, VSS

USARTCCP1

数据 EEPROM

DS40044D_CN 第 10 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

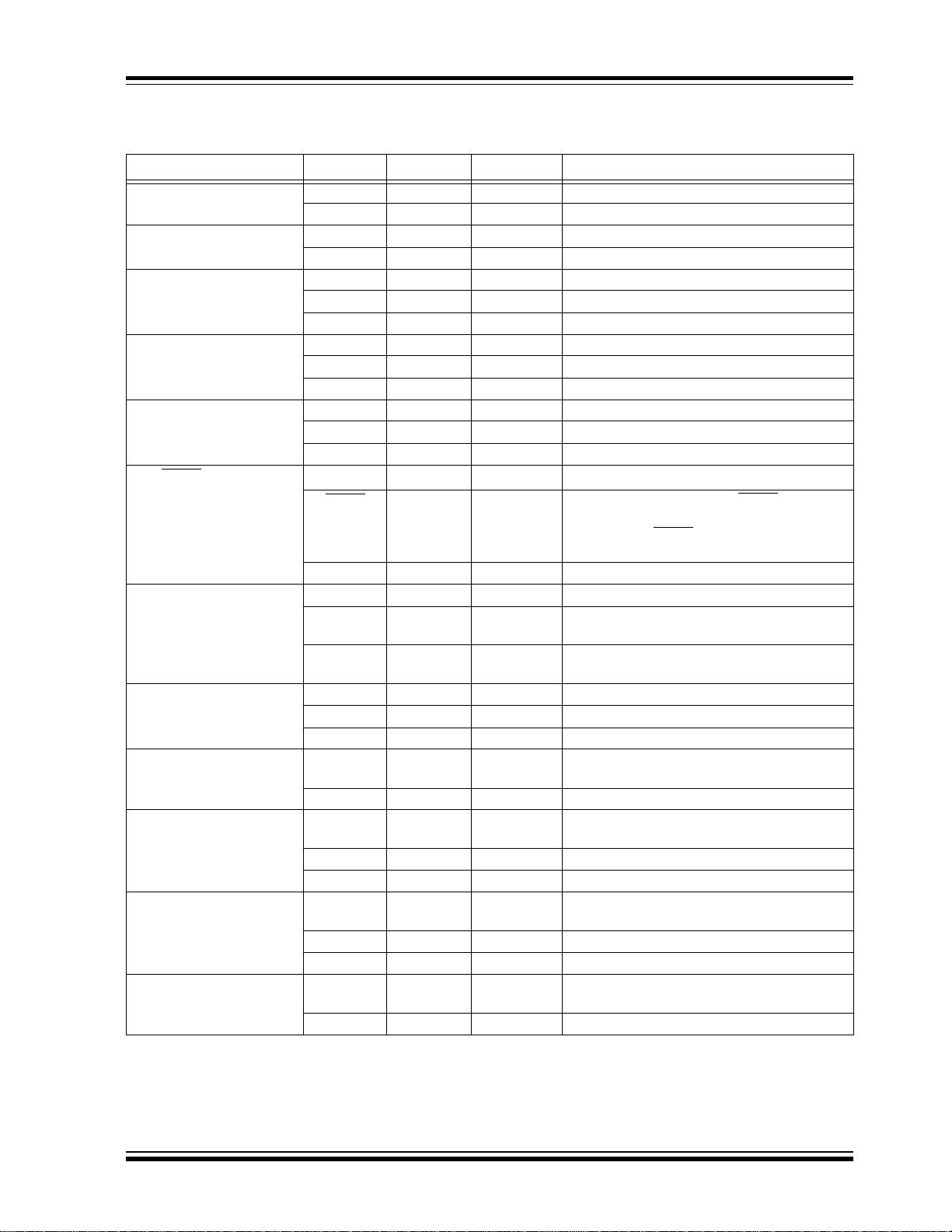

表 3-2: PIC16F627A/628A/648A 引脚配置描述

名称 功能 输入类型 输出类型 描述

RA0/AN0 RA0 ST CMOS

AN0 AN

RA1/AN1 RA1 ST CMOS

AN1 AN

RA2/AN2/V

RA3/AN3/CMP1 RA3 ST CMOS

RA4/T0CKI/CMP2 RA4 ST OD

RA5/MCLR

RA6/OSC2/CLKOUT RA6 ST CMOS

RA7/OSC1/CLKIN RA7 ST CMOS

RB0/INT RB0 TTL CMOS

RB1/RX/DT RB1 TTL CMOS

RB2/TX/CK RB2 TTL CMOS

RB3/CCP1 RB3 TTL CMOS

图注: O=输出 CMOS = CMOS 输出 P=电源

REF RA2 ST CMOS

AN2 AN

REF

V

AN3 AN

CMP1

T0CKI ST

CMP2

/VPP RA5

MCLR

PP

V

OSC2

CLKOUT

OSC1 XTAL

CLKIN ST

INT ST

RX ST

DT ST CMOS

TX

CK ST CMOS

CCP1 ST CMOS

— =未使用 I = 输入 ST = 施密特触发器输入

TTL = TTL 输入 OD = 漏极开路输出 AN = 模拟

-

-

-

ST

ST

- - 编程电压输入

-

-

-

- 模拟比较器输入

- 模拟比较器输入

- 模拟比较器输入

AN

- 模拟比较器输入

CMOS

- Timer0 时钟输入

OD

- 输入端口

-

XTAL

CMOS

- 振荡器晶振输入

- 外部时钟源输入。 RC 偏置引脚。

- 外部中断。

- USART 接收引脚

CMOS

双向 I/O 端口

双向 I/O 端口

双向 I/O 端口

VREF 输出

双向 I/O 端口

比较器 1 输出

双向 I/O 端口

比较器 2 输出

主复位。 如果将引脚配置为 MCLR

低电平有效的引脚,即低电平时器件复位。 器

件正常运行时 MCLR/VPP 上的电压不能超过

DD 。

V

双向 I/O 端口

振荡器晶振输出。 在晶体振荡器模式连接到晶

振或谐振器。

在 RC/INTOSC 模式, OSC2 引脚可以输出

CLKOUT,其频率为 OSC1 的 1/4。

双向 I/O 端口

双向 I/O 端口。 可以软件编程实现内部弱上

拉。

双向 I/O 端口。 可以软件编程实现内部弱上

拉。

同步数据 I/O

双向 I/O 端口。 可以软件编程实现内部弱上

拉。

USART 发送引脚

同步时钟 I/O

双向 I/O 端口。 可以软件编程实现内部弱上

拉。

捕捉 / 比较 /PWM I/O

,这是一个

2005 Microchip Technology Inc. DS40044D_CN 第 11 页

PIC16F627A/628A/648A

表 3-2: PIC16F627A/628A/648A 引脚配置描述 (续)

名称 功能 输入类型 输出类型 描述

RB4/PGM RB4 TTL CMOS

PGM ST

RB5 RB5 TTL CMOS

RB6/T1OSO/T1CKI/PGC RB6 TTL CMOS

T1OSO

T1CKI ST

PGC ST

RB7/T1OSI/PGD RB7 TTL CMOS

T1OSI XTAL

PGD ST CMOS

V

SS VSS

DD VDD

V

图注: O=输出 CMOS = CMOS 输出 P=电源

— =未使用 I = 输入 ST = 施密特触发器输入

TTL = TTL 输入 OD = 漏极开路输出 AN = 模拟

-

电源 - 逻辑和 I/O 引脚的接地参考点

电源 - 逻辑和 I/O 引脚的正电源

- 低电压编程输入引脚。 当低电压编程被使能

XTAL

- Timer1 时钟输入。

- ICSP

- Timer1 振荡器输入。

双向 I/O 端口。 引脚电平变化可触发中断。 可

以软件编程实现内部弱上拉。

时,禁止引脚电平变化触发中断以及弱上拉电

阻。

双向 I/O 端口。 引脚电平变化可触发中断。 可

以软件编程实现内部弱上拉。

双向 I/O 端口。 引脚电平变化可触发中断。 可

以软件编程实现内部弱上拉。

Timer1 振荡器输出。

TM

编程时钟。

双向 I/O 端口。 引脚电平变化可触发中断。 可

以软件编程实现内部弱上拉。

ICSP 数据 I/O

DS40044D_CN 第 12 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

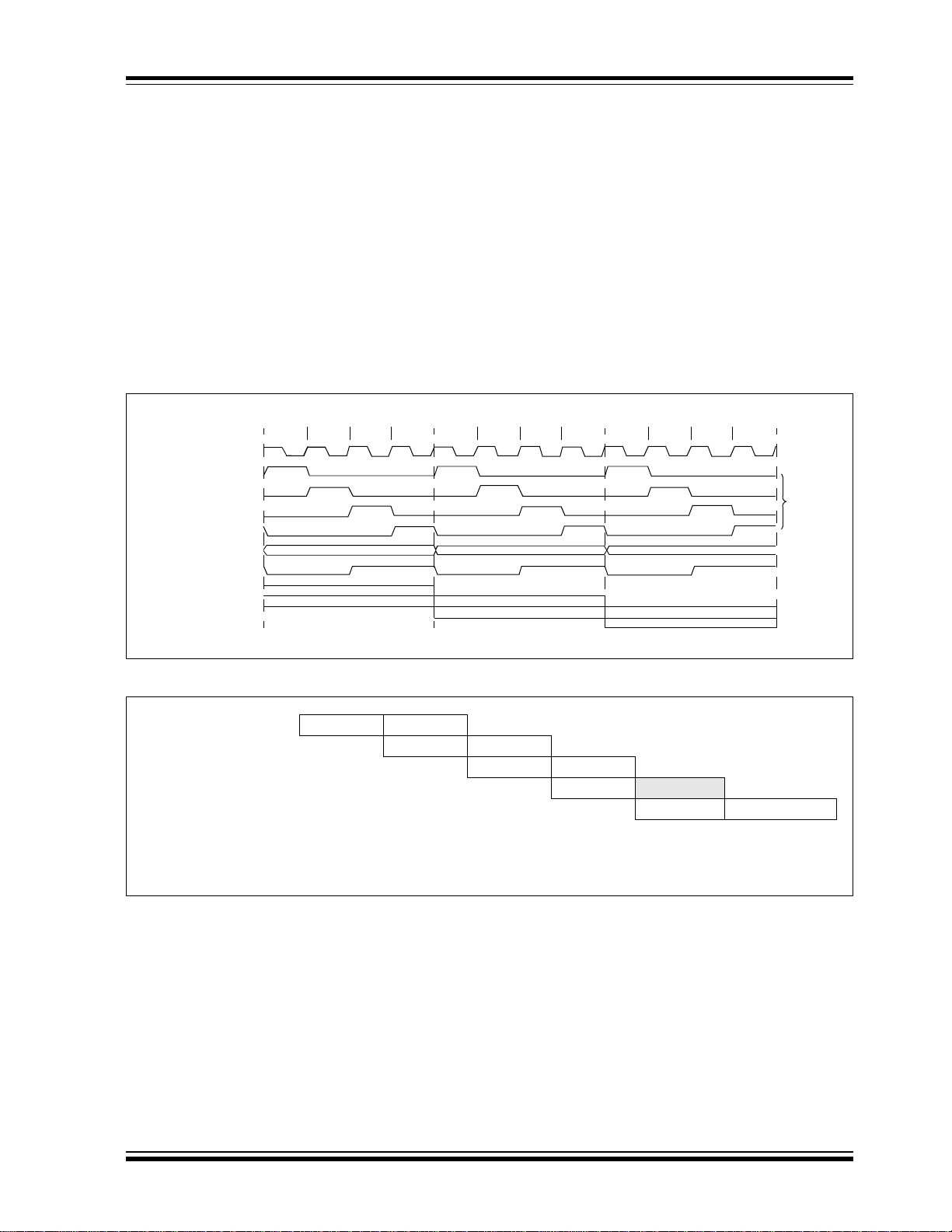

3.1 时序图 / 指令周期

时钟输入 (OSC1/CLKIN/RA7 引脚)信号在器件内部

经过 4 分频后产生 4 个不重叠的正交时钟信号,即 Q1、

Q2、Q3 和 Q4。 在此过程中,程序计数器(PC)在每

个 Q1 时递增 1,并在 Q4 时从程序存储器取指并将指令

锁存到指令寄存器中。 在接下来的 Q1 到 Q4 周期中进

行指令的译码和执行。 图 3-2所示为时钟和指令执行流

程。

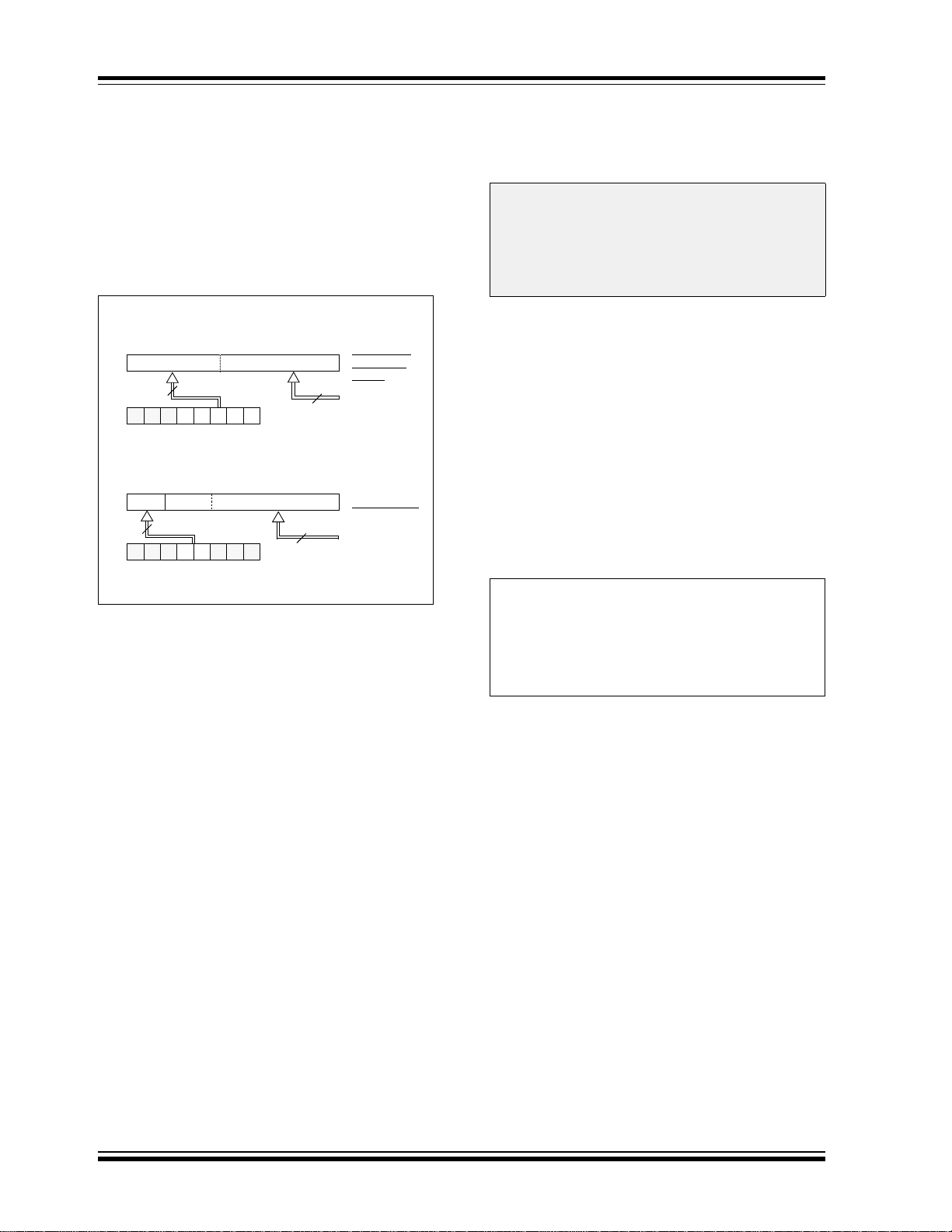

图 3-2:时钟/ 指令周期

Q2 Q3 Q4

OSC1

Q1

Q2

Q3

Q4

PC

CLKOUT

Q1

PC PC+1 PC+2

取指(PC)

执行指令(PC-1)取指(PC+1)

Q1

3.2 指令流 / 流水线

一个指令周期由 4 个 Q 周期组成 (Q1、 Q2、 Q3 和

Q4)。 取指和执行指令是流水线操作的,用一个指令周

期来取指,而用另一个指令周期来译码和执行取到的指

令。 但由于是流水线操作,所以每条指令的等效执行时

间都是一个指令周期。 如果指令(例如,GOTO)改变

了程序计数器,则需要两个指令周期来完成指令

(例 3-1)。

在 Q1 周期开始取指操作,程序计数器 (PC)加 1。

指令的执行过程:在 Q1 周期,将所取指令锁存到指令

寄存器(IR)。 在 Q2、Q3 和 Q4 周期中进行指令的译

码和执行。 其中读数据存储器 (读操作数)发生在 Q2

周期,写操作发生在 Q4 周期 (写入目标单元)。

Q2 Q3 Q4

执行指令(PC)取指(PC+2)

Q2 Q3 Q4

Q1

执行指令(PC+1)

内部

相位

时钟

例 3-1: 指令流水线流程图

1. MOVLW 55h

2. MOVWF PORTB

3. CALL SUB_1

4. BSF PORTA, 3

注: 除程序转移指令外,所有指令都是单周期指令。 由于程序转移指令导致取出的指令被从流水线中舍弃,需要重

新取指再执行指令,所以程序转移指令需要两个周期。

取指 1 执行 1

取指 2 执行 2

取指 3 执行 3

取指 4

舍弃

取指 SUB_1 执行 SUB_1

2005 Microchip Technology Inc. DS40044D_CN 第 13 页

PIC16F627A/628A/648A

注:

DS40044D_CN 第 14 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

4.0 存储器构成

4.1 程序存储器构成

PIC16F627A/628A/648A 有一个 13 位的程序计数器,

能寻址 8K x 14 的程序存储器空间。物理实现的只有

PIC16F627A 使用的第一个 1K x 14(0000h - 03FFh)

单元、PIC16F628A 使用的 2K x 14(0000h - 07FFh)

单元和 PIC16F648A 使用的 4K x 14 (0000h-0FFFH)

单元。对超出以上范围的单元寻址时,将会导致在第一

个 1K x 14 空间 (PIC16F627A)、2K x 14 空间

(PIC16F628A)或 4K x 14 空间 (PIC16F648A)内部

溢出返回。复位矢量位于 0000h,中断矢量位于 0004h

(图 4-1)。

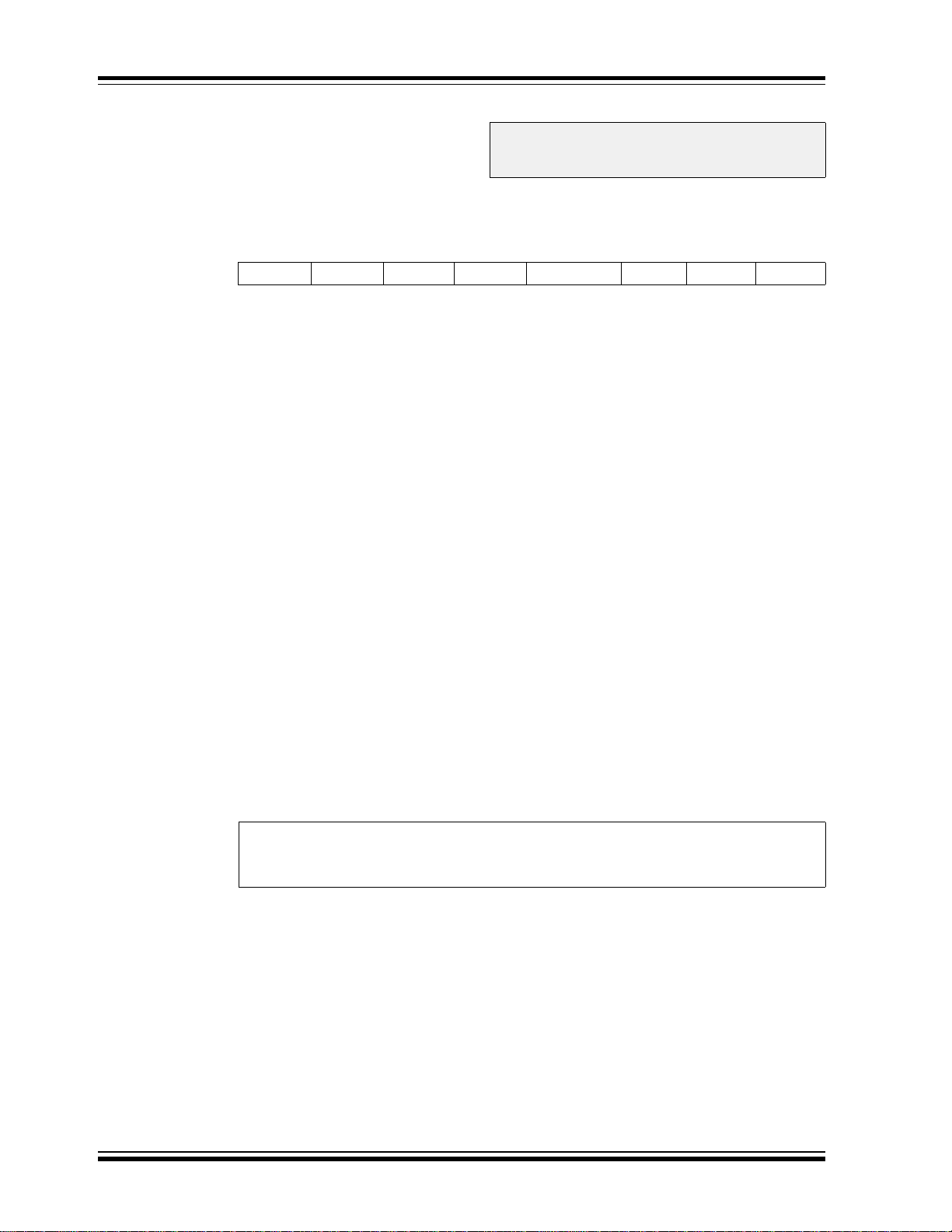

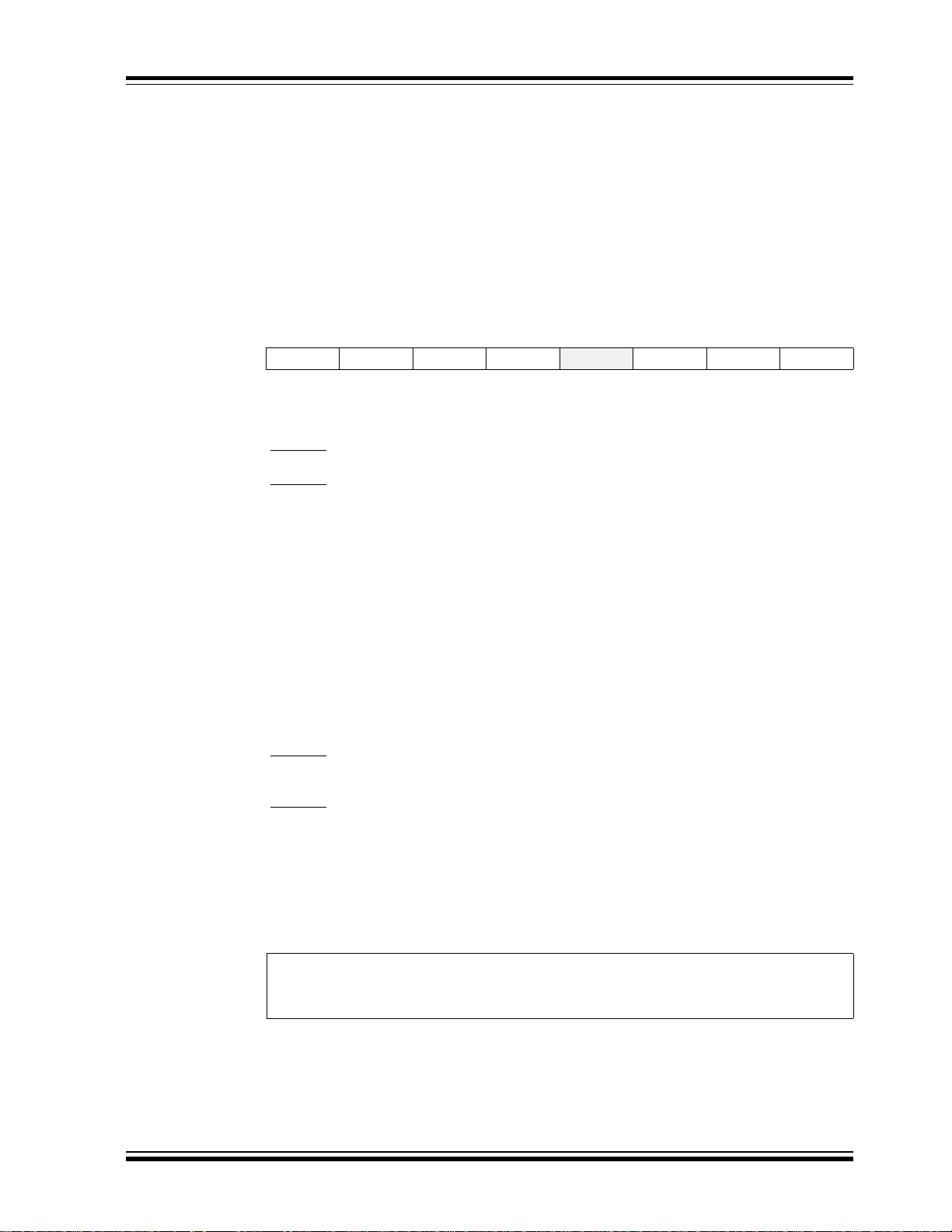

图 4-1: 程序存储器映射和堆栈

PC<12:0>

CALL, RETURN

RETFIE, RETLW

PIC16F627A、

PIC16F628A 和

PIC16F648A

PIC16F628A 和

PIC16F648A

堆栈深度 1

堆栈深度 2

堆栈深度 8

复位矢量

中断矢量

片上程序

存储器

片上程序

存储器

13

0000h

0004

0005

03FFh

07FFh

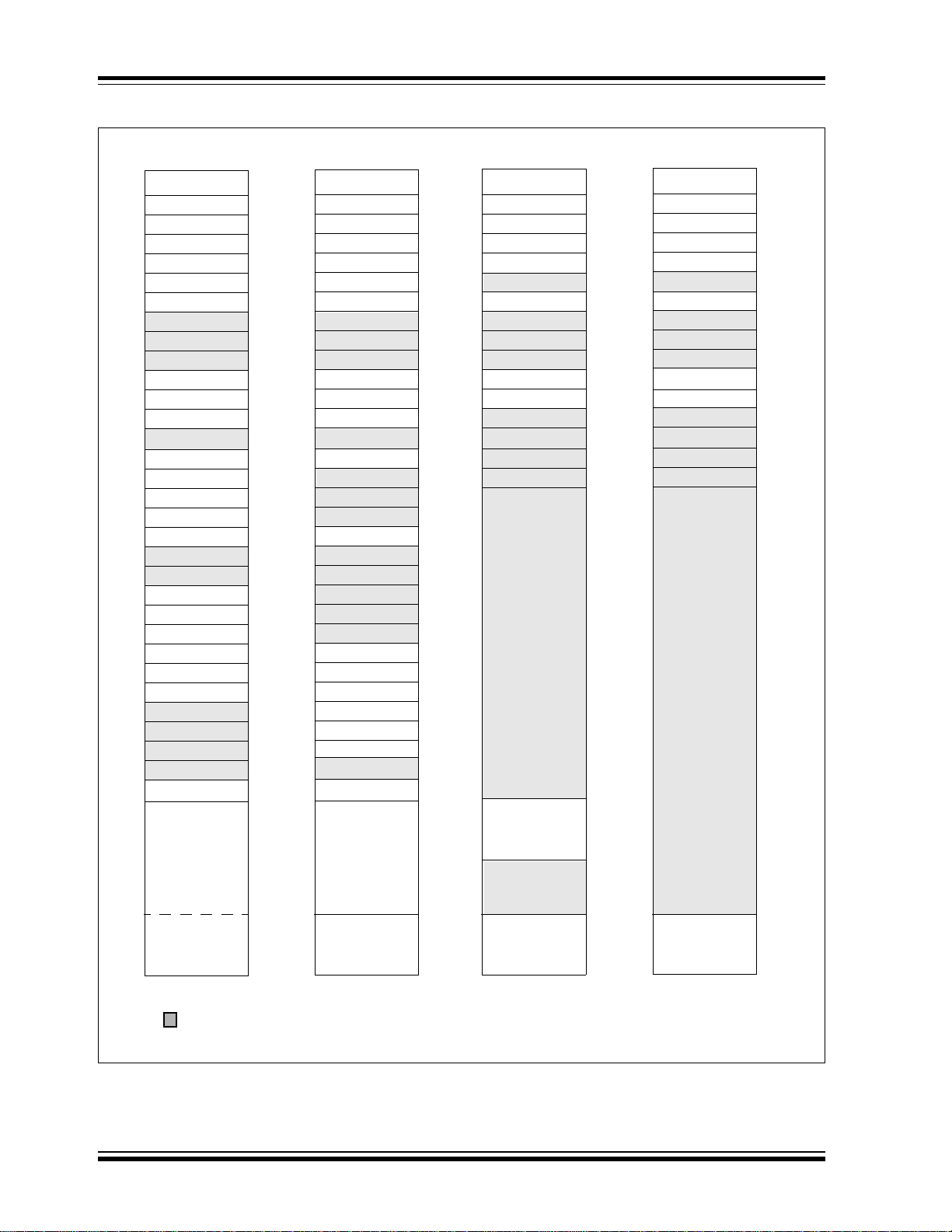

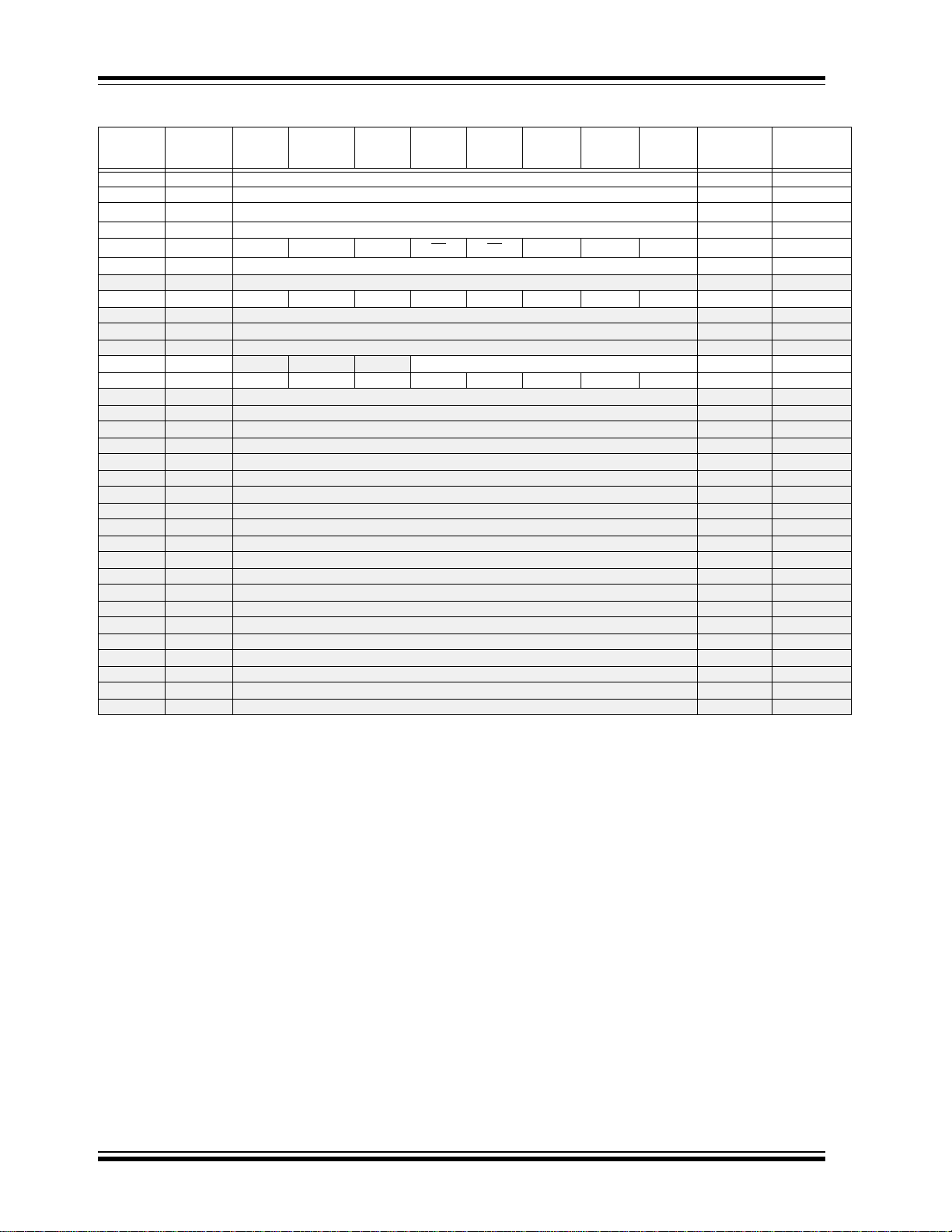

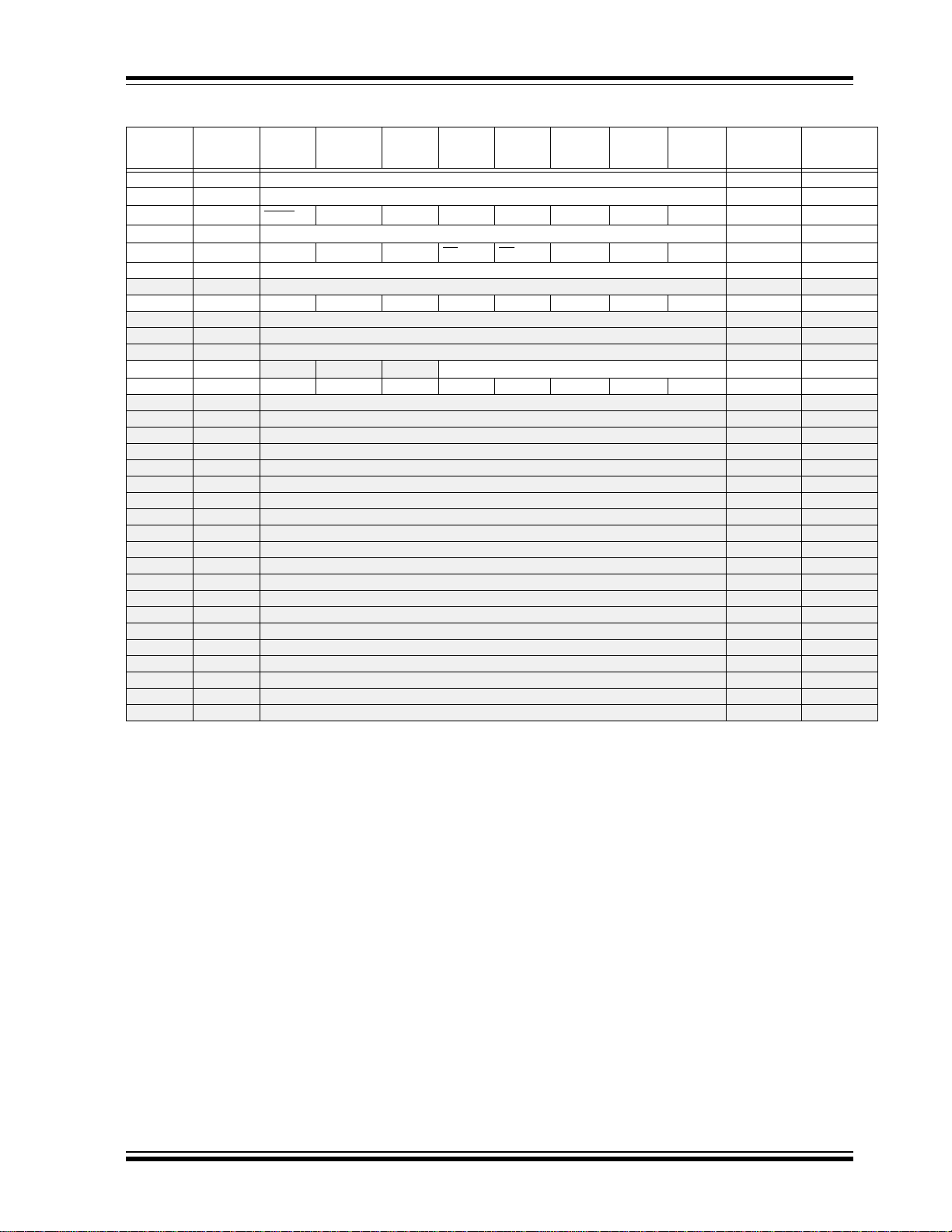

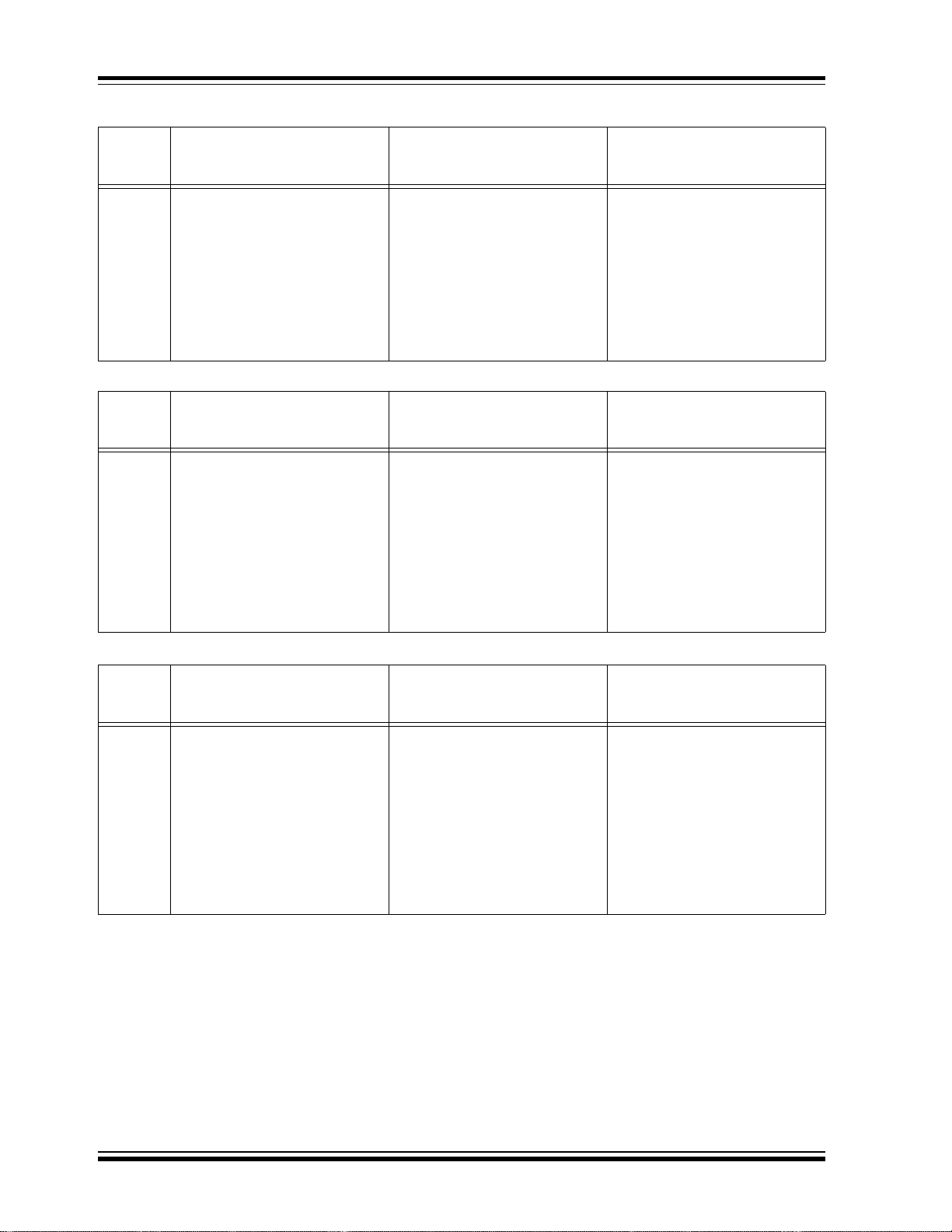

4.2 数据存储器构成

数据存储器 (图 4-2 和图 4-3)被划分为 4 块存储区,

其中包含通用寄存器 (General Purpose Register,

GPR)和特殊功能寄存器(Special Function Register,

SFR)。 SFR 位于每个存储区的前 32 个存储单元。每

个存储区中的通用寄存器都是以静态 RAM 的形式实现

的。表 4-1 列出了这 4 个存储区中可用作通用寄存器的

区域。

表 4-1:通用静态RAM 寄存器

PIC16F627A/628A PIC16F648A

存储区 0

存储区 1

存储区 2

存储区 3

地址为 F0h-FFh、 170h-17Fh 和 1F0h-1FFh 的存储单

元是以通用 RAM 的形式实现的,并映射回地址为 70h-

7Fh 的单元。

表 4-2 说明了如何通过 Status 寄存器的 RP1 和 RP0 位

访问这 4 个存储区中的寄存器。

120h-14Fh, 170h-17Fh 120h-17Fh

表 4-2: 访问存储区中的寄存器

存储区

0 00

1 01

2 10

3 11

4.2.1 通用文件寄存器

文件寄存器在 PIC16F627A/628A 中被组织为 224 x 8,

而在 PIC16F648A 中则是 256 x 8。可直接访问或通过

指针寄存器 (File Select Register, FSR)间接访问每

个寄存器,参见第 4.4 节 “间接寻址、INDF 和 FSR 寄

存器”。

20-7Fh 20-7Fh

A0h-FF A0h-FF

1F0h-1FFh 1F0h-1FFh

RP1 RP0

片上程序

存储器

仅 PIC16F648A

0FFFh

1FFFh

2005 Microchip Technology Inc. DS40044D_CN 第 15 页

PIC16F627A/628A/648A

图 4-2: PIC16F627A 和 PIC16F628A 的数据存储器映射

文件

地址

间接地址

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

TMR2

T2CON

CCPR1L

CCPR1H

CCP1CON

RCSTA

TXREG

RCREG

CMCON

通用

寄存器

80 字节

OPTION

PCL

STATUS

FSR

TRISA

TRISB

PCLATH

INTCON

PIE1

PCON

PR2

TXSTA

SPBRG

EEDATA

EEADR

EECON1

VRCON

通用

80 字节

(1)

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

(1)

9Dh

9Eh

9Fh

A0h

间接地址

寄存器

(1)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

间接地址

EECON2

寄存器

TMR0

PCL

STATUS

FSR

PORTB

PCLATH

INTCON

通用

48 字节

(1)

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

11F h

120h

14Fh

150h

间接地址

OPTION

PCL

STATUS

FSR

TRISB

PCLATH

INTCON

(1)

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

6Fh

16 字节

70h

7Fh

存储区 0

未实现的数据存储器单元,读作 0。

注 1: 非物理寄存器。

DS40044D_CN 第 16 页 2005 Microchip Technology Inc.

快速存取存储区

70h-7Fh

存储区 1

EFh

F0h

FFh

快速存取存储区

70h-7Fh

存储区 2

16Fh

170h

17Fh 1FFh

快速存取存储区

70h-7Fh

存储区 3

1EFh

1F0h

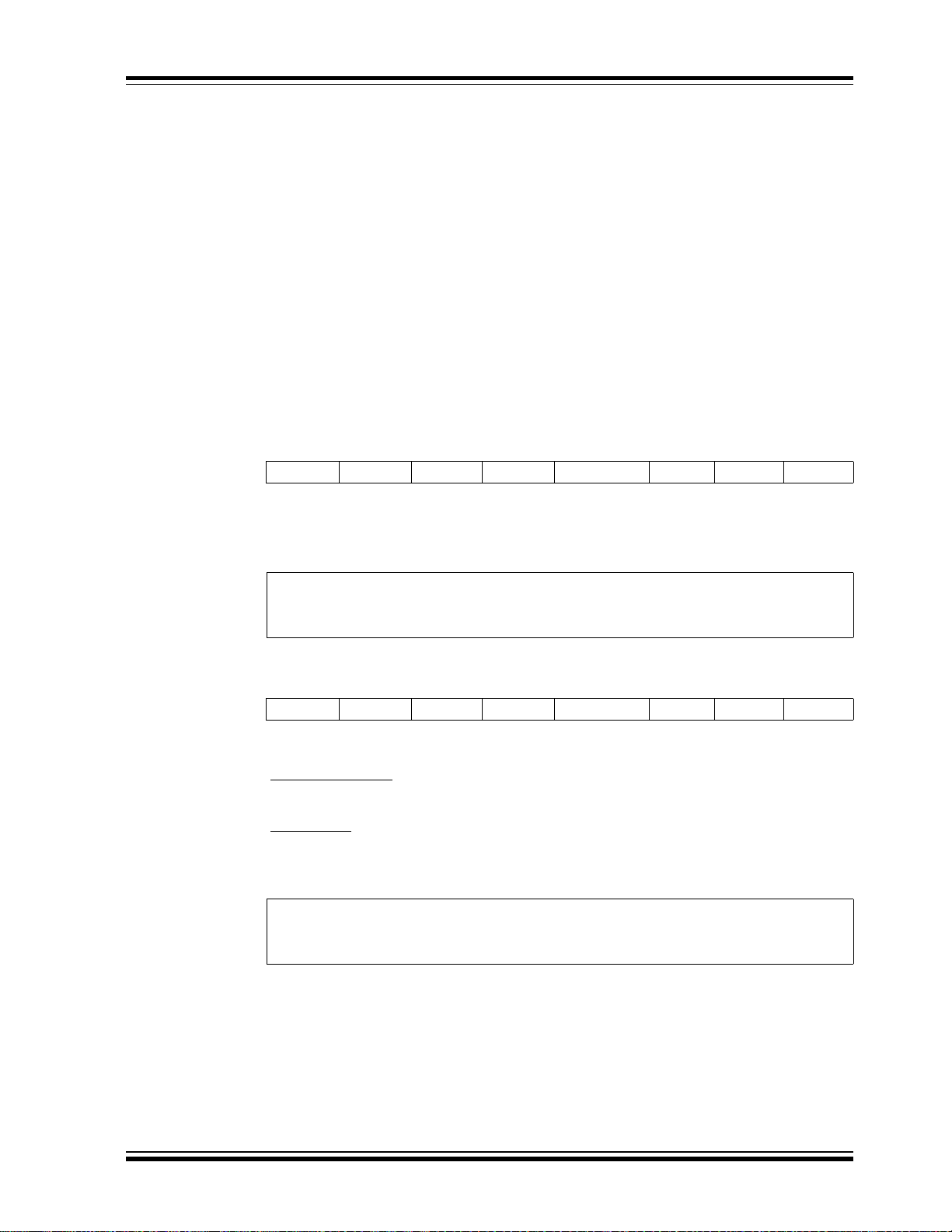

图 4-3: PIC16F648A 的数据存储器映射

PIC16F627A/628A/648A

文件

地址

间接地址

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

TMR2

T2CON

CCPR1L

CCPR1H

CCP1CON

RCSTA

TXREG

RCREG

CMCON

通用

寄存器

80 字节

OPTION

PCL

STATUS

FSR

TRISA

TRISB

PCLATH

INTCON

PIE1

PCON

PR2

TXSTA

SPBRG

EEDATA

EEADR

EECON1

VRCON

通用

80 字节

(1)

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

(1)

9Dh

9Eh

9Fh

A0h

间接地址

(1)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

间接地址

EECON2

寄存器

TMR0

PCL

STATUS

FSR

PORTB

PCLATH

INTCON

通用

寄存器

80 字节

(1)

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

11F h

120h

间接地址

OPTION

PCL

STATUS

FSR

TRISB

PCLATH

INTCON

(1)

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

6Fh

16 字节

70h

7Fh

存储区 0

未实现的数据存储器单元,读作 0。

注 1: 非物理寄存器。

2005 Microchip Technology Inc. DS40044D_CN 第 17 页

快速存取存储区

70h-7Fh

存储区 1

EFh

F0h

FFh

快速存取存储区

70h-7Fh

存储区 2

16Fh

170h

17Fh 1FFh

快速存取存储区

70h-7Fh

存储区 3

1EFh

1F0h

PIC16F627A/628A/648A

4.2.2 特殊功能寄存器

SFR 用于 CPU 和外设功能,控制器件执行期望操作的

寄存器 (表 4-3)。这些寄存器是静态 RAM。

这些特殊功能寄存器可以分成两类 (内核与外设)。本

节讲述与“内核”有关的 SFR。与外设功能部件操作有

关的 SFR 将外设功能部件章节中描述。

表 4-3: 特殊功能寄存器综述存储区 0

地址 名称

存储区 0

00h INDF

01h TMR0

02h PCL

03h STATUS

04h FSR

05h PORTA

06h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx 36

07h

08h

09h

0Ah PCLATH

0Bh INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 24

0Ch PIR1

0Dh

0Eh TMR1L

0Fh TMR1H

10h T1CON

11h TMR 2

12h T2CON

13h

14h

15h CCPR1L

16h CCPR1H

17h CCP1CON

18h RCSTA SPEN RX9 SREN CREN ADEN FERR OERR RX9D 0000 000x 71

19h TXREG

1Ah RCREG

1Bh

1Ch

1Dh

1Eh

1Fh CMCON C2OUT C1OUT

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

对此存储单元寻址会使用 FSR 的内容对数据存储器寻址 (非物理寄存器)

Timer0 模块寄存器

程序计数器 (PC)最低有效字节

IRP RP1 RP0 TO

间接数据存储器地址指针

RA7 RA6 RA5 RA4 RA3 RA2 RA1 RA0 xxxx 0000 31

- - - 程序计数器高 5 位的写缓冲器

EEIF CMIF RCIF TXIF

16 位 TMR1 最低有效字节的保持寄存器

16 位 TMR1 最高有效字节的保持寄存器

- -

TMR2 模块寄存器

捕捉 / 比较 /PWM 寄存器 (LSB)

捕捉 / 比较 /PWM 寄存器 (MSB)

USART 发送数据寄存器

USART 接收数据寄存器

TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 52

-

- -

T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 --00 0000 55

C2INV C1INV CIS CM2 CM1 CM0 0000 0000 61

PD ZDC C

CCP1IF TMR2IF TMR1IF 0000 -000 26

-

TMR1CS TMR1ON --00 0000 48

POR 复位

时的值

xxxx xxxx 28

xxxx xxxx 45

0000 0000 28

0001 1xxx 22

xxxx xxxx 28

---0 0000 28

xxxx xxxx 48

xxxx xxxx 48

0000 0000 52

xxxx xxxx 55

xxxx xxxx 55

0000 0000 77

0000 0000 80

图注: - = 未实现单元,读作 0, u = 未改变, x = 未知, q = 值随条件变化,

阴影 = 未实现

注 1: 如需了解寄存器表的初始化状态,请参见表 14-6 和表 1-7。

详情请见:

(1)

(页)

DS40044D_CN 第 18 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

表 4-4: 特殊功能寄存器综述存储区 1

地址 名称

存储区 1

80h INDF

81h OPTION RBPU

82h PCL

83h STATUS IRP RP1 RP0 TO

84h FSR

85h TRISA TRISA7 TRISA6 TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 1111 1111 31

86h TRISB TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 1111 1111 36

87h

88h

89h

8Ah PCLATH

8Bh INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 24

8Ch PIE1 EEIE CMIE RCIE TXIE

8Dh

8Eh PCON

8Fh

90h

91h

92h PR2

93h

94h

95h

96h

97h

98h TXSTA CSRC TX9 TXEN SYNC

99h SPBRG

9Ah EEDATA

9Bh EEADR

9Ch EECON1

9Dh EECON2

9Eh

9Fh VRCON VREN VROE VRR

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

对此存储单元寻址会使用 FSR 的内容对数据存储器寻址 (非物理寄存器)

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 23

程序计数器 (PC)最低有效字节

PD ZDCC0001 1xxx 22

间接数据存储器地址指针

- - - 程序计数器高 5 位的写缓冲器

CCP1IE TMR2IE TMR1IE 0000 -000 25

-

- - - -

Timer2 周期寄存器

波特率发生器寄存器

EEPROM 数据寄存器

EEPROM 地址寄存器

- - - -

EEPROM 控制寄存器 2 (非物理寄存器)

OSCF

-

WRERR WREN WR RD ---- x000 90

-

VR3 VR2 VR1 VR0 000- 0000 67

-

BRGH TRMT TX9D 0000 -010 73

POR

POR 复位

时的值

xxxx xxxx 28

0000 0000 28

xxxx xxxx 28

---0 0000 28

BOR ---- 1-0x 27

1111 1111 52

0000 0000 73

xxxx xxxx 89

xxxx xxxx 90

---- ---- 90

图注: - = 未实现单元,读作 0, u = 未改变, x = 未知, q = 值随条件变化,阴影 = 未实现

注 1: 如需了解寄存器表的初始化状态,请参见表 14-6 和表 1-7。

详情请见:

(1)

(页)

2005 Microchip Technology Inc. DS40044D_CN 第 19 页

PIC16F627A/628A/648A

表 4-5: 特殊功能寄存器综述存储区 2

地址 名称

存储区 2

100h INDF

101h TMR0

102h PCL

103h STATUS IRP RP1 RP0 TO

104h FSR

105h

106h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx 36

107h

108h

109h

10Ah PCLATH

10Bh INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 24

10Ch

10Dh

10Eh

10Fh

110 h

111h

112 h

113 h

114 h

115 h

116 h

117 h

118 h

119 h

11A h

11B h

11C h

11D h

11E h

11F h

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

对此存储单元寻址会使用 FSR 的内容对数据存储器寻址 (非物理寄存器)

Timer0 模块寄存器

程序计数器 (PC)最低有效字节

PD ZDCC0001 1xxx

间接数据存储器地址指针

- - - 程序计数器高 5 位的写缓冲器

POR 复位

时的值

xxxx xxxx 28

xxxx xxxx

0000 0000 28

xxxx xxxx 28

---0 0000 28

图注: - = 未实现单元,读作 0, u = 未改变, x = 未知, q = 值随条件变化,阴影 = 未实现

注 1: 如需了解寄存器表的初始化状态,请参见表 14-6 和表 1-7。

详情请见:

(1)

(页)

45

22

DS40044D_CN 第 20 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

表 4-6: 特殊功能寄存器综述存储区 3

地址 名称

存储区 3

180h INDF

181h OPTION RBPU

182h PCL

183h STATUS IRP RP1 RP0 TO

184h FSR

185h

186h TRISB TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 1111 1111 36

187h

188h

189h

18Ah PCLATH

18Bh INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 24

18Ch

18Dh

18Eh

18Fh

190h

191h

192h

193h

194h

195h

196h

197h

198h

199h

19Ah

19Bh

19Ch

19Dh

19Eh

19Fh

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

- 未实现位 - -

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

对此存储单元寻址会使用 FSR 的内容对数据存储器寻址 (非物理寄存器)

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 23

程序计数器 (PC)最低有效字节

PD ZDCC 0001 1xxx 22

间接数据存储器地址指针

- - - 程序计数器高 5 位的写缓冲器

POR 复位

时的值

xxxx xxxx 28

0000 0000 28

xxxx xxxx 28

---0 0000 28

图注: - = 未实现单元,读作 0, u = 未改变, x = 未知, q = 值随条件变化,阴影 = 未实现

注 1: 如需了解寄存器表的初始化状态,请参见表 14-6 和表 1-7。

详情请见:

(1)

(页)

2005 Microchip Technology Inc. DS40044D_CN 第 21 页

PIC16F627A/628A/648A

4.2.2.1 STATUS 寄存器

Status 寄存器 (如寄存器 4-1 所示)含有 ALU 的算术

运算结果状态、复位状态及数据存储器 (SRAM)存储

区选择位。

与其他寄存器一样,Status 寄存器也可以是任何指令的

目标寄存器。如果 Status寄存器作为一条影响 Z、DC 或

C 标志位的指令的目标寄存器,则会禁止写入这三个标

志位。根据器件逻辑,这些位会置位或清零。而且,TO

和 PD 位不可写。所以执行一条把 Status 寄存器作为目

标寄存器的指令所得到的结果可能和预想的不一样。

例如,执行指令 CLRF STATUS 将会把 STATUS 寄存器

的高 3 位清零,并将 Z 位置位。这将使 Status 寄存器的

结果为 000uu1uu (其中 u 表示未变化)。

因此,建议仅使用 BCF、 BSF、 SWAPF 和 MOVWF 指令

去改变 Status 寄存器,因为这些指令不会影响任何状态

位。对于其他不影响任何状态位的指令,请参见“指令

集综述”。

注 1:在减法运算中, C 和 DC 位分别作为借位

和辅助借位位。例如 SUBLW 和 SUBWF 指

令。

寄存器 4-1: STATUS — 状态寄存器 (地址:03h、 83h、 103h、 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO

bit 7 bit 0

bit 7 IRP:寄存器存储区选择位 (用于间接寻址)

1= 存储区 2, 3 (100h - 1FFh)

0= 存储区 0, 1 (00h - FFh)

bit 6-5 RP<1:0>:寄存器存储区选择位 (用于直接寻址)

00= 存储区 0 (00h - 7Fh)

01= 存储区 1 (80h - FFh)

10= 存储区 2 (100h - 17Fh)

11= 存储区 3 (180h - 1FFh)

bit 4 TO

bit 3 PD:掉电标志位

bit 2 Z:全零标志位

bit 1 DC:辅助进位 / 借位标志位 (ADDWF、 ADDLW、 SUBLW、 SUBWF 指令影响这些标志位)(对

bit 0 C:进位 / 借位

:超时位

1= 上电后,执行 CLRWDT 指令或 SLEEP 指令

0= 发生了 WDT 超时

1= 在上电后或执行 CLRWDT 指令

0= 执行 SLEEP 指令

1= 算术运算或逻辑运算结果为零

0= 算术运算或逻辑运算结果不是零

于借位,其极性是相反的)

1= 结果中发生了第 4 低位向高位的进位

0= 结果中第 4 低位没有向高位进位

标志位 (ADDWF、 ADDLW、 SUBLW、 SUBWF 指令影响这些标志位)

1= 结果中发生了最高位进位

0= 结果中未发生最高位进位

注: 对于借位,极性是相反的。执行减法是通过加上第二个操作数的二进制补码来完成

的。对于移位指令 (RRF 和 RLF),此位值来自源寄存器的最高位或最低位。

PD ZDCC

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

DS40044D_CN 第 22 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

4.2.2.2 OPTION 寄存器

OPTION 寄存器是可读写的寄存器,它包含各个控制

位,用来配置 TMR0/WDT 预分频器、外部 RB0/INT 中

断、 TMR0 和 PORTB 弱上拉。

寄存器 4-2: OPTION_REG — 选择寄存器 (地址:81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

bit 7 RBPU:PORTB 上拉使能位

1= 禁止 PORTB 上拉

0= 按各端口锁存器值使能 PORTB 上拉

bit 6 INTEDG:中断触发边沿选择位

1= 在 RB0/INT 引脚的上升沿触发中断

0= 在 RB0/INT 引脚的下降沿触发中断

bit 5 T0CS:TMR0 时钟源选择位

1=RA4/T0CKI/CMP2 引脚的信号作为时钟源

0= 内部指令周期时钟 (CLKOUT)作为时钟源

bit 4 T0SE:TMR0 计数边沿选择位

1= 在 RA4/T0CKI/CMP2 引脚电平发生下跳变时递增

0= 在 RA4/T0CKI/CMP2 引脚电平发生上跳变时递增

bit 3 PSA:预分频器分配位

1= 将预分频器分配给 WDT

0= 将预分频器分配给 Timer0 模块

bit 2-0 PS<2:0>:预分频器分频比选择位

位值 TMR0 分频比 WDT 分频比

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

注: 要使 TMR0 的预分频比达到 1:1,应将预分

频器分配给 WDT(PSA=1)。参 见 第 6.3.1

节 “切换预分频器的分配”。

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

2005 Microchip Technology Inc. DS40044D_CN 第 23 页

PIC16F627A/628A/648A

4.2.2.3 INTCON 寄存器

INTCON 寄存器是可读写的寄存器,其中包含除比较器

模块外的所有中断源的允许和标志位。如需了解比较器

中断允许和标志位的说明,请参见第 4.2.2.4 节 “PIE1

寄存器”和第 4.2.2.5 节 “PIR1 寄存器”。

注: 当一个中断条件发生时,不管相应的中断

允许位或全局允许位 GIE (INTCON<7>)

的状态如何,中断标志位都将置位。

寄存器 4-3: INTCON — 中断控制寄存器 (地址:0Bh、 8Bh、 10Bh、 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF

bit 7 bit 0

bit 7 GIE:全局中断允许位

1= 允许所有未屏蔽的中断

0= 禁止所有中断

bit 6 PEIE:外设中断允许位

1= 允许所有未屏蔽的外设中断

0= 禁止所有外设中断

bit 5 T0IE:TMR0 溢出中断允许位

1= 允许 TMR0 中断

0= 禁止 TMR0 中断

bit 4 INTE:RB0/INT 外部中断允许位

1= 允许 RB0/INT 外部中断

0= 禁止 RB0/INT 外部中断

bit 3 RBIE:RB 端口电平变化中断允许位

1= 允许 RB 端口电平变化中断

0= 禁止 RB 端口电平变化中断

bit 2 T0IF:TMR0 溢出中断标志位

1=TMR0 寄存器已经溢出 (必须用软件清零)

0=TMR0 寄存器未发生溢出

bit 1 INTE:RB0/INT 外部中断标志位

1= 发生了 RB0/INT 外部中断 (必须用软件清零)

0= 未发生 RB0/INT 外部中断

bit 0 RBIF:RB 端口电平变化中断标志位

1=RB<7:4> 引脚中至少有一个引脚改变了状态 (必须用软件清零)

0=RB<7:4> 各引脚的状态都没有改变

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

DS40044D_CN 第 24 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

4.2.2.4 PIE1 寄存器

此寄存器包含中断允许位。

寄存器 4-4: PIE1 — 外设中断允许寄存器 1 (地址:8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0

EEIE CMIE RCIE TXIE

bit 7 bit 0

bit 7 EEIE:EE 写操作完成中断允许位

1= 允许 EE 写操作完成中断

0= 禁止 EE 写操作完成中断

bit 6 CMIE:比较器中断允许位

1= 允许比较器中断

0= 禁止比较器中断

bit 5 RCIE:USART 接收中断允许位

1= 允许 USART 接收中断

0= 禁止 USART 接收中断

bit 4 TXIE:USART 发送中断允许位

1= 允许 USART 发送中断

0= 禁止 USART 发送中断

bit 3 未实现位:读作 0

bit 2 CCP1IE:CCP1 中断允许位

1= 允许 CCP1 中断

0= 禁止 CCP1 中断

bit 1 TMR2IE:TMR2 与 PR2 匹配中断允许位

1= 允许 TMR2 与 PR2 匹配中断

0= 禁止 TMR2 与 PR2 匹配中断

bit 0 TMR1IE:TMR1 溢出中断允许位

1= 允许 TMR1 溢出中断

0= 禁止 TMR1 溢出中断

-

CCP1IE TMR2IE TMR1IE

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

2005 Microchip Technology Inc. DS40044D_CN 第 25 页

PIC16F627A/628A/648A

4.2.2.5 PIR1 寄存器

此寄存器包含中断标志位。

注: 当一个中断条件发生时,不管相应的中断

寄存器 4-5: PIR1 — 外设中断 1 寄存器 (地址:0Ch)

R/W-0 R/W-0 R-0 R-0 U-0 R/W-0 R/W-0 R/W-0

EEIF CMIF RCIF TXIF

bit 7 bit 0

bit 7 EEIF:EEPROM 写操作中断标志位

1= 写操作完成 (必须用软件清零)

0= 写操作未完成或未开始

bit 6 CMIF:比较器中断标志位

1= 比较器输出发生了改变

0= 比较器输出没有改变

bit 5 RCIF:USART 接收中断标志位

1=USART 接收缓冲器已满

0=USART 接收缓冲器是空的

bit 4 TXIF:USART 发送中断标志位

1=USART 发送缓冲器是空的

0=USART 发送缓冲器已满

bit 3 未实现位:读作 0

bit 2 CCP1IF:CCP1 中断标志位

捕捉模式

1= 发生了 TMR1 寄存器捕捉 (必须用软件清零)

0= 没有发生 TMR1 寄存器捕捉

比较模式

1= 发生了 TMR1 寄存器比较匹配 (必须用软件清零)

0= 没有发生 TMR1 寄存器比较匹配

模式

PWM

在此模式下未使用

bit 1 TMR2IF:TMR2 与 PR2 匹配中断标志位

1= 发生了 TMR2 与 PR2 匹配 (必须用软件清零)

0=TMR2 与 PR2 不匹配

bit 0 TMR1IF:TMR1 溢出中断标志位

1=TMR1 寄存器溢出 (必须用软件清零)

0=TMR1 寄存器没有溢出

允许位或全局允许位 GIE (INTCON<7>)

的状态如何,中断标志位都将置位。用户软

件应在允许一个中断之前,确保先将相应

的中断标志位清零。

-

CCP1IF TMR2IF TMR1IF

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

DS40044D_CN 第 26 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

4.2.2.6 PCON 寄存器

PCON 寄存器包含用来区分上电复位、外部 MCLR 复

位、 WDT 复位或欠压复位的标志位。

注: BOR 在上电复位时未知。它必须在上电复

寄存器 4-6: PCON — 电源控制寄存器 (地址:8Eh)

U-0 U-0 U-0 U-0 R/W-1 U-0 R/W-0 R/W-x

- - - -

bit 7 bit 0

bit 7-4 未实现位:读作 0

bit 3 OSCF:INTOSC 振荡器频率位

1= 典型值 4 MHz

0= 典型值 48 kHz

bit 2 未实现位:读作 0

bit 1 POR:上电复位状态位

1= 没有发生上电复位

0= 发生了上电复位 (在上电复位发生之后必须用软件置位)

bit 0 BOR

:欠压复位状态位

1= 没有发生欠压复位

0= 发生了欠压复位 (必须在发生欠压复位后用软件置位)

位后由用户置位,并在接下来的复位中检

查 BOR 位是否为清零状态,从而指示是否

发生的是欠压复位。如果禁止了欠压电路

(将配置字中的 BOREN 位清零),则 BOR

状态位可忽略,也没必要对其内容作出预

测。

OSCF

-

POR

BOR

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

2005 Microchip Technology Inc. DS40044D_CN 第 27 页

PIC16F627A/628A/648A

4.3 PCL 和 PCLATH

程序计数器 (PC)为 13 位宽。它的低字节来自可读写

的 PCL 寄存器。高字节 (PC<12:8>)不可直接读写,

来自 PCLATH。任何复位时, PC 都会被清零。图 4-4

给出了装载 PC 的两种情况。图 4-4 中上面的示例给出

了在写 PCL(PCLATH<4:0> → PCH)时 ,装载 PC 的

过程。图 4-4 中下面的示例给出了在 CALL 或 GOTO 指

令执行时 (PCLATH<4:3> → PCH)装载 PC 的过程。

图 4-4: 在不同情况下装载 PC

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

11

8

将

PCL 作为

目标寄存器

的指令

ALU 结果

,CALL

GOTO

操作码 <10:0>

堆栈是作为循环缓冲器使用的。也就是说,压栈 8 次之

后,第 9 次压栈时进栈的数据将覆盖第 1 次压栈存储的

数据。而第 10 次压栈时进栈的数据将覆盖第 2 次压栈

存储的数据,依此类推。

注 1:没有用于表示堆栈溢出或堆栈下溢情形的

状态位。

2:没有称为 PUSH 或 POP 的指令或助记符。

这些是执行 CALL、 RETURN、 RETLW 和

RETFIE 指令,或转到中断向量地址时发

生的操作。

4.4 间接寻址、 INDF 和 FSR 寄存器

INDF 寄存器不是物理寄存器。对 INDF 寄存器寻址将导

致间接寻址。

使用 INDF 寄存器可以实现间接寻址。任何使用 INDF

寄存器的指令实际上访问的是由指针寄存器(FSR)所

指向的寄存器。间接读 INDF 本身会返回 00h。而使用

间接寻址对 INDF 寄存器进行写操作将导致执行一个空

操作 (虽然可能会影响状态位)。有效的 9 位地址是通

过组合 8 位 FSR 寄存器和 IRP 位(STATUS<7>)获 得

的,如图 4-5 所示。

例 4-1所示为一个使用间接寻址清零RAM单元20h-2Fh

的简单程序。

PCLATH

4.3.1 相对 GOTO

相对 GOTO 是通过向程序计数器加一个偏移量(ADDWF

PCL)来实现的。当使用相对 GOTO 指令方法进行读表操

作时,要注意表地址是否超过了 PCL 的存储边界 (每

块256个字节)。请参见应用笔记AN556“Implementing

a Table Read”( DS00556)。

4.3.2 堆栈

PIC16F627A/628A/648A 系列有一个 8 级深度, 13 位

宽的硬件堆栈 (图 4-1)。该堆栈既不占用程序存储空

间也不占用数据存储空间,且栈指针不能读写。当执行

CALL 指令或中断引起程序转移时,PC 的值会被压入堆

栈。而执行 RETURN、 RETLW 或 RETFIE 指令时, PC

值会从堆栈弹出。压栈(PUSH)或出栈(POP)的操

作不会影响 PCLATH。

例 4-1:间接寻址

MOVLW 0x20 ;initialize pointer

MOVWF FSR ;to RAM

NEXT CLRF INDF ;clear INDF register

INCF FSR ;inc pointer

BTFSS FSR,4 ;all done?

GOTO NEXT ;no clear next

;yes continue

DS40044D_CN 第 28 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

图 4-5: PIC16F627A/628A/648A 的直接 / 间接寻址

Status

寄存器

RAM

数据

寄存器

来自操作码

00h

7Fh

0

00 01 10 11

RP1 RP0 6

存储区选择 单元选择

存储区 0 存储区 1 存储区 2 存储区 3

注: 如需存储器映射的详细介绍,请参见图 4-3、图 4-2 和图 4-1。

Status

寄存器

IRP FSR 寄存器

存储区选择

180h

间接寻址间接寻址

7

1FFh

0

单元选择

2005 Microchip Technology Inc. DS40044D_CN 第 29 页

PIC16F627A/628A/648A

注:

DS40044D_CN 第 30 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

脚

5.0 I/O 口

PIC16F627A/628A/648A 有两个端口,PORTA 和

PORTB。这 些 I/O 端口的部分引脚与器件外设功能部件

的备用功能复用。通常,当外设使能时,其对应的引脚

就可能无法用作一般的 I/O 引脚。

5.1 IPORTA 和 TRISA 寄存器

PORTA 是一个 8 位宽的锁存器。 RA4 为施密特触发器

输入和漏极开路输出引脚。它与 T0CKI 时钟输入复用。

(1)

只是施密特触发器输入,没有输出驱动器。所有

RA5

其他的 RA 端口引脚都有施密特触发器输入电平和完整

的 CMOS 输出驱动器。所有引脚都有数据方向控制位

(在 TRIS 寄存器中),这些位可以将引脚配置为输入或

输出。

将 TRISA 寄存器的某位置 1,就可以将相应的输出驱动

器置为高阻态模式。将 TRISA 寄存器的某位清零,则将

输出锁存器的内容锁存到指定的引脚。

读 PORTA 寄存器是读取引脚上的电平状态,而写

PORTA 寄存器是将数据写入端口锁存器。所有写操作

都是读-修改-写操作。因此,对一个端口进行写操作

就意味着总是先读取端口引脚电平,然后修改这个值,

最后将该值写入端口数据锁存器。

PORTA 引脚与比较器和参考电压功能复用。这些引脚

的工作状态是通过 CMCON(比较器控制寄存器)寄存

器和 VRCON 寄存器(参考电压控制寄存器)中的控制

位选择的。当选择它们作为比较器输入时,这些引脚将

读作 0。

注 1:RA5 与 VPP 复用。当在 RA5 上加 VPP 电

压时,器件将进入编程模式。

2:在复位时,TRISA 寄存器各位全部被置为

输入。禁止数字输入 (RA<3:0>)并强制

比较器输入接地以降低电流消耗。

3:振荡器配置会改写 TRISA<6:7>。当改写

PORTA<6:7> 时,数据读为 0,并且忽略

TRISA<6:7> 位。

TRISA 控制 RA 引脚的输入 / 输出方向,即使引脚作为

比较器输入时也是如此。当将这些引脚作为比较器输入

时,用户必须确保将它们配置为输入引脚。

RA2 引脚也能作为参考电压的输出。当处于此模式时,

REF 引脚是极高阻抗的输出。用户必须配置 TRISA<2>

V

位为输入并使用高阻抗负载。

在 CMCON 寄存器定义的其中一种比较器模式下,RA3

和 RA4 引脚作为比较器的输出。为了使输出能使用此功

能,必须将 TRISA<4:3> 位清零。

例 5-1:初始化PORTA

CLRF PORTA ;Initialize PORTA by

MOVLW 0x07 ;Turn comparators off and

MOVWF CMCON ;enable pins for I/O

BCF STATUS, RP1

BSF STATUS, RP0 ;Select Bank1

MOVLW 0x1F ;Value used to initialize

MOVWF TRISA ;Set RA<4:0> as inputs

;setting

;output data latches

;functions

;data direction

;TRISA<5> always

;read as '1'.

;TRISA<7:6>

;depend on oscillator

;mode

图 5-1: RA0/AN0:RA1/AN1 引脚框

图

数据

总线

WR

PORTA

WR

TRISA

RD

TRISA

RD PORTA

数据锁存器

TRIS 锁存器

CK

CK

QD

Q

QD

Q

(CMCON 寄存器)

模拟

输入模式

施密特触发器

输入缓冲器

EN

VDD

I/O 引

VSS

DQ

到比较器

2005 Microchip Technology Inc. DS40044D_CN 第 31 页

PIC16F627A/628A/648A

脚

图 5-2: RA2/AN2/VREF 引脚框图

数据

总线

WR

PORTA

WR

TRISA

数据锁存器

TRIS 锁存器

CK

CK

QD

Q

QD

Q

(CMCON 寄存器)

模拟

输入模式

VDD

RA2 引

VSS

RD

TRISA

RD PORTA

到比较器

VROE

VREF

施密特触发器

输入缓冲器

DQ

EN

图 5-3: RA3/AN3/CMP1 引脚框图

数据

总线

WR

PORTA

WR

TRISA

CK

数据锁存器

CK

TRIS 锁存器

QD

比较器输出

Q

QD

Q

比较器模式 =110(CMCON 寄存器)

VDD

1

0

RA3 引脚

模拟

输入模式

(CMCON 寄存器)

VSS

RD

TRISA

RD PORTA

到比较器

施密特触发器

输入缓冲器

DQ

EN

DS40044D_CN 第 32 页 2005 Microchip Technology Inc.

图 5-4: RA4/T0CKI/CMP2 引脚框图

数据

总线

WR

PORTA

WR

TRISA

RD PORTA

CK

数据锁存器

CK

TRIS 锁存器

RD TRISA

QD

比较器输出

Q

QD

Q

比较器模式 =110

PIC16F627A/628A/648A

(CMCON 寄存器)

1

0

N

Vss

施密特触发器

输入缓冲器

DQ

EN

RA4 引脚

Vss

TMR0 时钟输入

图 5-5: RA5/MCLR

(配置位)

数据

总线

MCLRE

MCLR

滤波器

施密特触发器编程

输入缓冲器

HV 检测

VSS

DQ

EN

MCLR

电路

模式

RD

TRISA

RD

PORTA

/VPP 引脚框图 图 5-6: RA6/OSC2/CLKOUT 引脚

框图

来自

RA5/MCLR/V

VSS

PP

OSC1

CLKOUT(F

WR

PORTA

(

F

OSC

=

101, 111)

WR

TRISA

RD

TRISA

F

OSC

=

011, 100, 110

RD PORTA

OSC

DCKQ

数据锁存器

(2)

DCKQ

TRIS

(1)

/4

)

1

0

Q

Q

锁存器

QD

EN

OSC

电路

V

DD

V

SS

施密特触发器

输入缓冲器

注 1: INTOSC 模式下, RA6=I/O ;或 RC 模式下,

RA6=I/O。

2: INTOSC 模式下, RA6=CLKOUT ;或 RC 模式

下, RA6=I/O。

2005 Microchip Technology Inc. DS40044D_CN 第 33 页

PIC16F627A/628A/648A

图 5-7: RA7/OSC1/CLKIN 引脚框图

数据总线

WR PORTA

WR TRISA

RD TRISA

OSC = 100,101

F

RD PORTA

至时钟电路

CK

数据锁存器

D

CK

TRIS 锁存器

(1)

VDD

QD

RA7/OSC1/CLKIN 引脚

Q

Q

Q

DQ

施密特触发器

EN

输入缓冲器

VSS

注 1: INTOSC 模式下,用作 CLKOUT 或一般 I/O 引脚。

DS40044D_CN 第 34 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

表 5-1: PORTA 功能

名称 功能 输入类型 输出类型 描述

RA0/AN0 RA0 ST CMOS

AN0 AN

- 模拟比较器输入

RA1/AN1 RA1 ST CMOS

RA2/AN2/V

AN1 AN

REF RA2 ST CMOS

AN2 AN

V

REF

-

- 模拟比较器输入

- 模拟比较器输入

AN

RA3/AN3/CMP1 RA3 ST CMOS

AN3 AN

CMP1

-

- 模拟比较器输入

CMOS

RA4/T0CKI/CMP2 RA4 ST OD

RA5/MCLR

T0CKI ST

CMP2

-

/VPP RA5 ST

MCLR

V

PP HV

ST

- TMR0 外部时钟输入或比较器输出

OD

-

-

-

RA6/OSC2/CLKOUT RA6 ST CMOS

OSC2

CLKOUT

-

-

XTAL

CMOS

RA7/OSC1/CLKIN RA7 ST CMOS

OSC1 XTAL

CLKIN ST

- 振荡器晶振输入。在晶振模式下连接到晶体谐振器。

- 外部时钟源输入。 RC 偏置引脚。

图注: O=输出 CMOS = CMOS 输出 P=电源

- = 未使用 I=输入 ST = 施密特触发器输入

TTL = TTL 输入 OD = 漏极开路输出 AN = 模拟

双向 I/O 端口

双向 I/O 端口

双向 I/O 端口

VREF 输出

双向 I/O 端口

比较器 1 输出

双向 I/O 端口。输出是漏极开路型

比较器 2 输出

输入端口

主复位。当配置为 MCLR 时,此引脚为低电平且器件复位。

在器件正常工作期间, MCLR

/VPP 上的电压不得高于 VDD。

编程电压输入。

双向 I/O 端口

振荡器晶振输出。在晶振模式下连接到晶体谐振器。

在 RC 或 INTOSC 模式下, OSC2 引脚可以输出

CLKOUT,其频率为 OSC1 的 1/4。

双向 I/O 端口

表 5-2:与PORTA 相关的寄存器综述

地址 名称

05h PORTA RA7 RA6

85h TRISA TRISA7 TRISA6 TRISA5TRISA4TRISA3 TRISA2 TRISA1 TRISA0 1111 1111 1111 1111

1Fh CMCON

9Fh VRCON VREN VROE

图注:

注 1: RA5 的功能由 MCLRE 配置位设置。

- = 未实现单元,读作 0, u = 未改变, x = 未知, q = 值随条件变化

阴影单元表示 PORTA 未使用。

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

(2)

RA5

C2OUT C1OUT C2INV C1INV CIS CM2 CM1 CM0 0000 0000 0000 0000

VRR

RA4 RA3 RA2 RA1 RA0 xxxx 0000 qqqu 0000

VR3 VR2 VR1 VR0 000- 0000 000- 0000

-

POR

时的值

其他复位

时的值

2005 Microchip Technology Inc. DS40044D_CN 第 35 页

PIC16F627A/628A/648A

5.2 PORTB 和 TRISB 寄存器

PORTB是一个 8位宽的双向端口。相应的数据方向寄存

器是 TRISB。将 TRISB 寄存器的某位置 1,可以使相应

的输出驱动器为高阻态。而将 TRISB 寄存器的某位清

零,则将输出锁存器的内容锁存到选定的引脚上。

PORTB 与外部中断、 USART、 CCP 模块和 TMR1 时

钟输入 / 输出复用。其标准端口功能和备用端口功能如

表 5-3 所示。使能时,备用端口功能可能会使 TRIS 设

置无效。

读 PORTB 寄存器可读取引脚的电平状态,而写 PORTB

寄存器是将数据写入端口锁存器。所有写操作都是读-

修改-写操作。因此,对一个端口进行写操作就意味着

总是先读取端口引脚电平,再修改这个值,然后将该值

写入端口数据锁存器。

每个 PORTB 引脚都有一个内部弱上拉电路(通常约为

200µA)。单个控制位可以接通所有的上拉电路。这是

通过将 RBPU

PORTB 端口的引脚配置为输出时,其弱上拉电路会自

动切断。在上电复位后,弱上拉会被禁止。

PORTB 引脚中有 4 个(RB<7:4>)具有电平变化触发

中断的功能。只有当引脚配置为输入时才会发生此中断

(即,当 RB<7:4> 的任何一个引脚被配置为输出时,则

该引脚就不会具有电平变化触发中断的功能) 。当前

RB7:RB4 输入引脚上的电平与上次读 PORTB 时锁存的

旧值进行比较。将 RB7:RB4 上与旧值相比的 “失配”

输出进行或运算,以产生 RBIF 中断 (在 INTCON<0>

中锁存该中断标志)。

该中断可将器件从休眠中唤醒。在中断服务程序中,用

户可以通过下面的方式清除中断:

a)对PORTB 进行读 / 写操作。这将结束失配状态。

b)将RBIF 标志位清零。

失配状态会不断将 RBIF 标志位置位。而读 PORTB 将

结束失配状态,并且允许将 RBIF 标志位清零。

失配触发中断这个功能和这四个引脚上的可软件配置

的上拉功能,通过这些功能可以很容易地与键盘接口,

从而实现按键唤醒功能 (参见应用笔记 AN552

“Implementing Wake-up on Key Strokes”

(DS00552))。

(OPTION<7>)位清 零 实 现的。当 将

对于按键唤醒以及其他仅使用 PORTB 的电平变化触发

中断功能的操作,建议使用此电平变化触发中断功能来

实现。在使用电平变化触发中断功能时,建议不要查询

PORTB 的状态。

图 5-8: RB0/INT 引脚框图

DD

TTL

输入

缓冲器

V

P

弱上拉

VDD

RB0/INT

VSS

RBPU

数据总线

WR PORTB

WR TRISB

RD TRISB

RD PORTB

INT

D

CK

数据锁存器

D

CK

TRIS

锁存器

施密特

触发器

Q

Q

Q

Q

QD

EN

EN

注: 如果I/O 引脚的电平在执行读取操作时(Q2

周期的开始)发生改变,则 RBIF 中断标志

可能不会置位。

DS40044D_CN 第 36 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

图 5-9: RB1/RX/DT 引脚框图 图 5-10: RB2/TX/CK 引脚框图

RBPU

SPEN

VDD

P

弱上拉

VDD

RBPU

SPEN

VDD

P

弱上拉

VDD

USART 数据输出

数据总线

WR PORTB

WR TRISB

(1)

外设 OE

RD TRISB

RD PORTB

USART 接收输入

注 1: 只有外设选择有效时,外设 OE (输出使能)才会

有效。

D

Q

CK

Q

数据锁存器

D

Q

Q

CK

TRIS 锁存器

施密特

触发器

1

0

TTL

输入

缓冲器

QD

EN

VSS

RB1/

RX/DT

USART TX/CK 输出

数据总线

WR PORTB

WR TRISB

(1)

外设 OE

RD TRISB

RD PORTB

USART 从时钟输入

注 1: 只有外设选择有效时,外设 OE (输出使能)才会

有效。

D

Q

CK

Q

数据锁存器

D

Q

CK

TRIS 锁存器

施密特

Q

QD

EN

触发器

1

0

VSS

TTL

输入

缓冲器

RB2/

TX/CK

2005 Microchip Technology Inc. DS40044D_CN 第 37 页

PIC16F627A/628A/648A

图 5-11: RB3/CCP1 引脚框图

RBPU

CCP1CON

VDD

弱上拉

P

VDD

CCP 输出

数据总线

WR PORTB

WR TRISB

(1)

外设 OE

RD TRISB

RD PORTB

CCP 输入

注 1: 只有外设选择有效时,外设 OE (输出使能)才会

有效。

D

Q

CK

Q

数据锁存器

D

Q

Q

CK

TRIS 锁存器

施密特

触发器

0

1

QD

EN

TTL

输入

缓冲器

VSS

RB3/

CCP1

DS40044D_CN 第 38 页 2005 Microchip Technology Inc.

图 5-12: RB4/PGM 引脚框图

RBPU

PIC16F627A/628A/648A

VDD

P

弱上拉

数据总线

WR PORTB

WR TRISB

RD TRISB

(配置位)

LVP

RD PORTB

PGM 输入

D

Q

CK

Q

数据锁存器

D

Q

CK

Q

TRIS 锁存器

施密特

触发器

TTL

输入

缓冲器

QD

VDD

RB4/PGM

VSS

设置 RBIF

来自其他

RB<7:4> 引脚

注: 低电压编程会禁止 RB4 引脚的电平变化触发中断和弱上拉。

EN

QD

EN

Q1

Q3

2005 Microchip Technology Inc. DS40044D_CN 第 39 页

PIC16F627A/628A/648A

图 5-13: RB5 引脚框图

RBPU

DD

V

VDD

弱

P

上拉

数据总线

WR PORTB

WR TRISB

RD TRISB

RD PORTB

设置 RBIF

D

Q

Q

CK

数据锁存器

D

Q

CK

Q

TRIS 锁存器

来自其它

RB<7:4> 引脚

QD

EN

QD

EN

TTL

输入

缓冲器

RB5 引脚

VSS

Q1

Q3

DS40044D_CN 第 40 页 2005 Microchip Technology Inc.

图 5-14: RB6/T1OSO/T1CKI 引脚框图

PIC16F627A/628A/648A

RBPU

数据总线

WR PORTB

WR TRISB

RD TRISB

T1OSCEN

RD PORTB

TMR1 时钟

来自 RB7

D

Q

CK

Q

数据锁存器

D

Q

CK

Q

TRIS 锁存器

施密特

触发器

VDD

P

TTL

输入

缓冲器

弱上拉

VDD

VSS

RB6/

T1OSO/

T1CKI

引脚

串行编程时钟

设置 RBIF

来自其他

RB<7:4> 引脚

TMR1 振荡器

QD

EN

QD

EN

Q1

Q3

2005 Microchip Technology Inc. DS40044D_CN 第 41 页

PIC16F627A/628A/648A

图 5-15: RB7/T1OSI 引脚框图

RBPU

VDD

P

弱上拉

至 RB6

数据总线

WR PORTB

WR TRISB

RD TRISB

T10SCEN

RD PORTB

串行编程输入

D

CK

Q

数据锁存器

D

CK

Q

TRIS 锁存器

TMR1 振荡器

VDD

Q

RB7/T1OSI

引脚

Q

施密特

触发器

QD

VSS

TTL

输入

缓冲器

设置 RBIF

来自其他

RB<7:4> 引脚

EN

QD

EN

Q1

Q3

DS40044D_CN 第 42 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

表 5-3: PORTB 功能

名称 功能 输入类型 输出类型 说明

RB0/INT RB0 TTL CMOS

INT ST

- 外部中断。

RB1/RX/DT RB1 TTL CMOS

RX ST

- USART 接收引脚

DT ST CMOS

RB2/TX/CK RB2 TTL CMOS

TX

-

CMOS

CK ST CMOS

RB3/CCP1 RB3 TTL CMOS

CCP1 ST CMOS

RB4/PGM RB4 TTL CMOS

PGM ST

- 低电压编程输入引脚 。当低电压编程使能时,禁止引脚

RB5 RB5 TTL CMOS

RB6/T1OSO/T1CKI/

RB6 TTL CMOS

PGC

T1OSO

T1CKI ST

PGC ST

-

XTAL

- Timer1 时钟输入

- ICSP 编程时钟

RB7/T1OSI/PGD RB7 TTL CMOS

T1OSI XTAL

- Timer1 振荡器输入

PGD ST CMOS

图注: O=输出 CMOS = CMOS 输出 P=电源

- = 未使用 I=输入 ST = 施密特触发器输入

TTL = TTL 输入 OD = 漏极开路输出 AN = 模拟

双向 I/O 端口,可以软件编程实现内部弱上拉。

双向 I/O 端口。可以软件编程实现内部弱上拉。

同步数据 I/O

双向 I/O 端口

USART 发送引脚

同步时钟 I/O。可以软件编程实现内部弱上拉。

双向 I/O 端口。可以软件编程实现内部弱上拉。

捕捉 / 比较 /PWM/I/O

双向 I/O 端口。引脚电平变化触发中断。可以软件编程

实现内部弱上拉。

电平变化触发中断以及弱上拉电阻。

双向 I/O 端口。引脚电平变化触发中断。可以软件编程

实现内部弱上拉。

双向 I/O 端口。引脚电平变化触发中断。可以软件编程

实现内部弱上拉。

Timer1 振荡器输出

双向 I/O 端口。引脚电平变化触发中断。可以软件编程

实现内部弱上拉。

ICSP 数据 I/O

表 5-4:与PORTB 相关的寄存器综述

地址 名称

06h,

106h

86h,

186h

81h,

181h

图注: u = 未改变, x = 未知,阴影表示相应位未被 PORTB 使用。

注 1: RB4 的功能由 LVP 配置位设置。

2005 Microchip Technology Inc. DS40044D_CN 第 43 页

PORTB RB7 RB6 RB5 RB4

TRISB TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 1111 1111 1111 1111

OPTION RBPU

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

(2)

RB3 RB2 RB1 RB0 xxxx xxxx uuuu uuuu

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

POR 时

的值

其他

复位

时的值

PIC16F627A/628A/648A

5.3 I/O 编程注意事项

5.3.1 双向 I/O 端口

任何写操作指令,其内部操作都是读操作后跟一个写操

作。例如,BCF和BSF指令先会将寄存器的值读入CPU,

然后执行位操作,最后将结果写回寄存器。当某个端口

定义为既能输入又能输出时,对这些端口执行这些指令

时必须小心。例如,对 PORTB 的 bit 5 执行 BSF 操作

将使 PORTB 的所有 8 个位都被读入 CPU。然后在 bit

5 上进行 BSF 操作,并且 PORTB 被写入输出锁存器。

如果 PORTB 的另一个位用作双向 I/O 引脚 (例如 bit

0),并且此时被定义为输入,则该引脚上的输入信号本

身将被读入 CPU,并将该值重写入该特定引脚的数据锁

存器,覆盖了先前的内容。只要引脚一直是输入模式,

则不会有问题。但是,如果 bit 0 随后切换为输出模式,

则数据锁存器的内容将是未知的。

读端口寄存器将读取端口引脚的值。写端口寄存器将把

值写入端口锁存器。当对某个端口使用读 - 修改 - 写指

令(例如 BCF、BSF 等)时,首先会读取该端口引脚的

值,然后对读入值执行所需的操作,最后将操作结果写

入端口锁存器。

例 5-2 给出了对 I/O 端口连续执行两个读 - 修改 - 写指令

(例如 BCF、 BSF 等)的结果。

当某引脚正在输出低电平或高电平信号时,不应再同时

由外部器件驱动该引脚改变该引脚上的电平 (“线或”

或 “线与”)。产生的高输出电流可能会损坏芯片。

例 5-2:对I/O 端口执行读-修改-

写指令

;Initial PORT settings:PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-up and are

;not connected to other circuitry

;

; PORT latchPORT Pins

---------- ---------BCF STATUS, RP0 ;

BCF PORTB, 7 ;01pp pppp 11pp pppp

BSF STATUS, RP0 ;

BCF TRISB, 7 ;10pp pppp 11pp pppp

BCF TRISB, 6 ;10pp pppp 10pp pppp

;

;Note that the user may have expected the

;pin values to be 00pp pppp. The 2nd BCF

;caused RB7 to be latched as the pin value

;(High).

5.3.2 对 I/O 端口的连续操作

对 I/O 端口的写操作实际发生在指令周期的末尾;但对

于读操作,数据必须在指令周期的开始时就有效(图 5-

16)。因此,如果进行写操作之后,接着对同一个 I/O

端口执行读操作,就要特别注意。指令的执行顺序应该

允许在下一条导致数据写入 CPU 的指令执行之前,引

脚电压达到稳定 (与负载有关)。否则,读入 CPU 的

可能是引脚的前一个状态而非新状态。当状态不确定

时,最好用一个 NOP 指令或其他不访问该 I/O 端口的指

令隔开这些指令。

图 5-16:连续I/O 端口操作

Q1 Q2 Q3 Q4

PC

取出的指令

注 1:此例为写 PORTB 后,接着读 PORTB。

2:数据建立时间 =(0.25 T

此,在较高的时钟频率下,读取以后进行写操作可能会产生问题。

PC

MOVWF PORTB

写 PORTB

CY - TPD),其中 TCY= 指令周期, TPD=Q1 周期到输出有效的传播延时。因

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

PC+1

MOVF PORTB, W

读 PORTB

TPD

执行

MOVWF

PORTB

PC+2 PC+3

NOP NOP

端口引脚

在此采样

执行

MOVF

PORTB, W

执行

NOP

DS40044D_CN 第 44 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

6.0 TIMER0 模块

Timer0 模块定时器 / 计数器具有如下特点:

• 8 位定时器 / 计数器

• 读 / 写能力

• 8 位可软件编程的预分频器

• 内部或外部时钟选择

• FFh 到 00h 的溢出中断

• 外部时钟边沿选择

图 6-1 是 Timer0 模块的简化框图。更多信息,可查阅

《

PICmicro

(DS33023A_CN)。

可通过将 T0CS 位(OPTION<5>)清零选择定时器模

式。在定时器模式下,TMR0 寄存器的值在每个指令周

期递增 1 (不使用预分频器)。如果对 TMR0 寄存器执

行写操作,那么在接下来的两个指令周期将禁止对其进

行递增计数。用户可通过将校正值写入 TMR0 寄存器以

避开这一问题。

可通过将 T0CS 位置 1 选择计数器模式。在该模式下,

TMR0 寄存器的值将在 RA4/T0CKI/CMP2 引脚的每个

上升沿或下降沿递增计数。具体的递增沿由时钟源边沿

(T0SE)控制位 (OPTION<4>)决定。将 T0SE 位清

零选择上升沿。第 6.2 节 “Timer0 用于外部时钟计数”

中详细讨论了外部时钟输入的局限性。

预分频器由 Timer0 模块和看门狗共用。预分频器的分

配可通过软件设置 PSA 控制位 (OPTION<3>)来控

制。清零 PSA 位可将预分频器分配给 Timer0。预分频

器是不可读写的。当将预分频器分配给 Timer0 模块时,

可供选择的预分频比有 1:2, 1:4,……, 1:256。预分

频器的具体操作参见第 6.3 节 “Timer0 预分频器”。

®

中档单片机系列参考手册》

6.2 Timer0 用于外部时钟计数

当 Timer0 用于外部时钟输入的计数时,必须满足一定

要求。这是由于内部相位时钟(T

样,在同步之后 Timer0 仍然要经过一段延时才会真正

执行递增操作。

6.2.1 外部时钟同步

当不使用预分频器时,外部时钟输入与预分频器输出相

同。在内部相位时钟的 Q2 和 Q4 周期对预分频器输出

进行采样可实现 T0CKI 与内部相位时钟的同步 (图 6-

1)。因此,要求 T0CKI 引脚上的信号高、低电平都至

少保持 2TOSC (加上一小段 20ns 的 RC 延时)。具体

请参考所用器件的电气规范。

当使用预分频器时,外部时钟输入要先经过异步计数型

预分频器分频,而使预分频器的输出对称。为了使外部

时钟满足采样要求,必须考虑计数器。因此,要求

T0CKI 引脚上信号的周期至少为 4T

40 ns 的 RC 延时)供预分频器分频。 T0CKI 引脚的高

低电平只须满足最小脉宽为 10 ns 的要求。具体请参考

所用器件电气规范中的参数40、41和42。参见表 17-8。

OSC)同步引起的。同

OSC (加上一小段

6.1 Timer0 中断

当 TMR0 寄存器发生从 FFh 到 00h 的溢出时,即产生

Timer0 中断。该溢出将 T0IF 位置 1。中断可以通过清

零 T0IE 位(INTCON<5>)来屏蔽。在重新允许中断

前,必须在 Timer0 模块的中断服务程序中用软件方法

将 T0IF 位(INTCON<2>)清零。休眠状态时,由于定

时器被关闭,所以 Timer0 中断无法唤醒单片机。

2005 Microchip Technology Inc. DS40044D_CN 第 45 页

PIC16F627A/628A/648A

6.3 Timer0 预分频器

提供了一个 8 位的计数器作为 Timer0 模块的预分频器,

或作为看门狗的后分频器。如果把预分频器分配给

Timer0 模块就意味着看门狗无后分频器可用,反之亦

然。

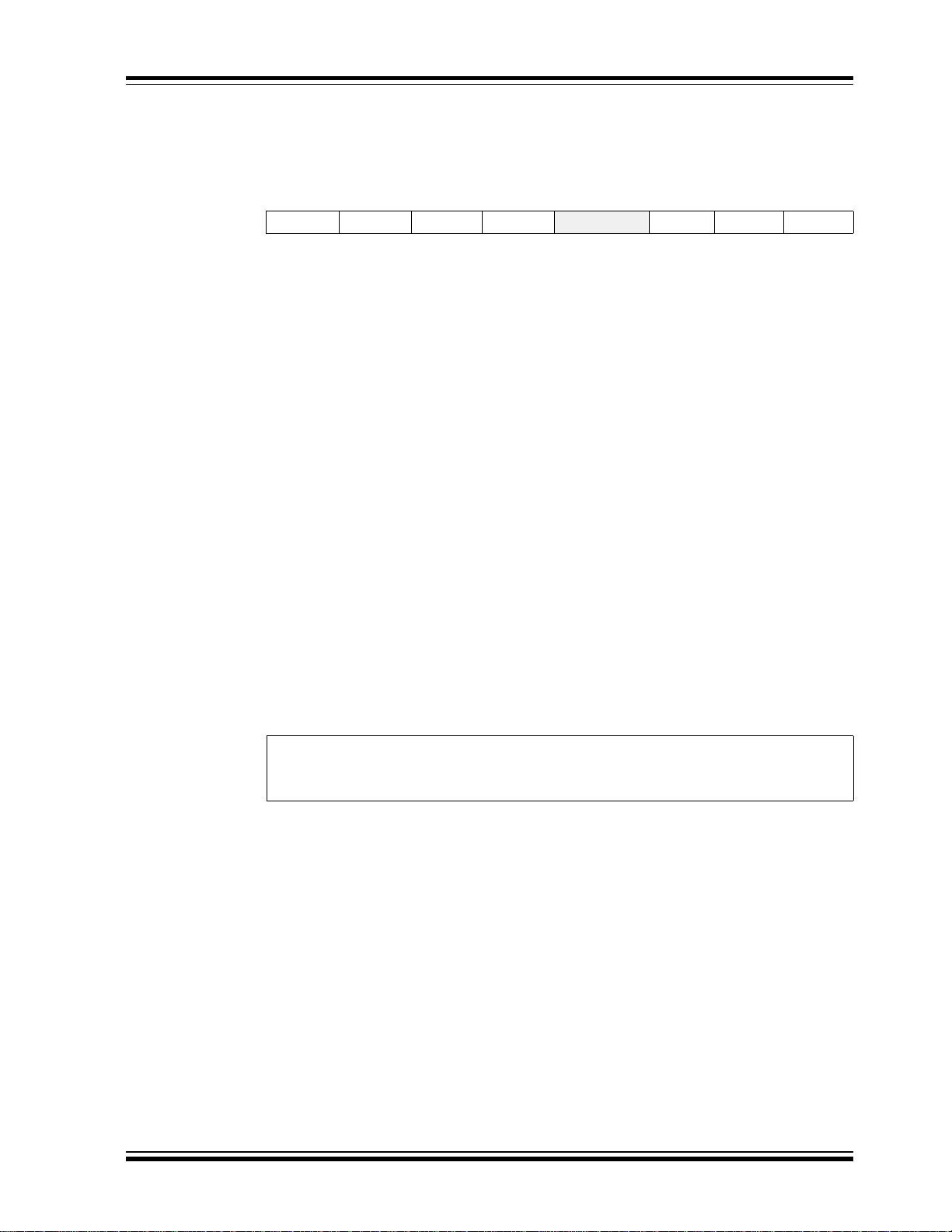

图 6-1: TIMER0/WDT 的框图

F

OSC/4

0

T0CKI

引脚

看门狗

定时器

T0SE

TMR0 时钟源

0

1

PSA

1

T0CS

WDT 后分频器 /

TMR0 预分频器

8

8选 1多路开关

PSA 和 PS<2:0> 位(OPTION<3:0>)决定预分频器的

分配和分频比。

当将预分频器分配给 Timer0 模块时,所有对 TMR0 寄

存器执行的写操作指令 (如 CLRF 1、 MOVWF 1 和

BSF 1, x 等)都将清零预分频器。当将预分频器分配

给 WDT 时,执行 CLRWDT 指令将同时清零预分频器和

看门狗。预分频器是不可读写的。

数据总线

8

1

0

PSA

同步

2 周期

PS<2:0>

TMR0 寄存器

溢出时置位标志位 T0IF

WDT 使能位

1

0

PSA

注: T0SE、T0CS、PSA和 PS<2:0>位在 Option寄存器中。

WDT

超时溢出

DS40044D_CN 第 46 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

6.3.1 切换预分频器的分配

预分频器的分配完全由软件控制(比如,它可在程序执

行期间 “随时”被改变)。当把预分频器从 Timer0 分

配给 WDT 时,必须执行例 6-1 中所示的指令序列,以

避免器件意外复位。

例 6-1: 改变预分频器 (TIMER0 →

WDT)

BCF STATUS, RP0 ;Skip if already in

CLRWDT ;Clear WDT

CLRF TMR0 ;Clear TMR0 and

BSF STATUS, RP0 ;Bank 1

MOVLW '00101111’b ;These 3 lines

MOVWF OPTION_REG ;are required only

CLRWDT ;000 or 001

MOVLW '00101xxx’b ;Set Postscaler to

MOVWF OPTION_REG ;desired WDT rate

BCF STATUS, RP0 ;Return to Bank 0

;Bank 0

;Prescaler

;(5, 6, 7)

;if desired PS<2:0>

;are

表 6-1:与TIMER0 相关的寄存器

地址 名称

01h、 101h

0Bh、 8Bh、

10Bh、 18Bh

81h、 181h

85h TRISA

图注:

注 1: Option 寄存器在 MPLAB

TMR0

INTCON GIE

OPTION

- = 未实现的地址单元,读作 0, u = 未改变, x = 未知。阴影单元表示在 Timer0 模块中未使用。

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Timer0 模块寄存器

PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

(2)

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

TRISA7 TRISA6

®

IDE 中用 OPTION_REG 表示。

TRISA5

TRISA4

要将预分频器从 WDT 分配给 Timer0 模块,使用例 6-2

所示的指令序列。即使 WDT 被禁止也要采取该预防措

施。

例 6-2: 改变预分频器 (WDT →

TIMER0)

CLRWDT ;Clear WDT and

BSF STATUS, RP0

MOVLW b'xxxx0xxx' ;Select TMR0, new

MOVWF OPTION_REG

BCF STATUS, RP0

TRISA3 TRISA2 TRISA1 TRISA0 1111 1111 1111 1111

;prescaler

;prescale value and

;clock source

POR 时

的值

xxxx xxxx uuuu uuuu

所有其他

复位时的值

2005 Microchip Technology Inc. DS40044D_CN 第 47 页

PIC16F627A/628A/648A

7.0 TIMER1 模块

Timer1 模块是由两个可读写 8 位寄存器 (TMR1H 和

TMR1L)组成的 16 位定时器 / 计数器。 TMR1 寄存器

对(TMR1H:TMR1L)从 0000h 开始递增计数,一直

递增到 FFFFh,然后从 0000h 重新开始递增计数。如

果允许 Timer1 中断,那么当用于锁存中断标志位

TMR1IF (PIR1<0>)的 TMR1 寄存器对发生溢出时就

会产生 Timer1 中断。可以通过对 Timer1 中断允许位

TMR1IE (PIE1<0>)置位 / 清零来允许 / 禁止该中断。

Timer1 有下列两种工作模式:

• 定时器模式

• 计数器模式

工作模式由时钟选择位 TMR1CS(T1CON<1>)决定。

在定时器模式下,TMR1 寄存器对的值在每个指令周期

递增计数。而在计数器模式下,它在外部时钟输入引脚

的每个上升沿递增计数。

可以通过对控制位 TMR1ON (T1CON<0>)置位 / 清

零来使能 / 禁止 Timer1。

Timer1 还有一个内部“复位输入”。这个复位可由 CCP

模块产生。(参见第 9.0 节 “捕捉 / 比较 /PWM (CCP)

模块”)寄存器 7-1 中是 Timer1 控制寄存器。

对于 PIC16F627A/628A/648A 而言,当使能 Timer1 的

振荡器 (T1OSCEN 位置 1)时, RB7/T1OSI/PGD 和

RB6/T1OSO/T1CKI/PGC 引脚就变为输入引脚。即

寄存器 7-1: T1CON — TIMER1 控制寄存器 (地址:10h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

- -

bit 7 bit 0

bit 7-6 未实现:读作 0

bit 5-4 T1CKPS<1:0>:Timer1 输入时钟预分频比选择位

11=1:8 预分频比

10=1:4 预分频比

01=1:2 预分频比

00=1:1 预分频比

bit 3 T1OSCEN:Timer1 振荡器使能控制位

1= 使能振荡器

0= 关闭振荡器

bit 2 T1SYNC:Timer1 外部时钟输入同步控制位

TMR1CS=1

1= 不同步外部时钟输入

0= 同步外部时钟输入

TMR1CS=0

此位被忽略。 TMR1CS=0 时, Timer1 使用内部时钟。

bit 1 TMR1CS:Tim er1 时钟源选择位

1= 选择来自 RB6/T1OSO/T1CKI/PGC 引脚的外部时钟 (上升沿有效)

0= 选择内部时钟 (F

bit 0 TMR1ON:Timer1 开启位

1= 使能 Timer1

0= 停止 Timer1

注 1:关断振荡器的反相器和反馈电阻以降低功耗。

(1)

T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

OSC/4)

TMR1CS TMR1ON

图注:

R= 可读位 W= 可写位 U= 未实现位,读作 0

-n=POR 时的值 1= 置位 0= 清零 x= 未知

DS40044D_CN 第 48 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

7.1 Timer1 工作在定时器模式

通过将 TMR1CS (T1CON<1>)位清零选择定时器模

式。在这种模式下,定时器的输入时钟是 F

OSC/4。因 为

内部时钟总是同步的,所以同步控制位 T1SYNC

(T1CON<2>)此时不起作用。

7.2 Timer1 工作在同步计数器模式

通过将 TMR1CS 位置 1 选择计数器模式。在这种模式

下, TMR1 寄存器对的值在引脚 RB7/T1OSI/PGD

(T1OSCEN 位置 1 时)或 RB6/T1OSO/T1CKI/PGC

(T1OSCEN 位清零时)上的每个输入时钟上升沿到来

时递增 1。

如果 T1SYNC

钟同步。同步是在预分频之后完成的。预分频器是一个

异步计数器。

在该模式配置下,由于在休眠模式下关断同步电路,所

以即使使用外部时钟,TMR1 寄存器对的值也不能递增

计数。但是预分频器会继续递增计数。

图 7-1: TIMER1 框图

RB6/T1OSO/T1CKI/PGC

RB7/T1OSI/PGD

位清零,那么外部时钟输入与内部相位时

溢出置位

标志位 TMR1IF

TMR1

TMR1H

T1OSC

TMR1L

T1OSCEN

使能

振荡器 (1)

F

内部

时钟

OSC/4

7.2.1 同步计数器模式下的外部时钟输入

当外部时钟输入用于同步计数器模式下的Timer1 时,必

须满足一定要求。这是由于内部相位时钟(To s c)同 步

引起的。而且在同步之后,TMR1 寄存器对的值仍然要

经过一段延时才会进行递增 1 操作。

当预分频比为 1:1 时,外部时钟输入和预分频器的输出

相同。在内部相位时钟的 Q2 和 Q4 周期,对预分频器

输出进行采样,可实现 T1CKI 与内部相位时钟的同步。

因此,必须要求 T1CKI 引脚上信号的高、低电平都至少

保持 2Tosc(加上一小段 20ns 的 RC 延时)。具体请参

考电气规范章节中的参数 45、 46 和 47。

当使用的预分分频比不是 1:1 时,外部时钟输入要先经

过异步计数型预分频器的分频,从而使预分频器的输出

对称。为了使外部时钟满足采样要求,必须考虑计数

器。因此,必须要求 T1CKI 引脚上信号的周期至少为

4Tosc (加上一小段 40ns 的 RC 延时)供预分频器分

频。T1CKI 引脚上信号的高低电平时间只需满足最小脉

宽为 10ns 的要求。具体请参考适用电气规范中的参数

45、 46 和 47。

同步的

时钟输入

同步

检测

休眠输入

TMR1ON

1

0

TMR1CS

0

1

T1SYNC

预分频器

1, 2, 4, 8

T1CKPS<1:0>

2

注 1: 当 T1OSCEN 位清零时,反相器和反馈电阻被关断以消除功耗。

2005 Microchip Technology Inc. DS40044D_CN 第 49 页

PIC16F627A/628A/648A

7.3 Timer1 工作在异步计数器模式

如果控制位 T1SYNC(T1CON<2>)置 1,外部时钟输

入就不同步。计数器继续进行与内部相位时钟异步的递

增计数。在休眠状态下计数器将仍继续运行,并在溢出

时产生中断,唤醒处理器。但在软件中应特别注意对计

数器的读写(第 7.3.2 节 “异步计数器模式下对 Timer1

的读写操作”)。

注: 在异步计数器模式下, Timer1 不能用作捕

捉器或比较器工作的时基。

7.3.1 异步时钟的外部时钟输入时序

如果控制位 T1SYNC 被置 1,计数器将完全异步地进行

递增计数。输入时钟必须满足高电平和低电平的最小脉

宽要求。参阅电气规范一章中的表 17-8 以及时序参数

45、 46 和 47。

7.3.2 异步计数器模式下对 TIMER1 的读写

操作

当计数器工作在外部异步时钟下时,读 TMR1H 或

TMR1L 寄存器能够产生有效的读取(由硬件完成)。但

用户应牢记,用读两个 8 位值来读一个 16 位定时器会

出现问题,这是因为在两次读取操作之间计数器可能会

溢出。

对于写操作,建议用户停止计数器后再写入需要的数

值。而寄存器正在递增计数时,向定时器寄存器写入数

据可能会产生写争用。这可能在定时器寄存器中产生无

法预知的值。

读 16 位值时应非常注意。例 7-1 是读取 16 位定时器值

的程序示例。在定时器无法停止时,该程序很有帮助。

例 7-1: 读取独立运行的 16 位定时

器

; All interrupts are disabled

MOVF TMR1H, W ;Read high byte

MOVWF TMPH ;

MOVF TMR1L, W ;Read low byte

MOVWF TMPL ;

MOVF TMR1H, W ;Read high byte

SUBWF TMPH, W ;Sub 1st read with

;2nd read

BTFSC STATUS,Z ;Is result = 0

GOTO CONTINUE ;Good 16-bit read

;

; TMR1L may have rolled over between the

; read of the high and low bytes. Reading

; the high and low bytes now will read a good

; value.

;

MOVF TMR1H, W ;Read high byte

MOVWF TMPH ;

MOVF TMR1L, W ;Read low byte

MOVWF TMPL ;

; Re-enable the Interrupts (if required)

CONTINUE ;Continue with your

;code

DS40044D_CN 第 50 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

7.4 Timer1 振荡器

在 T1OSI (输入)和 T1OSO (放大器输出)引脚之间

内接有晶振电路。通过将控制位 T1OSCEN

(T1CON<3>)置 1 使能该电路。它在休眠状态下可以

继续工作。一般倾向于使用 32.768 kHz 的时钟晶振。

表 7-1 给出了 Timer1 振荡器的电容选择。

用户必须提供软件时间延迟来确保振荡器正确起振。

表 7-1: TIMER1 振荡器的电容选择

频率

32.768 kHz 15 pF 15 pF

注:这些值仅供设计参考。

想要获取更多有关晶振 / 电容选择的信息,请查

阅 AN826 “Crystal Oscillator Basics and Crys-

tal Selection for rfPIC

(DS00826)。

C1 C2

®

and PICmicro® Devices ”

7.5 用 CCP 触发器输出复位 Timer1

如果在比较模式下将 CCP1 模块配置为产生“特殊事件

触发信号”(CCP1M<3:0> =1011),则该信号会复位

Timer1。

注: CCP1模块的特殊事件触发信号不会将中断

标志位 TMR1IF (PIR1<0>)置 1。

为了利用这一特点,Timer1 必须设置为定时器或同步计

数器模式。如果 Timer1 在异步计数器模式下运行,该

复位操作可能不起作用。

当对 Timer1 的写操作与 CCP1 的特殊事件触发信号同

时发生时,写操作优先。

在这种工作方式下,寄存器对 CCPRxH:CCPRxL 实际

上变成了 Timer1 的周期寄存器。

7.6 复位 Timer1 寄存器对 (TMR1H, TMR1L)

除了 CCP1 特殊事件触发信号 (参见第 9.2.4 节 “特

殊事件触发”)外, POR 或其他复位都不会将 TMR1H

和 TMR1L 复位至 00h。

T1CON寄存器在上电复位或欠压复位时复位为00h,这

样就关闭了定时器并得到 1:1 的预分频比。在所有其他

复位中,寄存器都不受影响。

7.7 Timer1 预分频器

在对 TMR1H 或 TMR1L 寄存器进行写操作时,预分频

器计数器被清零。

表 7-2: 与作为定时器 / 计数器的 TIMER1 有关的寄存器

地址 名称

0Bh、 8Bh、

10Bh、 18Bh

0Ch PIR1

8Ch PIE1

0Eh TMR1L

0Fh TMR1H

10h T1CON

图注: x= 未知, u= 未改变,- = 未实现,读作 0。阴影部分表示在 Timer1 模块中未使用。

INTCON GIE PEIE

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

EEIF CMIF RCIF TXIF

EEIE CMIE RCIE TXIE

16 位 TMR1 寄存器低字节的保持寄存器

16 位 TMR1 寄存器高字节的保持寄存器

- -

T1CKPS1 T1CKPS0 T1OSCEN T1SYNC

-

-

CCP1IF TMR2IF TMR1IF 0000 -000 0000 -000

CCP1IE TMR2IE TMR1IE 0000 -000 0000 -000

POR 时的值所有其他

复位时的值

xxxx xxxx uuuu uuuu

xxxx xxxx uuuu uuuu

TMR1CS TMR1ON --00 0000 --uu uuuu

2005 Microchip Technology Inc. DS40044D_CN 第 51 页

PIC16F627A/628A/648A

8.0 TIMER2 模块

Timer2 是一个 8 位定时器,带一个预分频器和一个后分

频器。它可用作 CCP 模块 PWM 模式的时基。TMR2 寄

存器是可读写的,任何器件复位都会使之清零。

输入时钟 (F

1:1、 1:4 或 1:16,可通过控制位 T2CKPS<1:0>

(T2CON<1:0>)来进行选择。

Timer2 模块有一个 8 位周期寄存器 PR2。 TMR2 寄存

器的值从 00h 开始递增计数,直到与 PR2 寄存器的值

匹配为止,然后在下一个计数周期复位至 00h。PR2 寄

存器为可读写的寄存器。复位将 PR2 寄存器初始化为

FFh。

Timer2 的匹配输出通过 4 位后分频器(可提供从 1:1 到

1:16 的分频比)产生 Timer2 中断 (锁存在 TMR2IF 标

志位 (PIR1<1>)中)。

通过清零控制位 TMR2ON (T2CON<2>)可以 关 闭

Timer2,以最大限度地降低功耗。

寄存器 8-1 中是 Timer2 控制寄存器。

osc/4)可以选择三种预分频比,分别是

8.1 Timer2 预分频器和后分频器

当发生下列任一种情况时,都会将预分频器和后分频器

计数器清零:

• 对 TMR2 寄存器进行写操作

• 对 T2CON 寄存器进行写操作

• 任何器件复位 (上电复位、 MCLR

复位、看门狗

复位或者欠压复位)

当对 T2CON 进行写操作时, TMR2 寄存器并不清零。

8.2 TMR2 输出

将 TMR2 输出(在后分频器之前)馈送至同步串行端口

模块,亦可选择将其用于生成移位时钟。

图 8-1: TIMER2 框图

置位标志位

TMR2IF

后分频器

1:1 1:16

TOUTPS<3:0>

TMR2

输出

复位

TMR2 寄存器

至

4

相等

比较器

PR2 寄存器

预分频器

1:1, 1:4, 1:16

2

T2CKPS<1:0>

F

OSC/4

DS40044D_CN 第 52 页 2005 Microchip Technology Inc.

PIC16F627A/628A/648A

寄存器 8-1: T2CON — TIMER2 控制寄存器 (地址:12h)

U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

-

bit 7 bit 0

bit 7 未实现位:读作 0

bit 6-3 TOUTPS<3:0>:Timer2 输出后分频比选择位

0000 = 1:1 后分频比

0001 = 1:2 后分频比

•

•

•

1111 = 1:16 后分频比

bit 2 TMR2ON:Timer2 使能位

1 = 使能 Timer2

0 = 停止 Timer2

bit 1-0 T2CKPS<1:0>:Timer2 时钟预分频比选择位

00 = 1:1 预分频比

01 = 1:4 预分频比

1x = 1:16 预分频比