MT6329 PMIC Data Sheet

Free Datasheet http://www.datasheet4u.com/

Version: 0.4

Release date: 2012/01/20

© 2011 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 2 of 97

Revision

Date

Author

Description

0.1

2011/09/30

Trevor Chou

Initial

0.2

2011/12/16

Trevor Chou

1. Update Package Dimensions

2. Update Electrical Characteristics

3. Update Register table

0.3

2011/12/28

Trevor Chou

1. Modify VRF LDO functional description

2. Update Buck Converter Un-Use application note

0.4

2012/01/20

Trevor Chou

1. Modify Figure 3: Power-on/off control sequence

Free Datasheet http://www.datasheet4u.com/

Document Revision History

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 3 of 97

Free Datasheet http://www.datasheet4u.com/

Table of Contents

Document Revision History .................................................................................................................. 2

Table of Contents ................................................................................................................................... 3

1 Overview ........................................................................................................................................ 5

1.1 Features ................................................................................................................................ 6

1.2 Applications .......................................................................................................................... 6

1.3 General Descriptions ............................................................................................................ 6

1.4 Ordering Information ............................................................................................................. 7

1.5 Top Marking Definition .......................................................................................................... 7

1.6 Pin Assignments and Descriptions ....................................................................................... 8

2 Electrical Characteristics .......................................................................................................... 13

2.1 Absolute Maximum Ratings over Operating Free-Air Temperature Range ....................... 13

2.2 Thermal Characteristic ....................................................................................................... 13

2.3 Pin Voltage Rating (TBD) ................................................................................................... 13

2.4 Recommended Operating Range ....................................................................................... 13

2.5 Electrical Characteristics .................................................................................................... 14

2.6 Regulator Output ................................................................................................................ 15

2.7 Class AB/D Audio Amplifier ................................................................................................ 20

2.8 Battery Charger .................................................................................................................. 22

2.9 Driver .................................................................................................................................. 23

2.10 Analog Switch ..................................................................................................................... 23

2.11 BC1.1 .................................................................................................................................. 23

2.12 Down Load Without Battery ................................................................................................ 24

2.13 Fuel Gauge ......................................................................................................................... 24

3 Functional Descriptions ............................................................................................................ 25

FOR zlixin@ waterworld.com.cn USE ONLY

3.1 General Descriptions .......................................................................................................... 25

3.2 PMIC Functional Blocks ..................................................................................................... 25

3.2.1 Power-On/Off Sequence .................................................................................... 26

Power on/off sequence ................................................................................................................. 26

3.2.2 The Battery Charger (Charger Controller) ......................................................... 28

3.2.3 Buck Converter ................................................................................................... 32

3.2.4 DVFS Control (Dynamic Voltage Frequency Scaling) ....................................... 33

3.2.5 Low Dropout Regulator (LDOs) and Reference ................................................. 35

3.2.6 Drivers ................................................................................................................ 39

3.2.7 Analog Switch ..................................................................................................... 43

3.2.8 Class-AB/D Audio Amplifier ............................................................................... 43

MEDIATEK CONFIDENTIAL

3.2.9 Fuel Gauge ......................................................................................................... 44

3.2.10 I2C Interface ....................................................................................................... 48

3.3 Register Table and Descriptions ........................................................................................ 50

3.3.1 Bank 0 ................................................................................................................ 50

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 4 of 97

Free Datasheet http://www.datasheet4u.com/

3.3.2 Bank 1 ................................................................................................................ 76

3.4 Connection to Baseband .................................................................................................... 93

4 Application Notes ....................................................................................................................... 94

4.1 Hardware External Shutdown ............................................................................................. 94

4.2 Buck Converter (VRF18) with LDO Mode .......................................................................... 94

4.3 Buck Converter Un-Use Configuration ............................................................................... 95

5 MT6329 Packaging ..................................................................................................................... 96

5.1 Package Dimensions .......................................................................................................... 96

Appendix ............................................................................................................................................... 97

Lists of Figures

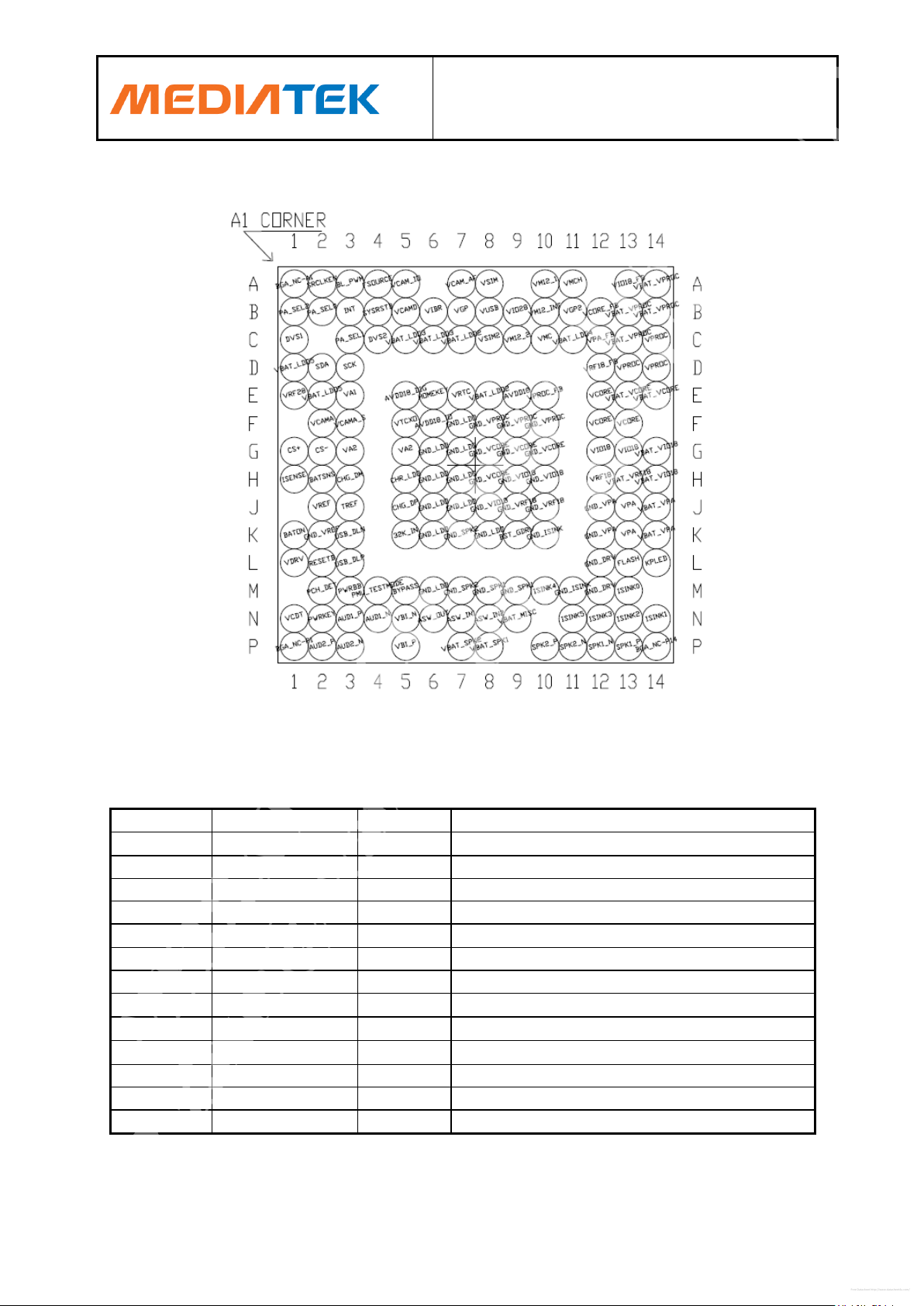

Figure 1: MT6329 TFBGA 155 (7.6x7.6mm) pin assignment ................................................................. 8

Figure 2: MT6329 block diagram…………………………………………………………………………….27

Figure 3: Power-on/off control sequence by pressing PWRKEY .......................................................... 26

Figure 4: PCHR block diagram ............................................................................................................. 28

Figure 5: Charging states diagram ........................................................................................................ 30

Figure 6: LDO block diagram ................................................................................................................ 35

Figure 7: Configuration for parallel BL LED drivers .............................................................................. 40

Figure 8: Configuration for serial BL LED drivers ................................................................................. 40

Figure 9: Configuration for flash light LED driver .................................................................................. 41

Figure 11: Block diagram of class-AB/D ............................................................................................... 44

Figure 12: Fuel gauge block diagram and external connection ............................................................ 45

Figure 13: Watchdog ............................................................................................................................. 48

Figure 14: Connection to BB ................................................................................................................. 93

Figure 15: Hardware external shut-down function ................................................................................ 94

Figure 16: DC/DC and LDO mode HW setting application note ........................................................... 95

Lists of Tables

Table 1: MT6329 pin descriptions……………………………………………………………………………..8

Table 2: Absolute maximum ratings ...................................................................................................... 13

Table 3: Operation condition ................................................................................................................. 13

Table 4: General electrical specifications .............................................................................................. 14

Table 5: Regulator specifications .......................................................................................................... 15

Table 6: Power switch specifications ....................................................... Error! Bookmark not defined.

Table 7: Class AB/D audio amplifier specifications ............................................................................... 20

Table 8: Charger specifications ............................................................................................................. 22

Table 9: Driver specifications ................................................................................................................ 23

Table 10: Analog switch specifications .................................................................................................. 23

Table 11: LDO types and brief specifications ........................................................................................ 35

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 5 of 97

Free Datasheet http://www.datasheet4u.com/

1 Overview

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 6 of 97

1.1 Features

Free Datasheet http://www.datasheet4u.com/

Handles all 2G/3G/smart phone baseband

power management

Input range: 3.4 ~ 4.3V

Charger input of up to 10V

5 buck converters and 21 LDOs optimized

for specific 2G/3G/smart phone

subsystems

Dual-channel, 3.7V 0.7W into 8Ω Class

AB/D audio amplifiers

Flexibility for various configurations of

backlight LED drivers: 6ISINK/10WLED

boost controller

I2C interface

Pre-charge indication

Li-ion battery charging function

Multi-purpose pins support either current

sinks or analog switches

Multi-purpose pins support either an RGB

LED driver or an audio receiver

VPROC with DVFS control

Over-current and thermal overload

protection

Programmable under voltage lockout

protection

Watchdog timer

Flexibility hardware PMIC reset function

Power-on reset and start-up timer

Precision voltage, temperature, and

current measurement fuel gauge

155-pin TFBGA package

1.2 Applications

Ideal for power management of 2G, 3G, smart

phones and other portable systems.

MT6329 for MediaTek 3G smart phone platform,

MT6575.

MEDIATEK CONFIDENTIAL

phones, especially those based on the

MediaTek MT6575 system solution. MT6329

contains 15 buck converters and 21 LDOs,

which are optimized for specific 2G/3G/smart

phone subsystems.

MT6329 provides dual-channel, 0.7W into 8Ω,

high efficiency Class AB/D audio amplifiers and

flexibility for various applications of backlight

LED drivers. It supports up to 6 WLEDs in

parallel or alternative series 10WLED

configurations. Flexible control keeps high

power efficiency while supporting multiple

drivers.

Sophisticated controls are available for powerup, battery charging and the RTC alarm.

MT6329 is optimized for maximum battery life.

The selectable 1-step or 2-step RTC LDO

design makes MT6329 suitable for different

RTC modules in BB chips. It allows the RTC

circuit to stay alive without a battery for several

hours. The battery charger in MT6329 supports

lithium- ion (Li-ion) battery and provides precharge indication. The charger input voltage

can be up to 10V and allows USB charging, too.

Some multi-purpose pins enable MT6329 to be

configured in various applications. MT6329

implements dedicate analog switches, KPLED

and 450mA FLASH LED driver.

MT6329 adopts I2C interface to control buck

converters (dedicate 2 pins DVFS control and 3

pins PA_SEL control), LDOs, Class AB/D,

various drivers and charger. Besides, it provides

enhanced safety control and protocol for

handshaking with BB.

MT6329 is available in a 155-pin TFBGA

package. The operating temperature ranges

from -25 to +85°C.

1.3 General Descriptions

MT6329 is a power management system chip

optimized for 2G/3G handsets and smart

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 7 of 97

Order #

Marking

Temp. range

Package

MT6329A

-25 ~ +85°C

TFBGA - 155L

MEDIATEK

M T 6 3 2 9 A

DDDD- B G & H

C $ $ $ $ $

O

Free Datasheet http://www.datasheet4u.com/

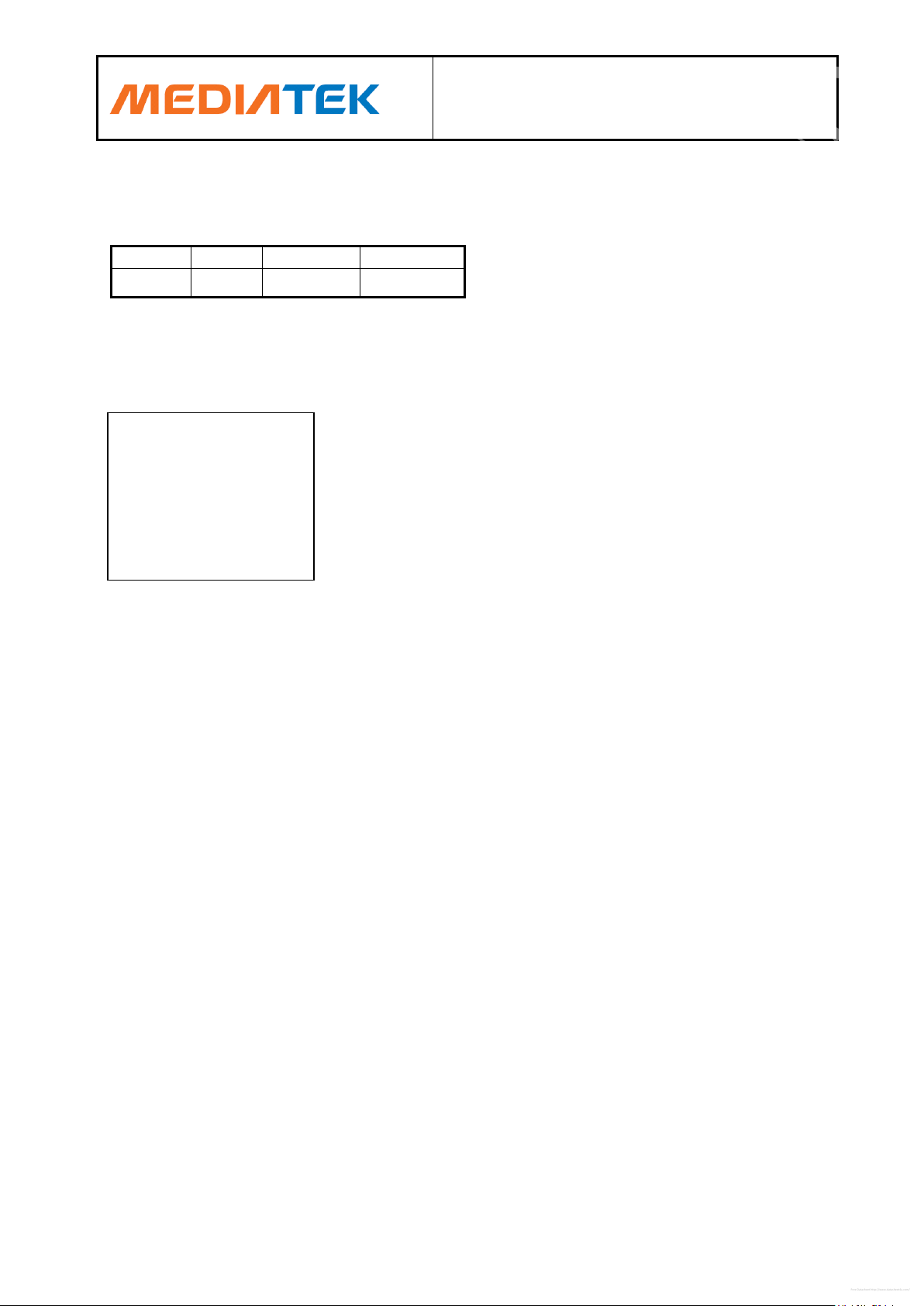

1.4 Ordering Information

1.5 Top Marking Definition

MT6329A

DDDD: Date code

$$$$$: LOT No.

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 8 of 97

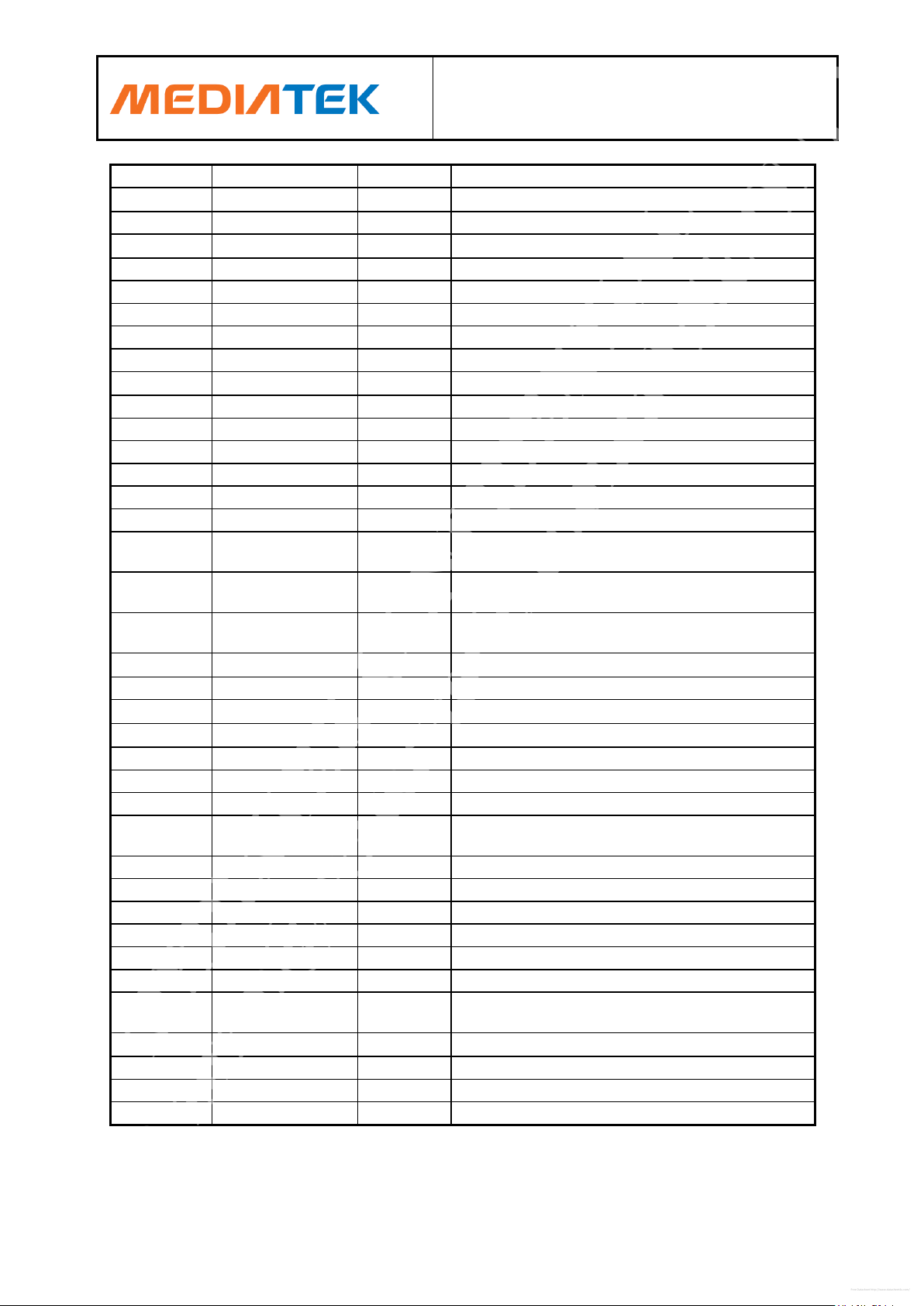

Ball

Symbol

I/O

Description

A1

BGA_NC-A1

I/O

NC

A2

SRCLKEN

I

Source clock enabling signal

A3

BL_PWM

I

External backlight CABC PWM control input signal

A4

FSOURCE

I

Connects to AVDD18_DIG in normal mode

A5

VCAM_IO

O

LDO output used for camera IO

A7

VCAM_AF

O

LDO output used for camera auto-focus

A8

VSIM

O

LDO output used for SIM card

A10

VM12_1

O

LDO output used for 1.2V DRAM

A11

VMCH

O

LDO output for SD 3.0 memory card

A13

VIO18_FB

I

VIO18 feedback input

A14

VBAT_VPROC

PWR

VBAT for VPROC

B1

PA_SEL2

I

PA output voltage selection

B2

PA_SEL0

I

PA output voltage selection

Free Datasheet http://www.datasheet4u.com/

1.6 Pin Assignments and Descriptions

Figure 1: MT6329 TFBGA 155 (7.1x7.1mm) pin assignment

Table 2: MT6329 pin descriptions

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 9 of 97

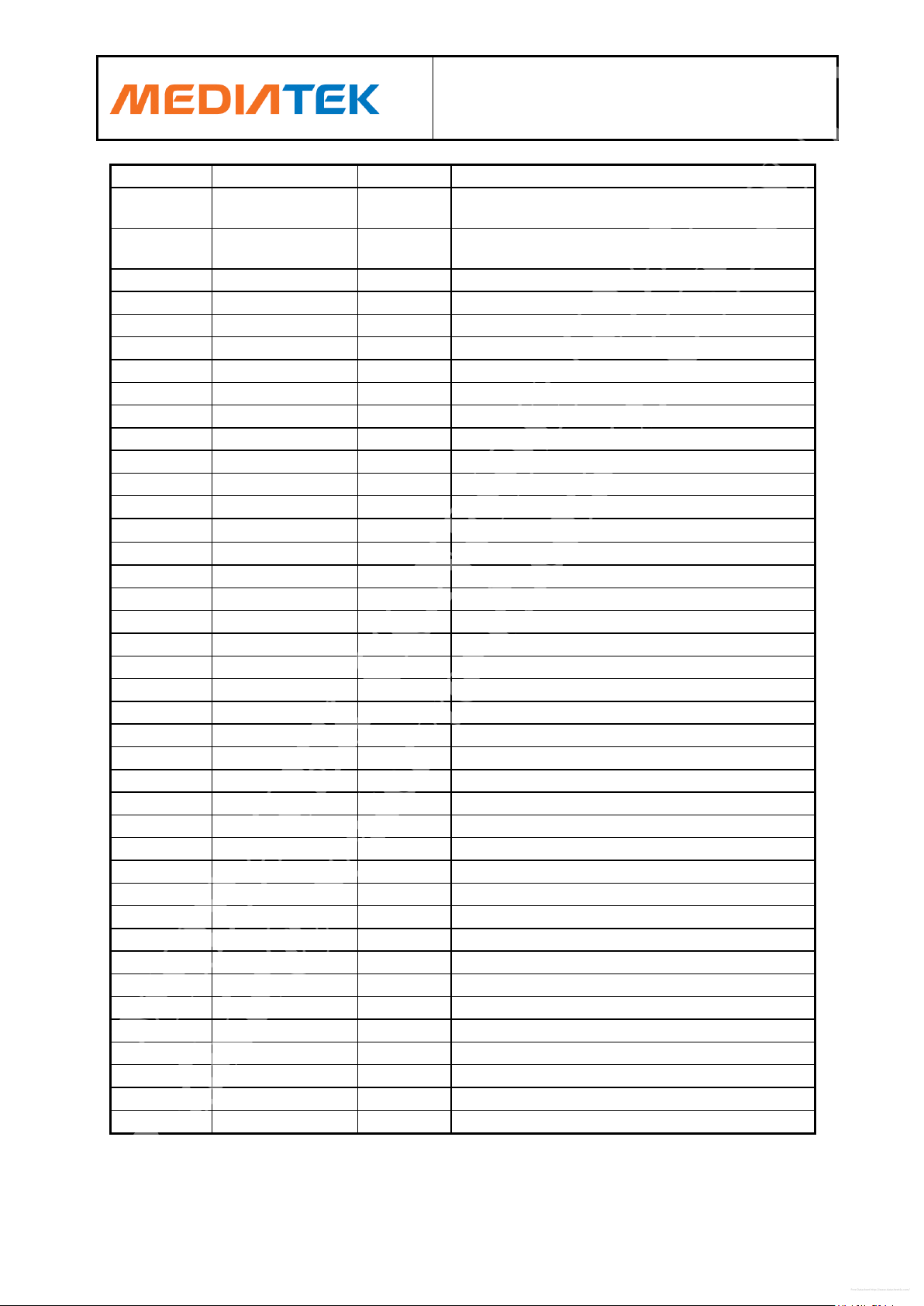

Ball

Symbol

I/O

Description

B3

INT

O

Interrupt output

B4

SYSRSTB

I

External system reset input pin (active low)

B5

VCAMD

O

LDO output used for camera digital

B6

VIBR

O

LDO output used for vibrator

B7

VGP

O

LDO output reserved for further system use

B8

VUSB

O

LDO output used for USB

B9

VIO28

O

LDO output used for 2.8V IO

B10

VM12_INT

O

LDO output used for 1.2V SRAM

B11

VGP2

O

LDO output reserved for further system use

B12

VCORE_FB

I

VCORE feedback input

B13

VBAT_VPROC

PWR

VBAT for VPROC

B14

VBAT_VPROC

PWR

VBAT for VPROC

C1

DVS1

I

VPROC output voltage selection

C3

PA_SEL1

I

PA output voltage selection

C4

DVS2

I

VPROC output voltage selection

C5

VBAT_LDO3

PWR

VBAT for VIBR, VCAM_IO, VCAMD, VRTC and

IBIAS_DLDO1

C6

VBAT_LDO3

PWR

VBAT for VIBR, VCAM_IO, VCAMD, VRTC and

IBIAS_DLDO1

C7

VBAT_LDO2

PWR

VBAT for VIO28, VSIM, VSIM2, VUSB, VGP and

VCAM_AF

C8

VSIM2

O

LDO output used for 2nd SIM card

C9

VM12_2

O

LDO output for 1.2V DRAM or AST3002

C10

VMC

O

LDO output for memory card

C11

VBAT_LDO4

PWR

VBAT for VMC, VMCH, VGP2 and IBIAS_DLDO2

C12

VPA_FB

I

VPA feedback input

C13

VBAT_VPROC

PWR

VBAT for VPROC

C14

VPROC

O

VPROC switching output

D1

VBAT_LDO5

PWR

VBAT for VA1, VA2, VCAMA, VTCXO, VRF28

and IBIAS_ALDO

D2

SDA

I

I2C serial data

D3

SCK

I

I2C serial clock

D12

VRF18_FB

I

VRF18 feedback input

D13

VPROC

O

VPROC switching output

D14

VPROC

O

VPROC switching output

E1

VRF28

O

LDO output for RF

E2

VBAT_LDO5

PWR

VBAT for VA1, VA2, VCAMA, VTCXO, VRF28

and IBIAS_ALDO

E3

VA1

O

LDO output for analog baseband

E5

AVDD18_DIG

O

LDO output bypass pin

E6

HOMEKEY

I

Homekey

E7

VRTC

O

LDO output for RTC

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 10 of 97

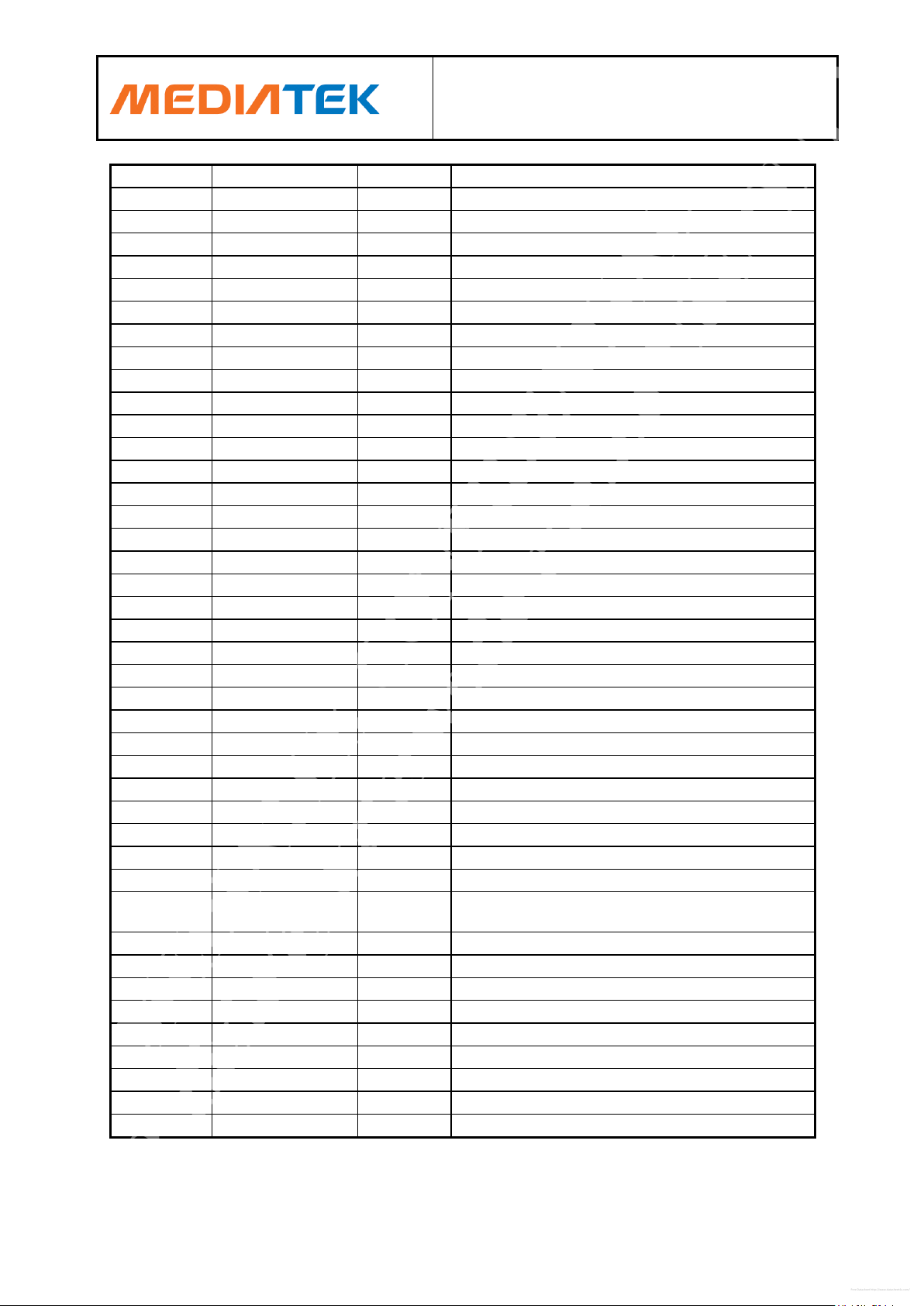

Ball

Symbol

I/O

Description

E8

VBAT_LDO2

PWR

VBAT for VIO28, VSIM, VSIM2, VUSB, VGP and

VCAM_AF

E9

AVDD18

PWR

1.8V power input for VM12_1, VM12_2 and

VM12_INT

E10

VPROC_FB

I

VPROC feedback input

E12

VCORE

O

VCORE switching output

E13

VBAT_VCORE

PWR

VBAT for VCORE

E14

VBAT_VCORE

PWR

VBAT for VCORE

F2

VCAMA

O

LDO output for camaera analog

F3

VCAMA_S

I

Sense input for VCAMA LDO

F5

VTCXO

O

LDO output for TCXO

F6

AVDD18_IO

PWR

1.8V IO power input for internal GPIO

F7

GND_LDO

GND

GND for LDO

F8

GND_VPROC

GND

GND for VPROC

F9

GND_VPROC

GND

GND for VPROC

F10

GND_VPROC

GND

GND for VPROC

F12

VCORE

O

VCORE switching output

F13

VCORE

O

VCORE switching output

G1

CS+

I

Fuel gauge positive current sense point

G2

CS-

I

Fuel gauge negative current sense point

G3

VA2

O

LDO output for analog baseband

G5

VA2_BUF

O

LDO output for analog baseband

G6

GND_LDO

GND

GND for LDO

G7

GND_LDO

GND

GND for LDO

G8

GND_VCORE

GND

GND for VCORE

G9

GND_VCORE

GND

GND for VCORE

G10

GND_VCORE

GND

GND for VCORE

G12

VIO18

O

VIO18 switching output

G13

VIO18

O

VIO18 switching output

G14

VBAT_VIO18

PWR

VBAT for VIO18

H1

ISENSE

I

Charging current sense input

H2

BATSNS

I

Battery voltage sense input

H3

CHG_DM

I

USB D- for BC1.1 standard

H5

CHR_LDO

O

Charger LDO output bypass pin

H6

GND_LDO

GND

GND for LDO

H7

GND_LDO

GND

GND for LDO

H8

GND_VCORE

GND

GND for VCORE

H9

GND_VIO18

GND

GND for VIO18

H10

GND_VIO18

GND

GND for VIO18

H12

VRF18

O

VRF18 switching output

H13

VBAT_VRF18

PWR

VBAT for VRF18

H14

VBAT_VIO18

PWR

VBAT for VIO18

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 11 of 97

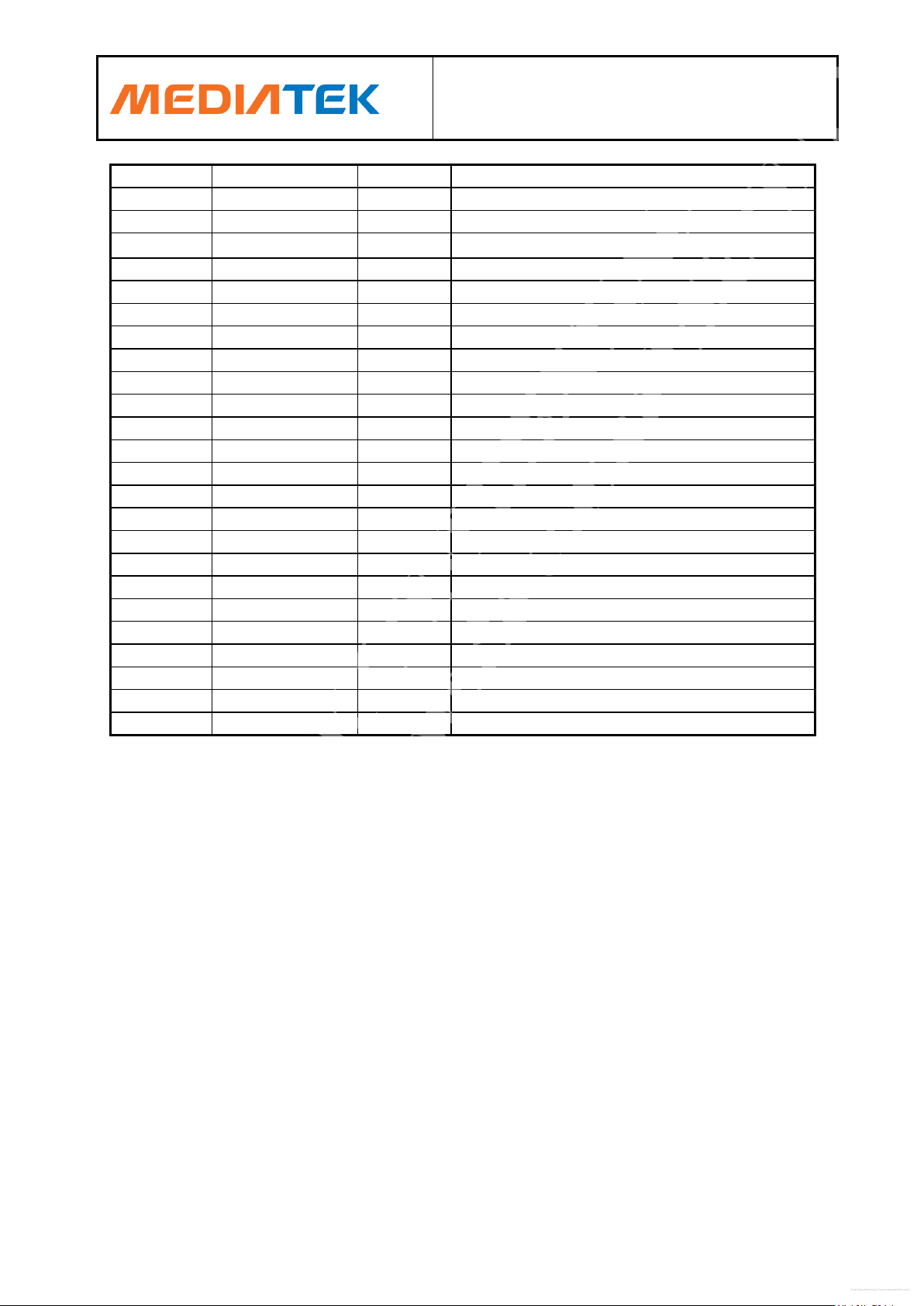

Ball

Symbol

I/O

Description

J2

VREF

O

Internal reference bypass

J3

TREF

O

Battery thermal detection reference voltage

J5

CHG_DP

I

USB D+ for BC1.1 standard

J6

GND_LDO

GND

GND for LDO

J7

GND_LDO

GND

GND for LDO

J8

GND_VIO18

GND

GND for VIO18

J9

GND_VRF18

GND

GND for VRF18

J10

GND_VRF18

GND

GND for VRF18

J12

GND_VPA

GND

GND for VPA

J13

VPA

O

VPA switching output

J14

VBAT_VPA

PWR

VBAT for VPA

K1

BATON

I

Battery thermal detection input

K2

GND_VREF

GND

GND for reference

K3

USB_DLN

I

USB download key

K5

32K_IN

I

RTC 32K input used for fuel gauge operation

K6

GND_LDO

GND

GND for LDO

K7

GND_SPK2

GND

GND for speaker channel 2

K8

GND_LDO

GND

GND for LDO

K9

BST_GDRV

O

Boost controller gate drvie output

K10

GND_ISINK

GND

GND for ISINK

K12

GND_VPA

GND

GND for VPA

K13

VPA

O

VPA switching output

K14

VBAT_VPA

PWR

VBAT for VPA

L1

VDRV

O

Charger current drive output

L2

RESETB

O

Reset output

L3

USB_DLP

I

USB download key

L12

GND_DRV

GND

GND for flashligh and keypad LDO drivers

L13

FLASH

O

Flashlight open drain output

L14

KPLED

O

Keypad LED open drain output

M2

PCH_DET

O

Charging indicator current sink output

M3

PWRBB

I

Power on RTC domain latch signal

M4

PMU_TESTMODE

I

Test mode input (normal function should tie to

GND)

M5

BYPASS

O

SPK common mode voltage bypass

M6

GND_LDO

GND

GND for LDO

M7

GND_SPK2

GND

GND for speaker channel 2

M8

GND_SPK1

GND

GND for speaker channel 1

M9

GND_SPK1

GND

GND for speaker channel 1

M10

ISINK4

O

Current sink channel 4 output

M11

GND_ISINK

GND

GND for ISINK

M12

GND_DRV

GND

GND for flashligh and keypad LDO drivers

M13

ISINK0

O

Current sink channel 0 output

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 12 of 97

Ball

Symbol

I/O

Description

N1

VCDT

I

Ratioed charger input voltage

N2

PWRKEY

I

Power key

N3

AUD1_P

I

Audio channel 1 differential input (positive)

N4

AUD1_N

I

Audio channel 1 differential input (negative)

N5

VBI_N

I

Voice differential input (negative)

N6

ASW_OUT

O

Analog switch output

N7

ASW_IN1

I

Analog switch input 1

N8

ASW_IN2

I

Analog switch input 2

N9

VBAT_MISC

PWR

VBAT for buck, driver and speaker controller

N11

ISINK5

O

Current sink channel 5 output

N12

ISINK3

O

Current sink channel 4 output

N13

ISINK2

O

Current sink channel 3 output

N14

ISINK1

O

Current sink channel 1 output

P1

BGA_NC-P1

I/O

NC

P2

AUD2_P

I

Audio channel 2 differential input (positive)

P3

AUD2_N

I

Audio channel 2 differential input (negative)

P5

VBI_P

I

Voice differential input (positive)

P7

VBAT_SPK2

PWR

VBAT for speaker channel 2

P8

VBAT_SPK1

PWR

VBAT for speaker channel 1

P10

SPK2_P

O

Speaker channel 2 differential output (positive)

P11

SPK2_N

O

Speaker channel 2 differential output (negative)

P12

SPK1_N

O

Speaker channel 1 differential output (negative)

P13

SPK1_P

O

Speaker channel 1 differential output (positive)

P14

BGA_NC-P14

I/O

NC

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

FOR zlixin@ waterworld.com.cn USE ONLY

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 13 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

Free-air temperature range

-40 85

°C

Storage temperature range

-65 150

°C

Battery input voltage range

4.3

V

ESD robustness

HBM

2,000

V

Charger input withstand

10

V

Parameter

Conditions

Min.

Typical

Max.

Unit

Thermal resistance from

junction to ambient

In free air

39.8[1]

°C/W

Parameter

Conditions

Min.

Typical

Max.

Unit

Operating temperature range

-25 85

°C

Free Datasheet http://www.datasheet4u.com/

2 Electrical Characteristics

2.1 Absolute Maximum Ratings over Operating Free-Air Temperature Range

Stresses beyond those listed under Table 3 may cause permanent damage to the device. These

numbers are stress ratings only, and functional operation of the device at these or any other

conditions beyond those indicated in the operational sections of specifications is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect the device reliability.

Table 3: Absolute maximum ratings

2.2 Thermal Characteristic

Note: The device is mounted on a 4-metal-layer PCB and modeled per JEDEC51-9 condition.

2.3 Pin Voltage Rating (TBD)

2.4 Recommended Operating Range

MEDIATEK CONFIDENTIAL

Table 4: Operation condition

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 14 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

Switch-off mode: supply current

VBAT < 2.4 V

RTC LDO OFF

85 μA

2.4 V < VBAT < 3.2 V

35 μA

3.2 V < VBAT

60 μA

Operation ground current

Standby

Low-power mode

300 μA

Under voltage (UV)

Under voltage falling threshold 1

UV_SEL[1:0] = 00

2.8

2.9

3.0

V

Under voltage falling threshold 2

UV_SEL[1:0] = 01

2.75 V

Under voltage falling threshold 3

UV_SEL[1:0] = 10

2.6 V

Under voltage falling threshold 4

UV_SEL[1:0] = 11

2.5 V

Under voltage rising threshold

UV_SEL[1:0] = xx

3.1

3.2

3.3

V

Reset generator

Output high

VIO-0.4

V

Output low

0.2

V

Output current (Ioh)

Vo > VIO-0.4V

1

mA

Delay Time from switched-on to

RESETB release

100

200

400

ms

Interrupt

Output high

VIO-0.4

V

Output low

0.2

V

Power key input

High voltage

0.7*VBAT

V

Low voltage

0.3*VBAT

V

De-bounce time

25

50

200

Control input voltage

PWRBB input high

2.1

V

PWRBB input low

0.54

V

Other control input high

(SRCLKEN, PA_SEL)

2.0

V

Other control input low

(SRCLKEN, PA_SEL)

0.5

V

Thermal shut-down

PMIC shut-down threshold

150

degree

SW high power latch threshold

125

degree

Interrupt threshold

110

degree

Free Datasheet http://www.datasheet4u.com/

2.5 Electrical Characteristics

VBAT = 3.4 ~ 4.2V, minimum loads applied on all outputs, unless otherwise noted.

Typical values are at TA = 25°C.

Table 5: General electrical specifications

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 15 of 97

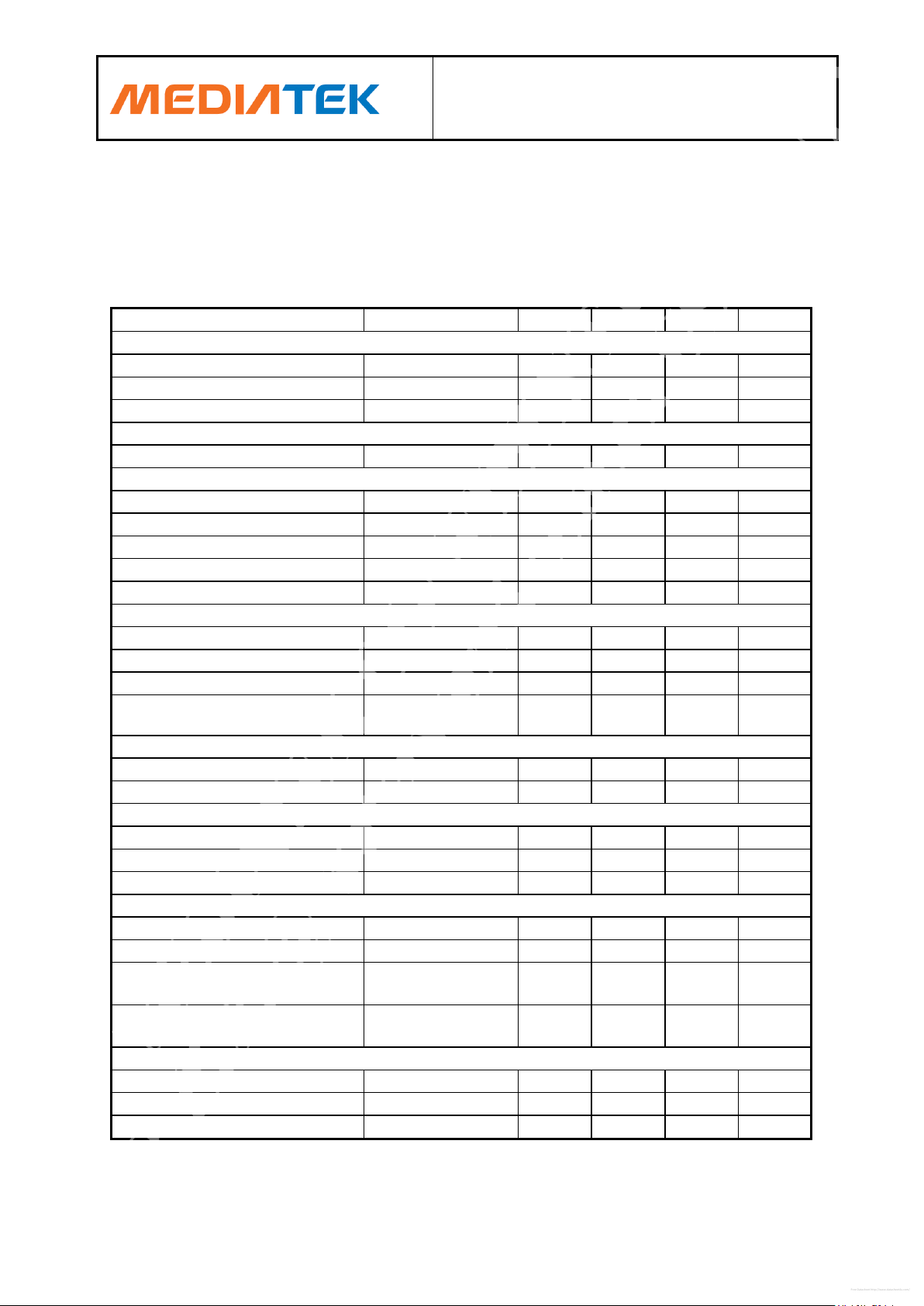

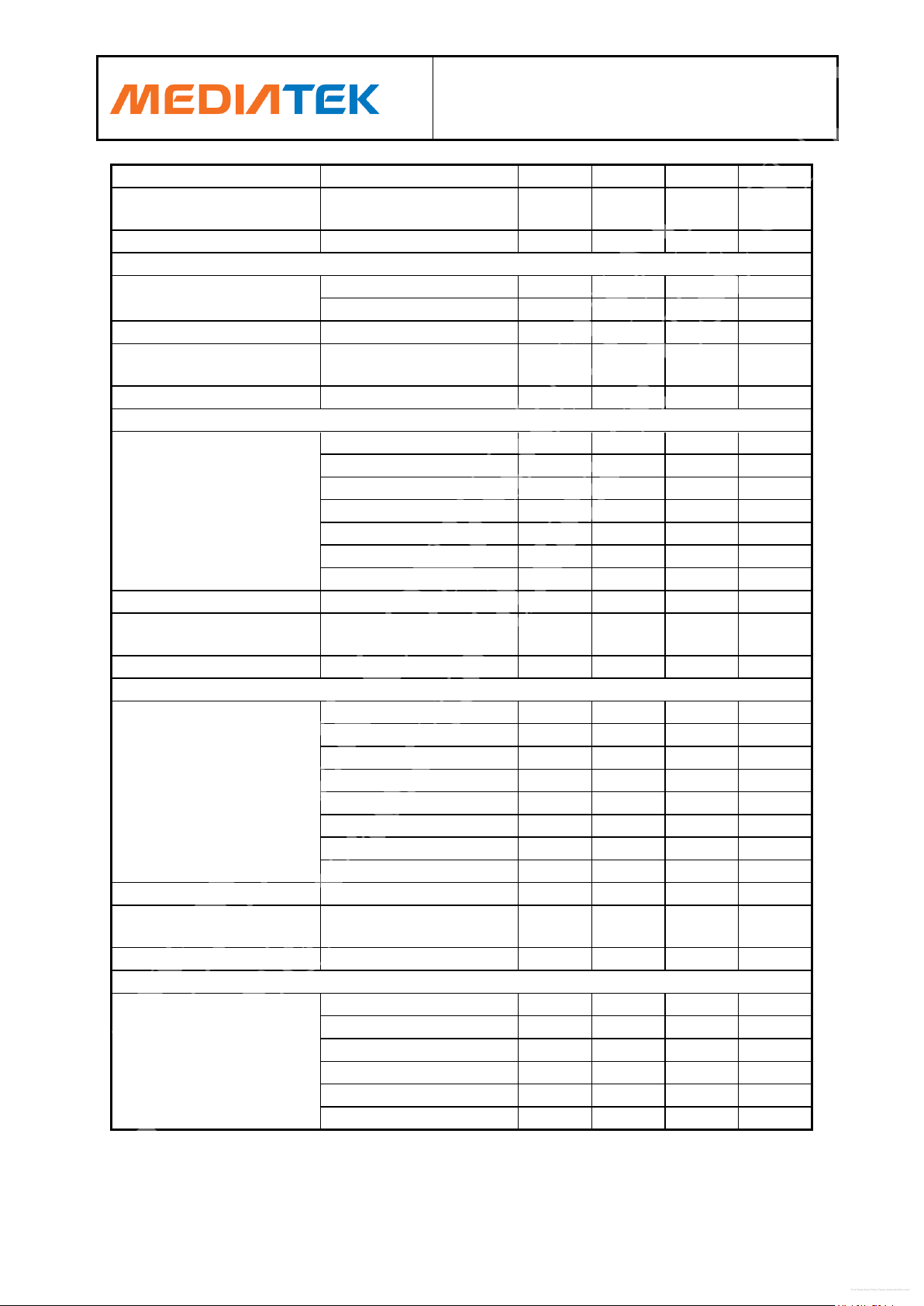

Parameter

Conditions

Min.

Typical

Max.

Unit

LDO enable response time

250 μs

Parameter

Conditions

Min.

Typical

Max.

Unit

Boost controller

Efficiency

Vin = 3.8V, 20mA, Vout =

35V

80 %

Switch on max. duty cycle

93 %

Regulated feedback voltage

(int.)

0.28

0.3

0.32

V

Turn-on rise time

1 ms

OVP on threshold

1.1

1.2

1.3

V

OVP off threshold

1 V

Buck - VCORE

Output voltage

1.1 V

Output current

1,000

mA

Turn-on overshoot

10

%

Load regulation

-10 10

%

Buck - VPROC

Output voltage

1.25 V

Output current

1,500

mA

Turn-on overshoot

10

%

Load regulation

-6 6

%

Buck - VIO18

Output voltage

1.8 V

Output current

1,000

mA

Turn-on overshoot

10

%

Buck - VRF18

Output voltage

1.825 V

Output current

250 mA

Turn-on overshoot

10

%

Free Datasheet http://www.datasheet4u.com/

2.6 Regulator Output

Table 6: Regulator specifications

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 16 of 97

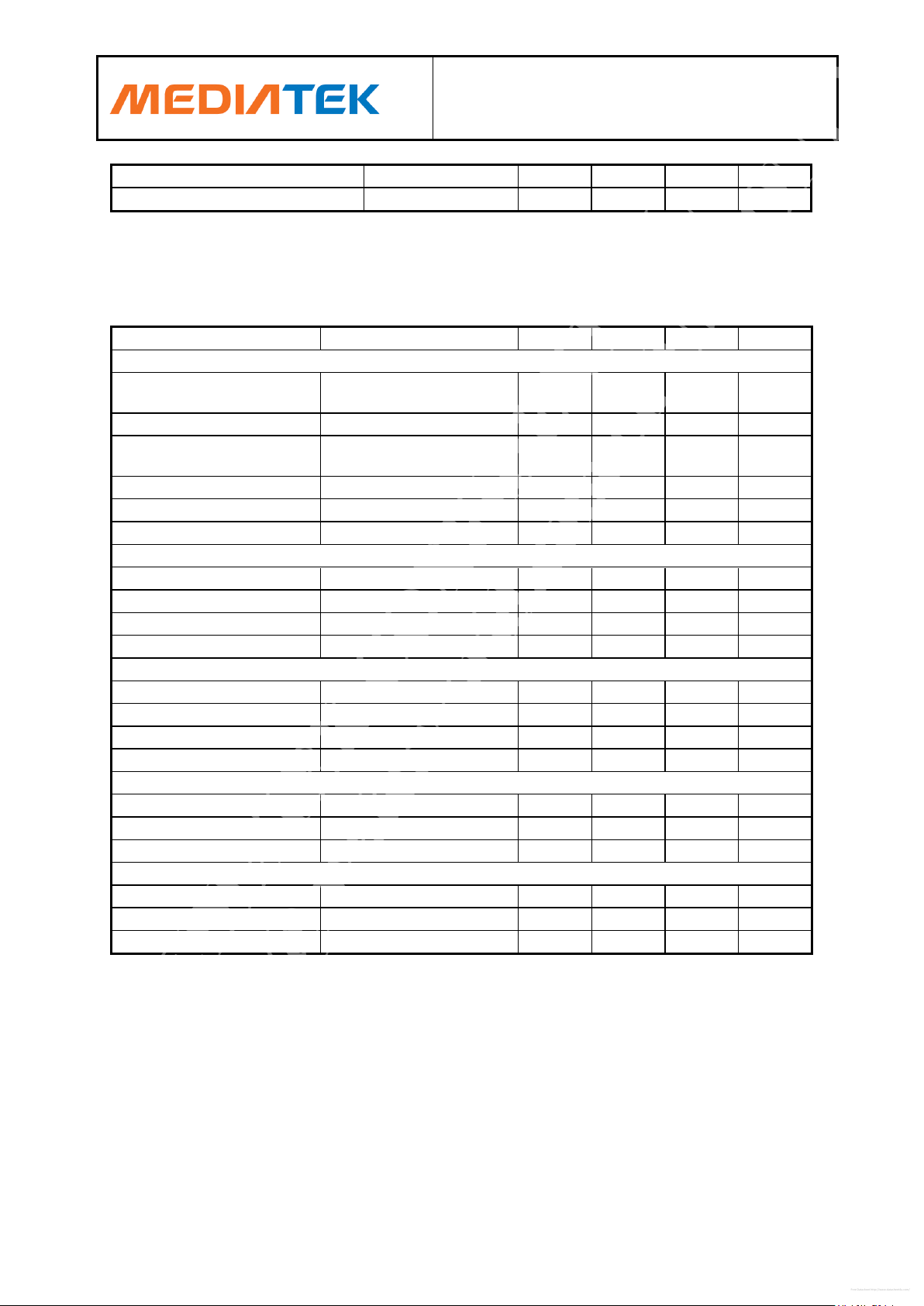

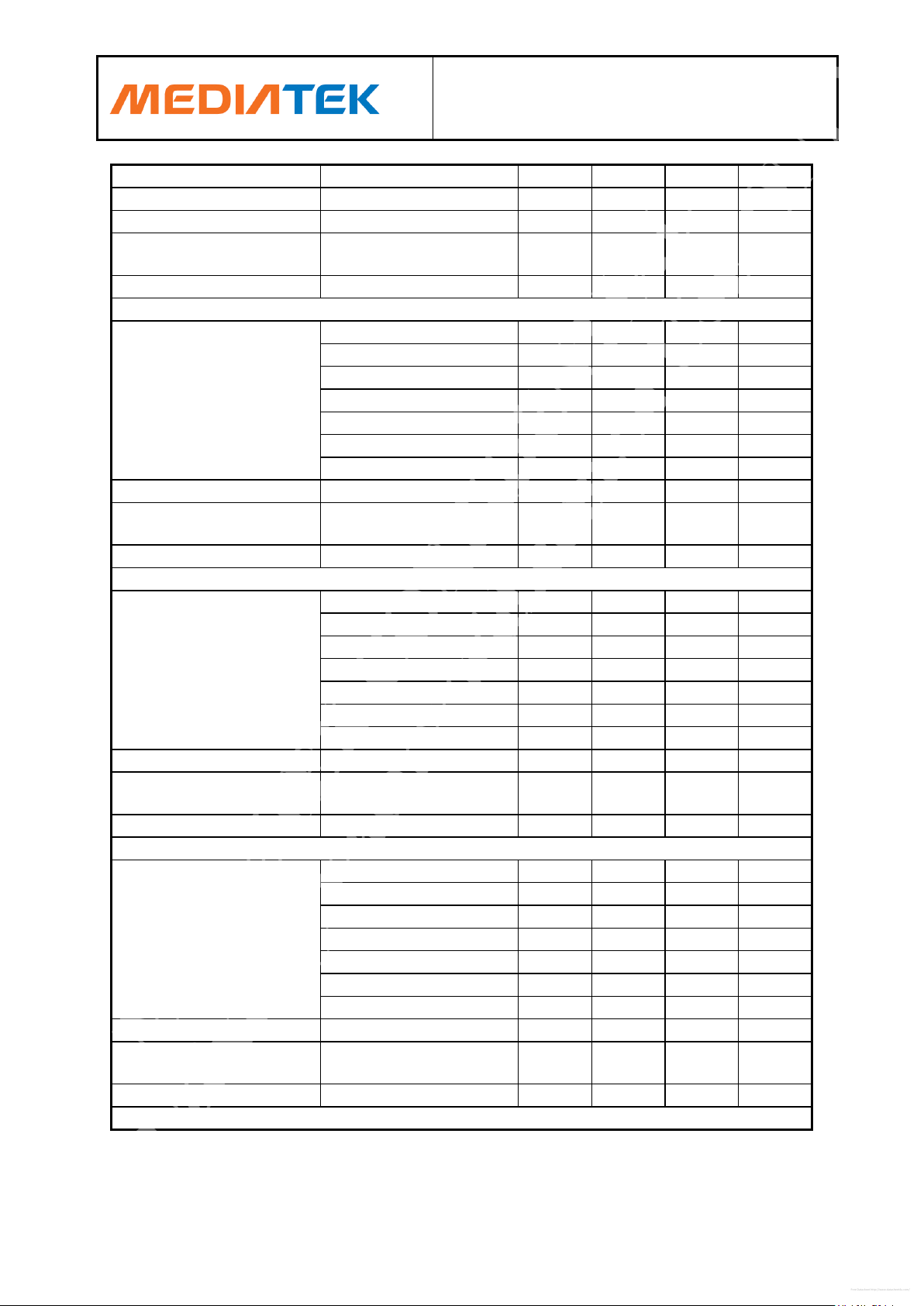

Parameter

Conditions

Min.

Typical

Max.

Unit

Buck - VPA

Output voltage

0.9 3.4

V

Output current

VOUT=3.4V

800 mA

Turn-on overshoot

10

%

ALDO - VRF28

Output voltage

2.7

2.85 3 V

Output current

200 mA

Output noise

Freq = 10 Hz to 80 kHz

Iout = 0.01Imax ~ full load

90

uVrms

PSRR

100 Hz < freq < 3 kHz

Iout = 0.01Imax/0.5Imax

65 dB

3 kHz < freq < 30 kHz

Iout = 0.01Imax/0.5Imax

45

Turn-on rise time

No load

240

us

ALDO - VTCXO

Output voltage

2.7

2.8

2.9

V

Output current

40 mA

Output noise

Freq = 10 Hz to 80 kHz

Iout = 0.01Imax ~ full load

90

uVrms

PSRR

100 Hz < freq < 3 kHz

Iout = 0.01Imax/0.5Imax

65 dB

3 kHz < freq < 30 kHz

Iout = 0.01Imax/0.5Imax

45

Turn-on rise time

No load

240

us

ALDO - VA1

Output voltage

2.35

2.5

2.65

V

Output current

100 mA

Output noise

Freq = 10 Hz to 80 kHz

Iout = 0.01Imax ~ full load

90

uVrms

PSRR

100 Hz < freq < 3 kHz

Iout = 0.01Imax/0.5Imax

65 dB

3 kHz < freq < 30 kHz

Iout = 0.01Imax/0.5Imax

45

Turn-on rise time

No load

360

us

ALDO - VA2

Output voltage

2.35

2.5

2.65

V

Output current

100 mA

Output Noise

Freq = 10 Hz to 80 kHz

Iout = 0.01Imax ~ full load

90

uVrms

PSRR

100 Hz < freq < 3 kHz

Iout = 0.01Imax/0.5Imax

65 dB

3 kHz < freq < 30 kHz

Iout = 0.01Imax/0.5Imax

45

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 17 of 97

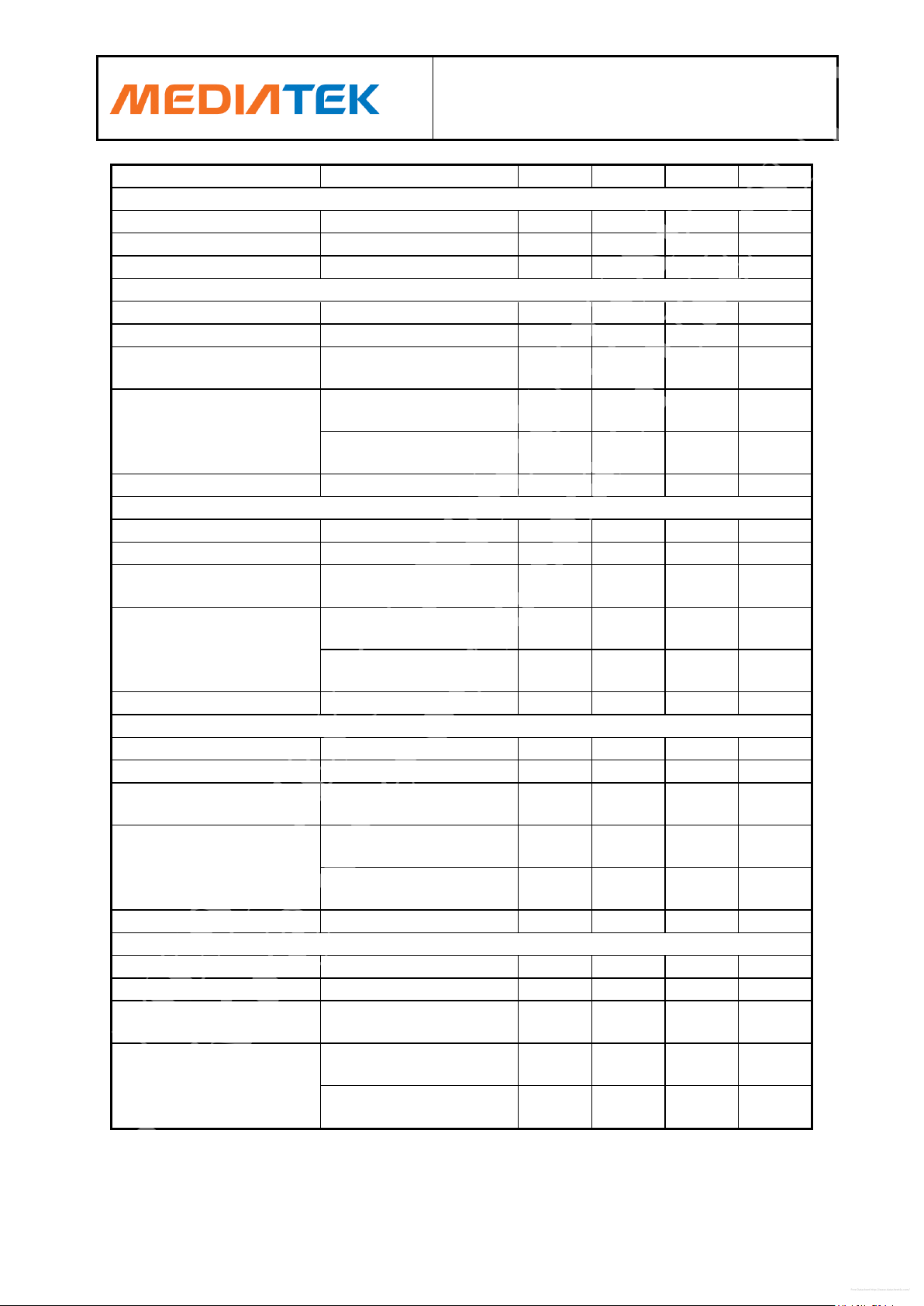

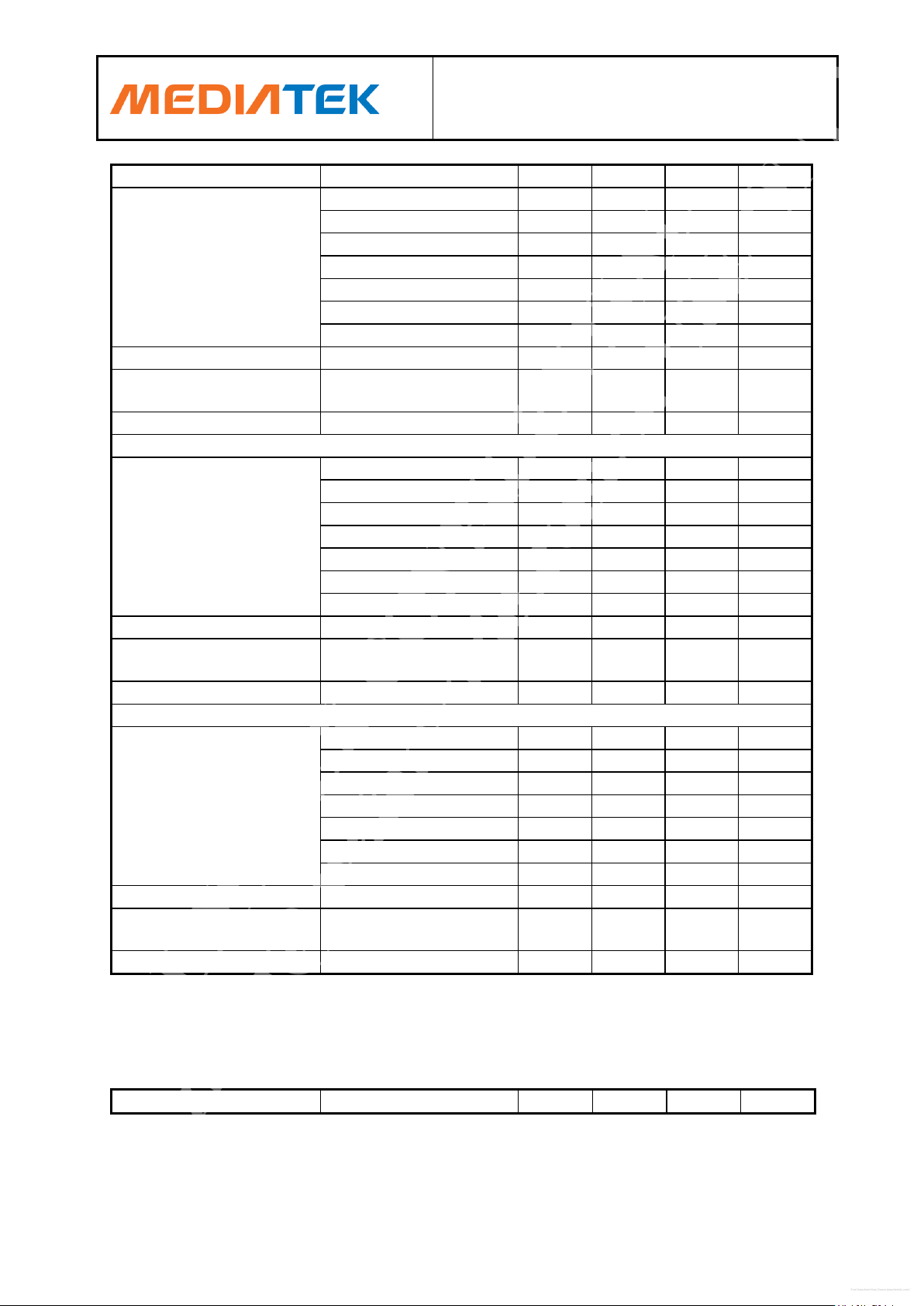

Parameter

Conditions

Min.

Typical

Max.

Unit

Turn-on rise time

No load

360

us

ALDO - VCAMA

Output voltage

VCAMA_SEL = 00

1.4

1.5

1.6

V

VCAMA _SEL = 01

1.7

1.8

1.9

V

VCAMA _SEL = 10

2.35

2.5

2.65

V

VCAMA _SEL = 11

2.65

2.8

2.95

V

Output current

200 mA

Output noise

Freq = 10 Hz to 80 kHz

Iout = 0.01Imax ~ full load

40

uVrms

PSRR

100 Hz < freq < 3 kHz

Iout = 0.01Imax/0.5Imax

65 dB

3 kHz < freq < 30 kHz

Iout = 0.01Imax/0.5Imax

45

Turn-on rise time

No load

1,000

us

Load transient response

IOUT = 1mA to full Load

(15mA/usec)

40

mV

DLDO - VM12_1

Output voltage

1.1

1.2

1.3

V

Output current

300 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VM12_2

Output voltage

1.1

1.2

1.3

V

Output current

300 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VM12_INT

Output voltage

1.1

1.2

1.3

V

Output current

360 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise Time

No load

360

us

DLDO - VIO28

Output voltage

2.65

2.8

2.95

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - USB

Output voltage

3.1

3.3

3.5

V

Output current

100 mA

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 18 of 97

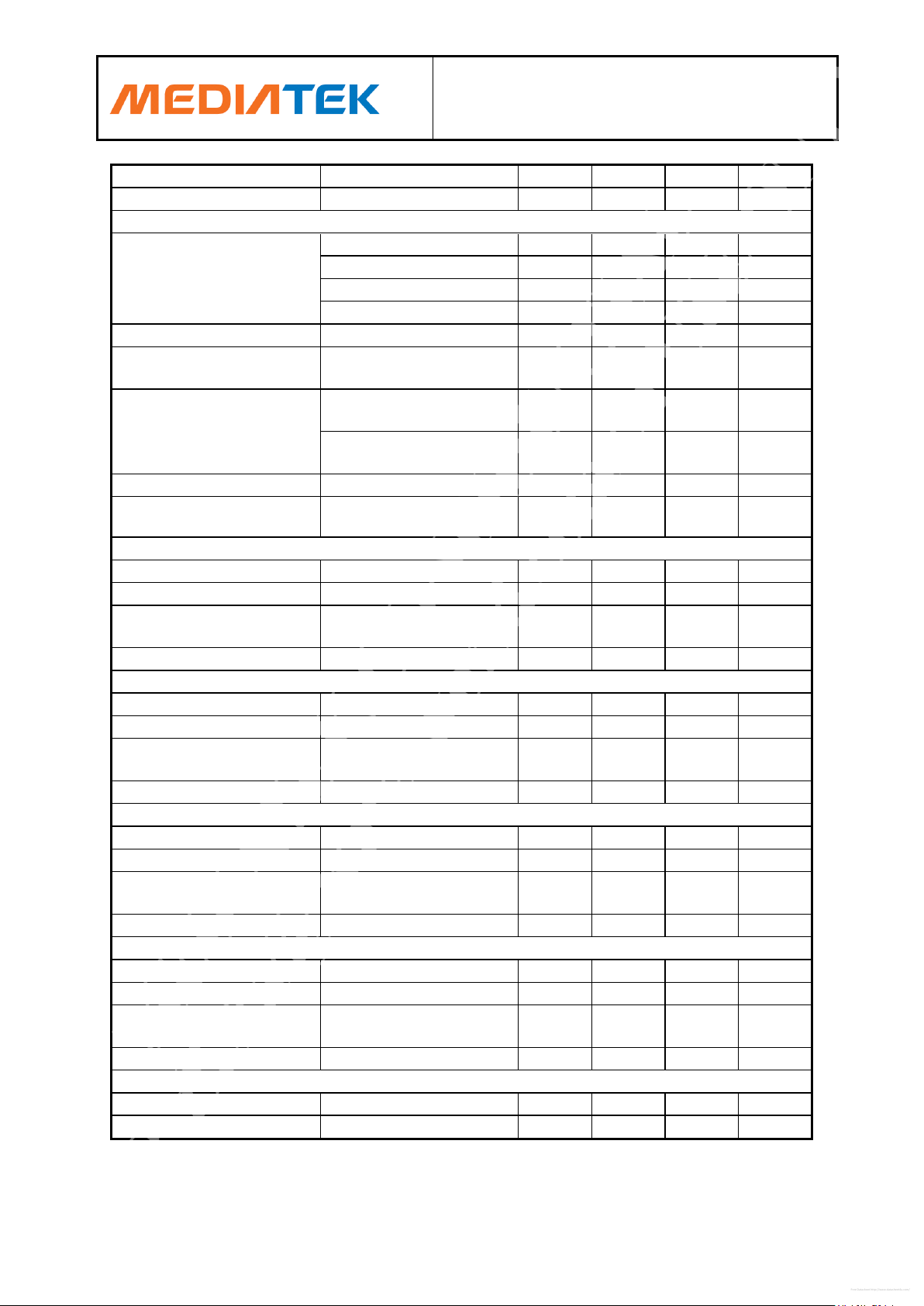

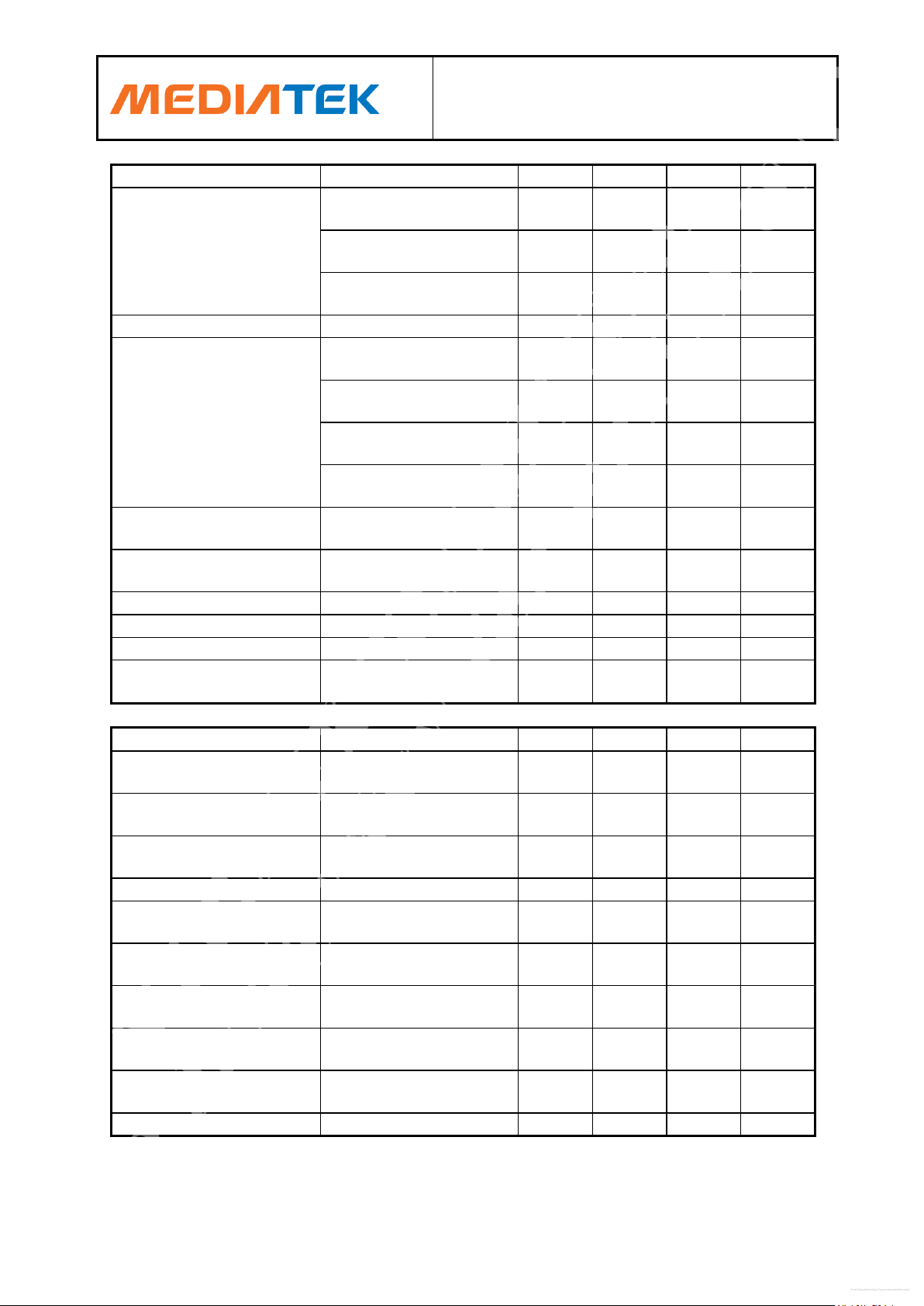

Parameter

Conditions

Min.

Typical

Max.

Unit

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - SIM1

Output voltage

VSIM1_SEL = 0

1.7

1.8

1.9

V

VSIM1_SEL = 1

2.85

3.0

3.15

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - SIM2

Output voltage

VSIM2_SEL = 000

1.2

1.3

1.4

V

VSIM2_SEL = 001

1.4

1.5

1.6

V

VSIM2_SEL = 010

1.7

1.8

1.9

V

VSIM2_SEL = 011

2.35

2.5

2.65

V

VSIM2_SEL = 100

2.65

2.8

2.95

V

VSIM2_SEL = 101

2.85

3.0

3.15

V

VSIM2_SEL = 110

3.1

3.3

3.5

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VCAMD

Output voltage

VCAMD_SEL = 000

1.2

1.3

1.4

V

VCAMD_SEL = 001

1.4

1.5

1.6

V

VCAMD_SEL = 010

1.7

1.8

1.9

V

VCAMD_SEL = 011

2.35

2.5

2.65

V

VCAMD_SEL = 100

2.65

2.8

2.95

V

VCAMD_SEL = 101

2.85

3.0

3.15

V

VCAMD_SEL = 110

3.1

3.3

3.5

V

VCAMD_SEL = 1111

1.1

1.2

1.3

Output current

300 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VCAM_IO

Output voltage

VCAM_IO_SEL = 000

1.2

1.3

1.4

V

VCAM_IO_SEL = 001

1.4

1.5

1.6

V

VCAM_IO_SEL = 010

1.7

1.8

1.9

V

VCAM_IO_SEL = 011

2.35

2.5

2.65

V

VCAM_IO_SEL = 100

2.65

2.8

2.95

V

VCAM_IO_SEL = 101

2.85

3.0

3.15

V

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 19 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

VCAM_IO_SEL = 110

3.1

3.3

3.5

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VCAM_AF

Output voltage

VCAM_AF_SEL = 000

1.2

1.3

1.4

V

VCAM_AF_SEL = 001

1.4

1.5

1.6

V

VCAM_AF_SEL = 010

1.7

1.8

1.9

V

VCAM_AF_SEL = 011

2.35

2.5

2.65

V

VCAM_AF_SEL = 100

2.65

2.8

2.95

V

VCAM_AF_SEL = 101

2.85

3.0

3.15

V

VCAM_AF_SEL = 110

3.1

3.3

3.5

V

Output current

200 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VMC

Output voltage

VMC_SEL = 000

1.2

1.3

1.4

V

VMC_SEL = 001

1.4

1.5

1.6

V

VMC_SEL = 010

1.7

1.8

1.9

V

VMC_SEL = 011

2.35

2.5

2.65

V

VMC_SEL = 100

2.65

2.8

2.95

V

VMC_SEL = 101

2.85

3.0

3.15

V

VMC_SEL = 110

3.1

3.3

3.5

V

Output current

200 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

40

us

DLDO - VMCH

Output voltage

VMCH_SEL = 000

1.2

1.3

1.4

V

VMCH_SEL = 001

1.4

1.5

1.6

V

VMCH_SEL = 010

1.7

1.8

1.9

V

VMCH_SEL = 011

2.35

2.5

2.65

V

VMCH_SEL = 100

2.65

2.8

2.95

V

VMCH_SEL = 101

2.85

3.0

3.15

V

VMCH_SEL = 110

3.1

3.3

3.5

V

Output current

400 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

40

us

DLDO - VGP1

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 20 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

Output voltage

VGP1_SEL = 000

1.2

1.3

1.4

V

VGP1_SEL = 001

1.4

1.5

1.6

V

VGP1_SEL = 010

1.7

1.8

1.9

V

VGP1_SEL = 011

2.35

2.5

2.65

V

VGP1_SEL = 100

2.65

2.8

2.95

V

VGP1_SEL = 101

2.85

3.0

3.15

V

VGP1_SEL = 110

3.1

3.3

3.5

V

Output current

200 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VGP2

Output voltage

VGP2_SEL = 000

1.2

1.3

1.4

V

VGP2_SEL = 001

1.4

1.5

1.6

V

VGP2_SEL = 010

1.7

1.8

1.9

V

VGP2_SEL = 011

2.35

2.5

2.65

V

VGP2_SEL = 100

2.65

2.8

2.95

V

VGP2_SEL = 101

2.85

3.0

3.15

V

VGP2_SEL = 110

3.1

3.3

3.5

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

DLDO - VIBR

Output voltage

VIBR_SEL = 000

1.2

1.3

1.4

V

VIBR_SEL = 001

1.4

1.5

1.6

V

VIBR_SEL = 010

1.7

1.8

1.9

V

VIBR_SEL = 011

2.35

2.5

2.65

V

VIBR_SEL = 100

2.65

2.8

2.95

V

VIBR_SEL = 101

2.85

3.0

3.15

V

VIBR_SEL = 110

3.1

3.3

3.5

V

Output current

100 mA

PSRR

Freq = 217 Hz

Iout = 0.01Imax/0.5Imax

40 dB

Turn-on rise time

No load

360

us

Class AB parameter

Conditions

Min.

Typical

Max.

Unit

Free Datasheet http://www.datasheet4u.com/

2.7 Class AB/D Audio Amplifier

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

Table 7: Class AB/D audio amplifier specifications

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 21 of 97

Class AB parameter

Conditions

Min.

Typical

Max.

Unit

RMS power

8Ω load, VBAT = 4.2 V

THD + N = 1%

850

mW

8Ω load, VBAT = 3.7 V

THD + N = 1%

700

mW

8Ω load, VBAT = 3.4 V

THD + N = 1%

600

mW

THD+N

1 kHz, Po = 0.5Wrms, 4.2V

0.05

0.2

%

PSRR

217 Hz, Vin = 200mVpk-pk

Input AC to ground

75

85 dB

1 kHz, Vin = 200mVpk-pk

Input AC to ground

75

85 dB

4 kHz, Vin = 200mVpk-pk

Input AC to ground

75

85 dB

20 kHz, Vin = 200mVpk-pk

Input AC to ground

50 dB

Noise level

VBAT = 3.3V 0dB gain

8Ω, A-weighted

25

70

μV

VBAT = 4.2V 0dB Gain

8Ω, A-weighted

25

70

uV

Gain adjustment

3

21

dB

Gain adjustment steps

3 dB

Quiescent current

No load 3 6 mA

CMRR

VBAT=3.4/3.8/4.2V

f=1kHz, Vin=200mVpk-pk

49

60 Ω

Class D parameter

Conditions

Min.

Typical

Max.

Unit

RMS power

8Ω load, VBAT = 4.2 V

THD + N = 1%

900

mW

8Ω load, VBAT = 3.7 V

THD + N = 1%

700

mW

8Ω load, VBAT = 3.4V

THD + N = 1%

600

mW

THD+N

1 kHz, Po = 0.5Wrms, 4.2V

0.2

%

PSRR

217 Hz, Vin = 200mVpk-pk

Input AC to ground

65

75 dB

1 kHz, Vin = 200mVpk-pk

Input AC to ground

65

75 dB

4 kHz, Vin = 200mVpk-pk

Input AC to ground

65

75 dB

20 kHz, Vin = 200mVpk-pk

Input AC to ground

50 dB

Noise level

VBAT = 3.3V 0dB gain

8Ω, A-weighted

25

70

μV

VBAT = 4.2V 0dB gain

25

70

uV

Free Datasheet http://www.datasheet4u.com/

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 22 of 97

Class D parameter

Conditions

Min.

Typical

Max.

Unit

8Ω, A-weighted

Efficiency

VBAT = 4.2V

0.8W, 8Ω with 68uH, 1 kHz

80

90 %

Gain adjustment

Mute 21

dB

Gain adjustment steps

3 dB

Quiescent current

No load 4 6 mA

CMRR

VBAT = 3.4/3.8/4.2V

f=1 kHz, Vin = 200mVpk-pk

49

60 Ω

Parameter

Conditions

Min.

Typical

Max.

Unit

CHRIN voltage

4.3 5 7

V

Operation range VCGRIN

3.2 5 8

V

OTG detection

0.8

2.4 4 V

VCDT CHRIN detection

threshold

VCDT_VTHL[3:0] = 0000 ~

1111

4.2

10.5

V

HV adaptive current @

pre_charge

VCDT switch threshold

(200mA => 70mA)

6

V

Pre-charging indicator

Vchg = 3.3/5V

4.5mA VISINK drop

1000

mV

VBAT CC

3.15

3.3

3.45

V

VBAT CV

4.15

4.2

4.25

V

VBAT OV

4.25

4.3

4.35

V

CC mode charging current

CS_VTH = 1111

14/R

sense

mA

CS_VTH = 1110

40/R

sense

mA

CS_VTH = 1101

80/R

sense

mA

CS_VTH = 1100

90/R

sense

mA

CS_VTH = 1011

110/R

sense

mA

CS_VTH = 1010

130/R

sense

mA

CS_VTH = 1001

140/R

sense

mA

CS_VTH = 1000

160/R

sense

mA

CS_VTH = 0111

180/R

sense

mA

CS_VTH = 0110

200/R

sense

mA

CS_VTH = 0101

220/R

sense

mA

CS_VTH = 0100

240/R

sense

mA

CS_VTH = 0011

260/R

sense

mA

CS_VTH = 0010

280/R

sense

mA

CS_VTH = 0001

300/R

sense

mA

Free Datasheet http://www.datasheet4u.com/

2.8 Battery Charger

Table 8: Charger specifications

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 23 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

CS_VTH = 0000

320/R

sense

mA

UVLO

VTHH 3.2 V

VTHL 2.9 V

DDLO

VTHH 2.7 V

VTHL 2.5 V

Parameter

Conditions

Min.

Typical

Max.

Unit

Flash dropout voltage

VFlash @ ISINK = 450mA

0.5

V

Flash soft start time

VFlash @ ISINK = 300mA

1

ms

KPLED dropout voltage

KPLED @ ISINK = 150mA

0.5

V

KPLED soft start time

KPLED @ ISINK = 150mA

1

ms

ISINK current matching

VISINK = 0.3 ~ 2.5V

4/24mA, 5 LEDs

-5 5

%

ISINK LED sink current

ISINK_SEL = 000

4

mA

ISINK_SEL = 001

8

ISINK_SEL = 010

12

ISINK_SEL = 011

16

ISINK_SEL = 100

20

ISINK_SEL = 101

24

ISINK dropout voltage

4 ~ 20mA

VISINK drop

150

250

mV

ISINK rise/fall time

VISINK > 0.3V

3.33

uS

Parameter

Conditions

Min.

Typical

Max.

Unit

Analog switch turn-on

resistance

VBAT = 3.3/4.2V

3

Ω

Analog switch turn-on THD

VBAT = 3.4/4.2V

1k ~ 8 kHz, 200mVpp

10kΩ

70

dB

Parameter

Conditions

Min.

Typical

Max.

Unit

BC11 Charging Port

Standard down-string port

35

70

94

mA

Free Datasheet http://www.datasheet4u.com/

2.9 Driver

Table 9: Driver specifications

2.10 Analog Switch

MEDIATEK CONFIDENTIAL

2.11 BC1.1

FOR zlixin@ waterworld.com.cn USE ONLY

Table 10: Analog switch specifications

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 24 of 97

Parameter

Conditions

Min.

Typical

Max.

Unit

Detection

Standard charging downstring port

35

70

94

mA

DP, DM short

140

200

260

mA

DP, DM floating

140

200

260

mA

BC11 Characteristics

IPU_DP, IPU_DM

9.6 uA

IPD_DP, IPD_DM

96 uA

VSRC on DP, DM

630 mV

Current pulse value under

2.2V

70 mA

Current pulse periode

under 2.2V

550 ms

OSC1M, timer

5

min

RTC, timer

35 min

BC1.1 flow on threshold

2.2 V

Parameter

Conditions

Min.

Typical

Max.

Unit

USBDL

Duration

8.0 s

Current

550 mA

Parameter

Conditions

Min.

Typical

Max.

Unit

FG current characteristics

Output resolution

16 Bit

Conversion time

1/2^15

s

Over-sampling ratio

2^11

2^13

Auto-calibration time

0.25

4.96

s

ADC characteristics

Input voltage range

-50 50

mV

Supply

2.5 V

Current

60 uA

Gain error

-2 2

%

Accuracy

0.03 %

Noise 5 uV

Free Datasheet http://www.datasheet4u.com/

2.12 Down Load Without Battery

2.13 Fuel Gauge

MEDIATEK CONFIDENTIAL

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 25 of 97

Free Datasheet http://www.datasheet4u.com/

3 Functional Descriptions

3.1 General Descriptions

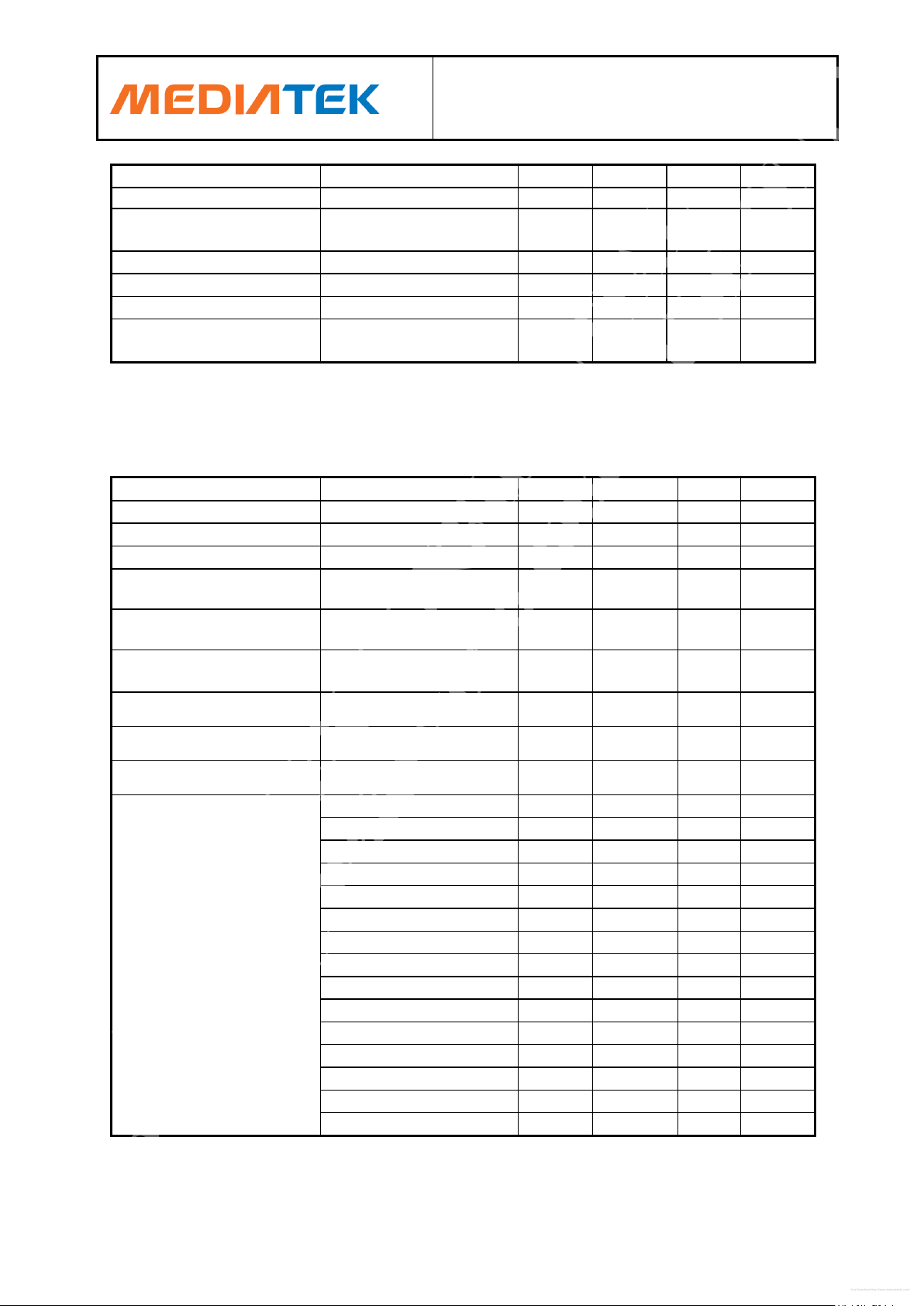

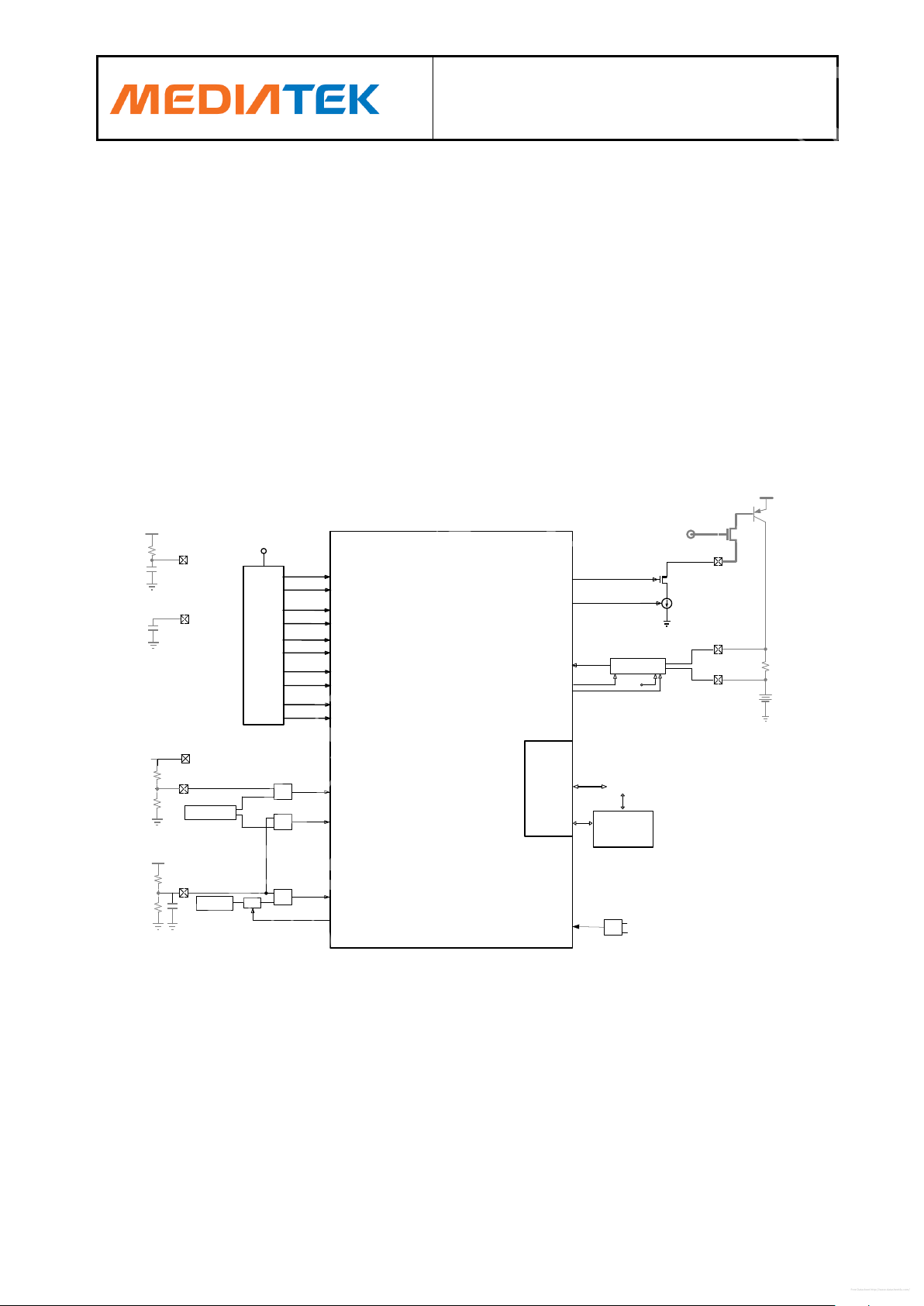

MT6329 is a fully integrated PMIC target for smart phone power provider. See Figure 2 the block

diagram for the whole picture of MT6329 PMIC.

Figure 2: MT6329 block diagram

3.2 PMIC Functional Blocks

MT6329 manages the power supply of the whole chip, such as the baseband, processor, memory,

SIM cards, camera, vibrator, etc. MT6329 includes the following analog functions for the use on smart

phone platforms.

LDO and BUCK: Provide regulated lower output voltage level from Li-Ion battery

Keypad/Flash LED driver (KPLED/FLASHLED) and current sink (ISINK) driver: Sink current for

keypad LED and LCM module

MEDIATEK CONFIDENTIAL

Controller: Generates power-on/off sequence, system reset and exceptional handling function

Charger controller: Controls/Protects battery charging procedure

Class-AB/D audio amplifier: Supports high-power/quality audio amplifier

Fuel gauge: Supports accurate battery capacity monitor

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 26 of 97

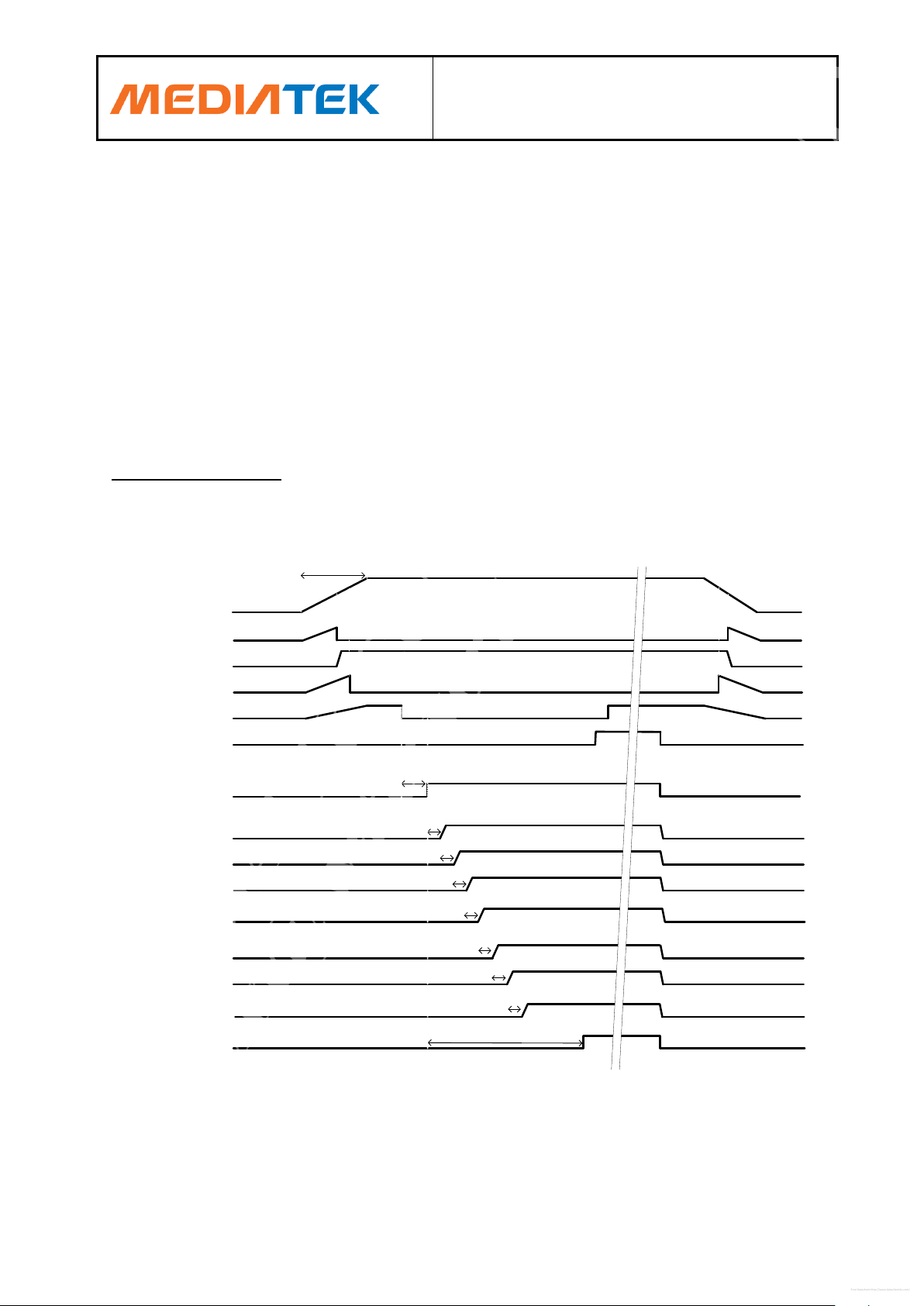

UVLO

DDLO

VM12_1 / VM12_2

RESETB

PWRON

PWRKEY

VCORE

VPROC

VIO18

VIO28 / VM12_INT

VA1 / VA2

2ms

2ms

2ms

2ms

2ms

150ms

de-bounce

50ms

VRTC

PWRBB

VBAT

2ms

VMC / VMCH

2ms

VUSB / VTCXO

< 100ms

Free Datasheet http://www.datasheet4u.com/

More detailed descriptions of each sub-block are explained in the following sections.

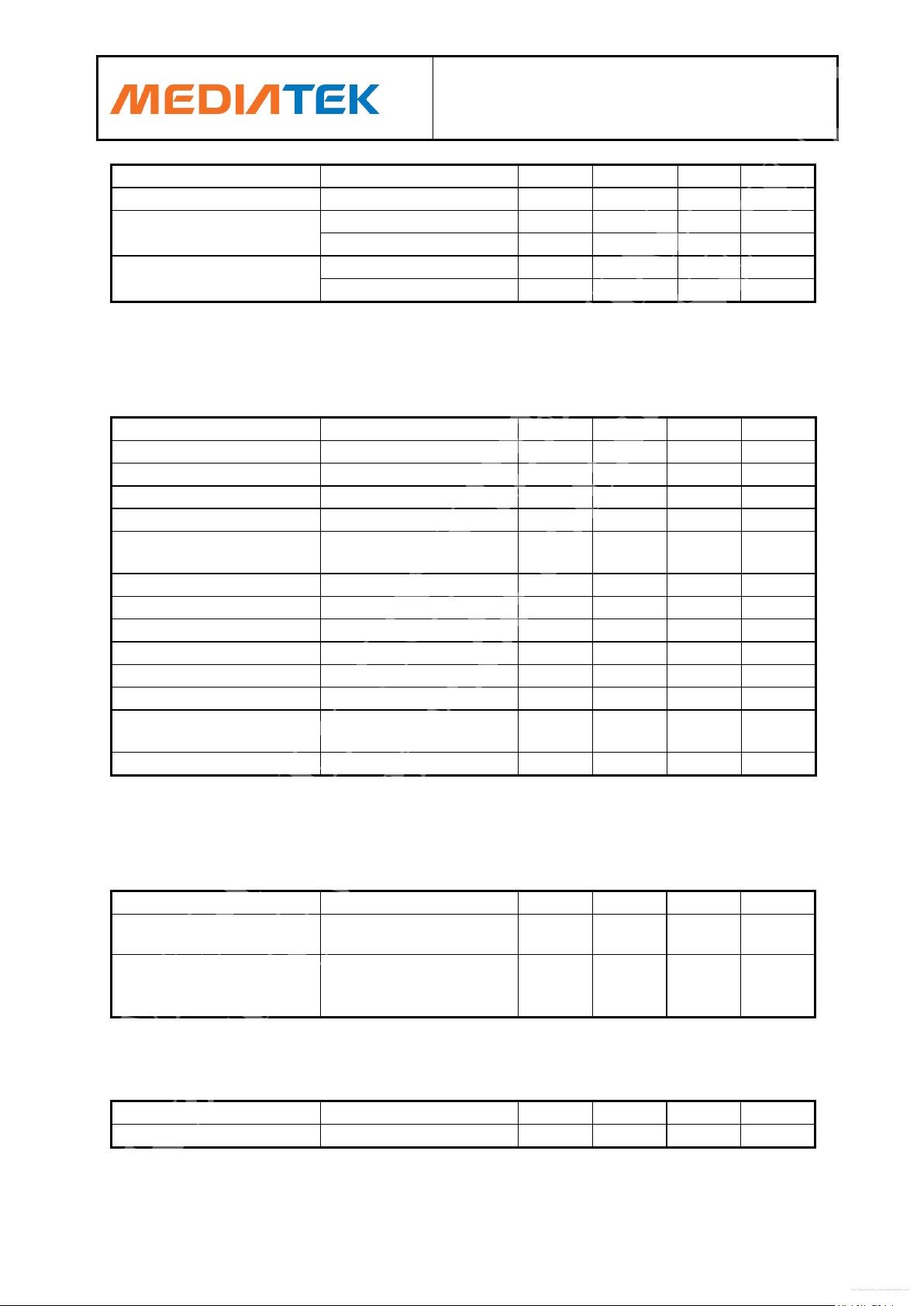

3.2.1 Power-On/Off Sequence

PMIC handles the powe-on and -off of the handset. If the battery voltage is neither in the UVLO state

(VBAT ≥ 3.4V) nor in the thermal condition, there are three methods to power on the handset system:

1) Pulling PWRKEY low (the user pushes PWRKEY), 2) Pulling PWRBB high (baseband BB_WakeUp)

and 3) Valid charger plug-in.

According to different battery voltage (VBAT) and phone state, control signals and regulators will have

different responses.

Power on/off sequence

The power-on/off sequence controlled by the “control” and “reset generator” is shown in the figure

below.

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

Figure 3: Power-on/off control sequence by pressing PWRKEY

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

This document contains information that is proprietary to MediaTek Inc.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 27 of 97

Free Datasheet http://www.datasheet4u.com/

Note that the figure above only shows one power-on/off. MT6329 handles the powe-on and -off of the

handset. The following three different ways methods switch on the handset (when VBAT ≥ 3.4V):

1. Pushing PWRKEY (pulling the PWRKEY pin to low level)

Pulling PWRKEY low is typical method to turn on the handset. The VCORE and VPROC buck

converters will be turned on first then VIO18 and VIO28 LDOs are turned on sequentially. The

supplies for the baseband are ready, and the system reset ends at the moment when all the

default-on regulators are fully turned on to ensure correct timing and function. After that, the

baseband sends the PWRBB signal back to PMIC for acknowledgement. To successfully power

on the handset, PWRKEY should be kept low until PMIC receives PWRBB from the baseband.

2. RTC module generates PWRBB to wake up the system

If the RTC module is scheduled to wake up the handset at some time, the PWRBB signal will be

directly sent to PMIC. In this case, PWRBB becomes high at specific moment and allows PMIC

power-on as the sequence described above. This is called the RTC alarm.

3. Valid charger plug-in (CHRIN voltage within valid range)

The charger plug-in will also turn on the handset if the charger is valid (no OVP takes place).

However, if the battery voltage is too low to power on the handset (UVLO state), the system will

not be turned on by any of the three methods. In this case, the charger will charge the battery first,

and the handset will be powered on automatically as long as the battery voltage is high enough.

Under-voltage lockout (UVLO)

The UVLO state in PMIC prevents start-up if the initial voltage of the main battery is below the 3.2V

threshold. It ensures that the handset is powered on with the battery in good condition. The UVLO

function is performed by a hysteretic comparator which ensures smooth power-on sequence. In

addition, when the battery voltage is getting lower, it will enter the UVLO stat,e and PMIC will be

turned off by itself, except for VRTC LDO, to prevent further discharging. Once PMIC enters the

UVLO state, it will draw low quiescent current. RTC LDO will still be working until DDLO disables it.

Deep discharge lockout (DDLO)

PMIC will enter the deep discharge lockout (DDLO) state when the battery voltage drops below 2.5V.

In this state, VRTC LDO will be shut down. Otherwise, it will draw very low quiescent current to

prevent further discharging or even damage to the cells.

Reset

PMIC contains a reset control circuit which takes effect at both power-up and power-down. The

RESETB pin is held low in the beginning of power-up and returns to high after the pre-determined

MEDIATEK CONFIDENTIAL

delay time. The delay time is controlled by a large counter, which uses the clock from the internal ringoscillator. At power-off, the RESETB pin will return to low immediately without any delay.

Over-temperature protection

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 28 of 97

Rsense

VBAT

CHRIN

8V LDMOS

DRV

ISENSE

BATSNS

(VBAT)

gain

CCHRLDO_DET_CMP

VBGR

DXT790AP5

Charger Core

And

Digital Controller

CHRIN

3.3K

1u

1u

CHRLDO28

VREF

CHR_LDO_DET

CHR_LDO_DET

Interface

BC1.1

Controller

To BB

CSDAC_EN

CSDAC_DAT<7:0>

CS_DET

CS_EN

CS_VTH[3:0]

TREF

24k

RNTC

BATON

OTG_BVAILD_EN

CHRIN

VCDT UpTo 10.5V

330k

39k

VCDT

10uF

VBAT_DDLO_DET

VBAT_DDLO_VTH<1:0>

VBAT_UVLO_DET

VBAT_UVLO_VTH<1:0>

VBAT_CC_DET

VBAT_CC_VTH[1:0]

VBAT_CV_DET

VBAT_CV_VTH[1:0]

VBAT_OV_DET

VBAT_OV_VTH[1:0]

BATON_UNDET

OTG_BVALID_DET

VCDT_DET

VCDT_VTH[3:0]

NTR4503N

CHRLDO 2.8V

MUX

VTH CGRLDOGOOD

VBAT

Voltage

divider

VBAT

VCDT VREF GEN

OTG/BATON VREF GEN

COMP

COMP

COMP

Current

Sensing

EN vr

set

in1

in2

VREF

COMP

ON Chip

Off Chip

Charger block diagram

Free Datasheet http://www.datasheet4u.com/

If the die temperature of PMIC exceeds 150°C, PMIC will automatically disable all LDOs except for

VRTC. Once the over-temperature state is resolved, a new power-on sequence will be required to

enable the LDOs.

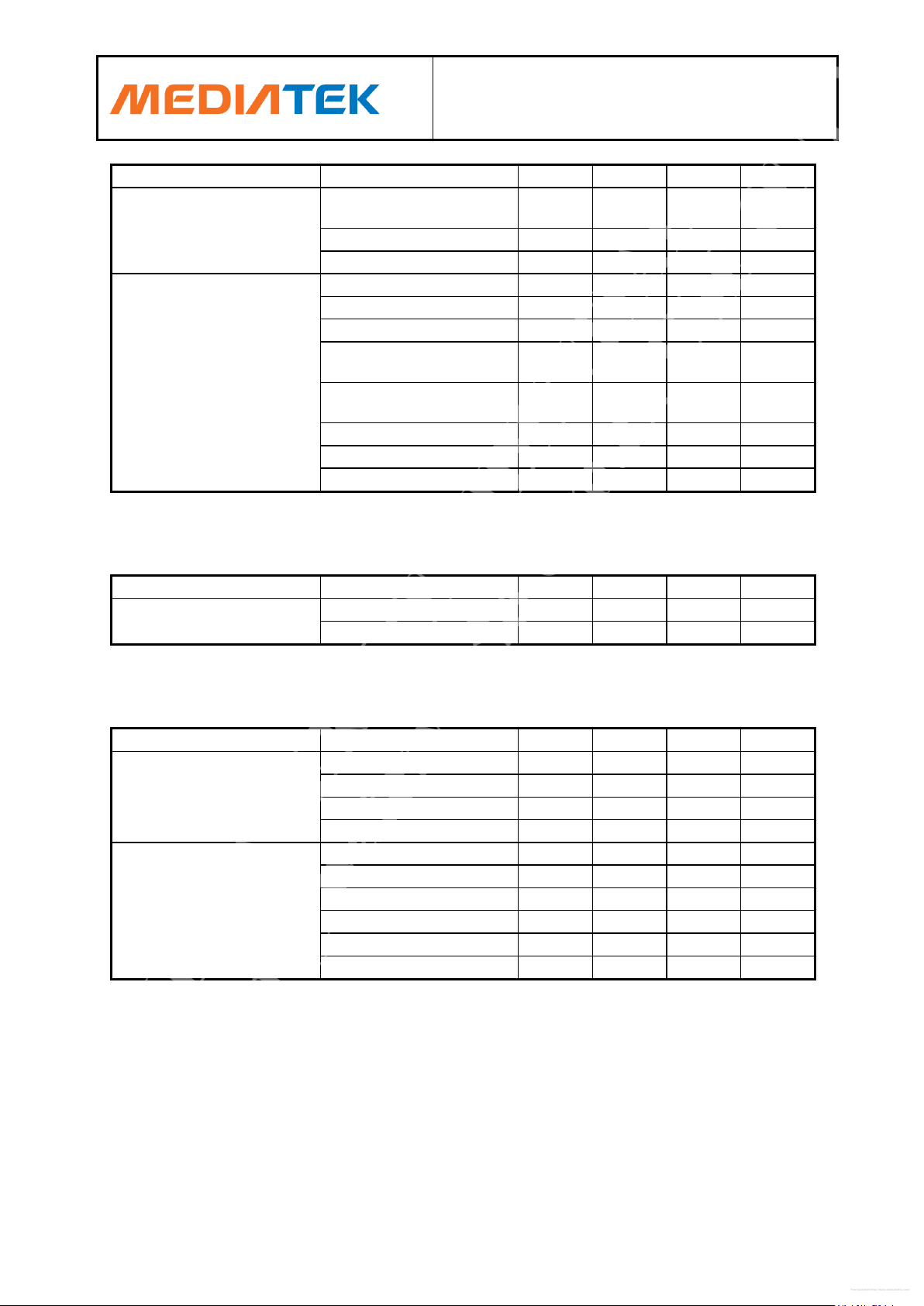

3.2.2 The Battery Charger (Charger Controller)

The charger controller senses the charger input voltage from either a standard AC-DC adaptor or an

USB charger. When the charger input voltage is within a pre-determined range, the charging process

will be activated. This detector resists higher input voltages than other parts of PMIC.

3.2.2.1 Block Descriptions

3.2.2.1.1 Charger Detection

Whenever an invalid charging source is detected (> 7.0V), the charger detector will stop the charging

process immediately to avoid burning out the chip or even the phone. Furthermore, if the charger-in

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Figure 4: PCHR block diagram

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 29 of 97

Free Datasheet http://www.datasheet4u.com/

level is not high enough (< 4.3V), the charger will also be disabled to avoid improper charging

behavior.

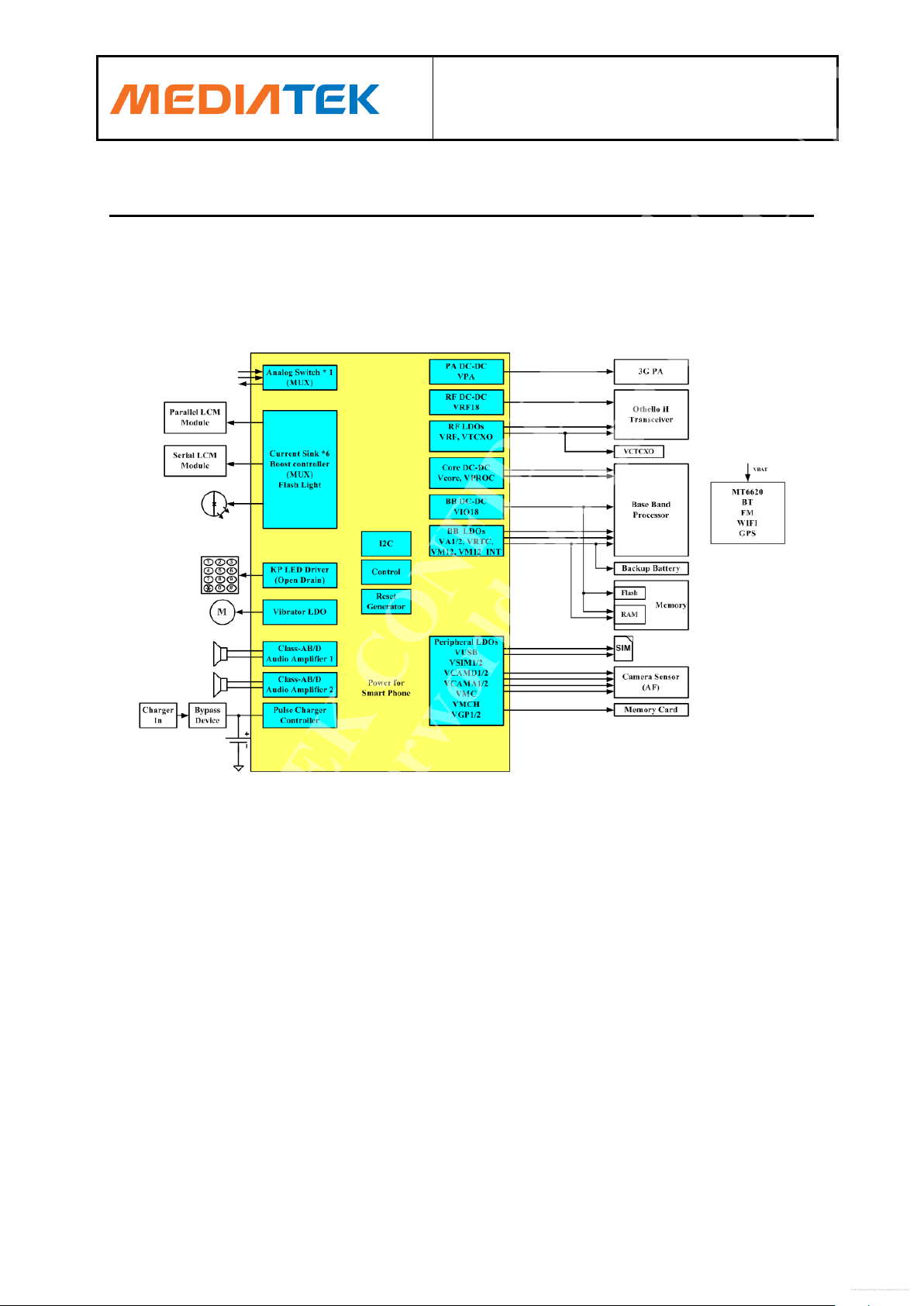

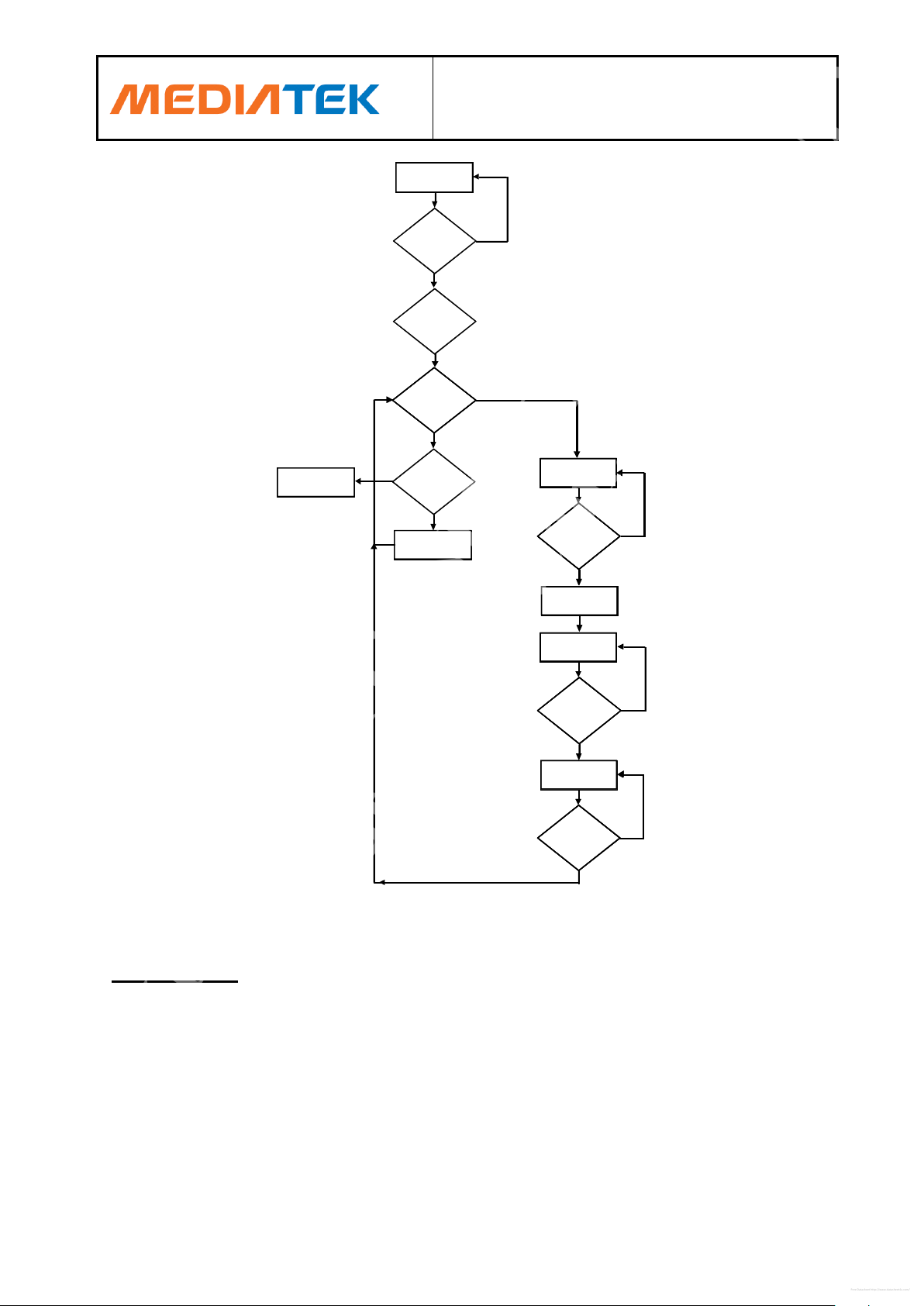

3.2.2.1.2 Charging Control

When the charger is active, the charger controller will manage the charging phase according to the

battery status. During the charging period, the battery voltage is constantly monitored. The battery

charger supports pre-charge mode (VBAT < 3.2V, PMIC power-off state), CC mode (constant current

mode or fast charging mode at the range of 3.2V < VBAT < 4.2V) and CV mode (constant voltage

mode) to optimize the charging procedure for Li-ion battery. See the figure below for the charging

states diagram.

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 30 of 97

YES

CC Mode

VBAT > 4.1V

YES

NO

VBAT < 4.35V

Charger OFF

More than N times

FULL

YES

YES

NO

CHRIN > 4.3V

PreCC

YES

VBAT > 4.2V

YES

YES

CHRIN DET

VBAT > 3.3V

NON-CHARGING

Dead Battery

VBAT<2.2V

45 min timeout

NO

YES

VBAT < 3.3V

45 min timeout

NO

YES

CV Mode

CHRIN

Charger OFF

NO

NO

Free Datasheet http://www.datasheet4u.com/

Figure 5: Charging states diagram

Pre-charge mode

When the battery voltage is in the UVLO state, the charger will operate in the pre-charge mode. There

are two steps in this mode. While the battery voltage is deeply discharged below 2.2V, PRECC0

trickle charging current is applied to the battery.

MEDIATEK CONFIDENTIAL

The PRECC1 trickle charging current is about 56mA continuous current when VBAT is under 2.2V.

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 31 of 97

Rsense

40mV

Rsense

V

I

SENSE

adapter ACPRECC2,

Rsense

14mV

Rsense

V

I

SENSE

HOSTUSB PRECC2,

Free Datasheet http://www.datasheet4u.com/

When the battery voltage exceeds 2.2V, i.e. the PRECC2 stage, the closed-loop pre-charge will be

enabled. The voltage drop across the external RSENSE is kept around 40mV (AC charger) or 14mV

(USB host). The closed-loop pre-charge current can be calculated:

Constant current mode

As the battery is charged up and over 3.3V, it can switch to the CC mode. (CHR_EN should be high)

In the CC mode, several charging currents can be set by programming registers or the external

RSENSE resistor. The charging current can be determined by CS_VTH/RSENSE, where CS_VTH is

programmed by registers. For example, if RSENSE is selected as 0.2ohm, the CC mode charging

current can be set from 70 to 800mA. It can accommodate the battery charger to various charger

inputs with different current capability.

Constant-voltage mode and over-voltage protection (OV)

While the battery voltage reaches about 4.2V, a constant current with much shorter period is used for

charging. It allows more often full battery detection in non-charging period. This is called the fullvoltage charging mode or constant-voltage charging mode in correspondence to a linear charger.

While the battery voltage actually reaches 4.2V, more than the pre-setting times within the limited

charging cycles, the end-of-charging process starts. It may prolong the charging and detecting period

for acquiring optimized full charging volume. The end of charging process is fully controlled by the

baseband and can be easily optimized for different battery packs. Once the battery voltage exceeds

4.35V, a hardware OV protection should be activated and turn off the charger immediately.

3.2.2.1.3 BC1.1 Dead-Battery Support of China Standard

MT6255 also support dead-battery condition from China standard (BC1.1). These specifications

protect dead-battery charging by timer and trickle current. Once the battery voltage is below 2.2V, a

period (TUNIT) of trickle current (IUNIT) will be applied to the battery.

If the battery voltage is still below 2.2V after applying the trickle current, the charger will be disabled.

On the other hand, once if the battery voltage rises up to above 2.2V, the charger will enter the

PRECC1 stage, and the charging current will be 70mA or 200mA depending on the type of the

charging port.

Under the condition of battery voltage from 2.2V to 3.3V, the charger will charge the battery with the

PRECC1 current.

A dedicated 5 mins. (T1) timer will be timed out and disable the charger if the battery voltage is always

below 2.7V under charging. Another 35 mins. (T2) timer will also be timed out and disable the charger

if the battery voltage is always kept between 2.7V and 3.3V under charging.

FOR zlixin@ waterworld.com.cn USE ONLY

MEDIATEK CONFIDENTIAL

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 32 of 97

BUCK name

Vout (Volt)

Imax (mA)

Application

VCORE

0.75 ~ 1.3 (25mV/step)

1,000

Digital CORE

VPROC/Vcore2

0.75 ~ 1.3 (25mV/step)

1,500

Processor

VIO18

1.8

1,000

IO

VRF_1V8

1.825

250

RF chip

V3GPA

0.9 ~ 3.4 (0.1V/step)

800

3G power amplifier

Free Datasheet http://www.datasheet4u.com/

The trickle current (IUNIT) and two dedicated timers protect the charging action if the battery is dead.

3.2.3 Buck Converter

There are 5 buck converters in MT6329 to efficiently generate regulated power for processor, digital

core, 3G power amplifier, memory IO and RF circuit. The block diagram is shown in Figure 10. The

buck converters operate with typically 2 MHz fixed frequency pulse width modulation (PWM) mode at

moderate to heavy load currents. At light load currents, the converter automatically enters pulse

frequency modulation (PFM) mode to save power and improve light load efficiency. It also has a forcePWM mode option to allow the converter to remain in the PWM mode regardless of the load current,

so that the noise spectrum of the converter can be minimized for certain highly-noise-sensitive

handset applications. The buck converters also have an internal over-current protection (OCP) circuit

to limit the maximum high-side power FET current in over-load conditions. It has an internal soft start

circuit to control the ramp-up rate of the output voltage during start-up.

Table 10: Buck converter brief specifications

1. Processor power, VPROC

VPROC is a high-current buck converter to provide a highly-efficient power supply for the handset

processor. Powering from a Li-ion battery, VPROC steps down the input voltage from 3.4 ~ 4.3V

to the typical output voltage of 1.2V with a maximum load current capability of 1.2A. The output

voltage can be adjusted between 0.7V and 1.3V. In order to optimize the overall system efficiency

for the processor, VPROC features a Dynamic Voltage Frequency Scaling (DVFS) function which

allows it to dynamically adjust its output voltage between 0.9V and 1.2V under different voltage

supply demands from the processor. For more details, refer to the “Dynamic Voltage Frequency

Scaling (DVFS)” section.

2. Digital CORE power, VCORE

VCORE is a high-current buck converter to provide a highly-efficient power supply for the handset

digital core. Powering from a Li-ion battery, VCORE steps down the input voltage from 3.4 ~ 4.3V

to the typical output voltage of 1.1V with a maximum load current capability of 1.0A. The output

voltage can be adjusted between 0.7V and 1.3V. In order to optimize the overall system efficiency

MEDIATEK CONFIDENTIAL

for digital core, VCORE features a Dynamic Voltage Frequency Scaling (DVFS) function which

allows it to dynamically adjust its output voltage between 0.9V and 1.1V under different voltage

supply demands from the digital core circuit. For more details, refer to the “Dynamic Voltage

Frequency Scaling (DVFS)” section.

FOR zlixin@ waterworld.com.cn USE ONLY

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

MT6329

PMIC Datasheet

Confidential A

MediaTek Confidential

© 2011 - 2012 MediaTek Inc.

Page 33 of 97

RG_VCORE_CTRL

Default:0

RG_VCORE_VOSEL

RG_VCORE_VOSEL_CON1

RG_VCORE_VOSEL

QI_VCORE_VOSEL[4:0]

0

1

0

1

SRCLKEN

0

1

RG_VCORE_VOSEL_SFCHG_EN

Default:0

SOFT_CHG

Free Datasheet http://www.datasheet4u.com/

3. IO & memory power, VIO18

VIO18 is a high-current buck converter to provide a highly-efficient power supply for the handset

I/O power. Powering from a Li-ion battery, VIO18 steps down the input voltage from 3.4 ~ 4.3V to

the typical output voltage of 1.8V with a maximum load current capability of 1.0A.

4. 3G PA power, VPA

VPA regulator is a DC-DC step-down converter which provides 0.9V to 3.4V programmable output

voltage (0.1V per step) and sources 800mA current at 3.4V and 150mA at 0.9V. In addition, its

output voltage can be configured at 1.35V by register settings. It provide 600mA current at 1.35V

and 1.5V output voltage to support DDRIII applications.

5. RF power, VRF18

VRF18 is a buck converter to provide a highly-efficient power supply for the handset RF power.

Powering from a Li-ion battery, VRF18 steps down the input voltage from 3.4 ~ 4.3V to the typical

output voltage of 1.825V with a maximum load current capability of 0.25A.

3.2.4 DVFS Control (Dynamic Voltage Frequency Scaling)

VCORE1, VPROC and VM12_INT have DVFS control respectively. There are two DVS modes: 1)

One-shot mode: If DVFS is issued, the voltage will directly jump to the target one. 2) Soft-change

mode: If DVFS is issued, the voltage will be switched step by step. See the figure below for the

VCORE DVFS voltage control logic:

There are two control modes:

1. Direct control by register (when @RG_VCORE_CTRL = 0)

2. Auto switch between normal operation mode and sleep mode voltage (when

@RG_VCORE_CTRL = 1)

See the figure below for the VPROC DVFS voltage control logic: