General Description

The MAX4357 is a 32 16 highly integrated video

crosspoint switch matrix with input and output buffers.

This device operates from dual ±3V to ±5V supplies or

from a single +5V supply. Digital logic is supplied from

an independent single +2.7V to +5.5V supply. All inputs

and outputs are buffered, with all outputs able to drive

standard 75Ω reverse-terminated video loads.

The switch matrix configuration and output buffer gain

are programmed through an SPI™/QSPI™-compatible,

3-wire serial interface and initialized with a single

update signal. The unique serial interface operates in

two modes facilitating both fast updates and initialization. On power-up, all outputs are initialized in the disabled state to avoid output conflicts in large-array

configurations.

Superior flexibility, high integration, and space-saving

packaging make this nonblocking switch matrix ideal

for routing video signals in security and video-ondemand systems.

The MAX4357 is available in a 128-pin TQFP package

and specified over an extended -40°C to +85°C temperature range.

Applications

Security Systems

Video Routing

Video-On-Demand Systems

Features

o 32 16 Nonblocking Matrix with Buffered Inputs

and Outputs

o Operates from ±3V, ±5V, or +5V Supplies

o Each Output Individually Addressable

o Individually Programmable Output Buffer Gain

(A

V

= +1V/V or +2V/V)

o High-Impedance Output Disable for Wired-OR

Connections

o 0.1dB Gain Flatness to 12MHz

o Minimum -62dB Crosstalk, -110dB Isolation at

6MHz

o 0.05%/0.1° Differential Gain/Differential Phase

Error

o Low 220mW Power Consumption (0.43mW per

point)

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

________________________________________________________________

Maxim Integrated Products

1

Ordering Information

19-2209; Rev 1; 5/09

Pin Configuration appears at end of data sheet.

SPI/QSPI are trademarks of Motorola, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

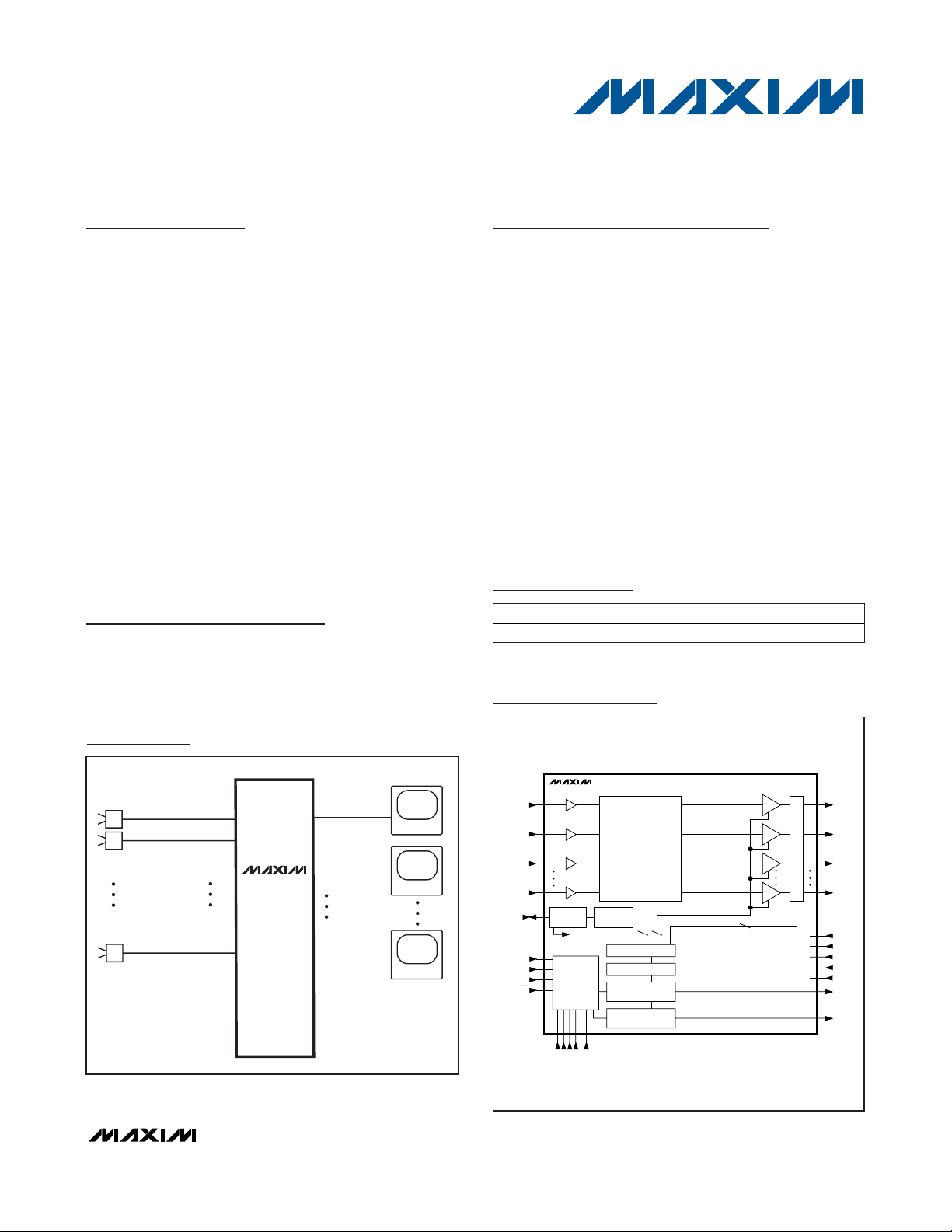

Typical Operating Circuit

MAX4357

32 x 16

SWITCH MATRIX

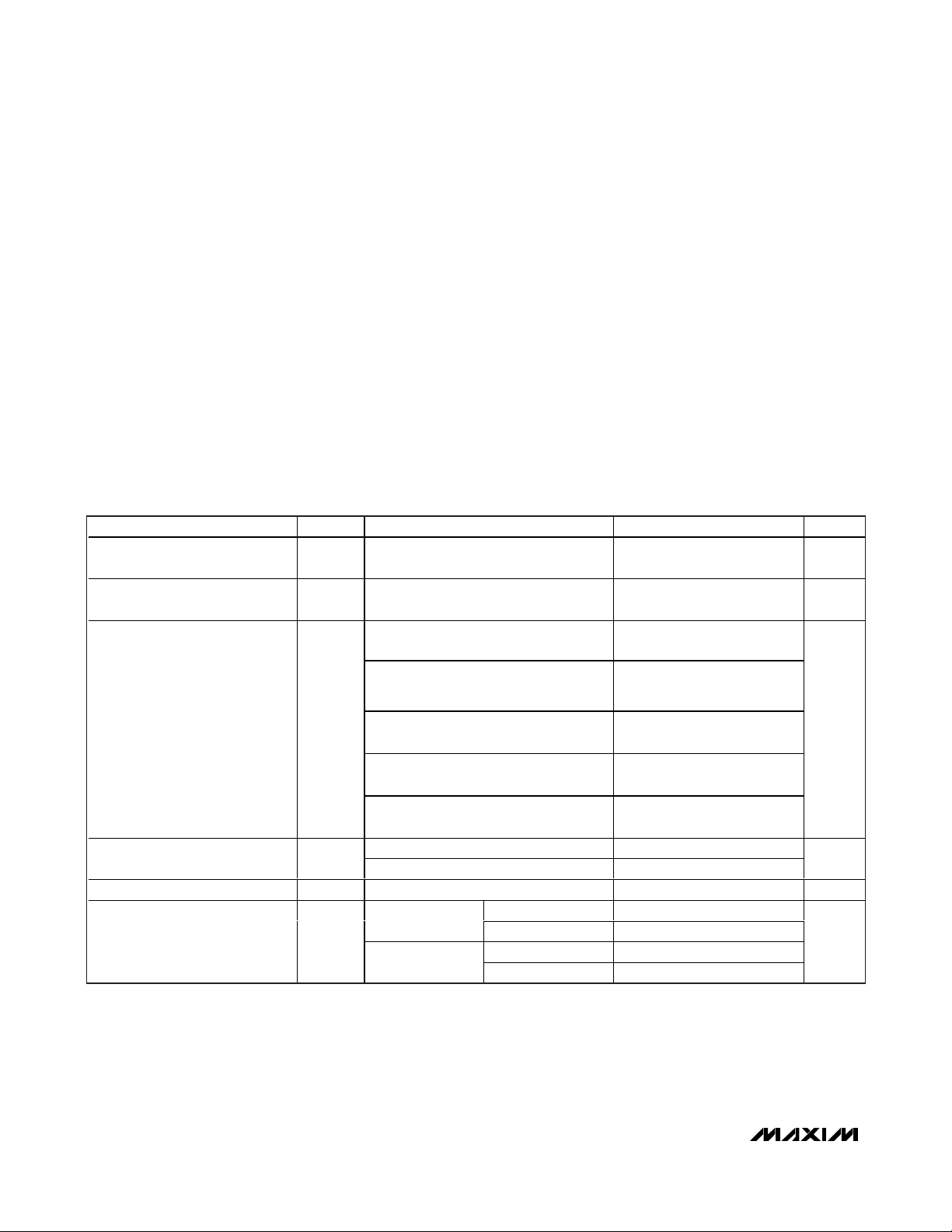

POWER-ON

RESET

SERIAL

INTERFACE

THERMAL

SHUTDOWN

DECODE LOGIC

DISABLE ALL OUTPUTS

LATCHES

512

16

16

MATRIX REGISTER

112 BITS

UPDATE REGISTER

16 BITS

ENABLE/DISABLE

AV*

AV*

AV*

AV*

*A

V

= +1V/V OR +2V/V

A0-A3 MODE

IN0

IN1

IN2

IN31

DIN

SCLK

UPDATE

CE

RESET

OUT0

OUT1

OUT2

OUT15

V

CC

V

EE

DGND

V

DD

DOUT

AOUT

AGND

Functional Diagram

PART TEMP RANGE PIN-PACKAGE

MAX4357ECD -40°C to +85°C 128 TQFP

CAMERAS

IN0

IN1

MAX4357

IN31

OUT0

OUT1

OUT15

MONITOR

MONITOR

MONITOR

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

2 _______________________________________________________________________________________

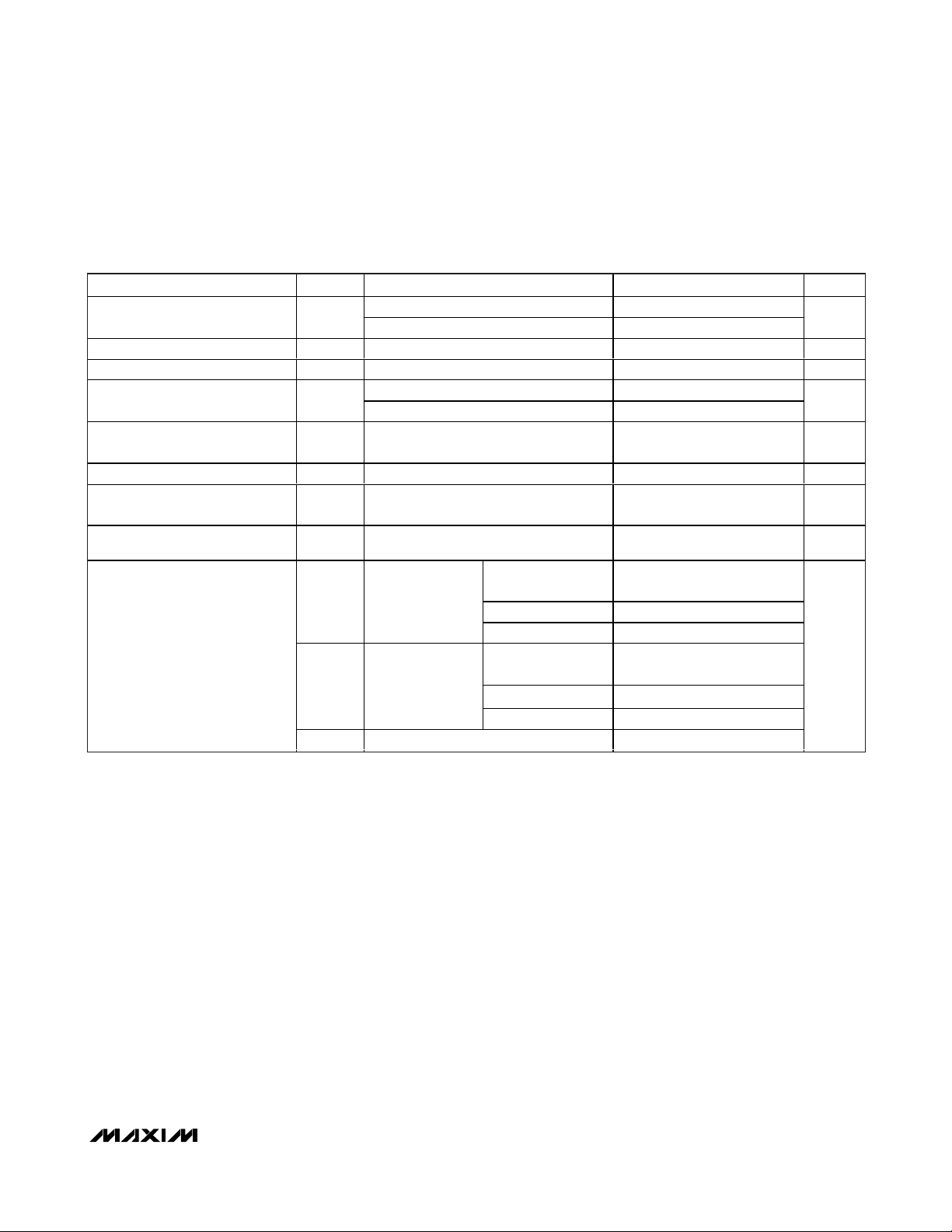

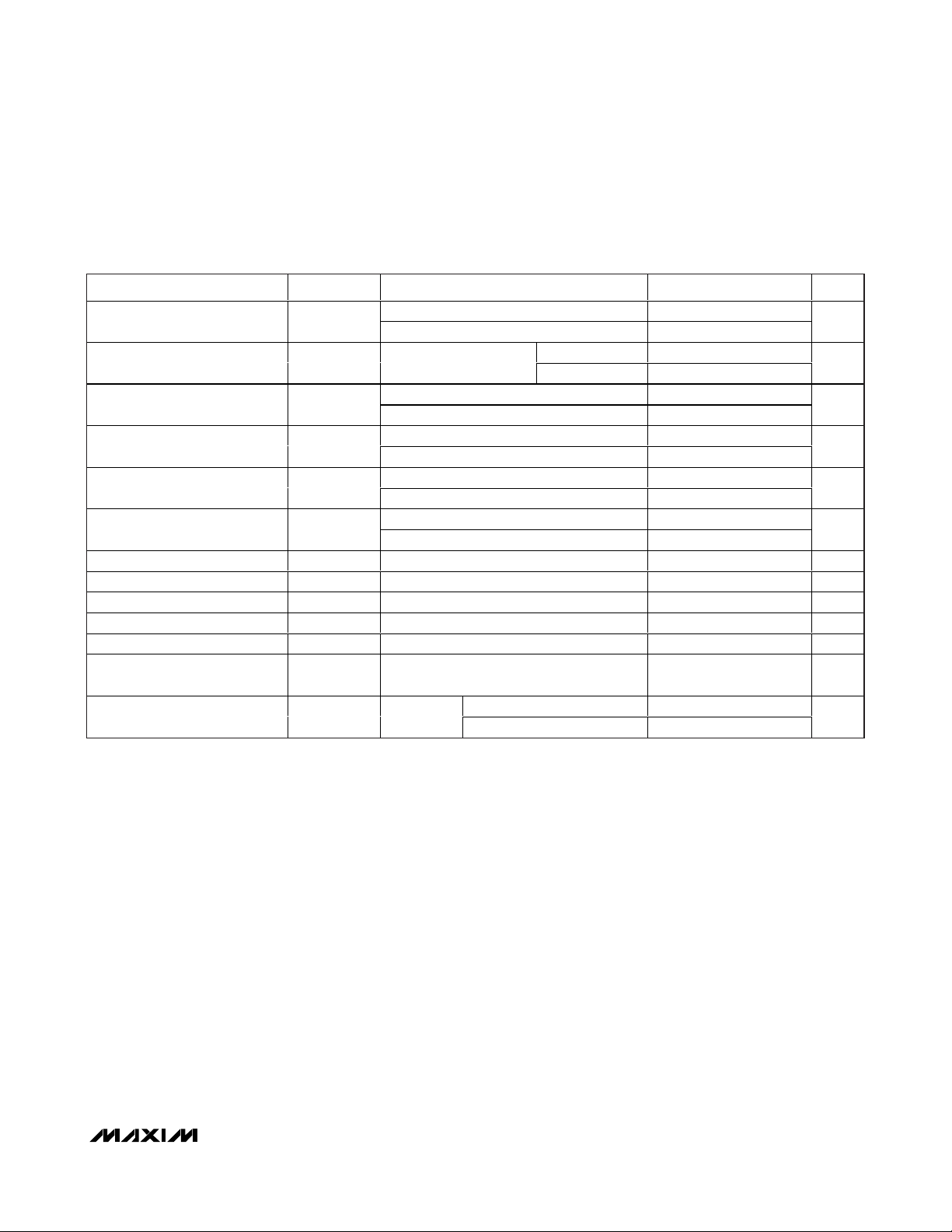

ABSOLUTE MAXIMUM RATINGS

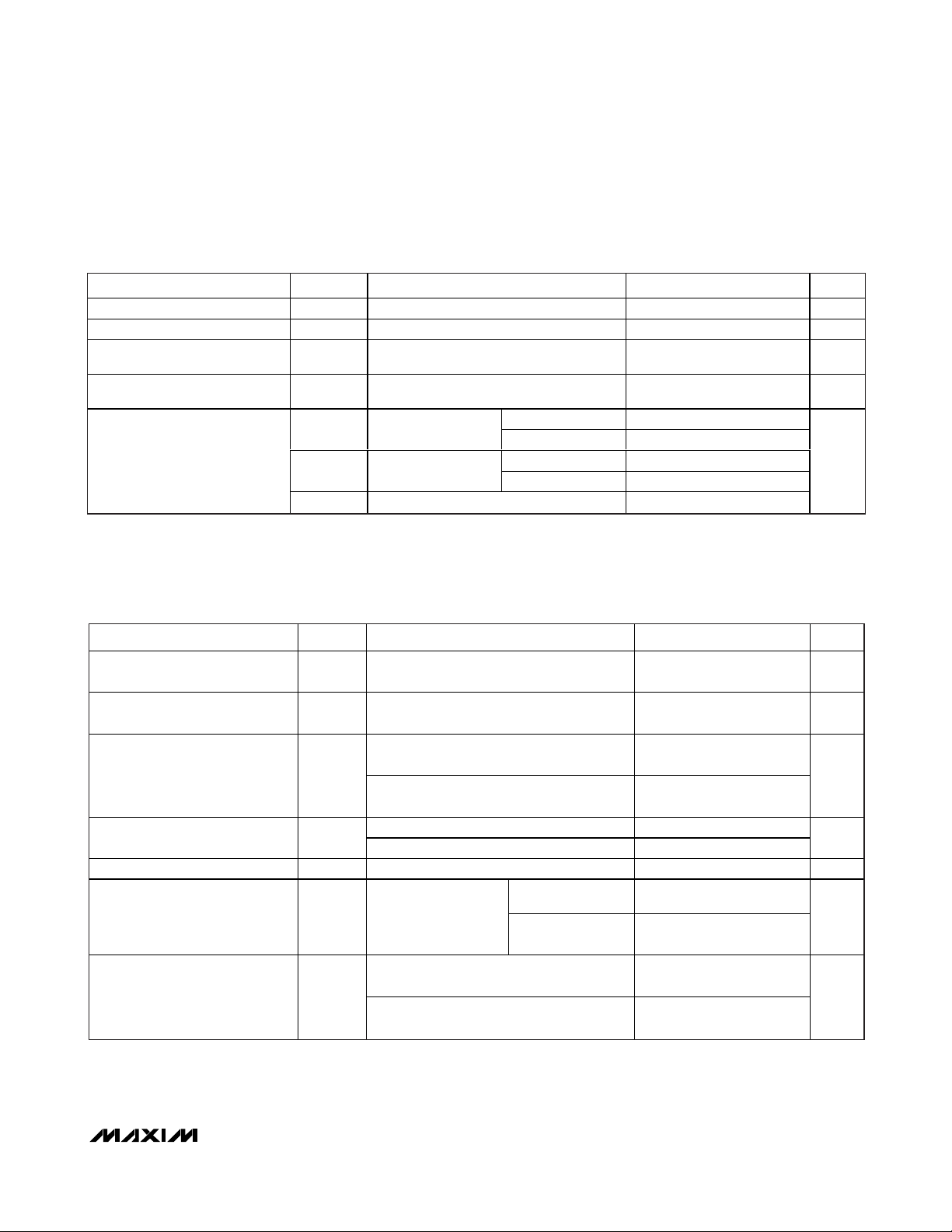

DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V

(VCC= +5V, VEE= -5V, VDD= +5V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

, unless otherwise

noted. Typical values are at T

A

= +25°C.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Analog Supply Voltage (VCC- VEE) .....................................+11V

Digital Supply Voltage (V

DD

- DGND) ...................................+6V

Analog Supplies to Analog Ground

(V

CC

- AGND) and (AGND - VEE) ..................................... +6V

Analog Ground to Digital Ground .........................-0.3V to +0.3V

IN_ Voltage Range .......................... (V

CC

+ 0.3V) to (VEE- 0.3V)

OUT_ Short-Circuit Duration to AGND, V

CC

, or VEE......Indefinite

SCLK, CE, UPDATE, MODE, A_, DIN, DOUT,

RESET, AOUT..........................(V

DD

+ 0.3V) to (DGND - 0.3V)

Current into Any Analog Input Pin (IN_) ...........................±50mA

Current into Any Analog Output Pin (OUT_).....................±75mA

Continuous Power Dissipation (T

A

= +70°C)

128-Pin TQFP (derate 25mW/°C above +70°C).................2W

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) ................................ +300°C

Operating Supply Voltage

Range

Logic-Supply Voltage Range

PARAMETER SYMBOL

V

CC

V

EE

VDD to

DGND

Guaranteed by PSRR test

(VEE + 2.5V) < VIN_ < (VCC - 2.5V),

= +1V/V, RL = 150Ω

A

V

CONDITIONS

MIN

4.5

2.7

0.97

TYP

0.995

MAX UNITS

10.5

5.5

1

V

V

Gain (Note 1)

Gain Matching

(Channel to Channel)

Temperature Coefficient of Gain TC

Input Voltage Range

VIN_

(VEE + 2.5V) < VIN_ < (VCC - 2.5V),

= +1V/V, RL = 10kΩ

A

V

A

(VEE + 3.75V) < VIN_ < (VCC - 3.75V),

V

AV = +2V/V, RL = 150Ω

(VEE + 3.75V) < VIN_ < (VCC - 3.75V)

AV = +2V/V, RL = 10kΩ

(VEE + 1V) < VIN_ < (VCC - 1.2V),

AV = +1V/V, RL = 10kΩ

RL = 10kΩ

RL = 150Ω

AV

AV = +1V/V

AV = +2V/V

RL = 10kΩ

RL = 150Ω

RL = 10kΩ

RL = 150Ω

0.99

1.92

1.94

0.95

V

+ 1

E E

V

E E

VEE + 3

V

E E

+ 2.5

+ 3.75

0.999

1.996

2.008

0.994

0.5

0.5

10

1

2.08

2.06

1

1.5

2

V

- 1.2

C C

V

- 2.5

C C

V

- 3.1

C C

V

- 3.75

C C

V/V

%

ppm/°C

V

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

_______________________________________________________________________________________ 3

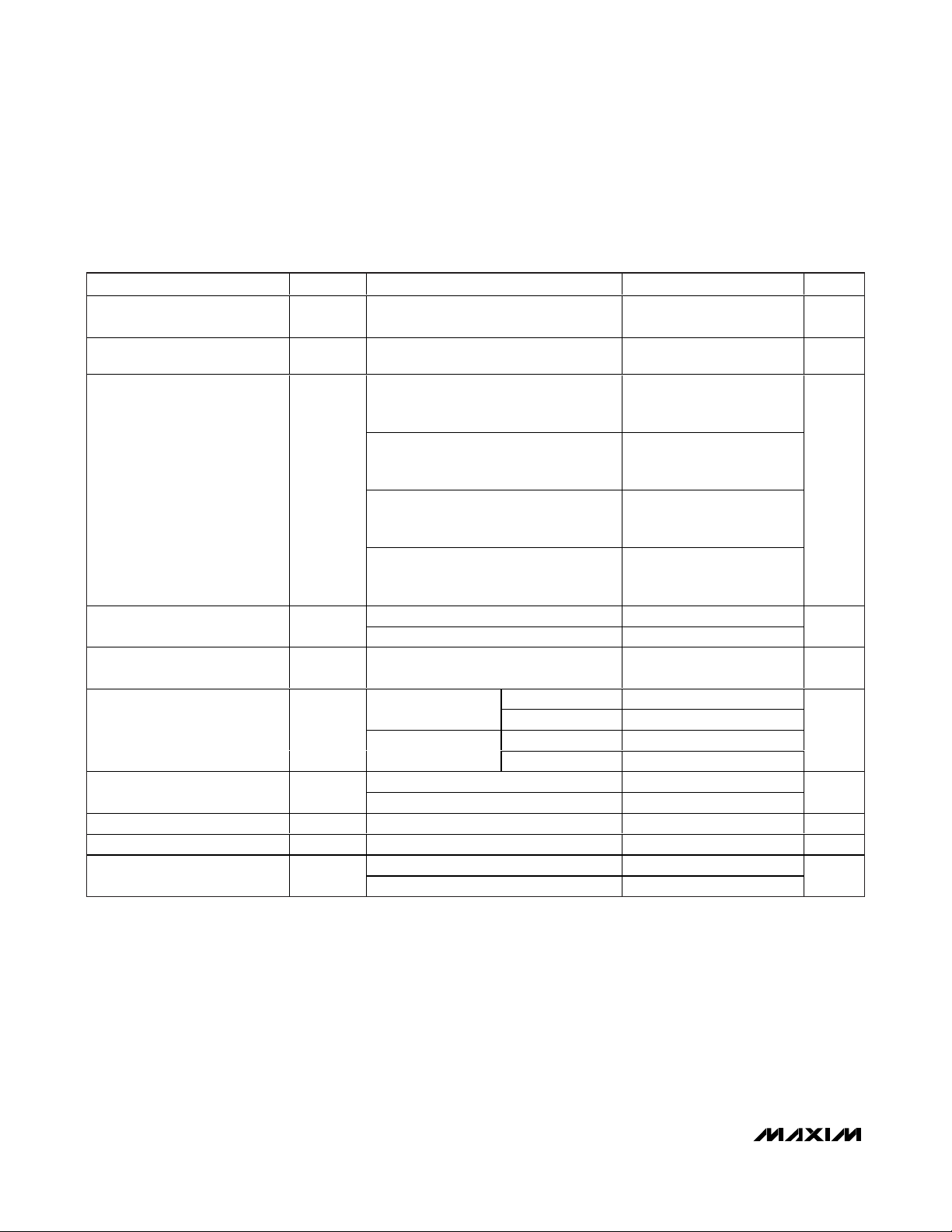

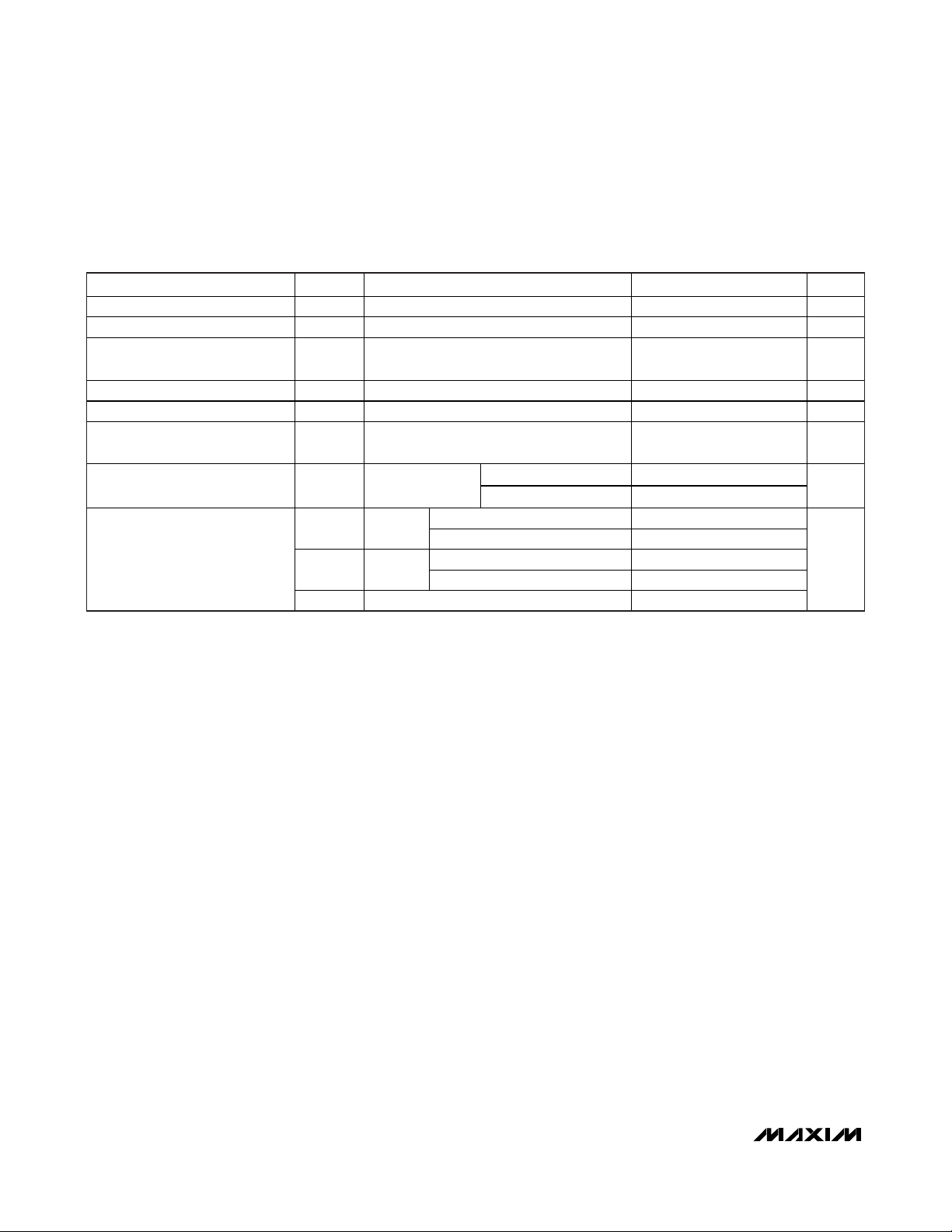

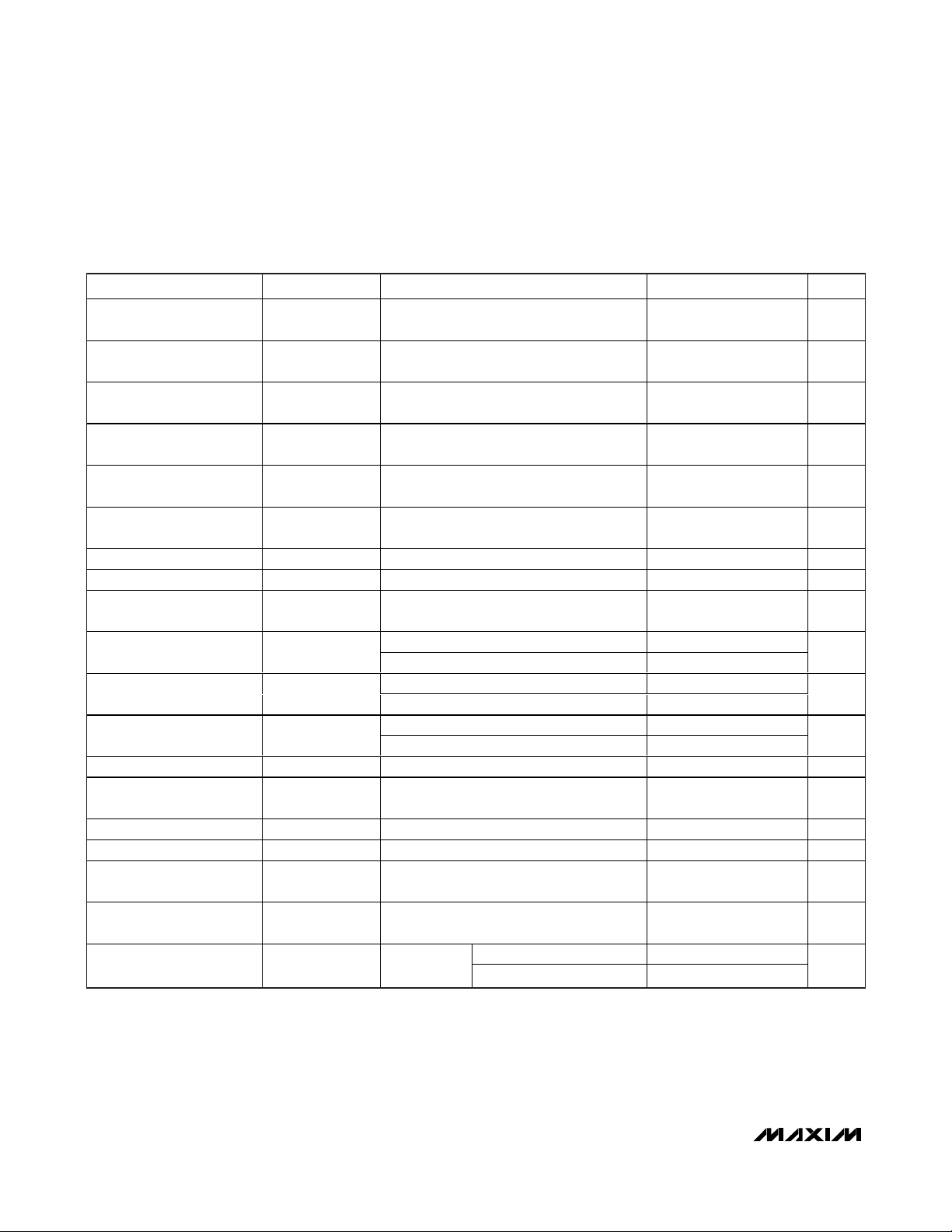

DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V (continued)

(VCC= +5V, VEE= -5V, VDD= +5V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

, unless otherwise

noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL

Output Voltage Range

Input Bias Current

Input Resistance

Output Offset Voltage

Output Short-Circuit Current

Enabled Output Impedance

Output Leakage Current,

Disable Mode

DC Power-Supply Rejection

Ratio

Quiescent Supply Current

CONDITIONS

V

OUT

I

RIN_ (VEE + 1V) < VIN_ < (VCC - 1.2V)

V

OFFSET

I

SC

Z

OUT

I

OD

PSRR 4.5V < (V

I

CC

I

EE

I

DD

RL = 10kΩ

RL = 150Ω

B

AV = +1V/V

AV = +2V/V

Sinking or sourcing, RL = 1Ω

(VEE + 1V) < VIN_ < (VCC - 1.2V)

(VEE + 1V) < V

CC

RL = ∞

RL = ∞

_ < (VCC - 1.2V)

OUT

- VEE) < 10.5V

Outputs enabled,

T

= +25°C

A

Outputs enabled

Outputs disabled

Outputs enabled,

= +25°C

T

A

Outputs enabled

Outputs disabled

MIN

VEE + 1

V

+ 2.5

E E

10

±5

60

55

95

50

TYP

4

±10

±40

0.2

0.004

70

100

4

MAX UNITS

V

- 1.2

C C

V

- 2.5

C C

11

±20

±40

1

150

175

75

150

175

75

8

V

µA

MΩ

mV

mA

Ω

µA

dB

mA

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

4 _______________________________________________________________________________________

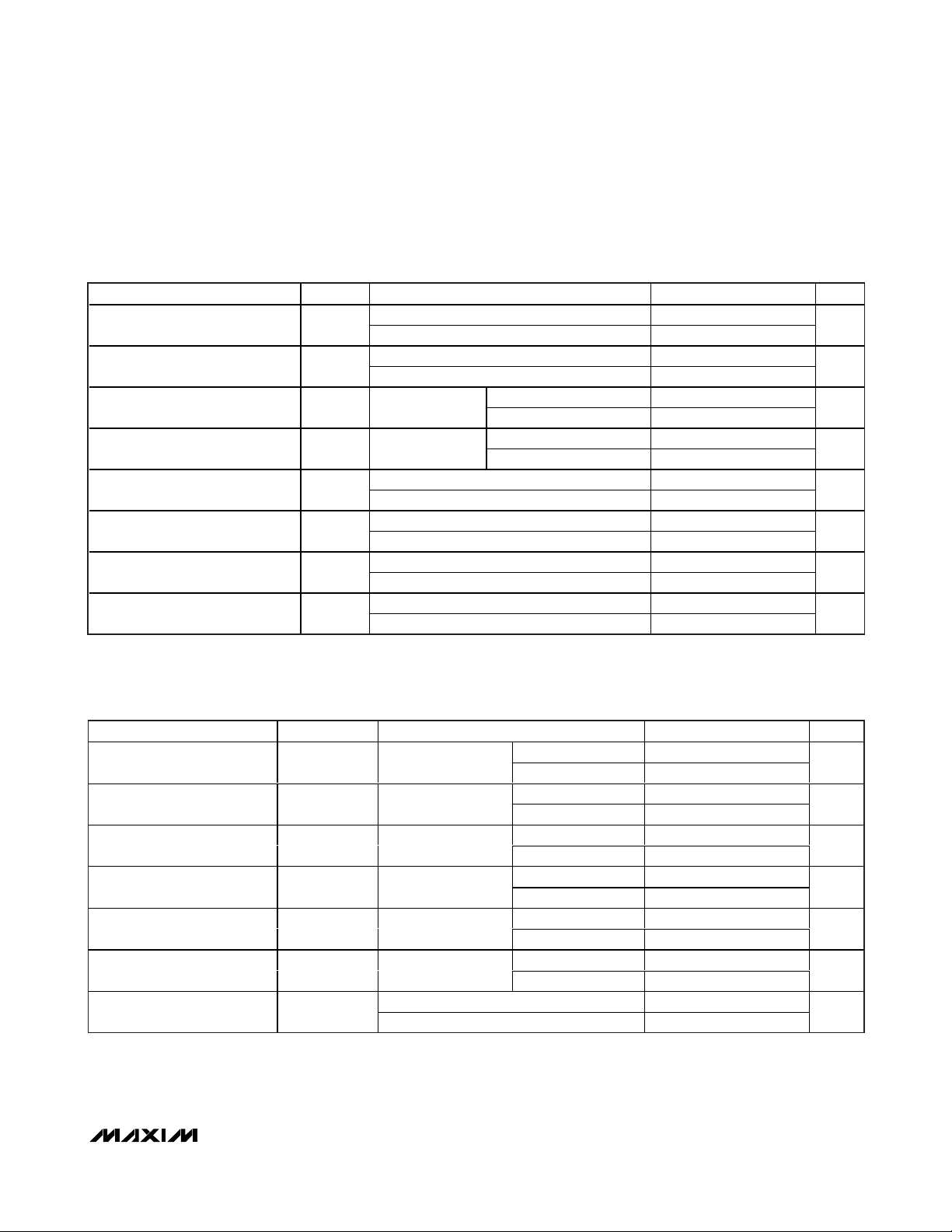

DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V

(VCC= +3V, VEE= -3V, VDD= +3V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

, unless otherwise

noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL

Operating Supply Voltage

Range

Logic-Supply Voltage Range

Gain (Note 1)

VCC - V

VDD to

DGND

A

V

CONDITIONS

Guaranteed by PSRR test

EE

(VEE + 1V) < VIN_ < (VCC - 1.2V),

A

= +1V/V, RL = 150Ω

V

(VEE + 1V) < VIN_ < (VCC - 1.2V),

= +1V/V, RL = 10kΩ

A

V

(VEE + 2V) < VIN_ < (VCC - 2.1V),

= +2V/V, RL = 150Ω

A

V

(VEE + 2V) < VIN_ < (VCC - 2.1V)

= +2V/V, RL = 10kΩ

A

V

MIN

4.5

2.7

0.94

0.96

1.92

1.94

TYP MAX UNITS

0.983

0.993

1.985 2.08

2.00

10.5

5.5

1

1

2.06

V

V

V/V

Gain Matching

(Channel to Channel)

Temperature Coefficient of

Gain

Input Voltage Range

Output Voltage Range

Input Bias Current

Input Resistance

Output Offset Voltage

TC

VIN_

V

OUT

I

R

V

OFFSET

B

IN

RL = 10kΩ

RL = 150Ω

AV

AV = +1V/V

AV = +2V/V

RL = 10kΩ

RL = 150Ω

RL = 10kΩ

RL = 150Ω

RL = 10kΩ

RL = 150Ω

(VEE + 1V) < VIN_ < (VCC - 1.2V)

AV = +1V/V

AV = +2V/V

VEE + 1

VEE + 1

VEE + 2

VEE + 2

VEE + 1

VEE + 1

0.5

0.5

10

4

1.5

2

VCC - 1.2

VCC - 1.2

VCC - 2.1

VCC - 2.1

VCC - 1.2

VCC - 1.2

11

ppm/°C

10

±5

±10

±20

±40

%

V

V

µA

MΩ

mV

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

_______________________________________________________________________________________ 5

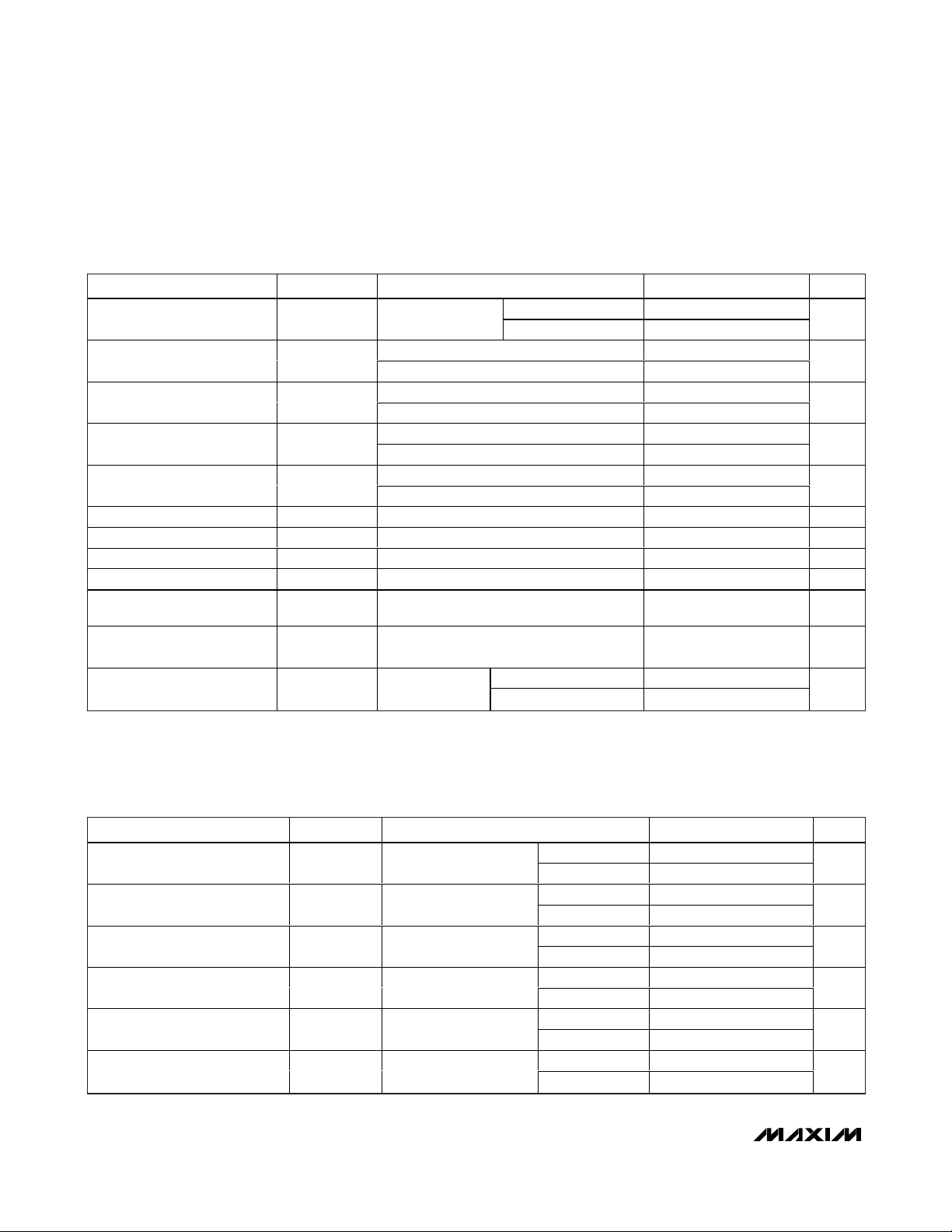

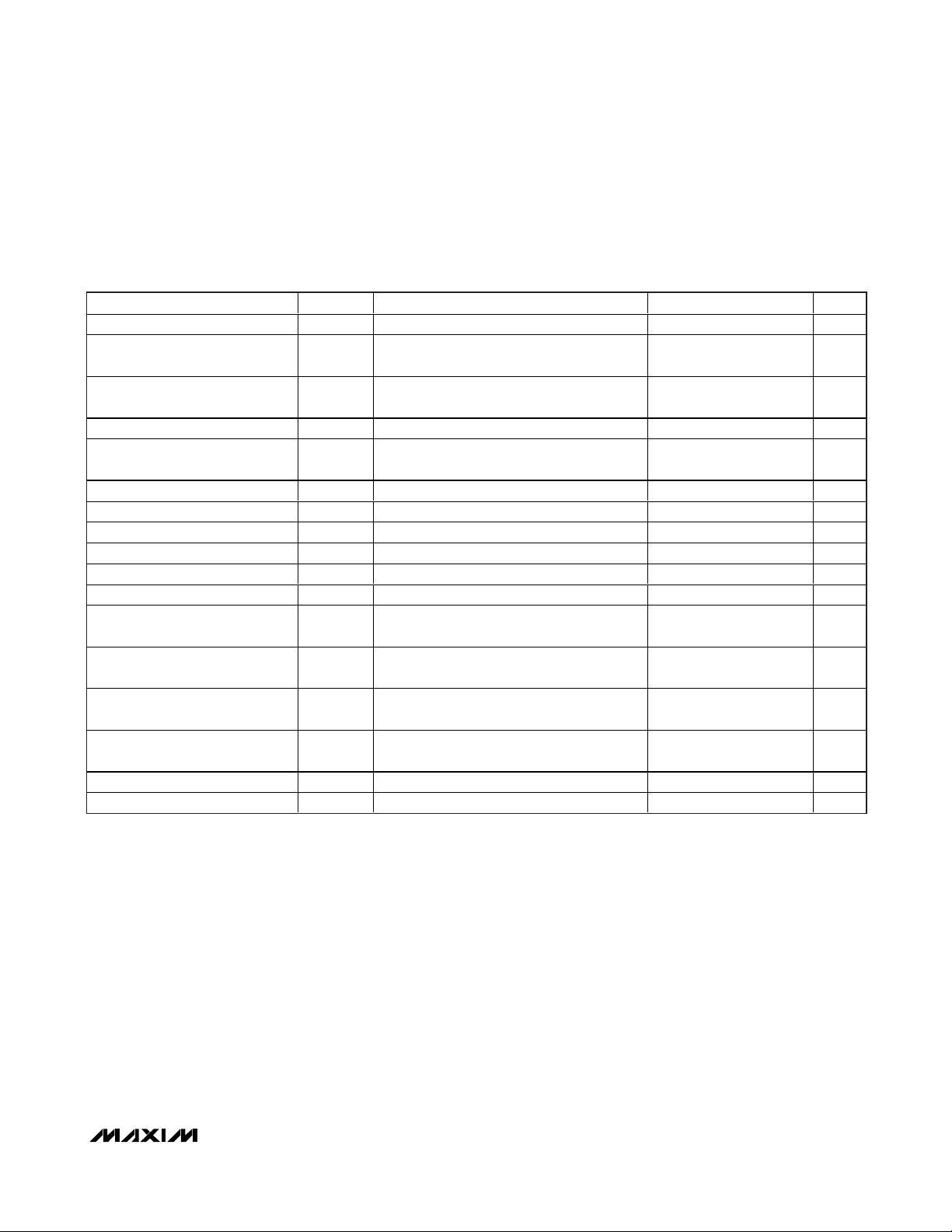

DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V (continued)

(VCC= +3V, VEE= -3V, VDD= +3V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

, unless otherwise

noted. Typical values are at T

A

= +25°C.)

DC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V

(VCC= +5V, VEE= 0, VDD= +5V, AGND = DGND = 0, VIN_ = +1.75V, AV= +1V/V, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

,

unless otherwise noted. Typical values are at TA= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output Short-Circuit Current I

Enabled Output Impedance Z

Output Leakage Current,

Disable Mode

DC Power-Supply Rejection

Ratio

Quiescent Supply Current

SC

OUT

I

OD

PSRR 4.5V < (V

I

CC

I

EE

I

DD

Sinking or sourcing, R

(V

+ 1V) < VIN_ < (VCC - 1.2V) 0.2 Ω

EE

(V

+ 1V) < V

EE

R

= ∞

L

RL = ∞

OUT

- VEE) < 10.5V 60 75 dB

CC

= 1Ω ±40 mA

L

_ < (V

- 1.2V) 0.004 1 µA

CC

Outputs enabled 90

Outputs disabled 45

Outputs enabled 85

Outputs disabled 40

3

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Operating Supply Voltage

Range

Logic-Supply Voltage Range

Gain (Note 1) A

Gain Matching (Channel to

Channel)

Temperature Coefficient of Gain TC

Input Voltage Range V

Output Voltage Range V

V

CC

V

DD

DGND

V

AV

IN

OUT

Guaranteed by PSRR test 4.5 5.5 V

to

2.7 5.5 V

(V

+ 1V) < V

EE

A

= +1V/V, RL = 150Ω

V

(V

+ 1V) < V

EE

A

= +1V/V, RL = 10kΩ

V

R

= 10kΩ 0.5 3

L

RL = 150Ω 0.5 3

< (VCC - 2.5V),

IN

< (VCC - 1.2V),

IN

0.94 0.995 1

0.94 0.995 1

10 ppm/°C

V

A

= +1V/V

V

AV = +1V/V,

R

= 10kΩ

L

A

= +1V/V,

V

R

= 150Ω

L

R

= 10kΩ

L

R

= 150Ω

L

+

EE

1

V

+

EE

1

V

+

EE

1

V

+

EE

1

VCC -

VCC -

VCC -

VCC -

1.2

2.5

1.2

2.5

mA

V

%

V

V

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

6 _______________________________________________________________________________________

DC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V (continued)

(VCC= +5V, VEE= 0, VDD= +5V, AGND = DGND = 0, VIN_ = +1.75V, AV= +1V/V, RL= 150Ω to AGND, and TA= T

MIN

to T

MAX

,

unless otherwise noted. Typical values are at TA= +25°C.)

Input Bias Current I

Input Resistance R

Output Offset

Voltage

Output Short-Circuit Current I

Enabled Output Impedance Z

Output Leakage Current,

Disable Mode

DC Power-Supply Rejection

Ratio

Quiescent Supply Current

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

4 11 µA

B

V

IN

V

OFFSET AV

SC

OUT

I

OD

PSRR

I

CC

I

EE

I

DD

+ 1V < VIN_ < VCC - 1.2V 10 MΩ

EE

= +1V/V ±10 ±40 mV

Sinking or sourcing, R

(V

+ 1V) < VIN_ < (VCC - 1.2V)

EE

(V

+ 1V) < V

EE

4.5V < V

V

< 5.5V

EE

R

= ∞

L

R

= ∞

L

OUT

-

CC

Outputs enabled, T

Outputs disabled 40

Outputs enabled, T

Outputs disabled 35

= 1Ω

L

_ < (VCC - 1.2V) 0.004 1 µA

T

= +25°C to +85°C 50 65

A

T

= -40°C to +85°C 35

A

= +25°C 90

A

= +25°C 85

A

±35

0.2

4

mA

Ω

dB

mA

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

_______________________________________________________________________________________ 7

LOGIC-LEVEL CHARACTERISTICS

(VCC- V

EE)

= +4.5V to +10.5V, VDD= +2.7V to +5.5V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and T

A

=

T

MIN

to T

MAX

, unless otherwise noted. Typical values are at TA= +25°C.) (Note 2)

AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V

(VCC= +5V, VEE= -5V, VDD= +5V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= +25°C, unless otherwise noted.)

Input Voltage High Level V

Input Voltage Low Level V

Input Current High Level I

Input Current Low Level I

Output Voltage High Level V

Output Voltage Low Level V

Output Current High Level I

Output Current Low Level I

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

VDD = +5.0V 3

IH

VDD = +3V 2

V

= +5.0V 0.8

IL

IH

IL

OH

OL

OH

OL

DD

VDD = +3V 0.6

V

> 2V

I

VI < 1V

I

SOURCE

I

SOURCE

I

= 1mA, VDD = +5V 0.1 0.3

SINK

I

= 1mA, VDD = +3V 0.1 0.3

SINK

VDD = +5V, V

VDD = +3V, V

VDD = +5V, V

VDD = +3V, VO = +0.3V 1 8

Excluding RESET -1 0.01 1

RESET -30 -20

Excluding RESET -1 0.01 1

RESET -300 -235

= 1mA, VDD = +5V 4.7 4.9

= 1mA, VDD = +3V 2.7 2.9

= +4.9V 1 4

O

= +2.7V 1 8

OUT

= +0.1V 1 4

O

V

V

µA

µA

V

V

mA

mA

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

A

= +1V/V 95

Small-Signal -3dB

Bandwidth

Medium-Signal -3dB

Bandwidth

Large-Signal -3dB

Bandwidth

Small-Signal 0.1dB

Bandwidth

Medium-Signal

0.1dB Bandwidth

Large-Signal 0.1dB

Bandwidth

BW

BW

BW

BW

BW

BW

0.1dB-SS

0.1dB-MS

0.1dB-LS

Slew Rate SR

SS

MS

LS

V

_ = 20mVp-p

OUT

V

_ =

OUT

200mVp-p

V

_ = 2Vp-p

OUT

V

_ = 20mVp-p

OUT

V

_ =

OUT

200mVp-p

V

_ = 2Vp-p

OUT

V

_ = 2V step, AV = +1V/V 150

OUT

V

_ = 2V step, AV = +2V/V 160

OUT

V

A

= +2V/V 70

V

A

= +1V/V 90

V

A

= +2V/V 70

V

A

= +1V/V 40

V

A

= +2V/V 50

V

A

= +1V/V 15

V

A

= +2V/V 15

V

A

= +1V/V 15

V

A

= +2V/V 15

V

A

= +1V/V 12

V

A

= +2V/V 12

V

MHz

MHz

MHz

MHz

MHz

MHz

Vµs

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

8 _______________________________________________________________________________________

AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V

(VCC= +3V, VEE= -3V, VDD= +3V, AGND = DGND = 0, VIN_= 0, RL= 150Ω to AGND, AV= +1V/V, and TA= +25°C, unless

otherwise noted.)

AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V (continued)

(VCC= +5V, VEE= -5V, VDD= +5V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, and TA= +25°C, unless otherwise noted.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

A

= +1V/V 60

V

_ = 0 to 2V

Settling Time t

Switching Transient (Glitch)

(Note 3)

AC Power-Supply Rejection

Ratio

Differential Gain Error

(Note 4)

Differential Phase Error

(Note 4)

S 0.1%

OUT

step

A

= +1V/V 50

V

AV = +2V/V 50

f = 100kHz 70

f = 1MHz 68

R

= 1kΩ 0.01

L

RL = 150Ω 0.05

R

= 1kΩ 0.03

L

RL = 150Ω 0.1

Crosstalk, All Hostile f = 6MHz -62 dB

Off-Isolation, Input-to-Output f = 6MHz -110 dB

Input Noise Voltage Density e

Input Capacitance C

Disabled Output

Capacitance

Capacitive Load at 3dB

Output Peaking

Output Impedance Z

n

IN

Amplifier in disable mode 3 pF

30 pF

OUT

BW = 6MHz 73 µV

5 pF

f = 6MHz

V

A

= +2V/V 60

V

Output enabled 3

Output disabled 4k

ns

mV

dB

%

D eg r ees

RMS

Ω

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

A

= +1V/V 90

Small-Signal

-3dB Bandwidth

Medium-Signal

-3dB Bandwidth

Large-Signal -3dB

Bandwidth

Small-Signal

0.1dB Bandwidth

Medium-Signal

0.1dB Bandwidth

Large-Signal 0.1dB

Bandwidth

BW

SS

BW

MS

BW

LS

BW

0.1dB-SS

BW

0.1dB-MS VOUT

BW

0.1dB-LS

V

_ = 20mVp-p

OUT

V

_ = 200mVp-p

OUT

V

_ = 2Vp-p

OUT

V

_ = 20mVp-p

OUT

_ = 200mVp-p

V

_ = 2Vp-p

OUT

V

A

= +2V/V 65

V

A

= +1V/V 90

V

A

= +2V/V 65

V

A

= +1V/V 30

V

A

= +2V/V 35

V

A

= +1V/V 15

V

A

= +2V/V 15

V

A

= +1V/V 15

V

A

= +2V/V 15

V

A

= +1V/V 12

V

A

= +2V/V 12

V

MHz

MHz

MHz

MHz

MHz

MHz

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

_______________________________________________________________________________________ 9

AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V (continued)

(VCC= +3V, VEE= -3V, VDD= +3V, AGND = DGND = 0, VIN_ = 0, RL= 150Ω to AGND, AV= +1V/V, and TA= +25°C, unless

otherwise noted.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Slew Rate SR

Settling Time t

S 0.1%

Switching Transient (Glitch)

(Note 3)

AC Power-Supply Rejection

Ratio

Differential Gain Error

(Note 4)

Differential Phase Error

(Note 4)

OUT

V

_ = 2V step AV = +2V/V 120

OUT

A

= +1V/V 60

= 0 to 2V step

V

O

A

= +1V/V 15

V

AV = +2V/V 20

f = 100kHz 60

f = 1MHz 40

R

= 1kΩ 0.03

L

RL = 150Ω 0.2

R

= 1kΩ 0.08

L

RL = 150Ω 0.2

V

A

= +2V/V 60

V

Vµs

ns

mV

dB

%

D eg r ees

V

_ = 2V step AV = +1V/V 120

Crosstalk, All Hostile f = 6MHz -63 dB

Off-Isolation, Input to Output f = 6MHz -112 dB

Input Noise Voltage Density e

Input Capacitance C

n

_ 5 pF

IN

BW = 6MHz 73 µV

RMS

Disabled Output Capacitance Amplifier in disable mode 3 pF

Capacitive Load at 3dB

Output Peaking

Output Impedance Z

30 pF

OUT

f = 6MHz

Output enabled 3

Output disabled 4k

Ω

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

10 ______________________________________________________________________________________

AC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V

(VCC= +5V, VEE= 0, VDD= +5V, AGND = DGND = 0, VIN_ = 1.75V, RL= 150Ω to AGND, AV= +1V/V, and TA= +25°C, unless

otherwise noted.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Small-Signal

-3dB Bandwidth

Medium-Signal -3dB

Bandwidth

Large-Signal

-3dB Bandwidth

Small-Signal

0.1dB Bandwidth

Medium-Signal

0.1dB Bandwidth

Large-Signal

0.1dB Bandwidth

Slew Rate SR V

Settling Time t

Switching Transient

(Glitch)

AC Power-Supply

Rejection Ratio

Differential Gain Error

(Note 4)

Differential Phase

Error (Note 4)

Crosstalk, All Hostile f = 6MHz -63 dB

Off-Isolation, Input-to-

Output

Input Noise Voltage

Input Capacitance C

Disabled Output

Capacitance

Capacitive Load at 3dB

Output Peaking

Output

Impedance

BW

BW

BW

BW

BW

0.1dB-MS

BW

SS

MS

LS

0.1dB-SS

0.1dB-LS

S 0.1%

V

_ = 20mVp-p 90 MHz

OUT

V

_ = 200mVp-p 90 MHz

OUT

V

_ = 1.5Vp-p 38 MHz

OUT

V

_ = 20mVp-p 12 MHz

OUT

V

_ = 200mVp-p 12 MHz

OUT

V

_ = 1.5Vp-p 12 MHz

OUT

_ = 2V step, AV = +1V/V 100 V/µs

OUT

V

_ = 0 to 2V step 60 ns

OUT

25 mV

f = 100kHz 70

f = 1MHz 69

R

= 1kΩ 0.03

L

RL = 150Ω 0.15

R

= 1kΩ 0.06

L

RL = 150Ω 0.2

f = 6MHz -110 dB

e

n

IN

_

BW = 6MHz 73 µV

5 pF

Amplifier in disable mode 3 pF

30 pF

Z

OUT

f = 6MHz

Output enabled 3

Output disabled 4k

dB

%

D eg r ees

RMS

Ω

MAX4357

SWITCHING CHARACTERISTICS

((VCC- VEE) = +4.5V to +10.5V, VDD= +2.7V to +5.5V, DGND = AGND = 0, VIN_ = 0 for dual supplies, VIN_ = +1.75V for single supply, RL= 150Ω to AGND, CL= 100pF, AV= +1V/V, and TA= T

MIN

- T

MAX

, unless otherwise noted. Typical values are at TA= +25°C.)

Note 1: Associated output voltage may be determined by multiplying the input voltage by the specified gain (A

V

)

and adding output

offset voltage.

Note 2: Logic-level characteristics apply to the following pins: DIN, DOUT, SCLK, CE, UPDATE, RESET, A3–A0, MODE, and AOUT.

Note 3: Switching transient settling time is guaranteed by the settling time (t

S

) specification. Switching transient is a result of updat-

ing the switch matrix.

Note 4: Input test signal: 3.58MHz sine wave of amplitude 40IRE superimposed on a linear ramp (0 to 100IRE). IRE is a unit of

video-signal amplitude developed by the International Radio Engineers: 140IRE = 1.0V.

Note 5: All devices are 100% production tested at T

A

= +25°C. Specifications over temperature limits are guaranteed by design.

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________ 11

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Delay: UPDATE to Video Out t

Delay: UPDATE to AOUT t

Delay: SCLK to DOUT Valid t

Delay: Output Disable t

Delay: Output Enable t

PdHOeVo VOUT

PdLOeVo

Setup: CE to SCLK t

Setup: DIN to SCLK t

Hold Time: SCLK to DIN t

Minimum High Time: SCLK t

Minimum Low Time: SCLK t

Minimum Low Time: UPDATE t

Setup Time: UPDATE to SCLK t

Hold Time: SCLK to UPDATE t

Setup Time: MODE to SCLK t

Hold Time: MODE to SCLK t

Minimum Low Time: RESET t

Delay: RESET t

PdUdVo

PdUdAo

PdDo

SuCe

SuDi

HdDi

MnHCk

MnLCk

MnLUd

SuHUd

HdHUd

SuMd

HdMd

MnLRst

PdRst

V

= 0.5V step 200 450 ns

IN

MODE = 0, time to AOUT = low after

UPDATE = low

Logic state change in DOUT on active

SCLK edge

= 0.5V, 1kΩ pulldown to AGND 300 800 ns

Output disabled, 1kΩ pulldown to AGND,

= 0.5V

V

IN

30 200 ns

30 200 ns

200 800 ns

100 ns

100 ns

100 ns

100 ns

100 ns

100 ns

Rising edge of UPDATE to falling edge of

SCLK

Falling edge of SCLK to falling edge of

UPDATE

Minimum time from clock edge to MODE

with valid data clocking

Minimum time from clock edge to MODE

with valid data clocking

100 ns

100 ns

100 ns

100 ns

300 ns

10kΩ pulldown to AGND 600 ns

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

12 ______________________________________________________________________________________

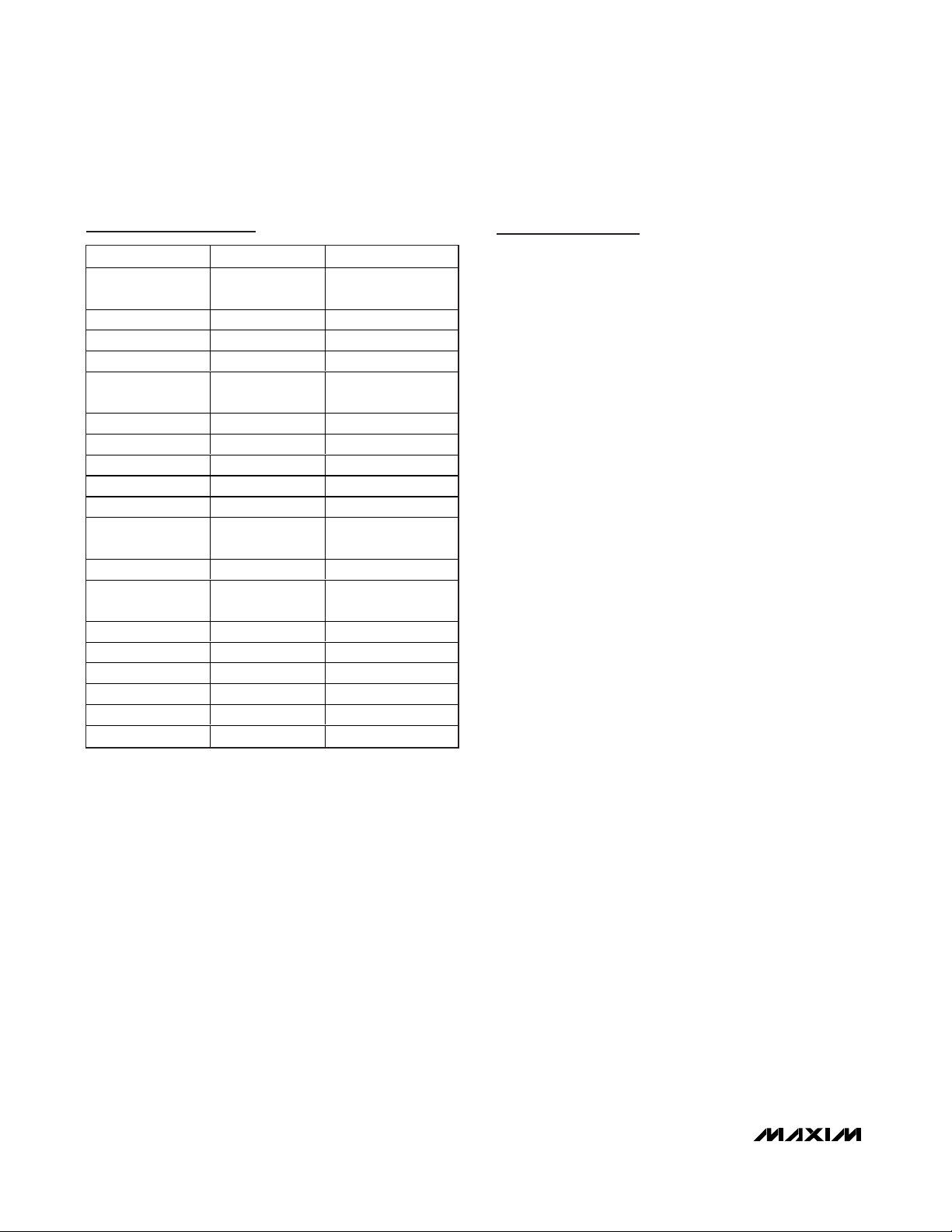

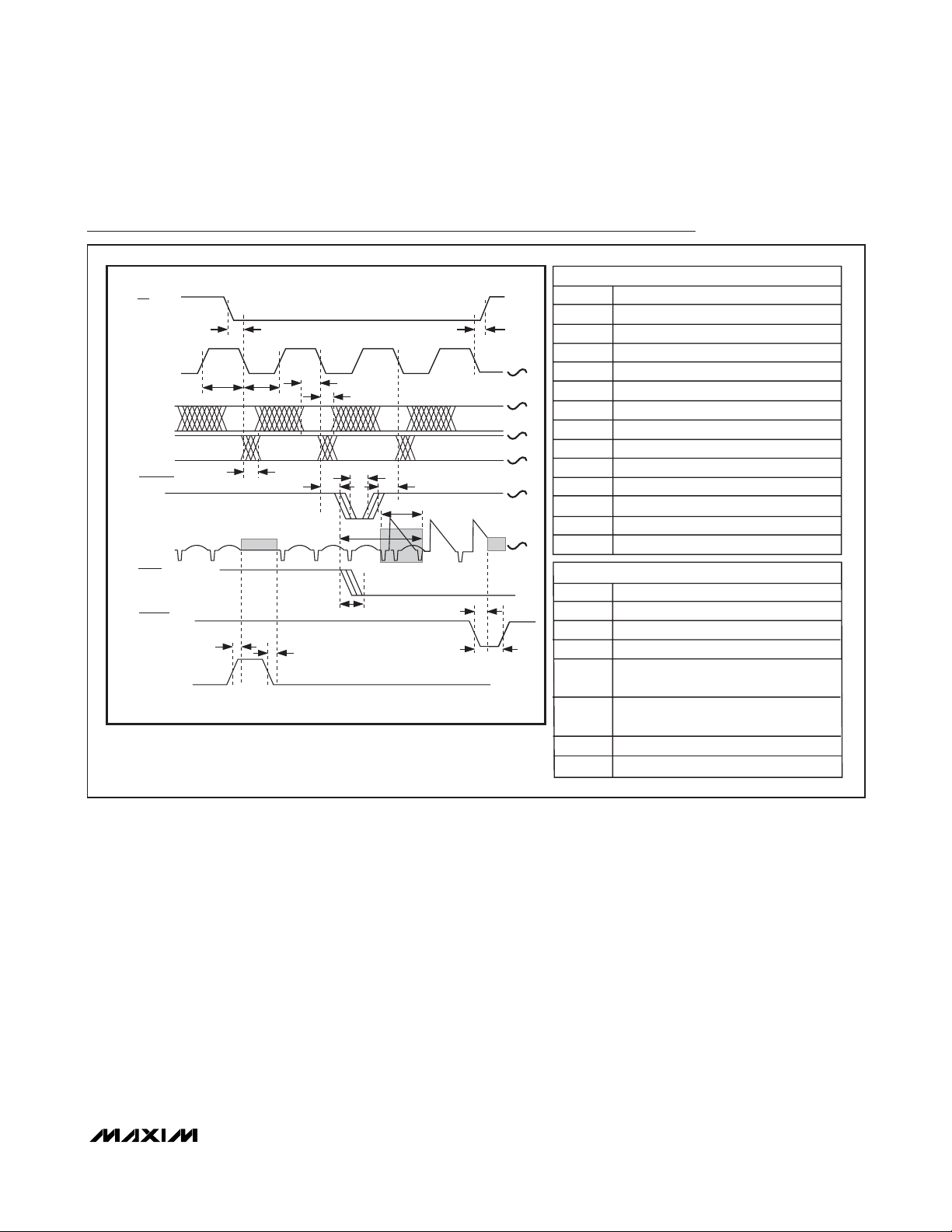

Naming Conventions

• All parameters with time units are given “t” designation, with

appropriate subscript modifiers.

• Propagation delays for clocked signals are from active edge

of clock.

• Propagation delay for level sensitive signals is from input to

output at 50% point of a transition.

• Setup and Hold times are measured from 50% point of signal transition to 50% point of clocking signal transition.

• Setup time refers to any signal that must be stable before

active clock edge, even if signal is not latched or clocked

itself.

• Hold time refers to any signal that must be stable during and

after active clock edge, even if signal is not latched or

clocked.

• Propagation delays to unobservable internal signals are

modified to setup and hold designations applied to observable I/O signals.

Symbol Definitions

SYMBOL TYPE DESCRIPTION

Ao Signal

Ce Signal Clock Enable (CE)

Ck Signal Clock (SCLK)

Di Signal Serial Data In (DIN)

Do Signal

Md Signal MODE

Oe Signal Output Enable

Rst Signal Reset Input (RESET)

Ud Signal UPDATE

Vo Signal Video Out (OUT)

H Property

Hd Property Hold

L Property

Mn Property Minimum

Mx Property Maximum

Pd Property Propagation delay

Su Property Setup

Tr Property Transition

W Property Width

Address Valid Flag

(AOUT)

Serial Data Output

(DOUT)

High or Low-to-High

Transition

Low or High-to-Low

Transition

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________ 13

Figure 1. Timing Diagram

Timing Diagram

Ce: CE

Ck: SCLK

Di: DIN

Do: DOUT

t

Ud: UPDATE

Vo: OUT_

Ao: AOUT

Rst: RESET

t

PdHOeVo

Oe: OUTPUT ENABLE

t

MnHCk

PdDo

DATA AND CONTROL TIMING

t

SuCe

t

t

MnLCk

SuDi

t

t

HdUd

Hi-Z

t

PdUdAo

t

PdLOeVo

t

HdDi

MnLUd

t

PdUdVo

t

WTrVo

t

SuUd

t

t

HdCe

PdRstVo

t

MnlRst

Hi-Z

TIMING PARAMETER DEFINITIONS

NAME DESCRIPTION

t

HdDi

t

MnHCk

t

MnLCk

t

MnLUd

t

SuHUd

Not Valid Setup Time: UPDATE to Clk with UPDATE Low

t

HdHUd

Not Valid Hold Time: Clk to UPDATE with UPDATE Low

t

PdDiDo

t

MnMd

t

MxTr

t

MnLRst

t

PdRstVo

TIMING PARAMETER DEFINITIONS

NAME DESCRIPTION

t

PdUdVo

t

PdUdAo

t

PdDo

t

PdHOeVo

t

PdLOeVo

t

SuCe

t

SuDi

Hold Time: Clock to Data In

Min High Time: Clk

Min Low Time: Clk

Min Low Time: Update

Setup Time: UPDATE to Clk with UPDATE High

Hold Time: Clk to UPDATE with UPDATE high

Asynchronous Delay: Data In to Data Out

Min Low Time: MODE

Max Rise Time: Clk, Update

Min Low Time: Reset

Delay: Reset to Video Output

Delay: Update to Video Out

Delay: UPDATE to Aout

Delay: Clk to Data Out

Delay: Output Enable to Video Output

(High: Disable)

Delay: Output Enable to Video Output

(Low: Enable)

Setup: Clock Enable to Clock

Setup Time: Data In to Clock

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

14 ______________________________________________________________________________________

Typical Operating Characteristics—Dual Supplies ±5V

(VCC= +5V and VEE= -5V, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc01

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 150Ω

AV = +1V/V

AV = +2V/V

3

-7

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc05

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 1kΩ

AV = +1V/V

AV = +2V/V

3

-7

0.1 1 10 100 1000

SMALL-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc06

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 1kΩ

AV = +2V/V

AV = +1V/V

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

(A

V

= +1V/V)

MAX4357 toc09

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

3

7

5

3

1

1

0

2

4

6

2

CL = 30pF

CL = 45pF

CL = 15pF

LARGE-SIGNAL FREQUENCY RESPONSE

3

RL = 1kΩ

2

1

0

-1

-2

-3

-4

NORMALIZED GAIN (dB)

-5

-6

-7

0.1 1 10 100 1000

AV = +1V/V

FREQUENCY (MHz)

AV = +2V/V

3

2

1

0

-1

-2

-3

-4

NORMALIZED GAIN (dB)

-5

-6

-7

MAX4357 toc04

MEDIUM-SIGNAL FREQUENCY RESPONSE

RL = 150Ω

AV = +1V/V

AV = +2V/V

0.1 1 10 100 1000

FREQUENCY (MHz)

MAX4357 toc02

NORMALIZED GAIN (dB)

SMALL-SIGNAL FREQUENCY RESPONSE

3

RL = 150Ω

2

1

0

-1

-2

-3

-4

-5

-6

-7

0.1 1 10 100 1000

AV = +2V/V

FREQUENCY (MHz)

AV = +1V/V

MAX4357 toc03

LARGE-SIGNAL GAIN FLATNESS

vs. FREQUENCY

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0.0

NORMALIZED GAIN (dB)

-0.1

-0.2

-0.3

0.1 1 10 100 1000

AV = +2V/V

FREQUENCY (MHz)

AV = +1V/V

0.3

0.2

MAX4357 toc07

0.1

0.0

-0.1

-0.2

-0.3

-0.4

NORMALIZED GAIN (dB)

-0.5

-0.6

-0.7

LARGE-SIGNAL GAIN FLATNESS

vs. FREQUENCY

RL = 1k

Ω

AV = +2V/V

0.1 1 10 100 1000

FREQUENCY (MHz)

AV = +1V/V

MAX4357 toc08

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

15

Typical Operating Characteristics—Dual Supplies ±5V (continued)

(VCC= +5V and VEE= -5V, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY RESPONSE

(A

V

= +1V/V)

MAX4357 toc11

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

9

-1

1

3

5

7

6

4

2

0

8

CL = 30pF

CL = 45pF

CL = 15pF

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY RESPONSE

(A

V

= +2V/V)

MAX4357 toc12

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

7

-3

-1

1

3

5

4

2

0

-2

6

CL = 30pF

CL = 45pF

CL = 15pF

-40

-100

0.1 10 1001 1000

MAX4357 toc13

FREQUENCY (MHz)

CROSSTALK (dB)

-90

-80

-70

-60

-50

CROSSTALK vs. FREQUENCY

AV = +1V/V

-40

-90

0.1 1 10 100 1000

CROSSTALK vs. FREQUENCY

-80

MAX4357 toc14

FREQUENCY (MHz)

CROSSTALK (dB)

-70

-60

-50

-55

-65

-75

-85

-45

AV = +2V/V

0.1 101 100 1000

DISABLED OUTPUT IMPEDANCE

vs. FREQUENCY

MAX4357 toc18

FREQUENCY (MHz)

OUTPUT IMPEDANCE (Ω)

1M

1

10

10k

1k

100

100k

LARGE-SIGNAL FREQUENCY RESPONSE

3

2

1

0

-1

-2

-3

-4

NORMALIZED GAIN (dB)

-5

-6

-7

0.1 1 10 100 1000

= +2V/V)

(A

V

CL = 30pF

CL = 15pF

FREQUENCY (MHz)

CL = 45pF

MAX4357 toc10

DISTORTION vs. FREQUENCY

0

AV = +1V/V

-10

-20

-30

-40

2ND HARMONIC

-50

-60

DISTORTION (dBc)

-70

-80

-90

-100

0.1 1 10 100 1000

3ND HARMONIC

FREQUENCY (MHz)

MAX4357 toc15

DISTORTION vs. FREQUENCY

0

AV = +2V/V

-10

-20

-30

2ND HARMONIC

-40

-50

-60

DISTORTION (dBc)

-70

-80

-90

-100

0.1 1 10 100 1000

ENABLED OUTPUT IMPEDANCE

vs. FREQUENCY

1000

3RD HARMONIC

FREQUENCY (MHz)

MAX4357 toc16

100

10

OUTPUT IMPEDANCE (Ω)

1

0.1

0.1 101 100 1000

FREQUENCY (MHz)

MAX4357 toc17

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

16 ______________________________________________________________________________________

Typical Operating Characteristics—Dual Supplies ±5V (continued)

(VCC= +5V and VEE= -5V, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

10k 1M100k 10M 100M

POWER-SUPPLY REJECTION RATIO

vs. FREQUENCY

MAX4357 toc20

FREQUENCY (Hz)

PSRR (dB)

-75

-70

-60

-65

-55

-50

1000

10

10 10k 100k 1M100 1k 10M

INPUT VOLTAGE NOISE vs. FREQUENCY

100

FREQUENCY (Hz)

VOLTAGE NOISE (nV√Hz)

MAX4357 toc21

SWITCHING TIME

(A

V

= +1V/V)

MAX4357 toc26

20ns/div

V

UPDATE

5V/div

V

OUT

500mV/div

SWITCHING TIME

(A

V

= +2V/V)

MAX4357 toc27

20ns/div

V

UPDATE

5V/div

V

OUT

1V/div

OFF-ISOLATION vs. FREQUENCY

-40

-50

-60

-70

-80

-90

OFF ISOLATION (dB)

-100

-110

-120

100k 10M 100M1M 1G

FREQUENCY (Hz)

MAX4357 toc19

LARGE-SIGNAL PULSE RESPONSE

INPUT

1V/div

OUTPUT

1V/div

MEDIUM-SIGNAL PULSE RESPONSE

INPUT

50mV/div

OUTPUT

100mV/div

(A

(A

V

20ns/div

V

= +1V/V)

= +2V/V)

MAX4357 toc22

MAX4357 toc25

INPUT

500mV/div

OUTPUT

1V/div

LARGE-SIGNAL PULSE RESPONSE

= +2V/V)

(A

V

20ns/div

MAX4357 toc23

INPUT

100mV/div

OUTPUT

100mV/div

MEDIUM-SIGNAL PULSE RESPONSE

= +1V/V)

(A

V

20ns/div

MAX4357 toc24

20ns/div

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

17

Typical Operating Characteristics—Dual Supplies ±5V (continued)

(VCC= +5V and VEE= -5V, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

SWITCHING TRANSIENT (GLITCH)

(A

V

= +1V/V)

MAX4357 toc28

20ns/div

V

UPDATE

5V/div

V

OUT

25mV/div

SWITCHING TRANSIENT (GLITCH)

(A

V

= +2V/V)

MAX4357 toc29

20ns/div

V

UPDATE

5V/div

V

OUT

25mV/div

0

100

50

200

150

250

300

-14 -10 -8 -6-12 -4 -2 0 2 4 6

OFFSET VOLTAGE DISTRIBUTION

MAX4357 toc30

OFFSET VOLTAGE (mV)

-0.05

01020304050607080 90100

01020304050607080 90100

DIFFERENTIAL GAIN AND PHASE vs.

DC VOLTAGE (R

L

= 150Ω)

0.00

0.00

-0.02

0.05

0.02

0.04

0.10

0.06

0.08

0.15

IRE

DIFF PHASE (°)

DIFF GAIN (%)

MAX4357 toc31

0.01

0.00

-0.01

01020304050607080 90100

01020304050607080 90100

DIFFERENTIAL GAIN AND PHASE vs.

DC VOLTAGE (R

L

= 1kΩ)

0.02

-0.005

0.03

0.000

0.005

0.04

0.010

0.015

0.05

IRE

DIFF PHASE (°)

DIFF GAIN (%)

MAX4357 toc32

LARGE-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

INPUT

1V/div

= 30pF, AV = +1V/V)

L

MAX4357 toc33

LARGE-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

INPUT

500mV/div

OUTPUT

1V/div

OUTPUT

1V/div

20ns/div

= 30pF, AV = +2V/V)

L

20ns/div

MAX4357 toc34

MEDIUM-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

INPUT

100mV/div

OUTPUT

100mV/div

20ns/div

= 30pF, AV = +1V/V)

L

MAX4357 toc35

MEDIUM-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

INPUT

50mV/div

OUTPUT

100mV/div

20ns/div

= 30pF, AV = +2V/V)

L

MAX4357 toc36

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

18 ______________________________________________________________________________________

Typical Operating Characteristics—Dual Supplies ±5V (continued)

(VCC= +5V and VEE= -5V, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

-0.20

-0.15

-0.10

-0.05

0

0.05

0.10

0.15

0.20

-50 0-25 255075100

GAIN vs. TEMPERATURE

MAX4357 toc37

TEMPERATURE (°C)

NORMALIZED GAIN (dB)

AV = +2V/V

AV = +1V/V

RESET DELAY vs. RESET CAPACITANCE

10

1

100m

10m

1m

100

μ

10

μ

RESET DELAY (s)

1

μ

100n

10n

100p10p 1n 100n 10μ100

1p 10n 1μ

C

(F)

RESET

70

60

MAX4357 toc38

50

40

30

SUPPLY CURRENT (mA)

20

10

μ

SUPPLY CURRENT vs. TEMPERATURE

I

CC

I

EE

I

DD

0

-50 0 25-25 50 75 100

TEMPERATURE (°C)

MAX4357 toc39

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

19

Typical Operating Characteristics—Dual Supplies ±3V

(VCC= +3V and VEE= -3V, VDD= +3V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc40

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

-0

-2

-4

-6

2

AV = +2V/V

RL = 150

Ω

AV = +1V/V

3

-7

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc41

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

-0

-2

-4

-6

2

AV = +2V/V

RL = 150

Ω

AV = +1V/V

3

-7

0.1 1 10 100 1000

SMALL-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc42

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

-0

-2

-4

-6

2

AV = +2V/V

RL = 150

Ω

AV = +1V/V

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

-5

MAX4357 toc43

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

-0

-2

-4

-6

2

AV = +1V/V

RL = 1k

Ω

AV = +2V/V

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

(A

V

= +1V/V)

-5

MAX4357 toc48

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

CL = 15pF

CL = 30pF

CL = 45pF

MEDIUM-SIGNAL FREQUENCY RESPONSE

3

RL = 1k

2

1

-0

-1

-2

-3

-4

NORMALIZED GAIN (dB)

-5

-6

-7

Ω

AV = +1V/V

0.1 1 10 100 1000

SMALL-SIGNAL FREQUENCY RESPONSE

3

RL = 1k

Ω

AV = +2V/V

0.1 1 10 100 1000

FREQUENCY (MHz)

AV = +2V/V

FREQUENCY (MHz)

2

MAX4357 toc44

1

-0

-1

-2

-3

-4

NORMALIZED GAIN (dB)

-5

-6

-7

AV = +1V/V

MAX4357 toc45

LARGE-SIGNAL GAIN FLATNESS

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

NORMALIZED GAIN (dB)

0.1

-0.1

AV = +2V/V

0

0.1 1 10 100 1000

vs. FREQUENCY

FREQUENCY (MHz)

AV = +1V/V

0.6

0.5

MAX4357 toc46

0.4

0.3

0.2

0.1

0.0

-0.1

NORMALIZED GAIN (dB)

-0.2

-0.3

-0.4

0.1 1 10 100 1000

RL = 1k

vs. FREQUENCY

Ω

AV = +2V/V

FREQUENCY (MHz)

AV = +1V/V

MAX4357 toc47

LARGE-SIGNAL GAIN FLATNESS

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

20 ______________________________________________________________________________________

Typical Operating Characteristics—Dual Supplies ±3V (continued)

(VCC= +3V and VEE= -3V, VDD= +3V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

0.1 101 100 1000

ENABLED OUTPUT IMPEDANCE

VS. FREQUENCY

MAX4357 toc56

FREQUENCY (MHz)

OUTPUT IMPEDANCE (Ω)

1000

0.1

1

10

100

1M

1

0.1 10 1001 1000

DISABLED OUTPUT IMPEDANCE

VS. FREQUENCY

MAX4357 toc57

FREQUENCY (MHz)

OUTPUT IMPEDANCE (Ω)

10

100

1k

10k

100k

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

(A

V

= +2V/V)

-5

MAX4357 toc49

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

-0

-2

-4

-6

2

CL = 30pF

CL = 15pF

CL = 45pF

-40

-90

100k 1M 10M 100M 1G

CROSSTALK VS. FREQUENCY

-80

MAX4357 toc52

FREQUENCY (Hz)

CROSSTALK (dB)

-70

-60

-50

-55

-65

-75

-85

-45

AV = + 1V/V

MEDIUM-SIGNAL FREQUENCY RESPONSE

9

8

7

6

5

4

3

2

NORMALIZED GAIN (dB)

1

0

1

0.1 1 10 100 1000

CL = 30pF

CL = 15pF

MEDIUM-SIGNAL FREQUENCY RESPONSE

= +1V/V)

(A

V

FREQUENCY (MHz)

CL = 45pF

7

6

MAX4357 toc50

5

4

3

2

1

0

NORMALIZED GAIN (dB)

-1

-2

-3

CL = 30pF

0.1 1 10 100 1000

= +2V/V)

(A

V

CL = 45pF

CL = 15pF

FREQUENCY (MHz)

MAX4357 toc51

DISTORTION VS. FREQUENCY

AV = + 2V/V

-10

-20

-30

-40

-50

-60

DISTORTION (dB)

-70

-80

-90

-100

100k 100M10M1M

2ND HARMONIC

FREQUENCY (Hz)

3RD HARMONIC

CROSSTALK (dB)

MAX4357 toc55

CROSSTALK VS. FREQUENCY

-30

AV = + 2V/V

-35

-40

-45

-50

-55

-60

-65

-70

-75

-80

100k 1M 10M 100M 1G

FREQUENCY (Hz)

MAX4357 toc53

DISTORTION (dB)

-100

AV = + 1V/V

-10

-20

-30

-40

-50

-60

-70

-80

-90

100k 100M10M1M

DISTORTION VS. FREQUENCY

MAX4357 toc54

2ND HARMONIC

3RD HARMONIC

FREQUENCY (Hz)

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

21

Typical Operating Characteristics—Dual Supplies ±3V (continued)

(VCC= +3V and VEE= -3V, VDD= +3V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

-40

-50

-60

-70

-80

-90

-100

-110

-120

100k 10M 100M1M 1G

OFF-ISOLATION VS. FREQUENCY

MAX4357 toc58

FREQUENCY (Hz)

OFF ISOLATION (dB)

10k 1M100k 10M 100M

POWER-SUPPLY

REJECTION RATIO vs. FREQUENCY

MAX4357 toc59

FREQUENCY (Hz)

PSRR (dB)

-50

-75

-70

-60

-65

-55

1000

10

10 10k 100k 1M100 1k 10M

INPUT VOLTAGE NOISE vs. FREQUENCY

100

MAX4357 toc60

FREQUENCY(Hz)

VOLTAGE NOISE (nV/

√

Hz)

LARGE-SIGNAL PULSE RESPONSE

(A

V

= +1V/V)

MAX4357 toc61

INPUT

1V/div

OUTPUT

1V/div

20ns/div

LARGE-SIGNAL PULSE RESPONSE

(A

V

= +2V/V)

MAX4357 toc62

INPUT

500mV/div

OUTPUT

1V/div

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE

(A

V

= +1V/V)

MAX4357 toc63

INPUT

100mV/div

OUTPUT

100mV/div

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE

(A

V

= +2V/V)

MAX4357 toc64

INPUT

50mV/div

OUTPUT

100mV/div

20ns/div

SWITCHING TIME

(A

V

= +1V/V)

MAX4357 toc65

V

OUT

500mV/div

20ns/div

V

UPDATE

3V/div

SWITCHING TIME

(A

V

= +2V/V)

MAX4357 toc66

V

OUT

1V/div

20ns/div

V

UPDATE

3V/div

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

22 ______________________________________________________________________________________

Typical Operating Characteristics—Dual Supplies ±3V (continued)

(VCC= +3V and VEE= -3V, VDD= +3V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

0.05

-0.05

0.15

10 30 40 5020 60 70 80 90 100

DIFFERENTIAL GAIN AND PHASE

(R

L

= 1kΩ)

MAX4357 toc71

IRE

DIFFERENTIAL

GAIN (%)

DIFFERENTIAL

PHASE (

°

)

0.05

-0.05

0.15

0.25

20ns/div

LARGE-SIGNAL PULSE RESPONSE

WITH CAPACITIVE LOAD

(C

L

= 30pF, AV = +1V/V)

INPUT

1V/div

OUTPUT

1V/div

MAX4357 toc72

20ns/div

LARGE-SIGNAL PULSE RESPONSE

WITH CAPACITIVE LOAD

(C

L

= 30pF, AV = +2V/V)

INPUT

500mV/div

OUTPUT

1V/div

MAX4357 toc73

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE

WITH CAPACITIVE LOAD

(C

L

= 30pF, AV = +1V/V)

INPUT

100mV/div

OUTPUT

100mV/div

MAX4357 toc74

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE

WITH CAPACITIVE LOAD

(C

L

= 30pF, AV = +2V/V)

INPUT

50mV/div

OUTPUT

100mV/div

MAX4357 toc75

50

0

150

100

250

200

300

-15 -11 -9 -7-13 -5 -3 -1 1 3 5

OFFSET VOLTAGE DISTRIBUTION

MAX4357 toc69

OFFSET VOLTAGE (mV)

20ns/div

SWITCHING TRANSIENT GLITCH

(A

V

= +1V/V)

V

UPDATE

3V/div

V

OUT

25mV/div

MAX4357 toc67

20ns/div

SWITCHING TRANSIENT GLITCH

(A

V

= +2V/V)

V

UPDATE

3V/div

V

OUT

25mV/div

MAX4357 toc68

0.05

-0.05

0.15

0.25

10 30 40 5020 60 70 80 90 100

DIFFERENTIAL GAIN AND PHASE

(R

L

= 150Ω)

MAX4357 toc70

IRE

DIFFERENTIAL

GAIN (%)

DIFFERENTIAL

PHASE (°)

0.05

-0.05

0.15

0.25

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

23

Typical Operating Characteristics—Dual Supplies ±3V (continued)

(VCC= +3V and VEE= -3V, VDD= +3V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

-50 0-25 255075100

GAIN VS. TEMPERATURE

MAX4357 toc76

TEMPERATURE (°C)

NORMALIZED GAIN (dB)

-0.20

-0.15

-0.05

-0.10

0.10

0.15

0.05

0.20

0

AV = +2V/V

AV = +1V/V

1p 10n 1

μ

100p10p 1n 100n 10μ100

μ

MAX4357 toc77

10n

10

μ

1

μ

100n

100

μ

1m

10m

100m

10

1

RESET DELAY (s)

C

RESET

(F)

RESET DELAY

vs. RESET CAPACITANCE

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

24 ______________________________________________________________________________________

Typical Operating Characteristics—Single Supply +5V

(VCC= +5V and VEE= 0, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

3

-7

0.1 1 10 100 1000

SMALL-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc83

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 1k

Ω

0.9

-0.1

0.1 1 10 100 1000

LARGE-SIGNAL GAIN FLATNESS

vs. FREQUENCY

0.1

MAX4357 toc84

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

0.3

0.5

0.7

0.6

0.4

0.2

0.0

0.8

0.6

-0.4

0.1 1 10 100 1000

LARGE-SIGNAL GAIN FLATNESS

vs. FREQUENCY

-0.2

MAX4357 toc85

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

0

0.2

0.4

0.3

0.1

-0.1

-0.3

0.5

RL = 1k

Ω

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY RESPONSE

(A

V

= +1V/V)

-5

MAX4357 toc86

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

CL = 30pF

CL = 15pF

CL = 45pF

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc78

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 150

Ω

3

-7

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc79

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 150

Ω

3

-7

0.1 1 10 100 1000

SMALL-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc80

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 150

Ω

3

-7

0.1 1 10 100 1000

LARGE-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc81

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 1k

Ω

3

-7

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY

RESPONSE

-5

MAX4357 toc82

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

-3

-1

1

0

-2

-4

-6

2

RL = 1k

Ω

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

25

Typical Operating Characteristics—Single Supply +5V (continued)

(VCC= +5V and VEE= 0, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

9

-1

0.1 1 10 100 1000

MEDIUM-SIGNAL FREQUENCY RESPONSE

(A

V

= +1V/V)

1

MAX4357 toc87

FREQUENCY (MHz)

NORMALIZED GAIN (dB)

3

5

7

6

4

2

0

8

CL = 30pF

CL = 45pF

CL = 15pF

-50

-100

100k 1M 10M 100M 1G

CROSSTALK vs. FREQUENCY

-90

MAX4357 toc88

FREQUENCY (Hz)

CROSSTALK (dB)

-80

-70

-60

-65

-75

-85

-95

-55

-10

-100

100k 100M10M1M

DISTORTION vs. FREQUENCY

-70

-90

-30

-50

0

-60

-80

-20

-40

MAX4357 toc89

FREQUENCY (Hz)

DISTORTION (dBc)

2nd HARMONIC

3rd HARMONIC

0.1 101 100 1000

ENABLED OUTPUT IMPEDANCE

vs. FREQUENCY

MAX4357 toc90

FREQUENCY (MHz)

OUTPUT IMPEDANCE (Ω)

1000

0.1

1

10

100

1M

1

0.1 10 1001 1000

DISABLED OUTPUT IMPEDANCE

vs. FREQUENCY

MAX4357 toc91

FREQUENCY (MHz)

OUTPUT IMPEDANCE (

Ω

)

10

100

1k

10k

100k

-40

-50

-60

-70

-80

-90

-100

-110

-120

100k 10M 100M1M 1G

OFF-ISOLATION vs. FREQUENCY

MAX4357 toc92

FREQUENCY (Hz)

OFF ISOLATION (dB)

10k 1M100k 10M 100M

POWER-SUPPLY

REJECTION RATIO vs. FREQUENCY

MAX4357 toc93

FREQUENCY (Hz)

PSRR (dB)

-50

-75

-70

-60

-65

-55

1000

10

10 10k 100k 1M100 1k 10M

INPUT VOLTAGE NOISE

vs. FREQUENCY

100

MAX4357 toc94

FREQUENCY (Hz)

VOLTAGE NOISE (NV/

√

Hz)

20ns/div

LARGE-SIGNAL PULSE RESPONSE

INPUT

1V/div

OUTPUT

1V/div

MAX4357 toc95

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

26 ______________________________________________________________________________________

Typical Operating Characteristics—Single Supply +5V (continued)

(VCC= +5V and VEE= 0, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE

INPUT

100mV/div

OUTPUT

100mV/div

MAX4357 toc96

20ns/div

SWITCHING TIME

V

UPDATE

5V/div

V

OUT

500mV/div

MAX4357 toc97

20ns/div

SWITCHING TRANSIENT (GLITCH)

V

UPDATE

5V/div

V

OUT

25mV/div

MAX4357 toc98

0

50

150

100

200

250

-20

-16

-18

-14-8-10-12 -6 -4

-2

0

OFFSET VOLTAGE HISTOGRAM

MAX4357 toc99

OFFSET VOLTAGE (mV)

IRE

DIFFERENTIAL GAIN AND PHASE

(R

L

= 150Ω)

DIFFERENTIAL

GAIN (%)

DIFFERENTIAL

PHASE (%)

MAX4357 toc100

0.25

0.20

0.15

0.10

0.05

0

-0.05

0.30

0.25

0.20

0.15

0.10

0

-0.05

-0.10

10

20

30 40 50 60

70

80 90

100

10

0

20

30 40 50 60

70

80 90

100

IRE

DIFFERENTIAL GAIN AND PHASE

(R

L

= 1kΩ)

DIFFERENTIAL

GAIN (%)

DIFFERENTIAL

PHASE (%)

MAX4357 toc101

0.04

0.03

0.02

0.01

0

-0.01

0.10

0.08

0.06

0.04

0.02

0

-0.02

10

20

30 40 50 60

70

80 90

100

10

0

20

30 40 50 60

70

80 90

100

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________

27

Typical Operating Characteristics—Single Supply +5V (continued)

(VCC= +5V and VEE= 0, VDD= +5V, AGND = DGND = 0, V

IN_

= 0, RL= 150Ω to AGND, AV= +1V/V, and TA = +25°C, unless

otherwise noted.)

1p 10n 1μ100p10p 1n 100n 10μ 100μ

RESET DELAY

vs. RESET CAPACITANCE

MAX4357 toc105

C

RESET

(F)

RESET DELAY (s)

10n

100m

1

10

100

10m

1m

100μ

10μ

1μ

100n

-0.20

-0.15

-0.10

-0.05

0

0.05

0.10

0.15

0.20

-50 0-25 255075100

GAIN vs. TEMPERATURE

MAX4357 toc104

TEMPERATURE (°C)

NORMALIZED GAIN (dB)

20ns/div

MEDIUM-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

L

= 30pF)

INPUT

100mV/div

OUTPUT

100mV/div

MAX4357 toc103

20ns/div

LARGE-SIGNAL PULSE RESPONSE WITH

CAPACITIVE LOAD (C

L

= 30pF)

INPUT

1V/div

INPUT

1V/div

MAX4357 toc102

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

28 ______________________________________________________________________________________

Pin Description

PIN NAME FUNCTION

1, 69, 73, 77, 81,

85, 89, 93, 97

2, 4, 6, 8, 10, 12, 14, 16, 18,

20, 22, 24, 26, 28, 30, 32,

34, 36, 38, 40, 42, 44, 65,

66, 100, 102, 103, 104, 106,

108, 110, 112, 114, 116, 118,

120, 122, 124, 126, 128

3, 5, 7, 9, 11, 13, 15, 17, 19,

21, 23, 25, 27, 29, 31, 33,

37, 39, 41, 43, 105, 107,

109, 111, 113, 115, 117,

119, 121, 123, 125, 127

35, 67, 71, 75, 79, 83,

87, 91, 95, 99

45 DGND Digital Ground

46 AOUT

47–50 A3–A0

51 DOUT

52 SCLK Serial Clock Input

53 CE Clock Enable Input. Drive low to enable the serial data interface.

54 MODE

V

EE

AGND Analog Ground

IN0–IN31 Buffered Analog Inputs

V

CC

Negative Analog Supply. Bypass each pin with a 0.1µF capacitor to AGND.

Connect a single 10µF capacitor from one V

Positive Analog Supply. Bypass each pin with a 0.1µF capacitor to AGND.

Connect a single 10µF capacitor from one V

Address Recognition Output. AOUT drives low after successful chip address

recognition.

Address Programming Inputs. Connect to DGND or V

Individual Output Address Mode (Table 3).

Serial Data Output. In Complete Matrix Mode, data is clocked through the 112-bit

Matrix Control Shift register. In Individual Output Address Mode, data at DIN

passes directly to DOUT.

S er i al Inter face M od e S el ect Inp ut. D r i ve hi g h for C om p l ete M atr i x M od e ( M od e 1) ,

or drive low for Individual Output Address Mode (Mode 0).

pin to AGND.

EE

pin to AGND.

CC

DD

to select the address for

Asynchronous Reset Input/Output. Drive RESET low to initiate hardware reset. All

55 RESET

56 UPDATE

57 DIN Serial Data Input. Data is clocked in on the falling edge of SCLK.

58–63, 101 N.C. No Connection. Not internally connected. Connect to AGND.

64 V

68, 70, 72, 74, 76, 78, 80,

82, 84, 86, 88, 90, 92, 94,

96, 98

DD

OUT0–OUT15

matrix settings are set to power-up defaults and all analog outputs are disabled.

Additional power-on reset delay may be set by connecting a small capacitor from

RESET to DGND.

Update Input. Drive UPDATE low to transfer data from mode registers to the

matrix switch.

Digital Logic Supply. Bypass VDD with a 0.1µF capacitor DGND.

Buffered Analog Outputs. Gain is individually programmable for AV = +1V/V or

AV = +2V/V through the serial interface. Outputs may be individually disabled

(high impedance). On power-up, or assertion of RESET, all outputs are disabled.

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________ 29

Detailed Description

The MAX4357 is a highly integrated 32 16 nonblocking video crosspoint switch matrix. All inputs and outputs are buffered, with all outputs able to drive

standard 75Ω reverse-terminated video loads.

A 3-wire interface programs the switch matrix and initializes with a single update signal. The unique serial

interface operates in one of two modes, Complete

Matrix Mode (Mode 1) or Individual Output Address

Mode (Mode 0).

The signal path of the MAX4357 is from the buffered

inputs (IN0–IN31), through the switching matrix,

buffered by the output amplifiers, and presented at the

outputs (OUT0–OUT15) (

Functional Diagram

). The

other functional blocks are the serial interface and control logic. Each of the functional blocks is described in

detail in the sections following.

Analog Outputs

The MAX4357 outputs are high-speed amplifiers capable of driving 150Ω (75Ω back-terminated) loads. The

gain, AV= +1V/V or +2V/V, is selectable through programming bit 5 of the serial control word. Amplifier compensation is automatically optimized to maximize the

bandwidth for each gain selection. Each output can be

individually enabled and disabled via bit 6 of the serial

control word. When disabled, the output is high impedance presenting typically 4kΩ load, and 3pF output

capacitance, allowing multiple outputs to be connected

together for building large arrays. On power-up (or asynchronous RESET) all outputs are initialized in the disabled state to avoid output conflicts in large array

configurations. The programming and operation of the

MAX4357 is output referred. Outputs are configured individually to connect to any one of the 32 analog inputs,

programmed to the desired gain (AV= +1V/V or +2V/V),

and enabled or disabled in a high-impedance state.

Functional Diagram

RESET

SCLK

UPDATE

IN0

IN1

IN2

IN31

DIN

MAX4357

AV*

A

*

32 x 16

SWITCH MATRIX

POWER-ON

RESET

SERIAL

CE

INTERFACE

THERMAL

SHUTDOWN

DISABLE ALL OUTPUTS

DECODE LOGIC

MATRIX REGISTER

UPDATE REGISTER

512

LATCHES

112 BITS

16 BITS

16

V

*

A

V

AV*

16

ENABLE/DISABLE

OUT0

OUT1

OUT2

OUT15

V

CC

V

EE

AGND

V

DD

DGND

DOUT

AOUT

A0-A3 MODE

*A

= +1V/V OR +2V/V

V

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

30 ______________________________________________________________________________________

Table 1. Operation Truth Table

Analog Inputs

The MAX4357 offers 32 analog input channels. Each

input is buffered before the crosspoint matrix switch,

allowing one input to cross-connect up to 16 outputs.

The input buffers are voltage feedback amplifiers with

high-input impedance and low-input bias current. This

allows the use of very simple input clamp circuits.

Switch Matrix

The MAX4357 has 512 individual T-switches making a

32 16 switch matrix. The switching matrix is 100%

nonblocking, which means that any input may be routed to any output. The switch matrix programming is

output referred. Each output may be connected to any

one of the 32 analog inputs. Any one input can be routed to all 16 outputs with no signal degradation.

Digital Interface

The digital interface consists of the following pins: DIN,

DOUT, SCLK, AOUT, UPDATE, CE, A3–A0, MODE, and

RESET. DIN is the serial-data input, DOUT is the serialdata output.

SCLK is the serial-data clock which clocks data into the

data input registers (Figure 3). Data at DIN is loaded in

at each falling edge of SCLK. DOUT is the data shifted

out of the 112-bit Complete Matrix Mode register (Mode

= 1). DIN passes directly to DOUT when in Individual

Output Address Mode (Mode = 0).

The falling edge of UPDATE latches the data and programs the matrix. When using Individual Output

Address Mode, the address recognition output AOUT

drives low when control-word bits D14 to D11 match

the address programming inputs (A3–A0) and UPDATE

is low (Table 1). Table 1 is the operation truth table.

Programming the Matrix

The MAX4357 offers two programming modes:

Individual Output Address Mode and Complete Matrix

Mode. These two distinct programming modes are

selected by toggling a single MODE pin high or low.

Both modes operate with the same physical board layout. This flexibility allows initial programming of the IC

by daisy-chaining and sending one long data word

while still being able to immediately address and

update individual outputs in the matrix.

Note: "X" = Don’t Care

CE UPDATE SCLK DIN DOUT MODE AOUT RESET OPERATION/COMMENTS

1 X X X X X X 1 No change in logic.

Data at DIN is clocked on negative edge of

01

00 XXX111

01

00 X

↓

↓

D

D

D

D

i

i

i

i-112

D

i

D

i

111

011

001

SCLK into 112-bit Complete Matrix Mode

register. DOUT supplies original data in

112 SCLK pulses later.

Data in serial 112-bit Complete Matrix

Mode register is transferred into parallel

latches, which control the switching matrix.

Data at DIN is routed to Individual Output

Address Mode shift register. DIN is also

connected directly to DOUT so that all

devices on the serial bus may be

addressed in parallel.

4-bit chip address A3–A0 is compared to

D14–D11. If equal, remaining 11 bits in

Individual Output Address Mode register

are decoded, allowing reprogramming for

a single output. AOUT signals successful

individual matrix update.

XX XXXXX0

Asynchronous reset. All outputs are

disabled. Other logic remains unchanged.

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

______________________________________________________________________________________ 31

Individual Output Address Mode (MODE = 0)

Drive MODE to logic low to select Mode 0. Individual

outputs are programmed via the serial interface with a

single 16-bit control word. The control word consists of

a don’t care MSB, the chip address bits, output

address bits, an output enable/disable bit, an output

gain-set bit, and input address bits (Table 2 through

Table 6, and Figure 2).

In Mode 0, data at DIN passes directly to DOUT

through the data routing gate (Figure 3). In this configuration, the 16-bit control word is simultaneously sent to

all chips in an array of up to 16 addresses.

Complete Matrix Mode (MODE = 1)

Drive MODE to logic high to select Mode 1. A single

112-bit control word, consisting of sixteen 7-bit control

words, programs all outputs. The 112-bit control word’s

first 7-bit control word (MSBs) programs output 15, and

the last 7-bit control word (LSBs) programs output 0

(Table 7 and Figures 4 and 5). Data clocked into the

112-bit Complete Matrix Mode register is latched on the

falling edge of UPDATE, and the outputs are immediately updated.

Initialization String

Complete Matrix Mode (Mode = 1) is convenient for

programming the matrix at power-up. In a large matrix

consisting of many MAX4357s, all the devices can be

programmed by sending a single bit stream equal to n

x 112 bits where n is the number of MAX4357 devices

on the bus. The first 112-bit data word programs the

last MAX4357 in line (see

Matrix Programming

section).

RESET

The MAX4357 features an asynchronous bidirectional

RESET with an internal 20kΩ pullup resistor to VDD.

When RESET is pulled low either by internal circuitry, or

Figure 2. Serial Interface Block Diagram

4

SCLK

MODE

CE

A0–A3

CHIP ADDRESS

4

SCLK

CE

MODE

DIN

16-BIT INDIVIDUAL OUTPUT

ADDRESS MODE REGISTER

11

112-BIT COMPLETE MATRIX MODE REGISTER

11

OUTPUT ADDRESS DECODE

UPDATE

EN

SWITCH MATRIX

112-BIT PARALLEL LATCH

512 16

7

SWITCH DECODE

7

112

MODE

OUTPUT ENABLE

MODE

S

A

DATA

ROUTING

GATE

B

MODE

112

112

1

AOUT

DOUT

MAX4357

32 x 16 Nonblocking Video Crosspoint Switch

with I/O Buffers

32 ______________________________________________________________________________________

driven externally, the analog output buffers are latched

into a high-impedance state. After RESET is released,

the output buffers remain disabled. The outputs may be

enabled by sending a new 112-bit data word or a 16-bit

individual output address word. A reset is initiated from

any of three sources. RESET can be driven low by

external circuitry to initiate a reset, or RESET can be

pulled low by internal circuitry during power-up (poweron reset) or thermal shutdown.

Since driving RESET low only clears the output-bufferenable bit in the matrix control latches, RESET can be

used to disable all outputs simultaneously. If no new

data has been loaded into the 112-bit Complete Matrix

Mode register, a single UPDATE restores the previous

matrix control settings.

Power-On Reset

The power-on reset ensures all output buffers are in a

disabled state when power is initially applied. A V

DD

voltage comparator generates the power-on reset.

When the voltage at VDDis less than 2.5V, the poweron-reset comparator pulls RESET low via internal circuitry. As the digital-supply voltage ramps up crossing

2.5V, the MAX4357 holds RESET low for 40ns (typ).

Connecting a small capacitor from RESET to DGND

extends the power-on-reset delay. (see the RESET

Delay vs. RESET Capacitance graph in the

Typical

Operating Characteristics)

.

Thermal Shutdown

The MAX4357 features thermal shutdown protection

with temperature hysteresis. When the die temperature

exceeds 150°C, the MAX4357 pulls RESET low, disabling the output buffer. When the die cools by 20°C,

the RESET pulldown is deasserted, and output buffers

remain disabled until the device is programmed again.

Applications Information

Building Large Video-Switching Systems

The MAX4357 can be easily used to create larger

switching matrices. The number of ICs required to

implement the matrix is a function of the number of

input channels, the number of outputs required, and

whether the array needs to be nonblocking.

The most straightforward technique for implementing

nonblocking matrices is to arrange the building blocks

in a grid. The inputs connect to each vertical bank of

devices in parallel with the other banks. The outputs of

each building block in a vertical column connect

together in a wired-OR configuration. Figure 6 shows a

128-input, 32-output, nonblocking array using eight

MAX4357 crosspoint devices.

Table 2. 16-Bit Serial Control Word Bit Assignments (Mode 0: Individual Output

Address Mode)

BIT NAME FUNCTION

15 (MSB) X Don’t care

14 IC Address A3 MSB of selected chip address

13 IC Address A2 MSB of selected chip address

12 IC Address A1 MSB of selected chip address

11 IC Address A0 LSB of selected chip address

10 Output Address B3 MSB of output buffer address

9 Output Address B2 MSB of output buffer address

8 Output Address B1 MSB of output buffer address

7 Output Address B0 LSB of output buffer address

6 Output Enable Enable bit for output, 0 = disable, 1 = enable