For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

General Description

The MAX1459 highly integrated analog-sensor signal

conditioner is optimized for piezoresistive sensor calibration and compensation with minimal external components. It includes a programmable current source for

sensor excitation, a 3-bit programmable-gain amplifier

(PGA), a 128-bit internal EEPROM, and four 12-bit DACs.

Achieving a total error factor within 1% of the sensor’s

repeatability errors, the MAX1459 compensates offset,

offset temperature coefficient (offset TC), full-span output

(FSO), FSO temperature coefficient (FSOTC), and FSO

nonlinearity of silicon piezoresistive sensors.

The MAX1459 calibrates and compensates first-order

temperature errors by adjusting the offset and span of

the input signal through digital-to-analog converters

(DACs), thereby eliminating quantization noise.

The MAX1459 allows temperature compensation via the

external sensor, an internal temperature-dependent

resistor, or a dedicated external temperature transducer. Accuracies better than 0.5% can be achieved with

low-cost external temperature sensors (i.e., silicon transistor), depending on sensor choice.

Built-in testability features on the MAX1459 result in the

integration of three traditional sensor-manufacturing

operations into one automated process:

• Pretest: Data acquisition of sensor performance

under the control of a host test computer.

• Calibration and compensation: Computation and

storage (in an internal EEPROM) of calibration and

compensation coefficients computed by the test

computer and downloaded to the MAX1459.

• Final test operation: Verification of transducer cali-

bration and compensation without removal from the

pretest socket.

Although optimized for use with piezoresistive sensors,

the MAX1459 may also be used with other resistive

sensors (i.e., accelerometers and strain gauges) with

some additional external components.

________________________Applications

4–20mA Transmitters

Piezoresistive Pressure and Acceleration

Industrial Pressure Sensors

Load Cells/Wheatstone Bridges

Strain Gauges

Temperature Sensors

Features

♦ Highly Integrated Sensor Signal Conditioner for

2-Wire, 4–20mA Transmitters

♦ Sensor Errors Trimmed Using Correction

Coefficients Stored in Internal EEPROM—

Eliminates the Need for Laser Trimming and

Potentiometers

♦ Compensates Offset, Offset TC, FSO, FSOTC,

FSO Linearity

♦ Programmable Current Source (0.1mA to 2.0mA)

for Sensor Excitation

♦ Fast Signal-Path Settling Time (≈1ms)

♦ Accepts Sensor Outputs from +1mV/V to +40mV/V

♦ Fully Analog Signal Path

♦ Internal or External Temperature Reference

Compensation

♦ Automated Pilot Production (Calibration/

Compensation) System Available

♦ Write Protection for EEPROM Data Security

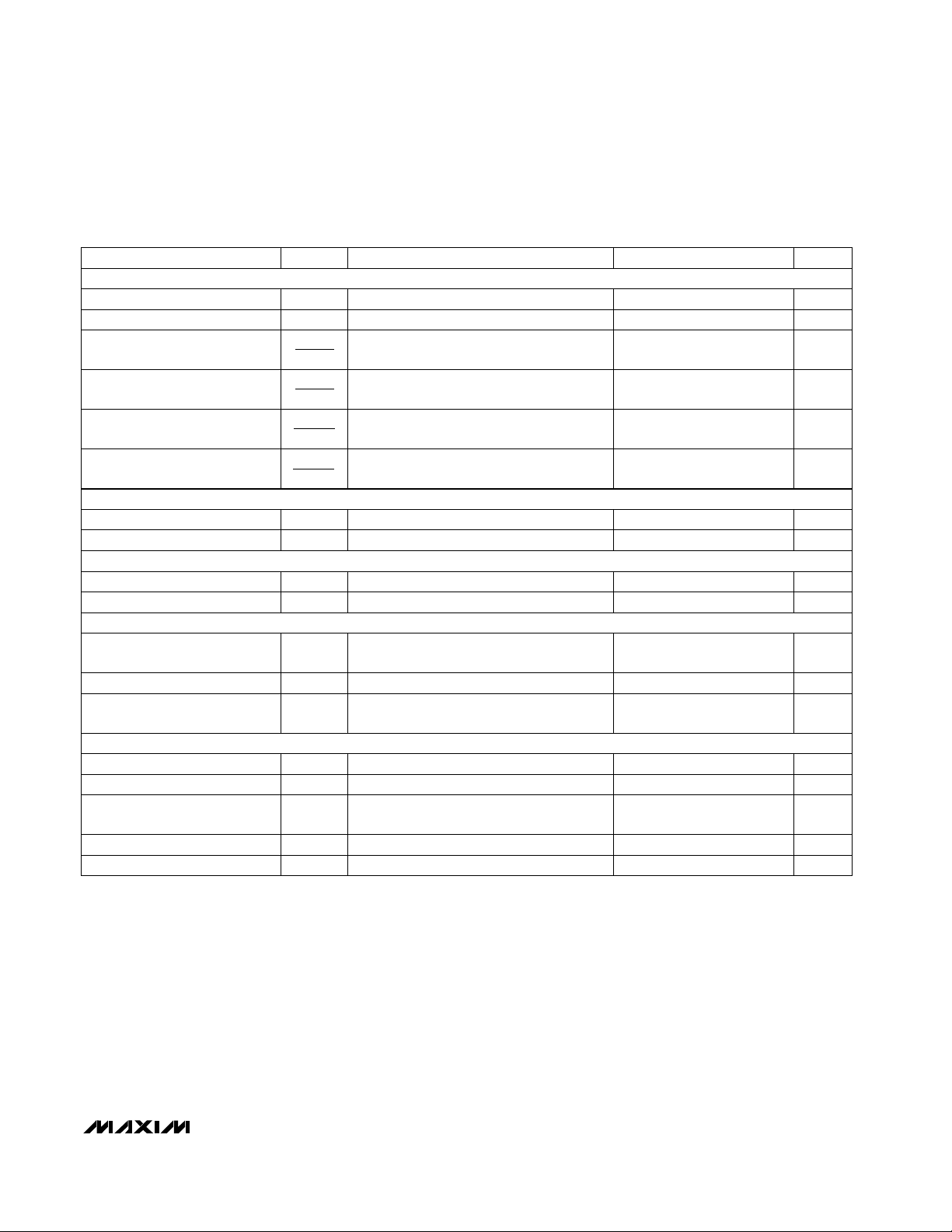

Pin Configuration

Ordering Information

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

________________________________________________________________ Maxim Integrated Products 1

19-1619; Rev 0; 1/00

*Dice are tested at TA= +25°C, DC parameters only.

Functional Diagram appears at end of data sheet.

EVALUATION KIT

AVAILABLE

20 SSOP

Dice*

20 SSOP

PIN-PACKAGETEMP. RANGE

0°C to +70°C

0°C to +70°C

-40°C to +125°CMAX1459AAP

MAX1459C/D

MAX1459CAP

PART

For custom versions of the MAX1459, see the Customization

section at end of data sheet.

TOP VIEW

FSOTC

AMP+

AMPOUT

TEMPIN

1

SCLK V

CS

2

DIO

3

MAX1459

4

WE

5

6

AMP-

7

8

9

ISRC

10

SSOP

20

NBIAS

19

CK50

18

TEMP2

17

TEMP1

16

INM

15

INP

14

BDRIVE

13

12

V

OUT

11

DD

SS

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Supply Voltage, VDDto VSS......................................-0.3V to +6V

All Other Pins ...................................(V

SS

- 0.3V) to (VDD+ 0.3V)

Short-Circuit Duration, FSOTC, OUT, BDRIVE ...........Continuous

Continuous Power Dissipation (T

A

= +70°C)

20-Pin SSOP (derate 8.00mW/°C above +70°C) ..........640mW

Operating Temperature Ranges

MAX1459CAP ......................................................0°C to +70°C

MAX1459AAP .................................................-40°C to +125°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

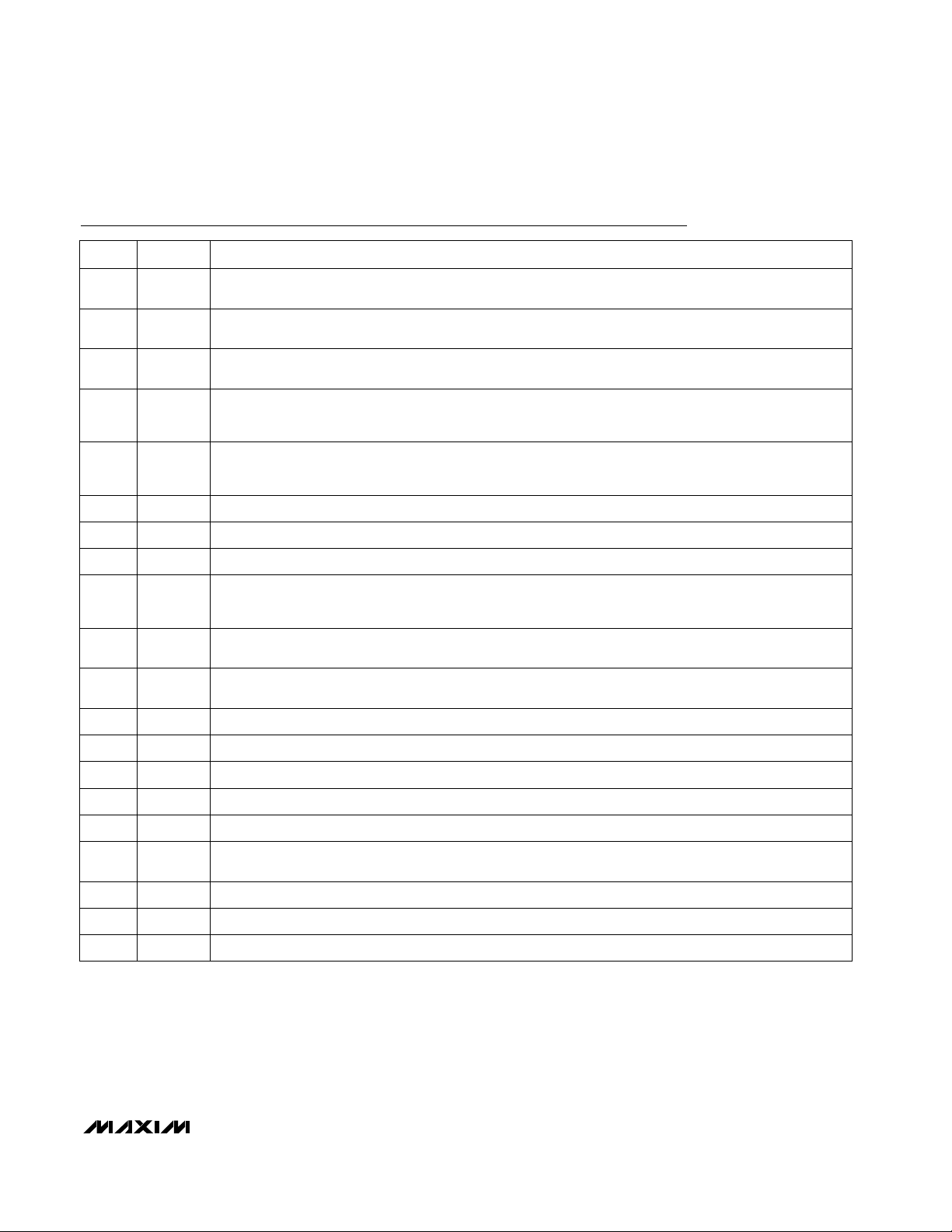

ELECTRICAL CHARACTERISTICS

(VDD= +5V, VSS= 0, TA= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL MIN TYP MAX UNITS

Amplifier Gain Nonlinearity 0.01 %V

DD

Input-Referred Offset Tempco ±0.5 µV/°C

Input Impedance R

IN

1 MΩ

Output Step Response 2 ms

Common-Mode Rejection Ratio CMRR 90 dB

Input-Referred Adjustable Offset

Range

±150 mV

Supply Voltage V

DD

4.5 5.0 5.5 V

Supply Current I

DD

2.0 2.5 mA

Input-Referred Adjustable FullSpan Output (FSO) Range

+1 to +40 mV/V

Differential Signal Gain Range +41 to +230 V/V

Minimum Differential Signal Gain +36 +41 +44 V/V

Differential Signal Gain Tempco ±50 ppm/°C

Output Current Range

-0.45 0.45

(sink) (source)

mA

Output Noise 500 µV

RMS

CONDITIONS

(Note 5)

(Notes 2, 3)

63% of final value

Selectable in eight steps

TA= T

MIN

to T

MAX

From VSSto V

DD

At minimum gain (Note 4)

TA= T

MIN

to T

MAX

V

OUT

= (VSS+ 0.25V) to (VDD- 0.25V)

DC to 10Hz (gain = 41,

source impedance = 5kΩ)

R

NBIAS

= 402kΩ, VDD= 5.0V (Note 1)

Output Voltage Swing

V

SS

+ 0.05 VDD- 0.05

V

No load

V

SS

+ 0.25 VDD- 0.2510kΩ load

GENERAL CHARACTERISTICS

ANALOG INPUT (PGA)

ANALOG OUTPUT (PGA)

Bridge Current Range I

BDRIVE

0.1 0.5 2.0 mA

Bridge Voltage Swing V

BDRIVE

V

SS

+ 1.3 VDD- 1.3 VI

BDRIVE

= 2mA

Reference Input Voltage Range

(ISRC)

V

ISRC

V

SS

+ 1.3 VDD- 1.3 V

CURRENT SOURCE

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +5V, VSS= 0, TA= +25°C, unless otherwise noted.)

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

_______________________________________________________________________________________ 3

FSO DAC Bit Weight

∆V

ISRC

∆Code

1.22 mV/bit

FSOTC DAC Bit Weight

∆V

FSOT

∆Code

0.6 mV/bit

DAC reference = VDD= 5.0V

DAC reference = V

BDRIVE

= 2.5V

Offset DAC Bit Weight

∆V

OUT

∆Code

2.8 mV/bit

Offset TC DAC Bit Weight

∆V

OUT

∆Code

1.4 mV/bit

DAC reference = VDD= 5.0V

DAC reference = V

BDRIVE

= 2.5V

DAC Resolution 12 Bits

Differential Nonlinearity DNL ±1.5 LSB

PARAMETER SYMBOL MIN TYP MAX UNITS

DAC Bit Weight 9 mV/bit

DAC Resolution 3 Bits

Output Voltage Swing 0.2 4.0 V

Current Drive -20 20 µA

Current Source Reference

Resistor

R

ISRC

100 kΩ

FSO Trim Resistor R

FTC

100 kΩ

Temperature-Dependent

Resistor

R

TEMP

100 kΩ

CONDITIONS

Input referred, VDD= 5V (Note 6)

No load, VB= 5V

V

FSOTC

= 2.5V

Input Common-Mode Range CMR V

SS

V

DD

V

Open-Loop Gain A

V

60 dB

Offset Voltage (as unity-gain

follower)

-30 30 mVVIN= VDD/2

Output Swing VSS+ 0.05 V

DD -

0.05 VNo load

Output Current ±1 mA

DIGITAL-TO-ANALOG CONVERTERS

IRO DAC

FSOTC BUFFER (FSOTC Pin)

INTERNAL RESISTORS

AUXILIARY OP AMP

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

4 _______________________________________________________________________________________

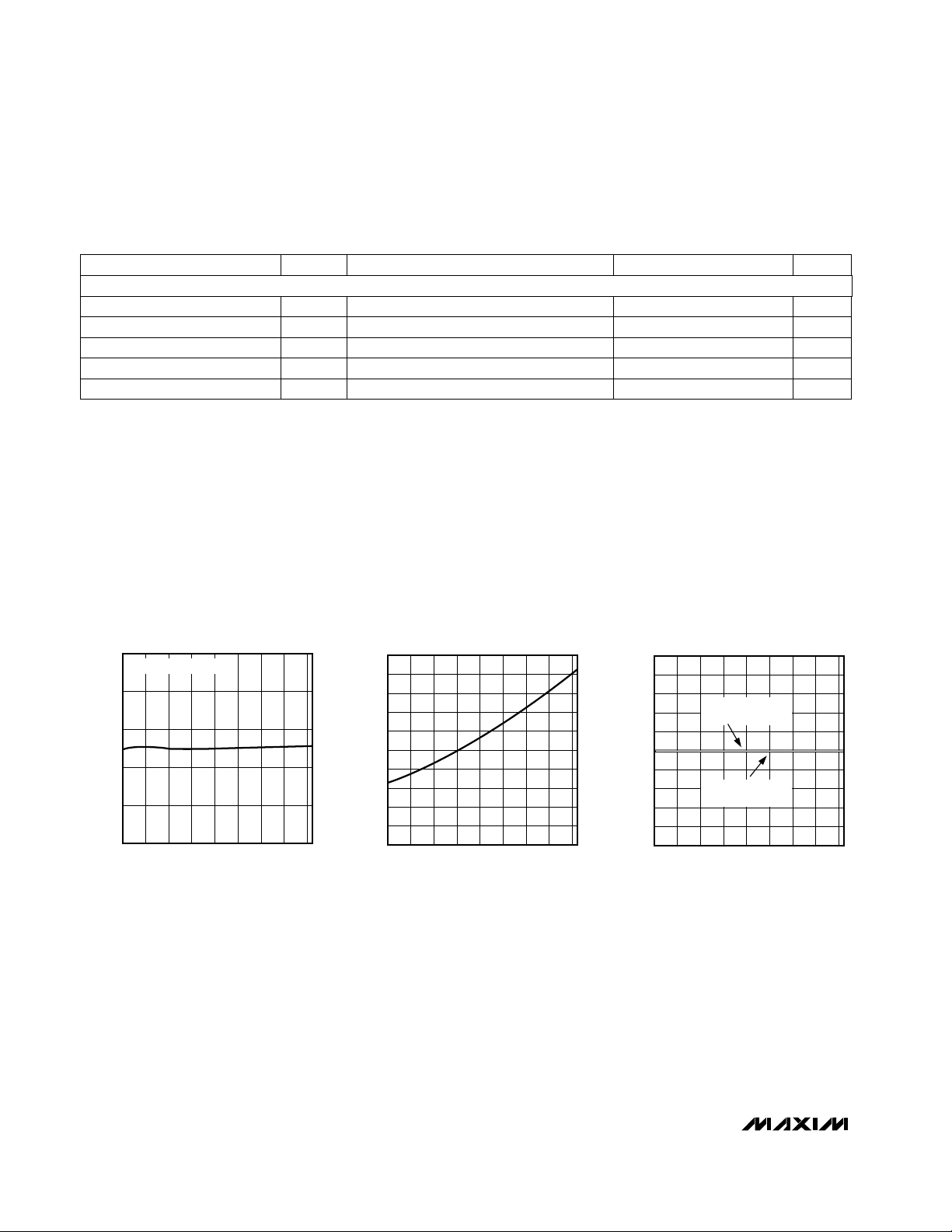

__________________________________________Typical Operating Characteristics

(VDD= +5V, VSS= 0, TA= +25°C, unless otherwise noted.)

0

0.5

1.0

1.5

2.0

2.5

-40 40 60020-20 80 100 120

SUPPLY CURRENT vs. TEMPERATURE

MAX1459 toc01

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

V

OUT

= 2.47V AT +25°C

-40 40 60020-20 80 100 120

R

TEMP

vs. TEMPERATURE

MAX1459 toc02

TEMPERATURE (°C)

R

TEMP

(Ω)

0

60

40

20

80

100

120

140

160

180

200

-40 40 60020-20 80 100 120

V

OUT

vs. TEMPERATURE

MAX1459 toc03

TEMPERATURE (°C)

V

OUT

(V)

0

1.5

1.0

0.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

V

OUT

= 2.5V AT +25°C

V

IN

= 56.5mV

V

OUT

= 2.47V AT +25°C

V

IN

= 0

Note 1: Excludes the sensor or load current.

Note 2: All electronics temperature errors are compensated together with sensor errors.

Note 3: The sensor and the MAX1459 must always be at the same temperature during calibration and use.

Note 4: This is the maximum allowable sensor offset.

Note 5: This is the sensor’s sensitivity normalized to its drive voltage, assuming a desired full-span output of 4V and a bridge

voltage of 2.5V. Sensors smaller than +10mV/V require an auxiliary op amp.

Note 6: Bit weight is ratiometric to V

DD

.

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +5V, VSS= 0, TA= +25°C, unless otherwise noted.)

I

SINK

= 2mA V0.5V

OL

Low-Level Output Voltage

I

SOURCE

= 1mA V4V

OH

High-Level Output Voltage

V2Input Hysteresis

V0.25 x V

DD

V

IL

Low-Level Input Voltage

V0.75 x V

DD

V

IH

High-Level Input Voltage

CONDITIONS UNITSMIN TYP MAXSYMBOLPARAMETER

DIGITAL PINS

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

_______________________________________________________________________________________ 5

Temperature Sensor Terminal 1TEMP116

Temperature Sensor Terminal 2. R

TEMP

is a 100kΩ temperature-dependent resistor with 4600ppm/°C

tempco.

TEMP217

Output Voltage. OUT is a Rail-to-Rail®output that can drive resistive loads down to 10kΩ and capacitive

loads up to 0.1µF.

OUT11

Negative Power Supply V

SS

12

Sensor Excitation Current Output. The current source that drives the bridge.BDRIVE13

Positive Sensor Input. Input impedance is typically 1MΩ. Rail-to-rail input range.INP14

Negative Sensor Input. Input impedance is typically 1MΩ. Rail-to-rail input range.INM15

Auxiliary Op Amp Negative InputAMP-7

Auxiliary Op Amp OutputAMPOUT8

Input pin for an External Temperature-Dependent Reference Voltage for FSOTC DAC and OTC DAC. In the

default mode, the MAX1459 uses the temperature-dependent bridge drive voltage as the FSOTC DAC and

OTC DAC reference.

TEMPIN9

Current Source Reference. An internal 100kΩ resistor (R

ISRC

) connects ISRC to VSS(see Functional

Diagram). Optionally, external resistors can be used in place of or in parallel with R

FTC

and R

ISRC

.

ISRC10

Auxiliary Op Amp Positive InputAMP+6

Buffered Full-Span Output Temperature Coefficient DAC Output. An internal 100kΩ resistor (R

FTC

) connects FSOTC to ISRC (see Functional Diagram). Optionally, external resistors can be used in place of or in

parallel with R

FTC

and R

ISC

.

FSOTC5

Write Enable, Dual-Function Input Pin. Used to enable EEPROM erase/write operations. Also used to set

the DAC refresh-rate mode. Internally pulled to VDDwith a 1MΩ (typ) resistor. See the Chip-Select (CS)

and Write-Enable (WE) section.

WE4

Data Input/Output. Used only during programming/testing. Internally pulled to VSSwith a 1MΩ (typical)

resistor. High impedance when CS is low.

DIO3

Positive Power-Supply Input. Connect a 0.1µF capacitor from VDDto VSS.V

DD

20

Clock Output, nominally 50kHzCK5018

Chip Current Bias Source. Connect an external 402kΩ ±1% resistor between VDDand NBIAS.NBIAS19

Pin Description

1

Chip-Select Input. The MAX1459 is selected when this pin is high. When low, OUT and DIO become high

impedance. Internally pulled to V

DD

with a 1MΩ (typical) resistor. Leave unconnected for normal operation.

CS2

Data Clock Input. Used only during programming/testing. Internally pulled to VSSwith a 1MΩ (typical) resistor.

Data is clocked in on the rising edge of the clock. Recommended SCLK frequency is below 50kHz.

SCLK

PIN FUNCTIONNAME

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

MAX1459

_______________Detailed Description

The MAX1459 provides an analog amplification path for

the sensor signal and a digital path for calibration and

temperature correction. Calibration and correction is

achieved by varying the offset and gain of a programmable-gain amplifier (PGA) and by varying the sensor

bridge current. The PGA utilizes a switched-capacitor

CMOS technology, with an input-referred offset trimming range of ±63mV (9mV steps). An additional output-referred fine offset trim is provided by the offset

DAC (approximately 2.8mV steps). The PGA provides

eight gain values from +41V/V to +230V/V. The bridge

current source is programmable from 0.1mA to 2mA.

The MAX1459 uses four 12-bit DACs with calibration

coefficients stored by the user in an internal 128-bit

EEPROM. This memory contains the following information as 12-bit-wide words:

• Configuration register

• Offset calibration coefficient

• Offset temperature error compensation coefficient

• Full-span output (FSO) calibration coefficient

• FSO temperature error compensation coefficient

• 24 user-defined bits for customer programming of

manufacturing data (e.g., serial number and date)

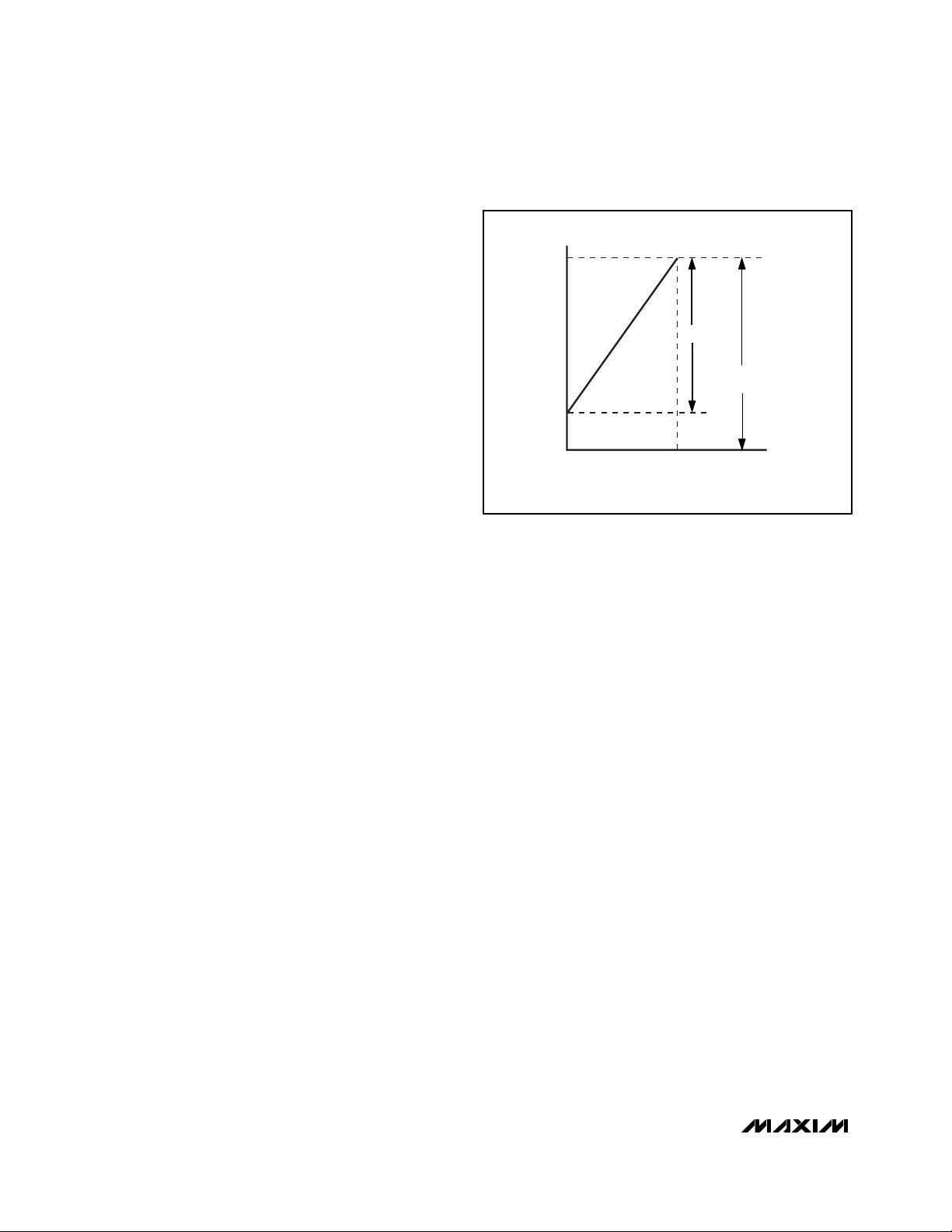

Figure 1 shows a typical pressure-sensor output and

defines the offset, full-scale, and FSO values as a function of voltage.

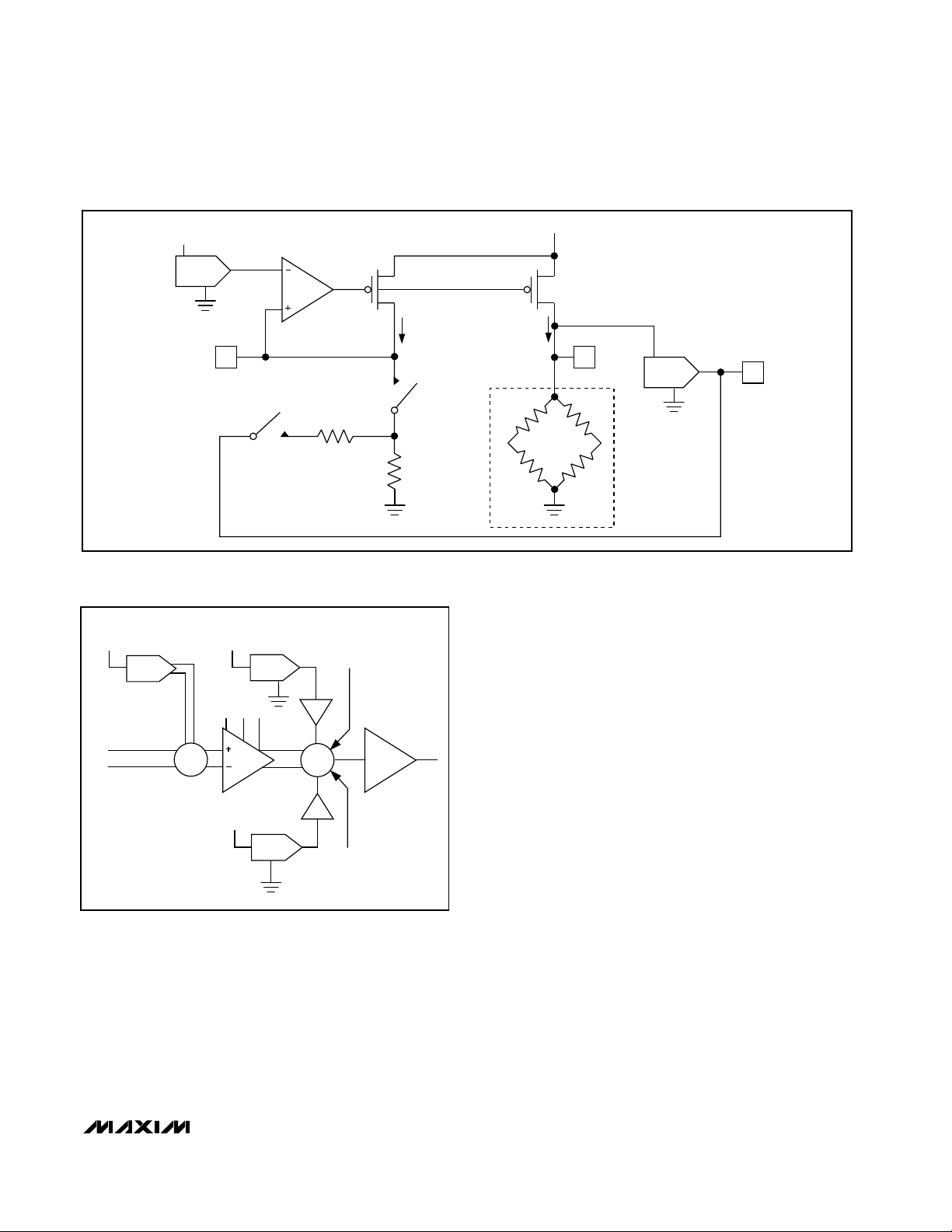

FSOTC Compensation

Silicon piezoresistive transducers (PRTs) exhibit a large

positive input resistance tempco (TCR) so that, while

under constant current excitation, the bridge voltage

(V

BDRIVE

) increases with temperature. This depen-

dence of V

BDRIVE

on the sensor temperature can be

used to compensate the sensor temperature errors.

PRTs also have a large negative full-span output sensitivity tempco (TCS) so that, with constant voltage excitation, FSO will decrease with temperature, causing a

full-span output temperature coefficient (FSOTC) error.

However, if the bridge voltage can be made to increase

with temperature at the same rate that TCS decreases

with temperature, the FSO will remain constant.

FSOTC compensation is accomplished by resistor

R

FTC

and the FSOTC DAC, which modulate the excitation reference current at ISRC as a function of temperature (Figure 2). FSO DAC sets V

ISRC

and remains

constant with temperature while the voltage at FSOTC

varies with temperature. FSOTC is the buffered output

of the FSOTC DAC. The reference DAC voltage is

V

BDRIVE

, which is temperature dependent. The FSOTC

DAC alters the tempco of the current source. When the

tempco of the bridge voltage is equal in magnitude and

opposite in polarity to the TCS, the FSOTC errors are

compensated and FSO will be constant with temperature.

OFFSET TC Compensation

Compensating offset TC errors involves first measuring

the uncompensated offset TC error, then determining

what percentage of the temperature-dependent voltage

V

BDRIVE

must be added to the output summing junction

to correct the error. Use the offset TC DAC to adjust the

amount of BDRIVE voltage that is added to the output

summing junction (Figure 3).

Analog Signal Path

The fully differential analog signal path consists of four

stages:

• Front-end summing junction for coarse offset correction

• 3-bit PGA with eight selectable gains ranging from

41 through 230

• Three-input-channel summing junction

• Differential to single-ended output buffer with rail-to-

rail output (Figure 3)

Coarse Offset Correction

The sensor output is first fed into a differential summing

junction (INM (negative input) and INP (positive input))

with a CMRR > 90dB, an input impedance of approximately 1MΩ, and a common-mode input voltage range

from V

SS

to VDD. At this summing junction, a coarse off-

set-correction voltage is added, and the resultant volt-

2-Wire, 4–20mA

Smart Signal Conditioner

6 _______________________________________________________________________________________

Figure 1. Typical Pressure-Sensor Output

4.5

FULL-SPAN OUTPUT (FSO)

P

MAX

FULL-SCALE (FS)

VOLTAGE (V)

0.5

OFFSET

P

MIN

PRESSURE

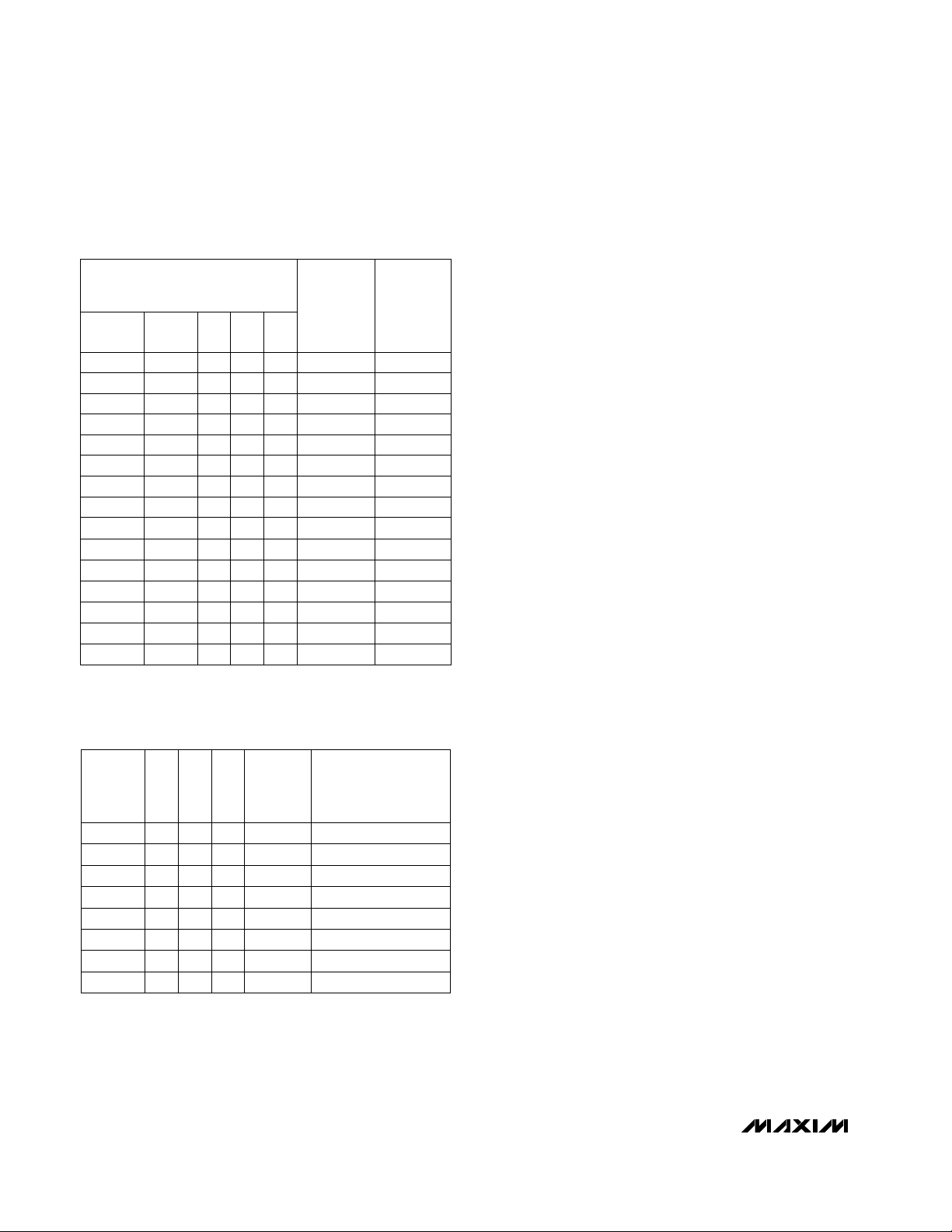

age is fed into the PGA. The 3-bit (plus sign) inputreferred offset DAC (IRO DAC) generates the coarse

offset-correction voltage. The DAC voltage reference is

1.25% of VDD; thus, a VDDof 5V results in a front-end

offset-correction voltage ranging from -63mV to +63mV,

in 9mV steps (Table 1). To add an offset to the input

signal, set the IRO sign bit high; to subtract an offset

from the input signal, set the IRO sign bit low. The IRO

DAC bits (C2, C1, C0, and IRO sign bit) are programmed in the configuration register (see Internal

EEPROM section).

Programmable-Gain Amplifier

The programmable-gain amplifier (PGA), which is used

to set the coarse FSO, uses a switched-capacitor

CMOS technology and contains eight selectable gain

levels from 41 to 230, in increments of 27 (Table 2). The

output of the PGA is fed to the output summing junction. The three PGA gain bits A2, A1, and A0 are stored

in the configuration register.

Output Summing Junction

The third stage in the analog signal path consists of a

summing junction for the PGA output, offset correction,

and the offset TC correction. Both the offset and the offset TC correction voltages are gained by a factor of 2.3

before being fed into the summing junction, increasing

the offset and offset TC correction range. The offset sign

bit and offset TC sign bit are stored in the configuration

register. The offset sign bit determines whether the offset correction voltage is added to (sign bit is high) or

subtracted from (sign bit is low) the PGA output.

Negative offset TC errors require a logic high for the offset TC sign bit. Alternately, positive offset TC errors dictate a logic low for the offset TC sign bit. The output of

the summing junction is fed to the output buffer.

MAX1459

2-Wire, 4–20mA

Smart Signal Conditioner

_______________________________________________________________________________________ 7

Figure 2. Bridge Excitation Circuit

Figure 3. Signal-Path Block Diagram

V

V

DD

FSO

DAC

DD

I = I

ISRC

I

SRC

R

FTC

R

ISRC

1.25% V

DD

IRO

DAC

INP

INM

BDRIVE

A2

V

A1 A0

PGA

DD

OFFTC

DAC

OFFSET

DAC

A = 2.3

A = 2.3

SOTC

±

OUT

ΣΣ

A = 1

±

SOFF

AA ≈ 12I

= I

ISRC

EXTERNAL

SENSOR

BDRIVE

BDRIVE

FSOTC

DAC

FSOTC

MAX1459

Output Buffer

The output buffer (OUT) can swing within 50mV of the

supply rails with no load, or within 0.25V of either rail

while driving a 10kΩ load. OUT can easily drive 0.1µF

of capacitance. The output is current limited and can

be shorted to either V

DD

or VSSindefinitely. If CS is

brought low, OUT goes high impedance, resulting in

typical output impedance of 1MΩ. This feature allows

parallel MAX1459 connections, reducing test system

wire harness complexity.

Bridge Drive

Fine FSO correction is accomplished by varying the

sensor excitation current with the 12-bit FSO DAC

(Figure 2). Sensor bridge excitation is performed by a

programmable current source capable of delivering up

to 2mA. The reference current at ISRC is established by

resistor R

ISRC

and by the voltage at node ISRC (con-

trolled by the FSO DAC). The reference current flowing

through this pin is multiplied by a current mirror (AA ≅

12) and then made available at BDRIVE for sensor excitation. Modulation of this current with respect to temperature can be used to correct FSOTC errors, while

modulation with respect to the output voltage (V

OUT

)

can be used to correct FSO linearity errors.

Voltage Drive Sensor

For sensors with negligible FSOTC, the MAX1459 can

be configured as a fixed-voltage drive by shorting ISRC

and BDRIVE. Offset TC can then be compensated with

R

TEMP

. Set configuration register bit 5 to 1, and connect TEMPIN to a temperature-dependent voltage

source. This source can easily be generated by inducing a current through R

TEMP

. For more information on

this application, refer to the MAX1459 Reference Manual.

Digital-to-Analog Converters

The four 12-bit, sigma-delta DACs typically settle in

less than 100ms. The four DACs have a corresponding

memory register in EEPROM for storage of correction

coefficients.

The FSO DAC takes its reference from VDDand controls V

ISRC

, which sets the baseline sensor excitation

current. The FSO DAC is used for fine adjustments to

the FSO. The offset DAC also takes its reference from

VDDand provides a 1.22mV resolution with a VDDof

5V. The output of the offset DAC is fed into the output

summing junction where it is gained by approximately

2.3, which increases the resulting output-referred offset-correction resolution to 2.8mV.

Both the offset TC and FSOTC DACs take their references from a temperature-dependent voltage. In

default mode, this voltage is internally connected to

BDRIVE. Alternatively, a different temperature sensor

can be used through TEMPIN by setting bit 5 of the

configuration register. This temperature sensor can be

either R

TEMP

or an external temperature resistor.

2-Wire, 4–20mA

Smart Signal Conditioner

8 _______________________________________________________________________________________

2.0702301117

1.8272030116

1.5841761015

1.3411490014

1.0981221103

0.855950102

0.612681001

0.369

OUTPUTREFERRED IRO

DAC STEP SIZE

(VDD= 5V) (V)

41

PGA

GAIN

(+V/+V)

0

PGA

VALUE

A0A2

000

A1

Table 2. PGA Gain Settings and IRO DAC

Step Size

0 0

-63-1.251110-7

-54-1.080110-6

-45-0.901010-5

-36-0.720010-4

-27-0.541100-3

-18-0.360100-2

-9-0.181000-1

0000-0

+9+0.181001+1

+18+0.360101+2

+27+0.541101+3

+36+0.720011+4

+45+0.901011+5

+54+1.080111+6

VALUE C0

C2 C1SIGN

+63

OFFSET

CORREC-

TION AT

V

DD

= 5V

(mV)

+1.25

OFFSET

CORREC-

TION

PERCENT

OF V

DD

(%)

1

IRO DAC

111+7

Table 1. Input-Referred Offset DAC

Correction Values

Loading...

Loading...