For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 408-737-7600 ext. 3468.

General Description

The MAX1450 sensor signal conditioner is optimized for

piezoresistive sensor calibration and temperature compensation. It includes an adjustable current source for

sensor excitation and a 3-bit programmable-gain amplifier (PGA). Achieving a total typical error factor within

1% of the sensor’s inherent repeatability errors, the

MAX1450 compensates offset, full-span output (FSO), offset tempco, FSO tempco, and FSO nonlinearity of silicon

piezoresistive sensors via external trimmable resistors,

potentiometers, or digital-to-analog converters (DACs).

The MAX1450 is capable of compensating sensors that

display close error distributions with a single temperature point, making it ideal for low-cost, medium-accuracy

applications. Although optimized for use with popular

piezoresistive sensors, it may also be used with other

resistive sensor types such as strain gauges.

Customization

Maxim can customize the MAX1450 for unique requirements including improved power specifications. With a

dedicated cell library consisting of more than 90 sensor-specific functional blocks, Maxim can quickly provide customized MAX1450 solutions. Contact the

factory for additional information.

Applications

Piezoresistive Pressure and Acceleration

Transducers and Transmitters

Manifold Absolute Pressure (MAP) Sensors

Automotive Systems

Hydraulic Systems

Industrial Pressure Sensors

Features

♦ 1% Sensor Signal Conditioning

♦ Corrects Sensor Errors Using Coefficients Stored

in External Trimmable Resistors, Potentiometers,

or DACs

♦ Compensates Offset, Offset TC, FSO, FSO TC,

and FSO Linearity

♦ Rail-to-Rail

®

Analog Output

♦ Programmable Current Source for Sensor

Excitation

♦ Fast Signal-Path Settling Time (< 1ms)

♦ Accepts Sensor Outputs from 10mV/V to 30mV/V

♦ Fully Analog Signal Path

MAX1450

Low-Cost, 1%-Accurate Signal Conditioner

for Piezoresistive Sensors

________________________________________________________________

Maxim Integrated Products

1

PGA

A = 1

OUT

ISRC

BDRIVE

INP

INM

SOTC

SOFF

OFFTC

OFFSET

BBUF

A2

FSOTRIM

A1

A0

+

-

V

DD

V

SS

CURRENT

SOURCE

V

DD

MAX1450

Pin Configuration

19-1365; Rev 0; 5/98

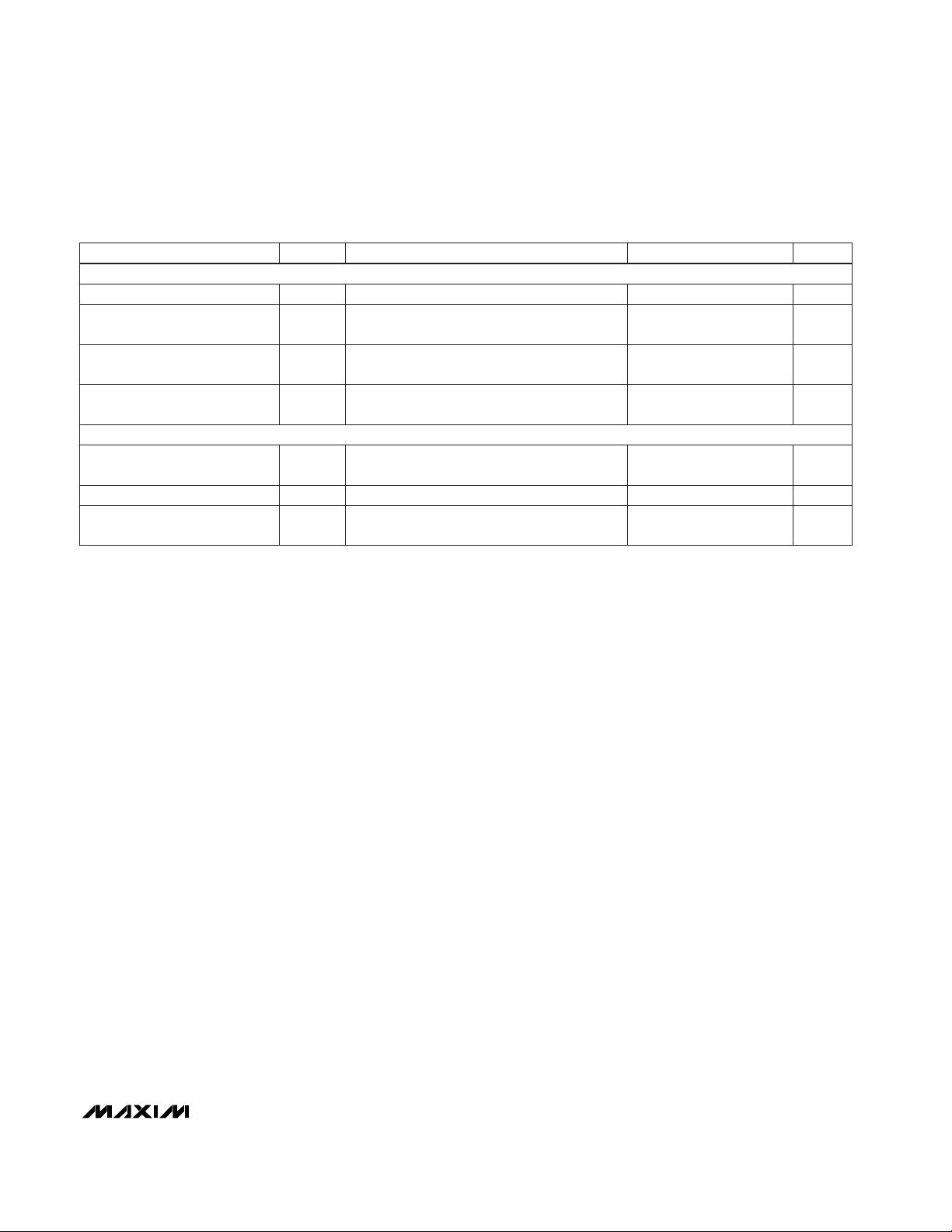

PART

MAX1450CAP

MAX1450C/D

MAX1450EAP -40°C to +85°C

0°C to +70°C

0°C to +70°C

TEMP. RANGE PIN-PACKAGE

20 SSOP

Dice*

20 SSOP

*

Dice are tested at TA = +25°C, DC parameters only.

Functional Diagram

Ordering Information

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

TOP VIEW

INP

I.C.

I.C.

SOFF

A1

A0

OFFSET

20

INM

19

V

SS

18

BDRIVE

17

ISRCSOTC

16

I.C.

15

V

DD

OUT

14

A2OFFTC

13

12

I.C.

11

FSOTRIMBBUF

1

2

3

4

MAX1450

5

6

7

8

9

10

SSOP

MAX1450

Low-Cost, 1%-Accurate Signal Conditioner

for Piezoresistive Sensors

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VDD= +5V, VSS= 0, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at TA= +25°C.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Supply Voltage, VDDto VSS......................................-0.3V to +6V

All Other Pins ...................................(VSS- 0.3V) to (VDD+ 0.3V)

Short-Circuit Duration, OUT, BBUF, BDRIVE.............Continuous

Continuous Power Dissipation (TA= +70°C)

SSOP (derate 8.00mW/°C above +70°C) ....................640mW

Operating Temperature Range

MAX1450CAP .....................................................0°C to +70°C

MAX1450EAP ..................................................-40°C to +85°C

Storage Temperature Range.............................-65°C to +165°C

Lead Temperature (soldering, 10sec).............................+300°C

TA= +25°C (Note 1)

DC to 10Hz, gain = 39,

sensor impedance = 5kΩ

V

OUT

= (VSS+ 0.25V) to (VDD- 0.25V)

,

TA= +25°C

(Note 5)

(Note 4)

5kΩ load to VSSor V

DD,

TA= +25°C

From VSSto V

DD

63% of final value

(Notes 2, 3)

Eight selectable gains (Table 3)

CONDITIONS

µV

RMS

500Output Noise

mA

-1.0 1.0

(sink) (source)

Output Current Range

V

V

SS +

V

DD -

0.25 0.25

Output Voltage Swing

V/V36 39 44

Minimum Differential Signal

Gain

V/V39 to 221Differential Signal Range Gain

mA2.8 3.5I

DD

Supply Current

mV/V10 to 30

Input-Referred Adjustable

Full-Span Output Range

mV±100

Input-Referred Adjustable Offset

Range

dB90CMRRCommon-Mode Rejection Ratio

ms1Output Step-Response Time

MΩ1.0R

IN

Input Impedance

µV/°C±0.5

Input-Referred Offset

Temperature Coefficient

%V

DD

0.01Amplifier Gain Nonlinearity

UNITSMIN TYP MAXSYMBOLPARAMETER

No load, TA= T

MIN

to T

MAX

V

SS +

V

DD -

0.05 0.05

V4.5 5.0 5.5V

DD

Supply Voltage

At any gain ppm/°C±50

Differential Signal Path

Temperature Coefficient

V/V1.15Offset TC Gain

V/V1.15Offset Gain

∆∆V

V

OUT

OFFSET

∆∆V

V

OUT

OFFTC

GENERAL CHARACTERISTICS

ANALOG OUTPUT (PGA)

ANALOG INPUT (PGA)

SUMMING JUNCTION (Figure 1)

MAX1450

Low-Cost, 1%-Accurate Signal Conditioner

for Piezoresistive Sensors

_______________________________________________________________________________________

3

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +5V, VSS= 0, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at TA= +25°C.)

Note 1: Contact factory for high-volume applications requiring less than 1.5mA.

Note 2: All electronics temperature errors are compensated together with the sensor errors.

Note 3: The sensor and the MAX1450 must always be at the same temperature during calibration and use.

Note 4: This is the maximum allowable sensor offset at minimum gain (39V/V).

Note 5: This is the sensor’s sensitivity normalized to its drive voltage, assuming a desired full-span output (FSO) of 4V and a bridge

voltage of 2.5V. Operating at lower bridge excitation voltages can accommodate higher sensitivities.

V

BDRIVE

= 2.5V

No load

(V

BDRIVE

- V

BBUF

) at V

BDRIVE

= 2.5V, no load

CONDITIONS

µA-100 100Current Drive

V

V

SS +

V

DD -

1.3 1.3

Voltage Swing

mV-20 20V

OFS

Offset Voltage

UNITSMIN TYP MAXSYMBOLPARAMETER

∆I

BDRIVE/

∆I

ISRC

(Figure 2)

V

V

SS +

V

DD -

1.3 1.3

V

BDRIVE

Bridge Voltage Swing

mA0.1 0.5 2.0I

BDRIVE

Bridge Current Range

µA/µA13AACurrent-Source Gain

V

V

SS +

V

DD-

1.3 1.3

V

ISRC

Current-Source Input Voltage

Range

BUFFER (BBUF)

CURRENT SOURCE

______________ Detailed Description

Analog Signal Path

The MAX1450’s signal path is fully differential and combines the following three stages: a 3-bit PGA with

selectable gains of 39, 65, 91, 117, 143, 169, 195, and

221; a summing junction; and a differential to singleended output buffer (Figure 1).

Programmable-Gain Amplifier

The analog signal is first fed into a programmable-gain

instrumentation amplifier with a CMRR of 90dB and a

common-mode input range from VSSto VDD. Pins A0,

A1, and A2 set the PGA gain anywhere from 39V/V to

221V/V (in steps of 26).

MAX1450

Low-Cost, 1%-Accurate Signal Conditioner

for Piezoresistive Sensors

4 _______________________________________________________________________________________

NAME FUNCTION

1 INP Positive Sensor Input. Input impedance is typically 1MΩ. Rail-to-rail input range.

PIN

2, 3,

12, 16

I.C. Internally connected. Leave unconnected.

4 SOTC

Offset TC Sign Bit Input. A logic low inverts V

OFFTC

with respect to V

SS.

This pin is internally pulled to V

SS

via a 1MΩ (typical) resistor. Connect to VDDto add V

OFFTC

to the PGA output, or leave unconnected (or

connect to VSS) to subtract V

OFFTC

from the PGA output.

8 OFFTC

Offset TC Adjust. Analog input summed with PGA output and V

OFFSET

. Input impedance is typically 1MΩ.

Rail-to-rail input range.

7 A0

PGA Gain-Set LSB Input. Internally pulled to VSSvia a 1MΩ (typical) resistor. Connect to VDDfor a logic

high or VSSfor a logic low.

6 A1

PGA Gain-Set Input. Internally pulled to VSSvia a 1MΩ (typical) resistor. Connect to VDDfor a logic high or

VSSfor a logic low.

5 SOFF

Offset Sign Bit Input. A logic low inverts V

OFFSET

with respect to VSS. This pin is internally pulled to VSSvia

a 1MΩ (typical) resistor. Connect to VDDto add V

OFFSET

to the PGA output, or leave unconnected (or con-

nect to VSS) to subtract V

OFFSET

from the PGA output.

14 OUT PGA Output Voltage. Connect a 0.1µF capacitor from OUT to VSS.

13 A2

PGA Gain-Set MSB Input. Internally pulled to VSSvia a 11kΩ (typical) resistor. Connect to VDDfor a logic

high or VSSfor a logic low.

11 FSOTRIM Bridge Drive Current-Set Input. The voltage on this pin sets the nominal I

ISRC

. See the

Bridge Drive

section.

10 BBUF

Buffered Bridge-Voltage Output (the voltage at BDRIVE). Use with correction resistor R

STC

to correct for FSO

tempco.

9 OFFSET

Offset Adjust Input. Analog input summed with PGA output and V

OFFTC

. Input impedance is typically

1MΩ. Rail-to-rail input range.

Pin Description

15 V

DD

Positive Supply Voltage Input. Connect a 0.1µF capacitor from VDDto VSS.

20 INM Negative Sensor Input. Input impedance is typically 1MΩ. Rail-to-rail input range.

19 V

SS

Negative Power-Supply Input.

18 BDRIVE Sensor Excitation Current Output. This pin drives a nominal 0.5mA through the bridge.

17 ISRC Current-Source Reference. Connect a 50kΩ (typical) resistor from ISRC to VSS.

Figure 1. Signal-Path Functional Diagram

INP

INM

A2

A1 A0

PGA

OFFTC SOTC

±

Σ

±

OFFSET SOFF

A = 1

OUT

Loading...

Loading...