查询DS21448供应商

www.maxim-ic.com

3.3V E1/T1/J1 Quad Line Interface

GENERAL DESCRIPTION

The DS21448 is a quad-port E1 or T1 line interface

unit (LIU) for short-haul and long-haul applications. It

incorporates four independent transmitters and four

independent receivers in a single 144-pin PBGA or

128-pin LQFP package.

The transmit drivers generate the necessary G.703

E1 waveshapes in 75W or 120W applications and the

DSX-1 or CSU line build-outs of 0dB, -7.5dB, -15dB,

and -22.5dB for T1 applications.

The DS21448 has a usable receiver sensitivity of

0 to -43dB for E1 applications and 0 to -36dB for T1

that allows it to operate on 0.63mm (22AWG) cables

up to 2.5km (E1) and 6000ft (T1) in length. The user

has the option to use internal receive termination,

software selectable for 75W, 100W, and 120W

applications, or external termination.

The on-board crystal-less jitter attenuator can be

placed in either the transmit or the receive data path,

and requires only a 2.048MHz MCLK for both E1 and

T1 applications (with the option of using a 1.544MHz

MCLK in T1 applications).

The DS21448 has diagnostic capabilities such as

loopbacks and PRBS pattern generation and

detection. 16-bit loop-up and loop-down codes can

be generated and detected. A single input pin can

power down all transmitters to allow the

implementation of hitless protection switching (HPS)

for 1+1 redundancy without the use of relays.

The device can be controlled through an 8-bit parallel

port (muxed or nonmuxed) or a serial port, and it can

be used in hardware mode. A standard boundary

scan interface supports board-level testing.

APPLICATIONS

Integrated Multiservice Access Platforms

T1/E1 Cross-Connects, Multiplexers, and Channel

Banks

Central-Office Switches and PBX Interfaces

T1/E1 LAN/WAN Routers

Wireless Base Stations

DS21448

FEATURES

§ Four Complete E1, T1, or J1 LIUs

§ Supports Long- and Short-Haul Trunks

§ Internal Software-Selectable Receive-Side

Termination for 75W/100W/120W

§ 3.3V Power Supply

§ 32-Bit or 128-Bit Crystal-Less Jitter Attenuator

Requires Only a 2.048MHz Master Clock for E1

and T1, with the Option to Use 1.544MHz for T1

§ Generates the Appropriate Line Build-Outs With

and Without Return Loss for E1, and DSX-1 and

CSU Line Build-Outs for T1

§ AMI, HDB3, and B8ZS Encoding/Decoding

§ 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz

Clock Output Synthesized to Recovered Clock

§ Programmable Monitor Mode for Receiver

§ Loopbacks and PRBS Pattern Generation/

Detection with Output for Received Errors

§ Generates/Detects In-Band Loop Codes, 1 to 16

Bits, Including CSU Loop Codes

§ 8-Bit Parallel or Serial Interface with Optional

Hardware Mode

§ Muxed and Nonmuxed Parallel Bus Supports

Intel or Motorola

§ Detects/Generates Blue (AIS) Alarms

§ NRZ/Bipolar Interface for Tx/Rx Data I/O

§ Transmit Open-Circuit Detection

§ Receive Carrier Loss (RCL) Indication (G.775)

§ High-Z State for TTIP and TRING

§ 50mA

§ JTAG Boundary Scan Test Port per IEEE 1149.1

§ Meets Latest E1 and T1 Specifications Including

ANSI.403-1999, ANSI T1.408, AT&T TR 62411,

ITU G.703, G.704, G.706, G.736, G.775, G.823,

I.431, O.151, O.161, ETSI ETS 300 166,

JTG.703, JTI.431, TBR12, TBR13, and CTR4

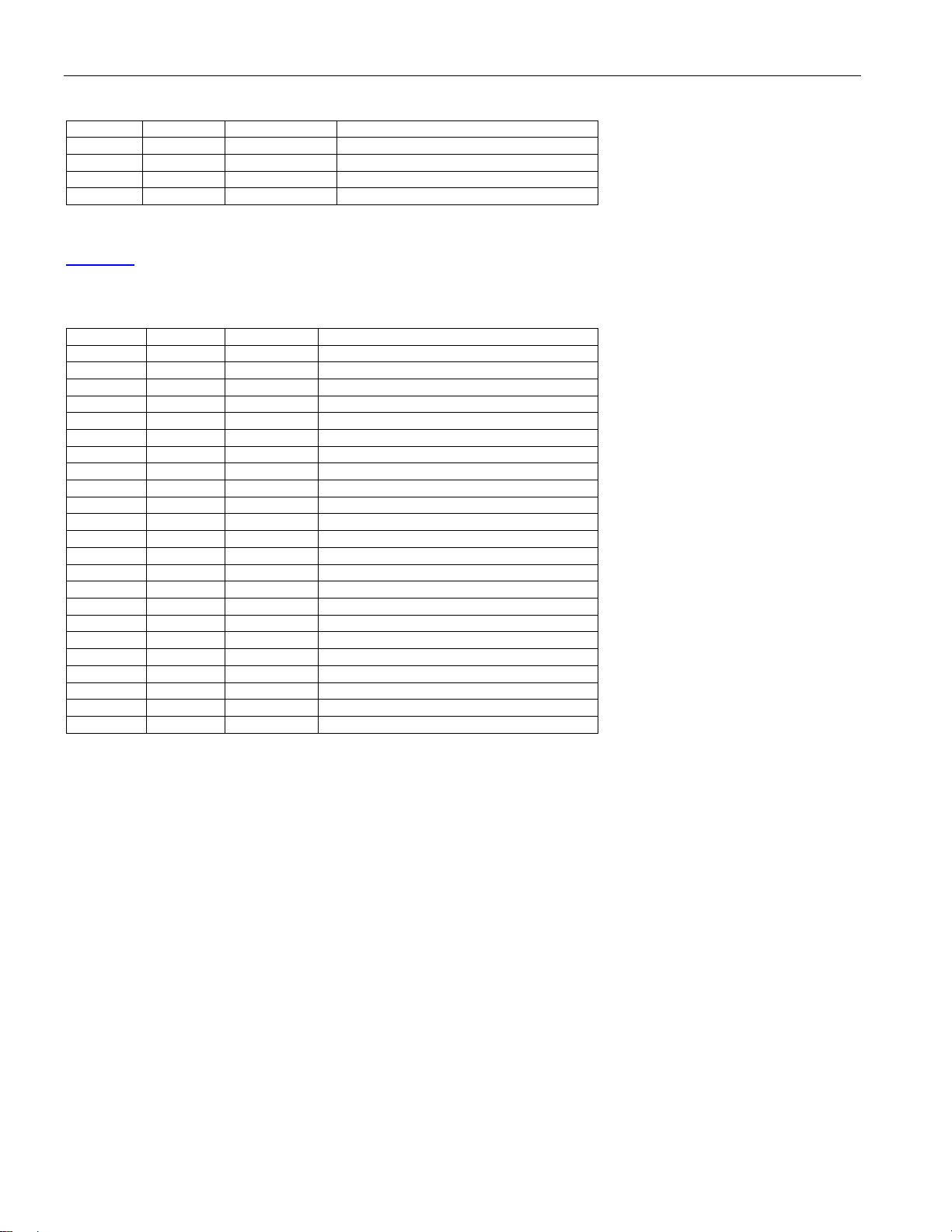

ORDERING INFORMATION

PART TEMP RANGE

DS21448 0°C to +70°C 3.3 144 BGA

DS21448N -40°C to +85°C 3.3 144 BGA

DS21448L 0°C to +70°C 3.3 128 LQFP

DS21448LN -40°C to +85°C 3.3 128 LQFP

Pin Configurations appear in Section 11.

Transmit Current Limiter

RMS

VOLTAGE

(V)

PINPACKAGE

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

1 of 60

REV: 012104

.

DS21448 3.3V T1/E1/J1 Quad Line Interface

TABLE OF CONTENTS

1. BLOCK DIAGRAMS...................................................................................................................... 5

2. PIN DESCRIPTION ....................................................................................................................... 7

3. DETAILED DESCRIPTION...........................................................................................................13

3.1 DS21448 AND DS21Q348 DIFFERENCES ....................................................................................13

4. PORT OPERATION......................................................................................................................13

4.1 HARDWARE MODE.......................................................................................................................13

4.2 SERIAL PORT OPERATION............................................................................................................15

4.3 PARALLEL PORT OPERATION .......................................................................................................17

4.3.1 Device Power-Up and Reset.................................................................................................................17

4.3.2 Register Map.........................................................................................................................................18

4.3.3 Control Registers ..................................................................................................................................19

5. STATUS REGISTERS..................................................................................................................23

6. DIAGNOSTICS ............................................................................................................................27

6.1 IN-BAND LOOP-CODE GENERATION AND DETECTION.....................................................................27

6.2 LOOPBACKS ................................................................................................................................31

6.2.1 Remote Loopback (RLB) ......................................................................................................................31

6.2.2 Local Loopback (LLB) ...........................................................................................................................31

6.2.3 Analog Loopback (LLB) ........................................................................................................................31

6.2.4 Dual Loopback (DLB)............................................................................................................................31

6.3 PRBS GENERATION AND DETECTION ...........................................................................................31

6.4 ERROR COUNTER........................................................................................................................31

6.5 ERROR COUNTER UPDATE...........................................................................................................32

6.6 ERROR INSERTION.......................................................................................................................32

7. ANALOG INTERFACE.................................................................................................................33

7.1 RECEIVER...................................................................................................................................33

7.2 TRANSMITTER .............................................................................................................................33

7.3 JITTER ATTENUATOR ...................................................................................................................34

7.4 G.703 SYNCHRONIZATION SIGNAL ...............................................................................................34

8. JTAG BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT..................................43

8.1 JTAG TAP CONTROLLER STATE MACHINE ...................................................................................43

8.2 INSTRUCTION REGISTER ..............................................................................................................45

8.3 TEST REGISTERS ........................................................................................................................46

9. OPERATING PARAMETERS.......................................................................................................48

10. AC TIMING PARAMETERS AND DIAGRAMS ............................................................................49

11. PIN CONFIGURATIONS ..............................................................................................................56

11.1 144-PIN BGA ..........................................................................................................................56

11.2 128-PIN LQFP.........................................................................................................................57

12. PACKAGE INFORMATION..........................................................................................................58

13. THERMAL INFORMATION ..........................................................................................................60

14. REVISION HISTORY....................................................................................................................60

2 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

LIST OF FIGURES

Figure 1-1. Block Diagram....................................................................................................................... 5

Figure 1-2. Receive Logic Detail.............................................................................................................. 6

Figure 1-3. Transmit Logic Detail............................................................................................................. 6

Figure 4-1. Serial Port Operation for Read Access (R = 1) Mode 1 ........................................................15

Figure 4-2. Serial Port Operation for Read Access (R = 1) Mode 2 ........................................................16

Figure 4-3. Serial Port Operation for Read Access (R = 1) Mode 3 ........................................................16

Figure 4-4. Serial Port Operation for Read Access (R = 1) Mode 4 ........................................................16

Figure 4-5. Serial Port Operation for Write Access (R = 0) Modes 1 and 2 .............................................17

Figure 4-6. Serial Port Operation for Write Access (R = 0) Modes 3 and 4 .............................................17

Figure 7-1. Basic Interface......................................................................................................................36

Figure 7-2. Protected Interface Using Internal Receive Termination.......................................................37

Figure 7-3. Protected Interface Using External Receive Termination......................................................38

Figure 7-4. Dual Connector-Protected Interface Using Receive Termination ..........................................39

Figure 8-5. E1 Transmit Pulse Template ................................................................................................40

Figure 8-6. T1 Transmit Pulse Template.................................................................................................41

Figure 7-7. Jitter Tolerance.....................................................................................................................42

Figure 7-8. Jitter Attenuation ..................................................................................................................42

Figure 8-1. JTAG Block Diagram............................................................................................................43

Figure 8-2. TAP Controller State Diagram ..............................................................................................44

Figure 10-1. Intel Bus Read Timing (PBTS = 0, BIS0 = 0) ......................................................................49

Figure 10-2. Intel Bus Write Timing (PBTS = 0, BIS0 = 0) ......................................................................50

Figure 10-3. Motorola Bus Timing (PBTS = 1, BIS0 = 0) ........................................................................50

Figure 10-4. Intel Bus Read Timing (PBTS = 0, BIS0 = 1) ......................................................................51

Figure 10-5. Intel Bus Write Timing (PBTS = 0, BIS0 = 1) ......................................................................52

Figure 10-6. Motorola Bus Read Timing (PBTS = 1, BIS0 = 1)...............................................................52

Figure 10-7. Motorola Bus Write Timing (PBTS = 1, BIS0 = 1) ...............................................................52

Figure 10-8. Serial Bus Timing (BIS1 = 1, BIS0 = 0)...............................................................................53

Figure 10-9. Receive-Side Timing ..........................................................................................................54

Figure 10-10. Transmit-Side Timing .......................................................................................................55

3 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

LIST OF TABLES

Table 2-A. Bus Interface Selection .......................................................................................................... 7

Table 2-B. Pin Assignments .................................................................................................................... 7

Table 2-C. Parallel Interface Mode Pin Description ................................................................................. 9

Table 2-D. Serial Interface Mode Pin Description ...................................................................................10

Table 2-E. Hardware Interface Mode Pin Description.............................................................................11

Table 3-A. DS21448 vs. DS21Q348 Pin Differences ..............................................................................13

Table 4-A. Loopback Control in Hardware Mode ....................................................................................14

Table 4-B. Transmit Data Control in Hardware Mode .............................................................................14

Table 4-C. Receive Sensitivity Settings in Hardware Mode ....................................................................14

Table 4-D. Monitor Gain Settings in Hardware Mode..............................................................................14

Table 4-E. Internal Rx Termination Select in Hardware Mode ................................................................14

Table 4-F. MCLK Selection in Hardware Mode.......................................................................................14

Table 4-G. Parallel Port Mode Selection.................................................................................................18

Table 4-H. Register Map ........................................................................................................................18

Table 4-I. Receive Sensitivity Settings....................................................................................................22

Table 4-J. Backplane Clock Select .........................................................................................................22

Table 4-K. Monitor Gain Settings............................................................................................................22

Table 4-L. Internal Rx Termination Select...............................................................................................22

Table 5-A. Received Alarm Criteria ........................................................................................................25

Table 5-B. Receive Level Indication .......................................................................................................27

Table 6-A. Transmit Code Length...........................................................................................................29

Table 6-B. Receive Code Length............................................................................................................29

Table 6-C. Definition of Received Errors.................................................................................................32

Table 6-D. Function of ECRS Bits and RNEG Pin ..................................................................................32

Table 7-A. Line Build-Out Select for E1 in Register CCR4 (ETS = 0)......................................................34

Table 7-B. Line Build-Out Select for T1 in Register CCR4 (ETS = 1)......................................................34

Table 7-C. Line Build-Out Select for E1 in Register CCR4 (ETS = 0) Using Alternate Transformer

Configuration ...................................................................................................................................35

Table 7-D. Transformer Specifications (3.3V Operation) ........................................................................35

Table 8-A. Instruction Codes for IEEE 1149.1 Architecture.....................................................................45

Table 8-B. ID Code Structure .................................................................................................................46

Table 8-C. Device ID Codes...................................................................................................................46

Table 8-D. Boundary Scan Control Bits ..................................................................................................47

Table 10-A. AC Characteristics—Multiplexed Parallel Port (BIS0 = 0)....................................................49

Table 10-B. AC Characteristics—Nonmultiplexed Parallel Port (BIS0 = 1) .............................................51

Table 10-C. AC Characteristics—Serial Port (BIS1 = 1, BIS0 = 0)..........................................................53

Table 10-D. AC Characteristics—Receive Side......................................................................................54

Table 10-E. AC Characteristics—Transmit Side .....................................................................................55

Table 13-A. Thermal Characteristics—BGA ...........................................................................................60

Table 13-B. Theta-JA (qJA) vs. Airflow—BGA..........................................................................................60

Table 13-C. Thermal Characteristics—LQFP..........................................................................................60

Table 13-D. Theta-JA (qJA) vs. Airflow—LQFP........................................................................................60

4 of 60

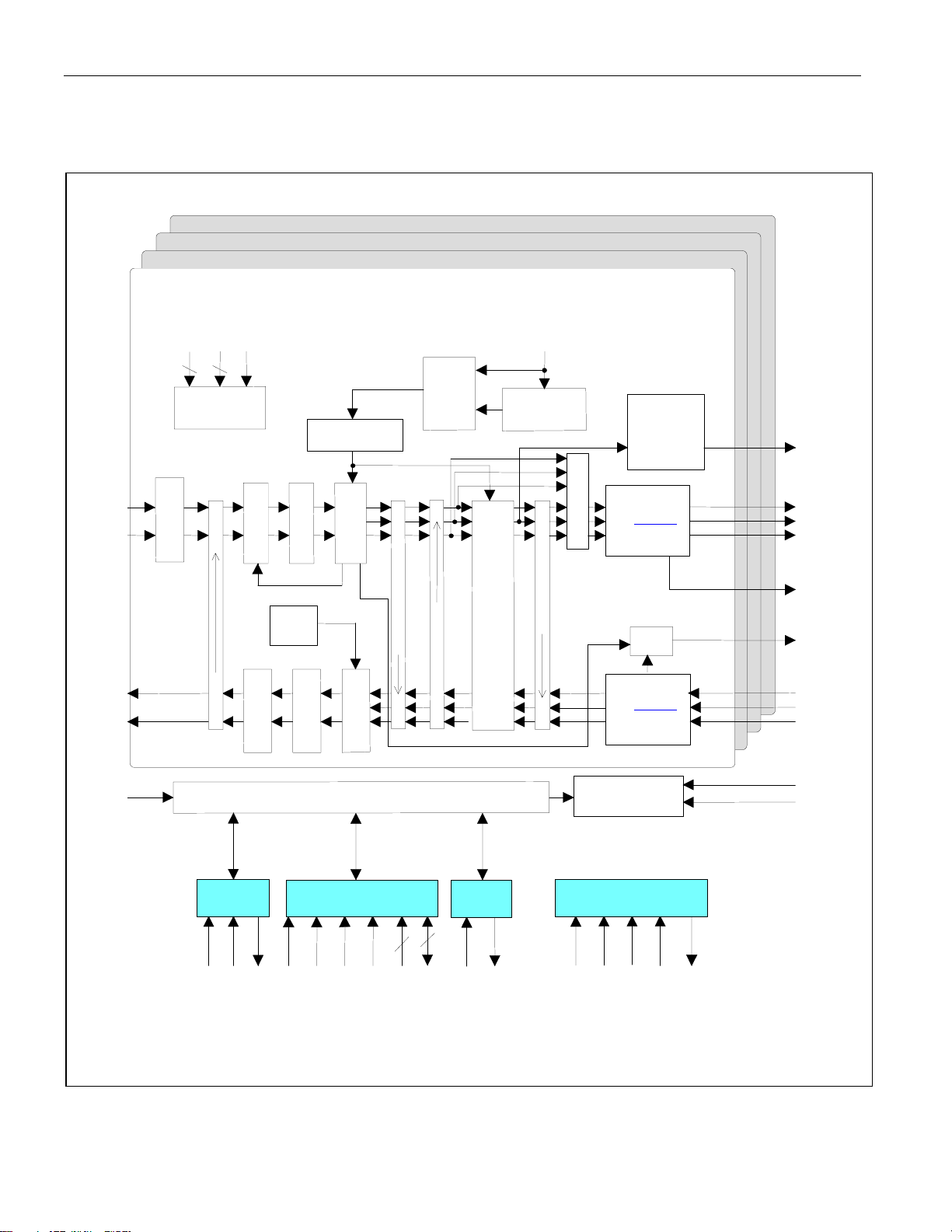

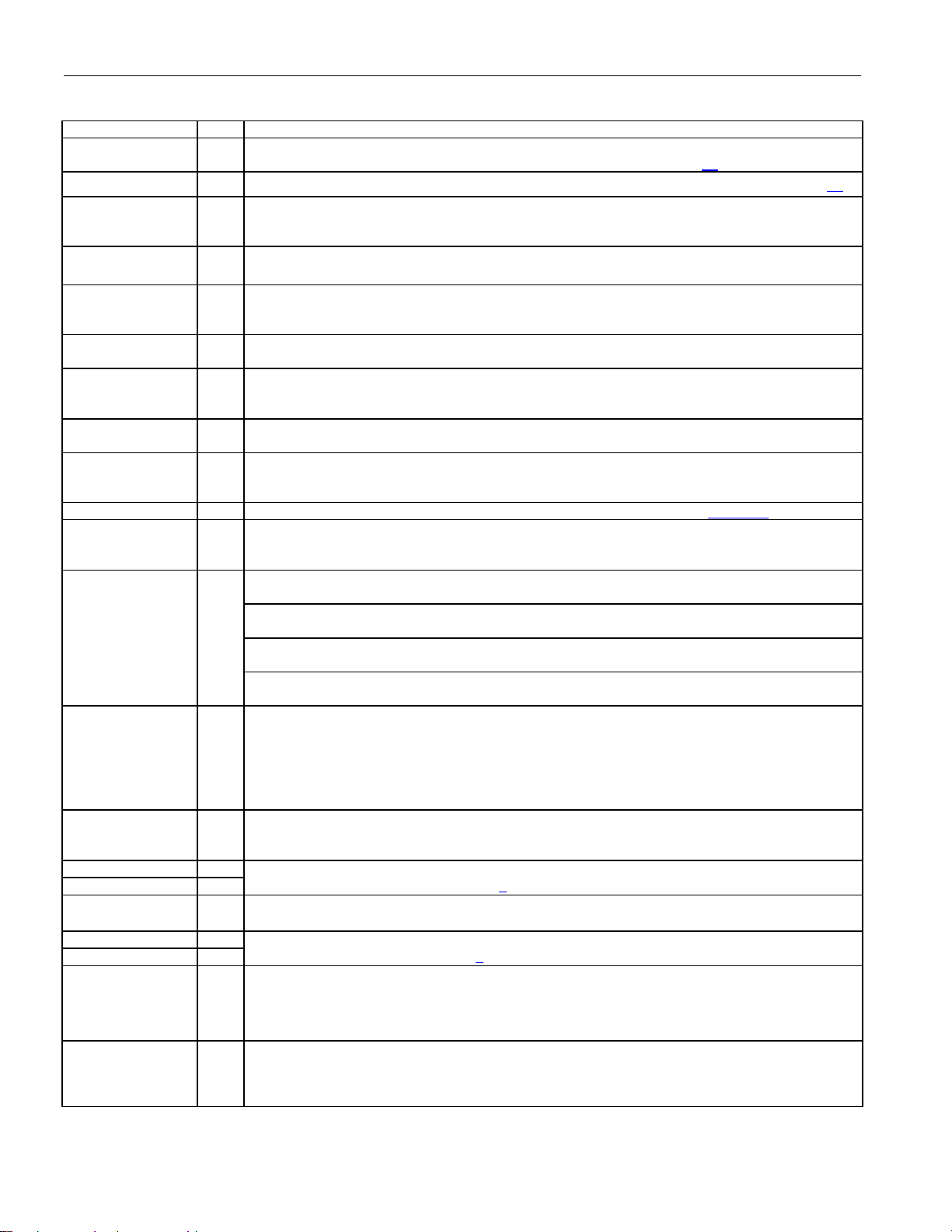

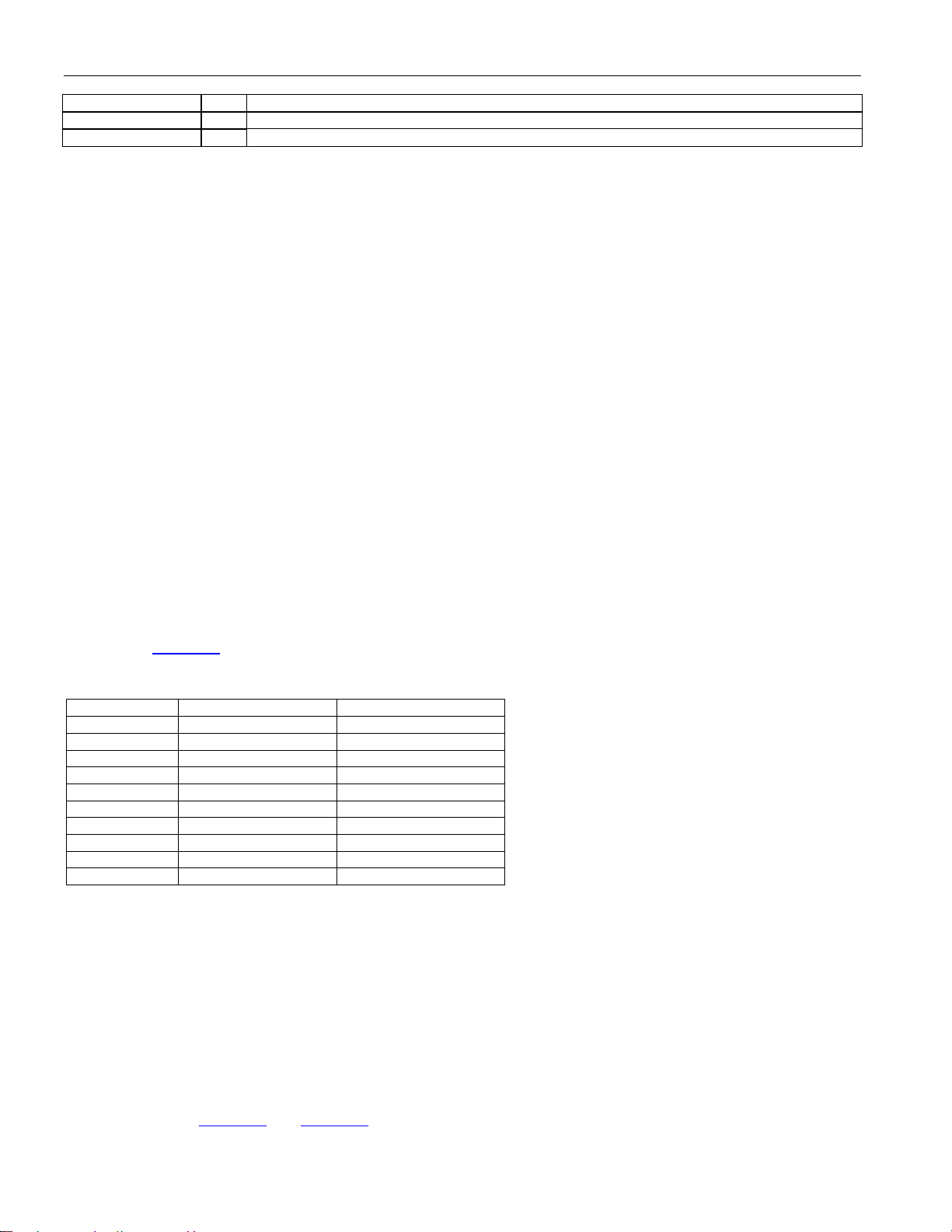

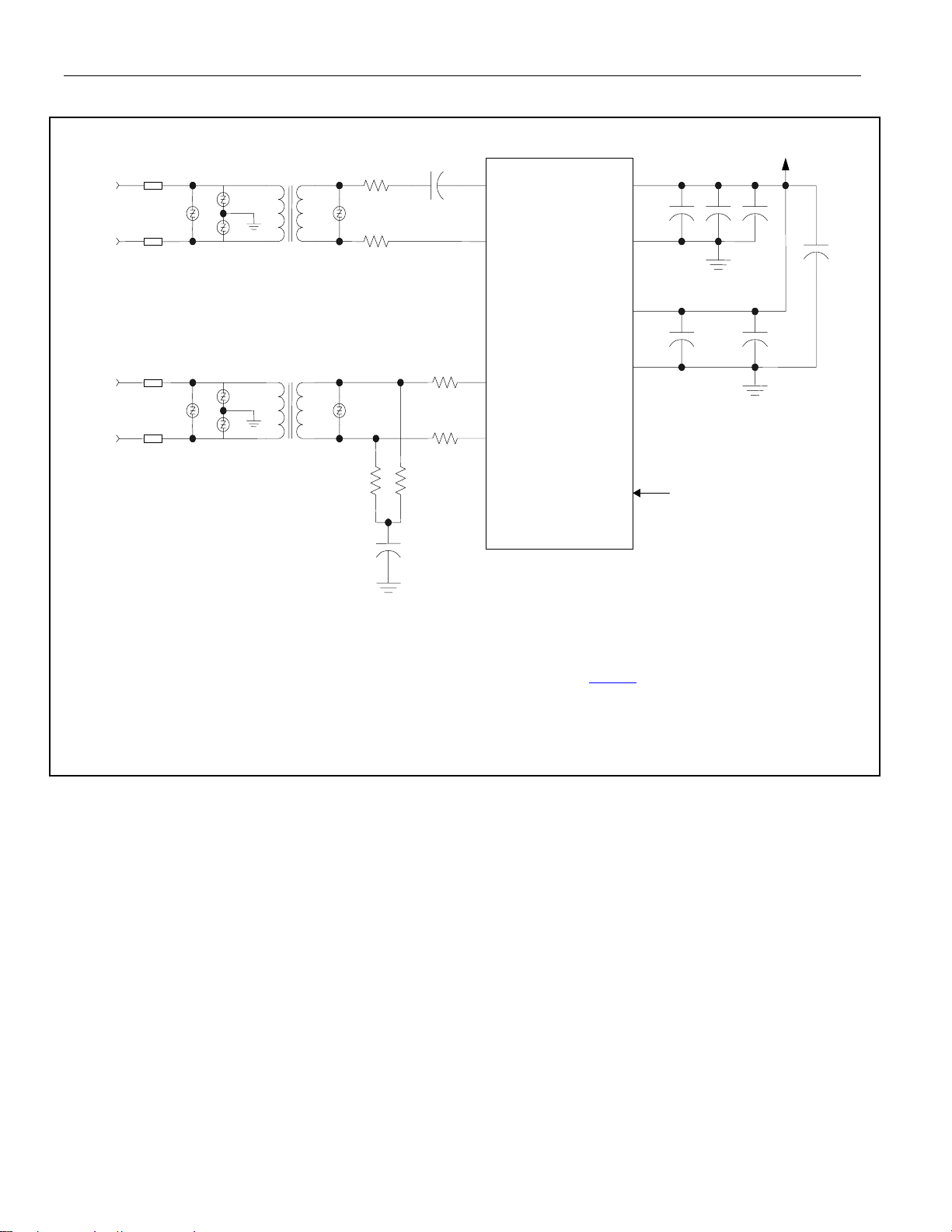

1. BLOCK DIAGRAMS

H

K

T

K

SDI

WR

(R/

W

)

RD(DS

)

(

S)

A0 TO A4

(

)

K

RECEIVE PATH)

K

Figure 1-1. Block Diagram

DS21448 3.3V T1/E1/J1 Quad Line Interface

RRING

RTIP

TRING

TTIP

CHANNEL 4

CHANNEL 3

CHANNEL 2

CHANNEL 1

2

OPTIONAL

TERMINANATION

DD

SS

V

V

2

POWER

CONNECTIONS

ANALOG LOOPBACK

VSM

FILTER

UNFRAMED

ALL-ONES

INSERTION

LINE DRIVERS

PEAK DETECT

CSU FILERS

VCO/PLL

RECOVERY

CLOCK/DATA

WAVESHAPING

JACLK

TYPICAL OF ALL FOUR CHANNELS

MCLK

MUX

JITTER

ATTENUATOR

DUAL MODE

n

2.048MHz TO

1.544MHz PLL

16.384MHz OR

8.192MHz OR

4.096MHz OR

2.048MHz

SYNTHESIZER

MUX

See Figure 1-2

REMOTE LOOPBAC

BPCLK

RPOS

RCLK

RNEG

PBEO

REMOTE LOOPBACK

JITTER ATTENUATION

LOCAL LOOPBAC

(CAN BE PLACED IN EITHER TRANSM IT OR

MUX

See Figure 1-3

RCL/LOTC

TPOS

TCLK

TNEG

Dallas

RST

TXDIS/TEST

BIS0

MUX (THE SERIAL, PARALLEL, AND HARDWARE INTERFACES

SERIAL

INTERFACE

SHARE DEVICE PINS)

PARALLEL INTERFACE

8

5

SCL

SDO

PBTS

A

ALE

CONTROL AND

(ROUTED TO

ALL BLOCKS)

CS

IN

CONTROL AND TEST

PORT (ROUTED TO

ALL BLOCKS)

JTAG PORT

JTMS

JRST

JTDI

JTCL

JTDO

Semiconductor

DS21448

D0 TO D7/AD0

TO AD7

5 of 60

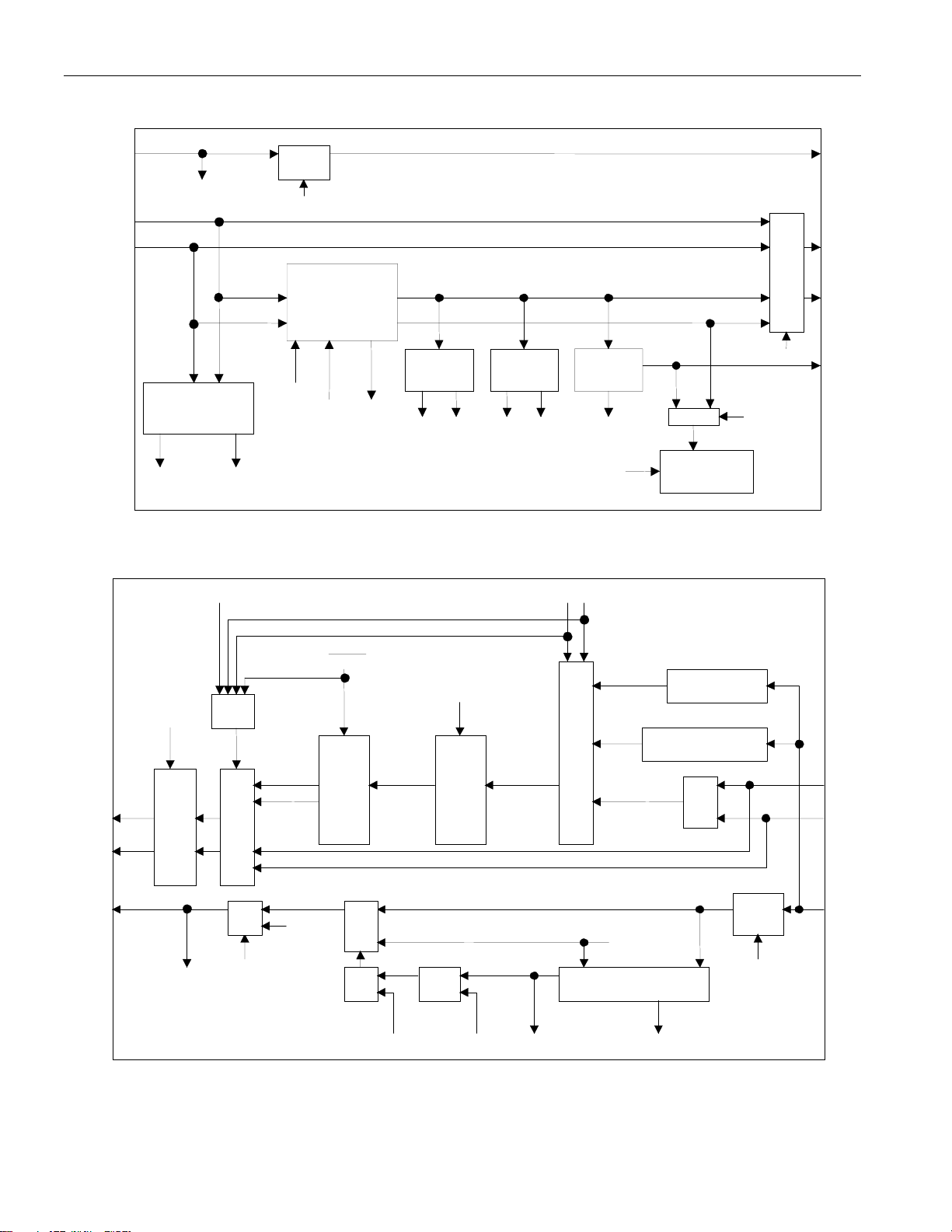

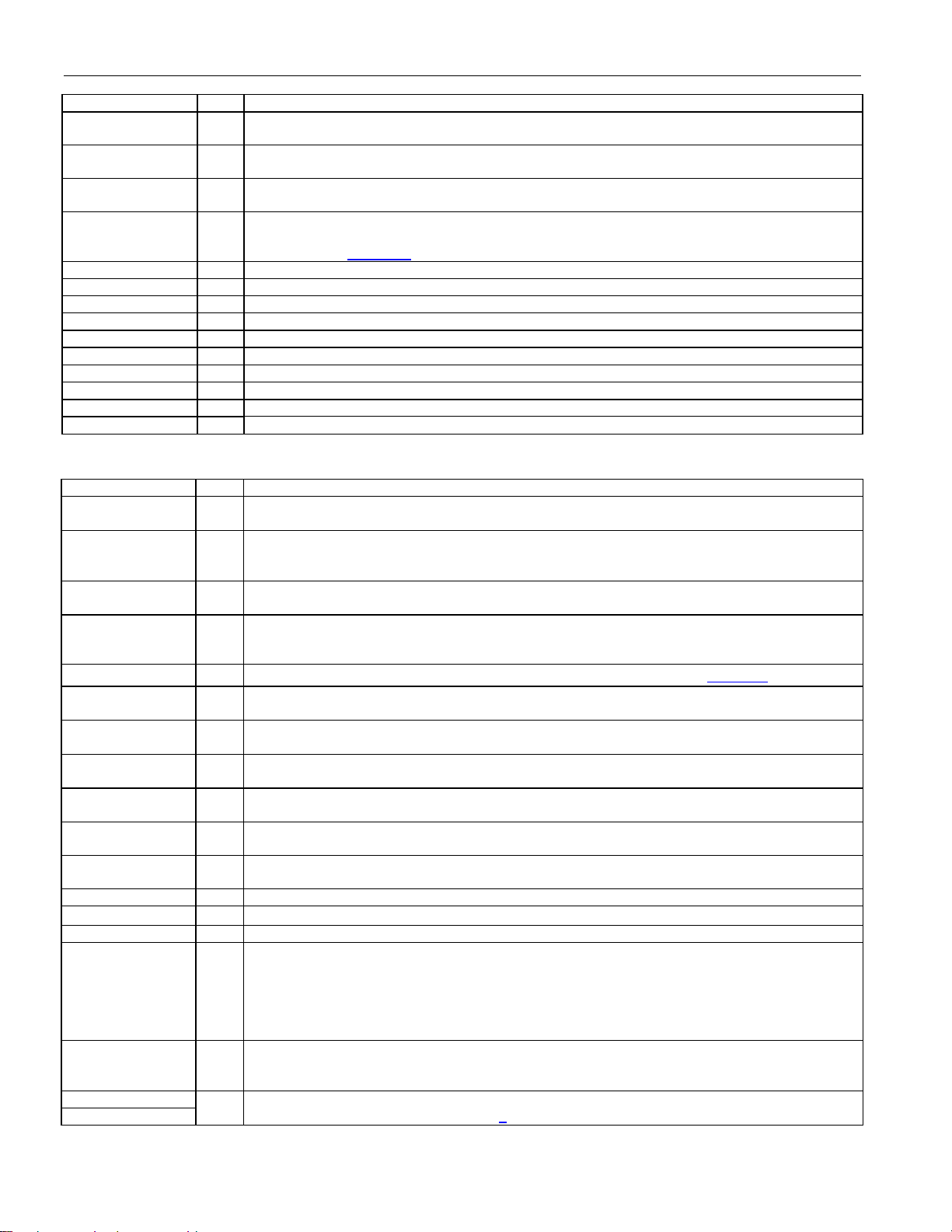

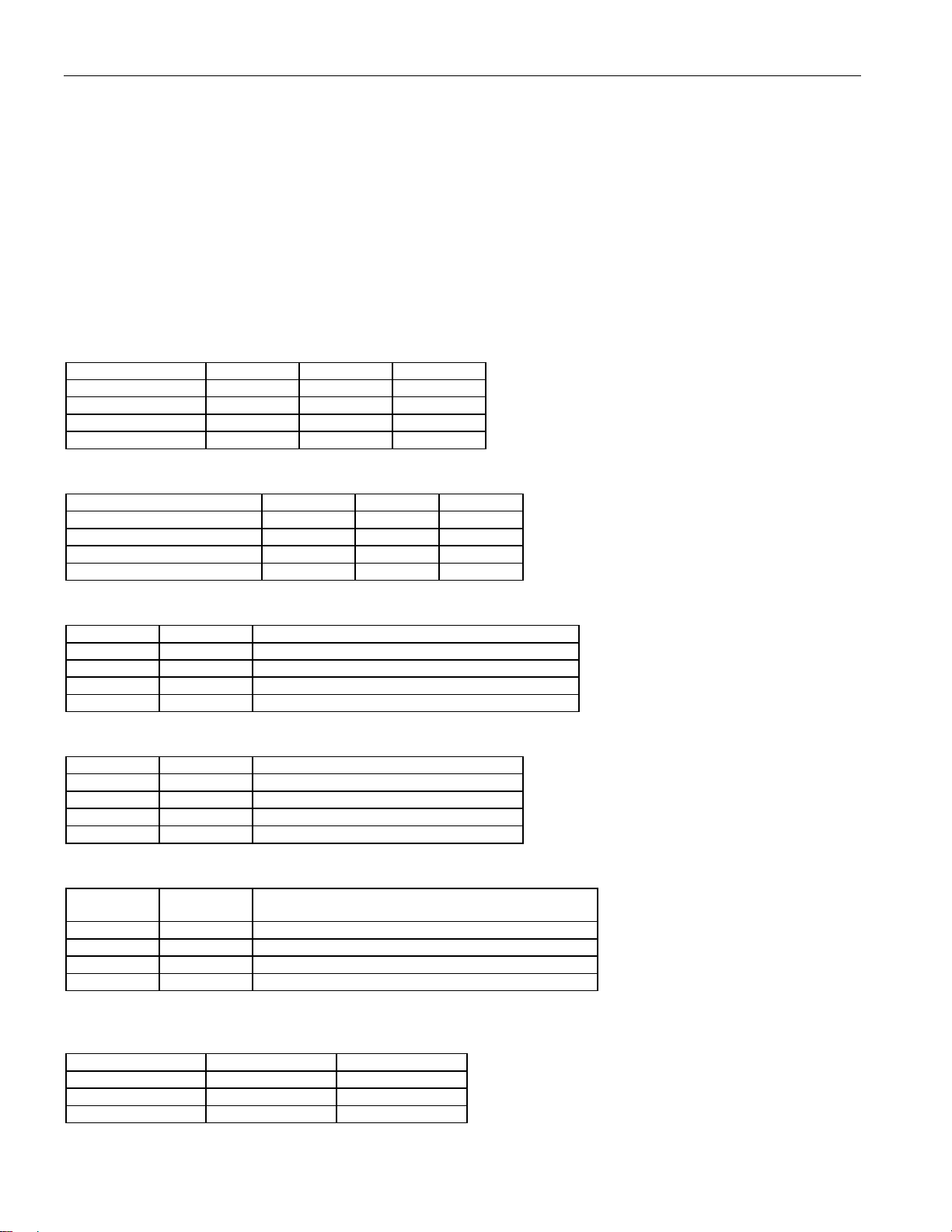

Figure 1-2. Receive Logic Detail

A

K

A

A

DS21448 3.3V T1/E1/J1 Quad Line Interface

CLOCK

INVERT

FROM

REMOTE

LOOPBACK

ROUTED TO

LL BLOCKS

4 OR 8 ZERO DETECT

16 ZERO DETECT

RIR1.7 RIR1.6

CCR2.0

B8ZS/HDB3

DECODER

CCR2.3

CCR6.2/

CCR6.0/

CCR6.1

Figure 1-3. Transmit Logic Detail

CCR1.6

RIR1.5

ALL-ONES

DETECTOR

NRZ DATA

BPV/CV/EXZ

LOOP CODE

DETECTOR

SR.6 SR.7SR.4 RIR1.3

CCR3.3

PRBS

DETECTOR

SR.0

CCR1.4

CCR3.4

MUX

16-BIT ERROR

COUNTER (ECR)

MUX

CCR1.6

CCR6.0

RCLK

RPOS

RNEG

PBEO

TO REMOTE

LOOPBAC

CCR3.1

BPV

INSERT

ROUTED TO

LL BLOCKS

OR

GA TE

MUX

MUX

CCR1.1

CCR2.2

CCR3.0

PRBS

GENERATOR

MUX

1

B8ZS/

HDB3

CODER

LOGIC

ERROR

INSERT

0

0

1

RCLK

MUX

OR

GA TE

CCR1.2

0

1

ND

GATE

CCR1.0

TO LOTC OUTPUT PIN

JACLK

(FROM MCLK)

LOSS-OF-TRANSMIT

CLOCK DETECT

LOOP CODE

GENERATOR

SR.5

OR

GATE

CLOCK

INVERT

CCR2.1

TPOS

TNEG

TCLK

6 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

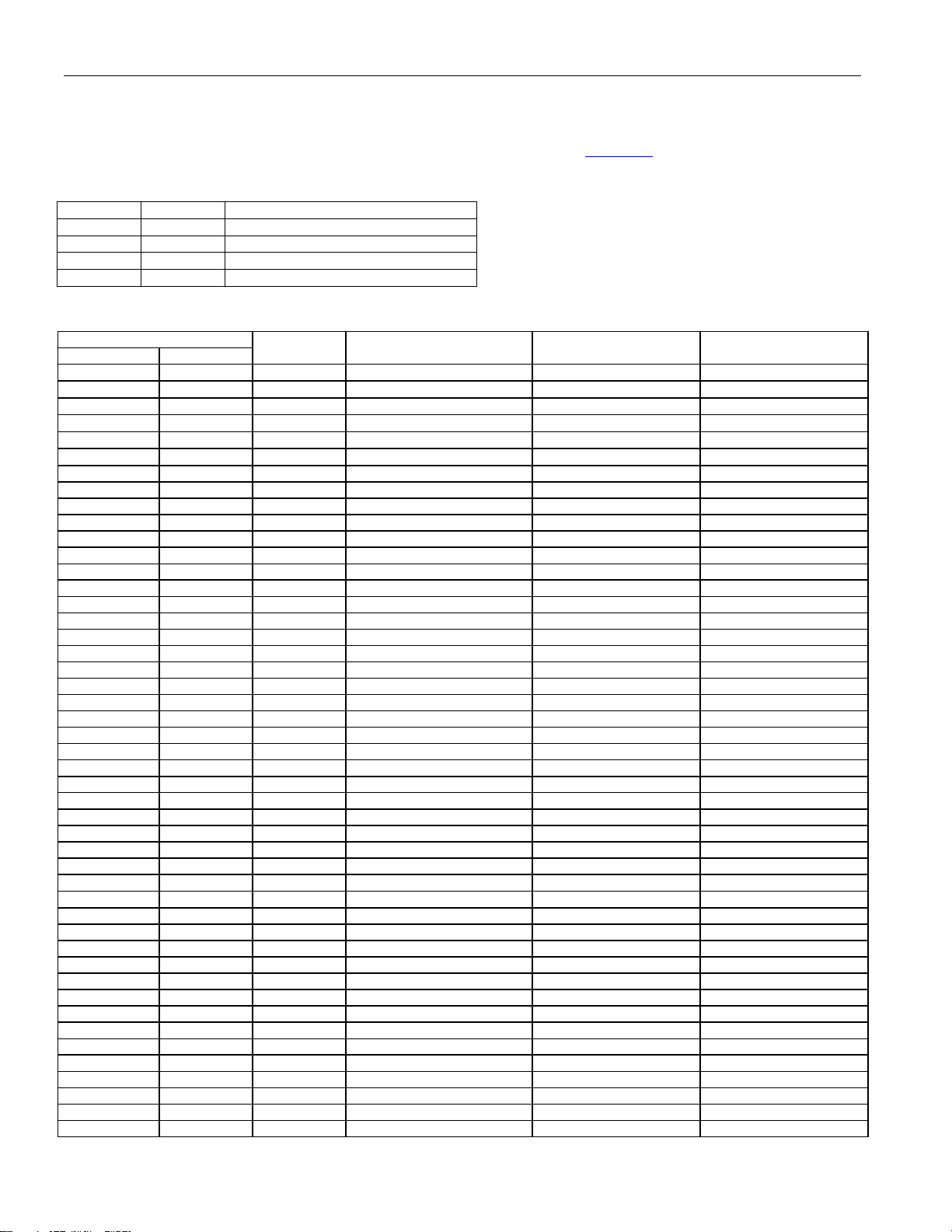

2. PIN DESCRIPTION

The DS21448 can be controlled in parallel port mode, serial port mode, or hardware mode. The bus interface select

bits 0 and 1 (BIS0, BIS1) determine the device mode and pin assignments (Table 2-A

Table 2-A. Bus Interface Selection

BIS1 BIS0 BUS INTERFACE TYPE

0 0 Parallel Port Mode (multiplexed)

0 1 Parallel Port Mode (nonmultiplexed)

1 0 Serial Port Mode

1 1 Hardware Mode

Table 2-B. Pin Assignments

PIN

BGA LQFP

J3 18 I

D3 57 I

D10 84 I

K10 114 I

J2 91 I

H1 92 I

K2 95 I ALE (AS) N/A SCLKE

J1 35 I N/A SCLK L2

K3 36 I N/A SDI L1

K1 62 I/O A4 SDO L0

L1 63 I A3 ICES DJA

H11 64 I A2 OCES JAMUX

H12 65 I A1 N/A JAS

G12 66 I A0 N/A HBE

J10 75 I/O D7/AD7 N/A CES

H10 76 I/O D6/AD6 N/A TPD

G11 77 I/O D5/AD5 N/A TX0

J9 78 I/O D4/AD4 N/A TX1

E3 79 I/O D3/AD3 N/A LOOP0

D4 80 I/O D2/AD2 N/A LOOP1

F3 81 I/O D1/AD1 N/A MM0

D5 82 I/O D0/AD0 N/A MM1

— 3 I VSM VSM VSM

L5 115–117 — VDD1 VDD1 VDD1

E4 19–21 — VDD2 VDD2 VDD2

D8 49–51 — VDD3 VDD3 VDD3

J8 85–87 — VDD4 VDD4 VDD4

M4 118–120 — VSS1 VSS1 VSS1

F4 22–24 — VSS2 VSS2 VSS2

D9 52–54 — VSS3 VSS3 VSS3

H9 88–90 — VSS4 VSS4 VSS4

K9 97 I/O

K5 110 O PBEO1 PBEO1 PBEO1

G3 111 O PBEO2 PBEO2 PBEO2

E10 121 O PBEO3 PBEO3 PBEO3

K8 123 O PBEO4 PBEO4 PBEO4

L6 126 O RCL1/LOTC1 RCL1/LOTC1 RCL1

D7 128 O RCL2/LOTC2 RCL2/LOTC2 RCL2

F9 1 O RCL3/LOTC3 RCL3/LOTC3 RCL3

J7 2 O RCL4/LOTC4 RCL4/LOTC4 RCL4

K7 98 I TXDIS/TEST TXDIS/TEST TXDIS/TEST

A1 124 I RTIP1 RTIP1 RTIP1

A4 28 I RTIP2 RTIP2 RTIP2

A7 60 I RTIP3 RTIP3 RTIP3

A10 93 I RTIP4 RTIP4 RTIP4

B2 125 I RRING1 RRING1 RRING1

B5 29 I RRING2 RRING2 RRING2

I/O PARALLEL PORT MODE SERIAL PORT MODE HARDWARE MODE

CS1 CS1

CS2 CS2

CS3 CS3

CS4 CS4

RD (DS)

WR (R/W)

INT INT

N/A ETS

N/A NRZE

7 of 60

).

EGL1

EGL2

EGL3

EGL4

RT1

DS21448 3.3V T1/E1/J1 Quad Line Interface

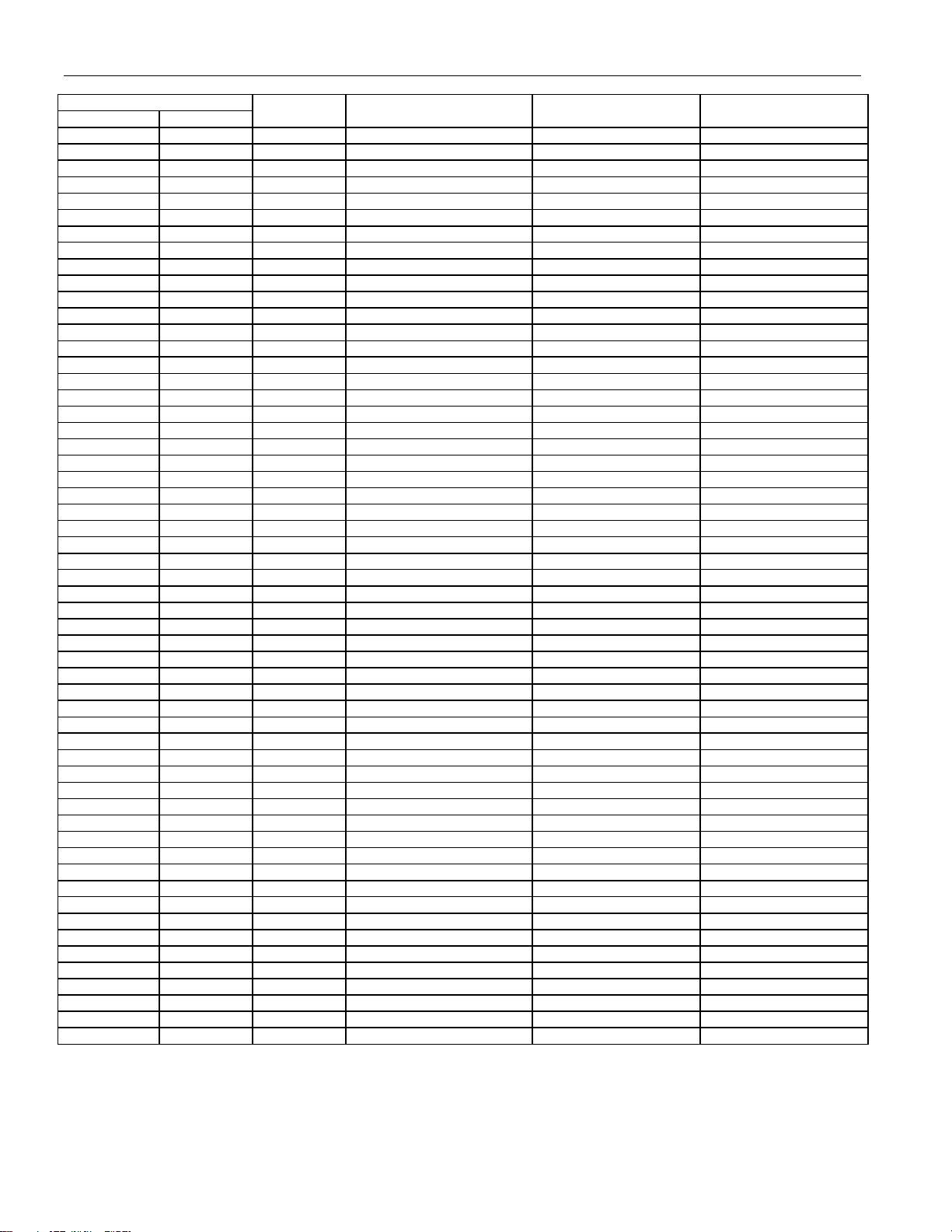

PIN

BGA LQFP

B8 61 I RRING3 RRING3 RRING3

B11 94 I RRING4 RRING4 RRING4

L9 106 I

J6 109 I MCLK MCLK MCLK

H4 122 O BPCLK1 BPCLK1 BPCLK1

D6 47 O BPCLK2 BPCLK2 BPCLK2

F10 56 O BPCLK3 BPCLK3 BPCLK3

L8 112 O BPCLK4 BPCLK4 BPCLK4

L7 107 I BIS0 BIS0 BIS0

M8 68 I BIS1 BIS1 BIS1

A2 6 O TTIP1 TTIP1 TTIP1

A5 38 O TTIP2 TTIP2 TTIP2

A8 71 O TTIP3 TTIP3 TTIP3

A11 102 O TTIP4 TTIP4 TTIP4

J4 7 — TVSS1 TVSS1 TVSS1

D1 39 — TVSS2 TVSS2 TVSS2

E9 72 — TVSS3 TVSS3 TVSS3

L10 103 — TVSS4 TVSS4 TVSS4

J5 8 — TVDD1 TVDD1 TVDD1

D2 40 — TVDD2 TVDD2 TVDD2

G9 73 — TVDD3 TVDD3 TVDD3

M9 104 — TVDD4 TVDD4 TVDD4

B3 9 O TRING1 TRING1 TRING1

B6 41 O TRING2 TRING2 TRING2

B9 74 O TRING3 TRING3 TRING3

B12 105 O TRING4 TRING4 TRING4

K4 10 O RPOS1 RPOS1 RPOS1

E1 12 O RPOS2 RPOS2 RPOS2

D11 14 O RPOS3 RPOS3 RPOS3

K11 16 O RPOS4 RPOS4 RPOS4

G2 11 O RNEG1 RNEG1 RNEG1

E2 13 O RNEG2 RNEG2 RNEG2

F11 15 O RNEG3 RNEG3 RNEG3

M10 25 O RNEG4 RNEG4 RNEG4

H3 127 O RCLK1 RCLK1 RCLK1

F1 31 O RCLK2 RCLK2 RCLK2

E11 58 O RCLK3 RCLK3 RCLK3

L11 96 O RCLK4 RCLK4 RCLK4

G1 26 I TPOS1 TPOS1 TPOS1

F2 30 I TPOS2 TPOS2 TPOS2

E12 33 I TPOS3 TPOS3 TPOS3

M11 55 I TPOS4 TPOS4 TPOS4

H2 27 I TNEG1 TNEG1 TNEG1

M1 32 I TNEG2 TNEG2 TNEG2

D12 34 I TNEG3 TNEG3 TNEG3

K12 59 I TNEG4 TNEG4 TNEG4

M2 17 I TCLK1 TCLK1 TCLK1

L2 43 I TCLK2 TCLK2 TCLK2

F12 83 I TCLK3 TCLK3 TCLK3

L12 113 I TCLK4 TCLK4 TCLK4

M12 108 I PBTS N/A RT0

L3 42 I JTRST JTRST JTRST

M3 48 I JTMS JTMS JTMS

M5 44 I JTCLK JTCLK JTCLK

M6 45 I JTDI JTDI JTDI

M7 46 O JTDO JTDO JTDO

Note 1: The VSM signal is not available with the BGA package option.

Note 2: The LQFP no-connect pin numbers are 4, 5, 37, 67, 69, 70, and 99–101.

Note 3: The BGA no-connect pin numbers are A3, A6, A9, A12, B1, B4, B7, B10, C1–C12, E5–E8, F5–F8, G4–G8, G10, H5–H8, J11, J12, K6,

and L4.

I/O PARALLEL PORT MODE SERIAL PORT MODE HARDWARE MODE

HRST HRST HRST

8 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

Table 2-C. Parallel Interface Mode Pin Description

PIN I/O FUNCTION

Read Input (Data Strobe). RD and DS are active-low signals. DS is active low when in

RD (DS)

WR (R/W)

ALE (AS) I

A4–A0 I

D7/AD7–D0/AD0 I/O

INT

TXDIS/TEST I

HRST

MCLK I

BIS0/BIS1 I Bus Interface Select Bit 0 and 1. Used to select bus interface option. See Table 2-A for details.

PBTS I

CS1–CS4

PBEO1–PBEO4 O

RCL1/LOTC1–

RCL4/LOTC4

RTIP1–RTIP4 I

RRING1–RRING4 I

BPCLK1–BPCLK4 O

TTIP1–TTIP4 O

TRING1–TRING4 O

RPOS1–RPOS4 O

RNEG1–RNEG4 O

I

nonmultiplexed, Motorola mode. See the bus timing diagrams in Section 10

I

Write Input (Read/Write). WR is an active-low signal. See the bus timing diagrams in Section 10.

Address Latch Enable (Address Strobe). When using multiplexed bus mode (BIS0 = 0), this pin

serves to demultiplex the bus on a positive-going edge. In nonmultiplexed bus mode (BIS0 = 1),

ALE should be wired low.

Address Bus. In nonmultiplexed bus operation (BIS0 = 1), these pins serve as the address bus.

In multiplexed bus operation (BIS0 = 0), these pins are not used and should be wired low.

Data Bus/Address/Data Bus. In nonmultiplexed bus operation (BIS0 = 1), these pins serve as the

data bus. In multiplexed bus operation (BIS0 = 0), these pins serve as an 8-bit multiplexed

address/data bus.

Interrupt (INT). The interrupt flags the host controller during conditions and change of conditions

O

defined in the status register. It is an active-low, open-drain output.

Tri-State Control, Multifunctional. Set this pin high, with all CS1–CS4 inputs inactive, to tri-state

TTIP1–TTIP4 and TRING1–TRING4. Set this pin high with any of the CS1–CS4 inputs active to

tri-state all outputs and I/O pins (including the parallel control port). Set low for normal operation.

Hardware Reset. Bringing HRST low resets the DS21448, setting all control bits to the all-zeros

I

default state.

Master Clock. A 2.048MHz (±50ppm) clock source with TTL levels is applied at this pin. This

clock is used internally for both clock/data recovery and for jitter attenuation. Use of a T1

1.544MHz clock source is optional (Note 1).

Parallel Bus Type Select. When using the parallel port, set PBTS high to select Motorola bus

timing; set low to select Intel bus timing. This pin controls the function of the RD (DS), ALE (AS),

and WR (R/W) pins.

Chip Select 1. Must be low to read or write to channel 1 of the device. CS1 is an active-low

signal.

Chip Select 2. Must be low to read or write to channel 2 of the device. CS2 is an active-low

signal.

I

Chip Select 3. Must be low to read or write to channel 3 of the device. CS3 is an active-low

signal.

Chip Select 4. Must be low to read or write to channel 4 of the device. CS4 is an active-low

signal.

PRBS Bit-Error Output. The receiver constantly searches for a 215 - 1 (E1) or a QRSS (T1)

PRBS, depending on the ETS bit setting (CCR1.7). It remains high if it is out of synchronization

with the PRBS pattern. It goes low when synchronized to the PRBS pattern. Any errors in the

received pattern after synchronization cause a positive-going pulse (with same period as E1 or

T1 clock) synchronous with RCLK. PRBS bit errors can also be reported to the ECR1 and ECR2

registers by setting CCR6.2 to logic 1.

Receive Carrier Loss/Loss-of-Transmit Clock. An output that toggles high during a receive carrier

O

loss (CCR2.7 = 0) or toggles high if the TCLK pin has not been toggled for 5ms ± 2ms (CCR2.7 =

1). CCR2.7 defaults to logic 0 when in hardware mode.

Receive Tip and Ring. Analog inputs for clock recovery circuitry. These pins connect through a

1:1 transformer to the line. See Section 7 for details.

Backplane Clock. A 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz clock output that is

referenced to RCLK selectable through CCR5.7 and CCR5.6.

Transmit Tip and Ring. Analog line-driver outputs. These pins connect through a step-up

transformer to the line. See Section 7 for details.

Receive Positive Data. These bits are updated on the rising edge (CCR2.0 = 0) or the falling

edge (CCR2.0 = 1) of RCLK with bipolar data out of the line interface. Set NRZE (CCR1.6) to 1

for NRZ applications. In NRZ mode, data is output on RPOS, and a received error (BPV, CV, or

EXZ) causes a positive-going pulse synchronous with RCLK at RNEG.

Receive Negative Data. Updated on the rising edge (CCR2.0 = 0) or the falling edge (CCR2.0 =

1) of RCLK with the bipolar data out of the line interface. Set NRZE (CCR1.6) to 1 for NRZ

applications. In NRZ mode, data is output on RPOS, and a received error (BPV, CV, or EXZ)

causes a positive-going pulse synchronous with RCLK at RNEG.

.

9 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

PIN I/O FUNCTION

RCLK1–RCLK4 O

TPOS1–TPOS4 I

TNEG1–TNEG4 I

TCLK1–TCLK4 I

JTRST I JTAG Reset

JTMS I JTAG Mode Select

JTCLK I JTAG Clock

JTDI I JTAG Data In

JTDO O JTAG Data Out

VSM I Voltage Supply Mode (LQFP only). Should be wired low for correct operation.

TVDD1–TVDD4 — 3.3V, ±5% Transmitter Positive Supply

VDD1–VDD4 — 3.3V, ±5% Positive Supply

TVSS1–TVSS4 — Transmitter Signal Ground

VSS1–VSS4 — Signal Ground

Receive Clock. Buffered recovered clock from the line. Synchronous to MCLK in absence of

signal at RTIP and RRING.

Transmit Positive Data. Sampled on the falling edge (CCR2.1 = 0) or the rising edge

(CCR2.1 = 1) of TCLK for data to be transmitted out onto the line.

Transmit Negative Data. Sampled on the falling edge (CCR2.1 = 0) or the rising edge

(CCR2.1 = 1) of TCLK for data to be transmitted out onto the line.

Transmit Clock. A 2.048MHz or 1.544MHz primary clock. It is used to clock data through the

transmit-side formatter. It can be sourced internally by MCLK or RCLK. See Common Control

Register 1 and Figure 1-3

.

Table 2-D. Serial Interface Mode Pin Description

PIN I/O FUNCTION

Interrupt (INT). Flags host controller during conditions and change of conditions defined in the

INT

TXDIS/TEST I

HRST

MCLK I

BIS0/BIS1 I Bus Interface Select Bit 0 and 1. Used to select bus interface option. See Table 2-A for details.

CS1

CS2

CS3

CS4

ICES I

OCES I

SCLK I Serial Clock. Serial interface clock.

SDI I Serial Data Input. Serial interface data input.

SDO O Serial Data Output. Serial interface data output.

PBEO1–PBEO4 O

RCL1/LOTC1–

RCL4/LOTC4

RTIP1–RTIP4

RRING1–RRING4

I/O

status register. Active-low, open-drain output.

Tri-State Control, Multifunctional. Set this pin high with all CS1–CS4 inputs inactive to tri-state

TTIP1–TTIP4 and TRING1–TRING4. Set this pin high with any of the CS1–CS4 inputs active to

tri-state all outputs and I/O pins (including the parallel control port). Set low for normal operation.

Hardware Reset. Bringing HRST low resets the DS21448, setting all control bits to the all-zeros

I

default state.

Master Clock. A 2.048MHz (±50ppm) clock source with TTL levels is applied at this pin. This

clock is used internally for both clock/data recovery and for jitter attenuation. A T1 1.544MHz

clock source is optional (Note 1).

Chip Select 1. Must be low to read or write to channel 1 of the device. CS1 is an active-low

I

signal.

Chip Select 2. Must be low to read or write to channel 2 of the device. CS2 is an active-low

I

signal.

Chip Select 3. Must be low to read or write to channel 3 of the device. CS3 is an active-low

I

signal.

Chip Select 4. Must be low to read or write to channel 4 of the device. CS4 is an active-low

I

signal.

Input Clock-Edge Select. Selects whether the serial interface data input (SDI) is sampled on the

rising (ICES = 0) or falling edge (ICES = 1) of SCLK.

Output Clock-Edge Select. Selects whether the serial interface data output (SDO) changes on

the rising (OCES = 1) or falling edge (OCES = 0) of SCLK.

PRBS Bit-Error Output. The receiver constantly searches for a 215 - 1 (E1) or a QRSS (T1)

PRBS, depending on the ETS bit setting (CCR1.7). It remains high if it is out of synchronization

with the PRBS pattern. It goes low when synchronized to the PRBS pattern. Any errors in the

received pattern after synchronization cause a positive-going pulse (with same period as E1 or

T1 clock) synchronous with RCLK. PRBS bit errors can also be reported to the ECR1 and ECR2

registers by setting CCR6.2 to logic 1.

Receive Carrier Loss/Loss-of-Transmit Clock. An output that toggles high during a receive carrier

O

loss (CCR2.7 = 0) or toggles high if the TCLK pin has not been toggled for 5ms ± 2ms

(CCR2.7 = 1). CCR2.7 defaults to logic 0 when in hardware mode.

Receive Tip and Ring. Analog inputs for clock recovery circuitry. These pins connect through a

I

1:1 transformer to the line. See Section 7

for details.

10 of 60

PIN I/O FUNCTION

BPCLK1–BPCLK4 O

TTIP1–TTIP4 O

TRING–TRING4 O

RPOS1–RPOS4 O

RNEG1–RNEG4 O

RCLK1–RCLK4 O

TPOS1–TPOS4 I

TNEG1–TNEG4 I

TCLK1–TCLK4 I

JTRST I JTAG Reset

JTMS I JTAG Mode Select

JTCLK I JTAG Clock

JTDI I JTAG Data In

JTDO O JTAG Data Out

VSM I Voltage Supply Mode (LQFP only). VSM should be wired low for correct operation.

TVDD1–TVDD4 — 3.3V, ±5% Transmitter Positive Supply

VDD1–VDD4 — 3.3V, ±5% Positive Supply

TVSS1–TVSS4 — Transmitter Signal Ground for Transmitter Outputs

VSS1–VSS4 — Signal Ground

Backplane Clock. A 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz clock output that is

referenced to RCLK selectable through CCR5.7 and CCR5.6.

Transmit Tip and Ring. Analog line-driver outputs. These pins connect through a step-up

transformer to the line. See Section 7

Receive Positive Data. Updated on the rising edge (CCR2.0 = 0) or the falling edge (CCR2.0 = 1)

of RCLK with bipolar data out of the line interface. Set NRZE (CCR1.6) to 1 for NRZ applications.

In NRZ mode, data is output on RPOS, and a received error (BPV, CV, or EXZ) causes a

positive-going pulse synchronous with RCLK at RNEG.

Receive Negative Data. Updated on the rising edge (CCR2.0 = 0) or the falling edge (CCR2.0 =

1) of RCLK with the bipolar data out of the line interface. Set NRZE (CCR1.6) to 1 for NRZ

applications. In NRZ mode, data is output on RPOS, and a received error (BPV, CV, or EXZ)

causes a positive-going pulse synchronous with RCLK at RNEG.

Receive Clock. Buffered recovered clock from the line. Synchronous to MCLK in absence of

signal at RTIP and RRING.

Transmit Positive Data. Sampled on the falling edge (CCR2.1 = 0) or the rising edge (CCR2.1 =

1) of TCLK for data to be transmitted out onto the line.

Transmit Negative Data. Sampled on the falling edge (CCR2.1 = 0) or the rising edge (CCR2.1 =

1) of TCLK for data to be transmitted out onto the line.

Transmit Clock. A 2.048MHz or 1.544MHz primary clock used to clock data through the transmit

side formatter. They can be sourced internally by MCLK or RCLK. See Common Control Register

1 and Figure 1-3.

for details.

Table 2-E. Hardware Interface Mode Pin Description

PIN I/O FUNCTION

E1/T1 Select

ETS I

NRZE I

SCLKE I

DJA I

JAMUX I

JAS I

HBE I

L0/L1/L2 I

0 = E1

1 = T1

NRZ Enable

0 = bipolar data at RPOS/RNEG and TPOS/TNEG

1 = NRZ data at RPOS and TPOS or TNEG; RNEG outputs a positive-going pulse when the

device receives a BPV, CV, or EXZ.

Receive and Transmit Synchronization Clock Enable. SCLKE combines RSCLKE (CCR5.3) and

TSCLKE (CCR5.2).

0 = disable 2.048MHz synchronization transmit and receive mode

1 = enable 2.048MHz synchronization transmit and receive mode

Disable Jitter Attenuator

0 = jitter attenuator enabled

1 = jitter attenuator disabled

Jitter Attenuator Clock Mux. Controls the source for JACLK.

0 = JACLK sourced from MCLK (2.048MHz or 1.544MHz at MCLK).

1 = JACLK sourced from internal PLL (2.048 MHz at MCLK).

Jitter Attenuator Path Select

0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

Receive and Transmit HDB3/B8ZS Enable. HBE combines RHBE (CCR2.3) and THBE

(CCR2.2).

0 = enable HDB3 (E1)/B8ZS (T1)

1 = disable HDB3 (E1)/B8ZS (T1)

Line Build-Out Select Bits 0,1, and 2. These pins set the transmitter build-out; see (Table 7-A

(E1) and Table 7-B

(T1).

DS21448 3.3V T1/E1/J1 Quad Line Interface

11 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

PIN I/O FUNCTION

Receive and Transmit Clock Select. Selects which RCLK edge to update RPOS and RNEG and

CES I

TPD I

TX0/TX1 I

LOOP0/LOOP1 I Loopback Select Bits 0 and 1. These inputs determine the active loopback mode (Table 4-A).

MM0/MM1 I

RT1/RT0 I

TEST I

HRST

MCLK I

BIS0/BIS1 I Bus Interface Select Bit 0 and 1. Used to select bus interface option (Table 2-A).

EGL1–EGL4 I

PBEO1–PBEO4 O

RCL1–RCL4 O Receive Carrier Loss. An output that toggles high during a receive carrier loss.

RTIP1–RTIP4 I

RRING1–RRING4 I

BPCLK1–BPCLK4 O Backplane Clock. A 16.384MHz clock output that is referenced to RCLK.

TTIP1–TTIP4

TRING1–TRING4

RPOS1–RPOS4 O

RNEG1–RNEG4 O

RCLK1–RCLK4 O

TPOS1–TPOS4 I

TNEG1–TNEG4 I

TCLK1–TCLK4 I

JTRST I JTAG Reset

JTMS I JTAG Mode Select

JTCLK I JTAG Clock

JTDI I JTAG Data In

JTDO O JTAG Data Out

VSM I Voltage Supply Mode (LQFP only). VSM should be wired low for correct operation.

TVDD1–TVDD4 – 3.3V, ±5% Transmitter Positive Supply

VDD1–VDD4 — 3.3V, ±5% Positive Supply

which TCLK edge to sample TPOS and TNEG. CES combines TCES and RCES.

0 = update RPOS/RNEG on rising edge of RCLK; sample TPOS/TNEG on falling edge of TCLK

1 = update RPOS/RNEG on falling edge of RCLK; sample TPOS/TNEG on rising edge of TCLK

Transmit Power-Down

0 = normal transmitter operation

1 = powers down the transmitter and tri-states TTIP and TRING pins

Transmit Data Source Select Bits 0 and 1. These inputs determine the source of the transmit

).

).

).

).

15

- 1 PRBS (ETS = 0) or a

for details.

for details.

.

data (Table 4-B

Monitor Mode Select Bits 0 and 1. These inputs determine if the receive equalizer is in a monitor

mode (Table 4-D

Receive LIU Termination Select Bits 0 and 1. These inputs determine the receive termination

(Table 4-E

Tri-State Control. Set high to tri-state all outputs and I/O pins (including the parallel control port).

Set low for normal operation. Useful in board-level testing.

Hardware Reset. Bringing HRST low resets the DS21448, setting all control bits to the all-zero

I

default state.

Master Clock. A 2.048MHz (±50ppm) clock source with TTL levels is applied at this pin. This

clock is used internally for both clock/data recovery and for jitter attenuation. A T1 1.544MHz

clock source is optional (Note 1). See Table 4-F for details.

Receive Equalizer Gain-Limit Select. These bits control the sensitivity of the receive equalizers

(Table 4-C

PRBS Bit-Error Output. The receiver constantly searches for a 2

QRSS PRBS (ETS = 1). The pattern is chosen automatically by the value of the ETS pin. It

remains high if it is out of synchronization with the PRBS pattern. It goes low when synchronized

to the PRBS pattern. Any errors in the received pattern after synchronization cause a positivegoing pulse (with same period as E1 or T1 clock) synchronous with RCLK.

Receive Tip and Ring. Analog inputs for clock recovery circuitry. These pins connect through a

1:1 transformer to the line. See Section 7

Transmit Tip and Ring. Analog line-driver outputs. These pins connect through a step-up

O

transformer to the line. See Section 7

Receive Positive Data. Updated on the rising edge (CES = 0) or the falling edge (CES = 1) of

RCLK with bipolar data out of the line interface. In NRZ mode (NRZE = 1), data is output on

RPOS, and a received error (BPV, CV, or EXZ) causes a positive-going pulse synchronous with

RCLK at RNEG.

Receive Negative Data. Updated on the rising edge (CES = 0) or the falling edge (CES = 1) of

RCLK with bipolar data out of the line interface. In NRZ mode (NRZE = 1), data is output on

RPOS, and a received error (BPV, CV, or EXZ) causes a positive-going pulse synchronous with

RCLK at RNEG.

Receive Clock. Buffered recovered clock from the line. Synchronous to MCLK in absence of

signal at RTIP and RRING.

Transmit Positive Data. Sampled on the falling edge (CES = 0) or the rising edge (CES = 1) of

TCLK for data to be transmitted out onto the line.

Transmit Negative Data. Sampled on the falling edge (CES = 0) or the rising edge (CES = 1) of

TCLK for data to be transmitted out onto the line.

Transmit Clock. A 2.048MHz or 1.544MHz primary clock used to clock data through the transmit

side formatter. It can be sourced internally by MCLK or RCLK. See Common Control Register 1

and Figure 1-3

12 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

PIN I/O FUNCTION

TVSS1–TVSS4 — Transmitter Signal Ground for Transmitter Outputs

VSS1–VSS4 — Signal Ground

Note 1: G.703 requires an accuracy of ±50ppm for T1 and E1. TR62411 and ANSI specs require ±32ppm accuracy for T1 interfaces.

3. DETAILED DESCRIPTION

The DS21448 contains four independent LIUs that share a common interface for configuration and status. The user

can choose between three different means of accessing the device: a parallel microprocessor interface, a serial

interface, and a hardwired mode, which configures the device by setting levels on the device’s pins. The

DS21448’s four chip selects (

CS1, CS2, CS3, and CS4) determine which LIU is accessed when using the parallel

or serial interface modes. Four sets of identical register maps exist, one for each channel. Using the appropriate

chip select accesses a channel’s register map.

The analog AMI/HDB3 waveform off the E1 line or the AMI/B8ZS waveform off the T1 line is transformer-coupled

into the RTIP and RRING pins of the DS21448. The user has the option to use internal termination, software

selectable for 75W/100W/120W applications, or external termination. The device recovers clock and data from the

analog signal and passes it through the jitter attenuation mux, outputting the received line clock at RCLK and

bipolar or NRZ data at RPOS and RNEG. The DS21448 contains an active filter that reconstructs the analogreceived signal for the nonlinear losses that occur in transmission. The receive circuitry is also configurable for

various monitor applications. The device has a usable receive sensitivity of 0 to -43dB for E1 and 0 to -36dB for T1

that allows the device to operate on 0.63mm (22AWG) cables up to 2.5km (E1) and 6k feet (T1) in length. Data

input at TPOS and TNEG is sent through the jitter attenuation mux to the waveshaping circuitry and line driver. The

DS21448 drives the E1 or T1 line from the TTIP and TRING pins through a coupling transformer. The line driver

can handle both CEPT 30/ISDN-PRI lines for E1 and long-haul (CSU) or short-haul (DSX-1) lines for T1.

3.1 DS21448 and DS21Q348 Differences

The DS21448 BGA is a monolithic quad-port LIU that is a replacement for the DS21Q348. The additional features

of JTAG, transmit driver disable, and the serial interface in the DS21448 have changed the function of several pins,

as shown in Table 3-A

.

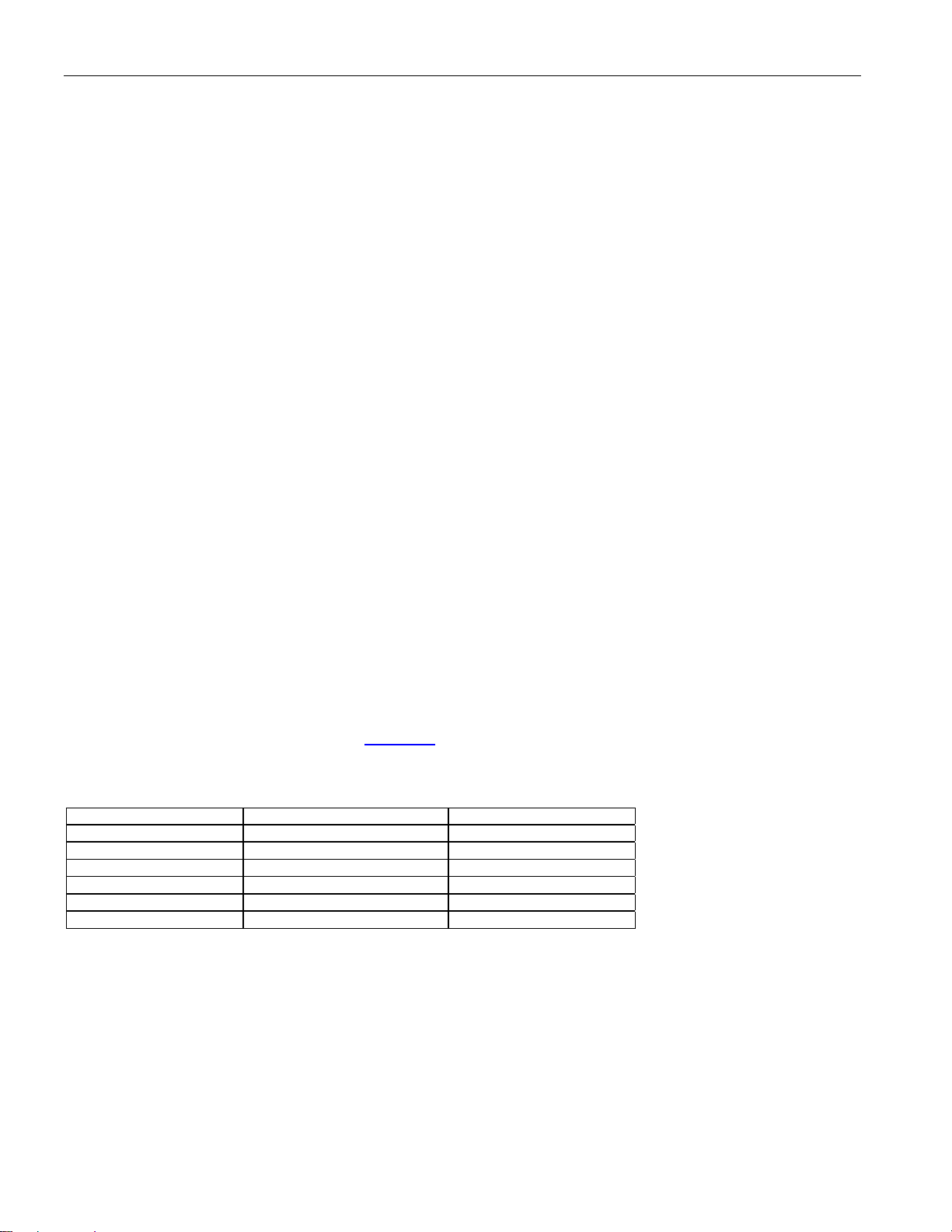

Table 3-A. DS21448 vs. DS21Q348 Pin Differences

PIN DS21Q348 DS21448

G4 VSM N.C.

J1 VSS SCLK

K1 A4 A4/SDO

K3 VSS SDI

K7 TEST TXDIS/TEST

L3 N.C. JTRST*

M3 N.C. JTMS*

M5 N.C. JTCLK

M6 N.C. JTDI*

M7 N.C. JTDO

*DS21448 pin is internally pulled up.

4. PORT OPERATION

4.1 Hardware Mode

The DS21448 supports a hardware configuration mode that allows the user to configure the device by setting levels

on the device’s pins. This mode allows the DS21448 configuration without the use of a microprocessor, simplifying

designs. Not all of the device features are supported in the hardware mode.

In hardware mode (BIS0 = 1, BIS1 = 1) several pins have been redefined so they can be used for initializing the

DS21448. Refer to Table 2-B

and Table 2-E for pin assignment and definition. Because of limited pin count, several

13 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

functions have been combined and affect all four channels in the device and/or treat the receive and transmit paths

as one block. Restrictions when using the hardware mode include the following:

· BPCLK pins only output a 16.384MHz signal.

· The RCL/LOTC pins are designated to RCL.

· The RHBE and THBE control bits are combined and controlled by HBE.

· RSCLKE and TSCLKE bits are combined and controlled by SCLKE.

· TCES and RCES are combined and controlled by CES.

· The transmitter functions are combined and controlled by TX1 and TX0.

· Loopback functions are controlled by LOOP1 and LOOP0.

· JABDS defaults to 128-bit buffer depth.

· All other control bits default to logic 0.

Table 4-A. Loopback Control in Hardware Mode

LOOPBACK SYMBOL LOOP1 LOOP0

Remote Loopback RLB 1 1

Local Loopback LLB 1 0

Analog Loopback ALB 0 1

No Loopback — 0 0

Table 4-B. Transmit Data Control in Hardware Mode

TRANSMIT DATA SYMBOL TX1 TX0

Unframed All Ones TUA1 1 1

Alternating Ones and Zeros TAOZ 1 0

TPOS and TNEG — 0 0

PRBS

TPRBSE

0 1

Table 4-C. Receive Sensitivity Settings in Hardware Mode

EGL ETS RECEIVE SENSITIVITY (dB)

0 0 (E1) -12 (short haul)

1 0 (E1) -43 (long haul)

1 1 (T1) -30 (limited long haul)

0 1 (T1) -36 (long haul)

Table 4-D. Monitor Gain Settings in Hardware Mode

MM1 MM0 INTERNAL LINEAR GAIN BOOST (dB)

0 0 Normal operation (no boost)

0 1 20

1 0 26

1 1 32

Table 4-E. Internal Rx Termination Select in Hardware Mode

RT1 RT0

0 0 Internal receive-side termination disabled

0 1 Internal receive-side 120Ω enabled

1 0 Internal receive-side 100Ω enabled

1 1 Internal receive-side 75Ω enabled

INTERNAL RECEIVE

TERMINATION CONFIGURATION

Table 4-F. MCLK Selection in Hardware Mode

MCLK (MHz) JAMUX ETS

2.048 0 0

2.048 1 1

1.544 0 1

14 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

C

(

)

4.2 Serial Port Operation

Setting BIS1 = 1 and BIS0 = 0 enables the serial bus interface on the DS21448 (Table 2-A). Serial port read/write

timing is unrelated to the system transmit and receive timing, allowing asynchronous reads or writes by the host.

See Section 10

Figure 4-2

for the AC timing of the serial port. All serial port accesses are LSB first. See Figure 4-1,

, Figure 4-3, Figure 4-4, Figure 4-5, and Figure 4-6 for additional details.

A serial bus access requires the use of four signals: serial clock (SCLK), one of the four chip selects (

CS), serial

data input (SDI), and serial data output (SDO). The DS21448 uses SCLK to sample data that is present on SDI and

output data onto SDO. Input clock-edge select (ICES) allows the user to choose which SCLK edge input data is

sampled on. Output clock-edge select (OCES) allows the user to choose which SCLK edge output data changes

on. When ICES is low, input data is latched on the rising edge of SCLK, and when ICES is high, input data is

latched on the falling edge of SCLK. When OCES is low, data is output on the falling edge of SCLK, and when

OCES is high, data is output on the rising edge of SCLK. Data is held until the next falling or rising edge of SCLK.

All data transfers are initiated by driving the appropriate port’s

must go inactive between data transfers. See the serial bus timing information in Section 10

transfers are terminated if the port’s

when all

CS pins are inactive.

CS input transitions high. Port control logic is disabled, and SDO is tri-stated

CS input low and ends with CS going inactive. CS

for details. All data

Reading from or writing to the internal registers requires writing one address/command byte prior to the transferring

register data. Two types of serial bus transfers exist, standard and burst. The standard serial bus access always

consists of two bytes, an address/command byte that is always supplied by the user on SDI, and a data byte that

can either be written to the DS21448 using SDI (write operation) or output by the DS21448 on SDO (read

operation). The burst serial bus access consists of a single address/command byte followed either by 22 read or 22

write data bytes.

The first bit written (LSB) of the address/command byte specifies whether the access is to be a read (1) or a write

(0). The next 5 bits identify the register address. Valid register addresses are 00h through 15h. Bit 7 is reserved

and must be set to 0 for proper operation. Bit 8, the last bit (MSB) of the address/command byte, is the burst modeenable bit. When the burst bit is enabled (set to 0) and a READ operation is performed, the DS21448 automatically

outputs the contents of registers 00h through 15h sequentially, starting with register address 00h. When the burst

bit is enabled and a WRITE operation is performed, data supplied on SDI is sequentially written into the DS21448’s

register space starting at address 00h. Burst operation is stopped once address 15h is read or

CS goes inactive.

For both burst read and burst write transfers, the address/command byte’s register address bits must be set to 0.

The user can broadcast register write accesses to multiple ports simultaneously by enabling the desired channels’

chip selects at the same time. However, only one port can be read at a time. Any attempt to read multiple ports

simultaneously results in invalid data being returned on SDO.

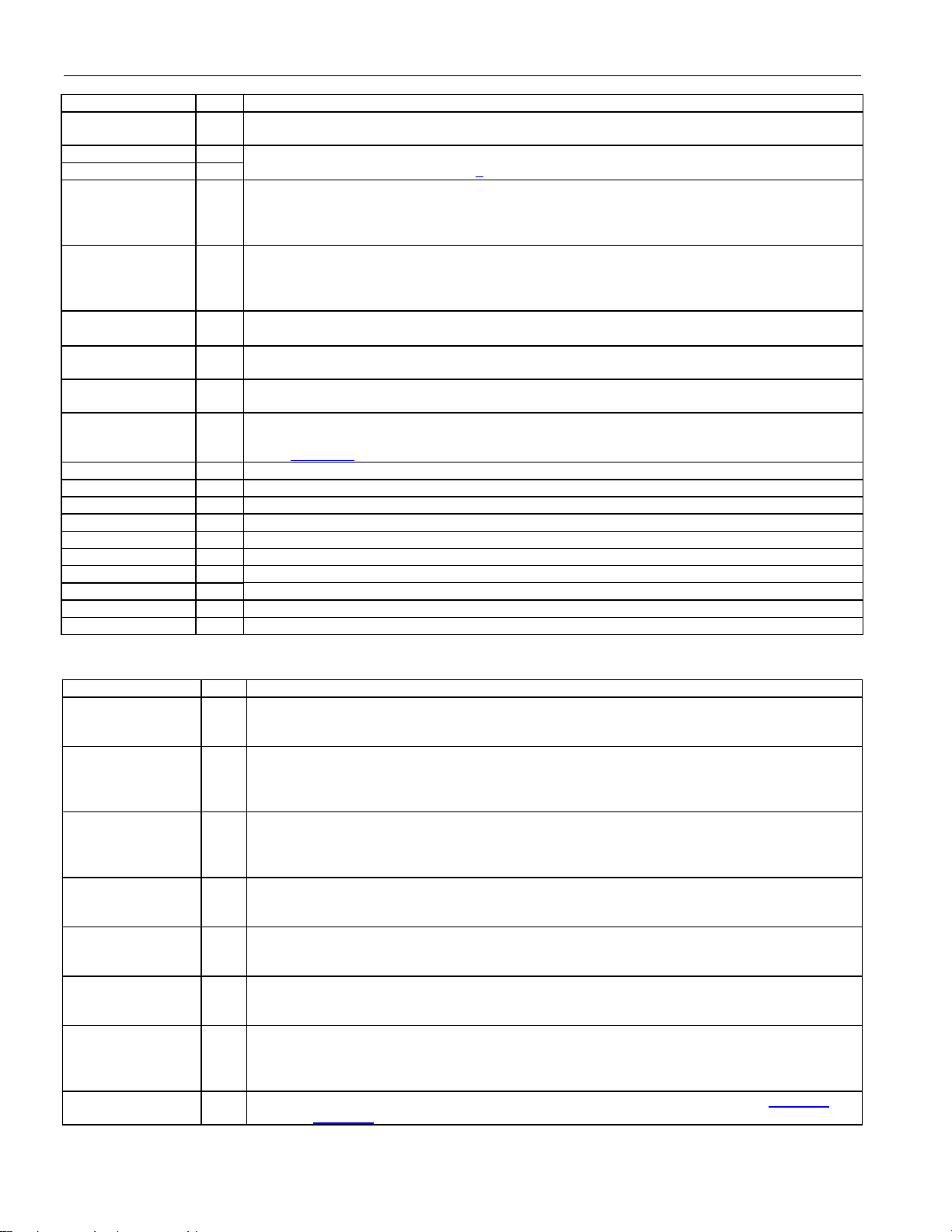

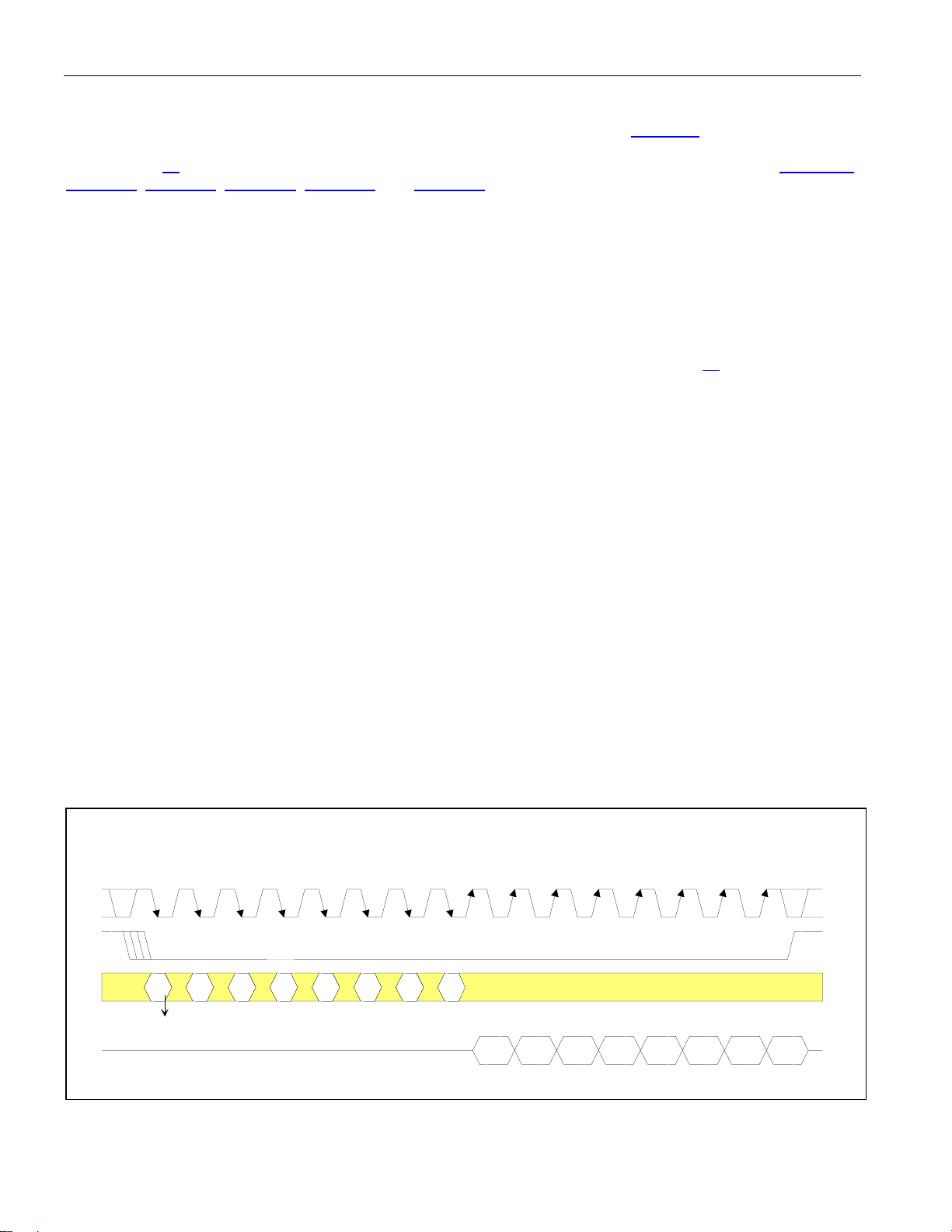

Figure 4-1. Serial Port Operation for Read Access (R = 1) Mode 1

ICES = 1 (SAMPLE SDI ON THE FALLING EDGE OF SCLK)

OCES = 1 (UPDATE SDO ON RISING EDGE OF SCLK)

SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

S

SDI

(LSB)

SDO

A1 A2 A3 A4 A5 0 B

1

READ ACCESS ENABLED

(MSB)

D0

D1 D2 D3 D4 D5 D6

LSB

D7

(MSB)

15 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

C

(

)

C

C

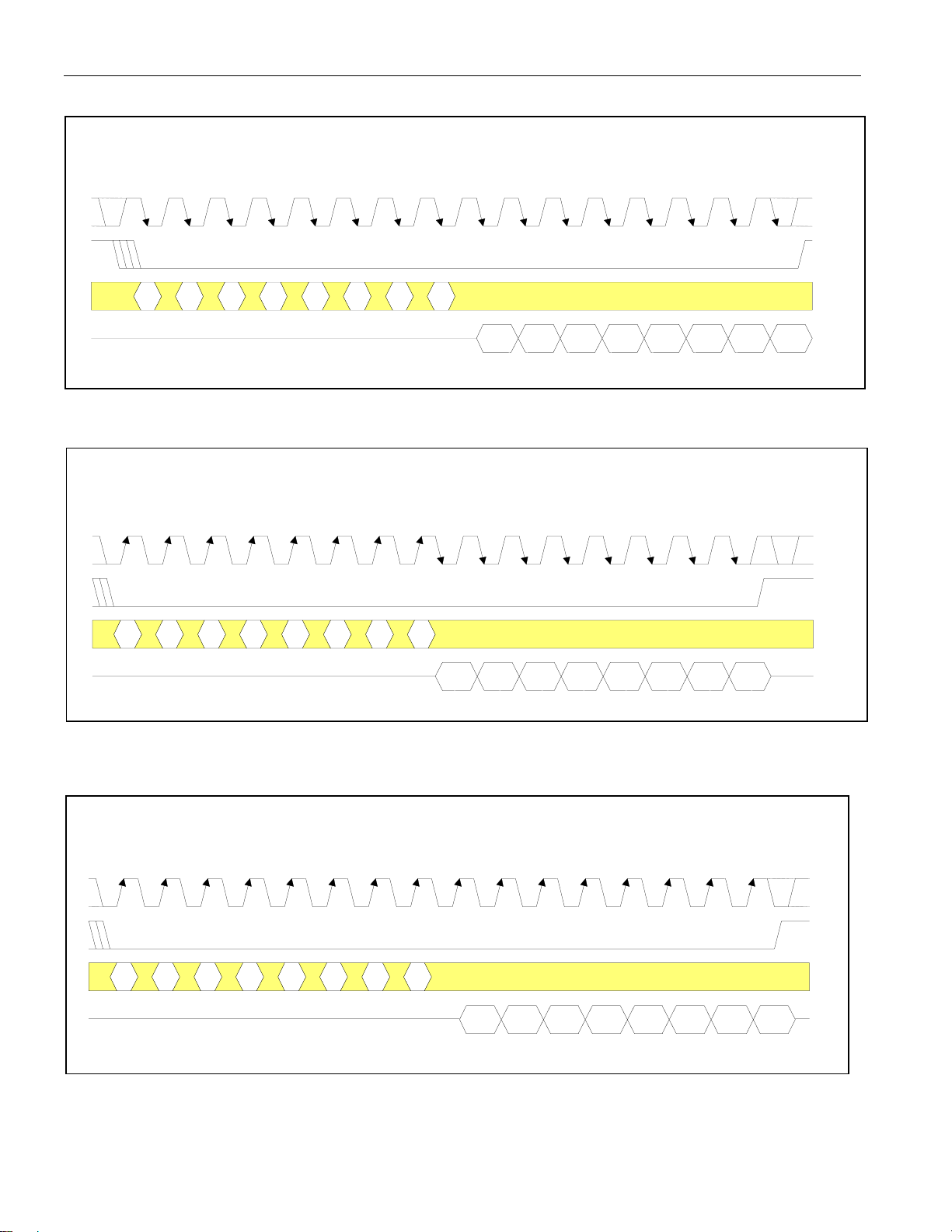

Figure 4-2. Serial Port Operation for Read Access (R = 1) Mode 2

ICES = 1 (SAMPLE SDI ON THE FALLING EDGE OF SCLK)

OCES = 0 (UPDATE SDO ON FALLING EDGE OF SCLK)

SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

S

SDI

SDO

A1 A2 A3 A4 A5 0 B

1

(LSB)

(MSB)

D1 D2 D3 D4 D5 D6

D0

LSB

Figure 4-3. Serial Port Operation for Read Access (R = 1) Mode 3

ICES = 0 (SAMPLE SDI ON THE RISING EDGE OF SCLK)

OCES = 0 (UPDATE SDO ON FALLING EDGE OF SCLK)

SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

S

SDI

(LSB)

SDO

A1 A2 A3 A4 A5 0 B

1

(MSB)

D1 D2 D3 D4 D5 D6

D0

(LSB)

Figure 4-4. Serial Port Operation for Read Access (R = 1) Mode 4

ICES = 0 (SAMPLE SDI ON THE RISING EDGE OF SCLK)

OCES = 1 (UPDATE SDO ON RISING EDGE OF SCLK)

SCLK

SDI

SDO

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

S

A1 A2 A3 A4 A5

1

(LSB) (MSB)

B

0

D1 D2 D3 D4 D5 D6 D0 D7

(LSB)

D7

(MSB)

D7

(MSB)

(MSB)

16 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

C

C

)

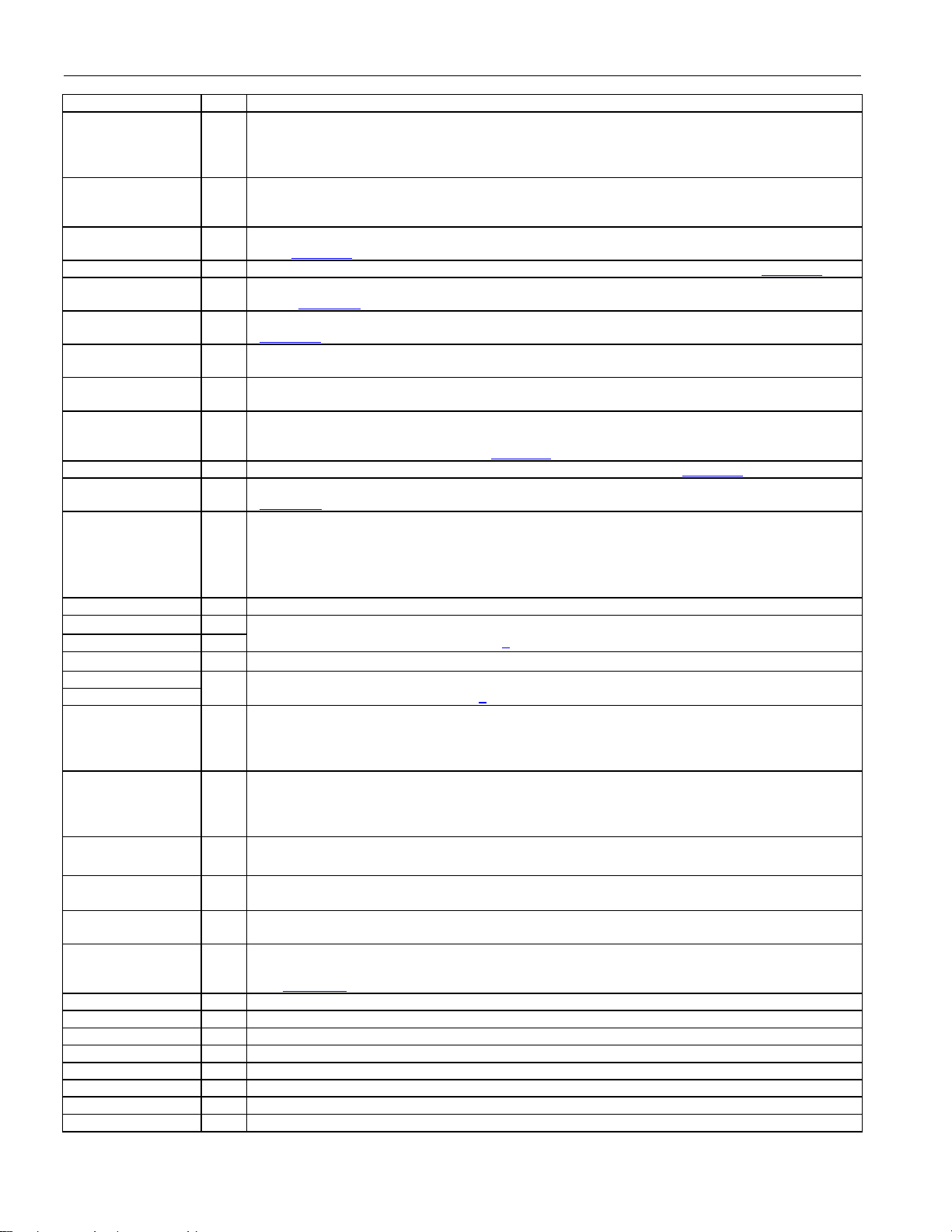

Figure 4-5. Serial Port Operation for Write Access (R = 0) Modes 1 and 2

ICES = 1 (SAMPLE SDI ON THE FALLING EDGE OF SCLK)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16SCLK

S

SDI

(LSB)

WRITE ACCESS ENABLED

SDO

A1 A2 A3 A4 A5 0 B

0

(MSB)

DO D6

D1 D2 D3 D4 D5 D7

(LSB)

(MSB)

Figure 4-6. Serial Port Operation for Write Access (R = 0) Modes 3 and 4

ICES = 0 (SAMPLE SDI ON THE RISING EDGE OF SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16SCLK

S

SDI

(LSB)

A1 A2 A3 A4 A5 0 B

0

(MSB)

DO D6

D1 D2 D3 D4 D5 D7

(LSB) (MSB)

WRITE ACCESS ENABLED

SDO

4.3 Parallel Port Operation

The option for either multiplexed bus operation (BIS0 = 0) or nonmultiplexed bus operation (BIS0 = 1) is available

when using the parallel interface. The DS21448 can operate with either Intel or Motorola bus timing configurations.

If the PBTS pin is wired low, Intel timing is selected; if wired high, Motorola timing is selected. All Motorola bus

signals are listed in parentheses (). Four sets of identical register maps exist, one for each channel. See Table 4-H

for register names and addresses. Use the appropriate chip select (

register map. See the timing diagrams in Section 10

for more details. Hardware and serial port modes are not

CS1, CS2, CS3, or CS4) to access a channel’s

supported when using parallel port operation.

4.3.1 Device Power-Up and Reset

The DS21448 resets itself upon power-up, setting all writeable registers to 00h and clearing the status and

information registers. CCR3.7 (TUA1) = 0 results in the LIU transmitting unframed all ones. After the power

supplies have settled, initialize all control registers to the desired settings, then toggle the LIRST bit (CCR3.2). The

DS21448 can at any time be reset to the default settings by bringing

down and powering up again.

HRST low (level triggered) or by powering

17 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

Table 4-G. Parallel Port Mode Selection

PBTS BIS0 PROCESSOR BUS INTERFACE TYPE

0 0 Intel Parallel Port Mode (Multiplexed)

0 1 Intel Parallel Port Mode (Nonmultiplexed)

1 0 Motorola Parallel Port Mode (Multiplexed)

1 1 Motorola Parallel Port Mode (Nonmultiplexed)

4.3.2 Register Map

Table 4-H shows the typical register map for all four ports. Use the appropriate chip select (CS1, CS2, CS3, or CS4)

to access a channel’s register map.

Table 4-H. Register Map

NAME R/W ADDRESS FUNCTION

CCR1 R/W 00h Common Control Register 1

CCR2 R/W 01h Common Control Register 2

CCR3 R/W 02h Common Control Register 3

CCR4 R/W 03h Common Control Register 4

CCR5 R/W 04h Common Control Register 5

CCR6 R/W 05h Common Control Register 6

SR R 06h Status Register

IMR R/W 07h Interrupt Mask Register

RIR1 R 08h Receive Information Register 1

RIR2 R 09h Receive Information Register 2

IBCC R/W 0Ah In-Band Code Control Register

TCD1 R/W 0Bh Transmit Code Definition Register 1

TCD2 R/W 0Ch Transmit Code Definition Register 2

RUPCD1 R/W 0Dh Receive-Up Code Definition Register 1

RUPCD2 R/W 0Eh Receive-Up Code Definition Register 2

RDNCD1 R/W 0Fh Receive-Down Code Definition Register 1

RDNCD2 R/W 10h Receive-Down Code Definition Register 2

ECR1 R 11h Error Count Register 1

ECR2 R 12h Error Count Register 2

TEST1 R/W 13h Test 1

TEST2 R/W 14h Test 2

TEST2 R/W 15h Test 3

— — (Note 1) —

Note 1: Register addresses 16h–1Fh do not exist.

18 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

4.3.3 Control Registers

CCR1 (00H): Common Control Register 1

(MSB)

ETS NRZE RCLA ECUE JAMUX TTOJ TTOR LOTCMC

NAME POSITION FUNCTION

ETS CCR1.7

NRZE CCR1.6

RCLA CCR1.5

ECUE CCR1.4

JAMUX CCR1.3

TTOJ CCR1.2

TTOR CCR1.1

LOTCMC CCR1.0

E1/T1 Select

0 = E1

1 = T1

NRZ Enable

0 = bipolar data at RPOS/RNEG and TPOS/TNEG

1 = NRZ data at RPOS and TPOS or TNEG; RNEG outputs a positive-going pulse when the

device receives a BPV, CV, or EXZ

Receive-Carrier-Loss Alternate Criteria

0 = RCL declared upon 255 (E1) or 192 (T1) consecutive zeros

1 = RCL declared upon 2048 (E1) or 1544 (T1) consecutive zeros

Error Counter Update Enable. A 0-to-1 transition forces the next receive clock cycle to load the

error counter registers with the latest counts and reset the counters. The user must wait a

minimum of two clock cycles (976ns for E1 and 1296ns for T1) before reading the error count

registers to allow for a proper update. See Section 6

Jitter Attenuator Clock Mux. Controls the source for JACLK (Figure 1-1

0 = JACLK sourced from MCLK (2.048MHz or 1.544MHz at MCLK)

1 = JACLK sourced from internal PLL (2.048MHz at MCLK)

TCLK to JACLK. Internally connects TCLK to JACLK (Figure 1-3

0 = disabled

1 = enabled

TCLK to RCLK. Internally connects TCLK to RCLK (Figure 1-3

0 = disabled

1 = enabled

Loss-of-Transmit Clock Mux Control. Determines whether the transmit logic should switch to

JACLK if the TCLK input should fail to transition (Figure 1-3).

0 = do not switch to JACLK if TCLK stops

1 = switch to JACLK if TCLK stops

for details.

).

).

).

(LSB)

19 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

CCR2 (01H): Common Control Register 2

(MSB)

RLPIN — SCLD CLDS RHBE THBE TCES RCES

NAME POSITION FUNCTION

RLPIN CCR2.7

— CCR2.6 Not Assigned. Should be set to 0 when written to.

SCLD CCR2.5

CLDS CCR2.4

RHBE CCR2.3

THBE CCR2.2

TCES CCR2.1

RCES CCR2.0

RCL/LOTC Pin Function Select. Forced to logic 0 in hardware mode.

0 = toggles high during a receive-carrier loss condition

1 = toggles high if TCLK does not transition for at least 5ms

Short Circuit-Limit Disable (ETS = 0). Controls the 50mA (RMS) current limiter.

0 = enable 50mA current limiter

1 = disable 50mA current limiter

Custom Line-Driver Select. Setting this bit to 1 redefines the operation of the transmit line

driver. When this bit is set to 1 and CCR4.5 = CCR4.6 = CCR4.7 = 0, the device generates a

square wave at the TTIP and TRING outputs instead of a normal waveform. When this bit is

set to 1 and CCR4.5 = CCR4.6 = CCR4.7 ¹ 0, the device forces TTIP and TRING outputs to

become open-drain drivers instead of their normal push-pull operation. This bit should be set

to 0 for normal operation of the device. Contact the factory for more details about how to use

this bit.

Receive HDB3/B8ZS Enable

0 = enable HDB3 (E1)/B8ZS (T1)

1 = disable HDB3 (E1)/B8ZS (T1)

Transmit HDB3/B8ZS Enable

0 = enable HDB3 (E1)/B8ZS (T1)

1 = disable HDB3 (E1)/B8ZS (T1)

Transmit Clock-Edge Select. Selects which TCLK edge to sample TPOS and TNEG.

0 = sample TPOS and TNEG on falling edge of TCLK

1 = sample TPOS and TNEG on rising edge of TCLK

Receive Clock-Edge Select. Selects which RCLK edge to update RPOS and RNEG.

0 = update RPOS and RNEG on rising edge of RCLK

1 = update RPOS and RNEG on falling edge of RCLK

(LSB)

20 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

CCR3 (02H): Common Control Register 3

(MSB)

TUA1 ATUA1 TAOZ TPRBSE TLCE LIRST IBPV IBE

NAME POSITION FUNCTION

TUA1 CCR3.7

ATUA1 CCR3.6

TAOZ CCR3.5

TPRBSE CCR3.4

TLCE CCR3.3

LIRST CCR3.2

IBPV CCR3.1

IBE CCR3.0

Transmit Unframed All Ones. The polarity of this bit is set such that the device transmits an allones pattern on power-up or device reset. This bit must be set to 1 to allow the device to transmit

data. The transmission of this data pattern is always timed off JACLK (Figure 1-1

0 = transmit all ones at TTIP and TRING

1 = transmit data normally

Automatic Transmit Unframed All Ones. Automatically transmit an unframed all-ones pattern at

TTIP and TRING during an RCL condition.

0 = disabled

1 = enabled

Transmit Alternate Ones and Zeros. Transmit a …101010… pattern at TTIP and TRING. The

transmission of this data pattern is always timed off TCLK.

0 = disabled

1 = enabled

Transmit PRBS Enable. Transmit a 215 - 1 (E1) or a QRSS (T1) PRBS at TTIP and TRING.

0 = disabled

1 = enabled

Transmit Loop-Code Enable. Enables the transmit side to transmit the loop-up code in the transmit

code definition registers (TCD1 and TCD2). See Section 6 for details.

0 = disabled

1 = enabled

Line Interface Reset. Setting this bit from 0 to 1 initiates an internal reset that resets the clock

recovery state machine and recenters the jitter attenuator. Normally this bit is only toggled on

power-up. It must be cleared and set again for a subsequent reset.

Insert Bipolar Violation (BPV). A 0-to-1 transition on this bit causes a single bipolar violation to be

inserted into the transmit data stream. Once this bit has been toggled from 0 to 1, the device waits

for the next occurrence of three consecutive 1s to insert the BPV. This bit must be cleared and set

again for a subsequent error to be inserted (Figure 1-3

Insert Bit Error. A 0-to-1 transition on this bit causes a single logic error to be inserted into the

transmit data stream. This bit must be cleared and set again for a subsequent error to be inserted

(Figure 1-3

).

).

).

(LSB)

CCR4 (03H): Common Control Register 4

(MSB)

L2 L1 L0 EGL JAS JABDS DJA TPD

NAME POSITION FUNCTION

L2 CCR4.7 Line Build-Out Select Bit 2. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

L1 CCR4.6 Line Build Out Select Bit 1. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

L0 CCR4.5 Line Build Out Select Bit 0. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

EGL CCR4.4 Receive Equalizer Gain Limit. This bit controls the sensitivity of the receive equalizer (Table 4-I).

JAS CCR4.3

JABDS CCR4.2

DJA CCR4.1

TPD CCR4.0

Jitter Attenuator Path Select

0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

Jitter Attenuator Buffer Depth Select

0 = 128 bits

1 = 32 bits (use for delay-sensitive applications)

Disable Jitter Attenuator

0 = jitter attenuator enabled

1 = jitter attenuator disabled

Transmit Power-Down

0 = normal transmitter operation

1 = powers down the transmitter and tri-states the TTIP and TRING pins

(LSB)

21 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

Table 4-I. Receive Sensitivity Settings

EGL

(CCR4.4)

0 0 (E1) -12 (short haul)

1 0 (E1) -43 (long haul)

1 1 (T1) -30 (limited long haul)

0 1 (T1) -36 (long haul)

CCR5 (04H): Common Control Register 5

(MSB)

BPCS1 BPCS0 MM1 MM0 RSCLKE TSCLKE RT1 RT0

NAME POSITION FUNCTION

BPCS1 CCR5.7 Backplane Clock Frequency Select 1. See Table 4-J for details.

BPCS0 CCR5.6 Backplane Clock Frequency Select 0. See Table 4-J for details.

MM1 CCR5.5 Monitor Mode Gain Select 1 (Table 4-K. )

MM0 CCR5.4 Monitor Mode Gain Select 0. See (Table 4-K.

RSCLKE CCR5.3

TSCLKE CCR5.2

RT1 CCR5.1 Receive Termination Select 1. See Table 4-L for details.

RT0 CCR5.0 Receive Termination Select 0. See Table 4-L for details.

ETS

(CCR1.7)

RECEIVE SENSITIVITY

(dB)

(LSB)

Receive Synchronization Clock Enable

0 = disable 2.048MHz synchronization receive mode

1 = enable 2.048MHz synchronization receive mode

Transmit Synchronization Clock Enable

0 = disable 2.048MHz transmit synchronization clock

1 = enable 2.048MHz transmit synchronization clock

Table 4-J. Backplane Clock Select

BPCS1

(CCR5.7)

0 0 16.384

0 1 8.192

1 0 4.096

1 1 2.048

BPCS0

(CCR5.6)

BPCLK FREQUENCY (MHz)

Table 4-K. Monitor Gain Settings

MM1

(CCR5.5)

0 0 Normal operation (no boost)

0 1 20

1 0 26

1 1 32

MM0

(CCR5.4)

INTERNAL LINEAR GAIN

BOOST (dB)

Table 4-L. Internal Rx Termination Select

RT1

(CCR5.1)

0 0 Internal receive-side termination disabled

0 1

1 0

1 1

RT0

(CCR5.0)

INTERNAL RECEIVE

TERMINATION CONFIGURATION

Internal receive-side 120W enabled

Internal receive-side 100W enabled

Internal receive-side 75W enabled

22 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

CCR6 (05H): Common Control Register 6

(MSB)

LLB RLB ARLBE ALB RJAB ECRS2 ECRS1 ECRS0

NAME POSITION FUNCTION

LLB CCR6.7

RLB CCR6.6

ARLBE CCR6.5

ALB CCR6.4

RJAB CCR6.3

ECRS2 CCR6.2 Error Count Register Select 2. See Section 6.4 for details.

ECRS1 CCR6.1 Error Count Register Select 1. See Section 6.4 for details.

ECRS0 CCR6.0 Error Count Register Select 0. See Section 6.4 for details.

Local Loopback. In local loopback, transmit data is looped back to the receive path, passing

through the jitter attenuator if it is enabled. Data in the transmit path acts as normal. See

Section 6.2

0 = loopback disabled

1 = loopback enabled

Remote Loopback. In remote loopback, data output from the clock/data recovery circuitry is

looped back to the transmit path, passing through the jitter attenuator if it is enabled. Data in

the receive path acts as normal, while data presented at TPOS and TNEG is ignored. See

Section 6.2

0 = loopback disabled

1 = loopback enabled

Automatic Remote Loopback Enable and Reset. When this bit is set high, the device

automatically goes into remote loopback when it detects loop-up code programmed into the

receive loop-up code definition registers (RUPCD1 and RUPCD2) for a minimum of 5

seconds; it also sets the RIR2.1 status bit. Once it is in an RLB state, the bit remains in this

state until it has detected the loop code programmed into the receive loop-down code

definition registers (RDNCD1 and RDNCD2) for a minimum of 5 seconds, at which point it

forces the device out of RLB and clears RIR2.1. Toggling this bit from 1 to 0 resets the

automatic RLB circuitry. The action of the automatic remote loopback circuitry is logically

ORed with the RLB (CCR6.6) control bit (i.e., either one can cause a RLB to occur).

Analog Loopback. In analog loopback, signals at TTIP and TRING are internally connected to

RTIP and RRING. The incoming line signals at RTIP and RRING are ignored. The signals at

TTIP and TRING are transmitted as normal. See Section 6.2

0 = loopback disabled

1 = loopback enabled

RCLK Jitter Attenuator Bypass. This control bit allows the receive-recovered clock and data to

bypass the jitter attenuation, while still allowing the BPCLK output to use the jitter attenuator.

See Section 7.3

0 = disabled

1 = enabled

for details.

for details.

for more details.

for details.

(LSB)

5. STATUS REGISTERS

The three registers that contain information about the device’s real-time status are the status register (SR) and

receive information registers 1 and 2 (RIR1/RIR2). When a particular event has occurred (or is occurring), the

appropriate bit in one of these registers is set to 1. Some bits in SR, RIR1, and RIR2 are latched bits and some are

real-time bits (denoted in the following register descriptions). For latched status bits, when an event or an alarm

occurs, the bit is set to 1 and remains set until the user reads that bit. The bit is cleared when it is read, and it is not

set until the event has occurred again. Two of the latched status bits (RUA1 and RCL) remain set after reading if

the alarm is still present.

The user always precedes a read of any of the three status registers with a write. The byte written to the register

informs the DS21448 which bits the user wishes to read and have cleared. The user writes a byte to one of these

registers with a 1 in the bit positions to be read and a 0 in the other bit positions. When a 1 is written to a bit

location, that location is updated with the latest information. When a 0 is written to a bit position, that bit position is

not updated, and the previous value is held. A write to the status and information registers is immediately followed

by a read of the same register. The read result should be logically ANDed with the mask byte that was just written,

and this value should be written back into the same register to ensure that bit does indeed clear. This second write

step is necessary because the alarms and events in the status registers occur asynchronously with respect to their

access through the parallel port. This write-read-write scheme allows an external microcontroller or microprocessor

to individually poll certain bits without disturbing the other bits in the register. This operation is key in controlling the

DS21448 with higher-order software languages.

23 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

The bits in the SR register have the unique ability to initiate a hardware interrupt through the

INT output pin. Each

of the alarms and events in the SR can be either masked or unmasked from the interrupt pin through the interrupt

mask register (IMR). The interrupts caused by the RCL, RUA1, and LOTC bits in the SR act differently than the

interrupts caused by the other status bits in the SR. The RCL, RUA1, and LOTC bits forces the

whenever they change state (i.e., go active or inactive). The

INT pin is allowed to return high (if no other interrupts

INT pin low

are present) when the user reads the alarm bit that caused the interrupt to occur, even if the alarm is still present.

The other status bits in the SR can force the

INT pin low when they are set. The INT pin is allowed to return high (if

no other interrupts are present) when the user reads the event bit that caused the interrupt to occur.

The host can quickly determine which of the four LIU channels is generating an interrupt by reading one of the

unused addresses in the 16h–1Fh range in any LIU channel. See the following LIU channel interrupt status

description for additional information.

LIU Channel Interrupt Status

(MSB)

— — — — LIU4 LIU3 LIU2 LIU1

NAME POSITION FUNCTION

N/A 7 Not Assigned. Could be any value when read.

N/A 6 Not Assigned. Could be any value when read.

N/A 5 Not Assigned. Could be any value when read.

N/A 4 Not Assigned. Could be any value when read.

LIU4 3

LIU3 2

LIU2 1

LIU1 0

LIU4 Status Register. A 1 in this bit position indicates that the status register (SR) in channel 4 is

asserting an interrupt.

LIU3 Status Register. A 1 in this bit position indicates that the status register (SR) in channel 3 is

asserting an interrupt.

LIU2 Status Register. A 1 in this bit position indicates that the status register (SR) in channel 2 is

asserting an interrupt.

LIU1 Status Register. A 1 in this bit position indicates that the status register (SR) in channel 1 is

asserting an interrupt.

(LSB)

SR (06H): Status Register

(MSB)

LUP LDN LOTC RUA1 RCL TCLE TOCD PRBSD

NAME POSITION FUNCTION

LUP

(Latched)

LDN

(Latched)

LOTC

(Real Time)

RUA1

(Latched)

RCL

(Latched)

TCLE

(Real Time)

TOCD

(Real Time)

PRBSD

(Real Time)

SR.7

SR.6

SR.5

SR.4

SR.3

SR.2

SR.1

SR.0

Loop-Up Code Detected. This bit is set when the loop-up code defined in registers RUPCD1 and

RUPCD2 is being received. See Section 6.1

Loop-Down Code Detected. This bit is set when the loop-down code defined in registers

RDNCD1 and RDNCD2 is being received. See Section 6.1

Loss-of-Transmit Clock. This bit is set when the TCLK pin has not transitioned for 5ms (±2ms),

forcing the LOTC pin high.

Receive Unframed All Ones. This bit is set when an unframed all-ones code is received at RRING

and RTIP (Table 5-A

Receive Carrier Loss. This bit is set when an RCL condition exists at RRING and RTIP. See

(Table 5-A

Transmit Current-Limit Exceeded. This bit is set when the 50mA (RMS) current limiter is activated

whether or not the current limiter is enabled.

Transmit Open-Circuit Detect. This bit is set when the device detects that the TTIP and TRING

outputs are open circuited.

PRBS Detect. This bit is set when the receive side detects a 2

pseudorandom bit sequence (PRBS).

) for details.

).

for details.

for details.

15

- 1 (E1) or a QRSS (T1)

(LSB)

24 of 60

DS21448 3.3V T1/E1/J1 Quad Line Interface

Table 5-A. Received Alarm Criteria

ALARM E1/T1 SET CRITERIA CLEAR CRITERIA

RUA1 E1 Fewer than two 0s in two frames (512 bits) More than two 0s in two frames (512 bits)

RUA1 T1

RCL