FEATURES

■

Regulated Output with Input Above, Below or Equal

to the Output

■

Single Inductor

■

Up to 90% Effi ciency

■

VIN Range: 1.8V to 5.5V

■

200mA at 3.3V

■

125mA at 3V

■

Fixed V

■

Adjustable V

■

Burst Mode® Operation, No External Compensation

■

Ultra Low Quiescent Current: 16μA, Shutdown

Versions (TSOT, DFN): 3.3V, 3V

OUT

from 3.6V Input

OUT

from 2.5V Input

OUT

Version (DFN): 2V to 5V

OUT

Current <1μA

■

Only 3 External Components Required

(Fixed Voltage Versions)

■

Short-Circuit Protection

■

Output Disconnect in Shutdown

■

Available in 6-Pin ThinSOT and 3mm × 3mm DFN

Packages

U

APPLICATIO S

■

Handheld Instruments

■

MP3 Players

■

Handheld computers

■

PDA/GPS

LTC3531/

LTC3531-3.3/LTC3531-3

200mA Buck-Boost

Synchronous DC/DC

Converters

U

DESCRIPTIO

The LTC®3531/LTC3531-3.3/LTC3531-3 are synchronous

buck-boost DC/DC converters that operate from input

voltages above, below or equal to the output voltage. The

topology incorporated in the ICs provides a continuous

transfer through all operating modes, making the product

ideal for single cell Li-Ion and multicell alkaline or nickel

applications. The converters operate in Burst Mode, minimizing solution footprint and component count as well as

providing high conversion effi ciency over a wide range of

load currents.

The devices include two 0.5Ω N-channel MOSFET switches

and two P-channel switches (0.5Ω, 0.8Ω). Quiescent

current is typically 16μA, making the parts ideal for battery power applications. Other features include a <1μA

shutdown current, current limiting, thermal shutdown

and output disconnect. The parts are offered in a 6-pin

ThinSOT

3mm DFN package for fi xed and adjustable versions.

, LT, LTC and LTM are registered trademarks of Linear Technology Corporation.

Burst Mode is a registered trademark of Linear Technology Corporation.

ThinSOT is a trademark of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

Protected by U.S. Patents including 6166527.

TM

package for fi xed voltage versions or a 3mm ×

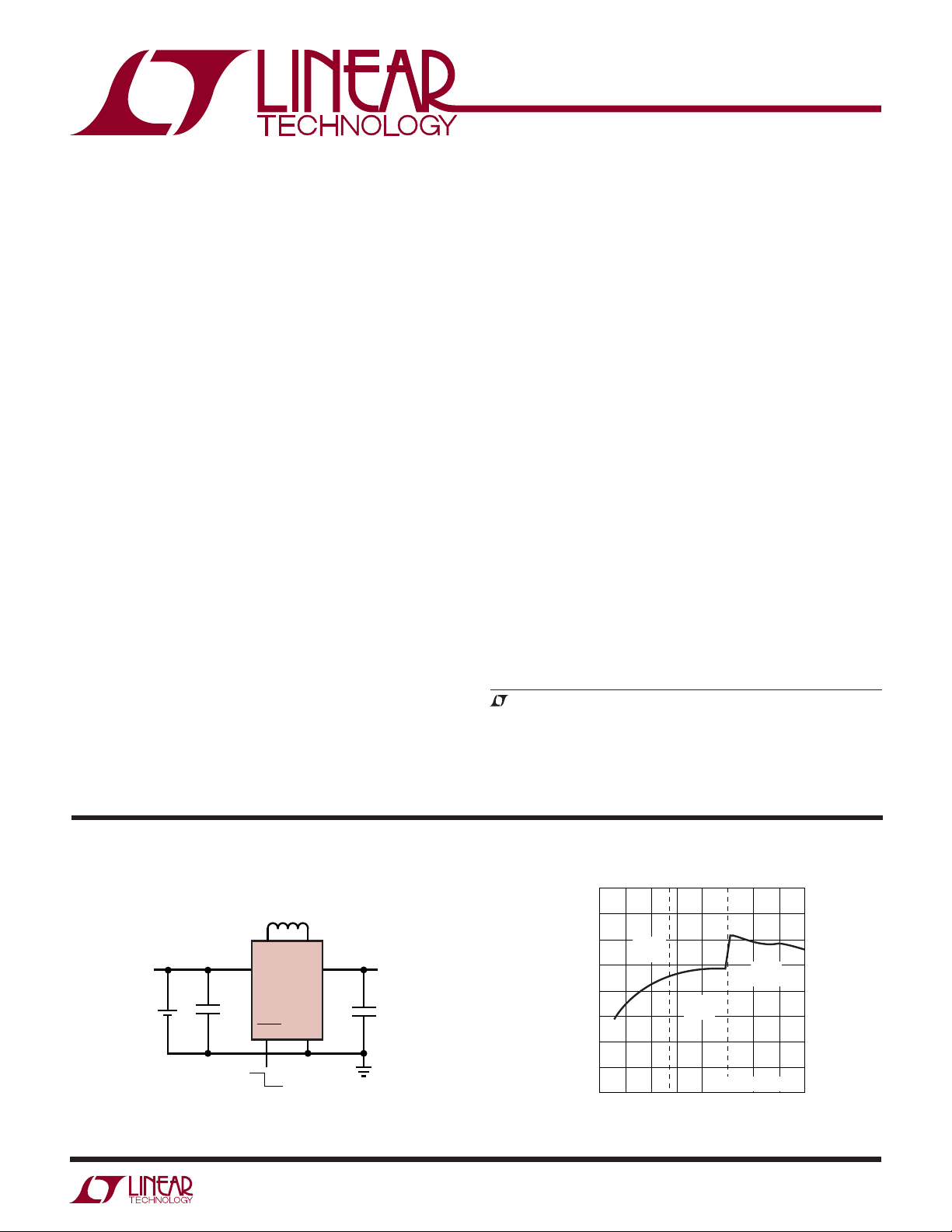

TYPICAL APPLICATIO

10μH

2.2μF

SW1 SW2

V

IN

LTC3531-3.3

SHDN GND

ON OFF

V

3.1V TO

4.2V

Li-Ion

IN

+

U

Effi ciency vs V

100

95

90

V

OUT

V

OUT

3.3V

160mA

10μF

3531 TA01a

85

80

75

EFFICIENCY (%)

70

65

60

1.5

BOOST

MODE

2

2.5

INPUT VOLTAGE (V)

3

4SW

MODE

3.5

3.3V

IN

4

BUCK

MODE

AT 100mA

OUT

4.5

5

3531 TA01b

5.5

3531fb

1

LTC3531/

LTC3531-3.3/LTC3531-3

WW

W

U

ABSOLUTE AXI U RATI GS

(Note 1)

VIN, VOUT, SW1, SW2,

SW1, SW2 Voltage, <100ns Pulse ..................–0.3 to 7V

SHDN

Voltage ...........–0.3 to 6V

Storage Temperature Range ................... –65°C to 125°C

Lead Temperature (TS6, Soldering, 10 sec) .......... 300°C

Operating Temperature Range (Notes 2, 3) –40°C to 85°C

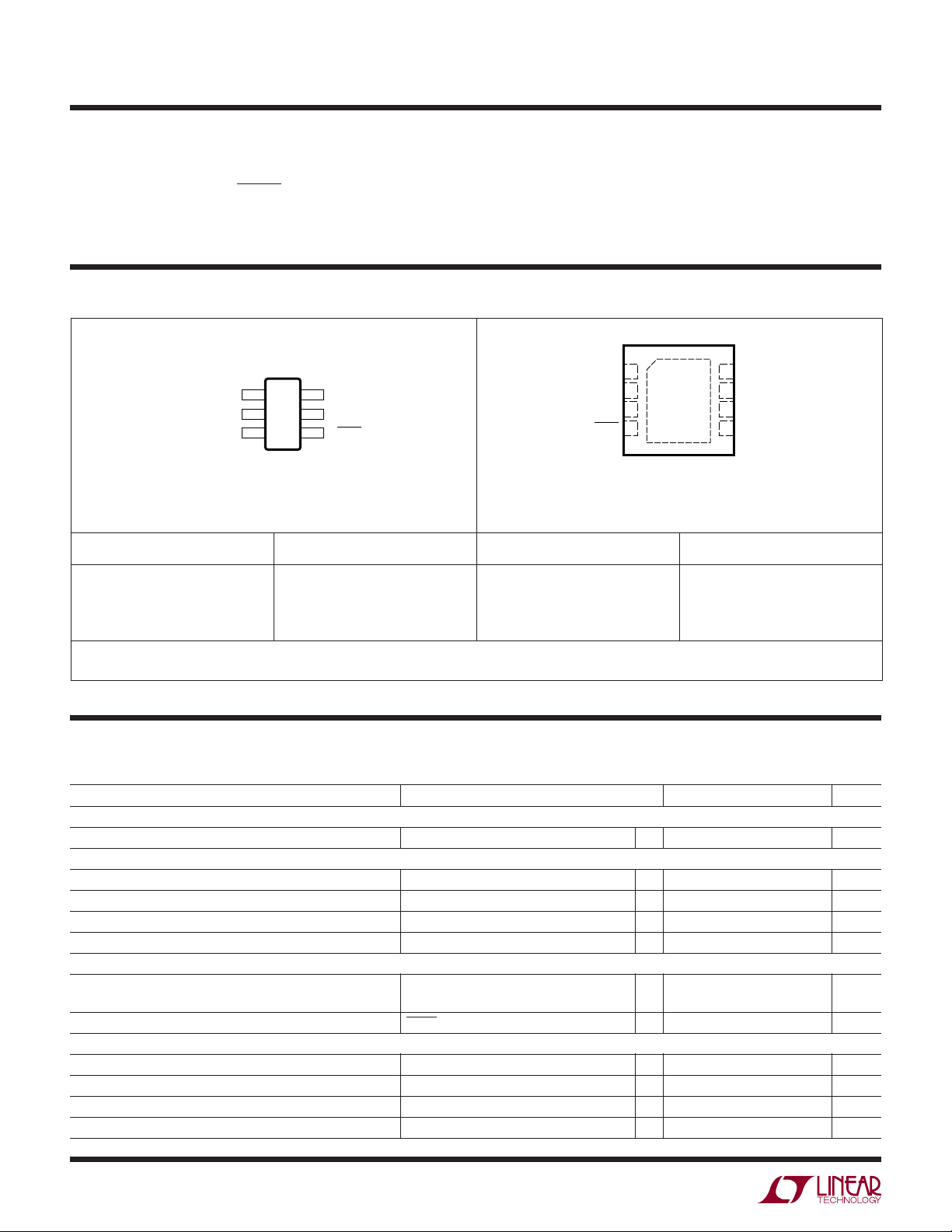

UUW

FOR ATIOPACKAGE/ORDER I

TOP VIEW

SW2 1

GND, PGND 2

V

3

OUT

6-LEAD PLASTIC TSOT-23

T

= 125°C, θJA = 102°C/W

JMAX

TOP VIEW

S6 PACKAGE

6 SW1

5 V

IN

4 SHDN

EXPOSED PAD IS GND (PIN 9), MUST BE SOLDERED TO PCB

1SW1

V

2

IN

GND

3

SHDN

4

8-LEAD (3mm × 3mm) PLASTIC DFN

T

JMAX

*NC FOR LTC3531-3.3V, LTC3531-3.0V.

9

DD PACKAGE

= 125°C, θJA = 43°C/W

ORDER PART NUMBER S6 PART MARKING ORDER PART NUMBER DD PART MARKING

8

PGND

SW2

7

V

6

OUT

FB*

5

LTC3531ES6-3.3

LTC3531ES6-3

Order Options Tape and Reel: Add #TR Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF

Lead Free Part Marking: http://www.linear.com/leadfree/

Consult LTC Marketing for parts specifi ed with wider operating temperature ranges.

The ● denotes the specifi cations which apply over the full operating

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifi cations are at TA = 25°C. VIN = 3.6V V

PARAMETER CONDITIONS MIN TYP MAX UNITS

V

IN

Minimum Startup Voltage ● 1.65 1.8 V

V

Regulation

OUT

Output Voltage (3.3V Version) No Load ● 3.25 3.32 3.39 V

Output Voltage (3V Version) No Load ● 2.95 3.02 3.09 V

FB Voltage (Adj Version) No Load ● 1.20 1.225 1.25 V

FB Input Current (Adj Version) VFB = 1.225V 1 50 nA

Operating Current

Quiescent Current in Sleep: VIN VIN = 5V, V

V

Shutdown Current VIN

Switch Performance

NMOS Switch Leakage Switches B and C 0.2 2 μA

PMOS Switch Leakage Switches A and D 0.2 2 μA

NMOS B, C R

PMOS A R

VIN = 5V 0.5 Ω

DSON

VIN = 5V 0.5 Ω

DSON

LTBWM

LTCBK

OUT

V

OUT

SHDN

LTC3531EDD

LTC3531EDD-3.3

LTC3531EDD-3

= 3.3V unless otherwise noted.

OUT

= 3.6V, FB = 1.3V 16 30 μA

OUT

= 3.6V 6 10 μA

= 0V, V

= 0V 1 μA

OUT

LBVC

LBWH

LCBV

3531fb

2

LTC3531/

LTC3531-3.3/LTC3531-3

ELECTRICAL CHARACTERISTICS

The ● denotes the specifi cations which apply over the full operating

temperature range, otherwise specifi cations are at T

= 25°C. VIN = 3.6V V

A

= 3.3V unless otherwise noted.

OUT

PARAMETER CONDITIONS MIN TYP MAX UNITS

PMOS D R

PMOS D R

(3.3V Version or Adjustable Version set to 3.3V) V

DSON

(3V Version)

DSON

VOUT

= 3.1V 0.8 Ω

OUT

= 2.8V 0.9 Ω

Peak Current Limit L = 10μH, VIN = 5V 295 365 460 mA

SHDN

Input Threshold 0.4 1

SHDN

Hysteresis 60 mV

SHDN

Leakage Current V

SHDN

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: This IC includes overtemperature protection that is intended

to protect the device during momentary overload conditions. Junction

0.01 1 μA

SHDN

Continuous operation above the specifi ed maximum operating junction

temperature may result in device degradation or failure.

Note 3: The LTC3531 is guaranteed to meet performance specifi cations

from 0°C to 70°C. Specifi cations over the –40°C to 85°C operating

temperature range are assured by design, characterization and correlation

with statistical process controls.

1.4

V

temperature will exceed 125°C when overtemperature protection is active.

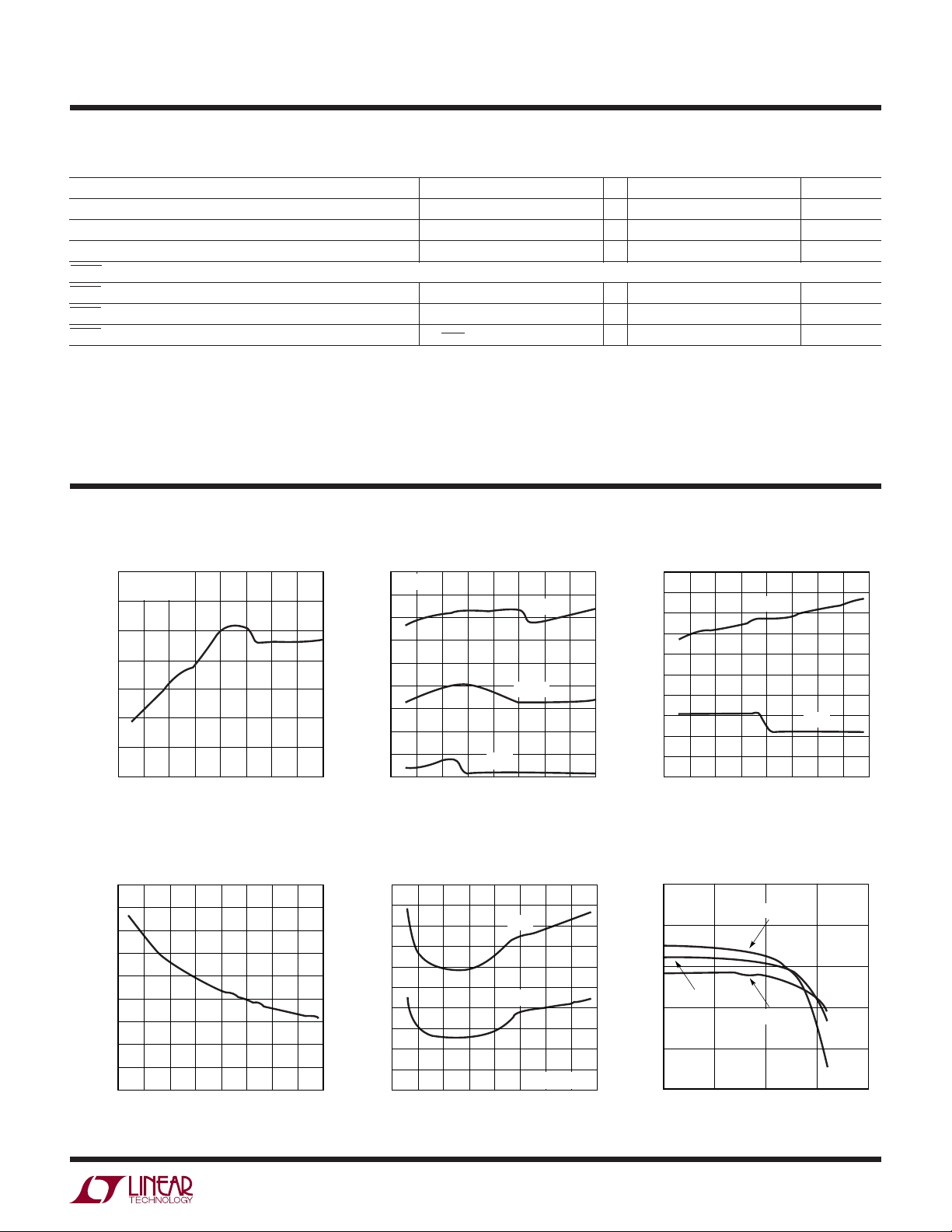

UW

3531 G01

CE CHARACTERISTICSA

I

PEAK

450

L = 10μH

400

350

300

250

200

CURRENT (mA)

150

100

50

0

1.5

, I

VALLEY

TA = 25°C unless otherwise specifi ed.

, I

vs V

ZERO

I

2.52

3.53

VIN (V)

ZERO

I

VALLEY

IN

I

PEAK

4.54

5.55

3531 G02

Sleep Currents

20

18

16

14

12

10

8

CURRENT (μA)

6

4

2

0

1.5

I

VIN

23

2.5

3.5

VIN (V)

I

VOUT

5

4.5

4

5.5

3531 G03

TYPICAL PERFOR

Maximum I

(3.3V Version)

350

L = 10μH

V

OUT

300

250

(mA)

200

OUT

150

MAXIMUM I

100

50

0

1.5

= 3.3V

vs V

OUT

2.52 3.5 5.5

IN

VIN (V)

4.5 543

IIN Short Circuit vs V

180

160

140

120

100

(mA)

IN

80

I

60

40

20

0

1.5 2

2.5 3

3.5 4

VIN (V)

V

Ripple vs C

OUT

IN

4.5 5

5.5

3531 G04

(3.3V Version)

100

90

80

70

(mV)

60

50

40

30

RIPPLE PEAK-PEAK

V

20

10

0

1.5

23

2.5

OUT

3.5

VIN (V)

10μF

22μF

4

50mA LOAD

5

4.5

3531 G05

5.5

Load Regulation vs C

(3.3V Version)

3.40

3.35

3.30

(V)

V

OUT

3.25

3.20

3.15

VIN = 3.6V

0.1

22μF

1

LOAD CURRENT (mA)

10μF

47μF

10

OUT

100

1000

3521 G06

3531fb

3

LTC3531/

LTC3531-3.3/LTC3531-3

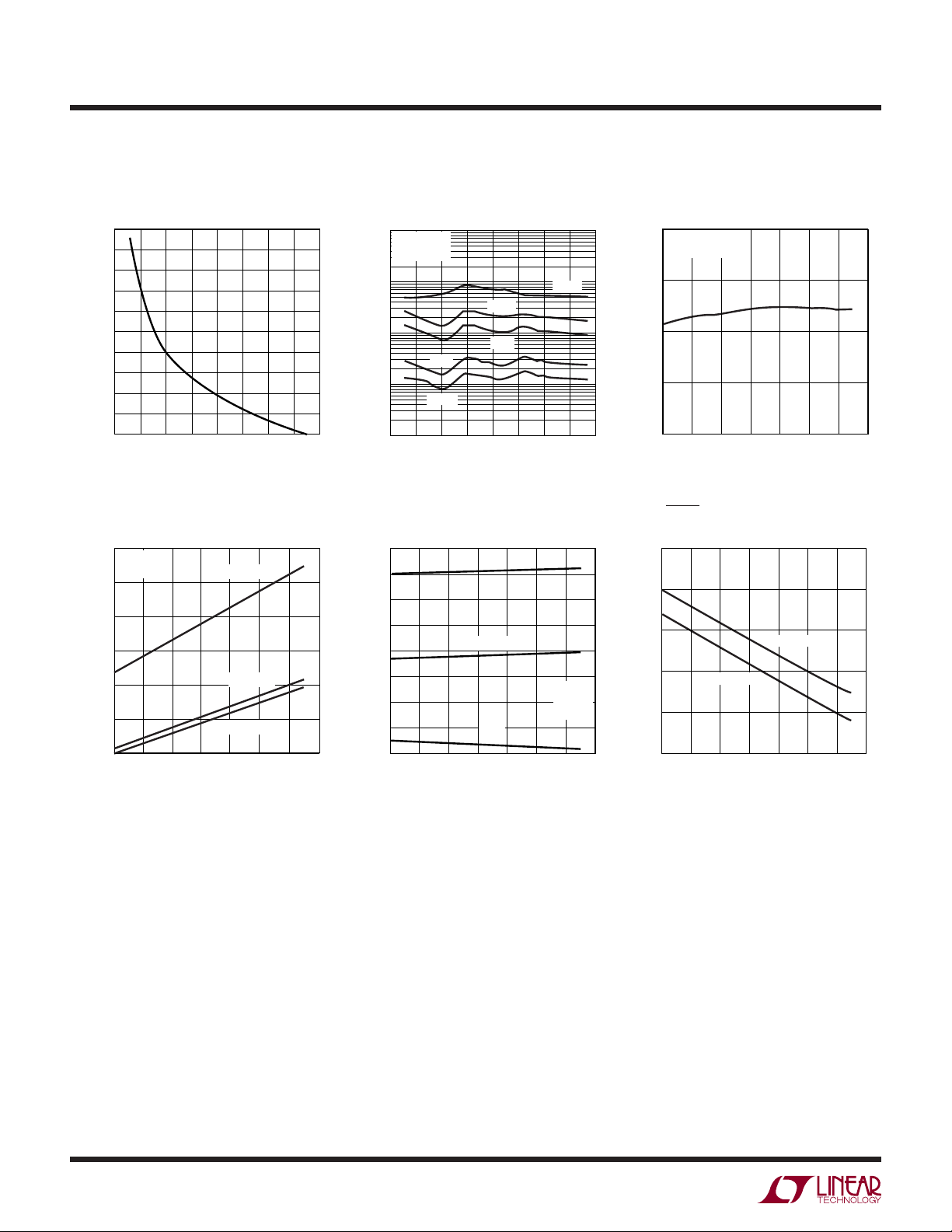

UW

TYPICAL PERFOR A CE CHARACTERISTICS

TA = 25°C unless otherwise specifi ed.

Start-Up into Resistive Load

L = 10μH

30

28

26

24

22

(Ω)

20

MIN

R

18

16

14

12

10

1.5

23

2.5

3.5

4

V

(V)

IN

4.5

5

3531 G07

Switch On Resistances I

1000

V

= 5V

IN

= 3.3V

900

800

(mΩ)

700

DSON

R

600

500

400

–40

V

OUT

02040

–20

TEMPERATURE (°C)

D (PMOS)

A (PMOS)

B,C (NMOS)

60 80 100

3531 G10

5.5

Burst Frequency vs Load

(3.3V Version)

1000

L = 10μH

C

= 10μF

OUT

100

10mA

10

FREQUENCY (kHz)

1

0.1

1.5 3.53 4.54 5.55

400

350

300

250

200

150

CURRENT (mA)

100

50

0

–40

1mA

0.5mA

2.52

, I

PEAK

VALLEY

–20 0 40

5mA

V

(V)

IN

vs Temperature

I

PEAK

I

VALLEY

I

ZERO

20

TEMPERATURE (°C)

V

Regulation vs Temperature

OUT

(3.3V Version)

3.350

VIN = 3.6V

= 10mA

I

LOAD

(V)

OUT

V

3.325

3.300

3.275

3.250

–40

–20 0 20 40

TEMPERATURE (°C)

60 80 100

3531 G09

50mA

3531 G08

SHDN Pin Threshold and

Hysteresis

1

0.9

0.8

0.7

2.5V

IN

3.3V

OUT

10μH

80 100

60

3531 G11

VOLTAGE (V)

0.6

0.5

–40

SHUTDOWN

02040

–20

TEMPERATURE (°C)

OPERATING

60 80 100

3531 G12

4

3531fb

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LTC3531/

LTC3531-3.3/LTC3531-3

TA = 25°C unless otherwise specifi ed.

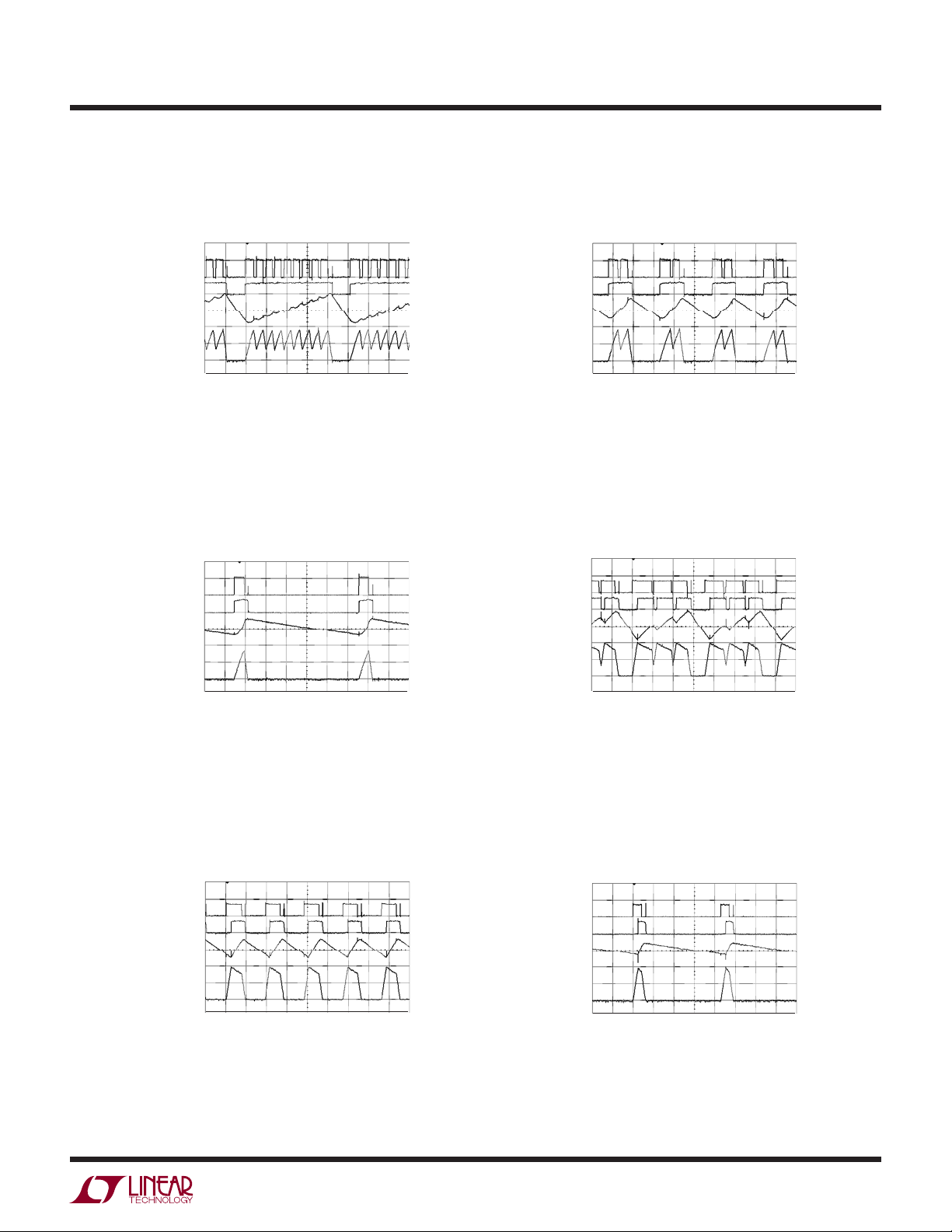

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

Buck Mode at 5V

OUT

OUT

= 22μF

200mA

I

L

3.3V

L = 10μH

C

,

IN

5μs/DIV 5μs/DIV

Buck Mode Waveforms at 5VIN,

3.3V

I

L

OUT

20mA

Buck Mode at 5V

OUT

OUT

= 22μF

100mA

3.3V

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

I

L

200mA/DIV

3531 G13 3531 G14

L = 10μH

C

,

IN

4 Switch Mode Waveforms at

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

3.6VIN, 3.3V

I

L

OUT

200mA

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

L = 10μH

= 22μF

C

OUT

5μs/DIV 5μs/DIV

4 Switch Mode Waveforms at

3.6V

I

L

L = 10μH

= 22μF

C

OUT

, 3.3V

IN

100mA

OUT

5μs/DIV 5μs/DIV

3531 G15

L = 10μH

= 22μF

C

OUT

3531 G16

4 Switch Mode Waveforms at

, 3.3V

3.6V

IN

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

I

L

200mA/DIV

3531 G17 3531 G18

L = 10μH

C

= 22μF

OUT

OUT

20mA

SW1

SW2

V

OUT

I

L

(AC)

3531fb

5

LTC3531/

LTC3531-3.3/LTC3531-3

UW

TYPICAL PERFOR A CE CHARACTERISTICS

TA = 25°C unless otherwise specifi ed.

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

200mA/DIV

Boost Mode Waveforms at

2.5VIN, 3.3V

I

L

L = 10μH

= 22μF

C

OUT

100mA

OUT

5μs/DIV 5μs/DIV

Shorted Output

I

L

Boost Mode Waveforms at

2.5VIN, 3.3V

SW1

5V/DIV

SW2

5V/DIV

(AC)

V

OUT

50mV/DIV

I

L

200mA/DIV

3531 G19 3531 G20

L = 10μH

= 22μF

C

OUT

OUT

20mA

Start-Up into 50mA Load at

3.3 V

(Shows Start, Buck,

OUT

Then 4sw Modes)

V

200mA/DIV

OUT

1V/DIV

200mA/DIV

I

L

V

(AC)

OUT

20mV/DIV

L = 10μH

= 22μF

C

OUT

= 5

V

IN

3.6VIN, 3.3V

1μs/DIV 25μs/DIV

Load Step

OUT

3531 G21

200mA to 80mA

100mA LOAD

20mA LOAD

= 22μF VIN = 3.6V

C

OUT

25μs/DIV 200ns/DIV

20mA LOAD

3531 G23 3531 G24

SW1

2V/DIV

200mA/DIV

SW2

2V/DIV

I

L

3531 G22

SW1 and SW2 Close-Up in Four

Switch Mode

= 3.3V

V

OUT

3531fb

6

UUU

PI FU CTIO S

LTC3531/

LTC3531-3.3/LTC3531-3

ThinSOT/DFN Packages

SW2 (Pin 1/Pin 7): Buck-Boost Switch Pin Where Internal

Switches C and D are Connected. An optional Schottky

diode can be connected from SW2 to V

effi ciency improvement. Minimize trace length to keep

EMI down.

GND (Pin 2/Pin 3): Signal Ground for the IC.

PGND (Pin 2/Pin 8): Power Ground for the IC. (Shared

on ThinSOT version)

(Pin 3/Pin 6): Output of the Buck-Boost Synchronous

V

OUT

Rectifi er. A fi lter capacitor is placed from V

A ceramic bypass capacitor is recommended as close to

the V

SHDN

voltage of < 0.4V shuts down the converter. A voltage

above >1.4V will enable the converter.

and GND pins as possible.

OUT

(Pin 4/Pin 4): External Shutdown Pin. An applied

for a moderate

OUT

to GND.

OUT

(Pin 5/Pin 2): Input Supply Pin for the Buck-Boost

V

IN

Converter. A minimum 2.2μF Ceramic Capacitor should

be placed between V

FB (NA/Pin 5): Feedback Pin for the Adjustable Version.

Connect the resistor divider tap here. The output voltage

can be adjusted from 2V to 5V.

V

=+

12251

OUT

SW1 (Pin 6/Pin 1): Buck-Boost Switch Pin Where Internal

Switches A and B are Connected. Connect the inductor

from SW1 to SW2.

Exposed Pad (Pin 9, DFN): Solder to PCB ground for

optimal thermal performance.

.

IN

⎛

⎜

⎝

and GND.

R

2

⎞

⎟

⎠

R

1

3531fb

7

LTC3531/

LTC3531-3.3/LTC3531-3

W

BLOCK DIAGRA

SW1 SW2

V

SHDN

SHUTDOWN

SW A

GATE DRIVERS

AND

ANTICROSS

STATE

AND

LOGIC

CONDUCTION

BUCK, 4SW,

BOOST

COMPARATOR

SW B SW C

MACHINE

THERMAL

SHUTDOWN

V

BEST

V

OUT

PGND

COMBINED

FOR TSOT

V

MODE DETECT

GND

IN

PEAK

CURRENT

365mA

V

1.65V

LIMIT

IN

UVLO

I

ZERO/IVALLEY

BEST

AND

1.225V V

FOR ADJ VERSION

SW D

DETECT

R1

INTERNAL

R1 AND R2

DISABLED

V

V

REF

IN

OUT

R2

3531 BD

V

OUT

FB

NOT BONDED

FOR 3.3V AND

3V VERSIONS

8

3531fb

OPERATIO

LTC3531/

LTC3531-3.3/LTC3531-3

U

The LTC3531, LTC3531-3.3 and LTC3531-3 synchronous buck-boost converters utilize a Burst Mode control

technique to achieve high effi ciency over a wide dynamic

range of load currents. A 2% accurate comparator is

used to monitor the output voltage. If V

is above its

OUT

programmed reference threshold no switching occurs and

only quiescent current is drawn from the power source

(sleep mode). When V

drops below the reference

OUT

threshold the IC “wakes up”, switching commences, and

the output capacitor is charged. The value of the output

capacitor, the load current, and the comparator hysteresis

(~1%) determines the number of current pulses required

to pump-up the output capacitor before the part returns

to sleep.

In order to determine the best operating mode for the

converter, the LTC3531 contains a second comparator

that monitors the relative voltage difference between V

and V

. Input and output voltages in the various modes

OUT

IN

as well as typical inductor currents are shown in Figure 1.

Regions of the current waveforms where switches A and

D are on provide the highest effi ciency since energy is

transferred directly from the input source to the output.

Boost Mode

is ~400mV below V

If V

IN

, the LTC3531 operates in

OUT

boost or step-up mode. Referring to Figure 1 (left side)

when V

and C are turned on (V

and current is ramped until I

falls below its regulation voltage, switches A

OUT

is applied across the inductor)

IN

is detected. When this

PEAK

occurs, C is turned off, D is turned on and current is delivered to the output capacitor (V

IN

– V

is applied across

OUT

the inductor). Inductor current falls when D is on, until an

I

VALLEY

is detected. Terminating at I

VALLEY

, rather than I

ZERO

,

results in an increased load current capability for a given

peak current. This AC then AD switch sequence is repeated

until the output is pumped above its regulation voltage, a

fi nal I

(I

VALLEY

V

OUT

is detected, and the part returns to sleep mode

ZERO

is ignored and I

is used in all modes once

ZERO

is above its programmed value).

4-Switch Mode

If (V

– 400mV) < ~VIN < (V

OUT

+ 800mV), the LTC3531

OUT

operates in 4-switch step-up/down mode. Returning to

Figure 1 (center) when V

falls below its regulation volt-

OUT

age, switches A and C are turned on and current is ramped

until I

is detected. As with Boost Mode operation, C

PEAK

is then turned off, D is turned on and current is delivered

to the output. When A and D are on, the inductor current

, V

slope is dependant on the relationship between V

and the R

of the switches. In 4-switch mode, a t

DSON

IN

OUT

OFF

,

timer (approximately 3μs) is used to terminate the AD

pulse. Once the t

B is turned on and inductor current is ramped down (V

is applied across the inductor) until I

timer expires, switch A is turned off,

OFF

is detected.

VALLEY

OUT

This sequence is repeated until the output is regulated,

BD switches are turned on, and a fi nal I

is detected.

ZERO

Anticross conduction circuitry in all modes ensures the

P-channel MOSFET and N-channel MOSFET switch pairs (A

and B or D and C) are never turned on simultaneously.

V

IN

A

SW1 SW2

BC

D

L

V

OUT

V

OUT

V

IN

I

MAX

I

PEAK

t

OFF

I

VALLEY

I

ZERO

AC AC AC AD AD ADADAD AD AD ACAC BD BDBD BD BD

BOOST MODE 4SW MODE BUCK MODE

Figure 1. Voltage and Current Waveforms

t

OFF

t

OFF

V

IN

3531 F01

3531fb

9

LTC3531/

LTC3531-3.3/LTC3531-3

U

OPERATIO

Buck Mode

is ~800mV above V

If V

IN

buck or step-down mode. The higher offset between V

and V

(800mV) is required to ensure suffi cient mag-

OUT

netizing voltage across the inductor when the R

, the LTC3531 operates in

OUT

IN

DSONS

are taken into account. At the beginning of a buck mode

cycle (Figure 1 right side) switches A and D are turned

IN

– V

on (V

is delivered to the output and ramped up until I

is applied across the inductor), current

OUT

PEAK

is

detected. When this occurs, A is turned off, B is turned

on and inductor current falls (–V

tor) until an I

is detected. This AD then BD switch

VALLEY

across the induc-

OUT

sequence is repeated until the output is pumped above

its regulation voltage, a fi nal I

is detected, and the

ZERO

part returns to sleep mode.

Start-Up Mode

Before V

reaches approximately 1.6V, the D switch is

OUT

disabled and its body diode is used to transfer current to

the output capacitor. In start-up mode, the I

VALLEY/IZERO

sense circuit is disabled and an alternate algorithm is used

to control inductor current. When the LTC3531 is brought

out of shutdown (assuming V

is discharged) switches

OUT

A and C are turned on until the inductor current reaches

. The AC switches are then turned off and inductor

I

PEAK

current fl ows to the output through the B switch and D

body diode. The period for the B switch/D body diode is

controlled by the t

AC switch-on to I

~800ns is repeated until V

timer to ~800nS. This sequence of

OFF

then B switch and D body diode for

PEAK

reaches ~1.6V. Once this

OUT

threshold is reached, the LTC3531 will transfer through the

required modes until V

is brought into regulation.

OUT

Due to propagation delays in the sense circuitry, the

magnitudes of the I

PEAK

shift depending on V

IN

, I

, V

, and I

VALLEY

and operating mode.

OUT

ZERO

currents may

OTHER LTC3531 FEATURES

SHDN

or V

IN

, as long

OUT

below

OUT

.

Shutdown: The part is shut down by pulling

0.4V, and made active by pulling the pin up to V

SHDN

Note that

an be driven above VIN or V

as it is limited to less than 6V.

Output Disconnect and Inrush Limiting: The LTC3531

is designed to allow true output disconnect by opening

both P-channel MOSFET rectifi ers. This allows V

OUT

to go

to zero volts during shutdown, drawing no current from

the input source. It also provides inrush current limiting

at turn-on, minimizing surge currents seen by the input

supply.

Thermal Shutdown: If the die temperature reaches approximately 150°C, the part will go into thermal shutdown and all switches will be turned off. The part will be

enabled again when the die temperature has dropped by

10°C (nominal). To deliver the power that the LTC3531

is capable of, it is imperative that a good thermal path be

provided to dissipate the heat generated within the package. It is recommended that multiple vias in the printed

circuit board be used to conduct heat away from the IC

and into a copper plane with as much area as possible.

Soldering the Exposed Pad to the GND plane (DFN version)

is recommended to improve thermal performance.

10

3531fb

LTC3531/

LTC3531-3.3/LTC3531-3

U

WUU

S I FOR ATIOAPPLICATIO

Component Selection

Only three power components are required to

complete the design of the buck-boost converter, V

programming resistors are needed for the adjustable

version. The high operating frequency and low peak

currents of the LTC3531 allow the use of low value, low

profi le inductors and tiny external ceramic capacitors.

Inductor Selection

For best effi ciency, choose an inductor with high frequency

core material, such as ferrite, to reduce core loses. The

inductor should have low DCR (DC resistance) to reduce

2

R losses, and must be able to handle the peak

the I

inductor current without saturating. A 10μH to 22μH in-

Table 2. Inductor Vendor Information

Supplier Series Phone Website

COEV DN4835 (800) 227-7040 www.coev.net

Coilcraft MSS4020 (847) 639-6400 www.coilcraft.com

LPO3310

DS1608

Murata LQH43CN USA: (814) 237-1431 www.murata.com

LQH32CN (800) 831-9172

Sumida CDRH4D18 USA: (847) 956-0666 www.sumida.com

CDRH3D16/HP Japan: 81-3-3607-5111

Toko D312C (847) 297-0070 www.tokoam.com

D412C

DB320C

OUT

ductor value with a >500mA current rating and <400mΩ

DCR is recommended. For applications where radiated

noise is a concern, a toroidal or shielded inductor can be

used. Table 2 contains a list of inductor manufacturers.

Capacitor Selection

The buck-boost convertor requires two capacitors. Ceramic

X5R types will minimize ESL and ESR while maintaining

capacitance at rated voltage over temperature. The V

capacitor should be at least 2.2μF. The V

capacitor

OUT

IN

should be between 4.7μF and 22μF. A larger output capacitor should be used if lower peak to peak output voltage

ripple is desired. A larger output capacitor will also improve

load regulation on V

. See Table 3 for a list of capacitor

OUT

manufacturers for input and output capacitor selection.

Table 3. Capacitor Vendor Information

Supplier Series Phone Website

AVX X5R (803) 448-9411 www.avxcorp.com

Murata X5R USA: (814) 237-1431 www.murata.com

(800) 831-9172

Sanyo POSCAP (619) 661-6322 www.sanyovideo.com

Taiyo Yuden X5R (408) 573-4150 www.taiyo-yuden.com

TDK X5R (847) 803-6100 www.component.tdk.com

3531fb

11

LTC3531/

LTC3531-3.3/LTC3531-3

U

WUU

S I FOR ATIOAPPLICATIO

SHUTDOWN

C

C

V

IN

GND GND

IN

4 – SHDN

5 – V

IN

6 – SW1 SW2 – 1

SOT PIN-OUT

OUT

V

OUT

L

V

– 3

OUT

GND – 2

Recommended Layout (SOT Versions)

12

3531fb

TYPICAL APPLICATIO

LTC3531/

LTC3531-3.3/LTC3531-3

U

5V/Li-Ion to 3.3V with ThinSOT (3.3V Version)

V

IN

3.1V TO

5V

5V/Li-Ion

V

IN

1.8V TO

3.2V

2 x AA

ALKALINE

10μH

SW1 SW2

V

V

IN

OUT

+

–

LTC3531-3.3

2.2μF10μF

SHDN GND

ON OFF

V

OUT

3.3V

160mA

3531 TA02a

95

90

85

80

EFFICIENCY (%)

75

70

65

0.1 10 100 1000

4.4V

IN

5V

IN

3.6V

IN

3.1V

IN

POWER LOSS AT 3.6V

1

LOAD CURRENT (mA)

IN

100

POWER LOSS (mW)

10

1

0.1

3531 TA02b

2 AA Alkaline to 3V with ThinSOT (3V Version)

90

10μH

SW1 SW2

V

V

IN

+

–

2.2μF10μF

+

–

ON OFF

OUT

LTC3531-3

SHDN GND

V

OUT

3V

80mA

3531 TA03a

85

80

2.5V

IN

3.2V

75

EFFICIENCY (%)

70

65

60

0.1 10 100 1000

IN

1.8V

POWER LOSS AT 3.2V

1

LOAD CURRENT (mA)

IN

IN

100

POWER LOSS (mW)

10

1

0.1

3531 TA03b

USB

4.35V TO

5.25V

1Ω

4.7μF

2.2μF

10μH

SW1 SW2

V

IN

LTC3531

SHDN GND

ON OFF

USB to 5V with 3 × 3 DFN (Adjustable Version)

V

V

OUT

R2

1M

FB

R1

324k

OUT

5V

200mA

10μF

3531 TA04a

95

90

85

80

EFFICIENCY (%)

75

70

65 0.1

0.1 10 100 1000

EFFICIENCY

POWER LOSS

1

LOAD CURRENT (mA)

3531 TA04b

100

POWER LOSS (mW)

10

1

3531fb

13

LTC3531/

LTC3531-3.3/LTC3531-3

U

PACKAGE DESCRIPTIO

S6 Package

6-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1636)

3.85 MAX

0.20 BSC

0.62

MAX

2.62 REF

RECOMMENDED SOLDER PAD LAYOUT

PER IPC CALCULATOR

DATUM ‘A’

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

0.95

REF

0.30 – 0.50 REF

1.22 REF

1.4 MIN

2.90 BSC

(NOTE 4)

2.80 BSC

0.09 – 0.20

(NOTE 3)

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193

1.50 – 1.75

(NOTE 4)

PIN ONE ID

0.95 BSC

0.80 – 0.90

1.00 MAX

1.90 BSC

0.30 – 0.45

6 PLCS (NOTE 3)

0.01 – 0.10

S6 TSOT-23 0302

14

3531fb

PACKAGE DESCRIPTIO

LTC3531/

LTC3531-3.3/LTC3531-3

U

DD Package

8-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1698)

0.675 ±0.05

3.5 ±0.05

1.65 ±0.05

(2 SIDES)2.15 ±0.05

PACKAGE

OUTLINE

0.25 ± 0.05

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

PIN 1

TOP MARK

(NOTE 6)

0.200 REF

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-1)

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON TOP AND BOTTOM OF PACKAGE

0.50

BSC

2.38 ±0.05

(2 SIDES)

3.00 ±0.10

(4 SIDES)

0.75 ±0.05

0.00 – 0.05

1.65 ± 0.10

(2 SIDES)

R = 0.115

TYP

0.25 ± 0.05

2.38 ±0.10

(2 SIDES)

BOTTOM VIEW—EXPOSED PAD

0.38 ± 0.10

85

14

0.50 BSC

(DD) DFN 1203

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

no responsibility is assumed for its use. Linear Technology Corporation makes no representation that

the interconnection of its circuits as described herein will not infringe on existing patent rights.

However,

3531fb

15

LTC3531/

LTC3531-3.3/LTC3531-3

U

TYPICAL APPLICATIO

Complete USB/Li-Ion Powered System

with 3.3V

and Linear Charger

OUT

5V (NOM)

FROM USB

CABLE

SUSPEND

USB POWER

+

Li-Ion

–

C1, C2: TAIYO YUDEN JMK316BJ106ML

L1: MURATA LQH43CN100K03 (650mA 0.24Ω)

IN1

IN2

HPWR

SUSP

BAT

GND

SHDN

LTC4055

CLPROG

WALL NTC

OUT

CHRG

ACPR

VNTC

TIMER

PROG

V

: USB OR BATTERY

OUT

100k

100k

0.1μF

OTHER

DC/DC

3.1V TO 5.25V

C1

22μF

L1

10μH

SW1 SW2

V

V

IN

OUT

LTC3531-3.3

SHDN

GND

V

OUT

3.3V

160mA

C2

10μF

3531 TA05

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LT1930/LT1930A 1A (I

I

LTC3400/LTC3400B 600mA (ISW), 1.2MHz Synchronous Step-Up DC/DC Converter VIN: 0.85V to 5V, V

I

LTC3401/LTC3402 1A/2A (ISW), 3MHz Synchronous Step-Up DC/DC Converter VIN: 0.5V to 5V, V

I

LTC3405/LTC3405A 300mA (I

I

LTC3406/LTC3406B 600mA (I

I

LTC3421 3A (ISW), 3MHz Synchronous Step-Up DC/DC Converter VIN: 0.5V to 4.5V, V

I

LTC3422 1.5A (ISW), 3MHz Synchronous Step-Up DC/DC Converter VIN: 0.5V to 4.5V, V

I

LTC3426 2A (I

LTC3428 4A (ISW), 1.2MHz Step-Up DC/DC Converter VIN: 1.6V to 5V, V

LTC3429 600mA (ISW), 500kHz Synchronous Step-Up DC/DC Converter VIN: 0.5V to 4.4V, V

I

LTC3440 600mA (I

I

LTC3441 600mA (I

I

LTC3442 2MHz Synchronous Buck-Boost with Auto-Burst VIN: 2.4V to 5.5V, V

LTC3443 1.2A (I

I

LTC3458 1.4A, 1.5MHz Synchronous Step-Up DC/DC Converter VIN: 1.5V to 6V, V

LTC3458L 1.7A, 1.5MHz Synchronous Step-Up DC/DC Converter VIN: 1.5V to 6V, V

LTC3459 10V Micropower Synchronous Step-Up DC/DC Converter VIN: 1.5V to 5.5V, V

LTC3525/LTC3525-3.3/ 400mA (ISW), Synchronous Step-Up DC/DC Converter VIN: 0.5V to 4.5V, IQ = 7μA, ISD < 1μA,

LTC3525-5 with Output Disconnect 2mm × 2mm SC70 Package

Linear Technology Corporation

16

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900

), 1.2MHz/2.2MHz, High Effi ciency Step-Up DC/DC Converter VIN: 2.6V to 16V, V

SW

), 1.5MHz Synchronous Step-Down DC/DC Converter VIN: 2.7V to 6V, V

OUT

), 1.5MHz Synchronous Step-Down DC/DC Converter VIN: 2.5V to 5.5V, V

OUT

), 1.2MHz Step-Up DC/DC Converter in SOT-23 VIN: 1.6V to 5V, V

SW

), 2MHz Synchronous Buck-Boost DC/DC Converter VIN: 2.5V to 5.5V, V

OUT

), 2MHz Synchronous Buck-Boost DC/DC Converter VIN: 2.5V to 5.5V, V

OUT

), 600kHz Synchronous Buck-Boost DC/DC Converter VIN: 2.4V to 5.5V, V

OUT

●

FAX: (408) 434-0507 ● www.linear.com

= 4.2mA/5.5mA, ISD < 1μA, ThinSOT Package

Q

= 19μA/300μA, ISD < 1μA, ThinSOT Package

Q

SD

SD

SD

SD

SD

SD

SD

SD

SD

= 34V,

OUT(MAX)

= 5V,

OUT(MAX)

= 6V, IQ = 38μA,

OUT(MAX)

< 1μA, MS Package

= 0.8V, IQ = 20μA,

OUT(MIN)

≤ 1μA, MS10 Package

= 0.6V, IQ = 20μA,

OUT(MIN)

≤ 1μA, ThinSOT Package

= 5.25V, IQ = 12μA,

OUT(MAX)

< 1μA, QFN Package

= 5.25V, IQ = 25μA,

OUT(MAX)

< 1μA, 3mm × 3mm DFN Package

up to 5.5V

OUT

up to 5.5V

OUT

= 5V, IQ = 20μA,

OUT(MIN)

< 1μA, QFN Package

= 5.5V, IQ = 25μA,

OUT(MIN)

< 1μA, MS, DFN Packages

= 5.5V, IQ = 25μA,

OUT(MIN)

< 1μA, DFN Package

up to 5.25V

OUT

= 5.25V, IQ = 28μA,

OUT(MIN)

< 1μA, MS Package

up to 7.5V

OUT

up to 6V

OUT

up to 10V

OUT

LT 0807 REV B • PRINTED IN USA

© LINEAR TECHNOLOGY CORPORATION 2006

3531fb

Loading...

Loading...