LINEAR TECHNOLOGY

LINEAR TECHNOLOGY

LINEAR TECHNOLOGY

JUNE 2008 VOLUME XVIII NUMBER 2

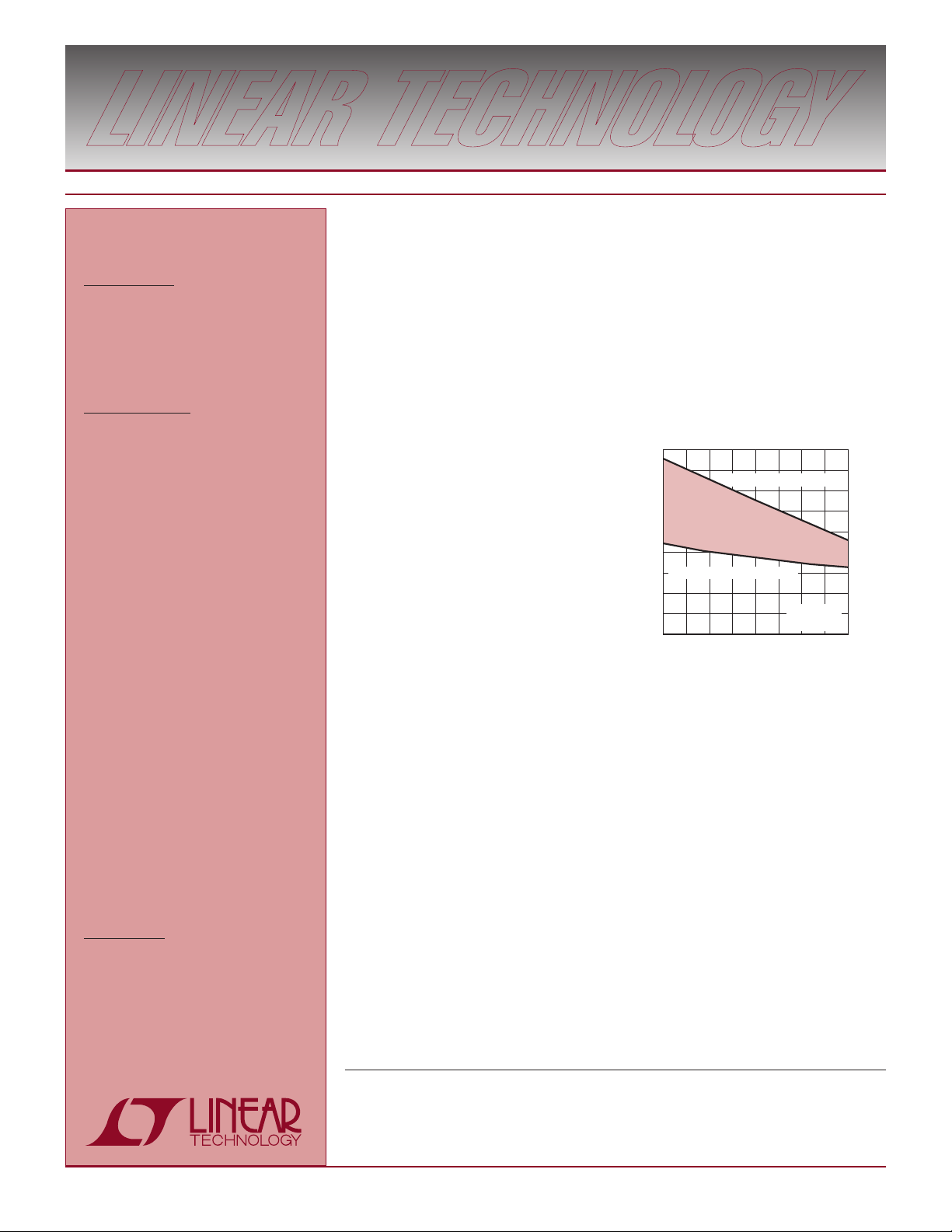

POWER DISSIPATION (W)

BATTERY VOLTAGE (V)

4.13.3

1.8

0

3.4 3.5 3.6 3.7 3.8 3.9 4.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

VIN = 5V

I

CHARGE

= 1A

LINEAR BATTERY CHARGER

SWITCHING BATTERY CHARGER

EN

ADDITIONAL

POWER AVAILABLE

FOR CHARGING

IN THIS ISSUE…

COVER ARTICLE

Speed Up Li-ion Battery Charging

and Reduce Heat with a Switching

PowerPath™ Manager ..........................1

Steven Martin

Linear in the News… ...........................2

DESIGN FEATURES

Hot Swap™ Controller Enables

Standard Power Supplies to

Share Load ........................................6

Vladimir Ostrerov

Understanding IP2 and IP3 Issues in

Direct Conversion Receivers for

WCDMA Wide Area Basestations .......10

Doug Stuetzle

Complete Dual-Channel Receiver

Combines 14-Bit, 125Msps ADCs,

Fixed-Gain Amplifiers and Antialias

Filters in a Single 11.25mm × 15mm

μModule™ Package ...........................14

Todd Nelson

Battery Manager Enables Integrated,

Efficient, Scalable and Testable

Backup Power Systems......................17

Mark Gurries

500nA Supply Supervisors Extend

Battery Life in Portable Electronics ..22

Bob Jurgilewicz

Quad Output Regulator Meets Varied

Demands of Multiple Power Supplies

.........................................................25

Michael Nootbaar

Buck, Boost and LDO Regulators

Combined in a 4mm × 4mm QFN ........28

Chris Falvey

DESIGN IDEAS

....................................................30–41

(complete list on page 30)

New Device Cameos ...........................42

Design Tools ......................................43

Sales Offices .....................................44

Speed Up Li-ion Battery Charging and Reduce Heat with a Switching PowerPath Manager

by Steven Martin

Introduction

Designers of handheld products race

to pack as many “cool” features as

possible into ever smaller devices. Big,

bright color displays, Wi-Fi, WiMax,

Bluetooth, GPS, cameras, phones,

touch screens, movie players, music

players and radios are just a few of

the features common in today’s battery powered portable devices. One

big problem with packing so many

features into such a small space is

that the “cool” product must actually

stay cool while in use. Minimizing dissipated heat is a priority in handhelds,

and a significant source of heat is the

battery charger.

One component of handhelds has

changed little over the years—the

Li-ion battery. While the capacities

of today’s batteries have increased

from a few hundred milliampere hours

to several ampere-hours to accommodate the ever expanding feature

set of modern portable products, the

basic Li-Ion battery technology has

remained unchanged. Why has Li-ion

survived so long? Unmatched energy

density (both by mass and volume),

high voltage, low self-discharge, wide

usable temperature range, no memory

effect, no cell reversal, no cell balancing, and low environmental impact all

make the Li-Ion battery the preferred

L

, LT, LTC, LTM, Burst Mode, OPTI-LOOP, Over-The-Top and PolyPhase are registered trademarks of Linear Technology

Corporation. Adaptive Power, Bat-Track, BodeCAD, C-Load, DirectSense, Easy Drive, FilterCAD, Hot Swap, LinearView,

µModule, Micropower SwitcherCAD, Multimode Dimming, No Latency ΔΣ, No Latency Delta-Sigma, No R

Filter, PanelProtect, PowerPath, PowerSOT, SmartStart, SoftSpan, Stage Shedding, SwitcherCAD, ThinSOT, True Color PWM,

UltraFast and VLDO are trademarks of Linear Technology Corporation. Other product names may be trademarks of the

companies that manufacture the products.

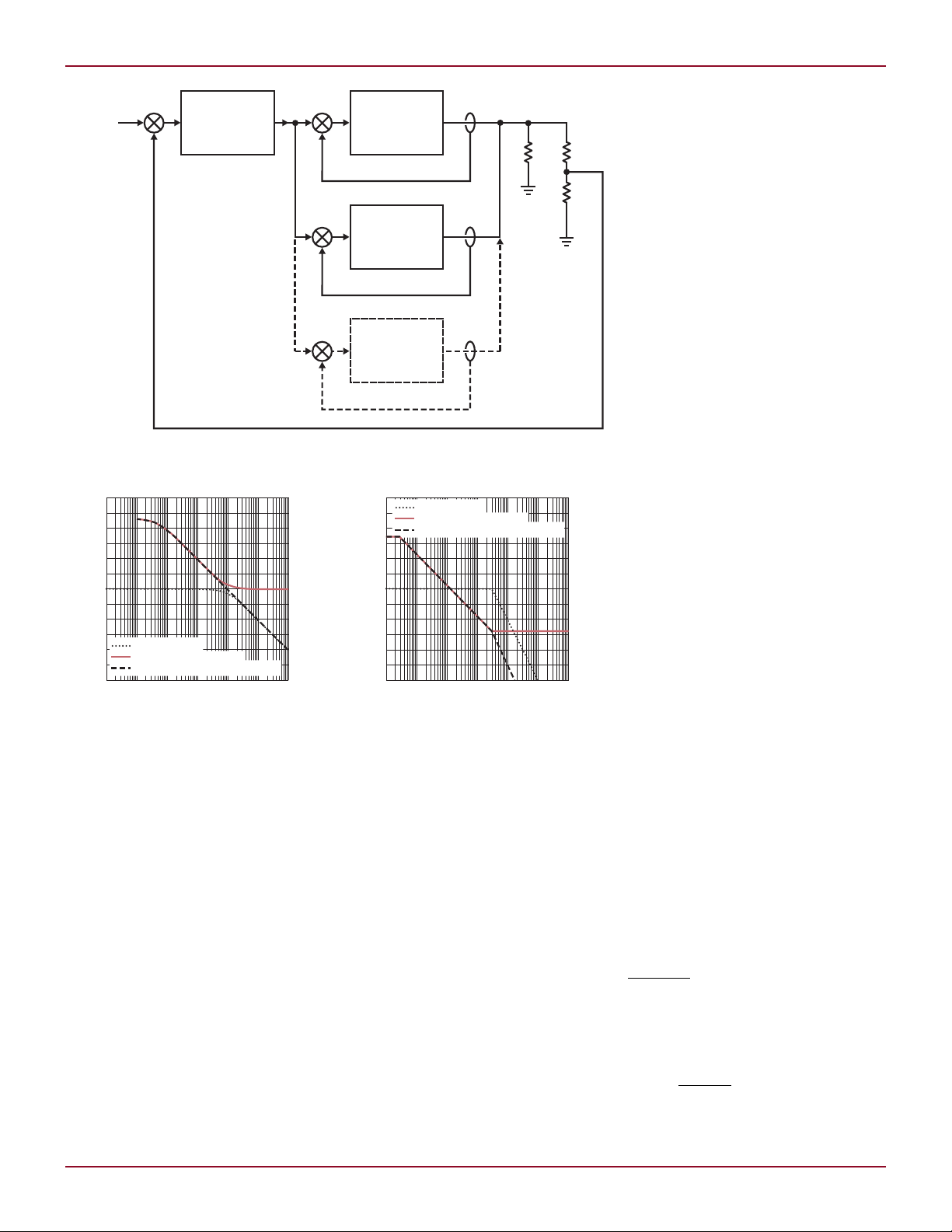

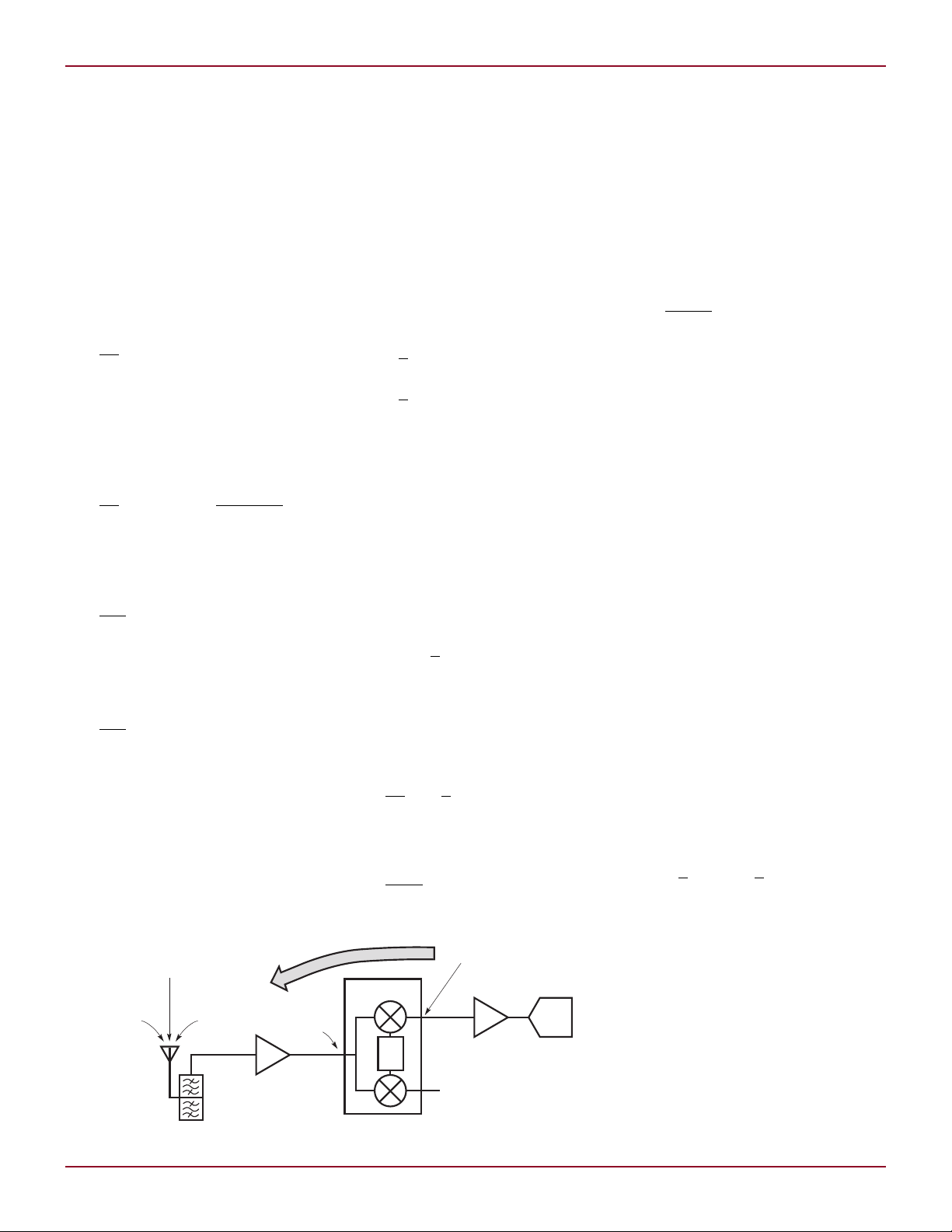

Figure 1. Reduce battery charge time and keep

handheld devices cool by using a switching

PowerPath manager/battery charger.

choice for high performance portable

products.

Charging today’s big batteries,

however, is no small deal. In order to

charge them in a reasonable amount

of time, they should be charged at a

rate commensurate with their capacity

and with a specific algorithm. For example, to fully charge a 1Ah battery in

approximately one hour requires one

amp of charge current. If USB powered

charging is desired, then only 500mA

of current is available, doubling the

charge time to two hours.

Another problem with higher charge

currents is the additional heat lost in

continued on page 3

, Operational

SENSE

L LINEAR IN THE NEWS

Linear in the News…

EDN Innovation Award for

Linear Power Device

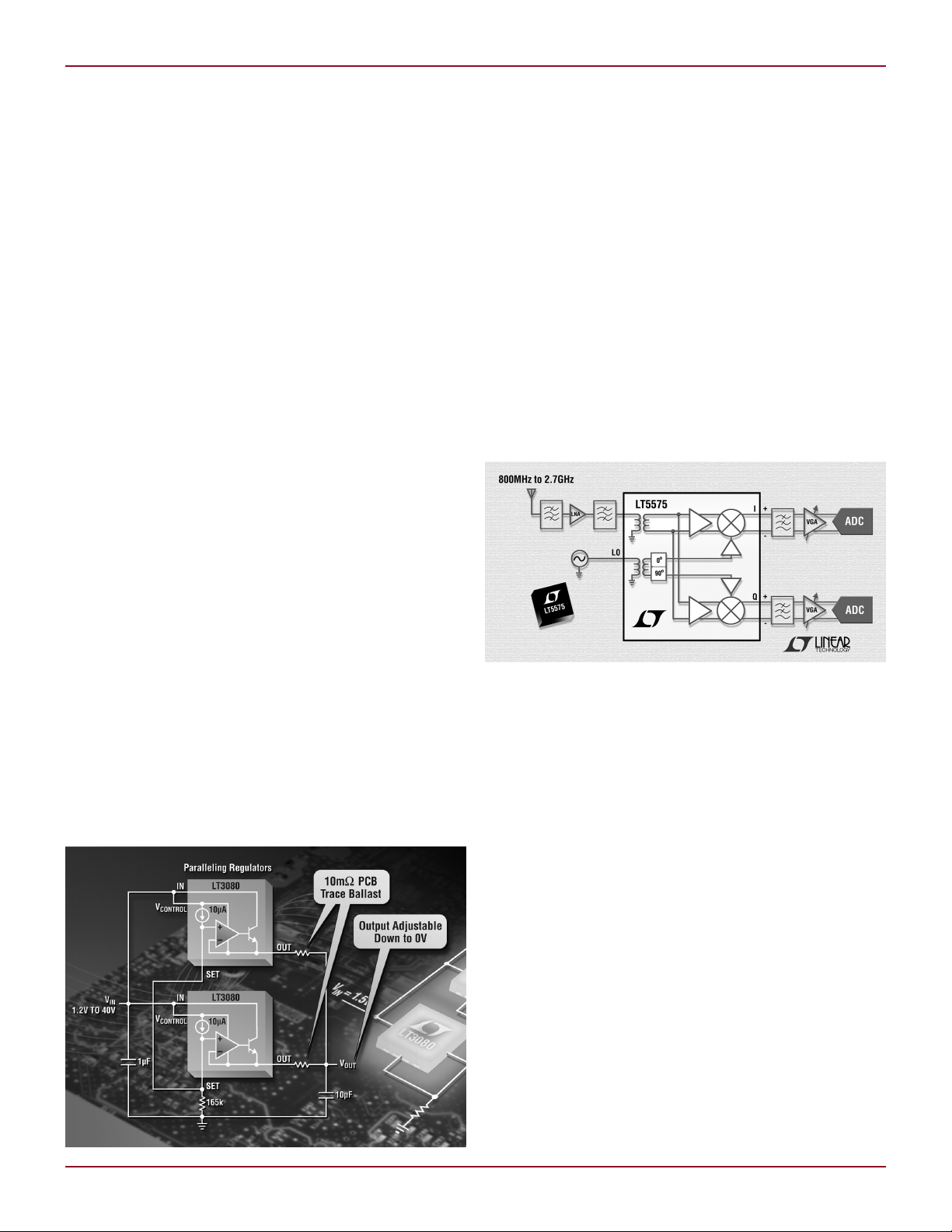

EDN magazine announced the selection of Linear’s LT3080

3-terminal parallelable low dropout linear regulator as

EDN’s Innovation of the Year in the Power ICs category.

The award was presented at the annual EDN Innovation

Awards ceremony to Linear Technology Vice President

Engineering and Chief Technical Officer Robert Dobkin and

Design Engineer Todd Owen, who developed the product.

Other Linear Technology finalists included the LTC6102

current sense amplifier in the Analog ICs category, Robert

Dobkin for Innovator of the Year, and Jim Williams’ article,

“Designing instrumentation circuitry with RMS/DC converters” for Best Contributed Article.

According to Ron Wilson, Executive Director of EDN

Worldwide, “Selected by their peers in the design community for their outstanding results, these innovators

stand in the front rank of the best and brightest electronics

engineering has to offer.”

Robert Dobkin stated, “The LT3080 solves two difficult

problems for linear regulators: spreading heat to eliminate

heat sinks and increasing output current by simply adding

additional devices. The circuit architecture is completely

new and just as easy to use as older devices. I am proud

to introduce this product.”

The LT3080 is a 1.1A 3-terminal linear regulator that can

easily be paralleled for heat spreading and higher output

current, and is adjustable to zero with a single resistor.

This is a new architecture for regulators and uses a current

reference and voltage follower to allow sharing between

multiple regulators, enabling multiamp linear regulation

in all surface-mount systems without heat sinks.

The LT3080 has a wide input voltage capability of 1.2V

to 40V, a dropout voltage of only 300mV and millivolt

regulation. The output voltage is adjustable, spanning

a wide range from 0V to 40V, and the on-chip trimmed

reference achieves high accuracy of ±1%.

Hot Products in Asia

EDN Asia magazine recently announced their list of the

100 Hot Products of 2007. Included in the list are three

Linear Technology products:

q

LTC6400 Low Noise, Low Distortion ADC Driver

q

LT4356 Overvoltage Protection Regulator

q

LT3080 3-Terminal Linear Regulator

For more information, visit www.linear.com.

Editor’s Choice Award

Portable Design magazine recently announced their

selections for their annual Editor’s Choice Awards. In the

RF/Microwave category, the award went to the LT5575

Direct Conversion I/Q Demodulator. The LT5575, which

was also selected by Electronic Products magazine as

Product of the Year, significantly reduces the cost of 3G

and WiMAX basestation receivers. The LT5575’s extended

operating frequency range from 800MHz to 2.7GHz covers

all of the cellular and 3G infrastructure, WiMAX and RFID

bands with a single part. Its capability to convert from

RF directly to baseband at DC or low frequency results

in simplified receiver designs, reduced component count

and use of lower cost, low frequency components.

The LT5575 offers an outstanding IIP3 of 28dBm and

IIP2 of 54.1dBm at 900MHz, and an IIP3 of 22.6dBm

and IIP2 of 60dBm at 1.9GHz. Moreover, the device has

a conversion gain of 3dB, which when combined with a

DSB Noise Figure of 12.7dB, produces excellent receiver

dynamic range. The device’s I (In-phase) and Q (Quadrature phase) outputs have typical amplitude and phase

matching of 0.04dB and 0.6°, respectively, providing an

unprecedented level of demodulation accuracy.

The LT5575 is capable of supporting multiband

basestations covering both the 850MHz GSM/EDGE bands

and the 1.9GHz/2.1GHz 3G wireless services (including

CDMA2000, WCDMA, UMTS, and TD-SCDMA). It is ideal

for single carrier micro- and pico-basestations, where low

cost architectures are key. The LT5575’s performance is

also well suited for 2.6GHz WiMAX basestations, and as

an IF demodulator in a microwave radio link or satellite

receiver.

L

2

2

Linear Technology Magazine • June 2008

LTC4088/LTC4098, continued from page 1

1V

CLPROG

I

SWITCH

/

h

CLPROG

+

–

15mV

IDEAL

DIODE

AVERAGE INPUT

CURRENT LIMIT

CONTROLLER

CONSTANT CURRENT

CONSTANT VOLTAGE

BATTERY CHARGER

+

–

TO SYSTEM

LOAD

SINGLE CELL

Li-Ion

BAT

V

IN

V

OUT

TO USB

OR WALL

ADAPTER

+

the charging process. Since charge

power for these devices usually comes

from a 5V source, such as a USB port

or 5V wall adapter, power loss can be

significant. Assuming a healthy LiIon battery spends significant time

at its “happy voltage” of 3.7V during

charging, then charging efficiency via

a linear charging element can at best

be 3.7V/5V or 74%. When the battery

voltage is less than 3.7V, losses are

even worse. Even at the maximum

float voltage of 4.2V, where the battery spends about 1/3 of the charge

time, charging efficiency can’t be better

than 84%.

With a 1Ah battery charged at a

“1C” rate, we can expect about 1.3W of

power to be lost while delivering 3.7W

to the battery over the longest part of

the charge cycle. Note, however, that

the energy delivered to the battery

doesn’t result in any significant temperature rise as the battery is storing

the energy for future use. This means

that the predominant source of heat

during charging is generated by the

charger itself. With this in mind, at

a given power level it makes sense to

move to a switching battery charger

for improved charging efficiency, less

charger generated heat and reduced

charge time.

Both the LTC4088 and LTC4098

are examples of single-cell Li-ion bat-

DESIGN FEATURES L

tery chargers from Linear Technology

that not only offer the high efficiency

of a switching battery charger but

also include PowerPath technology.

PowerPath control is a technique

that uses a third, or intermediate,

node to allow instant-on operation,

which provides power to the system

when the battery voltage is below the

system cutoff. Only products like the

LTC4088 and LTC4098 combine a step

down DC/DC switching regulator with

a linear battery charger in a unique

way that ensures high efficiency power

delivery to both the system load and

the battery. Before we delve into these

parts, let’s take a look at how it was

done before.

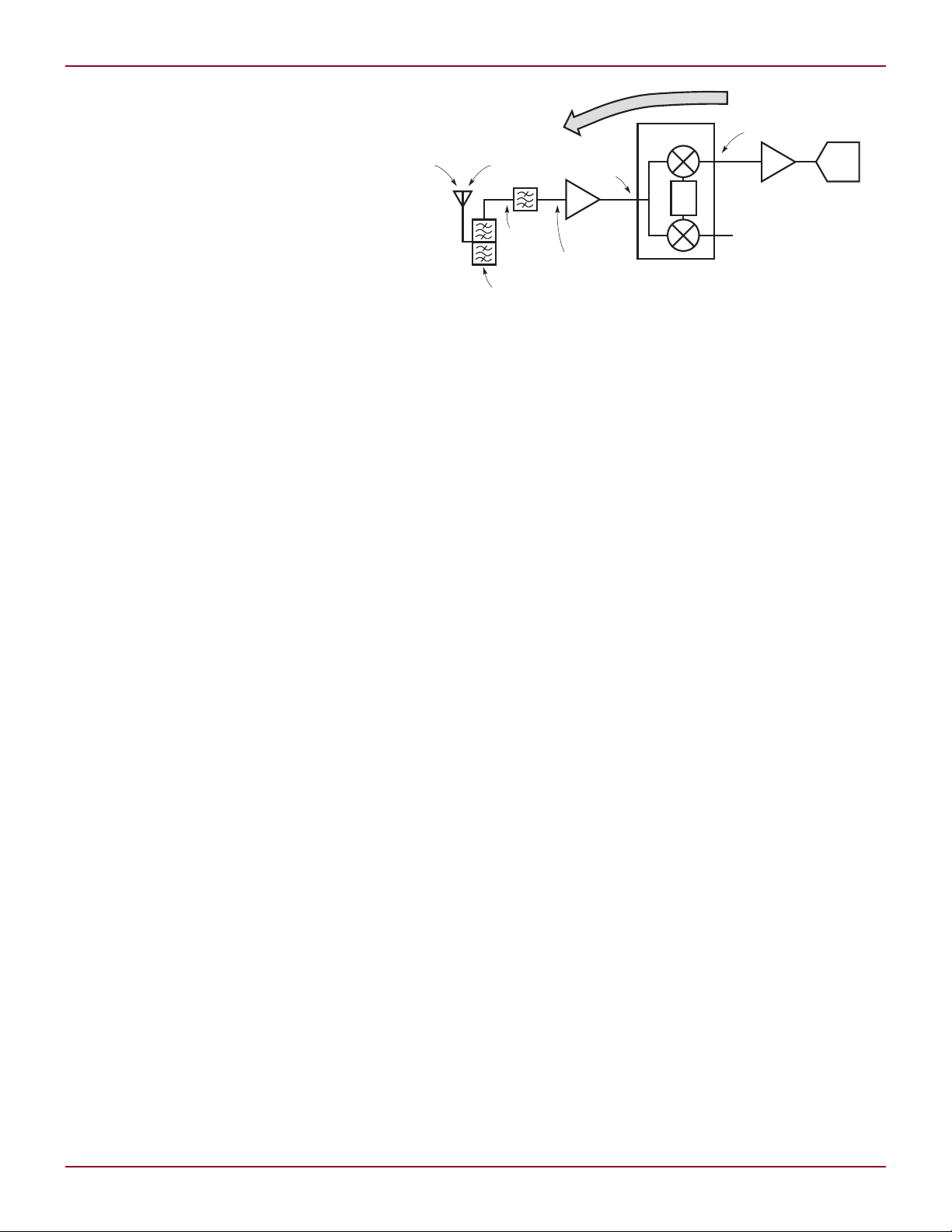

Old School: Linear PowerPath

The intermediate node topology isn’t

new. Figure 2 shows an example of

a linear PowerPath topology. In this

architecture, a current limited switch

delivers power from an input connector

to both the external load and linear

battery charger. The linear battery

charger then delivers power from the

intermediate node to the battery.

If the load current is far enough

below the input current limit to allow

some current to be directed to battery

charging, the voltage at V

equal to the input supply voltage, let’s

say 5V. In this case, the path from VIN to

is nearly

OUT

V

is extremely efficient since there

OUT

is no significant voltage drop across

the pass element. Note, however, that

the voltage drop between V

and V

(say 3.5V) means the linear

BAT

OUT

(~5V)

charger is running inefficiently. Thus,

power delivered to the load arrives efficiently while power delivered to the

battery arrives inefficiently.

Now take the alternate case where

the load current exceeds the input

current limit setting. Here the input

current limit control engages and the

voltage at the intermediate node, V

OUT

,

drops to just under the battery voltage, thus bringing in the battery as a

source of additional current. Although

this is desired behavior, ensuring

load current is prioritized over charge

current, notice that there is now inefficiency at the pass element because

a large voltage difference does exist

between the input pin, again at 5V,

and the output pin, which now may

be about 3.5V.

From these examples we can see

that while a linear PowerPath topology

performs the necessary PowerPath

control functions under all conditions,

it has some inherent inefficiencies.

Specifically, with the linear PowerPath

topology there is likely to be power

wasted in one or the other of the two

linear pass elements under various

conditions. In the next section we’ll see

how a switching PowerPath avoids the

pitfalls of the linear PowerPath.

Figure 2. Block diagram of a traditional linear PowerPath,

Linear Technology Magazine • June 2008

which has significant inherent efficiency limitations.

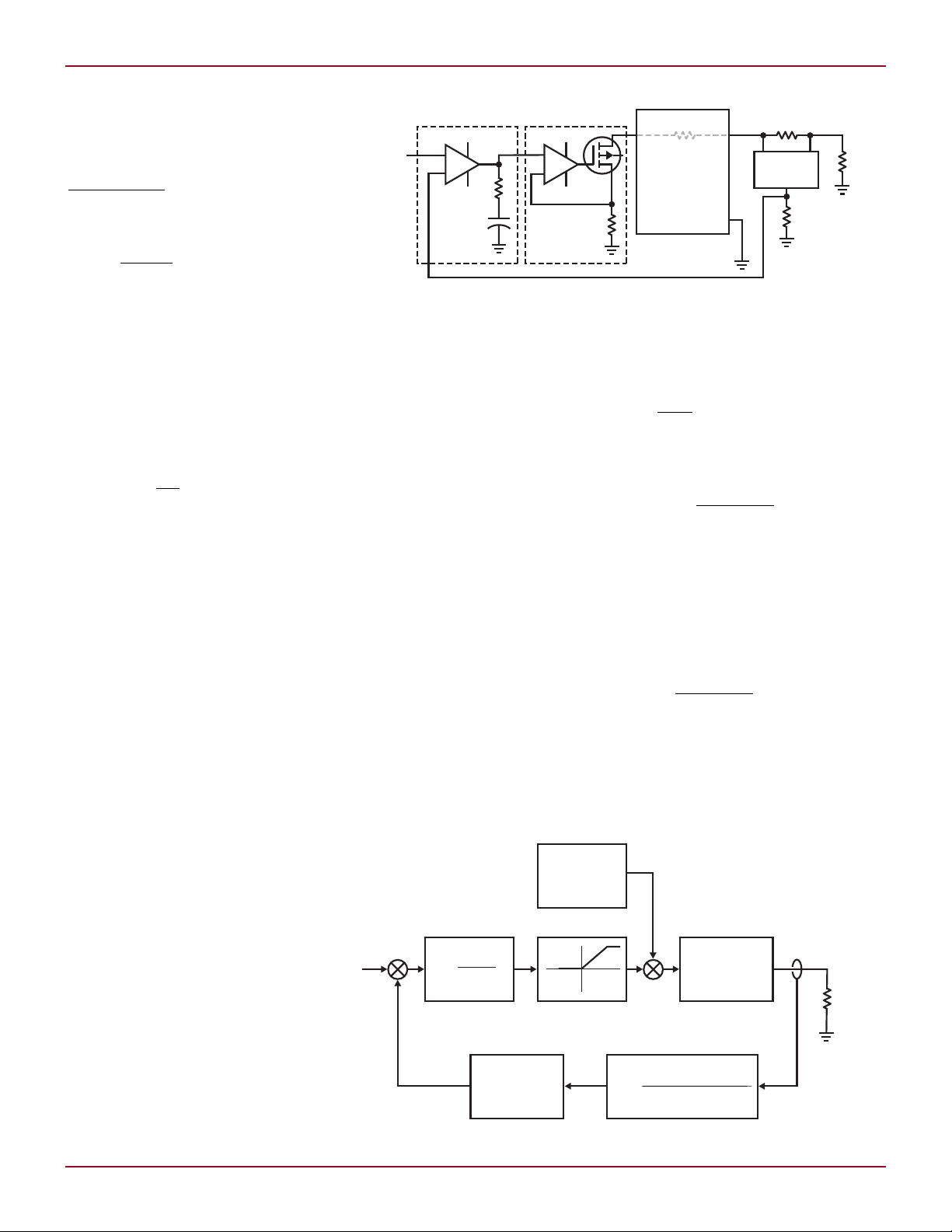

New School: High Efficiency

with Switching PowerPath

Figure 3 shows an alternative to

the linear PowerPath, a switching

PowerPath. Here a step-down DC/DC

converter delivers power from the

input connector to the intermediate

node V

. A linear battery charger is

OUT

connected from the intermediate node

to the battery as in the case of the

linear PowerPath. The big difference

from linear PowerPath is that the path

from VIN to V

maintains relatively

OUT

high efficiency regardless of the voltage difference since it is a switching,

rather than a linear, path.

Then what about the linear battery

charging path, the other big part of

3

L DESIGN FEATURES

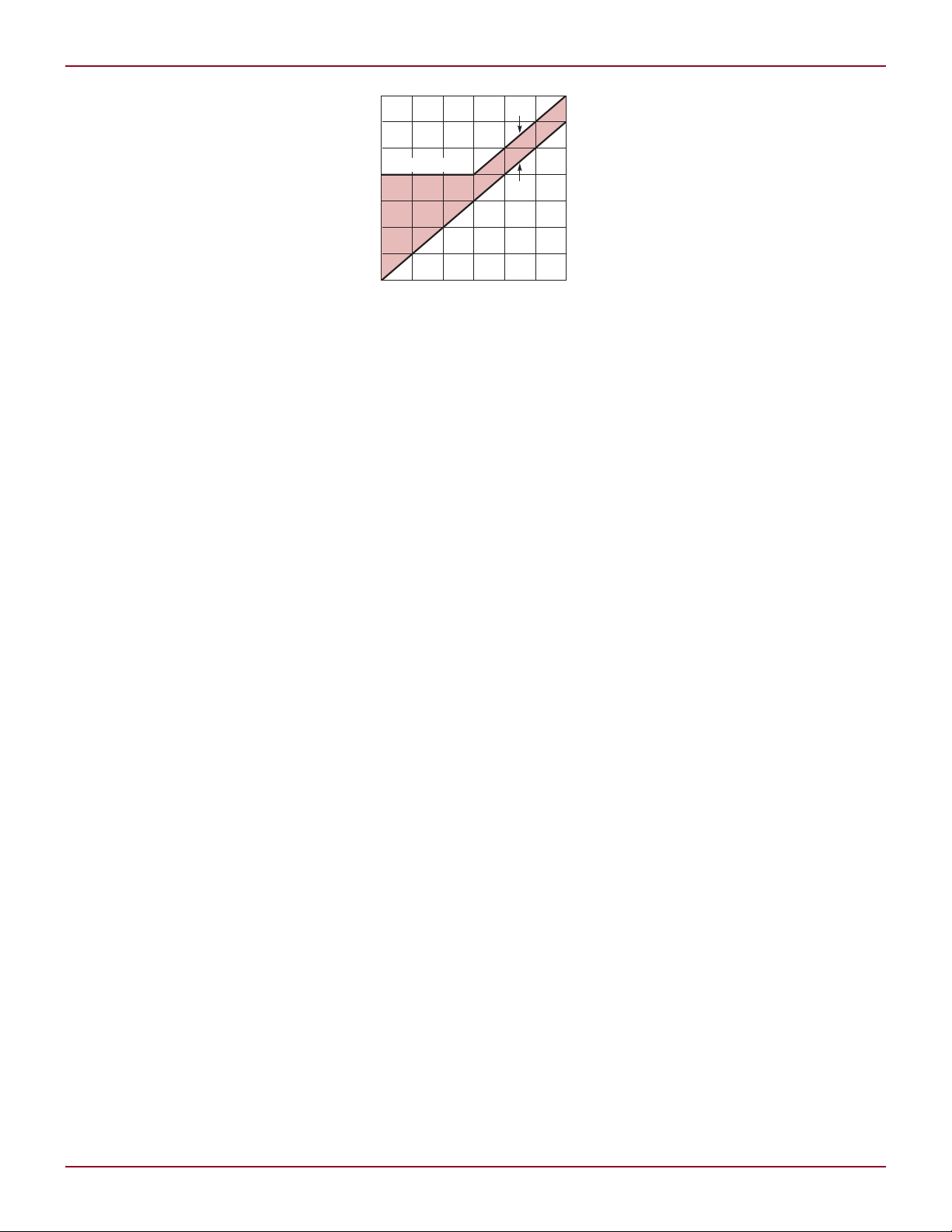

BATTERY VOLTAGE (V)

2.7

500

600

700

3.9

400

300

3.0 3.3 3.6 4.2

200

100

0

CHARGE CURRENT (mA)

V

BUS

= 5V

R

PROG

= 1k

R

CLPROG

= 2.94k

5x USB SETTING,

BATTERY CHARGER SET FOR 1A

+

–

+

+

–

0.3V

1.188V 3.6V

CLPROG

I

SWITCH

/

h

CLPROG

+

–

+

–

15mV

IDEAL

DIODE

PWM AND

GATE DRIVE

AVERAGE INPUT

CURRENT LIMIT

CONTROLLER

AVERAGE OUTPUT

VOLTAGE LIMIT

CONTROLLER

CONSTANT CURRENT

CONSTANT VOLTAGE

BATTERY CHARGER

+

–

GATE

V

OUT

SW

3.5V TO

(BAT + 0.3V)

TO SYSTEM

LOAD

OPTIONAL

EXTERNAL

IDEAL DIODE

PMOS

SINGLE CELL

Li-Ion

BAT

V

BUS

TO USB

OR WALL

ADAPTER

+

2.94k

8.2Ω

0.1µF

3.3µH

10µF

10µF

Si2333DS

LTC4088

Figure 3. Switching PowerPath block diagram. The big advantage of a switching PowerPath scheme over a linear

PowerPath is that the path from VIN to V

maintains relatively high efficiency regardless of the VIN/V

OUT

ratio.

BAT

the total efficiency picture? Voltage

drops between V

would pretty much erase the efficiency

gains made by the switching regulator.

Total efficiency remains high with the

the LTC4088 and LTC4098 because

of a feature called Bat-Track™. With

Bat-Track, the output voltage of the

switching regulator is programmed to

track the battery voltage plus a few

hundred millivolt difference. Since

the output voltage is never significantly above the battery voltage, little

power is ever lost to the linear battery

charger. The battery charger pass element leaves most of the voltage control

duties to the switching regulator and

exists merely to control charge current,

float voltage and battery safety monitoring—tasks at which it excels.

USB-Based

Constant-Power Charging

These days, an important feature

in many portable products is the

convenience of charging from a USB

port. The LTC4088 and LTC4098

have a unique control system that

allows them to limit their input current consumption for USB compliant

applications while maximizing power

available to the load and battery

charging. These two devices not only

have low and high power USB settings

of 100mA and 500mA, but they also

4

and the battery

OUT

support a higher power 1A setting for

wall adapter applications.

For products with large batteries,

USB current control can be the limiting factor in determining how much

power is delivered to the battery for

charging. With a linear PowerPath

topology, input and output are current

limited—the sum of the load current

and the battery charging current

cannot exceed the input current. In

this case, a switching PowerPath has

a significant advantage over a linear

PowerPath. In a switching PowerPath

topology the input is still current

limited, but this only limits available

power to the load and charger. This

is an important distinction. Figure 4

shows an example of how the LTC4088

can provide up to a 40% increase in

Figure 4. Input power limited charge current

charge current over a linear PowerPath

design.

Notice that while the USB current is

limited to 500mA, it’s possible for the

charge current to be above 500mA due

to the high efficiency of the switching

PowerPath system. So not only does the

higher efficiency produce little heat,

but it also reduces charge time.

The input current limited topology

of the LTC4088 and LTC4098 offers

a big advantage over devices that use

an output current controlled topology

to maintain USB compliance. This is

because as the battery voltage rises

throughout the charge cycle, the effective power consumed by the battery

also rises, assuming a constant current. In order to retain USB compliance

in an output current controlled system (assuming perfect efficiency) one

would have to limit the battery charge

current to its power-limited value at

the highest battery voltage.

For example, to remain below 2.5W

(5VIN • 500mA) of power delivery at a

4.2V battery voltage, the charge current must not exceed 595mA. This

current limit is overly conservative

when the battery voltage is low, say

3.4V, where it would be possible to

deliver 735mA without violating the

USB specification. Input current limited devices designed specifically for

USB compliance, such as the LTC4088

Linear Technology Magazine • June 2008

DESIGN FEATURES L

BAT (V)

2.4

4.5

4.2

3.9

3.6

3.3

3.0

2.7

2.4

3.3 3.9

2.7 3.0

3.6 4.2

V

OUT

(V)

NO LOAD

300mV

and LTC4098, allow the charger to use

this additional available current. In

contrast, an output current regulated

switching charger designed for USB

compliance must be programmed to

limit battery charging current to the

high voltage case (595mA), thus hamstringing it at low battery voltages. Said

another way, an input current limited

switching charger always extracts as

much power from the input source as

is allowed, whereas an output current

controlled one does not.

Instant-On

(Low Battery System Start)

Figure 5 shows the instant-on feature

of the switching PowerPath topology.

When the battery voltage is very low

and the system load does not exceed

the available programmed power,

the output voltage is maintained at

approximately 3.6V. This prevents

the system from having to wait for

the battery voltage to come up before

turning on the device—a frustrating

scenario to the end user.

This is the primary reason for having

a decoupled output node and battery

node (i.e. the 3-terminal topology).

This feature can be used to power

the system in a low power mode. For

example, it may be just enough power

to start up and indicate to the user

that the system is charging.

Automatic Load Prioritization

The current delivered to the system

at V

current, form a combined load on the

switching regulator. If this combined

load does not exceed the power level

programmed by the input current limit

circuit then the switching PowerPath

topology happily delivers charge and

load current without concern. If,

however, the total load exceeds the

available power, the battery charger

automatically gives up some or all of

its share of the power to support the

extra load. That is, the system load is

always prioritized and battery charging

is only performed opportunistically.

This algorithm provides uninterrupted

power to the system load. Even if the

system load alone exceeds the power

available from the input limiting cir-

Linear Technology Magazine • June 2008

, as well as the battery charge

OUT

Figure 5. V

OUT

vs BAT

cuit, the input current does not exceed

its programmed limit. Rather the

battery charger shuts off completely

and the extra power is drawn from the

battery via the ideal diode.

When the ideal diode is engaged, the

conduction path from the battery to the

output pin is approximately 180mΩ.

If this is sufficient for the application, then no external components

are needed. If greater conductance

is necessary, however, an external

MOSFET can be used to supplement

the internal ideal diode. The LTC4088

and LTC4098 both have a control pin

for driving the gate of the optional

external transistor. Transistors with

resistance of 30mΩ or lower can be

used to supplement the internal ideal

diode.

Full Featured Battery Charger

The LTC4088 and LTC4098 both

include a full featured battery charger. The battery chargers feature

programmable charge current, cell

preconditioning with bad-cell detection and termination, CC-CV charging,

C/10 end of charge detection, safety

timer termination, automatic recharge

and a thermistor signal conditioner for

temperature qualified charging.

LTC4098 Enhancements

The LTC4098 has a few features that

the LTC4088 does not. First, it supports the ability to control an external

high voltage switching regulator to

receive power from a second input supply such an automobile battery. It also

includes an independent overvoltage

protection module that can, in con-

junction with an external MOSFET,

provide significant input protection to

the low voltage (USB/WALL) input.

High Voltage Input Controller

The LTC4098’s external input control

circuit recognizes when a second input

supply is present and prioritizes that

input in the event that both it and

the USB/WALL input are powered

simultaneously. Furthermore, the

LTC4098 interfaces with a number

of Linear Technology high voltage

step-down switching regulators to

allow for higher voltage inputs, such

as an automotive battery. Using the

same Bat-Track technique described

above, the auxiliary input controller

commands the high voltage regulator to develop a voltage at V

OUT

that

tracks just above the battery. Again,

this technique results in high charging

efficiency even when charging from a

fairly high voltage.

Overvoltage Protection

The LTC4098 includes an overvoltage

protection controller that can be used

to protect the low voltage USB/Wall

input from the inadvertent application of high voltage or from a failed

wall adapter. This circuit controls

the gate of an external high voltage

N-type MOSFET. By using an external

transistor for high voltage standoff, the

protection level is not limited to the

process parameters of the LTC4098.

Rather the specifications of the external transistor determine the level of

protection provided.

Conclusion

The LTC4088 and LTC4098 represent

a new paradigm in power management

and battery charging. Both optimize

power delivery by combining constant

input power limiting with a high

efficiency switching regulator and

Bat-Track battery charging. Other

benefits include instant-on system

starting, automatic load prioritization

and unmatched charging efficiency.

The LTC4098 goes a step beyond

with an auxiliary input controller for

higher input voltages (such as a car

battery) and an overvoltage protection

controller.

L

5

L DESIGN FEATURES

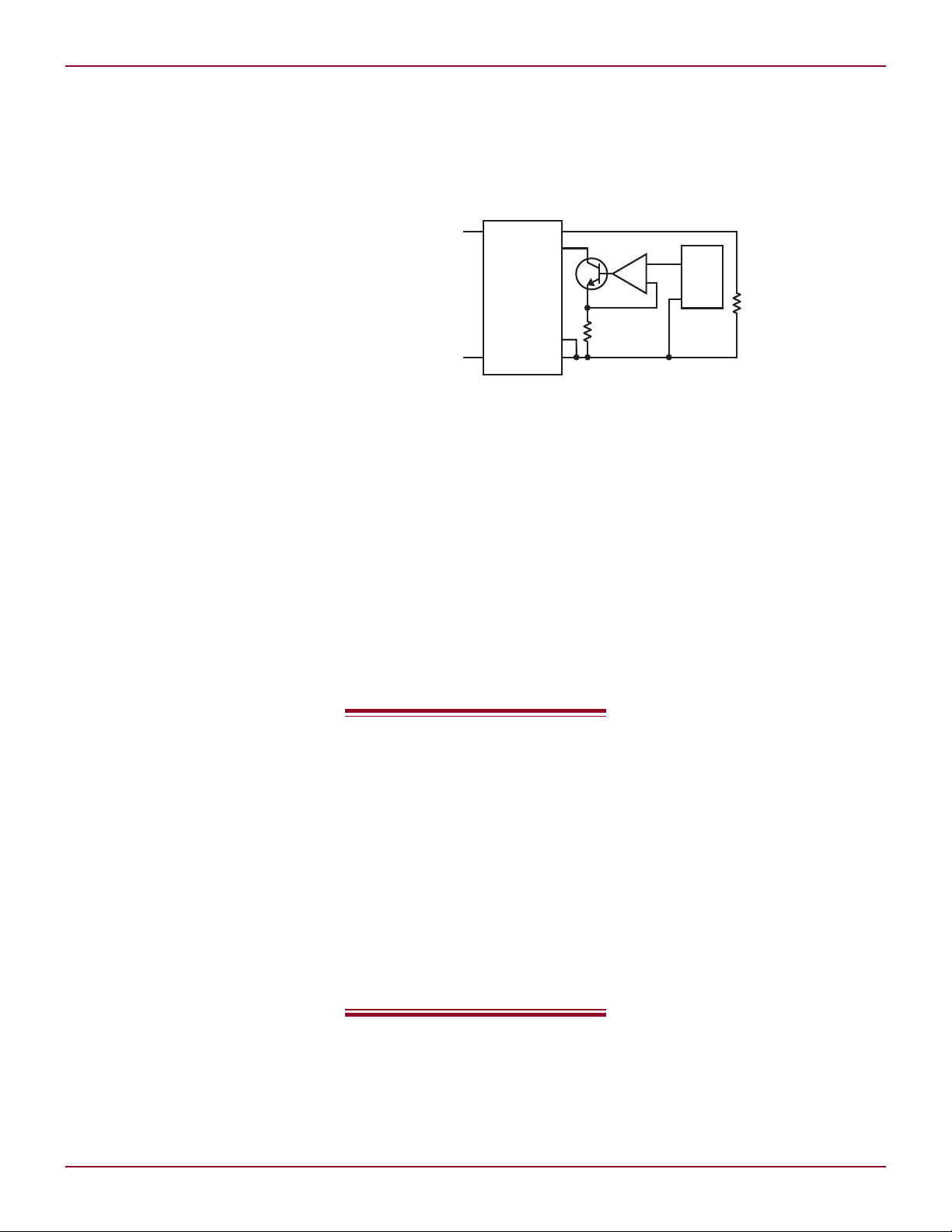

POWER SUPPLY

–V

IN

–V

OUT

+V

OUT

+SENSE

CH2

CH1

Q1

BC847BPN

R1 = R

PS(SENSE)

LT1784

LOAD

GND

OUTPUT

–SENSE

+V

IN

+

–

SINUSOIDAL

GENERATOR

Hot Swap Controller Enables Standard Power Supplies to Share Load

Introduction

The LTC4350 Hot Swap™ and load

share controller is a powerful tool for

developing high availability redundant and load sharing power supply

systems. It has the unique ability to

work with supplies with any output

stage topology, including output stages

using synchronous rectification.

Although the LTC4350 does much of

the heavy lifting in maintaining a well

balanced load share system, there are

a number of important considerations

in designing a stable system.

This article deals with some of the

more complex design details of the

LTC4350. If you are designing a load

share system and LTC4350 is new

to you, it may be helpful to first read

introductory details in the LTC4350

data sheet, and the article “Combo/Hot

Swap Load Share Controller Allows

the use of Standard Power Modules

in Redundant Power Systems” in the

June, 2003 issue of Linear Technology

magazine.

A Little Background

DC/DC converters are paralleled for

any of several reasons:

q

One converter may be

insufficient for the required

power level. For example, an

existing single regulator design

may be able to handle 100W,

but a new application calls

for up to 200W. Paralleling

two, production-proven 100W

converters saves time over

developing a new converter

capable of twice the power.

q

The product may need to be

scalable. Many rack-based

systems feature multiple slots,

which may be populated at some

future date, but why install power

supply sufficient to operate the

entire rack when only a fraction

of the slots are in use? Paralleling

supplies allows addition of power

on an as-needed basis.

6

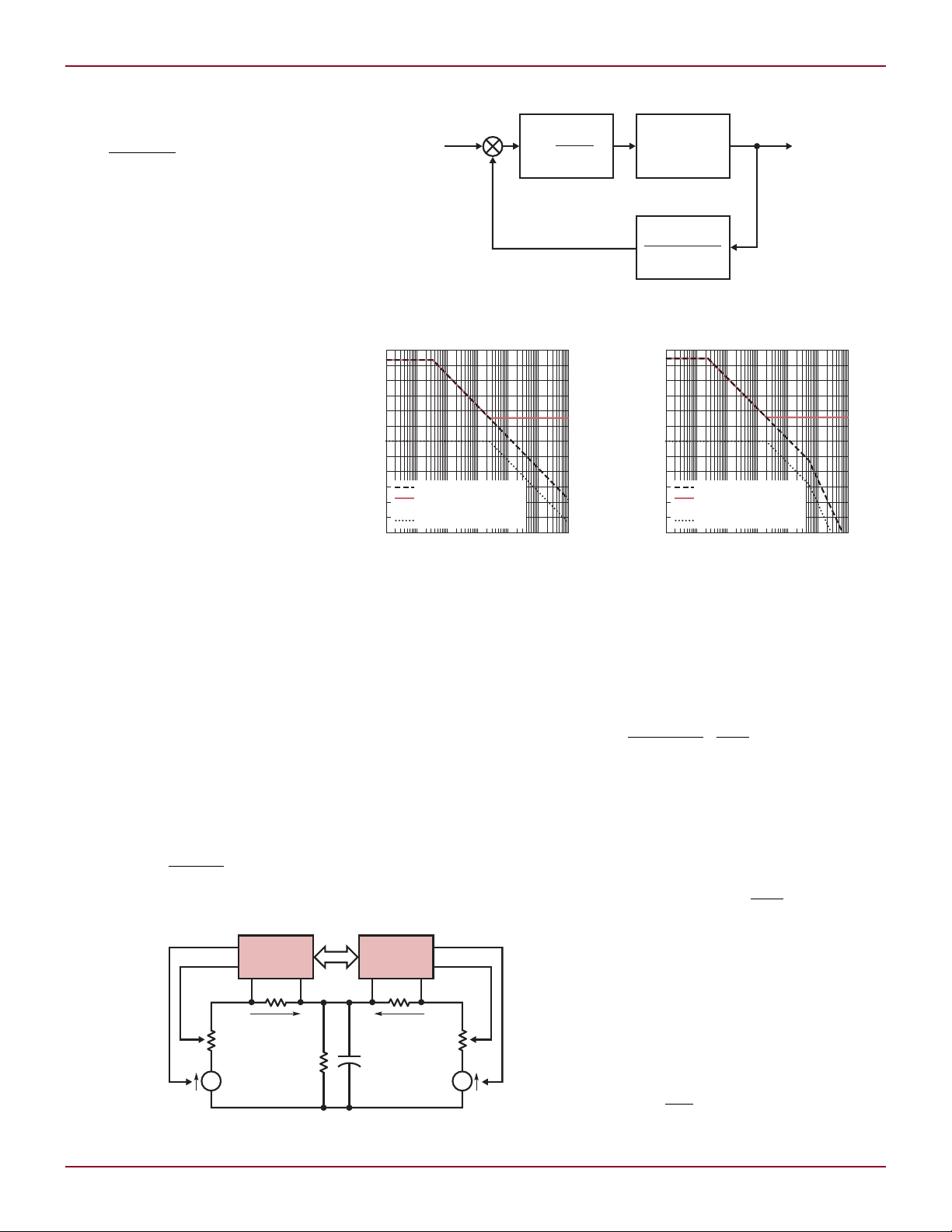

Figure 1. Power supply closed-loop Bode plot measurement block diagram

q

Redundancy. These systems,

often called N + 1 redundant, use

a number of small supplies where

N units are needed to power the

load, but a “+1” supply is added

for redundancy. The theory is, if

one supply fails, N units remain

to carry the load.

q

Efficiency. If the power system

must support widely ranging

loads, efficiency can be optimized

by adjusting the number of

operating supplies to the load.

The LTC4350 Hot Swap and

load share controller is a

powerful tool for developing

high availability redundant

and load sharing power

supply systems.

It has the unique ability

to work with supplies

with any output stage

topology, including output

stages using synchronous

rectification.

The key to parallel operation is

balancing the output current of each

supply, so that all are equally loaded if

the supplies are identical. If individual

supplies with different power ratings

are combined for parallel operation,

by Vladimir Ostrerov

the output current of each supply

must be proportional to the rated

supply power.

The LTC4350 performs this function. It forces multiple, paralleled

power supplies to share current. The

concept behind a LTC4350-based

load share controller is simple: a

single, overall voltage loop controls

the common output while each power

converter is controlled by a local current loop and contributes current in

the common output. Even so, such a

multi-loop feedback system requires

careful design.

Active control is achieved by sinking

additional current from the +SENSE

pin found on many common converter

modules, and fooling the converter

into believing the output voltage is

something different than what it

would otherwise detect. Increasing

this current causes the output to rise;

decreasing it causes the output to fall.

Thus the LTC4350 has a means of

modulating the output voltage, thereby

controlling the companion converter’s

contribution to the system.

AC Analysis

The design of a current sharing power

system involves not only the simple

matter of DC operating conditions, but

also AC analysis. This article covers

the AC design aspects of an LTC4350based load share system.

The design goal is to build a stable

system with maximum bandwidth,

Linear Technology Magazine • June 2008

G

T s

EA

POLE

+ 1

T

R C

POLE

O C

=

1

2π

PHASE (°)

1M1

180

120

60

0

–60

–120

–180

10

100 1k

10k 100k

MAGNITUDE (dB)

FREQUENCY (Hz)

50

60

–50

–60

–40

–30

–20

–10

40

30

20

10

0

SYNTHESIZED OPEN CURRENT LOOP

COMPENSATION NETWORK

POWER SUPPLY

PHASE (°)

1M1

180

120

60

0

–60

–120

–180

10

100 1k

10k 100k

MAGNITUDE (dB)

FREQUENCY (Hz)

50

60

–50

–60

–40

–30

–20

–10

40

30

20

10

0

SYNTHESIZED OPEN CURRENT LOOP

COMPENSATION NETWORK

POWER SUPPLY

ERROR

AMPLIFIER 1

ERROR

AMPLIFIER 2-1

POWER SUPPLY 1

R

N

R

N

REFERENCE

INPUT

SIGNAL

CURRENT 1 SIGNAL

CURRENT 2 SIGNAL

CURRENT N SIGNAL

+

ERROR

AMPLIFIER 2-2

POWER SUPPLY 2

LOAD

VOLTAGE SIGNAL

OUTPUT

VOLTAGE

DIVIDER FOR

FEEDBACK

SIGNAL

–

+

–

+

–

+

–

ERROR

AMPLIFIER 2-N

POWER SUPPLY N

Figure 2. Power system control loop

Figure 3. Current loop Bode design with power

supply having first order transfer function

with good transient response, and

to preserve as much of the inherent

performance of the individual power

supply as possible.

As each supply in a power system

is a fixed configuration component,

knowledge of its main characteristics

is indispensable for control system

design. Among the power supply

characteristics essential for design

purposes are power supply bandwidth, output stage topology and

power supply output voltage ramp

up behavior.

Figures for power supply bandwidth

can be obtained directly from the power

supply manufacturer or measured in

the lab. One way to experimentally

measure bandwidth is to use a simple

driver, a sine wave generator and an

oscilloscope. Figure 1 shows the block

Linear Technology Magazine • June 2008

DESIGN FEATURES L

Figure 4. Current loop synthesis

with 0,–1,–2 shape

diagram for this measurement. Scope

probes are connected to the generator

output and power supply output. A

power supply Bode plot can be obtained significantly faster using special

equipment for frequency response

measurement, such as a VENABLE

Frequency Response Analyzer or AP’s

Analog Network Analyzer. Power supply bandwidth should be measured

with 90%–100% load.

The power supply output stage topology should be taken into account

when designing the load share power

system. If it is a synchronously rectified

power supply output stage, it is able

to provide bidirectional energy flow

and as a result the power supply can

operate in the second quadrant and

sink current. In this case one of two

special measures should be taken:

either synchronize the activation of

the LTC4350 controller current share

ability with the MOSFET switch turnon process, or disable synchronous

rectification before the LTC4350 load

share capability is activated. Detailed

descriptions of those actions are presented below.

The power supply output voltage ramp-up behavior during turn

on should be checked to eliminate

LTC4350 operation in the area where

output voltage slew rate experiences

significant changes. An undervoltage

protection circuit, which is connected

with pin 1, performs this function.

Unified Approach to

Compensation Components

Parameters Evaluation

A power system with K power supplies operating in parallel is a K + 1

loop control system. This system has

one voltage loop, which is the highest

bandwidth loop, and K current loops.

These K current loops work with a

common input command signal and

individual feedback current signals.

All current loops operate in parallel.

A block diagram of the control loops

is shown in Figure 2.

There are two restrictions on loop

bandwidth. All current loops must

have equal bandwidths. The voltage loop bandwidth must be wider

than any current loop bandwidth to

eliminate current oscillation between

power supplies.

LTC4350 error amplifiers EA1 and

EA2 are transconductance operational

amplifiers. This restricts compensation circuit transfer functions to two

types: pole or a pole and zero with

T

> T

POLE

of one capacitor CC implements a

transfer function

where GEA is the error amplifier voltage

gain, gmRO, and,

RO is the internal error amplifier’s

output impedance.

. A compensation circuit

ZERO

[1]

.

7

L DESIGN FEATURES

G T s

T s

EA ZERO

POLE

( )++1

1

T

R C

ZERO

C C

=

1

2π

SLOPE

db

dec

K= −( • )20

ΔI

I

V

LIMIT

OUT

=

ΔV

I R

V

SENSE

LIMIT SENSE

OUT

=

G G G G

CO EA

DB

CSA

= • •

2

G

I R

V

R

CSA

LIMIT SENSE

OUT

GAIN

= • •

−103

ERROR AMPLIFIER 2 DRIVING BLOCK

CURRENT SENSE

AMPLIFIER FILTER

CURRENT SENSE AMPLIFIER

POWER SUPPLY

INITIAL OUTPUT

VOLTAGE OFFSET

MEASURED

TRANSFER FUNCTION

OR

MAGNITUDE

BODE PLOT

MAGNITUDE

BODE PLOT

(FIGURE 5)

V

OUT

R

LOAD

=

V

OUT/ILIMIT

V

SH(BUS)

+

+

+

–

G

EA2

T2Zs + 1

T2Ps + 1

G

CSA

=

V

OUT

– 0.2V

I

LIMIT

• R

SENSE

• R

GAIN

10

–3

V

OUT

–V

OUT

R

SET

R

GAIN

R

LOAD

R

SENSE

C

C

R

C

R

PS(SENSE)

VOLTAGE TO

CURRENT

CONVERTER

ERROR AMPLIFIER 2

WITH COMPENSATION

CIRCUIT

DRIVING BLOCK

SHARE BUS

POWER SUPPLY

+

–

+

–

+V

OUT

+SENSE

g

m

If a compensation circuit has

capacitor CC and resistor RC series

connected, it implements a transfer

function

[2]

where

The equations shown are based on

the assumption that RO >> RC.

Current Control Loop

Synthesis and Compensation

Component Calculation

The Bode amplitude characteristic

slope is defined by the integer K (0,

1, 2, etc.) to express the slope

As an outer loop, the voltage loop

must have larger bandwidth than the

inner current loop. The closed current

loop Bode plot should be shaped as

0,–1 or 0,–1,–2 with the –1 segment

at least 1.4 decades long.

1. If the power supply Bode ampli-

tude characteristic has shape

0,–1 or 0,–1,–2, and the –1

segment is 1.4 decades long,

the current loop error amplifier

compensation network allows for

a current loop bandwidth equal

to the power supply bandwidth.

This can be achieved by tailoring

the current loop compensation

network so that its zero frequency

is equal to the main power supply

pole frequency. Figure 3 demon-

strates this approach.

2. If the power supply Bode ampli-

tude characteristic has shape

0,–1,–2, and the –1 segment is

shorter than 1.4 decades—or

at the extreme, the shape is

0,–2—shifting the current loop

crossover frequency to the left

(this reduces the current loop

bandwidth to below the power

supply bandwidth) makes it pos-

sible to achieve a 0,–1,–2 closed

current loop shape with the –1

segment covering least 1.4 de-

cades. In the extreme case when

8

Figure 5. Current loop functional block diagram

the power supply closed loop

frequency response characteristic

is 0,–2, placing a compensation network zero exactly at the

coordinate where the amplitude

is –28db and the frequency is the

power supply bandwidth, and

placing the pole value so that the

crossover frequency is 25× lower

than the power supply bandwidth achieves the desired result.

Figure 4 illustrates synthesis of a

current loop with shape 0,–1,–2.

A current loop block diagram and

current loop control diagram are

shown in Figures 5 and 6.

Current open-loop gain is proportional to load and it must be calculated

at the power supply’s maximum available current. At maximum load current

(I

), an additional 1V output on the

LIMIT

Figure 6. Current loop control block diagram

power supply produces additional

current in the load as given by

and produces a corresponding signal

on the sense resistor as follows

.

Current open-loop gain equals

,

where G

is the error amplifier EA2

EA2

gain, GDB is the driving block gain,

and G

is the current sense amplifier

CSA

gain, which is given by

It should be noted that R

SENSE

is

a resistor connecting the power sup-

Linear Technology Magazine • June 2008

T s

T s V

f ZERO

f POLE OUT

( )

( )

.

+

+

•

1

1

1 22

T R C

f ZERO f f( )=1

T T

V

f POLE f ZERO

OUT

( ) ( )

.

= •

1 22

20

12

1 22

19 85log

.

.= db

ply output to the load. Driving block

G

R

R

DB

PS SENSE

SET

=

( )

f

f

G

POLE

ZERO

V OPEN

1

1

3 6

( )

( )

( )

( )= −

LTC4350 LTC4350

R

SENSE1

R1

DRAIN-SOURCE

I1 I2

EMF1 EMF2

R

LOAD

C

LOAD

R2

DRAIN-SOURCE

SHARE

BUS

R

SENSE2

+

–

+

–

PHASE (°)

1M1

180

120

60

0

–60

–120

–180

10

100 1k

10k 100k

MAGNITUDE (dB)

FREQUENCY (Hz)

50

60

–50

–60

–40

–30

–20

–10

40

30

20

10

0

CLOSED CURRENT LOOP

VOLTAGE LOOP

COMPENSATION NETWORK

OPEN VOLTAGE LOOP

PHASE (°)

1M1

180

120

60

0

–60

–120

–180

10

100 1k

10k 100k

MAGNITUDE (dB)

FREQUENCY (Hz)

50

60

–50

–60

–40

–30

–20

–10

40

30

20

10

0

CLOSED CURRENT LOOP

VOLTAGE LOOP

COMPENSATION NETWORK

OPEN VOLTAGE LOOP

ERROR

AMPLIFIER 1

CURRENT

CLOSE-LOOP

TRANSFER FUNCTION

OR MAGNITUDE

BODE PLOT

REFERNCE

INPUT

SIGNAL

OUTPUT VOLTAGE

DIVIDER GAIN

+

–

G

EA1

T1Zs + 1

T1Ps + 1

1.22(TFZs + 1)

V

OUT(KDIVTFZ

s + 1)

V

OUT

gain is

DESIGN FEATURES L

where R

resistor value and R

connected to the LTC4350 SET pin.

converter in the current sensing block

has a flat response from low frequencies up to 10kHz, where a low frequency

pass filter is implemented.

gain is 500–1000.

Voltage Control Loop

Synthesis and Compensation

Component Calculation

The voltage loop forward path contains

an error amplifier (Error Amplifier 1)

and the current loop, and the feedback

path contains an output voltage divider. A control diagram for the voltage

loop is shown in Figure 7.

gain is 1800–2200.

demonstrated in Figures 8 and 9. The

first plot explains the design when

the current closed-loop magnitude

response has shape 0,–1. To have

a voltage loop crossover frequency

6 to 7 times wider than the current

closed-loop bandwidth, the compensation should have a zero at the same

frequency as the bandwidth, but

the magnitude of the gain must be

15dB – 17dB [20log(6) = 15.5; 20log(7)

= 16.9]. The pole frequency equals

Linear Technology Magazine • June 2008

PS(SENSE)

is a power supply

is a resistor

SET

The LTC4350’s voltage-to-current

Measured Error Amplifier 2 voltage

Measured Error Amplifier 1 voltage

Bode design for the voltage loop is

Figure 10. Output power stage equivalent circuitry. The power

supply output characteristic exists in the second quadrant

Figure 7. Voltage loop control block diagram

Figure 8. Voltage loop Bode design with

current closed loop having 0,–1 shape

where G

is the voltage open-

V(OPEN)

loop gain.

The same relationship between voltage loop crossover frequency and the

current closed-loop bandwidth should

hold in the second case, when the current closed-loop magnitude response is

shaped as 0,–1,–2. The compensation

provided should be the same as the

first case, as shown in Figure 9.

An additional option exists for improvement of the voltage open-loop

magnitude response by placing in

the feedback path lead compensation

Figure 9. Voltage loop Bode design with

closed current loop having 0,–1,–2 shape

with lead ratio 1.22/V

. Shunting

OUT

the top resistor in the output voltage

divider with a capacitor implements

the transfer function

where

and

Rf1 is the top resistor in the voltage

divider and Cf is the shunting capacitor. This compensation allows bending

of the magnitude response and gives

a slope of –20db/dec around the

crossover frequency in the restricted

frequency area. It is the maximum

area for a 12V system; it takes

continued on page 16

9

L DESIGN FEATURES

a

Z IP

2

0

2

2

=

DIPLEXER

ADC

ADC

0°

I/Q DEMOD

AGC

BAND

FILTER

LOWPASS

FILTERS

BASEBAND

AMPLIFIERS

LNARF AT

1920 MHz–1980 MHz

FROM Tx

2110 MHz–2170 MHz

LO AT

1920 MHz–1980 MHz

90°

LO

RF TONE POWER = P

S

RF PASSBAND

SINGLE TONE EXAMPLE MODULATED SIGNAL EXAMPLE

DOWNCONVERSION

LO

RF PASSBAND

DC DUE TO 2ND ORDER

DISTORTION = a2PSZ

0

0 Hz 0 Hz

BASEBAND PSEUDO-RANDOM POWER

DUE TO 2ND ORDER DISTORTION

= 3a

2

2

Z0P

S

2

RF SIGNAL POWER = P

S

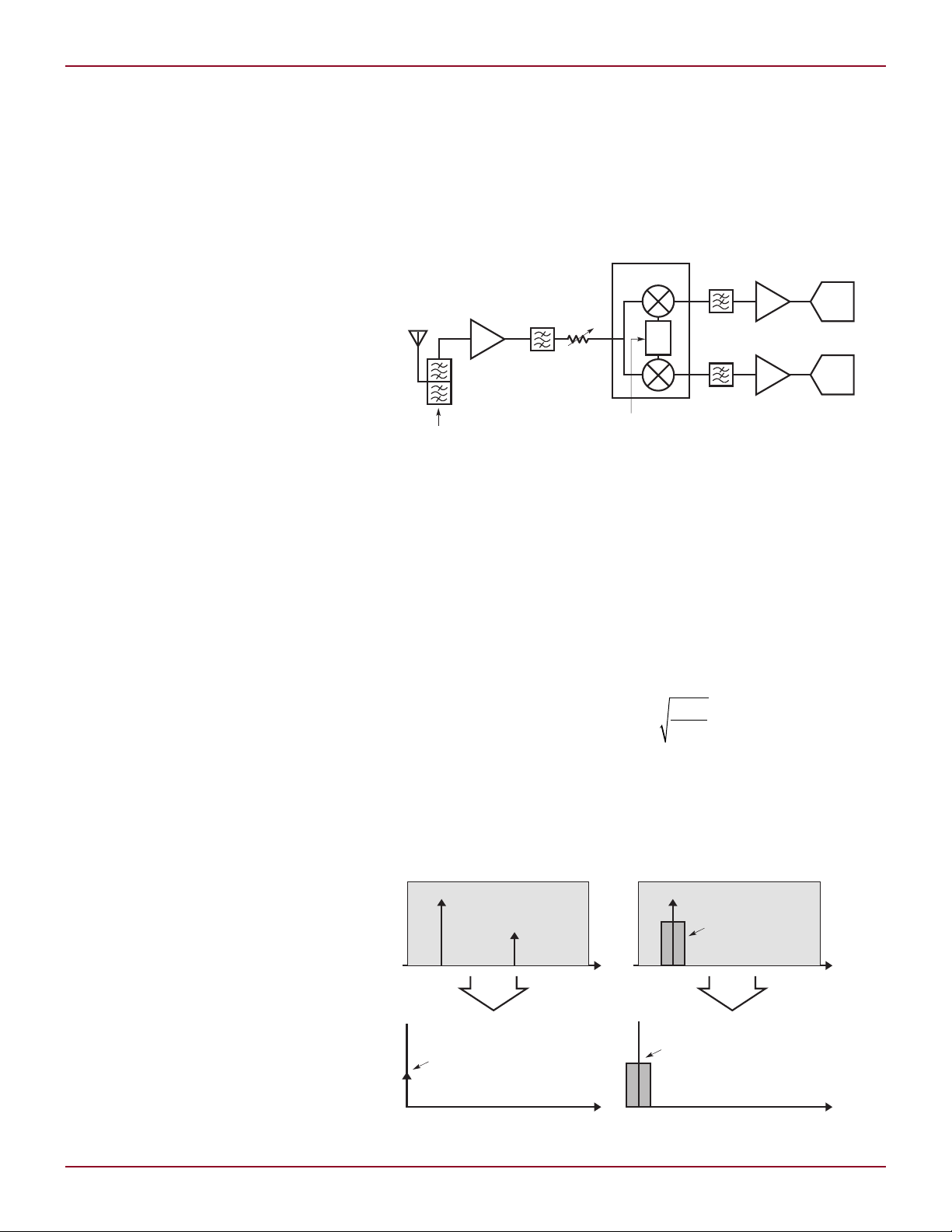

Understanding IP2 and IP3 Issues in Direct Conversion Receivers for WCDMA Wide Area Basestations

Introduction

A direct conversion receiver architecture offers several advantages over the

traditional superheterodyne. It eases

the requirements for RF front end

bandpass filtering, as it is not susceptible to signals at the image frequency.

The RF bandpass filters need only

attenuate strong out-of-band signals

to prevent them from overloading

the front end. Also, direct conversion

eliminates the need for IF amplifiers

and bandpass filters. Instead, the RF

input signal is directly converted to

baseband, where amplification and

filtering are much less difficult. The

overall complexity and parts count of

the receiver are reduced as well.

Direct conversion does, however,

come with its own set of implementation issues. Since the receive LO

signal is at the same frequency as

the RF signal, it can easily radiate

from the receive antenna and violate

regulatory standards. Also, a thorough

understanding of the impact of the

IP2 and IP3 issues is required. These

parameters are critical to the overall

performance of the receiver and the key

component is the I/Q demodulator.

Unwanted baseband signals can be

generated by 2nd order nonlinearity of

the receiver. A tone at any frequency

entering the receiver gives rise to a DC

offset in the baseband circuits. Once

generated, straightforward elimination

of DC offset becomes very problematic.

That is because the frequency response

of the post-downconversion circuits

must often extend to DC. The 2nd order

nonlinearity of the receiver also allows

a modulated signal—even the desired

signal—to generate a pseudo-random

block of energy centered about DC.

direct conversion receivers are susceptible to such 2nd order mechanisms

regardless of the frequency of the

incoming signal. So minimizing the

10

Unlike superheterodyne receivers,

effect of finite 2nd order linearity is

critical.

effect of 3rd order distortion on a direct

conversion receiver. In this case, two

signals separated by an appropriate

frequency must enter the receiver in

order for unwanted products to appear

at the baseband frequencies.

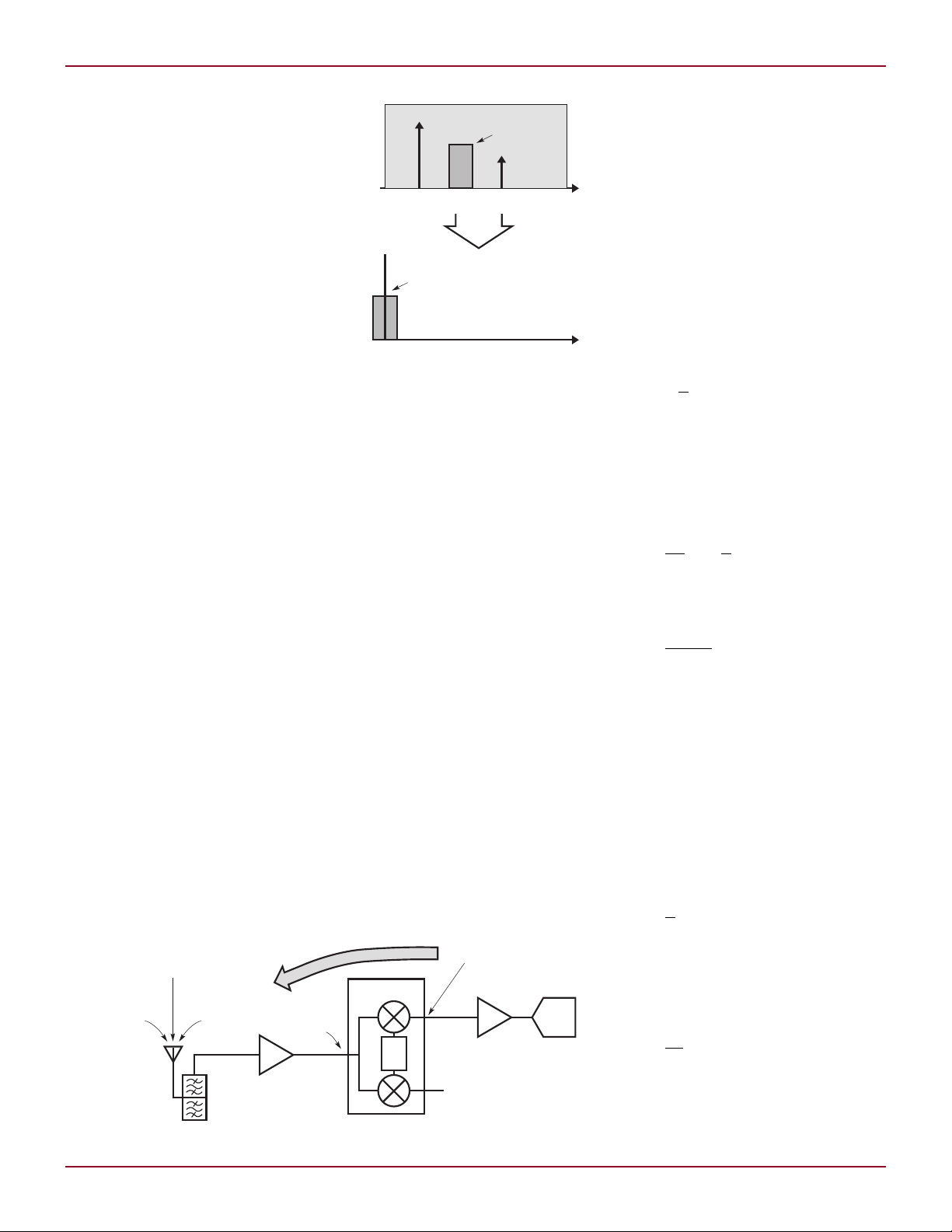

Second Order Distortion (IP2)

The second order intercept point (IP2)

of a direct conversion receiver system

is a critical performance parameter. It

is a measure of second order non-linearity and helps quantify the receiver’s

susceptibility to single- and 2-tone

interfering signals. Let’s examine how

this nonlinearity affects sensitivity.

Figure 1. Direct conversion receiver architecture

Later in this article we consider the

Figure 2. Effects of 2nd order distortion

by Doug Stuetzle

We can model the transfer function

of any nonlinear element as a Taylor

series:

y(t) = x(t) + a2x2 (t) + a3x3(t) + …

where x(t) is the input signal consisting of both desired and undesired

signals. Consider only the second order

distortion term for this analysis. The

coefficient a2 is equal to

where IP2 is the single tone intercept

point in watts. Note that the 2-tone

IP2 is 6dB below the single-tone IP2.

The more linear the element, the

smaller a2 is.

Linear Technology Magazine • June 2008

DESIGN FEATURES L

P

Z

E A t t

S

=

{ }

1

0

2

• ( )cosω

P

Z

E A t E

t

S

= •

{ }

•

+

1 1 2

2

0

2

( )

cos ω

P

Z

E A t

S

=

{ }

1

2

0

2

• ( )

P

A

Z

S

=

2

0

2

E A t Z P

S20

2( )

{ }

=

y t A t t

a A t t

Higher Orde

( ) ( ) cos

( )cos

=

+

+…

ω

ω

2

2

rr Terms

A t t

a A t

a A t t

=

+

+

( )cos

( )

( )cosωω

1

2

1

2

2

2

2

2

2

……

DC OFFSET a A a P Z

S

= =

1

2

2

2

2 0

•

P

Z

E a A t

BB

=

1 1

2

0

2

2

2

• ( )

P

a

Z

E A t

BB

=

( )

{ }

2

2

0

4

4

• ( )

E A t E A t

4 2

2

3( ) • ( )

{ }

=

{ }

P

a

Z

E A t

BB

=

( )

{ }

3

4

2

2

0

2

2

• ( )

P a Z P

BB S

=

( ) ( )

3

220

2

y t A t t

a A t t B t t

u

( ) ( ) cos

( )cos ( )cos

=

+ +

+

ω

ω ω

2

2

……

=

+ +

Higher Order Terms

A t t

a A t a

( )cos

( )

ω

1

2

1

2

2

2

2

AA t t

a A t B t t t

A t

u

2

2

2

2

( )cos

( ) ( ) cos cos

( )co

ω

ω ω+ …

= ss

( ) ( ) cos( )

ω

ω ω

t

a A t B t t

u

+…

+ − …

2

ADC

0°

I/Q DEMOD

GAIN = 30dB

GAIN = 20dB

EQUIVALENT

PSEUDO-RANDOM

DISTORTION

AT –118.7dBm

TOTAL Rx

THERMAL NOISE

= –101.2dBm

WCDMA

INTERFERER

AT –40dBm

WCDMA

INTERFERER

AT –20dBm

DISTORTION

AT –98.2dBm

90°

Every signal entering the nonlinear

element generates a signal centered

at zero frequency. Even the desired

signal gives rise to distortion products

at baseband. To illustrate this, let the

input signal be represented by x(t) =

A(t)cosωt, which may be a tone or a

modulated signal. If it is a tone, then

A(t) is simply a constant. If it is a

modulated signal, then A(t) represents

the signal envelope.

By definition, the power of the desired signal is

where E{β} is the expected value of

β. Since A(t) and cosωt are statistically independent, we can expand

E{(A(t)cosωt)2} as E{A2(t)} • E{cos2ωt}.

By trigonometry

The expected value of the second

term is simply ½, so the power of the

desired signal simplifies to:

[1]

In the case of a tone, A(t) may be

replaced by A. The signal power is, as

expected, equal to

In the more general case, the desired signal is digitally modulated by

a pseudo-random data source. We

can represent it as bandlimited white

noise with a Gaussian probability

distribution. The signal envelope A(t)

is now a Gaussian random variable.

The expected value of the square of the

envelope can be expressed in terms of

the power of the desired signal as:

[2]

Now substitute x(t) into the Taylor

terms of the desired signal power, we

must relate E{A4(t)} to E{A2(t)}. For a

Gaussian random variable, the follow-

ing relation is true:

series expansion to find y(t), which is

the output of the nonlinear element:

expressed as

terms of the desired signal power:

Consider the 2nd order distortion

term ½a2[A(t)]2. This term appears

centered about DC, whereas the other

2nd order term appears near the 2nd

harmonic of the desired signal. Only

the term near DC is important here,

as the high frequency tone is rejected

by the baseband circuitry.

In the case where the signal is a

to DC, and any modulated signal into

a baseband signal that makes 2nd

order performance critical to direct

conversion receiver performance. Unlike other nonlinear mechanisms, the

signal frequency does not determine

where the distortion product falls.

tone, the 2nd order result is a DC

offset equal to:

nonlinear element give rise to a beat

note/term. Let

[3]

If the desired signal is modulated,

then the 2nd order result is a modulated baseband signal. The power of

x(t) = A(t)cosωt + B(t)cosωut,

where the first term is the desired

signal and the second term is an unwanted signal.

this term is

This can be expanded to:

[4]

In order to express this result in

[5]

The distortion power can then be

Now express the expected value in

[6]

It is the conversion of any given tone

Any two signals entering the

Linear Technology Magazine • June 2008

Figure 3. 2nd Order distortion due to WCDMA carrier

The second order distortion term of

interest is a2A(t)B(t)cos(ω– ωu)t. This

term describes the distortion product

centered about the difference frequency between the two input signals. In the

case of two unwanted tones entering

the element, the result includes a tone

at the difference frequency. If the two

11

!$#

)1$%-/$

'!).D"

'!).D"

%15)6!,%.4

03%5$/2!.$/-

$)34/24)/.

!4nD"M

4/4!,2X

4(%2-!,./)3%

nD"M

4X3)'.!,

!4nD"M

4X3)'.!,

!4nD"M

$)34/24)/.

!4nD"M

4X3)'.!,

!4nD"M

4X3)'.!,

!4D"M

L DESIGN FEATURES

unwanted signals are modulated, then

the resultant includes a modulated

signal centered about their difference

frequency.

We can apply these principles to a

direct conversion receiver example.

Figure 1 shows the block diagram of

a typical WCDMA basestation receiver.

Here are some key characteristics of

this example:

q

Basestation Type: FDD, Band I

q

Basestation Class: Wide Area

q

Number of carriers: 1

q

Receive band: 1920MHz to

1980MHz

q

Transmit band: 2110MHz to

2170MHz

The RF section of this receiver includes a diplexer, a bandpass filter, and

at least one Low Noise Amplifier (LNA).

The frequency selective elements are

used to attenuate out-of-band signals

and noise. The LNA(s) establishes

the noise figure of the receiver. The

I/Q demodulator converts the receive

signal to baseband.

In the examples illustrated below,

the characteristics of the LT5575

I/Q demodulator as representative

of a basestation class device of this

type. Lowpass filters and baseband

amplifiers bandlimit and increase the

signal level before it is passed to the

A/D converters. The diplexer and RF

bandpass filter serve as band filters

only; they do not offer any carrier

selectivity.

The second order linearity of the

LNA is much less important than that

of the demodulator. This is because

any LNA distortion due to a single

signal is be centered about DC and

rejected by the demodulator. If there

are two unwanted signals in the receive

band (1960MHz, for example), then a

second order product is generated by

the LNA at the difference frequency.

This signal is demodulated and appears as a baseband artifact at the

A/D converter. We need not address

this condition, however, because out of

band signals emerging from the front

end diplexer are not strong enough

to create distortion products of any

importance.

Consider first a single unmodulated

tone entering the receiver (see Figure

12

Figure 4. Transmitter leakage effects

2). As detailed above, this tone gives

rise to a DC offset at the output of the

demodulator. If the baseband cascade

following the demodulator is DC-coupled, this offset is applied to the A/D

predicts a distortion at the LT5575

output of –98.7dBm. This result agrees

well with that given by equation 6,

which predicts a distortion power of

–98.2dBm.

converter, reducing its dynamic range.

The WCDMA specification (3GPP TS

25104.740) calls out an out-of-band

tone at –15dBm, located 20MHz or

more from either receive band edge

(section 7.5.1). Compute the DC offset

generated in the I/Q demodulator:

q

Tone entering receive antenna

port: –15dBm

q

Diplexer rejection at 20MHz

offset: 0dB

q

Bandpass rejection at 20MHz

at the LT5575 output is a noiselike

signal, created from the interfering

WCDMA carrier. If this signal is large

enough, it can add to the thermal

receiver and A/D converter noise

to degrade sensitivity. Compute the

equivalent thermal noise at the receiv-

er input with no added distortion:

q

q

q

offset: 2dB

q

RF gain preceding LT5575: 20dB

q

Tone entering LT5575: 3dBm

q

LT5575 IIP2, 2-tone: 60dBm

q

LT5575 a2: 0.00317

q

DC offset at LT5575 output:

0.32mV

q

Baseband voltage gain: 31.6

q

DC offset at A/D input: 10mV

Single WCDMA carriers can also

serve as interferers, as detailed in

section 7.5.1. In one case, this carrier

is offset by at least 10MHz from the

desired carrier, but is still in the receive

band. The power level is –40dBm, and

the receiver must meet a sensitivity of

–115dBm for a 12.2kbps signal at a

BER of 0.1%. Here are the details:

q

Signal entering receive antenna

port: –40dBm

q

RF gain preceding LT5575: 20dB

q

Signal entering LT5575: –20dBm

q

LT5575 IIP2, 2-tone: 60dBm

q

LT5575 a2: 0.00317

A MATLAB simulation performed

using a pseudo-random channel

q

Now refer the distortion signal back

to the receiver input:

q

q

in this case is 17.5dB below the thermal noise at the receiver input. The

resulting degradation in sensitivity is

<0.1dB, so the receiver easily meets

the specification of –115dBm. This is

illustrated in Figure 3. Single WCDMA

carriers can also appear out of band,

as specified in section 7.5.1. These

can be directly adjacent to the receive

band at levels as high as –40dBm. Here

again, the second order effect of such

carriers upon sensitivity is negligible,

as the preceding analysis shows.

from transmitter leakage in FDD systems, as shown in Figure 4. In an FDD

system, the transmitter and receiver

The baseband product that appears

Sensitivity: –121dBm

Processing + coding gain: 25dB

Signal to noise ratio at sensitivity:

5.2dB

Thermal noise at receiver input:

–101.2dBm

RF gain preceding LT5575: 20dB

Equivalent interference level at

Rx input: –118.7dBm

The baseband second order product

Another threat to sensitivity comes

Linear Technology Magazine • June 2008

DESIGN FEATURES L

y t A t t

a A t t B t t

u

( ) ( ) cos

( )cos ( )cos

= +…

+ +

ω

ω ω

3

33

3

2

3

+…

= +…

+

Higher Order Terms

A t t

a A t B

( )cos

( ) (ωtt t t

a A t B t t t

A

u

u

)cos cos

( ) ( )cos cos

2

3

2 2

3

ω ω

ω ω+ …

= (( )cos

( ) ( )cos( )

t t

a A t B t t

u

ω

ω ω

+…

+ − …

3

4

2

3

2

P

Z

E a A t B t

BB

=

1 3

4

0

3

2

2

• ( ) ( )

P

a

Z

E A t E B t

BB

=

( )

{ } { }

9

16

3

2

0

2 4

• ( ) • ( )

P P P Z a

BB S u

=

( ) ( ) ( )

9

2

2

0

232

•

P a Z P P

BB S u

=

( ) ( ) ( )

27

2

320

2 2

•

ADC

0°

I/Q DEMOD

GAIN = 30dB

GAIN = 20dB

EQUIVALENT

PSEUDO-RANDOM

DISTORTION

AT –155.7dBm

TOTAL Rx

THERMAL NOISE

= –101.2dBm

WCDMA

INTERFERER

AT –48dBm

+ TONE AT

–48dBm

INTERFERERS

AT –28dBm

DISTORTION

AT –135.7dBm

90°

MODULATED SIGNAL AND TONE EXAMPLE

DOWNCONVERSION

LO

RF PASSBAND

0Hz

BASEBAND PSEUDO-RANDOM POWER

DUE TO 3RD ORDER DISTORTION

=9/2a

3

2

Z

0

2

PSP

u

2

RF SIGNAL

POWER = P

S

TONE

POWER = P

u

are operating at the same time. For

the WCDMA Band I case, the transmit

band is 130MHz above the receive

band. A single antenna is commonly

used, with the transmitter and receiver

joined by a diplexer. Here are some

typical basestation coupled resonator-type diplexer specifications:

q

Isolation, Tx to Rx 2110MHz:

55dB

q

Diplexer insertion loss, Tx path:

1.2dB

In the case of a Wide Area basestation, the transmit power may be as high

as 46dBm. At the transmit port of the

diplexer the power is at least 47dBm.

This high level modulated signal leaks

to the receiver input, and some portion

of it drives the I/Q demodulator:

q

Receiver input power: –8dBm

q

Rx BPF rejection at 2110MHz:

40dB

q

RF gain preceding LT5575: 20dB

q

Signal entering LT5575: –28dBm

q

LT5575 IIP2, 2-tone: 60dBm

q

LT5575 a2: 0.00317

A MATLAB simulation performed

using a pseudo-random channel predicts the following:

q

Distortion at LT5575 output:

–114.7dBm

Refer this signal back to the receiver

input:

q

RF gain preceding LT5575: 20dB

q

Equivalent interference level at

Rx input: –134.7dBm

q

Thermal noise at receiver input:

–101.2dBm

This equivalent interference is

33.5dB below the thermal noise at the

receiver input. The resulting degradation in sensitivity is <0.1dB, so the

receiver easily meets the specification

of –121dBm.

modulated signal, then B(t) represents

the signal envelope.

to y(t):

Figure 5. Effects of 3rd order distortion

Third Order Distortion (IP3)

The third order intercept point (IP3)

has an effect upon the baseband signal

when two properly spaced channels or

signals enter the nonlinear element.

Refer back to the transfer function:

y(t) = x(t) + a2x2(t) + a3x3(t) + …, where

x(t) is the input signal consisting of

both desired and undesired signals.

Consider now the third order distortion term. The coefficient a3 is equal

to 2/(3Z0IP3) where IP3 is the single

tone intercept point in Watts. Note

that the 2-tone IP3 is 4.78dB below

the single-tone IP3.

Two signals entering the nonlinear

element generate a signal centered

at zero frequency if the spacing between the two signals is equal to the

distance to zero frequency. Let x(t) =

A(t)cosωt + B(t)cosωut, where the first

term is the desired signal and the

second term is an unwanted signal.

The unwanted signal may be a tone

or a modulated signal. If it is a tone,

then B(t) is simply a constant. If it is a

terest here is ¾a3A(t)B2(t)cos(2ωu – ω)t.

In order for this distortion to appear

at baseband, set ω = 2ωu. The power

of the distortion is

which can be expanded to

desired signal and a tone interferer;

B(t) may be replaced by B. See Figure

5. The value of E{B4} can be expressed

as (2Z0Pu)2, where Pu is the power of

the tone interferer. We can use Equation 2 to express E{A2(t)} in terms of the

desired signal power as 2ZoPs, where

Ps is the power of the desired signal.

The power level of the distortion at

baseband is then:

The output signal is then equal

The third order distortion term of in-

[7]

Consider the case of a modulated

[8]

Linear Technology Magazine • June 2008

Figure 6. 3rd Order distortion due to WCDMA carrier + tone interferer

If the undesired signal is modulated,

use Equations 2 and 5 to express

E{B4(t)} as 3(2Z0Pu)2, where Pu is the

power of the tone interferer:

[9]

In the direct conversion receiver

example, Section 7.6.1 of the WCDMA

specification calls for two interfering

continued on page 27

13

L DESIGN FEATURES

OF

GND

LO

VCC= 3V VDD= 3V

DIFFERENTIAL

AMPLIFIERS

MAIN

RF

INA

–

INA

+

V

REF

OV

DD

0.5V TO V

DD

SAW

FILTER

MUX

CLKOUT

ADC CLK

SPI

14-BIT

125Msps ADC

LO

DIVERSITY

RF

INB

–

INB

+

OGND

SAW

FILTER

14-BIT

125Msps ADC

DAC

DAC

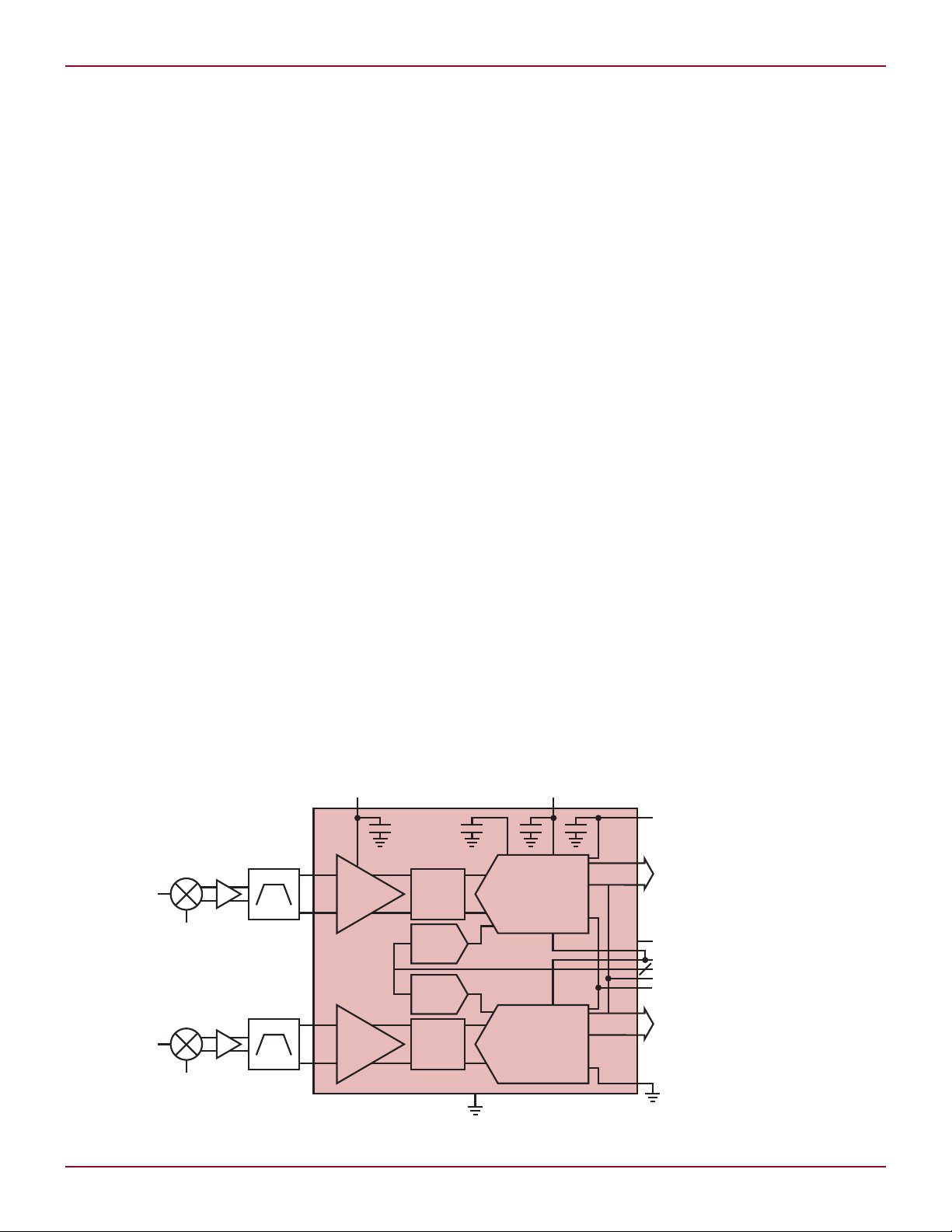

Complete Dual-Channel Receiver

Combines 14-Bit, 125Msps ADCs,

Fixed-Gain Amplifiers and Antialias

Filters in a Single 11.25mm × 15mm

μModule Package

Introduction

Extensive hands-on applications

experience is a prerequisite for any

designer hoping to take full advantage of an ADC’s capabilities when

sampling high dynamic range signals

in multichannel IF-sampling or in I/Q

baseband communications channels.

An intimate knowledge of the amplifier output stage and ADC front end

is required to match the impedances,

while careful attention to layout is

required to minimize coupling of

the digital outputs into the sensitive

analog input.

In fact, good layout is paramount

to maintaining ADC performance,

yet ever more demanding market

requirements call for smaller designs

and higher channel density, which

exacerbate layout issues. These

design requirements can challenge

even the most seasoned engineer if

his expertise lies in the RF or digital

worlds.

The LTM9002 dual-channel, IF/

baseband receiver harnesses years

of applications design experience

and squeezes it into an easy-to-use

11.25mm × 15mm µModule package.

Inside the package is a high performance dual 14-bit ADC sampling up

to 125Msps, antialiasing filters, two

fixed gain differential ADC drivers and

a dual auxiliary DAC. By combining

these components, the LTM9002 eliminates the burden of input impedance

matching, filter design, gain/phase

matching, isolation between channels

and high frequency layout, dramatically improving time to market. Even

in this small package, the LTM9002

guarantees high performance that will

enhance many communications and

instrumentation applications.

by Todd Nelson

Multichannel

ADC Applications

Multichannel applications have several unique requirements, such as

channel matching in terms of gain,

phase, DC offset, and channel-tochannel isolation. Gain and phase

errors directly affect the demodulation of the I and Q channels. And

since direct conversion receivers

are typically DC-coupled, DC offset

limits the dynamic range of the receiver. Multiple-input, multiple-output

(MIMO) systems depend on multiple

receiver channels all receiving the

same signal while detecting the slight

variations caused by multipath delays

so gain and phase errors affect these

systems as well. Like I/Q receivers,

diversity receivers require excellent

isolation between channels because

crosstalk appears as noise corruption

and can be more difficult to suppress

14

Figure 1. LTM9002 used for a Main/Diversity receiver.

Linear Technology Magazine • June 2008

DESIGN FEATURES L

FFT VALUE (dBFS)

FFT POINT

81921

0

–120

1024 2048 3072 4096 5120 6144 7168

–10

–110

–100

–90

–80

–70

–20

–30

–40

–50

–60

HD3

HD2

REF

BUFFER

10k

1.25V

1V (OPEN CIRCUIT,

4k THEVENIN

RESISTANCE)

10k

1000pF

2.49k

SENSE

RANGE

SELECT

REF

1.5V

REFERENCE

LTM9002

DAC

SDI

CS/LD

SCK

with digital filtering. Clearly, channel

matching and channel isolation of

the ADC and driver circuits directly

impact system-level performance.

For many multichannel applications,

these errors cannot be corrected in

the digital domain.

Performance

The LTM9002 achieves 66dB Signal

to Noise Ratio (SNR) and 74dB Spurious Free Dynamic Range (SFDR) at

140MHz input frequency. Figure 2

shows the FFT under these conditions.

SNR is a function of the ADC and

amplifier performance as well as the

amplifier gain and filter bandwidth.

The inherent amplifier noise is proportional to the voltage gain; therefore,

the 26dB amplification increases the

amplifier noise by 20 times whereas

8dB amplification would only increase

the noise by 2.5 times. Likewise, the

amplifier noise (in nV/√Hz) increases

with the square of the filter bandwidth.

It is important to remember these relationships when assessing the entire

signal chain.

For multichannel applications,

channel-to-channel matching and

isolation are important considerations.

The LTM9002 achieves 90dB isolation

at 140MHz input frequency despite

the small form factor. The overall gain

is typically 26dB on the default span

setting and varies just 0.1dB between

the two channels. The 12-bit auxiliary

DAC can be configured to adjust the

span by 61µV per step using the circuit

in Figure 3.

Another important performance

metric is printed circuit board (PCB)

area efficiency. Here, the LTM9002

excels. The LTM9002 requires no external components—no supply bypass

capacitors, no passive filtering, no

impedance matching or translating

components. In many IF-sampling

applications, gain can be obtained

through transformers, but they are

often large and difficult for automated

assembly equipment to mount. In

DC-coupled applications, amplifiers

are required as ADC drivers, along

with their associated antialias filter

network. It is not uncommon for the

entire IF/baseband receiver system to

Linear Technology Magazine • June 2008

Figure 2. FFT showing LTM9002 AC

performance with 140MHz input frequency.

consume two square inches of board

area (approximately 25mm × 50mm).

None of this external circuitry is required with the LTM9002 so it requires

only about one-quarter of a square

inch (11.25mm × 15mm), better by a

factor of eight.

Attributes and Configurations

The µModule construction allows the

LTM9002 to mix standard ADC and

amplifier components regardless of

their process technology and match

them with passive components for a

particular application. The µModule

receiver consists of wire-bonded die,

packaged components and passives

mounted on a high performance,

4-layer, Bismaleimide-Triazine (BT)

substrate. BT is similar to other laminate substrates such as FR4 but has

superior stiffness and a lower coefficient of thermal expansion.

The LTM9002-AA utilizes a dual, 14bit, 125Msps ADC, two 26dB fixed-gain

amplifiers and also includes a 12-bit

dual DAC configured for full-scale

span adjustment as shown in Figure 1.

Internal antialias filters limit the input

frequency to less than 170MHz. The

amplifiers present a 50Ω differential

input impedance and an input range

of ±50mV, or –16dBm. This default

span is set by connecting the SENSE

pin to VDD, and can be adjusted in

three ways. For a –3dBm lower span,

the SENSE pin can be connected to

1.5V. By connecting SENSE to VDD or

1.5V, the internal reference is used.

An external reference can be used by

applying 0.5V–1.0V to the SENSE pin.

The auxiliary DAC offers a final option

for selecting the range. Alternately,

fine adjustments to the span, such as

balancing the gain of the two channels,

can be made with external references

or the auxiliary DAC.

Multiple power saving modes include independently disabling either

amplifier or the ADC. The ADC has

two shutdown states: NAP and SLEEP

modes. In NAP mode, the internal

reference remains biased so that

conversions can resume within 100

clock cycles upon start-up. In SLEEP

mode the reference is shut down and

start-up takes 1µs or more. A clock

duty cycle stabilizer feature is available and an output clock signal is

provided for accurately latching the

output data. The two channels can be

Figure 3. Using an external reference and the internal auxiliary DAC for span adjustment.

15

L DESIGN FEATURES

output on separate parallel busses or

multiplexed onto a single parallel bus

to save processor pins.

Interfacing to the

Analog Inputs

The analog inputs of the LTM9002

present a differential 50Ω resistive

input impedance, which in most cases

exactly matches the signal path. The

input common mode level should

be approximately VCC/2. Traditionally, the input of an ADC requires

considerable care in terms of drive

current, settling time and response

to the nonlinear characteristics of