Linear Technology LTC1668 Datasheet

Final Electrical Specifications

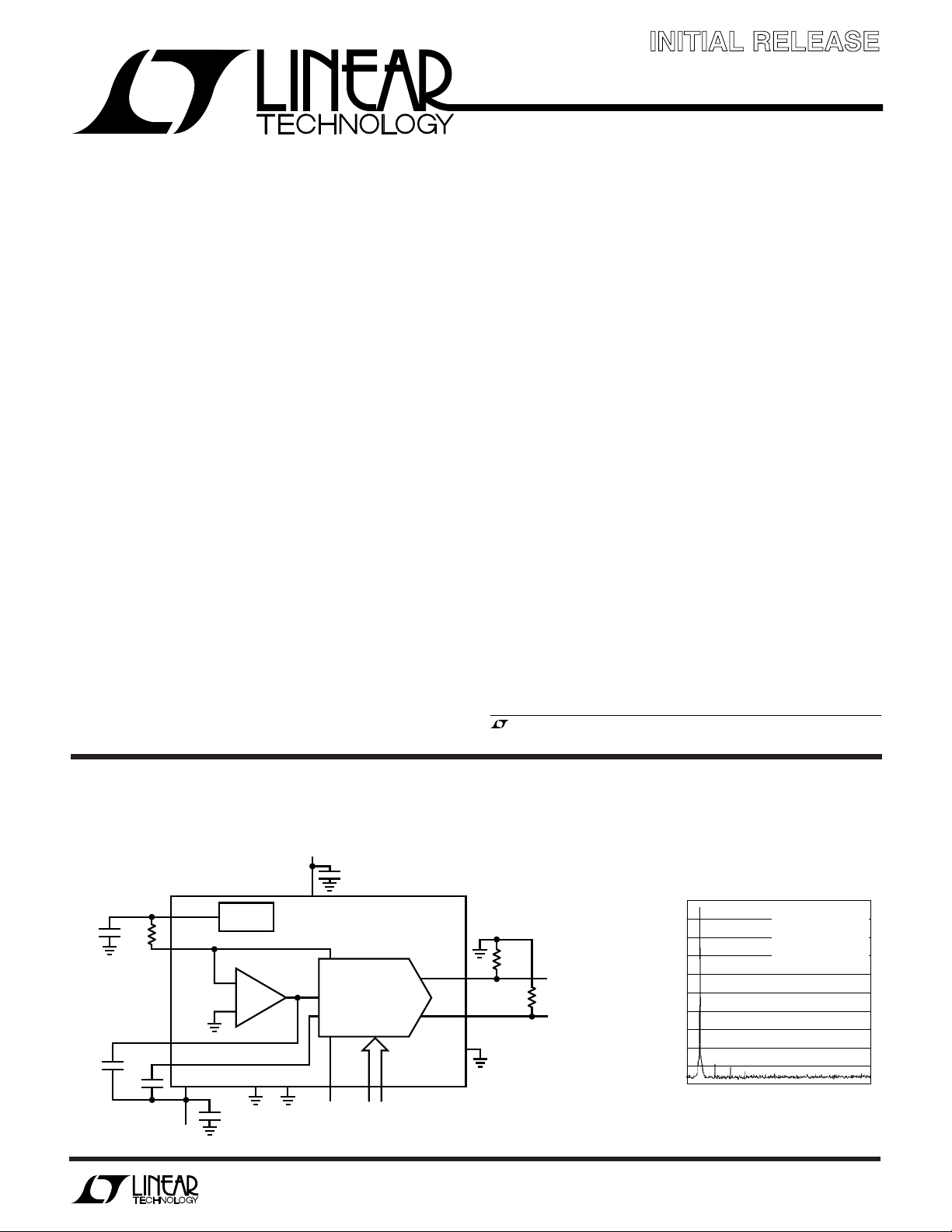

FREQUENCY (1.25MHz/DIV)

0.05

SIGNAL AMPLITUDE (dBm)

–45

–25

–5

1668 G01

–65

–85

–55

–35

–15

–75

–95

–105

6.3

12.55

f

CLOCK

= 25Msps

f

OUT

= 1.007MHz

AMPLITUDE = 0dBFS

= –8.5dBm

SFDR = 86dBc

FEATURES

LTC1668

16-Bit, 50Msps DAC

February 2000

U

DESCRIPTIO

■

50Msps Update Rate

■

16-Bit Resolution

■

High Spectral Purity: 87dB SFDR at 1MHz f

■

Differential Current Outputs

■

30ns Settling Time

■

5pV-s Glitch Impulse

■

Low Power: 180mW from ±5V Supplies

■

TTL/CMOS (3.3V or 5V) Inputs

■

Small Package: 28-Pin SSOP

U

APPLICATIO S

■

Cellular Base Stations

■

Multicarrier Base Stations

■

Wireless Communication

■

Direct Digital Synthesis (DDS)

■

xDSL Modems

■

Arbitrary Waveform Generation

■

Automated Test Equipment

■

Instrumentation

OUT

The LTC®1668 is a 16-bit, 50Msps differential current

output DAC implemented on a high performance BiCMOS

process with laser trimmed, thin-film resistors. The combination of a novel current-steering architecture and a

high performance process produces a DAC with exceptional AC and DC performance. This is the first 16-bit DAC

in the marketplace to exhibit an SFDR (spurious free

dynamic range) of 87dB for an output signal frequency of

1MHz.

Operating from ±5V supplies, the LTC1668 can be configured to provide full-scale output currents up to 10mA.

The differential current outputs of the DAC allow singleended or true differential operation. The –1V to 1V output

compliance of the LTC1668 allows the outputs to be connected directly to external resistors to produce a differential output voltage without degrading the converter’s

linearity. Alternatively, the outputs can be connected to the

summing junction of a high speed operational amplifier,

or to a transformer.

The LTC1668 is available in a 28-pin SSOP and is fully

specified over the industrial temperature range.

, LTC and LT are registered trademarks of Linear Technology Corporation.

TYPICAL APPLICATIO

REFOUT

R

0.1µF

0.1µF

SET

C1

C2

0.1µF

2k

I

REFIN

COMP1

COMP2

V

SS

–5V

U

16-Bit, 50Msps DAC

5V

0.1µF

V

2.5V

REFERENCE

+

–

AGND DGND CLK DB15 DB0

0.1µF

DD

HIGH SPEED

CLOCK

INPUT

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

16-BIT

DAC

16-BIT DATA

INPUT

LTC1668

I

OUT A

I

OUT B

LADCOM

1668 TA01

52.3Ω

52.3Ω V

+

OUT

–

1V

P-P

DIFFERENTIAL

Single Tone SFDR

1

LTC1668

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

Supply Voltage (VDD)................................................ 6V

Negative Supply Voltage (VSS) ............................... – 6V

Total Supply Voltage (VDD to VSS) .......................... 12V

Digital Input Voltage ....................–0.3V to (VDD + 0.3V)

Analog Output Voltage

(I

and I

OUT A

Power Dissipation............................................. 500mW

Operating Temperature Range

LTC1668C .............................................. 0°C to 70°C

LTC1668I........................................... –40°C to 85°C

Storage Temperature Range ................ –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

) ........ (VSS – 0.3V) to (VDD + 0.3V)

OUT B

UU

W

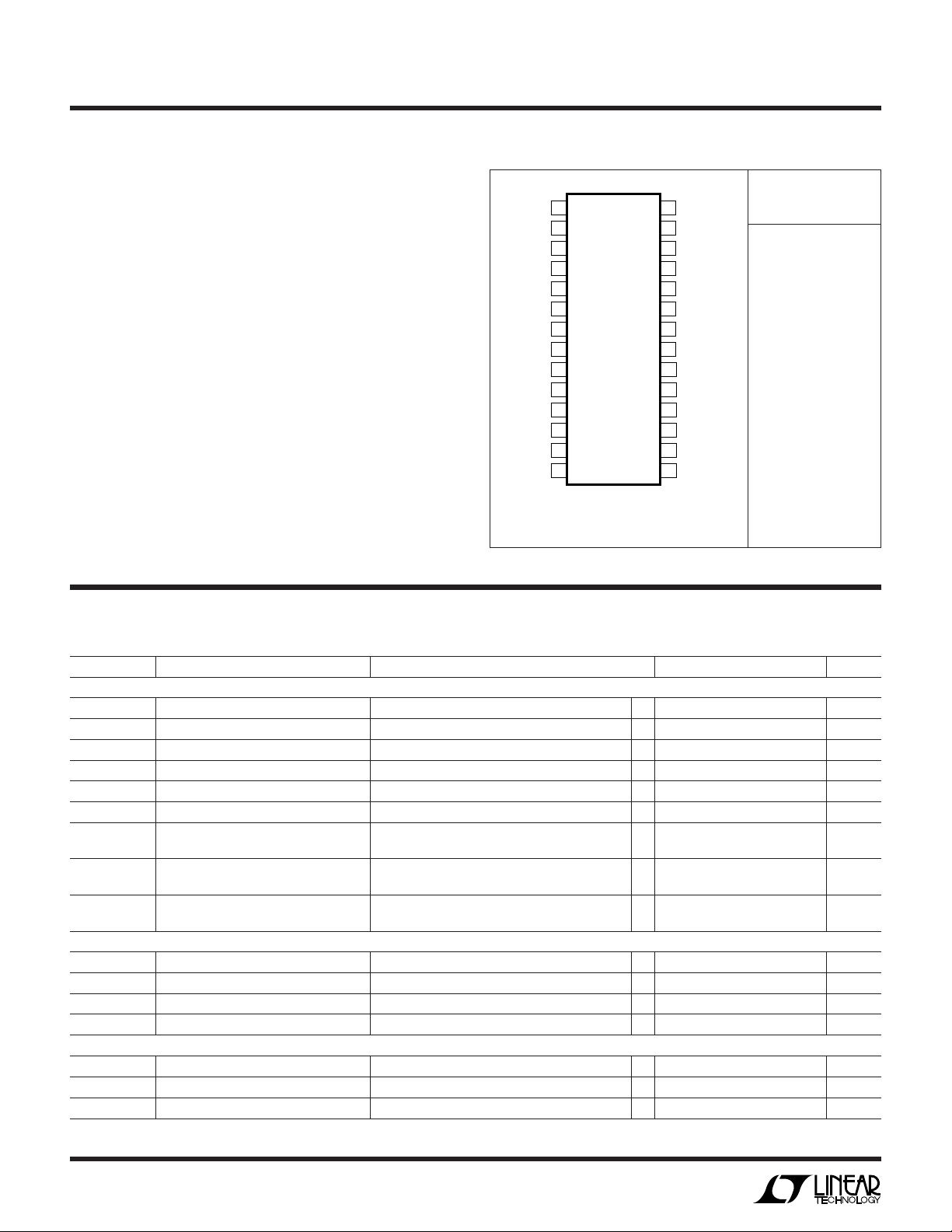

PACKAGE/ORDER I FOR ATIO

TOP VIEW

DB13

DB12

DB11

DB10

DB9

DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0 (LSB)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

G PACKAGE

28-LEAD PLASTIC SSOP

T

= 110°C, θJA = 100°C/W

JMAX

DB14

28

DB15 (MSB)

27

CLK

26

V

25

DGND

24

V

23

COMP2

22

COMP1

21

I

20

I

19

LADCOM

18

AGND

17

I

16

REFOUT

15

DD

SS

OUT A

OUT B

REFIN

Consult factory for Military grade parts.

ORDER PART

NUMBER

LTC1668CG

LTC1668IG

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VDD = 5V, VSS = –5V, LADCOM = AGND = DGND = 0V, I

The ● denotes specifications which apply over the full operating

= 10mA.

OUTFS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

DC Accuracy (Measured at I

, Driving a Virtual Ground)

OUTA

Resolution 16 Bits

Monotonicity 14 Bits

INL Integral Nonlinearity ±8 LSB

DNL Differential Nonlinearity ±1 ±4 LSB

Offset Error 0.1 ±0.2 % FSR

Offset Error Drift 5 ppm/°C

GE Gain Error Internal Reference, R

External Reference, V

= 2k 2 % FSR

IREFIN

= 2.5V, R

REF

= 2k 1 % FSR

IREFIN

Gain Error Drift Internal Reference 75 ppm/°C

External Reference 50 ppm/°C

PSRR Power Supply Rejection Ratio VDD = 5V ±5% ±0.1 % FSR/V

= –5V ±5% ±0.1 % FSR/V

V

SS

Analog Output

I

OUTFS

Full-Scale Output Current ● 110mA

Output Compliance Range IFS = 10mA ● –1 1 V

Output Resistance; R

IOUTA

, R

IOUTB

I

to LADCOM ● 0.7 1.1 1.5 kΩ

OUTA, B

Output Capacitance 5pF

Reference Output

Reference Voltage REFOUT Tied to I

Through 2kΩ 2.475 2.5 2.525 V

REFIN

Reference Output Drift 25 ppm/°C

Reference Output Load Regulation I

= 0mA to 5mA 6 mV/mA

LOAD

2

LTC1668

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VDD = 5V, VSS = –5V, LADCOM = AGND = DGND = 0V, I

The ● denotes specifications which apply over the full operating

= 10mA.

OUTFS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

Reference Input

Reference Small-Signal Bandwidth IFS = 10mA, C

= 0.1µF20kHz

COMP1

Power Supply

V

DD

V

SS

I

DD

I

SS

P

DIS

Positive Supply Voltage ● 4.75 5 5.25 V

Negative Supply Voltage ● –4.75 –5 –5.25 V

Positive Supply Current IFS = 10mA, f

Negative Supply Current IFS = 10mA, f

Power Dissipation IFS = 10mA, f

IFS = 1mA, f

= 25Msps, f

CLK

= 25Msps, f

CLK

= 25Msps, f

CLK

= 25Msps, f

CLK

= 1MHz ● 35 mA

OUT

= 1MHz ● 33 40 mA

OUT

= 1MHz ● 180 mW

OUT

= 1MHz ● 85 mW

OUT

Dynamic Performance (Differential Transformer Coupled Output, 50Ω Double Terminated, Unless Otherwise Noted)

f

CLOCK

t

S

t

PD

Maximum Update Rate ● 50 75 Msps

Output Settling Time To 0.1% FSR 30 ns

Output Propagation Delay 8ns

Glitch Impulse Single Ended 15 pV-s

Differential 5 pV-s

t

r

t

f

i

NO

Output Rise Time 4ns

Output Fall Time 4ns

Output Noise IFS = 10mA 50 pA/√Hz

IFS = 1mA 30 pA/√Hz

AC Linearity

SFDR Spurious Free Dynamic Range f

= 25Msps, f

CLK

OUT

= 1MHz

to Nyquist 0dB FS Output 78 87 dB

–6dB FS Output 87 dB

–12dB FS Output 86 dB

–18dB FS Output 80 dB

f

Spurious Free Dynamic Range f

Within a Window f

THD Total Harmonic Distortion f

= 50Msps, f

CLK

f

= 50Msps, f

CLK

f

= 50Msps, f

CLK

f

= 50Msps, f

CLK

= 25Msps, f

CLK

= 50Msps, f

CLK

= 25Msps, f

CLK

f

= 50Msps, f

CLK

= 1MHz 84 dB

OUT

= 2.5MHz 80 dB

OUT

= 5MHz 77 dB

OUT

= 20MHz 65 dB

OUT

= 1MHz, 2MHz Span 86 96 dB

OUT

= 5MHz, 4MHz Span 88 dB

OUT

= 1MHz –84 –77 dB

OUT

= 5MHz –76 dB

OUT

Digital Inputs

V

IH

V

IL

I

IN

C

IN

t

DS

t

DH

t

CLKH

t

CLKL

Digital High Input Voltage ● 2.4 V

Digital Low Input Voltage ● 0.8 V

Digital Input Current ● ±10 µA

Digital Input Capacitance 5pF

Input Setup Time ● 8ns

Input Hold Time ● 4ns

Clock High Time ● 5ns

Clock Low Time ● 8ns

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

3

LTC1668

UW

TYPICAL PERFOR A CE CHARACTERISTICS

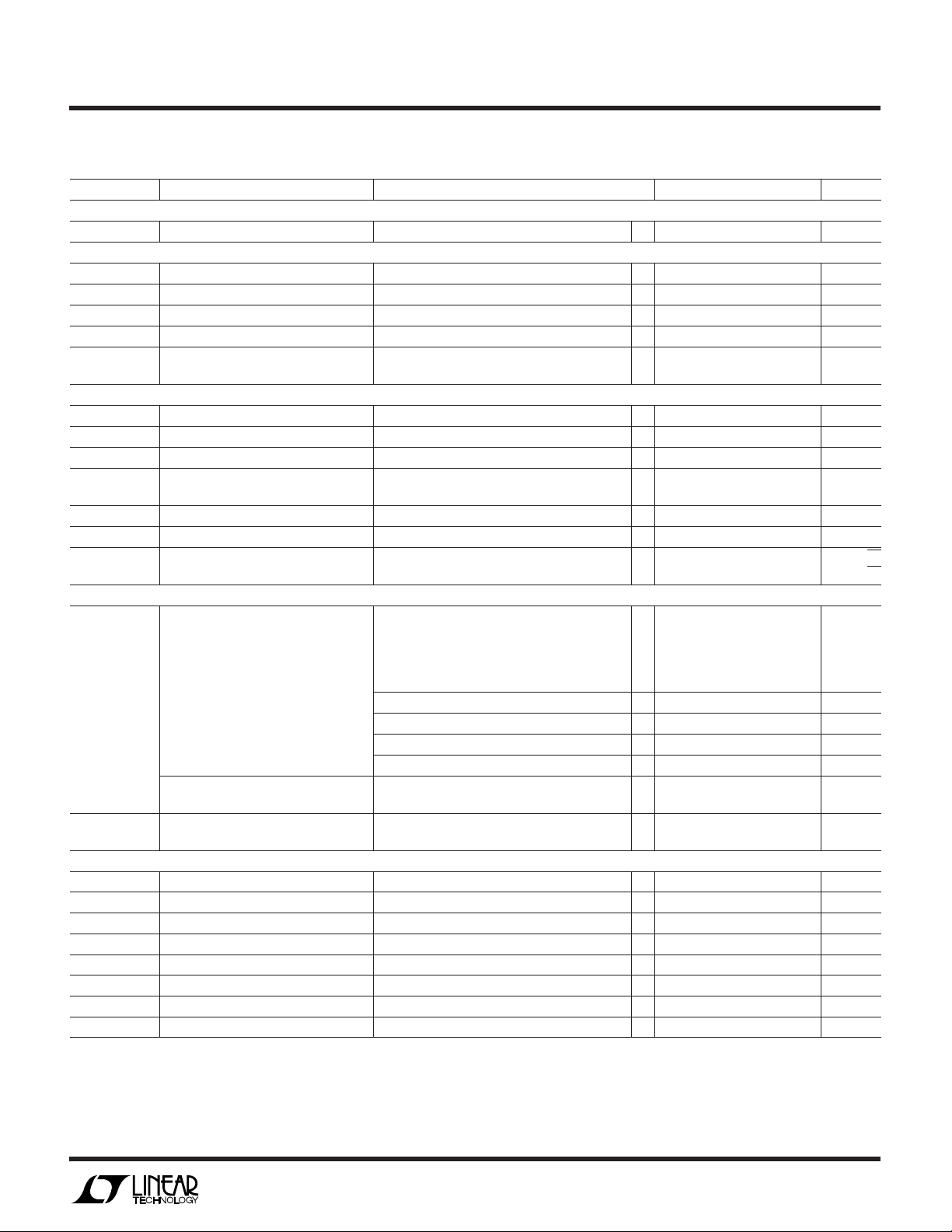

Single Tone SFDR 2-Tone SFDR

–5

–15

–25

–35

–45

–55

–65

–75

SIGNAL AMPLITUDE (dBm)

–85

–95

–105

0.05

FREQUENCY (1.25MHz/DIV)

f

= 25Msps

CLOCK

f

= 1.007MHz

OUT

AMPLITUDE = 0dBFS

= –8.5dBm

SFDR = 86dBc

6.3

1668 G01

12.55

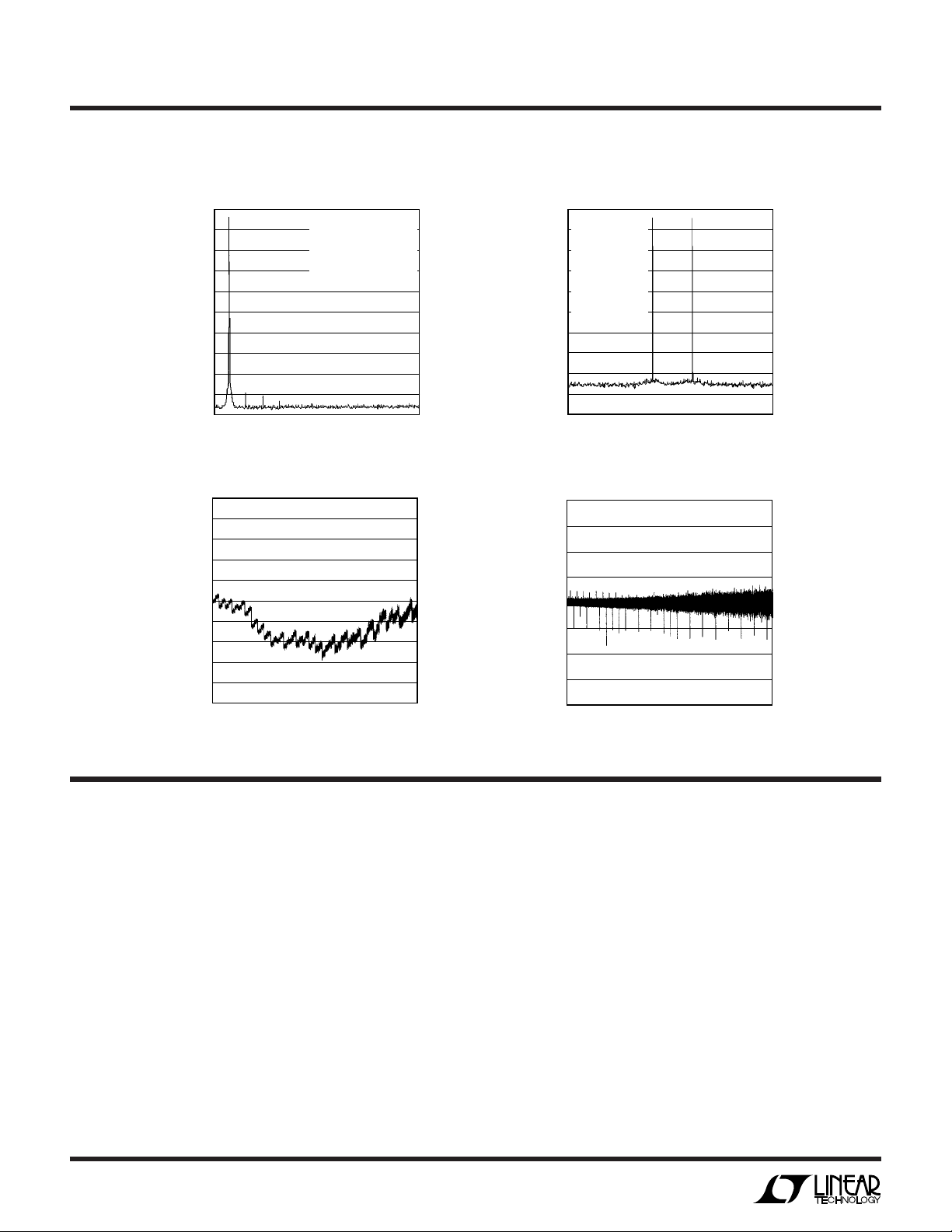

Integral Nonlinearity Differential Nonlinearity

5

4

3

2

1

0

–1

–2

–3

INTEGRAL NONLINEARITY (LSB)

–4

–5

16384

32768

DIGITAL INPUT CODE

49152

65535

1668 G03

–10

–20

–30

–40

–50

–60

–70

–80

SIGNAL AMPLITUDE (dBm)

–90

–100

–110

2.0

1.5

1.0

0.5

–0.5

–1.0

DIFFERENTIAL NONLINEARITY (LSB)

–1.5

–2.0

f

= 50Msps

CLOCK

=

f

OUT1

4.028MHz

=

f

OUT2

4.419MHz

AMPLITUDE 1, 2

= –6dBFS

= –14.5dBm

SFDR > 77dBc

3.2

0

0

4.2

FREQUENCY (0.2MHz/DIV)

16384

32768

DIGITAL INPUT CODE

49152

5.2

1668 G02

65535

1668 G04

U

UU

PI FU CTIO S

REFOUT (Pin 15): Internal Reference Voltage Output.

Nominal value is 2.5V. Requires a 0.1µF bypass capacitor

to AGND.

I

(Pin 16): Reference Input Current. Nominal value is

REFIN

1.25mA for IFS = 10mA. IFS = I

REFIN

• 8.

AGND (Pin 17): Analog Ground.

LADCOM (Pin 18): Attenuator Ladder Common. Normally

tied to GND.

I

(Pin 19): Complementary DAC Output Current. Full-

OUT B

scale output current occurs when all data bits are 0s.

I

(Pin 20): DAC Output Current. Full-scale output

OUT A

current occurs when all data bits are 1s.

4

COMP1 (Pin 21): Current Source Control Amplifier Compensation. Bypass to VSS with 0.1µF.

COMP2 (Pin 22): Internal Bypass Point. Bypass to V

SS

with 0.1µF.

VSS (Pin 23): Negative Supply Voltage. Nominal value is

–5V.

DGND (Pin 24): Digital Ground.

VDD (Pin 25): Positive Supply Voltage. Nominal value is 5V.

CLK (Pin 26): Clock Input. Data is latched and the output

is updated on positive edge of clock.

DB15 to DB0 (Pins 27, 28, 1 to 14): Digital Input Data Bits.

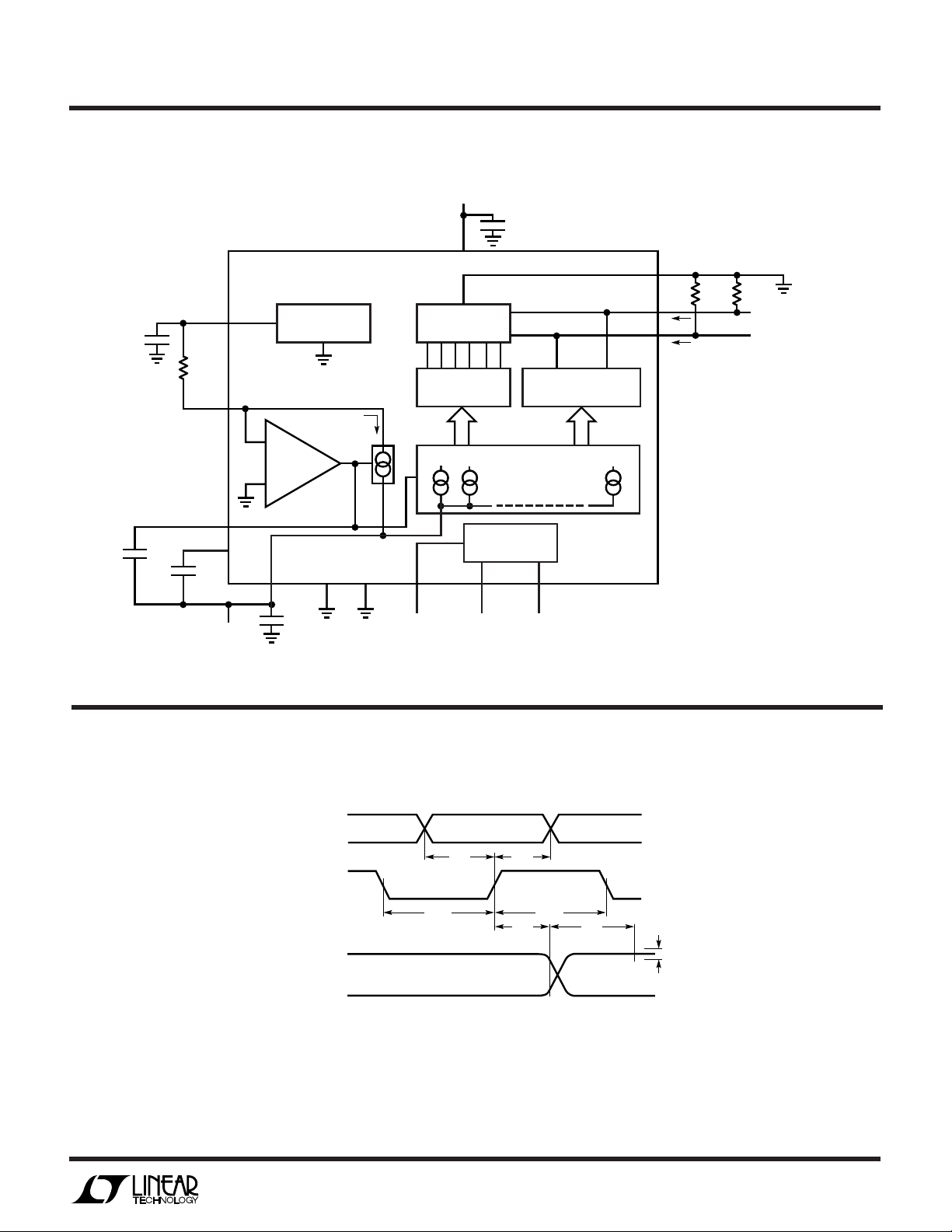

BLOCK DIAGRA

LTC1668

0.1µF

V

REF

REFOUT

15

R

SET

2k

IREFIN

16

W

2.5V

REFERENCE

IFS/8

5V

25

ATTENUATOR

LADDER

LSB SWITCHES

0.1µF

SEGMENTED SWITCHES

FOR DB15–DB12

LADCOM

I

OUT A

I

OUT B

18

20

19

52.3Ω 52.3Ω

+

–

LTC1668

V

OUT

1V

P-P

DIFFERENTIAL

COMP121

22

0.1µF

COMP2

0.1µF

–5V

UWW

TI I G DIAGRA

+

–

23

V

SS

0.1µF

AGND17DGND

DB0

TO DB15

CLK

I

INT

24

N – 1

CLK DB0DB15 • • •

26 27 14

CLOCK

INPUT

CURRENT SOURCE ARRAY

• • • • • •

INPUT LATCHES

16-BIT

DATA INPUT

N N + 1

t

DS

t

DH

1668 BD

I

OUT A/IOUT B

t

CLKL

N – 1 N

t

CLKH

t

PD

t

ST

0.1%

1668 TD

5

Loading...

Loading...