FEATURES

LT1809/LT1810

Single/Dual 180MHz, 350V/µs

Rail-to-Rail Input and Output

Low Distortion Op Amps

U

DESCRIPTIO

■

–3dB Bandwidth: 320MHz, AV = 1

■

Gain-Bandwidth Product: 180MHz, A

■

Slew Rate: 350V/µs

■

Wide Supply Range: 2.5V to 12.6V

■

Large Output Current: 85mA

■

Low Distortion, 5MHz: –90dBc

■

Input Common Mode Range Includes Both Rails

■

Output Swings Rail-to-Rail

■

Input Offset Voltage, Rail-to-Rail: 2.5mV Max

■

Common Mode Rejection: 89dB Typ

■

Power Supply Rejection: 87dB Typ

■

Open-Loop Gain: 100V/mV Typ

■

Shutdown Pin: LT1809

■

Single in 8-Pin SO and 6-Pin SOT-23 Packages

■

Dual in 8-Pin SO and MSOP Packages

■

Operating Temperature Range: –40°C to 85°C

≥ 10

V

U

APPLICATIO S

■

Driving A/D Converters

■

Low Voltage Signal Processing

■

Active Filters

■

Rail-to-Rail Buffer Amplifiers

■

Video Line Driver

, LTC and LT are registered trademarks of Linear Technology Corporation.

The LT®1809/LT1810 are single/dual low distortion railto-rail input and output op amps with a 350V/µs slew rate.

These amplifiers have a –3dB bandwidth of 320MHz at

unity-gain, a gain-bandwidth product of 180MHz (AV ≥ 10)

and an 85mA output current to fit the needs of low voltage,

high performance signal conditioning systems.

The LT1809/LT1810 have an input range that includes

both supply rails and an output that swings within 20mV

of either supply rail to maximize the signal dynamic range

in low supply applications.

The LT1809/LT1810 have very low distortion (–90dBc) up

to 5MHz that allows them to be used in high performance

data acquisition systems.

The LT1809/LT1810 maintain their performance for supplies from 2.5V to 12.6V and are specified at 3V, 5V and

±5V supplies. The inputs can be driven beyond the supplies without damage or phase reversal of the output.

The LT1809 is available in the 8-pin SO package with the

standard op amp pinout and the 6-pin SOT-23 package.

The LT1810 features the standard dual op amp pinout and

is available in 8-pin SO and MSOP packages. These

devices can be used as a plug-in replacement for many op

amps to improve input/output range and performance.

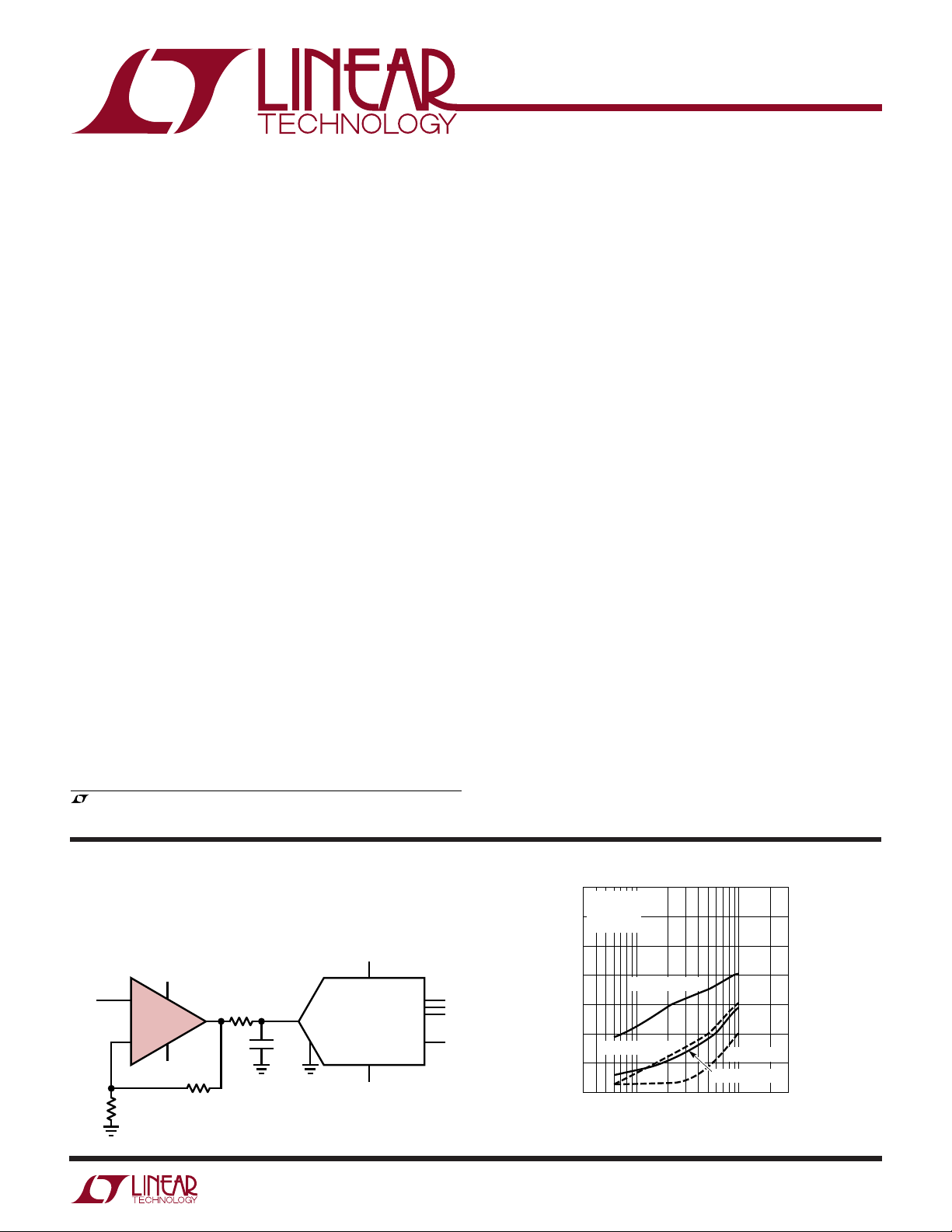

TYPICAL APPLICATIO

High Speed ADC Driver

5V

V

IN

1V

P-P

+

LT1809

–

–5V

R1

1k

R3

49.9Ω

C1

R2

1k

470pF

+A

U

IN

–A

LTC

PGA GAIN = 1

REF = 2.048V

IN

–5V

5V

®

1420

1809 TA01

•

•

•

12 BITS

10Msps

Distortion vs Frequency

–40

AV = +1

= 2V

V

IN

–50

VS = ±5V

–60

–70

–80

DISTORTION (dB)

–90

–100

–110

RL = 100Ω, 3RD

0.3

P-P

RL = 100Ω, 2ND

RL = 1k, 3RD

RL = 1k, 2ND

11030

FREQUENCY (MHz)

1809 TA02

1

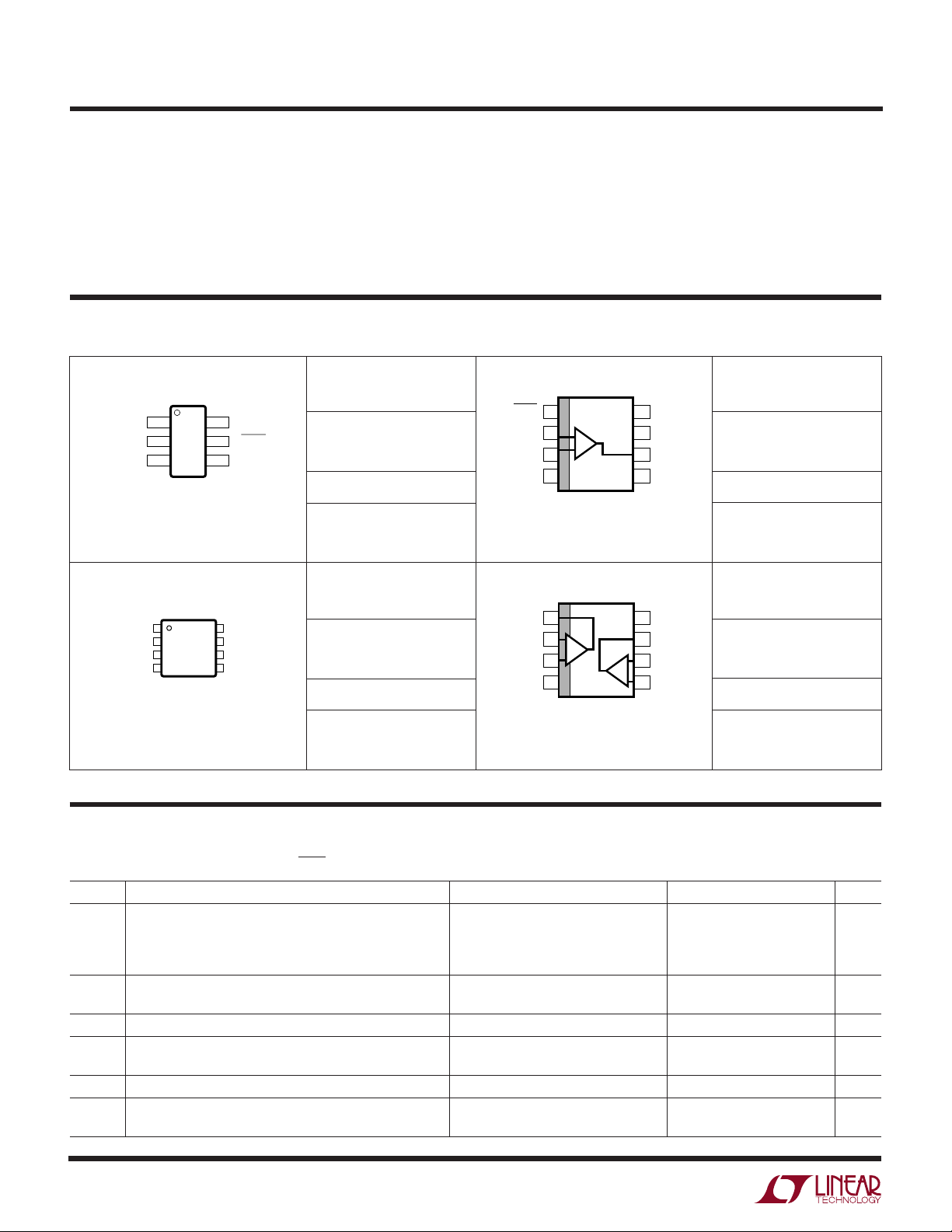

LT1809/LT1810

1

2

3

4

OUT A

–IN A

+IN A

V

–

8

7

6

5

V

+

OUT B

–IN B

+IN B

TOP VIEW

MS8 PACKAGE

8-LEAD PLASTIC MSOP

TOP VIEW

V

+

OUT B

–IN B

+IN B

OUT A

–IN A

+IN A

V

–

S8 PACKAGE

8-LEAD PLASTIC SO

1

2

3

4

8

7

6

5

A

B

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

Total Supply Voltage (V+ to V–) ........................... 12.6V

Input Voltage (Note 2) ..............................................±V

Input Current (Note 2) ........................................ ±10mA

Output Short-Circuit Duration (Note 3)............ Indefinite

Operating Temperature Range (Note 4) .. –40°C to 85°C

UU

W

PACKAGE/ORDER I FOR ATIO

ORDER PART

TOP VIEW

OUT 1

–

2

V

+IN 3

S6 PACKAGE

6-LEAD PLASTIC SOT-23

T

= 150°C, θJA = 145°C/W (Note 9)

JMAX

+

6 V

5 SHDN

4 –IN

NUMBER

LT1809CS6

LT1809IS6

S6 PART MARKING

LTKY

LTUF

ORDER PART

NUMBER

Specified Temperature Range (Note 5)... – 40°C to 85°C

Junction Temperature........................................... 150°C

S

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

TOP VIEW

ORDER PART

NUMBER

SHDN

–IN

+IN

1

2

–

+

3

–

V

4

8

NC

+

V

7

OUT

6

NC

5

LT1809CS8

LT1809IS8

S8 PART MARKING

S8 PACKAGE

8-LEAD PLASTIC SO

T

= 150°C, θJA = 100°C/W (Note 9)

JMAX

1809

1809I

ORDER PART

NUMBER

LT1810CS8

LT1810IS8

S8 PART MARKING

1810

1810I

T

= 150°C, θJA = 130°C/W (Note 9)

JMAX

LT1810CMS8

LT1810IMS8

MS8 PART MARKING

LTRF

LTTQ

T

= 150°C, θJA = 100°C/W (Note 9)

JMAX

Consult factory for parts specified with wider operating temperature ranges.

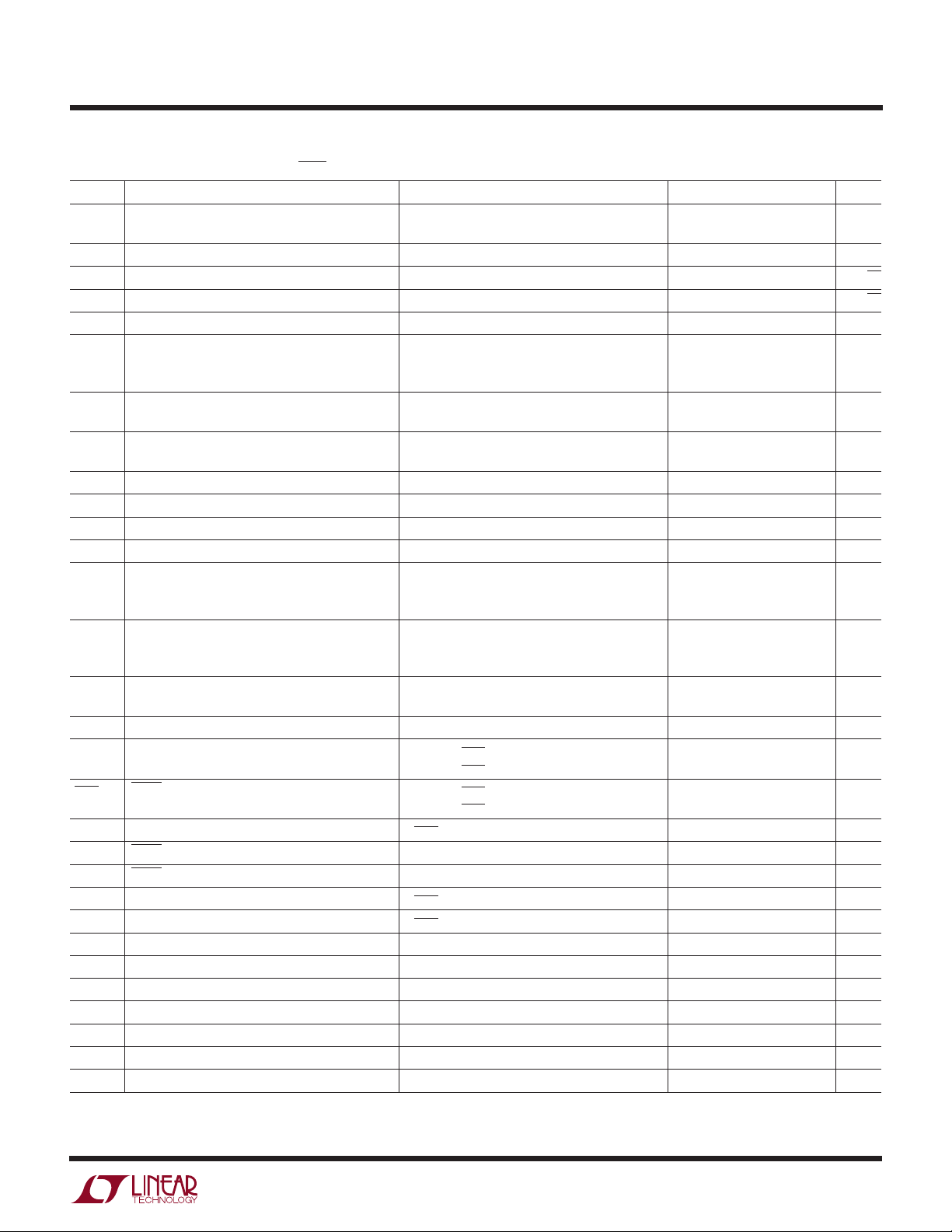

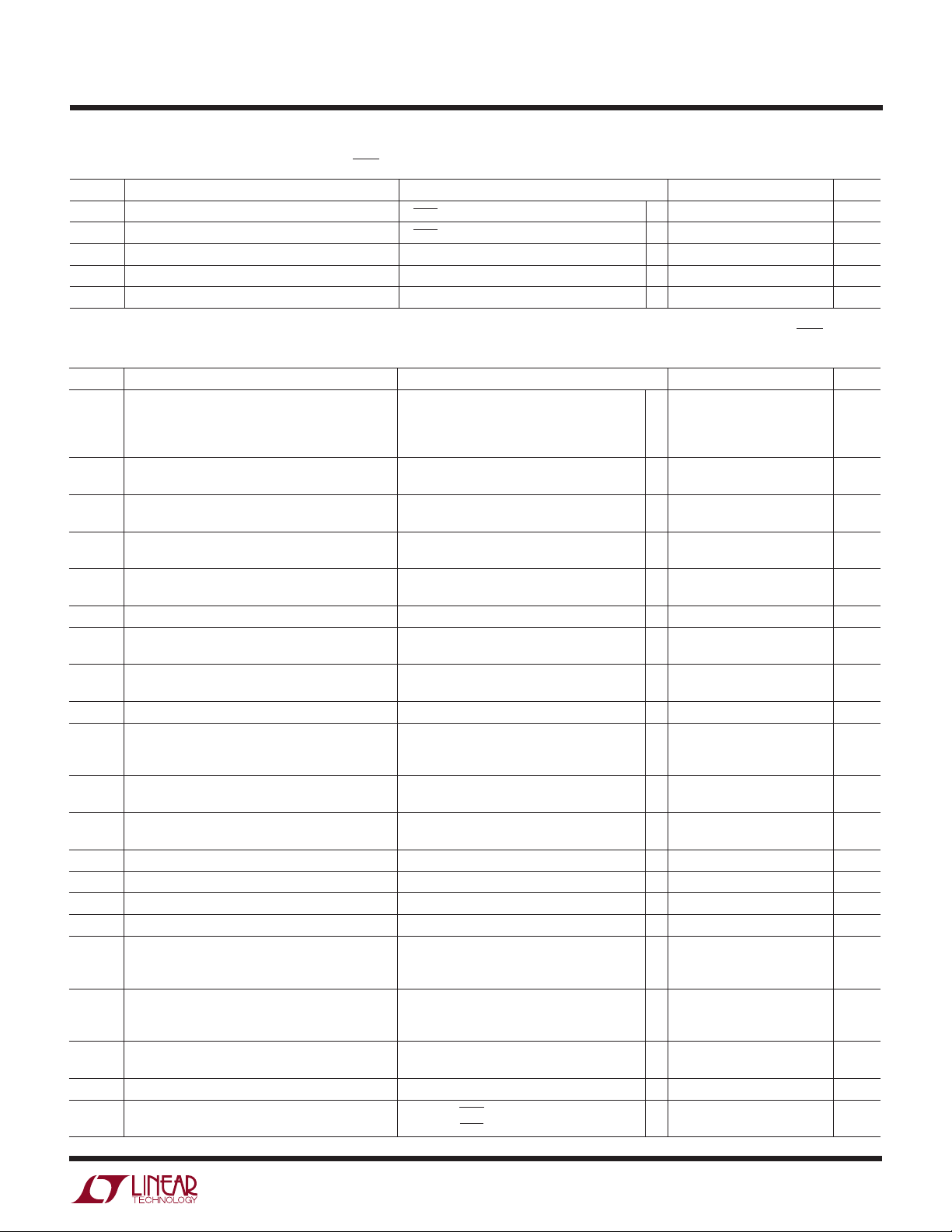

ELECTRICAL CHARACTERISTICS

T

= 25°C. V

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆V

OS

I

B

∆I

B

2

= 5V, 0V; VS = 3V, 0V; V

S

= open; VCM = V

SHDN

= half supply, unless otherwise noted.

OUT

Input Offset Voltage VCM = V+ LT1809 SO-8 0.6 2.5 mV

VCM = V– LT1809 SO-8 0.6 2.5 mV

+

V

= V

CM

–

VCM = V

Input Offset Shift VCM = V– to V+ LT1809 SO-8 0.3 2.0 mV

V

= V– to V

CM

+

0.6 3.0 mV

0.6 3.0 mV

0.3 2.5 mV

Input Offset Voltage Match (Channel-to-Channel) (Note 10) 0.7 6 mV

Input Bias Current VCM = V

Input Bias Current Shift VCM = V– + 0.2V to V

Input Bias Current Match (Channel-to-Channel) (Note 10) VCM = V

+

–

V

= V

CM

V

CM

+ 0.2V –27.5 –13 µA

+

+

= V– + 0.2V 0.2 8 µA

1.8 8 µA

14.8 35.5 µA

0.1 4 µA

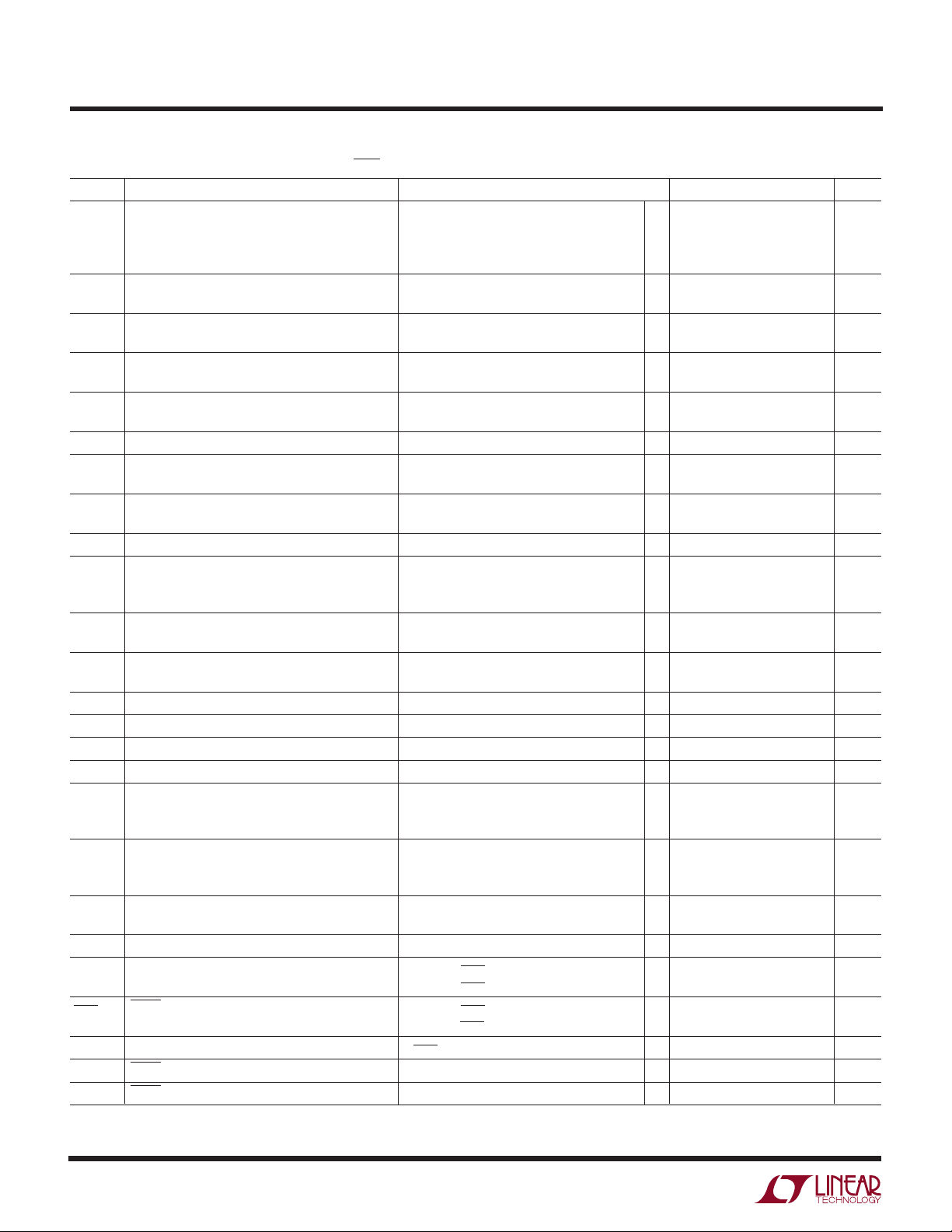

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

T

= 25°C. V

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

OS

∆I

OS

e

n

i

n

C

IN

A

VOL

CMRR Common Mode Rejection Ratio VS = 5V, V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, V

V

OL

V

OH

I

SC

I

S

I

SHDN

V

L

V

H

t

ON

t

OFF

GBW Gain-Bandwidth Product Frequency = 2MHz 160 MHz

SR Slew Rate VS = 5V, AV = –1, RL = 1k, VO = 4V

FPBW Full Power Bandwidth VS = 5V, V

THD Total Harmonic Distortion VS = 5V, AV = 1, RL = 1k, VO = 2V

t

S

∆G Differential Gain (NTSC) VS = 5V, AV = 2, RL = 150Ω 0.015 %

∆θ Differential Phase (NTSC) VS = 5V, AV = 2, RL = 150Ω 0.05 Deg

= 5V, 0V; VS = 3V, 0V; V

S

Input Offset Current VCM = V

Input Offset Current Shift VCM = V– + 0.2V to V

= open; VCM = V

SHDN

= half supply, unless otherwise noted.

OUT

+

V

= V– + 0.2V 0.2 4 µA

CM

+

0.05 1.2 µA

0.25 5.2 µA

Input Noise Voltage Density f = 10kHz 16 nV/√Hz

Input Noise Current Density f = 10kHz 5 pA/√Hz

Input Capacitance 2pF

Large-Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k to VS/2 25 80 V/mV

V

= 5V, VO = 1V to 4V, RL = 100Ω to VS/2 4 10 V/mV

S

= 3V, VO = 0.5V to 2.5V, RL = 1k to VS/2 15 42 V/mV

V

S

= V– to V

CM

= 3V, V

V

S

CMRR Match (Channel-to-Channel) (Note 10) VS = 5V, V

= 3V, V

V

S

= V– to V

CM

= V– to V

CM

= V– to V

CM

Input Common Mode Range V

PSRR Match (Channel-to-Channel) (Note 10) VS = 2.5V to 10V, V

+

+

+

+

= 0V 71 87 dB

CM

= 0V 65 87 dB

CM

66 82 dB

61 78 dB

60 82 dB

55 78 dB

–

+

V

Minimum Supply Voltage (Note 6) 2.3 2.5 V

Output Voltage Swing LOW (Note 7) No Load 12 50 mV

= 5mA 50 120 mV

I

SINK

I

= 25mA 180 375 mV

SINK

Output Voltage Swing HIGH (Note 7) No Load 20 80 mV

= 5mA 80 180 mV

I

SOURCE

= 25mA 330 650 mV

I

SOURCE

Short-Circuit Current VS = 5V ±45 ±85 mA

V

= 3V ±35 ±70 mA

S

Supply Current per Amplifier 12.5 17 mA

Supply Current, Shutdown VS = 5V, V

V

= 3V, V

S

SHDN Pin Current VS = 5V, V

= 3V, V

V

S

Output Leakage Current, Shutdown V

= 0.3V 0.1 75 µA

SHDN

= 0.3V 0.55 1.25 mA

SHDN

= 0.3V 0.31 0.90 mA

SHDN

= 0.3V 420 750 µA

SHDN

= 0.3V 220 500 µA

SHDN

SHDN Pin Input Voltage Low 0.3 V

SHDN Pin Input Voltage High VS – 0.5 V

Turn-On Time V

Turn-Off Time V

Settling Time 0.1%, VS = 5V, V

= 0.3V to 4.5V, RL = 100 80 ns

SHDN

= 4.5V to 0.3V, RL = 100 50 ns

SHDN

300 V/µs

23.5 MHz

OUT

P-P

= 4V

P-P

, fC = 5MHz –86 dB

P-P

= 2V, AV = –1, RL = 500Ω 27 ns

STEP

V

3

LT1809/LT1810

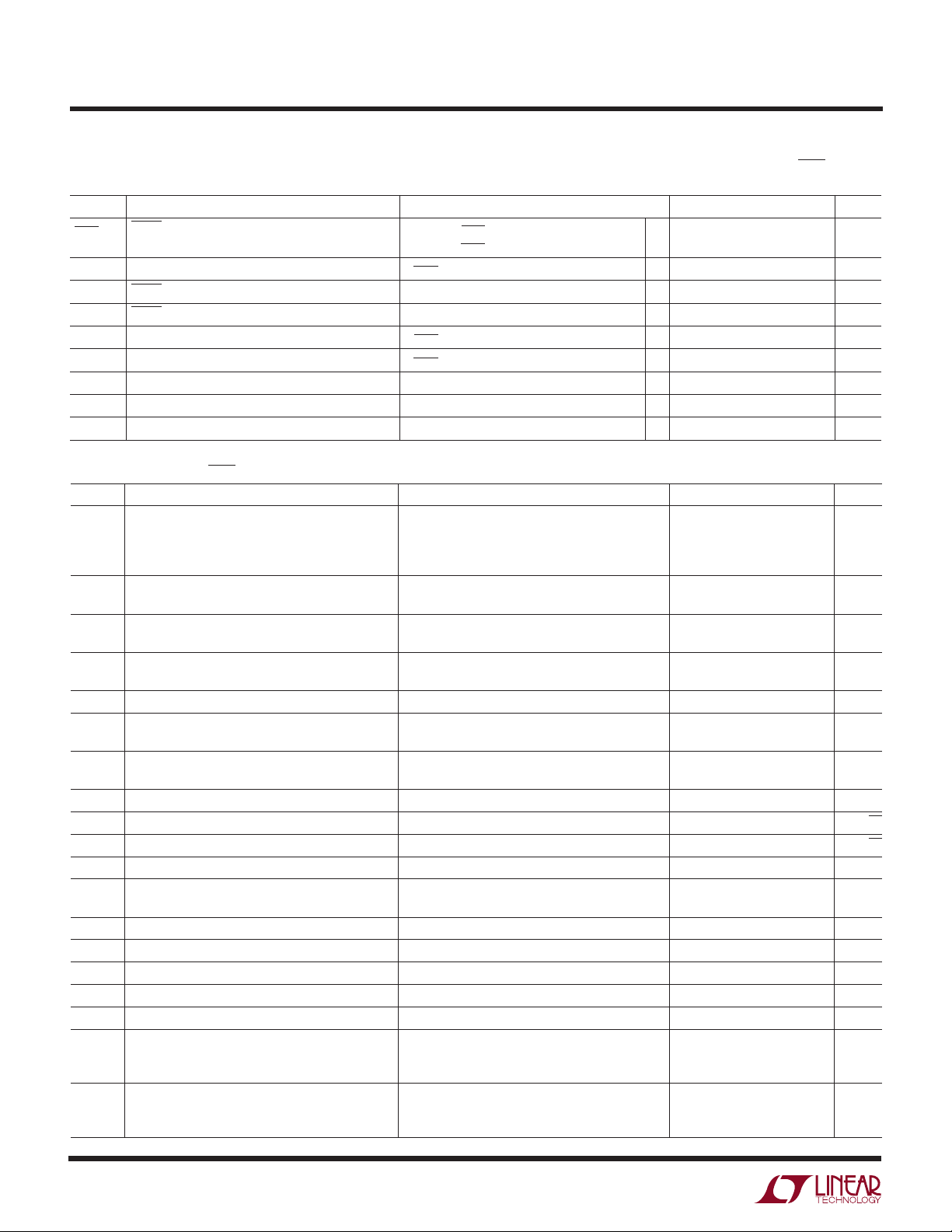

ELECTRICAL CHARACTERISTICS

temperature range. VS = 5V, 0V; VS = 3V, 0V; V

SHDN

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C

= open; VCM = V

= half supply, unless otherwise noted.

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

VOS TC Input Offset Voltage Drift (Note 8) VCM = V

∆V

Input Offset Voltage VCM = V+ LT1809 SO-8 ● 1 3.0 mV

Input Offset Voltage Shift VCM = V

OS

Input Offset Voltage Match (Channel-to-Channel) VCM = V–, VCM = V

VCM = V

VCM = V

VCM = V

VCM = V

VCM = V

–

LT1809 SO-8 ● 1 3.0 mV

+

–

+

–

–

+

to V

LT1809 SO-8 ● 0.5 2.5 mV

–

+

to V

+

● 1 3.5 mV

● 1 3.5 mV

● 925µV/°C

● 925µV/°C

● 0.5 3.0 mV

● 1.2 6.5 mV

(Note 10)

I

B

∆I

B

I

OS

∆I

OS

A

VOL

CMRR Common Mode Rejection Ratio VS = 5V, VCM = V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, V

Input Bias Current VCM = V+ – 0.2V ● 210 µA

Input Bias Current Shift VCM = V

Input Bias Current Match (Channel-to-Channel) VCM = V+ – 0.2V ● 0.1 5 µA

(Note 10) VCM = V

Input Offset Current VCM = V+ – 0.2V ● 0.05 1.5 µA

Input Offset Current Shift VCM = V

VCM = V

VCM = V

–

+ 0.4V ● –30 –14 µA

–

+ 0.4V to V+ – 0.2V ● 16 40 µA

–

+ 0.4V ● 0.5 10 µA

–

+ 0.4V ● 0.40 4.5 µA

–

+ 0.4V to V+ – 0.2V ● 0.45 6 µA

Large-Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k to VS/2 ● 20 75 V/mV

= 5V, VO = 1V to 4V, RL = 100Ω to VS/2 ● 3.5 8.5 V/mV

V

S

V

= 3V, VO = 0.5V to 2.5V, RL = 1k to VS/2 ● 12 40 V/mV

S

VS = 3V, VCM = V

CMRR Match (Channel-to-Channel) (Note 10) VS = 5V, VCM = V–, VCM = V

VS = 3V, VCM = V–, VCM = V

Input Common Mode Range ● V

PSRR Match (Channel-to-Channel) (Note 10) VS = 2.5V to 10V, V

–

+

to V

–

+

to V

+

+

= 0V ● 70 83 dB

CM

= 0V ● 64 83 dB

CM

● 64 80 dB

● 60 75 dB

● 58 80 dB

● 54 75 dB

–

+

V

Minimum Supply Voltage (Note 6) ● 2.3 2.5 V

V

OL

V

OH

I

SC

Output Voltage Swing LOW (Note 7) No Load ● 12 60 mV

I

= 5mA ● 55 140 mV

SINK

I

= 25mA ● 200 400 mV

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 50 120 mV

I

= 5mA ● 110 220 mV

SOURCE

I

= 25mA ● 370 700 mV

SOURCE

Short-Circuit Current VS = 5V ● ±40 ±75 mA

VS = 3V ● ±30 ±65 mA

I

S

I

SHDN

V

L

V

H

Supply Current per Amplifier ● 15 20 mA

Supply Current, Shutdown VS = 5V, V

VS = 3V, V

SHDN Pin Current VS = 5V, V

VS = 3V, V

Output Leakage Current, Shutdown V

= 0.3V ● 2 µA

SHDN

= 0.3V ● 0.58 1.4 mA

SHDN

= 0.3V ● 0.35 1.1 mA

SHDN

= 0.3V ● 420 850 µA

SHDN

= 0.3V ● 220 550 µA

SHDN

SHDN Pin Input Voltage Low ● 0.3 V

SHDN Pin Input Voltage High ● VS – 0.5 V

V

4

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

temperature range. VS = 5V, 0V; VS = 3V, 0V; V

SHDN

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C

= open; VCM = V

= half supply, unless otherwise noted.

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

t

t

ON

OFF

Turn-On Time V

Turn-Off Time V

= 0.3V to 4.5V, RL = 100 ● 80 ns

SHDN

= 4.5V to 0.3V, RL = 100 ● 50 ns

SHDN

GBW Gain-Bandwidth Product Frequency = 2MHz ● 145 MHz

SR Slew Rate VS = 5V, AV = –1, RL = 1k, VO = 4V

FPBW Full Power Bandwidth VS = 5V, V

OUT

= 4V

P-P

P-P

The ● denotes the specifications which apply over the – 40°C ≤ TA ≤ 85°C temperature range. V

VCM = V

= half supply, unless otherwise noted. (Note 5)

OUT

● 250 V/µs

● 20 MHz

= 5V, 0V; VS = 3V, 0V; V

S

SHDN

= open;

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

VOS TC Input Offset Voltage Drift (Note 8) VCM = V

∆V

Input Offset Voltage VCM = V+ LT1809 SO-8 ● 1 3.5 mV

= V– LT1809 SO-8 ● 1 3.5 mV

V

CM

+

VCM = V

–

= V

V

CM

+

–

VCM = V

Input Offset Voltage Shift VCM = V– to V+ LT1809 SO-8 ● 0.5 3.0 mV

OS

Input Offset Voltage Match (Channel-to-Channel) VCM = V+, VCM = V

–

= V

V

CM

–

● 1 4.0 mV

● 1 4.0 mV

● 925µV/°C

● 925µV/°C

● 0.5 3.5 mV

● 1.2 7 mV

(Note 10)

I

B

∆I

B

Input Bias Current VCM = V+ – 0.2V ● 212 µA

= V– + 0.4V ● –35 –17 µA

V

CM

Input Bias Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 19 47 µA

Input Bias Current Match (Channel-to-Channel) VCM = V+ – 0.2V ● 0.2 6 µA

(Note 10) V

I

OS

Input Offset Current VCM = V+ – 0.2V ● 0.08 2 µA

= V– + 0.4V ● 0.6 12 µA

CM

VCM = V– + 0.4V ● 0.5 6 µA

∆I

OS

A

VOL

CMRR Common Mode Rejection Ratio VS = 5V, VCM = V– to V

Input Offset Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 0.58 7.5 µA

Large-Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k to VS/2 ● 17 60 V/mV

= 5V, VO = 1V to 4V, RL = 100Ω to VS/2 ● 2.5 7 V/mV

V

S

= 3V, VO = 0.5V to 2.5V, RL = 1k to VS/2 ● 10 35 V/mV

V

S

= 3V, VCM = V– to V

V

S

CMRR Match (Channel-to-Channel) (Note 10) VS = 5V, VCM = V– to V

VS = 3V, VCM = V– to V

Input Common Mode Range ● V

+

+

+

+

● 63 80 dB

● 58 75 dB

● 57 78 dB

● 52 72 dB

–

+

V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, VCM = 0V ● 69 83 dB

PSRR Match (Channel-to-Channel) (Note 10) VS = 2.5V to 10V, VCM = 0V ● 63 83 dB

Minimum Supply Voltage (Note 6) ● 2.3 2.5 V

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 18 70 mV

= 5mA ● 60 150 mV

I

SINK

I

= 25mA ● 210 450 mV

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 55 130 mV

= 5mA ● 120 240 mV

I

SOURCE

I

= 25mA ● 375 750 mV

SOURCE

Short-Circuit Current VS = 5V ● ±30 ±70 mA

= 3V ● ±25 ±60 mA

V

S

Supply Current per Amplifier ● 15 21 mA

Supply Current, Shutdown VS = 5V, V

VS = 3V, V

= 0.3V ● 0.58 1.5 mA

SHDN

= 0.3V ● 0.35 1.2 mA

SHDN

V

5

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the –40°C ≤ TA ≤ 85°C temperature range. V

VCM = V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

SHDN

V

L

V

H

t

ON

t

OFF

GBW Gain-Bandwidth Product Frequency = 2MHz ● 140 MHz

SR Slew Rate VS = 5V, AV = -1, RL = 1k, VO = 4V

FPBW Full Power Bandwidth VS = 5V, V

T

= 25°C. VS = ±5V, V

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆V

OS

I

B

∆I

B

I

OS

∆I

OS

e

n

i

n

C

IN

A

VOL

CMRR Common Mode Rejection Ratio V

PSRR Power Supply Rejection Ratio V

V

OL

V

OH

= half supply, unless otherwise noted. (Note 5)

OUT

SHDN Pin Current VS = 5V, V

= 3V, V

V

S

Output Leakage Current, Shutdown V

= 0.3V ● 3 µA

SHDN

= 0.3V ● 420 900 µA

SHDN

= 0.3V ● 220 600 µA

SHDN

SHDN Pin Input Voltage Low ● 0.3 V

SHDN Pin Input Voltage High ● VS – 0.5 V

Turn-On Time V

Turn-Off Time V

= open, VCM = 0V, V

SHDN

= 0V, unless otherwise noted.

OUT

= 0.3V to 4.5V, RL = 100 ● 80 ns

SHDN

= 4.5V to 0.3V, RL = 100 ● 50 ns

SHDN

P-P

= 4V

OUT

P-P

Input Offset Voltage VCM = V+ LT1809 SO-8 0.8 3.0 mV

V

= V– LT1809 SO-8 0.8 3.0 mV

CM

+

V

= V

CM

–

V

= V

CM

Input Offset Voltage Shift VCM = V– to V+ LT1809 SO-8 0.35 2.5 mV

V

= V– to V

CM

Input Offset Voltage Match (Channel-to-Channel) VCM = V+, VCM = V

+

–

(Note 10)

Input Bias Current VCM = V

Input Bias Current Shift VCM = V– + 0.2V to V

Input Bias Current Match (Channel-to-Channel) VCM = V

(Note 10) V

Input Offset Current VCM = V

Input Offset Current Shift VCM = V– + 0.2V to V

+

V

= V– + 0.2V –30 –12.5 µA

CM

+

= V– + 0.2V 0.4 10 µA

CM

+

V

= V– + 0.2V 0.40 5 µA

CM

+

+

Input Noise Voltage Density f = 10kHz 16 nV/√Hz

Input Noise Current Density f = 10kHz 5 pA/√Hz

Input Capacitance f = 100kHz 2 pF

Large-Signal Voltage Gain VO = –4V to 4V, RL = 1k 30 100 V/mV

V

= –2.5V to 2.5V, RL = 100Ω 4.5 12 V/mV

CMRR Match (Channel-to-Channel) (Note 10) V

O

= V– to V

CM

= V– to V

CM

+

+

Input Common Mode Range V

+

= 2.5V to 10V, V– = 0V 71 87 dB

PSRR Match (Channel-to-Channel) (Note 10) V

+

= 2.5V to 10V, V– = 0V 65 90 dB

Output Voltage Swing LOW (Note 7) No Load 12 60 mV

I

= 5mA 50 140 mV

SINK

I

= 25mA 180 425 mV

SINK

Output Voltage Swing HIGH (Note 7) No Load 35 100 mV

I

= 5mA 90 200 mV

SOURCE

I

= 25mA 310 700 mV

SOURCE

= 5V, 0V; VS = 3V, 0V; V

S

● 180 V/µs

● 14 MHz

SHDN

= open;

0.8 3.5 mV

0.8 3.5 mV

0.35 3.0 mV

16 mV

210 µA

14.5 40 µA

0.1 5 µA

0.05 2 µA

0.45 7 µA

70 89 dB

64 89 dB

–

+

V

V

6

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

T

= 25°C. VS = ±5V, V

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

SC

I

S

Short-Circuit Current ±55 ±85 mA

Supply Current per Amplifier 15 20 mA

Supply Current, Shutdown V

I

SHDN

SHDN Pin Current V

Output Leakage Current, Shutdown V

V

V

t

t

L

H

ON

OFF

SHDN Pin Input Voltage Low 0.3 V

SHDN Pin Input Voltage High V+ – 0.5 V

Turn-On Time V

Turn-Off Time V

GBW Gain-Bandwidth Product Frequency = 2MHz 110 180 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, 175 350 V/µs

FPBW Full Power Bandwidth V

THD Total Harmonic Distortion AV = 1, RL = 1k, VO = 2V

t

S

Settling Time 0.1%, V

∆G Differential Gain (NTSC) AV = 2, RL = 150Ω 0.01 %

∆θ Differential Phase (NTSC) AV = 2, RL = 150Ω 0.01 Deg

= open, VCM = 0V, V

SHDN

= 0, unless otherwise noted.

OUT

= 0.3V 0.6 1.3 mA

SHDN

= 0.3V 420 750 µA

SHDN

= 0.3V 0.1 75 µA

SHDN

= 0.3V to 4.5V, RL = 100 80 ns

SHDN

= 4.5V to 0.3V, RL = 100 50 ns

SHDN

Measured at V

= 8V

OUT

= ±3V

O

P-P

= 8V, AV = –1, RL = 500Ω 34 ns

STEP

14 MHz

, fC = 5MHz –90 dB

P-P

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C temperature range. VS = ±5V, V

V

= 0V, unless otherwise noted.

OUT

= open, VCM = 0V,

SHDN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

VOS TC Input Offset Voltage Drift (Note 8) VCM = V

∆V

Input Offset Voltage VCM = V+ LT1809 SO-8 ● 1 3.25 mV

V

= V– LT1809 SO-8 ● 1 3.25 mV

CM

+

= V

V

CM

–

= V

V

CM

+

–

= V

V

CM

Input Offset Voltage Shift VCM = V– to V+ LT1809 SO-8 ● 0.5 2.75 mV

OS

Input Offset Voltage Match (Channel-to-Channel) VCM = V– to V

V

CM

= V– to V

+

+

● 1 3.75 mV

● 1 3.75 mV

● 10 25 µV/°C

● 10 25 µV/°C

● 0.5 3.25 mV

● 1.2 6.5 mV

(Note 10)

I

B

∆I

B

Input Bias Current VCM = V+ – 0.2V ● 2.5 12.5 µA

= V– + 0.4V ● –37.5 –15 µA

V

CM

Input Bias Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 17.5 50 µA

Input Bias Current Match (Channel-to-Channel) VCM = V+ – 0.2V ● 0.1 6 µA

(Note 10) V

I

∆I

A

OS

OS

VOL

Input Offset Current VCM = V+ – 0.2V ● 0.06 2.25 µA

Input Offset Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 0.56 8.25 µA

Large-Signal Voltage Gain VO = –4V to 4V, RL = 1k ● 27 80 V/mV

CMRR Common Mode Rejection Ratio V

CMRR Match (Channel-to-Channel) (Note 10) VCM = V– to V

Input Common Mode Range ● V

= V– + 0.4V ● 0.5 12 µA

CM

V

= V– + 0.4V ● 0.5 6 µA

CM

V

= –2.5V to 2.5V, RL = 100Ω ● 3.5 10 V/mV

O

= V– to V

CM

+

+

● 69 86 dB

● 63 86 dB

–

+

V

V

7

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

temperature range. V

= ±5V, V

S

= open, VCM = 0V, V

SHDN

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C

= 0V, unless otherwise noted.

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

PSRR Power Supply Rejection Ratio V

PSRR Match (Channel-to-Channel) (Note 10) V

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 20 80 mV

Output Voltage Swing HIGH (Note 7) No Load ● 60 140 mV

Short-Circuit Current ● ±45 ±75 mA

Supply Current per Amplifier ● 17.5 25 mA

Supply Current, Shutdown V

I

SHDN

SHDN Pin Current V

Output Leakage Current, Shutdown V

V

V

t

t

L

H

ON

OFF

SHDN Pin Input Voltage Low ● 0.3 V

SHDN Pin Input Voltage High ● V+ – 0.5 V

Turn-On Time V

Turn-Off Time V

+

= 2.5V to 10V, V– = 0V ● 70 83 dB

+

= 2.5V to 10V, V– = 0V ● 64 83 dB

I

= 5mA ● 50 160 mV

SINK

= 25mA ● 210 475 mV

I

SINK

= 5mA ● 120 240 mV

I

SOURCE

I

= 25mA ● 370 750 mV

SOURCE

= 0.3V ● 0.6 1.5 mA

SHDN

= 0.3V ● 420 850 µA

SHDN

= 0.3V ● 3 µA

SHDN

= 0.3V to 4.5V, RL = 100 ● 80 ns

SHDN

= 4.5V to 0.3V, RL = 100 ● 50 ns

SHDN

GBW Gain-Bandwidth Product Frequency = 2MHz ● 85 170 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, ● 140 300 V/µs

FPBW Full Power Bandwidth V

Measured at V

= 8V

OUT

P-P

= ±3V

O

● 12 MHz

The ● denotes the specifications which apply over the –40°C ≤ TA ≤ 85°C temperature range. VS = ±5V, V

V

= 0V, unless otherwise noted. (Note 5)

OUT

= open, VCM = 0V,

SHDN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

VOS TC Input Offset Voltage Drift (Note 8) VCM = V

∆V

Input Offset Voltage VCM = V+ LT1809 SO-8 ● 1 3.75 mV

V

= V– LT1809 SO-8 ● 1 3.75 mV

CM

+

= V

V

CM

–

= V

V

CM

+

–

V

= V

CM

Input Offset Voltage Shift VCM = V– to V+ LT1809 SO-8 ● 0.5 3.00 mV

OS

Input Offset Voltage Match (Channel-to-Channel) VCM = V– to V

V

CM

= V– to V

+

+

● 1 4.25 mV

● 1 4.25 mV

● 10 25 µV/°C

● 10 25 µV/°C

● 0.5 3.75 mV

● 1.2 7.5 mV

(Note 10)

I

B

∆I

B

Input Bias Current VCM = V+ – 0.2V ● 2.8 14 µA

= V– + 0.4V ● –45 –17 µA

V

CM

Input Bias Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 19.8 59 µA

Input Bias Current Match (Channel-to-Channel) VCM = V+ – 0.2V ● 0.1 7 µA

(Note 10) V

I

OS

∆I

OS

A

VOL

Input Offset Current VCM = V+ – 0.2V ● 0.08 2.5 µA

Input Offset Current Shift VCM = V– + 0.4V to V+ – 0.2V ● 0.68 10.5 µA

Large-Signal Voltage Gain VO = –4V to 4V, RL = 1k ● 22 70 V/mV

= V– + 0.4V ● 0.6 14 µA

CM

= V– + 0.4V ● 0.6 8 µA

V

CM

= –2.5V to 2.5V, RL = 100Ω ● 310 V/mV

V

O

8

LT1809/LT1810

ELECTRICAL CHARACTERISTICS

temperature range. V

= ±5V, V

S

= open, VCM = 0V, V

SHDN

The ● denotes the specifications which apply over the –40°C ≤ TA ≤ 85°C

= 0V, unless otherwise noted. (Note 5)

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

CMRR Common Mode Rejection Ratio V

CMRR Match (Channel-to-Channel) (Note 10) V

Input Common Mode Range ● V

PSRR Power Supply Rejection Ratio V

PSRR Match (Channel-to-Channel) (Note 10) V

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 23 100 mV

Output Voltage Swing HIGH (Note 7) No Load ● 75 160 mV

Short-Circuit Current ● ±30 ±75 mA

Supply Current per Amplifier ● 19 25 mA

Supply Current, Shutdown V

I

SHDN

SHDN Pin Current V

Output Leakage Current, Shutdown V

V

V

t

t

L

H

ON

OFF

SHDN Pin Input Voltage Low ● 0.3 V

SHDN Pin Input Voltage High ● V+ – 0.5 V

Turn-On Time V

Turn-Off Time V

= V– to V

CM

= V– to V

CM

+

= 2.5V to 10V, V– = 0V ● 69 83 dB

+

= 2.5V to 10V, V– = 0V ● 63 83 dB

= 5mA ● 60 170 mV

I

SINK

I

= 25mA ● 220 525 mV

SINK

I

SOURCE

I

SOURCE

SHDN

SHDN

SHDN

SHDN

SHDN

+

+

● 68 86 dB

● 62 86 dB

–

+

V

= 5mA ● 130 260 mV

= 25mA ● 375 775 mV

= 0.3V ● 0.65 1.6 mA

= 0.3V ● 420 900 µA

= 0.3V ● 4 µA

= 0.3V to 4.5V, RL = 100 ● 80 ns

= 4.5V to 0.3V, RL = 100 ● 50 ns

GBW Gain-Bandwidth Product Frequency = 2MHz ● 80 160 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, ● 110 220 V/µs

FPBW Full Power Bandwidth V

Measured at V

= 8V

OUT

P-P

= ±3V

O

● 8.5 MHz

V

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The inputs are protected by back-to-back diodes. If the differential

input voltage exceeds 1.4V, the input current should be limited to less than

10mA.

Note 3: A heat sink may be required to keep the junction temperature

below the absolute maximum rating when the output is shorted

indefinitely.

Note 4: The LT1809C/LT1809I and LT1810C/LT1810I are guaranteed

functional over the operating temperature range of –40°C and 85°C.

Note 5: The LT1809C/LT1810C are guaranteed to meet specified

performance from 0°C to 70°C. The LT1809C/LT1810C are designed,

characterized and expected to meet specified performance from –40°C

to 85°C but are not tested or QA sampled at these temperatures. The

LT1809I/LT1810I are guaranteed to meet specified performance from

–40°C to 85°C.

Note 6: Minimum supply voltage is guaranteed by power supply rejection

ratio test.

Note 7: Output voltage swings are measured between the output and

power supply rails.

Note 8: This parameter is not 100% tested.

Note 9: Thermal resistance varies depending upon the amount of PC board

metal attached to the V

amount of 2oz of copper metal trace connecting to the V

–

pin of the device. θJA is specified for a certain

–

pin as described

in the thermal resistance tables in the Applications Information section.

Note 10: Matching parameters are the difference between the two

amplifiers of the LT1810.

9

LT1809/LT1810

LOAD CURRENT (mA)

0.01

0.001

OUTPUT HIGH SATURATION VOLTAGE (V)

0.1

10

1100.1 100

1809 G09

0.01

1

VS = 5V, 0V

TA = 125°C

TA = –55°C

TA = 25°C

COMMON MODE VOLTAGE (V)

–1

INPUT BIAS CURRENT (µA)

5

2

1809 G06

–10

–20

01 3

–25

–30

10

0

–5

–15

456

VS = 5V, 0V

TA = –55°C

TA = –55°C

TA = 25°C

TA = 25°C

TA = 125°C

TA = 125°C

UW

TYPICAL PERFOR A CE CHARACTERISTICS

VOS Distribution, VCM = 0V

(PNP Stage)

50

VS = 5V, 0V

40

30

20

PERCENT OF UNITS (%)

10

0

–3

–1 0 1

–2

INPUT OFFSET VOLTAGE (mV)

Supply Current vs Supply Voltage

25

20

15

10

SUPPLY CURRENT (mA)

5

TA = 125°C

TA = 25°C

TA = –55°C

23

1809 G01

VOS Distribution, VCM = 5V

(NPN Stage)

50

VS = 5V, 0V

40

30

20

PERCENT OF UNITS (%)

10

0

–3

–1 0 1

–2

INPUT OFFSET VOLTAGE (mV)

Offset Voltage

vs Input Common Mode

2.0

1.5

1.0

0.5

0

–0.5

OFFSET VOLTAGE (mV)

–1.0

TA = 125°C

TA = 25°C

TA = –55°C

23

1809 G02

VS = 5V, 0V

TYPICAL PART

∆V

Shift for VCM = 0V to 5V

OS

25

VS = 5V, 0V

20

15

10

PERCENT OF UNITS (%)

5

0

–1

–0.75 –0.5 –0.25

INPUT OFFSET VOLTAGE (mV)

Input Bias Current

vs Common Mode Voltage

0 0.25

0.5 0.75 1

1809 G03

0

2

3

19

0

TOTAL SUPPLY VOLTAGE (V)

Input Bias Current vs Temperature

5

VS = 5V, 0V

3

1

–1

–3

–5

–7

–9

INPUT BIAS CURRENT (µA)

–11

–13

–15

10

–35 –5

–50

–20

TEMPERATURE (°C)

6

4

VCM = 5V

VCM = 0V

10

7

5

25 85

40

8

10

1809 G04

55

70

1809 G07

–1.5

10

1

0.1

0.01

OUTPUT LOW SATURATION VOLTAGE (V)

0.001

0.01

123 5

0

INPUT COMMON MODE VOLTAGE (V)

4

Output Saturation Voltage

vs Load Current (Output Low)

VS = 5V, 0V

TA = 125°C

TA = –55°C

TA = 25°C

1100.1 100

LOAD CURRENT (mA)

1809 G05

Output Saturation Voltage

vs Load Current (Output High)

1809 G08

UW

SHDN PIN VOLTAGE (V)

0

0

SUPPLY CURRENT (mA)

2

6

8

10

2

4

5

18

1809 G12

4

13

12

14

16

VS = 5V, 0V

TA = –55°C

T

A

= 25°C

T

A

= 125°C

TYPICAL PERFOR A CE CHARACTERISTICS

LT1809/LT1810

Supply Current

vs SHDN Pin Voltage

Minimum Supply Voltage

1.0

VCM = V– + 0.5V

0.8

0.6

0.4

0.2

TA = –55°C

0

–0.2

–0.4

–0.6

CHANGE IN OFFSET VOLTAGE (mV)

–0.8

–1.0

1.5

TA = 125°C

TA = 25°C

3.5

3.0

2.5

2.0

TOTAL SUPPLY VOLTAGE (V)

4.0

4.5

1809 G10

5.0

Output Short-Circuit Current

vs Power Supply Voltage

120

100

80

60

40

20

–20

–40

–60

–80

OUTPUT SHORT-CIRCUIT CURRENT (mA)

–100

TA = –55°C

TA = 125°C

0

TA = –55°C

TA = 25°C

1.5

2.5

2.0

POWER SUPPLY VOLTAGE (±V)

“SINKING”

“SOURCING”

3.5

3.0

TA = 25°C

TA = 125°C

4.0

4.5

5.0

1809 G11

SHDN Pin Current

vs SHDN Pin Voltage Open-Loop Gain Open-Loop Gain

SHDN PIN CURRENT (µA)

–50

–100

–150

–200

–250

–300

–350

–400

–450

50

0

0

VS = 5V, 0V

T

= –55°C

A

1

TA = 125°C

T

= 25°C

A

3

2

SHDN PIN VOLTAGE (V)

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

INPUT VOLTAGE (mV)

–1.5

–2.0

–2.5

0

4

5

1809 G13

0.5

1.5 2.0

1.0

OUTPUT VOLTAGE (V)

VS = 3V, 0V

RL = 1k

RL = 100Ω

2.5

3.0

1809 G14

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

INPUT VOLTAGE (mV)

–1.5

–2.0

–2.5

0

RL = 100Ω

1

2

OUTPUT VOLTAGE (V)

VS = 5V, 0V

R

= 1k

L

34

1809 G15

5

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

INPUT VOLTAGE (mV)

–1.5

–2.0

–2.5

–5

Open-Loop Gain

–3–4

–1–2

OUTPUT VOLTAGE (V)

R

RL = 100Ω

12 4

0

L

= 1k

VS = ±5V

3

1809 G16

Offset Voltage vs Output Current Warm-Up Drift vs Time (LT1809S8)

15

VS = ±5V

10

5

0

–5

OFFSET VOLTAGE (mV)

–10

5

–15

–60 –20 20 60

OUTPUT CURRENT (mA)

= 125°C

T

A

TA = –55°C

TA = 25°C

100–80–100 –40 0 40 80

1809 G17

180

TA = 25°C

160

140

120

100

80

60

40

CHANGE IN OFFSET VOLTAGE (µV)

20

0

0

40

20

TIME AFTER POWER UP (SEC)

= ±5V

V

S

VS = 5V, 0V

VS = 3V, 0V

80 100 120 140 160

60

1809 G18

11

LT1809/LT1810

TEMPERATURE (°C)

–55

SLEW RATE (V/µs)

400

25

1809 G25

250

150

–25 0 50

100

50

450

350

300

200

75 100 125

AV = 1

R

F

= RG = 1k

R

L

= 1k

RISING AND FALLING

SLEW RATE

VS = ±5V

VS = 5V, 0V

FREQUENCY (Hz)

–6

GAIN (dB)

12

15

–9

–12

9

0

6

3

–3

100k 10M 100M 500M

1809 G27

–15

1M

VS = 3V

AV = +2

VS = ±5V

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Input Noise Voltage vs Frequency

100

VS = 5V, 0V

90

80

70

60

50

NPN ACTIVE

V

= 4.5V

CM

V

= 2.5V

CM

1 10 100

FREQUENCY (kHz)

NOISE VOLTAGE (nV/√Hz)

40

30

PNP ACTIVE

20

10

0

0.1

1809 G19

Input Noise Current vs Frequency

20

VS = 5V, 0V

16

12

CURRENT NOISE (pA/√Hz)

8

4

0

0.1

NPN ACTIVE

= 4.5V

V

CM

1 10 100

FREQUENCY (kHz)

PNP ACTIVE

= 2.5V

V

CM

1809 G20

0.1Hz to 10Hz

Output Voltage Noise

10

8

6

4

2

0

–2

–4

OUTPUT VOLTAGE (µV/DIV)

–6

–8

–10

TIME (2 SEC/DIV)

1809 G21

Gain Bandwidth and Phase Margin

vs Supply Voltage

TA = 25°C

= 1k

R

L

PHASE MARGIN

190

185

180

175

GAIN BANDWIDTH (MHz)

170

165

160

GAIN BANDWIDTH

2

0

TOTAL SUPPLY VOLTAGE (V)

4

Gain and Phase vs Frequency

60

50

40

30

20

GAIN (dB)

10

0

–10

CL = 5pF

= 1k

R

L

–20

100k 10M 100M 1G

12

VS = 3V, 0V

VS = 3V, 0V

1M

FREQUENCY (Hz)

VS = ±5V

GAIN

6

PHASE

VS = ±5V

Gain Bandwidth and Phase Margin

vs Temperature

100

1809 G24

55

50

45

PHASE MARGIN (DEG)

40

35

30

125

55

25

VS = ±5V

VS = ±5V

VS = 3V, 0V

50

75

50

45

PHASE MARGIN (DEG)

40

35

GAIN BANDWIDTH (MHz)

8

10

1809 G23

200

190

180

170

160

150

–55

PHASE MARGIN

VS = 3V, 0V

GAIN BANDWIDTH

0

–25

TEMPERATURE (°C)

Slew Rate vs Temperature

Closed-Loop Gain vs Frequency Closed-Loop Gain vs Frequency

15

AV = +1

12

9

6

3

0

GAIN (dB)

–3

–6

–9

–12

–15

100k 10M 100M 500M

1M

FREQUENCY (Hz)

VS = 3V

VS = ±5V

1809 G26

1809 G22

100

80

60

PHASE (DEG)

40

20

0

–20

–40

–60

UW

FREQUENCY (MHz)

0.3

–70

DISTORTION (dB)

–60

–50

–40

11030

1809 G37

–80

–90

–100

–110

AV = +2

V

O

= 2V

P-P

VS = ±5V

RL = 100Ω, 2ND

RL = 100Ω, 3RD

RL = 1k, 3RD

RL = 1k, 2ND

TYPICAL PERFOR A CE CHARACTERISTICS

LT1809/LT1810

Output Impedance vs Frequency

600

VS = 5V, 0V

100

10

AV = 10

AV = 2

1

OUTPUT IMPEDANCE (Ω)

0.1

0.01

100k 1M 10M 100M 500M

AV = 1

FREQUENCY (Hz)

Series Output Resistor

vs Capacitive Load

40

VS = 5V, 0V

= +1

A

V

35

30

25

20

15

OVERSHOOT (%)

10

5

0

10

RS = 10Ω,

= ∞

R

L

RS = 20Ω, R

RL = RS = 50Ω

CAPACITIVE LOAD (pF)

= ∞

L

100 1000

1809 G28

1809 G32

Common Mode Rejection Ratio

vs Frequency

110

100

90

80

70

60

50

40

30

20

COMMON MODE REJECTION RATIO (dB)

10

100k 1M 10M 100M 500M

10k

FREQUENCY (Hz)

Series Output Resistor

vs Capacitive Load

50

VS = 5V, 0V

45

= +2

A

V

40

35

30

25

20

OVERSHOOT (%)

15

RL = RS = 50Ω

10

5

0

10

CAPACITIVE LOAD (pF)

RS = 20Ω

R

=

∞

L

100 1000

VS = 5V, 0V

1809 G30

RS = 10Ω

R

=

∞

L

1809 G33

Power Supply Rejection Ratio

vs Frequency

100

90

80

70

60

50

40

30

20

10

POWER SUPPLY REJECTION RATIO (dB)

0

1k 10k

NEGATIVE

SUPPLY

100k 1M 10M 100M

FREQUENCY (Hz)

0.01% Settling Time

INPUT SIGNAL

GENERATION

(2V/DIV)

OUTPUT

SETTLING

RESOLUTION

(2mV/DIV)

= ±5V 20ns/DIV 1809 G34

V

S

V

= ±4V

OUT

= –1

A

V

R

= 500Ω

L

tS = 110ns (SETTLING TIME)

VS = 5V, 0V

T

A

POSITIVE

SUPPLY

= 25°C

1809 G31

Distortion vs Frequency

–40

AV = +1

= 2V

V

P-P

O

–50

VS = ±5V

–60

–70

–80

DISTORTION (dB)

–90

–100

–110

0.3

RL = 100Ω, 2ND

RL = 100Ω, 3RD

11030

FREQUENCY (MHz)

RL = 1k, 3RD

RL = 1k, 2ND

1809 G35

Distortion vs Frequency

–40

AV = +1

V

= 2V

P-P

O

–50

VS = 5V

–60

–70

–80

DISTORTION (dB)

–90

–100

–110

0.3

RL = 1k, 2ND

RL = 100Ω, 2ND

RL = 100Ω, 3RD

11030

FREQUENCY (MHz)

Distortion vs Frequency

RL = 1k, 3RD

1809 G36

13

LT1809/LT1810

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Distortion vs Frequency

–40

AV = +2

V

= 2V

O

–50

VS = 5V

–60

–70

–80

DISTORTION (dB)

–90

–100

RL = 100Ω, 2ND

RL = 1k, 2ND

P-P

RL = 100Ω, 3RD

RL = 1k, 3RD

4.6

)

4.5

P-P

4.4

4.3

4.2

4.1

OUTPUT VOLTAGE SWING (V

4.0

Maximum Undistorted Output

Signal vs Frequency

VS = 5V

AV = –1

AV = +2

–110

0.3

11030

FREQUENCY (MHz)

1809 G38

3.9

0.1

±5V Large-Signal Response 5V Large-Signal Response±5V Small-Signal Response

VS = ±5V 10ns/DIV 1809 G40

AV = +1

= 1k

R

L

= ±5V 10ns/DIV 1809 G41

V

S

AV = +1

= 1k

R

L

5V Small-Signal Response Shutdown ResponseOutput Overdriven Recovery

V

IN

(1V/DIV)

0V

V

OUT

(2V/DIV)

0V

1 10 100

FREQUENCY (MHz)

= 5V 10ns/DIV 1809 G42

V

S

AV = +1

= 1k

R

L

V

SHDN

0V

V

OUT

0V

1809 G39

14

= 5V 10ns/DIV 1809 G43

V

S

AV = +1

= 1k

R

L

VS = 5V, 0V 100ns/DIV 1809 G44

AV = +2

V

= 5V, 0V 100ns/DIV 1809 G44

S

AV = +2

RL = 100Ω

WUUU

APPLICATIO S I FOR ATIO

LT1809/LT1810

Rail-to-Rail Characteristics

The LT1809/LT1810 have an input and output signal

range that includes both negative and positive power

supply. Figure 1 depicts a simplified schematic of the

amplifier. The input stage is comprised of two differential

amplifiers, a PNP stage Q1/Q2 and a NPN stage Q3/Q4

that are active over different ranges of common mode

input voltage. The PNP differential pair is active for

common mode voltages between the negative supply to

approximately 1.5V below the positive supply. As the

input voltage moves closer toward the positive supply,

the transistor Q5 will steer the tail current I1 to the current

mirror Q6/Q7, activating the NPN differential pair and

causing the PNP pair to become inactive for the rest of the

input common mode range up to the positive supply.

A pair of complementary common emitter stages

Q14/Q15 form the output stage, enabling the output to

swing from rail-to-rail. The capacitors C1 and C2 form the

local feedback loops that lower the output impedance at

high frequency. These devices are fabricated on Linear

Technology’s proprietary high speed complementary

bipolar process.

Power Dissipation

The LT1809/LT1810 amplifiers combine high speed with

large output current in a small package, so there is a need

to ensure that the die’s junction temperature does not

exceed 150°C. The LT1809 is housed in an SO-8 package

or a 6-lead SOT-23 package and the LT1810 is in an SO-8

or 8-lead MSOP package. All packages have the V– supply

pin fused to the lead frame to enhance the thermal conductance when connecting to a ground plane or a large metal

trace. Metal trace and plated through-holes can be used to

spread the heat generated by the device to the backside of

the PC board. For example, on a 3/32" FR-4 board with 2oz

copper, a total of 660 square millimeters connected to

Pin␣ 4 of LT1810 in an SO-8 package (330 square millimeters on each side of the PC board) will bring the thermal

resistance, θJA, to about 85°C/W. Without extra metal

trace connected to the V– pin to provide a heat sink, the

thermal resistance will be around 105°C/W. More information on thermal resistance for all packages with various

metal areas connecting to the V– pin is provided in Tables

1, 2 and 3 for thermal consideration.

SHDN

+

V

+

V

–

V

–

V

ESDD5

D9

ESDD6

R6

10k

R7

100k

Q16

Q17

BIAS

GENERATION

+IN

–IN

R3 R4 R5

–

+

V

V

ESDD2ESDD1

D6D7D8

D5

ESDD3ESDD4

–

+

V

V

D1

D2

Q4

Q7

Q5 V

Q3

Q6

BIAS

I

1

Q1

Q2

D3

D4

Q10

Q11

Q12

Q9

Q8

Q13 Q15

C

C

–

V

OUTPUT BIAS

R2R1

I

2

BUFFER

AND

C2

OUT

C1

Q14

1809 F01

Figure 1. LT1809 Simplified Schematic Diagram

15

LT1809/LT1810

WUUU

APPLICATIO S I FOR ATIO

Table 1. LT1809 6-Lead SOT-23 Package

COPPER AREA

TOPSIDE (mm

270 2500 135°C/W

100 2500 145°C/W

20 2500 160°C/W

0 2500 200°C/W

Device is mounted on topside.

Table 2. LT1809/LT1810 SO-8 Package

COPPER AREA

TOPSIDE BACKSIDE BOARD AREA THERMAL RESISTANCE

2

(mm

) (mm2) (mm2) (JUNCTION-TO-AMBIENT)

1100 1100 2500 65°C/W

330 330 2500 85°C/W

35 35 2500 95°C/W

35 0 2500 100°C/W

0 0 2500 105°C/W

Device is mounted on topside.

Table 3. LT1810 8-Lead MSOP Package

COPPER AREA

TOPSIDE BACKSIDE BOARD AREA THERMAL RESISTANCE

2

(mm

) (mm2) (mm2) (JUNCTION-TO-AMBIENT)

540 540 2500 110°C/W

100 100 2500 120°C/W

100 0 2500 130°C/W

30 0 2500 135°C/W

0 0 2500 140°C/W

Device is mounted on topside.

BOARD AREA THERMAL RESISTANCE

2

) (mm2) (JUNCTION-TO-AMBIENT)

Junction temperature TJ is calculated from the ambient

temperature TA and power dissipation PD as follows:

TJ = TA + (PD • θJA)

The power dissipation in the IC is the function of the supply

voltage, output voltage and the load resistance. For a given

supply voltage, the worst-case power dissipation P

D(MAX)

occurs at the maximum supply current with the output

voltage at half of either supply voltage (or the maximum

swing is less than 1/2 the supply voltage). P

D(MAX)

is given

by:

P

Example: An LT1810 in SO-8 mounted on a 2500mm

D(MAX)

= (VS • I

S(MAX)

) + (VS/2)2/R

L

2

area of PC board without any extra heat spreading plane

connected to its V– pin has a thermal resistance of

105°C/W, θJA. Operating on ±5V supplies with both

amplifiers simultaneously driving 50Ω loads, the worstcase power dissipation is given by:

P

D(MAX)

= 2 • (10 • 25mA) + 2 • (2.5)2/50

= 0.5 + 0.250 = 0.750W

The maximum ambient temperature that the part is allowed to operate is:

TA = TJ – (P

D(MAX)

• 105°C/W)

= 150°C – (0.750W • 105°C/W) = 71°C

To operate the device at higher ambient temperature,

connect more metal area to the V– pin to reduce the

thermal resistance of the package as indicated in Table 2.

Input Offset Voltage

The offset voltage will change depending upon which input

stage is active and the maximum offset voltage is guaranteed to be less than 3mV. The change of VOS over the entire

input common mode range (CMRR) is less than 2.5mV on

a single 5V and 3V supply.

Input Bias Current

The input bias current polarity depends upon a given input

common voltage at whichever input stage is operating.

When the PNP input stage is active, the input bias currents

flow out of the input pins and flow into the input pins when

the NPN input stage is activated. Because the input offset

current is less than the input bias current, matching the

source resistances at the input pin will reduce total offset

error.

Output

The LT1809/LT1810 can deliver a large output current,

so the short-circuit current limit is set around 90mA to

prevent damage to the device. Attention must be paid to

keep the junction temperature of the IC below the absolute maximum rating of 150°C (refer to the Power Dissipation section) when the output is continuously short

circuited. The output of the amplifier has reverse-biased

diodes connected to each supply. If the output is forced

16

WUUU

APPLICATIO S I FOR ATIO

LT1809/LT1810

beyond either supply, unlimited current will flow through

these diodes. If the current is transient and limited to

several hundred milliamps, no damage to the device will

occur.

Overdrive Protection

When the input voltage exceeds the power supplies, two

pairs of crossing diodes, D1 to D4, will prevent the output

from reversing polarity. If the input voltage exceeds either

power supply by 700mV, diodes D1/D2 or D3/D4 will turn

on, keeping the output at the proper polarity. For the

phase reversal protection to perform properly, the input

current must be limited to less than 5mA. If the amplifier

is severely overdriven, an external resistor should be used

to limit the overdrive current.

The LT1809/LT1810’s input stages are also protected

against differential input voltages of 1.4V or higher by

back-to-back diodes, D5/D8, that prevent the emitter-base

breakdown of the input transistors. The current in these

diodes should be limited to less than 10mA when they are

active. The worst-case differential input voltage usually

occurs when the input is driven while the output is shorted

to ground in a unity-gain configuration. In addition, the

amplifier is protected against ESD strikes up to 3kV on all

pins by a pair of protection diodes on each pin that are

connected to the power supplies as shown in Figure 1.

Capacitive Load

The LT1809/LT1810 is optimized for high bandwidth and

low distortion applications. It can drive a capacitive load

about 20pF in a unity-gain configuration and more with

higher gain. When driving a larger capacitive load, a

resistor of 10Ω to 50Ω should be connected between the

output and the capacitive load to avoid ringing or oscillation. The feedback should still be taken from the output so

that the resistor will isolate the capacitive load to ensure

stability. Graphs on capacitive loads indicate the transient

response of the amplifier when driving capacitive load with

a specified series resistor.

Feedback Components

When feedback resistors are used to set up gain, care must

be taken to ensure that the pole formed by the feedback

resistors and the total capacitance at the inverting input

does not degrade stability. For instance, the LT1809 in a

noninverting gain of 2, set up with two 1K resistors and a

capacitance of 3pF (device plus PC board), will probably

ring in transient response. The pole that is formed at

106MHz will reduce phase margin by 34 degrees when the

crossover frequency of the amplifier is around 70MHz. A

capacitor of 3pF or higher connected across the feedback

resistor will eliminate any ringing or oscillation.

SHDN Pin

The LT1809 has a SHDN pin to reduce the supply current

to less than 1.25mA. When the SHDN pin is pulled low, it

will generate a signal to power down the device. If the pin

is left unconnected, an internal pull-up resistor of 10k will

keep the part fully operating as shown in Figure 1. The

output will be high impedance during shutdown, and the

turn-on and turn-off time is less than 100ns. Because the

inputs are protected by a pair of back-to-back diodes, the

input signal will feed through to the output during shutdown mode if the amplitude of signal between the inputs

is larger than 1.4V.

17

LT1809/LT1810

TYPICAL APPLICATIO S

U

Driving A/D Converters

The LT1809/LT1810 have a 27ns settling time to 0.1% of

a 2V step signal and 20Ω output impedance at 100MHz

making it ideal for driving high speed A/D converters. With

the rail-to-rail input and output and low supply voltage

operation, the LT1809 is also desirable for single supply

applications. As shown in Figure 2, the LT1809 drives a

10Msps, 12-bit ADC, the LTC1420. The lowpass filter, R3

and C1, reduces the noise and distortion products that

might come from the input signal. High quality capacitors

5V

V

IN

1V

P-P

+

LT1809

–

–5V

R1

1k

R3

49.9Ω

R2

1k

and resistors, an NPO chip capacitor and metal-film surface mount resistors, should be used since these components can add to distortion. The voltage glitch of the

converter, due to its sampling nature, is buffered by the

LT1809 and the ability of the amplifier to settle it quickly

will affect the spurious-free dynamic range of the system.

Figure 2 to Figure 7 depict the LT1809 driving the LTC1420

at different configurations and voltage supplies. The FFT

responses show better than 90dB of SFDR for a ±5V

supply, and 80dB on a 5V single supply for the 1.394MHz

signal.

5V

C1

470pF

+A

IN

–A

LTC1420

PGA GAIN = 1

REF = 2.048V

IN

–5V

1809 F02

12 BITS

•

10Msps

•

•

Figure 2. Noninverting A/D Driver

0

–20

–40

–60

AMPLITUDE (dB)

–80

–100

–120

0

1234

FREQUENCY (MHz)

VS = ±5V

= +2

A

V

= 10Msps

f

SAMPLE

= 1.394MHz

f

IN

SFDR = 90dB

Figure 3. 4096 Point FFT Response

5

1809 F03

18

TYPICAL APPLICATIO S

LT1809/LT1810

U

V

IN

2V

P-P

ON 2.5V DC

0

–20

1k

1k

–

LT1809

+

5V

–5V

49.9Ω

470pF

+A

–A

PGA GAIN = 1

IN

REF = 2.048V

IN

5V

LTC1420

–5V

1809 F04

•

•

•

12 BITS

10Msps

–40

–60

AMPLITUDE (dB)

–80

–100

–120

0

1234

FREQUENCY (MHz)

VS = ±5V

= –1

A

V

= 10Msps

f

SAMPLE

= 1.394MHz

f

IN

SFDR = 90dB

5

1809 F05

Figure 4. Inverting A/D Driver Figure 5. 4096 Point FFT Response

0

–20

5V

3

2

1k

0.15µF

+

LT1809

–

5V

7

4

49.9Ω

6

1

470pF

1k

1

2

+A

IN

–A

LTC1420

PGA GAIN = 2

REF = 4.096V

IN

V

CM

3

1µF

1809 F06

•

•

•

12 BITS

10Msps

V

IN

1V

P-P

–40

–60

AMPLITUDE (dB)

–80

–100

–120

0

1234

FREQUENCY (MHz)

VS = 5V

= +2

A

V

= 10Msps

f

SAMPLE

= 1.394MHz

f

IN

SFDR = 80dB

5

1809 F07

Figure 6. Single Supply A/D Driver

Figure 7. 4096 Point FFT Response

19

LT1809/LT1810

TYPICAL APPLICATIO S

Single Supply Video Line Driver

U

The LT1809 is a wideband rail-to-rail op amp with a large

output current that allows it to drive video signals in low

supply applications. Figure 8 depicts a single supply video

line driver with AC coupling to minimize the quiescent

power dissipation. Resistors R1 and R2 are used to levelshift the input and output to provide the largest signal

swing. A gain of 2 is set up with R3 and R4 to restore the

signal at V

, which is attenuated by 6dB due to the

OUT

matching of the 75Ω line with the back-terminated

5V

C1

33µF

V

IN

R

T

75Ω

R1

5k

+

R2

5k

3

2

+

R3

1k

C2

150µF

+

LT1809

–

7

6

4

R4

1k

C4

3pF

resistor, R5. The back termination will eliminate any reflection of the signal that comes from the load. The input

termination resistor, RT, is optional—it is used only if

matching of the incoming line is necessary. The values of

C1, C2 and C3 are selected to minimize the droop of the

luminance signal. In some less stringent requirements,

the value of capacitors could be reduced. The –3dB bandwidth of the driver is about 95MHz on 5V supply and the

amount of peaking will vary upon the value of capacitor C4.

C3

1000µF

+

R5

75Ω

75Ω

COAX CABLE

R

LOAD

75Ω

1809 F08

V

OUT

Figure 8. 5V Single Supply Video Line Driver

5

VS = 5V

4

3

2

1

0

–1

–2

VOLTAGE GAIN (dB)

–3

–4

–5

0.2 10 100

1

FREQUENCY (MHz)

1809 F09

Figure 9. Video Line Driver Frequency Response

20

PACKAGE DESCRIPTIO

LT1809/LT1810

U

Dimensions in inches (millimeters) unless otherwise noted.

S6 Package

6-Lead Plastic SOT-23

(Reference LTC DWG # 05-08-1634)

(Reference LTC DWG # 05-08-1636)

2.80 – 3.10

(.110 – .118)

(NOTE 3)

SOT-23

(Original)

.90 – 1.45

A

(.035 – .057)

.00 – 0.15

A1

(.00 – .006)

.90 – 1.30

A2

(.035 – .051)

.35 – .55

L

(.014 – .021)

.20

(.008)

DATUM ‘A’

L

NOTE:

1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN

3. DRAWING NOT TO SCALE

4. DIMENSIONS ARE INCLUSIVE OF PLATING

5. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

6. MOLD FLASH SHALL NOT EXCEED .254mm

7. PACKAGE EIAJ REFERENCE IS:

SC-74A (EIAJ) FOR ORIGINAL

JEDEC MO-193 FOR THIN

SOT-23

(ThinSOT)

1.00 MAX

(.039 MAX)

.01 – .10

(.0004 – .004)

.80 – .90

(.031 – .035)

.30 – .50 REF

(.012 – .019 REF)

MILLIMETERS

(INCHES)

2.60 – 3.00

(.102 – .118)

.09 – .20

(.004 – .008)

(NOTE 2)

1.50 – 1.75

(.059 – .069)

(NOTE 3)

A

PIN ONE ID

.95

(.037)

REF

A2

1.90

(.074)

REF

.25 – .50

(.010 – .020)

(6PLCS, NOTE 2)

A1

S6 SOT-23 0401

21

LT1809/LT1810

PACKAGE DESCRIPTIO

U

Dimensions in inches (millimeters) unless otherwise noted.

MS8 Package

8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660)

0.118 ± 0.004*

(3.00 ± 0.102)

8

7

6

5

0.193 ± 0.006

(4.90 ± 0.15)

12

0.043

(1.10)

MAX

0.007

(0.18)

0.021

± 0.006

(0.53 ± 0.015)

* DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH,

PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

** DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

° – 6° TYP

0

SEATING

PLANE

0.009 – 0.015

(0.22 – 0.38)

0.0256

(0.65)

BSC

4

3

0.118 ± 0.004**

(3.00 ± 0.102)

0.034

(0.86)

REF

0.005

± 0.002

(0.13 ± 0.05)

MSOP (MS8) 1100

22

PACKAGE DESCRIPTIO

U

Dimensions in inches (millimeters) unless otherwise noted.

S8 Package

8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

0.189 – 0.197*

(4.801 – 5.004)

7

8

5

6

LT1809/LT1810

0.228 – 0.244

(5.791 – 6.197)

0.010 – 0.020

(0.254 – 0.508)

0.008 – 0.010

(0.203 – 0.254)

*

DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

**

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

× 45°

0°– 8° TYP

0.016 – 0.050

(0.406 – 1.270)

0.053 – 0.069

(1.346 – 1.752)

0.014 – 0.019

(0.355 – 0.483)

TYP

0.150 – 0.157**

(3.810 – 3.988)

1

3

2

4

0.004 – 0.010

(0.101 – 0.254)

0.050

(1.270)

BSC

SO8 1298

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

23

LT1809/LT1810

U

TYPICAL APPLICATIO

Single 3V Supply, 4MHz, 4th Order Butterworth Filter

Benefiting from a low voltage supply operation, low

distortion and rail-to-rail output of LT1809, a low distortion filter that is suitable for antialiasing can be built as

232Ω

47pF

232Ω

V

IN

Figure 10. Single 3V Supply, 4MHz, 4th Order Butterworth Filter

665Ω

220pF

–

1/2 LT1810

+

V

S

2

10

0

–10

–20

–30

–40

GAIN (dB)

–50

–60

–70

VS = 3V, 0V

–80

–90

= 2.5V

V

P-P

IN

10k 100k 1M 10M 100M

FREQUENCY (Hz)

shown Figure 10. On a 3V supply, the filter has a passband of 4MHz with 2.5V

signal and a stopband that is

P-P

greater than 70dB to frequency of 100MHz.

274Ω

22pF

274Ω

562Ω

470pF

1809 F11

–

1/2 LT1810

+

V

OUT

1809 F10

Figure 11. Filter Frequency Response

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LT1395 400MHz Current Feedback Amplifier 800V/µs Slew Rate, Shutdown

LT1632/LT1633 Dual/Quad 45MHz, 45V/µs Rail-to-Rail Input and Output Op Amps High DC Accuracy, 1.35mV V

Max Supply Current 5.2mA per Amplifier

LT1630/LT1631 Dual/Quad 30MHz, 10V/µs Rail-to-Rail Input and Output Op Amps High DC Accuracy, 525µV V

Max Supply Current 4.4mA per Amplifier

LT1806/LT1807 Single/Dual 325MHz, 140V/µs Rail-to-Rail High DC Accuracy, 550µV V

Input and Output Op Amps Low Distortion –80dBc at 5MHz

sn180910 180910fs LT/TP 1100 4K • PRINTED IN USA

24

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507 ● www.linear-tech.com

OS(MAX)

OS(MAX)

LINEAR TECHNOLOGY CORPORATION 2000

, 70mA Output Current,

OS(MAX)

, 70mA Output Current,

, Low Noise 3.5nV/√Hz,

Loading...

Loading...