Linear Technology LT1671CS8, LT1671CMS8, LT1671IS8 Datasheet

FEATURES

■

Low Power: 450µA

■

Fast: 60ns at 20mV Overdrive

85ns at 5mV Overdrive

■

Low Offset Voltage: 0.8mV

■

Operates Off Single 5V or Dual ±5V Supplies

■

Input Common Mode Extends to Negative Supply

■

No Minimum Input Slew Rate Requirement

■

Complementary TTL Outputs

■

Inputs Can Exceed Supplies without Phase Reversal

■

Pin Compatible with LT1394, LT1016 and LT1116

■

Output Latch Capability

■

Available in 8-Lead MSOP and SO Packages

U

APPLICATIO S

■

High Speed A/D Converters

■

Zero-Crossing Detectors

■

Current Sense for Switching Regulators

■

Extended Range V/F Coverters

■

Fast Pulse Height/Width Discriminators

■

High Speed Triggers

■

Line Receivers

■

High Speed Sampling Circuits

LT1671

60ns, Low Power,

Single Supply, Ground-Sensing

Comparator

U

DESCRIPTIO

The LT®1671 is a low power 60ns comparator with complementary outputs and latch. The input common mode

range extends from 1.5V below the positive supply down

to the negative supply rail. Like the LT1394, LT1016 and

LT1116, this comparator has complementary outputs

designed to interface directly to TTL or CMOS logic. The

LT1671 may operate from either a single 5V supply or dual

±5V supplies. Low offset voltage specifications and high

gain allow the LT1671 to be used in precision applications.

The LT1671 is designed for improved speed and stability

for a wide range of operating conditions. The output stage

provides active drive in both directions for maximum

speed into TTL, CMOS or passive loads with minimal

cross-conduction current. Unlike other fast comparators,

the LT1671 remains stable even for slow transitions

through the active region, which eliminates the need to

specify a minimum input slew rate.

The LT1671 has an internal, TTL/CMOS compatible latch

for retaining data at the outputs. The latch holds data as

long as the LATCH pin is held high. Device parameters

such as gain, offset and negative power supply current are

not significantly affected by variations in negative supply

voltage.

, LTC and LT are registered trademarks of Linear Technology Corporation.

TYPICAL APPLICATIO

1MHz Crystal Oscillator

5V

1MHz CRYSTAL

2k

2k

(AT-CUT)

+

LT1671

–

2k

0.068µF

U

OUTPUT

1671 TA01

1671 TA01

Propagation Delay vs Overdrive

140

120

100

80

TIME (ns)

60

40

20

0

FALLING EDGE (t

RISING EDGE (t

10 20 30 40

OVERDRIVE (mV)

VS = ±5V

= 100mV

V

STEP

= 25°C

T

A

= 1M

R

L

PDHL

PDLH

)

)

50

1671 TA02

1

LT1671

WW

W

ABSOLUTE MAXIMUM RATINGS

U

(Note 1)

Total Supply Voltage (V+ to V–) ............................... 12V

Positive Supply Voltage ............................................. 7V

Negative Supply Voltage .......................................... –7V

Differential Input Voltage ....................................... ±12V

Input and Latch Current (Note 2)........................±10mA

Output Current (Continuous)(Note 2) .................±20mA

U

W

PACKAGE/ORDER INFORMATION

ORDER PART

TOP VIEW

+

V

1

+IN

2

–IN

3

–

V

4

MS8 PACKAGE

8-LEAD PLASTIC MSOP

T

= 150°C, θJA = 250°C/W

JMAX

8

Q OUT

7

Q OUT

6

GND

5

LATCH

ENABLE

NUMBER

LT1671CMS8

MS8 PART MARKING

LTCT

Operating Temperature Range ................ –40°C to 85°C

Specified Temperature Range (Note 3)... –40°C to 85°C

Junction Temperature........................................... 150°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec.)................. 300°C

U

TOP VIEW

+

V

1

+IN

2

–IN

3

–

V

4

S8 PACKAGE

8-LEAD PLASTIC SO

T

= 150°C, θJA = 190°C/ W

JMAX

Q OUT

+

–

8

7

6

5

Q OUT

GND

LATCH

ENABLE

ORDER PART

NUMBER

LT1671CS8

LT1671IS8

S8 PART MARKING

1671

1671I

Consult factory for Military grade parts.

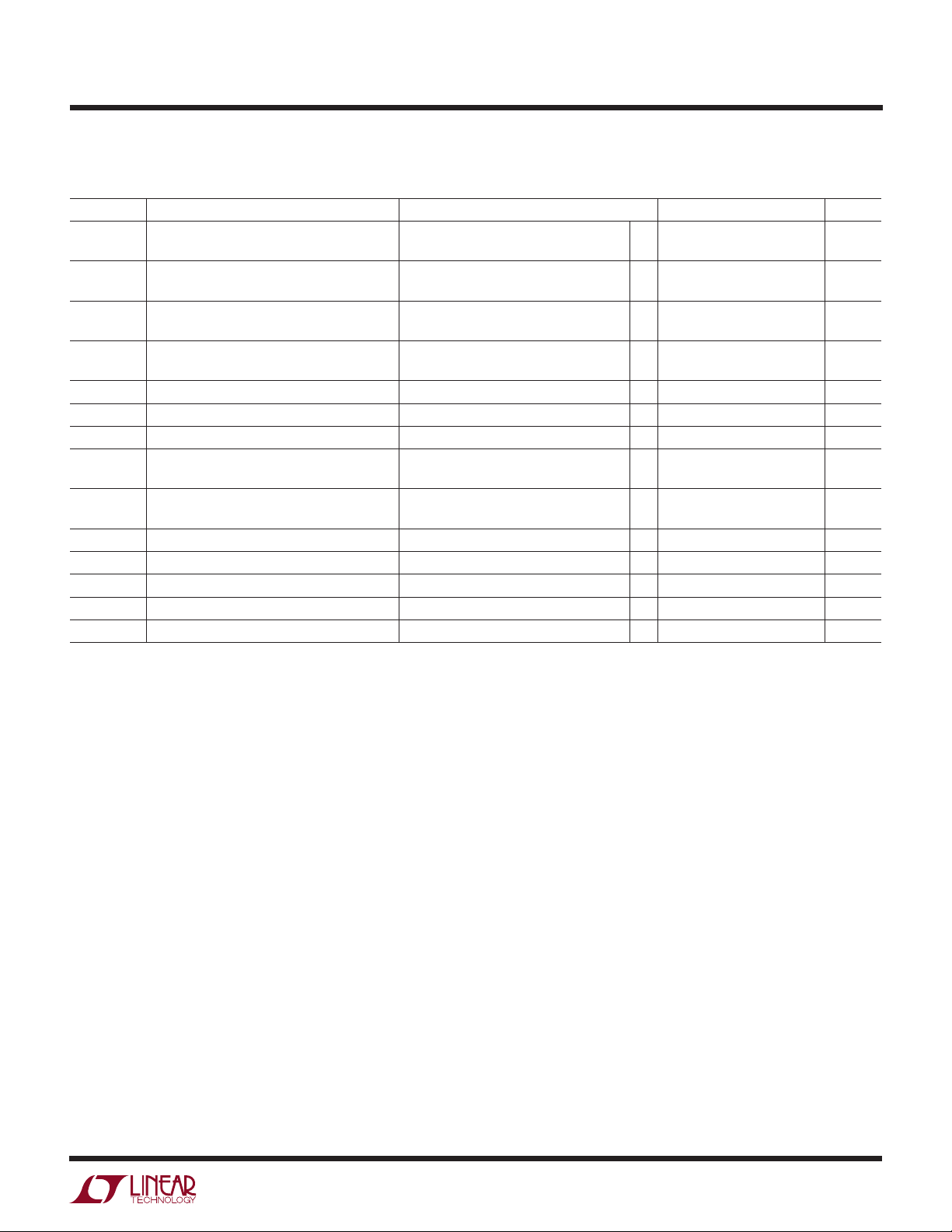

ELECTRICAL CHARACTERISTICS

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25°C.

V+ = 5V, V– = –5V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆V

OS

∆T

I

OS

I

B

V

CMR

CMRR Common Mode Rejection Ratio –5V ≤ VCM ≤ 3.5V, TA > 0°C 55 100 dB

PSRR Power Supply Rejection Ratio 4.6V ≤ V+ ≤ 5.4V ● 50 85 dB

A

V

Input Offset Voltage RS ≤ 100Ω (Note 4) 0.8 2.5 mV

Input Offset Voltage Drift ● 4 µV/°C

Input Offset Current 10 100 nA

Input Bias Current (Note 5) 120 280 nA

Input Voltage Range (Note 6) ● – 5 3.5 V

Small Signal Voltage Gain 1V ≤ V

(Q) = 1.4V, V

OUT

= VCM = 0V unless otherwise noted.

LATCH

Single 5V Supply

–5V ≤ V

Single 5V Supply

0V ≤ V

0V ≤ V

–7V ≤ V

≤ 3.3V, TA ≤ 0°C55 dB

CM

≤ 3.5V, TA > 0°C 55 100 dB

CM

≤ 3.3V, TA ≤ 0°C55 dB

CM

–

≤ –2V ● 60 90 dB

≤ 2V 2500 5000 V/V

OUT

● 4.0 mV

● 150 nA

● 350 nA

● 0 3.5 V

2

LT1671

ELECTRICAL CHARACTERISTICS

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25°C.

V+ = 5V, V– = –5V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OH

V

OL

+

I

–

I

V

IH

V

IL

I

IL

t

PD1

t

PD2

∆t

PD

t

LPD

t

SU

t

H

tPW(D) Minimum Disable Pulse Width 30 ns

Output Voltage Swing High V+ ≥ 4.6V, I

Output Voltage Swing Low I

Positive Supply Current 450 800 µA

Negative Supply Current 75 200 µA

LATCH Pin High Input Voltage ● 2V

LATCH Pin Low Input Voltage ● 0.8 V

LATCH Pin Current V

Propagation Delay ∆VIN = 100mV, VOD = 20mV 60 80 ns

Propagation Delay (Note 7) ∆VIN = 100mV, VOD = 5mV 85 100 ns

Differential Propagation Delay (Note 7) ∆VIN = 100mV, VOD = 5mV 15 30 ns

Latch Propagation Delay (Note 8) 60 ns

Latch Setup Time (Note 8) –15 ns

Latch Hold Time (Note 8) 35 ns

(Q) = 1.4V, V

OUT

= VCM = 0V unless otherwise noted.

LATCH

+

≥ 4.6V, I

V

OUT

I

OUT

LATCH

OUT

OUT

= –400µA ● 0.3 0.5 V

= –4mA 0.4 V

= 0V ● –1000 – 250 nA

= 400µA ● 2.7 3.1 V

= 4mA ● 2.4 3.0 V

● 1000 µA

● 250 µA

● 110 ns

● 130 ns

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: This parameter is guaranteed to meet specified performance

through design and characterization. It has not been tested.

Note 3: The LT1671CS8 and LT1671CMS8 are guaranteed to meet

specified performance from 0°C to 70°C and are designed, characterized

and expected to meet these extended temperature limits, but are not tested

at –40°C and 85°C. The LT1671IS8 is guaranteed to meet the extended

temperature limits.

Note 4: Input offset voltage (V

) is defined as the average of the two

OS

voltages measured by forcing first one output, then the other to 1.4V.

Note 5: Input bias current (I

) is defined as the average of the two input

B

currents.

Note 6: Input voltage range is guaranteed in part by CMRR testing and in

part by design and characterization.

Note 7: t

and ∆tPD cannot be measured in automatic handling

PD

equipment with low values of overdrive. The LT1671 is 100% tested with a

100mV step and 20mV overdrive. Correlation tests have shown that t

PD

and ∆tPD limits can be guaranteed with this test, if additional DC tests are

performed to guarantee that all internal bias conditions are correct.

Propagation delay (tPD) is measured with the overdrive added to the actual

. Differential propagation delay is defined as:

V

OS

∆tPD = t

Note 8: Latch propagation delay (t

respond when the LATCH pin is deasserted. Latch setup time (t

PDLH

– t

PDHL

) is the delay time for the output to

LPD

) is the

SU

interval in which the input signal must remain stable prior to asserting the

latch signal. Latch hold time (tH) is the interval after the latch is asserted in

which the input signal must remain stable.

3

LT1671

W

U

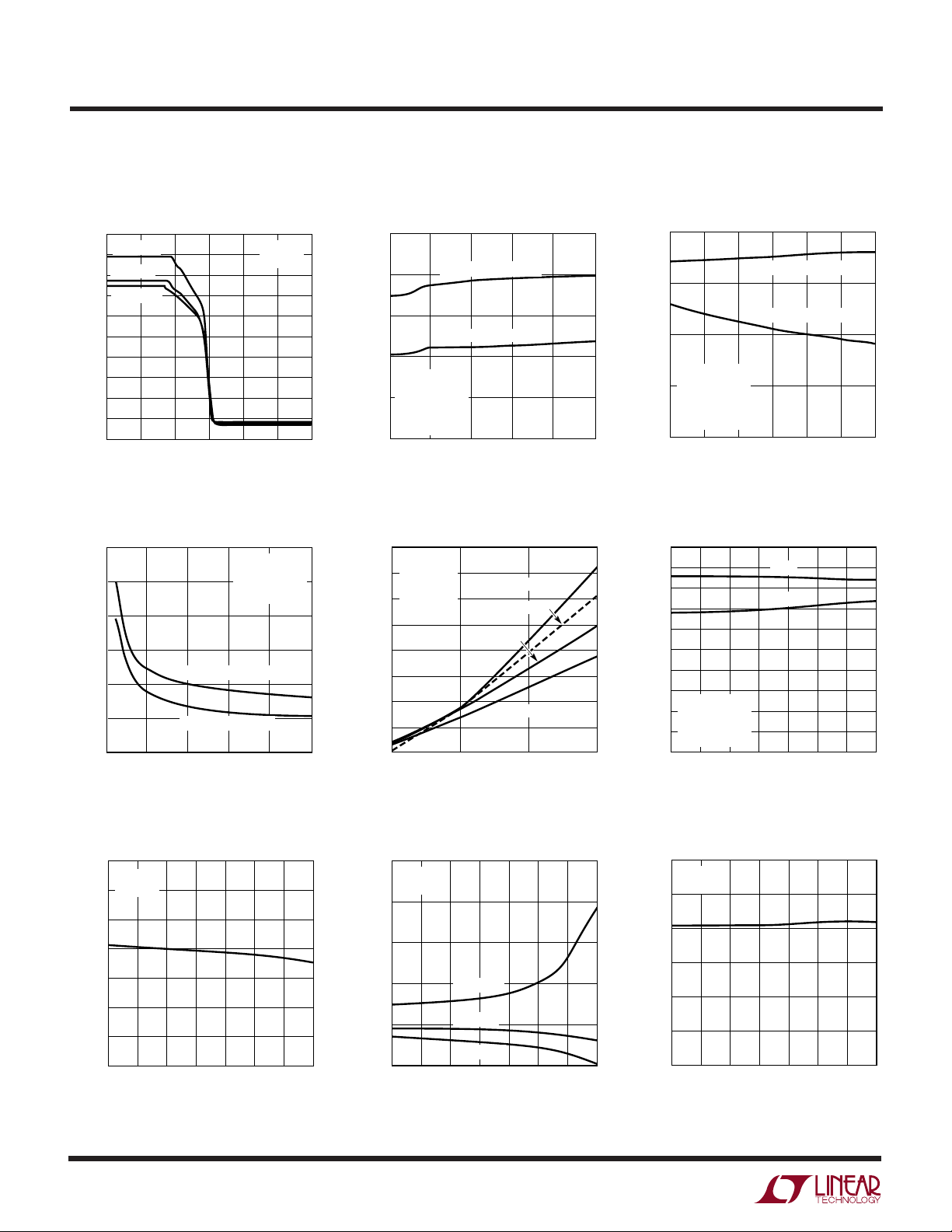

TYPICAL PERFORMANCE CHARACTERISTICS

Gain Characteristics

5.0

TA = 125°C

4.5

TA = 25°C

4.0

TA = –55°C

3.5

3.0

2.5

2.0

1.5

OUTPUT VOLTAGE (V)

1.0

0.5

0

–3 3

–1–2

DIFFERENTIAL INPUT VOLTAGE (mV)

1

0

Propagation Delay vs

Input Overdrive

140

120

100

80

TIME (ns)

60

40

20

0

FALLING EDGE (t

RISING EDGE (t

10 20 30 40

OVERDRIVE (mV)

VS = ±5V

V

STEP

= 25°C

T

A

= 1M

R

L

PDHL

PDLH

VS = ±5V

= 1M

R

L

2

1671 G01

= 100mV

)

)

1671 TA02

Propagation Delay vs

Load Capacitance

100

90

80

TIME (ns)

70

60

50

0

FALLING EDGE (t

RISING EDGE (t

VS = ±5V

= 100mV

V

STEP

= 5mV

V

OD

T

= 25°C

A

= 1M

R

L

10 20 30 40

OUTPUT LOAD CAPACITANCE (pF)

PDHL

PDLH

)

)

50

1671 G02

Propagation Delay vs

Source Resistance

200

VS = ±5V

= 1M

R

180

L

= 20mV

V

OD

= 25°C

T

160

A

140

120

TIME (ns)

100

80

60

40

50

0

SOURCE RESISTANCE (kΩ)

STEP SIZE = 800mV

400mV

200mV

STEP SIZE = 100mV

51015

1671 G05

Propagation Delay vs

Positive Supply Voltage

90

FALLING EDGE (t

80

70

TIME (ns)

V– = –5V

= 100mV

V

60

STEP

= 5mV

V

OD

= 25°C

T

A

= 1M

R

L

50

4.4

4.6 4.8 5.0 5.2 5.4

POSITIVE SUPPLY VOLTAGE (V)

Propagation Delay vs

Temperature

100

90

80

70

60

50

TIME (ns)

40

30

VS = ±5V

20

10

0

–50

V

V

R

STEP

OD

= 1M

L

–25

= 100mV

= 5mV

0

TEMPERATURE (°C)

RISING EDGE (t

t

PDHL

t

PDLH

50

25

75

PDHL

PDLH

)

)

100

5.6

1671 G03

125

1671 G06

Input Offset Voltage vs

Temperature

4

VS = ±5V

R

= 1M

L

3

2

1

0

VOLTAGE (mV)

–1

–2

–3

–50

–25

4

0

TEMPERATURE (°C)

50

25

Input Bias Current vs

Temperature

500

VS = ±5V

= 1M

R

L

400

300

200

INPUT BIAS CURRENT (nA)

100

100

125

1671 G07

75

0

–50

0

–25

TEMPERATURE (°C)

VCM = –5V

VCM = 0V

VCM = 3.5V

25

50

75

100

125

1671 G08

Positive Common Mode Limit vs

Temperature

6

VS = ±5V

R

= 1M

L

5

4

3

VOLTAGE (V)

2

1

0

–50

–25

0

TEMPERATURE (°C)

50

25

100

125

1671 G09

75

Loading...

Loading...