Page 1

( ) Preliminary Specification

(● ) Final Specification

LM230WF2

Liquid Crystal Display

Product Specification

SPECIFICATION

FOR

APPROVAL

23” Full HD TFT LCDTitle

BUYER

MODEL

APPROVED BY

/

/

/

Mitsubishi

SIGNATURE

DATE

SUPPLIER LG Display Co., Ltd.

*MODEL LM230WF2

SUFFIX SLA2

*When you obtain standard approval,

please use the above model name without suffix

APPROVED BY

J. H. Park / G.Manager

REVIEWED BY

D. I. Chung / Manager [C]

Y. H. Hwang / Manager [M]

G.T. Kim / Manager [P]

PREPARED BY

J.H. Oh / Engineer

SIGNATUR

E DATE

Please return 1 copy for your confirmation with

your signature and comments.

Ver. 1.0 Mar. 04. 2010

MNT Products Engineering Dept.

PDF created with pdfFactory Pro trial version www.pdffactory.com

LG Display Co., Ltd

1 / 34

Page 2

Product Specification

Contents

LM230WF2

Liquid Crystal Display

No ITEM

COVER

CONTENTS

RECORD OF REVISIONS

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATIONS

3-1 ELECTRICAL CHARACTREISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATIONS

3-4 SIGNAL TIMING WAVEFORMS

3-5 COLOR INPUT DATA REFERNECE

3-6 POWER SEQUENCE

3-7 V

4 OPTICAL SFECIFICATIONS

Power Dip Condition

LCD

Page

1

2

3

4

5

6

6

9

14

15

16

17

18

19

5 MECHANICAL CHARACTERISTICS

6 RELIABLITY

7 INTERNATIONAL STANDARDS

7-1 SAFETY

7-2 EMC

7-3 ENVIRONMENT

8 PACKING

8-1 DESIGNATION OF LOT MARK

8-2 PACKING FORM

9 PRECAUTIONS 31

25

28

29

29

29

29

30

30

30

Ver. 1.0 Mar. 04. 2010

2 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 3

Product Specification

RECORD OF REVISIONS

LM230WF2

Liquid Crystal Display

Revision

No

0.0 May. 22. 2009 - First Draft(Preliminary)

1.0 Mar. 04. 20 6,7,8 Update Electrical specification format

Revision Date Page Description

9,10 Update note of Interface connection

12 Delete LVDS 1port data format

14 Update Signal timing specification

15 Update Signal timing waveforms

18 Add V

19,20,21 Update optical specification

25 Update Mechanical characteristics

28 Update Environment test condition

29 Update International Standards

30,31,32 Update Packing form

33 Update operation precautions

- Final Specification

Power Dip condition

LCD

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

3 / 34

Page 4

LM230WF2

Liquid Crystal Display

Product Specification

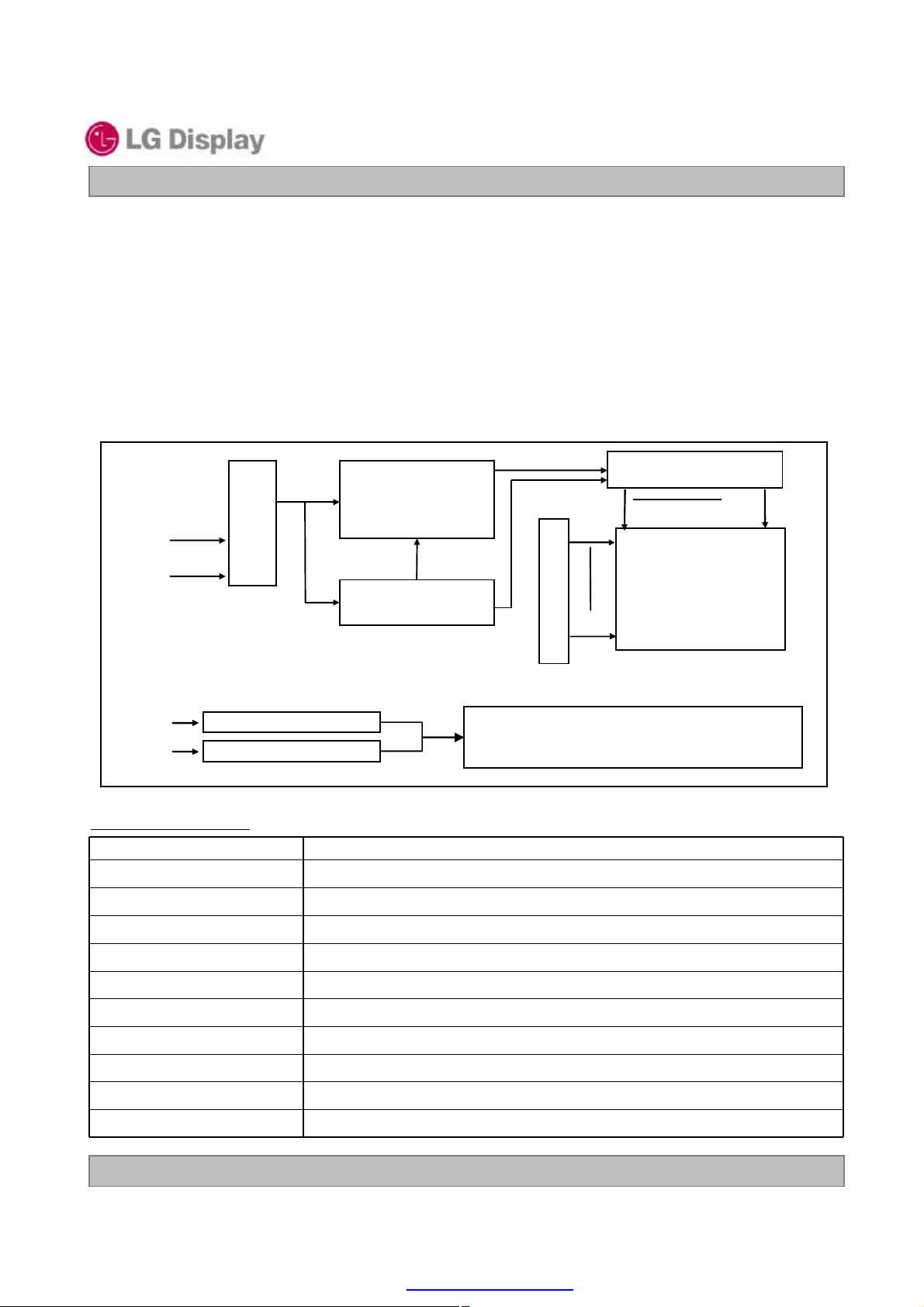

1. General Description

LM230WF2 is a Color Active Matrix Liquid Crystal Display with anintegral Cold Cathode Fluorescent

Lamp(CCFL) backlight system. The matrix employs a-Si Thin Film Transistor as the active element.

It is a transmissive type display operating in the normally black mode. It has a 23inch diagonally measured

active display area with WUXGA resolution (1080 vertical by 1920horizontal pixel array)

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the brightness of the sub-pixel color is determined with a 8-bit gray scale signal for each dot,

thus, presenting a palette of more than 16,7M(True) colors.

Ithas been designed to apply the 8Bit 2 port LVDS interface.

It is intended to support displays where high brightness, super wide viewing angle,

high color saturation, and high color are important.

RGB, Dclk, DE

Hsync, Vsync

(LVDS 2 port)

V

(+12V)

LCD

CN1

(30pin)

Timing Control

Block

Gate Driver circuit

Power Circuit Block

V

V

Lamp

Lamp

CN2, 3(2PIN)

Backlight Assembly(4 CCFL)

CN4, 5(2PIN)

General Features

Active Screen Size 23 inches(58.42cm) diagonal

Outline Dimension 533.2(H) x 312.0(V) x 17.0(D) mm(Typ.)

Pixel Pitch 0.265 mm x 0.265 mm

Source Driver Circuit

S1920S1

G1

TFT-LCD Panel

(1920 × 1080 pixels)

G1080

Pixel Format 1920 horiz. By 1080 vert. Pixels RGB stripes arrangement

Color Depth 8-bit, 16,777,216 colors

Luminance, White 300cd/m

2

( Center 1 points)

Viewing Angle(CR>10) View Angle Free (R/L 178(Typ.), U/D 178(Typ.))

Power Consumption Total 31.86 Watt (Typ.) ( 6.36 Watt @VLCD, 25.5 Watt @300cd/㎡])

Weight 3,000 g (Typ.)

Display Operating Mode Transmissive mode, normally black

Surface Treatment Hard coating(3H), Glare(Low Reflection treatment of the front polarizer)

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

4 / 34

Page 5

LM230WF2

Liquid Crystal Display

Product Specification

2. Absolute Maximum Ratings

The following are maximum values which, if exceeded, may cause faulty operation or damage to the unit.

Table 1. ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Power Input Voltage

Operating Temperature

Storage Temperature

Operating Ambient Humidity

Storage Humidity

VLCD -0.3 14 Vdc at 25 ± 2°C

TOP 0 50

TST -20 60

HOP 10 90 %RH

HST 10 90 %RH

Values

Units Notes

Min Max

°C

°C

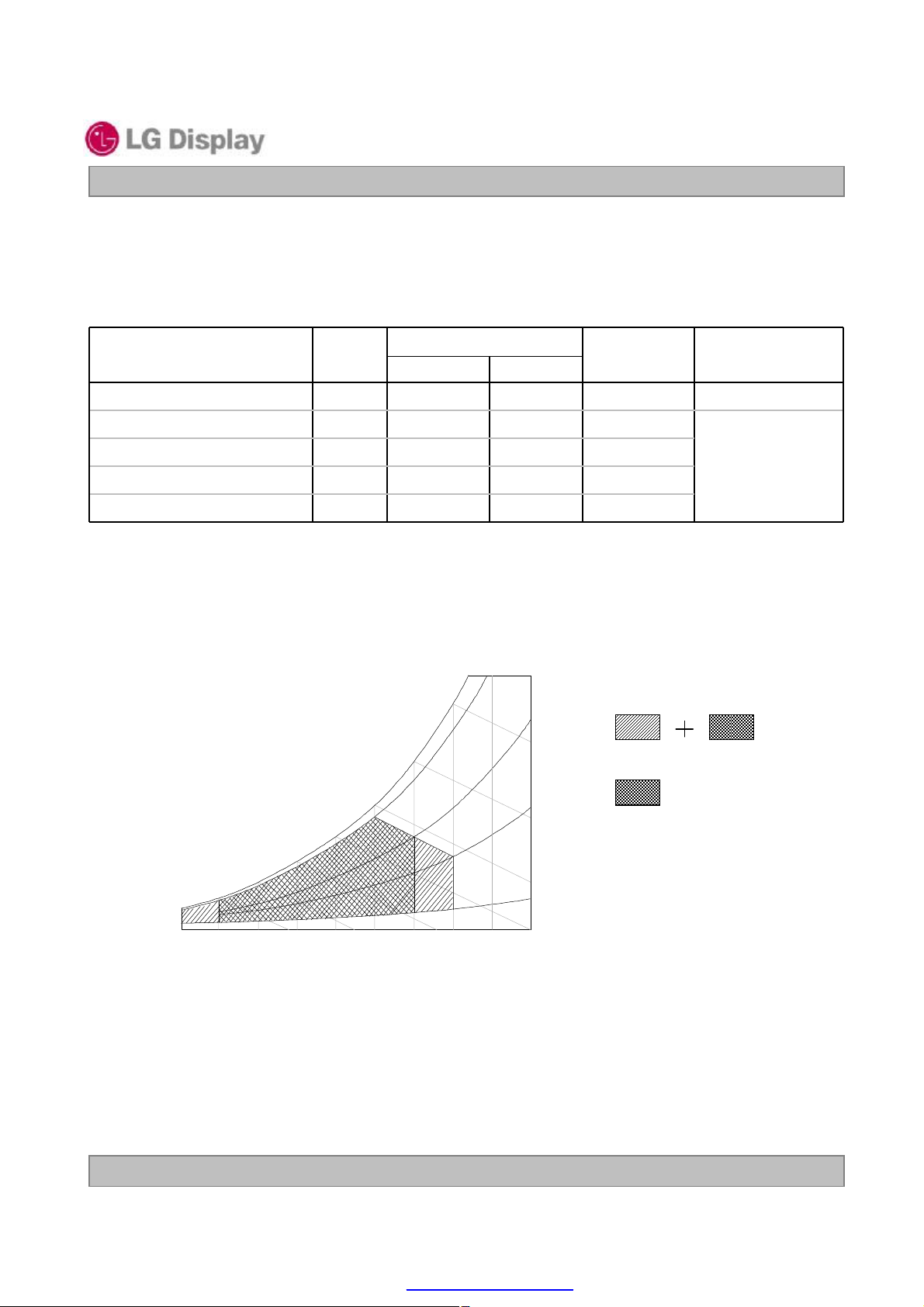

Note : 1. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be 39 °C Max, and no condensation of water.

Note : 2. Maximum Storage Humidity is up to 40℃, 70% RH only for 4 corner light leakage Mura.

90%

60

60%

Wet Bulb

Temperature [C]

10

0

20

30

40

50

40%

Humidity [(%)RH]

10%

Storage

Operation

1, 2

10 20 30 40 50 60 70 800-20

Dry Bulb Temperature [C]

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 / 34

Page 6

LM230WF2

Liquid Crystal Display

Product Specification

3. Electrical Specifications

3-1. Electrical Characteristics

It requires two power inputs. One is employed to power the LCD electronics and to drive the TFT array and

liquid crystal. The second input power for the CCFL, is typically generated by an inverter. The inverter is an

external unit to the LCDs.

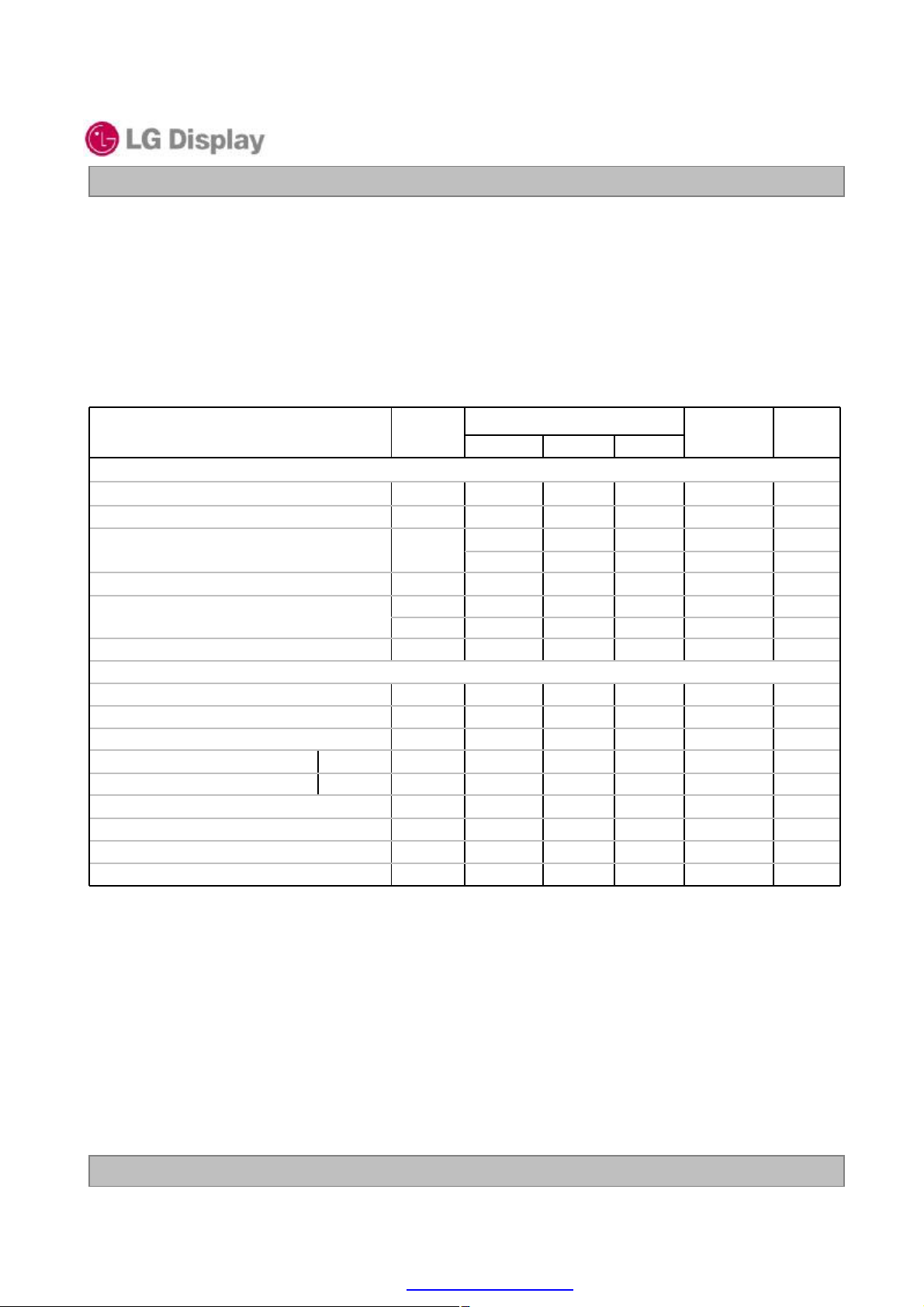

Table 2. ELECTRICAL CHARACTERISTICS

Parameter Symbol

MODULE :

Power Supply Input Voltage VLCD 11.4 12 12.6 Vdc

Permissive Power Input Ripple VRF - - 400 mV 13

Power Supply Input Current ILCD

Differential Impedance

Power Consumption

Rush current IRUSH - - 3 A 3

LAMP :

Operating Voltage VBL

Operating Current IBL

Established Starting Voltage Vs 4, 6

at 25 °C

at 0 °C

Operating Frequency fBL

Discharge Stabilization Time Ts

Power Consumption PBL

Life Time

Zm

PLCD - 6.63 7.32 Watt 1

PLCD - 8.54 9.83 Watt 2

Min Typ Max

- 530 610 mA 1

- 712 819 mA 2

- 100 110

830 850 1000

3.0 7.5 8.0

40 60 70

50,000

Values

25.5 28.1

1500

1800

3

Unit Notes

ohm

V

RMS

mA

RMS

V

RMS

V

RMS

kHz 7

Min 4, 8

Watt 9

Hrs 4, 10

4, 5

4

Note : The design of the inverter must have specifications for the lamp in LCD Assembly.

The performance of the Lamp in LCM, for example life time or brightness, is extremely influenced by

the characteristics of the DC-AC inverter. So all the parameters of an inverter should be carefully

designed so as not to produce too much leakage current fromhigh-voltage output of the inverter.

When you design or order the inverter, please make sure unwanted lighting caused by the mismatch

of the lamp and the inverter (no lighting, flicker, etc) never occurs. When you confirm it, the LCD–

Assembly should be operated in the same condition as installed in you instrument.

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

6 / 34

Page 7

LM230WF2

Liquid Crystal Display

Product Specification

Note. Do not attach a conducting tape to lamp connecting wire. If the lamp wire attach to a conducting tape,

TFT-LCD Module has a low luminance and the inverter has abnormal action. Because leakage current

is occurred between lamp wire and conducting tape.

1. The specified current and power consumption are under theV

whereas mosaic pattern(8 x 6) is displayed and fVis the frame frequency.

2. The current is specified at the maximum current pattern.See the figure 3.

3. The duration of rush current is about 5ms and rising timeof power Input is 500us ± 20%.(min.).

4. Specified values are for a single lamp.

5. Operating voltage is measured at 25 ± 2°C, and follows as below condition.

The variance of the voltage is ± 10%. (Based on single Lamp.)

The variance of the voltage is ± 20%. (Based on system & Test equipment tolerance.)

6. The voltage above VSshould be applied to the lamps for more than 1 second for start-up.

(Inverter open voltage must be more than lamp startingvoltage.)

Otherwise, the lamps may not be turned on. The used lamp current is the lamp typical current.

7. The output of the inverter must have symmetrical(negativeand positive) voltage waveform and

symmetrical current waveform (Unsymmetrical ratio is less than 10%). Please do not use the inverter

which has unsymmetrical voltage and unsymmetrical current and spike wave.

Lamp frequency may produce interface with horizontal synchronous frequency and as a result this may

cause beat on the display. Therefore lamp frequency shall be as away possible from the horizontal

synchronous frequency and from its harmonics in order to prevent interference.

8. Let’s define the brightness of the lamp after being lighted for 5 minutes as 100%.

TSis the time required for the brightness of the center of the lamp to be not less than 95%.

The used lamp current is the lamp typical current.

9. The lamp power consumption shown above does not include loss of external inverter.

The used lamp current is the lamp typical current. (PBL= VBLx IBLx N

10. The life is determined as the time at which brightness of the lamp is 50% compared to that of initial

value at the typical lamp current on condition of continuous operating at 25 ± 2°C.

11. Requirements for a system inverter design, which is intended to have a better display performance,

a better power efficiency and a more reliable lamp, are following.

It shall help increase the lamp lifetime and reduce leakagecurrent.

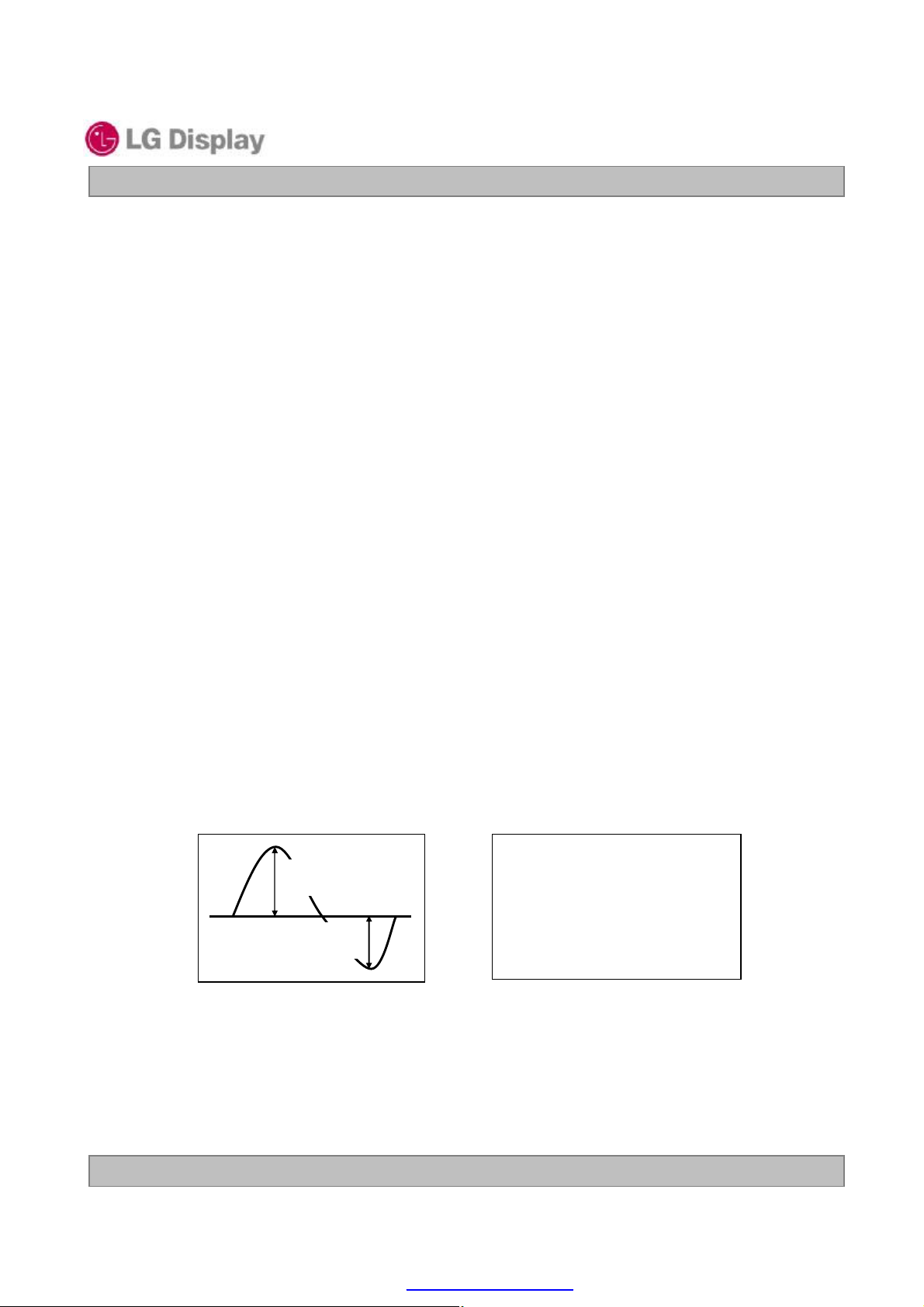

a. The asymmetry rate of the inverter waveform should be less than 10%.

b. The distortion rate of the waveform should be within √2 ±10%.

* Inverter output waveform had better be more similar to ideal sine wave.

=12V, 25 ± 2°C,fV=60Hz condition

LCD

)

Lamp

* Asymmetry rate:

I p

| I p– I –p| / I

* Distortion rate

I -p

I p(or I –p) / I

12. The inverter which is combined with this LCM, is highly recommended to connect coupling(ballast)

condenser at the high voltage output side. When you use the inverter which has not coupling(ballast)

condenser, it may cause abnormal lamp lighting becauseof biased mercury as time goes.

13. Permissive power ripple should be measured under V

=12.0V, 25°C, fV(frame frequency)=MAX

LCD

conditionand At that time, we recommend the bandwidth configuration of oscilloscope is to be under

20Mhz. See the figure 3.

14. In case of edgy type back light with over 4 parallel lamps, input current and voltage wave form should

be synchronized

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

rms

rms

x 100%

7 / 34

Page 8

Product Specification

LM230WF2

Liquid Crystal Display

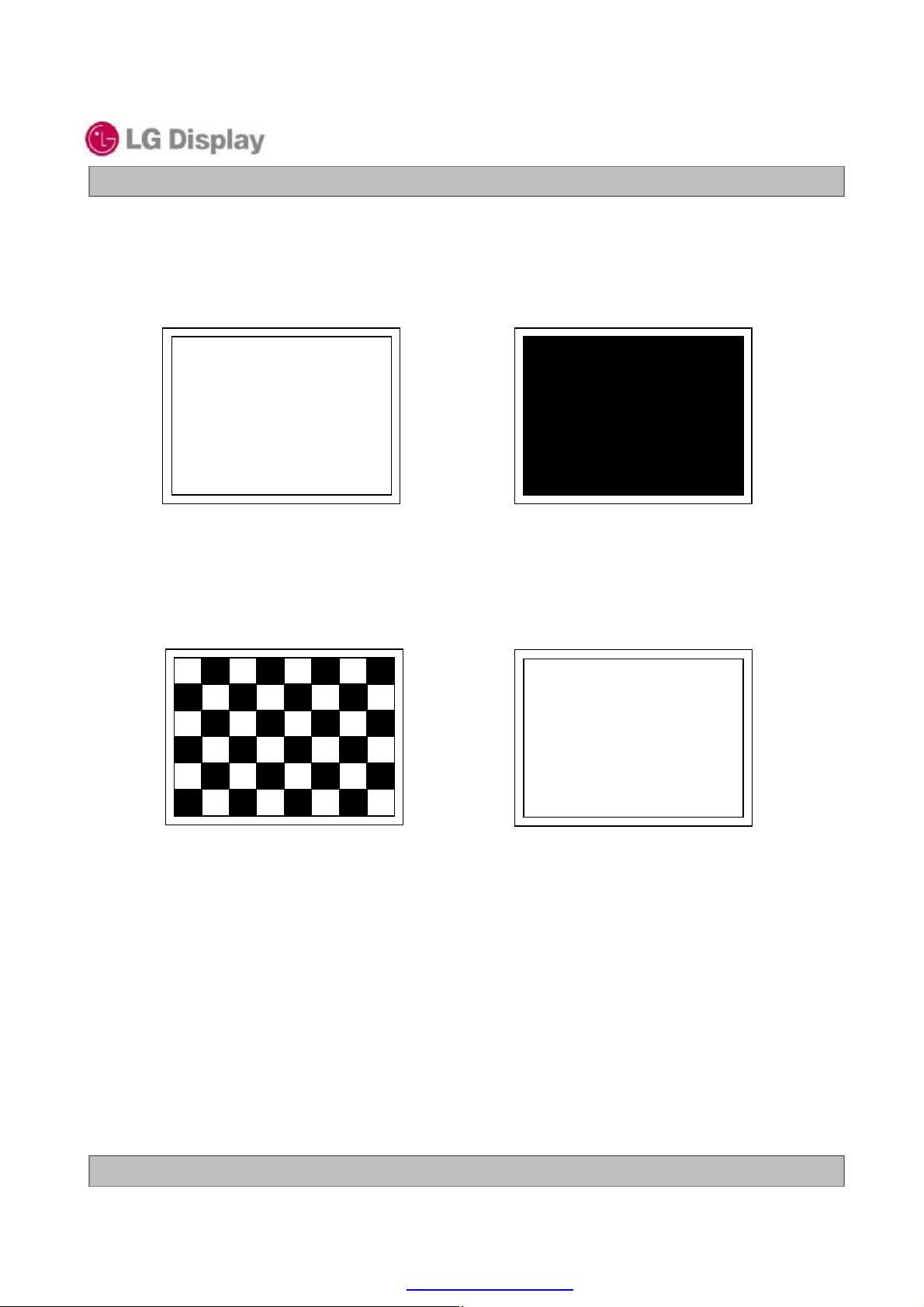

• Permissive Power input ripple (V

White pattern

• Power consumption (V

=12V, 25°C, fV (frame frequency=60Hz condition)

LCD

=12.0V, 25°C, fV(frame frequency)=MAX condition)

LCD

Black pattern

Typical power Pattern

Maximum power Pattern

[ Figure 3 ] Mosaic pattern & White Pattern for power consumption measurement

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

8 / 34

Page 9

Liquid Crystal Display

Product Specification

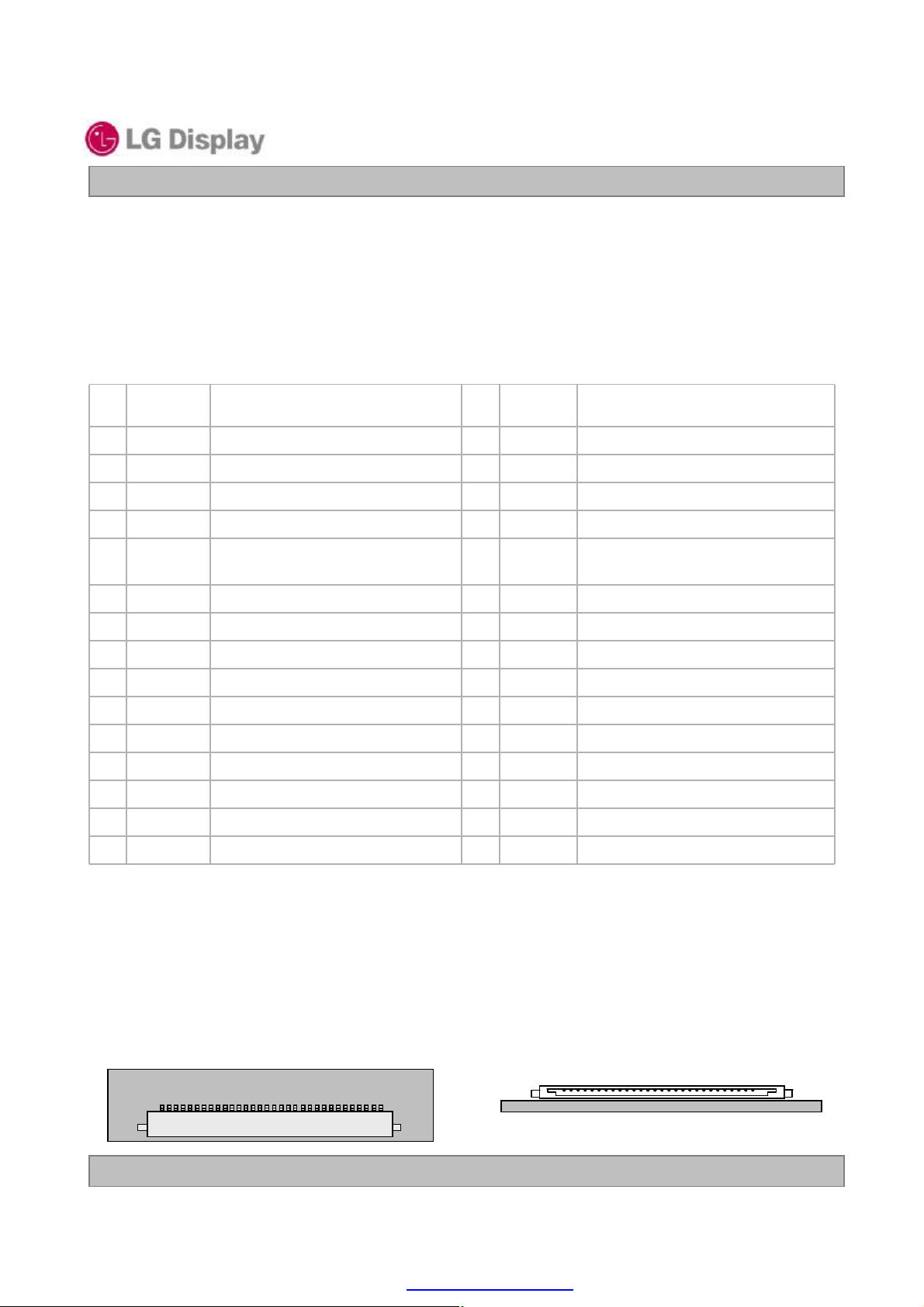

3-2. Interface Connections

3-2-1. LCD Module

-LCD Connector(CN1). : KDF71G-30S-1H, (Manufactured by Hirose ), IS100-L30B-C23(UJU)

-Mating Connector : FI-X30C2L (Manufactured by JAE) or Equivalent

Table 3 MODULE CONNECTOR(CN1) PIN CONFIGURATION

No Symbol Description No Symbol Symbol

LM230WF2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

FR0M

FR0P

FR1M

FR1P

FR2M

FR2P

GND

FCLKINM

FCLKINP

FR3M

FR3P

SR0M

SR0P

GND

SR1M

Minus signal of odd channel 0 (LVDS)

Plus signal of odd channel 0 (LVDS)

Minus signal of odd channel 1 (LVDS)

Plus signal of odd channel 1 (LVDS)

Minus signal of odd channel 2 (LVDS)

Plus signal of odd channel 2 (LVDS)

Ground

Minus signal of odd clock channel (LVDS)

Plus signal of odd clock channel (LVDS)

Minus signal of odd channel 3 (LVDS)

Plus signal of odd channel 3 (LVDS)

Minus signal of even channel 0 (LVDS)

Plus signal of even channel 0 (LVDS)

Ground

Minus signal of even channel 1 (LVDS)

16

SR1P

17

GND

18

SR2M

19

SR2P

SCLKIN

20

M

21

SCLKINP

22

SR3M

23

SR3P

24

GND

25

NC

26

NC

PWM_OUT For Control Burst frequency of Inverter

27

28

VLCD

29

VLCD

30

VLCD

Plus signal of even channel 1 (LVDS)

Ground

Minus signal of even channel 2 (LVDS)

Plus signal of even channel 2 (LVDS)

Minus signal of even clock channel (LVDS)

Plus signal of even clock channel (LVDS)

Minus signal of even channel 3 (LVDS)

Plus signal of even channel 3 (LVDS)

Ground

No Connection (I2C Serial interface for LCM)

No Connection.(I2C Serial interface for LCM)

Power Supply +12.0V

Power Supply +12.0V

Power Supply +12.0V

Note: 1. All GND(ground) pins should be connected together and to Vss which should also be connected to

the LCD’s metal frame.

2. All VLCD (power input) pins should be connected together.

3. Input Level of LVDS signal is based on the IEA 664Standard.

4. PWM_OUT signal controls the burst frequency of a inverter.

This signal is synchronized with vertical frequency.

It’s frequency is 3 times of vertical frequency, and it’s duty ratio is 50%.

If you don’t use this pin, it is no connection.

[ Figure 4 ] Connector diagram

KDF71G-30S-1H

#1 #30

#1 #30

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

Rear view of LCM

9 / 34

Page 10

Liquid Crystal Display

Product Specification

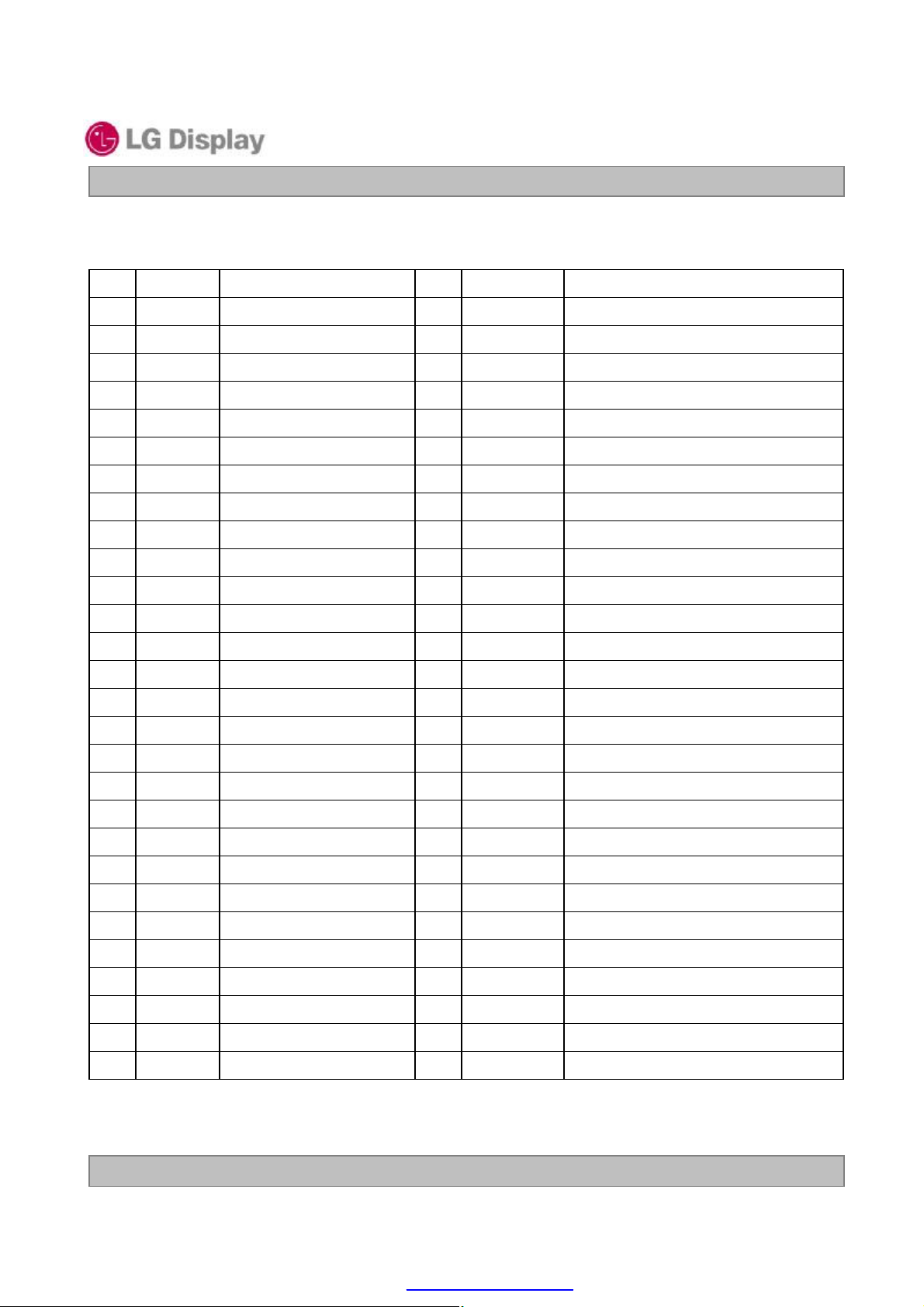

Table 4. REQUIRED SIGNAL ASSIGNMENT FOR Flat Link (TI:SN75LVDS83) Transmitter

Pin # Require SignalPin Name Pin # Require SignalPin Name

1 Power Supply for TTL InputVCC 29 Ground pin for TTLGND

2 TTL Input (R7)D5 30 TTL Input (DE)D26

3 TTL Input (R5)D6 31 TTL Level clock InputTXCLKIN

4 TTL Input (G0)D7 32 Power Down InputPWR DWN

5 Ground pin for TTLGND 33 Ground pin for PLLPLL GND

6 TTL Input (G1)D8 34 Power Supply for PLLPLL VCC

7 TTL Input (G2)D9 35 Ground pin for PLLPLL GND

8 TTL Input (G6)D10 36 Ground pin for LVDSLVDS GND

9 Power Supply for TTL InputVCC 37 Positive LVDS differential data output 3TxOUT3+

10 TTL Input (G7)D11 38 Negative LVDS differential data output 3TxOUT3-

LM230WF2

11 TTL Input (G3)D12 39 Positive LVDS differential clock outputTXCLKOUT+

12 TTL Input (G4)D13 40 Negative LVDS differential clock outputTXCLKOUT-

13 Ground pin for TTLGND 41 Positive LVDS differential data output 2TXOUT2+

14 TTL Input (G5)D14 42 Negative LVDS differential data output 2TXOUT2-

15 TTL Input (B0)D15 43 Ground pin for LVDSLVDS GND

16 TTL Input (B6)D16 44 Power Supply for LVDSLVDS VCC

17 Power Supply for TTL InputVCC 45 Positive LVDS differential data output 1TXOUT1+

46 Negative LVDS differential data output 1TXOUT1-18 TTL Input (B7)D17

19 TTL Input (B1)D18

20 TTL Input (B2)D19

22 TTL Input (B3)D20

23 TTL Input (B4)D21

24 TTL Input (B5)D22

25 TTL Input (RSVD)D23

26 Power Supply for TTL InputVCC 54 TTL Input (R2)D2

47 Positive LVDS differential data output 0TXOUT0+

48 Negative LVDS differential data output 0TXOUT0-

49 Ground pin for LVDSLVDS GND21 Ground pin for TTL InputGND

50 TTL Input (R6)D27

51 TTL Input (R0)D0

52 TTL Input (R1)D1

53 Ground pin for TTLGND

55 TTL Input (R3)D327 TTL Input (HSYNC)D24

56 TTL Input (R4)D428 TTL Input (VSYNC)D25

Notes : 1. Refer to LVDS Transmitter Data Sheet for detail descriptions.

2. 7 means MSB and 0 means LSB at R,G,B pixel data

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

10 / 34

Page 11

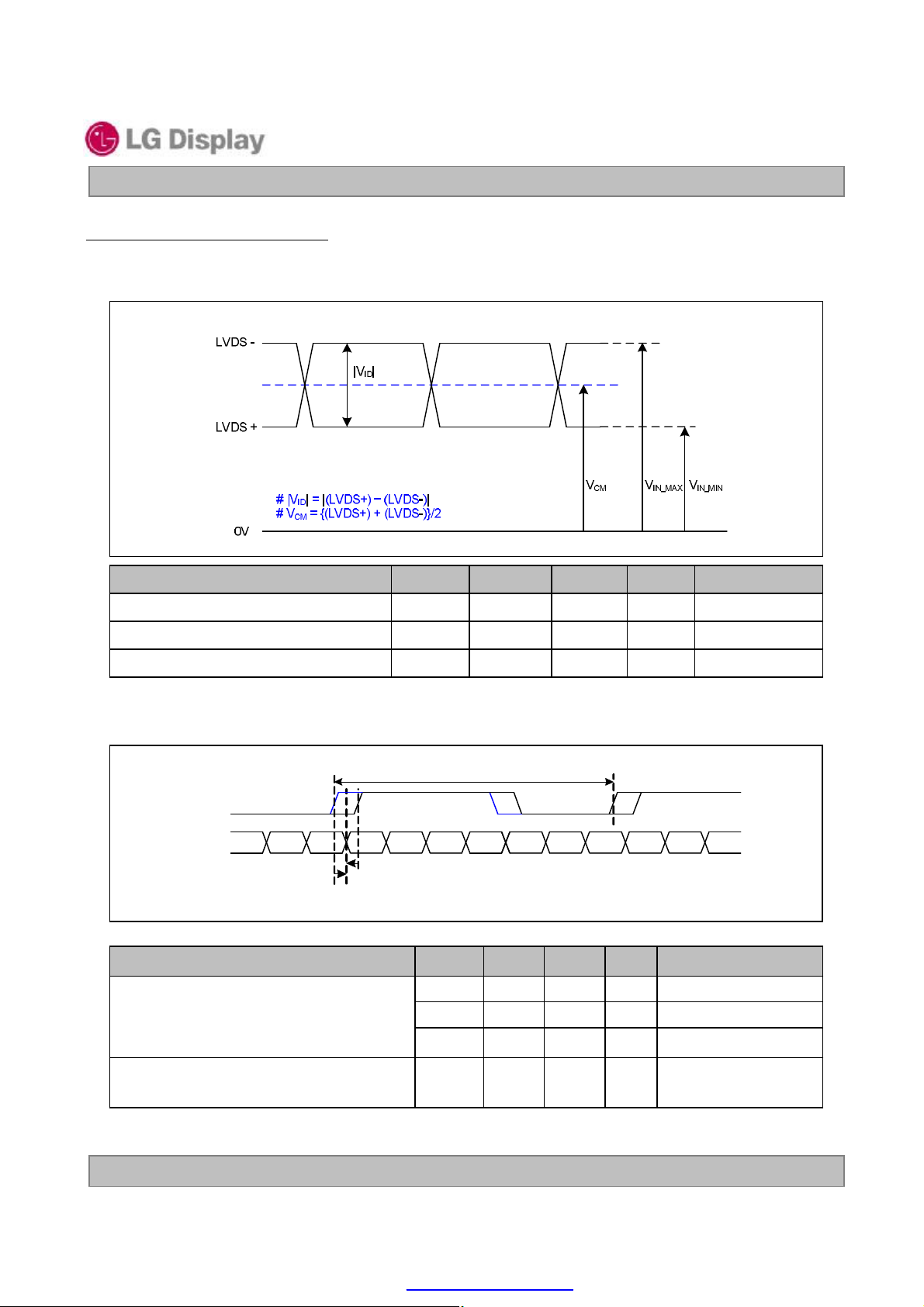

LVDS Input characteristics

1. DC Specification

LM230WF2

Liquid Crystal Display

Product Specification

Description Symbol Min Max Unit Notes

LVDS Differential Voltage |VID| 100 600 mV LVDS Common mode Voltage V

LVDS Input Voltage Range V

CM

IN

0.6 1.8 V -

0.3 2.1 V -

2. AC Specification

Tclk

LVDS Clock

LVDS Data

Description Symbol Min Max Unit Notes

LVDS Clock to Data Skew Margin

SKEW (Fclk

t

SKEW

t

1) 95MHz > Fclk ≥85MHz : -300 ~ +300

2) 85MHz > Fclk ≥65MHz : -400 ~ +400

3) 65MHz > Fclk ≥30MHz : -600 ~ +600

t

SKEW

t

SKEW

t

SKEW

= 1/T

clk

)

-300 + 300 ps 95MHz > Fclk ≥ 85MHz

-400 + 400 ps 85MHz > Fclk ≥ 65MHz

-600 + 600 ps 65MHz > Fclk ≥ 30MHz

LVDS Clock to Clock Skew Margin (Even to

Odd)

t

SKEW_EO

-1/7 + 1/7 T

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

clk

-

11 / 34

Page 12

3. Data Format

1) LVDS 2 Port

LM230WF2

Liquid Crystal Display

Product Specification

< Clock skew margin between channel >

< LVDS Data Format >

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

12 / 34

Page 13

LM230WF2

Liquid Crystal Display

Product Specification

Table 5. BACKLIGHT CONNECTOR PIN CONFIGURATION(CN2,CN3,CN4,CN5)

The backlight interface connector is a model 35001HS-02LD manufactured by Yeonho. The mating

connector part number are 35001WR-02L or equivalent. The pin configuration for the connector is shown in

the table below.

Pin Symbol Description NOTES

1 HV High Voltage for Lamp 1

2 LV Low Voltage for Lamp 1, 2

Note : 1. The high voltage power terminal is colored White, Pink

The low voltage pin color is White, Blue.

2. The backlight ground should be common with LCD metal frame.

3. 35001HS-02LD (Locking type)

Up Side

Down Side

Lamp1

Lamp2

Lamp3

Lamp4

[ Figure 5 ] Backlight connector diagram

CN2

CN3

CN4

CN5

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

13 / 34

Page 14

LM230WF2

Liquid Crystal Display

Product Specification

3-3. Signal Timing Specifications

This is signal timing required at the input of the TMDS transmitter. All of the interface signal timing should be

satisfied with the following specifications for it’s proper operation.

Table 6. TIMING TABLE

ITEM Symbol Min Typ Max Unit Note

DCLK

Horizontal

Vertical

Period tCLK

Frequency -

total tHP

Frequency fH

Blanking

valid tWH

total tVP

Frequency fV

Blanking

valid tWV

11.76 13.89 15.38

60 72 87.5

1000 1088 1120

64 66 83

40 128 160

960 960 960

1090 1100 1160

50 60 75

10 20 80

1080 1080 1080

ns

MHz

tCLK

KHz

tCLK

tCLK/2

tHP

Hz

tHP

tHP

Note:

1. DE Only mode operation. The input of Hsync & Vsync signal does not

have an effect on LCD normal operation.

2. The performance of the electro-optical characteristics may be influenced by variance of the

vertical refresh rates.

3. Horizontal period should be even.

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

14 / 34

Page 15

3-4. Signal Timing Waveforms

1. DCLK , DE, DATA waveforms

LM230WF2

Liquid Crystal Display

Product Specification

DCLK

tCLK

First data

Second data

DE(Data Enable)

2. Horizontal waveform

Invalid data

Invalid data

Valid data

Pixel 0,0

Valid data

Pixel 1,0

Pixel 2,0

Pixel 3,0

tHV

Invalid data

Invalid data

tHP

DE(Data Enable)

3. Vertical waveform

tVV

tHP

DE(Data Enable)

Ver. 1.0 Mar. 04. 2010

DE

t

VP

DE

15 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 16

LM230WF2

Liquid Crystal Display

Product Specification

3-5. Color Input Data Reference

The Brightness of each primary color(red,green,blue) is based onthe 8-bit gray scale data input for the color;

the higher the binary input, the brighter the color. The table below provides a reference for color versus data

input.

Table 7. COLOR DATA REFERENCE

Input Color Data

Basic

Color

RED

Color

Black 0 0 0 0 0 0 0 00 0 0 0 0 0 0 00 0 0 0 0 0 0 0

Red (255) 1 1 1 1 1 1 1 10 0 0 0 0 0 0 00 0 0 0 0 0 0 0

Green (255) 0 0 0 0 0 0 0 01 1 1 1 1 1 1 10 0 0 0 0 0 0 0

Blue (255) 0 0 0 0 0 0 0 00 0 0 0 0 0 0 01 1 1 1 1 1 1 1

Cyan 0 0 0 0 0 0 0 01 1 1 1 1 1 1 11 1 1 1 1 1 1 1

Magenta 1 1 1 1 1 1 1 10 0 0 0 0 0 0 01 1 1 1 1 1 1 1

Yellow 1 1 1 1 1 1 1 11 1 1 1 1 1 1 10 0 0 0 0 0 0 0

White 1 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 1

RED (000) Dark 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0

RED (001) 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0

... ... ... ...

RED (254) 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0

RED (255) 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0

GREEN (000) Dark 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

MSB LSB

R7 R6 R5 R4 R3 R2 R1 R0G7 G6 G5 G4 G3 G2 G1 G0B7 B6 B5 B4 B3 B2 B1 B0

RED

MSB LSB

GREEN

BLUE

MSB LSB

GREEN (001) 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

GREEN

GREEN (254) 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

GREEN (255) 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0

BLUE (000) Dark 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

BLUE (001) 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

BLUE

BLUE (254) 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0 1 1 1 1 1 1 1 0

BLUE (255) 0 0 0 0 0 0 0 00 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

... ... ... ...

... ... ... ...

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

16 / 34

Page 17

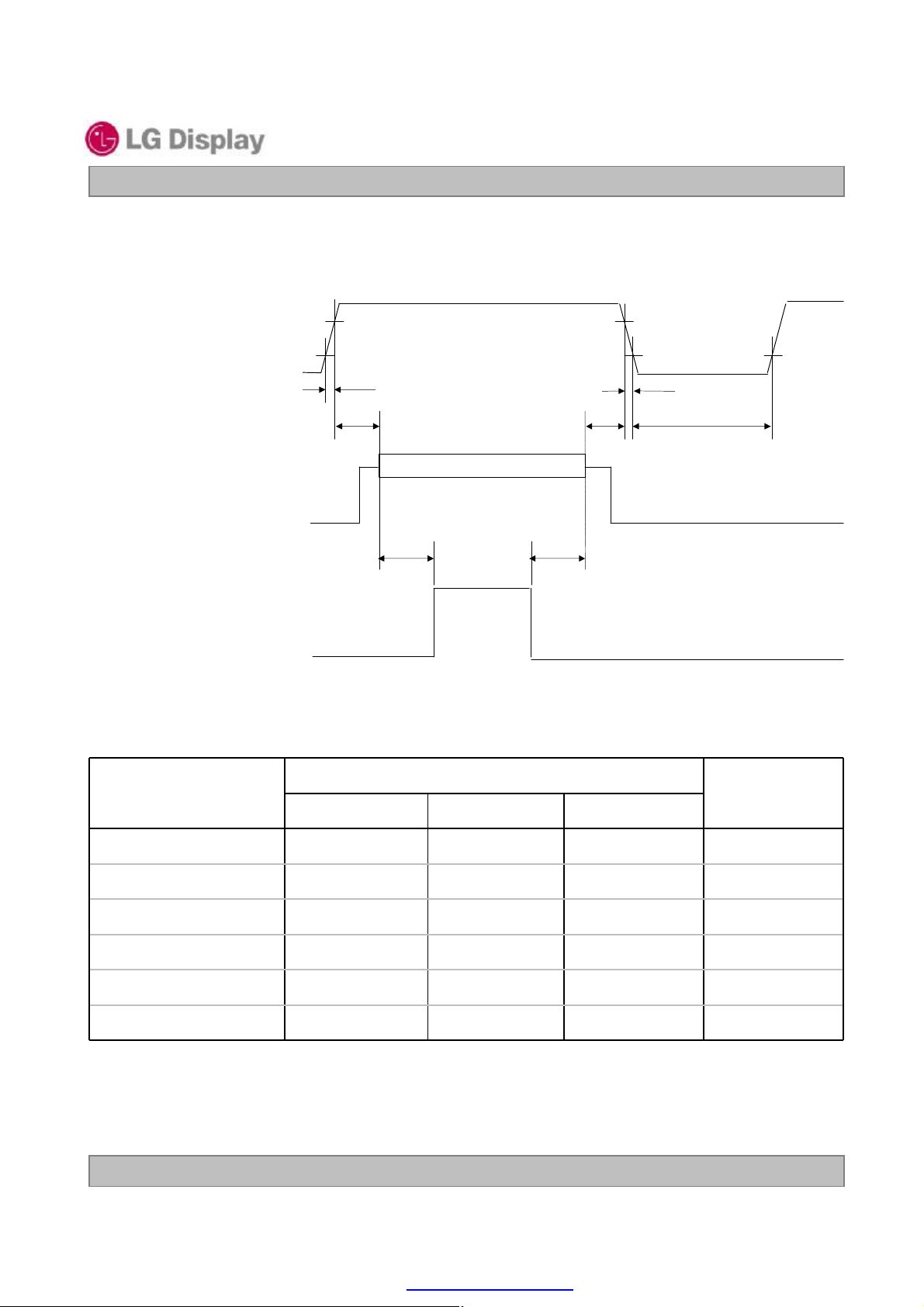

3-6. Power Sequence

Power Supply, VLCD

Interface Signal, Vi

(Digital RGB signal,

SCDT ,Vsync, Hsync,

DE, Clock to PanelLink

Transmitter)

LM230WF2

Liquid Crystal Display

Product Specification

V

LCD

0V

0V

90%

10%

T1

T2 T5 T7

Valid Data

T3

T4

90%

10%

T6

Power Supply for

LAMP ONLAMP OFF

Backlight Inverter

[ Figure 6 ] Power sequence

Table 8. POWER SEQUENCE

Values

Parameter

Min Typ Max

T1 0.5 - 10 ms

T2 0.01 - 50 ms

T3 500 - - ms

T4 200 - - ms

T5 0.01 - 50 ms

T7 1000 - ms

Notes : 1. Please avoid floating state of interface signal at invalid period.

2. When the interface signal is invalid, be sure to pull down the power supply for LCD V

3. Lamp power must be turn on after power supply forLCD and interface signal are valid.

LAMP OFF

Units

LCD

to 0V.

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

17 / 34

Page 18

Product Specification

LM230WF2

Liquid Crystal Display

3-7. V

LCD

1) Dip condition

2) V

Power Dip Condition

10V ≤V

< 10V

LCD

< 11V , td≤20ms

LCD

10V

t

d

[ Figure 7 ] Power dip condition

V

12V

LCD

V

-dip conditions should also follow the Power On/Off conditions for supply voltage.

LCD

Ver. 1.0 Mar. 04. 2010

18 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 19

LM230WF2

Liquid Crystal Display

Product Specification

4. Optical Specifications

Optical characteristics are determined after the unit has been ‘ON’ for approximately 30 minutes

in a dark environment at 25±2°C. The values specified are at an approximate distance 50cm fromthe LCD

surface at a viewing angle of Φ and θ equal to 0 ° and aperture 1 degree.

FIG. 1 presents additional information concerning the measurement equipment and method.

PR 880 or RD 80S

or PR650

Optical Stage(x,y)

LCD Module

50cm

FIG. 1 Optical Characteristic Measurement Equipment and Method

Table 9. OPTICAL CHARACTERISTICS

Parameter Symbol

Contrast Ratio CR 600 1000 - 1

Surface Luminance, white L

Luminance Variation δ

Response Time Gray To Gray T

RED Rx

GREEN Gx 0.303

Color Coordinates

[CIE1931]

(By PR650)

BLUE Bx 0.145

WHITE Wx 0.313

Color Shift

(Avg. Δu’v’ < 0.02)

Horizontal

Vertical

Viewing Angle (CR>10)

General

GSR @ 60dgree

(Gamma shift rate)

Horizontal θ

Vertical θ

Horizontal

Vertical δ

WPT (White Point Tracking) - -300 G255 CCT +700 K 8

Color gamut (CG, CIE1976)

Gray Scale - 2.2 9

WH

WHITE

GTG_AVR

Ry 0.335

Gy 0.613

By 0.070

Wy 0.329

θ

CST_H

θ

CST_V

H

V

δ

Gamma_H

Gamma_V

(Ta=25 °C, V

Min Typ Max

250 300 - cd/m

=12V, fV=60Hz Dclk=144MHz, IBL=7.5mA)

LCD

Values

Units Notes

2

75 - - % 3

- 14 25 ms 4

0.644

Typ

-0.03

- 140 -

Typ

+0.03

Degree 5

- 100 -

170 178 170 178 -

- - 20

Degree 6

% 7

- - 20

-

82 - %

2

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

19 / 34

Page 20

Product Specification

24

Notes 1. Contrast Ratio(CR) is defined mathematically as : (By PR880)

RatioContrast =

It is measured at center point(Location P1)

2. Surface luminance(LWH)is luminance value at Center 1 point(P1) across the LCD surface50cm

from the surface with all pixels displaying white. For more information see FIG 2. (By PR880)

3. The variation in surface luminance , δ WHITE is defined as : (By PR880)

LM230WF2

Liquid Crystal Display

pixels whiteall with Luminance Surface

pixelsblack all with Luminance Surface

=

δ

WHITE

Where L1to L9 are the luminance with all pixels displaying white at 9 locations.

For more information see FIG 2.

4. Gray to gray response time is the time required for the display to transition from gray to gray. For

additional information see Table 10. (By RD80S)

5. Color shift is the angle at which the average color difference for all Macbeth is lower than 0.02.

For more information see FIG 3 and FIG 4. (By EZ Contrast)

-Color difference (Δu’v’)

4

'

=

u

x

3122

++−

yx

24

∆

1∑=

i

)''(

=∆

vuAvg

-Pattern size : 25% Box size

-Viewing angle direction of color shift : Horizontal, Vertical

6. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are

determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which

is normal to the LCD surface. For more information see FIG 4. (By PR880)

…

'

=

v

)''(

ivu

)L .. ,L,Minimum(L

P9P2P1

100

×

)L .... ,L ,(L Maximum

P9P2P1

9

y

3122

++−

yx

u’1, v’1 : u’v’ value at viewing angle direction

u’2, v’2 : u’v’ value at front (θ=0)

i : Macbeth chart number (Define 23 page)

2

21

2

)''()''('' vvuuvu −+−=∆

21

7. GSR is the rate of gamma shift at up, down, left and right 60 degree viewing angle compare with

center gamma. For more information see FIG 5 and FIG 6 (By EZ Contrast)

-GSR (δ

.

8. WPT (White Point Tracking) is the variation of color temperature between G255 and G63.

(By PR650)

Ver. 1.0 Mar. 04. 2010

) is defined as :

Gamma

1 ×

−=GSR

PDF created with pdfFactory Pro trial version www.pdffactory.com

Degree) 60Light Reft, Down, (Up, Value Gamma angle View

Degree) (0 Value GammaCenter

100

20 / 34

Page 21

Product Specification

Notes 9. Gamma Value is approximately 2.2. For more information see Table 11.

Measuring point for surface luminance & measuring point for luminance variation.

H

LM230WF2

Liquid Crystal Display

H/2

●

●

P2

P5

V/2

V

●

V/10

P7

●

●

●

P3

P1

P8

●

●

●

H/10

P4

P6

P9

FIG. 2 Measure Point for Luminance

The Gray to Gray response time is defined as the following figure and shall be measured by switching the input

signal for “Gray To Gray “.

-Gray step : 5 Step

-TGTG_AVR is the total average time at rising time and falling time for “Gray To Gray “.

-if system use ODC ( Over Driving Circuit) function, Gray to Gary response time may be 5ms~8ms GtG

* it depends on Overshoot rate.

Table. 10 GTG Gray Table

Gray to Gray

G255 G191 G127 G63 G0

Falling Time G255

G191

G127

G63

G0

Ver. 1.0 Mar. 04. 2010

Rising Time

21 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 22

LM230WF2

Liquid Crystal Display

Product Specification

Color shift is defined as the following test pattern and color.

25% Box size

FIG. 3 Color Shift Test Pattern

Average RGB values in Bruce RGB for Macbeth Chart

Dark skin (i=1) Light skin Blue sky Foliage Blue flower Bluish green

R 98 206 85 77 129 114

G 56 142 112 102 118 199

B 45 123 161 46 185 178

Orange Purplish blue Moderate red Purple Yellow green Orange yellow

R 219 56 211 76 160 230

G 104 69 67 39 193 162

B 24 174 87 86 58 29

Blue Green Red Yellow Magenta Cyan

R 26 72 197 241 207 35

G 32 148 27 212 62 126

B 145 65 37 36 151 172

White Neutral 8 Neutral 6.5 Neutral 5 Neutral 3.5 Black

R 240 206 155 110 63 22

G 240 206 155 110 63 22

B 240 206 155 110 63 22

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

22 / 34

Page 23

Dimension of viewing angle range.

LM230WF2

Liquid Crystal Display

Product Specification

φ

= 180°, Left

φ

= 270°, Down

Normal

E

θ

φ

FIG. 4 Viewing angle

Y

φ

= 90°, Up

φ

= 0°, Right

FIG. 5 Sample Luminance vs. gray scale

(using a 256 bit gray scale)

r

LaVL +=

b

FIG. 6 Sample Log-log plot of luminance

vs. gray scale

Here the Parameter α and γ relate the signal level V to the luminance L.

The GAMMA we calculate from the log-log representation (FIG. 6)

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

b

+=−

)log()log()log( aVrLL

23 / 34

Page 24

Table 11. Gray Scale Specification

Gray Level Relative Luminance [%] (Typ.)

LM230WF2

Liquid Crystal Display

Product Specification

0

31 1.08

63 4.72

95 11.49

127 21.66

159 35.45

191 53.00

223 74.48

255 100

0.11

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

24 / 34

Page 25

LM230WF2

Liquid Crystal Display

Product Specification

5. Mechanical Characteristics

The contents provide general mechanical characteristics. In addition the figures in the next page are detailed

mechanical drawing of the LCD.

Horizontal 533.2mm

Outline Dimension

Bezel Area

Active Display Area

Weight Typ : 3000 g , Max : 3150 g

Surface Treatment

Vertical 312.0mm

Depth 17.0 mm

Horizontal 513.8mm

Vertical 291.0mm

Horizontal 509.184mm

Vertical 286.416mm

Hard coating(3H)

Glare(Low Reflection treatment of the front polarizer)

Notes : Please refer to a mechanic drawing in terms of toleranceat the next page.

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

25 / 34

Page 26

<FRONT VIEW>

LM230WF2

Liquid Crystal Display

Product Specification

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

26 / 34

Page 27

<REAR VIEW>

LM230WF2

Liquid Crystal Display

Product Specification

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

27 / 34

Page 28

Product Specification

6. Reliability

Environment test condition

No Test Item Condition

1 High temperature storage test Ta= 60°C 240h

2 Low temperature storage test Ta= -20°C 240h

3 High temperature operation test Ta= 50°C 50%RH 240h

4 Low temperature operation test Ta= 0°C 240h

Wave form : random

5

Vibration test

(non-operating)

Vibration level : 1.47G RMS

Bandwidth : 5-200Hz

Duration : X,Y,Z, 33 min

One time each direction

LM230WF2

Liquid Crystal Display

Shock level : 100G

6

7 Humidity condition Operation Ta= 40 °C ,90%RH

8

9

Shock test

(non-operating)

Altitude

storage / shipment 0 -40,000 feet(12192m)

Maximum Storage Humidity for

4 corner light leakage Mura.

Waveform : half sine wave, 2ms

Direction : ±X, ±Y, ±Z

One time each direction

Max 70%RH , Ta=40℃

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

28 / 34

Page 29

LM230WF2

Liquid Crystal Display

Product Specification

7. International Standards

7-1. Safety

a) UL 60950-1, Second Edition, Underwriters Laboratories Inc.

Information Technology Equipment -Safety -Part 1 : General Requirements.

b) CAN/CSA C22.2 No.60950-1-07, Second Edition, Canadian Standards Association.

Information Technology Equipment -Safety -Part 1 : General Requirements.

c) EN 60950-1:2006 + A11:2009, European Committee for Electrotechnical Standardization (CENELEC).

Information Technology Equipment -Safety -Part 1 : General Requirements.

d) IEC 60950-1:2005, Second Edition,The International Electrotechnical Commission (IEC).

Information Technology Equipment -Safety -Part 1 : General Requirements.

7-2. EMC

a) ANSI C63.4 “American National Standard for Methods of Measurement of Radio-Noise

Emissions from Low-Voltage Electrical and Electronic Equipment in the Range of 9 kHz to 40 GHz.”

American National Standards Institute (ANSI), 2003.

b) CISPR 22 “Information technology equipment – Radio disturbance characteristics – Limit and

methods of measurement." International Special Committeeon Radio Interference

(CISPR), 2005.

c) CISPR 13 “Sound and television broadcast receivers and associated equipment – Radio disturbance

characteristics – Limits and method of measurement." International Special Committee on Radio

Interference (CISPR), 2006.

7-3. Environment

a) RoHS. Directive 2002/95/EC of the European Parliament and of the Council on the reduction of the

use of certain hazardous substances in electrical and electronic equipment. January 2003

Ver. 1.0 Mar. 04. 2010

29 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 30

8. Packing

8-1. Designation of Lot Mark

a) Lot Mark

A B C D E F G H I J K L M

A,B,C : SIZE(INCH) D : YEAR

E : MONTH F ~ M : SERIAL NO.

Note

1. YEAR

LM230WF2

Liquid Crystal Display

Product Specification

Year

Mark

321

200452005

4

200320022001

2006720078200892009

6

2. MONTH

Month

Mark

Apr5May

4

Jun7Jul8Aug9Sep

6

b) Location of Lot Mark

Serial No. is printed on the label. The label is attached to thebackside of the LCD module.

This is subject to change without prior notice.

2010

0

Oct

A

Nov

B

DecMarFebJan

C321

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

30 / 34

Page 31

8-2. Packing Form

a) Package quantity in one box : 7EA

b) Box Size : 424 X 328 X 603

LM230WF2

Liquid Crystal Display

Product Specification

NO. DESCRIPTION MATERIAL

1 LCM

2 BAG

3 TAPE OPP

4 PACKING, BOTTOM EPS

5 PACKING, TOP

6 BOX

7 TAPE

8 LABEL

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

PE

EPS

PAPER, SW

OPP

ART

31 / 34

Page 32

8-3. Pallet Form

LM230WF2

Liquid Crystal Display

Product Specification

NO. DESCRIPTION MATERIAL

1 PACKING ASS’Y

2 PALLET

3 BAND

4 CLIP, BAND

5 ANGLE, PACKING

6 LABEL

7 Wrapping

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

PLYWOOD_1030X870X117.5

PP

STEEL

PAPER (SW)

PAPER

LLDPE

32 / 34

Page 33

LM230WF2

Liquid Crystal Display

Product Specification

9. PRECAUTIONS

Please pay attention to the followings when you use this TFT LCDmodule.

9-1. MOUNTING PRECAUTIONS

(1) You must mount a module using holes arranged in four cornersor four sides.

(2) You should consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to the

module. And the case on which a module is mounted should have sufficient strength so that external

force is not transmitted directly to the module.

(3) Please attach the surface transparent protective plate to the surface in order to protect the polarizer.

Transparent protective plate should have sufficient strength in order to the resist external force.

(4) You should adopt radiation structure to satisfy the temperature specification.

(5) Acetic acid type and chlorine type materials for the cover case are not desirable because the former

generates corrosive gas of attacking the polarizer at high temperature and the latter causes circuit break

by electro-chemical reaction.

(6) Do not touch, push or rub the exposed polarizers with glass,tweezers or anything harder than HB

pencil lead. And please do not rub with dust clothes with chemical treatment.

Do not touch the surface of polarizer for bare hand or greasy cloth.(Some cosmetics are detrimental

to the polarizer.)

(7) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like

chamois soaks with petroleum benzene. Normal-hexane is recommended for cleaning the adhesives

used to attach front / rear polarizers. Do not use acetone, toluene and alcohol because they cause

chemical damage to the polarizer.

(8) Wipe off saliva or water drops as soon as possible. Their long time contact with polarizer causes

deformations and color fading.

(9) Do not open the case because inside circuits do not have sufficient strength.

9-2. OPERATING PRECAUTIONS

(1) The spike noise causes the mis-operation of circuits. It should be lower than following voltage:

V=±200mV(Over and under shoot voltage)

(2) Response time depends on the temperature.(In lower temperature, it becomes longer.)

(3) Brightness depends on the temperature. (In lower temperature, it becomes lower.)

And in lower temperature, response time(required time that brightness is stable after turned on) becomes

longer.

(4) Be careful for condensation at sudden temperature change. Condensation makes damage to polarizer or

electrical contacted parts. And after fading condensation, smearor spot will occur.

(5) When fixed patterns are displayed for a long time, remnant image is likely to occur.

(6) Module has high frequency circuits. Sufficient suppression to the electromagnetic interference shall be

done by system manufacturers. Grounding and shielding methods may be important to minimized the

interference.

(7) Please do not give any mechanical and/or acoustical impact to LCM. Otherwise, LCM can’t be operated

its full characteristics perfectly.

(8) A screw which is fastened up the steels should be a machine screw.

(if not, it causes metallic foreign material and deal LCM afatal blow)

(9)Please do not set LCD on its edge.

(10) When LCMs are used for public display defects such as Yogure, image sticking can not be guarantee.

Ver. 1.0 Mar. 04. 2010

33 / 34

PDF created with pdfFactory Pro trial version www.pdffactory.com

Page 34

LM230WF2

Liquid Crystal Display

Product Specification

9-3. ELECTROSTATIC DISCHARGE CONTROL

Since a module is composed of electronic circuits, it is not strong to electrostatic discharge. Make certain that

treatment persons are connected to ground through wrist band etc. And don’t touch interface pin directly.

9-4. PRECAUTIONS FOR STRONG LIGHT EXPOSURE

Strong light exposure causes degradation of polarizer and color filter.

9-5. STORAGE

When storing modules as spares for a long time, the following precautions are necessary.

(1) Store them in a dark place. Do not expose the module to sunlight or fluorescent light. Keep the temperature

between 5°C and 35°C at normal humidity.

(2) The polarizer surface should not come in contact with any other object.

It is recommended that they be stored in the container in which they were shipped.

9-6. HANDLING PRECAUTIONS FOR PROTECTION FILM

(1) The protection film is attached to the bezel with a small masking tape.

When the protection film is peeled off, static electricity is generated between the film and polarizer.

This should be peeled off slowly and carefully by people who are electrically grounded and with well ionblown equipment or in such a condition, etc.

(2) When the module with protection film attached is stored for a long time, sometimes there remains a very

small amount of glue still on the bezel after the protection film is peeled off.

(3) You can remove the glue easily. When the glue remains on thebezel surface or its vestige is recognized,

please wipe them off with absorbent cotton waste or other soft material like chamois soaked with normalhexane.

Ver. 1.0 Mar. 04. 2010

PDF created with pdfFactory Pro trial version www.pdffactory.com

34 / 34

Loading...

Loading...