LG Display LM215WF2-SLD1 Specification

Global LCD Panel Exchange Center

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

SPECIFICATION

FOR

APPROVAL

( ) Preliminary Specification

) Final Specification

(

BUYER

MODEL

APPROVED BY

/

/

HP

SIGNATURE

DATE

21.5” Full HD TFT LCDTitle

SUPPLIER LG Display Co., Ltd.

*MODEL LM215WF2

SUFFIX SLD1

*When you obtain standard approval,

please use the above model name without suffix

APPROVED BY

B.C. Kim / G.Manager

REVIEWED BY

J. H. Kim / Manager [C]

Y.H. Huang / Manager[M]

SIGNATUR

E DATE

M. S. Kang / Manager [P]

PREPARED BY

/

S. H. Han / Engineer

Please return 1 copy for your confirmation with

your signature and comments.

Ver. 1.0 Nov. 29 . 2010

MNT Products Engineering Dept.

LG Display Co., Ltd

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

1/32

www.panelook.com

Global LCD Panel Exchange Center

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

Contents

No ITEM

COVER

CONTENTS

RECORD OF REVISIONS

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATIONS

3-1 ELECTRICAL CHARACTREISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATIONS

3-4 SIGNAL TIMING WAVEFORMS

3-5 COLOR INPUT DATA REFERNECE

3-6 POWER SEQUENCE

3-7 V

4 OPTICAL SFECIFICATIONS

Power Dip Condition

LCD

Page

1

2

3

4

5

6

6

9

14

15

16

17

18

19

5 MECHANICAL CHARACTERISTICS

6 RELIABLITY

7 INTERNATIONAL STANDARDS

7-1 SAFETY

7-2 EMC

7-3 ENVIRONMENT

8 PACKING

8-1 DESIGNATION OF LOT MARK

8-2 PACKING FORM

9 PRECAUTIONS 31

25

28

29

29

29

29

30

30

30

Ver. 1.0 Nov. 29 . 2010

2/32

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Global LCD Panel Exchange Center

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

RECORD OF REVISIONS

Revision

No

0.0 Aug. 30.2010 - First Draft(Preliminary)

1.0 Nov. 29.2010 - Final specification

Revision Date Page Description

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

3/32

www.panelook.com

Global LCD Panel Exchange Center

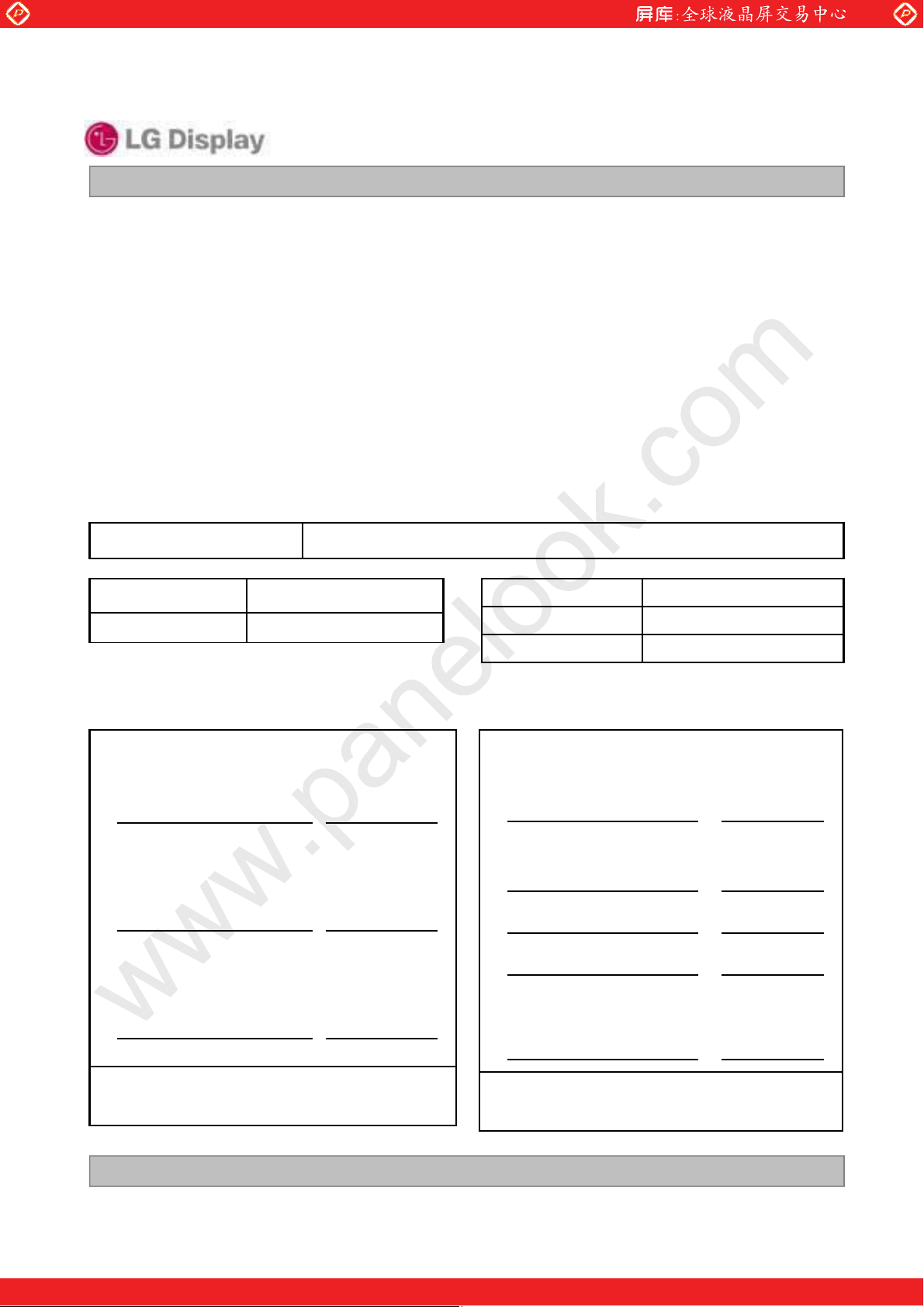

1. General Description

LM215WF2 is a Color Active Matrix Liquid Crystal Display with an integral Cold Cathode Fluorescent

Lamp(CCFL) backlight system. The matrix employs a-Si Thin Film Transistor as the activ e element.

It is a transmissive type display operating in the normally black mode. It has a 21.5 inch diagonally measured

active display area with FHD resolution (1080 vertical by 1920horizontal pixel array)

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the brightness of the sub-pixel color is determined with a 8-bit gray scale signal for each dot,

thus, presenting a palette of more than 16,7M colors with A-FRC(Adv anced Frame Rate Control).

It has been designed to apply the 8Bit 2 port LVDS interface.

It is intended to support displays where high brightness, super wide viewing angle,

high color saturation, and high color are important.

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

RGB

LVDS

2port

+12.0V

CN1

(30pin)

+12.0V

Timing

Controller

Power Circuit

G1

Gate Driver Circuit

G1080

Block

V

Lamp

V

Lamp

General Features

CN2, (2PIN)

CN3, (2PIN)

[Figure1]Blockdiagram

Active Screen Size 21.46 inches(545.22mm) diagonal

Outline Dimension 495.6(H) x 292.2(V) x 16.5(D) mm (Typ.)

Pixel Pitch 0.2475 mm x 0.2475mm

Source Driver Circuit

S1 S1920

TFT - LCD Panel

(1920 RGB 1080 pixels)

Back light Assembly

(2CCFL)

Pixel Format 1920 horiz. By 1080 vert. Pixels RGB stripes arrangement

Color Depth 16,7M colors

Luminance, White 250 cd/m

2

(1point)

Viewing Angle(CR>10) View Angle Free (R/L 178(Typ.), U/D 178(Typ.))

Power Consumption Total 18.46 Watt (Typ.) ( 3.66 Watt

@VLCD, 14.8 Watt @ I

= 12.5mA)

BL

Weight 2450 g (typ.)

Display Operating Mode Transmissive mode, normally black

Surface Treatment Hard coating(3H), Anti-Glare treatment of the front polarizer

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

4/32

www.panelook.com

Global LCD Panel Exchange Center

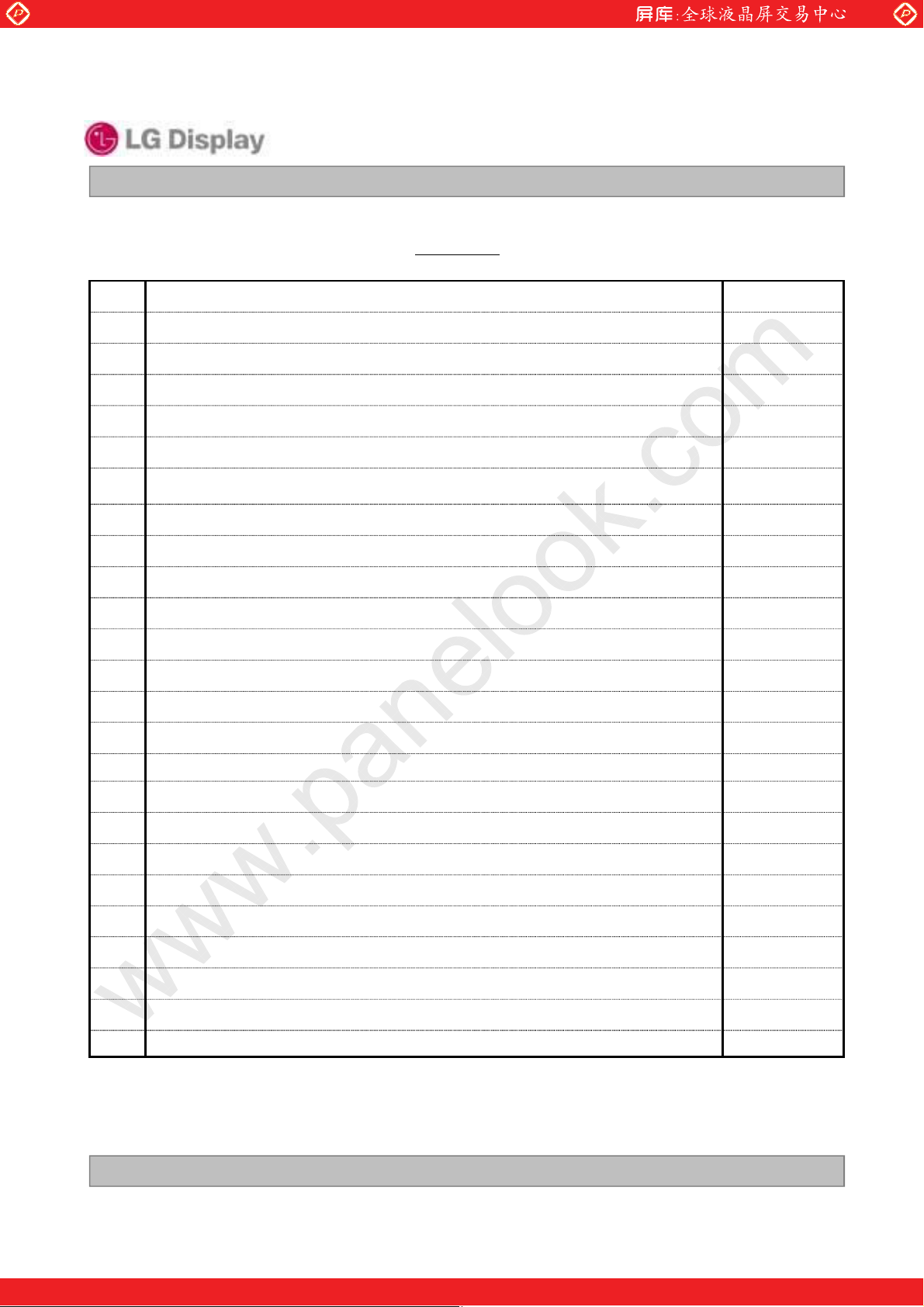

2. Absolute Maximum Ratings

The following are maximum values which, if exceeded, may cause faulty operation or damage to the unit.

Table 1. ABSOLUTE MAXIMUM RATINGS

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

Parameter Symbol

Power Input Voltage

Operating Temperature

Storage Temperature

Operating Ambient Humidity

Storage Humidity

VLCD

TOP

TST

HOP

HST

Values

Min Max

-0.3 14

050

-20 60

10 90

10 90

Units Notes

Vdc at 25 ± 2C

C

C

%RH

%RH

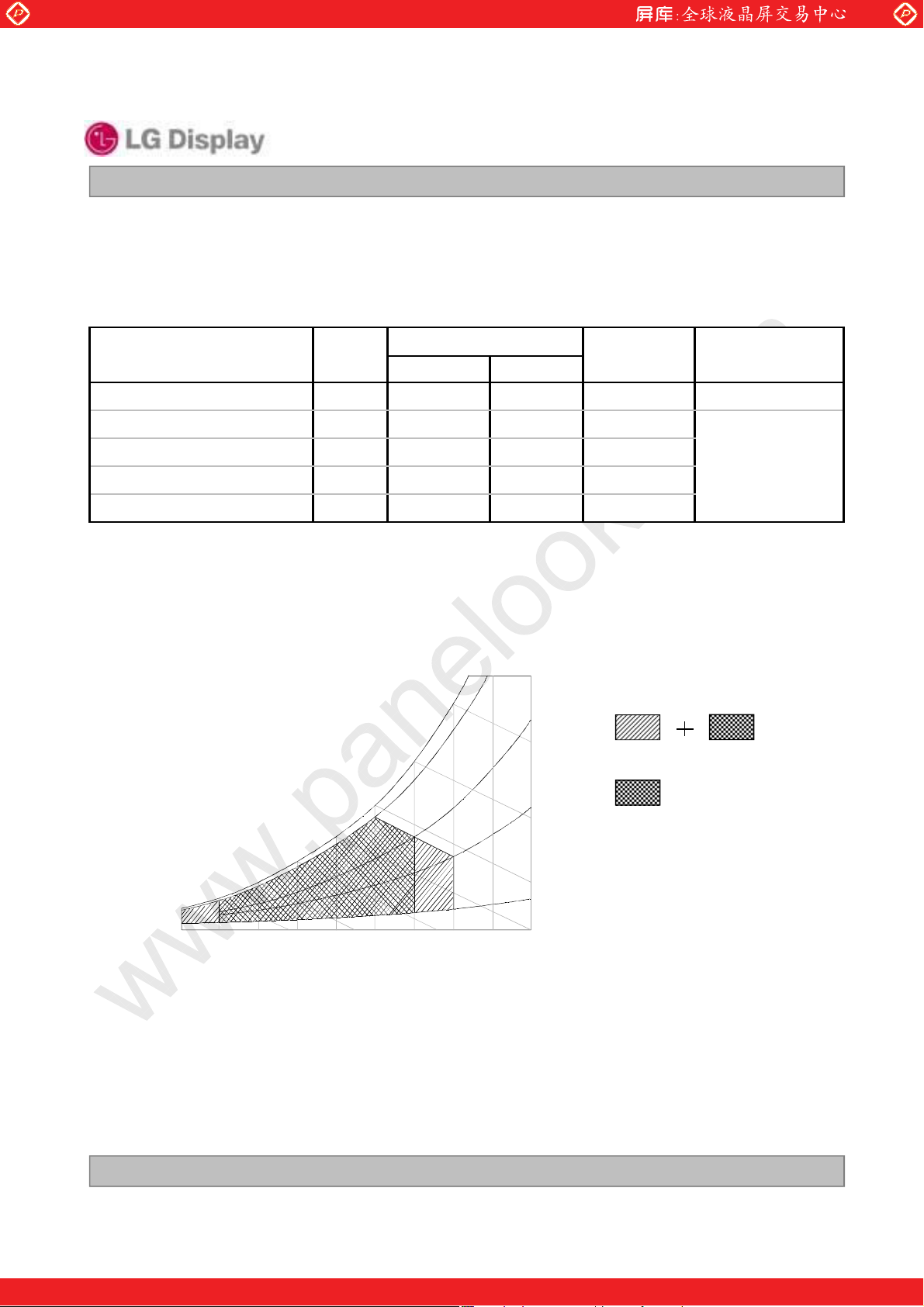

Note : 1. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be 39 C Max, and no condensation of water.

Note : 2. Maximum Storage Humidity is up to 40, 70% RH only for 4 corner light leakage Mura.

90%

60

60%

Wet Bulb

Temperature [C]

10

0

20

50

40

40%

30

Humidity [(%)RH]

10%

Storage

Operation

1, 2

10 20 30 40 50 60 70 800-20

Dry Bulb Temperature [C]

[ Figure 2 ] Temperature and relative humidity

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

5/32

www.panelook.com

Global LCD Panel Exchange Center

3. Electrical Specifications

3-1. Electrical Characteristics

It requires two power inputs. One is employed to power the LCD electronics and to drive the TFT array and

liquid crystal. The second input power for the CCFL, is typically generated by an inverter. The inverter is an

external unit to the LCDs.

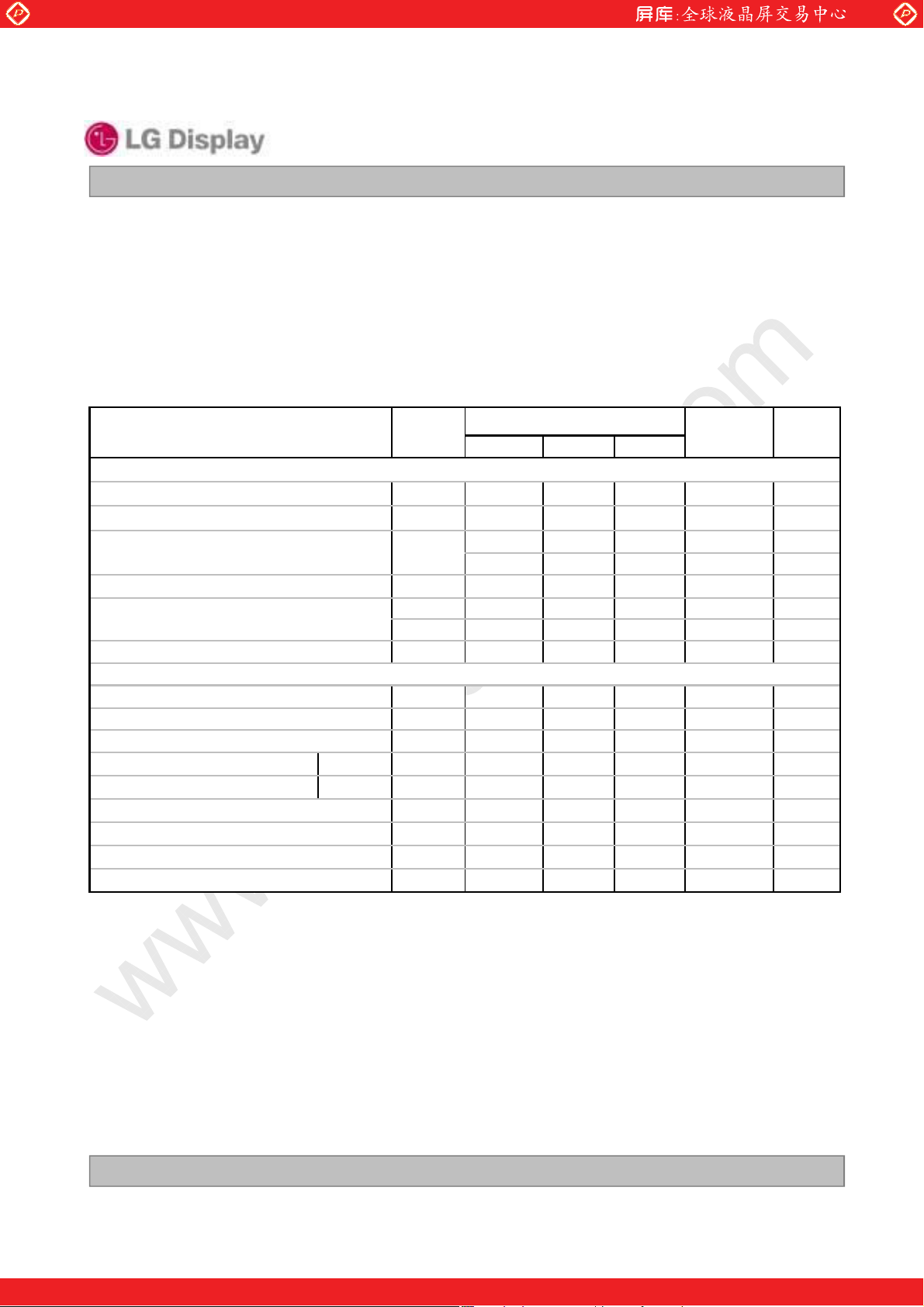

Table 2. ELECTRICAL CHARACTERISTICS

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

Parameter Symbol

MODULE :

Power Supply Input Voltage V

Permissive Power Input Ripple V

Power Supply Input Current I

Differential Impedance

Power Consumption

Rush current I

LAMP :

Operating Voltage V

Operating Current I

EstablishedStarting Voltage Vs 4, 6

LCD 11.4 12 12.6 Vdc

RF - - 100 mV 13

LCD

Zm

LCD 4.25 4.89 Watt 1

P

P

LCD 5.51 6.34 Watt 2

RUSH --3A3

BL

BL

Min Typ Max

276 340 413 mA 1

352 434 528 mA 2

90 100 110

580 590 840

2.5 12.5 13.0

at 25 C

at 0 C

Operating Frequency

Discharge Stabilization Time

Power Consumption

Life Time

fBL

Ts

PBL

40 - 70

50,000 Hrs 4, 10

Values

14.8 16.3

mA

1150 V

1550 V

3

Unit Notes

ohm

V

RMS

RMS

RMS

RMS

kHz 7

Min 4, 8

Watt 9

4, 5

4

Note : The design of the inverter must have specifications for the lamp in LCD Assembly.

The performance of the Lamp in LCM, for example life time or brightness, is extremely influenced by

the characteristics of the DC-AC inverter. So all the parameters of an inverter should be carefully

designed so as not to produce too much leakage current from high-voltage output of the inverter.

When you design or order the inverter, please make sure unwanted lighting caused by the mismatch

of the lamp and the inverter (no lighting, flicker, etc) never occurs. When you confirm it, the LCD–

Assembly should be operated in the same condition as installed in you instrument.

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

6/32

www.panelook.com

Global LCD Panel Exchange Center

Note. Do not attach a conducting tape to lamp connecting wire. If the lamp wire attach to a conducting tape,

TFT-LCD Module has a low luminance and the inverter has abnormal action. Because leakage current

is occurred between lamp wire and conducting tape.

1. The specified current and power consumption are under the V

whereas mosaic pattern(8 x 6) is displayed and f

2. The current is specified at the maximum current pattern. See the figure 3.

3. The duration of rush current is about 5ms and rising time of power Input is 500us ± 20%.(min.).

4. Specified values are for a single lamp.

5. Operating voltage is measured at 25 ± 2C, and follows as below condition.

The variance of the voltage is ± 10%. (Based on single Lamp.)

The variance of the voltage is ± 20%. (Based on system & Test equipment tolerance.)

6. The voltage above V

(Inverter open voltage must be more than lamp starting voltage.)

Otherwise, the lamps may not be turned on. The used lamp current is the lamp typical current.

7. The output of the inverter must have symmetrical(negative and positive) voltage waveform and

symmetrical current waveform (Unsymmetrical ratio is less than 10%). Please do not use the inverter

which has unsymmetrical voltage and unsymmetrical current and spike wave.

Lamp frequency may produce interface with horizontal synchronous frequency and as a result this may

cause beat on the display. Therefore lamp frequency shall be as away possible from the horizontal

synchronous frequency and from its harmonics in order to prevent interference.

8. Let’s define the brightness of the lamp after being lighted for 5 minutes as 100%.

is the time required for the brightness of the center of the lamp to be not less than 95%.

T

S

The used lamp current is the lamp typical current.

9. The lamp power consumption shown above does not include loss of external inverter.

The used lamp current is the lamp typical current. (P

10. The life is determined as the time at which brightness of the lamp is 50% compared to that of initial

value at the typical lamp current on condition of continuous operating at 25 ± 2C.

11. Requirements for a system inverter design, which is intended to have a better display performance,

a better power efficiency and a more reliable lamp, are following.

It shall help increase the lamp lifetime and reduce leakage current.

a. The asymmetry rate of the inverter waveform should be less than 10%.

b. The distortion rate of the waveform should be within √2 10%.

* Inverter output waveform had better be more similar to ideal sine wave.

should be applied to the lamps for more than 1 second for start-up.

S

www.panelook.com

Product Specification

is the frame frequency.

V

= VBLx IBLx N

BL

LM215WF2

Liquid Crystal Display

=12V, 25 ± 2C,fV=60Hz condition

LCD

)

Lamp

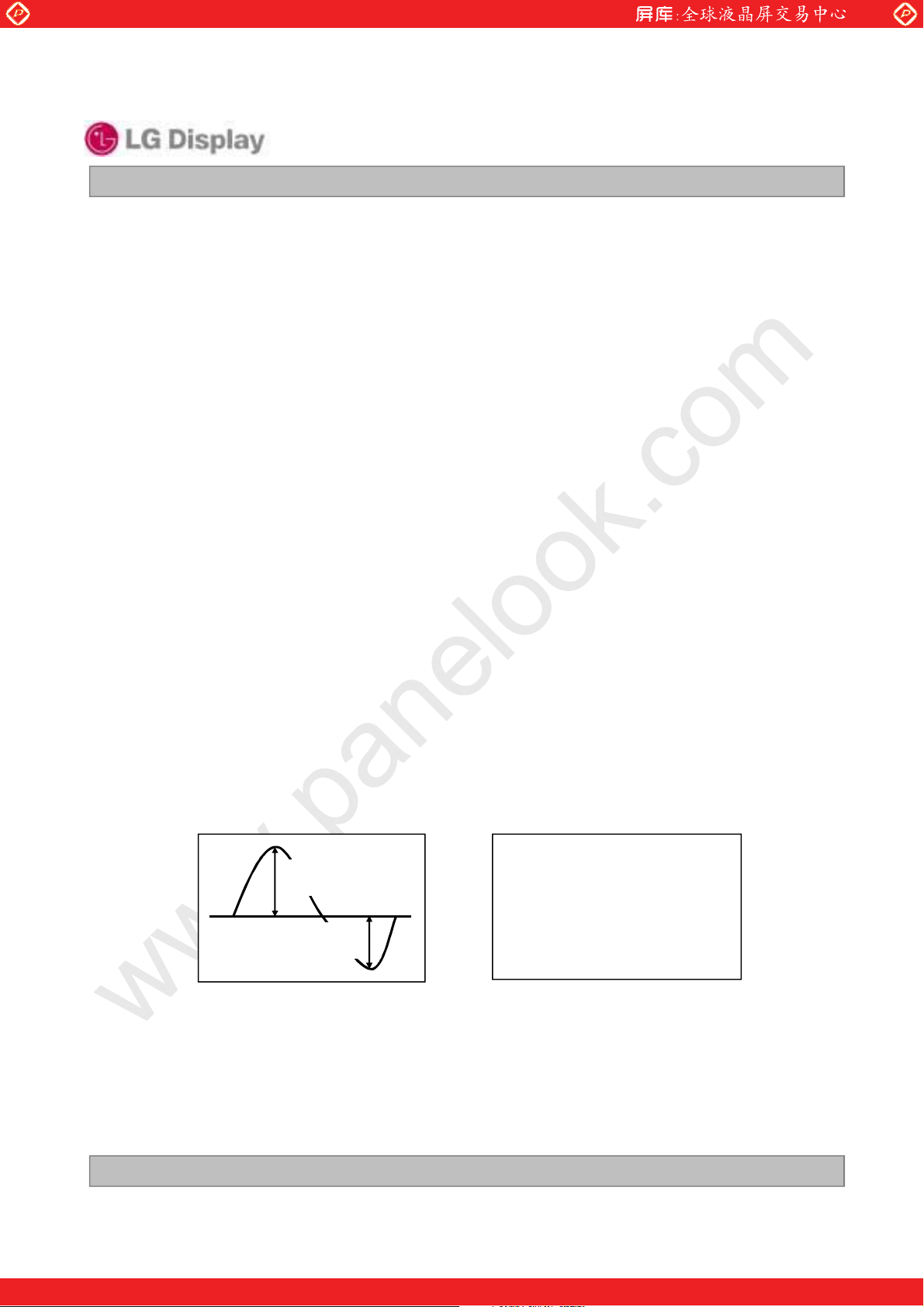

* Asymmetry rate:

I p

|I

p–I–p

|/I

rms

x 100%

* Distortion rate

I -p

(or I–p)/I

I

p

rms

12. The inverter which is combined with this LCM, is highly recommended to connect coupling(ballast)

condenser at the high voltage output side. When you use the inverter which has not coupling(ballast)

condenser, it may cause abnormal lamp lighting because of biased mercury as time goes.

13. Permissive power ripple should be measured under V

=12.0V, 25C, fV(frame frequency)=MAX

LCD

condition and At that time, we recommend the bandwidth configuration of oscilloscope is to be under

20Mhz. See the figure 3.

14. In case of edgy type back light with over 4 parallel lamps, input current and voltage wave form should

be synchronized

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

7/32

www.panelook.com

Global LCD Panel Exchange Center

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

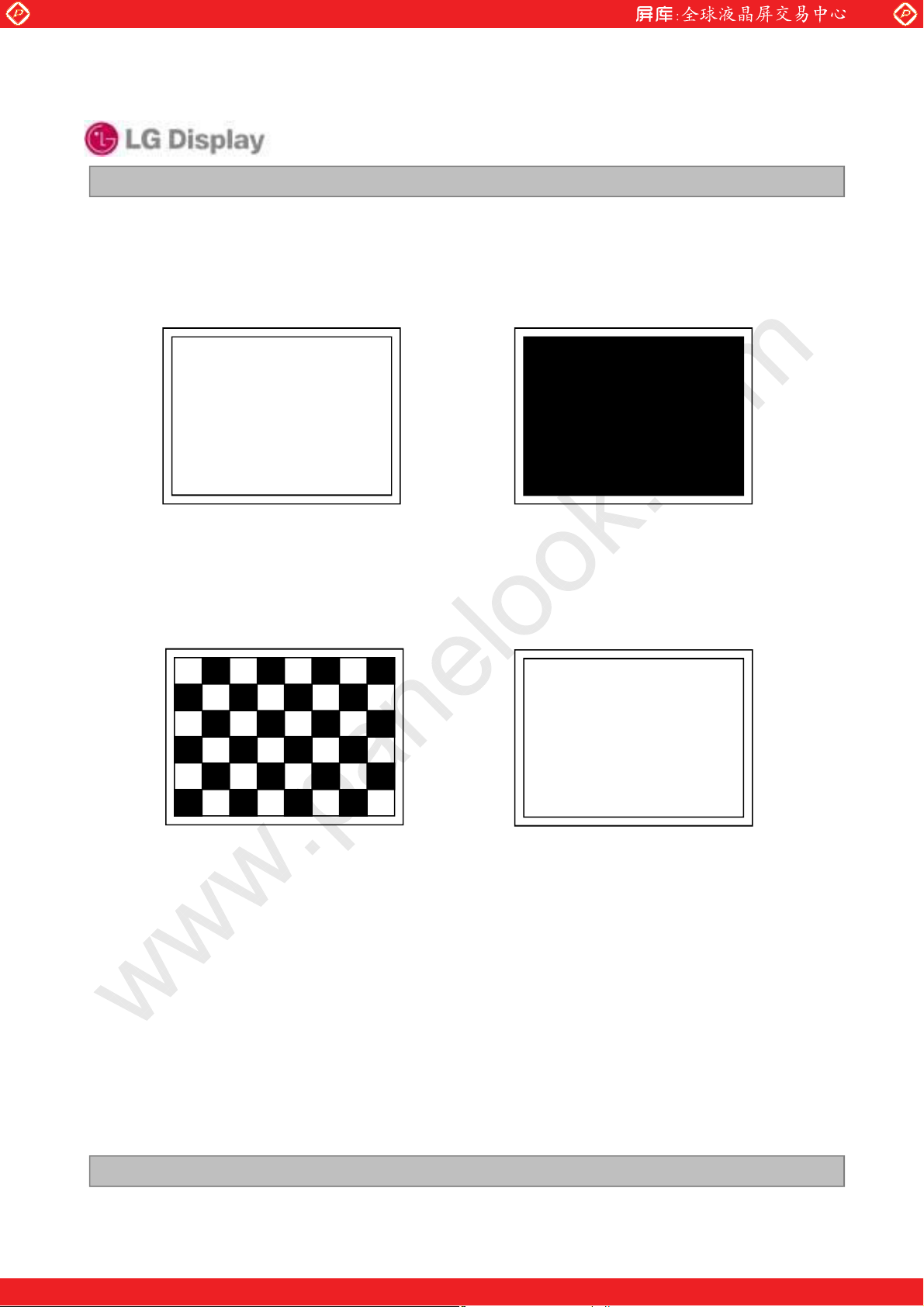

• Permissive Power input ripple (V

White pattern

• Power consumption (V

=12V, 25C, fV (frame frequency=60Hz condition)

LCD

=12.0V, 25C, fV(frame frequency)=MAX condition)

LCD

Black pattern

Typical power Pattern

[ Figure 3 ] Mosaic pattern & White Pattern for power consumption measurement

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Maximum power Pattern

8/32

www.panelook.com

Global LCD Panel Exchange Center

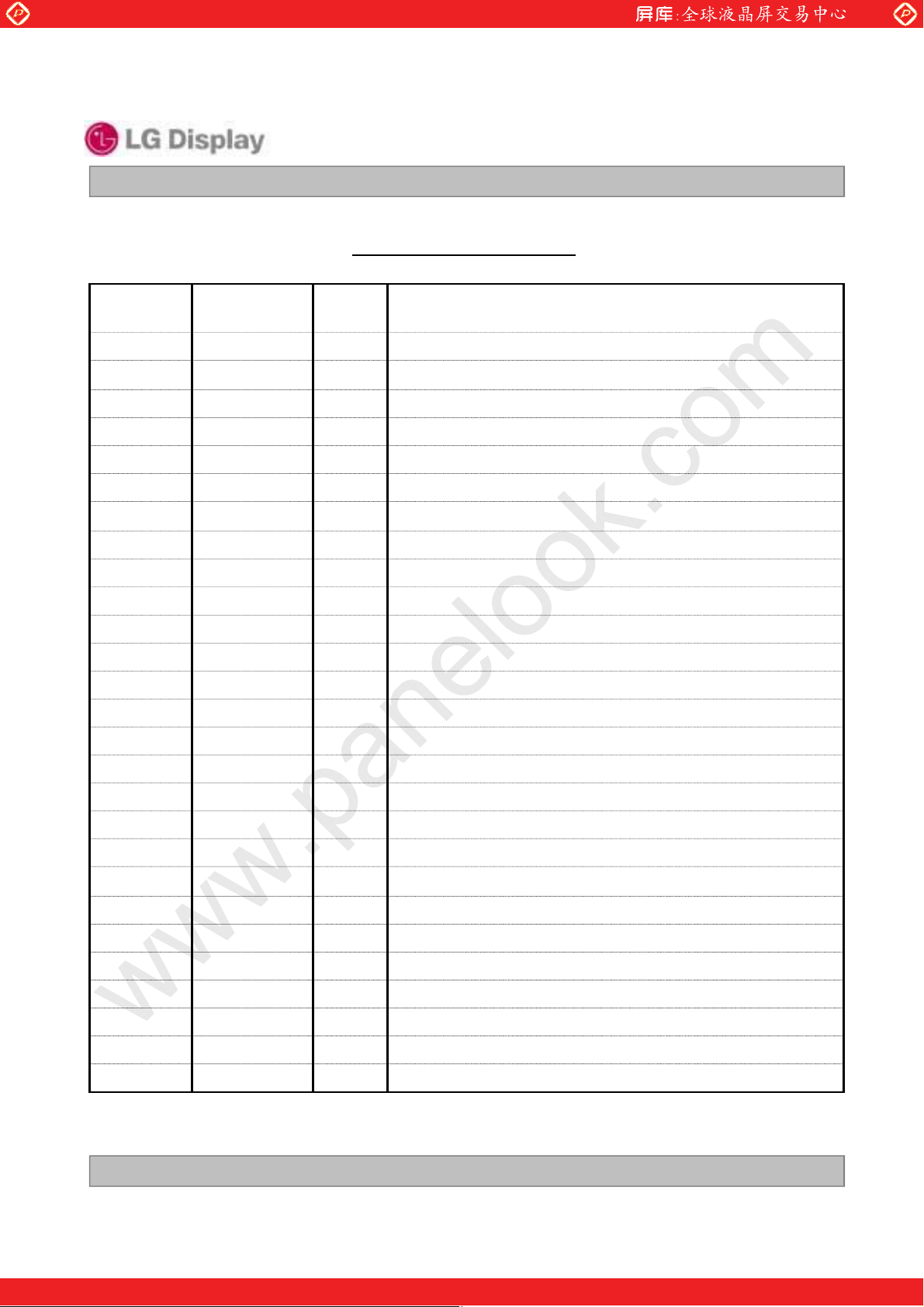

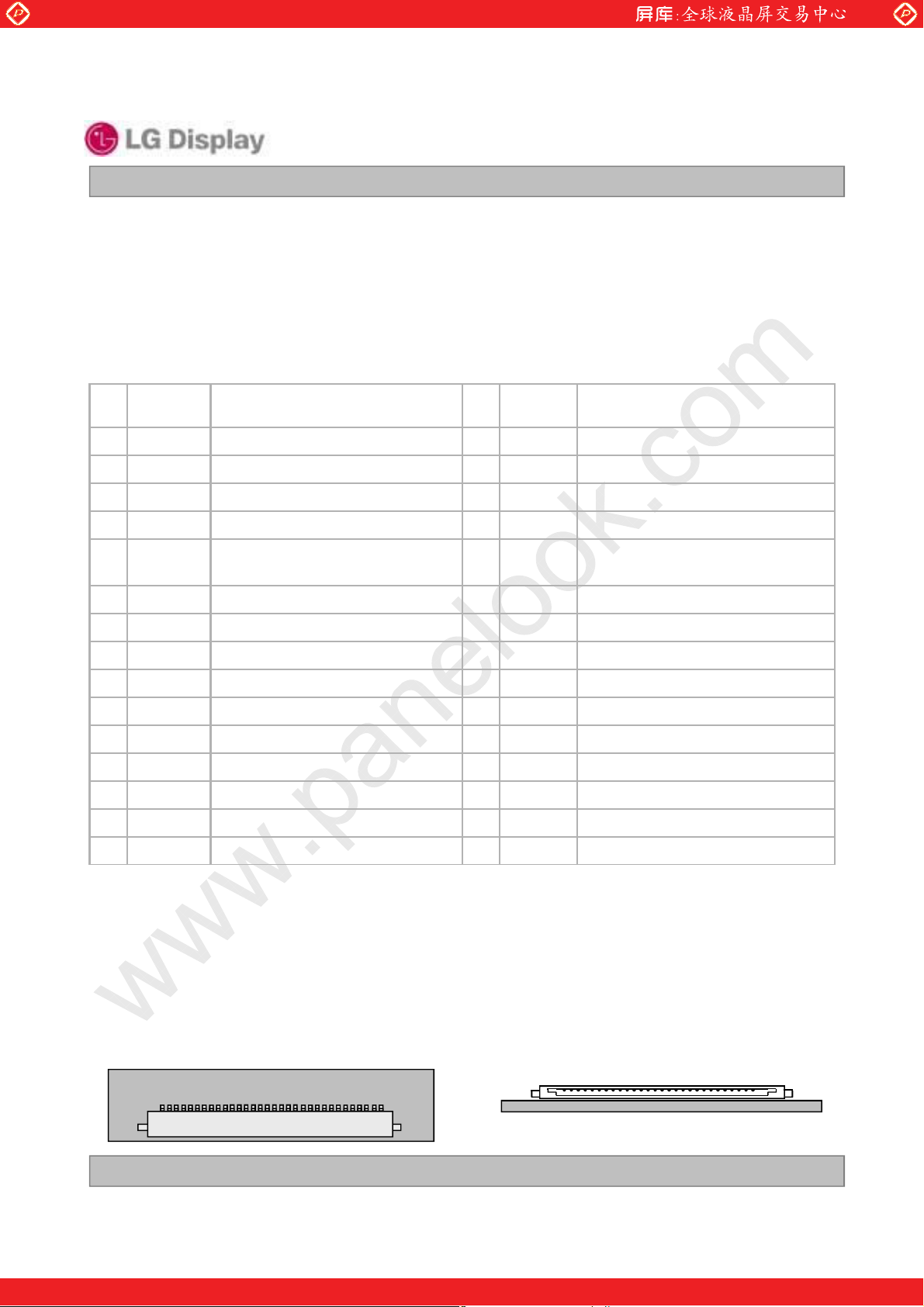

3-2. Interface Connections

3-2-1. LCD Module

-LCD Connector(CN1). IS100-L30B-C23(UJU), GT103-30S-H23 (LSC)

- Mating Connector : FI-XC30C2L (Manufactured by JAE) or Equivalent

Table 3 MODULE CONNECTOR(CN1) PIN CONFIGURATION

No Symbol Description No Symbol Symbol

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

FR0M

FR0P

FR1M

FR1P

FR2M

FR2P

GND

FCLKINM

FCLKINP

FR3M

FR3P

SR0M

SR0P

GND

SR1M

Minus signal of odd channel 0 (LVDS)

Plus signal of odd channel 0 (LVDS)

Minus signal of odd channel 1 (LVDS)

Plus signal of odd channel 1 (LVDS)

Minus signal of odd channel 2 (LVDS)

Plus signal of odd channel 2 (LVDS)

Ground

Minus signal of odd clock channel (LVDS)

Plus signal of odd clock channel (LVDS)

Minus signal of odd channel 3 (LVDS)

Plus signal of odd channel 3 (LVDS)

Minus signal of even channel 0 (LVDS)

Plus s ignal of even channel 0 (LVD S)

Ground

Minus signal of even channel 1 (LVDS)

16

SR1P

17

GND

18

SR2M

19

SR2P

SCLKIN

20

M

21

SCLKINP

22

SR3M

23

SR3P

24

GND

25

NC

26

NC

PWM_OUT For Control Burst frequency of Inverter

27

28

VLCD

29

VLCD

30

VLCD

Plus signal of even channel 1 (LVDS)

Ground

Minus signal of even channel 2 (LVDS)

Plus signal of even channel 2 (LVDS)

Minus signal of even clock channel (LVDS)

Plus signal of even clock chann el (LVDS)

Minus signal of even channel 3 (LVDS)

Plus signal of even channel 3 (LVDS)

Ground

No Connection (I2C Serial interface for LCM)

No Connection.(I2C Serial interface for LCM)

Power Supply +12.0V

Power Supply +12.0V

Power Supply +12.0V

Note: 1. All GND(ground) pins should be connected together and to Vss which should also be connected to

the LCD’s metal frame.

2. All V

LCD (power input) pins should be connected together.

3. Input Level of LVDS signal is based on the IEA 664 Standard.

4. PWM_OUT signal controls the burst frequency of a inverter.

This signal is synchronized with vertical frequency.

It’s frequency is 3 times of vertical frequency, and it’s duty ratio is 50%.

If you don’t use this pin, it is no connection.

[ Figure 4 ] User Connector diagram

IS100-L30B-C23(UJU)

#1 #30

#1 #30

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

9/32

www.panelook.com

Global LCD Panel Exchange Center

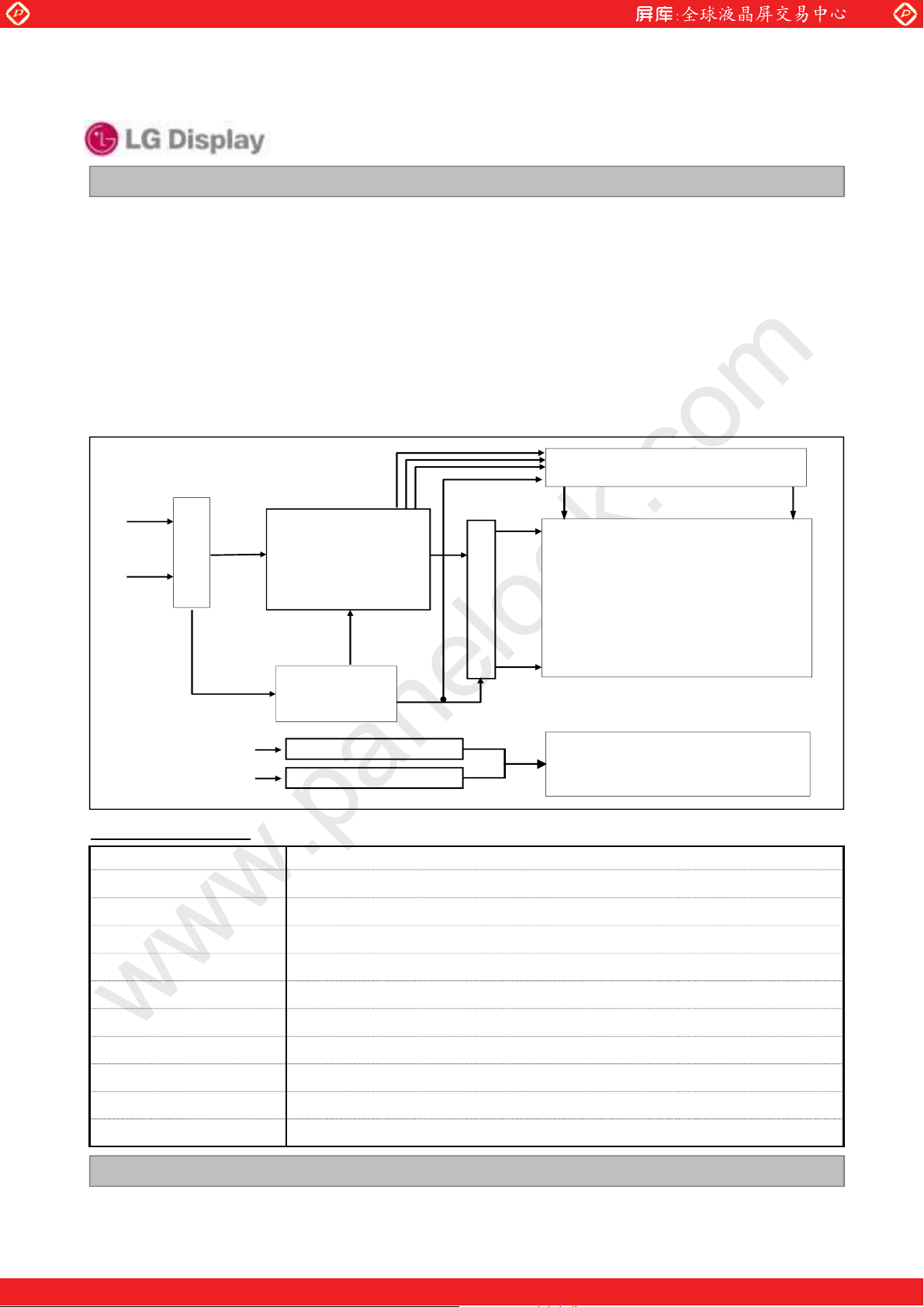

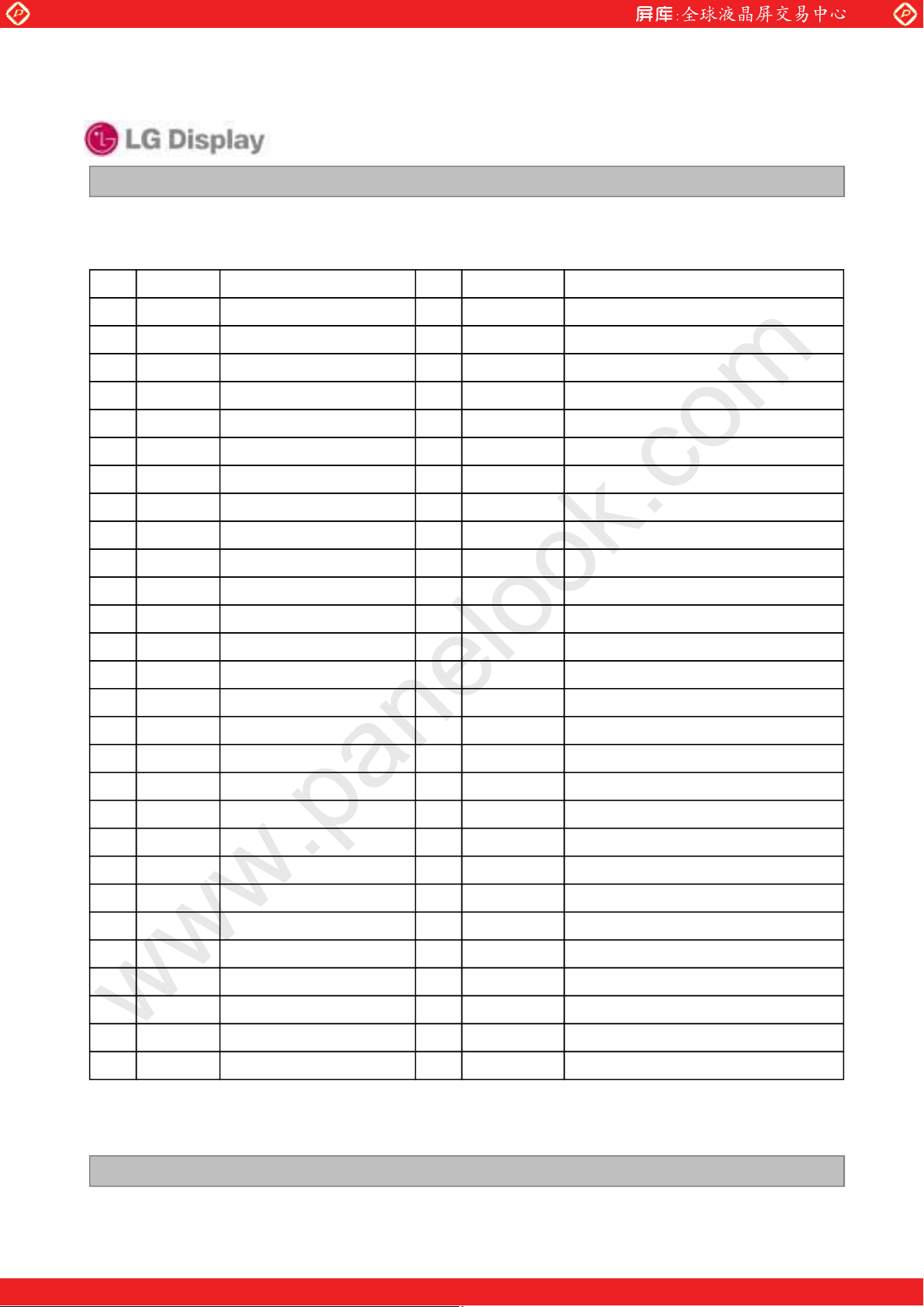

Table 4. REQUIRED SIGNAL ASSIGNMENT FOR Flat Link (TI:SN75LVDS83) Transmitter

Pin # Require SignalPin Name Pin # Require SignalPin Name

1 Power Supply for TTL InputVCC 29 Ground pin for TTLGND

2 TTL Input (R7)D5 30 TTL Input (DE)D26

3 TTL Input (R5)D6 31 TTL Level clock InputTXCLKIN

4 TTL Input (G0)D7 32 Power Down InputPWR DWN

5 Ground pin for TTLGND 33 Ground pin for PLLPLL GND

6 TTL Input (G1)D8 34 Power Supply for PLLPLL VCC

www.panelook.com

LM215WF2

Liquid Crystal Display

Product Specification

7 TTL Input (G2)D9 35 Ground pin for PLLPLL GND

8 TTL Input (G6)D10 36 Ground pin for LVDSLVDS GND

9 Power Supply for TTL InputVCC 37 Positive LVDS differential data output 3

10 TTL Input (G7)D11 38 Negative LVDS differential data output 3

11 TTL Input (G3)D12 39 Positive LVDS differential clock output

12 TTL Input (G4)D13 40 Negative LVDS differential clock output

13 Ground pin for TTLGND 41 Positive LVDS differential data output 2

14 TTL Input (G5)D14 42 Negative LVDS differential data output 2

15 TTL Input (B0)D15 43 Ground pin for LVDSLVDS GND

16 TTL Input (B6)D16 44 Power Supply for LVDSLVDS VCC

17 Power Supply for TTL InputVCC 45 Positive LVDS differential data output 1

18 TTL Input (B7)D17

19 TTL Input (B1)D18

20 TTL Input (B2)D19

22 TTL Input (B3)D20

23 TTL Input (B4)D21

46 Negative LVDS differential data output 1

47 Positive LVDS differential data output 0

48 Negative LVDS differential data output 0

49 Ground pin for LVDSLVDS GND21 Ground pin for TTL InputGND

50 TTL Input (R6)D27

51 TTL Input (R0)D0

TxOUT3

TxOUT3

TXCLKOUT

TXCLKOUT

TXOUT2

TXOUT2

TXOUT1

TXOUT1

TXOUT0

TXOUT0

24 TTL Input (B5)D22

25 TTL Input (RSVD)D23

26 Power Supply for TTL InputVCC 54 TTL Input (R2)D2

52 TTL Input (R1)D1

53 Ground pin for TTLGND

55 TTL Input (R3)D327 TTL Input (HSYNC)D24

56 TTL Input (R4)D428 TTL Input (VSYNC)D25

Notes : 1. Refer to LVDS Transmitter Data Sheet for detail descriptions.

2. 7 means MSB and 0 means LSB at R,G,B pixel data

Ver. 1.0 Nov. 29 . 2010

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

10 / 32

www.panelook.com

Loading...

Loading...