LG XXLA74*-Z, XXLA71*-Z, XXLA69/66*-Z, XXLA64/62/61*-Z, XXLN57*-Z Schematic

2013 LED/LCD TV

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Engineering guide

< Applicable Model : Mid-end Platform >

XXLA74*-Z*

XXLA71*-Z*

XXLA69/66*-Z*

XXLA64/62/61*-Z*

XXLN57*-Z*

1/ 88

◈ CONTENT ◈

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

1. New features

2. Main PCBs

3. Block Diagrams, IIC Map

4. Structure of TV set and connection of sub ass’ys

5. New sub ass’ys

- Instruction of new sub ass’ys

6. Adjust way of new features

7. Repair guide

2/ 88

EPI Interface

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

EPI(Embedded Point-Point Interface)

Features

• Point-Point topology (support 2 Pair option)

• CDR (Clock Data Recovery)

• Bandwidth up to 1.85Gbps/pair

at FHD 120Hz 10 bit application

• Lock signal cascading and feedback to T-Con

• Embedded Control Data

Merits

VCC

TCON

LOCK

2

1

Figure1. Topology

• Better reliability on common noise

• No data skew and better EMI margin

• Fewer lines than mini-LVDS

• Slim PCB design

3/ 88

EPI Interface (mini-LVDS vs. EPI)

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Comparison

HF mini-LVDS

HF mini-

LVDS

No. of Signal 36 36 72

Connector

60Hz 120Hz 240Hz

60pin

(2ea)

-Difficult to upgrade bandwidth limit

-Multiple number of wires needed for higher bandwidth

EPI (Embedded clock P-to-P Interface)

EPI

No. of Signal 12 12 32

Connector -

-Better reliability on common noise

-No data skew. Better EMI margin

-Lower cost ( Cable, Connector )

-Slim S-PCB design (14mm Æ 10mm) helps slimmer TV

60Hz 120Hz 240Hz

960ch 960ch 720ch

FHD (10bit)

60pin

(2ea)

FHD (10bit)

50 pin

(2ea)

80pin

(2ea)

70pin

(2ea)

What to change

LCM (T-con to S-Driver IC)

HF mini-LVDS

18

VCC

1

EPI

2

VCC

* Bandwidth Capability

- FHD 120Hz 10Bit : 594Mbps@36Lines → 1.65Gbps@12Lines

- FHD 240Hz 10Bit : 594Mbps@72Lines → 1.25Gbps@32Lines

1

TCON

18

(FHD 120Hz)

TCON

LOCK

(FHD 120Hz)

4/ 88

EPI Interface (mini-LVDS vs. EPI)

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

HF mini-LVDS EPI

Topology

Protocol

Features

@10bit, FHD120

Merit

TCON

• Multi Drop

• Data rate: 660Mbps

• External clock

• Simple structure

• Standardization

TCON

2

1

• Point to Point

• Data rate : 1.8Gbps

• Embedded clock, Control

• Fewer Lines : 12

• Embedded clock

: low EMI, Clock skew free

Lock

Demerit

• Too many lines : 36

• Clock skew

• EMI due to clock lines

• Bandwidth limit

• Easy to PCB design

• Transmission Overhead

: 4bit delimiter

5/ 88

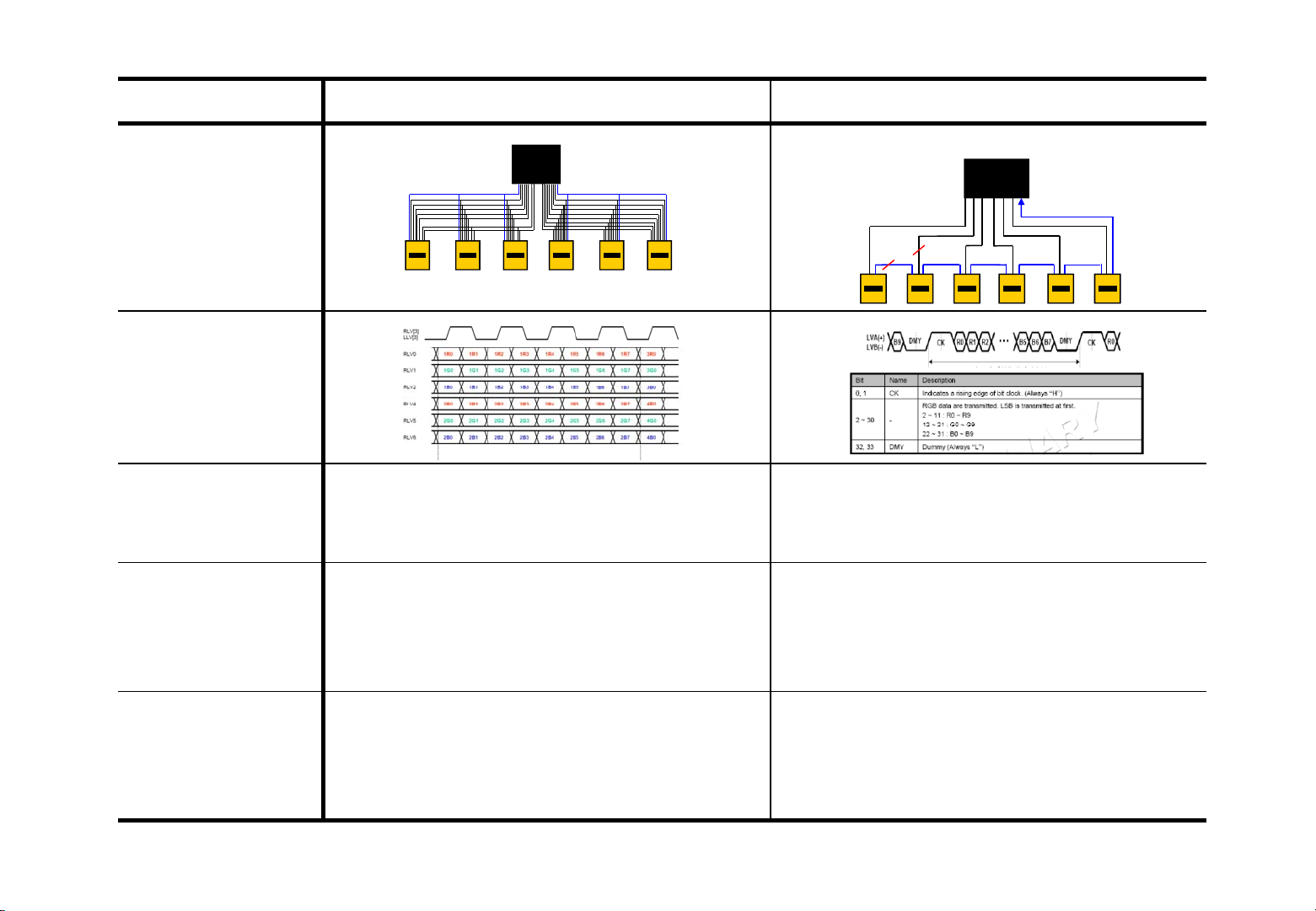

NFC (Near field communication)

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Near field communication (NFC) is a set of standards for smartphones and similar devices to establish radio communication

with each other by touching them together or bringing them into close proximity, usually no more than a few centimetres.

Present and anticipated applications include contactless transactions, data exchange, and simplified setup of more complex

communications such as Wi-Fi. Communication is also possible between an NFC device and an unpowered NFC chip, called

a "tag".

From Smart phone

to TV

User Action Area

Samrt phone close to

NFC Tag

Player choose

From TV

to Smart phone

6/ 88

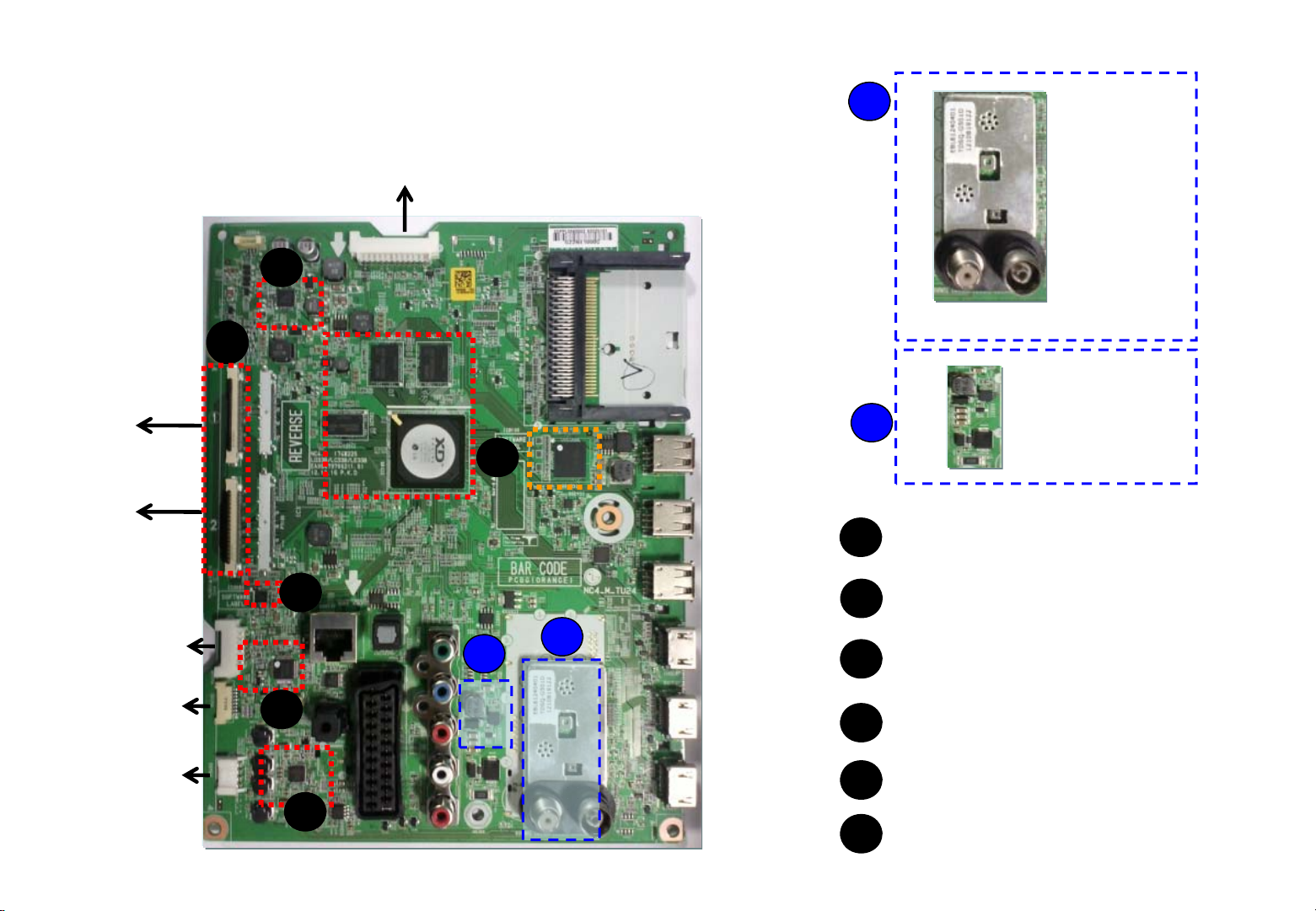

Main PCB for Broadband

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

xxLA660S-Zx

To PSU

3

5

Main + TCON all in one

1

Chassis : LD33B

PCB P/No : EAX64797003

S

model

To module

6

WIFI/BT

Key+IR

2

Front Spk

4

2

Only S model

1

LNB IC Block

Main processor, DDR Memory

1

eMMC Memory

Micom for Key/IR sensing

2

1

2

3

4

5

6

PMIC

Audio AMP

EPI Wafer

Level shifter

7/ 88

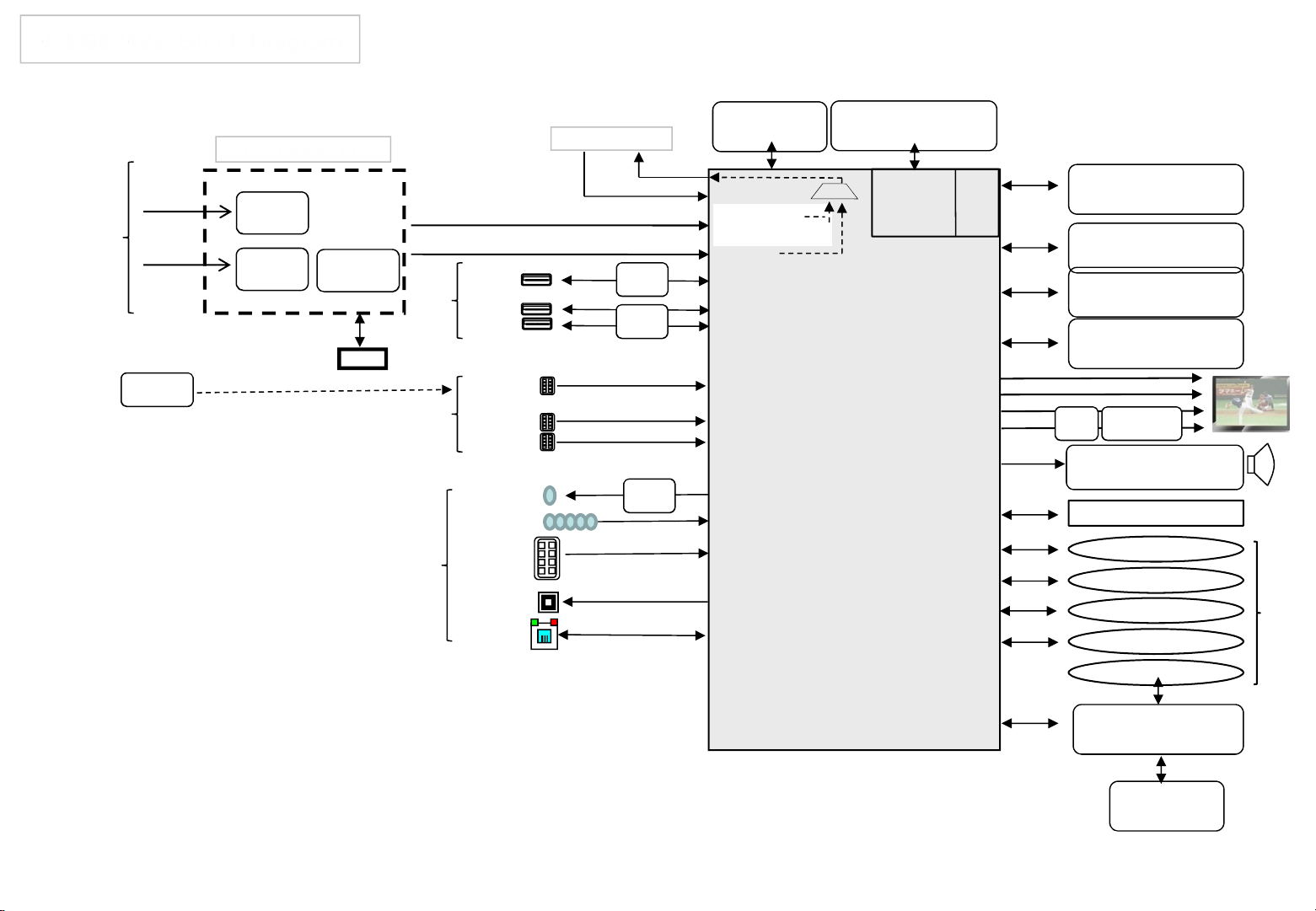

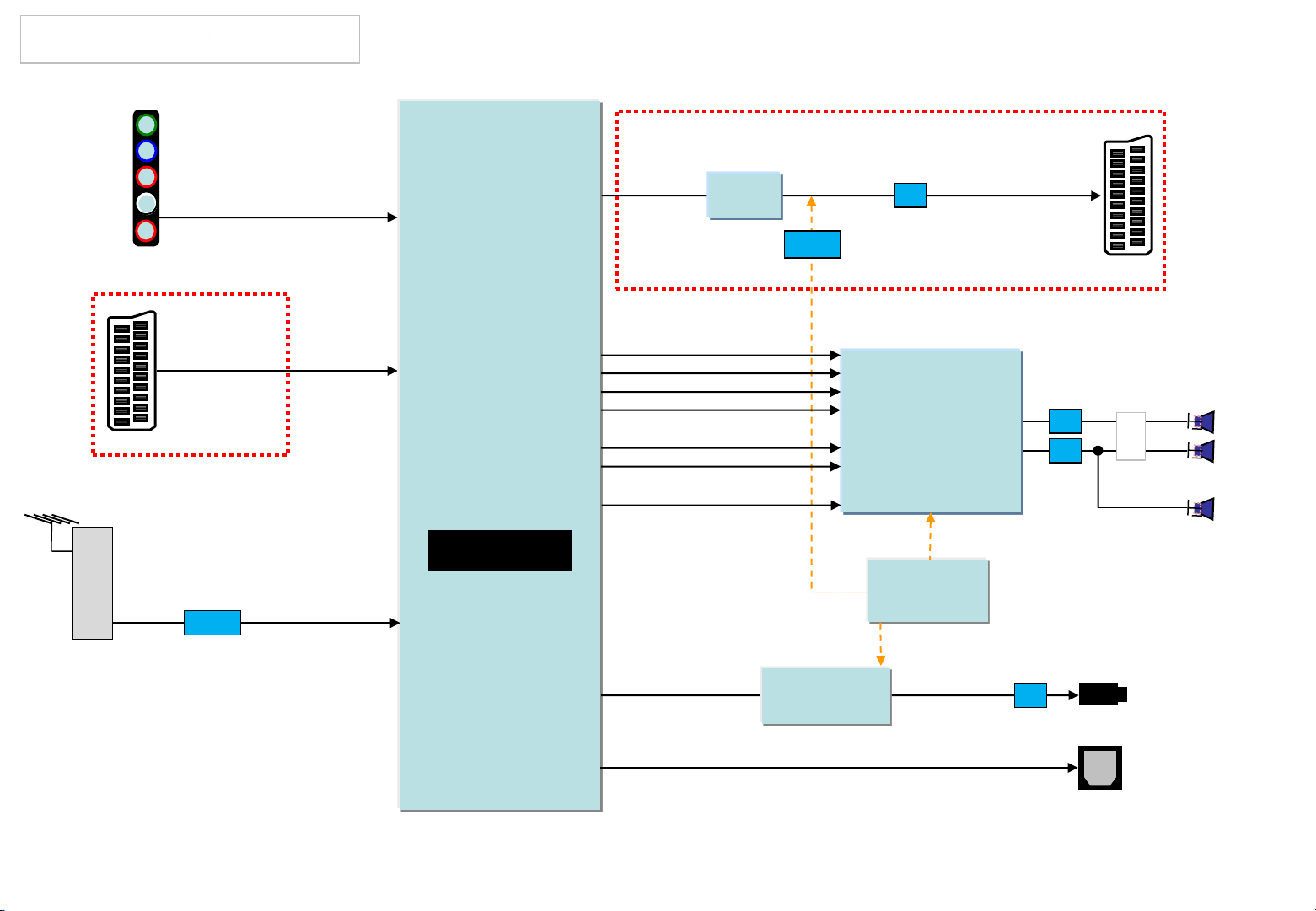

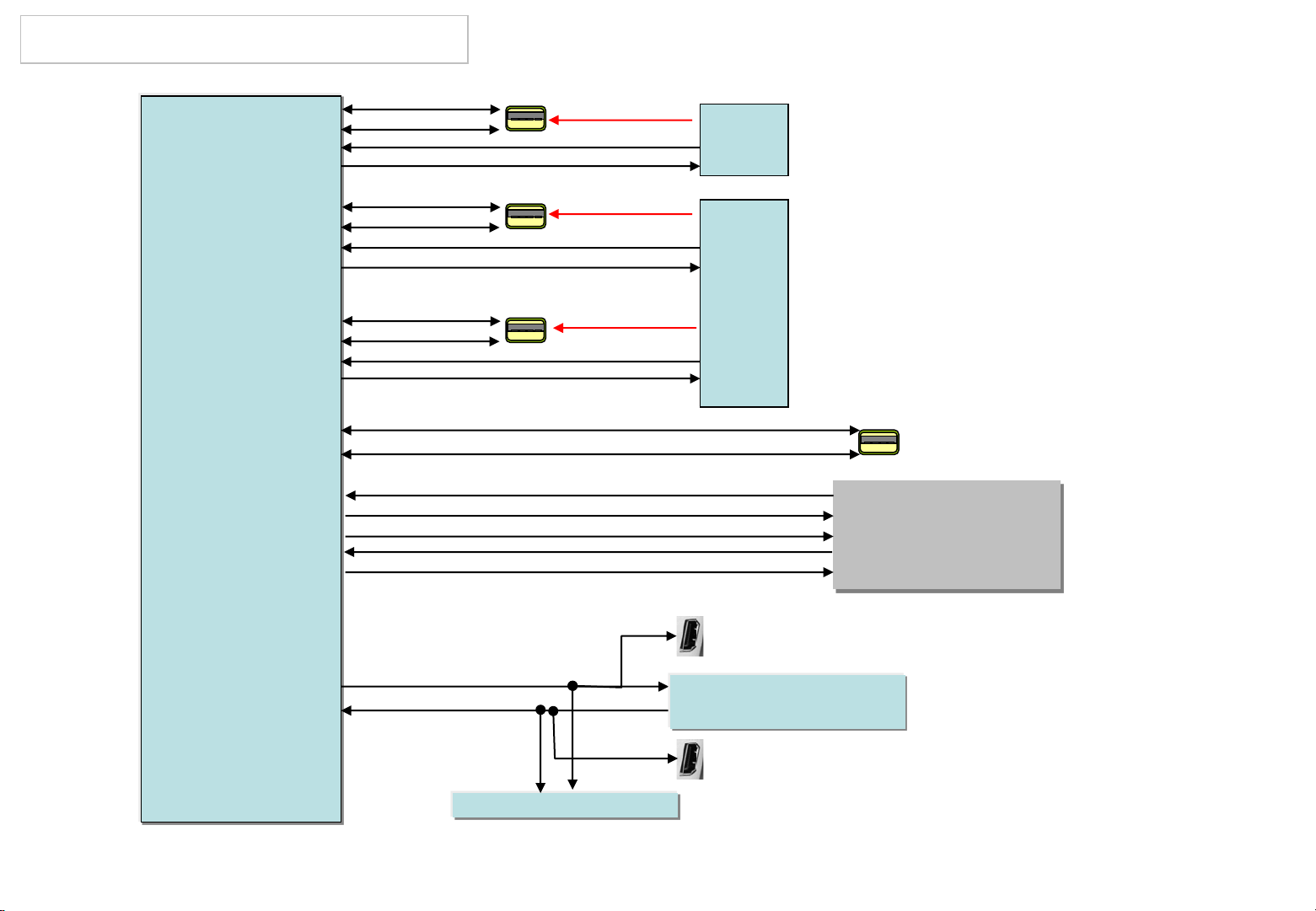

1. LGE2122 Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Cable

R

E

A

DVB-S

R

(H)

MHL 1A

SIL1392

MHL : I2C 4

Air/

T/C/S2 Without ATV

TUNER

(T/C/A)

TUNER

(S2)

DVB-S : I2C 4

MHL

DEMOD

(S2)

LNB

Tuner : I2C 6

USB1

S

(HDD)

I

USB2

D

USB3

E

HDMI1

S

I

HDMI2

D

HDMI3

E

H/P

AV/COMP

R

SCART

E

A

R

OPTIC

LAN

CI Slot

P_TS

IF (+/-)

P_TS

OCP

2.5A

OCP

1A

AMP

TI

P_TS

X_TAL

27MHz

T/C Demod

Analog Demod

P_TS

USB

HDMI

MUX

CVBS/YPbPr

CVBS/RGB

SPDIF OUT

ETHERNET

DDR3 1600 X 16

(512MB X 2EA)

LGE 2122

A B

I2C 5

I2C 1

LVDS

EPI

I2C 2

I2S Out

I2C 1

I2C 1

UART

KEY

USB_WIFI

DDR3 1600 X 16

(256MB X 1EA)

SYSTEM EEPROM

(256Kb)

HDCP EEPROM

(16Kb)

eMMC

(4GB)

51P

41P

50P

50P

IR

PM ICLEVEL

SHIFTER

Audio AMP

(NTP7513)

LOCAL DIMMING

BLUTOOTH

IR / NFC

KEY

WIFI

LOGO LIGHT

SUB

ASSY

I2C 3

Sub Micom

(RENESAS R5F1000G)

X_TAL

32.768KHz

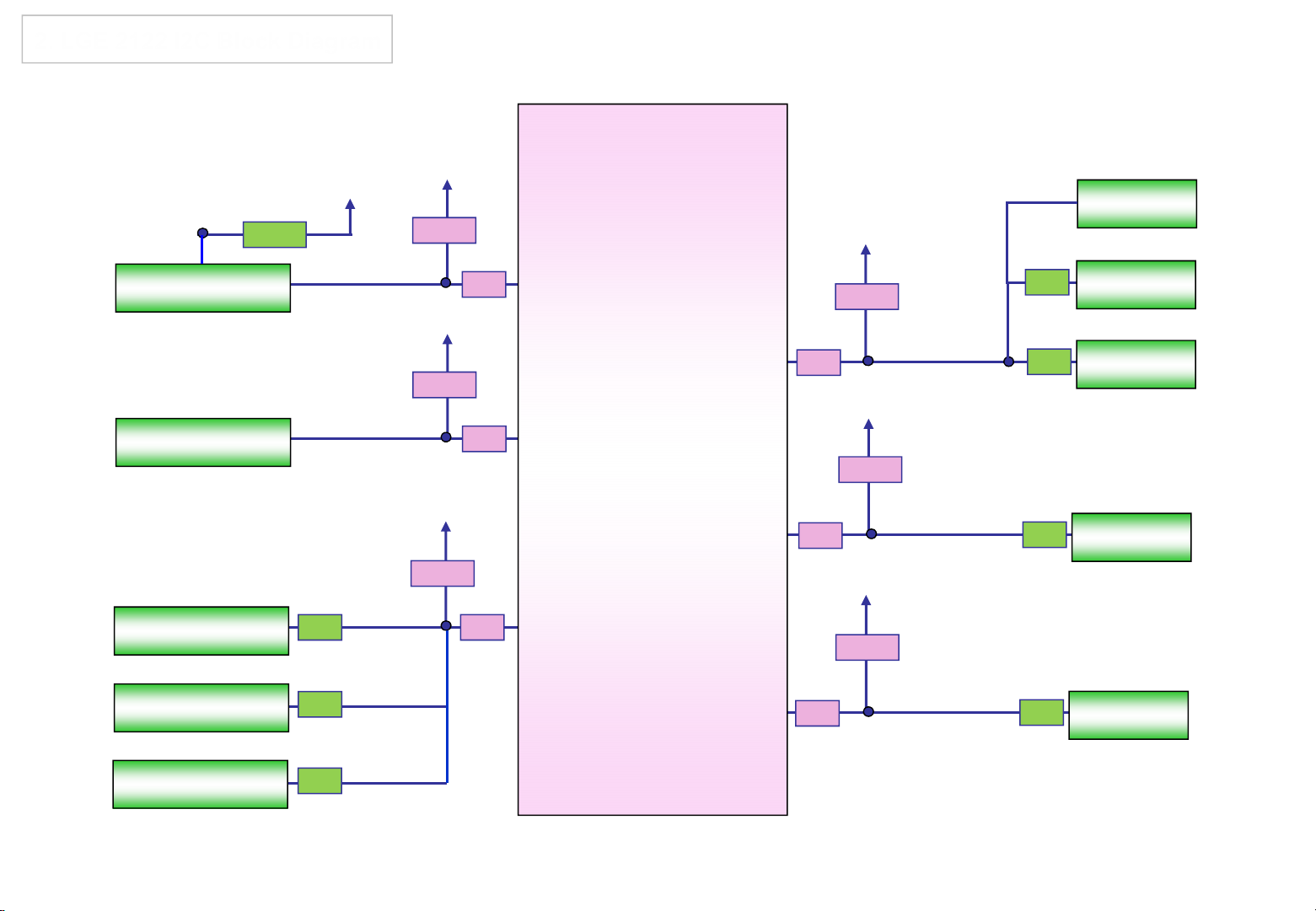

2. LGE 2122 I2C Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

IC3000

Renesas MICOM

IC7700

PMIC

IC8101

NTP7513(AMP)

3.3KΩ

+3.5V_ST

100Ω

+3.3V_Normal

2.7KΩ

33Ω

+3.3V_Normal

2.7KΩ

33Ω

+3.3V_Normal

1.2KΩ

33Ω

IC105

LGE 2122

I2C_SDA3

I2C_SCL3

I2C_SDA2

I2C_SCL2

I2C_SDA1

I2C_SCL1

I2C_SDA4

I2C_SCL4

I2C_SDA5

I2C_SCL5

+3.3V_Normal

2.7KΩ

33Ω

+3.3V_Normal

2.7KΩ

33Ω

+3.3V_Normal

2.7KΩ

33Ω

22Ω

33Ω

IC3304

MHL

LNB

TUNER(S)

IC100

NVRAM

P7600

Local dimming

IC101

HDCP EEPROM

33Ω

22Ω

I2C_SDA6

I2C_SCL6

33Ω

33Ω

TUNER(D)

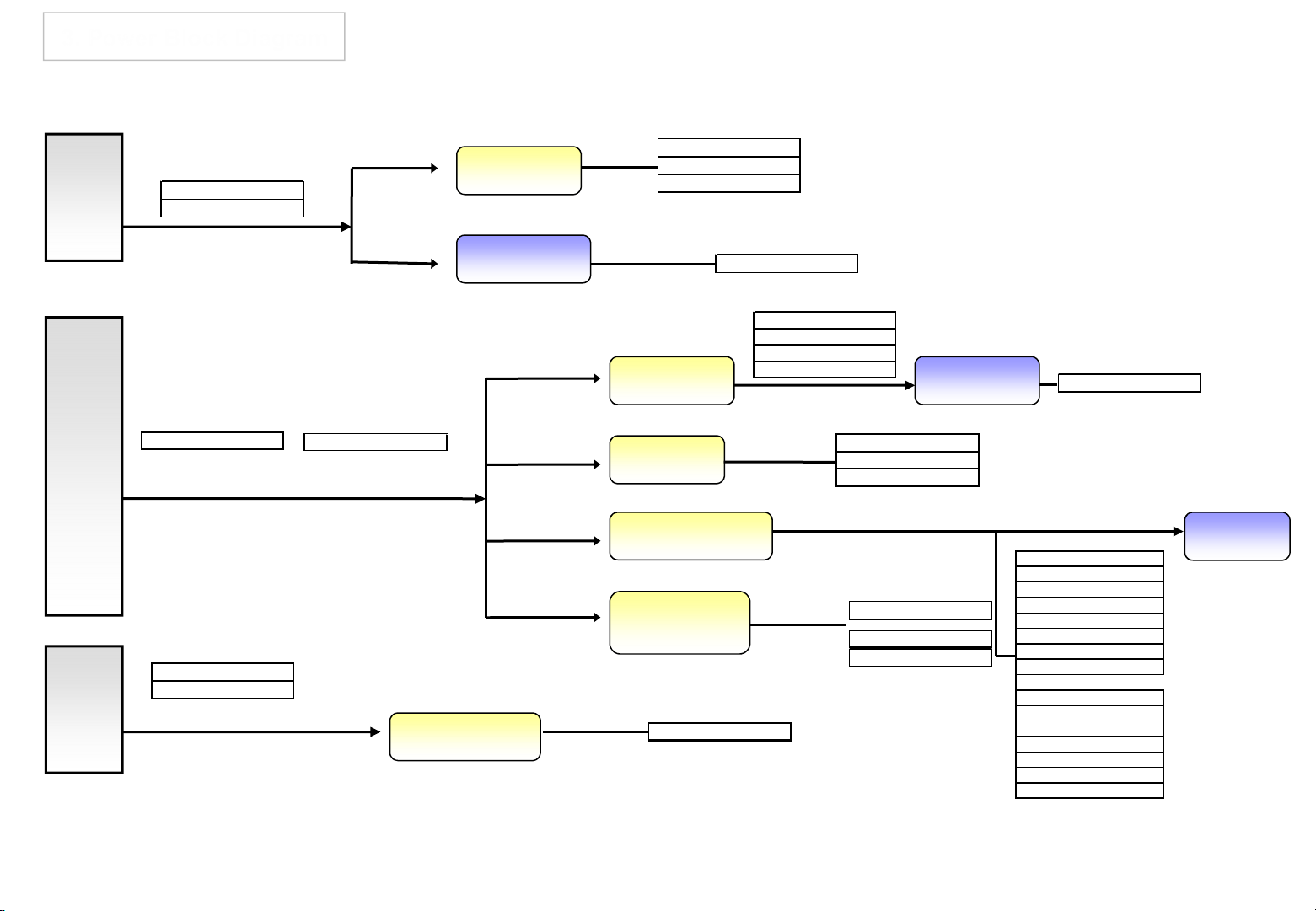

3. Power Block Diagram

(

)

y

(

)

)

)

L

)

)

A

(

)

Q)

T

)

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

3.5V

12V

24V

MICOM(VDD)

IR A'ssy

PANEL_VCC

PANEL_POWER

NTP_7400(PVDD1)

NTP_7400(PVDD2)

AMP

+12V_LNB

LNB option

1.5V DDR

5V USB 3A

3A

1.23V

2A

MTK (DDRV)

DDR(VDD)

DDR(VDDQ)

TUNER(+1.23V)

5V Normal

3A

1.2V Core

6A

3.3V Noraml

4A

5V USB

1CH DCDC 4A

2CH OCP 1.2A

USB1(DVR Max 1.5A

HDMI_EEPROM

RGB_EEPROM

CI (+5V_CI_ON)

TUNER(+5V_TU)

MTK(AVDD12_LVDS)

MTK

MTK(VCCK)

AVDD_

USB_WIFI

USB2(Max 1.2A)

USB3(Max 1.2A)

3.3V DAC

MTK(AVDD33_DAC)

SPDIF

IR A'ss

M_REMOTE

HDCP EEPROM

NVRAM

DVDD3V3

MTK

MTK (AVDD33_AADC

MTK (AVDD3V3

MTK(AVDD3V3_MEMPL

MTK(AVDD3V3_LVDS

MTK(AVDD33_STB

UDIO AMP

EARPHONE AMP

VCC

EMMC

EMMC(VCC

UNER(+3.3V_TU)

1.8V_TU

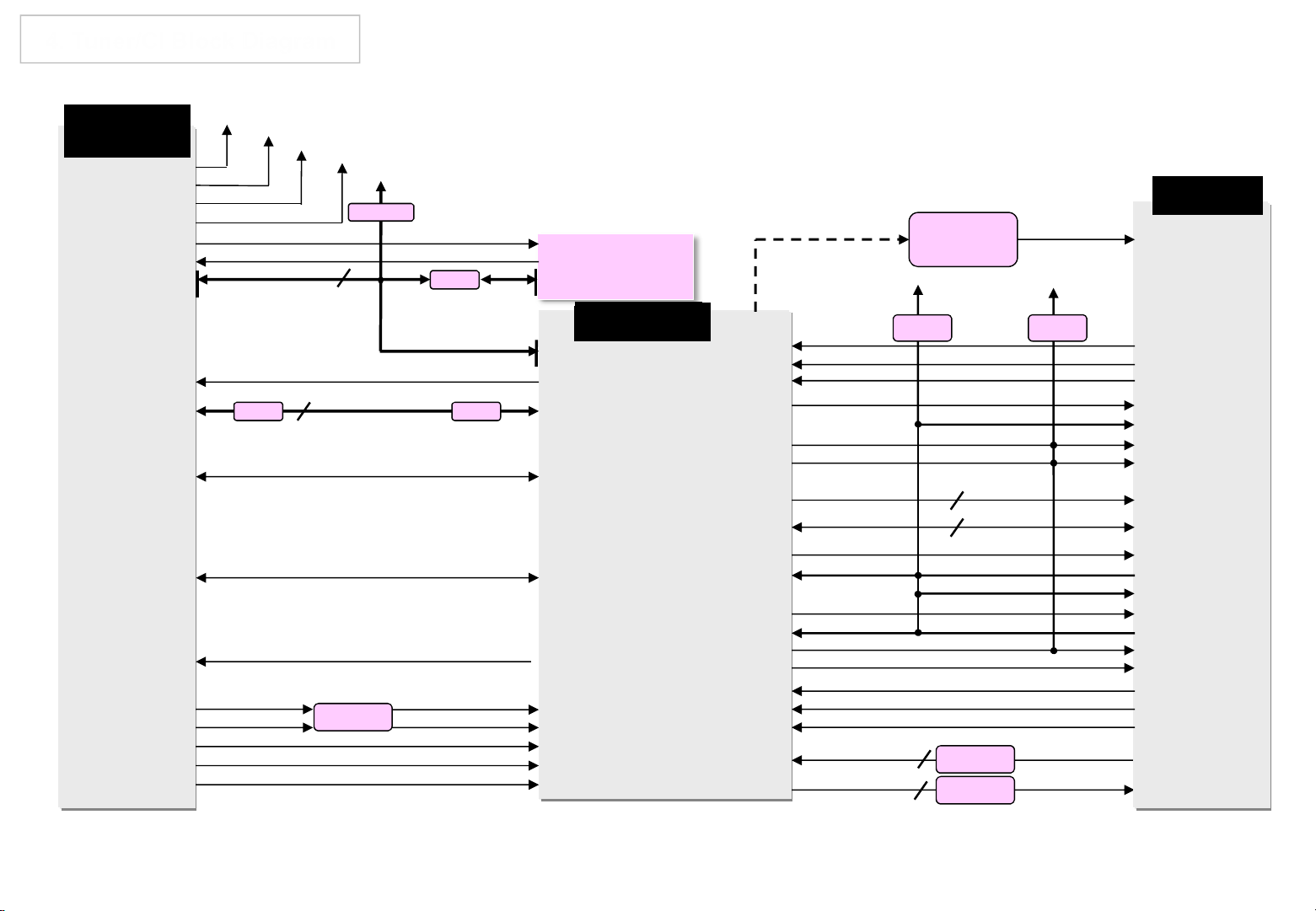

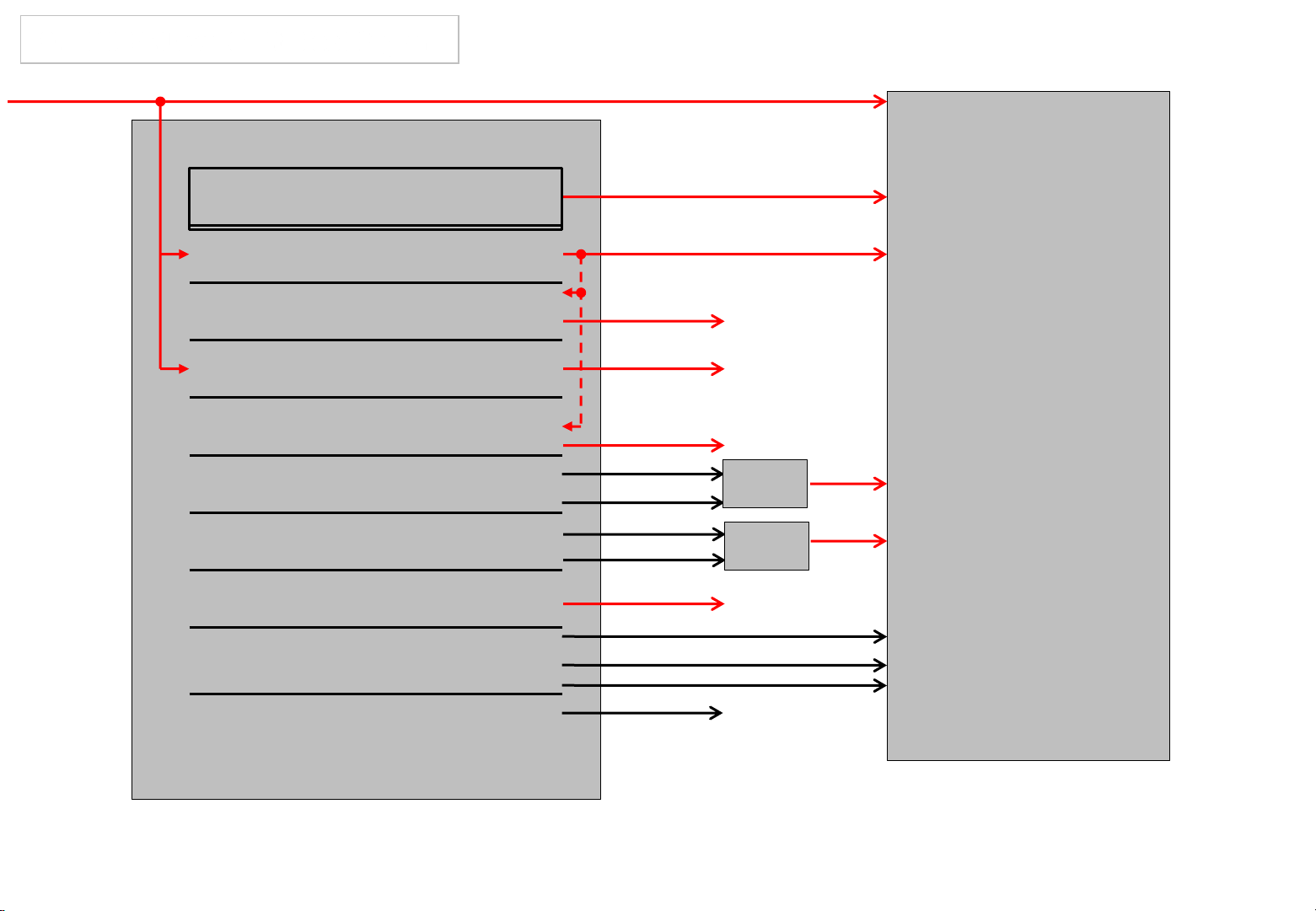

4. Tuner/CI Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

TDSQG501D

[+3.3V_S2_DEMOD] 32

[+3.3V_TUNER] 5

[+.1.8V_TUNER] 7

[+1.23V_S2_DEMOD] 30

[S2_F22_OUTPUT] 33

[LNB] 36

[S2_SCL] 34

[S2_SDA] 35

+3.3V_D_Demod

+3.3V_TU

+1.8_TU

+1.23V_D_Demod

LNB_TX

LNB_OUT

I2C_SCL4

+3.3V_NORMAL

3.3K Ω

22 Ω

10 [TONECTRL]

2 [LNB]

7 [SCL]

8 [SDA]

I2C_SDA4

[RESET] 2 AG24 [ADIN6_SRV]

[SLC] 3

[SDA] 4

[ERROR] 16

[SYNC] 17

[VALID] 18

[MCLK] 19

/TU_RESET1

IC2_SDA6

IC2_SCL6

FE_DEMOD1_TS_SYNC

FE_DEMOD1_TS_VAL

FE_DEMOD1_TS_CLK

33 Ω33Ω

FE_DEMOD1_TS_DATA [0-7]

[D0-7] 20-27

[S2_RESET] 31 AM18 [ADIN7_SRV]

[T/C_DIF[P]] 10

[T/C_DIF[N]] 11

IF_P

IF_N

/S2_RESET

Attenuator

TUNER_SIF(for T2/C/S)

ADCINP_DEMOD

ADCINN_DEMOD

AM27 [ADCINP_DEMOD]

AN27 [ADCINN_DEMOD]

TU_CVBS(for

T2/C/S)

IF_AGC

A8303SESTR-TB

IC6900

LGE 2122

AP6 [S CL3]

AR6 [S DA3]

AF19[OPCTRL1]

AJ19 [OPCTRL0]

R29 [DEMOD_TSSYNC]

P27 [DEMOD_TSVAL]

P30 [DEMOD_TSCLK]

[DEMOD_TSDATA0-7]

LNB

T34[DEMOD_RST]

P34[PVR_TSDATA1]

P33[PVR_TSDATA0]

R33[PVR_TSSYNC]

R35[CI_TSDATA0]

PCM_5V_CTL

CI 5V

Power detect

+5V_CI_ON

VCC

+5V_CI_ON +3.3V_NORMAL

F28[TCON12]

L33[SPI_CLK]

L30[SPI_CLK1]

M31[CI_TSCLK] CARD_EN1

N34[SPI_DATA]

N35[SPI_CLE]

[GPIO0-14]

[GPIO26-33]

N36[CI_INT]

R36[CI_TSVAL]

R37[CI_TSSYNC]

CI_ADDR[0-14] CI_A_ADDR[0-14]

CI_DATA[0-7] CI_A_DATA[0-7]

MTK5398_TS_CLK

R3[PVR_TSCLK]

[GPIO34-41] TS_OUT[0-7]

[GPIO18-25] TS_IN[0-7]

MTK5398_TS_VAL

MTK5398_TS_SYNC

MT5398_TS_IN[0-7] CI_TS_DATA[0-7]

MT5398_TS_OUT[0-7] CI_MDI[0-7]

10K Ω

/CI_CD1

/CI_CD2

CI_VS1

/PCM_CE1

/PCM_CE2

/PCM_IOWR

/PCM_IORD

PCM_RST

/PCM_WAIT

PCM_INPACK

/PCM_A_REG

/PCM_IRQA

/PCM_OE

/PCM_WE

47 Ω

47 Ω

47K Ω

CI_TS_CLK

CI_TS_VAL

CI_TS_SYNC

CI_DET1

CI_DET2

VS1M27[PVR_TS_VAL]

CARD_EN2

IOWD

IORD

ADDR[0-14]

DAT[0-7]

CI_RESET

CI_WAIT

INPACK

REG

/IRQA

O_EN

WR_EN

TS_OUT_CLK

TS_OUT_VAL

TS_OUT_SYNC

CI Slot

5. Video/Audio In Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

JK501

SCART

COMP1_Y/AV1_CVBS

COMP1_Pb

COMP1_Pr

COMP1/AV1/DVI_L_IN

COMP1/AV1/DVI_R_IN

SC_CVBS_IN

SC_ID/FB

SC_R/G/B

SC_L/R_IN

Jack Side

SoC Side

COMP1_Y/AV1_CVBS_SOC

COMP1_Pb_SOC

COMP1_Pb_SOC

COMP1/AV1/DVI_L_IN_SOC

COMP1/AV1/DVI_R_IN_SOC

SC_CVBS_IN_SOC

SC_FB_SOC

SC_R/G/B_SOC

SC_L/R_IN_SOC

[CVBS2P]

[PB0P]

[PR0P]

[AIN4_L_AADC]

[AIN4_R_AADC]

LGE 2122

[CVBS3P]

[ADIN0_SRV, SOY1]

[PR1P, PB1P, Y1P]

[AIN1_L/R_AADC]

JK4600

Tuner

TU_CVBS

TUNER_SIF, IF_P/N

Parallel TS / ERROR,VAL,SYNC,CLK

TU_CVBS

TUNER_SIF, IF_P/N

Parallel TS / ERROR,VAL,SYNC,CLK

[CVBS1P]

[MPXP, ADCINP_DEMOD, ADCINN_DEMOD]

6. Audio Out Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

COMP1/AV1/DVI_L_IN_SOC

COMP1/AV1/DVI_R_IN_SOC

JK501

SCART

[AIN4_L_AADC]

[AIN4_R_AADC]

[AL1_ADAC]

[AR1_ADAC]

SCART_L/Rout

IC6000

AZ4580MTR

OP AMP

Mute CTRL

(TR)

SCART_MUTE

LPF

SCART

DTV/MNT_L/R_OUT

JK4600

DVB only

JK4600

Tuner

SC_L_IN / SC_R_IN

DVB only

TR BUF

TUNER_SIF

[AIN1_L_AADC]

[AIN1_R_AADC]

LGE 2122

[MPXP]

[AOMCLK]

[AOSDATA0]

[AOLRCK]

[AOBCK]

[STB_SDA]

[STB_SCL]

[OPCTRL4]

[AL0_ADAC]

[AR0_ADAC]

[ASPDIF0]

AUD_MASTER_CLK

AUD_LRCH

AUD_LRCK

AUD_SCK

I2C_SDA1

I2C_SCL1

AMP_RESET_N

HP_L/ROUT_MAIN

SPDIF_OUT

IC6100

TPA6138A2PWR

HP AMP

IC8101

Audio AMP

NTP7513

AMP_MUTE

IC3000

MICOM

SIDE_HP_MUTE

HP_L/ROUT_AMP

LPF

LPF

LPF

JK3700

JK3602

4P WAFER

SPEAKER_L

SPEAKER_R

WOOFER

HEAD PHONE

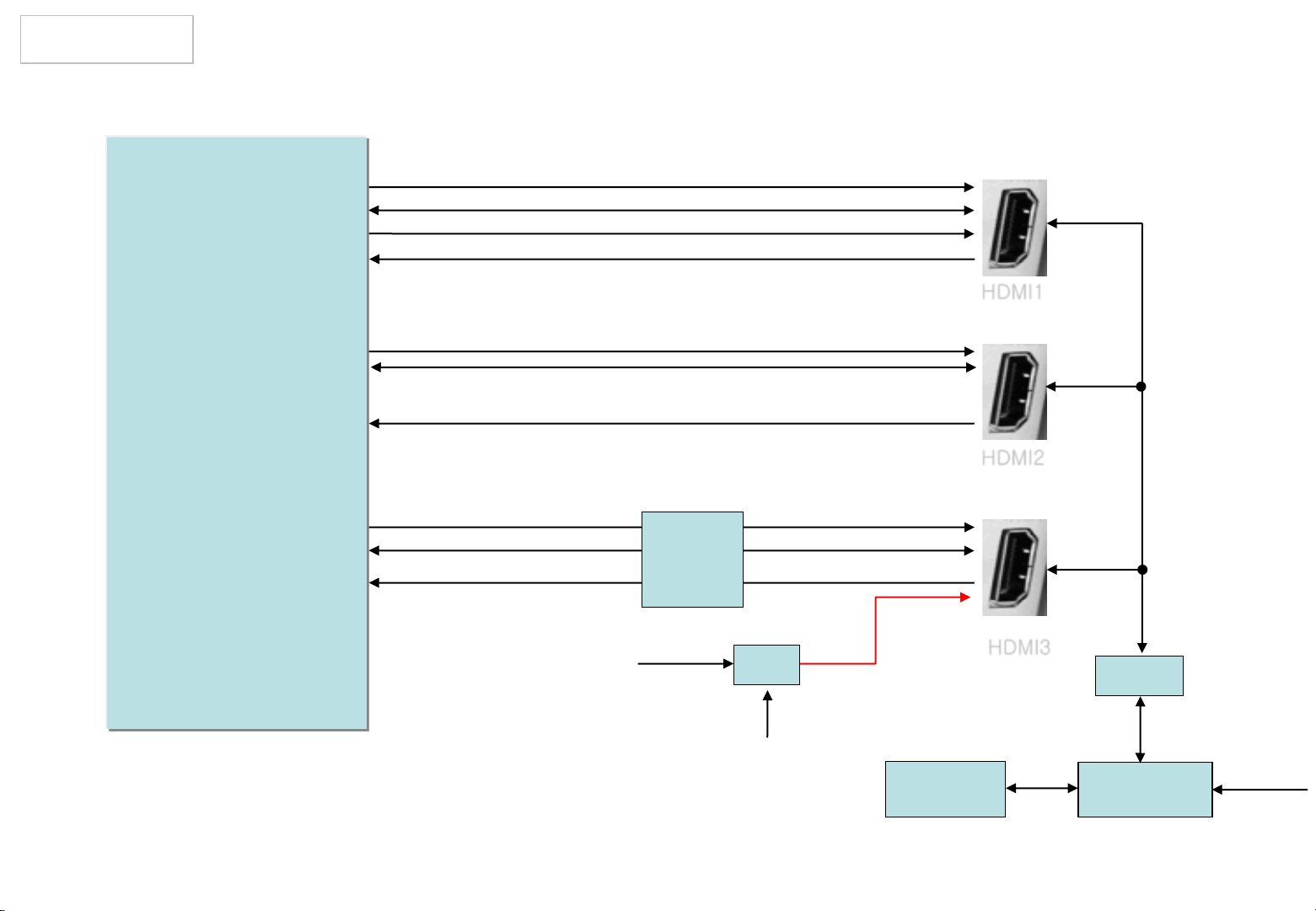

7. HDMI

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

DDC_SCL_1_SOC

DDC_SDA_1_SOC

HDMI_ARC

TMDS Link 8bits

HDMI1

LGE 2122

DDC_SCL_2_JACK

DDC_SDA_2_JACK

TMDS Link 8bits

I2C_SCL4

I2C_SDA4

TMDS Link 8bits

SIL1292

5V_MHL

OCP

MHL_DET

DDC_SCL_3_JACK

DDC_SDA_3_JACK

TMDS Link or MHL Link

5V_BUS

X-tal

32.768kHz

HDMI2

HDMI3

CEC_REMOTE

Q3001

HDMI_CEC

RENESAS

MICOM

WOL_CTL

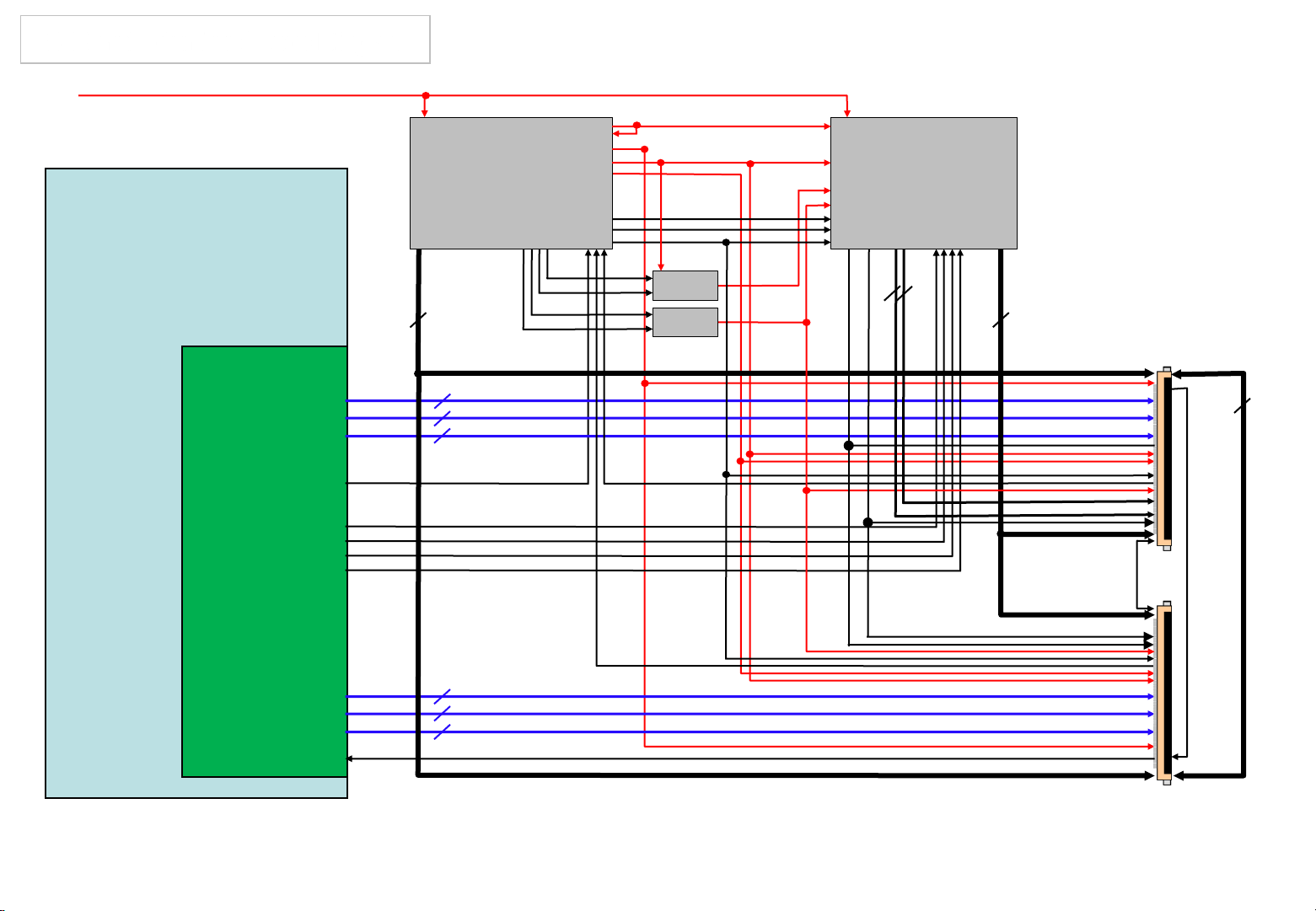

8. Panel Interface Block Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

PANEL_VCC

(+12V)

LGE 2122

EPI Tx

Block

VCC

VCC1.8

VDD

PMIC

H_VDD

TPS65178

VCOM_P

SWP

CTRLP

6

GMA4/GMA5/GAM7/GMA12/GMA14/ GMA15

2

2

2

SWN

CTRLN

EPI CH1 +/EPI CH2 +/EPI CH3 +/-

VCOM_DYN VCOMLFB

VCOM_N

TR/

Diode

TR/

Diode

VCOM_LOOP

VGH

VGL

VCOM

EO

GST

GCLK

MCLK

Level Shift

TPS65198

2

VGL_I

GIP_RST

VST

CLK1_I~CLK6_I

2

6

50Pin X 2

6

GMA1/GMA3/GAM9/GMA10/GMA16/GMA18

VGH_EVEN/VGH_ODD

VGH_F/VGH_R

EPI_LOCK3

Z_Out

VCOMRFB

2

2

2

GMA4/GMA5/GAM7/GMA12/GMA14/GMA15

EPI CH4 +/EPI CH5 +/EPI CH6 +/-

EPI_LOCK6_SOURCE EPI_LOCK6

9. PMIC & Level Shift Bloc Diagram

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

PANEL_VCC

Boost Converter

Buck 1 converter(VCC)

Buck 2 converter(Vcore)

Buck 3 converter(HVdd)

Buck 4 converter(VCC18)

Positive Charge Pump Controller

Negative Charge Pump Controller

6-Ch Gamma Buffer(DAC output)

Vcom reference & gain

Reset

Vdd

VCC

Vcore

HVdd

VCC18

SWN

CTRLN

SWP

CTRLP

GAM4/5/7/12/14/15

VCOM_P

VCOM_N

VCOM_LOOP

PMIC_RESET

TR/

Diode

TR/

Diode

Level Shift

TPS65198

VGL

VGH

TPS65178

PMIC

10. USB / WIFI / M-REMOTE / UART

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

[USB_DM_P2]

[USB_DP_P2]

[GPIO43]

[GPIO46]

[USB_DM_P1]

[USB_DP_P1]

[GPIO42]

[TCON12]

[USB_DM_P0]

[USB_DP_P0]

[GPIO44]

[ADIN2_SRV]

[USB_DM_P3]

[USB_DP_P3]

[U1RX]

[U1TX]

[ADIN4_SRV]

[OPCTRL49]

[OPCTRL50]

USB_DM1

USB_DP1

/USB_OCD1

USB_CTL1

USB_DM2

USB_DP2

/USB_OCD2

USB_CTL2

USB_DM3

USB_DP3

/USB_OCD3

USB_CTL3

WIFI_DM

WIFI_DP

USB1

USB2

USB3

+5V_USB_1

+5V_USB_2

+5V_USB_3

M_REMOTE_RX

M_REMOTE_TX

M_RFModule_RESET

RTS

CTS

OCP

OCP

USB_WIFI

Motion Remote

Receiver

[U0TX]

[U0RX]

LGE 2122

SOC_TX

SOC_RX

RENESAS MICOM

HDMI2

4Pin debugging

wafer

HDMI3

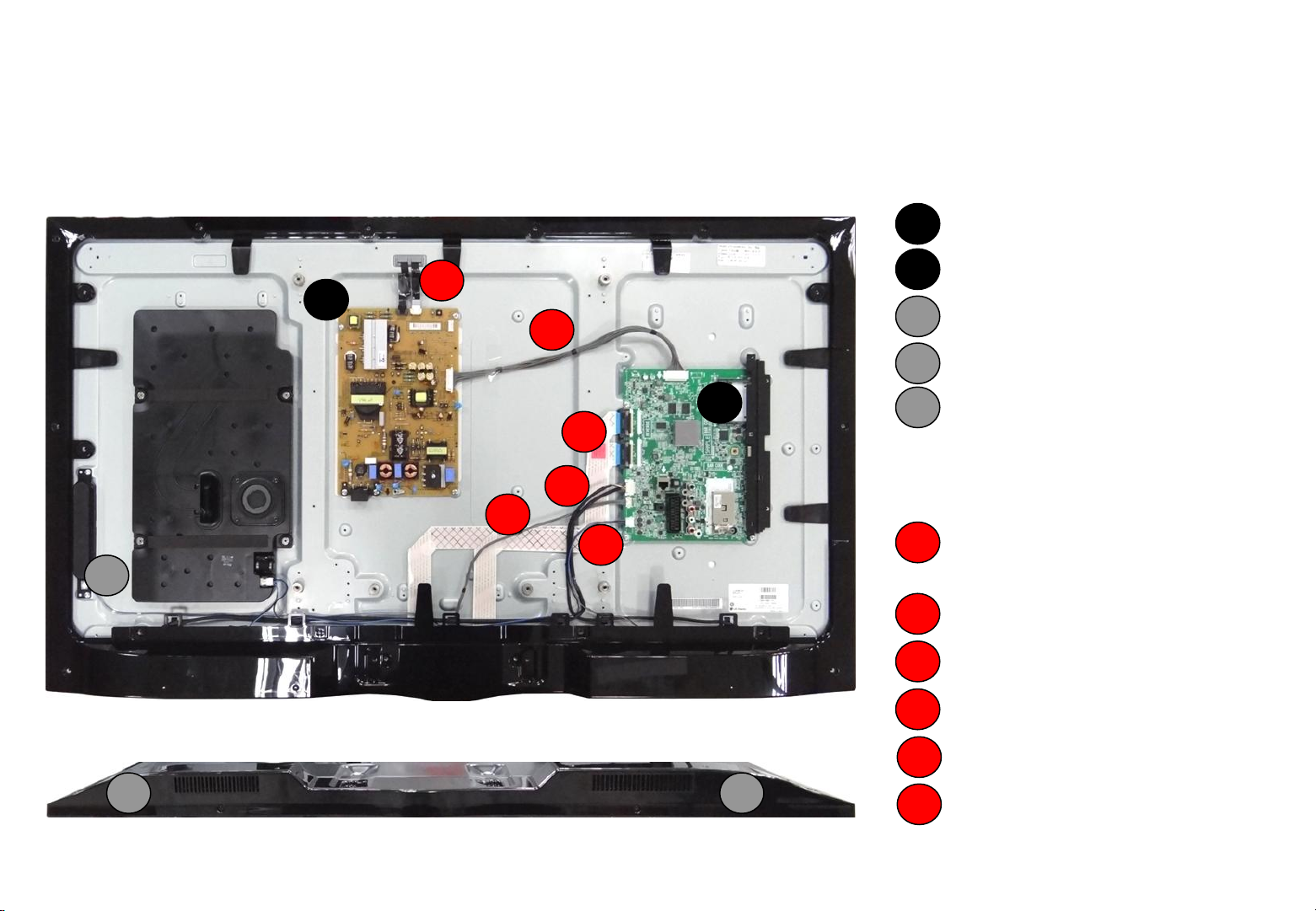

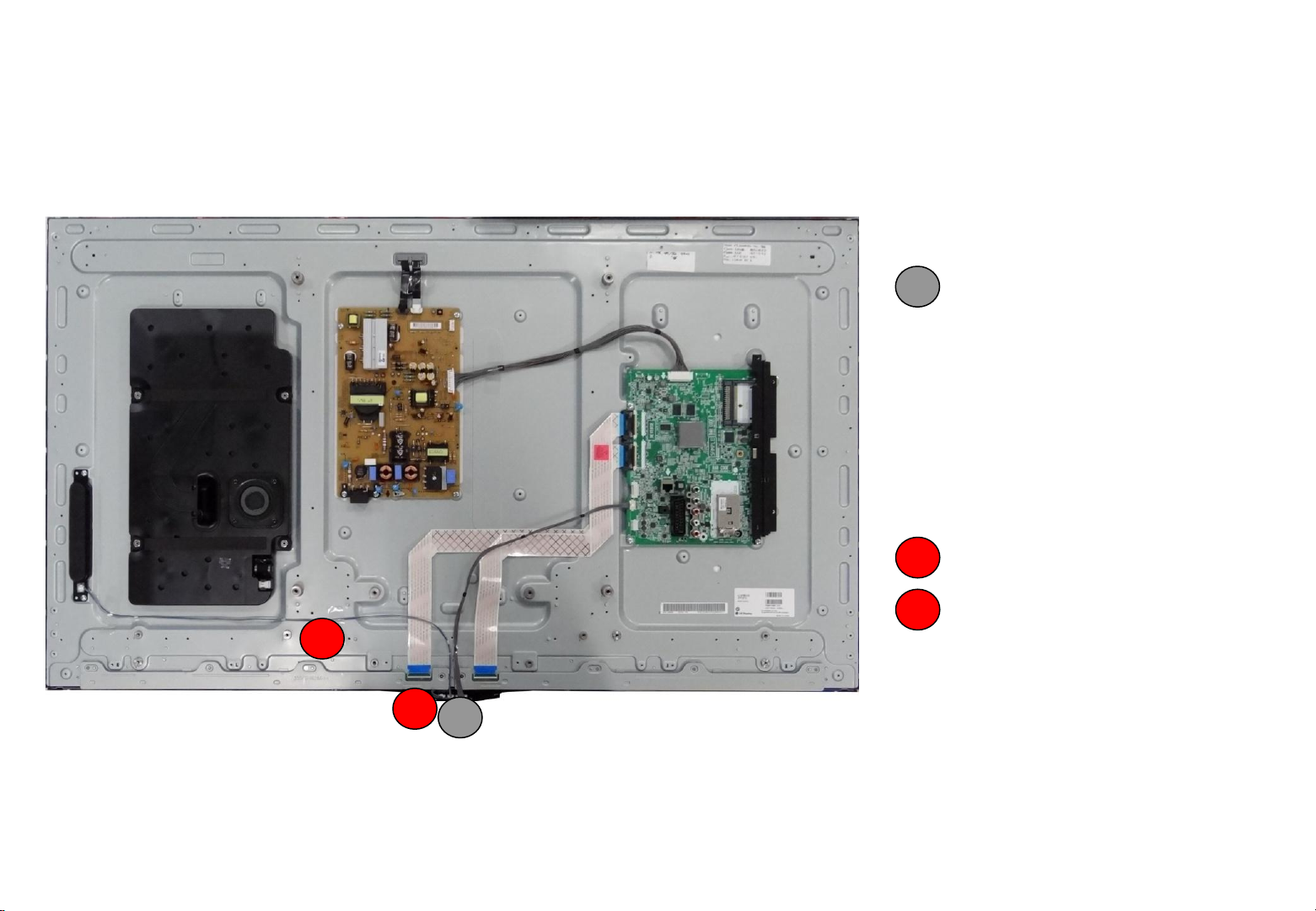

Interconnection - 1

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

47LA660S-ZA

[PCBs]

3

2

3

4

1

5

2

6

1

1

2

3

4

5

Main PCB

Power Board

Local key Assy

RF Assy

WIFI Assy

[Cables]

1

Main / LPB 24Pin + Local

Dimming Cable

Main / Module EPI Cable

2

50& 50Pin

LED driver / PSU

3

4

IR 8Pin Cable

4 5

1 / 88

5

WiFi 6Pin + RF 8Pin Cable

6

SPK Cable

Interconnection - 2

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

47LA660S-ZA

[PCBs]

7

8

6

6

IR Assy

[Cables]

IR to Local Key 3Pin Cable

7

8

IR to Logo Assy 4Pin Cable

2 / 88

Introductions of 13Y RF ass’y + Magic Remote control

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

1. System

2. Remote Buttons

3. MR13 Block Diagram

4. Function List

5. Pairing/Un-pairing Method

3 / 88

1. System

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

RF

UART

or USB

RF Receiver

Remote

Pairing Information Transmission (Send to TV after Paired)

• Static Calibration Data (Bypass only)

• Remote FW ver. (Save also in Receiver)

• BD_ADDR (Save also in Receiver)

• Pairing Information Transmission Sequence

• When it is paired, the remote sends packets(pairing success, F/W version, BD_ADDR) to the receiver.

• The receiver sends the pairing success packet to TV directly.

• F/W version and BD_ADDR packets are just saved on the receiver.

• The receiver sends F/W version or BD_ADDR packet to TV when it is required.

Motion Data Transmission

• Period : 7.5msec

• Motion Data : gyro, accelerometer

Voice Data Transmission

• Period : 10msec

• Voice sampling : 16khz 16bit

TV

4 / 88

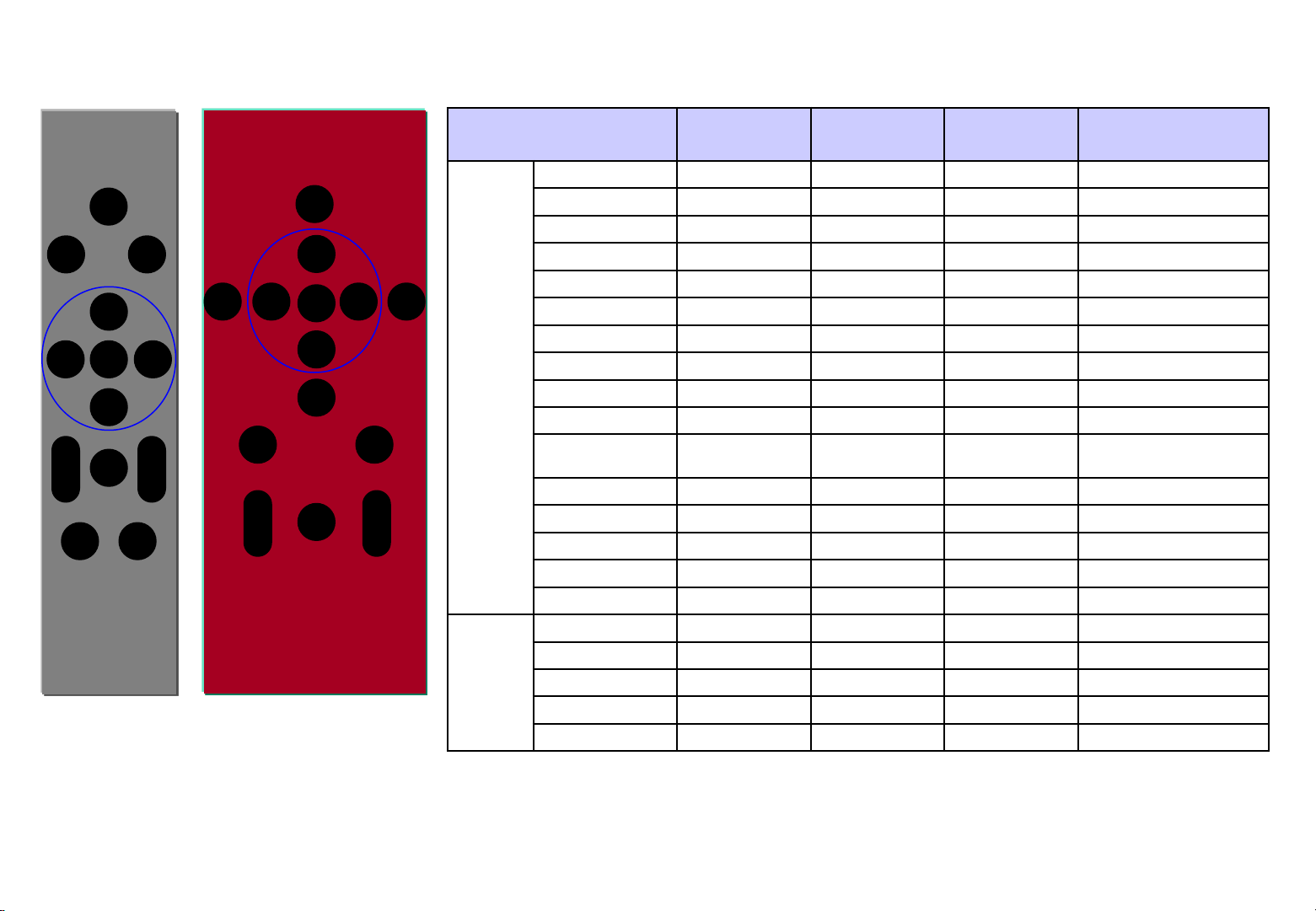

2. Remote Buttons (M4 vs. MR13)

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

POWER

BACK HOME

↑

OK

← →

BACK SMART

POWER

↑

OK

← →

↓

VOICE

↓

Screen RMT

Q.MENU

MUTE

MUTE

VOL CH

3D MYAPPS

3D

VOL CH

M4 Remote MR13 Remote

Phsical

Buttons

Logical

Buttons

BUTTON

POWER 0x08 NONE Y IR only

BACK 0x28 0x8028 Y

SMART 0x7C 0x807C Y

← 0x07 0x8007 Y

→ 0x06 0x8006 Y

↑ 0x40 0x8040 Y

↓ 0x41 0x8041 Y

OK 0x75 0x8044 Y

VOICE 0xDE 0x808B Y = VOICE_START

3D 0xDC 0x80DC Y

Screen RMT

/ Q.MENU

CH + 0x00 0x8000 Y

CH - 0x01 0x8001 Y

VOL + 0x02 0x8002 Y

VOL - 0x03 0x8003 Y

MUTE 0x09 0x8009 Y

AUTO_WAKEUP X 0x800C

VOICE_START X 0x800A

VOICE_STOP X 0x800D

POINT_START X 0x803E

POINT_STOP X 0x803F

RF Unpaired

IR_CODE

0xDE

RF Paired

RF_CODE

0x80DE

IR continuous

repeat

Y

ETC.

5 / 88

Loading...

Loading...