Page 1

ИЗМЕНЕНИЕ ДАННЫХ

Приведенные в настоящем руководстве данные не могут рассматриваться в качестве обязательств

компании LGE, и могут быть изменены без предварительного уведомления. Кроме того, компания LGE

оставляет за собой право на внесение изменений без предварительного уведомления в конструкцию

оборудования в связи с совершенствованием технологий проектирования и производства.

Настоящее руководство содержит информацию необходимую для установки, программирования,

эксплуатации и технического обслуживания изделия G7030.

- 1 -

Page 2

-2-

Page 3

СОДЕРЖАНИЕ

1. ВВЕДЕНИЕ .................................... 4

1.1 Назначение ........................................

1.2 Регламентирующие положения.....

1.3 Список сокращений .........................

2. РАБОЧИЕ ХАРАКТЕРИСТИКИ .... 7

2.1 Название изделия.............................

2.2 Поддерживаемые стандарты.........

2.3 Основные узлы: стандарт GSM .....

2.4 Характеристики аппаратной

части ...................................................

2.5 Характеристики программного

обеспечения .....................................

2.6 Стандарты испытаний ...................

3. КРАТКАЯ ТЕХНИЧЕСКАЯ

ИНФОРМАЦИЯ............................. 13

3.1 Цифровой процессор

низкочастотной части ...................

3.2 Аналоговый процессор

низкочастотной части ...................

3.3 Интерфейс дисплея и гибкой

печатной платы ................................

3.4 Аудио интерфейс ..............................

3.5 Подсветка клавиатуры ...................

3.6 Соединения клавиатуры .................

3.7 Общее описание РЧ блока

приемопередатчика .........................

4

4

6

7

7

7

7

9

11

13

19

32

33

36

37

38

6. ЗАГРУЗКА ПРОГРАММНОГО

ОБЕСПЕЧЕНИЯ................................ 78

7. СЕРВИСНОЕ ПРОГРАММНОЕ

ОБЕСПЕЧЕНИЕ И КАЛИБРОВКА .. 82

7.1 Сервисное программное

обеспечение ……………………………..

7.2 Калибровка ............................................

8. БЛОК-СХЕМА ................................... 89

8.1 Основная плата ....................................

8.2 Плата РЧ части .....................................

9. ПРИНЦИПИАЛЬНАЯ

ЭЛЕКТРИЧЕСКАЯ СХЕМА ............. 91

9.1 Интерфейс соединительного

устройства.............................................

9.2 Интерфейс низкочастотной части ..

9.3 Интерфейс блока памяти ...................

9.4 Интерфейс аудио блока ......................

9.5 Мультимедийный интерфейс (MMI) ..

9.6 Интерфейс РЧ части ...........................

10. ТОПОЛОГИЯ ПЕЧАТНОЙ ПЛАТЫ .97

10.1 Вид сверху ............................................

10.2 Вид снизу ..............................................

82

85

89

90

91

92

93

94

95

96

97

98

4. УСТРАНЕНИЕ

НЕИСПРАВНОСТЕЙ ……………….. 44

4.1 Громкоговоритель ..........................

4.2 Микрофон...........................................

4.3 Модуль ЖКД.......................................

4.4 Виброзвонок .....................................

4.5 Зарядное устройство.......................

4.6 Разъем гарнитуры

«свободные руки» ……………………

4.7 Устранение проблем тракта

приема ………………………………….

4.8 Устранение проблем тракта

передачи ............................................

5. ПОРЯДОК РАЗБОРКИ ................. 71

5.1 Разборка. ……………………………….

44

46

48

50

52

54

56

64

71

11. СЕРВИСНЫЙ РЕЖИМ .................. 99

12. ТЕСТ «STAND ALONE»................. 100

12.1 Порядок настройки ...........................

13. СБОРОЧНЫЙ ЧЕРТЕЖ И СПИСОК

ЗАМЕНЯЕМЫХ ДЕТАЛЕЙ ............ 103

13.1 Сборочный чертеж............................

13.2 Аксессуары ........................................

13.3 Список заменяемых деталей

< Механические детали > ………….

13.3 Список заменяемых деталей

< Основная плата > ………………….

-3-

100

103

105

106

108

Page 4

1. ВВЕДЕНИЕ

1.1 Назначение

В настоящем руководстве приводится техническое описание устройства и необходимая

информация для выполнения ремонта, калибровки, а также загрузки программного обеспечения.

1.2 Регламентирующие положения

А. Безопасность

Мошеннический доступ, т. е. несанкционированное использование телекоммуникационной системы

неуполномоченной стороной (например, лицами, не являющимися служащими компании, ее

представителями, субподрядчиками, либо действующими от имени компании) может стать

причиной представления необоснованных счетов за пользование телекоммуникационными

услугами. Пользователи системы несут ответственность за безопасность собственной системы.

Имеется определенный риск коммутационного мошенничества в отношении Вашей

телекоммуникационной системы. Пользователи системы несут ответственность за

программирование и конфигурирование своего оборудования с целью предотвращения

несанкционированного использования системы. Компания LGE не может гарантировать

защищенность данного изделия в отношении вышеупомянутых случаев, и его возможностей по

предотвращению несанкционированного пользования телекоммуникационными услугами

коммерческих линий связи путем получения доступа или подключения оборудования. Компания

LGE не несет ответственности за любые расходы, понесенные в результате подобного

несанкционированного пользования телекоммуникационными услугами.

B. Причинение ущерба

В случае, если компания телефонной связи определит, что предоставленное клиенту

оборудование является неисправным и его использование может нанести ущерб или нарушить

работу телефонной сети связи, компания может временно приостанавливать оказание услуг

телефонной связи на время необходимое для ремонта.

C. Изменения в предоставлении услуг

Местная компания телефонной связи может вносить изменения в свое оборудование связи и

изменять порядок его работы. При наличии оснований полагать, что такие изменения способны

оказать воздействие на работу изделия G7030, либо его совместимость с телефонной сетью,

компании телефонной связи следует заранее письменно уведомить об этих изменениях

пользователя, тем самым предоставляя ему возможность предпринять необходимые меры с целью

дальнейшего пользования услугами телефонной связи.

D. Ограничения на выполнение техобслуживания

Некоторые работы по техническому обслуживанию данной модели могут быть выполнены только

предприятием-изготовителем, либо его уполномоченными представителями. Пользователю

запрещается вносить какие-либо изменения и/или производить ремонт, за исключением случаев,

специально оговоренных в настоящем руководстве. Следует иметь в виду, что любые

несанкционированные модификации либо ремонт могут повлечь изменение нормативного статуса

системы и стать основанием для аннулирования всего периода гарантии.

- 4 -

Page 5

E. Уведомление о наличии излучения

Данное устройство соответствует нормативам местных контролирующих органов в отношении

радиации и радиочастотного излучения. Согласно действующим положениям данных

контролирующих органов Вас могут обязать предоставить такую информацию конечному

пользователю.

F. Иллюстрации

Иллюстрации в настоящем руководстве приведены исключительно для наглядности. Ваше

реальное оборудование может выглядеть немного иначе.

G. Помехи и подавление сигнала

Сигналы G7030 могут влиять на работу чувствительного лабораторного, медицинского и иного

оборудования. На работу самого телефона могут влиять помехи, исходящие от машин и

электродвигателей не оборудованных устройствами подавления помех.

H. Приборы, чувствительные к статическому электричеству

ВНИМАНИЕ!

Платы, имеющие чувствительные к статическому электричеству элементы, обозначены

соответствующей пиктограммой . Приведенная ниже информация касается порядка работы с

такими деталями:

• Выполняя замену плат системы, технические специалисты должны иметь закрепленную на кисти руки линию

заземления;

• При выполнении работ на системной плате специалист должен стоять на антистатическом покрытии (также

заземленном);

• Паяльник (соответствующий выполняемой работе) должен быть заземлен;

• Чувствительные к статическому электричеству детали следует хранить в защитной упаковке вплоть до их

непосредственного использования;

• Перед отправкой на завод системные платы, а также детали подобные EEPROM необходимо упаковать

указанным способом.

- 5 -

Page 6

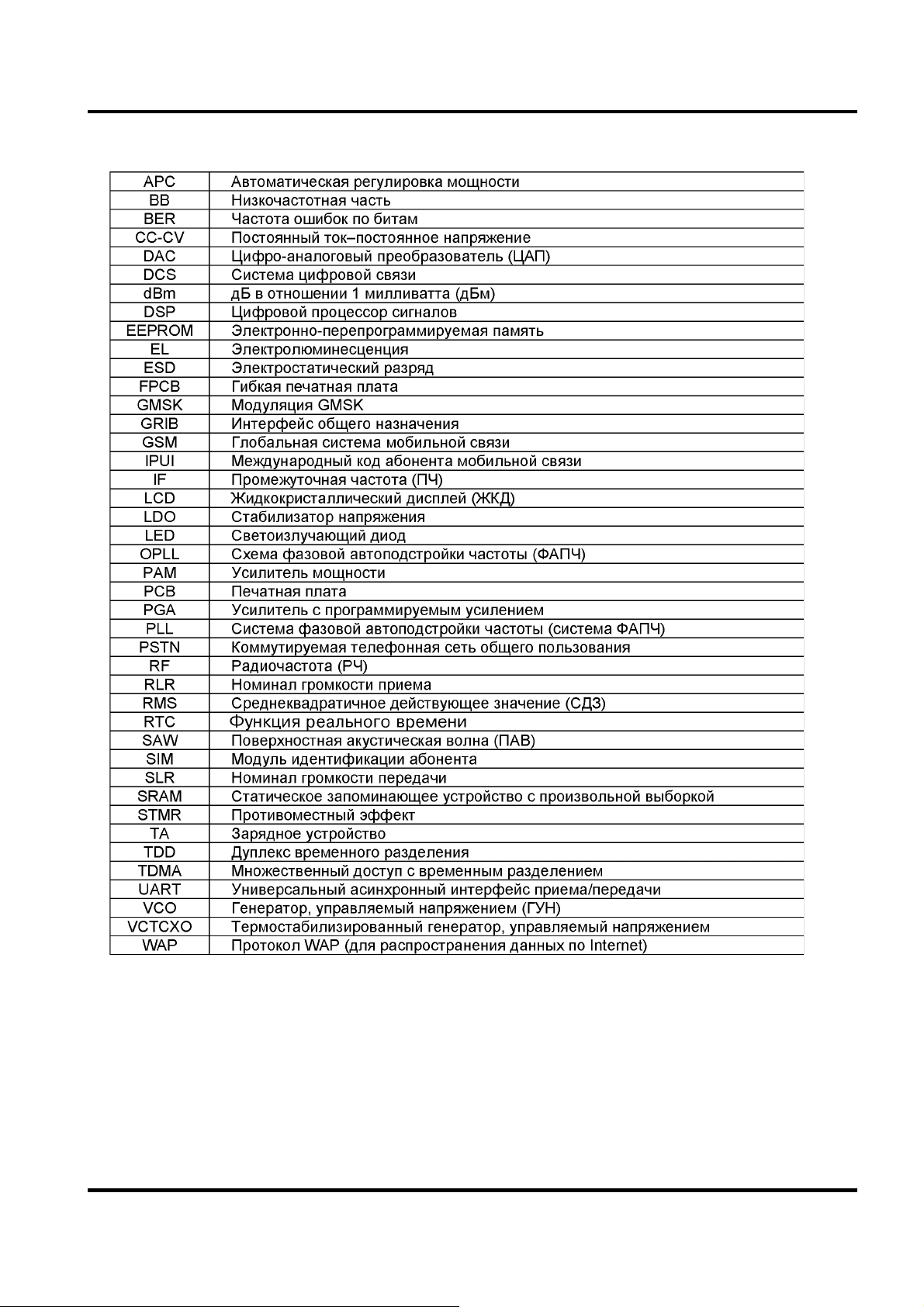

1.3 Список сокращений

- 6 -

Page 7

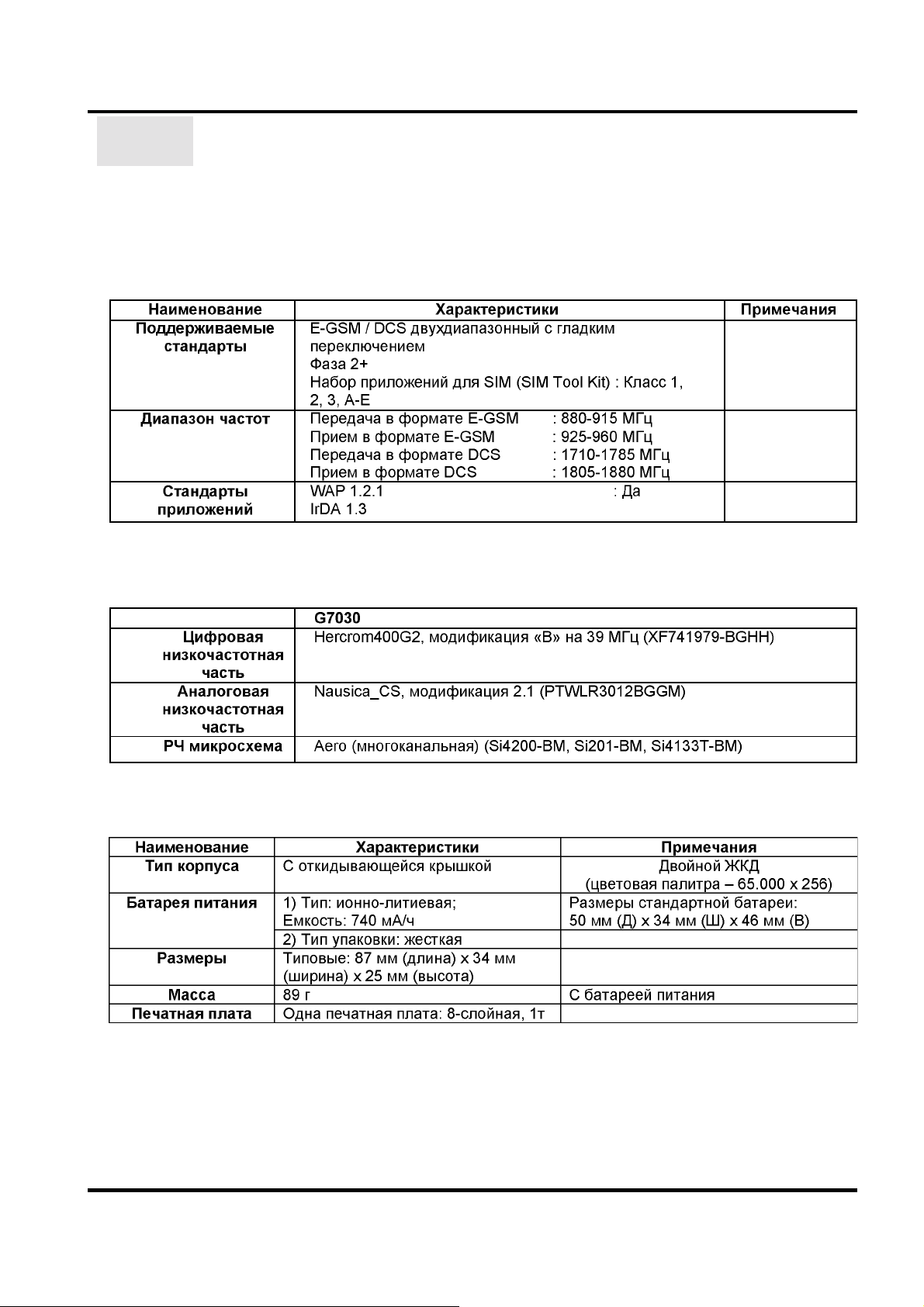

2. РАБОЧИЕ ХАРАКТЕРИСТИКИ

2.1 Наименование изделия

G7030: Поддержка GPRS (системы пакетной радиосвязи общего пользования), Класс 10.

2.2 Поддерживаемые стандарты

2.3 Основные узлы: формат GSM

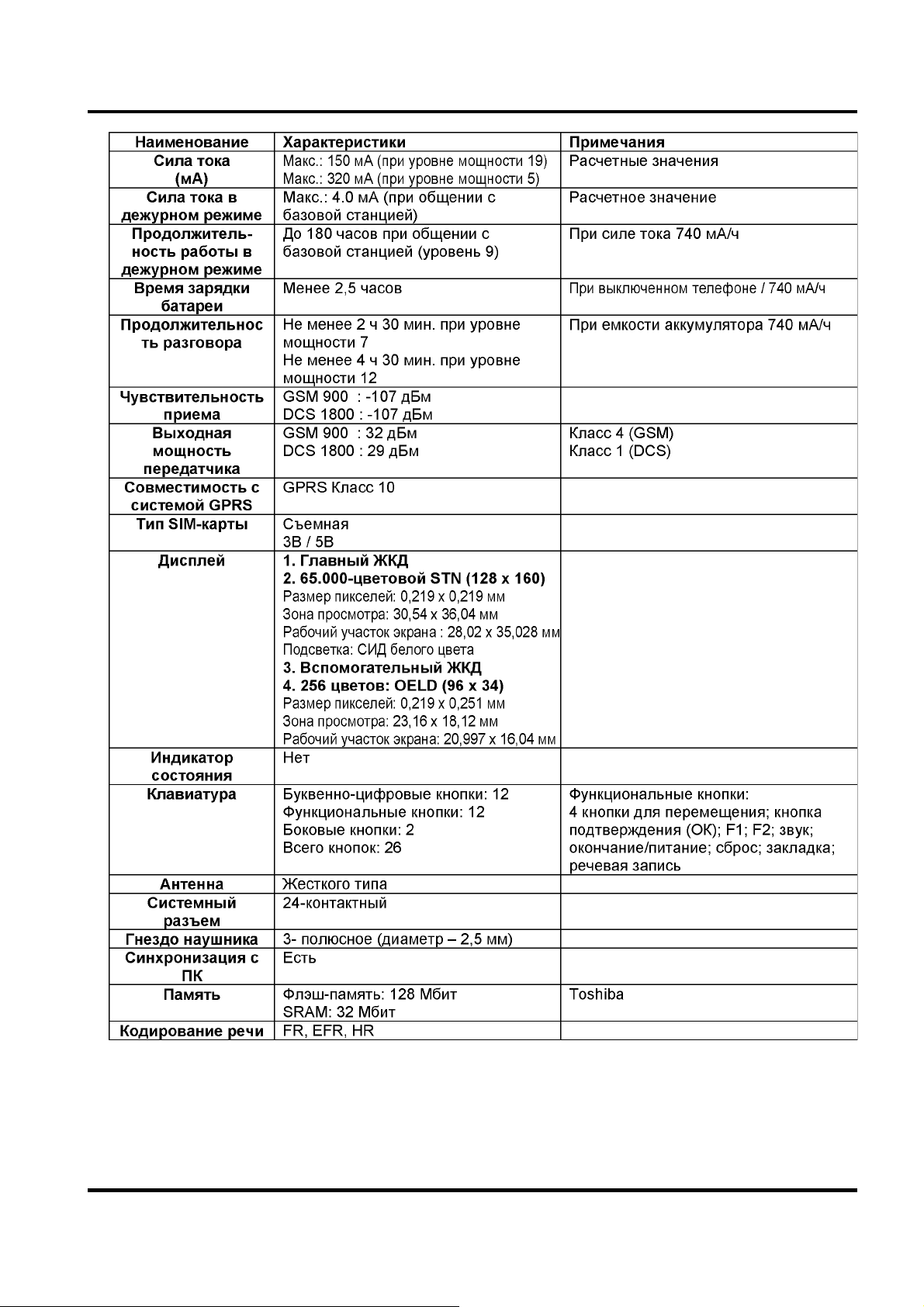

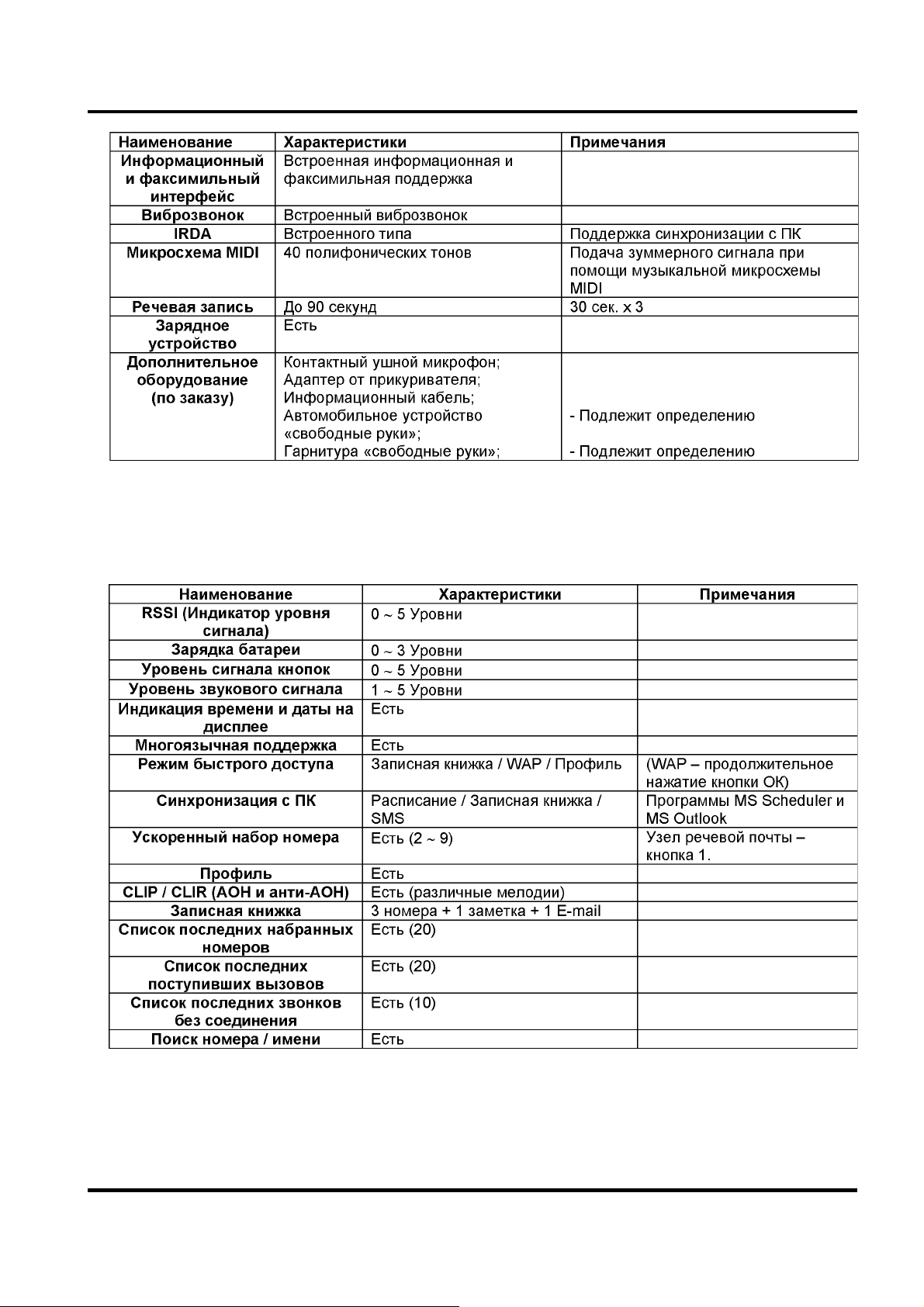

2.4 Характеристики аппаратного оборудования

- 7 -

Page 8

- 8 -

Page 9

* Емкость аккумуляторной батареи: 740 мА/ч (в настоящее время)

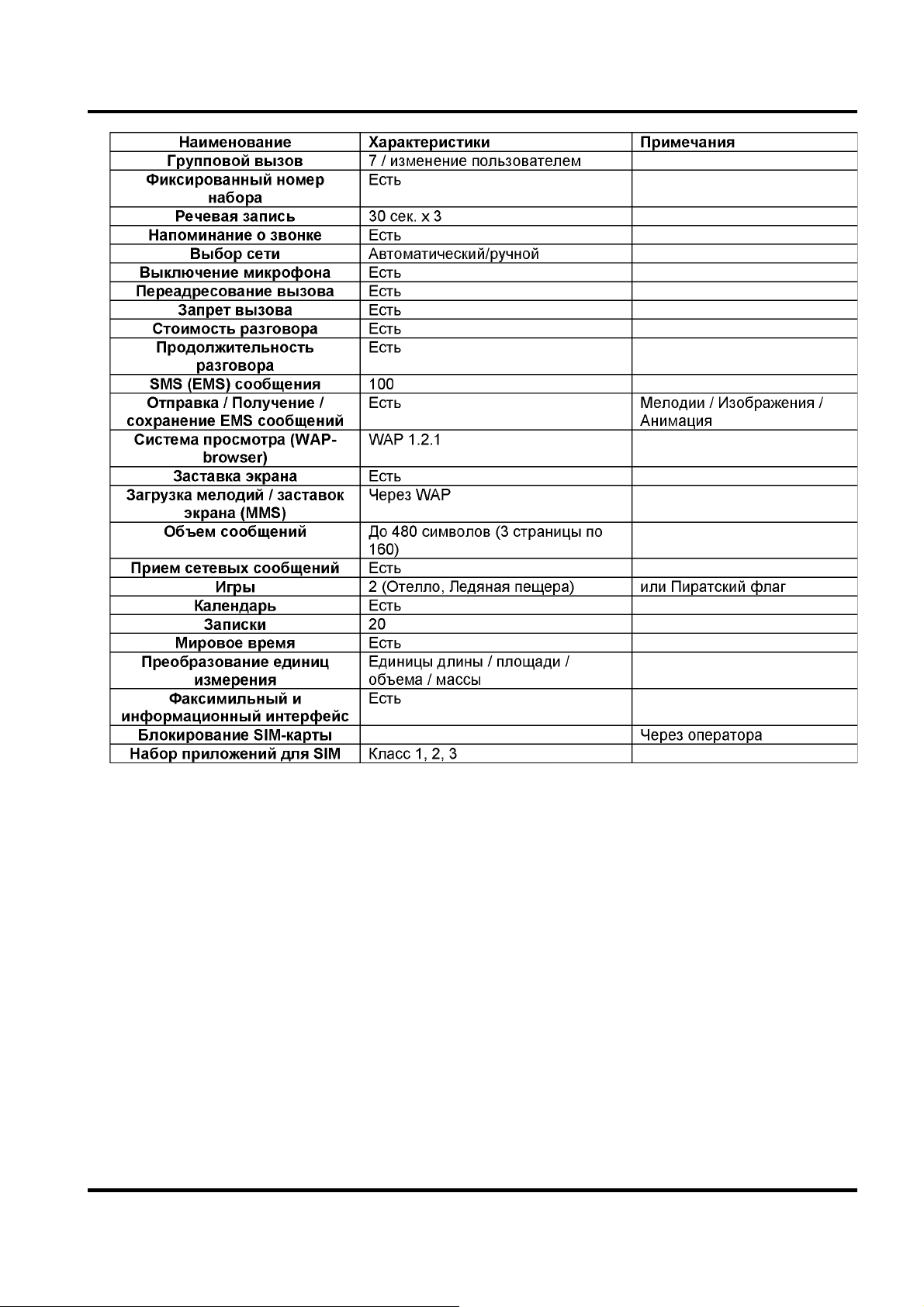

2.5 Характеристики программного обеспечения

- 9 -

Page 10

- 10 -

Page 11

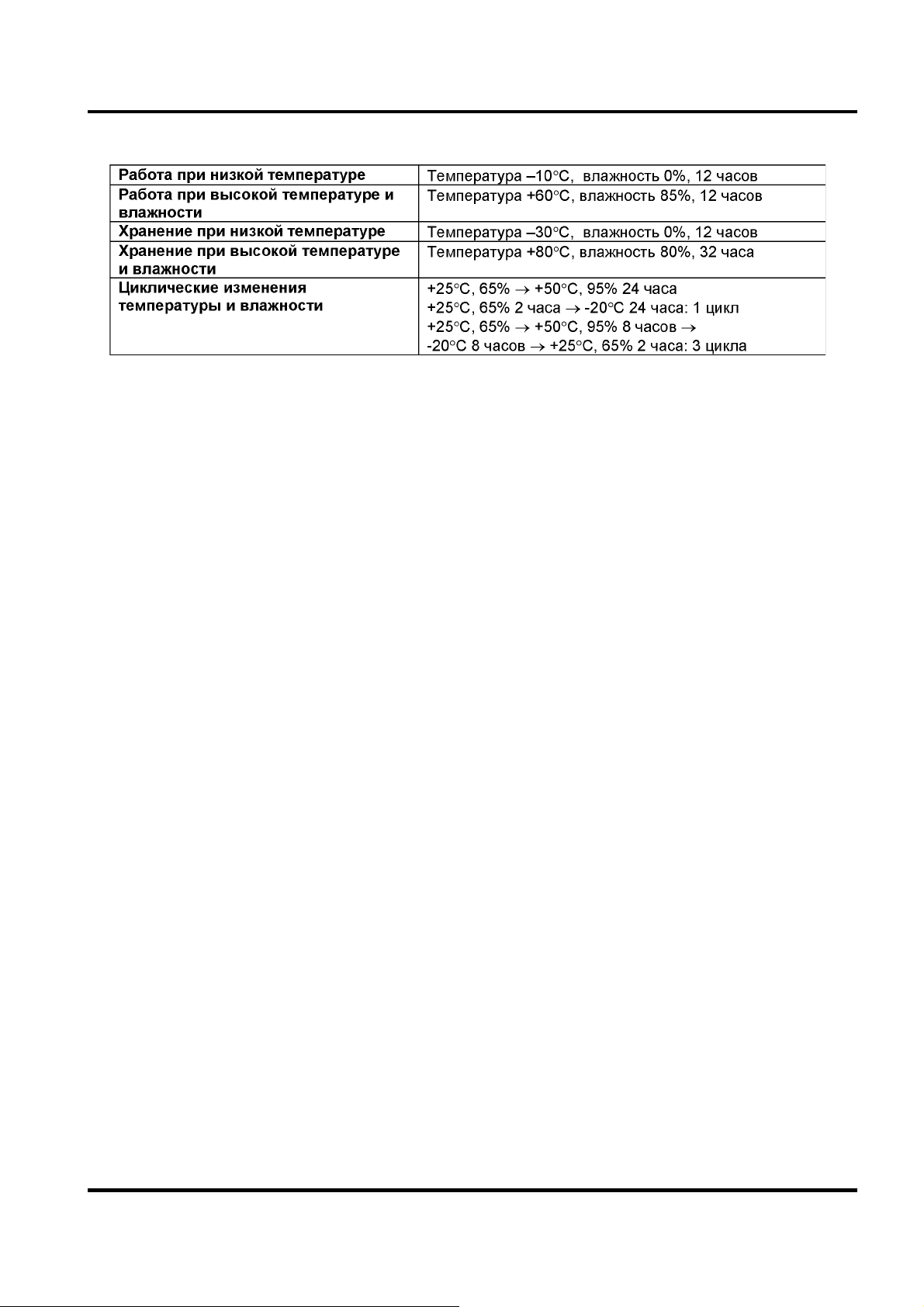

2.6 Стандарты испытаний

2.6.1 Испытания общего характера

2.6.2 Испытания на ударную нагрузку

2.6.3 Испытания на вибрацию

- 11 -

Page 12

2.6.4 Испытания на воздействие окружающей среды

- 12 -

Page 13

3. КРАТКАЯ ТЕХНИЧЕСКАЯ ИНФОРМАЦИЯ

3.1 Цифровой процессор низкочастотной части

Микросхема CALYPSO отвечает за цифровую обработку сигналов низкочастотной части

мобильного телефона GSM/GPRS. Микросхема состоит из субпроцессора цифровой обработки

сигнала со своей программой и памятью для хранения данных, ядра микропроцессорного

управляющего устройства со средствами эмуляции (ARM7TDMIE), 8 Кбайт встроенной памяти

аппаратного загрузчика, 4 Мбит статической оперативной памяти (SRAM), генератора

прямоугольных тактовых импульсов, нескольких скомпилированных однопортовых и двухпортовых

вентильных схем RAM и CMOS-памяти.

Данная схема предназначена для управления обработкой сигналов низкочастотной части GSM/

GPRS посредством протоколов уровней 1, 2 и 3 в соответствии с описанием стандарта ETSI. При

этом она отвечает за энергопотребление как в GSM режиме, так и в нерабочем режиме, а также за

функции системы пакетной радиосвязи общего пользования (GPRS). Микросхема полностью

соответствует утвержденным стандартам испытаний всех уровней GSM в отношении речевого

кодирования в полноскоростном, улучшенном полноскоростном и полускоростном режимах.

CALYPSO имеет все характеристики для структурного испытания логической схемы (полное

сканирование (full-SCAN), встроенный самоконтроль (BIST), РМТ, JTAG, периферийное

сканирование).

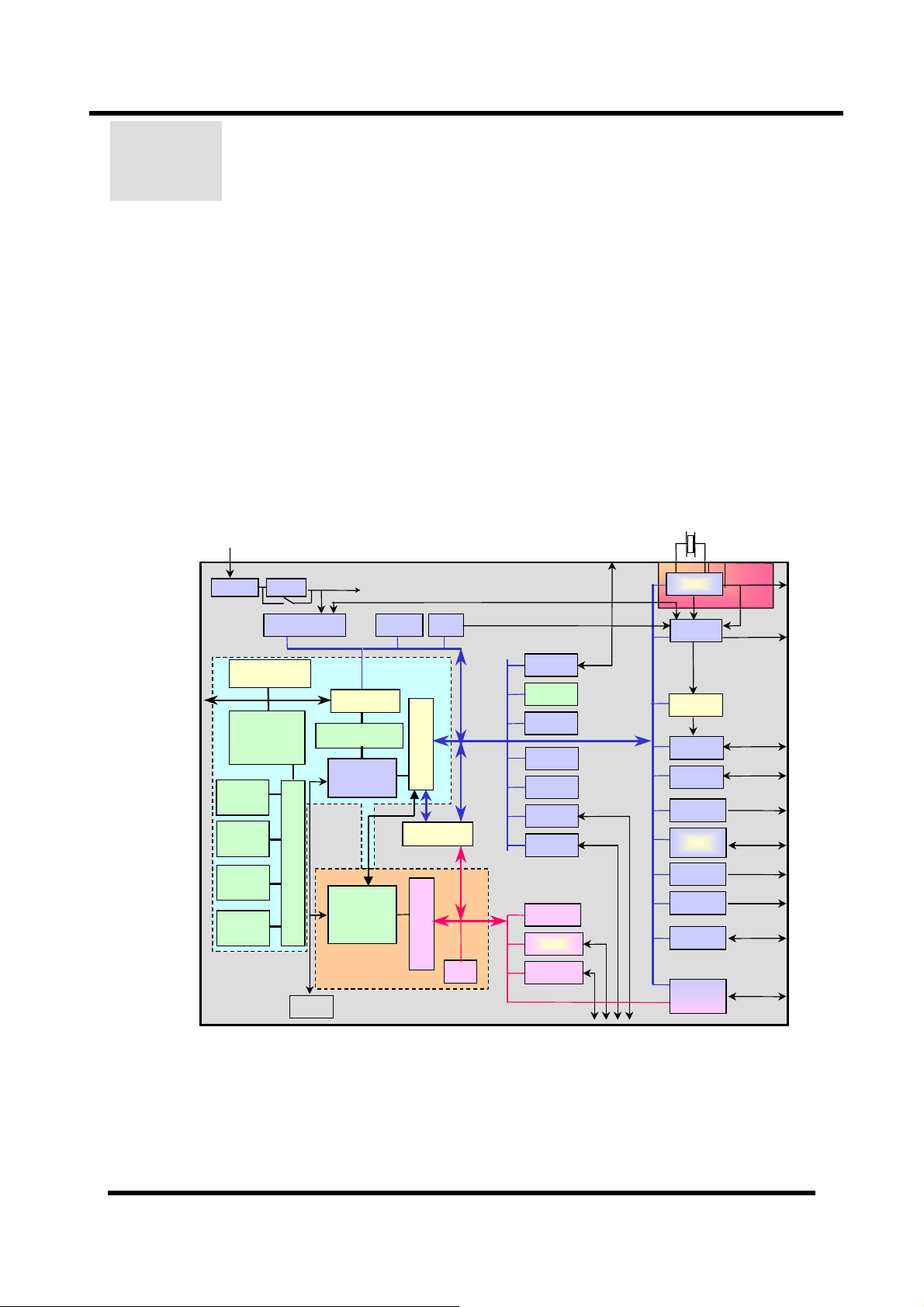

3.1.1 Блок-схема

RTC

CK32Khz

ULPD

32KHz CRYSTAL

IT Alarm

13MHz or 26 MHz TCXO

SLICER

DIV - 2

DPLL&CLKM

13MHz

WTDOG

INTH

ENABLE_CK13Mhz

Asynchronous WAKE_UP

Boot ROM

External

ARM7

Memories

Memory

Protect

Debug Unit

Unit

1Mbit

SRAM

W

1Mbit

SRAM

1Mbit

SRAM

1Mbit

SRAM

Надписи на схеме:

External ARM7 Memories Внешние ЗУ микроконтроллера ARM7

Slice Ограничитель по максимуму и минимуму

Boot ROM Аппаратный загрузчик

ENABLE_CK13Mhz Включение тактового генератора 13МГц

ARM7

r

i

t

e

b

u

f

.

DSP subchip

JTAG

MCU top-cell

MEMIF

8K API

cDSP

S28C128

B

R

I

D

G

E

B

R

I

D

G

E

INTH

SPI

GEA

Die ID

TIMER1

TIMER2

ARMIO

uWIRE

CRYPT

MCSI

Asynchronous WAKE_UP Линия асинхронного запуска

Debug unit Отладочный блок

Memory protect unit Блок защиты памяти

Write buf. Буфер записи

RHEA bus

RIF

GSM time

TPU

TSP

SIM

PWL

UART

IRDA

PWT

LPG

I2C

UART

modem

Рис. 3-1-1. Блок-схема Calypso G2 (HERCROM400G2)

-13-

Page 14

3.1.2 Техническое описание блоков микросхемы

Микросхема CALYPSO построена на базе двух основ (ядер) процессоров ARM7 и LEAD2,

использующих шину информационного канала TI RHEA как интерфейс связи с периферийными

устройствами. Микросхема CALYPSO состоит из следующих блоков:

!!

! ARM7TDMIE

!!

Ядро центрального процессора ARM7TDMIE (32/16-разрядный RISC-процессор)

+ ARM модуль эмуляции (ice crusher).

!!

! Субкристалл цифрового процессора сигналов S28C128

!!

Ядро цифрового процессора сигналов LEAD2, с 28К слов ОЗУ и 128К слов ПЗУ.

+ API (8.000 слов из 28.000 ОЗУ)

+ Интерфейс с системной службой.

+ Таймер

!!

! Ячейка генератора тактовых импульсов прямоугольной формы

!!

!!

! Периферийные устройства ARM:

!!

Периферийные устройства общего назначения:

• Интерфейс памяти ARM для внешних устройств памяти ОЗУ, флэш или ПЗУ.

• Мост RHEA

• Статическое ОЗУ на 4 Мбайта с буфером записи

• Блок защиты памяти (MPU)

• Отладочный блок (DU)

• 64 Кбайта сдвоенный ROM для внутренней загрузки.

• Ячейка идентификации кристалла (48 байт + 5 резервных)

Периферийные устройства прикладного назначения:

• Универсальные устройства ввода-вывода ARM с интерфейсом клавиатуры и 2 сигналами

широтно-импульсной модуляции для подсветки и зуммера с возможностью генерирования

тональных сигналов.

• Микропроводный интерфейс для ЖКД и электронно-перепрограммируемого ПЗУ (EEPROM).

•3 таймера (групповой, сторожевой).

• Интерфейс универсального асинхронного приемопередатчика (UART) 16С750 (UART_IRDA) с:

- средствами управления IRDA;

- управлением потоком данных (UART);

- протоколом последовательности операций аппаратных средств (DCD, CTS/RTS)

• Интерфейс UART 16С750 (UART_MODEM) с:

- протоколом последовательности операций аппаратных средств (DCD, CTS/RTS)

- функцией автобод.

• Интерфейс SIM-карты.

• Блок обработки прерываний ARM (INTH).

• Контроллер последовательности операций GSM в реальном масштабе времени (TPU)

• Последовательный порт синхронизации операций GSM в реальном масштабе времени (TSP)

• DMA-контроллер (4 канала, 2 порта).

• Генератор импульсов истинного времени (RTC).

• Устройство сверхмалой мощности GSM (ULPD).

• Генератор тактовых импульсов и управляющее устройство цифровой фазовой

автоподстройки (CLKM).

• Программируемый контроллер для генерирования импульсов светодиодов (LPG).

•· Генератор тональных сигналов (PWT).

• Псевдошумовой модулятор для управления уровнем яркости (PWL).

• Последовательный интерфейс главной внутренней интегральной схемы.

• Модули 1 и 2 алгоритма шифрования системы пакетной радиосвязи общего пользования GPRS.

- 14 -

Page 15

! Периферийные устройства цифрового процессора:

Периферийные устройства общего назначения:

• Мост RHEA.

Периферийные устройства прикладного назначения:

• Радио-интерфейс (RIF).

• Многоканальный последовательный интерфейс (MCSI).

• Устройства шифрования А51/А52 (CRYPT).

• Интерфейс UART 16С750 (UART_MODEM) с:

- протоколом последовательности операций аппаратных средств (DCD, CTS/RTS)

- функцией автобод, эхоподавлением.

• DMA-контроллер (4 канала).

• Блок обработки прерываний цифрового процессора сигналов DSP (INTH).

! Прочие периферийные устройства специализированной микросхемы:

• Контроллер порта доступа к средствам тестирования (ТАР) JTAG.

- 15 -

Page 16

3.1.2.1 Мегаячейка ARM (ARM7TDMIE)

ARM7TDMIE представляет собой ядро 32-разрядного микропроцессора с сокращенным набором

команд (RISC). Данный обрабатывает команды в 32- и 16-разрядном формате, а информацию – в

32-, 16- и 8-разрядном формате. Архитектура ARM7TDMIE построена на основе процессора с

сокращённым набором команд (RISC). Для обеспечения непрерывной работы всех элементов

систем памяти и обработки данных применяется конвейерный режим. Таким образом, во время

выполнения одной команды происходит расшифровка следующей команды, и одновременное

извлечение из памяти третьей команды. Микропроцессор ARM7 из серии CALYPSO предназначен

для работы только в режиме следования байтов, начиная с младшего.

3.1.2.2 Субкристалл цифрового процессора сигналов S28C128

Субкристалл DSP является ядром цифрового процессора сигналов серии TMS320C54х.

Ядро центрального процессора LEAD2 связано с :

- Интерфейсом порта ARM (API);

- Блоком обработки прерываний;

- Параллельным интерфейсом XIO (выполнения ввода-вывода);

- Таймером;

-28К слов ОЗУ, включая 8К слов общей памяти с API;

- 128К слов ПЗУ;

- Последовательным портом;

- Интерфейсом JTAG.

Частоту входного сигнала тактового генератора задает внешнее устройство цифровой фазовой

автоподстройки (DPLL), а диапазон частоты рабочего цикла определен в пределах 0-91 МГц.

3.1.2.3 Генератор тактовых импульсов прямоугольной формы

Ячейка генератора тактовых импульсов является аналоговой ячейкой, служащей для изменения

формы входного сигнала тактового генератора, поступающего от внешнего генератора. Входной

сигнал тактового генератора считается псевдо-синусоидальным с ограниченной динамикой; ячейка

генератора тактовых импульсов преобразует его в импульс с прямоугольной формой волны и

амплитудой напряжения питания.

3.1.3 Интерфейс устройств памяти

• 64 Мбайта х 2 флэш / 32 Мбайт псевдо-SRAM (статической оперативной памяти).

• 16-разрядная параллельная шина данных.

• ADD01 ~ ADD22.

Интерфейс устройств памяти: Интерфейс внешних/внутренних устройств памяти.

_CS0 : FLASH2, TH50VPF5783AASB, 16-разрядный доступ, тройное состояние ожидания;

_CS1 : FLASH1 в TH50VPF5783AASB, 16-разрядный доступ, тройное состояние ожидания;

_CS2 : Внешняя псевдо-SRAM память, 16-разрядный доступ, тройное состояние ожидания;

_CS3 : главный ЖКД, вспомогательный ЖКД, адресация музыкальной микросхемы MIDI, 16- и 8-

разрядный доступ, тройное состояние ожидания;

_CS6 : внутренняя статическая оперативная память SRAM, 32-разрядный доступ.

* Примечание: Тройное состояние ожидания на внутреннем 39МГц процессоре микросхемы

CALYPSO необходим для обеспечения 80-нс выборки, поскольку цикл процессора составляет 25

нс (25 х 4 = 100 нс).

- 16 -

Page 17

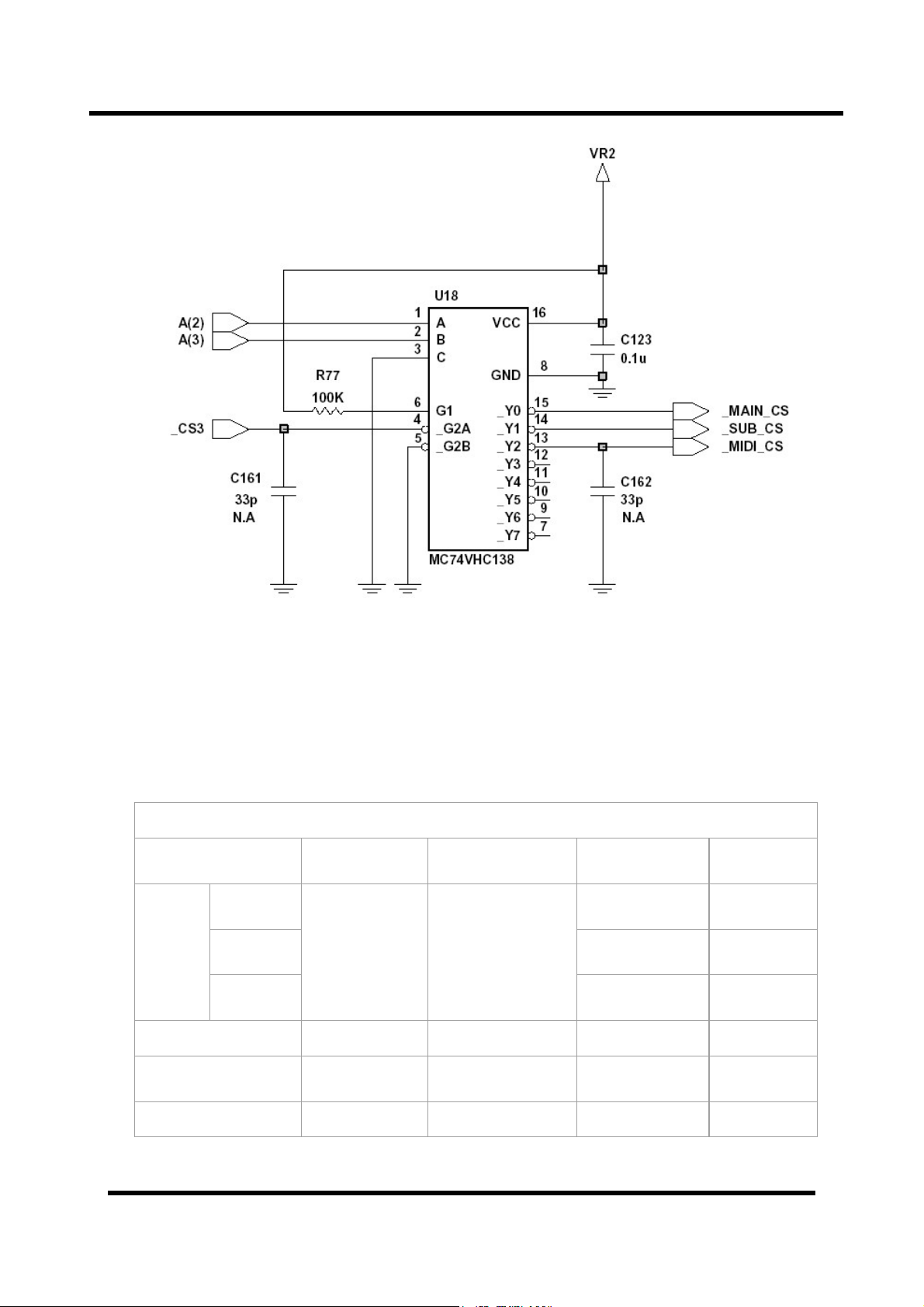

Рис. 3-1-2. Схема декодирования

3.1.4 Соединение с внешними устройствами

Таблица 3-1-1. Интерфейс внешних устройств

Интерфейс

Устройства Изготовитель № детали

Флэш-1

Память

Флэш-2

Toshiba

TH50VPF5783

AASB

Псевдо-

SRAM

Время цикла

записи

70нс 70нс

70нс 70нс

70нс 70нс

Время цикла

считывания

Главный ЖКД SDI UG12R61A

Вспомогательный ЖКД

Samsung

NEC

Микросхема MIDI Yamaha YMU762B 50нс 80нс

-17-

Page 18

3.1.5 РЧ интерфейс

Таблица 3-1-2. Описание РЧ интерфейса

3.1.6 Интерфейс универсального асинхронного приемопередатчика (UART)

G7030 имеет два задающих устройства универсального асинхронного приемопередатчика:

UART1: контроль последовательности операций аппаратных средств / факсимильная связь и

модем для передачи данных.

UART1: управление устройством «свободные руки» / трассировка программного обеспечения или

модема IRDA.

Таблица 3-1-3. Описание интерфейса универсального асинхронного приемопередатчика (UART)

- 18 -

Page 19

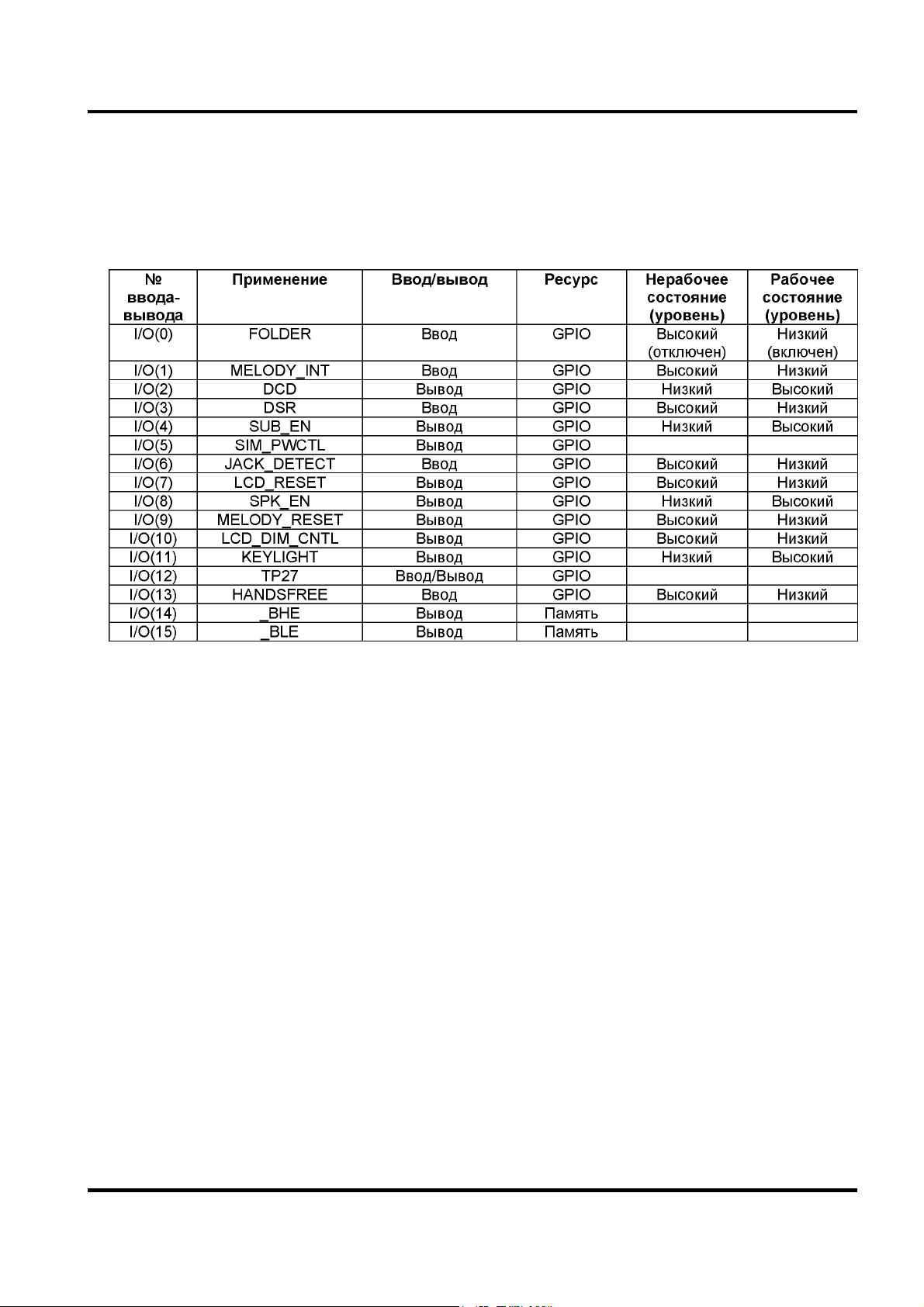

3.1.7 Карта универсальных устройств ввода-вывода (GPIO)

Из 16 имеющихся ресурсов G7030 использует 13, три оставшихся относятся к SIM-карте и памяти.

Ниже в таблице приведена карта универсальных устройств ввода-вывода (GPIO) телефонного

аппарата G7030, с указанием применения, состояния ввода-вывода, уровня разрешения.

Таблица 3-1-4. Таблица универсальных устройств ввода-вывода (GPIO)

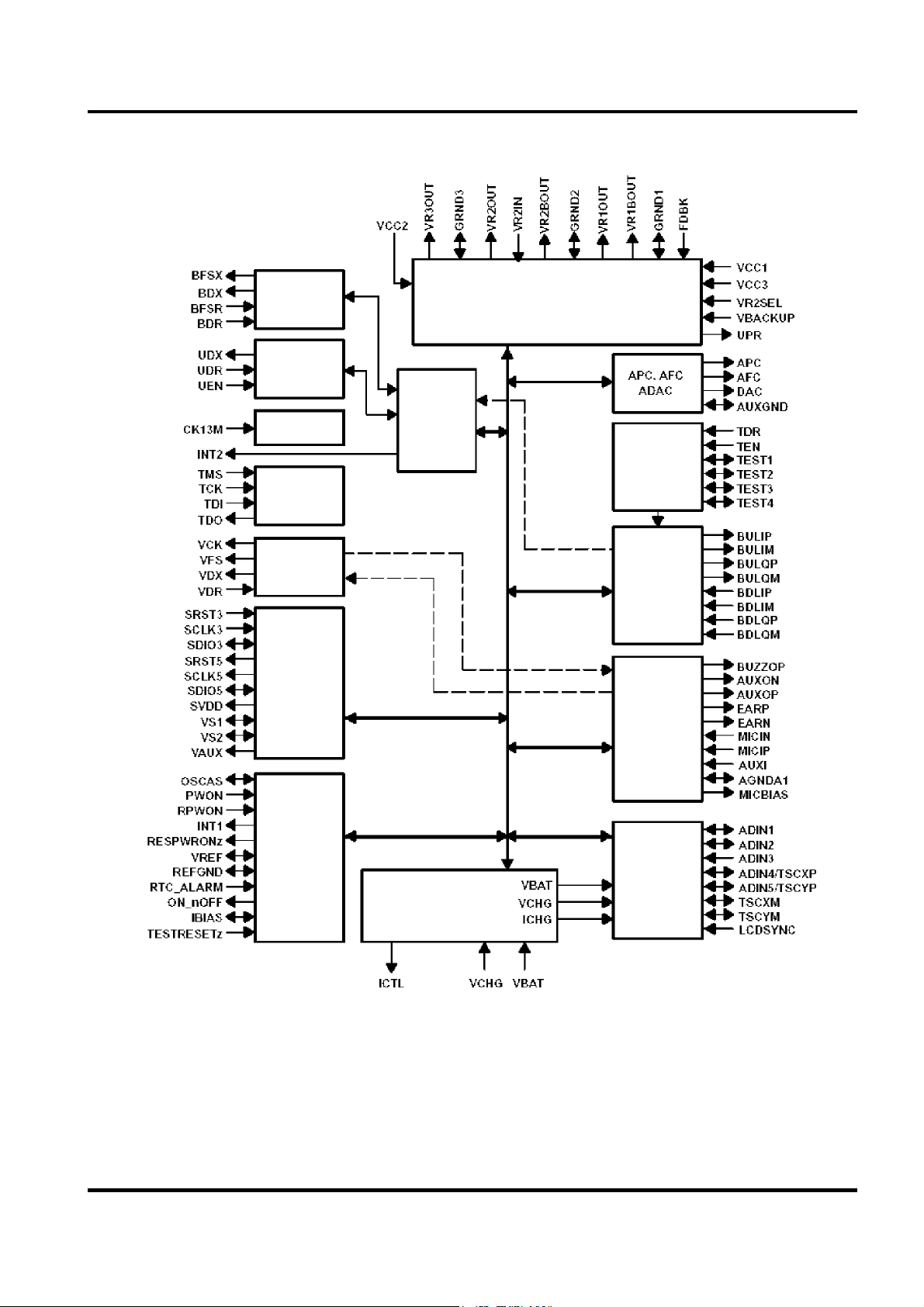

3.2 Аналоговый процессор низкочастотной части (АВВ)

Данное устройство имеет наименование TWL3012В, и наряду с цифровым процессором

низкочастотной части (DBB) предназначено для применения в телефонных аппаратах сотовой

связи, включая стандарты GSM 900, DCS 1800 и PCS 1900 (двухдиапазонный). Устройство

TWL3012В включает полный набор функций низкочастотной части, обеспечивающих интерфейс и

обработку поступающих речевых сигналов, синфазных (I) и квадратурных (Q) сигналов, и

поддерживающих как одноканальные, так и многоканальные режимы. Устройство TWL3012В также

обеспечивает сопряженное вспомогательное управление РЧ, регулирование подаваемого

напряжения, управление зарядкой аккумуляторной батареи, анализ включения/выключения

системы. Устройство TWL3012В имеет интерфейсное взаимодействие с цифровым процессором

низкочастотной части (DBB) через цифровой последовательный порт низкочастотной части (BSP) и

последовательный порт речевого канала (VSP). Порты передачи сигналов сообщаются с ядром

цифрового процессора сигналов (LEAD). Последовательный порт микроконтроллера (USP) связан

с ядром микроконтроллера, а последовательный порт синхронизации (TSP) – с контроллером

последовательности операций GSM в реальном масштабе времени (TPU).

Для поддержки интерфейса 3В/5В SIM-карты есть специальный модуль. Данный модуль

контролирует подачу напряжения на SIM-карту, а также необходимое смещение уровня для

обеспечения соответствия между уровнями сигналов SIM-карты и уровнями сигналов вводавывода микроконтроллера. Устройство TWL3012В отвечает требованиям стандарта

контролепригодности JTAG («Объединенная рабочая группа по автоматизации тестирования») –

IEEE Std 1131.1-1990. Тестирование производится чере з стандартный порт контрольного доступа

(ТАР) методом периферийного сканирования. Устройство TWL3012В также имеет источник

опорного напряжения на том же кристалле, схемы обнаружения понижения напряжения и сброса

цепей включения питания.

- 19 -

Page 20

3.2.1 Блок-схема

Последовательный

порт

низкочастотной

части (BSP)

Последовательный

порт

микроконтроллера

(USP)

Генератор

тактовой частоты

(CKG)

Порт

контрольного

доступа

(ТАР)

Последовательный

порт речевого

канала

(VSP)

Регулировка напряжения

(VREG)

Внутренний

шинный

контроллер

(IBIG)

(2,7 В, 1,8 В)

Последовательный

порт

синхронизации

(TSP)

Кодек

низкочастотной

части

(ВВС)

Стабилизатор

напряжения

SIM-карты, и

схемы сдвига

уровня 3В/5В

(SIMS)

Источник

опорного

напряжения и

схема цепей

включения

питания

(VRPC)

(АРС) – Автоматическая регулировка мощности

(AFC) – Автоматическая подстройка частоты

(ADAC) – Аналого-цифро-аналоговый преобразователь

Рис. 3-2-1. Блок-схема устройства Nausica

Интерфейс зарядного

устройства

(ВСI)

Кодек речевого

канала

(VBC)

Контрольный

аналого-

цифровой

преобразователь

(MADC)

- 20 -

Page 21

3.2.2 Характеристики

Устройство TWL3012В обеспечивает поддержку следующих элементов:

• Прикладные системы, включая телефоны сотовой связи форматов GSM 900, PCS 1900 и DSC

1800.

• Речевой кодер/декодер (кодек).

• Одноканальный и многоканальный РЧ интерфейс I и Q сигналов с кодеком низкочастотной части.

• Вспомогательные РЧ преобразователи.

• Интерфейс SIM-карты.

• Управление зарядкой ионно-литиевой или никеле-металлогидридной батареи.

• Шесть малошумящих линейных стабилизатора напряжения.

• Детекторы напряжений (с задержкой выключения).

• Пятиканальный аналого-цифровой преобразователь.

• Низкий ток покоя.

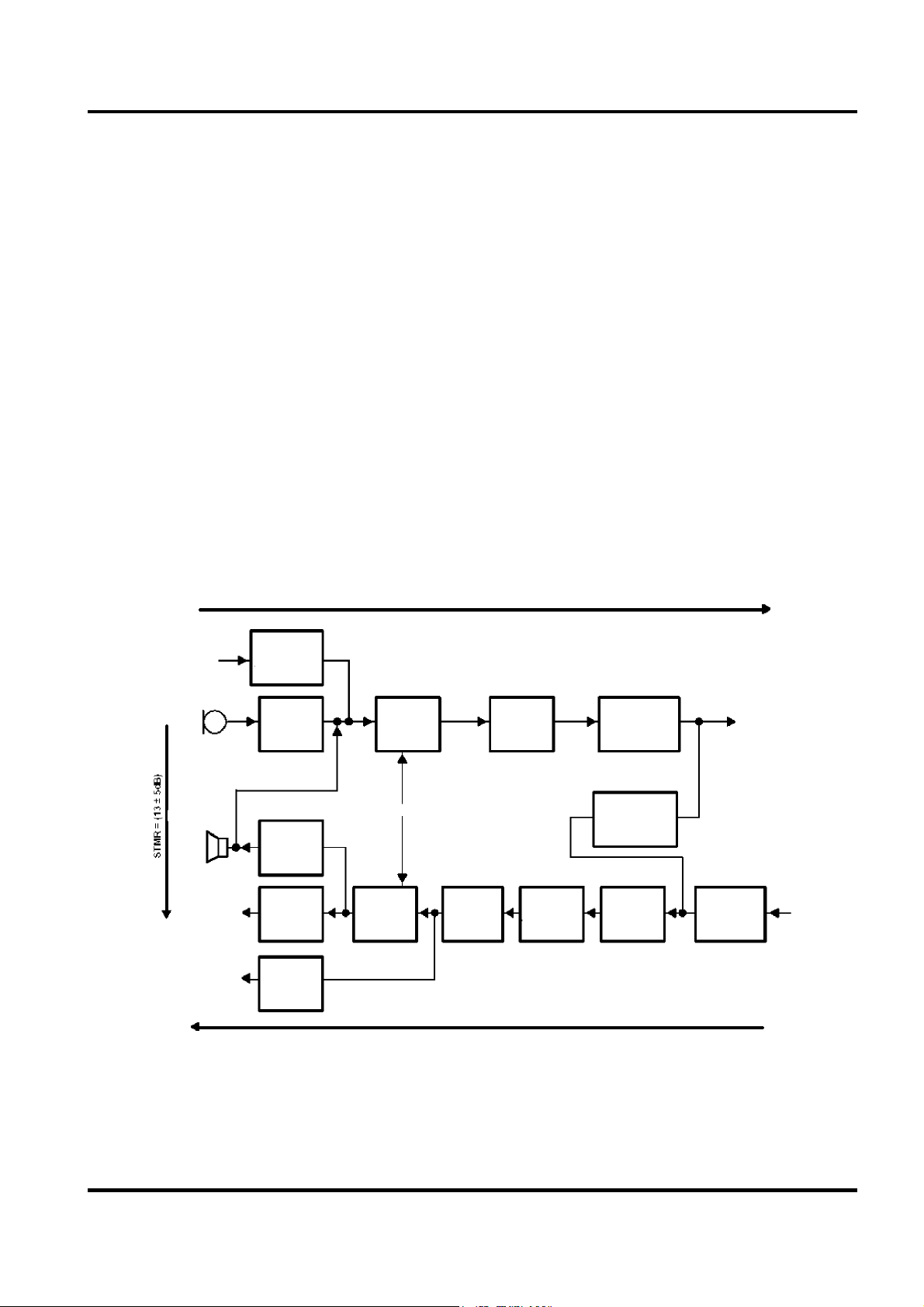

3.2.2.1 Кодек речевого канала

Схемы кодека речевого канала выполняют обработку аналоговых звуковых сигналов восходящего

речевого канала (VUL), и последующую передачу этих сигналов для их конечной модуляции в

низкочастотной части. Схемы кодека также преобразуют речевые данные нисходящего речевого

канала, поступающие через последовательный интерфейс голосового диапазона (VSP), в

аналоговые звуковые сигналы. В нижеследующих параграфах приводится более подробное

описание системы двунаправленной передачи данных.

365 мВ (ср. квадр.)

Чувствительность

–49,3 дБВ/Па

32,5 мВ (ср. квадр.)

1,385 В (ср. квадр.)

Чувствительность 106,7 дБ

уровень звукового давления/

блок-модуль опознавания

речевых команд

692 мВ (ср. квадр.)

0 В на AVDD

AUXI

4,6 – 28,2 дБ

Усилитель

микрофона

25,6 дБ

Усилитель

наушника

1 дБ

Вспомогательный

усилитель

-5 дБ

Зуммер

Широтноимпульсная

модуляция

1 МГц

620 мВ (ср. квадр.)

Аналого-цифровой

1,237 В (ср. квадр.)

Цифро-аналоговый

преобразователь и

сглаживающий

фильтр 0 дБ

Номинальный уровень громкости передачи = (8 ± 3 дБ)

Цифровой

модулятор

0 дБ

восходящего

преобразователь

2,5 дБ

VREF 1,75В

1Б + 1Б

4Б

Номинальный уровень громкости приема = (2 ± 3 дБ)

Фильтр

тракта

3,5 дБ

Усилитель с

программируемым

усилением

Усиление: 0 дБ

-6 дБ до 6 дБ

1-дБ шаг

Усилитель с

программируемым

усилением

Усиление: 0 дБ

12 дБ до –12 дБ

1-дБ шаг

Sidetone:

1 дБ до –23 дБ

отключение звука

Фильтр

нисходящего

тракта

0 дБ

3 дБм0

Полная шкала

16 бит

Регулятор громкости

0 дБ до –24 дБ

+ отключение звука

3 дБм0

Полная шкала

16 бит

Рис. 3-2-2. Блок-схема кодека речевого канала

- 21 -

Page 22

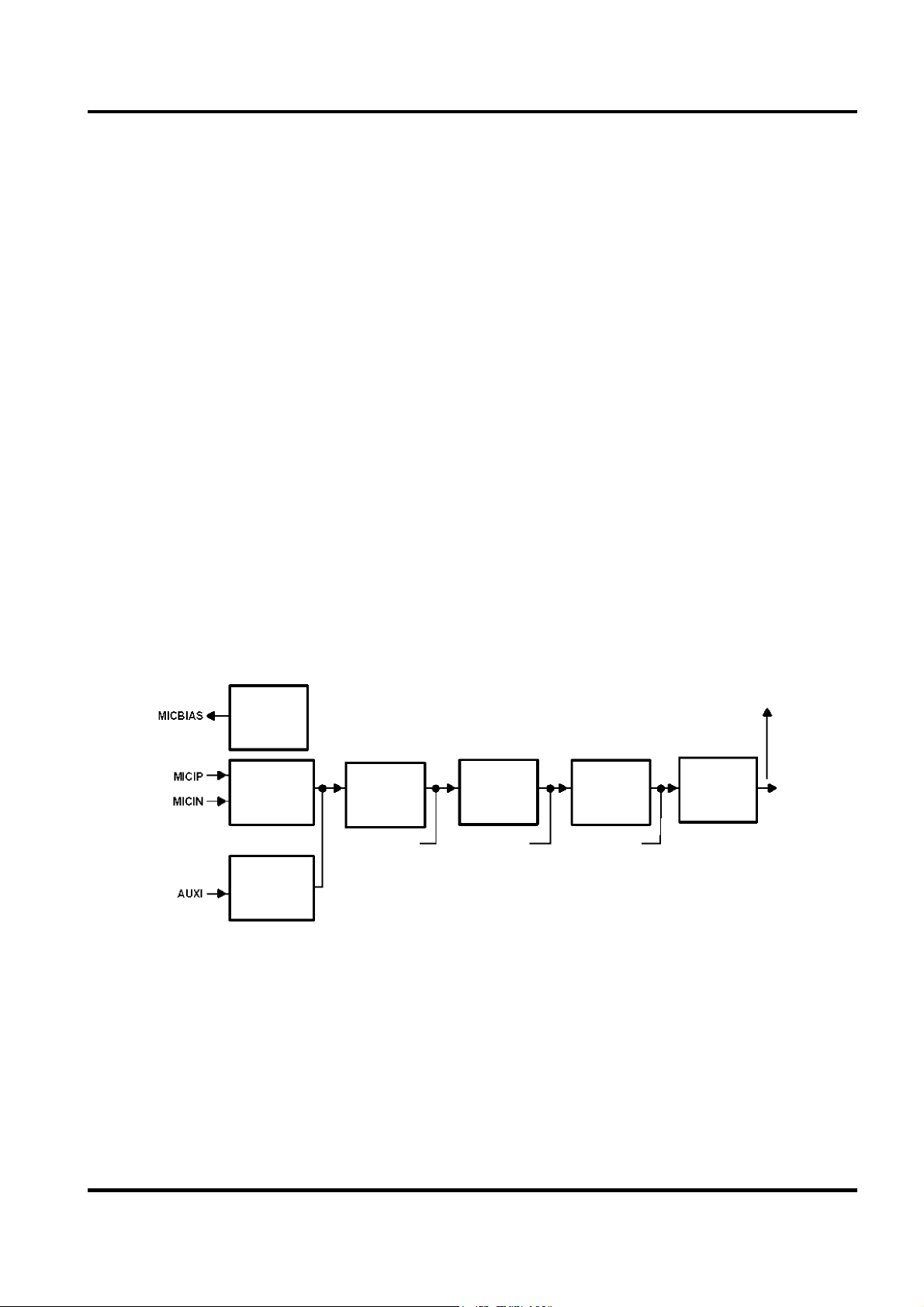

3.2.1.1 Восходящий тракт речевых сигналов

Восходящий тракт речевых сигналов состоит из двух входных каскадов. Первый каскад – это

микрофонный усилитель, совместимый с электронными микрофонами, оборудованный буферной

схемой на полевом транзисторе и открытым стоком на выводе. Микрофонный усилитель с

номинальным коэффициентом усиления 25,6 дБ (± 1 дБ) подает на микрофон напряжение

смещения 2,0 В - 2,5 В (К9, MICBIAS). Вспомогательный звуковой вход может быть задействован в

качестве альтернативного источника звуковых сигналов высшего уровня. В данном каскаде

производится преобразование несимметричных сигналов в дифференциальные, а также

программируемое усиление с 4,6 дБ до 28,2 дБ. В случае использования вспомогательного

звукового входа микрофонный вход запирается, и питание на него не подается.

Полученный полностью дифференцированный сигнал поступает на аналого-цифровой

преобразователь определяемый величиной внутреннего опорного напряжения.

Аналого-цифровое преобразование выполняется S-D модулятором третьего порядка с частотой

амплитудно-импульсной модуляции 1 МГц. Выходной сигнал с аналого-цифрового

преобразователя подается на цифровой фильтр звуковых частот, который производит сужение

диапазона до 8 Кгц и ограничивает полосу пропускания сигнала как по нижним, так и по верхним

частотам. Программируемое усиление задается в цифровом виде в пределах от –12 дБ до + 12 дБ

при шаге в 1 дБ, с помощью разрядов 4-0 (VULPG(4:0)) регистра восходящего тракта речевого

диапазона (см. параграф 5.3.12.2). Затем речевые сигналы через последовательный порт речевого

канала передаются на цифровой процессор сигналов с частотой 8 Кгц. Имеется 15 значащих

разрядов вывода.

Программируемые функции восходящего тракта речевых сигналов, включение питания, выборка

входных сигналов, а также усиление управляются через последовательные порты низкочастотной

части или микроконтроллера. Питание восходящего тракта речевых сигналов отключается при

помощи разряда 0 (VULON) регистра отключения питания.

Генератор

напряжения

смещения

Микрофонный

усилитель

25,6 дБ

Вспомогательный

усилитель с 4,6 дБ до

28,2 дБ

Сигма-Дельта-

модулятор 2,48 дБ

1 Частота

дискретизации = 1 Мгц

Фильтр

синхроимпульсов

2 Частота

дискретизации = 40 Кгц

Полосно-пропускающий

фильтр восходящего

тракта 3,52 дБ

3 Частота

дискретизации = 8 Кгц

Рис. 3-2-3. Восходящий тракт речевых сигналов

Боковой тональный сигнал к

нисходящему тракту речевых

Усилитель с

программируемым

усилением

от 12 до –12 дБ

сигналов

К последовательному

интерфейсу речевых

сигналов

- 22 -

Page 23

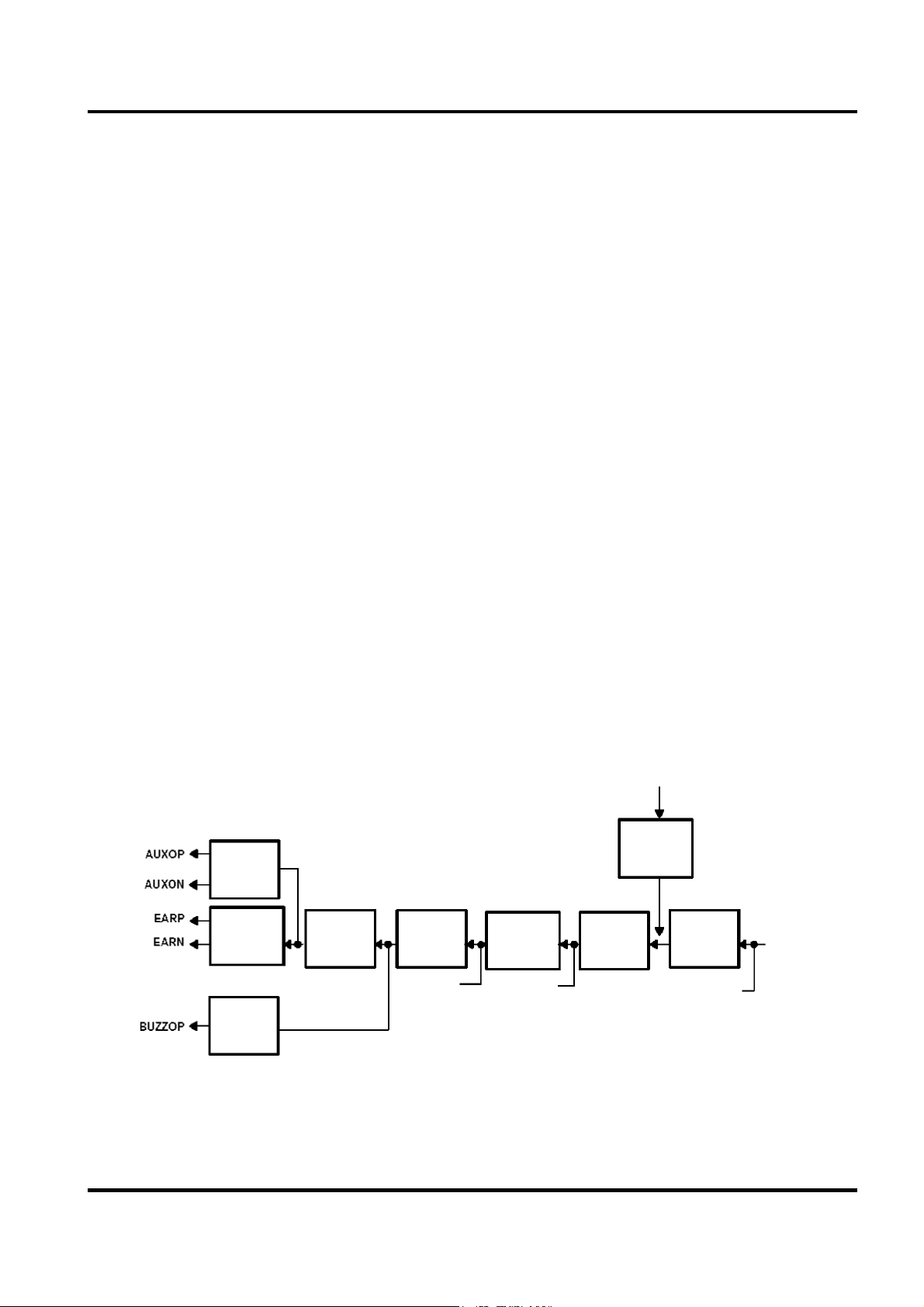

3.2.1.2 Нисходящий тракт речевых сигналов

Речевые сигналы в импульсной форме поступают с цифрового процессора сигналов через

последовательный порт речевого канала на нисходящий тракт с частотой дискретизации 8 Кгц.

Здесь происходит их преобразование в аналоговые сигналы для управления внешним

преобразователем речевых сигналов.

Поступающие с цифров ог о процессора оцифрованные речевые сигналы сначала подаю тся на

цифровой фильтр речевых сигналов, который имеет две функции. Первая из них – интерполирование

входного сигнала и повышение частоты амплиту дно-импульсной мо ду ляции с 8 Кгц до 40 Кгц, в це лях

последующего цифро-аналогового преобразования сигнала при помощи цифров ог о модулятора с

избыточной частотой дискре тизации. Второй функцией цифровог о филь тра являе т ся ограничение

полосы пропускания сигнала, как по нижним, так и по верхним часто там. Филь тр можно обойти путем

программирования разряда 9 (VFBYP) в управляющем регистре речевог о диапазона.

Интерполированный сигнал ограниченного диапазона подается на S-D мо дулятор второго порядка с

частотой дискретизации 1 Мгц, который производит 4-разрядный (9-уровневый) сигнал с избыточной

частотой дискретизации. Затем сигнал пропускается через блок согласования динамических

элементов, после чег о он поступает на 4-разрядный цифро-аналоговый преобразователь.

В результате произведенного преобразования с избыточной частотой дискретизации, при выходе

аналогового сигнала с 4-разрядного цифро-аналогового преобразователя происходит смешивание

сигнала с высокочастотными шумами. Однако, поскольку сигнал выдается в 4-разрядном

цифровом виде, для отделения от него помех достаточно резистивно-ёмкостного фильтра

(входящего в состав 4-разрядного цифро-аналогового преобразователя).

Регулирование громкости и программируемого усиления осуществляются при помощи цифрового

фильтра передатчика. Регулировка громкости производится ступенчато, с шагом 6 дБ, в интервале

от 0 дБ до –24 дБ. В режиме выключения звука коэффициент ослабления превышает 40 дБ. Точная

регулировка усиления возможна в интервале от –6 дБ до +6 дБ с величиной шага 1 дБ для

калибровки системы применительно к техническим параметрам наушника. Программирование этой

конфигурации производится в управляющем регистре нисходящего тракта речевых сигналов.

С усилителя наушника полностью дифференцированный сигнал подается на выводы Н9 (EARP) и

Н8 (EARN), а со вспомогательного выходного усилителя дифференцированный сигнал поступает

на выводы J9 (AUXOP) и J10 (AUXON). Питание нисходящего тракта речевых сигналов можно

отключить программированием разряда 1 (VDLON) регистра понижения мощности.

Зуммер приводится в действие находящимся на плате биполярным транзистором. Управление

осуществляется при помощи пода чи выходного сигнала BUZZOP (с вывода К10) на базу транзистора

в виде по тока бит ов широко-импульсной мо дуляции с про должительностью импульса в1 Мгц.

Боковой тональный

сигнал от

восходящего тракта

Вспомогательный

усилитель

-5 дБ

Усилитель наушника

1 дБ

Широко-импульсный

модулятор зуммера

Аналого-цифровой

преобразователь и

фильтр нижних

частот

4-разрядный

выходной сигма-

дельта модулятор

1 Частота

дискретизации = 1 Мгц

Усилитель с

программируемым

усилением входящего

сигнала

(с –6 до 6 дБ, с шагом

в 1 дБ)

2 Частота

дискретизации = 40 Кгц

речевых сигналов

Полосно-

пропускающий

фильтр нисходящего

тракта с бесконечной

импульсной

характеристикой

Регулирование

громкости

3 Частота

дискретизации = 8 Кгц

От последовательного

интерфейса речевых

сигналов

Рис. 3-2-4. Нисходящий тракт кодека речевых сигналов

3.2.2.1.2 Нисходящий тракт речевых сигналов

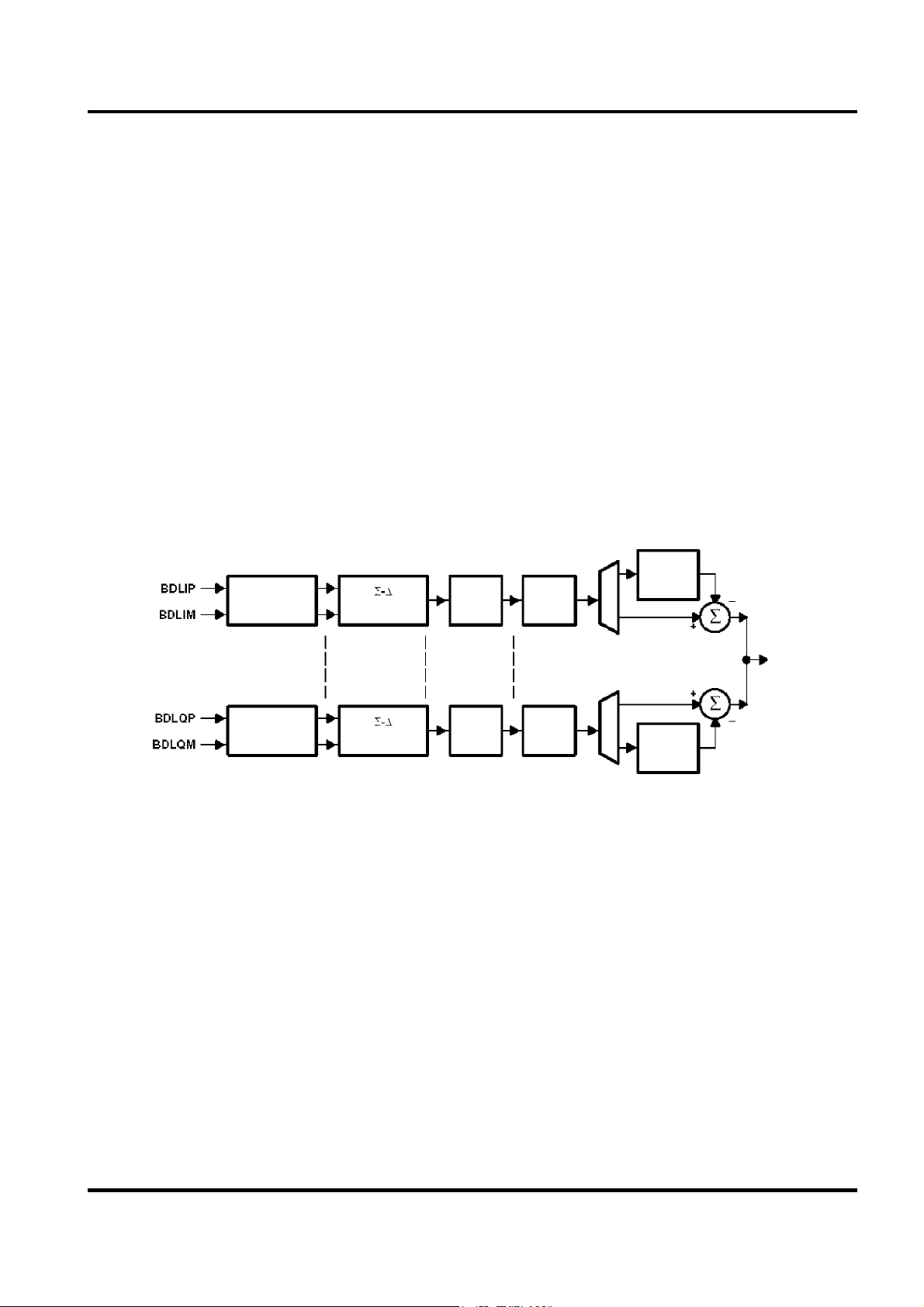

Кодек низкочастотной части состоит из двухканального восходящего тракта низкочастотной части

(BUL) и двухканального нисходящего тракта низкочастотной части (BDL).

- 23 -

Page 24

3.2.2.2.1 Восходящий тракт речевых сигналов

Блок модулятора восходящего тракта низкочастотной части выполняет GMSK-модуляцию в

соответствии со стандартом GSM. На модулятор сигналы поступают с РЧ интерфейса цифрового

процессора (RIF) через последовательный порт низкочастотной части (BSP).

Модулятор GMSK являе тся цифровым, фильтр Гаусса рассчитан на поток 4-разрядных входящих

данных, закодированных по справ очным таб лицам синусов/косинусов в ПЗУ. Модулятор производит

синфазные (I) и квадра турные (Q) оцифрованные сигналы с коэффициентом интерполяции 16.

Данные оцифрованные подвергаются дискретизации с частотой 4,33 Мгц, и подаются на входы

пары 10-разрядных цифро-аналоговых преобразователей. После них аналоговые выходные

сигналы пропускают через фильтры Бесселя третьего порядка для уменьшения внеполосных

шумов и боковых гармоник, и для получения спектра модулированных выходных сигналов

соответствующих стандарту GSM.

Полностью дифференцированные сигналы поступают на выводы С9 (BULIP), C10 (BULIM), D8

(BULQP) и D9 (BULQM).

С целью максимального снижения погрешности фазовой траектории, смещение постоянной

составляющей каналов I и Q может быть сведено к минимуму путем выпо лнения калибровки смещения.

В проц ессе калибровки смещения коды входа 10-разрядног о цифро-аналогового преобраз ов ат е ля

устанавливаются на «0», а для минимизации смещения постоянной состав ляющей вых одных

аналоговых сигналов используе тся 6-разрядный вспомога те льный цифро-аналоговый преобразова те ль.

До начала передачи все элементы пакетного сигнала, включая сторожевые разр яды, хвост овые разряды и

информационные разр яды хранятся в одном или дв ух 160-разр ядных буферных запоминающих

устройствах паке тной передачи. Наличие двух пакетных буферных ЗУ объясняе тся необхо димостью

поддержания мног оканальной передачи: в то время, как в о дно буферное ЗУ происходит загрузка новых

данных, данные из другого устройства выводятся на GMSK-модулятор для передачи.

Выбор одноканального или многоканального режима осуществляется при помощи разряда 6

(MSLOT) управляющего регистра кодека низкочастотной части. В случае выбора одноканального

режима, модуляции подвергается только содержимое буферного ЗУ 1.

Выходной уровень выбирается при помощи разряда 8 (OUTLEV1) или 7 (OUTLEV0) управляющего

регистра кодека низкочастотной части.

Обычная последовательность пакетной передачи включает следующие этапы:

1.Включение питания двухканального восходящего тракта низкочастотной части.

2.Выполнение калибровки смещения (не обязательно).

3.Модулирование содержимого буферного ЗУ.

Синхронизация данной последов а тельности контролиру ется через последовательный порт

синхронизации, принимающий сигнал управления в реальном масштабе времени с блока обработки

по времени (TPU)цифрового процессора низкочастотной части (DBB). Передача пакета данных

осуществляется при помощи трех управляющих сигналов: BULON, BULCAL и BULENA. Каждому

сигналу соответствует окно времени. Сигнал BULON включает при высоком уровне активный режим

двухканального восхо дящег о тракта низкочастотной части после задержки, связанной с установкой

времени включения аналоговог о блока. Сигнал BULCAL активизирует окно калибровки смещения . При

поступлении команды BULCAL, коды сигналов входа на 10-разрядный цифро-аналоговый

преобразоват ель прину дительно устанавливаются на «0», а компаратор малого смещения замер яет

уровень на выво дах С9/С10 (BULIP/BULIM) и D8/D9 (BULQP/BULQM). Результат сравнения

используется для обнов ления содержания регистров смещения, с помощью которых 6-разрядный

вспомогательный цифро-аналоговый преобразова т ель уменьшает ошибки смещения постоянной

составляющей. Продолжительность периода калибровки зависит от времени необходимого для

развертки динамического диапазона вспомогат ельного цифро-аналогового преобраз ов ателя. Процесс

модулирования на чинается с верхнего края сигнала BULENA, и заканчивается чере з 32 четвертных

бита после нижнег о края сигнала BULENA. По завершении модулирования модулятор

инициализируется заново путем у становки указателей буферных ЗУ пакетной передачи и ПЗУ

фильтра на адрес базы. Вектор I устанавлив ае т ся на максимальное значение, а вектор Q – на 0.

Подача мощности для рассогласования усиления между каналами I и Q дает возможность

компенсировать естественную несогласованность либо несовершенство у силения РЧ смесителя

через разряды 5 (IQSEL), 3 (GO) и 4 (G1) управляющего регистра кодека низкочаст отной части.

Выходное напряжение синфазного сигнала на выводах С9 (BULIP), С10 (BULIM), D8 (BULQP) и D9

(BULQM) может быть установлено на VDD/2 с фиксированным зна чением 1,35 В, либо на VGAP при

помощи разрядов 1 (SELVMID1) и 0 (SELVMID0) управляющего регистра кодека низко част о тной части.

- 24 -

Page 25

От последовательного порта

синхронизации (TSP)

Управление

синхронизацией

6-разрядный

цифро-

аналоговый

усилитель

Регистр

смещения

От последовательного порта

низкочастотной части (BSP)

Буфер 1 пакетной

передачи

Буфер 2 пакетной

передачи

270 Кгц

Модулятор GMSK

Таблица

косинусов

Таблица

синусов

10-разрядный

цифро-

аналоговый

усилитель

10-разрядный

цифро-

аналоговый

усилитель

6-разрядный

цифро-

аналоговый

усилитель

16 х 270 Кгц

Фильтр низких

частот

Фильтр низких

частот

Регистр

смещения

Рис. 3-2-5. Блок-схема восходящего тракта низкочастотной части

3.2.2.2.2 Нисходящий тракт низкочастотной части

Нисходящий тракт низкочастотной части (BDL) состоит из двух идентичных контуров для обработки

аналоговых I и Q сигналов низкочастотной части, вырабатываемых РЧ контуром. Первый каскад

нисходящего тракта низкочастотной части представляет собой аналоговый фильтр второго порядка

для защиты от наложения спектров внеполосных частот, возникающих в результате дискретизации

сигналов в аналого-цифровом преобразователе. Данный фильтр также выполняет функцию

каскада адаптации между внешними и внутрикристальными схемами.

За фильтром защиты от наложения спектров следует S-D-модулятор третьего порядка,

выполняющий аналого-цифровое преобразование при частоте дискретизации 6,5 Мгц. Аналогоцифровой преобразователь подает двухразрядные слова на цифровой фильтр, который при

коэффициенте прореживания 24 снижает частоту дискретизации до 270,8 Кгц. Аналого-цифровой

преобразователь также производит разделение каналов путем подавления смежных частот – для

обеспечения соответствия технических характеристик демодуляции стандарту GSM.

Нисходящий тракт низкочастотной части также имеет регистр смещения, сохраняющий значение

величины смещения постоянной составляющей канала. Данное значение вычитается из величины

выходного сигнала перед тем, как оцифрованные сигналы передаются на цифровой процессор

сигналов через последовательный порт низкочастотной части. После сброса значение регистра

смещения при загрузке устанавливается на «0». Содержимое регистра обновляется в процессе

калибровки.

Обычная последовательность приема пакетного сигнала включает следующие этапы:

1.Включение питания нисходящего тракта низкочастотной части.

2.Выполнение калибровки смещения (не обязательно).

3.Преобразование и фильтрование I и Q составляющих и передача оцифрованных сигналов.

Синхронизация данной последовательности контролируется через последовательный порт

синхронизации, принимающий сигнал управления в реальном масштабе времени с блока

обработки по времени (TPU) цифрового процессора низкочастотной части (DBB). Передача пакета

данных осуществляется при помощи трех управляющих сигналов: BDLON, BDLCAL и BDLENA.

Каждому сигналу соответствует окно времени.

- 25 -

Page 26

Сигнал BDLON включает при высоком уровне активный режим нисходящего тракта низкочастотной

части после задержки, связанной с установкой времени включения аналогового блока. Сигнал

BDLCAL активизирует окно калибровки смещения. Выбор одного из двух возможных режимов

калибровки смещения определяется состоянием разряда 9 (EXTCAL) управляющего регистра

кодека низкочастотной части. При нулевом значении EXTCAL входы аналоговых сигналов

отключаются от внешних устройств и внутренне закорачиваются. Результат выполненного в данном

состоянии преобразования сохраняе тся в регистре смещения. При значении EXTCAL равном «1»

вход аналоговых сигналов остается подключенным к внешним схемам, а результат

преобразования, включающий в данном случае внутреннее смещение плюс смещение на внешних

схемах, сохраняется в регистре смещения. Продолжительность окна калибровки главным образом

зависит от времени установления цифрового фильтра.

Преобразование данных начинается с верхнего края сигнала BDLENA, о днако, первые восемь

дискретизированных сигналов I и Q на цифровой процессор сигналов не передаются, так как они

являются незначимыми вследствие групповой задержки цифрового фильтра. Верхний край

сигнала BDLENA также используется внутренним контроллером интерфейса шины для

воздействия на тракт передачи от последовательного порта низкочастотной части к восходящему

тракту низкочастотной части в течение всего окна приема. На нижнем краю сигнала BDLENA

происходящее преобразование завершается, а сигналы передаются до момента завершения

преобразования. И в завершение сигнал BDLON переводит нисходящий тракт низкочастотной

части в неактивный режим при низком уровне.

Регистр

смещения

Фильтр защиты от

наложения спектров

модулятор

Фильтр

синхро-

импульсов

Фильтр с

конечной

импульсной

характеристикой

К последовательному

порту низкочастотной части

Фильтр защиты от

наложения спектров

Частота дискретизации

= 6,5 Мгц

модулятор

Частота дискретизации

= 1,08 Мгц

Фильтр

синхро-

импульсов

Частота дискретизации

= 270,8 Кгц

Фильтр с

конечной

импульсной

характеристикой

Регистр

смещения

Рис. 3-2-6. Блок-схема нисходящего тракта низкочастотной части

3.2.2.3 Последовательный интерфейс порта синхронизации (TSP)

Последовательный интерфейс порта синхронизации дает возможность последовательной

передачи управляющих окон низкочастотной части для кодека низкочастотной части Nausica.

Операции осуществляются при посредстве блока обработки во времени, обеспечивающем

четвертьразрядное разрешение в системе GSM и точную установку команд кодека в кадре GSM

TDMA. Формат данных для этой передачи включает семь разрядов, в том числе команды

управления восходящим/нисходящим трактами (включение, калибровка, разрешение операций) и

стартовый бит для аналого-цифрового преобразователя. Этот командный бит обеспечивает

точность начала преобразования сигналов аналого-цифровым преобразователем в кадре

множественного доступа с временным уплотнением (TDMA).

Этот канал передачи не дает доступ к регистру Nausica, воспринимается только передача от Calypso

к Nausica К порту синхронизации Calypso также подключен последовательный интерфейс Aero

(производства «Si Lab»). Чере з это звено Calypso осуществляет программирование синтезаторов,

приемного устройства, схемы фазовой автоподстройки частоты, контроллера усилителя мощности.

Тактовая частота последовательного порта синхронизации составляет 6,5 Мгц.

- 26 -

Page 27

3.2.2.4 Последовательный интерфейс RIF/BSP (радио-интерфейс / последовательный порт

низкочастотной части)

Этот интерфейс предназначен для восходящей и нисходящей передач дискретизированных

сигналов I и Q между цифровым процессором сигналов и кодеком низкочастотной части, а также

для доступа к регистру Nausica. По восходящему тракту цифровой процессор сигналов посылает

на кодек пакетные разряды для модулирования, в то время как по нисходящему тракту процессор

принимает немодулированные сигналы I и Q.

Доступ для записи на регистр Nausica осуществляется в том же формате данных, что и на

восходящем тракте. Основными функциями являются:

• Программирование параметров автоматической регулировки мощности (уровни, задержки,

коэффициенты линейных изменений);

• Автоматическая регулировка частоты;

• Управление кодеком речи.

Доступы к регистру можно считать синхронизированными с кадром множественного доступа с

временным разделением (ТDMA), так как цифровой процессор сигналов принимает команды на

границе начала кадра ТDMA. Тактовая частота последовательного сопряжения радио-интерфейса/

порта низкочастотной части составляет 13 Мгц. Доступ к последовательному порту низкочастотной

части запрещается при значении ACTIVMCLK = 0.

3.2.2.5 Последовательный интерфейс SPI/USP (интерфейс с системной службой /

последовательный порт микроконтроллера) процессора ARM

Данный интерфейс относится к регистру записи и считывания Nausica, с доступом с микросхемы

Calypso. Данный канал предоставляет доступ ко всем регистрам Nausica, в то время как порт USP

используется для конфигурирования и управления состоянием каждого блока устройства Nausica.

Через данный интерфейс возможно считывание результатов преобразования сигналов аналогоцифровым преобразователем. Доступ является асинхронным в отношении кадра TDMA, его

приоритет выше, чем у доступа последовательного порта низкочастотной части. Разрешение

конфликтов, возникающих в результате одновременного обращения интерфейса с системной

службой ARM и радио-интерфейса LEAD, возложено на внутренний контроллер шинного

интерфейса Nausica. Тактовая частота данного последовательного соединения составляет 13 Мгц.

3.2.2.6 Последовательный интерфейс SPI/VSP (интерфейс с системной службой /

последовательный порт речевого канала) процессора LEAD

При помощи данного интерфейса осуществляется прохождение оцифрованных речевых сигналов

по нисходящему и восходящему тракту между цифровым процессором сигналов и кодеком

речевого диапазона Nausica. Последовательный порт речевого канала Nausica является главным

портом передачи сигналов. Тактовая частота данного соединения – 500 Кгц.

3.2.2.7 Интерфейс JTAG

Порт доступа к средствам тестирования (TAP) соотве тству е т стандарту контролеприг одности JTAG (IEEE

Std1131.1-1990). Через данный порт возможна у становка типовых программ стандар та JTAG, а также

частных программ для специального конфигурирования устройства в ц е лях тестирования или от ладки.

3.2.2.7 Генераторы тактовой частоты

На устройство Nausica т актовые импульсы поступают с двух тактовых генера торов микропроцессора

Calypso.

Сигналы генератора малой тактовой частоты («медленного» г енера тора) CLK32K_OUT используются

цифровым процессором низкочастотной части в качестве опорных сигналов в неактивных режимах

(архивации, ожидания ). Аналоговый процессор низкочастотной части принимает данный тактовый

генератор в качестве синхронизирующего генератора для управ ления включением питания по

источнику опорного напряжения (VRPC), и в качестве г енера тора опорных тактовых импульсов при

отсутствии генератора большой тактовой частоты («быстрог о » генератора).

- 27 -

Page 28

Импульсы генератора большой тактовой частоты CLK13М_OUT используются и цифровым и

аналоговым процессорами процессором низкочастотной части в качестве опорных сигналов во

всех режимах, включая режим последовательной передачи.

Кристалл на 32 Кгц встроен между входом и выходом генератора (выводы OS32K_IN и

OSC32K_OUT). Соединение выполнено как можно более коротким. На кристалле соединены два

нагрузочных конденсатора, и общая точка (цепь с замыканием через корпус) должна соединяться с

выводом VSSO заземления выделенного генератора.

Подающий на генератор питание фильтрующий конденсатор соединяется с выводом VSSO (та же

точка, что и точка возврата нагрузочного конденсатора кристалла) и напрямую с ближайшим

выводом VDDRTC при минимально возможной длине соединения. Это делается с целью защиты

параметров дрожания частоты от исходящих с линии питания помех, порождаемых быстрыми

переходами внутренней логической схемы.

3.2.2.9 Прерывания

Устройство Nausica может вырабатывать два вида сигналов прерывания:

• Сигнал экстренного прерывания, подаваемый на вывод EXT_FIQ устройства Calypso,

означающий обнаружение низкого напряжения аккумуляторной батареи.

• Подаваемый на вывод EXT_FIQ устройства Calypso сигнал прерывания при обнаружении

состояния:

- Нижний или верхний край сигнала на выводе RPWON.

- Нижний край сигнала на выводе PWON.

- Завершение преобразования из аналоговой формы в цифровую.

- Подключение зарядного устройства к сети электропитания.

3.2.2.10 Сигналы управления питанием

Три сигнала, управляющие состоянием системы и изменениями состояния системы, подаются на

участок питания VRRTC.

• Сигнал nRESPWONZ.

- генерируется аналоговым процессором низкочастотной части.

- частично сбрасывает питание цифрового процессора низкочастотной части.

- задействуется только один раз (при наличии любого вида питания – ВВ или МВ) при первом

включении аппарата. Логическая схема управления питанием распространяет данный сигнал

для выполнения всеобщего сброса по мере запитывания остальной части кристалла.

• Сигнал ON_nOFF.

- генерируется цифровым процессором низкочастотной части.

- сбрасывает в исходное состояние модули ASIC, ARM, LMM.

- находится на низком логическом уровне при каждом выключении системы. Сигнал

вырабатывается логической схемой управления питанием и подается в остальную часть цепи.

• Сигнал ITWAKEUP.

- генерируется цифровым процессором низкочастотной части.

- используется для запуска системы из неактивных режимов (сохранения, ожидания).

- построен в виде комбинации всех запросов на прерывание, запускающих модуль ULPD

микропроцессора Calypso и систему реального времени (RTC)

- 28 -

Page 29

3.2.2.11 Стабилизация напряжения (VREG)

На кристалле аналогового процессора низкочастотной части имеется 5 стабилизаторов

напряжения низкой выходной мощности (LDO). Значения напряжений на выходе этих пяти

стабилизаторов приведены в нижеследующей таблице. На схеме (рис. 3-6) показаны связанные с

подачей питания блоки цифрового и аналогового процессоров низкочастотной части и их

интерфейсы в G7030.

MB

VBACKUP

BUB

VCC2

0.2 Ω

VBAT

NAUSICA

BBS

VR2

VR1

ABB

VRPC core

VR2_BU

VR2B_BU

VR1_BU

CLK13M

VR2

10uF

VR2B

10uF

VR1

1.8V

10uF

UPR

1uF

2.8V I/O

2.8V I/O

2.8V I/O

2.8V

2.8V

VR2B

VDDS-RTC

External

ON_nOFF

VBACKUP

RESPWONZ

XO32K_OUT

2.8V

VDD-RTC

LDO

IT_WAKEUP

CLK13M_OUT

VDDS_MIF

VDD , VDDPLL

VDDS1,VDDS2,VDDANG

Split Power ring

RTC & SPLIT DOMAIN

DATA & CONTROL

Split

Power

Logic

RTC and XO32K

reset

IT_WAKE_FROM_SLEEP

RTC_ALARM

XO32K Conf

registers

XO32K

CALYPSO

Powerdown

of internal

level shifter

G2_ON_nOFF

G2_RESPWONZ

Рис. 3-2-7. Совместимое соединение с Nausica

Надписи на схеме:

ABB VRPC core Узел управления подачей питания и стабилизации

External LDO

Split power ring Кольцо деления мощности

RTC&SPLIT DOMAIN Область генератора импульсов истинного времени и

напряжения аналогового процессора низкочастотной части

Внешний стабилизатор

делителя мощности

Таблица 3-2-1. Напряжения на выходе стабилизаторов

Напряжение на выходе Применение

VR1 1,8 B

VR1B 2,0 B

VR2 2,85 B

VR2B 2,85 B

VR3 2,85 B

Цифровое ЗУ (ядро) цифрового процессора

низкочастотной части

Цифровое ЗУ (ядро) аналогового процессора

низкочастотной части

Интерфейс памяти цифрового процессора

низкочастотной части

Цифровые вводы-выводы цифрового и аналогового

процессоров низкочастотной части

Аналоговый блок аналогового процессора

низкочастотной части

-29-

Split power logic Логическая схема управления питанием

Powerdown of internal

level shifter

RTC and X032K reset Сброс генератора импульсов истинного времени и

X032K Conf registers Регистры конфигурирования X032K

Отключение внутренней внутренней схемы сдвига

уровня

X032K

Page 30

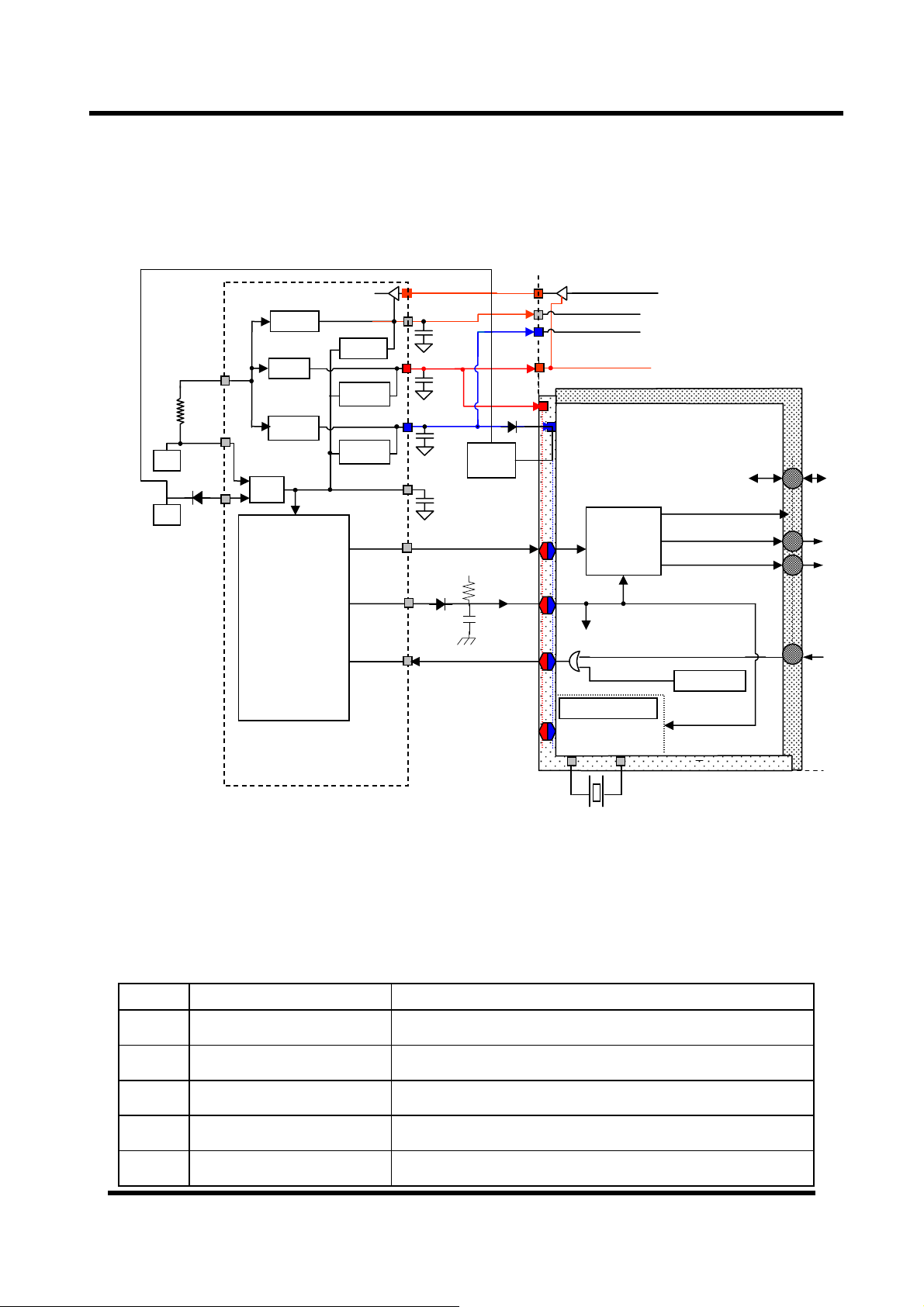

3.2.2.12 Каналы аналого-цифрового преобразователя

Блок аналого-цифрового преобразователя аналогового процессора низкочастотной части состоит

из четырех внутренних и пяти внешних каналов аналого-цифрового преобразователя. Данный блок

управляет зарядкой батареи и другими связанными с зарядкой процессами, считывая значения

напряжения батареи и другие аналоговые параметры.

Таблица 3-2-2. Характеристики каналов аналого-цифрового преобразователя

3.2.2.13 Подача питания

На приведенной выше схеме указаны соединения подачи питания от Nausica к Calypso. на этой

схеме следует выделить следующие моменты:

- При отсутствии подключения МВ (основной б атареи) напряжения на выходах стабилизаторов не бу дет.

- Резервный стабилизатор генератора импульсов истинного времени (RRTC) всегда находится в

активном состоянии, подавая напряжение на участок управления питанием микропроцессора

Calypso в любом функциональном режиме системы.

- Значение напряжения на стабилизаторе генератора импульсов истинного времени и

стабилизаторе цифрового процессора низкочастотной части (RDBB) может быть выбрано между

1,4 В и 1,8 В через входной вывод VL RTC.

- По умолчанию значение напряжения RMEM может находиться между 2,8 В и 1,8 В через

входной вывод VLMEM.

- Стабилизатор цифровог о процессора низкочастотной части измеряет внешнее напряжение для

более точной стабилизации напряжения на вхо дном выводе VSDBB. В ре зуль тате исключается

падение напряжения от клавиатуры и проводных соединений к выводу подачи питания

микропроцессора Calypso. Чтобы данная функция была действенной, точка считывания

возвратного напряжения должна находиться как можно ближе к выводу микропроцессора Calypso.

- Схемы сдвига уровня ввода-вывода генератора импульсов истинного времени (RTC) в

приложении Nausica к Calypso применяются с одинаковыми значениями напряжения с обеих

сторон => VDD-RTC = VDD-RTC = 1,8 В.

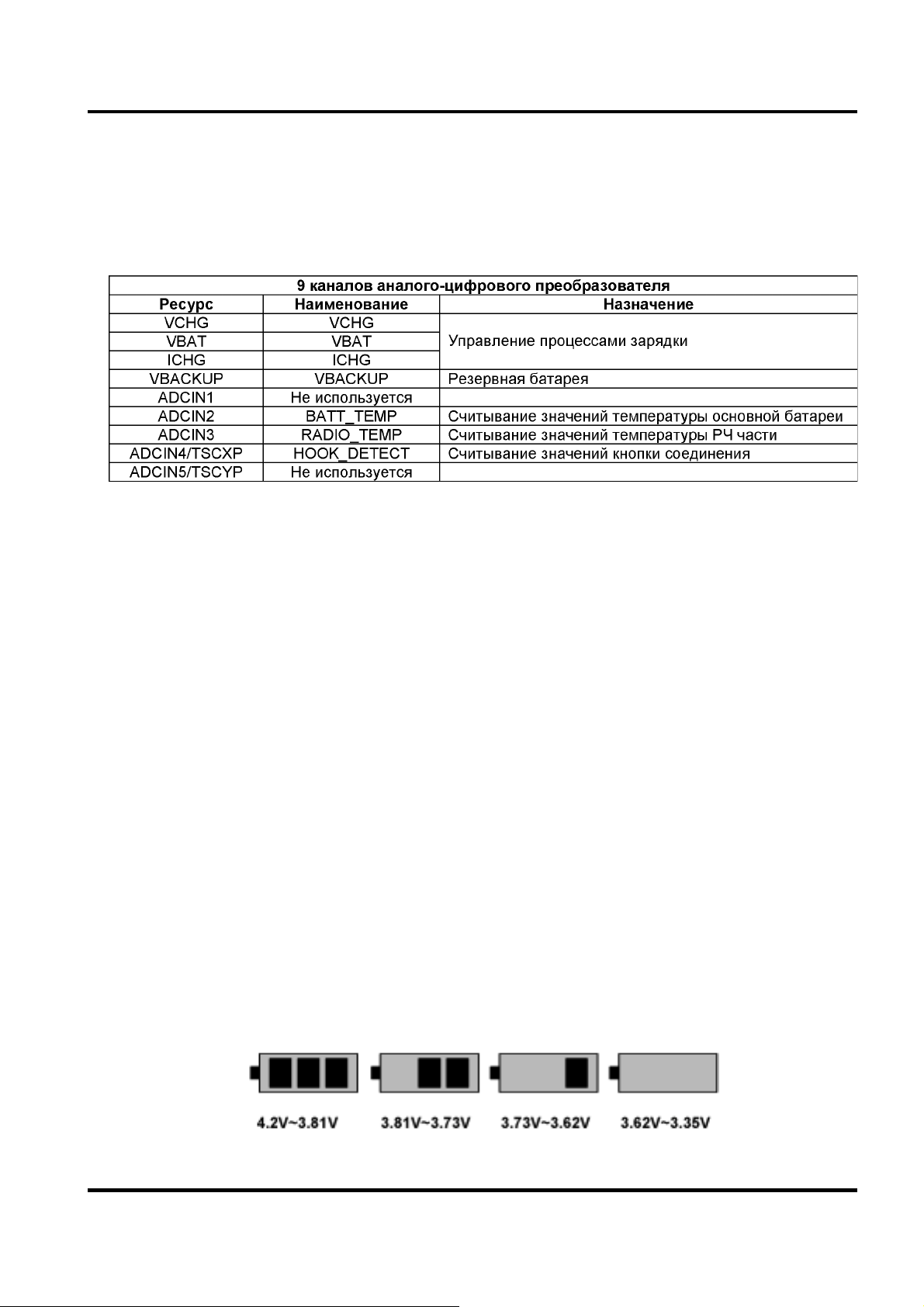

3.2.2.14 Зарядка

Блок контроля зарядки в аналоговом процессоре низкочастотной части осуществляет управление

процессом зарядки батареи при помощи значений VBAT, ICHG через канал аналого-цифрового

преобразователя. На рисунке ниже приведена индикация уровня заряженности батареи аппарата

G7030 и соответствующие значения напряжения.

Рис. 3-2-7. Индикатор уровня заряженности батареи

- 30 -

Page 31

1. Метод зарядки: СС-СV (постоянный ток - постоянное напряжения).

2. Напряжение обнаружения зарядного устройства: 4,0 В.

3. Время зарядки: 2 часа.

4. Иконка остановки заряда: 65 мА.

5. Ток зарядки: 480 мА.

6. Стабилизированное напряжение: 4,2 В.

7. Ток отключения: 40 мА.

8. Ток индикации полностью заряженной батареи (остановка иконки): 65 мА.

9. Напряжение перезарядки: 4,16 В.

10. Сигнал низкого уровня заряда батареи

а. В нерабочем режиме: 3,62 В.

б. В рабочем режиме: 3,50 В.

11. Интервал подачи сигнала о низком уровне заряда батареи

а. В нерабочем режиме: 3 мин.

б. В рабочем режиме: 1 мин.

12. Напряжение отключения: 3,35 В.

13. Температурный диапазон аналого-цифрового преобразователя необходимый для выполнения

подзарядки.

а. Температура в помещении < -5°С: зарядка батареи не производится.

б. -5°С < Температура в помещении < 45°С: зарядка производится.

в. 45°С < Температура в помещении: зарядка не производится.

3.2.2.15 Интерфейс SIM-карты

Цифровой интерфейс SIM-карты в аналоговом процессоре низкочастотной части обеспечивает

преобразование логических уровней между цифровым процессором низкочастотной части и SIMкартой, для передачи 3 различных сигналов:

- Синхронизирующий сигнал, полученный от тактового генератора и обработанный цифровым

процессором низкочастотной части, на SIM-карту (DBBSCK SIM_CK).

- Сигнал сброса от цифрового процессора низкочастотной части на SIM-карту (DBBSRST

SIM_RST).

- Последовательные данные от цифрового процессора низкочастотной части на SIM-карту

(DBBSIO SIM_IO), и наоборот.

Интерфейс SIM-карты может быть запрограммирован для работы SIM-картой на 3 Вили5 В.

Таблица 3-2-3. Интерфейс SIM-карты

Интерфейс SIM-карты с цифровым и аналоговым процессорами низкочастотной части

SIM_RST Сброс SIM-карты.

SIM_PWCTRL Включение питания SIM-карты.

SIM_IO Двунаправленная линия передачи данных SIM-карты.

SIM_CLK Опорный тактовый сигнал для SIM-карты.

Рис. 3-2-8. Интерфейс SIM-карты

-31-

Page 32

3.3 Интерфейс дисплея и гибкой печатной платы

Модуль ЖКД соединен с основной платой через 34-контактный гибкий шлейф. В него входят

двухрежимный громкоговоритель, виброзвонок и резервная батарея.

Рис. 3-2-8. Интерфейс дисплея и гибкой печатной платы

- 32 -

Page 33

3.4 Аудиоинтерфейс

3.4.1 Цепимикрофона

Рис. 3-4-1. Схемыподключениямикрофона

При установлении вызова сигнал MICBIAS повышается на<2,0V> в G7030. Устройство

Nausica(аналоговый процессор низкочастотной части) подает в цепь 2,0 Ви2,5 Вдля

сигнала MICBIAS. Для повышения защиты от электростатических разрядов используются

VA5, VA6

3.4.2 Интерфейс гнезда для подключения наушника

Рис. 3-4-2. Интерфейс гнезда для подключения наушника

-33-

Page 34

Когд а вконтактное гнездо вставлен штекер контактного ушного микрофона или наушника, уровень

сигнала JACK_DELETE изменяется с <Н> на <L>. Если кнопка соединения нажата в течение одной

секунды для того, чтобы сделать звонок, то состояние сигнала изменяется с <L> на <Н>. Окончание

звонка происходит таким же способом при нажатии кнопки соединения на ремешке контактного

ушного микрофона. Нажатие кнопки соединения обычно обнаруживается при непрерывном сигналев

течение 20 мсек.

3.4.3 Цепигромкоговорителя

Рис. 3-4-3. Переключательсистемыдвухрежимногогромкоговорителя

Находящиеся в одной упаковке двойные аналоговые переключатели используются для поддержки

обеих режимов одного громкоговорителя - голосового режима и звукового режима микросхемы

MIDI. Громкоговоритель поддерживает параметры как приемного устройства, так и собственно

громкоговорителя. Если порт SPK_EN установлен на <<Н>>, то он работает в качестве

громкоговорителя В противном случае порт SPK_EN остается в состоянии <<L>>.

-34-

Page 35

3.4.4 Описание схемы MIDI SOUND

Рис. 3-4-4. Переключатель системы двухрежимного громкоговорителя

Цепь синтезатора MIDI включает в себя YMU762B, внешний стабилизатор (3,3 Внавыходе) и

перемычки в зависимости от типа YMU759B или YMU762B, R125, R108 используются поочередно.

В настоящее время R108 используется для поддержки YMU762B (звуковая микросхема с 40

полифоническими элементами).

3.4.4.1 YMU762B имеет следующие характеристики:

- Одновременное генерирование до 40 звуковых тонов.

- использование полифонического синтезатора.

- имеет предопределенные по умолчанию звуковые тона для синтезаторов таблицы частотной

модуляции и форм сигнала в ПЗУ. Звуковые тона могут быть загружены в ОЗУ.

- Воспроизведение при помощи адаптивной дифференциальной импульсно-кодовой модуляции.

- Программный механизм прерываний для внешней синхронизации.

- Имеет 8-разрядный параллельный интерфейс для осуществления управления со стороны

центрального процессора.

- Имеет усилитель громкоговорителя и эквалайзер.

- Имеет встроенную систему фазовой автоподстройки частоты для поддержки входящих сигналов

от генератора опорных импульсов частотой до 20 Мгц.

- Включает в себя 16-разрядный стереофонический цифро-аналоговый преобразователь.

-35-

Page 36

3.5 Подсветка клавиатуры

Рис. 3-5-1. Переключательподсветкиклавиатуры

Управление системой переключения подсветки клавиатуры осуществляется при помощи сигнала

включена, потребление энергии составляет около 30 мА при напряжении подачи от основной батареи

равном 3,7 В.

-36-

Page 37

3.6 Соединения клавиатуры

Цифровой процессор низкочастотной части обеспечивает поддержку 25-кнопочной клавиатуры и кнопки

включения питания, которая соединена напрямую с аналоговым процессором низкочастотной части (см.

Рис. 6-1).

Рис. 3-6-1. Схемаматрицыклавиатуры

Клавиатура соединена с микропроцессором с помощью:

- Входных выводов KBR (4:0) для горизонтальных рядов.

- Выходныхвыводов KBC (4:0) длявертикальныхрядов.

При нажатии одной из кнопок матрицы клавиатуры происходит замыкание соответствующих

горизонтальных и вертикальных рядов, идентифицируя тем самым нажатую кнопку. Все входные

выводы (KBR) внутренне подведены к VCC, а все выходные выводы КВС действуют на низком уровне.

При нажатии на кнопку подается сигнал прерывания на микроконтроллер, который, в свою очередь,

начинает последовательное сканирование вертикальных рядов кнопок. В данной схеме G7030

обеспечивает поддержку 25 кнопок, а нажатие кнопки питания (ON_OFF) обнаруживается

устройством Nausica.

-37-

Page 38

3.7 Общее описание РЧ блока приемопередатчика

Радиочастотные компоненты включают в себя передающее устройство, приемное устройство

синтезатор частот, источник напряжения, термостабилизированный генератор, управляемый

напряжением.

Приемопередатчик Aero состоит из трех наборов микросхем - Si4200-BM[U6], Si4133T-BM[U5] и

Si4201-BM[U7], обеспечивая двух- и трех диапазонную GSM/GPRS беспроводную связь.

Приемопередатчик Aero имеет встроенное приемное устройство, основанное на архитектуре

низкой промежуточной частоты (100 МГц), и передатчик, основанный на архитектуре контура

модуляции. Синтезатор [U403], использующий микропроцессорный набор Si4133T-BM (Silicon

Labs), является полным двухдиапазонным синтезатором со встроенными ГУН.

В приемном устройстве задействован трехпроводный последовательный интерфейс, позволяющий

внешнему системному контроллеру выполнять ввод регистров команд делителей частот, усиление

радиоканала приема, установку падения мощности, и прочие управляющие операции.

Рис. 3-7-1. Блок схема РЧ входного каскада

-38-

Page 39

3.7.1 Приемное устройство

В приемном устройстве используется приемник ПЧ, размещенный на одном кристалле с фильтром

выбора каналов, устраняющий необходимость применения фильтров подавления боковых

гармоник и фильтра ПАВ ПЧ, являющихся элементами обычной супергетеродинной схемы.

Микросхема Si4200-BM [U6] включает в себя три малошумящих усилителя дифференциального

входа, согласованных с 200-омными фильтрами симметричного выхода через внешние

согласующие LC-схемы.

Квадратурный смеситель с подавлением боковых гармоник преобразует РЧ сигнал с понижением

до 100 кГц промежуточной частоты (ПЧ) при помощи местного РЧ гетеродина на Si4133Т-BM [U5].

Выходной сигнал со смесителя усиливается аналоговым усилителем с программируемым

усилением, а квадратурный сигнал ПЧ преобразовывается в цифровую форму высокоточными

аналого-цифровыми преобразователями. Si4201-ВМ[U7] преобразует выходной сигнал с АЦП с

понижением частоты при помощи сигнала от местного цифрового 100-Гц квадратурного

гетеродина. Цифровая обработка сигнала и фильтры применяются для выбора канала с целью

устранения блокировки и помех. После того, как канал выбран, цифровой выход корректируется

при помощи регулируемого усилителя, управляемого разрядами DGAIN (5:0) в регистре 5h.

Усиленный цифровой выходной сигнал проходит через цифро-аналоговые преобразователи, с

которых дифференциальный аналоговый сигнал поступает на выводы RXIP, RXIN, RXQP и RXQN

для сопряжения с стандартными интегральными схемами НЧ части аналого-цифрового

преобразователя.

Количество штрихов индикации Мощность (дБм)

≥ -85

≥ -90

≥ -95

≥ -100

≥ -105

Индикатор

антенного приема

5

4

3

2

1

0 < -105

Рис. 3-7-2. Блок-схема приемного устройства

-39-

Page 40

3.7.2 Синтезатор

Интегральная схема синтезатора . Si4133T-BM[U5] является монолитной интегральной схемой

комплементарной метал-окисидной полупроводниковой (КМОП) структуры, выполняющей синтез

ПЧ и РЧ. Две полные системы ФАПЧ (фазовой автоподстройки частоты) интегрированы с

включением в себя ГУН генераторов, параметрических диодов, резонаторов, контурных фильтров,

опорных делителей и делителей ГУН, фазовых детекторов. Дифференциальные выходы на

системы ФАПЧ ПЧ и РЧ предназначены для прямого соединения с ИС приемопередатчика Si4200BM[U6]. Схема ФАПЧ РЧ использует два мультиплексных ГУН.

ГУН РЧ1 работает в режиме приема, аГУНРЧ2 . в режиме передачи. Схема ФАПЧ задействована

только в режиме приема, и использует одинарный ГУН. Средняя частота каждого из трех ГУН

интегральной схемы Si4133T задается подключением внешней индуктивности (Lext).

Программируемый делитель на выводе XIN обеспечивает 13 либо 26 МГц с внешнего кварцевого

генератора. Частота регенерации фазового детектора схемы ФАПЧ ПЧ программируется битом

RFUP

в регистре 31h на 100 кГц, либо 200 кГц. В схеме ФАПЧ ПЧ всегда используется частота 200 кГц.

В режиме приема в диапазонах DCS1800 и PCS1900используется частота 100 кГц, а в диапазонах

GSM 850 и E-GSM900 . 200 кГц.

В режиме передачи всегда используется частота 200 кГц. Частоты выходного сигнала ПЧ и РЧ

задаются программированием регистров N-делителя, а также программируются через

трехпроводный интерфейс с контроллером внешней системы.

Рис. 3-2 Блок-схема синтезатор частот Si4133T

-40-

Page 41

3.7.3 Передатчик

Передающая часть Si4200-BM[U6] состоит из I/Q преобразователя с повышением частоты в НЧ

части, схемы фазовой автоподстройки частоты (ФАПЧ), и двух 50-омных выходных буферов,

приводящих в действие внешние усилители мощности. Системе ФАПЧ не требуется внешний

антенный аттенюатор для ослабления помех при передаче и паразитных сигналов в диапазоне

приема. Кроме того, на выходе ГУН (ГУН передачи) создается сигнал с постоянной огибающей,

который уменьшает проблему расширения спектра, создаваемую нелинейностью усилителя

мощности. Квадратурный смеситель частот преобразует дифференциальные I/Q сигналы с

повышением частоты при посредстве местного гетеродина для генерирования сигнала ПЧ одной

боковой полосы, который проходит через фильтр и используется в качестве опорного входного

сигнала для системы фазовой автоподстройки частоты. Микропроцессор Si4133T[U5] формирует

частоту местного гетеродина ПЧ. Частота гетеродина делится пополам для генерирования

квадратурных сигналов местного гетеродина для квадратурного модулятора. Система ФАПЧ

состоит из преобразователя частоты обратной связи, фазового детектора, контурного фильтра и

полностью интегрированного ГУН («генератор, управляемый напряжением») передачи.

Частота ГУН расположена по центру между DCS 1800 и PCS 1900, а его выходной сигнал делится

на 2 для диапазонов GSM 850 и E-GSM 900. Si4133T генерирует частоту местного гетеродина РЧ

между 1272 и 1483 МГц. Для того, чтобы обеспечить использование единственного ГУН для

местного гетеродина РЧ, используется высокая подача сигнала для диапазонов GSM 850 и E-GSM

900, и низкая подача для диапазонов DCS 1800 и PCS 1900.

Низкочастотные фильтры перед фазовым детектором системы ФАПЧ снижают гармоническую

составляющую квадратурного модулятора и выходных сигналов преобразователя частоты

обратной связи. Частота среза фильтров программируется разрядами FIF (3:0) в регистре 04h.

RF3133 [U4] является трехдиапазонным (GSM/DCS/PCS) модулем усилителя мощности,

использующим метод непрямого регулирования мощности по замкнутому циклу. Непрямое

регулирование по замкнутому циклу полностью автономно, и не требует оптимизации схемы. Оно

запускается непосредственно с выхода аналого-цифрового преобразователя в цепи НЧ части.

Внутриплатное регулирование мощности обеспечивает диапазон регулирования свыше 35 дБ с

аналоговой подачей напряжения, а также отключение питания при «низком» логическом уровне в

дежурном режиме. Его эффективность составляет 55% в диапазонах GSM и DCS.

Мощность на выходе передающего устройства GSM 900

- 41 -

Page 42

Мощность на выходе передающего устройства GSM 900

Уровень регулирования

мощности

0 30

1 28

2 26

3 24

4 22

5 20

6 18

7 16

8 14

9 12

10 10

11 8

12 6

Мощность на выходе

передатчика

дБм

Допустимые отклонения

Обычные

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±3 дБ ±4 дБ

±4 дБ ±5 дБ

±4 дБ ±5 дБ

±4 дБ ±5 дБ

±4 дБ ±5 дБ

Крайние

13 4

14 2

15 0

±4 дБ ±5 дБ

±5 дБ ±6 дБ

±5 дБ ±6 дБ

Рис. 3-7-4. Блок-схема передатчика

-42-

Page 43

3.7.4 Модуль антенного переключателя

Модуль антенного переключателя (LMSP54AA-097) предназначен для использования в

двухдиапазонных телефонах. Ниже в таблице приведены параметры логической схемы и питания.

Таблица 3-7-1 Логическая схем а и сила тока

- 43 -

Page 44

4. УСТРАНЕНИЕ НЕИСПРАВНОСТЕЙ

4.1 Громкоговоритель

L14

L15

-44-

Page 45

- 45 -

Page 46

4.2 Микрофон

Pin1 Pin2

-46-

Mic1

Page 47

- 47 -

Page 48

4.3 Модуль ЖКД

J1

-48-

FB6

Page 49

- 49 -

Page 50

4.4 Виброзвонок

R6

U19

R131

-50-

Page 51

- 51 -

Page 52

4.5 Зарядное устройство

-52-

Page 53

- 53 -

Page 54

4.6 Разъем гарнитуры «свободные руки»

Pin1 Pin2

Pin3 Pin4 Pin5

-54-

Page 55

- 55 -

Page 56

4.7 Устранение проблем тракта приема

- 56 -

Page 57

4.7.1 Проверка схемы стабилизатора

Проверить вывод 1

Pin6

Есть 2,85 В?

Нет

Уровень

на выводе 6

высокий?

Нет

Проверить U12

Да

Да

Схема стабилизатора в порядке.

См. ниже порядок проверки

термостабилизированного ГУН

Заменить U9

Pin1

-57-

Page 58

4.7.2 Проверка схемы термостабилизированного генератора, управляемого напряжением

(ГУН)

Проверить вывод 3

Есть 13 Мгц?

Нет

На выводе 4 есть

2,85 В?

Нет

Проверить U9

Да

Да

Схема термостабилизированного ГУН в

порядке. См. ниже порядок проверки

антенного переключателя и подвижного

переключателя.

Заменить Х1

-58-

Page 59

Pin4 Pin3

Pin3

Pin4

-59-

Page 60

4.7.3 Проверка схемы системы ФАПЧ

- 60 -

Page 61

4.7.4 Проверка антенного переключателя и

подвижного переключателя

VC2

SW1 pin1

Проверить выводы 1 и 2 на

SW1 при отсоединенном

РЧ кабеле

SW1 pin2

VC1

SW1 при подсоединенном РЧ кабеле

Нужен режим

«Stand alone»

на приеме

Антенный переключатель и подвижный

переключатель в порядке. См. ниже

Цепь

закорочена?

Да

Проверить выводы 1 и 2 на

Цепь

разомкнута?

Да

Проверить VC1,

VC2 на FL1

VC1 = низкий

VC2 = низкий

Да

Проверить РЧ

уровень на

выводах 1 и 10 FL1

≥ - 63 дБм

Да

порядок проверки ПАВ-фильтра.

Нет

Нет

Нет

Нет

Заменить

Переклю-

чатель

SW1

Заменить

Переклю-

чатель

SW1

Заменить

плату

Заменить

Переклю-

чатель

SW1

-61-

Page 62

4.7.5 Проверка схемы ПАВ-фильтра

FL2 pin4

Нужен режим

«Stand alone»

на приеме

Антенный переключатель и подвижный

переключатель в порядке. См. ниже порядок

FL3 pin4

Проверить РЧ уровень

на выводе 4 FL2 и

выводе 4 FL3

Нет

≥ - 65 дБм

Да

проверки I и Q сигналов на приеме

Заменить

переключатель SW1

-62-

Page 63

4.7.6 Проверка I и Q сигналов на приеме

Проверить I и Q

сигналы

RXQP

RXQN

RXIP

Такие же?

Нет

Да

Перезагрузить программное

обеспечение и выполнить

калибровку

RXQP RXIP

RXIN

Заменить U7

-63-

Page 64

4.8 Устранение проблем тракта передачи

- 64 -

Page 65

4.8.1 Проверка схемы стабилизатора

Проверить

вывод 1

Есть 2,85 В?

Нет

Схема стабилизатора в порядке.

Да

См. ниже порядок проверки

термостабилизированного ГУН

Pin6

Pin1

Уровень на

выводе 6

высокий?

Нет

Проверить U12

Да

Заменить U9

Pin1

Pin6

-65-

Page 66

4.8.2 Проверка схемы термостабилизированного генератора, управляемого

напряжением (ГУН)

Проверить вывод 3

Есть 13 Мгц?

Нет

На выводе 4

Есть 2,85 В?

Нет

Проверить U9

Pin4 Pin3

Да

Схема термостабилизированного ГУН в

порядке. См. ниже порядок проверки

антенного переключателя и подвижного

переключателя.

Да

Заменить Х1

Pin3

Pin4

-66-

Page 67

4.8.3 Проверка схемы системы ФАПЧ

S_EN

S_DATA

S_CLK

Проверить сигналы

S_CLK, S_DATA и S_EN

Нет

Уровень высокий?

Да

Нет

Такой же?

Да

Управляющий сигнал в

порядке.

См. ниже порядок проверки

антенного переключателя и

подвижного переключателя.

Загрузить программное

обеспечение

Загрузить программное

обеспечение

S_EN S_DATA S_CLK S_EN S_DATA S_CLK

-67-

Page 68

4.8.4 Проверка I и Q сигналов на передаче

Проверить I и Q

сигналы

Такие же?

Да

Нет

Заменить U11

TXIP

TXIN

Перезагрузить программное

обеспечение и выполнить

калибровку

TXQN

TXIP TXQP

TXQP

-68-

Page 69

4.8.5 Проверка управляющих сигналов усилителя мощности

Проверить сигналы PA_ON,

PA_LEVEL, PA_BAND, PA_VREG

PA_VREG

PA_ON

PA_BAND

Такие же?

Да

Управляющий сигнал в норме.

См. ниже порядок проверки

антенного переключателя и

подвижного переключателя.

Нет

PA_LEVEL

PA_BAND

Загрузить

программное

обеспечение

PA_ON

PA_VREG

PA_LEVEL

-69-

Page 70

4.8.6 Проверка антенного переключателя и подвижного переключателя

SW1 pin1 SW1 pin2