Page 1

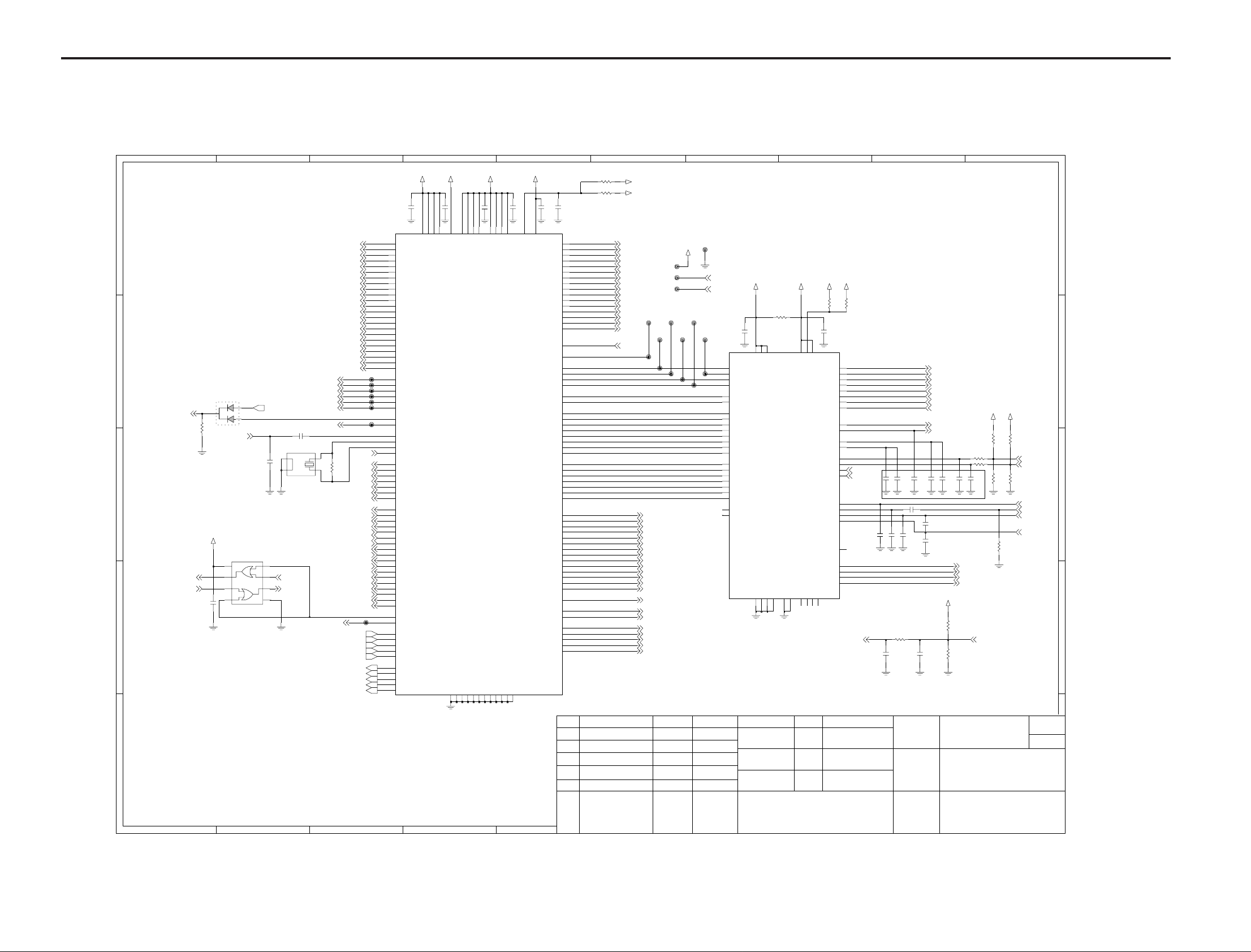

8. CIRCUIT DIAGRAM

8.1 MAIN

1

A

B

KDS121E

RPWRON

R104

100K

C

2V8_VMEM

_SUBLCD_CS

ADD2

C131

0.1u

D

3

D101

13MHZ

U103 NL27WZ32US

8

VCC

7

Y1

6

B2

5

A2

2

1

C110

1000p

(n.a.)

A1

B1

Y2

GND

ONNOFF

1

2

3

4

C109

1000p

X101 MC-146

3

32.768KHz

ADD3

_MIDI_CS

_RAM_CS

_ROM_CS1

_WR

_LBS

_UBS

CLKON

4

12

_ROM_CS2

_RD

R107

10M

HOOK_DETECT

3

ADD0

ADD1

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD9

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

ADD22

_RAM_CS

_ROM_CS1

F/WE

_LBS

_UBS

_RD

CLKON

_RESET

USC0

USC1

USC2

USC3

USC4

USC5

ACC_DET

VIBRATOR

DEBUG_RX

HFK_EAR

DEBUG_TX

CHRDET

FLIP

_MIDI_IRQ

SPK_EN

JACK_DETECT

LED_G

LCD_RES

LED_B

INDLED_R

CHG_EN

EOC

_MIDI_RST

AMP_EN

_ROM_CS2

KEYROW0

KEYROW1

KEYROW2

KEYROW3

KEYROW4

KEYCOL0

KEYCOL1

KEYCOL2

KEYCOL3

KEYCOL4

H4

J3

J2

J4

K3

K2

K4

L4

L1

L3

L5

M1

M2

N1

P1

N2

P2

N3

M3

P4

N4

M4

P5

M14

M13

P14

P13

N12

M11

B2

G14

L12

B3

A3

N14

C14

D12

A14

A13

E11

C12

B13

D11

D10

B12

C11

D9

B11

A11

C10

D8

A10

C9

C7

B9

A9

B8

A8

D6

B7

L13

M12

A6

F4

D4

B5

A5

C4

E4

B4

A4

C3

1V8_VCORE

C101

47n

ADD0

ADD1

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD9

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

ADD22

RAMCS

ROMCS

WE

LWR

HWR

RD

PWRON

CLKON

CLKIN

OSCOUT

OSCIN

RESET

USC0

USC1

USC2

USC3

USC4

USC5

USC6

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPCS1

GPCS0

KEYPADROW0

KEYPADROW1

KEYPADROW2

KEYPADROW3

KEYPADROW4

KEYPADCOL0

KEYPADCOL1

KEYPADCOL2

KEYPADCOL3

KEYPADCOL4

8. CIRCUIT DIAGRAM

C111

C119

39p

( 1% )

C112 C113

0.1u

C120

39p

100R110

C130

0.01u

92

10p39p

0.1uC132

TXIP

TXIN

TXQN

TXQP

RXIP

RXIN

RXQP

RXQN

AFC

TX_RAMP

C114

39p

C117

39p

C121

39p

( 1% )

( 1% )

R146 1K

R145

C115

C133 C134

39p

1u

(1608)

CLOSE TO AD6521

CLOSE TO AD6521

VOUTNORP

VOUTNORN

AUXOP

AUXON

VBAT

R111

220K

R112

220K

2V8_VMEM

39p

MVBAT

A

A

B

B

2V8_VMEM

R105

R106

120K

120K

R108

LCD_ID

TEMPSENSE

R140

82K

82K

1K

C

AUXIP

AUXIN

VINNORP

VINNORN

R147

2.2K

D

VEXT4

GND11

D3

C103

47n

VSSRTC

E3

5

2V0_VRTC

C105

47n

A2

DATA0

VPEG1

DATA1

VDDRTC

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

GPIO_32

JTAGEN

GPIO_21

GPIO_20

GPIO_19

GPIO_18

GPO_0

GPO_1

CLKOUT

CLKOUT_GATE

GPO_24

GPO_5

GPO_6

BSOFS

GPO_2

GPO_3

GPO_4

GPO_7

GPO_8

GPO_9

GPO_10

GPO_11

GPO_16

GPO_17

GPO_18

GPO_19

GPO_20

GPO_21

DISPLAYCS

GPO_22

GPO_23

GPIO_22

GPIO_23

GPIO_24

SIMCLK

SIMDATAOP

ASDI

ASDO

ASFS

BSDO

BSDI

BSIFS

VSDI

VSDO

VSFS

C106

47n

R102

n.a.

N6

P6

M6

N7

M7

L7

P8

N8

M8

P9

M9

P10

N10

M10

P11

N11

L14

K11

J11

J12

H13

H14

B1

C2

D1

D2

E1

A1

C1

E2

F1

F2

F3

G4

G2

G1

G3

H3

H2

G13

G12

H12

F14

F13

H11

F12

E14

E13

G11

E12

D14

D13

F11

M5

A7

C5

J14

L10

K13

K12

J13

4

2V8_VMEM

VSIM

C102

47n

L9

H1

P7

K14

C8

VCC1

VCC2

VCC3

VCC4

J1

VSIM

GND1

GND2

K1

VMEM1L2VMEM2N5VMEM3

GND3

P3

C104

47n

N9

N13

B14

VEXT1

VMEM4

U101

AD6525XCA-REEL

GND4

GND5

GND6

GND7

GND8

L11

P12

L6

L8

C13

B10

A12

C6

VEXT2

GND9

D7

D5

VEXT3

GND10

B6

6 10

0R101

2V8_VMEM

0

1V8_VCORE

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DSR

TP101

JTAGEN

TDO_1

ONNOFF

DIM_CNTL

RF_EN

IRDA_SD

VREG

ANT_SW1

GATE_EN

ANT_SW2

PA_EN

PA_BAND

PDNB

S_EN

S_DATA

S_CLK

_MAIN_LCD_CS

LCD_BACKLIGHT

KEY_BACKLIGHT

SIMVSEL

SIM_RST

SIM_EN

SIM_CLK

SIM_DATAOP

RPWON

TP102

VBAT

TP601

FWE

TP108

TP105

TP104

TDI

TMS

TCK

TP603

TP103

_WR

RPWRON

TDO_0

B2

B1

C2

C1

J4

K4

J2

K1

J3

K3

J1

H1

H2

G2

F2

F1

E2

D1

E1

D2

B4

A3

K2

7

C107

47n

TDI

TDO

TMS

TCK

RXON

TXON

MCLK

MCLKEN

RESET

ARSM

ATSM

ASDO

ASDI

ASFS

BSDI

BSIFS

BSDO

BSOFS

VSDO

VSDI

VSFS

IDACOUT

IDACREF

2V55_VAN

F10

B3

AVDD1

AGND4

J7

J8

AVDD2A9AVDD3

AGND3

B8

AGND1G9AGND2

1V8_VCORE

100KR103

U102

AD6521

DGND1

DGND2

J5

A2

A1

DVDD1

NC1

J9

2V8_VMEM

K5

DVDD2G1DVDD3

AFCDAC

RAMPDAC

AUXADC1

AUXADC2

AUXADC3

AUXADC4

VINAUXP

VINAUXN

VINNORP

VINNORN

VOUTNORP

VOUTNORN

VOUTAUXP

VOUTAUXN

NC2B9NC3

B6

B7

8

C108

47n

ITXP

ITXN

QTXN

QTXP

IRXP

IRXN

QRXP

QRXN

REFCAP

REFOUT

BUZZER

NC4

R113

0

1V8_VCORE

R114

0

(n.a.)

F9

E9

C9

D9

E10

D10

C10

B10

A10

H9

A8

A7

A6

A5

B5

A4

H10

G10

J10

K10

J6

K8

K7

K9

K6

AUXADC4

BOARD_TEMP

AUXADC4

C124

0.01u

C118

39p

E

LGIC(42)-A-5505-10:01

Section

Designer

Checked

Approved

Iss.

1

2

3

4

5

Notice No.

Date

Name

03/06

2003

03/06

2003

03/06

2003

LG Electronics Inc.

Sign & NameDate

KN KIM

DH YUN

JS KEE

MODEL

DRAWING

NAME

DRAWING

NO.

G5400(toshiba)

HERCULES/PEGASUS

V1.3

Sheet/

Sheets

1/6

LG Electronics Inc.

- 95 -

Page 2

8. CIRCUIT DIAGRAM

8.2 AUDIO

_MIDI_RST

_MIDI_IRQ

A

DATA15

DATA14

DATA13

DATA12

DATA11

DATA10

_MIDI_CS

2V8_VMEM

B

C

D

E

LGIC(42)-A-5505-10:01

DATA9

DATA8

ADD0

_RD

_WR

13MHz

HFK_EAR

C205

0.1u

1

1

AUXIP

_MIDI_RST

_MIDI_IRQ

ADD0

C206

0.1u

C239

2V8_VMEM

100K

C208

0.1u

0.1u

R232

HFK_EAR

C240

39p

0

1

AUXIN

R219

100K

U201

48

_RESET

1

_IRQ

2

IFSEL

18

D7

19

D6

20

D5

21

D4

22

D3

23

D2

25

D1

26

D0

14

ILE

15

_CS

16

_RD

17

_WR

30

CLOCK

3

SYNC

46

TEST1

47

PTESTIN2

29

PTESTIN1

13

PTESTO2

36

PTESTO1

28

DVDD1

44

DVDD2

27

VDDIO

38

DRVGND

24

DGND1

45

DGND2

2V8_VMEM

CONNECTION

HEADSET

HFK

2

ML2870GDZ060

0R255

(n.a.)

U205

MAX4599EXT-T

2

PANEL

VIB

PWMD

PWMC

PWMB

PWMA

AOUTR

AOUTL

VREFR

VREFL

TESTA3

TESTA2

TESTA1

AVDD

AGND

C219

39p

39

37

43

42

41

40

35

P4

34

P3

33

P2

32

P1

31

P0

11

10

9

8

7

6

5

4

12

C220

10uF

HFK_AUXIP

2V8_VMEM

(1608)

3

R247 0

AMP_EN

R204 560K

C202 0.022u

R202 20K

0.022u

2V8_VMEM

R212

2.2K

R214

3.3K

C230

0.1u

C207

0.1u

2V8_VMEM

R213

1M

C232

0.1u

2V8_VMEM

VIN-

4

VIN+

3

R215

620K

HEADSET_MIC_P

VCC

GND

5

2

LED_R

C201

C236

39p

U206

MAX9075EXK-T

1

OUT

RPWRON

20KR201

R203

560K

C203

1u

HOOK_DETECT

VBAT 0R263

C241

0.1u

RPWRON

0

1

U208

MAX4599EXT-T

CONNECTION

VCHARGE

7COLOR

34

VCHARGE

R260

2.7K

U207 LM4890LD

5

IN-

4

IN+

1

SHUTDOWN

2

BYPASS

7

NC1

9

NC2

R259

10K

INDLED_R

C242

0.1u

VDD

GND1

GND2

REC_SPK-

REC_SPK+

SPK_EN

8

2V8_VMEM

C235

39p

HFK_AUXOP AUXON

AUXOP

HEADSET_SPK_P

HFK_EAR

2V55_VAN

R207

C212

10uF

(1608)

1K

R208

1.2K

MAX4684EUBU204

1

V+

2

NO1

3

COM1

4

IN1

5

NC1

10

A

10

NO2

9

COM2

8

IN2

7

NC2

6

GND

HFK_AUXON

C221

0.1u

B

5

VBAT

6

VO1

10

VO2

8

3

C231

11

0.1u

VOUTNORP

VOUTNORN

64 9

2V8_VMEM

VBAT

R266R265

0

(n.a.)

C237

39p

U203 MAX4684EUB

1

2

3

R220

R221

4.7

C226

47p

4.7

C227

47p

4

5

7

0

10

NO2

V+

9

COM2

NO1

8

COM1

IN2

7

IN1

NC2

6

GND

NC1

C204

47p

R205

100K

C210

39p

C

C214

0.1u

100

C216

0.1u

100

(1608)

C222 10uF

C224

47p

R211

1.2K

Date

03/06

2003

03/06

2003

03/06

2003

LG Electronics Inc.

C215

39p

SP207

CLOSE TO MIC

4.7R216

4.7R217

C225

47p

Sign & Name

KN KIM

DH YUN

JS KEE

SP208

SP204

R218

MIC201

VA204

VA203

C244

C245

39p

39p

SP201

SP202

AVL14K02200

VA202

VA201

1M

SP206

SP205

AVL14K02200

AVL14K02200

MODEL

DRAWING

NAME

DRAWING

NO.

OBG-13L42-C33

AVL14K02200

Headset jack

J201

5

1

3

4

2

G5400(toshiba)

AUDIO

V1.3

Sheet/

Sheets

2/6

D

2V8_VMEM

R261

100K

(n.a.)

Iss.

2V8_VMEM 2V8_VMEM

R257

1M

VIN-

4

VCC

VIN+

3

GND

2

R258

620K

Notice No.

C243

39p

U209

MAX9075EXK-T

5

1

OUT

R264

VINNORP

VINNORN

JACK_DETECT

0R262

(n.a.)

0

HEADSET_SPK_P

HEADSET_MIC_P

R209

R210

Section

Designer

Checked

Approved

Date

Name

5

LG Electronics Inc.

- 96 -

Page 3

8.3 MIDI

8. CIRCUIT DIAGRAM

22

VBAT

19

DGND

11

EOC

CHG_EN

CHRDET

GATE_EN

VBAT2

27

VRTCIN

VSIM

VCORE

VTCXO

VMEM

VRTC

REFOUT

_RESET

MVBAT

AGND

2

VAN

NC1

NC2

NC3

7

C302

0.1u

(n.a.)

18

21

23

25

20

3

26

16

5

17

24

32

C307

0.1u

2V8_VMEM

100K

C301

10uF

(1608)

R306

R308

10K

C308

0.22u

(1608)

(n.a.)

98

10

A

VSIM

1V8_VCORE

2V55_VAN

2V75_VTCXO

2V8_VMEM

2V0_VRTC

R304 100

MVBAT

C306

100p1000p

R310 0

(n.a.)

C310

C309

2.2u

C311

2.2u

0.1u

(1608)

0R311

SIMVSEL

C312

0.22u

(1608)

C313

2.2u

(1608)

C314

0.1u

BAT301

2V0_VRTC

R316

10K

C315

(n.a.)(1608)

0.1u

C305

100p

_RESET

B

CC

1

2

3

4

5

6

A

VBAT

2V8_VMEM

R315

100K

C3190.1u

CHG_EN

CHRDET

GATE_EN

U302

ADP3522

30

31

29

28

15

10

12

14

4

13

33

EOC

_PWRONKEY

ROWX

PWRONIN

TCXOEN

1

SIMEN

RESCAP

8

SIMVSEL

9

GATEDR

GATEIN

ISENSE

6

CHRDET

CHGEN

BATSNS

7

CHRIN

EOC

GND

C321

0.1u

(n.a.)

C320

0.1u

J3

G4

K4

H5

H6

K7

G7

J8

K3

H4

J4

K5

J7

H7

K8

H8

J5

G5

J6

J9

G3

A1

A10

B1

B10

C1

F1

F6

F9

F10

G1

G6

G10

L1

L10

M1

M10

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VCCF1

VCCF2

VCCPS

U301

TH50VPF5783AASB

VSS0

VSS1

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

DATA0

B

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

_CEF1

_CEF2

_WE

_BYTE

RY_BY

_WP_ACC

_RESET

_CE1PS

CE2PS

DU1

DU2

G2

A0

F2

A1

E2

A2

D2

A3

F3

A4

E3

A5

D3

A6

C3

A7

C7

A8

E7

A9

F7

A10

C8

A11

D8

A12

E8

A13

F8

A14

D9

A15

G9

A16

F4

A17

E4

A18

D7

A19

E6

A20

E9

A21

H2

F5

H3

_OE

C6

H9

E5

C5

D5

C4

_LB

D4

_UB

J2

D6

K6

G8

R318 0

TP301

R320 0

R322 NA

ADD1

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD9

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

ADD22

0R324

_RESET

2V8_VMEM

_LBS

_UBS

_RAM_CS

NAR321

_ROM_CS2

_ROM_CS1

_RD

_WR

2V8_VMEM

R323

10K

C322

NC

2V8_VMEM

R319

10K

(2012)

D302

CUS02

C303

10uF

VBAT

VCHARGE

R301

0.33

Q301

6

7

8

D5

D6

TPCF8102

G45S

D33D4

D2

2

D1

1

POWERKEY

KEYROW0

RPWRON

CLKON

SIM_EN

C304

D

E

LGIC(42)-A-5505-10:01

D

Section

Designer

Checked

Approved

Notice No.

1

2

4

53

Date

NameIss.

Date

03/06

2003

03/06

2003

03/06

2003

Sign & Name

KN KIM

DH YUN

JS KEE

LG Electronics Inc.

MODEL

DRAWING

NAME

DRAWING

NO.

G5400(toshiba)

MEMORY/3522

V1.3

Sheet/

Sheets

3/6

LG Electronics Inc.

- 97 -

Page 4

8. CIRCUIT DIAGRAM

8.4 RF CIRCUIT

ANT1

12nHL408

L401

3.9nH

C402

1.5p

G1G2

ANT

RF

G3

G4

MHC-173 SW401

2

FL401

C416

22p

13

12

9

7

6

4

8

GND6

GND5

GND4

GND3

GND2

GND1

ANT

LMSP54AA-097

C425 1.5p

VC111VC2

EGSM_RX

DCS_RX

EGSM_TX

DCS_TX

C428

2p

L406 4.7nH

C405

NA

RXQP

RXQN

RXIP

RXIN

TXIN

TXIP

TXQP

TXQN

13MHZ

AD6521_AFCDAC

AFC

R401 0

R402

R403 0

R404

C406

NA

GPO_18

PDNB

GPO_19

S_EN

GPO_21

S_CLK

0

GPO_20

S_DATA

ANT_SW1

GSM_TX

DCS_TX

RX

L402

33nH

C407

3.3p

L403

33nH

C412

10p

C432 NA

C417

2.2pC426

8

9

10

11

VCC2

12

10

1

5

3

L409

3.9nH

ANT_SW2

L

H

L

C408

10p

C413

27p

SAFSD942MFM0T00 FL402

2

27p

2

GND10

GND11

GND1225GND13

GND14

22

23

24

26

VCC1

GSM_OUT

RF3133

U404

VCC_OUT

DCS_OUT

BAND_SELECT

GND3

GND416GND5

GND6

GND7

14

15

17

18

19

H

L

L

ANT_SW1

ANT_SW2

IN4O1

G3

IN4O1

5

20

21

GND8

GND9

VRAMP

VBATT

TX_ENABLE

GND1

GND2

13

GPO_9

C438

C424

22n

22n

24

23

22

21

20

19

18

17

RF2.85V

C431

22n

C410

22n

RFOD

VDD1

RFIGN

RFIGP

RFIDN

RFIDP

RFIPN

RFIPP

21

20

19

18

17

16

15

RF2.85V

RFOG

DIAG1

GND8

RFLA

RFLB

GND7

RFLC

RFLD

GND6

GPO_11

1p1pC415

L404

C433

27nH

(1608)

L405

7.5nH

(1608)

1.2pC423

C434

10u

C435

22p

47p

R409

47

R410

130

36R416

R417

150

O2

6

C419

1G13G25

FL403SAFSD1G84FA0T00R00

O2

6

G11G23G3

GSM_IN

7

6

VREG

5

4

3

2

DCS_IN

1

C420 1.2p

VBAT

C429

RF2.85V

C430

33p

10p

RF2.85V

R411

130

R418

150

25

16

VDD4

DIAG2

26

27

NC129NC2

GND2

U401

SI4200-BM

RFLON

VDD2

14

15

22

GND9

RFLON

SDI

GND5

14

28

GND330GND4

RFLOP

GND1

12

13

11

23

24

25

VDDR

RFLOPSCLK

U403

SI4133T-BM

SENB

12

13

11

RF2.85V

31

PDNB

IFLON

10

26

IFLON

SDO

10

32

VDD3

ION

IOP

CKN

CKP

TXIP

TXIN

TXQP

TXQN

IFLOP

9

RF2.85V

27

VDDI

IFLOPPDNB

GND1

GND2

VDDD

GND3

GND4

9

C411

33

28

IFLB

IFLA

8

22n

C437

10p

29

GND10

XIN

C414

22n

15

14

13

C441

100p

12

11

1

2

3

4

5

6

7

8

RF2.85V

1

2

3

4

5

6

7

C443

10p

L407

4.7nH

SDO

PDNB

XEN

ION

IOP

RF2.85V

C409

17

18

16

206

SDI

SCLK

SENB

XOUT

VDDA

GND1

RXQP

U402

RXQN

SI4201-BM

RXIP

RXIN

VDDC

XIN

CKN

CKP

GND2

719

9

8

10

C422

22n

C439

100p

22n

21

GND3

1

2

3

4

5

RF2.85V

2V75_VTCXO

R414

100

C444

2.2u

(2125)

3

4

C440

1000p

R405

0

R406

0

R407

0

R408

0

C427

C436

1MR412

5

VCC

2

4

OUT

IN

GND

U406

3

1

2

SN74AHC1GU04DCKR

R415

C442

1000p

X401

CTL

OUT

GND

VCC

13MHz

PDNB

S_EN

S_CLK

S_DATA

C403

C404

NA

NA

C418

NA

C421

NA

NA

NA

R413

100

15K

RF2.85V

R423

270K

R425

680

R427

4.7K

R424

22K

BOARD_TEMP

C449

10u

(2125)

RF2.85V

C445

27p

R428

0

C446

27p

470pC451

C447

C448

1000p

22p

U405 ADP3330

1

_SD

OUT

3

_ERR

5

GND

NR

15KR419

TX_RAMP

R420

0

R4210100

100

R422

VBAT

C450

2.2u

(2125)

R426

0

6

2

IN

4

VREG

PA_EN

PA_BAND

RF_EN

AD6521_RAMPDAC

GPO_8

GPO_16

GPO_17

GPO_4

Iss.

Notice No.

Date

Name

Section

Designer

Checked

Approved

LG Electronics Inc.

Date

03/06

2003

03/06

2003

03/06

2003

Sign & Name

Ryu K H

LEE K B

CHO J G

MODEL

DRAWING

NAME

DRAWING

NO.

G5400(toshiba)

RF

V 1.3

Sheet/

Sheets

4/6

- 98 -

Page 5

8.5 Keypad

8. CIRCUIT DIAGRAM

A

B

C

POWERKEY

SP501

KEYROW0

KEYROW1

KEYROW2

KEYROW3

KEYROW4

KEYCOL0

KEYCOL1

KEYCOL2

KEYCOL3

KEYCOL4

LD508

R513

100K

6

7

KEY BACKLIGHT

20R555

20R553

20R564

R563 20

LD503

SP502

R519

20

R554 20

LD504

LD506

LD505

Q502 IMX9T110

1

25

3

R520

20

R557 20

LD507

6

4

SP504

LD509

20

R558

R551

LD510

20

20R559

LD511

R552

R561 20

R560 20

LD512

20

VBAT

LD513

20R562

LD514

8

VIBRATOR

VIBRATOR

R507

R505

15

2

1.5K

R508

100K

3

1

Q501

2SC5585

VIBRATOR-

FLIP SWITCH

2V8_VMEM

C501

0.1u

U501

R506

51K

A3212ELH

C502

10p

FLIP

10

A

A

B

B

C

KB22

CLR

KB9

LEFT

KB10

UP

KB11

RIGHT

KB12

DOWN

SP503

SP509

SP514

SP519

SP524

4

KB8

MENU

KB13

SELECT

KB14

SEND

KB15

CONFIRM

5

KEY_BACKLIGHT

VBAT

20R556

R512

1.5K

1

KB1

END

R504

OUT1

100

VA501

AVL14K02200

SP505

SP510

SP515

SP520

2

SIDE1

KB4

KB5

KB6

KB7

OUT3

VA502

R503

100

1

SP506

4

SP511

7

SP516

R502

100

OUT2

AVL14K02200

*

SP521

3 9

OUT4

SIDE2

AVL14K02200

KB20

2

KB21

5

KB2

8

0

VA503

SP507

SP512

SP517

SP522

R501

100

SIDE3

VA504

AVL14K02200

KB16

3

SP508

KB17

6

SP513

KB18

9

SP518

KB19KB3

#

SP523

LCD_BACKLIGHT

D

E

VIBRATOR-

REC_SPKREC_SPK+

LGIC(42)-A-5505-10:01

128 x 160 LCD CONNECTOR

DATA15

DATA14

DATA13

DATA12

DATA11

DATA10

DATA9

DATA8

LED_G

LCD_ID

LED_B

C534

27p

1

C535

27p

C536

27p

2

C537

27p

C538

27p

C539

27p

C540

27p

C541

27p

2V8_VMEM

C506

27p

CN501

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17 18

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

1KR521

1K

R523

1KR525

1KR527

1K

R529

1KR531

R533 1K

1KR535 R536 1K

1KR538

R540 1K

1KR544

R547 0

C542

27p

C543

27p

C544

27p

C545

27p

C546

27p

C547

27p

C548

27p

C549

27p

C550

27p

C551

27p

C507

27p

VBAT

C552

27p

C509

C510

27p

C511

27p

C512

27p

C513

27p

C514

27p

C515

27p

C516

27p

Designer

Checked

Approved

Iss.

3

4

5

Notice No.

Date

Name

1K

R522

R524 1K

R526 1K

1KR528

R530 1K

1KR532

R534 1K

1K

R537

1K

R539

R541 1K

R543 1K

R545 1K

R546

1K

R548

1K

C519

C517

27p

C518

27p

27p

Date

03/06

2003

03/06

2003

03/06

2003

C520

27p

C521

Sign & NameSection

KN KIM

DH YUN

JS KEE

27p

LG Electronics Inc.

C523

C522

C524

27p 27p

27p

27p

C526

C527 C531

C525

27p

27p

MODEL

DRAWING

NAME

DRAWING

NO.

C528

C530

C529

27p

27p27p

27p

G5400(toshiba)

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

ADD1

_WR

LED_R

_SUBLCD_CS

_MAIN_LCD_CS

LCD_RES

DIM_CNTL

C533

C532

27p

27p

27p

Sheet/

Sheets

D

5/6

MMI

V1.3

LG Electronics Inc.

- 99 -

Page 6

8. CIRCUIT DIAGRAM

8.6 SIM, IrDA, Battery etc

C601

220n

SIM_SOCKET

7

6

5

SP602

R617 47

R612 47

R615

R619 47

R620 47

R625 47

R613 47

R623 4.7

R626

R614

IO

VPP

GND

4.7R622

4

SP601

3

CLK

2

RST

1

VCC

J601

5 8

2V8_VMEM

R630 0

C611

0.1u

R629

VBAT

33

0R604

0R602

IRDA

DEBUG_TX

DEBUG_RX

IRDA_SD

I/O CONNECTOR

(n.a.)

(n.a.)

47

47R624

47R618

47R621

100

47

1

A

B

C

2

SIM CONNECTOR

SIM_RST

SIM_CLK

SIM_DATAOP

C602

1000p

SP603

(n.a.)

USC3

DSR

USC0

USC1

USC2

USC4

USC5

ACC_DET

DEBUG_RX

DEBUG_TX

HFK_AUXON

HFK_AUXOP

HFK_AUXIP

C603

1000p

RPWRON

3

SP604

(n.a.)

2V8_VMEM

R606 R631

R605

100K

100K

R607

100K

VSIM

R601

20K

C604

220n

R608

100K

100K

SP605

VSIM

R603

0

6

CIM-80S7B-TU601

LEDA

1

LEDK

2

TXD

3

4

5

6

7

RXD

SD

VCC

GND

SHIELD

8

7

BATTERY CONNECTOR

VBAT

TEMPSENSE

C605

39p

SP606

VCHARGE

VBAT

CN602

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

VBAT

TEMPSENSE

C606

39p

CN601

1

2

3

GND

9

10

A

B

C

SP608

Name

C609

C610

39p

39p

SP607

Section

Designer

Checked

Approved

Date

03/06

2003

03/06

2003

03/06

2003

LG Electronics Inc.

Sign & Name

KN KIM

DH YUN

JS KEE

MODEL

DRAWING

NAME

DRAWING

NO.

G5400(toshiba)

IO/SIM/IRDA

V1.3

Sheet/

Sheets

6/6

D

C608

D

E

1

2

3

C607

39p

39p

SP609

SP610

SP611

SP612

Iss.

4

5

SP613

SP615

SP614

Notice No.

SP616

SP617

SP618

SP619

SP620

Date

SP621

LG Electronics Inc.

- 100 -

Page 7

9. PCB LAYOUT

9. PCB LAYOUT

- 101 -

Page 8

9. PCB LAYOUT

9. PCB LAYOUT

- 102 -

Loading...

Loading...