LG CED-8042B Service Manual

3

INTRODUCTION

FEATURES

1. General

1) Enhanced IDE interface.

2) Internal 5.25 inch, halfheight CD-R/RW Drive.

3) 2 Mbyte buffer memory.

4) Audio CD like tray loading of a disc without using a caddy.

5) Power loading and power eject of a disc. The disc can also be ejected manually.

6) Supports Power saving mode and Sleep mode.

2.

Supported disc formats

1) Reads and writes data in each CD-ROM, CD-ROMXA, CD-I FMV, Video CD, and CD-EXTRA

2) Reads data in Photo CD (Single and Multi session).

3) Reads and writes standard CD-DA.

4) Reads and writes CD-R discs conforming to “Orange Book Part 2”.

5) Reads and writes CD-RW discs conforming to “Orange Book Parts 3”.

3.

Supported write method

1) Disc at once (DAO), Session at once (SAO), Track at once (TAO), Variable packet, Fixed packet.

4.

Performance

1) Random 120 ms average access time.

2) Max 3,600 kB/sec (Max 24X) Sustained Transfer rate.

3) Supports real time error correction and real time layered error correction at each speeds.

4) Supports CD-R write operation at each standard speed, double speed and quadruple speed.

5) Supports CD-RW write operation at double speed.

6) PIO Mode 4 & Multi DMA Mode 2 Support.

7) MPC-3 Spec compliant.

5. Audio

1) Output 16 bit digital data over ATA interface.

2) 8 fs Oversampling Filter for CD Audio

3) Software Volume Control

4) Equipped with audio line output and headphone jack for audio CD playback.

5) Front panel Volume Control for Headphone Output.

This service manual provides a variety of service

information.

It contains the mechanical structure of the CD-RW

Drive and the electronic circuits in schematic form.

This CD-RW Drive was manufactured and

assembled under our strict quality control

standards and meets or exceeds industry

specifications and standards.

This CD-R/RW drive is an internal drive unit

designed for use with IBM PC, HP Vectra, or

compatible computer. It can write as much as 650

Mbytes of digital data into CD-R/RW disc, and can

read as much as 650 Mbytes of digital data stored

in a CD-ROM, CD-R and CD-RW disc.

The CED-8041B can easily meet the upcoming

MPC level 3 specification, and its Enhanced

Intelligent Device Electronics (E-IDE) and ATAPI

interface allows Plug and play integration in the

majority of today’s PCs without the need of an

additional interface card.

4

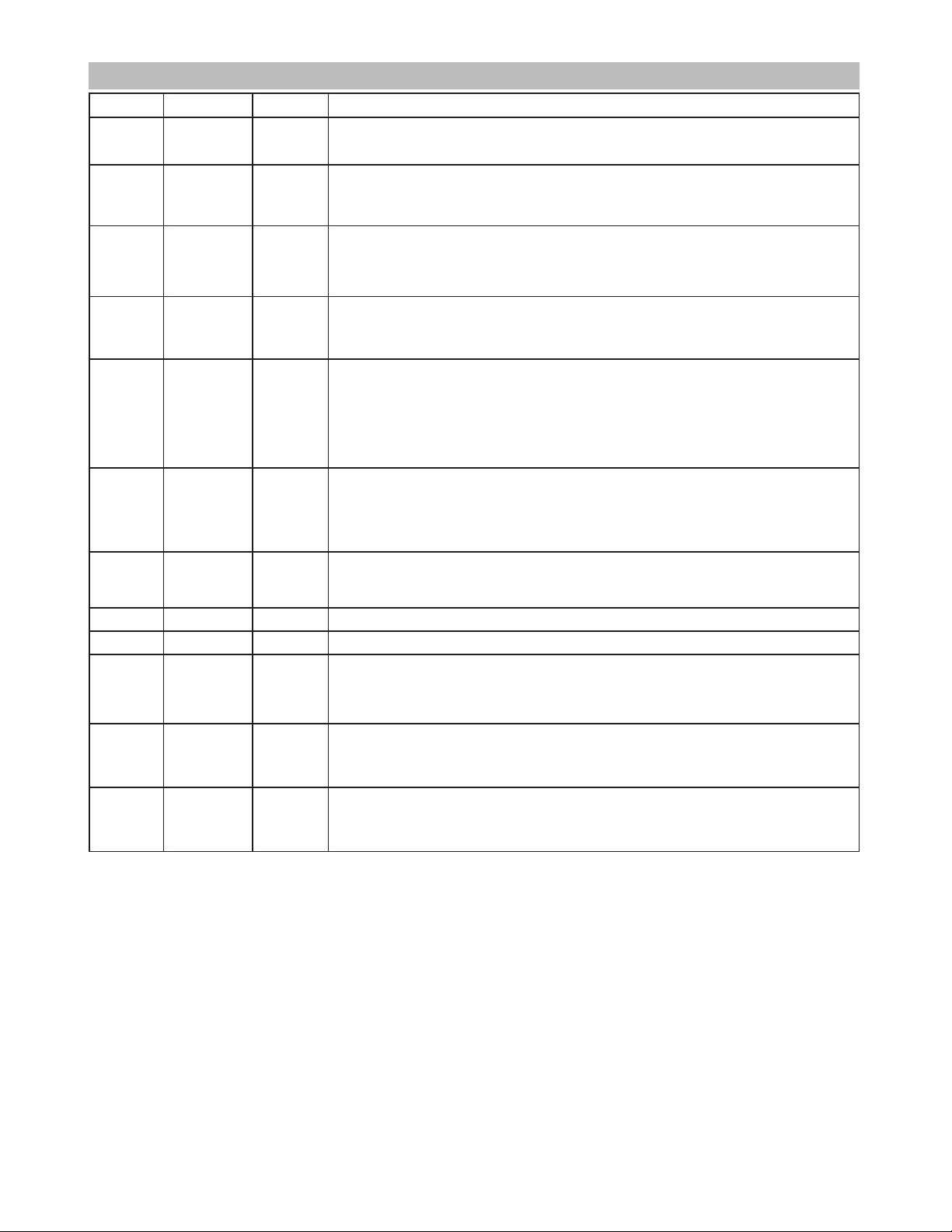

SPECIFICATIONS

1. SYSTEM REQUIREMENTS

-CPU: IBM Compatible Pentium 100MHZ (or faster)

(For 4X Write speed, 166MHz or faster recommended.)

-16MB Memory or greater

2. SUPPORTING OPERATING SYSTEM

3. GENERAL

1) Host Interface.......................................................................................................................ATAPI compliant

2) Read Function

• Acceptable discs...............................................................CD-ROM Mode1 (basic format), CD-ROM XA

CD-Audio

Mixed Mode (Audio and Data Combined)

Photo-CD (Single and Multi-Session)

CD-I Ready, Video CD

CD-Plus/CD-Extra,

CD-R (Conforming to “Orange Book Part2”)

CD-RW (Conforming to “Orange Book Part3”)

3) Write function

• Applied Format..................................................................CD-ROM Mode-1

CD-ROM XA

CD-Audio

Mixed Mode (Audio and Data Combined)

Video CD

CD-Plus/CD-Extra,

• Writing Method..................................................................Disc at once

Session at once

Track at once

Variable packet writing

Fixed packet writing

Multi-session

4) Cache memory (R/W) .........................................................2 Mbyte

5) Disc diameter

......................................................................12 cm (8 cm Read only)

6) Data capacity (Yellow-Book)

• User Data/Block................................................................2,048 bytes/block (Mode 1 & Mode 2 Form 1)

2,336 bytes/block (Mode 2)

2,324 bytes/block (Mode 2 Form 2)

2,352 bytes/block (CD-DA)

7) Rotational Speed

CD-Audio.............................................................................1X Approx. 500-200 rpm at CLV=1.2m/s

CD-RW data........................................................................8X Approx. 4000 rpm-1600 rpm at CLV=1.2 m/s

CD-ROM/CD-R data

............................................................10X~24X(CAV) Approx. 5000 rpm

8) MTBF

• 125, 000 POH at an operating duty of 10% at room temperature.

4. DRIVE PERFORMANCE

1) Data Transfer Rate

* Sustained Data Transfer Rate

..........................................150 Kbytes/s (1X)

300 Kbytes/s (2X)

600 Kbytes/s (4X)

1,200 Kbytes/s (8X)

1,500 to 3,600 Kbytes/s 10 to 24X CAV

• DOS 3.1 or Higher

• Windows 3.1

• Windows ‘95/’98

• OS/2 Warp (Ver 3.0)

• Solaris Ver 2.4 or higher

• Linux Slackware Ver 2.3

• Windows NT 4.0 or later

5

* Burst Data Transfer Rate (ATAPI)....................................16.67 Mbytes/sec (PIO Mode 4)

16.67 Mbytes/sec (MULTI-DMA Mode 2)

2) Average Access Time

Random Access..................................................................120 ms Typical (Max.24X) : INCLUDING LATENCY

3) Data Buffer Capacity...........................................................2 Mbytes

5. POWER REQUIREMENTS

1) Voltage

+5 V DC with + 5% tolerance, less than 90 mVp-p Ripple voltage

+12 V DC with +5% tolerance, less than 90 mVp-p Ripple voltage

2) Current

• Hold Track State ...............................................................+5V DC 0.8A, +12 V DC 0.5A

• Seeking & Spin up ............................................................

+5 V DC 1A, +12 V DC 1.4A

6. AUDIO PERFORMANCE

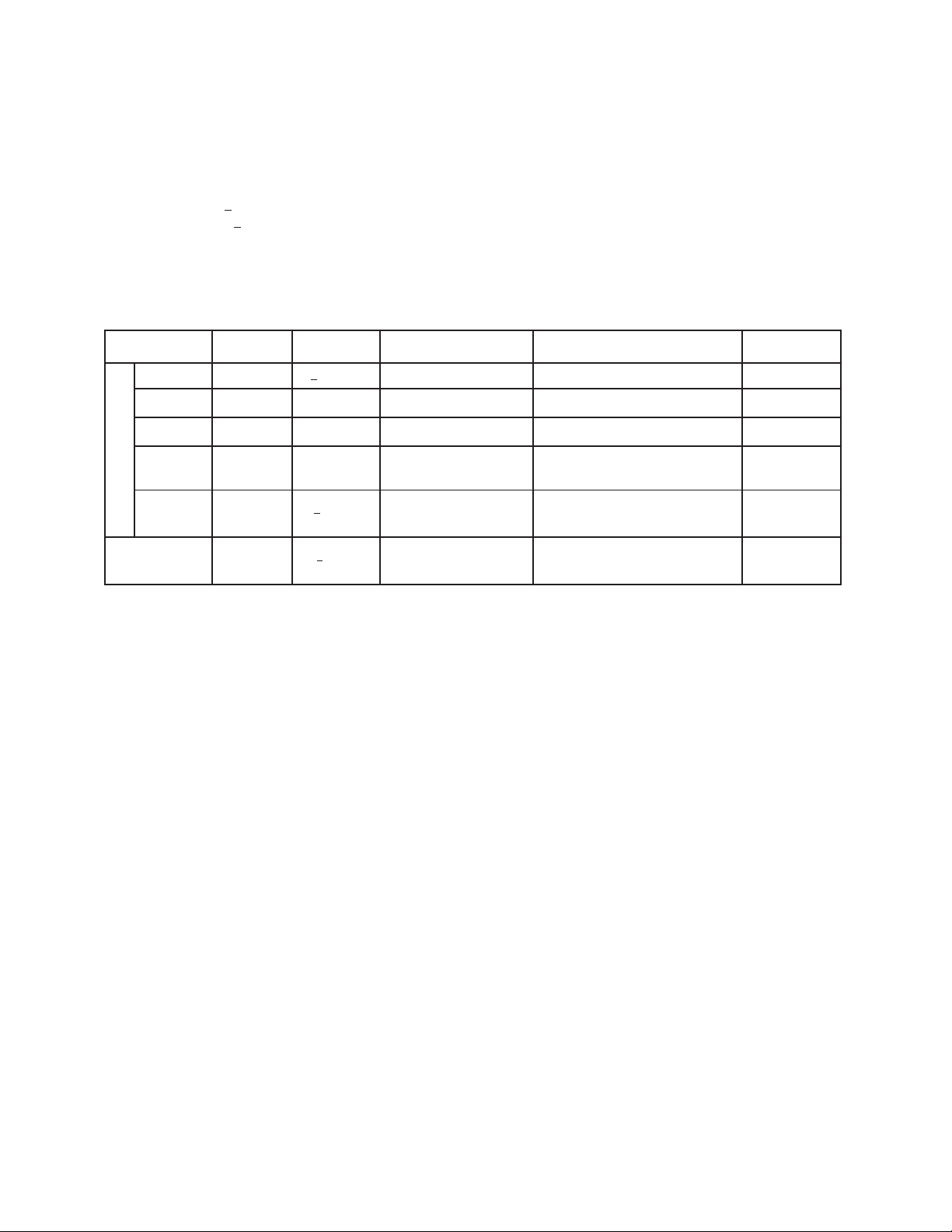

Item Typ. Limit Test Signal Test Condition Note

Output Level

0.8 Vrms

+

10 % 1KHz 0 dB No Filter at 47 kW

S/N 85 dB 80 dB 1KHz 0 dB with IHF-A + 20KHz LPF at 47kW

THD 0.05 % 0.15 % 1KHz 0 dB with IHF-A + 20KHz LPF at 47kW

Channel

75 dB 70 dB 1KHz 0 dB with IHF-A + 20KHz LPF at 47kW

Separation

Frequency

Response

H/P

Output Level

AUDIO OUT

+

3 dB 20Hz~20KHz 0 dB No Filter

at 47 kW

0.6Vrms

+

20 % 1KHz 0dB No Filter H/P Volume MAX at 32 W

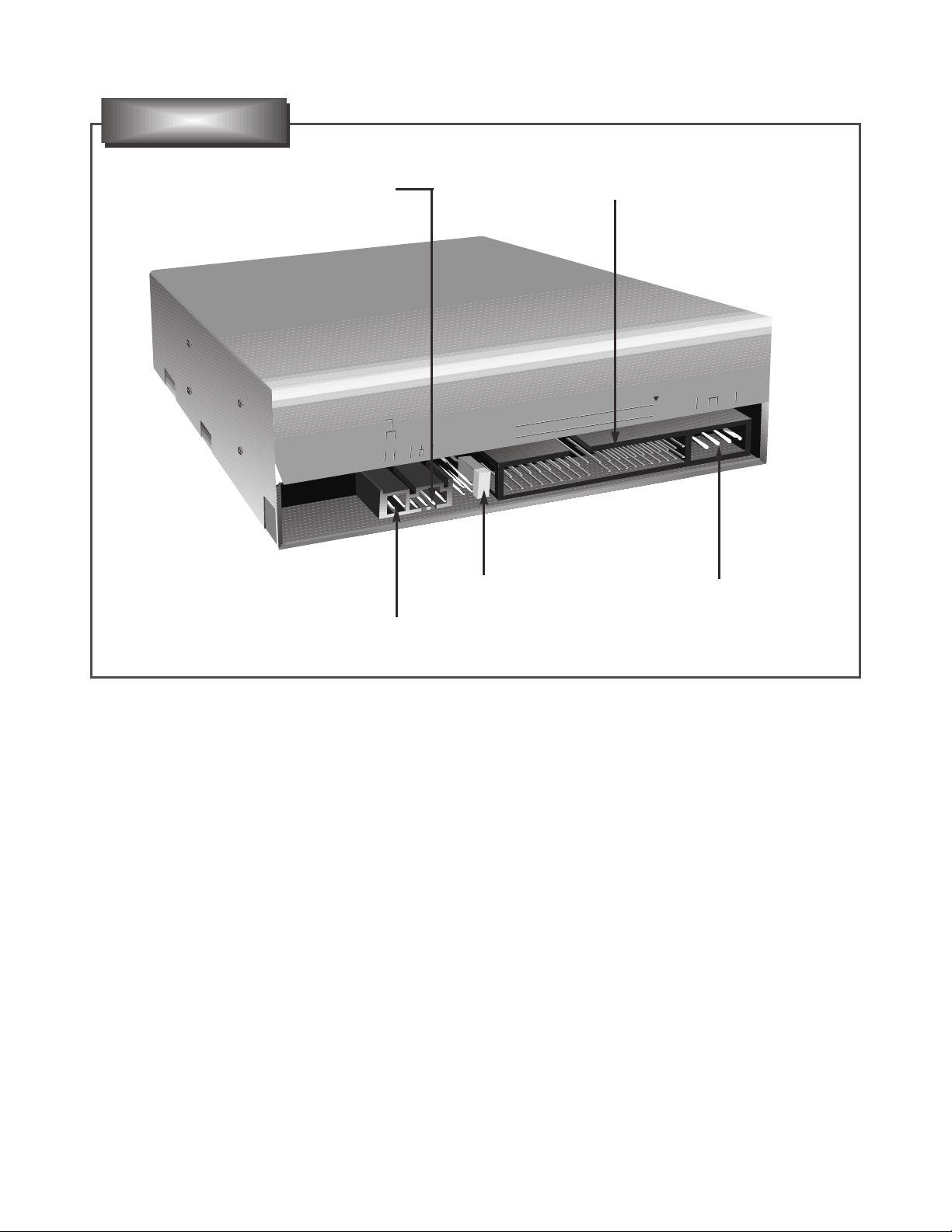

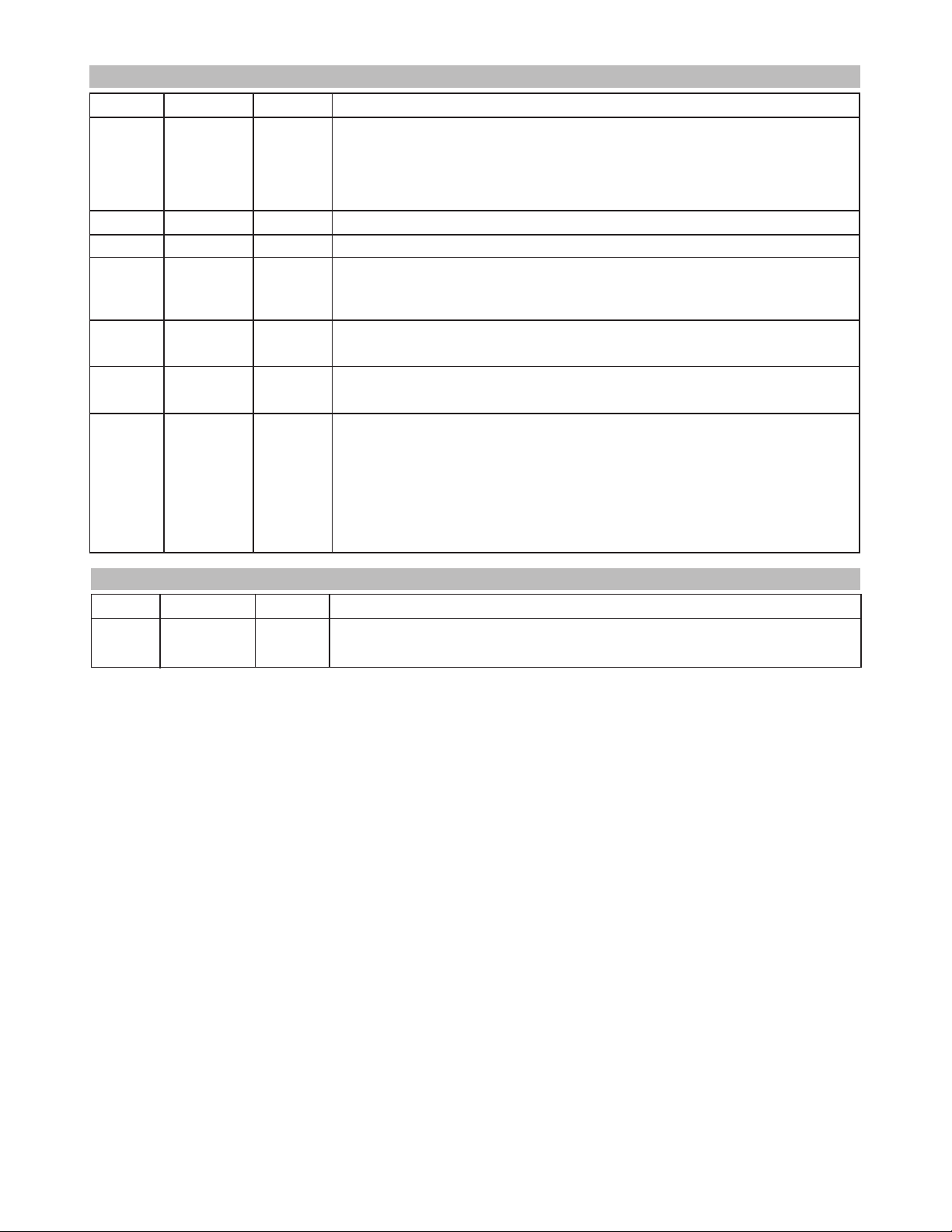

LOCA TION OF CUSTOMER CONTROLS

6

1.

Disc tray

This is the tray for the disc. Place the disc on the

ejected disc tray, then lightly push the tray (or

push the eject button) and the CD will be loaded.

NOTE: Don’t pull out or push in the disc tray

forcibly. This might cause damage to the loading

section of the drive.

2. Stop/Eject button

This button is pressed to open the CD tray.

This button works only when power is supplied to

the drive.

If an Audio CD is playing, pressing this button will

stop it, and pressing it again will open the tray.

3. Play/Skip button

When an Audio CD is in the disc drawer, pressing

this button will start playing Audio CDs from the

first track. If an Audio CD is playing, pressing this

button will skip to the next track.

4.

Volume control

This is used to adjust the output volume of the

headphone jack. It can’t be used to adjust the

output volume for the audio output connectors on

the rear panel.

NOTE : Turn the volume down before turning on

the power. Sudden loud noises can damage your

hearing.

5. Headphone jack

This jack is for connecting headphones or minispeakers.

6. Drive activity indicators

Two colored LEDs are used to indicate the

operation of CD-R/RW Drive.

(1) Read

The orange color is displayed when the spindle

motor begins the Spin up operation: accessing

data, reading data, playing Audio, and up loading

tray.

(2) Write

The green color is flashed during disc writing

sessions.

READ

READ

WRITE

WRITE

COMPACT

Headphone Jack

Volume

Control

Drive Activity Indicators

Play/Skip Button

Stop/Eject Button

Disc Tray

Front Panel

7

1.

Power Connector

Connects to the power supply (5-and 12-V DC) of

the host computer.

NOTE : Be careful to connect with the proper

polarity. Connecting the wrong way may damage

the system (and is not guaranteed). Usually this

connector can only be attached one-way.

2. IDE Interface Connector

Connect to the IDE (Integrated Device

Electronics) Interface using a 40-pin flat IDE

cable.

NOTE : Do not connect or disconnect the cable

when the power is on, as this could cause a short

circuit and damage the system. Always turn the

power OFF when connecting or disconnecting the

cable.

3.

Jumper Connector

This jumper determines whether the drive is

configured as a master or slave. Changing the

master-slave configuration takes effect after

power-on reset.

4. Analog Audio Output Connector

Provides output to a sound card (analog signal).

Generally you need this to play a regular audio

CD.

5.

Digital Audio Output Connector

Provides output to a sound card (digital Signal).

DIGITAL

ANALOG

INTERFACE

POWER

D

R

C

S

M

S

L

A

G

L

G

39

1

+5

+12

GND

40

2

AUDIO

AUDIO

Digital Audio Output

Connector

Jumper Connector

Analog Audio Output Connector

IDE Interface Connector

Power Connector

Rear Panel

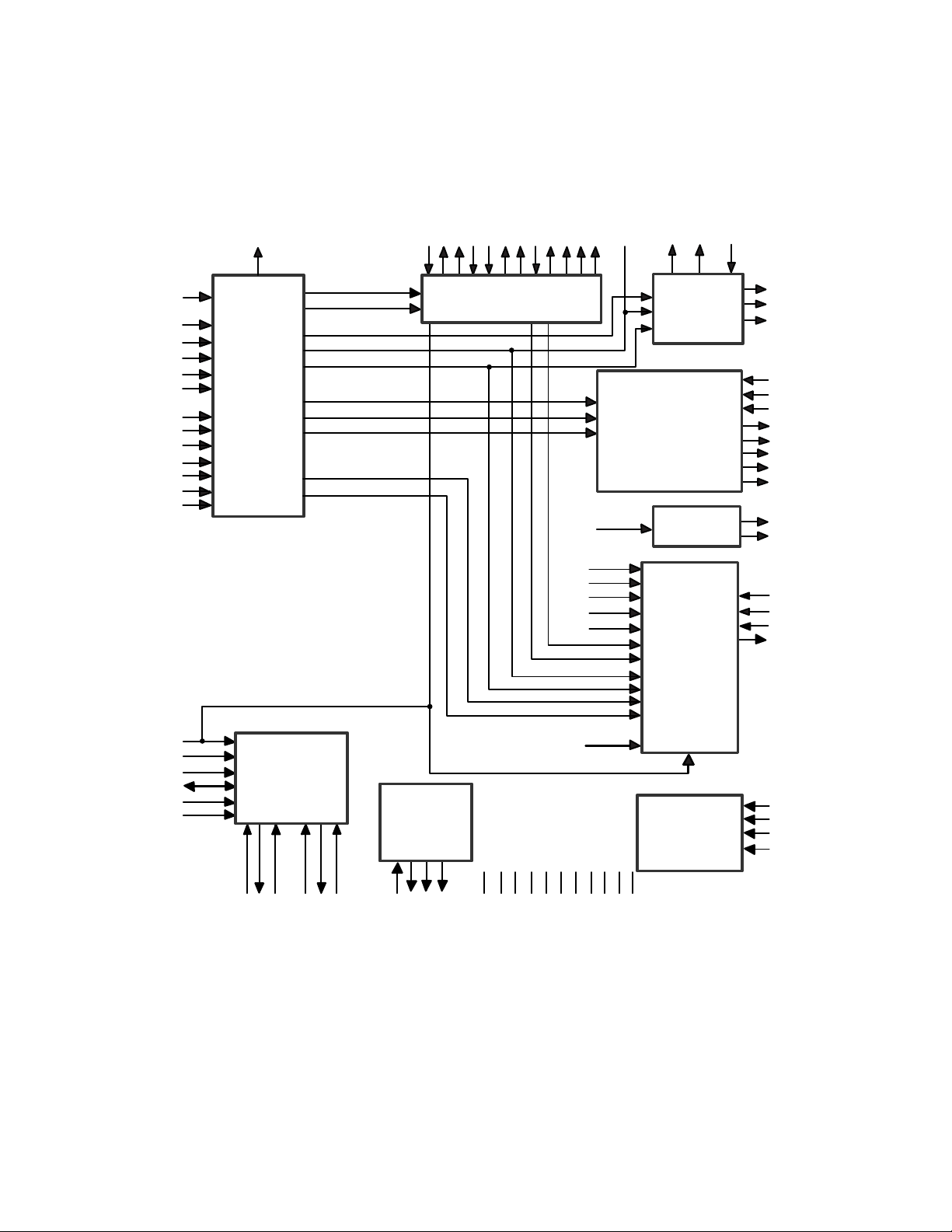

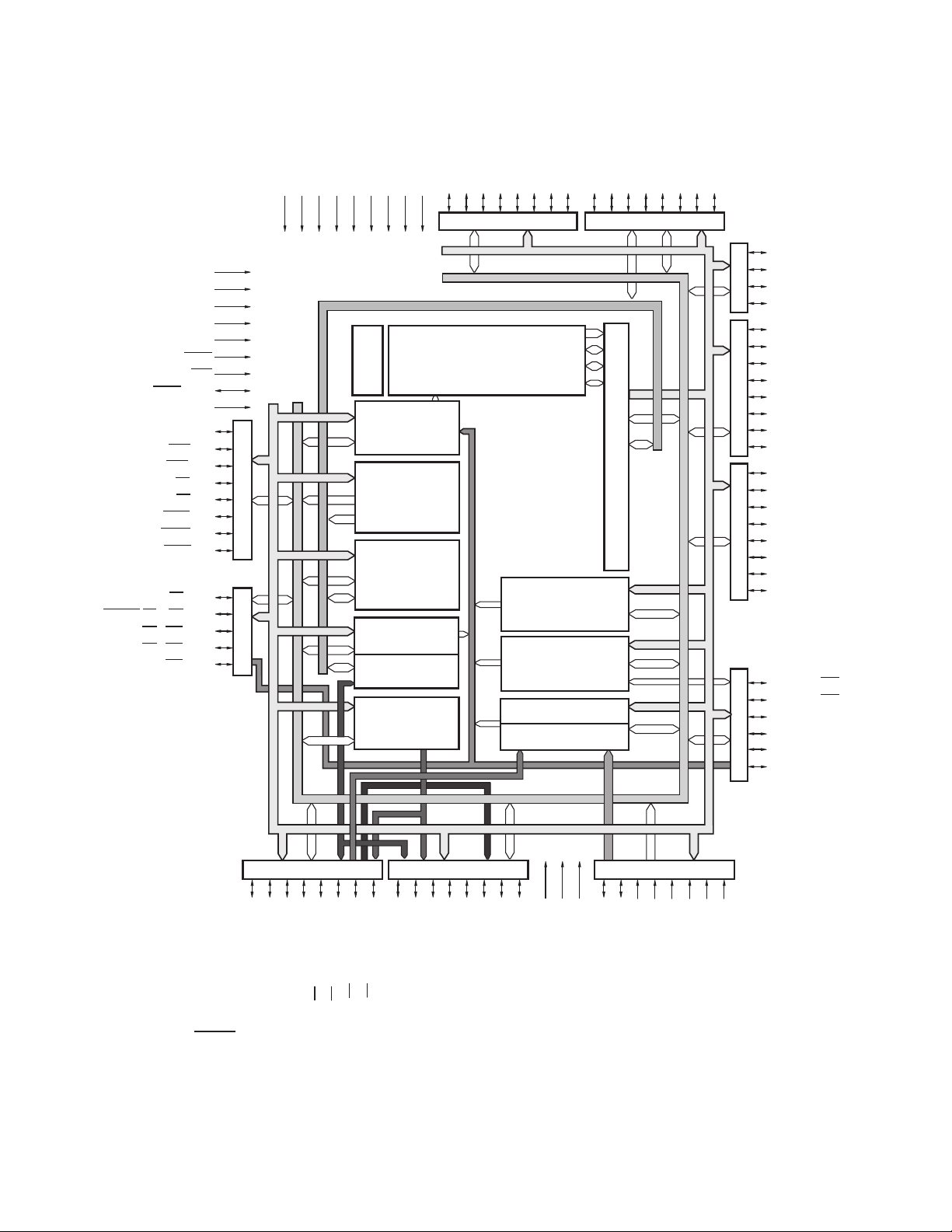

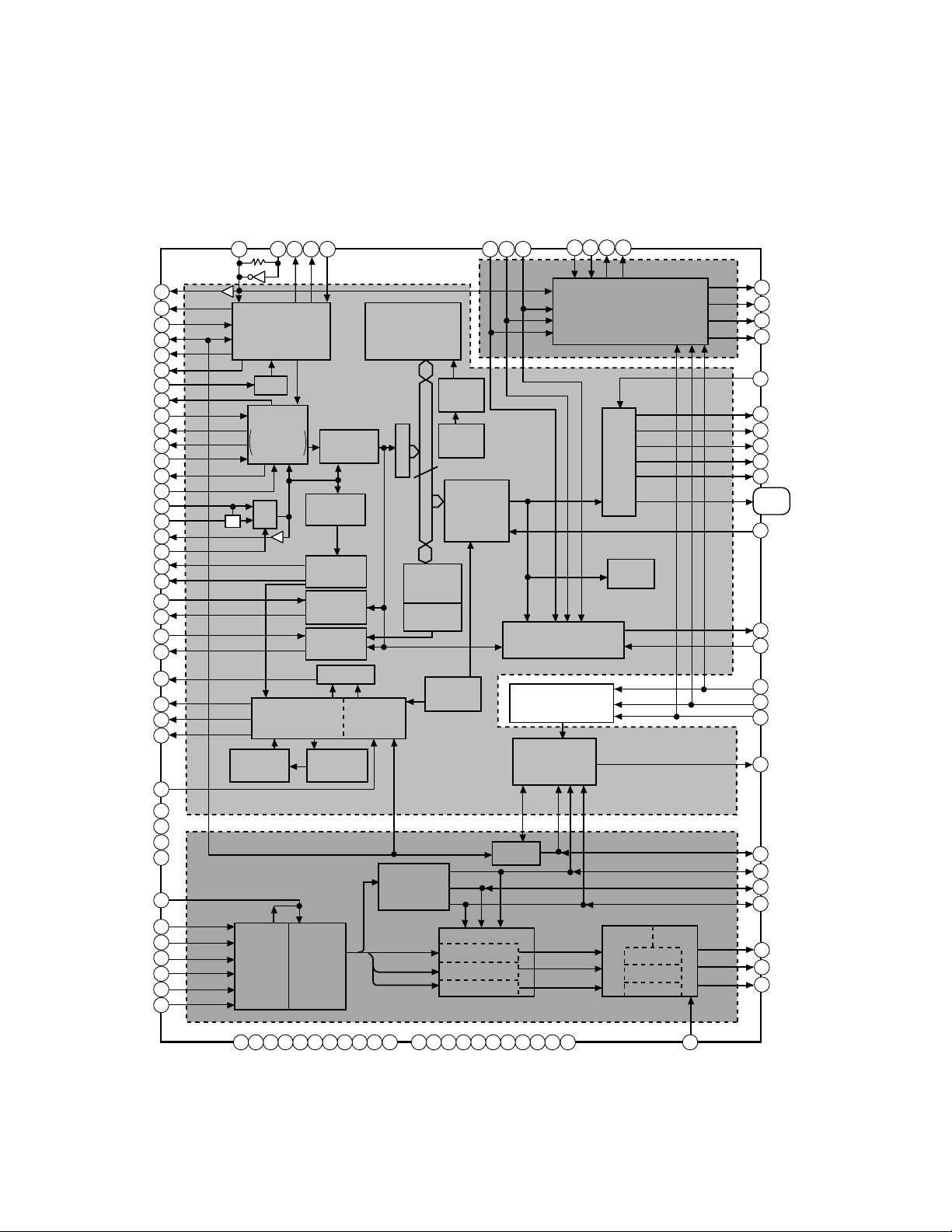

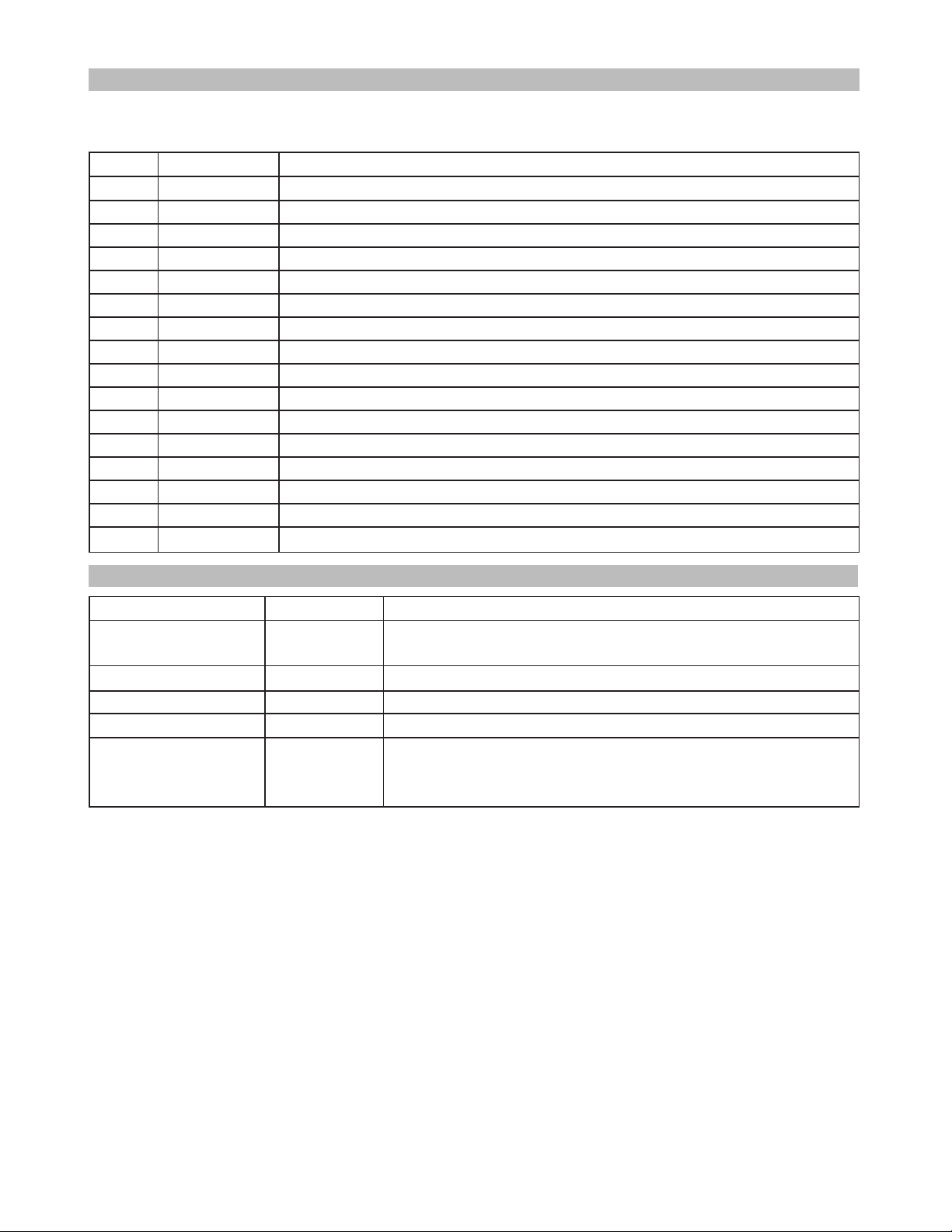

MAJOR IC INTERNAL BLOCK DIAGRAM AND PIN DESCRIPTION

IC601 (AK8563) : Analog Signal Processor LSI for CD-R/RW

Block Diagram

29

HAVC

SRFO

TZC

XTAND

XTOR

AGCON

GAINUP2

GAINUP3

ATFM

ATFG

AGC1C

AGC2C

AGC3C

PHO

BCO

AUX1

AUX2

AUX3

MPXOUT

SDATA

VREF

WLDON

RFPDSH

WFPDSH

FPDO

FPDIN

FVREF

SCLK

XRAT

XRST

VSS

DVSS

DVDD

AVSS3

AVDD3

AVSS2

AVDD2

AVSS1

AVDD1

MCLK

TESTAGC

BIAS

AGND2

AGND1

VREF

WREF

VWDC

VWDCN

RREF

VRDC

VRDCN

RRF

FE

TE

ATFM

VRDC

VWDC

RFO

FEO

MPP

SPPO

ADO

BCO

SADBC

RFOM

WRF

WRF

SLHOLD

RRF

TESTEQRF

DECEFM

XDECEFM

SLLPFN

SLLPFP

RRF

RZC

RECDIN

RECD1

RECD2

OSTC

TESTEQRF

MPP

FE

TE

TEIN

MPDSH

AIN

BIN

CIN

DIN

SPDSH

EIN

FIN

GIN

HIN

WBLSH

GAINUP1

SH_MATRIX

RF_EQUALIZER

FOCUS &

TRACK

ATIP

P/H&B/H

MPX

REG

VREF

APC

30

Pin No. Name I/O Pin Description

1 AVDD3 I Analog Positive Power Source Pin

2 FPDIN I Laser Monitor Diode Contact Pin

3 FVREF I Reference Voltage Level Input Pin for APC

4 FPDO I/O Laser Monitor Output (Connect I/V conversion resistor between FPDIN)/

Laser Monitor Voltage Input

5 WREF I Power Setting Voltage Input for Write APC

6 VWDC O Laser Driver Control Output for Write

7 VWDCN I Laser Driver Control Amp (-) Pin for Write

8 MPP O Main Push-Pull Signal Output

9 TEIN I Input for Tracking Signal Processor

10 TE O Tracking Error Signal Output

11 FE O Focus Error Signal Output

12 BIAS O Bias Resistance Contact Pin. RBIAS=4.7kW

13 AGND1 O Decoupling Pin for Internal Reference Voltage

14

VREF I/O Decoupling Pin for Internal Reference Voltage / Reference Voltage Input Pin

15 NC(VSS) 16 XLAT I Latch Input for Register Settings

17

SDATA I Data Input for Register Settings

18 SCLK I Clock Input for Register Settings

19 MCLK I Main Clock Input (34.5744 MHz)

20

DVSS I Digital Ground Pin

21 DVDD I Digital Positive Power Source Pin

22

ATFG O ATIP FG Output (Wobble signal after binary operation)

23 XTOR O

Tracking Amplitude Detection Output

24

XTAND O Off-Track Detection Output

25

TZC O

Tracking Zero-Cross Detection Signal Output

26 RECD2 O Recording Area Detection Signal 2.”H” Recorded Section, “L” Unrecorded Section

27 RECD1 O Recording Area Detection Signal 1.”H” Recorded Section, “L” Unrecorded Section

28 RZC O RF Zero-Cross Detection Signal Output

29 DECEFM O EFM Output after Slice (reverse)

30 XDECEFM

O

EFM Output after Slice (normal rotation)

31 GAINUP3 I 0, +18dB Switch Control Input Pin. “H”+18dB, “L” 0dB

32

GAINUP2

I 0, +18dB Switch Control Input Pin. “H”+18dB, “L” 0dB

33 GAINUP1 I 0, +18dB Switch Control Input Pin. “H”+18dB, “L” 0dB

34

SLHOLD I Slice Level Hold Signal Input Pin. “H” Hold

35

MPDSH I

Sample Pulse Input for Main Beam Signal. “H” Sample, “L” Hold

36 SPDSH I Sample Pulse Input for Side Beam Signal. “H” Sample, “L” Hold

37

WBLSH I

Sample Pulse Input for Wobble Signal. “H” Sample, “L” Hold

38 RFPDSH I Sample Pulse Input for Read APC. “H” Sample, “L” Hold

39

WFPDSH I

Sample Pulse Input for Write APC. “H” Sample, “L” Hold

40 AVSS2

I

Analog Ground Pin

41 AVDD2 I Analog Positive Power Source Pin

• Pin Description

31

Pin No. Name I/O Pin Description

42 XRST I Register Reset Pin. ”L” Register Initialization

43 WLDON I Write LD Control Input. “L” Write APC Setting to Zero, “H” LD ON

44 AGCON I Wobble AGC Enable Input. “H” AGC ON, “L” AGC reset

45

TESTAGC O Test Pin

46 ATFM O Wobble Signal Output

47 AGC1C O External CAP Connector Pin for AGC Response Speed Setting

48 AGC2C O External CAP Connector Pin for AGC Response Speed Setting

49 AGC3C O External CAP Connector Pin for AGC Response Speed Setting

50 AGND2 O Decoupling Pin for Internal Reference Voltage

51 BHO O RRF Signal Bottom Level Output Pin

52 PHO O RRF Signal Peak Level Output Pin

53

TESTEQRFN

O Test Pin

54

TESTEQRFP

O Test Pin

55 SLLPFP I LPF Input (+) for Auto Slice

56

SLLPFN I LPF Input (-) for Auto Slice

57 OSTCC O CAP Connector Pin for Equalizer Output Offset Canceller fc

58 WRF O

Write RF Signal Output

59 NC(VSS) 60 AVSS1 I

Analog Ground Pin

61

AVDD1 I Analog Positive Power Source Pin

62

RECDIN I RF Input for Recording Area Detection

63 RRF O Read RF Signal Output

64

MPXOUT O Multiplexer Output for Signal Monitoring

65 AUX1 I Auxiliary Input Pin for Signal Monitoring (1)

66

AUX2 I

Auxiliary Input Pin for Signal Monitoring (2)

67

AUX3 I Auxiliary Input Pin for Signal Monitoring (3)

68 GIN I Side Beam Signal (G) Input

69 HIN I Side Beam Signal (H) Input

70 EIN I Side Beam Signal (E) Input

71

FIN

I Side Beam Signal (F) Input

72 HAVC I Main • Side Beam Signal Midpoint Voltage Input

73

DIN I

Main Beam Signal (D) Input

74 CIN I Main Beam Signal (C) Input

75 BIN

I Main Beam Signal (B) Input

76

AIN I

Main Beam Signal (A) Input

77 RREF I Power Setting Voltage Input for Read APC

78

VRDCN

I Laser Driver Control Amp (-) Pin for Read

79 VRDC O Laser Driver Control Output for Read

80

AVSS3 I Analog Ground Pin

* Use NC (unused) pin by connecting to Vss.

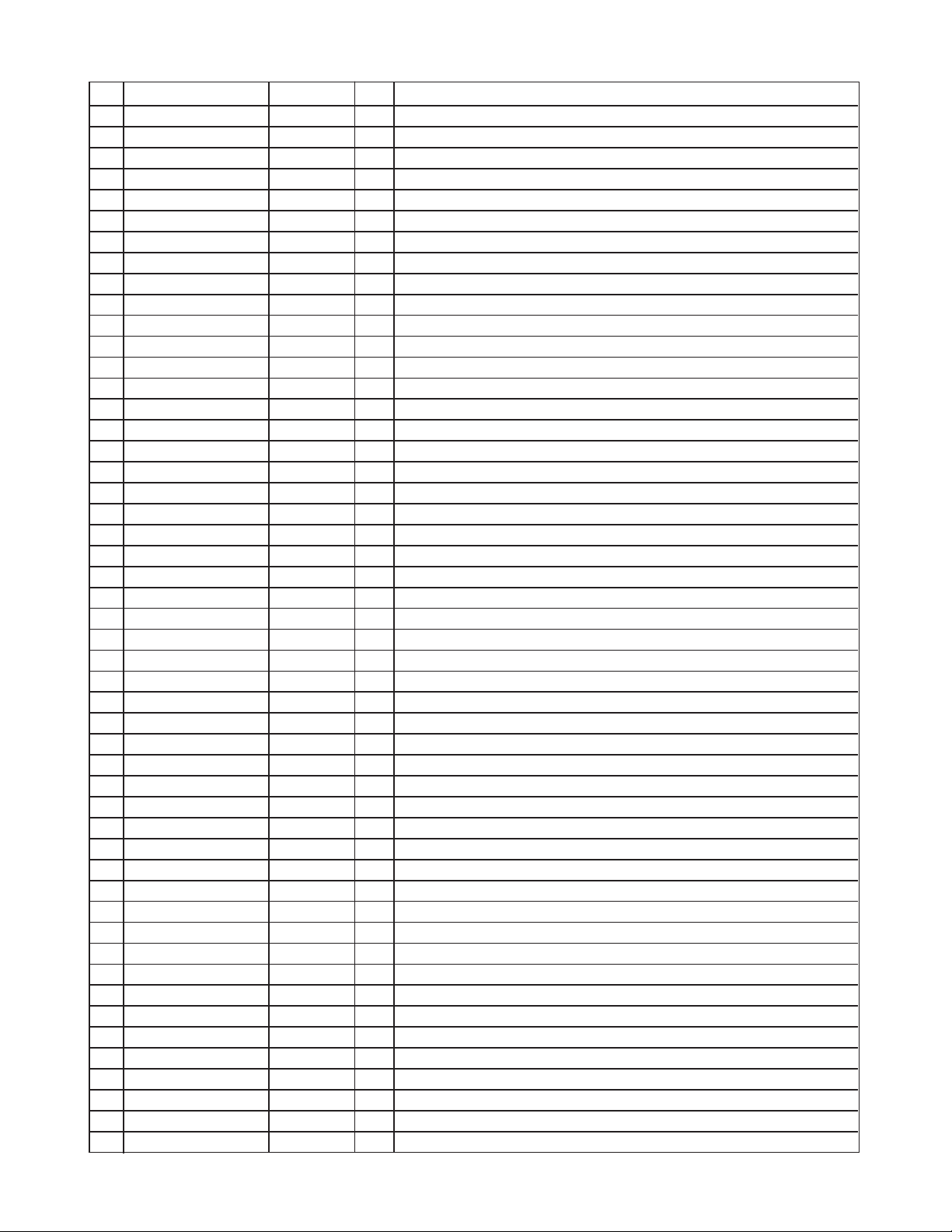

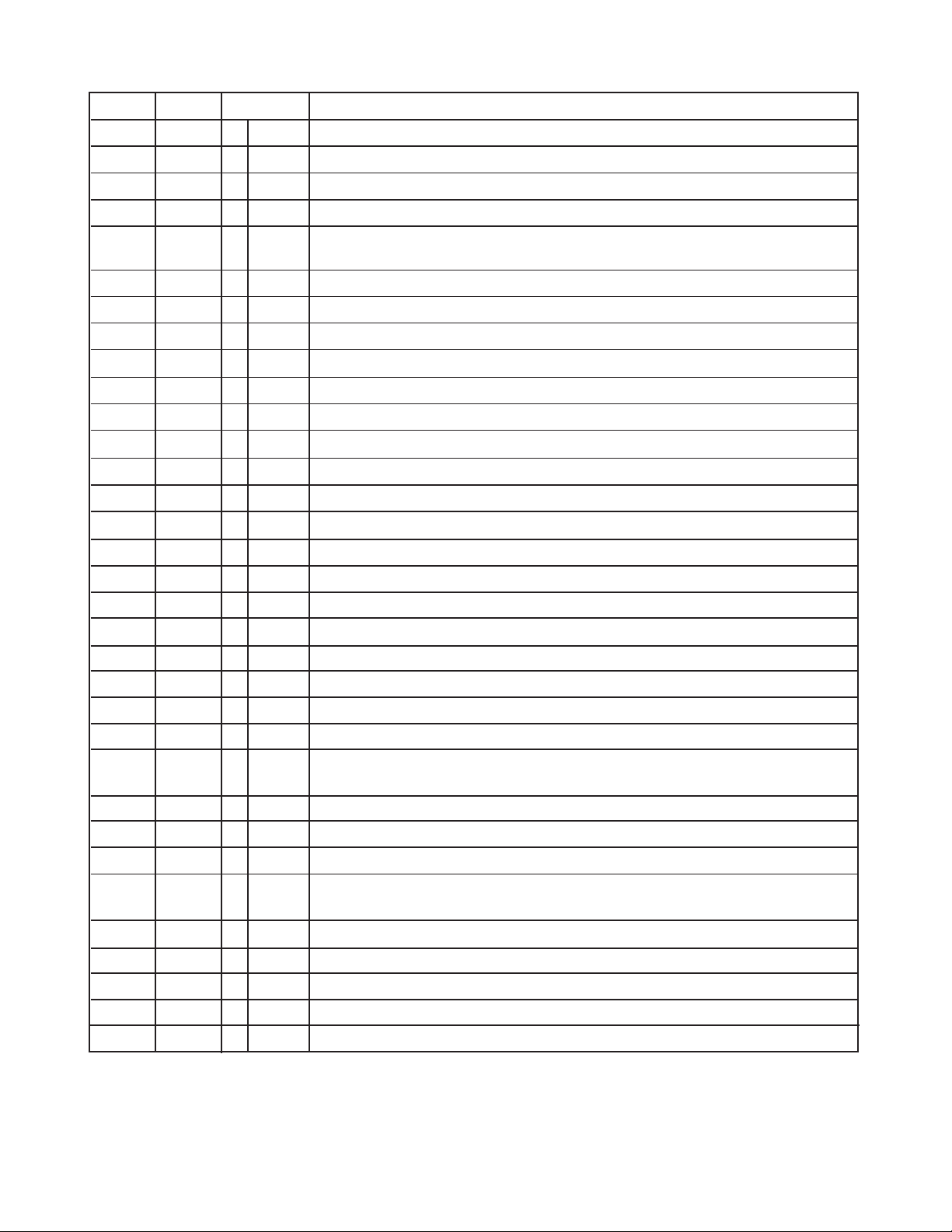

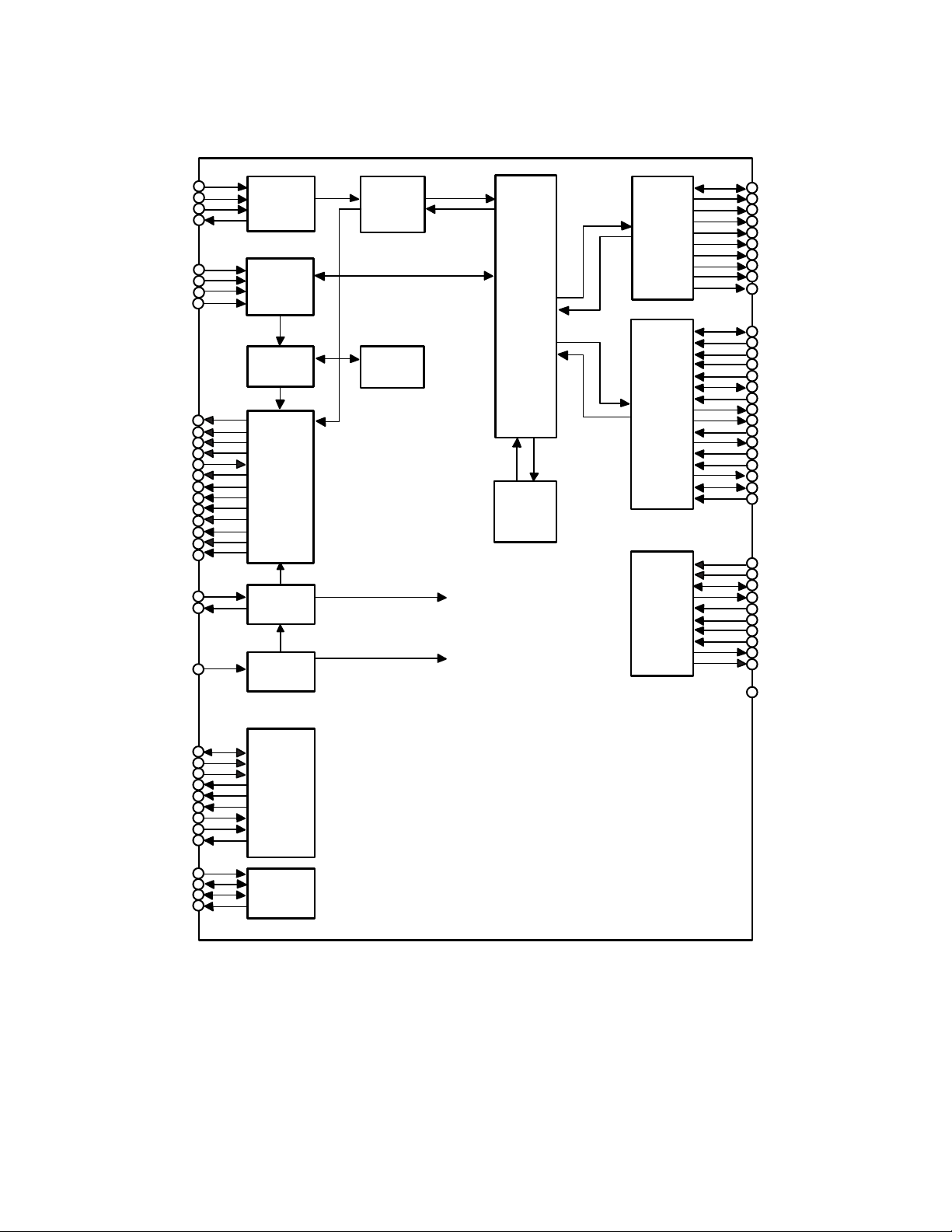

IC202 (HD64F3062) : MICOM

Block Diagram

32

Port 3

Address bus

Data bus (upper)

Data bus (lower)

H8/300H CPU

Interrupt controller

ROM

RAM

16-bit timer unit

Programmable

timing pattern

controller (TPC)

8-bit timer unit

(mask ROM or

flash memory)

Clock pulse

Port 6Port 8

generator

Port 4

Port 5

P5 /A

3

19

RESO/FWE*

ø/P6

7

6

LWR/P6

P4 /D

0

0

P4 /D

1

1

P4 /D

2

2

P4 /D

3

3

P4 /D

4

4

P4 /D

5

5

P4 /D

6

6

P4 /D

7

7

P3 /D

0

8

P3 /D

1

9

P3 /D

2

10

P3 /D

3

11

P3 /D

4

12

P3 /D

5

13

P3 /D

6

14

P3 /D

7

15

VSSVSSVSSVSSVSSVSSVCCVCCV

CC

MD

2

MD

1

MD

0

EXTAL

XTAL

STBY

P5 /A

2

18

P5 /A

1

17

P5 /A

0

16

Port 9

P9 /SCK /IRQ

5

1 5

P9 /SCK

4

0

P9 /RxD

3

1

P9 /RxD

2

0

P9 /TxD

1

1

P9 /TxD

0

0

Port 2

P2 /A

7

15

P2 /A

6

14

P2 /A

5

13

P2 /A

4

12

P2 /A

3

11

P2 /A

2

10

P2 /A

1

9

P2 /A

0

8

Port 1

P1 /A

7

7

P1 /A

6

6

P1 /A

5

5

P1 /A

4

4

P1 /A

3

3

P1 /A

2

2

P1 /A

1

1

P1 /A

0

0

/IRQ

4

Bus controller

Watchdog timer

Serial communication

interface

(SCI) x 2 channels

A/D converter

D/A converter

(WDT)

RES

NMI

5

HWR/P6

4

RD/P6

3

AS/P6

2

BACK/P6

1

BREQ/P6

0

WAIT/P6

40

CS /P8

3

31

ADTRG/CS /IRQ /P8

2

22

CS /IRQ /P8

1

13

CS /IRQ /P8

0

0

IRQ /P8

7

15

TP /PB

6

14

TP /PB

5

13

TP /PB

4

12

TP /PB

3

11

3

4

CS /TMIO /TP /PB

2

10

25

CS /TMO /TP /PB

1

9

1

6

CS /TMIO /TP /PB

0

8

0

7

CS /TMO /TP /PB

7

7

2

20

A /TIOCB /TP /PA

6

6

221

5

5

122

4

4

123

A /TIOCA /TP /PA

A /TICOB /TP /PA

A /TICOA /TP /PA

3

3

0

TCLKD/TIOCB /TP /PA

2

2

0

TCLKC/TIOCA /TP /PA

1

1

0 0

TCLKB/TP /PA

TCLKA/TP /PA

7 71

DA /AN /P7

6 60

DA /AN /P7

5 5

AN /P7

4 4

AN /P7

3 3

AN /P7

2 2

AN /P7

1 1

AN /P7

0 0

AN /P7

REF

V

CCAVSS

AV

Port A Port 7Port B

* Functions as RESO in the mask ROM versions and as FWE in the flash memory version.

33

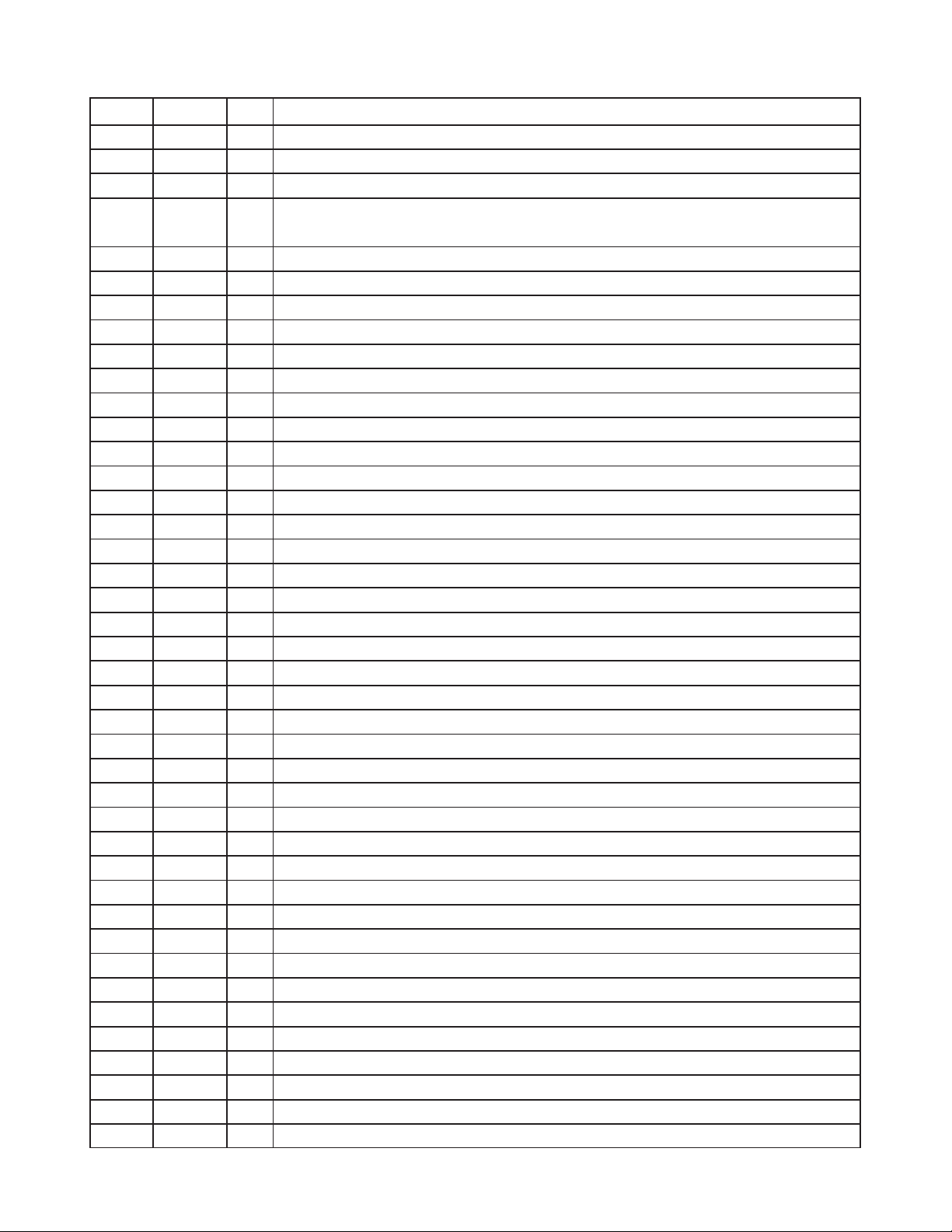

No. Port Name Assign

I/O Description

1 Vcc Vcc I 5V

2 CS7/TMO0/TP8/PB0 ACT_MUTE O FCS, TPK, and SLD ON/OFF

3 CS6/TMIO1/TP9/PB1 /CSMODE O address decoder enable output

4 CS5/TMO2/TP10/PB2 /CS1RL O CHIP SELECT1 (Enable to access buffer memories)

5 CS4/TMIO3/TP11/PB3 /CS0RL O CHIP SELECT0 (Enable to access internal registers)

6 TP12/PB4 /XRST O CXD3011 reset output

7 TP13/PB5 LD_ON O Laser diode on/off control output

8 TP14/PB6 AUD_MUTE O Audio mute output

9 TP15/PB7 FWE_ON O Flash writing enable output

10 RESO/FWE FWE I Flash writing mode setting

11 Vss Vss I GND

12 P90/TxD0 /XRST_R O Ricoh reset

13 P91/TxD1 BTS_TXD O Serial communication transmit

14 P92/RxD0 TESTADJ O

15 P93/RxD1 BTS_RXD I Serial communication receive

16 IRQ4/SCK0/P94 SCOR I SCOR input (High when either subcode sync S0 or S1 is detected)

17 IRQ5/SCK1/P95 SHOCK I

18 D0/P40 SDATAO O Serial data output

19 D1/P41 SCLK O Interface clock output

20 D2/P42 ATIPGUP O CDRW gainup control output

21 D3/P43 /EPCS O E2PROM selection

22 Vss Vss I GND

23 D4/P44 /AKCS

O AK interface latch signal output

24 D5/P45 /DACS

O D/A interface latch signal output

25

D6/P46 /CXDCS O

CXD3011 interface latch signal output

26

D7/P48 SENSCLK O

SENS serial data readout clock output

27

D8/P30 SD0 I/O

DATA IN / OUT

28 D9/P31 SD1

I/O DATA IN / OUT

29 D10/P32 SD2

I/O DATA IN / OUT

30 D11/P33 SD3 I/O DATA IN / OUT

31 D12/P34 SD4 I/O DATA IN / OUT

32 D13/P35 SD5 I/O DATA IN / OUT

33 D14/P36 SD6 I/O DATA IN / OUT

34 D15/P37 SD7 I/O DATA IN / OUT

35 Vcc Vcc I 5V

36

A0/P10 SA0

O

Address output

37 A1/P11 SA1 O Address output

38

A2/P12 SA2

O

Address output

39 A3/P13 SA3 O Address output

40

A4/P14 SA4

O

Address output

41 A5/P15 SA5 O Address output

42

A6/P16 SA6

O

Address output, address decoder selection signal output

43 A7/P17

SA7 O Address output, address decoder selection signal output

44

Vss Vss

I

GND

45 A8/P20

/LOAD_SW

I Load switch input

46

A9/P21

/OPEN_SW I

Open switch input

47 A10/P22

FOK I

Focus OK input

48 A11/P23 RECD1 I Recording area detection signal input

49

A12/P24 RECD2

I

Recording area detection signal input

50 A13/P25 LOCK I Input is “L” when the GFS signal sampled is “L” 8 or more times is succession

•Pin Description

34

No. Port Name Assign

I/O Description

51 A14/P26 /PLAY_KEY I Play_key input

52 A15/P27 /EJECT_KEY I Eject_key input

53 A16/P50 SENS I SENS input

54 A17/P51 MA/SL I Master / slave detection input

55 A18/P52 MONIT I

56 A19/P53 SQSO I Sub-Q 80bit input

57 Vss Vss I GND

58 P60/WAIT SRDY I Data ready input

59 P61/BREQ AGCON O Wobble AGC enable output

60

P62/BACK SQCK O SQSO(Sib-Q 80bit) readout clock

61 P67/Pi SDATAI I E2PROM data input

62

/STBY /STBY

I Standby input

63 /RES /RESET I RESET input

64 NMI NMI I Nonmaskable interrupt input

65 Vss Vss I Ground

66 EXTAL EXTAL I Crystal resonator connection input

67 XTAL XTAL I Crystal resonator connection input

68 Vcc Vcc I 5V

69

P63/AS AS O

70

P64/RD /SREB O

Ricoh read latch output

71 P65/HWR /SWEB O

Address Decoder Enable output Ricoh write latch output

72 P66/LWR /LWR O

73 MD0 MD0 I

Input for setting the operation mode

74 MD1 MD1 I

Input for setting the operation mode

75 MD2 MD2 I

Input for setting the operation mode

76 AVcc AVcc I

Analog 5V

77

Vref VREF I

A/D reference input

78

P70/AN0 ASYM1 I

RRF peak hold input

79 P71/AN1 ASYM2

I RRF bottom hold input

80 P72/AN2 2V

I 2V

81 P73/AN3

MPXO I Multiplexer input for signal monitering

82 P74/AN4

B_LEVEL0 I B_level0 input

83

P75/AN5 B_LEVEL2 I B_level2 input

84 P76/AN6/DA0/Q104 SLDADJ I Input for sled adjusting

85

P77/AN7/DA1/Q103

SLDMOVE O

Sled control output

86 AVss AVss I Analog GND

87

IRQ0/P80

ATSY(ESFS) I

Encode subcode frame sync input

88 IRQ1/CS3/P81 SINT0 I Ricoh interrupt group input (ricoh interrupt source 4,3)

89 IRQ2/CS2/P82 SINT1 I Ricoh interrupt group input (ricoh interrupt source 0,1,2)

90

IRQ3/CS1/ADTRIG/P83 ADTRIG I A/D conversion external trigger input

91 CS0/P84 CS0 O

92

Vss Vss

I GND

93 TP0/TCLKA/PA0 COUT I Track count signal input

94

TP1/TCLKB/PA1 MIRR

I Mirror signal input

95 TP2/TCLKC/TIOCA0/PA2 SPNFG I Spindle FG signal input

96 TP3/TCLKD/TIOCB0/PA3

N.D.

97 TP4/TIOCA1/A23/PA4 SLDFG I Sled FG signal input

98

TP5/TIOCB1/A22/PA5 XTOR

I Tracking error amplitude detection input

99

TP6/TIOCA2/A21/PA6 SPNREV I Detection input for spindle revolution direction

100

TP7/TIOCB2/A20/PA7 USER

I

35

No. Port Name Assign

I/O Description

1 /OE /OE I Output enable input

2 O0 XTSEL O CXD3011R-1 crystal selection output

3 D0 SD4 I Data input

4 D1 SD5 I Data input

5 O1 ASYMCLR O Control output for discharging ASYM1/ASYM2

6 O2 SPNBOOST O spindle gain selection output

7

D2 SD6 I Data input

8 D3 SD7 I Data input

9 3 SPN8/12CM O 8/12cm Disc control output

10 GND GND

11 CP CP I Clock input

12 O4 SPNON O SPINDLE start / stop control output

13 D4 SD3 I Data input

14 D5 SD2 I Data input

15 O5 LED2 O LED2 control output

16

O6 LED1 O

LED1 control output

17

D6 SD1 I

Data input

18

D7 SD0 I

Data input

19

O7 PWRCTL1 O

Power save control1 output

20

Vcc Vcc 5V-2

No.

Port Name Assign

I/O

Description

1

/OE /OE I

Output enable input

2

O0 PWRCTL4 O

Power save control4 output

3 D0 SD4 I Data input

4 D1 SD5 I Data input

5 O1 TRAY_MUTE O Tray mute output

6 O2 ODOFF O CDR over drive power control output

7 D2 SD6 I Data input

8 D3 SD7 I Data input

9 3 SPN_PHASE O spindle loop phase selection output

10

GND GND

11 CP CP I Clock input

12

O4

SLDSEL O

Control output for sled adjusting

13 D4 SD3 I Data input

14

D5

SD2 I

Data input

15 O5 RRWMODE O Control output for switching between MIRR and MIRR_RRW

16

O6 WR/RE

O

Write / read control output

17 D6 SD1 I Data input

18

D7 SD0

I

Data input

19 O7 CDR/RW O CDR/RW selection output

20

Vcc Vcc

5V-2

IC204 (74VHC374MTC) : Expander

• Pin Description

IC205 (74VHC374MTC) : Expander

• Pin Description

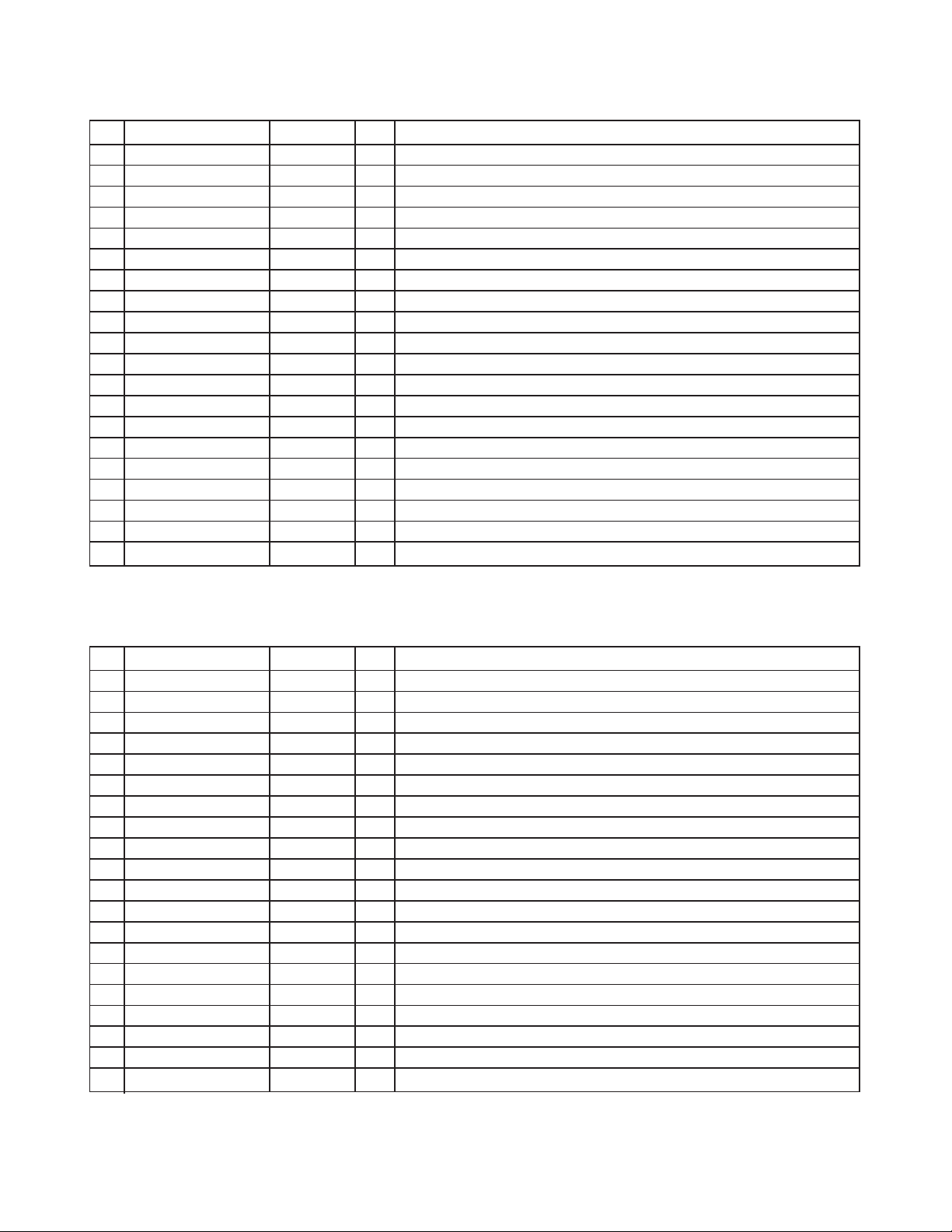

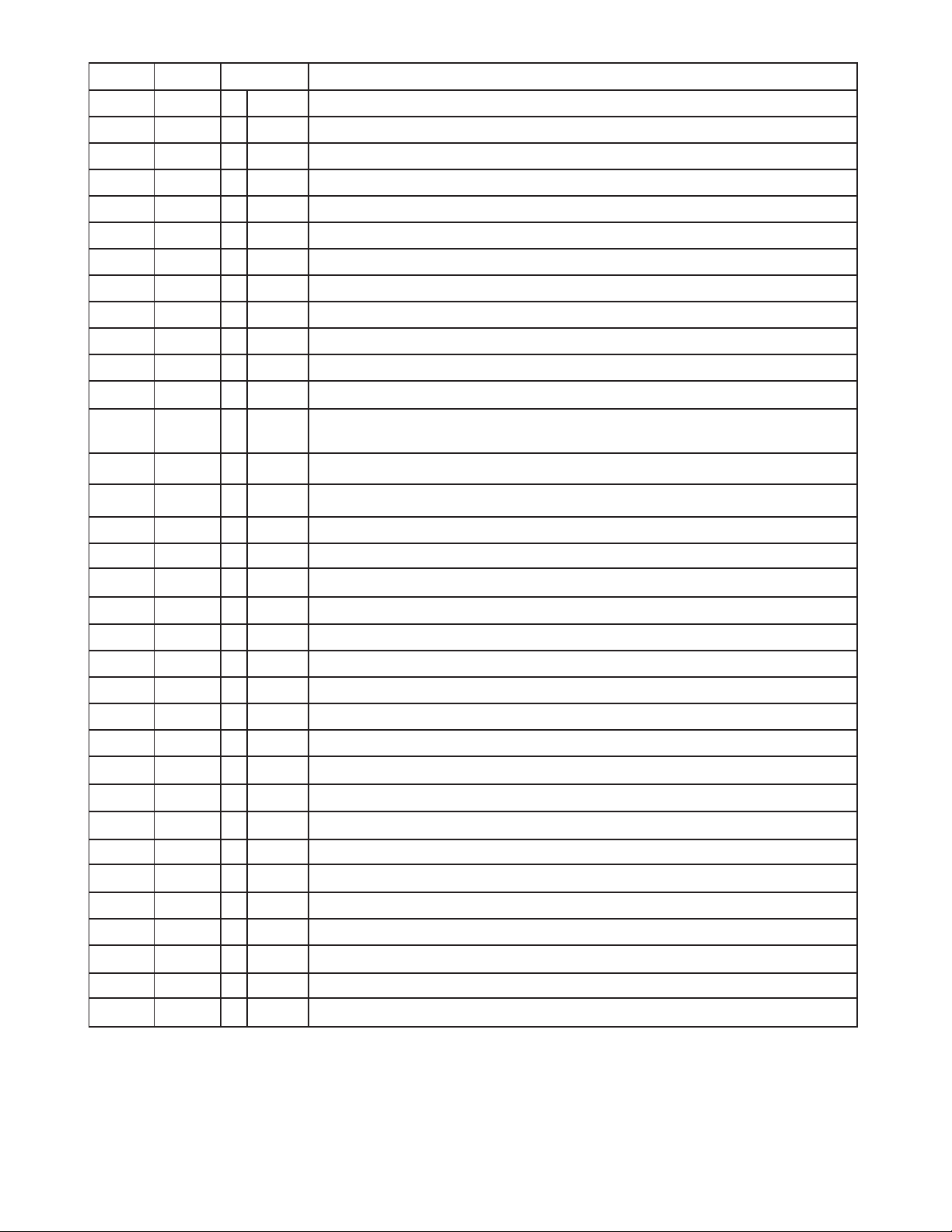

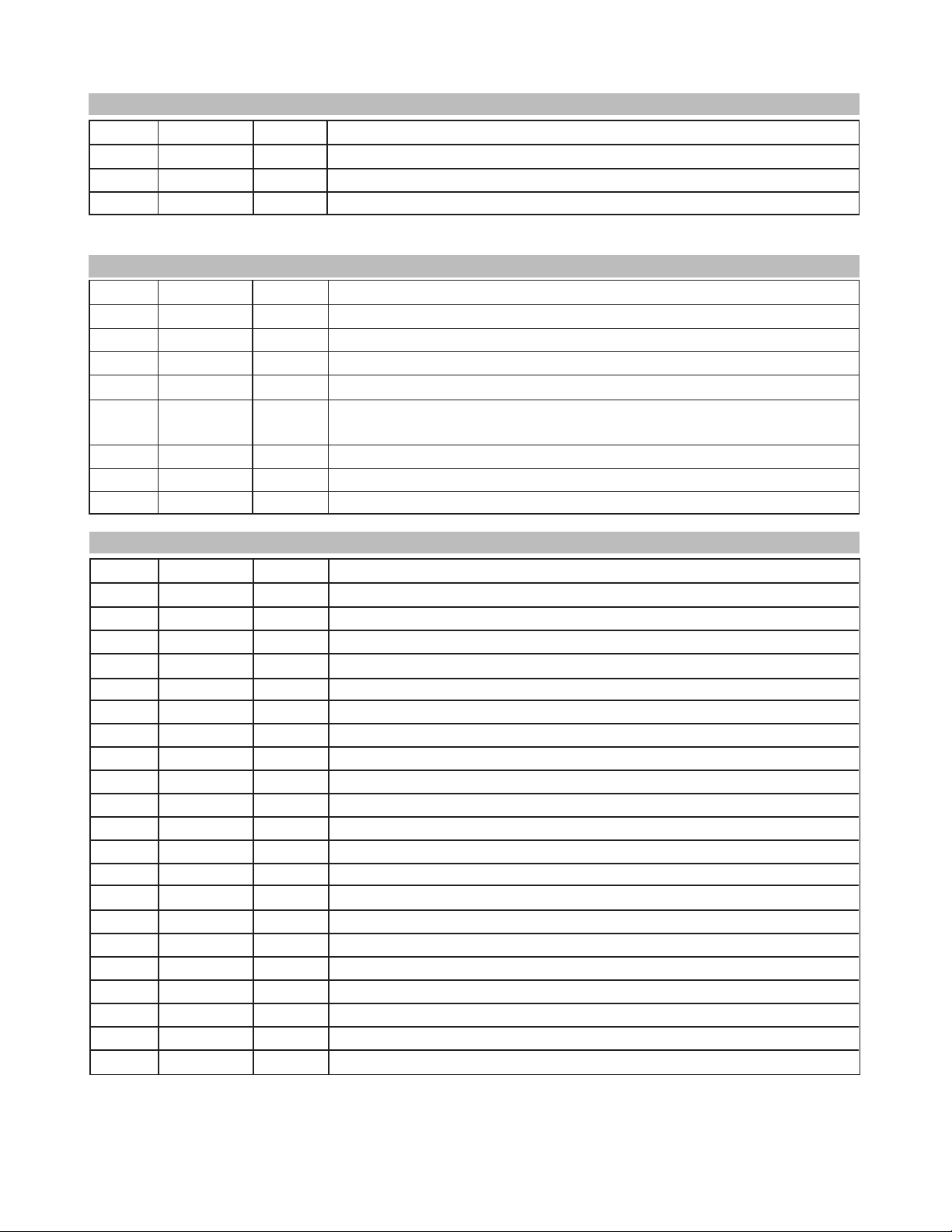

IC501 (CXD3011 R-1) : CD Digital Signal Processor with Built-in Digital

Servo and DAC

Block Diagram

36

52

83 84 5 6 51

136

135

57

58

59

7

134

122

107

129

123

124

141

132

131

13

15

16

24

64

65

67

66

69

68

117

118

116

133

71

140

142

143

22 43 60 94

130

17

137

93 81 82 23 50 77

101

105

102

100

103

104

121

12

139

86 78 85

110 114

111

95

99

98

62

63

25

79

80

88

87

29

61

112

113

115

4

3

2

10

11

9

8

Clock

Generator

32K RAM

Digital PLL

Vari-Pitch

double

speed

EFM

Demodulator

Sync

D/A

protector

Address

generator

8Fs Digital Filter

+

1 bit DAC

Priority

encoder

Timing

CLV

Servo

auto

CAV

Digital Out

Generator1

Timing

Generator2

Noise

Shaper

18~times

oversampling

filter

P~W

Subcode

Subcode Q

processor

processor

processor

processor

CPU

interface

Servo

Interface

SERVO DSP

DAC OpAmp

FOCUS SERVO

TRACKINGSERVO

FOCUS

SLED

TRACKING

SLED SERVO

OpAmp

AnaSw

A/D

CONVERTER

MIRR

DFCT

FOK

Peak

detector

Error

corrector

data

processor

Serial/parallel

processor

Register

XTLO

DV

DD

1

DV

DD

2

DV

DD

3

DV

DD

4

DV

DD

5

DV

SS

1

DV

SS

2

DV

SS

3

DV

SS

4

DV

SS

5

AV

SS

1

AV

SS

2

AV

SS

3

AV

SS

4

AV

SS

5

AV

SS

6

BSSD

AV

DD

1

AV

DD

2

AV

DD

3

AV

DD

4

AV

DD

5

AV

DD

6

XTLI

VPCO1

VPCO2

XTSL

PCMDI

BCKI

LRCKI

DTSO

XWO

RMUTO

LMUTO

Error Rate

Counter

sequencer

Selector

OSC

MCKO

V16M

VCKI

FSTIO

C4M

C16M

VCTL

PDO

PCO

VCOI

FILI

FILO

CLTV

RFAC

ASYI

ASYO

ASYE

WFCK

SCOR

EXCK

SBSO

SQCK

SQSO

MDP

MDS

MON

FSW

PWMI

TEST

TES2

TES3

XRST

ADIO

RFDC

CE

TE

SE

FE

VC

SAO

TAO

FAO

COUT

SENS

DATA

DOUT

MUTE

PSSL

PWMLP

PWMLN

PWMRP

PWMRN

DA16(48PCM)

DA15(48BCK)

DA14(64PCM)

DA13(64BCK)

DA12(64LRCK)

DA11

~DA01

MD2

CLOK

XLAT

MIRR

DFCT

FOK

VCOO

SIGNAL PROCESSOR BLOCK

SERVO BLOCK

DAC BLOCK

35

38~42,

44~49

34

33

31

30 32 28 74 75 76

8

MUX

*

* : Asymmetry

Correction

37

• Pin Description

Pin No. Symbol I/O Description

2 SE I Slide Error input

3 FE I Focus Error input

4 VC I Center voltage input

5 VPCO1 O 1, Z, 0 Output of VCO2 charge pump for vari-pitch EFM PLL

6 VPCO2 O 1, Z, 0 Output 2 of VCO2 charge pump for vari-pitch EFM PLL

ON/OFF switching by Command £§E

7 VCTL I Input of VCO2 control voltage for vari-pitch EFM PLL

8 FILO O Analog Output of Filter for master PLL (slave = digital PLL)

9 FILI I Input of filter for master PLL

10 PCO O 1, Z, 0 Output of charge pump for master PLL

11 CLTV I VCO control voltage lnput

12 A VSS1 Analog GND

13 RFAC I EFM signal input

14 BIAS I Asymmetry circuit constant current input

15

ASYI I Asymmetry comparator circuit voltage input

16 ASYO O

1, 0 EFM full-swing output (L=VSS, H=V

DD)

17

A VDD1

Analog power supply

22 D VDD1 Digital power supply

23 D VSS1 Digital GND

24

ASYE I Asymmetry circuit ON/OFF (L=OFF, H=ON)

25 PSSL I Input used to switch the audio data output mode. (L=serial, H=parallel)

26

WDCK O 1, 0

D/A interface for 48-bit slot. Word clock f=2Fs

27

LRCK O 1, 0

D/A interface for 48-bit slot. LR clock f=Fs

28 LRCKI I LR clock input to DAC (48-bit slot)

29 DA16 O 1, 0 Outputs DA16 (MSB) when PSSL=1, or serial data output from the 48-bit slot (2's

complements, MSB first) when PSSL=0.

30 PCMDI I Audio data input to DAC (48-bit slot)

31 DA15 O 1, 0 Outputs DA15 when PSSL=1, or bit clock output from the 48-bit slot when PSSL=0.

32 BCKI I Bit clock input to DAC (48-bit slot)

33

DA14 O

1, 0

Outputs DA14 when PSSL=1, or serial data output from the 64-bit slot (2's

complements, LSB first) when PSSL=0.

34

DA13 O

1, 0

Outputs DA13 when PSSL=1, or bit clock output from the 64-bit slot when PSSL=0.

35 DA12 O 1, 0 Outputs DA12 when PSSL=1, or LR clock output from the 64-bit slot when PSSL=0.

38

DA11 O

1, 0 Outputs DA11 when PSSL=1, or GTOP when PSSL=0.

39

DA10 O

1, 0

Outputs DA10 when PSSL=1, or XUGF when PSSL=0.

40 DA09 O 1, 0 Outputs DA9 when PSSL=1, or XPLCK when PSSL=0.

38

Pin No. Symbol I/O Description

41 DA08 O 1, 0 Outputs DA8 when PSSL=1, or GFS when PSSL=0.

42 DA07 O 1, 0 Outputs DA7 when PSSL=1, or RFCK when PSSL=0.

43 DVDD2 Digital Power supply

44 DA06 O 1, 0 Outputs DA6 when PSSL=1, or C2PO when PSSL=0.

45 DA05 O 1, 0 Outputs DA5 when PSSL=1, or XRAOF when PSSL=0.

46 DA04 O 1, 0 Outputs DA4 when PSSL=1, or MNT3 when PSSL=0.

47 DA03

O 1, 0 Outputs DA3 when PSSL=1, or MNT2 when PSSL=0.

48 DA02 O 1, 0 Outputs DA2 when PSSL=1, or MNT1 when PSSL=0.

49 DA01 O 1, 0 Outputs DA1 when PSSL=1, or MNT0 when PSSL=0.

50 DVSS2 Digital GND

51 XTSL I X'tal selection input

52 MCKO O 1, 0 Clock output. Inverse output of XTLI

57 FSTIO I/O 1, 0 Clock input/output for Digital servo

(2/3 frequency demultiplication input of XTLI)

58 C4M O 1, 0

1/4 frequency demultiplication output of XTLI. Affected by vari-pitch

59

C16M O 1, 0

16.9344MHz output. Subject to vari-pitch control.

60 DVDD

3 Digital power supply

61

MD2 I Digital-Out ON/OFF control. "H" for ON, "L" for OFF.

62

DOUT O 1, 0

Digital-Out output.

63 MUTE I

"H" for muting, "L" for release.

64

WFCK O 1, 0

WFCK (Write Frame Clock) output

65 SCOR O

1, 0 "H" when subcode Sync S0 or S1 is detected.

66 SBSO O 1, 0

Serial output of Sub P to W

67

EXCK I Clock input for reading SBSO

68 SQSO

O

1, 0 Outputs 80-bit Sub Q and 16-bit PCM peak-level data.

69

SQCK I Clock input for reading SQSO

70 SCSY I Input of GRSCOR

71 XRST I System reset. "L" for resetting

74

XWO I

Window open input for DAC synchronization. Generally, at "L" window open

75 RMUTO O 1, 0 Audio DAC, zero detecting block for R channel

76

LMUTO O

1, 0 Audio DAC, zero detecting block for L channel

77 DVSS3 Digital GND

78 AVSS4 Analog GND

79

PWMRN O

1, Z, 0 PWM output for Audio DAC, R channel, Reverse phase

80 PWMRP O 1, Z, 0 PWM output for Audio DAC, R channel

39

Pin No. Symbol I/O Description

81 AVDD4 Analog power supply

82 AVDD5 Power supply for master clock

83 XTLO O 1, 0 X'tal oscillation circuit output of master clock.

84 XTLI I X'tal oscillation circuit input of master clock.

85 AVSS5 GND for master clock

86 AVSS3 Analog GND

87 PWMLP

O 1, Z, 0 PWM output for Audio DAC, L channel

88 PWMLN O 1, Z, 0 PWM output for Audio DAC, L channel, Reverse phase

93 AVDD3 Analog power supply

94 DVDD4 Digital power supply

95 SENS O 1, Z,0 SENS output to CPU

96 SCLK I Clock for SENS serial data

97 ATSK I Pin for Anti-shock

98 DATA I Serial Data input from CPU

99 XLAT I Latch input from CPU

100 CLOK I Serial Data transfer clock input from CPU

101

DVSS4

Digital GND

102

COUT I/O 1, 0

Track number count signal input/output

103 MIRR I/O

1, 0 Mirror signal input/output

104

DFCT I/O 1, 0

Defect signal input/output

105 FOK I/O

1, 0 Focus OK input/output

106 TESO O Test pin

107

FSW O 1, Z,0

SCOR of command

£§8, GRSCOR output when SEL="H"

110 AVSS6

Analog GND

111 SAO

O DAC analog output of Sled filter

112 TAO O DAC analog output of Tracking filter

113 FAO O DAC analog output of Focus filter

114

BSSD I

Constant current input for DAC analog of servo filter

115 AVDD6 Analog power supply

116

MON O

1, 0 Output for spindle motor ON/OFF control

117 MDP O 1, Z, 0 Output for spindle motor servo control

118 MDS O 1, Z, 0 Output for spindle motor servo control

119

LOCK I/O

1, 0 Output is "H" when the GFS signal sampled at 460Hz is "H". Output is "L" when the

GFS signal is "L" 8 or more times is succession.

120 SSTP I Disc inner periphery detection signal input

121

DVSS5 Digital GND

122 DTS0

I

Test pin. Normally "L"

40

Notes :

• The data at the 64-bit slot is output in 2's complements on an LSB-first basis.

The data at the 48-bit slot is output in 2's complements on an MSB-first basis.

• GTOP monitors the state of Frame Sync protection. ("H" : Sync protection window released)

• XUFG is a negative Frame Sync pulse obtained from the EFM signal before Frame Sync protection is

effected.

• XPLCK is an inversion of the EFM PLL clock. The PLL is designed so that the falling edge of XPLCK

coincides with a change point of the EFM signal.

• The GFS signal turns "H" upon coincidence between Frame Sync and the timing of interpolation protection.

• RFCK is a signal generated at 136-•Ïs periods using a crystal oscillator.

• C2PO is a signal to indicate data error.

• XRAOF is a signal issued when a jitter margin of °æ28F is exceeded by the 32K RAM.

Pin No. Symbol I/O Description

123 TES2 I Test Pin. Normally "L"

124 TES3 I Test Pin. Normally "L"

129 PWMI I External input of spindle motor

130 DVDD5 I Digital power supply

131 VCOO O 1, 0 Output of oscillation circuit analog EFM PLL

132 VCOI I Input to oscillation circuit for analog EFM PLL. fLOCK=8.6436MHz

133 TEST I Test Pin. Normally "L"

134 PDO O 1, Z, 0 Output of charge pump for analog EFM PLL

135 VCKI I Clock input from external VCO for vari-pitch control. fccenter=16.9344MHz

136 V16M O 1, Z, 0 Output of VC02 oscillation for vari-pitch EFM PLL

137 AVDD2 Analog power supply

138 IGEN I Resistor connection pin of current source reference for OP Amp

139 AVSS2 Analog GND

140 ADIO O OP Amp output

141

RFDC I RF signal input

142 CE I Center servo analog input

143 TE I Tracking error signal input

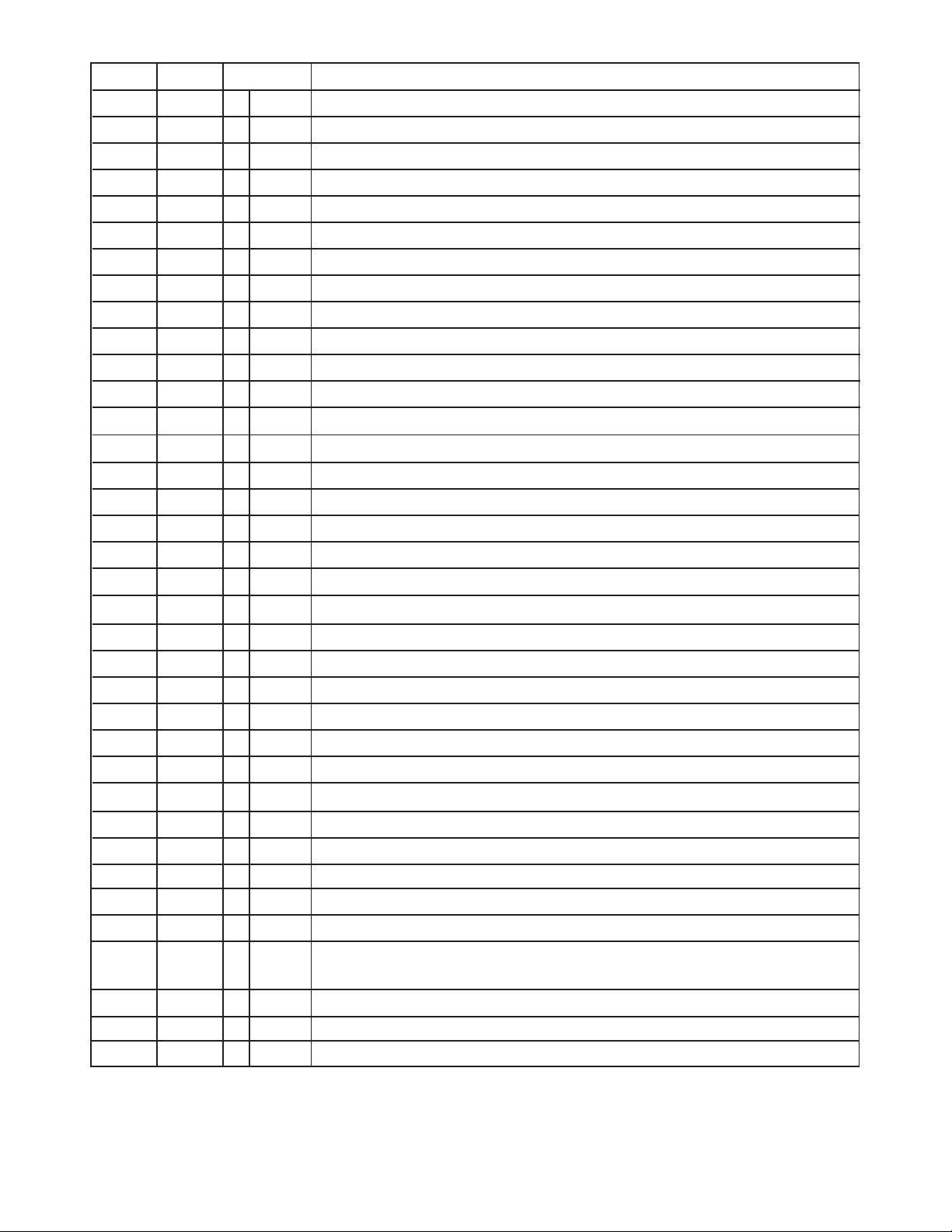

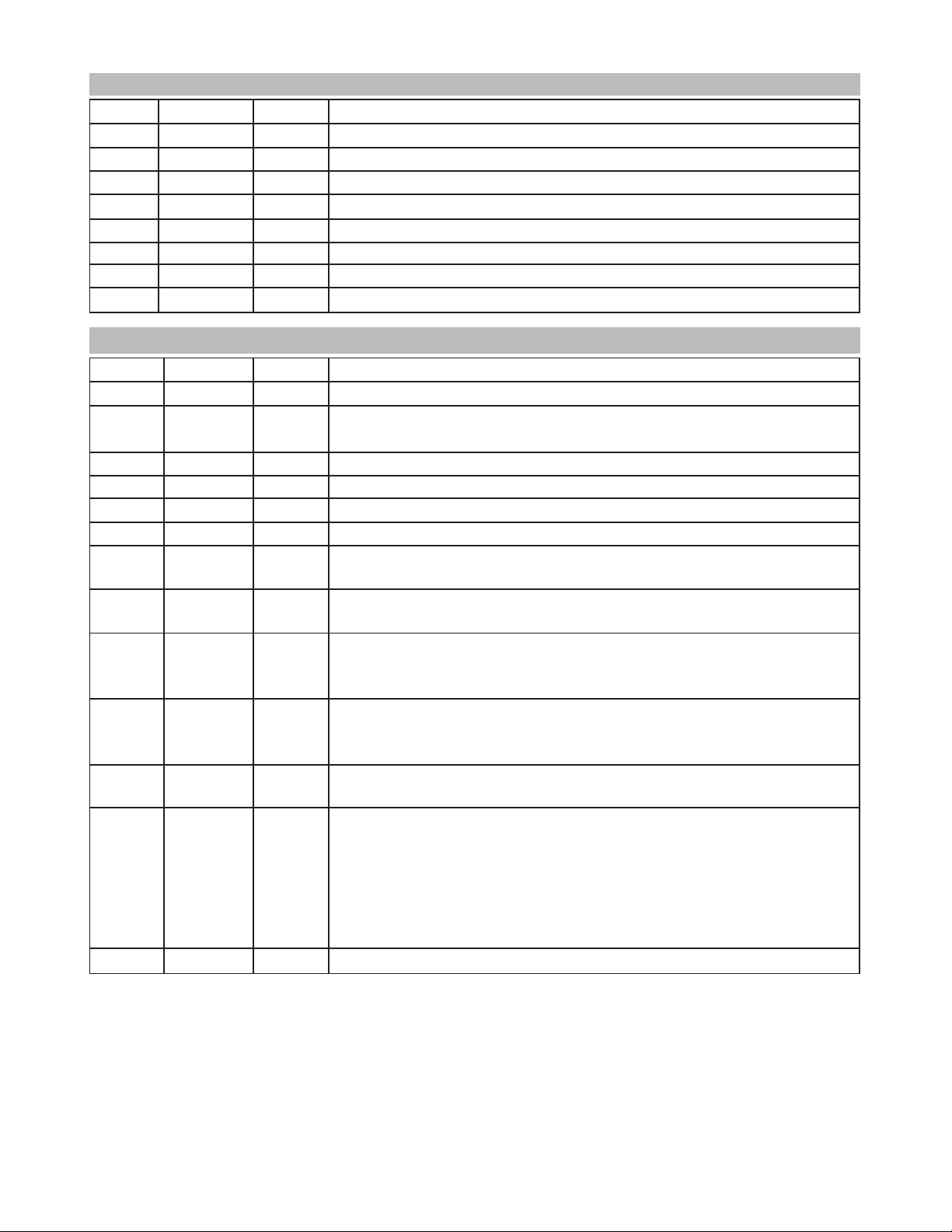

IC209 (RL5E808B)

Block Diagram

41

ATIP

Decoder

DEFS

Subcode

if

CD-DA if

RAM if

CIRC

Encoder

Buffer

Manager

DRAM if

AT API if

Sector

Processor

SysCon if

CD

Encoder

Clock

Synthesizer

Clock

Generator

Motor

Speed

Controller

Subcode

Operator

DSFS

SUBIN

SUBCK

LRCKIN

SDIN

BTCK

C2PO

ESFS

EEFS

WGA TE

HFSW

P ANICIN

EFMNT1-4

E11TP

E11TS

RESMP

ROPC1

ROPC2

VCOIN

CPOUT

PLLCK

XCK

CLKIN

(33.8688MHz)

TON

DEFS

DPLOCK

MPWM

DMCON

MON

FGIN

REVDET

SBRK

WBLIN

A TIPIO

A TIPCK

ASYNC

SRESB

SINT1

SINT0

CS1B

CS0B

SREB

SWEB

SRDY

SA[15:0]

SAD[7:0]

DRSTB

DD[15:0]

DREQ

DIOWB

DIORB

DIORDY

DACKB

DINT

IOCS16B

DA1

DA0

DA2

CS1FXB

CS3FXB

DASPB

RA[8:0]

RA9:RRAS3B

RA10:RRAS2B

RA11:RRAS1B

RRAS0B

RWE0B

RCAS1B:RWE1B

RCAS0B

ROEB

RD[15:0]

DIAGB

SALE

EFM1

EFM2

34.5744MHZ

Pin No. Pin Name Type Description

142 CLKIN IN CLOCK IN : System Clock

146 VCOIN IN VCO IN : Input for VCO

147 CPOUT OUT CHARGE PUMP OUT : Clock Systhesizer Charge Pump output

• Pin Description

Pin No. Pin Name Type Description

133 LRCKIN IN LEFT RIGHT CLOCK IN : Left/Right channel select from CD-DA DSP

134 SDIN IN SERIAL DATA IN : Data input on Decoding from CD-DA DSP

135 BTCK IN BIT CLOCK : Clock input for strobing serial data from CD-DA DSP

136 C2PO IN C2POINTER IN : Serial erasure error data input on Decoding from CD-DA DSP

137 SUBCK OUT SUBCODE CLOCK : Clock output for latch Subcode data from CD-DA DSP on

Decoding.

138 SUBDIN IN SUBCODE DATA IN : Subcode data input from CD-DA DSP

139 DSFS IN

DECODE SUBCODE FRAME SYNC : Subcode frame sync from CD-DA DSP on Decoding.

140 DEFS IN

DECODE EFM SYNC : EFM frame sync input from CD-DA DSP on Decoding.

CD-DA DSP Interface

Pin No. Pin Name Type

Description

152 EFM1 OUT (TS)

EFM 1 : EFM output

153 EFM2 OUT

EFM 2 : EFM peak pulse

154 EFCK OUT

EFM BIT CLOCK : EFM bit clock generated from internal clock CD Encoder

155 EEFMNT1 OUT

EFM NT1 : EFM pit pattern length indicator

156 EEFMNT2 OUT

EFM NT2 : EFM pit pattern length indicator

157 EEFMNT3 OUT

EFM NT3 : EFM pit pattern length indicator

158

EEFMNT4 OUT EFM NT4 : EFM pit pattern length indicator

159

E11TP OUT EFM 11T PIT PATTERN : EFM 11T sample-hold signal of recording (erasing) power on writing

160

E11TS OUT EFM 11T SPACE PATTERN : EFM 11T sample-hold signal of reading power on writing

162

RESMP OUT READ LEVEL SAMPLE : Sample-hold signal of read level on writing

163

ROPC1 OUT

RUNNING OPC1 : Sample-hold signal 1 of reflected ray form’s for running OPC on writing

164

ROPC2 OUT

RUNNING OPC2 : Sample-hold signal 2 of reflected ray form’s for running OPC on writing

166

WGATE OUT

WRITE GATE :

167

HFSW OUT

HIGH FREQUENCY : High frequency modulation switch

168

PANICIN IN (PD)

PANIC IN : Panic input

169

ESFS OUT

ENCODER SUBCODE FRAME SYNC : Subcode frame sync generated from internal clock in CD Encoder

170

EEFS OUT

ENCODER EFM SYNC : EFM Sync generated from internal clock in CD Encoder

171

ASYNC OUT

ATIP SYNC : Detected ATIP sync

172

ATIPIO I/O (PU)

ATIP : ATIP signal output after FSK decoding when use internal FSK ATIP input when use external FSK

173

ATIPCK I/O (PU)

ATIP CLOCK : Clock for ATIP data strobe output when use internal FSK Clock input when use external FSK

174

WBLIN IN

WOBBLE IN : Wobble input (digital signal)

CD Encoder Interface

42

Clock

Motor Interface

Pin No. Pin Name Type Description

1 DPLOCK IN (PD) DSP PLL LOCK : CD-DA DSP PLL locked

2 FGIN IN FG IN : FG, HG (tacho.) pulse input

3 REVDET IN (PD) REVERSE DETECT : Detection to reverse of motor driver

4 DMCON OUT DSP MOTOR CONTROL ON : Servo switch signal between RL5E808 and CD-DA DSP

5 MON OUT MOTOR ON : Motor driver on

6 SBRK OUT SHORT BREAK : Motor brake by a short

8 MPWM OUT(TS) MOTOR PWM : PWM pulse output (L, H, Z)

176 TON I/O (PD) TRACKING SERVO ON : Flag of tracking servo on

Pin No. Pin Name Type Description

52 DASPB I/O (PU) DRIVE ACTIVE/SLAVE PRESENT : Slave device present

53 CS3FXB, IN (PU) CHIP SELECT 1FX, 3FX : ATA chip select

54 CS1FXB

55, 59, 56

DA [2 : 0] IN (PU) ADDRESS :

Address signals

58

DIAGB I/O (PU) DIAGNOSTIC : Diagnostic ATA drive

60

IOCS16B OUT (OD) IOCS16 : ATA 16 bit I/O

61

DINT OUT (TS) DRIVE INTERRUPT REQUEST : Device interrupt

63

DACKB/

IN (PU)

DATA ACKNOWLEDGE/DMA REQUEST : ATAPI DMA acknowledge

HREQ

DMA request in case of connection to SCSI DMA

64

DIORDY/

OUT (TS)

I/O READY : I/O channel ready (DSTROBE in case of Ultra DMA)

DSTROBE

DIORB/

DRIVE I/O READ/DMA WRITE STROBE : ATAPI drive I/O read

65

HWRB/ I/O (PU) DMA write strobe in case of connection to SCSI DMA

HSTROBE

(HSTROBE in case of Ultra DMA)

DIOWB/

DRIVE I/O WRITE/DMA READ STROBE : ATAPI drive I/O write

66 HRDB/

I/O (PU) DMA read strobe in case of connection to SCSI

STOP (STOP in case of Ultra DMA)

67 DREQ/ OUT (TS) DATA REQUEST/DMA ACKNOWLEDGE : ATAPI DMA request

HACKB

DMA acknowledge in case of connection to SCSI DMA

69, 70, 72,

73, 74, 75,

77, 78, 79,

DD [15 : 0]

I/O (PU) DATA : Data signals

80, 82, 83,

84, 85, 87,

88

89 DRSTB

IN (PU) ATA RESET : ATA drive reset

ATAPI Local Bus Interface

43

Pin No. Pin Name Type Description

12~19 SA [15 :8] IN

ADDRESS :

Use these pins when access through 64Kbyte buffer memory window.

ADDRESS :

20~27 SA [7 : 0] IN

Use these pins in case of connection with a microprocessor which has separated

address and data bus.

29~32 SAD [7 : 0] I/O (PU)

ADDRESS AND DATA : Address and data are multiplexed in a same pin.

34~37

In the case of input/output only data, fix SALE to GND.

These signals are Hi-Z when this LSI is reset.

ADDRESS LATCH ENABLE :

39

SALE IN

Use this pin in case of connection with a microprocessor which has multiplexed

address and data bus.

READY : Data ready

40 SRDY OUT Selectable use/no use by setting internal registers.

(PU, TS)

In the case of access internal registers or buffer memory, this signal is asserted after

fixing driven data.

In case of no access, this pin is Hi-Z.

WRITE ENABLE/DATA READ WRITE STATUS : Write enable/data read write

status input for read.

41 SWEB/RWB IN

In the case of CPUTYPE = Open (: 86 type), this pin is write enable.

In the case of CPUTYPE = GND (: 68 type), this pin is read/write status.

READ ENABLE/DATA STROBE : Read enable /data strobe input for read

42 SREB/DSB IN In the case of CPUTYPE = Open (: 86 type), this pin is read enable.

In the case of CPUTYPE = GND (: 68 type), this pin is data strobe.

43 CS1B IN CHIP SELECT 1 : Enable to access buffer memories.

44 CS0B IN CHIP SELECT 0 : Enable to access internal registers.

46 CPUTYPE IN (PU) CPU TYPE SELECT : Microprocessor type select

Open : 86 type

GND : 68 type

SYSTEM INTERRUPT REQUEST 0,1 :

47, 48 SINT1,

I/O (PU)

Possible output pin whether SINT1 or SINT0 by using internal registers at each

SINT0 interrupt groups (8bit unit)

SYSTEM RESET : Internal state machines are reset and all registers are set to default.

49 SRESB IN (PU) More than 1CLKIN active time is needed when assertion or negation of SRESB,

because it is through a de-glitch circuit.

System Controller Interface

44

Pin No. Pin Name Type Description

92, 93, 94,

95, 97, 98,

RA [11 : 0] OUT (TS) RAM ADDRESS : Address for DRAM

99, 100, 102,

These pins are multiplexed address output.

103, 104, 105

107 ROEB OUT (TS) OUTPUT ENABLE : OE for DRAM

108 RRAS0B OUT (TS) ROW ADDRESS STROBE 0 : RAS for DRAM

109 RCAS1B/ OUT (TS) COLUMN ADDRESS STROBE 1/WRITE ENABLE 1 : CAS1/WE1 for DRAM

RWE1B In case of 16 bit data bus is selected, set CAS decode or WE decode by setting

internal registers.

110 RWE0B OUT (TS)

WRITE ENABLE 0 : WE 0 for DRAM

Write strobe in case of 16 bit data bus is selected.

111 RCAS0B OUT (TS) COLUMN ADDRESS STROBE 0 : CAS0 for DRAM

In case of 16 bit bus size is selected, this pin is used by a strobe.

113, 114, 115,

116, 118, 119,

120, 121, 123,

RD [15 : 0] I/O (PU) RAM DATA : Data for DRAM

124, 125, 126,

Possible to set bus size (16 bit/8bit) by setting internal registers.

128, 129, 130,

131

Buffer Memory Interface

45

Pin No. Pin Name Type

Description

9 MONIT0 OUT

Monitor 0 : Monitor pin

This pin is as follows by setting register 0X3E.

Monitor

IN Input Pin

OUT Output Pin

I/O Input/Output Pin

IN (PU) Input Pin with Internal Pullup Resister

IN (PD) Input Pin with Internal Pulldown Resister

I/O (PU) : Input/Output Pin with Internal Pullup Resister

I/O (PD) : Input/Output Pin with Internal Pulldown Resister

OUT (TS) :

Three State Output Pin

OUT

(OD) : Open Drain Output Pin

OUT (PU, TS) :

Three State Output Pin with Internal Pullup Resister

Monitor Register (0X3E)

bit3..0 Monitor 0 Description

0 Reserved Reserved

1 BSYNC BSYNC

2 PROTECT PROTECT

3 READSTART READSTART

4 IDSFS Internal Subcode Frame Sync : Sync after operation of insertion

5 ACRCOK ACRCOK

6 FGLOCK FG servo lock

7 WBLOCK WBL servo lock

8 REFE PLL phase comparator reference output

9 VIRT PLL phase comparator virtual output

A FSCK FSCK

B AXREF AX servo reference output

C

DREQ ATAPI DREQ

D

COD ATAPI COD

E

BSY ATAPI BSY

F

I/O ATAPI I/O

The source of Monitor 0 is set by setting registers. as bellow.

Monitor 0 Sel (bit-0) [R/W]

Pin No. Pin Name Description

33, 45, 62, 76, 86, 96,

DVCC5V

5V VCC : +5V Pin. Connect to digital +5V

106, 117, 132, 165

10, 50, 90, 141, 144 DVCC3V 3V VCC : +3.3V Pin. Connect to digital +3.3V

145 AVCC3V 3V VCC : +3.3V Pin. Connect to analong +3.3V for PLL

148

AGND GND Pin : Connect to analong GND for PLL

7, 11, 28, 38, 51, 57, 68,

71, 81, 91, 101, 112, 122,

DGND GND Pin : Connect to digital GND

127, 143, 149, 161, 175

Power Supply

46

Loading...

Loading...