Internal Use Only

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

LED TV

SERVICE MANUAL

CHASSIS : LB42B

MODEL : 65LB7200/720T/729Y

65LB720/720T/729Y-TA

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

Printed in KoreaP/NO : MFL6798520 (1404-REV00)

CONTENTS

CONTENTS .............................................................................................. 2

SAFETY PRECAUTIONS ........................................................................ 3

SERVICING PRECAUTIONS .................................................................... 4

SPECIFICATION ....................................................................................... 6

ADJUSTMENT INSTRUCTION .............................................................. 12

BLOCK DIAGRAM ................................................................................. 20

EXPLODED VIEW .................................................................................. 21

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

Only for training and service purposes

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental sh orts of the cir cui try that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

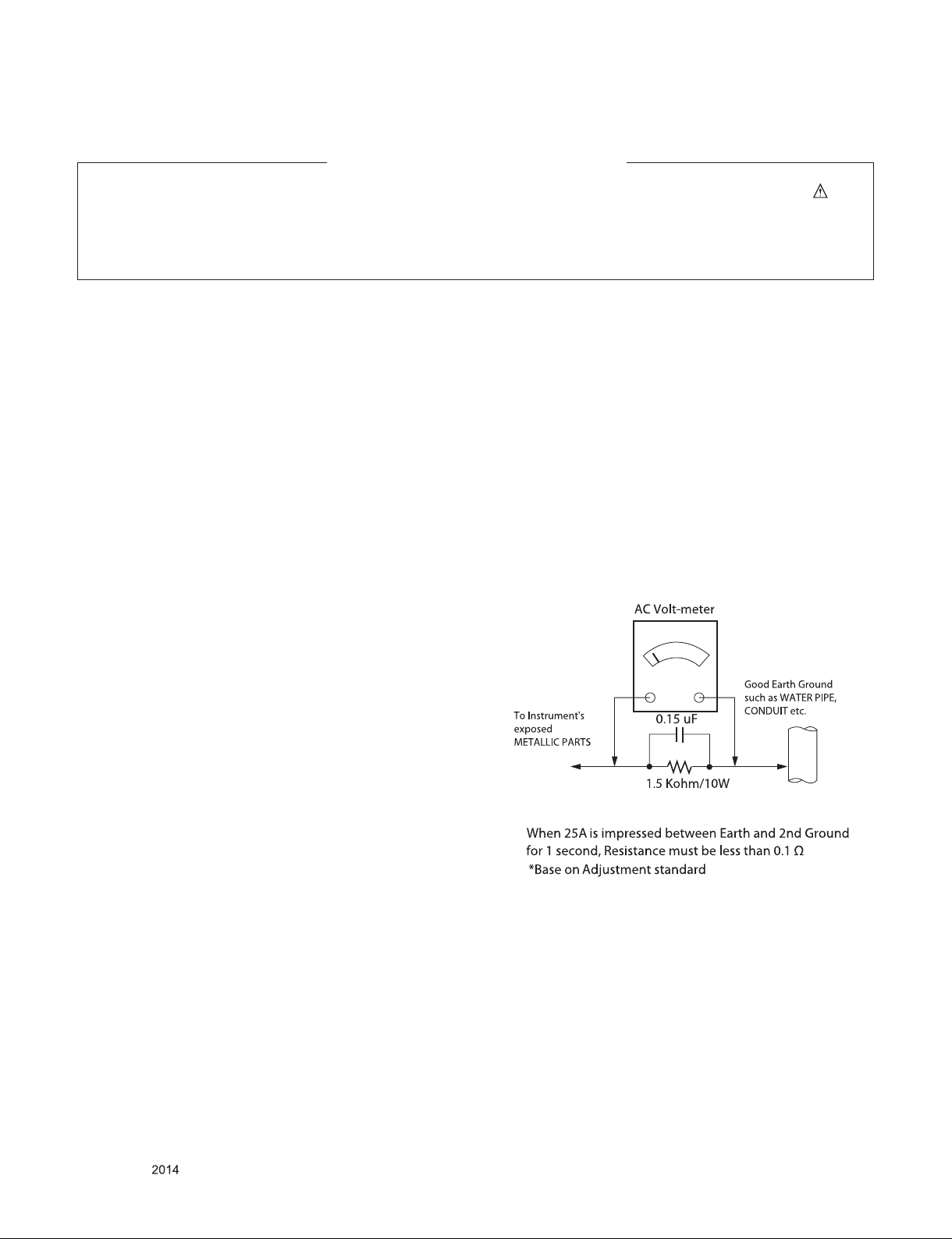

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exposed metallic part. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

Only for training and service purposes

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

SERVICING PRECAUTIONS

CAUTION: Before servicing receivers covered by this service

manual and its supplements and addenda, read and follow the

SAFETY PRECAUTIONS on page 3 of this publication.

NOTE: If unforeseen circumstances create conict between the

following servicing precautions and any of the safety precautions

on page 3 of this publication, always follow the safety precautions. Remember: Safety First.

General Servicing Precautions

1. Always unplug the receiver AC power cord from the AC power

source before;

a. Removing or reinstalling any component, circuit board

module or any other receiver assembly.

b. Disconnecting or reconnecting any receiver electrical plug

or other electrical connection.

c. Connecting a test substitute in parallel with an electrolytic

capacitor in the receiver.

CAUTION: A wrong part substitution or incorrect polarity

installation of electrolytic capacitors may result in an explosion hazard.

2. Test high voltage only by measuring it with an appropriate

high voltage meter or other voltage measuring device (DVM,

FETVOM, etc) equipped with a suitable high voltage probe.

Do not test high voltage by "drawing an arc".

3. Do not spray chemicals on or near this receiver or any of its

assemblies.

4. Unless specied otherwise in this service manual, clean

electrical contacts only by applying the following mixture to the

contacts with a pipe cleaner, cotton-tipped stick or comparable

non-abrasive applicator; 10 % (by volume) Acetone and 90 %

(by volume) isopropyl alcohol (90 % - 99 % strength)

CAUTION: This is a ammable mixture.

Unless specied otherwise in this service manual, lubrication

of contacts in not required.

5. Do not defeat any plug/socket B+ voltage interlocks with which

receivers covered by this service manual might be equipped.

6. Do not apply AC power to this instrument and/or any of its

electrical assemblies unless all solid-state device heat sinks

are correctly installed.

7. Always connect the test receiver ground lead to the receiver

chassis ground before connecting the test receiver positive

lead.

Always remove the test receiver ground lead last.

8. Use with this receiver only the test xtures specied in this

service manual.

CAUTION: Do not connect the test xture ground strap to any

heat sink in this receiver.

Electrostatically Sensitive (ES) Devices

Some semiconductor (solid-state) devices can be damaged easily by static electricity. Such components commonly are called

Electrostatically Sensitive (ES) Devices. Examples of typical ES

devices are integrated circuits and some eld-effect transistors

and semiconductor “chip” components. The following techniques

should be used to help reduce the incidence of component damage caused by static by static electricity.

1. Immediately before handling any semiconductor component or

semiconductor-equipped assembly, drain off any electrostatic

charge on your body by touching a known earth ground. Alternatively, obtain and wear a commercially available discharging wrist strap device, which should be removed to prevent

potential shock reasons prior to applying power to the unit

under test.

2. After removing an electrical assembly equipped with ES

devices, place the assembly on a conductive surface such as

aluminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder

ES devices.

4. Use only an anti-static type solder removal device. Some sol-

der removal devices not classied as “anti-static” can generate

electrical charges sufcient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate

electrical charges sufcient to damage ES devices.

6. Do not remove a replacement ES device from its protective

package until immediately before you are ready to install it.

(Most replacement ES devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or

comparable conductive material).

7. Immediately before removing the protective material from the

leads of a replacement ES device, touch the protective material to the chassis or circuit assembly into which the device will

be installed.

CAUTION: Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion such as the

brushing together of your clothes fabric or the lifting of your

foot from a carpeted oor can generate static electricity sufcient to damage an ES device.)

General Soldering Guidelines

1. Use a grounded-tip, low-wattage soldering iron and appropriate tip size and shape that will maintain tip temperature within

the range or 500 °F to 600 °F.

2. Use an appropriate gauge of RMA resin-core solder composed

of 60 parts tin/40 parts lead.

3. Keep the soldering iron tip clean and well tinned.

4. Thoroughly clean the surfaces to be soldered. Use a mall wirebristle (0.5 inch, or 1.25 cm) brush with a metal handle.

Do not use freon-propelled spray-on cleaners.

5. Use the following unsoldering technique

a. Allow the soldering iron tip to reach normal temperature.

(500 °F to 600 °F)

b. Heat the component lead until the solder melts.

c. Quickly draw the melted solder with an anti-static, suction-

type solder removal device or with solder braid.

CAUTION: Work quickly to avoid overheating the circuit

board printed foil.

6. Use the following soldering technique.

a. Allow the soldering iron tip to reach a normal temperature

(500 °F to 600 °F)

b. First, hold the soldering iron tip and solder the strand

against the component lead until the solder melts.

c. Quickly move the soldering iron tip to the junction of the

component lead and the printed circuit foil, and hold it there

only until the solder ows onto and around both the component lead and the foil.

CAUTION: Work quickly to avoid overheating the circuit

board printed foil.

d. Closely inspect the solder area and remove any excess or

splashed solder with a small wire-bristle brush.

Only for training and service purposes

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

IC Remove/Replacement

Some chassis circuit boards have slotted holes (oblong) through

which the IC leads are inserted and then bent at against the circuit foil. When holes are the slotted type, the following technique

should be used to remove and replace the IC. When working with

boards using the familiar round hole, use the standard technique

as outlined in paragraphs 5 and 6 above.

Removal

1. Desolder and straighten each IC lead in one operation by

gently prying up on the lead with the soldering iron tip as the

solder melts.

2. Draw away the melted solder with an anti-static suction-type

solder removal device (or with solder braid) before removing

the IC.

Replacement

1. Carefully insert the replacement IC in the circuit board.

2. Carefully bend each IC lead against the circuit foil pad and

solder it.

3. Clean the soldered areas with a small wire-bristle brush.

(It is not necessary to reapply acrylic coating to the areas).

"Small-Signal" Discrete Transistor

Removal/Replacement

1. Remove the defective transistor by clipping its leads as close

as possible to the component body.

2. Bend into a "U" shape the end of each of three leads remaining on the circuit board.

3. Bend into a "U" shape the replacement transistor leads.

4. Connect the replacement transistor leads to the corresponding

leads extending from the circuit board and crimp the "U" with

long nose pliers to insure metal to metal contact then solder

each connection.

Power Output, Transistor Device

Removal/Replacement

1. Heat and remove all solder from around the transistor leads.

2. Remove the heat sink mounting screw (if so equipped).

3. Carefully remove the transistor from the heat sink of the circuit

board.

4. Insert new transistor in the circuit board.

5. Solder each transistor lead, and clip off excess lead.

6. Replace heat sink.

Diode Removal/Replacement

1. Remove defective diode by clipping its leads as close as possible to diode body.

2. Bend the two remaining leads perpendicular y to the circuit

board.

3. Observing diode polarity, wrap each lead of the new diode

around the corresponding lead on the circuit board.

4. Securely crimp each connection and solder it.

5. Inspect (on the circuit board copper side) the solder joints of

the two "original" leads. If they are not shiny, reheat them and

if necessary, apply additional solder.

3. Solder the connections.

CAUTION: Maintain original spacing between the replaced

component and adjacent components and the circuit board to

prevent excessive component temperatures.

Circuit Board Foil Repair

Excessive heat applied to the copper foil of any printed circuit

board will weaken the adhesive that bonds the foil to the circuit

board causing the foil to separate from or "lift-off" the board. The

following guidelines and procedures should be followed whenever this condition is encountered.

At IC Connections

To repair a defective copper pattern at IC connections use the

following procedure to install a jumper wire on the copper pattern

side of the circuit board. (Use this technique only on IC connections).

1. Carefully remove the damaged copper pattern with a sharp

knife. (Remove only as much copper as absolutely necessary).

2. carefully scratch away the solder resist and acrylic coating (if

used) from the end of the remaining copper pattern.

3. Bend a small "U" in one end of a small gauge jumper wire and

carefully crimp it around the IC pin. Solder the IC connection.

4. Route the jumper wire along the path of the out-away copper

pattern and let it overlap the previously scraped end of the

good copper pattern. Solder the overlapped area and clip off

any excess jumper wire.

At Other Connections

Use the following technique to repair the defective copper pattern

at connections other than IC Pins. This technique involves the

installation of a jumper wire on the component side of the circuit

board.

1. Remove the defective copper pattern with a sharp knife.

Remove at least 1/4 inch of copper, to ensure that a hazardous

condition will not exist if the jumper wire opens.

2. Trace along the copper pattern from both sides of the pattern

break and locate the nearest component that is directly connected to the affected copper pattern.

3. Connect insulated 20-gauge jumper wire from the lead of the

nearest component on one side of the pattern break to the

lead of the nearest component on the other side.

Carefully crimp and solder the connections.

CAUTION: Be sure the insulated jumper wire is dressed so the

it does not touch components or sharp edges.

Fuse and Conventional Resistor

Removal/Replacement

1. Clip each fuse or resistor lead at top of the circuit board hollow

stake.

2. Securely crimp the leads of replacement component around

notch at stake top.

Only for training and service purposes

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

.

1. Application range

This specification is applied to the LED TV used LB42B

chassis.

2. Requirement for Test

Each part is tested as below without special appointment.

(1) Temperature: 25 °C ± 5 °C(77 °F ± 9 °F), CST: 40 °C ± 5 °C

(2) Relative Humidity: 65 % ± 10 %

(3) Power Voltage

: Standard input voltage (AC 100-240 V~, 50/60 Hz)

* Standard Voltage of each products is marked by models.

(4) Specification and performance of each parts are followed

ea ch dra wing and spe cificat ion by part n umber in

accordance with BOM.

(5) The receiver must be operated for about 20 minutes prior

to the adjustment.

3. Test method

(1) Performance: LGE TV test method followed

(2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

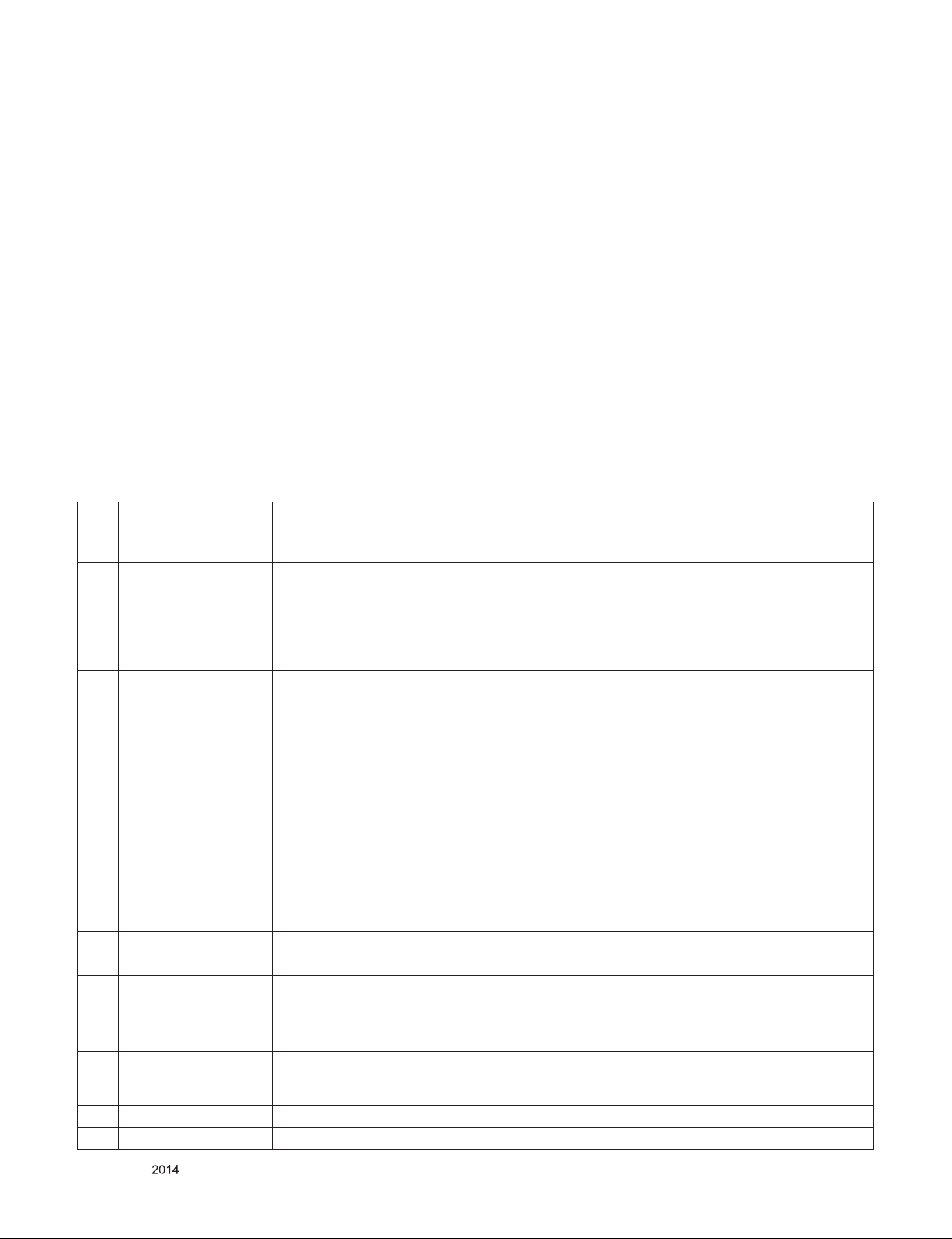

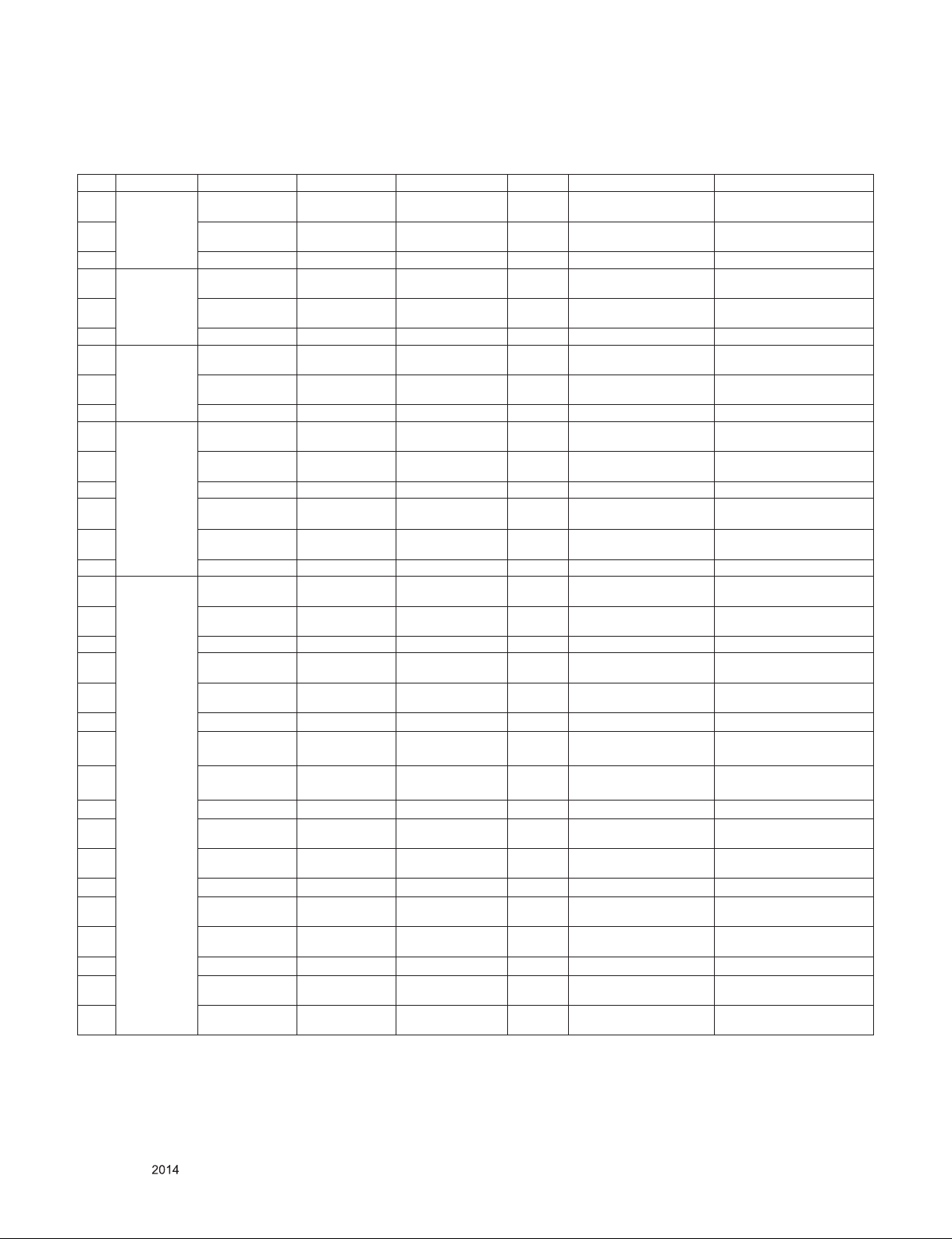

4. Model General Specification

No. Item Specication Remarks

1 Market

2 Television system

3 Channel Storage ATV / DTV - 1500EA

4 Receiving system

5 Video Input RCA PAL, SECAM, NTSC 4 System : PAL, SECAM, NTSC, PAL60

6 Component Input Y/Pb/Pr

7 Head phone out

8 HDMI Input HDMI1-DTV, HDMI2-DTV, HDMI3-DTV

9 Audio Input (3EA)

10 SDPIF out (1EA) SPDIF out

11 USB Input For My Media(Movie/Photo/Music List) or For SVC

Asia, Oceania, Africa, Middle East

(PAL/DVB Market)

1) Digital TV

- DVB-T(*DVB-T/T2)

2) Analogue TV

PAL B/B, PAL B/G, PAL D/K, PAL-I,

SECAM B/G, SECAM D/K, NTSC-M

Analog : Upper Heterodyne

Digital : COFDM(DVB-T) Only DVB-T Model

Digital : COFDM(DVB-T/T2) Only DVB-T2 Model

Antenna, AV1, Component, HDMI1, HDMI2,

HDMI3, USB1, USB2, USB3

DVI Audio

Component/AV2

AV1

► DVB-T

- Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32

- Modulation : Code Rate

QPSK : 1/2, 2/3, 3/4, 5/6, 7/8

16-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

64-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

► DVB-T2 (Model : T2 only Model)

- Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32, 1/128, 19/128, 19/256,

- Modulation : Code Rate

QPSK : 1/2, 2/5, 2/3, 3/4, 5/6

16-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

64-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

256-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

PC(HDMI Ver. 1.4)

Support HDCP

L/R Input.

Only for training and service purposes

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

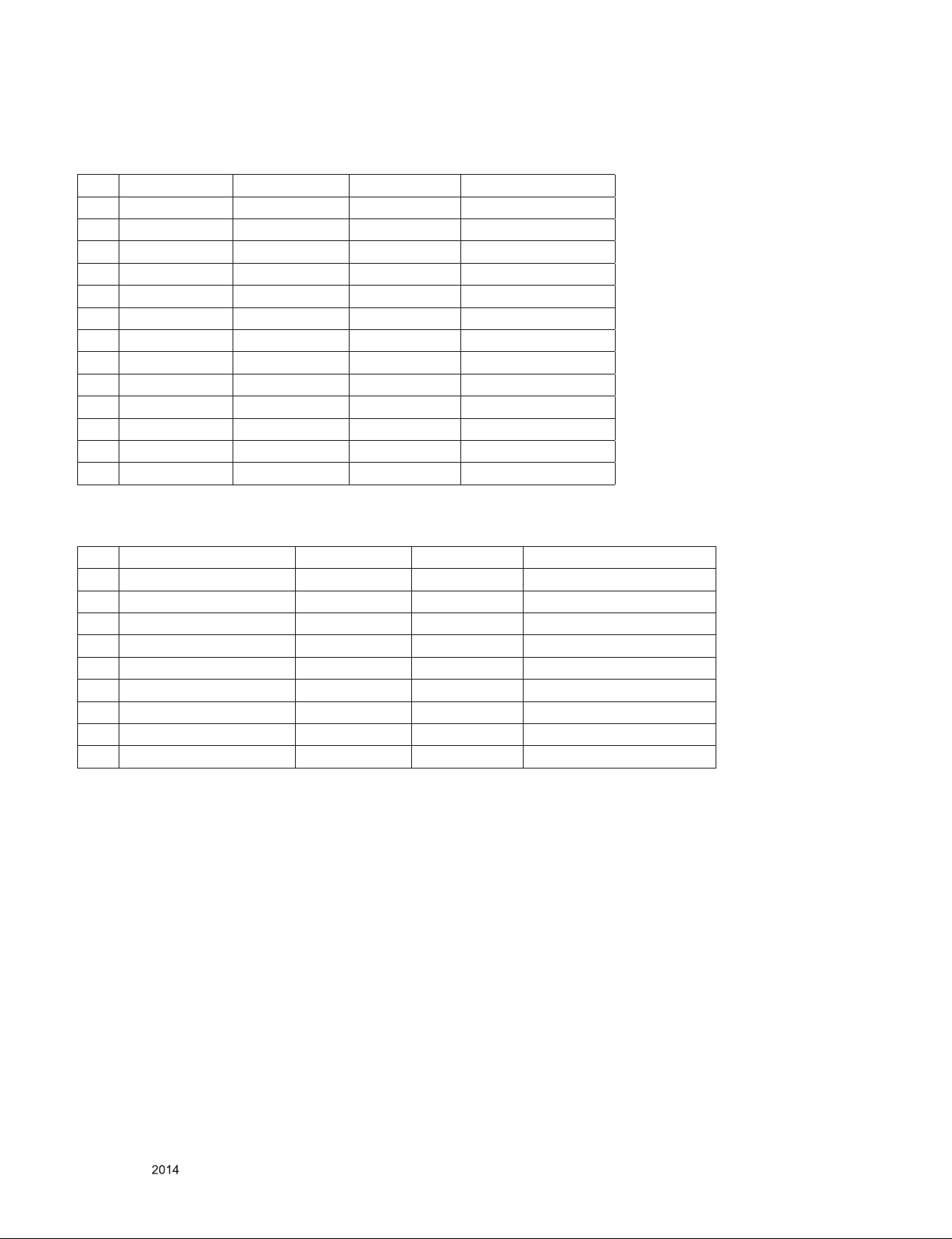

5. Component Video Input (Y, Pb, Pr)

No.

1. 720×480 15.73 60.00 SDTV, DVD 480i

2. 720×480 15.63 59.94 SDTV, DVD 480i

3. 720×480 31.47 59.94 480p

4. 720×480 31.50 60.00 480p

5. 720×576 15.625 50.00 SDTV, DVD 625 Line

6. 720×576 31.25 50.00 HDTV 576p

7. 1280×720 45.00 50.00 HDTV 720p

8. 1280×720 44.96 59.94 HDTV 720p

9. 1280×720 45.00 60.00 HDTV 720p

10. 1920×1080 31.25 50.00 HDTV 1080i

11. 1920×1080 33.75 60.00 HDTV 1080i

12. 1920×1080 33.72 59.94 HDTV 1080i

13. 1920×1080 56.250 50 HDTV 1080p

14. 1920×1080 67.5 60 HDTV 1080p

Resolution H-freq(kHz) V-freq(Hz) Pixel clock

Specication

Only for training and service purposes

- 7 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

6. HDMI Input

6.1. DTV mode

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz)

1. 640*480 31.469 / 31.5 59.94/60 SDTV 480P

2. 720*480 31.469 / 31.5 59.94 / 60 SDTV 480P

3. 720*576 31.25 50 SDTV 576P

4. 720*576 15.625 50 SDTV 576I

5. 1280*720 37.500 50 HDTV 720P

6. 1280*720 44.96 / 45 59.94 / 60 HDTV 720P

7. 1920*1080 33.72 / 33.75 59.94 / 60 HDTV 1080I

8. 1920*1080 28.125 50.00 HDTV 1080I

9. 1920*1080 26.97 / 27 23.97 / 24 HDTV 1080P

10. 1920*1080 28.125 25 HDTV 1080P

11. 1920*1080 33.716 / 33.75 29.976 / 30.00 HDTV 1080P

12. 1920*1080 56.250 50 HDTV 1080P

13. 1920*1080 67.43 / 67.5 59.94 / 60 HDTV 1080P

6.2. PC mode

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz)

1 640 x 350 @70Hz 31.468 70.09 EGA

2 720 x 400 @70Hz 31.469 70.08 DOS

3 640 x 480 @60Hz 31.469 59.94 VESA(VGA)

4 800 x 600 @60Hz 37.879 60.31 VESA(SVGA)

5 1024 x 768 @60Hz 48.363 60.00 VESA(XGA)

6 1152 x 864 @60Hz 54.348 60.053 VESA

7 1280 x 1024 @60Hz 63.981 60.020 VESA(SXGA)

8 1360 x 768 @60Hz 47.712 60.015 VESA(WXGA)

9 1920 x 1080 @60Hz 67.5 60.00 WUXGA(Reduced Blanking)

Only for training and service purposes

- 8 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

7. 3D Mode

7.1. HDMI 1.4b (3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) VIC 3D input proposed mode Proposed

1

640*480

2 62.938/63 59.94/ 60 50.35/50.4 1

3 31.469 / 31.5 59.94/ 60 50.35/50.4 1 Side-by-side(Full) (SDTV 480P)

4

720*480

5 62.938/63 59.94 / 60 54/54.06 2,3

6 31.469 / 31.5 59.94 / 60 54/54.06 2,3 Side-by-side(Full) (SDTV 480P)

7

720*576

8 62.5 50 54 17,18

9 31.25 50 54 17,18 Side-by-side(Full) (SDTV 576P)

10

11 75 50 148.5 19

12 37.500 50 148.5 19 Side-by-side(Full) (HDTV 720P)

1280*720

13 44.96 / 45 59.94 / 60 74.18/74.25 4

14 89.91/90 59.94 / 60 148.35/148.5 4

15 44.96 / 45 59.94 / 60 148.35/148.5 4 Side-by-side(Full) (HDTV 720P)

16

17 67.432 / 67.50 59.94 / 60 148.35/148.5 5

18 33.72 / 33.75 59.94 / 60 148.35/148.5 5 Side-by-side(Full) (HDTV 1080I)

19 28.125 50.00 74.25 20

20 56.25 50.00 148.5 20

21 28.125 50.00 148.5 20 Side-by-side(Full) (HDTV 1080I)

22 26.97 / 27 23.97 / 24 74.18/74.25 32

23 43.94/54 23.97 / 24 148.35/148.5 32

1920*1080

24 26.97 / 27 23.97 / 24 148.35/148.5 32 Side-by-side(Full) (HDTV 1080P)

25 28.125 25 74.25 33

26 56.24 25 148.5 33

27 28.12 25 148.5 33 Side-by-side(Full) (HDTV 1080P)

28 33.716 / 33.75 29.976 / 30.00 74.18/74.25 34

29 67.432 / 67.5 29.976 / 30.00 148.35/148.5 34

30 33.716 / 33.75 29.976 / 30.00 148.35/148.5 34 Side-by-side(Full) (HDTV 1080P)

31 56.250 50 148.5 31

32 67.43 / 67.5 59.94 / 60 148.35/148.50 16

31.469 / 31.5 59.94/ 60 25.125 1

31.469 / 31.5 59.94 / 60 27.00/27.03 2,3

31.25 50 27 17,18

37.5 50 74.25 19

33.72 / 33.75 59.94 / 60 74.18/74.25 5

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Field alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Field alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

(SDTV 480P)

Secondary(SDTV 576P)

Secondary(SDTV 576P)

Secondary(SDTV 576P)

(SDTV 576P)

Primary(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

(HDTV 720P)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

Primary(HDTV 1080I)

(HDTV 1080I)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

Primary(HDTV 1080I)

(HDTV 1080I)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

(HDTV 1080P)

Secondary(HDTV 1080P)

Secondary(HDTV 1080P)

Secondary(HDTV 1080P)

(HDTV 1080P)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

Primary(HDTV 1080P)

(HDTV 1080P)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

Only for training and service purposes

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

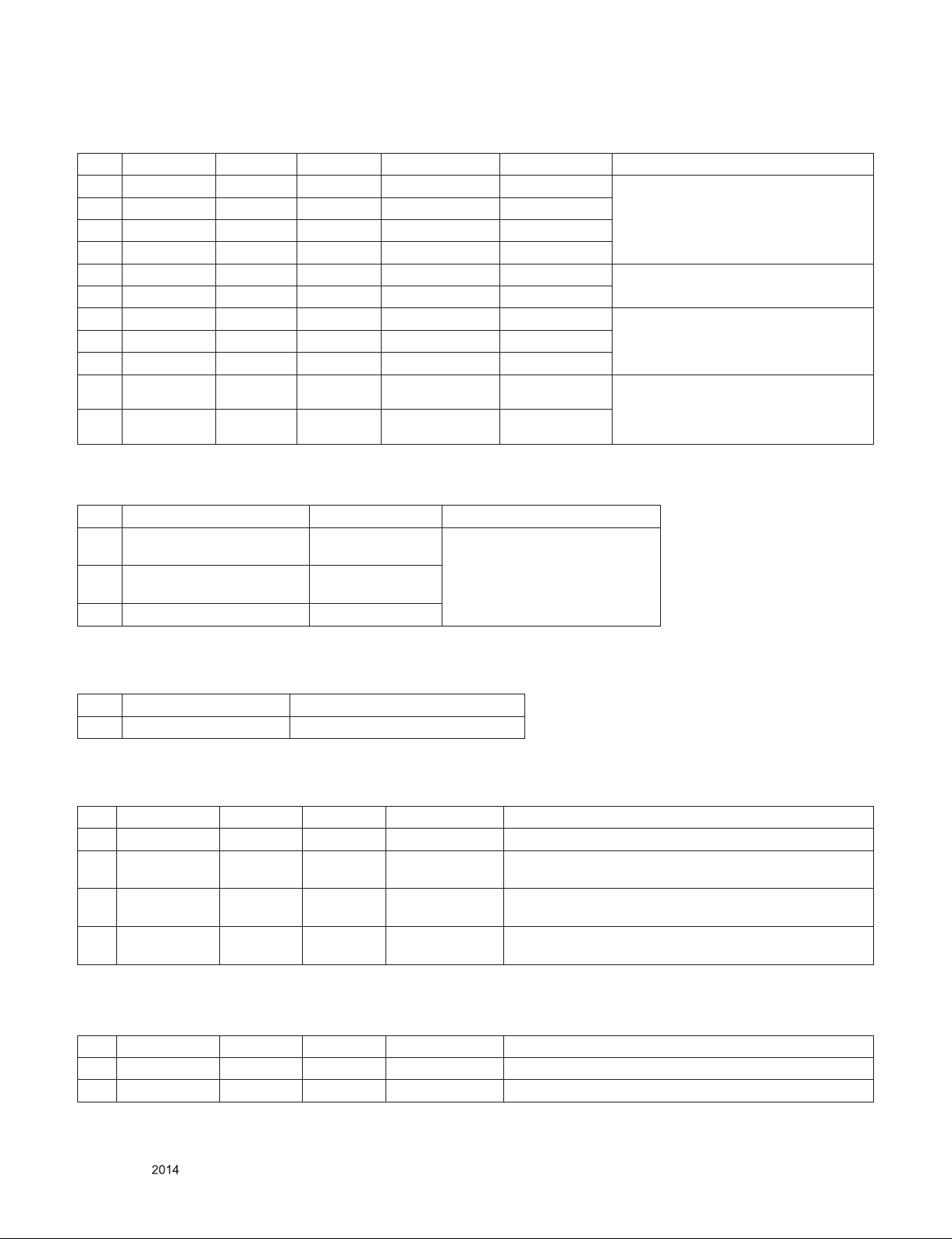

7.2. HDMI Input(1.3)

No. Resolution H-freq(kHz) V-freq.(kHz) Pixel clock(MHz) Proposed 3D input proposed mode

1 720*480 31.5 60 27.03 SDTV 480P

2 720*576 31.25 50 27 SDTV 576P

3 1280*720 45.00 60.00 74.25 HDTV 720P

4 1280*720 37.500 50 74.25 HDTV 720P

5 1920*1080 33.75 60.00 74.25 HDTV 1080I

6 1920*1080 28.125 50.00 74.25 HDTV 1080I

7 1920*1080 27.00 24.00 74.25 HDTV 1080P

8 1920*1080 28.12 25 74.25 HDTV 1080P

9 1920*1080 33.75 30.00 74.25 HDTV 1080P

10 1920*1080 67.50 60.00 148.5 HDTV 1080P

11 1920*1080 56.250 50 148.5 HDTV 1080P

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board, Frame Sequential,

Row Interleaving, Column Interleaving

2D to 3D, Side by Side(Half), Top & Bottom

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board, Row Interleaving,

Column Interleaving

2D to 3D, Side by Side(Half), Top &

Bottom, Checker Board, Single Frame

Sequential, Row Interleaving, Column

Interleaving

7.3. RF Input(3D supported mode manually)

No. Resolution Proposed 3D input proposed mode

1 HD

2 SD

3 SD (ATV : CVBS / SCART) -

1080I

720P

576P

576I

2D to 3D

Side by Side(Half)

Top & Bottom

7.4. RF Input (3D supported mode automatically)

No. Signal 3D input proposed mode

1 Frame Compatible Side by Side(Half), Top & Bottom

7.5. USB, DLNA (Movie) Input (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 Under 704x480 - - - 2D to 3D

Over 704x480

2

interlaced

Over 704x480

3

progressive

Over 704x480

4

progressive

- - - 2D to 3D, Side by Side(Half), Top & Bottom

- 50 / 60 -

- others -

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board,

Row Interleaving, Column Interleaving, Frame Sequential

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board,

Row Interleaving, Column Interleaving

7.6. USB, DLNA (Photo) Input (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 Under 320x240 - - - 2D to 3D

2 Over 320x240 - - - 2D to 3D, Side by Side(Half), Top & Bottom

Only for training and service purposes

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

* USB, DNLA Input (3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 1080P 33.75 30 -

Side by Side(Half), Top & Bottom, Checker Board,

MPO(Photo), JPS(Photo)

7.7. HDMI-PC Input (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1024*768 48.36 60 65

2 1360*768 47.71 60 85.5

3 1920*1080 67.500 60 148.50

4 Others - - -

2D to 3D, Side by Side(half)

Top & Bottom

2D to 3D, Side by Side(half), Top

& Bottom, Checker Board, Single

Frame Sequential, Row Interleaving,

Column Interleaving

2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 768P

HDTV 1080P

640*350

720*400

640*480

800*600

1152*864

7.8. Component Input(3D) (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock Proposed 3D input proposed mode

1 1280*720 45.00 60.00 74.25 HDTV 720P

2 1280*720 37.500 50 74.25 HDTV 720P

3 1920*1080 33.75 60.00 74.25 HDTV 1080I

4 1920*1080 28.125 50.00 74.25 HDTV 1080I

5 1920*1080 27.00 24.00 74.25 HDTV 1080P

6 1920*1080 28.12 25 74.25 HDTV 1080P

7 1920*1080 33.75 30.00 74.25 HDTV 1080P

8 1920*1080 67.50 60.00 148.5 HDTV 1080P

9 1920*1080 56.250 50 148.5 HDTV 1080P

10 Others - - - SDTV

2D to 3D, Side by Side(Half), Top & Bottom

7.9. Miracast, Widi (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 1024X768p - 30 / 60 -

2D to 3D, Side by Side(Half), Top & Bottom2. 1280x720p - 30 / 60 -

3 1920X1080p 30 / 60

4 Others - 2D to 3D

7.10. 3D Input mode

No. Side by Side Top & Bottom Checker board

1

ii.

Only for training and service purposes

iii.

iv.

- 11 -

Single Frame

Sequential

Frame

Packing

v.

vi.

2D to 3D

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

ADJUSTMENT INSTRUCTION

1. Application Range

This specification sheet is applied to all of the LED TV with

LB42B chassis.

2. Designation

(1) Because this is not a hot chassis, it is not necessary to

use an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order.

(3) The adjustment must be performed in the circumstance of

25 °C ± 5 °C of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep AC 100-240

V~, 50/60 Hz.

(5) The receiver must be operated for about 5 minutes prior to

the adjustment when module is in the circumstance of over

15.

In case of keeping module is in the circumstance of 0 °C, it

should be placed in the circumstance of above 15 °C for 2

hours.

In case of keeping module is in the circumstance of below

-20 °C, it should be placed in the circumstance of above 15

°C for 3 hours.

[Caution]

When still image is displayed for a period of 20 minutes or

longer (Especially where W/B scale is strong. Digital pattern

13ch and/or Cross hatch pattern 09ch), there can some

afterimage in the black level area.

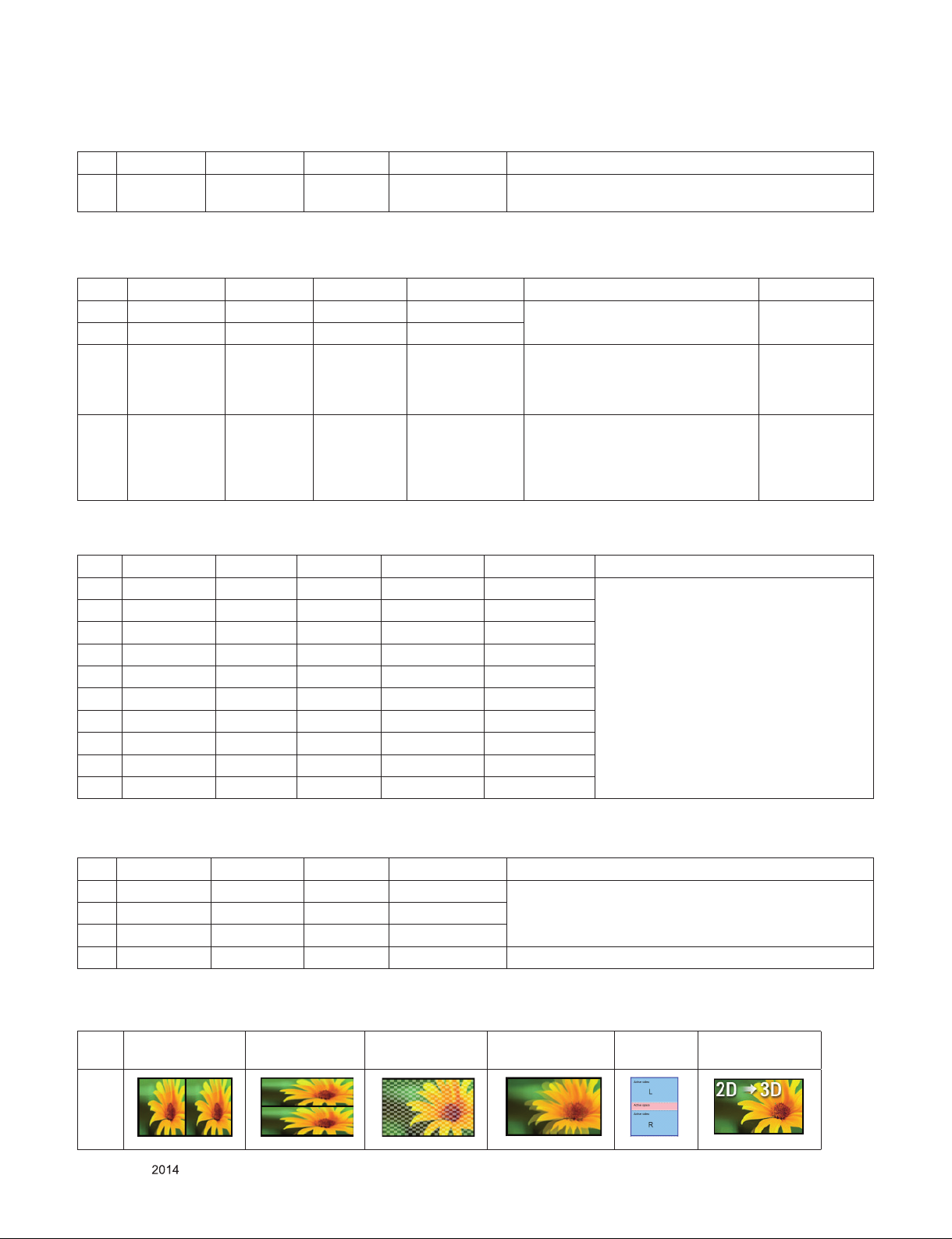

3.2. LAN Inspection

3.2.1. Equipment & Condition

▪ Each other connection to LAN Port of IP Hub and Jig

3.2.2. LAN inspection solution

▪ LAN Port connection with PCB

▪ Setting automatic IP

▪ If you want manual connection, enter Network connection at

MENU Mode of TV. Press Start connection key, then

Network will be connected.

3. Automatic Adjustment

3.1. MAC address D/L, CI+ key D/L, Widevine

key D/L, ESN D/L, HDCP14/20 D/L

Connect: USB port

Communication Prot connection

▪ Com 1,2,3,4 and 115200(Baudrate)

Mode check: Online Only

▪ Check the test process: DETECT → MAC → CI → Widevine

→ ESN → HDCP14 → HDCP20

▪ Play: Press Enter key

▪ Result: Ready, Test, OK or NG

▪ Printer Out (MAC Address Label)

3.2.3. WIDEVINE key Inspection

- Confirm key input data at the "IN START" MENU Mode.

Only for training and service purposes

- 12 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

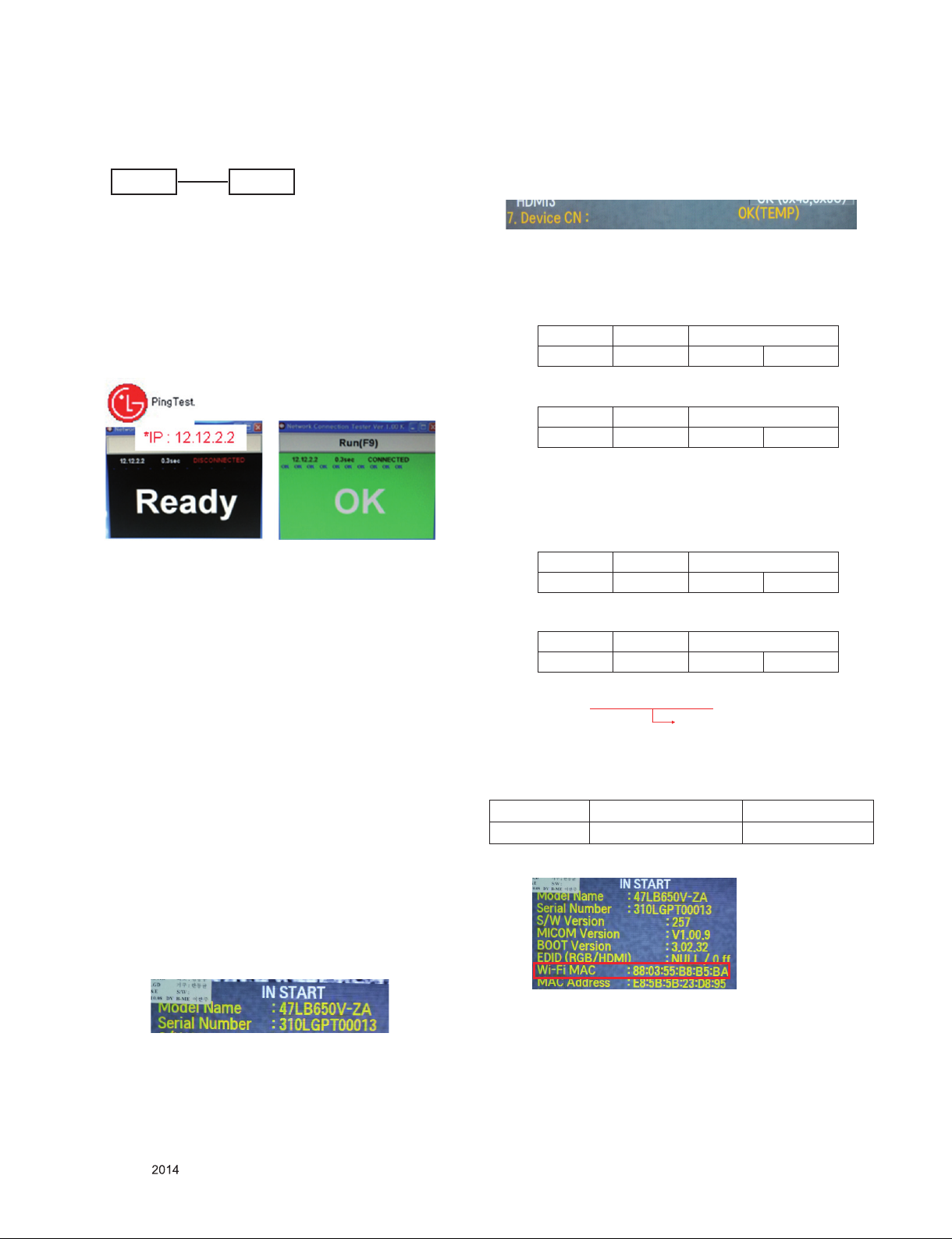

3.3. LAN PORT INSPECTION(PING TEST)

Connect SET → LAN port == PC → LAN Port

SET PC

3.3.1. Equipment setting

(1) Play the LAN Port Test PROGRAM.

(2) Input IP set up for an inspection to Test Program.

*IP Number : 12.12.2.2

3.3.2. LAN PORT inspection(PING TEST)

(1) Play the LAN Port Test Program.

(2) Connect each other LAN Port Jack.

(3) Play Test (F9) button and confirm OK Message.

(4) Remove LAN cable.

3.4. Model name & Serial number Download

3.4.1. Model name & Serial number D/L

▪ Press "P-ONLY" key of service remote control.

(Baud rate : 115200 bps)

▪ Connect RS-232C Signal to USB Cable to USB.

▪ Write Serial number by use USB port.

▪ Must check the serial number at Instart menu.

3.4.2. Method & notice

(1) Serial number D/L is using of scan equipment.

(2) Setting of scan equipment operated by Manufacturing

Technology Group.

(3) Serial number D/L must be conformed when it is produced

in production line, because serial number D/L is mandatory

by D-book 4.0.

* Manual Download (Model Name and Serial Number)

If the TV set is downloaded by OTA or service man, sometimes

model name or serial number is initialized.(Not always)

It is impossible to download by bar code scan, so It need

Manual download.

1) Press the "Instart" key of Adjustment remote control.

2) Go to the menu "7.Model Number D/L" like below photo.

3) Input the Factory model name(ex 47LB650V-ZA) or Serial

number like photo.

3.5. CI+ Key checking method

- Check the Section 3.1

Check whether the key was downloaded or not at ‘In Start’

menu. (Refer to below).

=> Check the Download to CI+ Key value in LGset.

3.5.1. Check the method of CI+ Key value

(1) Check the method on Instart menu

(2) Check the method of RS232C Command

1) Into the main ass’y mode(RS232: aa 00 00)

CMD 1 CMD 2 Data 0

A A 0 0

2) Check the key download for transmitted command

(RS232: ci 00 10)

CMD 1 CMD 2 Data 0

C I 1 0

3) Result value

- Normally status for download : OKx

- Abnormally status for download : NGx

3.5.2. Check the method of CI+ key value(RS232)

1) Into the main ass’y mode(RS232: aa 00 00)

CMD 1 CMD 2 Data 0

A A 0 0

2) Check the mothed of CI+ key by command

(RS232: ci 00 20)

CMD 1 CMD 2 Data 0

C I 2 0

3) Result value

i 01 OK 1d1852d21c1ed5dcx

CI+ Key Value

3.6. WIFI MAC ADDRESS CHECK

(1) Using RS232 Command

H-freq(kHz) V-freq.(Hz)

Transmission [A][I][][Set ID][][20][Cr] [O][K][X] or [NG]

(2) Check the menu on in-start

4) Check the model name Instart menu. → Factory name

displayed. (ex 47LB650V-ZA)

5) Check the Diagnostics.(DTV country only) → Buyer

model displayed. (ex 47LB650V-ZA)

Only for training and service purposes

- 13 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

4. Manual Adjustment

* ADC adjustment is not needed because of OTP(Auto ADC

adjustment)

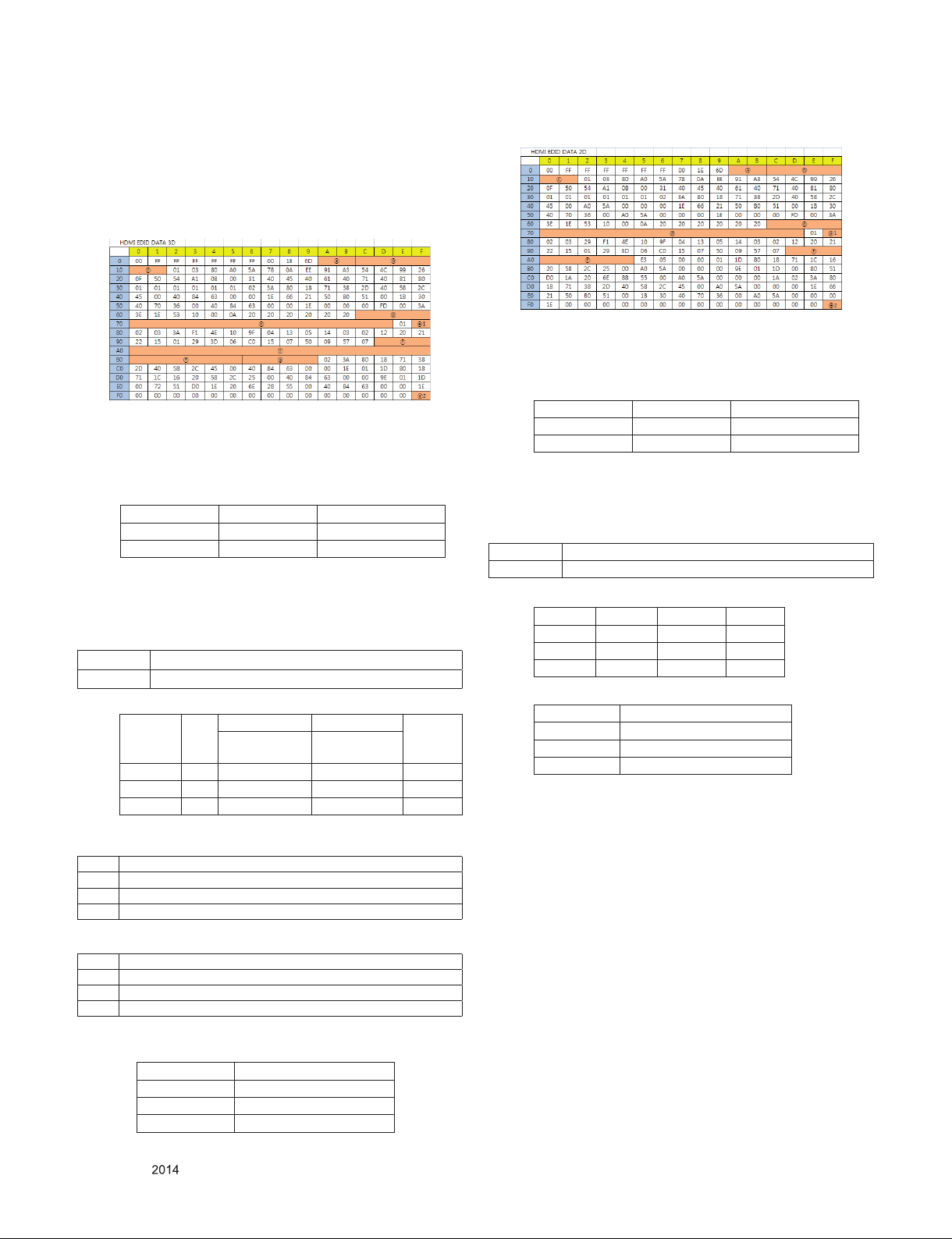

4.1. EDID DATA

4.1.1. 3D EDID

▪ Reference

- HDMI1 ~ HDMI3

- In the data of EDID, bellows may be different by S/W or

Input mode.

ⓐ Product ID

HEX EDID Table DDC Function

0001 0100 Analog

0001 0100 Digital

ⓑ Serial No: Controlled on production line.

ⓒ Month, Year: Controlled on production line:

ex) Monthly : ‘01’ → ‘01’

Year : ‘2014’ → ‘18’

ⓓ Model Name(Hex): LGTV

Chassis MODEL NAME(HEX)

LB42B 00 00 00 FC 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20

ⓔ Checksum(LG TV): Changeable by total EDID data.

ⓔ2 ⓔ2

ⓔ1

HDMI1 E7 85 CC X

HDMI2 E7 75 BC X

HDMI3 E7 65 AC X

10bit

/none XvYcc

8bit

/none XvYcc

ⓕ Vendor Specific(HDMI)

1) Deep color (module 10bit)

INPUT MODEL NAME(HEX)

HDMI1 78 03 0C 00 10 00 B8 2D 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

HDMI2 78 03 0C 00 20 00 B8 2D 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

HDMI3 78 03 0C 00 30 00 B8 2D 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

ⓔ3

4.1.2. 2D EDID

▪ Reference

- HDMI1 ~ HDMI3

- In the data of EDID, bellows may be different by S/W or

Input mode.

ⓐ Product ID

HEX EDID Table DDC Function

0001 0100 Analog

0001 0100 Digital

ⓑ Serial No: Controlled on production line.

ⓒ Month, Year: Controlled on production line:

ex) Monthly : ‘01’ → ‘01’

Year : ‘2014’ → ‘18'

ⓓ Model Name(Hex): LGTV

Chassis MODEL NAME(HEX)

LB42B 00 00 00 FC 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20

ⓔ Checksum(LG TV): Changeable by total EDID data.

ⓔ1 ⓔ2 ⓔ3

HDMI1 42 1B X

HDMI2 42 0B X

HDMI3 42 FB X

ⓕ Vendor Specific(HDMI)

INPUT MODEL NAME(HEX)

HDMI1 67 03 0C 00 10 00 80 1E

HDMI2 67 03 0C 00 20 00 80 1E

HDMI3 67 03 0C 00 30 00 80 1E

2) None deep color (module 8bit)

INPUT MODEL NAME(HEX)

HDMI1 78 03 0C 00 10 00 80 1E 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

HDMI2 78 03 0C 00 20 00 80 1E 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

HDMI3 78 03 0C 00 30 00 80 1E 20 C0 0E 01 4F 3F FC 08 10 18 10 06 10 16 10 28 10

ⓖ Colorimetry Data Block(HDMI)

1) The Model not supporting XvYcc

INPUT MODEL NAME(HEX)

HDMI1 E3 05 00 00

HDMI2 E3 05 00 00

HDMI3 E3 05 00 00

Only for training and service purposes

- 14 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

4.2. White Balance Adjustment

4.2.1. Overview

▪ W/B adj. Objective & How-it-works

(1) Objective: To reduce each Panel's W/B deviation

(2) How-it-works : When R/G/B gain in the OSD is at 192, it

means the panel is at its Full Dynamic Range. In order to

prevent saturation of Full Dynamic range and data, one

of R/G/B is fixed at 192, and the other two is lowered to

find the desired value.

(3) Adjustment condition : normal temperature

1) Surrounding Temperature : 25 °C ± 5 °C

2) Surrounding Humidity : 20 % ~ 80 %

4.2.2. Equipment

(1) Color Analyzer: CA-210 (LED Module : CH 14)

(2) Adjustment Computer(During auto adj., RS-232C protocol

is needed)

(3) Adjustment Remote control

(4) Video Signal Generator MSPG-925F 720p/204-Gray

(Model: 217, Pattern: 49)

→ Only when internal pattern is not available

▪ Color Analyzer Matrix should be calibrated using CS-1000.

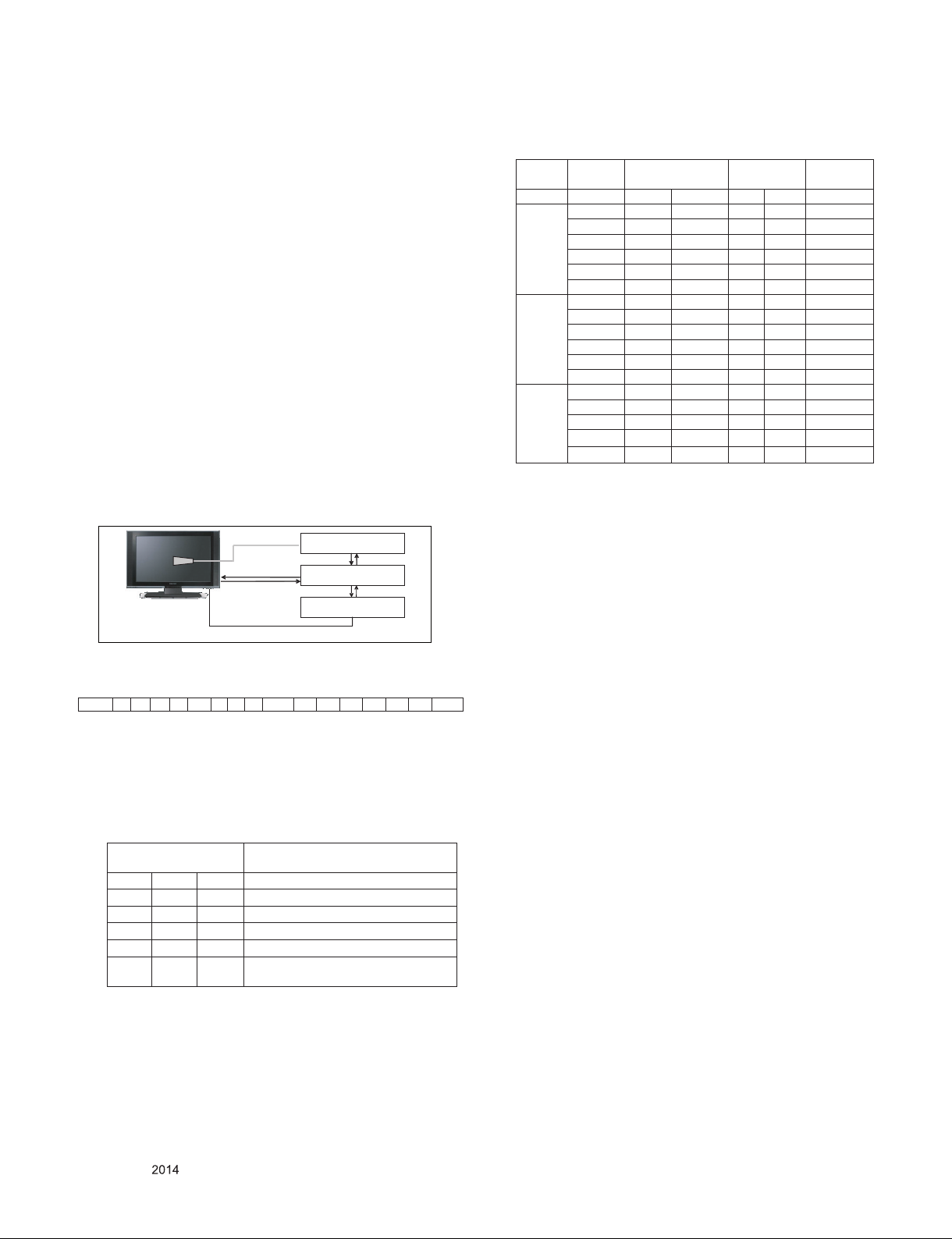

4.2.3. Equipment connection MAP

Col or Analy zer

Pro be

USB t o RS-23 2C

Sig nal Sou rce

* If TV internal pattern is used, not needed

4.2.4. Adj. Command (Protocol)

<Command Format>

START 6E A 50 A LEN A 03 A CMD A 00 A VAL A CS STOP

- LEN: Number of Data Byte to be sent

- CMD: Command

- VAL: FOS Data value

- CS: Checksum of sent data

- A: Acknowledge

Ex) [Send: JA_00_DD] / [Ack: A_00_okDDX]

▪ RS-232C Command used during auto-adjustment.

RS-232C COMMAND

[CMD ID DATA]

wb 00 00 Begin White Balance adjustment

wb 00 10 Gain adjustment(internal white pattern)

wb 00 1f Gain adjustment completed

wb 00 20 Offset adjustment(internal white pattern)

wb 00 2f Offset adjustment completed

wb 00 ff

Ex) wb 00 00 -> Begin white balance auto-adj.

wb 00 10 -> Gain adj.

ja 00 ff -> Adj. data

jb 00 c0

...

...

wb 00 1f → Gain adj. completed

*(wb 00 20(Start), wb 00 2f(end)) → Off-set adj.

wb 00 ff → End white balance auto-adj.

End White Balance adjustment

(internal pattern disappears )

RS- 232C

Com puter

RS- 232C

* Pat tern Ge nerat or

Explanation

▪ Adj. Map

Applied Model : LB42B Chassis ALL MODELS

Cool

Medium

Warm

Adj. item

R Gain j g 00 C0

G Gain j h 00 C0

B Gain j i 00 C0

R Cut

G Cut

B Cut

R Gain j a 00 C0

G Gain j b 00 C0

B Gain j c 00 C0

R Cut

G Cut

B Cut

R Gain j d 00 C0

G Gain j e 00 C0

B Gain j f 00 C0

R Cut

G Cut

Command

(lower caseASCII)

CMD1 CMD2 MIN MAX

Data Range

(Hex.)

4.2.5. Adj. method

(1) Auto adj. method

1) Set TV in adj. mode using P-Only key.

2) Zero calibrate probe then place it on the center of the

Display.

3) Connect Cable.(RS-232C to USB)

4) Select mode in adj. Program and begin adj.

5) When adj. is complete (OK Sign), check adj. status pre

mode. (Cool, Medium, Warm)

6) Remove probe and RS-232C cable to complete adj.

▪ W/B Adj. must begin as start command “wb 00 00” , and

finish as end command “wb 00 ff”, and Adj. offset if need.

(2) Manual adjustment. method

1) Set TV in Adj. mode using P-Only key.

2) Zero Calibrate the probe of Color Analyzer, then place it

on the center of LCD module within 10 cm of the surface.

3) Press ADJ key → EZ adjust using adj. R/C → 7. WhiteBalance then press the cursor to the right(key ►).

(When right key(►) is pressed 204 Gray internal pattern

will be displayed)

4) One of R Gain / G Gain / B Gain should be fixed at 192,

and the rest will be lowered to meet the desired value.

5) Adjustment is performed in COOL, MEDIUM, WARM 3

modes of color temperature.

▪ If internal pattern is not available, use RF input. In EZ Adj.

menu 7.White Balance, you can select one of 2 Testpattern: ON, OFF. Default is inner(ON). By selecting OFF,

you can adjust using RF signal in 204 Gray pattern.

▪ Adjustment condition and cautionary items

1) Lighting condition in surrounding area

Surrounding lighting should be lower 10 lux. Try to

isolate adj. area into dark surrounding.

2) Probe location

: Color Analyzer(CA-210) probe should be within 10 cm

and perpendicular of the module surface (80° ~ 100°)

Default

(Decimal)

Only for training and service purposes

- 15 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

4.2.6. Reference (White balance Adj. coordinate and

color temperature)

▪ Luminance : 204 Gray

▪ Standard color coordinate and temperature using CS-1000

(over 26 inch)

Mode

Coordinate

x y

Temp ∆uv

Cool 0.271 0.270 13000 K 0.0000

Medium 0.286 0.289 9300 K 0.0000

Warm 0.313 0.329 6500 K 0.0000

▪ Standard color coordinate and temperature using CA-210(CH 14)

Mode

Coordinate

x y

Temp ∆uv

Cool 0.271 ± 0.002 0.270 ± 0.002 13000 K 0.0000

Medium 0.286 ± 0.002 0.289 ± 0.002 9300 K 0.0000

Warm 0.313 ± 0.002 0.329 ± 0.002 6500K 0.0000

4.2.7. LED White balance table

- EDGE LED module change color coordinate because of

aging time.

- Apply under the color coordinate table, for compensated

aging time.

Only march to December & Global

Model: (normal line)LGD (LB5xxx, LB6xxx, LB7xxx, LB8xxx)

NC4.0

Aging

time

(Min)

1 0-2 282 289 297 308 324 348

2 3-5 281 287 296 306 323 346

3 6-9 279 284 294 303 321 333

4 10-19 277 280 292 299 319 339

5 20-35 275 277 290 296 317 336

6 36-49 274 274 289 293 316 333

7 50-79 273 272 288 291 315 331

8 80-119 272 271 287 290 314 330

9 Over 120 271 270 286 289 313 329

Only January to Febuary & Global

Model: (normal line)LGD (LB5xxx, LB6xxx, LB7xxx, LB8xxx)

NC4.0

Aging

time

(Min)

1 0-5 286 295 301 314 328 354

2 6-10 284 290 299 309 326 349

3 11-20 282 287 297 306 324 346

4 21-30 279 283 294 302 321 342

5 31-40 276 278 291 297 318 337

6 41-50 274 275 289 294 316 334

7 51-80 273 272 288 291 315 331

8 81-119 272 271 287 290 314 330

9 Over 120 271 270 286 289 313 329

Cool Medium Warm

x y x y x y

271 270 286 289 313 329

Cool Medium Warm

x y x y x y

271 270 286 289 313 329

AUO, INX, Sharp, CSOT, BOE (Cool : 13000 K)

NC4.0

spec 271 270 286 289 313 329

target 278 280 293 299 320 339

Cool Medium Warm

x y x y x y

4.3. Local Dimming Function Check

(1) Normal Edge LED Model

Step 1) Turn on TV.

Step 2) Press “TILT” key on the Adj. Remote control.

Step 3) A t the Local D im mi ng mo de , module Edge

Backlight moving right to left Back light of IOP

module moving.

Step 4) Confirm the Local Dimming mode.

Step 5) Press "exit" key.

(2) Only 50inch AUO Local dimming Model(50LA66)

- Test method

Insert the USB memo ry included vide o fi le below

inspection pattern in Poweronly mode.

Play repeat first, second pattern once per second

(3) Only LA71 Series LGD Local Dimming Model (47/55LA71,

16 block)

Step 1) Turn on TV

Step 2) Press “TILT” key on the Adj. R/C.

Step 3) A t the Local D im mi ng mo de , module Edge

Backlight moving left to right, bottom to Up, Back

light of ALEF module moving. (No1->2->3->….->14

->15->16)

Step 4) Confirm the Local Dimming mode

Step 5) Press “exit” Key

Only for training and service purposes

- 16 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

4.4. Magic Motion Remote control test

- Results are automatically marked in Instart OSD after

through the AP/Magic Remocon Equipment on the line

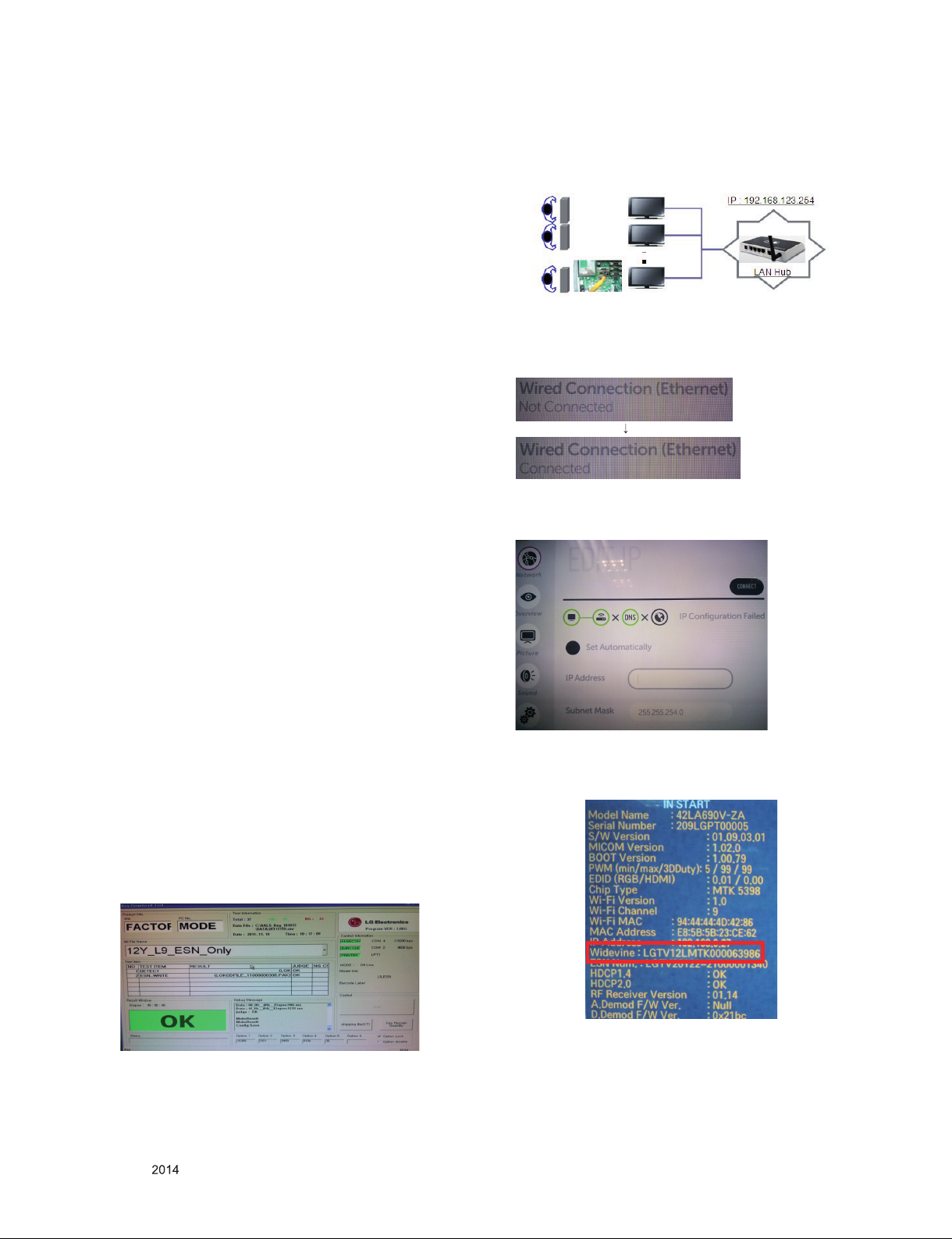

4.5. 3D function test(Except Non-3D product)

(Pattern Generator MSHG-600, MSPG-6100[Support HDMI1.4])

* HDMI mode NO. 872 , pattern No.83

(1) Please input 3D test pattern like below.

4.6. Wi-Fi Test

Step 1) Turn on TV

Step 2) Select Wi-Fi Connection option in Network Menu.

Step 3) Click Off Button to On in Wi-Fi Connection.

Step 4) The system finds any AP like blow PIC.

(2) When 3D OSD appear automatically, then select OK key.

(3) Don't wear a 3D Glasses, check the picture like below.

Only for training and service purposes

- 17 -

Step 5) Select the AP you want to connect.

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

4.7. LNB voltage and 22KHz tone check

(only for DVB-S/S2 model)

▪ Test method

(1) Set TV in Adj. mode using POWER ON.

(2) Connect cable between satellite ANT and test JIG.

(3) Press Yellow key(ETC+SWAP) in Adj Remote control to

make LNB on.

(4) Check LED light ‘ON’ at 18 V menu.

(5) Check LED light ‘ON’ at 22 KHz tone menu.

(6) Press Blue key(ETC+PIP INPUT) in Adj Remote control

to make LNB off.

(7) Check LED light ‘OFF’ at 18 V menu.

(8) Check LED light ‘OFF’ at 22 KHz tone menu.

▪ Test result

(1) After press LNB On key, ‘18 V LED’ and ‘22 KHz tone

LED’ should be ON.

(2) After press LNB OFF key, ‘18 V LED’ and ‘22 KHz tone

LED’ should be OFF.

7. GND and Internal Pressure check

7.1. Method

(1) GND & Internal Pressure auto-check preparation

- Check that Power cord is fully inserted to the SET.

(If loose, re-insert)

(2) Perform GND & Internal Pressure auto-check

- Unit fully inserted Power cord, Antenna cable and A/V

arrive to the auto-check process.

- Connect D-terminal to AV JACK TESTER

- Auto CONTROLLER(GWS103-4) ON

- Perform GND TEST

- If NG, Buzzer will sound to inform the operator.

- If OK, changeover to I/P check automatically.

(Remove CORD, A/V form AV JACK BOX.)

- Perform I/P test

- If NG, Buzzer will sound to inform the operator.

- If OK, Good lamp will lit up and the stopper will allow the

pallet to move on to next process.

4.8. Option selection per country

4.8.1. Overview

- Option selection is only done for models in Non-EU

4.8.2. Method

(1) Press ADJ key on the Adj. R/C, then select Country Group

Meun.

(2) Select Country Group Code 04 or Country Group EU.

5. Tool Option selection

▪ Method : Press "ADJ" key on the Adjustment remote control,

then select Tool option.

6. Ship-out mode check(In-stop)

▪ After final inspection, press "IN-STOP" key of the Adjustment

remote control and check that the unit goes to Stand-by

mode.

7.2. Checkpoint

▪ TEST voltage

(1) DQA Test

- GND: 1.5 KV / min at 100 mA

- SIGNAL: 3 KV / min at 100 mA

(2) Mass Production Line Test

- GND: AC 1.5 KV / sec, Cut off current not exceed 100 mA

▪ TEST time: DQA 1 min, Mass Production Line 1 sec

▪ TEST POINT

- GND TEST = POWER CORD GND & SIGNAL CABLE

METAL GND

- Internal Pressure TEST = POWER CORD GND & LIVE &

NEUTRAL

▪ LEAKAGE CURRENT: At 0.5 mArms

8. Audio

Measurement condition:

No. Item Min Typ Max Unit Remark

Audio practical

max Output, L/R

1.

(Distortion=10%

max Output)

Speaker (8Ω

2.

Impedance)

(1) RF input: Mono, 1 KHz sine wave signal, 100 % Modulation

(2) CVBS, Component: 1 KHz sine wave signal 0.5 Vrms

(3) RGB PC: 1 KHz sine wave signal 0.7 Vrms

9 10 12 W

8.10 10.8 Vrms

9 10 12 W

EQ Off

AVL Off

Clear Voice Off

Only for training and service purposes

- 18 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

9. USB S/W Download(Service only)

(1) Put the USB Stick to the USB socket.

(2) Go to General menu then enter to About This TV.

(3) Enter the USB EXPERT MODE.

(4) Updating is starting.

(5) Updating completed, the TV will restart automatically

(6) If your TV is turned on, check your updated version and

Tool option. (explain the Tool option, next stage)

* If downloading version is more high than your TV have,

TV can lost all channel data. In this case, you have to

channel recover. if all channel data is cleared, you didn’t

have a DTV/ATV test on production line.

* After downloading, have to adjust Tool Option again.

(1) Push "IN-START" key in service remote control.

(2) Select "Tool Option 1" and push "OK" key.

(3) Punch in the number. (Each model has their number)

Only for training and service purposes

- 19 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

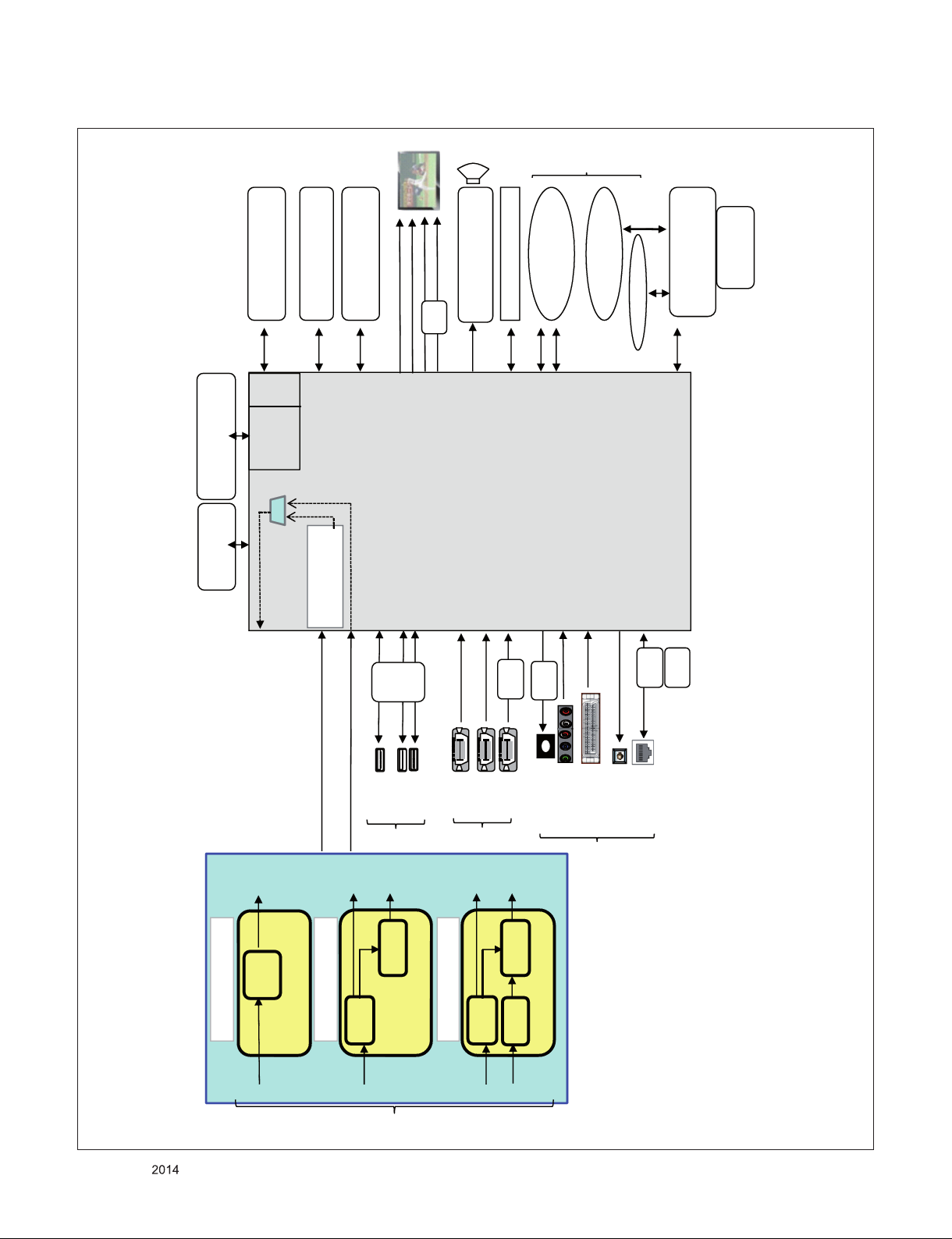

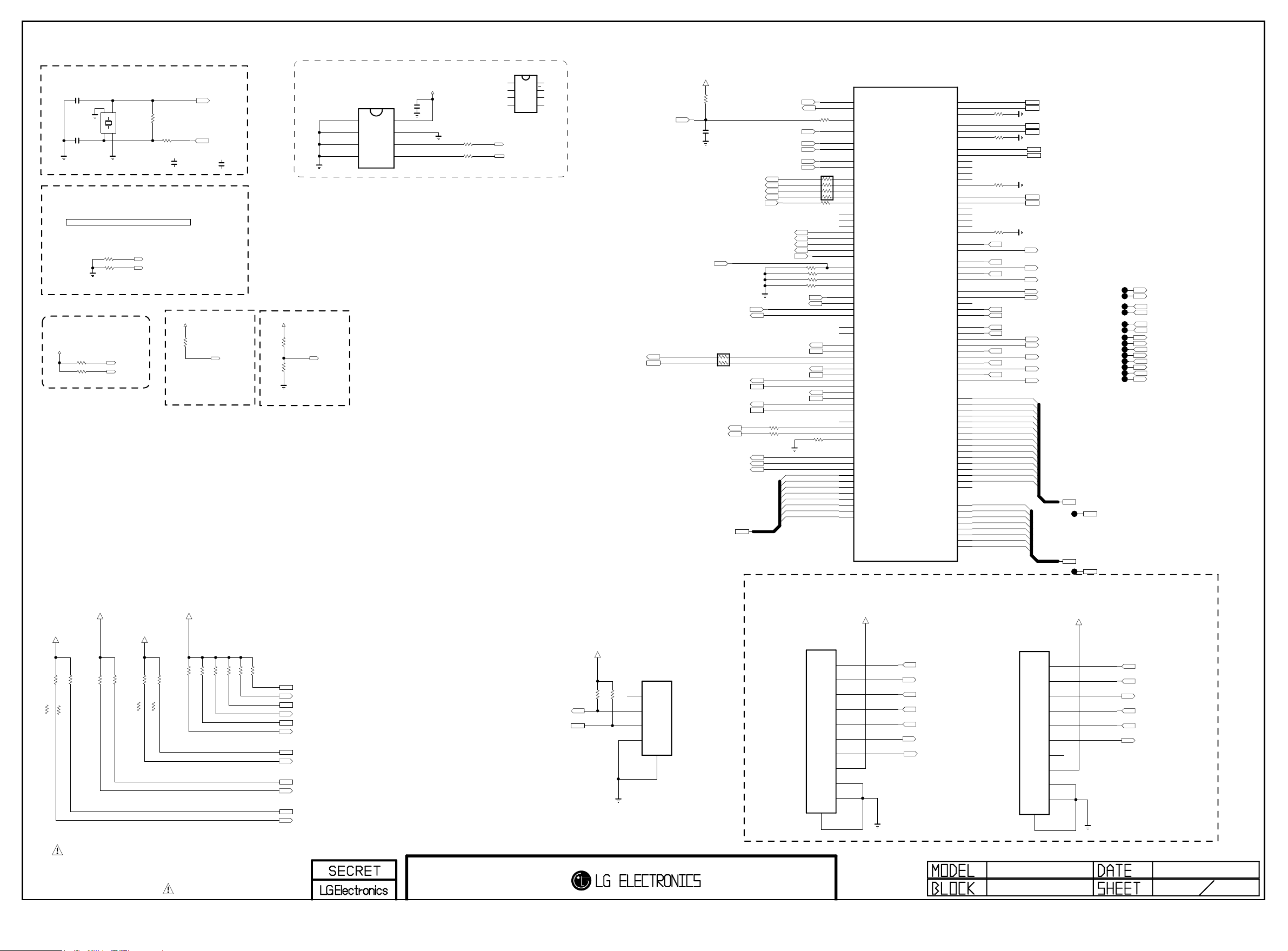

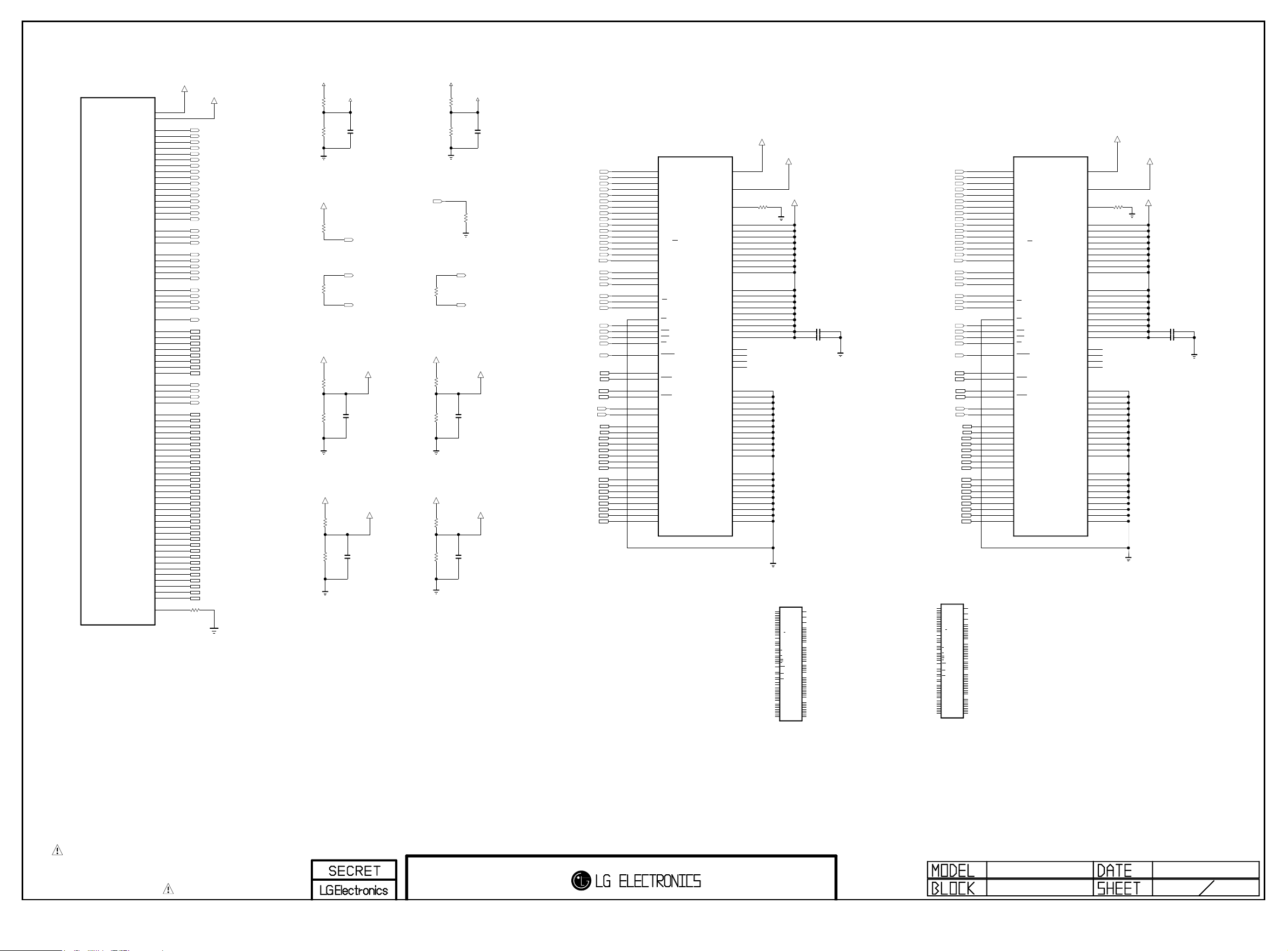

BLOCK DIAGRAM

IR

KEY

I2C(EYE)

eMMC

(4/8GB)

(256Kb)

(512MB X 2EA)

DDR3 1600 X 16

(512MB X 2EA)

DDR3 1600 X 16

X_TAL

24MHz

SYSTEM EEPROM

PM

50P

41P

51P

I2C 5

A B

P_TS P_TS

Analog Demod

Digital Demod(T/C)

P_TS

IF (+/-)

EPI

LVDS

USB 2.0

OCP

1.5A

NTP

Audio AMP

LOCAL DIMMING

IC

50P

I2C 2

I2C 1

I2C 2

I2S Out

M14

IC101

HDMI / MHL Rx.

HDMI Rx.

1A

OCP

WIFI

BLUTOOTH

USB_WIFI

UART_BT

TI

AMP

IR / KEY/EYE

CVBS/YPbPr

CVBS/RGB

SPDIF OUT

Sub Micom

PWM

LOGO LIGHT

I2C 3

ETHERNET

PHY

LAN

X_TAL

X_TAL

(RENESAS

25MHz

32.768KHz

R5F1000G)

IF

Si2158B

DVB T/C TUNER

ATV /

DVB-T/C

Only for training and service purposes

USB1(2.0)

Tuner : I2C 6

D-Demod : I2C 4

AIF

SID

TS_ [0:7]

USB2(2.0)

E

HDMI1

USB3(2.0)

SID

AIF

DIF

SI2169B

(MHL)

HDMI2

(ARC)

HDMI3

H/P (Line Out)

E

SCART

AV/COMP

(IR Bla Ready)

REA

TS_ [0:7]

DIF

SI2169B

LAN

OPTIC

R

IQ

DVB T2/C TUNER

Si2158B

ATV /

DVB-T/C

REA

DVB T2/C/S2 TUNER

R

(H)

- 20 -

RDA

5815M

Si2158B

ATV /

DVB-S

DVB-T/C

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

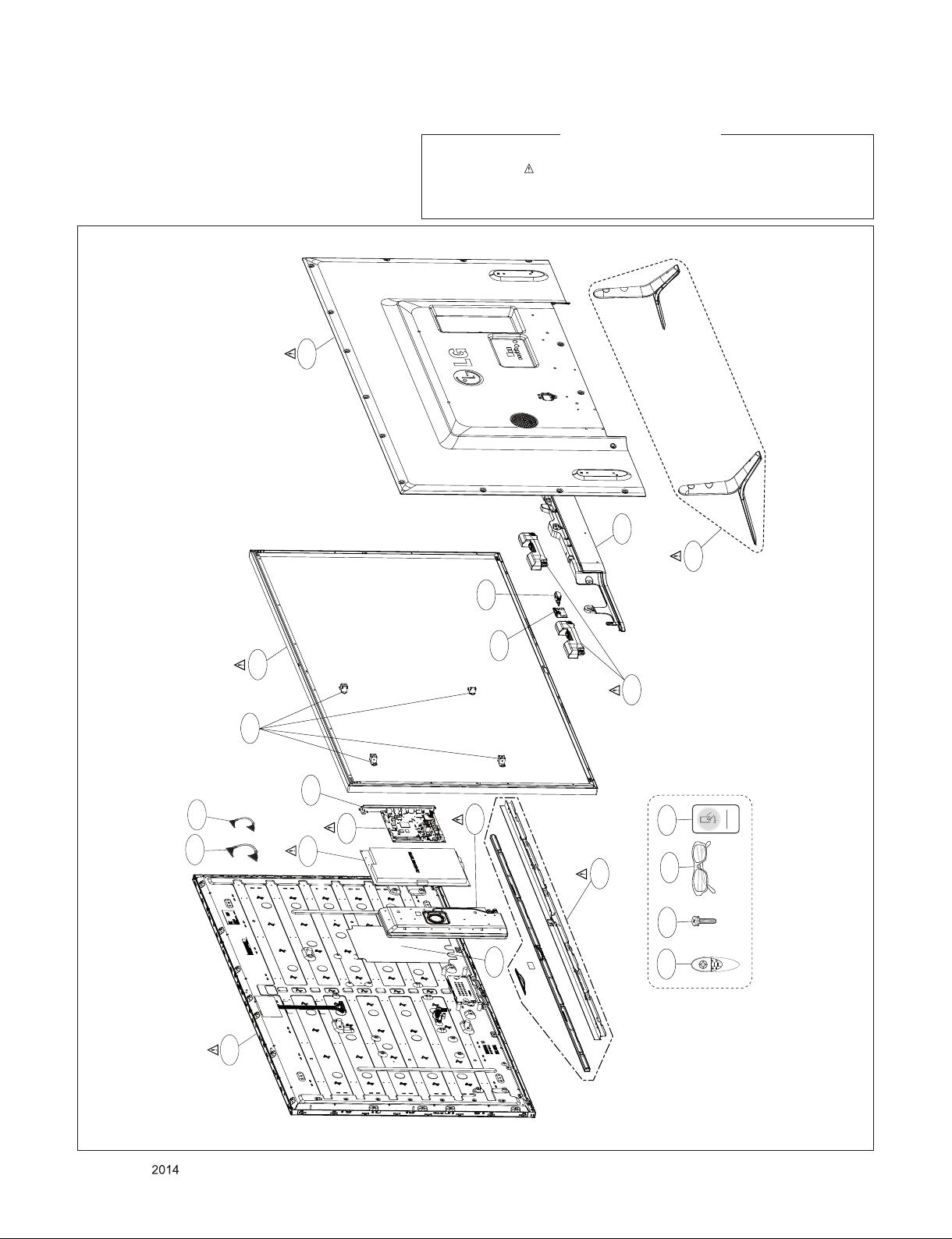

400

EXPLODED VIEW

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essenti al that these sp ecial safet y parts shoul d be replac ed with the same compon ents as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

410

900

500

570

310

120

800

521

LV2

540

LV1

530

122

820

300

AT1

AG1

A10

A22

Set + Stand

200

Only for training and service purposes

- 21 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

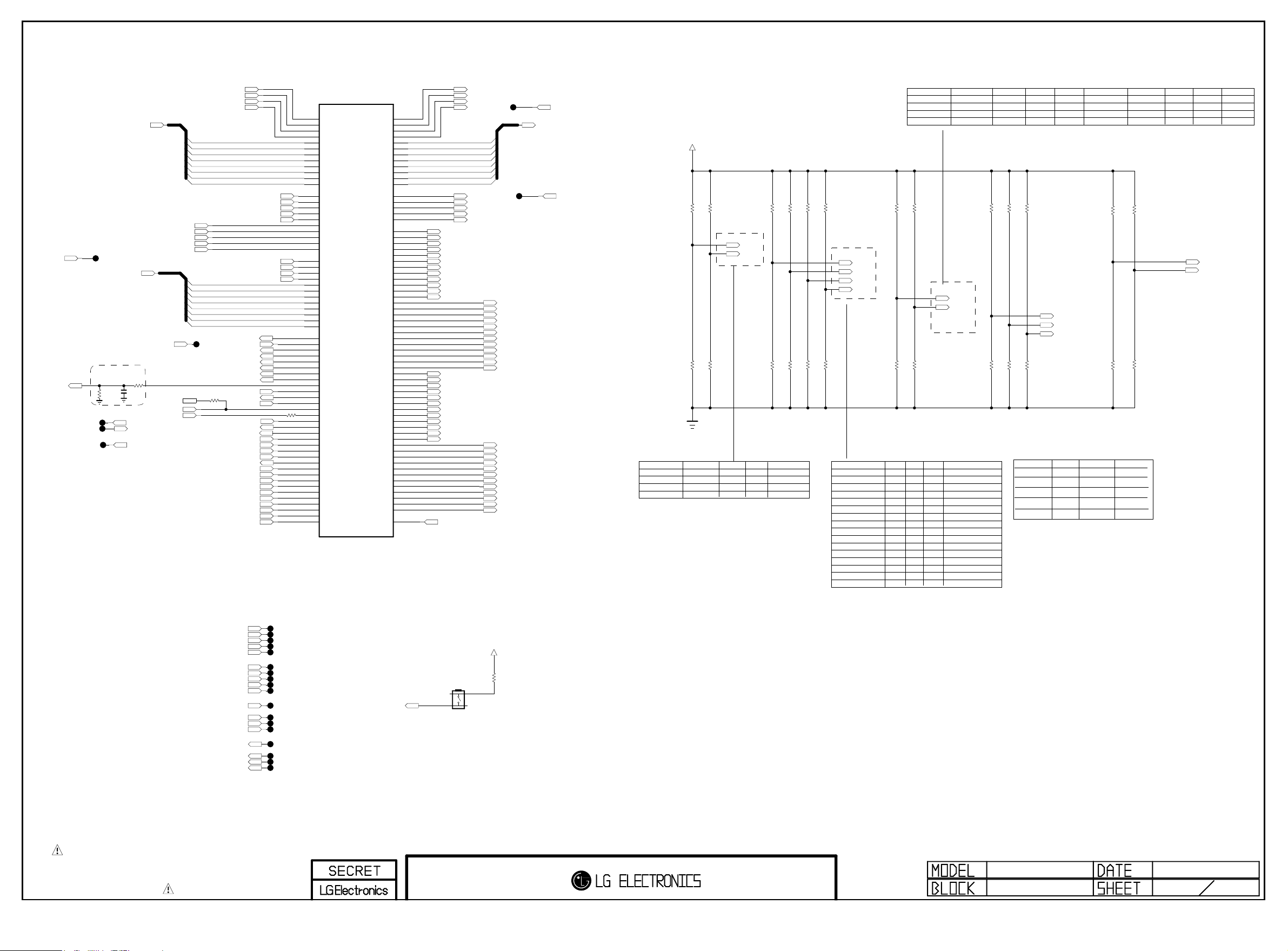

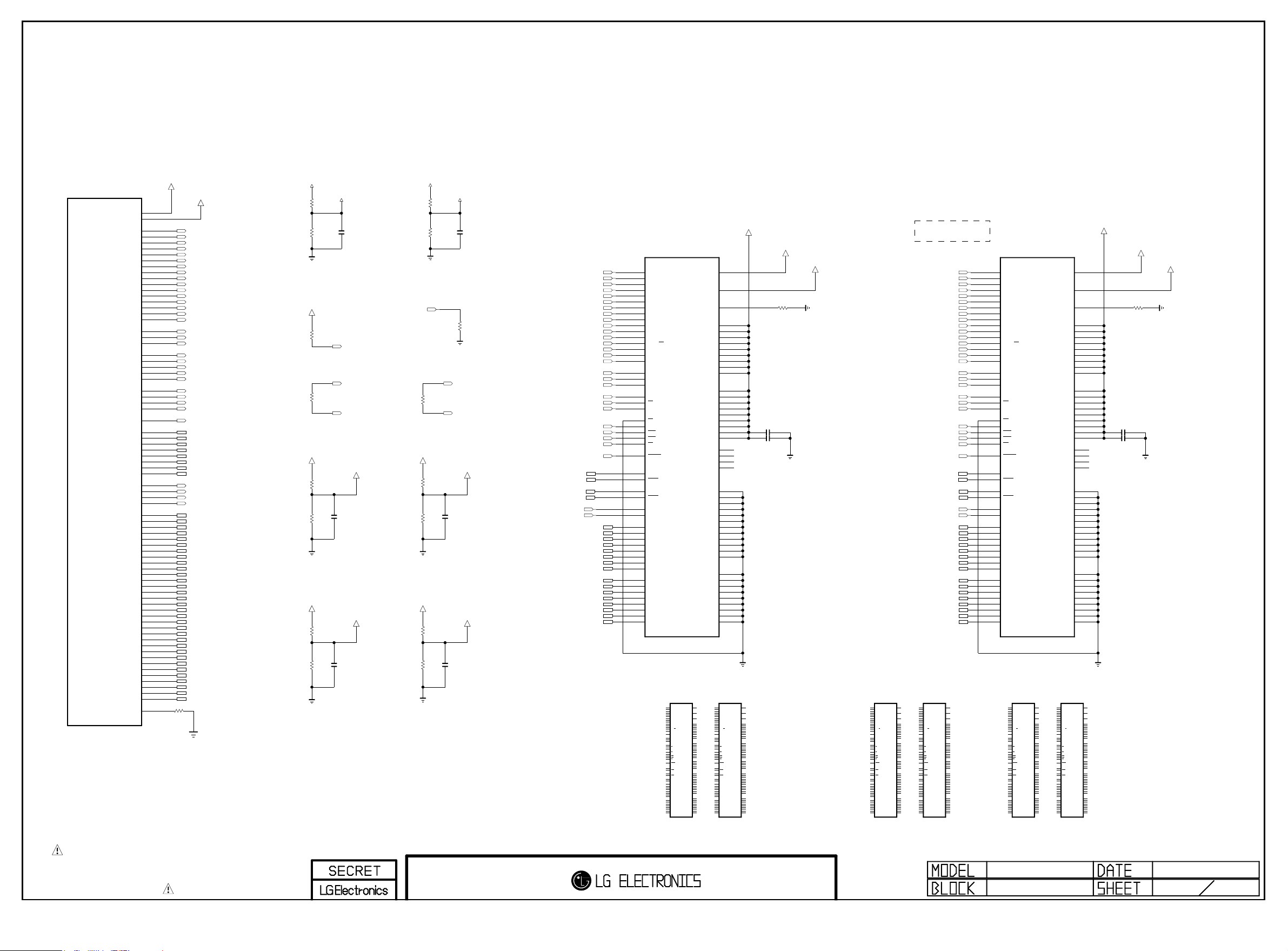

System Configuration

Copyright © 2014 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Clock for M14-A0

MAIN Clock(24Mhz)

LOADCAP_ATSC_PCB

10pF

C101

C102

LOADCAP_ATSC_PCB

System Clock for Analog block(24Mhz)

PLL SET[1:0] : internal pull up

"00" : CPU(1200Mhz),M0 / M1 DDR(792,792 Mhz)

"01" : CPU(1056Mhz),M0 / M1 DDR(672,672 Mhz)

"10" : CPU(1056Mhz),M0 / M1 DDR(792,792 Mhz)

"11" : CPU( 960Mhz),M0 / M1 DDR(792,792 Mhz)

OP MODE[1:0]

"00" : Normal Mode

"01/10/11" : Internal Test mode

+3.3V_NORMAL

R101 3.3K

R102 3.3K

Extenal test only

+3.3V_NORMAL

+3.3V_TUNER

R148

3.3K

R146

3.3K

KR_PIP_NOT

KR_PIP_NOT

1.5K

1.5K

KR_PIP

R146-*1

KR_PIP

R148-*1

10pF

Extenal test only

OPT

OPT

R149

2

3

OPT

R103 3.3K

R104 3.3K

OPT

3.3K

X-TAL_1

GND_1

1

4

X-TAL_2

GND_2

OPM1

OPM0

24MHz

X101

R118

PLLSET1

PLLSET0

+3.3V_TUNER

R150

3.3K

R155

1.2K

KR_PIP_NOT

KR_PIP_NOT

3.3K

KR_PIP

KR_PIP

R155-*1

1M

R180

560

LOADCAP_DVB_PCB

C101-*1

6.8pF

50V

+3.3V_NORMAL

INSTANT boot MODE

"1 : Instant boot

"0 : normal

3.3K

R121

(internal pull down)

OPT

INSTANT_MODE0

+3.3V_NORMAL

R158

R157

R156

3.3K

R156-*1

3.3K

1.2K

XTAL_IN

XTAL_OUT

LOADCAP_DVB_PCB

C102-*1

6.8pF

50V

INSTANT_BOOT

I2C PULL UP

R159

3.3K

3.3K

R160

3.3K

R161

+3.3V_NORMAL

3.3K

R127

OPT

3.3K

R128

BOOT_MODE0

I2C

I2C_1 : AMP

I2C_2 : T-CON,L/DIMING

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod, LNB

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

R162

3.3K

3.3K

IC103

AT24C256C-SSHL-T

A0

1

A1

2

A2

3

GND

4

NVRAM_ATMEL

BOOT MODE

"0 : EMMC

"1 : TEST MODE

BOOT_MODE

I2C_SDA1

I2C_SCL1

I2C_SDA_MICOM_SOC

I2C_SCL_MICOM_SOC

I2C_SDA2

I2C_SCL2

I2C_SDA4

I2C_SCL4

I2C_SDA5

I2C_SCL5

I2C_SDA6

I2C_SCL6

NVRAM

VCC

8

WP

7

SCL

6

SDA

5

+3.3V_NORMAL

C107

0.1uF

16V

Write Protection

- Low : Normal Operation

- High : Write Protection

R143 33

R144 33

IC103-*1

M24256-BRMN6TP

E0

VCC

1

8

WC

E1

7

2

SCL

E2

6

3

SDA

VSS

5

4

NVRAM_ST

I2C_SCL5

I2C_SDA5

I2C_SCL_MICOM_SOC

I2C_SDA_MICOM_SOC

LOCAL DIMMING I2C CONTROL

+3.3V_NORMAL

OPT

OPT

R105

3.3K

R106

3.3K

LED_SCL

LED_SDA

SOC_RESET

FORCED_JTAG_0

P102

12507WS-04L

1

2

3

4

5

+3.3V_NORMAL

R163

10K

OPT

C104

0.1uF

16V

L/DIM0_VS

L/DIM0_SCLK

L/DIM0_MOSI

IRB_SPI_MOSI/TDO1

IRB_SPI_MISO/TDI1

M_REMOTE_RX

M_REMOTE_TX

1/16W

33

AR100

I2C_SCL4

I2C_SDA4

I2C_SCL6

I2C_SDA6

PWM_DIM2

PWM_DIM

EMMC_CLK

EMMC_CMD

EMMC_RST

EMMC_DATA[0-7]

OPT

XTAL_IN

XTAL_OUT

BOOT_MODE

PLLSET0

PLLSET1

TCK0

TDI0

TRST_N1

IRB_SPI_SS/TMS1

IRB_SPI_CK/TCK1

I2C_SCL1

I2C_SDA1

I2C_SCL2

I2C_SDA2

I2C_SCL5

I2C_SDA5

33

R107

33

R108

OPM0

OPM1

R178 33

OPT

R182 10K

R183 10K

R184 10K

R185 10K

SOC_RX

SOC_TX

EMMC_DATA[7]

EMMC_DATA[6]

EMMC_DATA[5]

EMMC_DATA[4]

EMMC_DATA[3]

EMMC_DATA[2]

EMMC_DATA[1]

EMMC_DATA[0]

12505WS-10A00

JTAG_CPU

B23

A23

R169

AG21

33

AJ18

AB8

AC8

AD8

AE8

AR101

AG30

AG28

AG29

AH29

AJ27

AH27

AG26

AH26

AJ12

AJ13

AH12

AG12

AH23

AG22

AH11

AG11

AG10

AH22

AJ22

AH10

AJ10

AG23

AH24

Y7

Y6

W7

W6

W5

AH7

AJ7

AG8

AH8

AH9

AG9

AJ9

AC6

AC7

AD7

AB7

G32

G33

G31

D31

F33

F32

E32

F31

D33

D32

E31

33

R179

10K

1/16W

5%

Jtag-0 I/F

+3.3V_NORMAL

P103

1

2

3

4

5

6

7

8

9

10

11

IC101

LG1311

XIN_MAIN

XO_MAIN

PORES_N

BOOT_MODE

PLLSET0

PLLSET1

OPM0

OPM1

L_VSOUT_LD/TRST0_N

DIM0_SCLK/TMS0

DIM1_SCLK/TCK0

DIM1_MOSI/TDI0

DIM0_MOSI/TDO0

SPI_CS0

SPI_SCLK0

SPI_DO0

SPI_DI0/TRST1_N

SPI_CS1/TMS1

SPI_SCLK1/TCK1

SPI_DO1/TDO1

SPI_DI1/TDI1

EXT_INTR0

EXT_INTR1

EXT_INTR2

EXT_INTR3

UART0_RXD

UART0_TXD

UART1_RXD

UART1_TXD

UART1_RTS_N

UART1_CTS_N

SCL0

SDA0

SCL1

SDA1

SCL2

SDA2

SCL3

SDA3

SCL4

SDA4

SCL5

SDA5

PWM0

PWM1

PWM2

PWM_IN

EMMC_CLK

EMMC_CMD

EMMC_RESETN

EMMC_DATA7

EMMC_DATA6

EMMC_DATA5

EMMC_DATA4

EMMC_DATA3

EMMC_DATA2

EMMC_DATA1

EMMC_DATA0

USB2_0_DP0

USB2_0_DM0

USB2_0_TXRTUNE

USB2_1_DP0

USB2_1_DM0

USB2_1_TXRTUNE

USB3_DP0

USB3_DM0

USB3_TXP0

USB3_TXM0

USB3_RXP0

USB3_RXM0

USB3_RESREF0

USB3_DP1

USB3_DM1

USB3_TXP1

USB3_TXM1

USB3_RXP1

USB3_RXM1

USB3_RESREF1

HUB_PORT_OVER0

HUB_VBUS_CTRL0

EB_CS3

EB_CS2

EB_CS1

EB_CS0

EB_WE_N

EB_OE_N

EB_WAIT

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

CAM_CE1_N

CAM_CE2_N

CAM_IREQ_N

CAM_RESET

CAM_INPACK_N

CAM_VCCEN_N

CAM_WAIT_N

CAM_REG_N

EB_ADDR0

EB_ADDR1

EB_ADDR2

EB_ADDR3

EB_ADDR4

EB_ADDR5

EB_ADDR6

EB_ADDR7

EB_ADDR8

EB_ADDR9

EB_ADDR10

EB_ADDR11

EB_ADDR12

EB_ADDR13

EB_ADDR14

EB_ADDR15

EB_DATA0

EB_DATA1

EB_DATA2

EB_DATA3

EB_DATA4

EB_DATA5

EB_DATA6

EB_DATA7

L/DIM0_VS

TDI0

L/DIM0_MOSI

L/DIM0_SCLK

TCK0

SOC_RESET

FORCED_JTAG_0

AN9

AM9

AN8

H32

J31

H33

N31

N32

P33

P32

M32

M33

P31

K33

K32

L32

L31

K31

J32

M31

W28

W29

H28

J30

J28

J29

G30

F30

H29

G29

G28

P28

P27

U28

R29

V27

T28

T29

R28

U27

N29

K30

E30

M30

N28

M28

M29

L29

K29

K28

L28

D30

EB_ADDR[10]

F29

EB_ADDR[11]

C32

EB_ADDR[12]

C33

EB_ADDR[13]

C31

EB_ADDR[14]

B33

B32

A32

B31

A31

A30

B30

C30

C29

(TRST0_N)

(TDO0)

(TMS0)

R1712001%

R1722001%

R1732001%

R1742001%

/USB_OCD1

/USB_OCD2

/USB_OCD3

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

CAM_IREQ_N

CAM_INPACK_N

CAM_WAIT_N

EB_ADDR[0]

EB_ADDR[1]

EB_ADDR[2]

EB_ADDR[3]

EB_ADDR[4]

EB_ADDR[5]

EB_ADDR[6]

EB_ADDR[7]

EB_ADDR[8]

EB_ADDR[9]

EB_DATA[0]

EB_DATA[1]

EB_DATA[2]

EB_DATA[3]

EB_DATA[4]

EB_DATA[5]

EB_DATA[6]

EB_DATA[7]

12505WS-10A00

WIFI_DP

WIFI_DM

USB_DP3

USB_DM3

USB_DP1

USB_DM1

USB_DP2

USB_DM2

USB_CTL1

USB_CTL2

USB_CTL3

EB_WE_N

EB_OE_N

/PCM_CE1

/PCM_CE2

PCM_RESET

PCM_5V_CTL

CAM_REG_N

Jtag-1 I/F

+3.3V_NORMAL

P104

OPT

1

2

3

4

5

6

7

8

9

10

11

EB_ADDR[0-14]

TP102

EB_DATA[0-7]

TP103

PAGE 1

TP104

TP105

TP106

TP107

TP108

TP109

TP110

TP111

TP112

TP113

TP114

TP115

TP116

TP117

EB_ADDR[0-14]

EB_DATA[0-7]

EB_WE_N

EB_OE_N

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

/PCM_CE1

/PCM_CE2

CAM_IREQ_N

PCM_RESET

CAM_INPACK_N

PCM_5V_CTL

CAM_WAIT_N

CAM_REG_N

TRST_N1

IRB_SPI_MISO/TDI1

IRB_SPI_MOSI/TDO1

IRB_SPI_SS/TMS1

IRB_SPI_CK/TCK1

SOC_RESET

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

M14-Peripheral

MID_LG1311

M14 Symbol A

2013.04.04

1

31

PAGE 2

Copyright © 2014 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

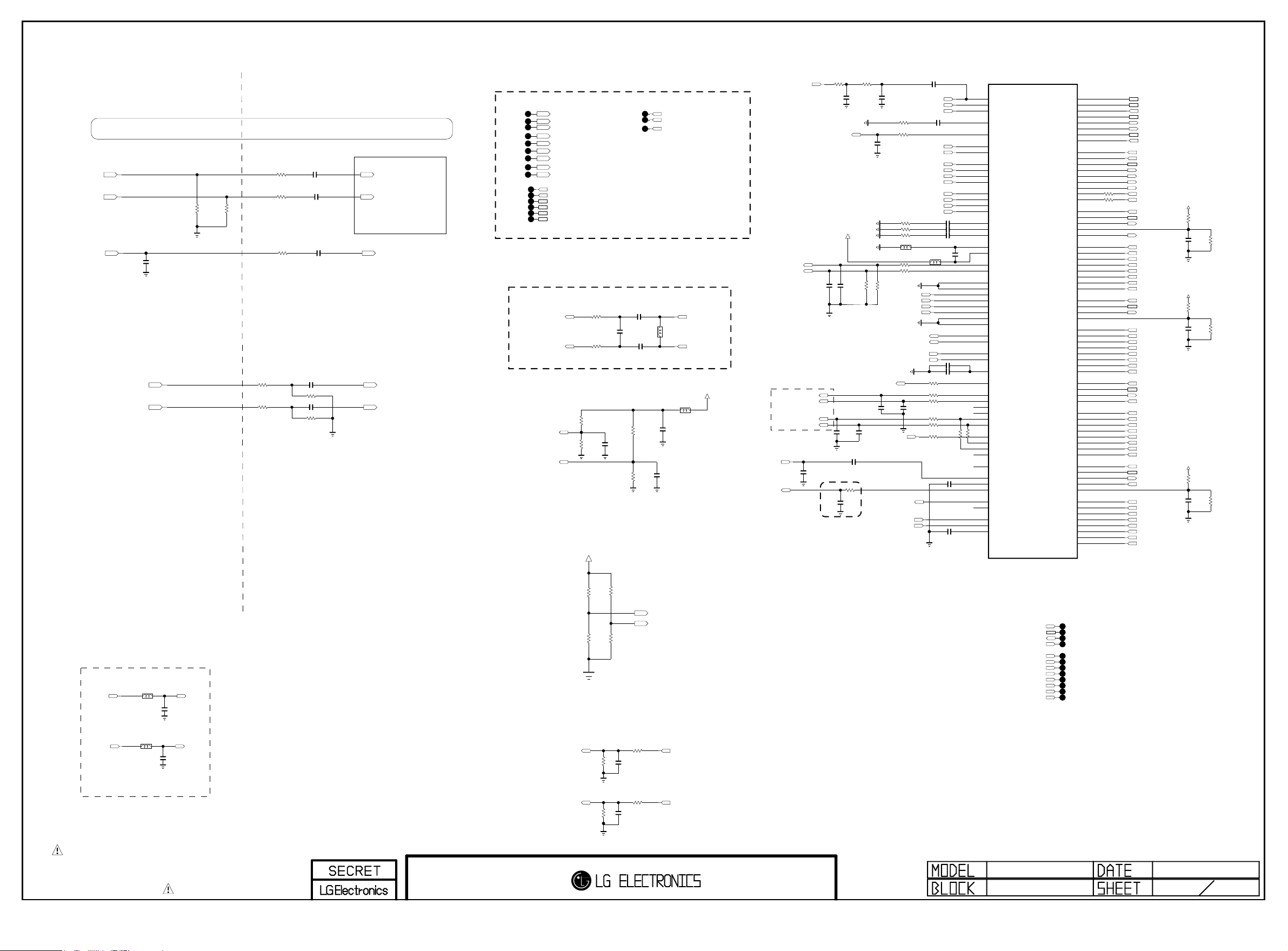

FE_DEMOD1_TS_DATA[0-7]

TPI_ERR

AMP_RESET_N

TP226

TP227

TP228

FE_DEMOD3_TS_CLK

FE_DEMOD3_TS_SYNC

FE_DEMOD3_TS_VAL

FE_DEMOD3_TS_DATA

TPI_DATA[0-7]

Near AMP

C200

1000pF

50V

R231

4.7K

CAM_SLIDE_DET

CAM_TRIGGER_DET

/RST_HUB

SC_DET

R226

100

1/16W

5%

LED_SDA

INSTANT_BOOT

LED_SCL

FE_DEMOD1_TS_CLK

FE_DEMOD1_TS_SYNC

FE_DEMOD1_TS_VAL

FE_DEMOD1_TS_ERROR

FE_DEMOD1_TS_DATA[7]

FE_DEMOD1_TS_DATA[6]

FE_DEMOD1_TS_DATA[5]

FE_DEMOD1_TS_DATA[4]

FE_DEMOD1_TS_DATA[3]

FE_DEMOD1_TS_DATA[2]

FE_DEMOD1_TS_DATA[1]

FE_DEMOD1_TS_DATA[0]

FE_DEMOD2_TS_CLK

FE_DEMOD2_TS_SYNC

FE_DEMOD2_TS_VAL

FE_DEMOD2_TS_ERROR

FE_DEMOD2_TS_DATA

TPI_DATA[0]

TPI_DATA[1]

TPI_DATA[2]

TPI_DATA[3]

TPI_DATA[4]

TPI_DATA[5]

TPI_DATA[6]

TPI_DATA[7]

MODEL_OPT_11

TP225

/RST_PHY

2D/3D_CTL

RF_SWITCH_CTL

/TU_RESET1

/TU_RESET2

BT_RESET

R224

OPT

33

CAM_SLIDE_DET

CAM_TRIGGER_DET

MODEL_OPT_12

/RST_HUB

COMP1_DET

AV1_CVBS_DET

IR_B_RESET

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10 EPI_LOCK8/6

SC_DET

HP_DET

OPC_EN

DEBUG

BIT0

BIT1

BIT2

BIT3

BIT4

BIT5

BIT6

BIT7

TPI_CLK

TPI_SOP

TPI_VAL

TPI_ERR

IC101

LG1311

AH30

TP_DVB_CLK

AH32

TP_DVB_SOP

AH31

TP_DVB_VAL

AH33

TP_DVB_ERR

AM33

TP_DVB_DATA7

AL32

TP_DVB_DATA6

AL33

TP_DVB_DATA5

AK32

TP_DVB_DATA4

AK33

TP_DVB_DATA3

AK31

TP_DVB_DATA2

AJ30

TP_DVB_DATA1

AJ31

TP_DVB_DATA0

AL31

STPI0_CLK

AN32

STPI0_SOP

AM32

STPI0_VAL

AN31

STPI0_ERR

AM31

STPI0_DATA

AH28

STPI1_CLK

AJ28

STPI1_SOP

AK30

STPI1_VAL

AJ29

STPI1_ERR

AG27

STPI1_DATA

A28

TPI_CLK

B28

TPI_SOP

B29

TPI_VAL

C28

TPI_ERR

A27

TPI_DATA0

B27

TPI_DATA1

C27

TPI_DATA2

B26

TPI_DATA3

C26

TPI_DATA4

B25

TPI_DATA5

A25

TPI_DATA6

C25

TPI_DATA7

AG13

GPIO31

AJ19

GPIO30

AG14

GPIO29

AG15

GPIO28

AJ15

GPIO27

AH19

GPIO26

AH18

GPIO25

AG19

GPIO24

AH5

GPIO23

AJ5

GPIO22

AJ6

GPIO21

AH6

GPIO20

AG6

AG24

AH16

AJ21

AH21

AG16

AJ24

AH17

AG17

AH13

AH15

AG18

AH14

AJ16

AH20

GPIO19

AG5

GPIO18

AF7

GPIO17

AG7

GPIO16

GPIO15

GPIO14

V29

GPIO13

GPIO12

GPIO11

V28

GPIO10

GPIO9

GPIO8

GPIO7

GPIO6

GPIO5

GPIO4

GPIO3

GPIO2

GPIO1

GPIO0

R225

OPT

33

TPIO_CLK

TPIO_SOP

TPIO_VAL

TPIO_ERR

TPIO_DATA0

TPIO_DATA1

TPIO_DATA2

TPIO_DATA3

TPIO_DATA4

TPIO_DATA5

TPIO_DATA6

TPIO_DATA7

EPI_SOE

EPI_MCLK

EPI_GCLK

EPI_EO

EPI_VST

TX_0N

TX_0P

TX_1N

TX_1P

TX_2N

TX_2P

TX_3N

TX_3P

TX_4N

TX_4P

TX_5N

TX_5P

TX_6N

TX_6P

TX_7N

TX_7P

TX_8N

TX_8P

TX_9N

TX_9P

TX_10N

TX_10P

TX_11N

TX_11P

TX_12N

TX_12P

TX_13N

TX_13P

TX_14N

TX_14P

TX_15N

TX_15P

TX_16N

TX_16P

TX_17N

TX_17P

TX_18N

TX_18P

TX_19N

TX_19P

TX_20N

TX_20P

TX_21N

TX_21P

TX_22N

TX_22P

TX_23N

TX_23P

TX_LOCKN

D28

E29

E28

F28

D27

E27

F27

E26

F26

E25

D25

F25

AA5

AB5

AA7

AA6

AB6

AK8

AL8

AK7

AL7

AM6

AN6

AK6

AL6

AK5

AL5

AN4

AN3

AM2

AM1

AM4

AM3

AL4

AL3

AK2

AK1

AK4

AK3

AJ4

AJ3

AH2

AH1

AH4

AH3

AG4

AG3

AF2

AF1

AF4

AF3

AE4

AE3

AD2

AD1

AD4

AD3

AC4

AC3

AB2

AB1

AB4

AB3

AA4

AA3

AM8

TPO_CLK

TPO_SOP

TPO_VAL

TPO_ERR

TPO_DATA[0]

TPO_DATA[1]

TPO_DATA[2]

TPO_DATA[3]

TPO_DATA[4]

TPO_DATA[5]

TPO_DATA[6]

TPO_DATA[7]

EPI_SOE

MCLK_SOC

GCLK_SOC

EO_SOC

GST_SOC

TXB4N/TX0N

TXB4P/TX0P

TXB3N/TX1NFE_DEMOD3_TS_ERROR

TXB3P/TX1P

TXBCLKN/TX2N

TXBCLKP/TX2P

TXB2N/TX3N

TXB2P/TX3P

TXB1N/TX4N

TXB1P/TX4P

TXB0N/TX5N

TXB0P/TX5P

TXD4N/TX12N

TXD4P/TX12P

TXD3N/TX13N

TXD3P/TX13P

TXDCLKN/TX14N

TXDCLKP/TX14P

TXD2N/TX15N

TXD2P/TX15P

TXD1N/TX16N

TXD1P/TX16P

TXD0N/TX17N

TXD0P/TX17P

TPO_DATA[0-7]

TXA4N/TX6N

TXA4P/TX6P

TXA3N/TX7N

TXA3P/TX7P

TXACLKN/TX8N

TXACLKP/TX8P

TXA2N/TX9N

TXA2P/TX9P

TXA1N/TX10N

TXA1P/TX10P

TXA0N/TX11N

TXA0P/TX11P

TXC4N/TX18N

TXC4P/TX18P

TXC3N/TX19N

TXC3P/TX19P

TXCCLKN/TX20N

TXCCLKP/TX20P

TXC2N/TX21N

TXC2P/TX21P

TXC1N/TX22N

TXC1P/TX22P

TXC0N/TX23N

TXC0P/TX23P

TPO_ERR

EPI_SOE

+3.3V_NORMAL

BIT0_1

R201 10K

BIT0_0

R202 10K

BIT [0/1]

0 / 0

0 / 1

1 / 0

1 / 1

TAIWAN/COLOM

CHINA/HONGKONG

ASIA/AFRICA

EU/CIS

BIT1_1

R203 10K

BIT1_0

R204 10K

ATSC

N/AMERICA

KOREA

S/AMERCIA

Model Option

BIT3_1

BIT2_1

R205 10K

R207 10K

BIT0

BIT1

BIT3_0

BIT2_0

R206 10K

R208 10K

JP

JAPAN

BIT4_1

R209 10K

BIT4_0

R210 10K

BIT5_1

R211 10K

BIT5_0

R212 10K

BIT2

BIT3

BIT4

BIT5

BACK-END OPTIONAREA OPTION

BIT[2/3/4/5]DVB

0 / 0 / 0 / 0

0 / 0 / 0 / 1

0 / 0 / 1 / 0

0 / 0 / 1 / 1

0 / 1 / 0 / 0

0 / 1 / 0 / 1

0 / 1 / 1 / 0

0 / 1 / 1 / 1

1 / 0 / 0 / 0

1 / 0 / 0 / 1

1 / 0 / 1 / 0

1 / 0 / 1 / 1

1 / 1 / 0 / 0

1 / 1 / 0 / 1

1 / 1 / 1 / 0

1 / 1 / 1 / 1

BIT6_1

R213 10K

BIT [6/7]

BIT7_1

R215 10K

0 / 0

0 / 1

1 / 0

1 / 1

EU/CIS

T/C

T2/C/S2/ATV_EXT

T2/C

T2/C/S2/ATV_SOC

BIT6

BIT7

BIT6_0

BIT7_0

R214 10K

R216 10K

TYPE

EPI FHD, 120Hz, V14 (8 lane)

EPI FHD, 120Hz, v14_32inch (6 lane)

EPI FHD, 120Hz, V13 (6 lane)

EPI FHD, 120Hz, V12 (6 lane)

EPI FHD, 60Hz, V14_32 inch (6lane)

LVDS FHD, 120Hz

LVDS FHD, 60Hz

LVDS HD, 60Hz

LVDS FHD, 60Hz, CP BOX

LVDS HD, 60Hz SMALL SMART

Vby1 FHD, 120Hz

LVDS FHD, 120Hz OLED

FRC

FHD

PANEL TYPE

OLED

AJJA

T/C

T2/C/ATV_EXT

T2/C/ATV_SOC

T2/C/S2

DDR3_DDP

R219 10K

R217 10K

DDR3_1.5GB

DDR3_2GB

R220 10K

R218 10K

DDR3_NON_DDP

TAIWAN/COL

T/C

T2/C PIP

T2/C

DDR_3G

R221 10K

R222 10K

NON_DDR_3G

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

MODEL_OPT_11

MODEL_OPT_12

BRAZILKOREA

ISDB PIP

ISDB

ATV_SOC

ATV_EXT

OPT

R227 10K

NORTH AMERICA

ATSC PIP

ATV_SOC

ATV_EXT

OPT

R229 10K

CHINA/HONG

Default Default

ATSC PIP

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

OPT

OPT

R230 10K

R228 10K

DDR3

DDR3

FOR UD

LOW

NON_DDP

NON_DDR3 3G

HIGH

DDP

1.5GB

2GB

DDR3 3G

JAPAN

MODEL_OPT_11

MODEL_OPT_12

FE_DEMOD2_TS_CLK

FE_DEMOD2_TS_SYNC

FE_DEMOD2_TS_VAL

FE_DEMOD2_TS_ERROR

FE_DEMOD2_TS_DATA

FE_DEMOD3_TS_CLK

FE_DEMOD3_TS_SYNC

FE_DEMOD3_TS_VAL

FE_DEMOD3_TS_ERROR

FE_DEMOD3_TS_DATA

TPI_DATA[0-7]

TPO_DATA[0-7]

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

M14-Display In/Out

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

TPI_CLK

TPI_SOP

TPI_VAL

TPO_CLK

TPO_SOP

TPO_VAL

TP202

TP203

TP204

TP205

TP206

TP207

TP208

TP209

TP210

TP211

TP212

TP213

TP214

TP215

TP221

TP218

TP219

TP220

DEBUG

+3.3V_NORMAL

SW201

JTP-1127WEM

12

3

4

For ISP

R223

3.3K

MID_LG1311

M14 Symbol B

2013.04.04

2

31

PLACE AT JACK SIDE

Copyright © 2014 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Place JACK Side

AV1_CVBS/COMP1_Y Circuit was moved to 34Page

COMP1_Pb

COMP1_Pr

TU_CVBS

COMP1/AV1/DVI_L_IN

COMP1/AV1/DVI_R_IN

C303

150pF

50V

OPT

1005

75

1%

R318

1005

1%

75

R326

Place SOC Side

33

R333

R335 33

TU_ALL_2178B

R329 100

AUDIO IN

R309 27K

R310 27K

C316 4.7uF

1%

C317 4.7uF

1%

C322 0.047uF

C324 0.047uF

C318 0.047uF

R322 10K

1%

R323 10K

1%

TU_ALL_2178B

COMP2_PB_IN_SOC

COMP2_PR_IN_SOC

TU_CVBS_SOC

AUAD_L_CH3_IN

AUAD_R_CH3_IN

COMP

TP308

TP310

TP311

TP312

TP313

TP314

TP315

TP316

TP317

TP302

TP303

TP304

TP305

TP306

TP307

SC_CVBS_IN_SOC

SC_FB_SOC

SC_ID_SOC

COMP1_PB_IN_SOC

COMP1_Y_IN_SOC

COMP1_Y_IN_SOC_SOY

COMP1_PR_IN_SOC

AUAD_L_CH2_IN

AUAD_R_CH2_IN

SMARTCARD_DATA/SD_EMMC_CLK

SMARTCARD_VCC/SD_EMMC_CMD

SMARTCARD_DET/SD_EMMC_DATA[3]

SMARTCARD_RST/SD_EMMC_DATA[2]

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

SMARTCARD_CLK/SD_EMMC_DATA[0]

TP318

TP319

TP320

Placed as close as possible to LG1311

Tuner IF Filter

ADC_I_INN

ADC_I_INP

TU_ALL_IntDemod

To ADC

TU_ALL_IntDemod

R344

51

R345

51

TU_ALL_IntDemod

C332

0.01uF

C331

22pF

TU_ALL_IntDemod

0.01uF

TU_ALL_IntDemod

C333

Placed as close as possible to IC101

R37 4

51K

AUAD_L_REF

1%

R37 8

47K

1%

C313

4.7uF

10V

AUAD_R_REF

DDR3 VENDOR OPTION

+3.3V_NORMAL

R38 0

51K

1%

R38 1

47K

1%

SCART_LOUT_SOC

SCART_ROUT_SOC

DTV/MNT_V_OUT_SOC

IF_N

L303

OPT

IF_P

AVDD25

L307

120-ohm

C354

10uF

10V

C353

4.7uF

10V

SOC_CVBS_OUT

SCART_LOUT_SOC

SCART_ROUT_SOC

TUNER_SIF

IF_AGC

AUD_MASTER_CLK

AUD_LRCH

AUD_SCK

AUD_LRCK

MAIN I2S_I/F

OPT

INT_ADEMOD

R11022

390

INT_ADEMOD

DTV/MNT_V_OUT_SOC

AVDD25

EU

C334

0.01uF

50V

C335

22pF

OPT

TU_ALL_2178B

C312 0.1uF

C309

1000pF

50V

C338

0.1uF

OPT

Close to IC101

INT_ADEMOD

R11023

390

INT_ADEMOD

C11009

68pF

50V

OPT

EU

C336

0.01uF

EU

50V

R351 22K

SPDIF_OUT

C337

33pF

OPT

TU_ALL_IntDemod

R350

470

SOC_CVBS_OUT

C11010

68pF

50V

R356

R353 0

C339

100pF

50V

COMP1_Y_IN_SOC_SOY

COMP2_Y_IN_SOC_SOY

R357 68

R358 68

R359 68

BLM15BD121SN1

R354 0

R355 0

EU

AUAD_L_CH2_IN

AUAD_R_CH2_IN

R352 22K

AUAD_L_CH3_IN

AUAD_R_CH3_IN

C340

22pF

OPT

I2S_AMP

ADC_I_INP