LG 50PK550-SA Schematic

PLASMA TV

SERVICE MANUAL

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

CHASSIS : PB01A

MODEL : 50PK550 50PK550-SA

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

Internal Use Only

Printed in Korea

P/NO : MFL63141001(1005-REV00)

- 2 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

CONTENTS

CONTENTS ............................................................................................................................... 2

SAFETY PRECAUTIONS...........................................................................................................3

SPECIFICATION.........................................................................................................................4

ADJUSTMENT INSTRUCTION..................................................................................................6

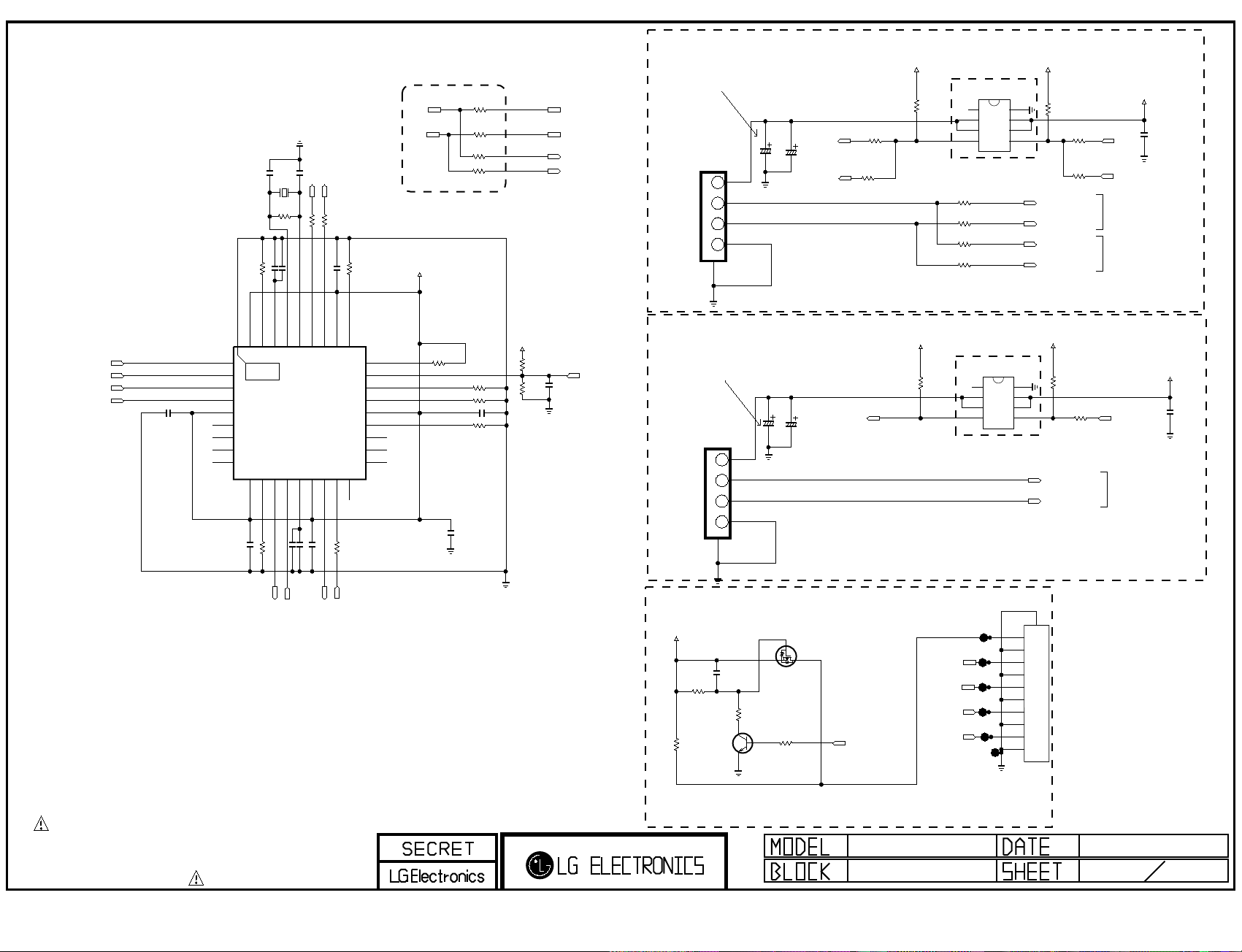

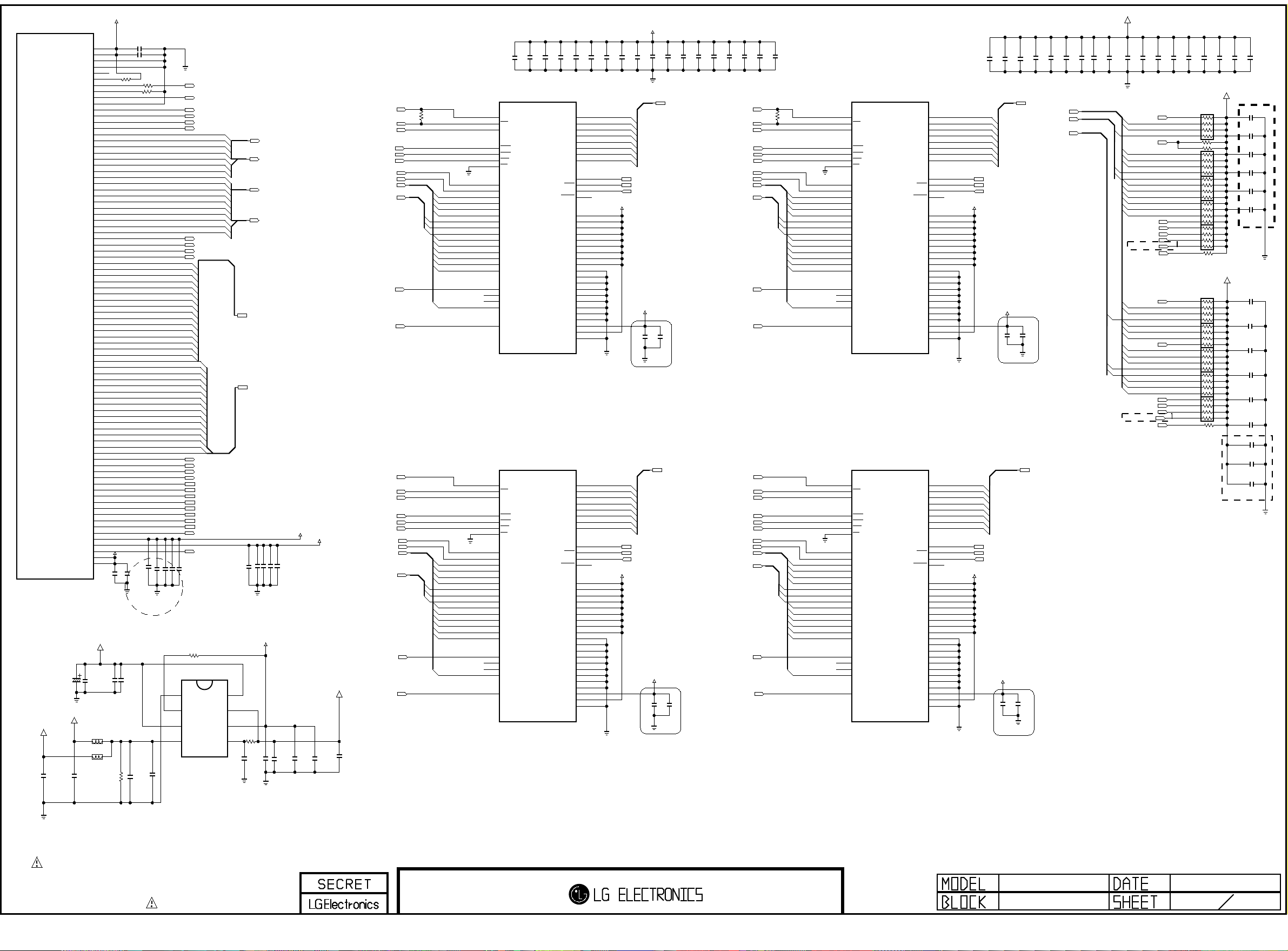

BLOCK DIAGRAM ...................................................................................................................14

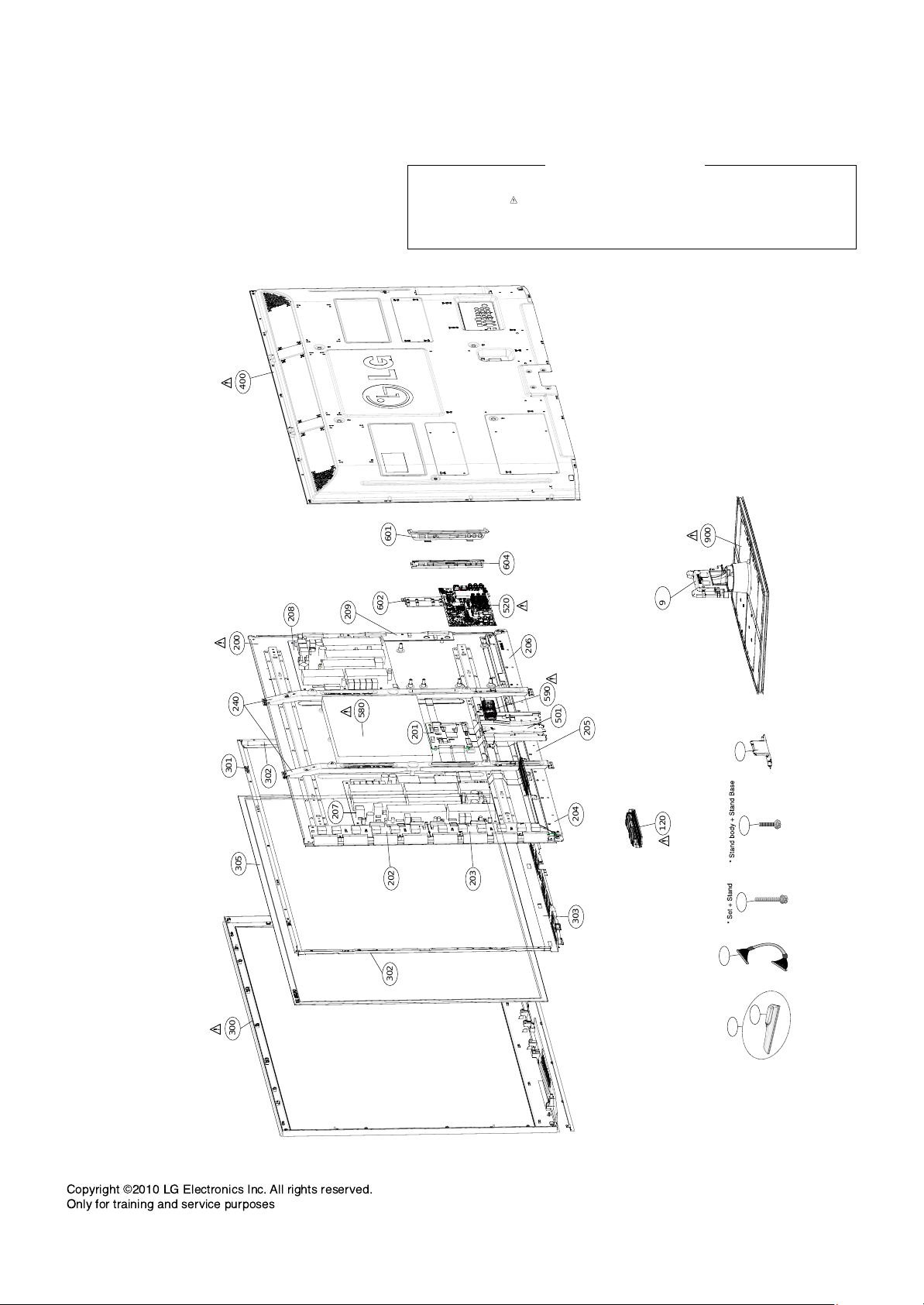

EXPLODED VIEW ...................................................................................................................15

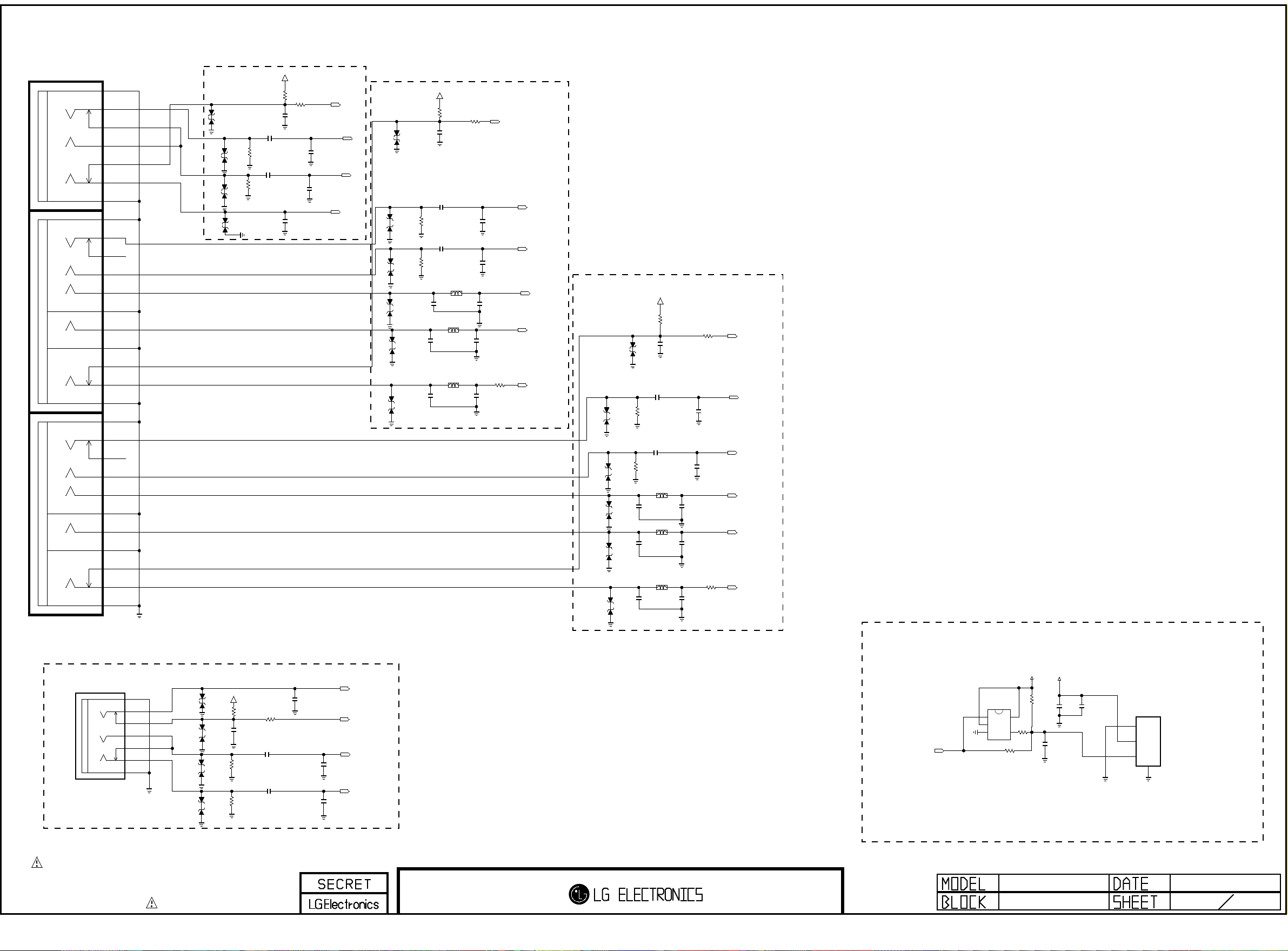

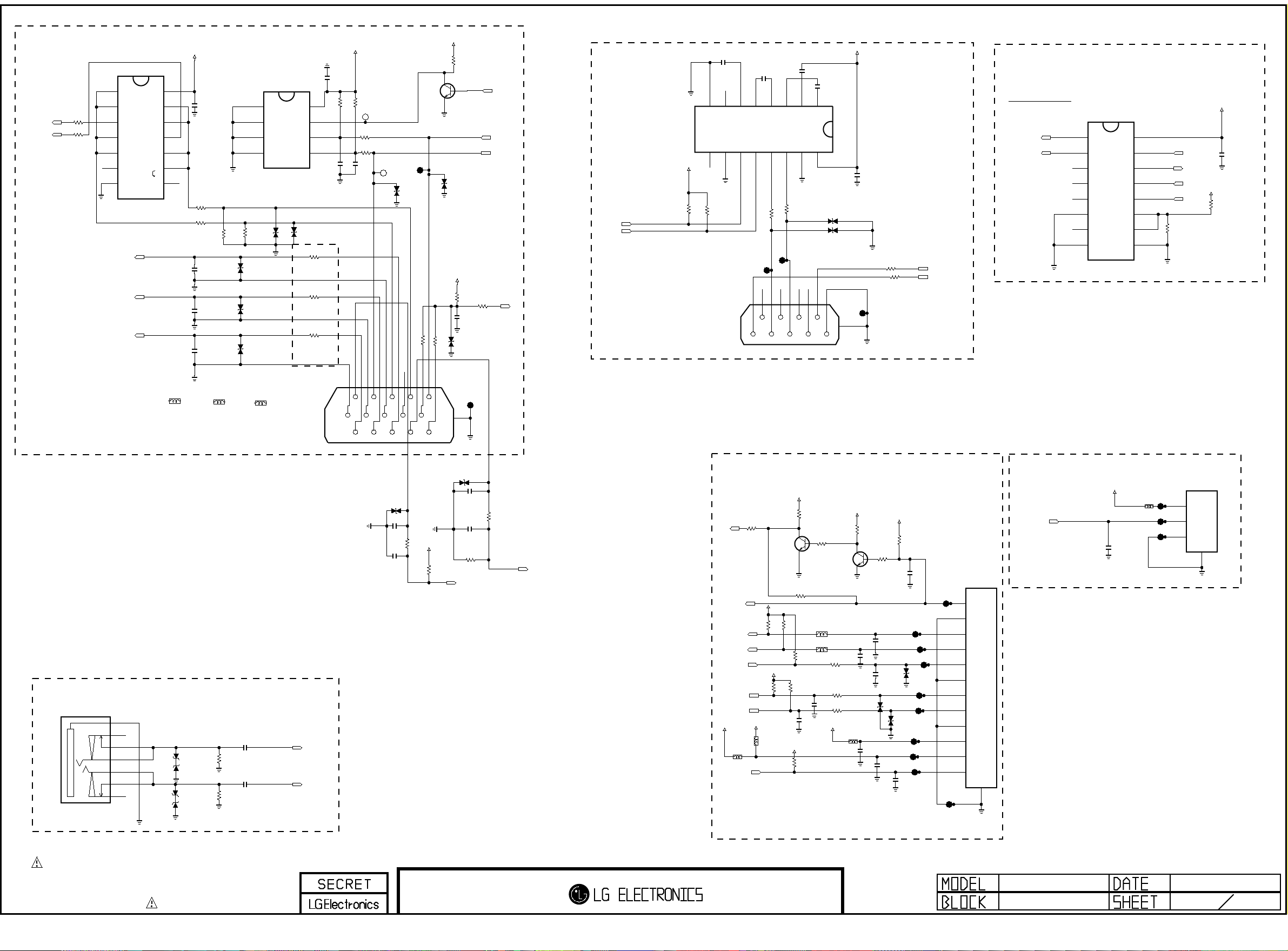

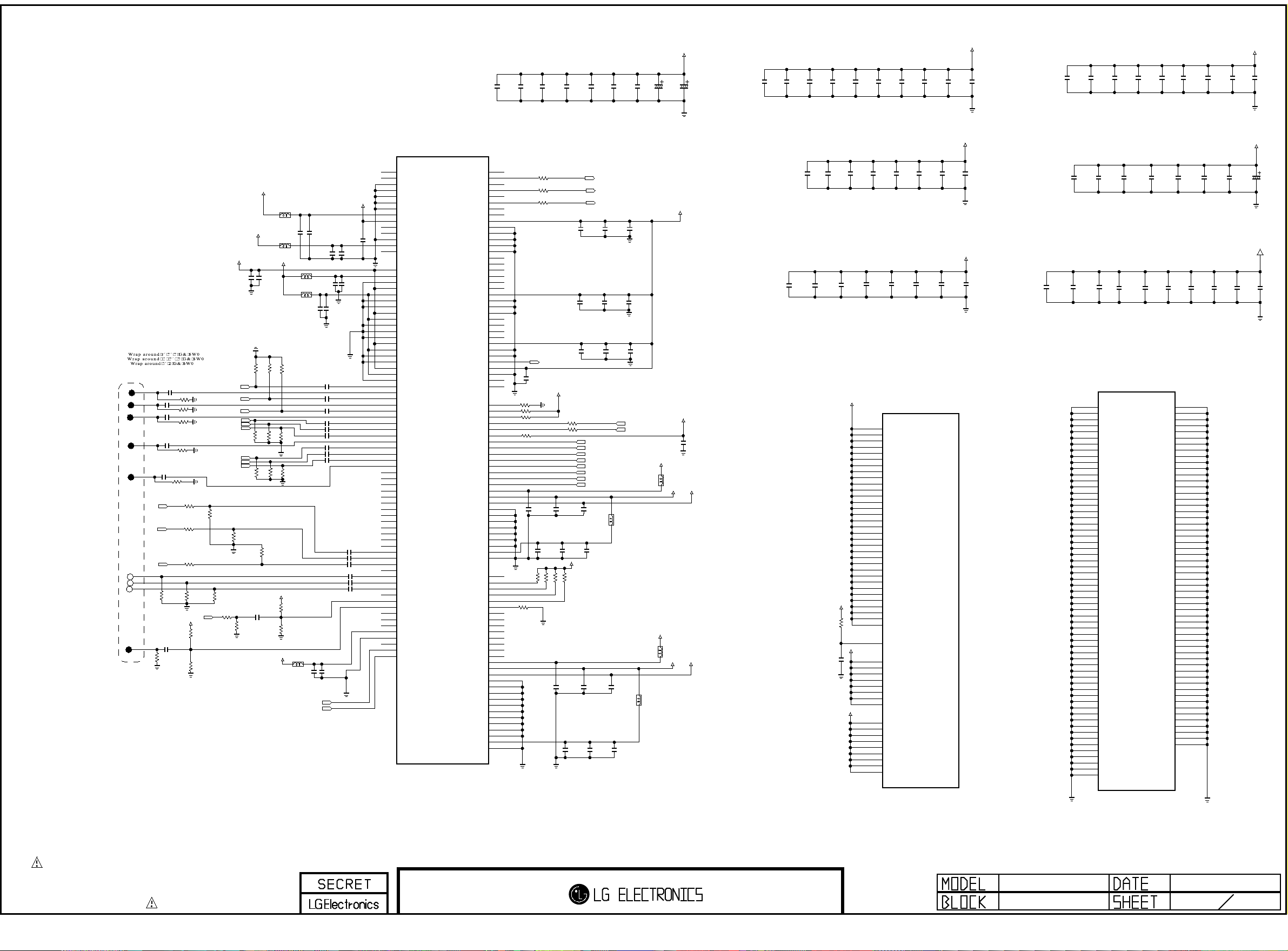

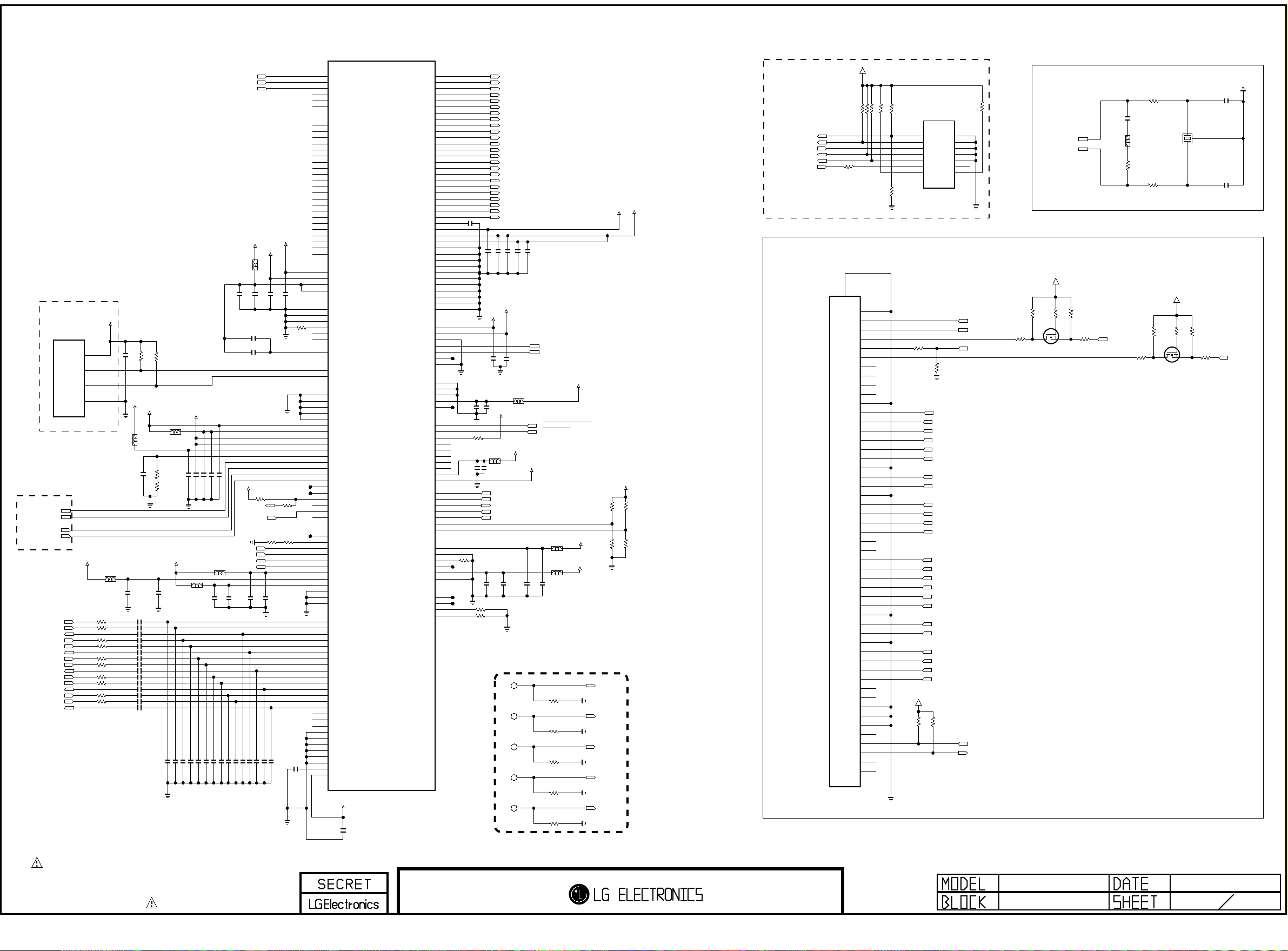

SVC. SHEET ................................................................................................................................

- 3 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

SAFETY PRECAUTIONS

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in

the Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to

prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of the circuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this monitor is blown, replace it

with the specified.

When replacing a high wattage resistor (Oxide Metal Film

Resistor, over 1W), keep the resistor 10mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Due to high vacuum and large surface area of picture tube,

extreme care should be used in handling the Picture Tube.

Do not lift the Picture tube by it's Neck.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect

an electrical jumper across the two AC plug prongs. Place the

AC switch in the on position, connect one lead of ohm-meter to

the AC plug prongs tied together and touch other ohm-meter

lead in turn to each exposed metallic parts such as antenna

terminals, phone jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1MΩ and 5.2MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

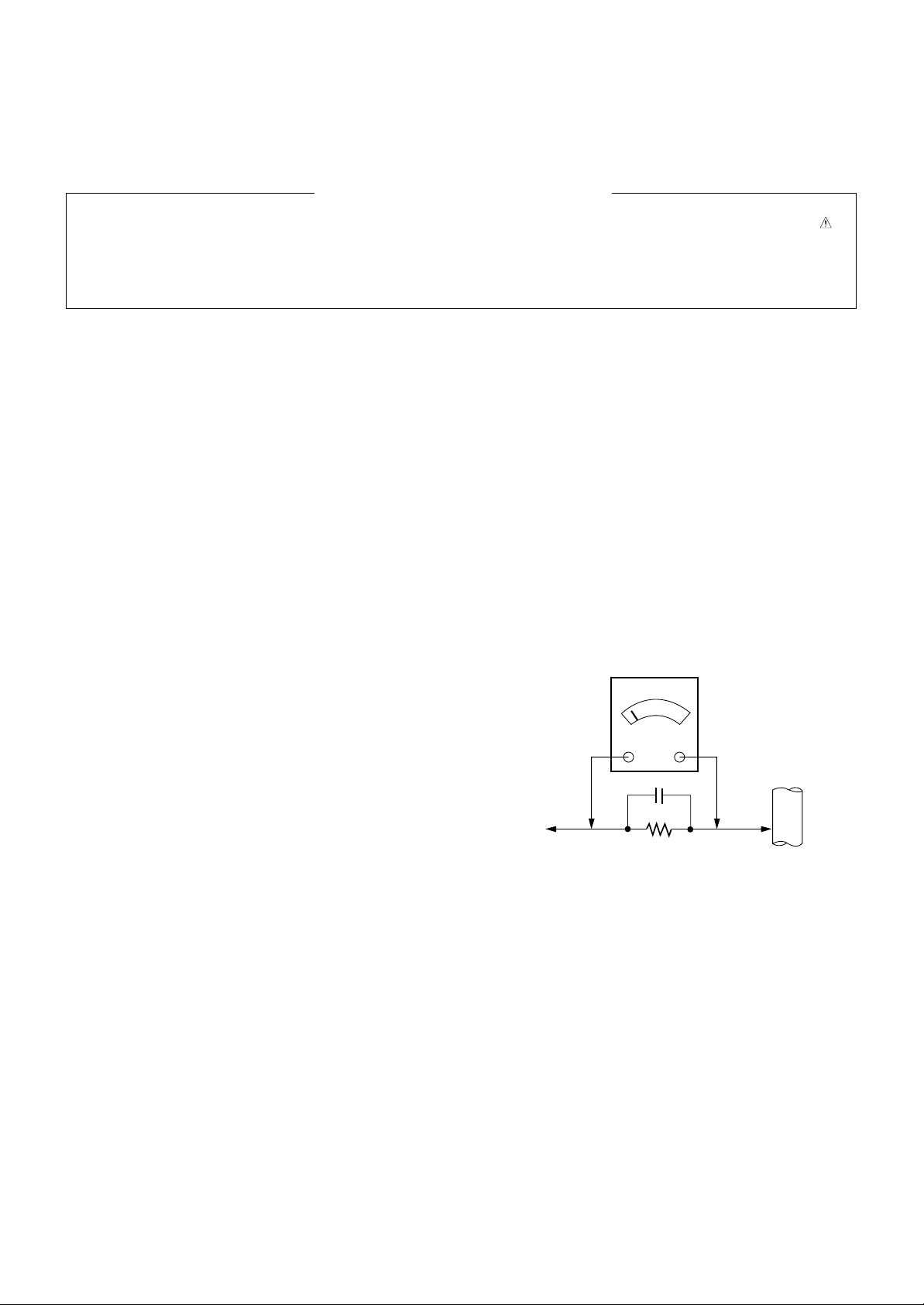

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5K/10watt resistor in parallel with a 0.15uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC

voltage measurements for each exposed metallic part. Any

voltage measured must not exceed 0.75 volt RMS which is

corresponds to 0.5mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

1.5 Kohm/10W

To Instrument's

exposed

METALLIC PARTS

Good Earth Ground

such as WATER PIPE,

CONDUIT etc.

AC Volt-meter

IMPORTANT SAFETY NOTICE

0.15uF

- 4 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

SPECIFICATIONS

NOTE : Specifications and others are subject to change without notice for improvement

.

1. Application Range

(1) This spec sheet is applied all of PDP TV with PB01A chassis.

2. Specification

Each part is tested as below without special appointment.

(1) Temperature : 25 °C ± 5 °C (77 °F ± 9 °F), CST : 40 °C ± 5 °C

(2) Relative Humidity : 65 % ± 10 %

(3) Power Voltage : Standard input voltage (100 V - 240 V ~ 50 / 60 Hz)

* Standard Voltage of each product is marked by models

(4) Specification and performance of each parts are followed each drawing and specification by part number in accordance with

BOM.

(5) The receiver must be operated for about 5 minutes prior to the adjustment.

3. Test Method

(1) Performance : LGE TV test method followed.

(2) Demanded other specification

Safety: UL, CSA, IEC specification, CE

EMC : FCC, ICES, IEC specification, CE

Model Name Market Brand

50PK550-SA Brazil LG

Model Name Market Appliance

50PK550-SA Brazil Safety : IEC/EN60065

- 5 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

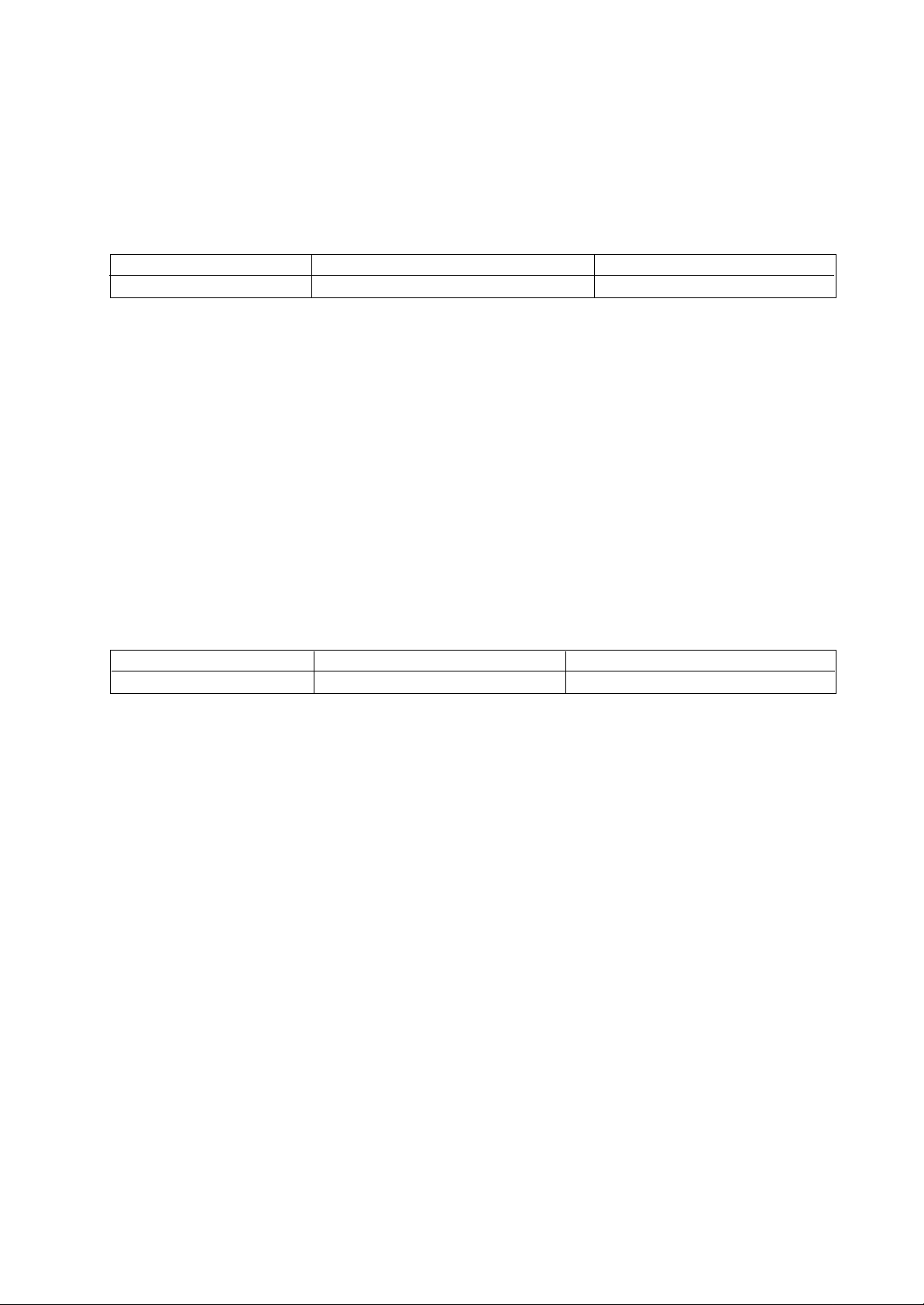

4. General Specification

No Item Specification Model Remark

1. Receiving System 1) SBTVD / NTSC / PAL-M / PAL-N PK550, PK950

2) NTSC / PAL-M / PAL-N PK950R Analog model

2. Available Channel 1) VHF : 02~13 PK550, PK950

2) UHF : 14~69

3) DTV : 07-69 (VHF high/UHF)

4) CATV : 02~135

1) VHF : 02~13 PK950R Analog model

2) UHF : 14~69

3) CATV : 02~135

3. Input Voltage 1)AC 100 V ~ 240 V 50 / 60 Hz

4. Market BRAZIL PK550, PK950

Latin America PK950R

5. Screen Size 50 inch Wide(1920 X1080) 50PK550-SA, 50PK950-SA

50PK950R-MA

60 inch Wide(1920 X 1080) 60PK550-SA, 60PK950-SA

6. Aspect Ratio 16:9 60PK950R-MA

7. Tuning System FS

8. Module PDP50R1#### (1920 X 1080) 50PK550-SA, 50PK950-SA

50PK950R-MA

PDP60R1#### (1920 X 1080) 60PK550-SA, 60PK950-SA

60PK950R-MA

9. Operating Environment 1) Temp : 0 deg ~ 40 deg

2) Humidity : ~ 80 %

10. Storage Environment 1) Temp : -20 deg ~ 60 deg

2) Humidity : 0 % ~ 90 %

- 6 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

ADJUSTMENT INSTRUCTION

1. Application Range

This spec. sheet applies to PB01A Chassis applied PDP TV

all models manufactured in TV factory.

2. Specification

(1) Because this is not a hot chassis, it is not necessary to use

an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order. But it is

flexible when its factory local problem occurs.

(3) The adjustment must be performed in the circumstance of

25 cC ± 5 cC of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep 100 V - 240 V,

50 / 60 Hz.

(5) Before adjustment, execute Heat-Run for 5 minutes.

V After Receive 100% Full white pattern (06CH) then

process Heat-run

(or “8. Test pattern” condition of Ez-Adjust status)

V How to make set white pattern

1) Press Power ON button of Service Remocon

2) Press ADJ button of Service remocon. Select “10.

Test pattern” and, after select “White” using

navigation button, and then you can see 100% Full

White pattern.

* In this status you can maintain Heat-Run useless any

pattern generator

* Notice: if you maintain one picture over 20 minutes

(Especially sharp distinction black with white pattern –

13Ch, or Cross hatch pattern – 09Ch) then it can

appear image stick near black level.

3. Adjustment items

3-1. PCB Assembly adjustment

(1) Adjust 480i Comp1

(2) Adjust 1080p Comp1/RGB

- If it is necessary, it can adjustment at Manufacture Line

- You can see set adjustment status at “9. ADJUST

CHECK” of the “In-start menu”

3-2. Set Assembly Adjustment

(1) EDID (The Extended Display Identification Data )

(2) Color Temperature (White Balance) Adjustment

(3) Make sure RS-232C control

(4) Selection Factory output option

4. PCB Assembly Adjustment

4-1. Using RS-232C

- Adjust 3 items at 3-1 PCB assembly adjustments

“ (3) Adjustment sequence” one after the order.

(1) Adjustment protocol

(2) Necessary items before Adjustment items

O Pattern Generator : (MSPG-925FA)

O Adjust 480i Comp1

(MSPG-925FA:model :209, pattern :65) – Comp1 Mode

O Adjust 1080p Comp1

(MSPG-925FA:model :225 , pattern :65) – Comp1 Mode

O Addjust RGB (MSPG-925FA:model :225 , pattern :65)

– RGB-PC Mode

* If you want more information then see the below Adjustment

method (Factory Adjustment)

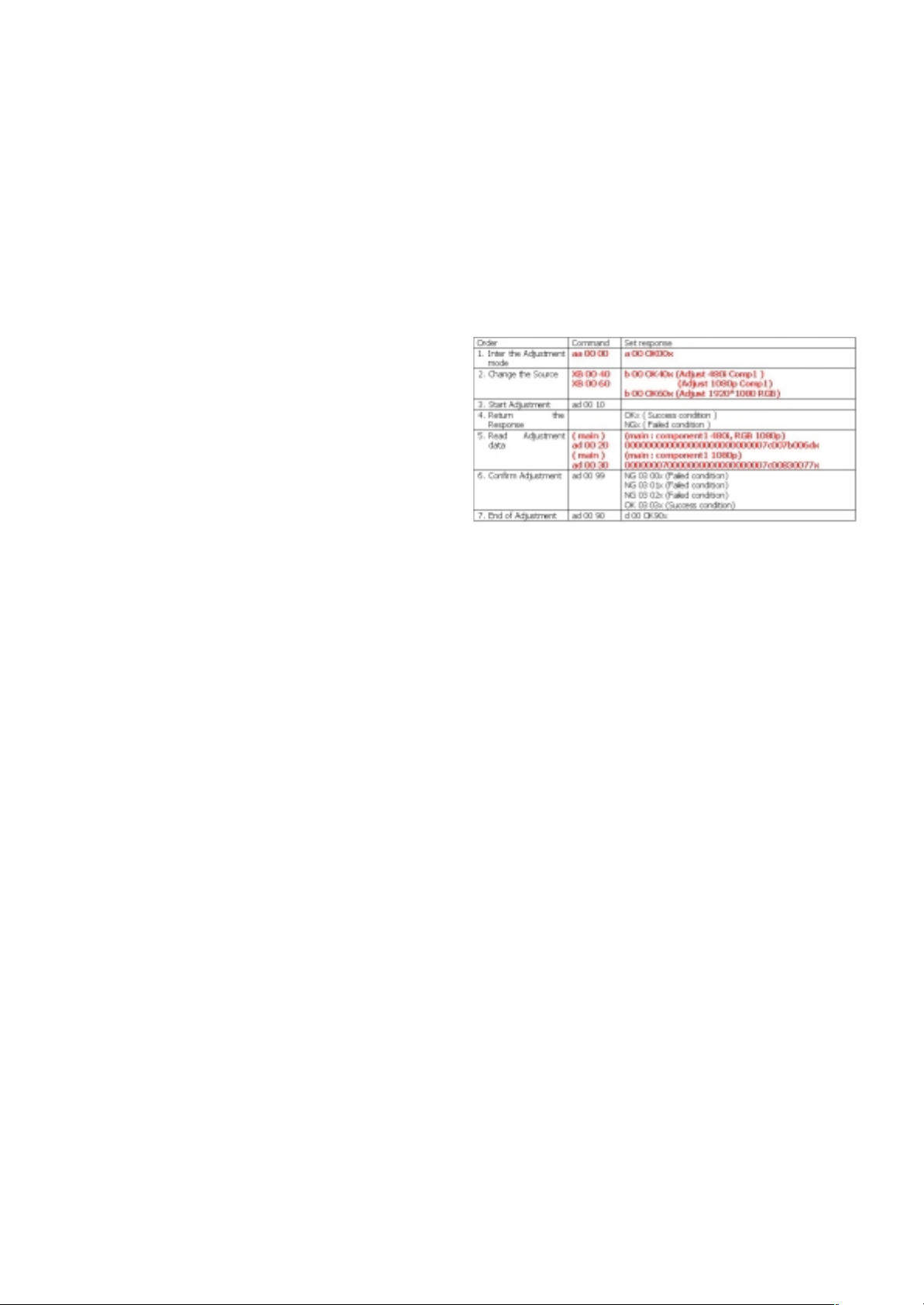

(3) Adjustment sequence

O aa 00 00: Enter the ADC Adjustment mode.

O xb 00 40: Change the mode to Component1 (No actions)

O ad 00 10: Adjust 480i Comp

O ad 00 10: Adjust 1080p comp

O xb 00 60: Change to RGB-PC mode(No action)

O ad 00 10: Adjust 1080p RGB

O xb 00 90: Endo of Adjustmennt

< See ADC Adjustment RS232C Protocol_Ver1.0 >

5. Factory Adjustment

PB01A : USE EXTERNAL ADC(BCM) : using instrument.

PB02A : USE INTERNAL ADC(S7) : using internal pattern.

5-1. Auto Adjust Component

480i/1080p RGB 1080p

(1) Summary : Adjustment component 480i/1080i and RGB

1080p is Gain and Black level setting at Analog

to Digital converter, and compensate the RGB

deviation

(2) Using instrument

1) Adjustment remocon, 801GF(802B, 802F, 802R) or

MSPG925FA pattern generator

(It can output 480i/1080i horizontal 100 % color bar

pattern signal, and its output level must setting

0.7 V ± 0.1 V p-p correctly)

* You must make it sure its resolution and pattern cause every

instrument can have different setting

2) Adjustment method 480i Comp1, Adjust 1080p

Comp1/RGB (Factory adjustment)

O ADC 480i Component1 adjustment -

- Check connection of Component1

- MSPG-925FA Ë Model: 209, Pattern 65

O Set Component 480i mode and 100% Horizontal

Color Bar Pattern(HozTV31Bar), then set TV set to

Component1 mode and its screen to “NORMAL”

O ADC 1080p Component1 / RGB adjustment

- Check connection both of Component1 and RGB

- MSPG-925FA Ë Model: 225, Pattern 65

O Set Component 1080p mode and 100% Horizontal

Color Bar Pattern(HozTV31Bar), then set TV set to

Component1 mode and its screen to “NORMAL”

O After get each the signal, wait more a second and

enter the “IN-START” with press IN-START key of

Service remocon. After then select “7. External ADC”

with navigator button and press “Enter”.

O After Then Press key of Service remocon “Right

Arrow(VOL+)”

O You can see “ADC Component1 Success”

O Component1 1080p, RGB 1080p Adjust is same

method.

O Component 1080p Adjustment in Component1 input

mode

O RGB 1080p adjustment in RGB input mode

O If you success RGB 1080p Adjust. You can see “ADC

RGB-DTV Success”

Caution : Set Volume 0 after adjustment

5-2. Use Internal ADC(S7)

- ADJ(EZ ADJUST) -> 6.ADC Calibration -> ADC

Calibration(START)

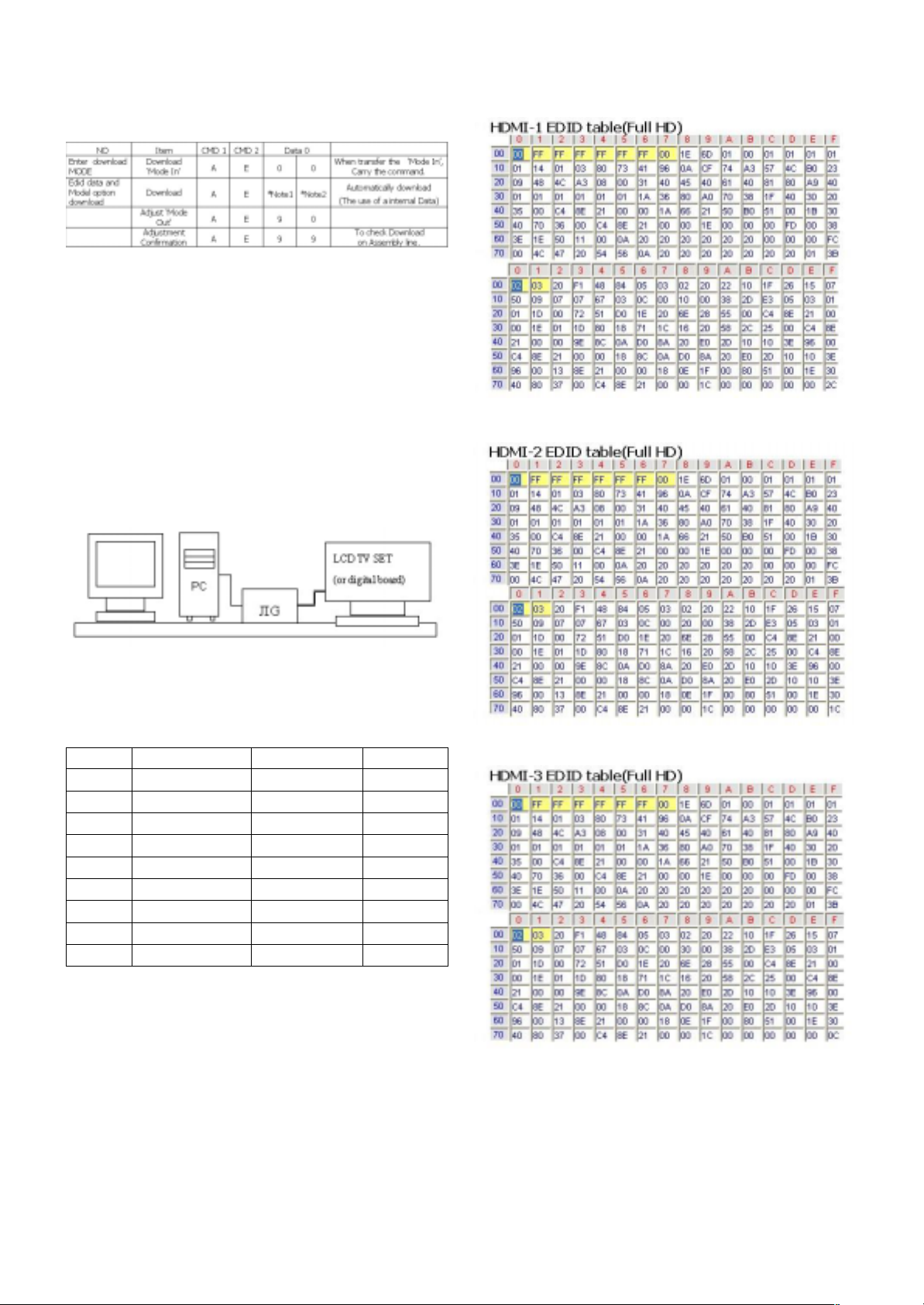

5-3. EDID(The Extended Display

Identification Data) / DDC(Display Data

Channel) download

(1) Summary

1) It is established in VESA, for communication between

PC and Monitor without order from user for building user

condition. It helps to make easily use realize “Plug and

Play” function.

2) For EDID data write, we use DDC2B protocol.

5-4. Auto Download

(1) After enter Service Mode by pushing “ADJ” key,

(2) Enter EDID D/L mode.

(3) Enter “START” by pushing “OK” key.

Caution

- Never connect HDMI & D-sub Cable when the user

downloading .

- Use the proper cables below for EDID Writing.

- 7 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

< Adjustment pattern : 480i / 1080p 60Hz Pattern >

* Edid data and Model option download(RS232)

5-5. Manual Download

(1) Write HDMI EDID data

1) Using instruments

- Jig. (PC Serial to D-Sub connection) for PC, DDC

adjustment.

- S/W for DDC recording (EDID data write and read)

- D-sub jack

- Additional HDMI cable connection Jig.

2) Preparing and setting.

- Set instruments and Jig. Like pic.5), then turn on PC

and Jig.

- Operate DDC write S/W (EDID write & read)

- It will operate in the DOS mode.

- EDID data (Model name = LG TV)

- 2010 EDID DATA CHECK SUM.

- 8 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

BLOCK(0) BLOCK(1)

HD HDMI1 3B 2C

HDMI2 3B 1C

HDMI3 3B 0C

RGB A3

FHD HDMI1 3B 2C

HDMI2 3B 1C

HDMI3 3B 0C

HDMI4 3B FC

RGB A3

< For write EDID data, setting Jig and another instruments >

- 9 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

* See Working Guide if you want more information about EDID

communication.

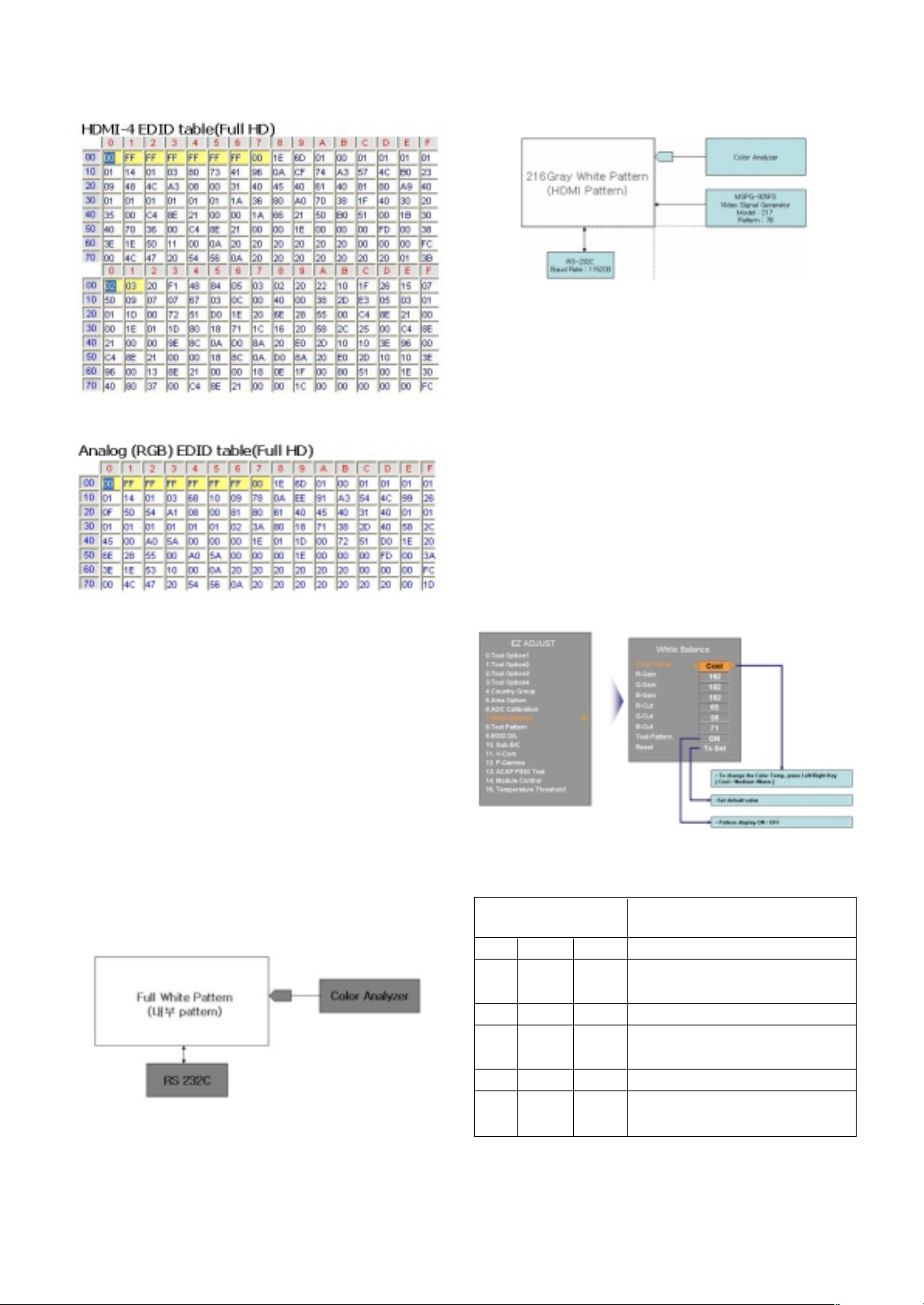

5-6. Adjustment Color Temperature

(White balance)

(1) Using Instruments

1) Color Analyzer: CA-210 (CH 9)

- Using LCD color temperature, Color Analyzer (CA-210)

must use CH 9, which Matrix compensated (White,

Red, Green, Blue compensation) with CS-2100. See

the Coordination bellowed one.

2) Auto-adjustment Equipment (It needs when Autoadjustment – It is availed communicate with RS-232C :

Baud rate: 115200)

3) Video Signal Generator MSPG-925F 720p, 216Gray

(Model: 217, Pattern 78)

(2) Connection Diagram (Auto Adjustment)

1) Using Inner Pattern

2) Using HDMI input

(3) White Balance Adjustment

- If you can’t adjust with inner pattern, then you can adjust it

using HDMI pattern. You can select option at “Ez-Adjust

Menu – 7. White Balance” there items “NONE, INNER,

HDMI”. It is normally setting at inner basically. If you can’t

adjust using inner pattern you can select HDMI item, and

you can adjust.

- In manual Adjust case, if you press ADJ button of service

remocon, and enter “Ez-Adjust Menu – 7. White Balance”,

then automatically inner pattern operates. (In case of

“Inner” originally “Test-Pattern. On” will be selected in The

“Test-Pattern. On/Off”.

O Connect all cables and equipments like Pic.5)

O Set Baud Rate of RS-232C to 115200. It may set

115200 orignally.

O Connect RS-232C cable to set

O Connect HDMI cable to set

V RS-232C COMMAND(Commonly apply)

< Connection Diagram for Adjustment White balance >

RS-232C COMMAND

[CMD ID DATA] Meaning

wb 00 00 White Balance adjustment start.

wb 00 10 Start of adjust gain

(Inner white pattern)

wb 00 1f End of gain adjust

wb 00 20 Start of offset adjust

(Inner white pattern)

wb 00 2f End of offset adjust

wb 00 ff End of White Balance adjust

(Inner pattern disappeared)

- 10 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

O wb 00 00”: Start Auto-adjustment of white balance.

O “wb 00 10”: Start Gain Adjustment (Inner pattern)

O “jb 00 c0” :

O …

O “wb 00 1f”: End of Adjustment

* If it needs, offset adjustment (wb 00 20-start, wb 00 2f-

end)

O “wb 00 ff”: End of white balance adjustment (inner pattern

disappear)

V Adjustment Mapping information

O When Color temperature (White balance) Adjustment

(Automatically)

- Press “Power only key” of service remocon and

operate automatically adjustment.

- Set BaudRate to 115200.

O You must start “wb 00 00” and finish it “wb 00 ff”.

O If it needs, then adjustment “Offset”.

(4) White Balance Adjustment (Manual adjustment)

1) Test Equipment: CA-210

- Using PDP color temperature, Color Analyzer (CA-210)

must use CH 10, which Matrix compensated (White,

Red, Green, Blue compensation) with CS-2100. See

the Coordination bellowed one.

2) Manual adjustment sequence is like bellowed one.

- Turn to “Ez-Adjust” mode with press ADJ button of

service remocon.

- Select “10.Test Pattern” with CH+/- button and press

enter. Then set will go on Heat-run mode. Over 30

minutes set let on Heat-run mode.

- Let CA-210 to zero calibration and must has gap more

10cm from center of PDP module when adjustment.

- Press “ADJ” button of service remocon and select

“7.White-Balance” in “Ez-Adjust” then press “

G” button

of navigation key. (When press “

G” button then set will

go to full white mode)

- Adjust at three mode (Cool, Medium, Warm)

- If “cool” mode

Let B-Gain to 192 and R, G, B-Cut to 64 and then

control R, G gain adjustment High Light adjustment.

- If “Medium” and “Warm” mode Let R-Gain to 192 and

R, G, B-Cut to 64 and then control G, B gain

adjustment High Light adjustment.

- All of the three mode

Let R-Gain to 192 and R, G, B-Cut to 64 and then

control G, B gain adjustment High Light adjustment.

- With volume button (+/-) you can adjust.

- After all adjustment finished, with Enter (_ key) turn to

Ez-Adjust mode. Then with ADJ button, exit from

adjustment mode

* Attachment: White Balance adjustment coordination and color

temperature.

O Using CS-1000 Equipment.

- COOL : T=11000K, _uv=0.000, x=0.276 y=0.283

- MEDIUM : T=9300K, _uv=0.000, x=0.285 y=0.293

- WARM : T=6500K, _uv=0.000, x=0.313 y=0.329

O Using CA-210 Equipment. (10 CH)

- Contras value : 216 Gray

- Brighness spec.

6. Test of RS-232C control.

- Press In-Start button of Service Remocon then set the “4.Baud

Rate” to 115200. Then check RS-232C control and

7. Selection of Country option.

- Selection of country option is allowed only North American

model (Not allowed Korean model). It is selection of Country

about Rating and Time Zone.

(1) Models: All models which PB82C Chassis (See the first

page.)

(2) Press “In-Start” button of Service Remocon, then enter the

“Option” Menu with “PIP CH-“ Button

(3) Select one of these three (USA, CANADA, MEXICO)

defends on its market using “Vol. +/-“button.

Caution : Don’t push The INSTOP KEY after completing the

function inspection

Caution : Inspection only PAL M

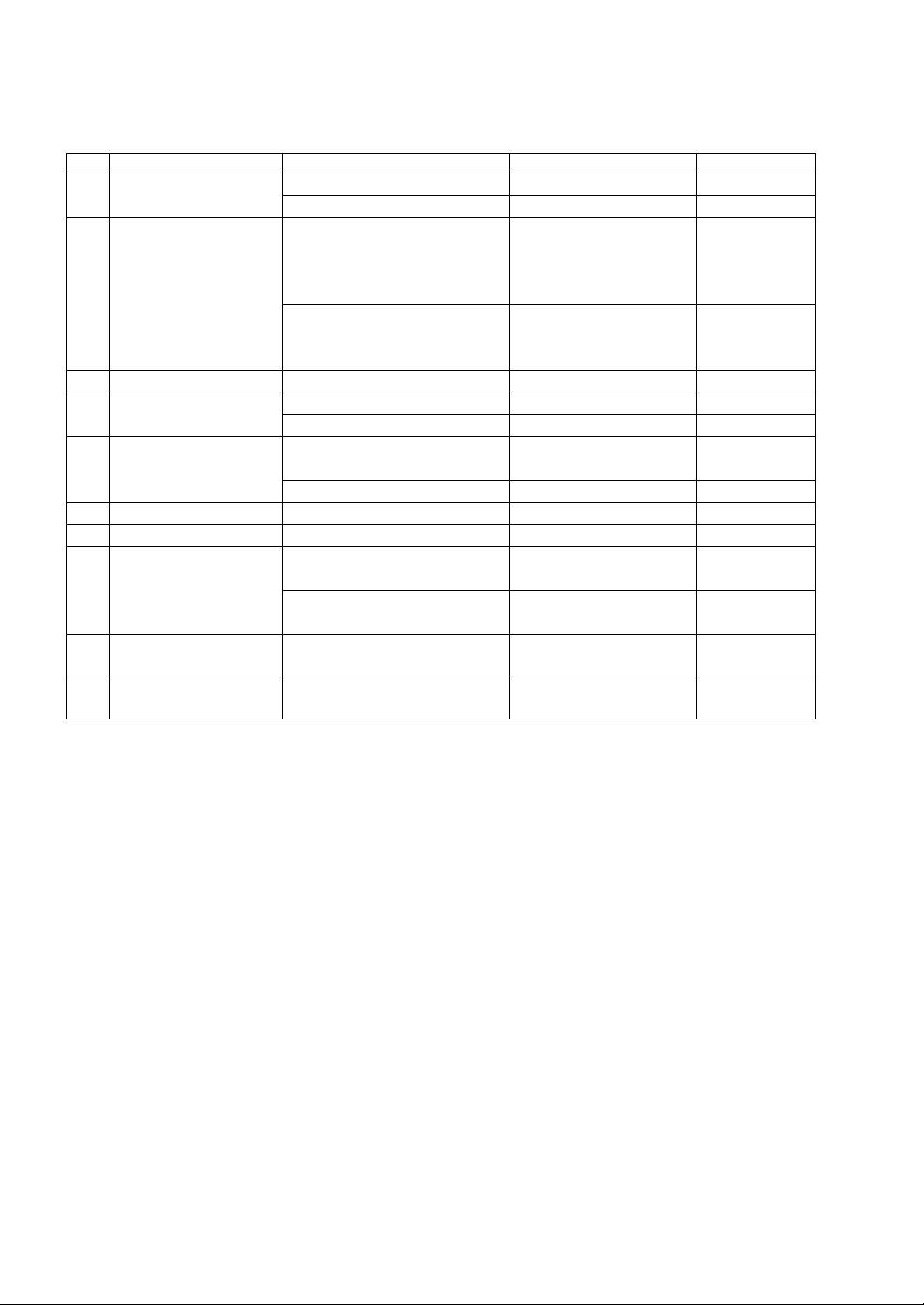

RS-232C COMMAND

CENTER

[CMD ID DATA] MIN (DEFAULT) MAX

Cool Mid Warm Cool Mid Warm

R Gain jg Ja jd 00 184 192 192 192

G Gain jh Jb je 00 187 183 159 192

B Gain ji Jc jf 00 192 161 95 192

R Cut 64 64 64 127

G Cut 64 64 64 127

B Cut 64 64 64 127

Color Test Color Coordination

temperature Equipment x y

COOL CA-210 0.276±0.002 0.283±0.002

MEDIUM CA-210 0.285±0.002 0.293±0.002

WARM CA-210 0.313±0.002 0.329±0.002

Item Min Typ Max Unit Remark

White 49 60 - cd/m - 100%Window White

average Pattern

brightness - 100IRE(255Gray)

- Picture: Vivid(Medium )

Brightness -20 +20 % - 85IRE(216Gray) 100%

uniformity Window White Pattern

- Picture: Vivid(Medium)

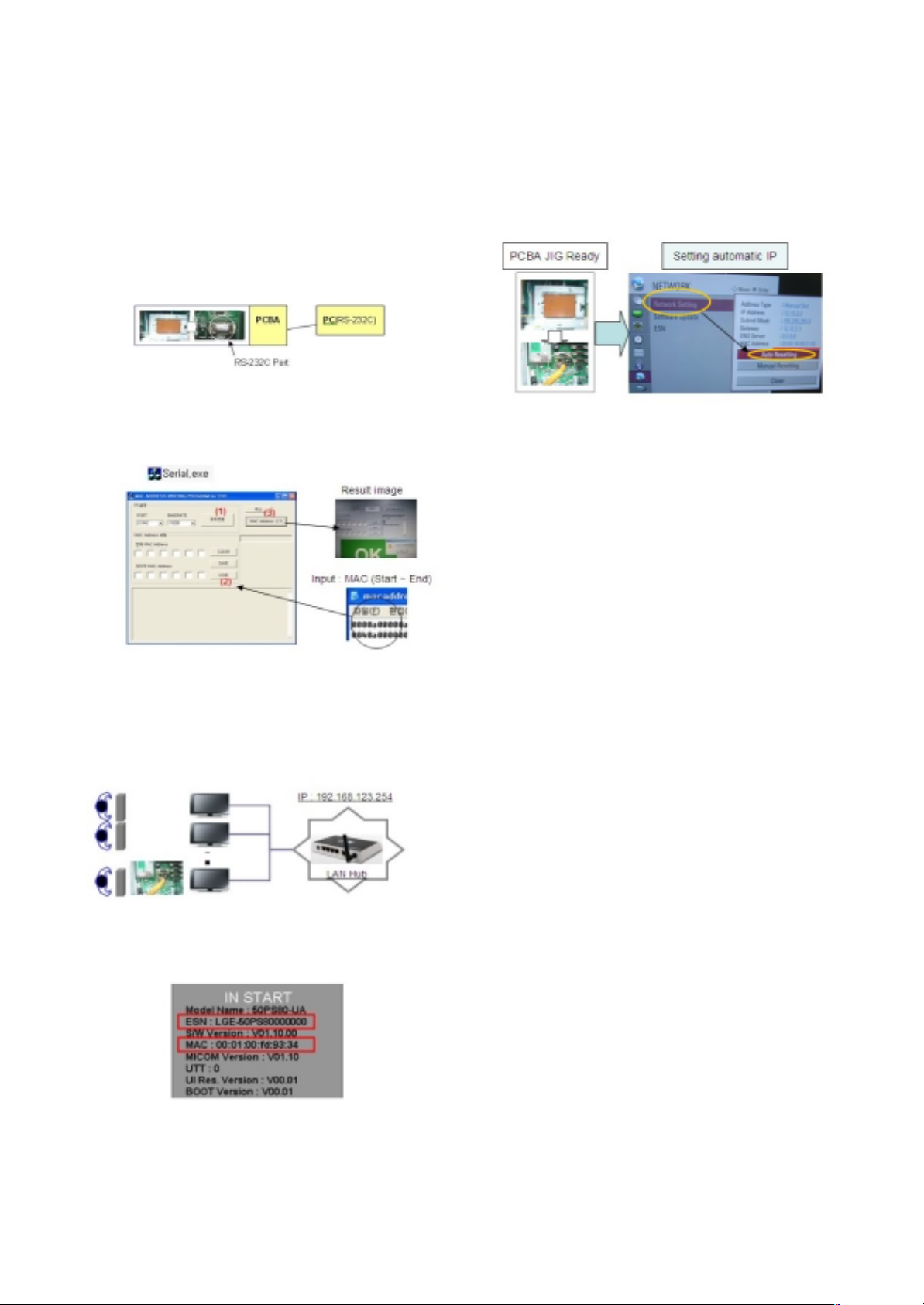

8. MAC Address and ESN Key Write

8-1. Equipment & Condition

- Play file: Serial.exe

- MAC Address edit

- Input Start / End MAC address

8-2. Download method

(1) Communication Prot connection

Connect: PCBA Jig-> RS-232C Port== PC-> RS-232C Port

(2) MAC Address Download

- Com 1,2,3,4 and 115200(Baudrate)

- Port connection button click(1)

- Load button click(2) for MAC Address write.

- Start MAC Address write button(3)

- Check the OK Or NG

8-3. Equipment & Condition

- Each other connection to LAN Port of IP Hub and Jig

8-4. MAC Address

- Push “IN-START” Key in service remote controller.

- Check ESN KEY only north America model

8-5. LAN PORT INSPECTION(PING TEST)

- LAN Port connection with PCB

- Network setting at MENU Mode of TV

- setting automatic IP

- Setting state confirmation

-> If automatic setting is finished, you confirm IP and MAC

Address.

- remove LAN CABLE

9. GND and ESD Testing

9-1. Prepare GND and ESD Testing.

- Check the connection between set and power cord

9-2. Operate GND and ESD auto-test.

(1) Fully connected (Between set and power cord) set enter

the Auto-test sequence.

(2) Connect D-Jack AV jack test equipment.

(3) Turn on Auto-controller(GWS103-4)

(4) Start Auto GND test.

(5) If its result is NG, then notice with buzzer.

(6) If its result is OK, then automatically it turns to ESD Test.

(7) Operate ESD test

(8) If its result is NG, then notice with buzzer.

(9) If its result is OK, then process next steps. Notice it with

Good lamp and STOPER Down.

9-3. Check Items.

(1) Test Voltage

GND: 1.5KV/min at 100mA

Signal: 3KV/min at 100mA

(2) Test time: just 1 second.

(3) Test point

GND test: Test between Power cord GND and Signal cable

metal GND.

ESD test: Test between Power cord GND and Live and

neutral.

(4) Leakage current: Set to 0.5mA(rms)

- 11 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

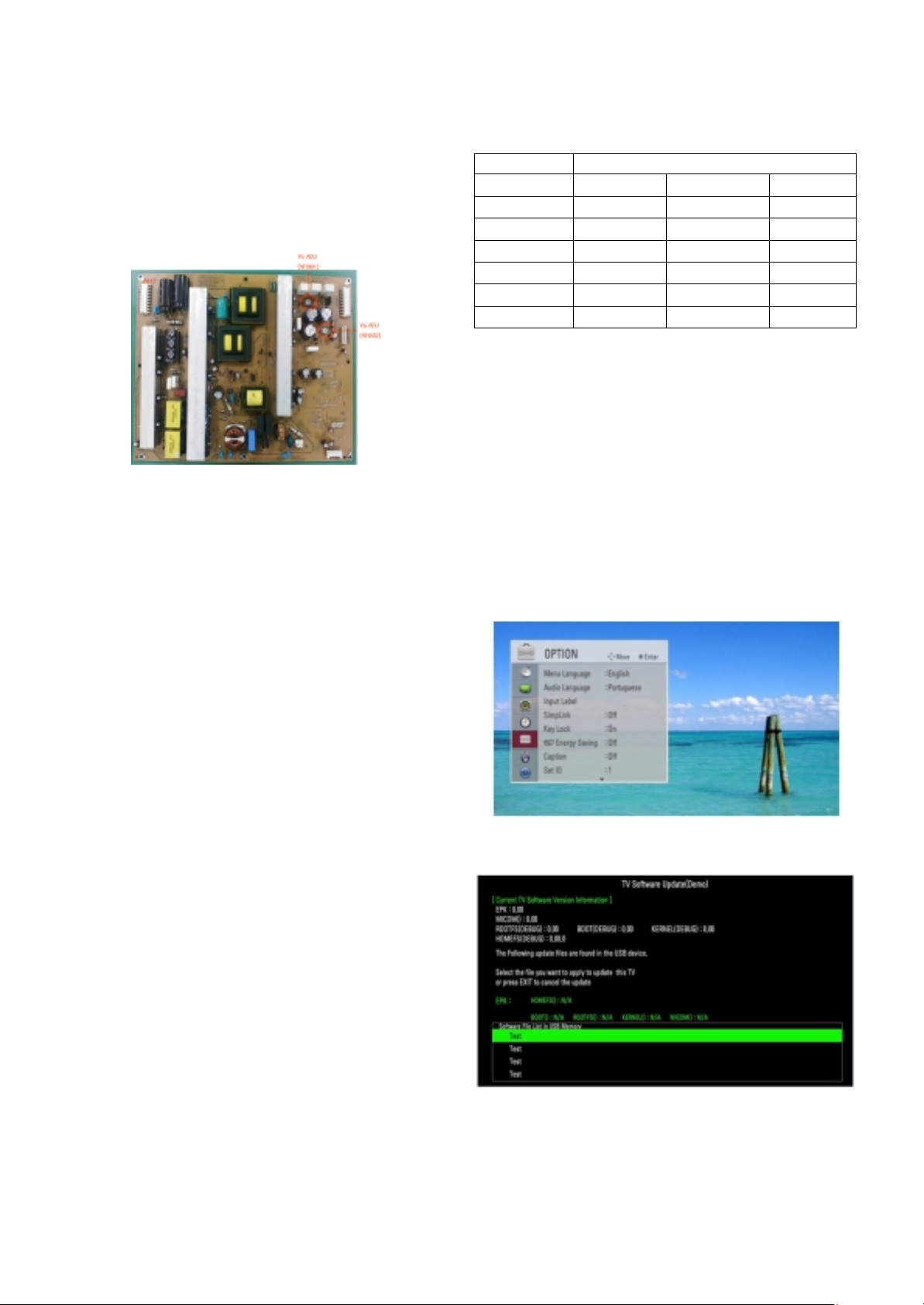

10. POWER PCB Ass’y Voltage

Adjustment

(Va/Vs Voltage Adjustment)

(1)Test equipment : D.M.M 1EA

(2) Connection Diagram for Measuring : refer to fig.1

10-1. Adjustment method

(1) Vs adjustment (refer fig.1)

1) Connect + terminal of D.M.M. to Vs pin of

P812(42”:P811), connect -terminal to GND pin of

P812(42”:P811)

2) After turning VR901, voltage of D.M.M adjustment as

same as Vs voltage which on label of panel left/top (

deviation ; ±0.5V)

(2) Va adjustment (refer fig.1)

1) After receiving 100% Full White Pattern, HEAT RUN.

2) Connect + terminal of D.M.M. to Va pin of

P812(42”:P811), connect -terminal to GND pin of

P811(42”:P812).

3) After turning VR502,voltage of D.M.M adjustment as

same as Va voltage which on label of panel left/top

(deviation; ±0.5V)

11. Default Service option.

11-1. ADC-Set.

V R-Gain adjustment Value (default 128)

V G-Gain adjustment Value (default 128)

V B-Gain adjustment Value (default 128)

V R-Offset adjustment Value (default 128)

V G-Offset adjustment Value (default 128)

V B-Offset adjustment Value (default 128)

11-2. White balance. Value.

11-3. Temperature Threshold

V Threshold Down Low 20

V Threshold Up Low 23

V Threshold Down High 70

V Threshold Up High 75

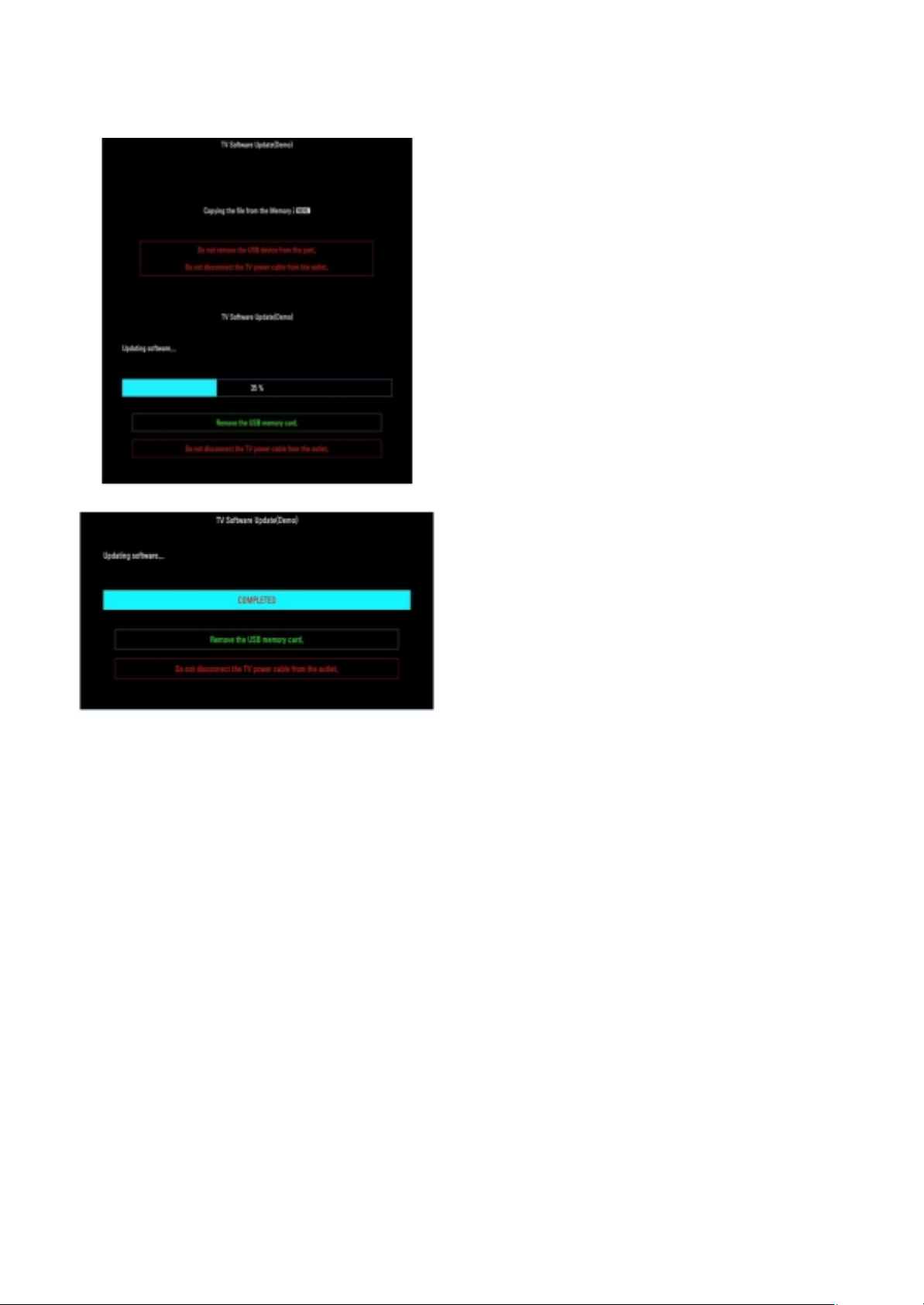

11. USB DOWNLOAD

(*.epk file download)

V Put the USB Stick to the USB socket

V Press Menu key, and move OPTION

V Press “FAV” Press 7 times.

- 12 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

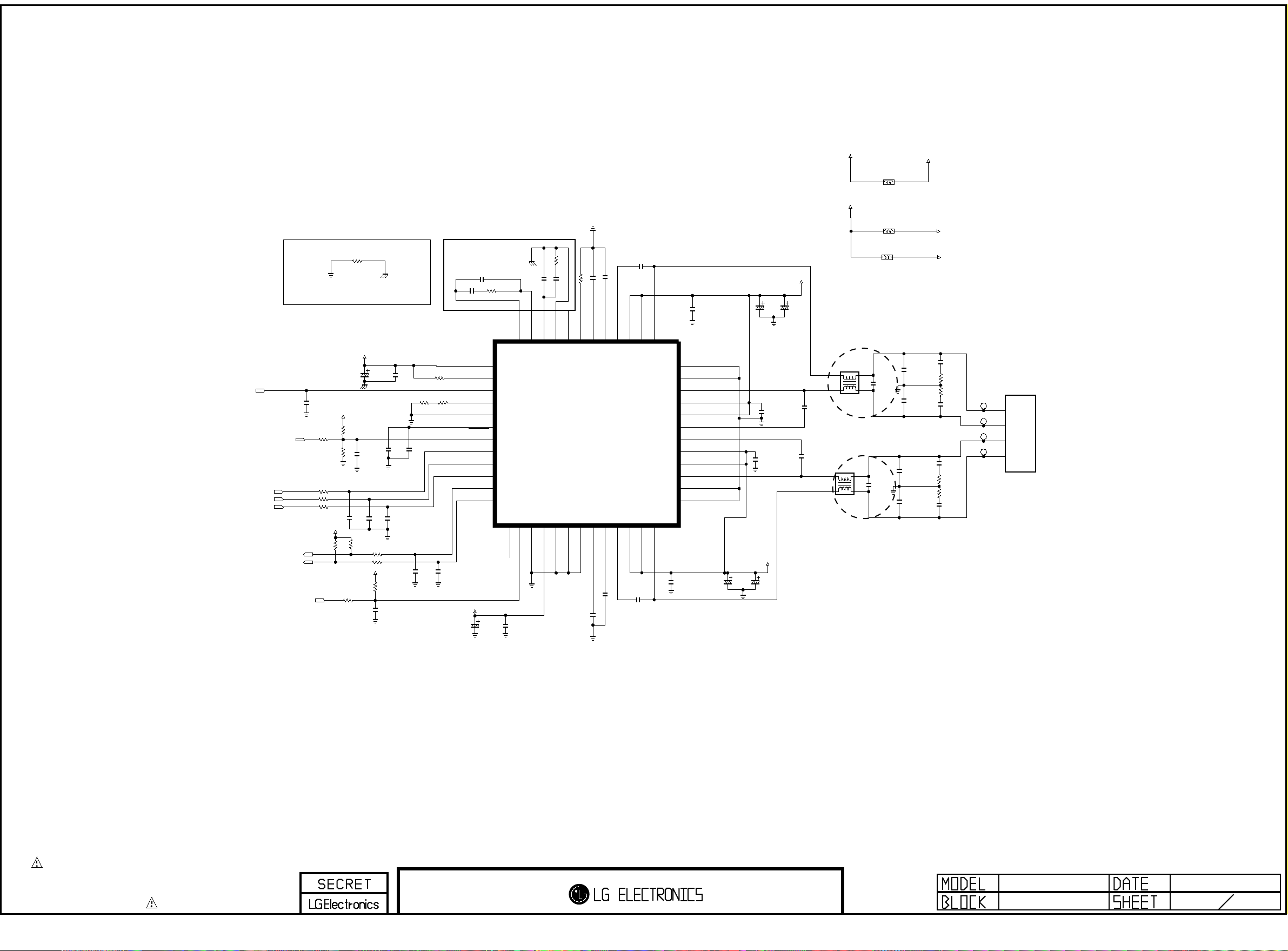

< fig.1 : 50 FHD Power PCB Assy Voltage adjustment >

CENTER (DEFAULT)

Cool Mid Warm

R Gain 192 192 192

G Gain 192 192 192

B Gain 192 192 192

R Cut 64 64 64

G Cut 64 64 64

B Cut 64 64 64

V Select download file (epk file)

V After download is finished, remove the USB stick.

V Press “IN-START” key of ADJ remote control, check the

S/W version.

CAUTION

- DO NOT REMOVE USB MEMORY CARD FROM USB PORT

WHEN YOU FIND BELOW DESCRIPTION

- " Do not remove the memory card from the port! "

- 13 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

- 14 -

LGE Internal Use OnlyCopyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

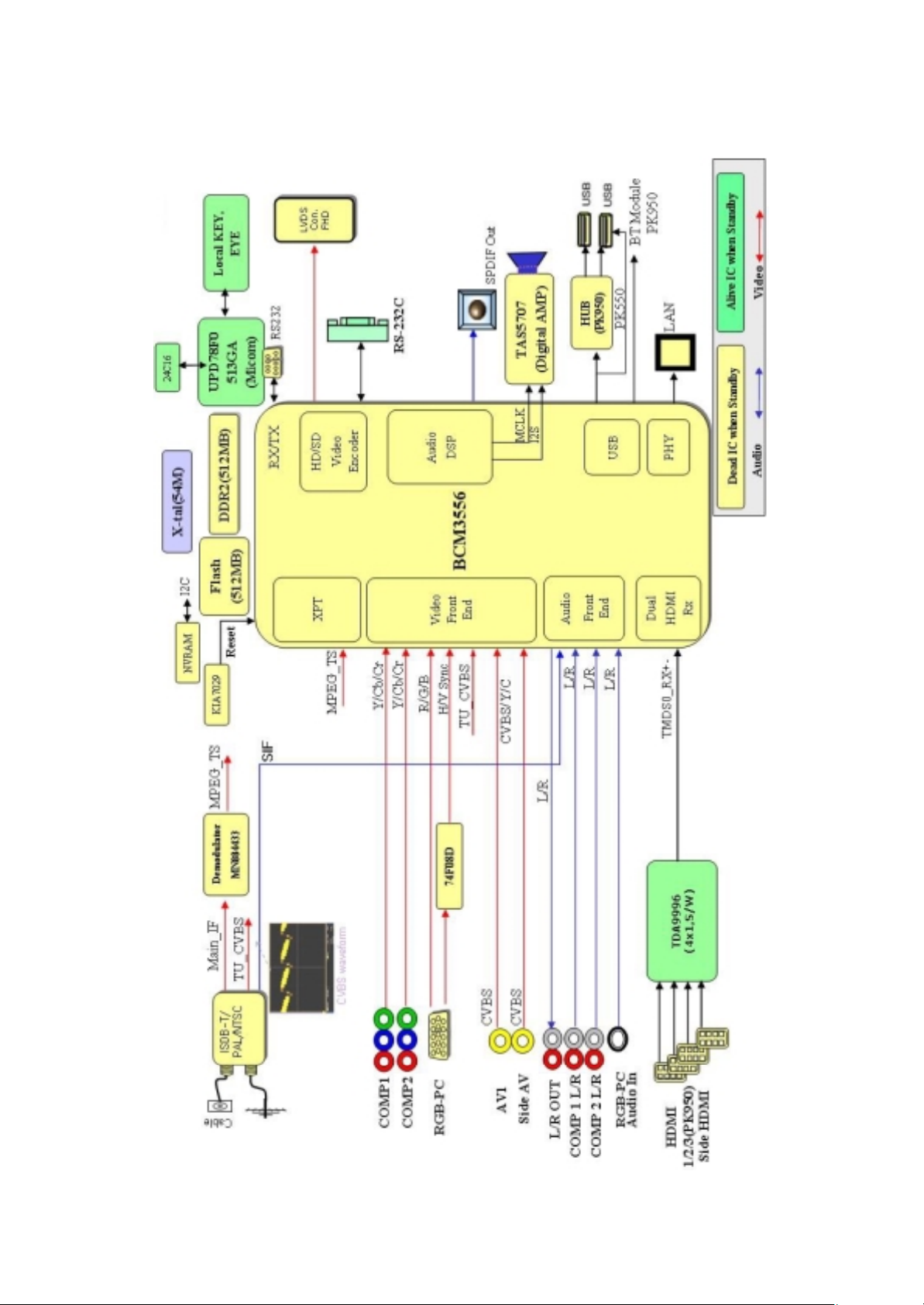

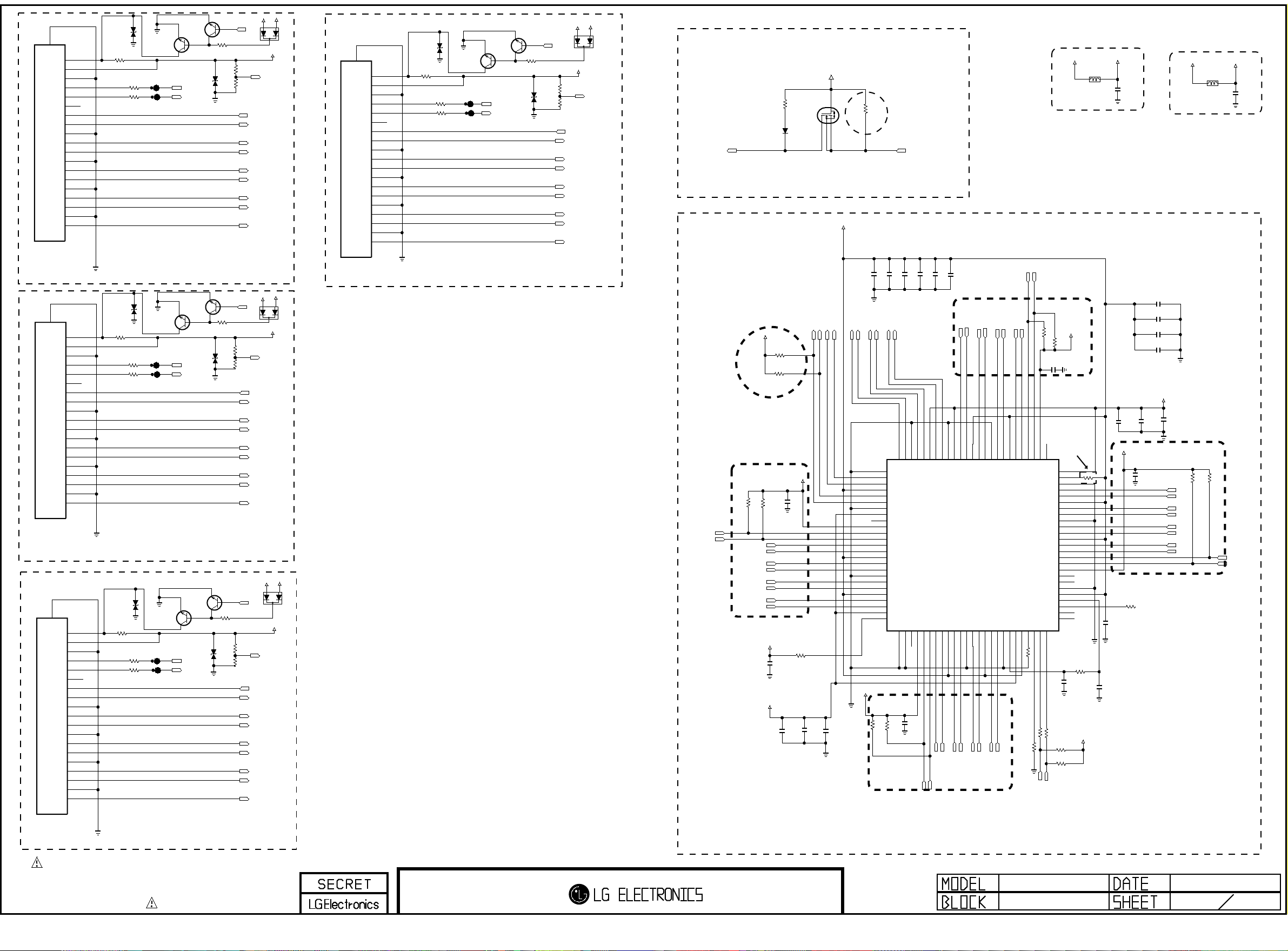

BLOCK DIAGRAM

- 15 -

LGE Internal Use Only

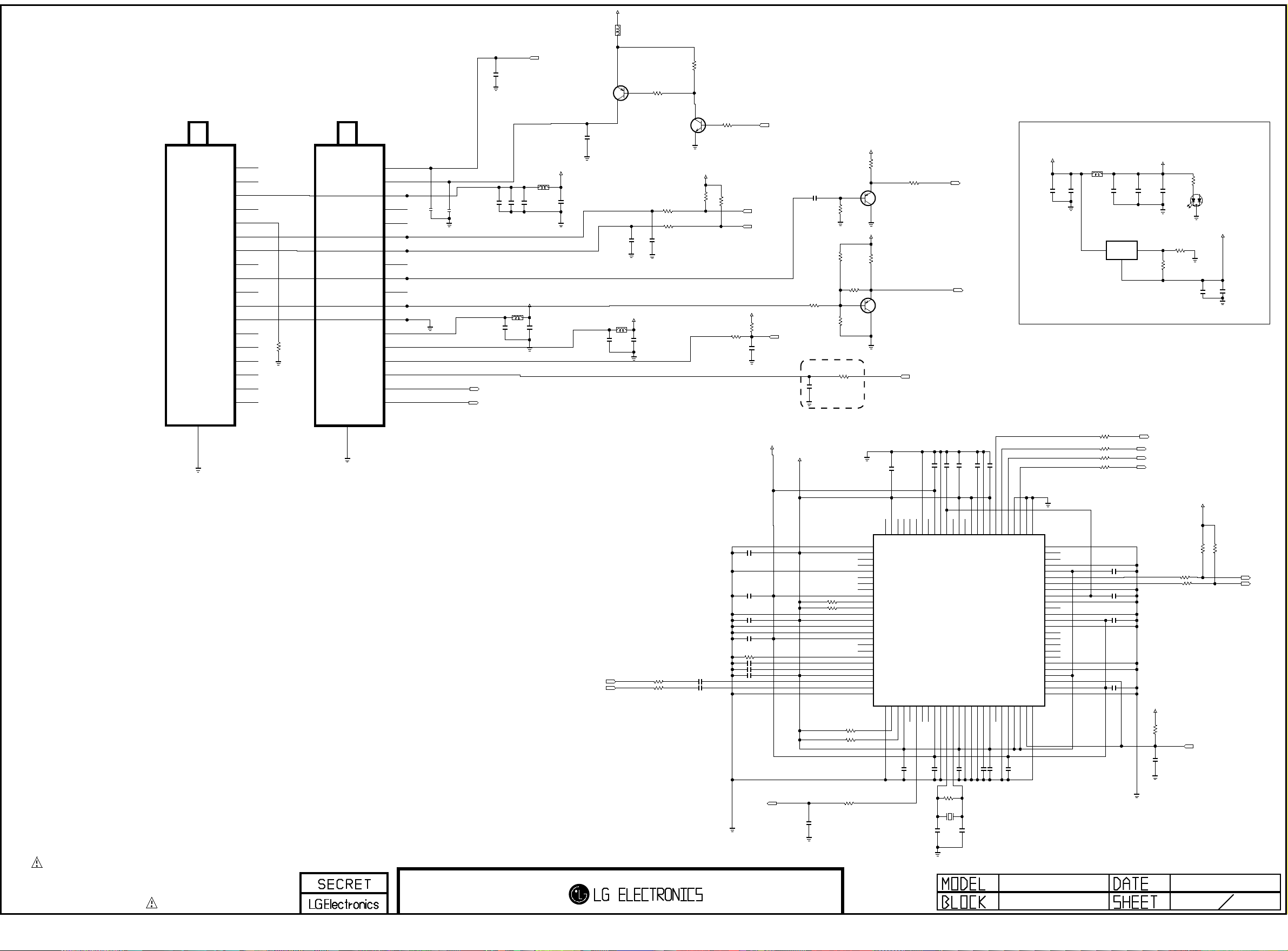

EXPLODED VIEW

Copyright ©2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

400

602

601

520

900

305

300

301

302

303

501

590

200

580

205

202

203

208

209

204

206

207

201

240

604

120

302

910

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

A10

A9

LV1

A12

A21

A2

USB HUB

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

C1105

15p F

50V

USB1 SIDE UPPER

CLOSE TO BCM3556

0

D3.3V

R1143

R1142

R1144

R1145

PK950

0

PK950

0

PK550

0

PK550

BT_DM_T

BT_DP_T

BT_USB_DM

BT_USB_DP

BT_DM

BT_DP

C1108

15p F

USB_DP

50V

24MHz

X1100

1M

R1102

0. 1uF C 1103

12K R1101

USB_DM

0

0R1140

R1141

0MER_NON/RWP_LACOL/DNI_PSUS

C1104

PK950

1uF

R1104

PK950

100K

0. 1uF C1109

Ca pac ito rs on VBU SA sho uld be

pl a ce d a s cl o sd t o c on ne c to r a s po s si bl e .

JK1 100

EAG4194540 1

KJA -UB-4- 0004

C1117

100 uF

16V

1

2

3

MAERTS NWOD BSU

4

5

USB1_OCD

C1116

100 uF

16V

PK950

PK550

0R1115

D3.3V D3.3V

R1120

10K

0R1118

R1125

R1126

R1123

R1124

SWITCH ADDED

IC1102

AP2191SG-13

NC

8

OUT_2

7

OUT_1

6

FLG

5

0

PK950

0

PK950

0

PK550

0

PK550

GND

1

IN_1

2

IN_2

3

EN

4

R1130

10K

READY

PK550

PK950

USB1_DM_to_HUB

USB1_DP_to_HUB

BT_USB_DM

BT_USB_DP

P_+5V

0R1132

USB1_CTL

0R1131

USB1_CTL_HUBUSB1_OCD_HUB

US B1 D ato t o US B2 512

USB 1 Da to to MAIN(B CM)

C1119

0. 1u F

16V

USB1_DM_to_HUB

USB1_DP_to_HUB

USB2_DM_to_HUB

USB2_DP_to_HUB

0. 1uF C1100

USBDN1_DM

USBDN1_DP

USBDN2_DM

USBDN2_DP

VDDA33_1

NC_1

NC_2

NC_3

NC_4

VSS

1

2

3

4

5

6

7

8

9

THERMAL

37

10

TEST

VDDA33_2

0. 1uF C1101

VDD18PLL35RBIAS36VDD33PLL

XTAL1/CLKIN

34

USB2512A_AEZG

11

12

OCS1_N

PRTPWR1

0 R1100

USB1_CTL_HUB

33

PK950

IC1 100

13

0. 1uF C1102

USB1_OCD_HUB

XTAL2

USBUP_DP

VDDA33_330USBUP_DM

32

14

VDD18

28

31

29

VBUS_DET

27

RESET_N

26

HS_IND/CFG_SEL1

25

SCL/SMBCLK/CFG_SEL0

24

VDD33

23

SDA/SMBDATA/NON_REM1

22

NC_8

21

NC_7

20

NC_6

19

16

17

18

15

NC_5

OCS2_N

VDD33CR

PRTPWR2

0 R1103

1uF C110 6

0. 1uF C1107

R1105

4. 7K

C1110

4. 7uF

100K R1108

100K R1106

0. 1uF C1111

100K R1107

D3.3V

READY

R1109

100K

R1133

100K

C1112

0. 1u F

16V

READY

/RST_HUB

USB2 SIDE UNDER

Ca pac ito rs on VBU SA sho uld be

pl a ce d a s cl o sd t o c on ne c to r a s po s si bl e .

001 :H1

PK950

JK1 101

EAG4194540 1

KJA -UB-4- 0004

1

2

3

MAERTS NWOD BSU

4

5

PK950

C1114

100 uF

16V

PK950

USB2_OCD_HUB

C1115

100 uF

16V

PK950

GND

IN_1

IN_2

EN

D3.3V

R1129

10K

READY

PK950

USB2_DM_to_HUB

USB2_DP_to_HUB

0R1127

USB2_CTL_HUB

US B2 D ato t o US B2 512

P_+5V

C1118

0. 1u F

16V

PK950

D3.3V

R1119

PK950

10K

SWITCH ADDED

IC1101

AP2191SG-13

NC

8

OUT_2

7

OUT_1

6

FLG

5

1

2

3

4

BLUETOOTH

1uF

C1113

PK950

C

E

BLUETOOTH

R1112

4.7K

PK950

B

S

R1113

4.7K

PK950

G

D

Q1101

PK950

RTR030P02

BT_ON/OFF

BT_DM_T

BT_DP_T

BT_RESET

VREG_CTR

USB2_CTL_HUB

USB2_OCD_HUB

D3.3V

47K

R1111

PK950

PK950

2SC3052

0

R1110

READY

Q1100

11

10

9

8

7

6

5

4

3

2

PK950

1

12507WR-10L

P1102

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

EAX61354901

USB HUB

1 3 1 3

COMPONENT1/2,AV1

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

JK1 001

PP J23 7-0 1

[RD1]E-LUG

6C

[RD1]O-SPRI NG

5C

[RD1]CONTACT

4C

[WH1]O-SPRING

5B

[YL1]CONTACT

4A

[YL1]O-SP RING

5A

[YL1]E-LUG

6A

[RD2]E-LUG

6H

[RD2]O- SPRING_2

5H

[RD2]CONTACT

4H

[WH2]O-SPRING

5G

[RD2]O- SPRING_1

5F

[RD2] E-LUG- S

7F

[BL2]O- SPRING

5E

[BL2 ]E-LUG- S

7E

[GN2]CONTACT

4D

[GN2]O-SPRING

5D

[GN2]E-LUG

6D

[RD3]E-LUG

6N

[RD3]O- SPRING_2

5N

[RD3]CONTACT

4N

[WH3]O-SPRING

5M

[RD3]O- SPRING_1

5L

[RD3] E-LUG- S

7L

[BL3]O- SPRING

5K

[BL3 ]E-LUG- S

7K

[GN3]CONTACT

4J

[GN3]O-SPRING

5J

[GN3]E-LUG

6J

ZD1011

5.1 V

ZD1010

5.1 V

ZD1008

5.1 V

ZD1009

5.1 V

ZD1006

5.1 V

ZD1007

5.1 V

ZD1032

5.1 V

ZD1033

5.1 V

C1007

100pF

C1004

R1007

470K

C1003

R1006

470K

50V

D3.3V

1uF

25V

25V

1uF

R1012

2.7K

R1013

1K

COMPOSITE1_SW

C1011

100p F

READY

C1010

100p F

READY

C1006

47pF

50V

COMPOSITE1_IN

AV 1

001:H2

AV_R_IN_1

002:A5

AV_L_IN_1

002:A5

003:B 4

ZD1034

5.1 V

ZD1035

5.1 V

ZD1020

ZD1021

ZD1019

ZD1018

ZD1017

ZD1016

ZD1014

ZD1015

ZD1012

ZD1013

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

R1015

470K

R1014

470K

D3.3V

R1018

C1016

25V

1uF

C1015

25V

1uF

C1014

27pF

50V

C1013

27pF

50V

C1012

27pF

50V

2.7K

C1017

100pF

50V

L1002

270nH

L1001

270nH

L1000

270nH

COMPONENT2

1K

C1022

100p F

READY

C1021

100p F

READY

C1020

27pF

50V

C1019

27pF

50V

C1018

27pF

50V

COMP2_SW

001:H3

COMP_R_IN_2

R1020

10

COMP_L_IN_2

COMP2_Pr

COMP2_Pb

COMP2_Y

R1019

002:A5

002:A5

003:B 3

003:B 4

003:B 3

ZD1031

ZD1030

ZD1028

ZD1029

ZD1027

ZD1025

ZD1026

ZD1024

ZD1023

ZD1022

ZD1036

ZD1037

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

R1022

470K

R1021

470K

C1025

27pF

50V

C1024

27pF

50V

C1023

27pF

50V

D3.3V

R1024

2.7K

C1027

25V

1uF

C1026

25V

1uF

L1005

270nH

L1004

270nH

L1003

270nH

C1028

100pF

50V

COMPONENT1

R1026

1K

COMP1_SW

READY

C1033

100p F

READY

C1032

100p F

C1031

27pF

50V

C1030

27pF

50V

R1027

10

C1029

27pF

50V

COMP1_SW

001:H3

002:A5

COMP_R_IN_1

002:A5

COMP_L_IN_1

COMP1_Pr

003:B 3

COMP1_Pb

003:B 3

COMP1_Y

003:B 3

SIDE_AV

PPJ 235 -01

JK100 0

5A

[YL]E-LUG

4A

[YL]O-SPRING

3A

[YL]CONTACT

4B

[WH]O-SPRING

3C

[RD]CONTACT

4C

[RD]O-SPRING

5C

[RD]E-LUG

ZD1038

5.1 V

ZD1039

5.1 V

ZD1005

ZD1004

ZD1003

ZD1002

ZD1000

ZD1001

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

5.1 V

D3.3V

R1002

2.7K

C1000

100pF

50V

R1001

470K

R1000

470K

R1003

1K

25V

1uF

C1002

25V

C1001

C1005

47pF

50V

1uF

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

C1009

100p F

READY

C1008

100p F

READY

COMPOSITE2_IN

SIDEAV_DET

SIDE_LIN

SIDE_RIN

SPDIF

SPDIF_OUT

GND

NL17SZ00DFT2G

1A5

NAND

B

2

GATE

3

READY

IC1000

4

R1029

100

D3.3V

R1028

1K

READY

VCC

READY

R1030

100

Y

EAX61354901

JACK

C1036

22pF

D3.3V

C1034

0. 1uF

50V

C1035

10uF

16V

READY

GND

VCC

VINPUT

JK100 2

JST 122 3-00 1

1

2

3

4

FIX_POLE

citpO rebiF

9 13

R,G,B PC INPUT

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

IC900

74F08D

D0A

1

D0B

D1A

D1B

GND

Q0

Q1

RGB_B

RGB_G

RGB_R

2

3

4

5

6

7

RGB_HSYNC

003:C 5

RGB_VSYNC

003:C 5

R900

22

R901

22

P_+5V

1K

5%

R919

1/10W

C

Q900

B

KRC102S

D909

5.6V

D3.3V

READY

C911

100pF

50V

D908

5.6V

EDID_WP

001:H5

DDC_SDA

R921

1K

DSUB_DET

DDC_SCL

E

READY

R918

2.7K

0849R

0

949R

RS232C

RS232C_TXD

RS232C_RXD

+3.3V _ST

50V

0.1 uF

C906

519R

+5V_ST

K7.2

2.7K

R916

R914

22

1/10W

R913

5%

22

1/10W

5%

18pF

50V

C908

D906

5.6V

READY

P_+5V

VCC

14

D3B

D3A

Q3

D2B

D2A

Q2

READY

READY

READY

C903

0.1 uF

R903

22

R902

22

C902

47pF

50V

C901

47pF

50V

C900

47pF

50V

GND

10K

R909

10K

R906

13

12

11

10

9

8

IC901

AT24C02BN-10SU-1.8

A0

A1

A2

D903

30V

1

2

3

4

8

7

6

5

D904

30V

R912

D902

5.5V

RGB_R

R911

D901

5.5V

RGB_R

R910

D900

5.5V

RGB_R

BCM Refe renc e

0

0

0

VCC

WP

SCL

SDA

C907

50V

18pF

R922

4.7 K

R923

4.7 K

8

9

C914

0. 1uF

50V

2NIR

2TUOR

2TUOD

7

01

2NID

JK902

6

MAX3232CDR

11

SPG09-D B-009

C915

0. 1uF

50V

-2C

-V

5

IC9 02

21

1TUOR

1NID

R930

100

6

1

2

+2C

4

31

1NIR

R931

-1C

3

$0. 179

41

1TUOD

100

7

3

C918

0. 1uF

50V

+V

2

51

DNG

8

4

+3.3V _ST

C919

0. 1uF

50V

+1C

1

61

CCV

C920

0. 1uF

50V

READY

D910

ADUC30S03010L_AMODIODE

30V

D911

READY

ADUC30S03010L_AMODIODE

30V

9

10

5

READY

READY

RS232 DEBUG SWITCH

- NEC/S7

A/B

OUTPUT

LOW X0 Y0 NEC

X1 Y1 S7M

HIGH

TO HDMI JACK FOR WIRELESS

BCM_RX

NEC_RXD

0R941

SUB_SCL

0R940

SUB_SDA

Y1

Y0

Z1

Z

Z0

INH

VEE

VSS

IC9 03

MC14053BDR2G

0ISTL0 0024A

1

2

3

4

5

6

7

8

+3.3V _ST

VDD

16

Y

15

X

14

X1

13

X0

12

A

11

B

10

C

9

RS232C_RXD

RS232C_TXD

BCM_TX

NEC_TXD

TO HDMI JACK FOR WIRELESS

R944

47K

D3.3V

R945

4.7 K

C930

0. 1uF

16V

PC AUDIO

JK900

PEJ 027 -01

E_SPRING

3

T_TERMINAL1

6A

B_TERMINAL1

7A

R_SPRING

4

T_SPRING

5

B_TERMINAL2

7B

T_TERMINAL2

6B

R91 2-*1

BLM18PG600SN1D

RGB_BEAD

ZD903

5.1 V

ZD902

5.1 V

ZD901

5.1 V

ZD900

5.1 V

R91 1-*1

BLM18PG600SN1D

RGB_BEAD

470K

R905

470K

R904

R91 0-*1

BLM18PG600SN1D

RGB_BEAD

C905

1uF

25V

C904

1uF

25V

PC_R_IN

PC_L_IN

RED2GREEN3BLUE4GND_15DDC_GND

RED_GND7GREEN_GND

6

SPG09-D B-010

JK901

GND_2

11

1

BLUE_GND9NC10SYNC_GND

H_SYNC14V_SYNC

DDC_DATA

12

8

13

DDC_CLOCK

15

SHILED

16

FOR PK/J90 - BREATING

D907

CDS3C30GTH

30V

D905

CDS3C30GTH

READY

50V

270p F

D3.3V

C910

10

R917

50V

82pF

READY

R951

5%

C909

1K

1/16W

PC_SER_DATA

002:G3

50V

50V

R950

1K

1/16W

5%

270p F

82pF

READY

C913

10

R920

READY

ROM DOWNLOAD FOR PDP

C912

PC_SER_CLK

002:G3

P_+5V

SUB Board I/F

+3.3V _ST

R932

10K

R946

4.7 K

D3.3V

PK550

2SC3052

+3.3V _ST

R928

10K

47K

C

Q901

B

E

READY

R929

0

MLB-2 01209-0 120P-N 2

MLB-2 01209-0 120P-N 2

R926

4.7 K

READY

R947

4.7 K

C916

10pF

READY

D3.3V

R925

4.7 K

IR_NEC

IR_NEC

KEY1

KEY2

SUB_SCL

SUB_SDA

L901

MLB-20 1209-01 20P-N2

PK950

LED_WHITE

R924

22

IR

LED_RED

READY

L900

R927

D3.3V

R933

10K

L903

L902

READY

C917

10pF

+3.3V _ST

R936

22

+3.3V _ST

R937

47K

C

Q902

E

2SC3052

C923

10pF

R935

22

R934

22

L904

MLB-20 1209-01 20P-N2

B

C921

0. 1uF

16V

R939

2.2 K

R938

47K

C927

C925

10pF

C924

10pF

D912

CDS3C05HDMI1

5.6 V

D913

CDS3C05HDMI1

5.6 V

C922

0. 1uF

16V

10pF

C926

10pF

+3.3V _ST

D914

GND

KEY1

KEY2

LED-RED

GND

SDA

GND

3.3V_ ST

3.3V_MULTI

LED-WHITE

IR

SCL

P902

12507WR-12L

1

2

3

4

5

6

7

8

9

10

11

12

13

GND

LED_BREATHING

C929

10pF

PK950

P_+5V

PK950

L905

MLB-20 1209-01 20P-N2

PK950

P903

12507WR-03L

1

2

3

4

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

EAX61354901

LVDS/RS232//RGB

1 0 1 3

PK950

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

SHIELD

20

20332095GAE

JK802

YKF45-7058V

SHIELD

20

20332095GAE

JK801

YKF45-7058V

SHIELD

20

10332095GAE

JK800

YKF45-7054V

HP_DET

19

5V

18

GND

17

DDC_DATA

16

DDC_CLK

15

NC

14

CE_REMOTE

13

CK-

12

CK_GND

11

10

9

8

7

6

5

4

3

2

1

HP_DET

19

18

GND

17

DDC_DATA

16

DDC_CLK

15

NC

14

CE_REMOTE

13

12

CK_GND

11

10

9

8

7

6

5

4

3

2

1

19

18

17

DDC_DATA

16

DDC_CLK

15

14

CE_REMOTE

13

12

CK_GND

11

10

9

8

7

6

5

4

3

2

1

CK+

D0-

D0_GND

D0+

D1-

D1_GND

D1+

D2-

D2_GND

D2+

5V

CK-

CK+

D0-

D0_GND

D0+

D1-

D1_GND

D1+

D2-

D2_GND

D2+

HP_DET

5V

GND

NC

CK-

CK+

D0-

D0_GND

D0+

D1-

D1_GND

D1+

D2-

D2_GND

D2+

GND

GND

GND

R802

R801

READY

1K

READY

1K

READY

R800

D802

5.5 V

D801

5.5 V

1K

D800

5.5 V

GND

R807

0

R808

GND

R805

0

R806

0

R804

0

R803

0

0

GND

GND

KRC104S

Q802

JP8 03

JP8 04

GND

KRC104S

Q801

JP8 01

JP8 02

GND

KRC104S

Q800

JP8 00

JP8 05

E

E

C

KRC104S

Q805

B

DDC_SDA_1

008 :X13

DDC_SCL_1

008 :X12

HDMI_HPD_1

001 :H2

B

R811

4.7 K

C

00 8: I29 ;0 08 :Z1 4

1.8 K

D805

5.5 V

READY

3.3 K

GND

008 :H1 7; 008 :H8 ;00 8:R 26; 008 :X2 5

UI_HW_PORT1

E

E

C

KRC104S

Q804

B

DDC_SDA_2

008:AD5

DDC_SCL_2

008:AD5

HDMI_HPD_2

B

R810

4.7 K

C

1.8 K

D804

5.5 V

READY

3.3 K

GND

008 :H2 6; 008 :H8 ;00 8:R 26; 008 :X2 5

UI_HW_PORT2

E

HDMI_HPD_3

B

R809

4.7 K

C

D803

1.8 K

5.5 V

READY

3.3 K

GND

008 :H2 6;0 08 :H1 7;0 08: R26 ;00 8:X 25

E

C

DDC_SDA_3

008:AN 12

DDC_SCL_3

008:AN 12

KRC104S

Q803

B

UI_HW_PORT3

P_+5V

D808

5V_HDMI_1

R837

HDMI_POWER_1

R838

CEC_REMOTE

CK-_HDMI1

008 :Y12

CK+_HDMI1

008 :Y12

D0-_HDMI1

008 :Y12

D0+_HDMI1

008 :Y11

D1-_HDMI1

008 :Y11

D1+_HDMI1

008 :Y11

D2-_HDMI1

008 :Y10

D2+_HDMI1

008 :Y10

00 8:I 19; 008 :A B7

P_+5V

D806

5V_HDMI_2

00 8:I 20; 008 :A B7

R839

HDMI_POWER_2

R840

CEC_REMOTE

CK-_HDMI2

008: AE6

CK+_HDMI2

008: AE6

D0-_HDMI2

008: AE6

D0+_HDMI2

008: AE6

D1-_HDMI2

008: AF6

D1+_HDMI2

008: AF6

D2-_HDMI2

008: AF6

D2+_HDMI2

008:AG6

P_+5V

D807

5V_HDMI_3

008 :I1 1; 008 :AK 15

R841

HDMI_POWER_3

R842

CEC_REMOTE

CK-_HDMI3

008: AL12

CK+_HDMI3

008: AL12

D0-_HDMI3

008: AL13

D0+_HDMI3

008: AL13

D1-_HDMI3

008: AL13

D1+_HDMI3

008: AL13

D2-_HDMI3

008: AL14

D2+_HDMI3

008: AL14

5V_HDMI_1

A1CA2

5V_HDMI_2

A1CA2

5V_HDMI_3

A1CA2

008 :I 9;0 08: AK1 5

JACK_GND

GND

20

19

18

17

16

15

14

13

12

11

JK803

10

EAG42463001

KJA -ET -0- 0032

HP_DET

5V

GND

DDC_DATA

DDC_CLK

NC

CE_REMOTE

CK-

CK_GND

CK+

D0-

9

D0_GND

8

D0+

7

D1-

6

D1_GND

5

D1+

4

D2-

3

D2_GND

2

D2+

1

GND

R812

D809

5.5 V

READY

1K

GND

R813

0

R814

0

P_+5V

HDMI_HPD_4

D811

D810

5.5 V

READY

GND

008 :H2 6;0 08: H17 ;00 8:H 8; 008 :X2 5

GND

KRC104S

Q806

JP8 06

JP8 07

E

C

KRC104S

Q807

B

DDC_SDA_4

008:AH 21

DDC_SCL_4

008:AH 21

E

B

R815

4.7 K

C

SIDE_HDMI_PORT4

5V_HDMI_4

A1CA2

00 8:S 28; 00 8:A I1 9

5V_HDMI_4

00 8:S 29; 00 8:A I1 9

1.8 K

R843

HDMI_POWER_4

3.3 K

R844

CEC_REMOTE

CK-_HDMI4

008:AG 19

CK+_HDMI4

008:AG 19

D0-_HDMI4

008:AG 19

D0+_HDMI4

008:AG 19

D1-_HDMI4

008: AF19

D1+_HDMI4

008: AF19

D2-_HDMI4

008: AF19

D2+_HDMI4

008: AE19

* HDMI CEC

CEC_REMOTE

008 :H2 6; 008 :H1 7;0 08: H8; 008 :R2 6

HDMI1

R816

47K

DDC_SDA_1

DDC_SCL_1

CK-_HDMI1

CK+_HDMI1

D0-_HDMI1

D0+_HDMI1

D1-_HDMI1

D1+_HDMI1

D2-_HDMI1

D2+_HDMI1

MMBD301LT1G

P_+5V

R817

47K

P_+5V

+1.8V_HDMI

R821

D812

C802

0. 1uF

22K

R820

3.3 K

R819

3.3 K

5V_HDMI_1

16V

C801

0. 1uF

C800

0. 1uF

16V

R818

0

+3.3 V_ST

D

003 :E3

003 :E3

HDMI_SCL

HDMI_SDA

C803

0. 1uF

16V

G

S

B

Q808

+3.3V_HDMI

003 :D3

003 :D3

HDMI0_RXC+_BCM

HDMI0_RXC-_BCM

C804

0. 1uF

16V

BSS83

003 :D3

HDMI0_RX0-_BCM

OUT_DDC_CLK

OUT_DDC_DAT

VDDDC[1V8]_1

RXA_DDC_DAT

RXA_DDC_CLK

VDDH[3V3]_1

VDDH[3V3]_2

VDDH[1V8]_1

91K

R845

1/16W

0. 1uF

003 :D4

003 :D3

HDMI0_RX0+_BCM

HDMI0_RX1-_BCM

VSS_1

OUT_C+

OUT_C-

VDDO[3V3]

VSS_2

RXA_HPD

RXA_5V

RXA_C-

RXA_C+

RXA_D0-

RXA_D0+

VSS_3

RXA_D1-

RXA_D1+

RXA_D2-

RXA_D2+

AUX_5V

5V_HDMI_2

1%

003 :D4

HDMI0_RX1+_BCM

R822

47K

HDMI2

L800

BLM18PG121SN1D

HDMI4

R833

1%

12K

0

READY

R832

+3.3V_HDMI

+1.8V_HDMI

5V_HDMI_3

R834

C815

2. 2uF

C814

6800 pF

50V

C817

0. 1uF

C816

0. 1uF

16V

READY

+1.8V_HDMI

C819

0. 1uF

16V

C818

0. 1uF

16V

0

C823

C824

C821

C822

0. 1uF

0. 1uF

0. 1uF

0. 1uF

C820

0. 1uF

16V

D3.3V

BLM18PG121SN1D

R835

47K

D2+_HDMI3

D2-_HDMI3

D1+_HDMI3

D1-_HDMI3

D0+_HDMI3

D0-_HDMI3

CK+_HDMI3

CK-_HDMI3

L801

HDMI3

+3.3V_HDMI

R836

47K

C825

0. 1uF

DDC_SCL_3

DDC_SDA_3

D1.8V

001 :G6

HDMI_CEC

DDC_SCL_4

0. 1uF

C807

0. 1uF

C808

0. 1uF

28

RXB_HPD

C806

0. 1uF

16V

0. 1uF

C809

OUT_D1+

VDDO[1V8]

OUT_D1-98VSS_12

95

96

97

29

30

31

32

RXB_C-

RXB_5V

RXB_DDC_CLK

RXB_DDC_DAT

DDC_SCL_2

DDC_SDA_2

C810

0. 1uF

C811

D2-_HDMI4

D1-_HDMI4

D2+_HDMI4

D1+_HDMI4

VSS_11

RXD_D2-90RXD_D2+91VDDDC[1V8]_3

OUT_D2+94OUT_D2-

VDDH[3V3]_8

92

93

88

89

IC800

TDA19997

33

34

35

38

39

36

37

40

41

VSS_5

RXB_C+

RXB_D0-

RXB_D1-

RXB_D2-

RXB_D1+

RXB_D0+

VDDH[3V3]_3

CK-_HDMI2

CK+_HDMI2

VDDH[3V3]_4

D1-_HDMI2

D0-_HDMI2

D0+_HDMI2

D1+_HDMI2

D0-_HDMI4

D0+_HDMI4

42

43

VSS_6

RXB_D2+

D2-_HDMI2

D2+_HDMI2

C805

003 :D4

003 :D4

HDMI0_RX2+_BCM

HDMI0_RX2-_BCM

OUT_D0+

OUT_D0-

99

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

26

VSS_4

TEST1

R823

47K

DDC_SDA_4

CK+_HDMI4

CK-_HDMI4

RXD_C+

RXD_DDC_DAT79RXD_DDC_CLK

VDDH[3V3]_783RXD_D0-84RXD_D0+85VSS_1086RXD_D1-87RXD_D1+

RXD_C-

81

82

80

44

45

47

TEST2

0R8 26

CDEC_DDC

VDDDC[1V8]_246VDDDC[1V8]_4

R824

0

R831

47K

C813

to TDA9996

RXD_5V

RXD_HPD

77

78

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

48PD49

50

I2C_SCL

I2C_SDA

22

R825

SDA2_3.3V

SCL2_3. 3V

R829

READY

READY

5V_HDMI_4

R830

47K

0. 1uF

16V

Pl ac e cl os e

VDDH[1V8]_2

R12K

VSS_9

RXC_D2+

RXC_D2-

VDDH[3V3]_6

RXC_D1+

RXC_D1-

VSS_8

RXC_D0+

RXC_D0-

VDDH[3V3]_5

RXC_C+

RXC_C-

RXC_DDC_CLK

RXC_DDC_DAT

RXC_5V

RXC_HPD

CEC

VSS_7

VDDS[3V3]

CDEC_STBY

INT_N/MUTE

RXE_DDC_DAT

RXE_DDC_CLK

C812

0. 1uF

16V

22

R828

R827

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

EAX61354901

HDMI

6 13

AMP

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

P_17V

L704

0LCML00003B

MLB- 201209 -0120P -N2

D3.3V

+17V_AMP

001 :H2

AUD_MASTER_CLK

001 :H6 ;00 5:C 2

AUD_LRCK

AUD_SCK

AUD_LRCH

Separate DGND AND AVSS

AVSS

C700

22pF

READY

+3.3V_DVDD

READY

001 :E5

R705

1K

PULL DOWN

0

0

0

+3.3V_DVDD

R701

4.7 K

READY

READY

R708

R702

R704

22K

R703

R706

33

AC_DET

SDA1_3.3V

SCL1_3. 3V

AMP_RESET_N

R710

0

+3.3V_AU_AVDD

R709

1K

C702

1000 pF

50V

READY

C701

22pF

READY

R707

4.7 K

READY

+3.3V_DVDD

C704

1000 pF

READY

C703

10uF 16V

C705

22pF

READY

R712

READY

R711

2K

33

33R713

AVSS

C707

0. 1uF

C706

22pF

READY

C708

0. 01u F

C710

4. 7uF

10V

READY

R714

200

C709

33pF

1%

T hi s pa rt s ar e L o c a t e d

on AV SS a rea.

C714

4700 pF

C713

R717

470

0.0 47 uF

TESTOUT

R716

0

READY

1%

OSC_RES

18K

R715

C711

33pF

READY

AVDD

MCLK

DVSS_1

VR_DIG

LRCLK

SCLK

SDIN

+3.3V_DVDD

PDN

SDA

SCL

C712

10uF 16V

13

14

15

16

17

18

19

20

21

22

23

24

C715

0. 01u F

L703

120- ohm

470

R719

AVSS

4700 pF

C716

PLL_FLTP

PLL_FLTM

VR_ANA

10

11

12

22K

C717

0.0 47 uF

AVSS

2200 pFC720

R718

SSTIMER

OC_ADJ

6

7

8NC9

TAS5709PHPR

IC 70 0

26STEST

27DVDD

29GND

30AGND

25

28DVSS_2

31VREG

RESET

C718

0. 1uF

C723

Fu1127C

0.0 33 uF

50V

C725

0. 01u F

BST_A

PVDD_A_13PVDD_A_2

C722

OUT_A

1

2

35PVDD_D_2

34PVDD_D_1

0.0 33 uF

50V

36OUT_D

48

47

46

45

44

43

42

41

40

39

38

37

C724

0. 01u F

PGND_AB_2

PGND_AB_1

OUT_B

PVDD_B_2

PVDD_B_1

BST_B

BST_C

PVDD_C_2

PVDD_C_1

OUT_C

PGND_CD_2

PGND_CD_1

C726

68uF

35V

C728

0. 01u F

+17V_AMP

C727

68uF

35V

GVDD_OUT_1

4

5

32GVDD_OUT_2

33BST_D

917C

Fu1

C730

68uF

35V

C729

0. 01u F

C731

68uF

35V

+17V_AMP

50V

0.0 33 uF

C733

50V

0.0 33 uF

C732

L701

AD-9060

2S

1S 1F

EAP6100 8401

L700

AD-9060

2S

1S 1F

EAP6100 8401

L702

120- ohm

C735

0. 47u F

50V

C737

0. 1uF

C736

0. 1uF

C739

0. 1uF

C738

0. 1uF

2F

2F

C734

0. 47u F

50V

+3.3V_AU_AVDD

+3.3V_DVDD

C743

0. 01u F

R722

3. 3

R723

3. 3

C742

0. 01u F

C741

0. 01u F

R721

3. 3

R720

3. 3

C740

0. 01u F

SPK_L+

SPK_L-

SPK_R+

SPK_R-

WAFER-ANGLE

4

3

2

1

P700

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

EAX61354901

AUDIO AMP

7 13

+5V_TU

C605

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

0. 1uF

16V

DEMOD_OPT

RF_SWITCH_CTL

Pu l l- u p c a n’ t b e a p pl i ed

becau se of MODEL_ OPT_2

Q600

ISA1530AC1

DEMOD_OPT

BRAZIL_TUNER

19

SHIELD

TU601

UDA45AL

ANT_PWR[OPT]

1

BST_CNTL

2

+B

3

NC[RF_AGC]

4

AS

5

SCL

6

SDA

7

NC( IF_TP )

8

SI F

9

NC

10

VIDEO

11

GND

12

1. 2V

13

3. 3V

14

RESET

15

IF_AGC_CNTL

16

DIF_ 1

17

DIF_ 2

18

0

R641

READY

TU600

TDTR-T035F

10

11

12

13

14

15

16

17

18

19

SHIELD

RF_S/W_CTL

1

BST_CTL

2

+B1 [5V]

3

NC_1[RF_AGC]

4

NC_2

5

SCLT

6

SDAT

7

NC_3

8

SI F

9

NC_4

VIDEO

GND

+B 2[1 .2V]

+B 3[3 .3V]

RESET

IF/AGC

DI F_1 [N]

DI F_2 [P]

DEMOD_OPT

C600

1200p F

50V

DEMOD_OPT

C601

1200p F

50V

C603

1200 pF

50V

TUNER_IF_N

TUNER_IF_P

C607

C604

4. 7uF

+1.2V_DE

L600

C602

4. 7uF

0. 1uF

+5V_TU

L601

C606

0. 1uF

C608

22uF

16V

< PANASONIC Demod.>

TUNER_IF_N

TUNER_IF_P

C610

0. 01u F

25V

DEMOD_OPT

L603

MLB-2 01209-0 120P-N 2

DEMOD_OPT

E

B

DEMOD_OPT

C

C612

47pF

50V

D3.3V

L602

C609

C611

4. 7uF

0. 1uF

DEMOD_OPT

R603

2.2 K

2SC3052

DEMOD_OPT

100

R602

100

R601

C613

47pF

50V

R612

100

100

R613

DEMOD_OPT

Cl os e t o R6 22, R6 23

Q601

DEMOD_OPT

C

E

R604

3K

READY

V61

DEMOD_OPT

R605

10K

DEMOD_OPT

B

Fu1.0

716C

816C

Fu1.0

V61

DEMOD_OPT

D3.3V

R608

10K

R607

READY

3K

R606

0

1/10W

5%

+1.2V_DE

C625

DEMOD_OPT

C624

DEMOD_OPT

DEMOD_OPT

C622

DEMOD_OPT

C623

DEMOD_OPT

R620

10K

DEMOD_OPT

DEMOD_OPT

DEMOD_OPT

ISDB_IF_AGC

SCL0_3. 3V

SDA0_3.3V

D3.3V

R609

100K

C614

0. 1uF

16V

0. 1uF

0. 1uF

0. 1uF

0. 1uF

1%

0. 1uFC620

0. 1uFC621

0. 1uFC619

RF_BOOSTER

TUNER_RESET

C616

100p F 50V

C615

0. 1uF

16V

DEMOD_OPT

+3.3V_DE

R626

R627

DEMOD_OPT

C626

0. 1uF

+5V_TU

R619

B

R616

4.7 K

R615

1K

R618

READY

100

READY

R617

0R611

READY

Cl o se t o t he tu n er

R614

1K

R610

1K

DEMOD_OPT

2.2 K

DEMOD_OPT

2.2 K

DEMOD_OPT

DEMOD_OPT

DEMOD_OPT

R623

B

VSS_1

DEMOD_OPT

AVDD_S

AIQ_S

AVSS_S

VRT_S

VRB_S

TCPO_S

VDDL_1

MSCL_S

MSDA_S

VSS_2

VSSH

VDDL_2

TCPO_T

VRT_T

VRB_T

AVDD_T

AIN_T

AIP_T

AVSS_T

2.2 KR625

2.2 KR624

10K

DEMOD_OPT

470

E

C

+5V_TU

0

E

C

AII _S

PSEL

ZSEL

ACKI

IR_T

Q603

Q602

ISA1530AC1

DEMOD_OPT

AGC_S

VDDH_5

99

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

VSS_3

MSCL_T

C627

0. 1uF

DEMOD_OPT

R622

82

ISA1530AC1

ISDB_IF_AGC

C628

0. 1uF

16V

29

30

31

28

GPO1

AGCI_T

VDDH_1

MSDA_T

16V

DEMOD_OPT

TU_SIF

TU_CVBS

DEMOD_OPT

DEMOD_OPT

DEMOD_OPT

C631

DEMOD_OPT

0. 1uF

SCKB94TEST095SDOB96PCKB97DENB98GPO2

93

C635

C632

16V

25V

25V

1uF

1uF

7

RON

NC_388HDVDDH89NC_490HDVDDL191VSS_1192VDDL_

87

IC600

MN884433

32

33

34

36XO37

35

38

39

XI

VSS_4

VDDL_3

DEMOD_OPT

R628

1M

25MHz

C629

30pF

50V

READY

X600

DEMOD_OPT

VDDH_2

GPI140GPI0

C634

0. 1uF

16V

DEMOD_OPT

C633

30pF

50V

GPO0

AGCR_T

C630

0. 1uF

16V

DEMOD_OPT

DEMOD_OPT

50V

0. 01u F

86

41

TEST4

DEMOD_OPT

C637

0. 1uF

16V

DEMOD_OPT

C640

C636

16V

0. 1uF

VSS_1085HDVPP

84

42

43

44

NC_1

SHVPP

SHVDDH

DEMOD_OPT

C638

0. 1uF

16V

D3.3V

C641

10uF

6.3 V

TEST278SCKA79GPI280SDOA

TEST1

PCKA82DENA83VDDH_4

77

76

81

45

46

47

TCK

VSS_5

VDDL_4

C639

0. 1uF

16V

VSS_9

75

INTB

74

INTA

73

SADR

72

VDDH_3

71

SCL

70

SDA

69

VSS_8

68

HDVDDL0

67

SADR_S

66

NC_2

65

SADR_T

64

VDDL_6

63

VSS_7

62

ERRB

61

SYNCB

60

ERRA

59

SYNCA

58

TDO

57

CSEL1

56

CSEL0

55

TMS

54

TRST

53

VDDL_5

52

VSS_6

51

48

49

50

TDI

NRST

TEST3

L604

MLB-2 01209-0 120P-N 2

DEMOD_OPT

C642

0. 1uF

16V

AZ1117H-ADJTRE1(EH11A)

INPUT

22

DEMOD_OPT

22

DEMOD_OPT

22

DEMOD_OPT

22

DEMOD_OPT

DEMOD_OPT

C643

IC6 01

3

OUTPUT

R631

R632

R629

R630

DEMOD_OPT

DEMOD_OPT

DEMOD_OPT

DEMOD_OPT

0. 1uF

16V

2

0. 1uFC648

0. 1uFC647

0. 1uFC646

0. 1uFC645

DEMOD_OPT

1

+3.3V_DE

DEMOD_OPT

C644

0. 1uF

16V

ADJ/GND

R633

1.2 K

R1

FE_TS_VAL

FE_TS_SYN

FE_TS_SERIAL

FE_TS_CLK

+3.3V_DE

2.7 K

R634

READY

C650

0. 1uF

16V

0. 1uF

READY

C649

16V

R2

R635

10

C652

DEMOD_OPT

R637

22

22

R636

DEMOD_OPT

READY

10uF

6.3 V

R638

2.2 K

A1[GN]

DEMOD_OPT

C

1K

R640

A2[RD]

D600

DEMOD_OPT

SAM2333

+1.2V_DE

+3.3V_DE

R639

2.2 K

DEMOD_RESET

C651

10uF

6.3 V

READY

SCL2_3. 3V

SDA2_3.3V

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

EAX61354901

TUNER

1 1 1 3

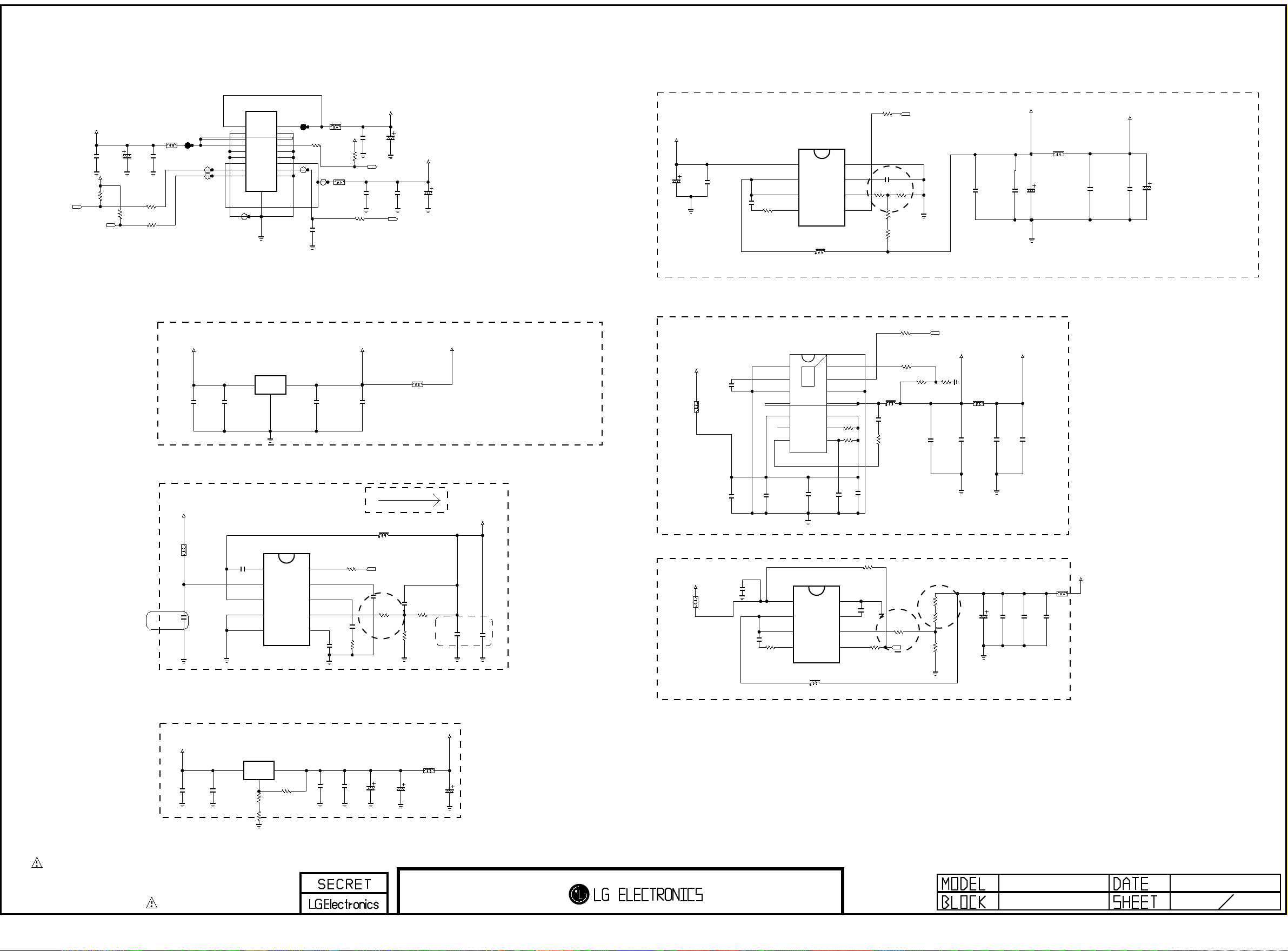

POWER B/D

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

POWER Wafer 24P

P_+5V

C501

C500

100 uF

10u F

16V

6. 3V

READY

+5V_ST

READY

R500

10K

RL_ON

5V_ON

READY

R501

10K

P500

SMAW200-H18S1

2

CURRENT: MAX 6A

EAM38058401

CB4532UK121E

C507

0. 1u F

16V

R502

10 0

R506

10 0

L501

1

4

3

6

5

8

7

9

10

12

11

13

14

16

15

18

17

19

Stand-b y ( 5 V ST -- > + 3 . 3V)

+5V_ST

IC 506

EAN5880170 1

C502

10u F

6. 3V

C503

0. 1u F

16V

AP2 121N- 3.3TR E1

VIN

VOUT

2

3

1

GND

CURRENT: MAX 3A

L505

0LCML00003B

MLB- 201209 -0120P -N2

D3.3V

0 R512

READY

CURRENT: MAX 3A

MLB- 201209 -0120P -N2

L506

0LCML00003B

C520

0. 1u F

16V

C508

10u F

6. 3V

R513

10K

C521

0. 1u F

16V

R514

10 0

C518

0. 1u F

50V

READY

+3.3 V_ST

C509

0. 1u F

16V

P_17V

C519

33u F

25V

ERROR_DET

C522

10u F

6. 3V

+5V_ST

100 uF

AC_DET

L502

EAM44020101

CB3216PA501E

C523

16V

+3.3V_NEC_ST

Multi Powe r ( 5 V - - > 3 . 3 V )

P_+5V

C526

47uF

16V

+5V_ST

L507

C527

22uF

10V

C528

0. 1uF

MP8706EN-C247-LF-Z

IN

SW_1

SW_2

C534

0. 1uF

47

BST

R519

AGND

1

SS

2

PGND_1

3

SW_1

4

IN_1

5

NC

6

BS

7

MP2208DL-LF-Z

1

2

3

4

IC50 3

THERMAL

IC504

3A

L508

3.6 uH

15

0. 1uF

C542

16V

C543

0. 1uF

16V

A1.2V

D3.3V

L514

UBW2012-121F

C548

100u F

16V

C549

22uF

10V

0. 1uF

C550

16V

A3.3V

C551

100u F

16V

READY

001 :H5

+3.3V_EN

0

R527

GND

8

VCC

7

FB

6

EN/SYNC

5

EP

FB

14

EN/SYNC

13

PGND_2

12

SW_2

11

IN_2

10

POK

R515

9

100K

R516

VCC

8

10

R537

0

1/10W

5%

39K1%R528

1.2 K1%R529

C535

0. 1uF

R520

0

L509

2uH

1uF

C540

R1

R530

13K

1/8W

1%

R522

R523

0

0

R2

R521

470K

1%

R1

C536

22uF

16V

Vou t=0 .8* (1+ R1/ R2)

1.2V_ 1.8V_EN

D1.2V

R525

820K

1%

R2

BLM18PG121SN1D

C537

22uF

16V

L510

C541

22uF

10V

C538

22uF

16V

Vout =0.9*( 1+R2/R 1)=1.8 45

+5V_ST

EN105J12CIC

IC5 01

MP2108DQ

0. 01u F

25V

C510

PGND

SGND

BST

1

VIN

2

3A

LX

3

4

5

RUN

10

VREF

9

COMP

8

FB

7

SS

6

C I N

L500

Plac ed o n SM D-TO P

C504

22uF

10V

Multi Powe r ( 5 V - - > 2 . 5 V )

P_+5V

READY

C505

10u F

6. 3V

C506

0. 1u F

16V

INPUT

IC5 02

0IPMG78346A

AZ1085S-ADJ TR/E1

OUTPUT

2

3

1

ADJ/GND

9101%R504

R2

1%

66 .5

R505

R509

1K

1%

R1

V0 = 1.2 5( 1+R 2/ R1)

MUST BE CHANGE ADJ LDO

AFTER THEN CHECK CST

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

300 mA

L503

R508

10K

C561

0. 01u F

25V

C514

3300 pF

50V

R503

6.8 K

3.6 uH

NR8040T3R6N

1.2V_ 1.8V_EN

READY

100p F

R539

0

1/10W

5%

50V

C562

R510

10K

1/10W

1%

R2

R511

10. 5K

R1

1%

Re pl ac e d Pa rt

C511

0. 01u F

25V

BCM3556 core 2.5V

L504

0LCML00003B

MLB- 201209 -0120P -N2

READY

C515

C513

10u F

6. 3V

0. 1u F

16V

C516

100 uF

16V

C517

100 uF

16V

C512

22uF

10V

A2.5V

C525

100 uF

16V

D1.8V

Plac ed o n SM D-TO P

C564

0. 1uF

C529

0. 1uF

TUNER 5V

P_17V

L511

C530

22uF

16V

MP8706EN-C247-LF-Z

C544

10uF

25V

C553

0. 1uF

47

1/10W

R532

5%

SW_1

SW_2

BST

IN

C531

0. 1uF

IC505

1

2

3A

3

4

L515

10uH

NR8040T100M

C532

1uF

10V

Vou t=0 .8* (1+ R1/ R2)

C533

22uF

R531

100K

READY

GND

8

7

6

5

VCC

FB

EN/SYNC

C552

1uF

50V

10K

R533

R538

300K

1/10W

5%

RL_ON

1%

18K

R540

R1

15K1%R535

6.2 K1%R536

R2

Vo ut=(1+R1/R2 )*0 .8

130mA

C556

100 uF

16V

C559

0. 1u F

16V

+5V_TU

L516

0LCML00003B

MLB- 201209 -0120P -N2

C557

C558

10u F

10u F

6. 3V

6. 3V

BCM AUS DVR

SMPS POWER

08/10/ x x

5 1 3

LGE3556C (C0 V ERSION)

Copyright © 2010 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

IC10 0

DDR_PLL_TEST

DDR_PLL_LDO

DDR_EXT_CLK

DDR_VDDP1P8_1

DDR_VDDP1P8_

DDR_BVDD0

DDR_BVDD1

DDR_BVSS0

DDR_BVSS1

DDR01_CKE

DDR_COMP

DDR01_ODT

DDR0_CLK

DDR0_CLKB

DDR1_CLK

DDR1_CLKB

DDR01_A00

DDR01_A01

DDR01_A02

DDR01_A03

DDR0_A04

DDR0_A05

DDR0_A06

DDR01_A07

DDR01_A08

DDR01_A09

DDR01_A10

DDR01_A11

DDR01_A12

DDR01_A13

DDR1_A04

DDR1_A05

DDR1_A06

DDR01_BA0

DDR01_BA1

DDR01_BA2

DDR01_CASB

DDR0_DQ00

DDR0_DQ01

DDR0_DQ02

DDR0_DQ03

DDR0_DQ04

DDR0_DQ05

DDR0_DQ06

DDR0_DQ07

DDR0_DQ08

DDR0_DQ09

DDR0_DQ10

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR0_DQ15

DDR1_DQ00

DDR1_DQ01

DDR1_DQ02

DDR1_DQ03

DDR1_DQ04

DDR1_DQ05

DDR1_DQ06

DDR1_DQ07

DDR1_DQ08

DDR1_DQ09

DDR1_DQ10

DDR1_DQ11

DDR1_DQ12

DDR1_DQ13

DDR1_DQ14

DDR1_DQ15

DDR0_DM0

DDR0_DM1

DDR1_DM0

DDR1_DM1

DDR0_DQS0

DDR0_DQS0B

DDR0_DQS1

DDR0_DQS1B

DDR1_DQS0

DDR1_DQS0B

DDR1_DQS1

DDR1_DQS1B

DDR01_RASB

DDR_VREF0

DDR_VREF1

DDR01_WEB

A6

A24

B7

B24

F20

B23

B17

C22

E16

C23

B12

C12

A13

A12

B15

E14

A15

D15

E13

E12

F13

C14

F14

B14

D14

C13

D13

B13

F15

C15

D16

F16

B16

E15

A17

A8

B11

B8

D11

E11

C8

C11

C9

D8

E10

E9

F11

F12

E8

D10

F8

C18

C20

A18

B21

C21

B18

B20

D18

E18

D21

F18

E20

A22

F17

B22

E17

A10

C10

A20

F19

B10

B9

F10

F9

B19

C19

E19

D19

C16