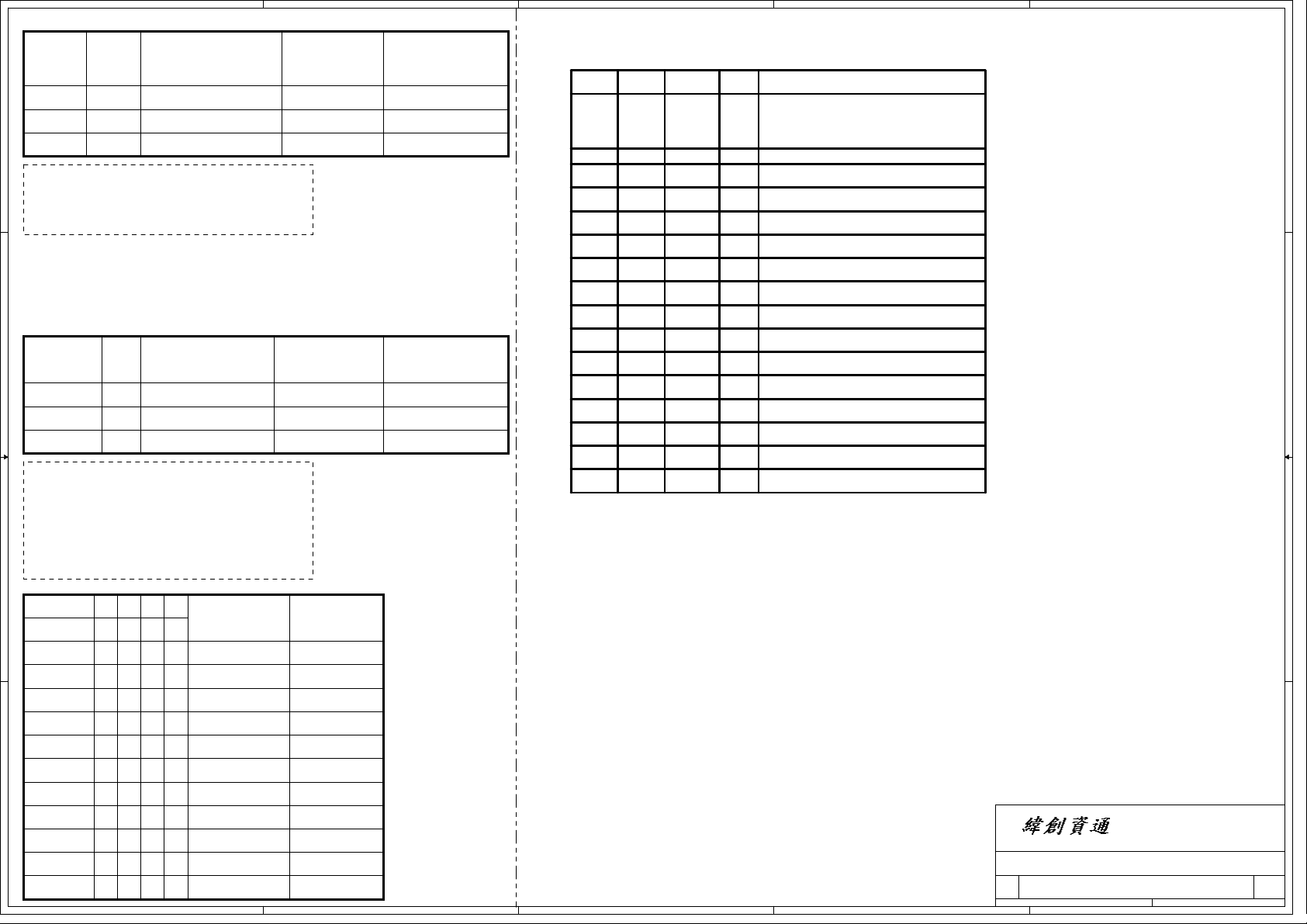

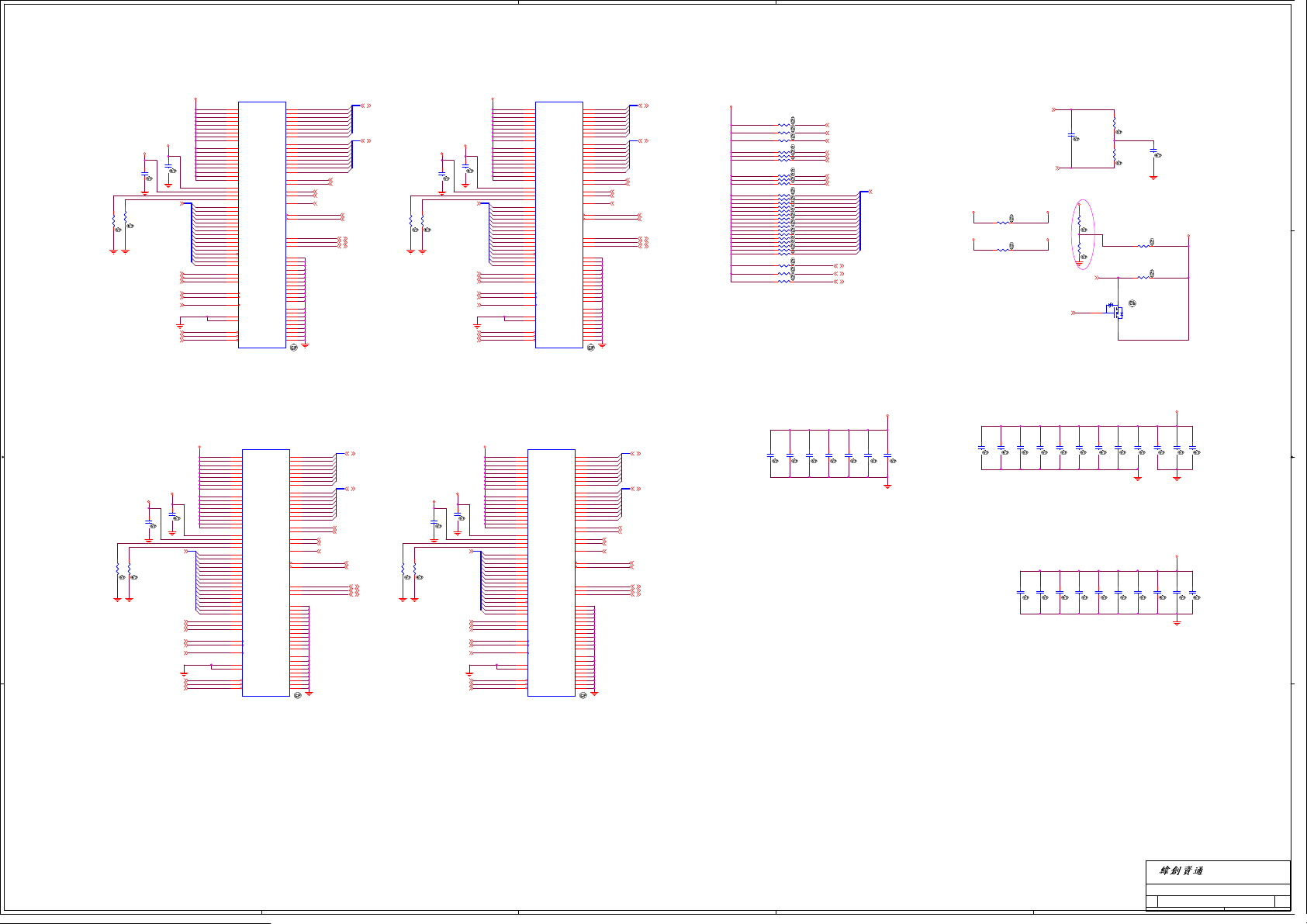

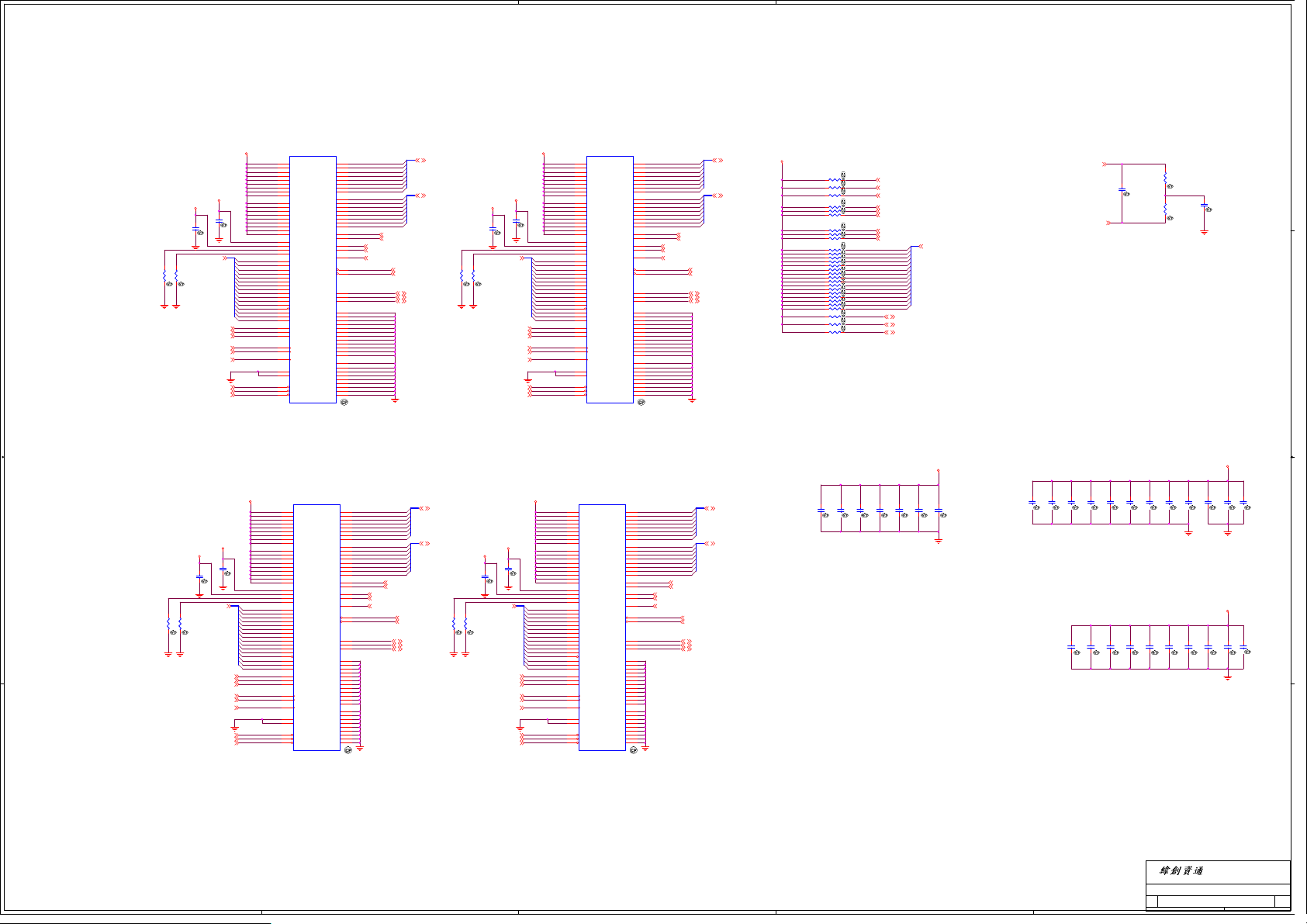

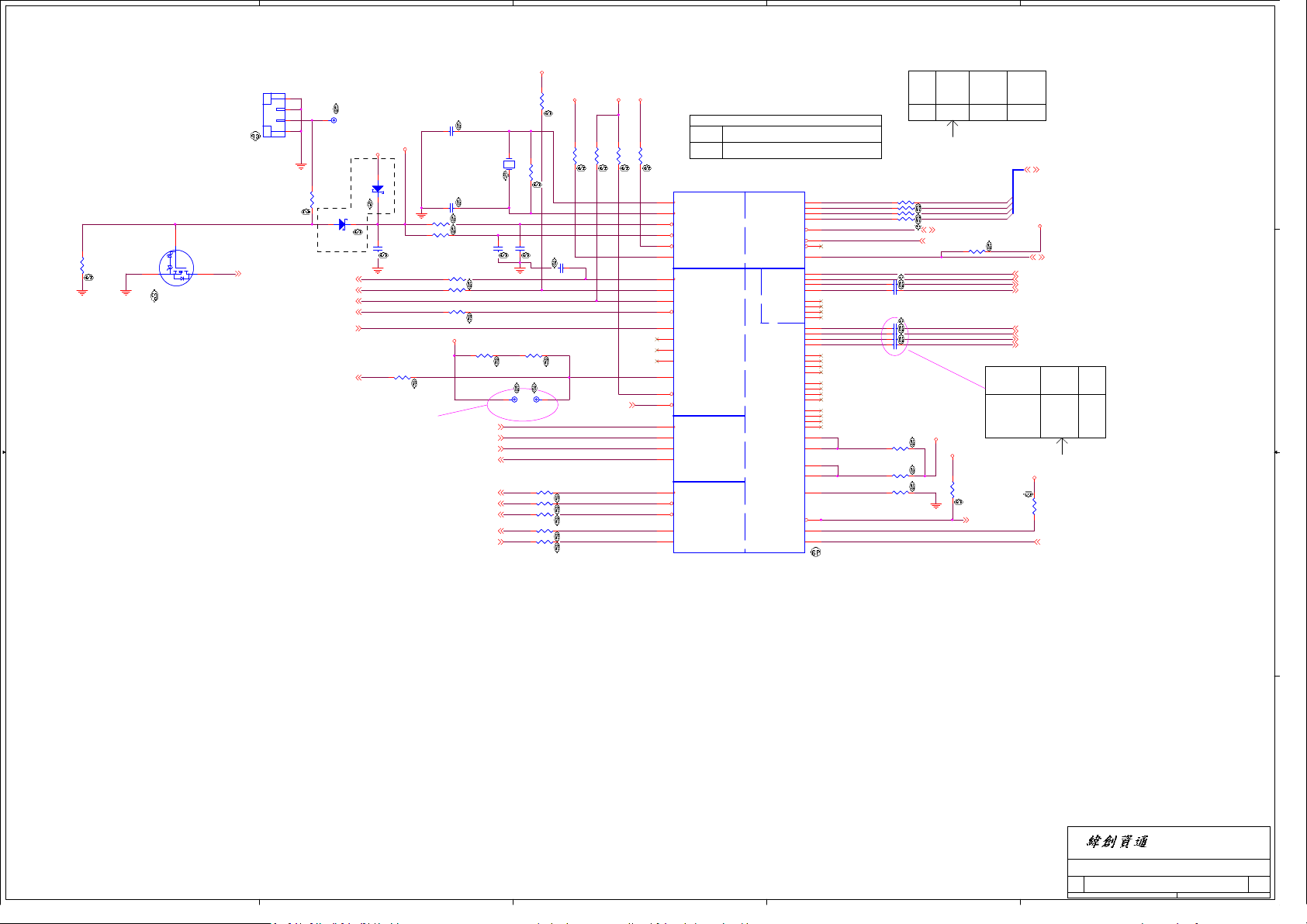

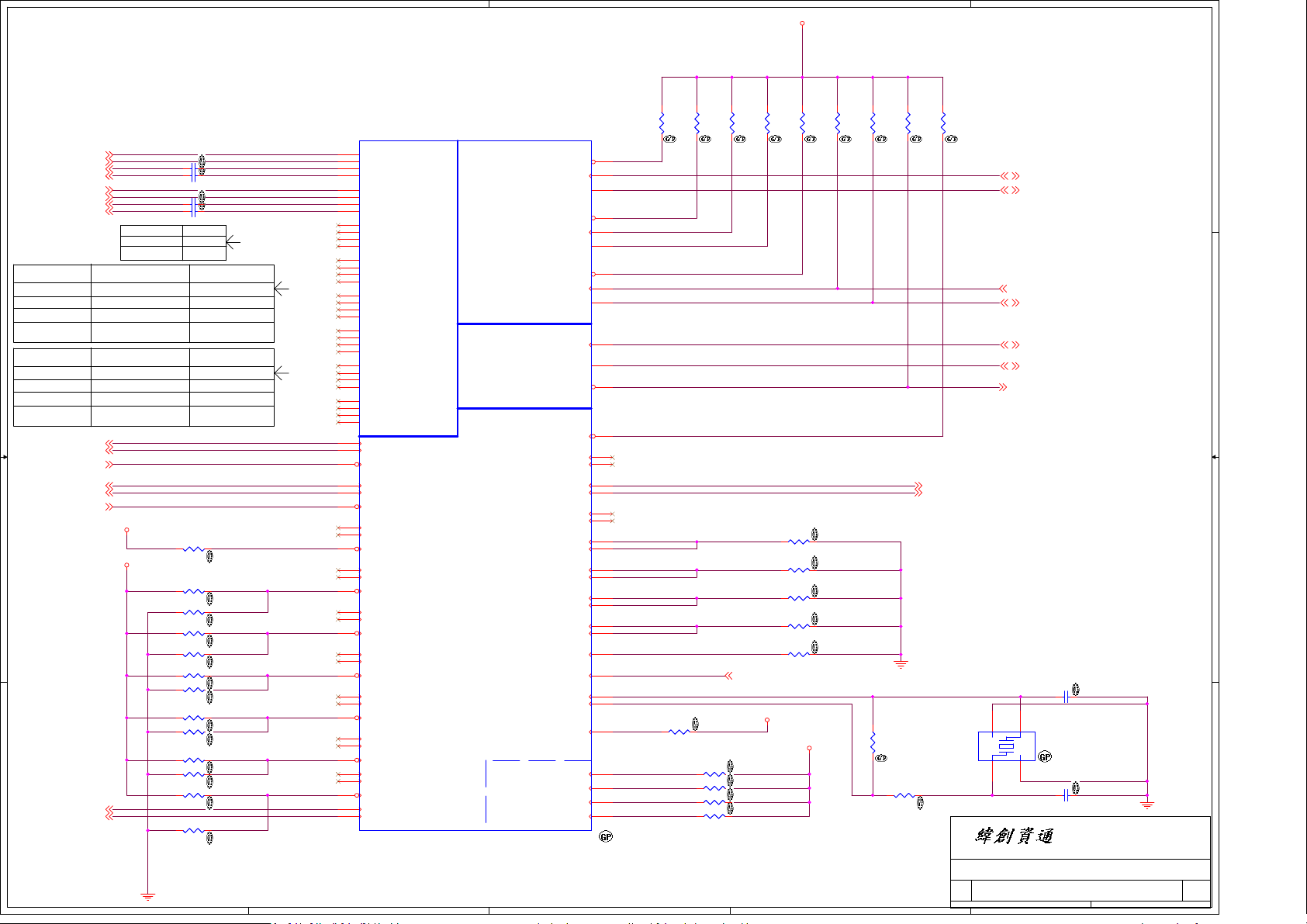

Lenovo X1 Carbon Schematic

I2C Bus / SM Bus

Bus Switch IC

70

UNBUFFERED

DDR3 SODIMM

SMBus

12,13

SATA

USB2.0(AOU)

Finger Print

Bluetooth

SATA

CONN

Audio

Codec

USB 3.0

42

64

42

Channel A / B

DDR3 1333

Serial ATA I/F

40

Azalia bus

43

CH1

42

CH9

CH10

CH11

Port0

USB3.0

USB 2.0

Intel

Ivy Bridge

DDR3 1333MHz

INTEGRATED GRAHPICS

3,4,5,6,7,8,9,10

DMI x4

Intel

Panther Point

LVDS CRT

Display Port

USB 2.0 (14 ports)

USB 3.0 (4 ports)

LAN Connect I/F (LCI)

Serial ATA 300MB/s

HDA Interface

ACPI 2.0

LPC I/F

PCI Rev 2.3

PCI Express

INT. RTC

24,25,26,27,28,29,30,31,32

SPI

SPI-FLASH

58

G-Sensor

Touch Pad

FDI

67

64

LVDS

Display Port

USB 2.0 CH13

PCI Express

SATA

USB 2.0 CH3

PCI Express

USB 2.0 CH12

EC

MEC1619

60,61,62

Int. KB

Track point IV

XDP

Conn.

13'' HD+ LCD

AC Coupling

Camera (LCD Conn)

Media Card

Reader

Mini PCI-E

WWAN Card

Mini PCI-E

WLAN Card

FAN

64

Genesis-1 Block Diagram

11

34

38

34

54

53

53

LPC Bus / 33MHz

Thinker

Engine

71,72

66

LGS-1 91.4RQ01.001

JULY. 18, 2011

Display Port

4-in-1 Slot

37

55

LPC Debug

Board Conn

DC-IN

Battery Input

ST19NP18-TPM-A

58

<Core Design>

<Core Design>

<Core Design>

73

74

TCPA

68

PCB Layer Stackup

L1:Component

L2:GND

L3:Signal 1

L4:VCC

L5:Signal 2

L6:Signal 3

L7:VCC

L8:Signal 4

L9:GND

L10:Component

Battery Charger/Selector

BQ24760

INPUTS

VINT20 CHARGER_OUT12

75

OUTPUTS

System DC/DC

TPS51220ARSN

VINT20

79

VCC5M

VCC3M

CPU DC/DC

VT1318M/VT1324S

VCC5M_OUT

80

VCCCPUCORE

GMCH GFX CORE

VT1324S

VCC5M_OUT VCCGFXCORE

81

VCC1R5B

VT355FCX

VCC5M_OUT

86

VCC1R5B

VCC0R675B

MAX1510

VCC1R35A

VT356FCX

VCC5M_OUT VCC1R35A

VCC1R35A VCC0R675B

87

88

VCC1R8B

BD9139

VCC5M_OUT

89

VCC1R8B

VCC1R05AMT

VT356FCX

VCC1R05LANVCC5M_OUT

85

VCC1R05B_VTT

VT356

VCC5M_OUT

VCC1R05B_VTT

84

VCCSA

VT371

VCC5M_OUT

VCCSA

90

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Genesis-1

Genesis-1

Genesis-1

1 100Monday, January 30, 2012

1 100Monday, January 30, 2012

1 100Monday, January 30, 2012

SC

SC

SC

A

B

C

D

E

RESISTOR

Symbol name

4 4

The naming rule is value + R + size + tolerance

For the value, it can be read by the number before R. (R means resistor)

For the tolerance, it can be read from the last letter.

For the rating, we don't show on the symbol name.

For the size, R2=>0402, R3=>0603, R5=>0805,....

Value

Tolerance

(J: 5%, F: 1%, D: 0.5%, B: 0.1 %)

Rating

0402=> 1/16W, 25V

0603 => 1/16W, 75V

0805 => 1/10W, 100V

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

EC HISTORY

Stage Date

EC No. Page

Note

CAPACITOR

3 3

Symbol name

Tolerance

(M: +/-20, K: +/-10, Z: +80/-20)

RatingValue

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

The naming rule is

Capacitor type + value + rating + size + tolerance + material

SCD1U10V2MX-1

SC=> SMT Ceremic, TC=> POS cap or SP cap

D1U => 0.1uF

10V => the voltage rating is 10V

2=> 0402, 3=>0603, 5=>0805

M=>tolerance M, K, Z

X=> X7R/X5R, Y=> Y5V

-1 => symbol version, nonsense to EE characteristic

2 2

PLANAR_ID[3..0]

IBEXPEAK-M 39

PLANAR_IDn

1 1

38

48 49

3

2

1

0 0

0 0 0 1

0 0 01

0 01

1 0 0 0

1 0 0 1

0

10 0 0

1 10 0

1 10 0

1 1 10

A

0

0

1

0101

Planar ID Version

Genesis-1 initial

FVT N/A

SIT SC

Planar PCB Version

N/A

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

B

C

D

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Reference

Reference

Reference

Genesis-1

Genesis-1

Genesis-1

2 100Monday, January 30, 2012

2 100Monday, January 30, 2012

2 100Monday, January 30, 2012

E

SC

SC

SC

A

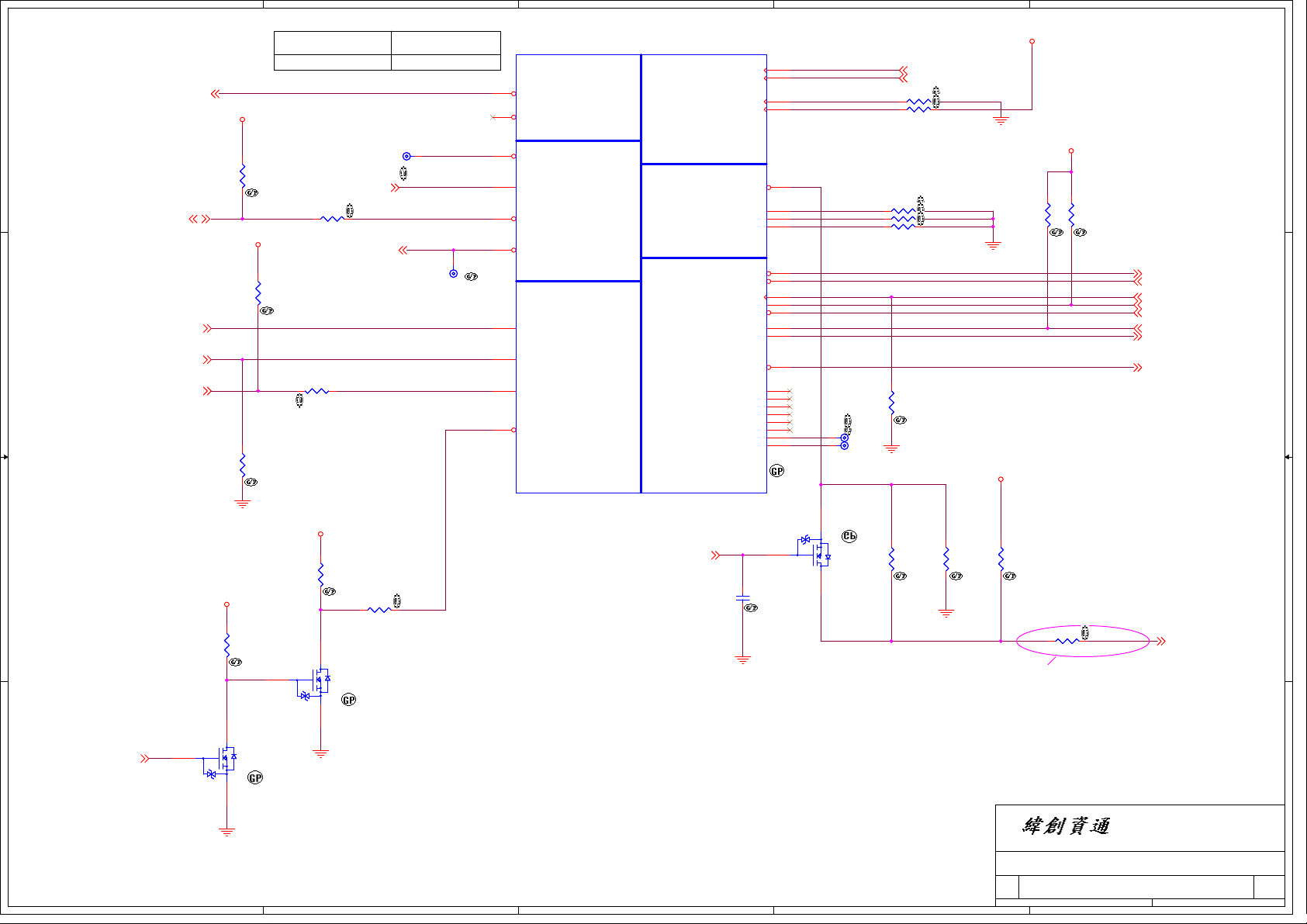

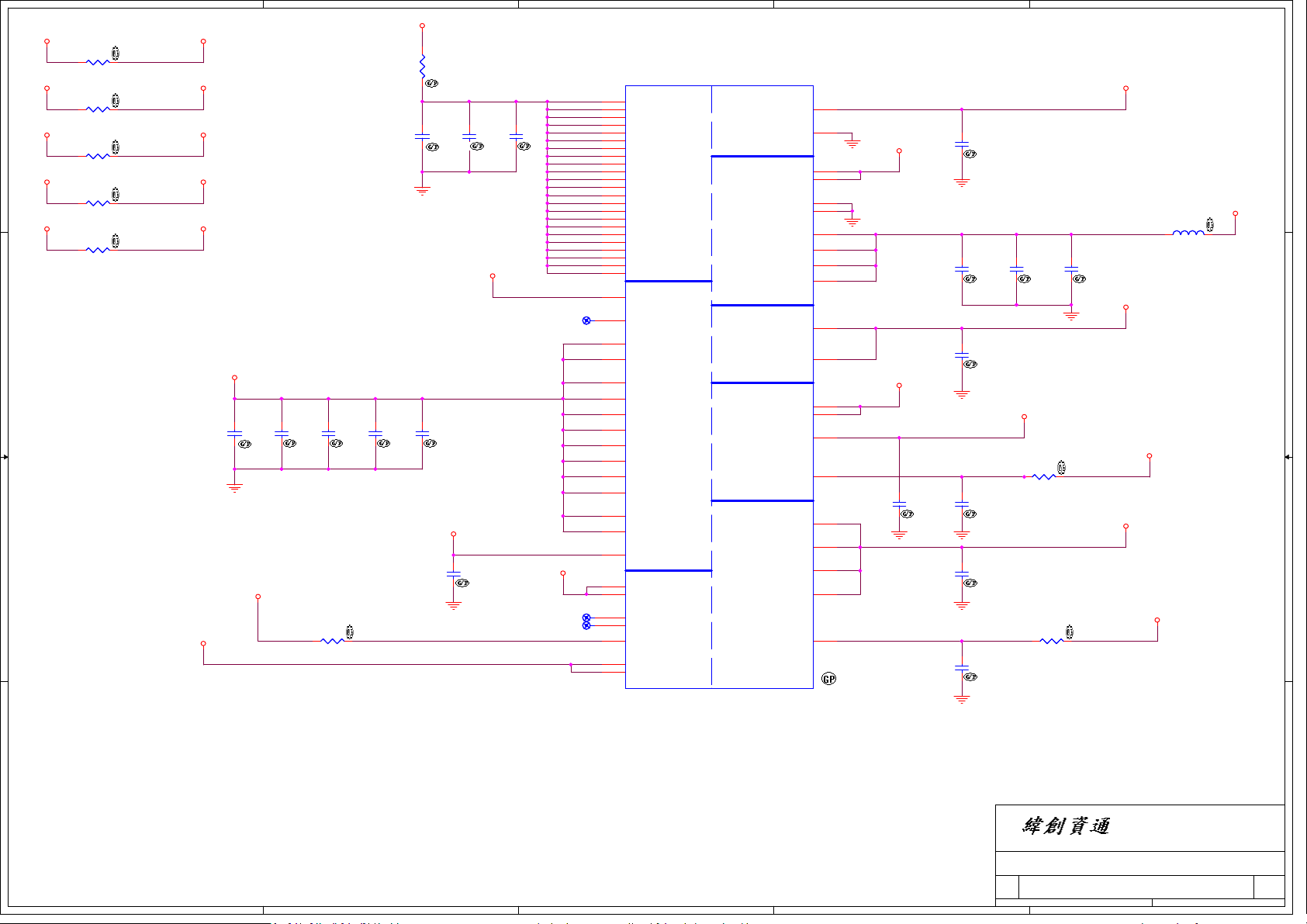

FDI_FSYNC026

FDI_FSYNC126

FDI_INT26

FDI_LSYNC026

FDI_LSYNC126

1 2

DMI_TXN[3..0]26

DMI_TXP[3..0]26

DMI_RXN[3..0]26

DMI_RXP[3..0]26

FDI_TXN[7..0]26

FDI_TXP[7..0]26

4 4

3 3

VCC1R05B_VTT_CPU

R2 24D9R2F-L-GPR2 24D9R2F-L-GP

2 2

B

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

eDP_COMP_CPU

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

U1A

U1A

M2

P6

P1

P10

N3

P7

P3

P11

K1

M8

N4

R2

K3

M7

P4

T3

U7

W11

W1

AA6

W6

V4

Y2

AC9

U6

W10

W3

AA7

W7

T4

AA3

AC8

AA11

AC12

U11

AA10

AG8

AF3

AD2

AG11

AG4

AF4

AC3

AC4

AE11

AE7

AC1

AA4

AE10

AE6

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

DMI_RX#0

DMI_RX#1

DMI_RX#2

DMI_RX#3

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX#0

DMI_TX#1

DMI_TX#2

DMI_TX#3

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI0_TX#0

FDI0_TX#1

FDI0_TX#2

FDI0_TX#3

FDI1_TX#0

FDI1_TX#1

FDI1_TX#2

FDI1_TX#3

FDI0_TX0

FDI0_TX1

FDI0_TX2

FDI0_TX3

FDI1_TX0

FDI1_TX1

FDI1_TX2

FDI1_TX3

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

EDP_COMPIO

EDP_ICOMPO

EDP_HPD#

EDP_AUX#

EDP_AUX

EDP_TX#0

EDP_TX#1

EDP_TX#2

EDP_TX#3

EDP_TX0

EDP_TX1

EDP_TX2

EDP_TX3

C

1 OF 9

1 OF 9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#0

PEG_RX#1

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

PEG_COMP_CPU

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

D

R1 24D9R2F-L-GPR1 24D9R2F-L-GP

1 2

E

VCC1R05B_VTT_CPU

1 1

A

B

C

D

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU(1/8):DMI/EDP/PEG/FDI

CPU(1/8):DMI/EDP/PEG/FDI

CPU(1/8):DMI/EDP/PEG/FDI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

3 100Monday, January 30, 2012

3 100Monday, January 30, 2012

3 100Monday, January 30, 2012

E

SC

SC

SC

A

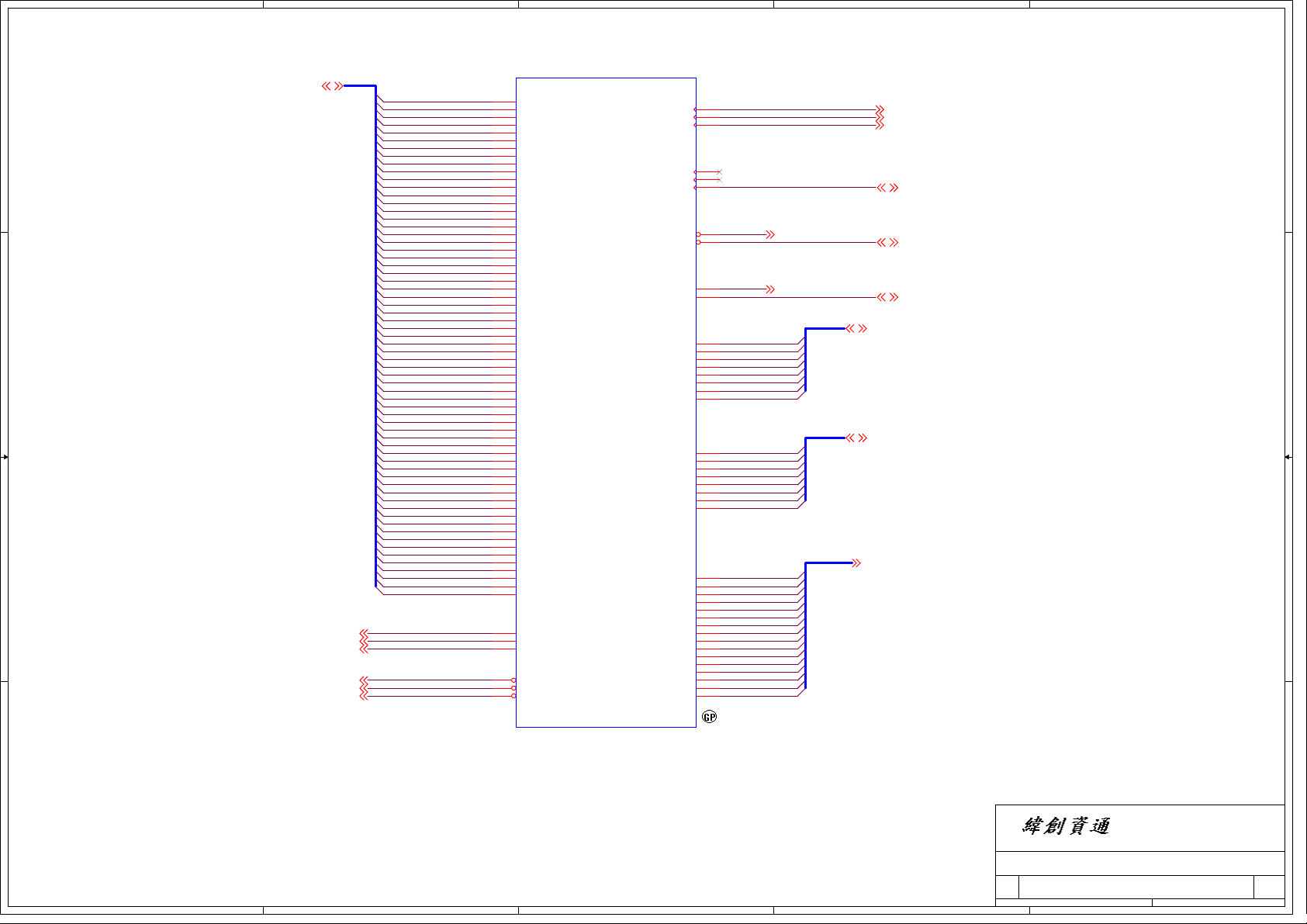

Table -PROC_SELECT(-PROC_IVY)

Sandy Bridge

Ivy Bridge

-PROC_IVY29

4 4

-PROCHOT62,80

PM_SYNC26

3 3

CPUPWRGD11,29

DRAMPW RG26,32,87

VCC1R05B_VTT_CPU

12

R5

R5

62R2J-GP

62R2J-GP

VCC1R35_VDDQ

12

R12

R12

200R2J-L1-GP

200R2J-L1-GP

12

R15

R15

10KR2J-3-GP

10KR2J-3-GP

R7 56R2J-4-GPR7 56R2J-4-GP

1 2

R73

R73

12

130R2J-GP

130R2J-GP

TPAD40-GP

TPAD40-GP

PECI62

-THERMTRIP29

TP2

TP2

B

High

Low

CATERR#

1

PROCHOT_CPU

1

SM_DRAMPWROK

TP1

TP1

TPAD40-GP

TPAD40-GP

-CPURST

U1B

U1B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

C

2 OF 9

2 OF 9

MISC

MISC

CLOCKS

CLOCKS

THERMAL

THERMAL

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

TDI

J3

H2

AG3

AG1

AT30

SM_RCOMP0_CPU

BF44

SM_RCOMP1_CPU

BE43

SM_RCOMP2_CPU

BG43

N53

N55

L56

L55

J58

M60

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

DPLL_REF_CLKDPLL_REF_CLK

-DPLL_REF_CLL

R6 140R2F-GPR6 140R2F-GP

R10 25D5R2F-GPR10 25D5R2F-GP

R11 200R2F-L-GPR11 200R2F-L-GP

TPAD40-GP

TPAD40-GP

TP118

TP118

1

1

TP119

TP119

TPAD40-GP

TPAD40-GP

SM_DRAMRST_CPU

D

CPU_CLK_100M 25

-CPU_CLK_100M 25

R70 1KR2J-1-GPR70 1KR2J-1-GP

1 2

R72 1KR2J-1-GPR72 1KR2J-1-GP

1 2

1 2

1 2

1 2

12

R13

R13

51R2J-2-GP

51R2J-2-GP

VCC1R05B_VTT_CPU

51R2J-2-GP

51R2J-2-GP

VCC1R35A

VCC1R05B_VTT_CPU

12

R8

R8

12

R9

R9

51R2J-2-GP

51R2J-2-GP

E

-XDP_PRDY 11

-XDP_PREQ 11

XDP_TCK 11

XDP_TMS 11

-XDP_TRST 11

XDP_TDI 11

XDP_TDO 11

-XDP_DBR 11,26

VCC1R05B_VTT_CPU

Q2

12

R1309

2 2

VCC3B

12

R14

R14

1KR2J-1-GP

1KR2J-1-GP

G

DS

LSK3541G1ET2L-GP

LSK3541G1ET2L-GP

-PLTRST_FAR11,28,58,60

1 1

A

G

Q5

Q5

R1309

75R2J-1-GP

75R2J-1-GP

R1308 43R2J-GPR1308 43R2J-GP

1 2

-CPURST_R

DS

LSK3541G1ET2L-GP

LSK3541G1ET2L-GP

Q4

Q4

B

DRAMRST_GATE12,28

C

G

12

DY

DY

C1

C1

SCD047U25V2KX-GP

SCD047U25V2KX-GP

Q2

LSK3541G1ET2L-GP

LSK3541G1ET2L-GP

D S

12

R17

R17

0R2J-2-GP

0R2J-2-GP

D

DY

DY

-DRAMRST_R

12

R18

R18

5K1R2J-4-GP

5K1R2J-4-GP

12

R19

R19

1KR2J-1-GP

1KR2J-1-GP

R88 1KR2J-1-GPR88 1KR2J-1-GP

1 2

-DRAMRST 12,13

Place near DIMM connector.

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU(2/8):CLK/MISC/JTAG

CPU(2/8):CLK/MISC/JTAG

CPU(2/8):CLK/MISC/JTAG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

4 100Monday, January 30, 2012

4 100Monday, January 30, 2012

4 100Monday, January 30, 2012

E

SC

SC

SC

A

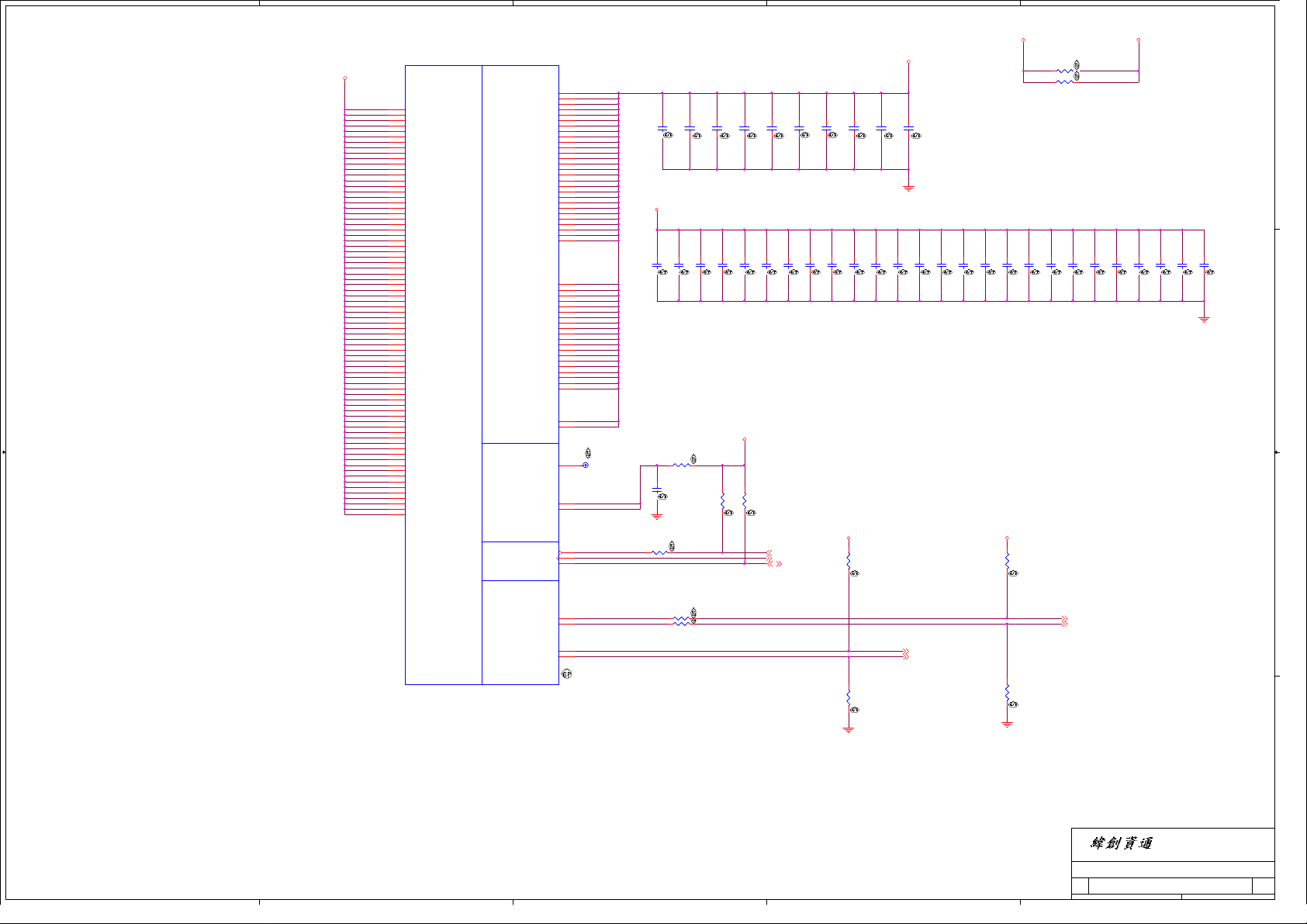

M_A_DQ[63..0]12

4 4

3 3

2 2

M_A_BS012

M_A_BS112

M_A_BS212

-M_A_CAS12

-M_A_RAS12

-M_A_WE12

B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60M_A_DQ60

M_A_DQ61M_A_DQ61

M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62M_A_DQ62

M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63M_A_DQ63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

U1C

U1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

C

3 OF 9

3 OF 9

AU36

SA_CK0

AV36

SA_CK#0

AY26

SA_CKE0

AT40

SA_CK1

AU40

SA_CK#1

BB26

SA_CKE1

BB40

SA_CS#0

BC41

SA_CS#1

AY40

SA_ODT0

BA41

SA_ODT1

AL11

SA_DQS#0

AR8

SA_DQS#1

AV11

SA_DQS#2

AT17

SA_DQS#3

AV45

SA_DQS#4

AY51

SA_DQS#5

AT55

SA_DQS#6

AK55

SA_DQS#7

AJ11

SA_DQS0

AR10

SA_DQS1

AY11

SA_DQS2

AU17

SA_DQS3

AW45

SA_DQS4

AV51

SA_DQS5

AT56

SA_DQS6

AK54

SA_DQS7

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

BG35

SA_MA0

BB34

SA_MA1

BE35

SA_MA2

BD35

SA_MA3

AT34

SA_MA4

AU34

SA_MA5

BB32

SA_MA6

AT32

SA_MA7

AY32

SA_MA8

AV32

SA_MA9

BE37

SA_MA10

BA30

SA_MA11

BC30

SA_MA12

AW41

SA_MA13

AY28

SA_MA14

AU26

SA_MA15

M_A_DDRCLK0_800M

-M_A_DDRCLK0_800M

M_A_CKE0

-M_A_DQS0

-M_A_DQS1

-M_A_DQS2

-M_A_DQS3

-M_A_DQS4

-M_A_DQS5

-M_A_DQS6

-M_A_DQS7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

-M_A_CS0 12

M_A_ODT0 12

D

M_A_DDRCLK0_800M 12

-M_A_DDRCLK0_800M 12

M_A_CKE0 12

M_A_CKE1 12

-M_A_CS1 12

M_A_ODT1 12

-M_A_DQS[7..0] 12

M_A_DQS[7..0] 12

M_A_A[15..0] 12

E

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

1 1

A

B

C

D

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU(3/8):DDR3 Channel-A

CPU(3/8):DDR3 Channel-A

CPU(3/8):DDR3 Channel-A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

5 100Monday, January 30, 2012

5 100Monday, January 30, 2012

5 100Monday, January 30, 2012

E

SC

SC

SC

A

M_B_DQ[63..0]13

4 4

3 3

2 2

M_B_BS013

M_B_BS113

M_B_BS213

-M_B_CAS13

-M_B_RAS13

-M_B_WE13

B

U1D

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63 M_B_A2

AL4

AL1

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BD13

BF12

BF8

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

C

4 OF 9

4 OF 9

BA34

SB_CK0

AY34

SB_CK#0

AR22

SB_CKE0

BA36

SB_CK1

BB36

SB_CK#1

BF27

SB_CKE1

BE41

SB_CS#0

BE47

SB_CS#1

AT43

SB_ODT0

BG47

SB_ODT1

AL3

SB_DQS#0

AV3

SB_DQS#1

BG11

SB_DQS#2

BD17

SB_DQS#3

BG51

SB_DQS#4

BA59

SB_DQS#5

AT60

SB_DQS#6

AK59

SB_DQS#7

AM2

SB_DQS0

AV1

SB_DQS1

BE11

SB_DQS2

BD18

SB_DQS3

BE51

SB_DQS4

BA61

SB_DQS5

AR59

SB_DQS6

AK61

SB_DQS7

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

BF32

SB_MA0

BE33

SB_MA1

BD33

SB_MA2

AU30

SB_MA3

BD30

SB_MA4

AV30

SB_MA5

BG30

SB_MA6

BD29

SB_MA7

BE30

SB_MA8

BE28

SB_MA9

BD43

SB_MA10

AT28

SB_MA11

AV28

SB_MA12

BD46

SB_MA13

AT26

SB_MA14

AU22

SB_MA15

M_B_DDRCLK0_800M

-M_B_DDRCLK0_800M

-M_B_DQS0

-M_B_DQS1

-M_B_DQS2

-M_B_DQS3

-M_B_DQS4

-M_B_DQS5

-M_B_DQS6

-M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CKE0

-M_B_CS0 13

M_B_ODT0 13

D

M_B_DDRCLK0_800M 13

-M_B_DDRCLK0_800M 13

M_B_CKE0 13

-M_B_DQS[7..0] 13

M_B_DQS[7..0] 13

M_B_A[15..0] 13

E

M_B_CKE1 13

-M_B_CS1 13

M_B_ODT1 13

IVY-BRIDGE-GP-NF

1 1

A

B

C

D

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU(4/8):DDR3 Channel-B

CPU(4/8):DDR3 Channel-B

CPU(4/8):DDR3 Channel-B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

6 100Monday, January 30, 2012

6 100Monday, January 30, 2012

6 100Monday, January 30, 2012

E

SC

SC

SC

A

VCCCPUC ORE

4 4

3 3

2 2

B

POWER

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

POWER

CORE SUPPLY

CORE SUPPLY

U1F

U1F

A26

A29

A31

A34

A35

A38

A39

A42

C26

C27

C32

C34

C37

C39

C42

D27

D32

D34

D37

D39

D42

E26

E28

E32

E34

E37

E38

F25

F26

F28

F32

F34

F37

F38

F42

G42

H25

H26

H28

H29

H32

H34

H35

H37

H38

H40

J25

J26

J28

J29

J32

J34

J35

J37

J38

J40

J42

K26

K27

K29

K32

K34

K35

K37

K39

K42

L25

L28

L33

L36

L40

N26

N30

N34

N38

6 OF 9

6 OF 9

AF46

VCCIO1

AG48

VCCIO3

AG50

VCCIO4

AG51

VCCIO5

AJ17

VCCIO6

AJ21

VCCIO7

AJ25

VCCIO8

AJ43

VCCIO9

AJ47

VCCIO10

AK50

VCCIO11

AK51

VCCIO12

AL14

VCCIO13

AL15

VCCIO14

AL16

VCCIO15

AL20

VCCIO16

AL22

VCCIO17

AL26

VCCIO18

AL45

VCCIO19

AL48

VCCIO20

AM16

VCCIO21

AM17

VCCIO22

AM21

VCCIO23

AM43

VCCIO24

AM47

VCCIO25

AN20

VCCIO26

AN42

VCCIO27

AN45

VCCIO28

AN48

VCCIO29

AA14

VCCIO30

AA15

VCCIO31

AB17

VCCIO32

RAILS

RAILS

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VCCIO41

VCCIO42

VCCIO43

VCCIO44

VCCIO45

VCCIO46

VCCIO47

VCCIO48

VCCIO49

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE1

VCCPQE2

VIDALERT#

VIDSCLK

VIDSOUT

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

1

VIDALERT_CPU

PEG IO AND DDR IO

PEG IO AND DDR IO

SVID QUIET

SVID QUIET

TP21

TP21

TPAD14-GP

TPAD14-GP

VCCPQE

C

12

C2

SC10U6D3V3MX-GPC3SC10U6D3V3MX-GP

SC22U6D3V3MX-L-GPC2SC22U6D3V3MX-L-GP

VCC1R05B_VT T_CPU

C107

C107

C109

C109

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

R403

R403

1 2

D01RL0816F-L- GP

D01RL0816F-L- GP

12

C843

C843

SC1U10V2KX-1GP

SC1U10V2KX-1GP

R23 43R2J-GPR23 43R2J-GP

1 2

12

C3

C111

C111

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

75R2J-1-GP

75R2J-1-GP

12

C4

SC10U6D3V3MX-GPC4SC10U6D3V3MX-GP

C113

C113

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

R21

R21

12

C5

SC10U6D3V3MX-GPC5SC10U6D3V3MX-GP

C115

C115

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC1R05B_VT T_CPU

12

R22

R22

130R2J-GP

130R2J-GP

12

C6

SC10U6D3V3MX-GPC6SC10U6D3V3MX-GP

C117

C117

C155

C155

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

-SVID_ALERT 80

SVID_CLK 80

SVID_DATA 80

D

VCC1R05B_VT T_CPU

12

12

C7

SC22U6D3V3MX-L-GPC7SC22U6D3V3MX-L-GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C8

C9

SC10U6D3V3MX-GPC9SC10U6D3V3MX-GP

SC22U6D3V3MX-L-GPC8SC22U6D3V3MX-L-GP

C156

C156

C158

C158

C157

C157

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC1R05B_VT T VCCCPUC ORE

12

R24

R24

10R2F-L-GP

10R2F-L-GP

12

12

C105

C105

C10

C10

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C179

C179

C160

C160

C159

C159

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

E

VCC1R05B_VT T VCC1R05B_VT T_CPU

R20 D01RL0816F -L-GPR20 D01RL0816F -L-GP

1 2

R87 D01RL0816F -L-GPR87 D01RL0816F -L-GP

1 2

C189

C189

C188

C188

C184

C184

C183

C183

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C190

C190

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

R25

R25

100R2F-L1-GP- U

100R2F-L1-GP- U

C192

C192

C191

C191

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

Z0 = 27.4 OHM

PU/PD < 1inch

C193

C193

C194

C194

C195

C195

C197

C197

C198

C198

C199

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C199

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES

SENSE LINES

IVY-BRIDGE-GP-N F

IVY-BRIDGE-GP-N F

1 1

A

B

VSS_SENSE_CPU

G43

AN16

AN17

VCC_SENSE_C PU

F43

R27 0R2J-2-G PR27 0R2J-2-G P

1 2

R26 0R2J-2-G PR26 0R2J-2-G P

1 2

C

12

R28

R28

10R2F-L-GP

10R2F-L-GP

VCC_SENSE_V TT 84

VSS_SENSE_VTT 84

D

12

R29

R29

100R2F-L1-GP- U

100R2F-L1-GP- U

VCCSENSE 80

VSSSENSE 80

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O .C.

Taipei Hsie n 221, Taiwan, R.O .C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O .C.

CPU(5/8):Processor Power

CPU(5/8):Processor Power

CPU(5/8):Processor Power

Genesis-1

Genesis-1

Genesis-1

7 100Monday, January 30, 2012

7 100Monday, January 30, 2012

E

7 100Monday, January 30, 2012

SC

SC

SC

A

VCCGFXCORE_I

C108

C108

C110

C110

12

4 4

VCCGFXCORE_I

As for placement, please follow

"Chief River Platform Power Delivery Design Guide"

(Intel DocNo.458544)

3 3

2 2

1 1

SC22U4V3MX-GP

SC22U4V3MX-GP

SC22U4V3MX-GP

SC22U4V3MX-GP

C201

C201

C200

C200

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

EMI request.

C933

C933

12

12

SC22U4V3MX-GP

SC22U4V3MX-GP

C217

C217

C218

C218

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCCGFX_SENSE_I80

VSSGFX_SENSE_I80

VCC1R8B

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCCSA

A

C20

C20

C934

C934

12

12

SC22U4V3MX-GP

SC22U4V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C295

C295

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCCGFXCORE_I

R34

R34

D01RL0816F-L-GP

D01RL0816F-L-GP

12

C34

C34

C33

C33

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C627

C627

C21

C21

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C368

C368

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

R30

R30

100R2J-2-GP

100R2J-2-GP

12

R33

R33

100R2J-2-GP

100R2J-2-GP

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

R37

R37

1 2

D01RL0816F-L-GP

D01RL0816F-L-GP

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C369

C369

12

12

SC22U4V3MX-GP

SC22U4V3MX-GP

DY

DY

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C69

C69

C22

C22

12

SC22U4V3MX-GP

SC22U4V3MX-GP

C370

C370

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

R31

R31

1 2

1 2

R32 0R2J-2-GPR32 0R2J-2-GP

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

C834

C834

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C23

C23

12

12

C835

C835

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

C70

C70

C371

C371

12

0R2J-2-GP

0R2J-2-GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C844

C844

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC1R8B_CPU

VCCSA_CPU

C836

C836

12

C837

C837

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

B

VCCGFXCORE_I

C845

C845

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VAXG_SENSE_CPU

VSSAXG_SENSE_CPU

C838

C838

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

B

U1G

U1G

AA46

AB47

AB50

AB51

AB52

AB53

AB55

AB56

AB58

AB59

AC61

AD47

AD48

AD50

AD51

AD52

AD53

AD55

AD56

AD58

AD59

AE46

N45

P47

P48

P50

P51

P52

P53

P55

P56

P61

T48

T58

T59

T61

U46

V47

V48

V50

V51

V52

V53

V55

V56

V58

V59

W50

W51

W52

W53

W55

W56

W61

Y48

Y61

F45

G45

BB3

BC1

BC4

L17

L21

N16

N20

N22

P17

P20

R16

R18

R21

U15

V16

V17

V18

V21

W20

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

VAXG55

VAXG56

VAXG_SENSE

VSSAXG_SENSE

VCCPLL1

VCCPLL2

VCCPLL3

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA9

VCCSA10

VCCSA11

VCCSA12

VCCSA13

VCCSA14

VCCSA15

VCCSA16

POWER

POWER

VREF

VREF

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

VCCSA VID

VCCSA VID

7 OF 9

7 OF 9

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

VDDQ24

VDDQ25

VDDQ26

VCCDQ1

VCCDQ2

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

SENSE LINES

VCCSA_VID0

VCCSA_VID1

lines

lines

C

AY43

BE7

BG7

12

R668

R668

1KR2F-3-GP

1KR2F-3-GP

DY

DY

VCC1R35_VDDQ

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

PN12 PWRNCPN12 PWRNC

BC43

PN13 PWRNCPN13 PWRNC

BA43

U10

D48

D49

C

VCCSA_SENSE 90

VCCSA_VID0_CPU

VCCSA_VID1_CPU

VCC1R35_VDDQ

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC1R35_VDDQ

12

C846

C846

SC1U10V2KX-1GP

SC1U10V2KX-1GP

R1318 0R2J-L-GPR1318 0R2J-L-GP

1 2

R36 0R2J-L-GPR36 0R2J-L-GP

1 2

12

R669

R669

1KR2F-3-GP

1KR2F-3-GP

Place under CPU

12

12

As for placement, please follow

"Huron River Platform Power Delivery Design Guide Rev1.0"

(Intel DocNo.439028)

C26

C26

C27

C27

SC1U10V2KX-1GP

SC1U10V2KX-1GP

D

DDR3_VREF_DQ_SA_M3 12

DY

DY

12

C28

C28

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

Sandy Bridge

Ivy Bridge

VCC1R05B_VTT_CPU

12

DY

DY

R1317

R1317

10KR2J-3-GP

10KR2J-3-GP

12

R1319

R1319

10KR2J-3-GP

10KR2J-3-GP

D

12

C29

C29

12

12

12

C30

C30

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

R35

R35

10KR2J-3-GP

10KR2J-3-GP

R38

R38

10KR2J-3-GP

10KR2J-3-GP

E

VCC1R35_VDDQ

12

R671

R671

1KR2F-3-GP

12

DY

DY

C24

C24

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

NEED SC2D2U4V2MX-1GP

78.22510.5FL

12

C31

C31

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

C32

C32

C36

C36

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

DY

DY

C25

C25

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

12

C35

C35

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1KR2F-3-GP

12

R670

R670

1KR2F-3-GP

1KR2F-3-GP

Place near CPU

12

C37

C37

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCCSA_SEL0 VCCSA_SEL1 VCCSA

0

LOW

0

1

High

1

VCCSA_SEL0 90

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCCSA_SEL1 90

CPU(6/8):Graphics Power

CPU(6/8):Graphics Power

CPU(6/8):Graphics Power

0

1

0

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

0.90V

0.80V

0.725V

0.675V

8 100Monday, January 30, 2012

8 100Monday, January 30, 2012

8 100Monday, January 30, 2012

E

SC

SC

SC

A

U1H

U1H

B

8 OF 9

8 OF 9

C

U1I

U1I

9 OF 9

9 OF 9

D

E

BG17

VSS181

A13

VSS1

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

A17

VSS2

A21

VSS3

A25

VSS4

A28

VSS5

A33

VSS6

A37

VSS7

A40

VSS8

A45

VSS9

A49

VSS10

A53

VSS11

A9

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

AJ7

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS

VSS

4 4

3 3

2 2

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

BG21

VSS182

BG24

VSS183

BG28

VSS184

BG37

VSS185

BG41

VSS186

BG45

VSS187

BG49

VSS188

BG53

VSS189

BG9

VSS190

C29

VSS191

C35

VSS192

C40

VSS193

D10

VSS194

D14

VSS195

D18

VSS196

D22

VSS197

D26

VSS198

D29

VSS199

D35

VSS200

D4

VSS201

D40

VSS202

D43

VSS203

D46

VSS204

D50

VSS205

D54

VSS206

D58

VSS207

D6

VSS208

E25

VSS209

E29

VSS210

E3

VSS211

E35

VSS212

E40

VSS213

F13

VSS214

F15

VSS215

F19

VSS216

F29

VSS217

F35

VSS218

F40

VSS219

F55

VSS220

G51

VSS221

G6

VSS222

G61

VSS223

H10

VSS224

H14

VSS225

H17

VSS226

H21

VSS227

H4

VSS228

H53

VSS229

H58

VSS230

J1

VSS231

J49

VSS232

J55

VSS233

K11

VSS234

K21

VSS235

K51

VSS236

K8

VSS237

L16

VSS238

L20

VSS239

L22

VSS240

L26

VSS241

L30

VSS242

L34

VSS243

L38

VSS244

L43

VSS245

L48

VSS246

L61

VSS247

M11

VSS248

M15

VSS249

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

VSS

VSS

:

:

NCTF TEST PIN

NCTF TEST PIN

NCTF

NCTF

VSS_NCTF_1#A5

VSS_NCTF_2#A57

VSS_NCTF_3#BC61

VSS_NCTF_8#BG5

VSS_NCTF_9#BG57

VSS_NCTF_10#C3

VSS_NCTF_13#E1

VSS_NCTF_14#E61

A5,A57,BC61,BG5

BG57,C3,E1,E61

A5,A57,BC61,BG5

BG57,C3,E1,E61

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_11

VSS_NCTF_12

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BG5

BG57

C3

E1

E61

BD3

BD59

BE4

BE58

C58

D59

1 1

A

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

B

C

D

Date: Sheet of

CPU(7/8):GND

CPU(7/8):GND

CPU(7/8):GND

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

9 100Monday, January 30, 2012

9 100Monday, January 30, 2012

9 100Monday, January 30, 2012

E

SC

SC

SC

A

4 4

CPU_CFG011

ADD VIA

#C51,#A51

3 3

2 2

B

TP80

TP80

TPAD14-GP

TPAD14-GP

TP79

TP79

TPAD14-GP

TPAD14-GP

C

5 OF 9

U1E

U1E

B50

1

1

CFG0

C51

CFG1

B54

CFG2

D53

CFG3

A51

CFG4

C53

CFG5

C55

CFG6

H49

CFG7

A55

CFG8

H51

CFG9

K49

CFG10

K53

CFG11

F53

CFG12

G53

CFG13

L51

CFG14

F51

CFG15

D52

CFG16

L53

CFG17

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

RESERVED

RESERVED

5 OF 9

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

DC_TEST_A4

DC_TEST_C4

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_A61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BG61

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BG1

DC_TEST_BD1

1

1

1

1

1

1

1

1

D

TP43TPAD40-GP TP43TPAD40-GP

TP44TPAD40-GP TP44TPAD40-GP

TP48TPAD40-GP TP48TPAD40-GP

TP49TPAD40-GP TP49TPAD40-GP

TP50TPAD40-GP TP50TPAD40-GP

TP51TPAD40-GP TP51TPAD40-GP

TP52TPAD40-GP TP52TPAD40-GP

TP53TPAD40-GP TP53TPAD40-GP

E

1 1

A

B

C

D

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU(8/8):CFG/Reserved

CPU(8/8):CFG/Reserved

CPU(8/8):CFG/Reserved

A3

A3

A3

Taipei Hsien 221, Taiwan, R.O.C.

Genesis-1

Genesis-1

Genesis-1

10 100Monday, January 30, 2012

10 100Monday, January 30, 2012

10 100Monday, January 30, 2012

E

SC

SC

SC

5

VCC1R05B_VTTVCC3B VCC3MVCC3M

12

12

R44

R44

R45

R45

51R2J-2-GP

51R2J-2-GP

1KR2J-1-GP

1KR2J-1-GP

D D

XDP_TCK4

XDP_TMS4

XDP_TDI4

-XDP_TRST4

XDP_TDO4

-XDP_DBR4,26

-PLTRST_FAR4,28,58,60

-XDP_CLK_100M25

XDP_CLK_100M25

CPU_CFG010

CPUPWRGD4,29

C C

R49 1KR2J-1-GPR49 1KR2J-1-GP

R50 0R2J-2-GPR50 0R2J-2-GP

BPWRG26,32,56,61,62,70,72

R51 1KR2J-1-GPR51 1KR2J-1-GP

R53 1KR2J-1-GPR53 1KR2J-1-GP

-XDP_PRDY4

-XDP_PREQ4

1 2

1 2

1 2

1 2

R59

R59

51R2J-2-GP

51R2J-2-GP

-PLTRST_FAR_XDP

BPWRG_XDP

CPU_CFG0_XDP

CPUPWRGD_XDP

12

MLX-CON26-8-GP

MLX-CON26-8-GP

MLX-52435-2671 MLX-52435-2671

4

DY

DY

CN24

CN24

28

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

27

PCH_TCK24

PCH_TMS24

PCH_TDI24

PCH_TDO24

-XDP_DBR4,26

R52 1KR2J-1-GPR52 1KR2J-1-GP

1 2

R54 1KR2J-1-GPR54 1KR2J-1-GP

MPWRG26,32,56,72

1 2

3

12

220R2J-L2-GP

220R2J-L2-GP

BPWRG_XDP_PCH

12

100R2J-2-GP

100R2J-2-GP

R46

R46

R55

R55

2

12

12

R47

R47

R48

R48

220R2J-L2-GP

220R2J-L2-GP

220R2J-L2-GP

220R2J-L2-GP

-PLTRST_XDP_PCH

12

R57

R57

12

R58

R58

51R2J-2-GP

51R2J-2-GP

12

R56

R56

100R2J-2-GP

100R2J-2-GP

100R2J-2-GP

100R2J-2-GP

DY

DY

CN25

CN25

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

MLX-CON26-8-GP

MLX-CON26-8-GP

28

27

1

DEBUG Interface for Processor.

XDP1 XDP2

TDO

TRST#

DBRST#

B B

RESET#

CFG0

PWRGD

BPWRG

NOTE:"ASM" FOR PDV/SDV ONLY NOTE:"ASM" FOR PDV/SDV ONLY

ENABLE DISABLE

R45

R59

R44

R49

R51

R53

R50

CN24

ASM DY

ASM ASM

ASM ASM

ASM DY

ASM DY

ASM DY

ASM DY

ASM DY

PDV Logic

DEBUG Interface for PCH.

ENABLE DISABLE

TDO

TMS

TDI

TCK

R46

R55

R48

R57

R47

R56

R58

R52

R54

CN25

220 DY

100

220

100 DY

220 DY

100 DY

51 51

ASM DYMPWRG

ASM

ASM

DY

DY

DY

DY

PDV Logic

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

XDP Connector

XDP Connector

XDP Connector

Genesis-1

Genesis-1

Genesis-1

1

11 100Monday, January 30, 2012

11 100Monday, January 30, 2012

11 100Monday, January 30, 2012

SC

SC

SC

A

B

C

D

E

VCC1R35A_DIMM

4 4

DDR3_VREF_DQ_SA DDR3_VREF_DQ_SA

DDR3_VREF_CA

12

C120

C120

12

C119

C119

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

M_A_A[15..0]5

12

R6944

R6944

12

R6909

R6909

240R2J-3-GP

240R2J-3-GP

240R2J-3-GP

240R2J-3-GP

M_A_BS05

M_A_BS15

M_A_BS25

M_A_DDRCLK0_800M5

-M_A_DDRCLK0_800M5

M_A_CKE05

-M_A_WE5

-M_A_CAS5 -M_A_CAS5

12

DDR3_VREF_CA

12

R6946

R6946

240R2J-3-GP

240R2J-3-GP

-M_A_DDRCLK0_800M5

12

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

M_A_DDRCLK0_800M5

-M_A_RAS5

DDR3_VREF_DQ_SA

C124

C124

M_A_A[15..0]5

M_A_BS05

M_A_BS15

M_A_BS25

M_A_CKE05

-M_A_WE5

-M_A_CAS5

-M_A_RAS5

VCC1R35A_DIMM

12

C123

C123

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

3 3

R6911

R6911

240R2J-3-GP

2 2

240R2J-3-GP

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

U78

U78

K8

VDD

K2

VDD

N1

VDD

R9

VDD

B2

VDD

D9

VDD

G7

VDD

R1

VDD

N9

VDD

A8

VDDQ

A1

VDDQ

C1

VDDQ

C9

VDDQ

D2

VDDQ

E9

VDDQ

F1

VDDQ

H9

VDDQ

H2

VDDQ

H1

VREFDQ

M8

VREFCA

L8

ZQ

L9

NC#L9

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M7

NC#M7

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK#

K9

CKE

D3

UDM

E7

LDM

L3

WE#

K3

CAS#

J3

RAS#

EDJ8216E5MB-DJ-F-GP

EDJ8216E5MB-DJ-F-GP

U80

U80

K8

VDD

K2

VDD

N1

VDD

R9

VDD

B2

VDD

D9

VDD

G7

VDD

R1

VDD

N9

VDD

A8

VDDQ

A1

VDDQ

C1

VDDQ

C9

VDDQ

D2

VDDQ

E9

VDDQ

F1

VDDQ

H9

VDDQ

H2

VDDQ

H1

VREFDQ

M8

VREFCA

L8

ZQ

L9

NC#L9

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M7

NC#M7

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK#

K9

CKE

D3

UDM

E7

LDM

L3

WE#

K3

CAS#

J3

RAS#

EDJ8216E5MB-DJ-F-GP

EDJ8216E5MB-DJ-F-GP

UDQS#

LDQS#

RESET#

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS

LDQS

NC#L1

NC#J9

NC#J1

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

RESET#

M_A_DQ5

E3

DQ0

M_A_DQ7

F7

DQ1

M_A_DQ0

F2

DQ2

M_A_DQ2

F8

DQ3

M_A_DQ4

H3

DQ4

M_A_DQ6

H8

DQ5

M_A_DQ1

G2

DQ6

M_A_DQ3

H7

DQ7

M_A_DQ15

D7

DQ8

M_A_DQ10

C3

DQ9

M_A_DQ14

C8

M_A_DQ12

C2

M_A_DQ11

A7

M_A_DQ9

A2

M_A_DQ8

B8

M_A_DQ13

A3

C7

B7

F3

M_A_DQS0 5

G3

-M_A_DQS0 5

K1

M_A_ODT0 5

ODT

L2

CS#

T2

L1

J9

J1

J8

VSS

M1

VSS

M9

VSS

J2

VSS

P9

VSS

G8

VSS

B3

VSS

T1

VSS

A9

VSS

T9

VSS

E1

VSS

P1

VSS

G1

F9

E8

E2

D8

D1

B9

B1

G9

M_A_DQ36

E3

DQ0

M_A_DQ34

F7

DQ1

M_A_DQ32

F2

DQ2

M_A_DQ35

F8

DQ3

M_A_DQ33

H3

DQ4

M_A_DQ39

H8

DQ5

M_A_DQ37

G2

DQ6

M_A_DQ38

H7

DQ7

M_A_DQ47

D7

DQ8

M_A_DQ42

C3

DQ9

M_A_DQ41

C8

DQ10

M_A_DQ40

C2

DQ11

M_A_DQ46

A7

DQ12

M_A_DQ45

A2

DQ13

M_A_DQ43

B8

DQ14

M_A_DQ44

A3

DQ15

C7

UDQS

B7

UDQS#

F3

M_A_DQS4 5

LDQS

G3

LDQS#

NC#L1

NC#J9

NC#J1

-M_A_DQS4 5

K1

M_A_ODT0 5

ODT

L2

CS#

T2

L1

J9

J1

J8

VSS

M1

VSS

M9

VSS

J2

VSS

P9

VSS

G8

VSS

B3

VSS

T1

VSS

A9

VSS

T9

VSS

E1

VSS

P1

VSS

G1

VSSQ

F9

VSSQ

E8

VSSQ

E2

VSSQ

D8

VSSQ

D1

VSSQ

B9

VSSQ

B1

VSSQ

G9

VSSQ

M_A_DQ[7..0] 5 M_A_DQ[23..16] 5

M_A_DQ[15..8] 5

DDR3_VREF_CA

M_A_DQS1 5

-M_A_DQS1 5

-M_A_CS0 5

-DRAMRST 4,13

M_A_DQS5 5

-M_A_DQS5 5

-M_A_CS1 5

M_A_CKE1 5

M_A_ODT1 5

M_A_DQ[39..32] 5

M_A_DQ[47..40] 5

-M_A_CS0 5

-DRAMRST 4,13

-M_A_CS1 5

M_A_CKE1 5

M_A_ODT1 5

240R2J-3-GP

240R2J-3-GP

R6912

R6912

240R2J-3-GP

240R2J-3-GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

R6945

R6945

R6910

R6910

240R2J-3-GP

240R2J-3-GP

M_A_DDRCLK0_800M5

-M_A_DDRCLK0_800M5

DDR3_VREF_CA

12

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

M_A_A[15..0]5

12

12

R6947

R6947

240R2J-3-GP

240R2J-3-GP

M_A_BS05

M_A_BS15

M_A_BS25

M_A_DDRCLK0_800M5

-M_A_DDRCLK0_800M5

12

C122

C122

M_A_A[15..0]5

M_A_BS05

M_A_BS15

M_A_BS25

M_A_CKE05

DDR3_VREF_DQ_SA

C126

C126

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

M_A_CKE05

-M_A_WE5

-M_A_CAS5

-M_A_RAS5

VCC1R35A_DIMM

12

C121

C121

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

-M_A_WE5

-M_A_RAS5

VCC1R35A_DIMM

12

C125

C125

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

U79

U79

K8

K2

N1

R9

B2

D9

G7

R1

N9

A8

A1

C1

C9

D2

E9

F1

H9

H2

H1

M8

L8

L9

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

D3

E7

L3

K3

J3

EDJ8216E5MB-DJ-F-GP

EDJ8216E5MB-DJ-F-GP

U81

U81

K8

VDD

K2

VDD

N1

VDD

R9

VDD

B2

VDD

D9

VDD

G7

VDD

R1

VDD

N9

VDD

A8

VDDQ

A1

VDDQ

C1

VDDQ

C9

VDDQ

D2

VDDQ

E9

VDDQ

F1

VDDQ

H9

VDDQ

H2

VDDQ

H1

VREFDQ

M8

VREFCA

L8

ZQ

L9

NC#L9

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M7

NC#M7

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK#

K9

CKE

D3

UDM

E7

LDM

L3

WE#

K3

CAS#

J3

RAS#

EDJ8216E5MB-DJ-F-GP

EDJ8216E5MB-DJ-F-GP

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREFDQ

VREFCA

ZQ

NC#L9

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

NC#M7

BA0

BA1

BA2

CK

CK#

CKE

UDM

LDM

WE#

CAS#

RAS#

RESET#

M_A_DQ16

E3

DQ0

M_A_DQ19

F7

DQ1

M_A_DQ17

F2

DQ2

M_A_DQ18

F8

DQ3

M_A_DQ20

H3

DQ4

M_A_DQ23

H8

DQ5

M_A_DQ21

G2

DQ6

M_A_DQ22

H7

DQ7

M_A_DQ27

D7

DQ8

M_A_DQ25

C3

DQ9

M_A_DQ31

C8

DQ10

M_A_DQ29

C2

DQ11

M_A_DQ28

A7

DQ12

M_A_DQ30

A2

DQ13

M_A_DQ26

B8

DQ14

M_A_DQ24

A3

DQ15

C7

UDQS

B7

UDQS#

F3

LDQS

G3

LDQS#

K1

ODT

L2

CS#

T2

RESET#

L1

NC#L1

J9

NC#J9

J1

NC#J1

J8

VSS

M1

VSS

M9

VSS

J2

VSS

P9

VSS

G8

VSS

B3

VSS

T1

VSS

A9

VSS

T9

VSS

E1

VSS

P1

VSS

G1

VSSQ

F9

VSSQ

E8

VSSQ

E2

VSSQ

D8

VSSQ

D1

VSSQ

B9

VSSQ

B1

VSSQ

G9

VSSQ

M_A_DQ50

E3

DQ0

M_A_DQ55

F7

DQ1

M_A_DQ52

F2

DQ2

M_A_DQ54

F8

DQ3

M_A_DQ48

H3

DQ4

M_A_DQ51

H8

DQ5

M_A_DQ53

G2

DQ6

M_A_DQ49

H7

DQ7

M_A_DQ59

D7

DQ8

M_A_DQ61

C3

DQ9

M_A_DQ62

C8

DQ10

M_A_DQ57

C2

DQ11

M_A_DQ63

A7

DQ12

M_A_DQ56

A2

DQ13

M_A_DQ58

B8

DQ14

M_A_DQ60

A3

DQ15

C7

UDQS

B7

UDQS#

F3

LDQS

LDQS#

NC#L1

NC#J9

NC#J1

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

M_A_DQS6 5

G3

-M_A_DQS6 5

K1

M_A_ODT0 5

ODT

L2

CS#

T2

L1

J9

J1

J8

VSS

M1

VSS

M9

VSS

J2

VSS

P9

VSS

G8

VSS

B3

VSS

T1

VSS

A9

VSS

T9

VSS

E1

VSS

P1

VSS

G1

F9

E8

E2

D8

D1

B9

B1

G9

M_A_DQS2 5

-M_A_DQS2 5

M_A_ODT0 5

M_A_DQS7 5

-M_A_DQS7 5

M_A_DQS3 5

-M_A_DQS3 5

-M_A_CS0 5

-DRAMRST 4,13

-M_A_CS0 5

-DRAMRST 4,13

M_A_DQ[31..24] 5

-M_A_CS1 5

M_A_CKE1 5

M_A_ODT1 5

M_A_DQ[55..48] 5

M_A_DQ[63..56] 5

-M_A_CS1 5

M_A_CKE1 5

M_A_ODT1 5

VCC0R675B_DIMM

R6917 36R2J-GPR6917 36R2J-GP

1 2

R6918 36R2J-GPR6918 36R2J-GP

1 2

R6919 36R2J-GPR6919 36R2J-GP

1 2

R6920 36R2J-GPR6920 36R2J-GP

1 2

R6921 36R2J-GPR6921 36R2J-GP

1 2

R6922 36R2J-GPR6922 36R2J-GP

1 2

R6923 36R2J-GPR6923 36R2J-GP

1 2

R6924 36R2J-GPR6924 36R2J-GP

1 2

R6925 36R2J-GPR6925 36R2J-GP

1 2

R6926 36R2J-GPR6926 36R2J-GP

1 2

R6927 36R2J-GPR6927 36R2J-GP

1 2

R6928 36R2J-GPR6928 36R2J-GP

1 2

R6929 36R2J-GPR6929 36R2J-GP

1 2

R6930 36R2J-GPR6930 36R2J-GP

1 2

R6931 36R2J-GPR6931 36R2J-GP

1 2

R6932 36R2J-GPR6932 36R2J-GP

1 2

R6933 36R2J-GPR6933 36R2J-GP

1 2

R6934 36R2J-GPR6934 36R2J-GP

1 2

R6935 36R2J-GPR6935 36R2J-GP

1 2

R6936 36R2J-GPR6936 36R2J-GP

1 2

R6937 36R2J-GPR6937 36R2J-GP

1 2

R6938 36R2J-GPR6938 36R2J-GP

1 2

R6939 36R2J-GPR6939 36R2J-GP

1 2

R6940 36R2J-GPR6940 36R2J-GP

1 2

R6941 36R2J-GPR6941 36R2J-GP

1 2

R6942 36R2J-GPR6942 36R2J-GP

1 2

R6943 36R2J-GPR6943 36R2J-GP

1 2