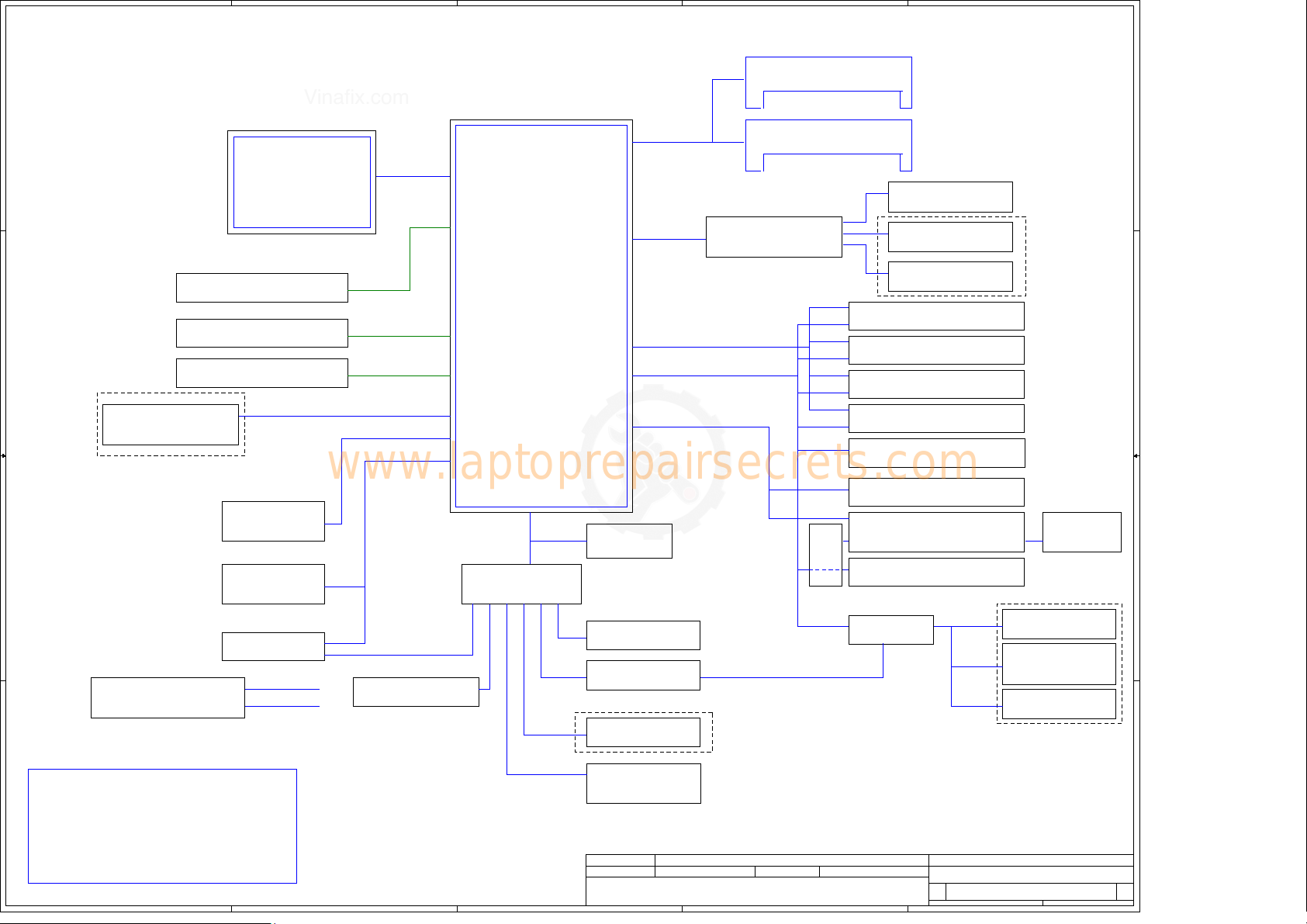

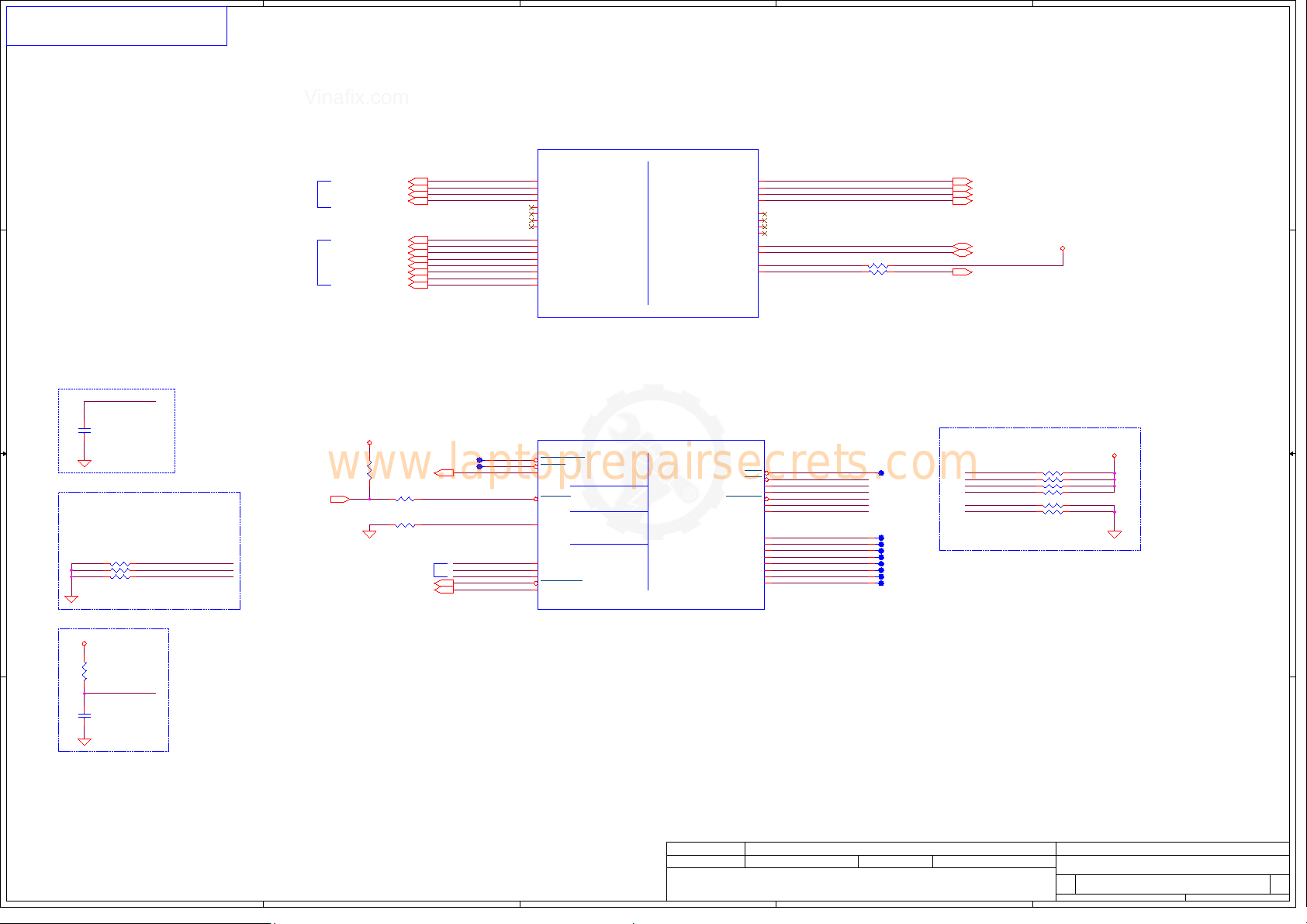

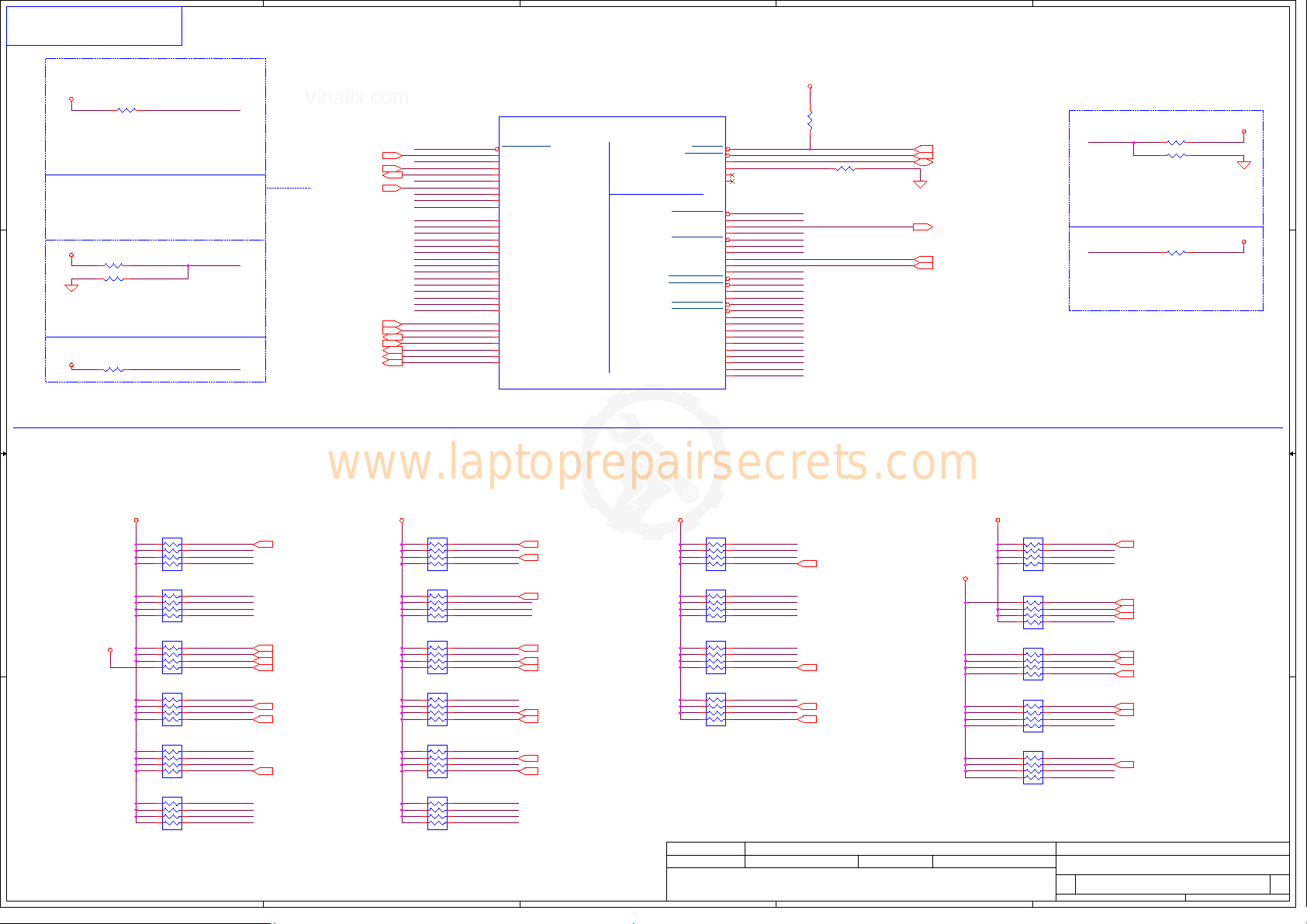

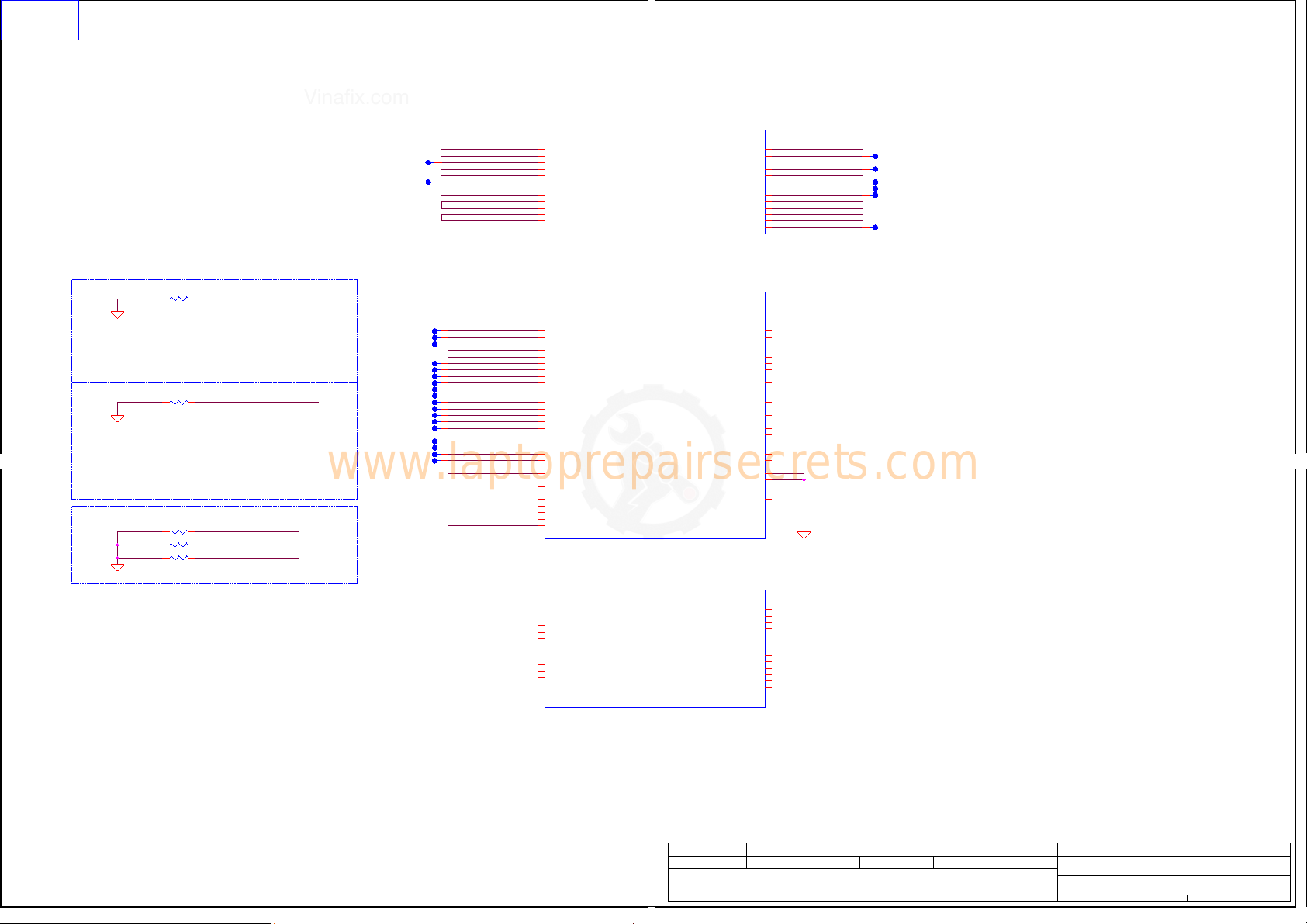

Lenovo ThinkPad Yoga S5 Schematic

Vinafix.com

1

www.laptoprepairsecrets.com

2

3

4

5

CompalConfidential

ModelName:ZIUS1(Lenovo)

A A

ZIUS2(NEC)

FileName:LA‐B591P

B B

CompalConfidential

AsahiM/BSchematicsDocument

IntelCrescentBayBroadwellUProcessorwithDDR3L

+ NVIDAN15S‐GTGPU

C C

D D

Security Classification

Security Classification

1

2

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

for KPS4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

150Tuesday, March 25, 2014

150Tuesday, March 25, 2014

150Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

A

www.laptoprepairsecrets.com

CompalConfidential

B

C

D

E

A‐chDDR3L‐SO‐DIMMX1

1 1

NVN15S‐GT

23mm*23mm

(20W)

PCI‐EX4

DDR3*4

VRAM256*16

eDP

eDPConnector

MemoryBus

DDR31600MHz(1.35V)

HDAudio

AudioCodec

Realtek ALC283

B‐chDDR3L‐SO‐DIMMX1

2ChannelSpeaker

DigitalMIC*2

AudiocomboJack

(SubBoard)

Intel

2 2

DisplayPort(OneLink)

CardReader

Realtek RTS5227E-GR

HDMIConnector

HDMI

DP

PCI‐E

SPI

Broadwell

ULT(15W)

BGA

USB3.0

USB2.0

SATA

SMBus

(SubBoard)

SPIROM

3 3

SecurityROM

EC

ENE KBC9022

LPCBUS

TPM

USBPORT3.0(AOU)

USBPORT3.0

USBPORT3.0(OneLink)

Camera(3D/720P)

TouchScreen

SATA3.0HDDCONN

M.2SSD/WWAN

USB

M.2 (B-type) Card

Hub

USBPORT2.0

SIMCard

ClickPad

M.2WLAN/BT

M.2 (A-type) Card

Sub-Board List:

4 4

PCI‐E(WLAN)

USB(BT)

PS2

Int.KBD

LS-B591P PWR Board

Proximity‐sensor

Accelerometer

HallSensor*2

ThermalSensor

Fintek F75303M

CPU & RAM

(SubBoard)

SensorHub

ALS

eCompass

Accelerometer

Gyro

(SubBoard)

LS-B592P Card Reader Board

LS-B593P 3D Sensor Board

Security Classification

Security Classification

LS-B594P 2D Sensor Board

LS-B595P OneLink Board

A

B

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

D

for KSP4

LA-B591P_SDV

Date: Sheet

Date: Sheet

Date: Sheet

E

250Tuesday, March 25, 2014

250Tuesday, March 25, 2014

250Tuesday, March 25, 2014

of

of

of

0.1

0.1

0.1

Vinafix.com

1

www.laptoprepairsecrets.com

2

3

4

5

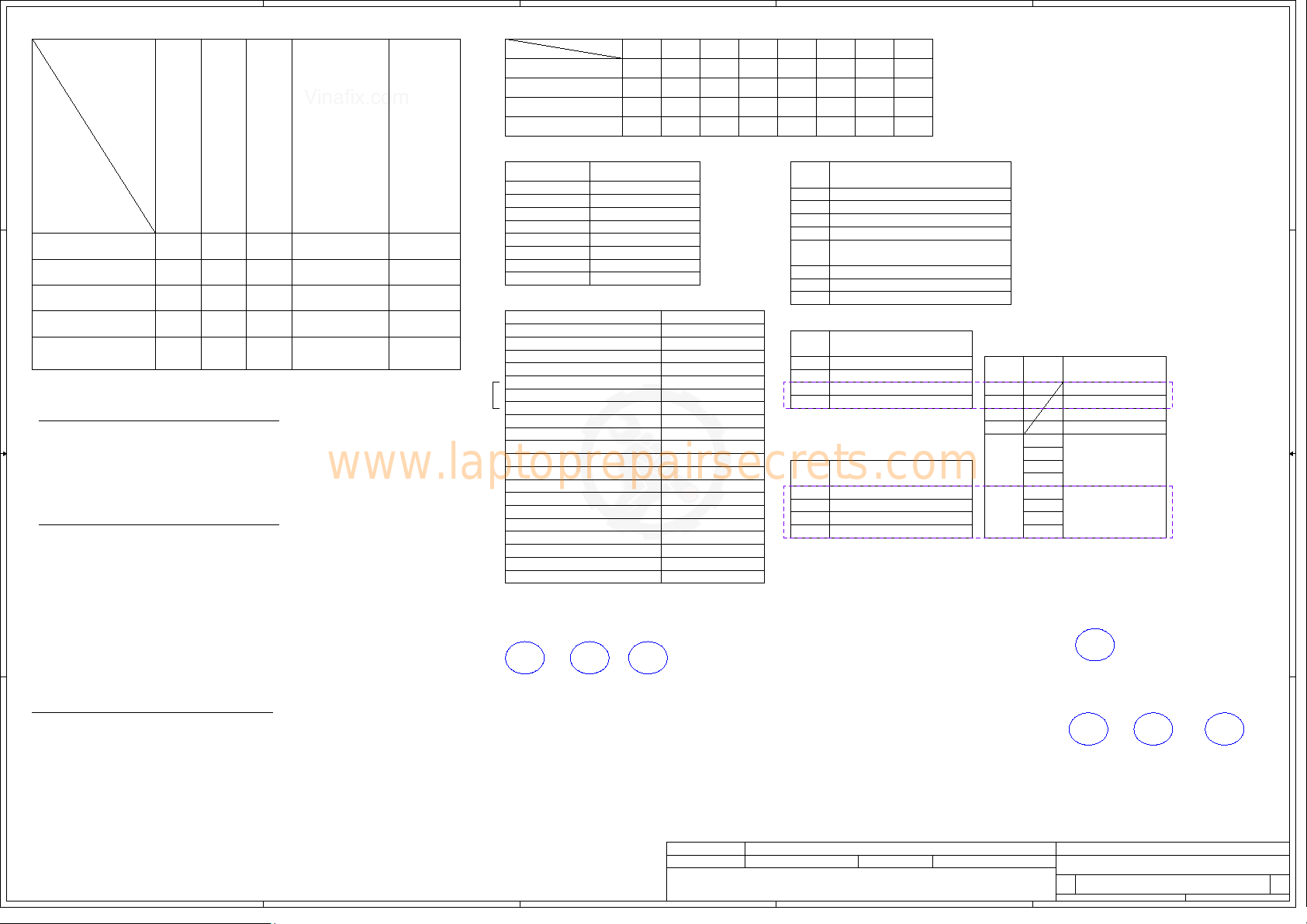

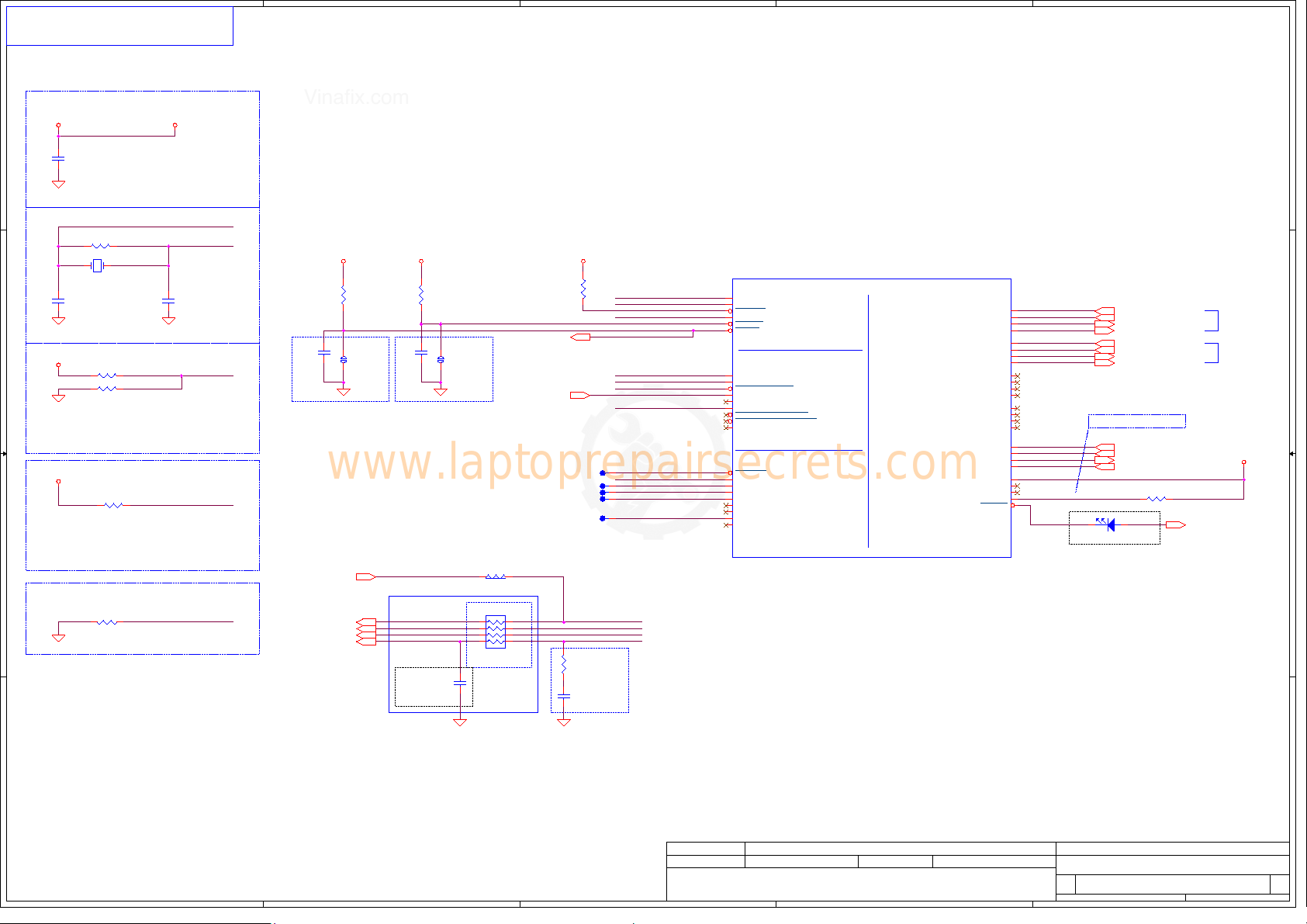

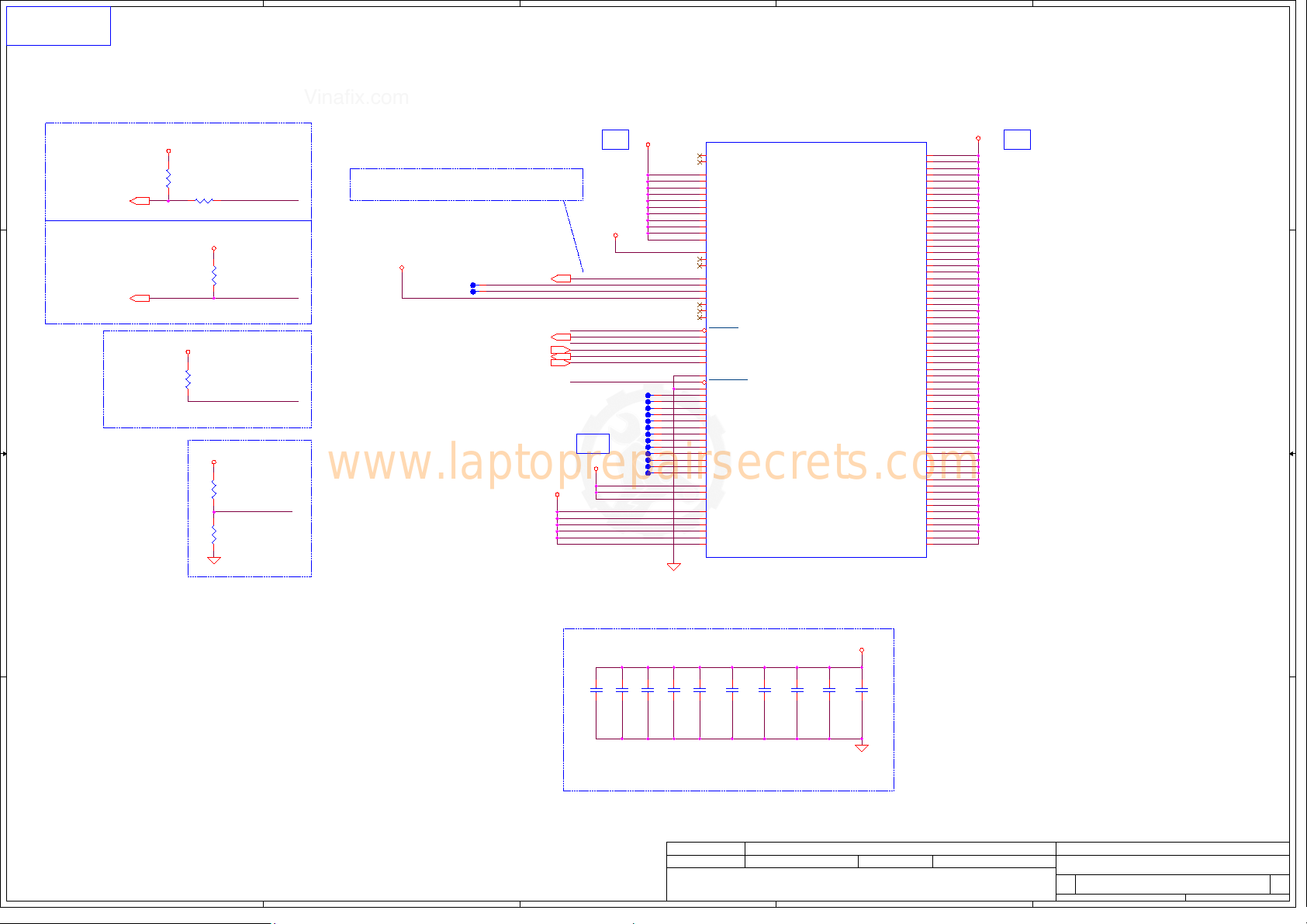

Voltage Rails

SIGNAL

STATE

+5VS

power

plane

A A

State

+5VALW

+B

+1.35V

+3VALW

+3VS

+1.5VS

+VCCP

+CPU_CORE

+VGA_CORE

+VCC_GFXCORE_AXG

+1.8VS

+0.675VS

+1.05VS

+3VM

+1.05VM

(SBA Only)

Full ON

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

BOARD ID Table

Board ID

0

1

2

3

S0

S3

S5 S4/AC

S5 S4/ Battery only

B B

S5 S4/AC & Battery

don't exist

O

O

O

O

O

O

O

XX

X

X

X

X

XX X

OO

X

X

O

M3 Supported

O

M3 Supported

O

M3 Supported

VRAM

EC SM Bus1 address

Device

Smart Battery

Charger

Touch HOME botton

Address

0001 011X b

0001 011X b

HEX

16H

12H

4

5

6

7

BOM Structure Table

BTO Item BOM Structure

Connector ME@

Unpop

Micron 2G VRAM

Hynix 2G VRAM

Samsung 2G VRAM

w/ 3G

w/o 3G

Trick Point TP@

SBA

no SBA

EC SM Bus2 address

Device

Thermal Sensor Fintek F75303M

C C

Thermal Sensor ON-semi ADM1032

P - Sensor

Intel BDW-U

Nvidia N15S-GT

Address

1001_101xb

0100_110xb

HEX

9AH

4CH

28H0010_1000b

EMI Un-Mount @EMI@

EMI Mount

CPU

U1

U1

BDW QG21

HSW QFSY

HSW QFSY

CPU1@

CPU1@

SA00007AM20

SA00007AM20

BDW QG21

CPU2@

CPU2@

SA00007OS00

SA00007OS00

PCH SM Bus address

Device Address

DDR DIMM1

DDR DIMM2

Security Rom

Synaptics Inter Touch Click Pad

M.2 mSATA

D D

M.2 WLAN

1001 000Xb

0010_110xb 2CH

HEX

A0H

A8H1010 100xb

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

ON ON ON

ON

OFF

OFFLOW LOW LOW

HIGH HIGH HIGH

LOW

HIGH

HIGH

LOWLOW

HIGH

USB 2.0 Port Table

PCB Revision

0.1

0.2

0.3

1.0

USB 3.0 Port Table

@

DIS@Nviida GPU

UMA@Intel UMA

X76M2G@

X76H2G@

X76S2G@

AOAC@AOAC Mount

3G@

NO3G@

SBA@

NOSBA@

GC6@GPU GC6

NOGC6@GPU NO GC6

TPM@TPM

EMI@

U1

U1

U1

U1

BDW QG22

BDW QG22

CPU3@

CPU3@

SA00007OT00

SA00007OT00

SATA Port Table

OFF

OFF

OFF

OFF

OFF

OFF

Port

0

1

2

3

4

5

6

7

Port

1

2

3

4

Port

3

2

1

03

3 External

USB Port

USB 3.0 AOU Port (MB-Left)

USB 3.0 Port (MB-Right)

USB 3.0 Port (OneLink)

Camera (2D)

M.2 BT (w/o 3G)

USB2 Hub (w/ 3G)

Touch Screen

Sensor Hub

USB2 Port (MB-Right)

USB 3.0 Port (MB-Left)

USB 3.0 Port (MB-Right)

USB 3.0 Port (OneLink)

Camera (3D)

M.2 WWAN/SSD

HDD

PCIE Port Table

Port

Lane

1

2

3

4

5

6

0

1

2

3

0

1

2

M.2 WLAN

Card Reader

GPU

PCB

ZZZ

ZZZ

LA-B591P

DA_PCB

DA_PCB

DA80010I000

DA80010I000

VRAM

ZZZ

ZZZ

Hynix_512MB

Hynix_512MB

X76H2G@

X76H2G@

X7656639L01

X7656639L01

ZZZ

ZZZ

MICRON_512MB

MICRON_512MB

X76M2G@

X76M2G@

X7656639L02

X7656639L02

ZZZ

ZZZ

Samsung_512MB

Samsung_512MB

X76S2G@

X76S2G@

X7656639L03

X7656639L03

1

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

350Tuesday, March 25, 2014

350Tuesday, March 25, 2014

350Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

1

www.laptoprepairsecrets.com

2

3

4

5

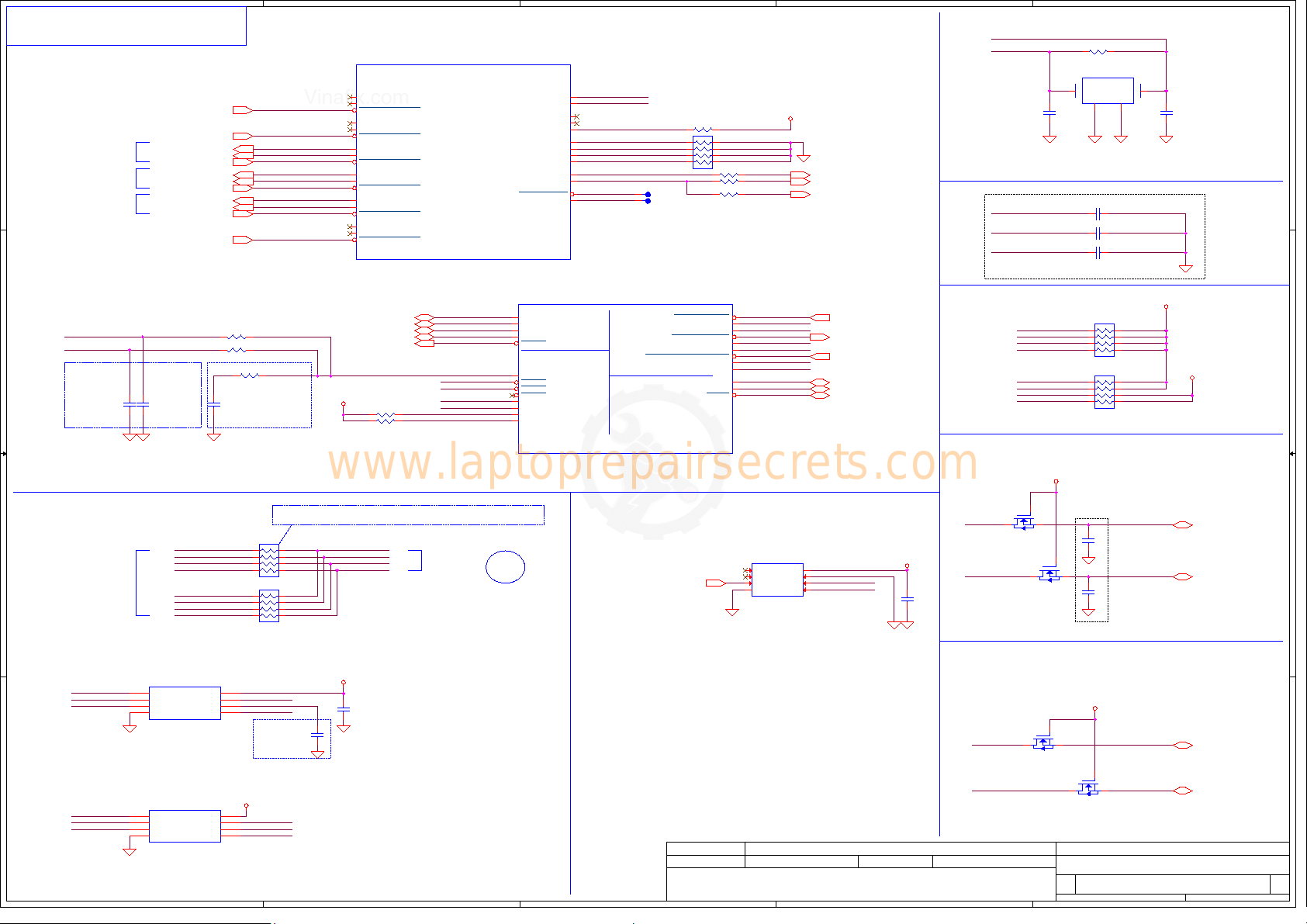

A A

B B

C C

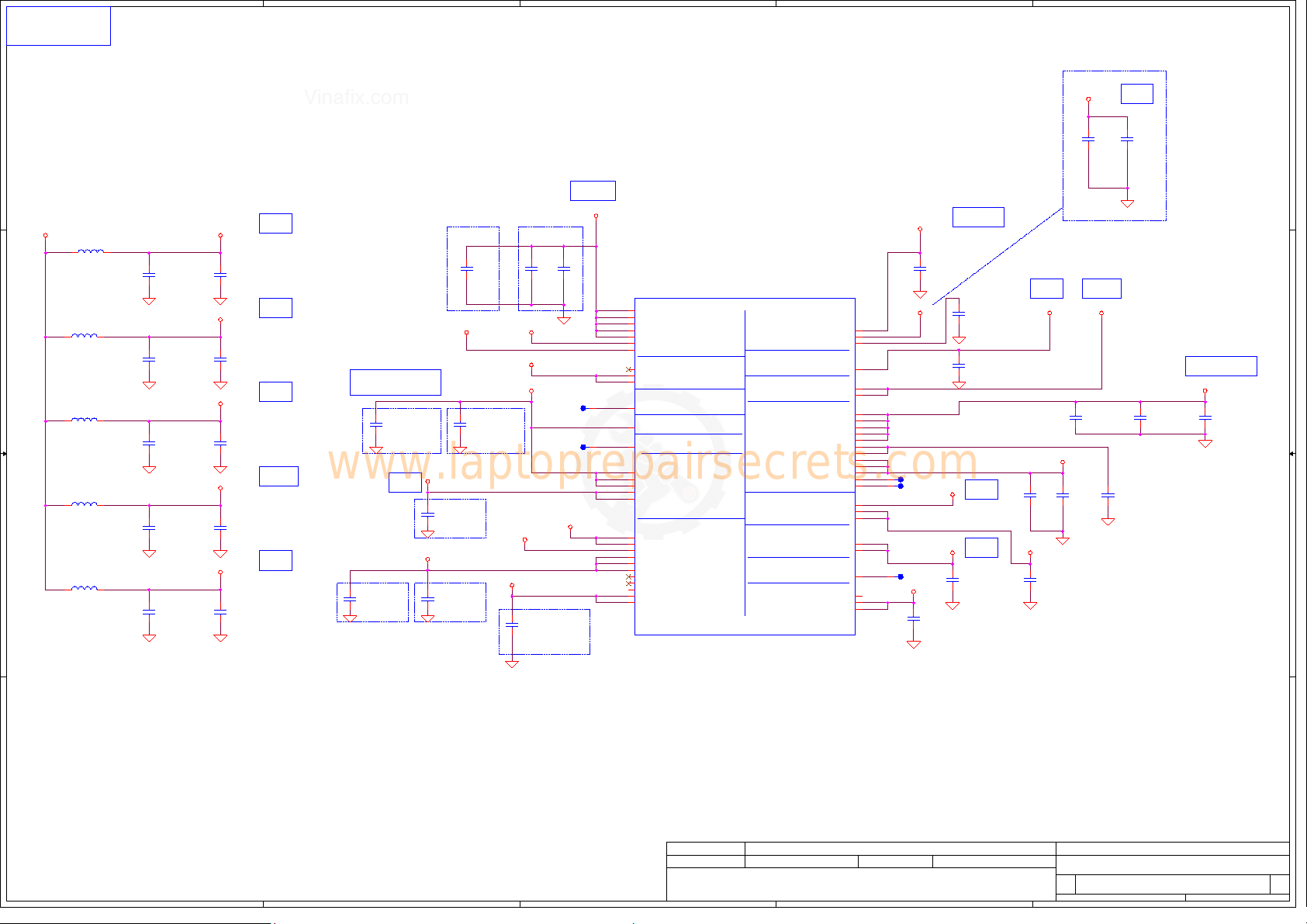

H_2P3

H_2P3

H5

H5

@

@

1

H6

H6

H_2P3

H_2P3

1

DIMM

@

@

H7

H7

H_2P3

H_2P3

@

@

1

H_4P0

H_4P0

H_4P0

H_4P0

H18

H18

1

H17

H17

1

H1

H1

H_2P3

H_2P3

H8

H8

H_2P3

H_2P3

@

@

@

@

FIDUCIAL_C40M80

FIDUCIAL_C40M80

FIDUCIAL_C40M80

FIDUCIAL_C40M80

H2

1

@

@

1

@

@

1

CPU

FD3

FD3

1

FD1

FD1

1

@H_2P3H2@H_2P3

H_4P0

H_4P0

@

@

@

@

H20

H20

1

H3

H3

H_2P3

H_2P3

@

@

1

H16

H16

H_4P0

H_4P0

1

GPU

@

@

FIDUCIAL_C40M80

FIDUCIAL_C40M80

FIDUCIAL_C40M80

FIDUCIAL_C40M80

H15

H15

H_4P0

H_4P0

@

@

@

@

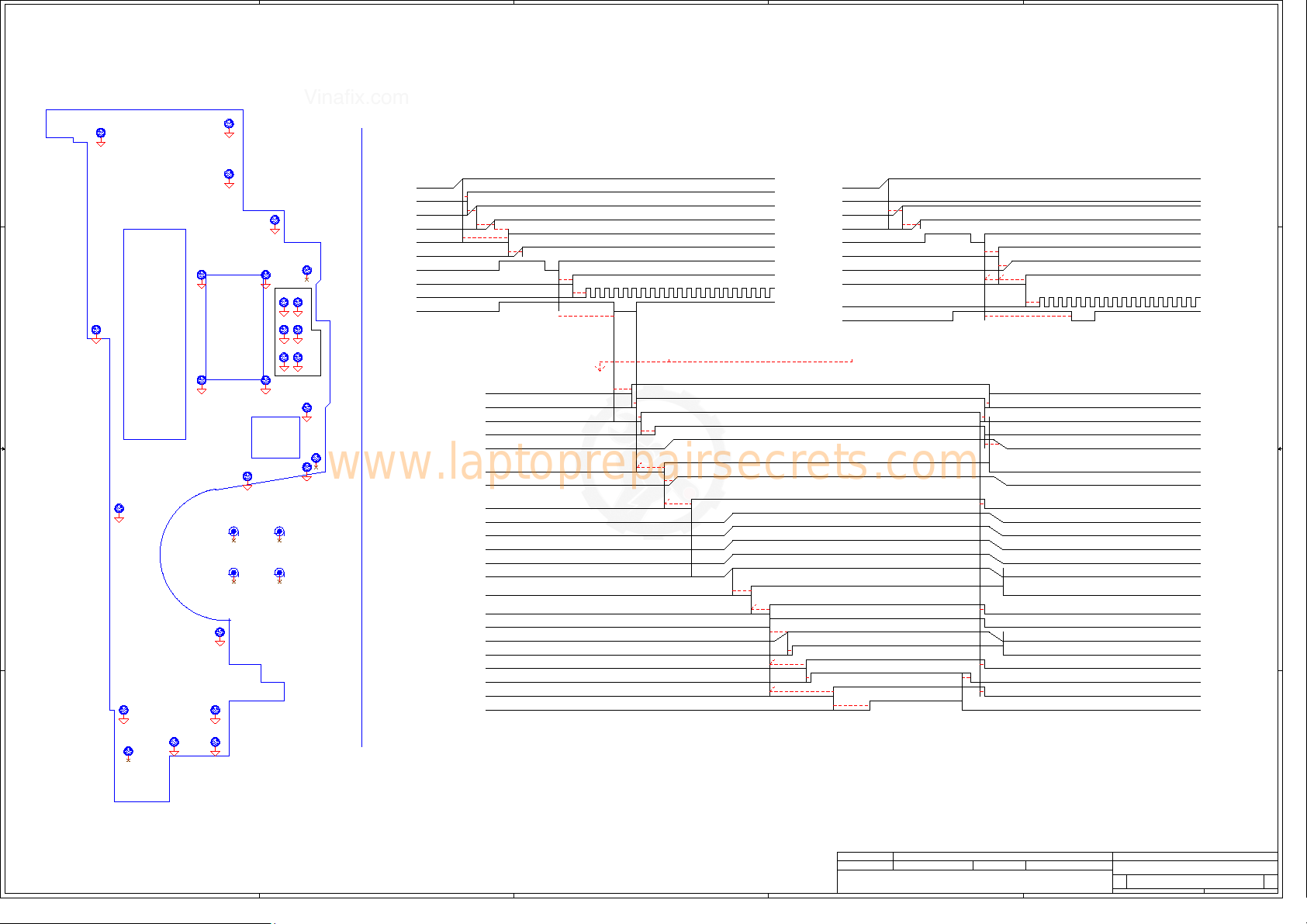

[AC Mode]

AC_IN

AC_PRESENT

B+

1

H21

H21

H_2P5N

H_2P5N

@

@

1

CLIP1

CLIP1

CLIP4

CLIP4

HOLEA

HOLEA

HOLEA

HOLEA

1

1

CLIP5

CLIP5

CLIP2

CLIP2

HOLEA

HOLEA

HOLEA

HOLEA

1

1

CLIP6

CLIP6

CLIP3

CLIP3

HOLEA

HOLEA

HOLEA

HOLEA

1

1

H19

H19

H_4P0

H_4P0

@

@

1

+3VLP/+VL

EN_5V/EN_3V

+5VALW/+3VALW

ON/OFFBTN#

EC_RSMRST#

SUSCLK

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

T=10ms

moniter AC_IN (51_ON)

Moniter ON/OFFBTN# rising edge

T=10ms

20ms

Moniter ON/OFFBTN# rising edge

T=110ms

Montier PBTN_OUT# falling edge.

[DC Mode]

BATT+

AC_PRESENT

B+

+3VLP/+VL

ON/OFFBTN#

+5VALW/+3VALW

EC_RSMRST#

SUSCLK

T=10ms

Moniter ON/OFFBTN#EN_5V/EN_3V

T=10ms

Moniter ON/OFFBTN# and EN_3/5V both of risgin edge

20ms

Moniter ON/OFFBTN# rising edgePBTN_OUT# T=110ms

DDR_VTT_PG_CTRL

H23

H23

H_2P5X2P9N

H_2P5X2P9N

@

@

H4

H4

1

H_2P3

H_2P3

@

@

1

FD4

FD4

@

@

1

FD2

FD2

@

@

1

+0.675VS

SYSON

+1.35V

SUSP#

+5VS

+3VS

+1.8VS

+1.5VS

+1.05VS

VCCST_PG_PWR (VCCST Powr Good from PWR IC)

VCCST_PG_EC (ALL_SYS_PWRGD,non CPU code VR)

VR_ON

T=10ms

After PM_SLP_S4# moniter PBTN_OUT#

T=10ms

After PM_SLP_S3# moniter SYSON rising edge.

After VCCST_PG_PWR risign edge ,OD pin

T=10ms

immediately, VCCST_PG_PWR & VCCST_PG_EC risign edge

immediately, After PM_SLP_S4# falling edge

immediately, After PM_SLP_S3# falling edge

immediately, After SUSP# falling edge

Vboot+CPU_CORE

VGATE

PCH_PWROK After VCCST_PG_EC rising edge

T=10ms

immediately, After SUSP# falling edge

H_CPUPWRGD

T=99ms

H11

H11

H_2P3

H_2P3

@

@

1

H_3P3

H_3P3

H24

H24

H_2P5X2P9N

H_2P5X2P9N

@

@

1

D D

H9

@H_2P3H9@H_2P3

1

H12

H12

H10

H10

H_3P3

H_3P3

@

@

@

@

1

1

PCH_PLTRST#

After VCCST_PG_EC assertionSYS_PWROK

After CPUPWRGD/PCH_PWRGD/SYS_PWROK assertion

immediately, After SUSP# falling edge

1

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Deciphered Date

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Screw Hole

Screw Hole

Screw Hole

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet

Date: Sheet

Date: Sheet

5

of

450Tuesday, March 25, 2014

of

450Tuesday, March 25, 2014

of

450Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

4

3

2

1

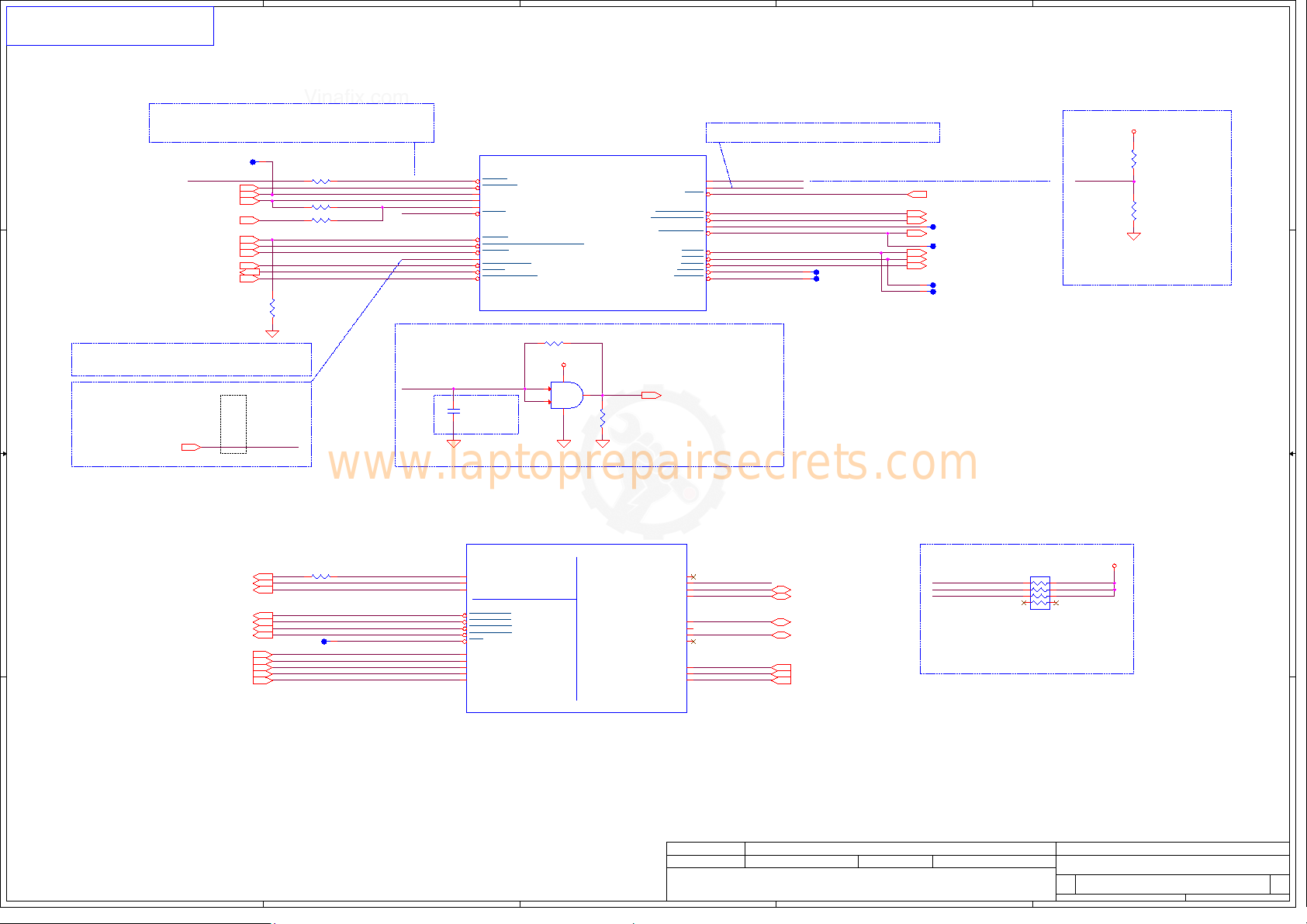

DDI/ MSIC/ XDP

D D

BDW_ULT_DDR3L

U1A

@

U1A

@

BDW_ULT_DDR3L

CPU_DP1_N0[32]

CPU_DP1_P0[32]

DockingDP

HDMI

C C

H_CPUPWRGD

1

C2222

C2222

100P_0402_50V8J

100P_0402_50V8J

@EMI@

@EMI@

2

EMI

DDR3CompensationSignals

DDR3CompensationSignals:

20milstocompsignals

25milstonon‐compsignals

500milforMaxtracelength

1 2

R9 200_0402_1%R9 200_0402_1%

1 2

B B

R10 120_0402_1%R10 120_0402_1%

1 2

R11 100_0402_1%R11 100_0402_1%

+1.35V

12

R29

R29

470_0402_5%

470_0402_5%

DIMM_DRAMRST#

1

C107

@ C107

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

H_PROCHOT#[39]

DDR3CompensationSignals

CPU_DP1_N1[32]

CPU_DP1_P1[32]

CPU_DP2_N0[27]

CPU_DP2_P0[27]

CPU_DP2_N1[27]

CPU_DP2_P1[27]

CPU_DP2_N2[27]

CPU_DP2_P2[27]

CPU_DP2_N3[27]

CPU_DP2_P3[27]

+1.05VS

12

R2

R2

62_0402_5%

62_0402_5%

R3 56_0402_5%R3 56_0402_5%

R6 10K_0402_5%R6 10K_0402_5%

1 2

1 2

DIMM_DRAMRST#[16,17]

DDR_PG_CTRL[16]

T111 @T111 @

H_PECI[39]

T2 @T2 @

H_PROCHOT#_R

H_CPUPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DIMM_DRAMRST#

DDR_PG_CTRL

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

U1B

U1B

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

EDPDDI

EDPDDI

EDP_DISP_UTIL

1 OF 19

1 OF 19

BDW_ULT_DDR3L

THERMAL

THERMAL

DDR3L

DDR3L

MISC

MISC

PWR

PWR

BDW_ULT_DDR3L

2 OF 19

2 OF 19

JTAG

JTAG

@

@

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_COMP

CPU_INV_PWM

1 2

R1 24.9_0402_1%R1 24.9_0402_1%

1 2

R31 0_0402_5%@R31 0_0402_5%@

EDP_TXN0 [26]

EDP_TXP0 [26]

EDP_TXN1 [26]

EDP_TXP1 [26]

EDP_AUXN [26]

EDP_AUXP [26]

INVPWM [26,9]

EDP_COMP: Trace width=20 mils,Spacing=25mil,Max length=100mils

PU/PDforJTAGsignals

PRDY

PREQ

J62

XDP_PRDY#

K62

XDP_PREQ#

E60

XDP_TCK

E61

XDP_TMS

E59

XDP_TRST#

F63

XDP_TDI

F62

XDP_TDO

J60

XDP_BPM#0

H60

XDP_BPM#1

H61

XDP_BPM#2

H62

XDP_BPM#3

K59

XDP_BPM#4

H63

XDP_BPM#5

K60

XDP_BPM#6

J61

XDP_BPM#7

T102 @T102 @

T16 @T16 @

T107 @T107 @

T15 @T15 @

T97 @T97 @

T98 @T98 @

T99 @T99 @

T100 @T100 @

T101 @T101 @

XDP_PREQ#

XDP_TMS

XDP_TDI

XDP_TDO

XDP_TCK

XDP_TRST#

+VCCIOA_OUT

1 2

R17 51_0402_5%@R17 51_0402_5%@

1 2

R15 51_0402_5%@R15 51_0402_5%@

1 2

R16 51_0402_5%@R16 51_0402_5%@

1 2

R18 51_0402_5%@R18 51_0402_5%@

1 2

R25 51_0402_5%R25 51_0402_5%

1 2

R28 51_0402_5%@R28 51_0402_5%@

+1.05VS

A A

Security Classification

Security Classification

5

4

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

HSW MCP(1/11) DDI,MSIC,XDP

HSW MCP(1/11) DDI,MSIC,XDP

HSW MCP(1/11) DDI,MSIC,XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

550Tuesday, March 25, 2014

550Tuesday, March 25, 2014

550Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

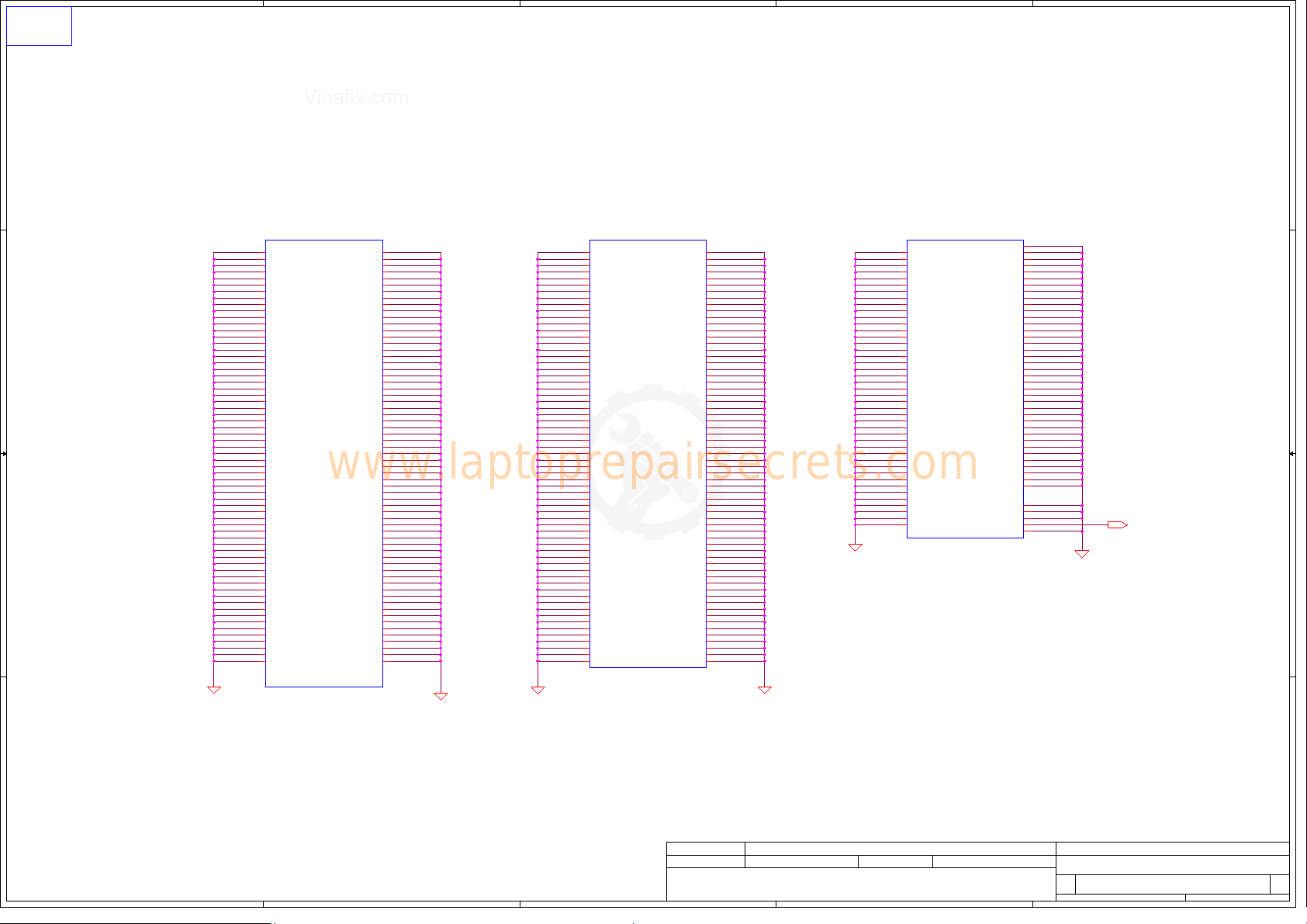

Memory I/F

4

3

2

1

D D

C C

B B

DDR_A_D[0..63][16]

DDR_A_MA[0..15][16]

DDR_A_DQS#[0..7][16]

DDR_A_DQS[0..7][16]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U1C

U1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

DDR_B_D[0..63][17]

DDR_B_MA[0..15][17]

DDR_B_DQS#[0..7][17]

DDR_B_DQS[0..7][17]

BDW_ULT_DDR3L

@

@

BDW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

DDRA_ODT0

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

SA_CLK_DDR#0 [16]

SA_CLK_DDR0 [16]

SA_CLK_DDR#1 [16]

SA_CLK_DDR1 [16]

DDRA_CKE0_DIMMA [16]

DDRA_CKE1_DIMMA [16]

DDRA_CS0_DIMMA# [16]

DDRA_CS1_DIMMA# [16]

T4 @T4 @

DDR_A_RAS# [16]

DDR_A_WE# [16]

DDR_A_CAS# [16]

DDR_A_BS0 [16]

DDR_A_BS1 [16]

DDR_A_BS2 [16]

SM_DIMM_VREFCA [16]

SA_DIMM_VREFDQ [16]

SB_DIMM_VREFDQ [17]

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U1D

U1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

@

@

BDW_ULT_DDR3L

BDW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDRB_ODT0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

SB_CLK_DDR#0 [17]

SB_CLK_DDR0 [17]

SB_CLK_DDR#1 [17]

SB_CLK_DDR1 [17]

DDRB_CKE0_DIMMA [17]

DDRB_CKE1_DIMMA [17]

DDRB_CS0_DIMMA# [17]

DDRB_CS1_DIMMA# [17]

T5 @T5 @

DDR_B_RAS# [17]

DDR_B_WE# [17]

DDR_B_CAS# [17]

DDR_B_BS0 [17]

DDR_B_BS1 [17]

DDR_B_BS2 [17]

4 OF 19

3 OF 19

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

A A

5

3 OF 19

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

Compal Secret Data

Compal Secret Data

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

4 OF 19

Deciphered Date

Deciphered Date

Deciphered Date

2

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

HSW MCP(2/11) DDRIII

HSW MCP(2/11) DDRIII

HSW MCP(2/11) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet

1

of

650Tuesday, March 25, 2014

650Tuesday, March 25, 2014

650Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

4

3

2

1

RTC/ SATA/ XDP

RTCBattery

+RTCVCC +RTCBATT

D D

C C

+RTCVCC

INTVRMEN(+1.05VA)

*

+3VALW_PCH

HDA_SDOUT

MEdebugmode,thissignalhasaweakinternalPD

Low=Disabled(Default)

*

High=Enabled[FlashDescriptorSecurityOveride]

B B

PH/PDforPCHJTAG

W=20mils

1

C179

C179

1U_0402_6.3V6K

1U_0402_6.3V6K

2

Safty suggestion remove EE side ,Keep PWR side

PCH_RTCX1

1 2

R33 10M_0402_5%R33 10M_0402_5%

1 2

Y1

Y1

32.768KHZ_12.5PF_1TJF125DP1A000D

32.768KHZ_12.5PF_1TJF125DP1A000D

1

C3

C3

15P_0402_50V8J

15P_0402_50V8J

2

R39 330K_0402_5%R39 330K_0402_5%

R40 330K_0402_5%@R40 330K_0402_5%@

H

IntegratedVRMenable

IntegratedVRMdisable

L

R86 51_0402_5%@R86 51_0402_5%@

12

12

1 2

@

@

R5181 1K_0402_5%

R5181 1K_0402_5%

1 2

PCH_RTCX2

1

C4

C4

15P_0402_50V8J

15P_0402_50V8J

2

PCH_INTVRMEN

HDA_SDOUT

PCH_JTAG_TCK

+RTCVCC +RTCVCC +RTCVCC

20K_0402_1%

20K_0402_1%

C5

C5

1U_0603_10V6K

1U_0603_10V6K

12

R37

R37

1

JME2

JME2

SHORT PADS

SHORT PADS

2

1 2

@

@

12

R36

R36

20K_0402_1%

20K_0402_1%

1

C2

C2

1U_0603_10V6K

1U_0603_10V6K

2

JME1

JME1

SHORT PADS

SHORT PADS

1 2

@

@

CMOS ME CMOS

JME2ShortPADplacementtoBottomside.

1 2

ME_FLASH[39]

R53 0_0402_5%@R53 0_0402_5%@

ClosedtoCPU

RP14

RP14

C5211

C5211

1

2

1 8

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

EMI@

EMI@

HDA_SDOUT_AUDIO[28]

HDA_SYNC_AUDIO[28]

HDA_RST_AUDIO#[28]

HDA_BITCLK_AUDIO[28]

68P_0402_50V8J

68P_0402_50V8J

@EMI@

@EMI@

RF

PCH_RTCRST#[38]

EMI

HDA_SDIN0[28]

1M_0402_5%

1M_0402_5%

12

R35

R35

12

R7545

R7545

33_0402_5%

33_0402_5%

@EMI@

@EMI@

C5390

C5390

22P_0402_50V8J

22P_0402_50V8J

@EMI@

@EMI@

T108 @T108 @

T120 @T120 @

T113 @T113 @

T119 @T119 @

T106 @T106 @

HDA_SDOUT

HDA_SYNC

HDA_RST#

HDA_BIT_CLK

EMI

PCH_RTCX1

PCH_RTCX2

SM_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST#

PCH_RTCRST#

HDA_BIT_CLK

HDA_SYNC

HDA_RST#

HDA_SDIN0

HDA_SDOUT

PCH_JTAG_RST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TCK_JTAGX

U1E

U1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

@

@

RTC

RTC

AUDIO SATA

AUDIO SATA

JTAG

JTAG

BDW_ULT_DDR3L

BDW_ULT_DDR3L

5 OF 19

5 OF 19

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

J5

H5

B15

A15

J8

SATA_PRX_DTX_N1

H8

SATA_PRX_DTX_P1

A17

SATA_PTX_DRX_N1

B17

SATA_PTX_DRX_P1

J6

H6

B14

C15

F5

E5

C17

D17

V1

EC_SMI#

U1

TS_PRSNC#

V6

PCH_GPIO36

AC1

PCH_GPIO37

A12

L11

K10

C12

SATA_RCOMP

U3

SATALED#

SATA_PRX_DTX_N0 [36]

SATA_PRX_DTX_P0 [36]

SATA_PTX_DRX_N0 [36]

SATA_PTX_DRX_P0 [36]

SATA_PRX_DTX_N1 [35]

SATA_PRX_DTX_P1 [35]

SATA_PTX_DRX_N1 [35]

SATA_PTX_DRX_P1 [35]

SATARCompwithin500mils

EC_SMI# [39]

TS_PRSNC# [10]

PCH_GPIO36 [10]

PCH_GPIO37 [10]

R43 3.01K_0402_1%R43 3.01K_0402_1%

LED1

@ LED1

@

1 2

19-217-R6C-P1Q2-3T_RED

19-217-R6C-P1Q2-3T_RED

CustomerRequest

HDD

mSATA

+1.05VS_ASATA3PLL

1 2

PCH_SATALED# [10]

A A

Security Classification

Security Classification

5

4

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

HSW MCP(3/11) RTC,SATA,XDP

HSW MCP(3/11) RTC,SATA,XDP

HSW MCP(3/11) RTC,SATA,XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet

1

of

750Tuesday, March 25, 2014

750Tuesday, March 25, 2014

750Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

4

3

2

1

CLK/ SPI/ SMBUS

BDW_ULT_DDR3L

U1F

@

U1F

@

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

EMI

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

LPC_AD0[38,39]

LPC_AD1[38,39]

LPC_AD2[38,39]

LPC_AD3[38,39]

LPC_FRAME#[38,39]

+3VM

1 2

R5001 1K_0402_1%R5001 1K_0402_1%

1 2

R5002 1K_0402_1%R5002 1K_0402_1%

12

PCH_GPIO18

PCH_GPIO19

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

WLAN_CLKREQ#

CLK_PCIE_CR#

CLK_PCIE_CR

CR_CLKREQ#

CLK_PEG_VGA#

CLK_PEG_VGA

PEG_CLKREQ#

PCH_GPIO23

1

C5215

C5215

68P_0402_50V8J

68P_0402_50V8J

@EMI@

@EMI@

2

PCH_GPIO18[10]

PCH_GPIO19[10]

CLK_PCIE_WLAN#[34]

CLK_PCIE_WLAN[34]

WLAN_CLKREQ#[10,34]

CLK_PCIE_CR#[38]

CLK_PCIE_CR[38]

CR_CLKREQ#[10,38]

CLK_PEG_VGA#[18]

CLK_PEG_VGA[18]

PEG_CLKREQ#[10,18]

PCH_GPIO23[10]

RF

1 2

R107 33_0402_5%EMI@R107 33_0402_5%EMI@

1 2

R108 33_0402_5%SBA@R108 33_0402_5%SBA@

R7546 33_0402_5%@EMI@R7546 33_0402_5%@EMI@

C5391

C5391

22P_0402_50V8J

22P_0402_50V8J

@EMI@

@EMI@

D D

WLAN

Card Reader

GPU

C C

PCH_SPI_CLK_R0

PCH_SPI_CLK_R1

C5212

C5212

68P_0402_50V8J

68P_0402_50V8J

@EMI@

@EMI@

1

2

BDW_ULT_DDR3L

CLOCK

CLOCK

SIGNALS

SIGNALS

6 OF 19

6 OF 19

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_MOSI

PCH_SPI_MISO

PCH_SPI_WP#

PCH_SPI_HOLD#

XTAL24_IN

XTAL24_OUT

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

U1G

U1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

A25

XTAL24_IN

B25

XTAL24_OUT

K21

RSVD

M21

RSVD

C26

XCLK_BIASREF

C35

ULT_TESTLOW1

C34

ULT_TESTLOW2

AK8

ULT_TESTLOW3

AL8

ULT_TESTLOW4

AN15

CLKOUT_LPC0

AP15

CLKOUT_LPC1

B35

CLK_BCLK_ITP#

A35

CLK_BCLK_ITP

BDW_ULT_DDR3L

BDW_ULT_DDR3L

@

@

LPC

LPC

SMBUS

SMBUS

C-LINKSPI

C-LINKSPI

1 2

R91 3.01K_0402_1%R91 3.01K_0402_1%

1 8

RP28 10K_8P4R_5%RP28 10K_8P4R_5%

2 7

3 6

4 5

R96 22_0402_5%R96 22_0402_5%

R97 22_0402_5%TPM@R97 22_0402_5%TPM@

T21 @T21 @

R99 22_0402_5%@R99 22_0402_5%@

T26 @T26 @

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML1ALERT/PCHHOT/GPIO73

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

7 OF 19

7 OF 19

CL_CLK

CL_DATA

CL_RST

+1.05VS_AXCK_LCPLL

12

12

12

AN2

PCH_GPIO11

AP2

SMBCLK

AH1

SMBDATA

AL2

FW_UPDATE

AN1

SML0CLK

AK1

SML0DATA

AU4

PCH_GPIO73

AU3

SML1CLK

AH3

SML1DATA

AF2

AD2

AF4

CLK_LPC_EC [39]

CLK_PCI_TPM [38]

CLK_PCI_DB [38]

PCH_GPIO11 [10]

FW_UPDATE [30]

PCH_GPIO73 [10]

CL_CLK [34]

CL_DAT [34]

CL_RST# [34]

SMBus:RAMSPD/SecurityROM/ClickPad/NFC/M.2SSD/M.2WLAN

XTAL24_OUT

XTAL24_IN

CLK_LPC_EC

CLK_PCI_TPM

CLK_PCI_DB

RF Request

SML0CLK

SML0DATA

SML1DATA

SML1CLK

SMBCLK

SMBDATA

PCH_SMB_DATA

PCH_SMB_CLK

R87 1M_0402_5%R87 1M_0402_5%

1

C6

C6

15P_0402_50V8J

15P_0402_50V8J

2

+3VS

12

Y2

Y2

24MHZ_12PF_7V24000020

24MHZ_12PF_7V24000020

1

1

GND

2

@EMI@

@EMI@

C5411 22P_0402_50V8J

C5411 22P_0402_50V8J

@EMI@

@EMI@

C5412 22P_0402_50V8J

C5412 22P_0402_50V8J

@EMI@

@EMI@

C5413 22P_0402_50V8J

C5413 22P_0402_50V8J

RP45

RP45

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

RP13

RP13

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

GND

4

3

3

1

C7

C7

2

+3VALW_PCH

15P_0402_50V8J

15P_0402_50V8J

+3VS

SBA - 2 SPI Device = 33 ohm - P/N: SD309330A80

SPISignal

PCH_SPI_HOLD0#

PCH_SPI_MISO_0

B B

ROM side

PCH_SPI_MOSI_0

PCH_SPI_HOLD1#

PCH_SPI_WP1#

PCH_SPI_MISO_1

PCH_SPI_MOSI_1

Non-SBA - 1 SPI Device = 15 ohm - P/N: SD300001P00

SBA@

SBA@

RP43

RP43

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

33_0804_8P4R_5%

RP44

RP44

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

33_0804_8P4R_5%

SBA@

SBA@

PCH_SPI_HOLD#

PCH_SPI_WP#PCH_SPI_WP0#

PCH_SPI_MISO

PCH_SPI_MOSI

PCH side

RP43

RP43

15_8P4R_5%

15_8P4R_5%

NOSBA@

NOSBA@

SD300001P00

SD300001P00

SecurityROM

U11

U11

1

NC

2

NC

PLT_RST_BUF#[18,29,34,38,39,9]

3

PROT#

4

GND

PCA24S08AD_SO8

PCA24S08AD_SO8

8

VCC

7

WP

6

PCH_SMB_CLK

SCL

5

PCH_SMB_DATA

SDA

+3VS

1

C91

C91

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

SPIROM

1st:SA00004MK00

SMBDATA

SMBCLK

2

6 1

Q3A

Q3A

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

5

3 4

Q3B

Q3B

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

1

C2226

C2226

100P_0402_50V8J

100P_0402_50V8J

@

@

2

1

C2227

C2227

100P_0402_50V8J

100P_0402_50V8J

@

@

2

CustomerRequest

PCH_SMB_DATA

PCH_SMB_CLK

PCH_SMB_DATA [16,17,34,35,37]

PCH_SMB_CLK [16,17,34,35,37]

2nd:SA00004ML00

SPIROM(8MByte)

C5214

C5214

@EMI@

@EMI@

1

2

+3VM

1

C5392

C5392

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

SPIROM8MB

1st:SA000039A20‐Winbond

2nd:SA000046400‐E‐ON

SPIROM4MB

1st:SA00003K800‐Winbond

2nd:SA00004LI00‐E‐ON

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

PCH_SPI_CS0#

PCH_SPI_WP0#

U2000

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25Q64FVSSIQ_SO8

W25Q64FVSSIQ_SO8

/HOLD(IO3)

DI(IO0)

VCC

CLK

8

7

PCH_SPI_HOLD0#PCH_SPI_MISO_0

6

PCH_SPI_CLK_R0

5

PCH_SPI_MOSI_0

68P_0402_50V8J

68P_0402_50V8J

U2000

RF

SPIROM(4MByte)

A A

U2202

U2202

PCH_SPI_CS1#

PCH_SPI_MISO_1

PCH_SPI_WP1#

1

/CS

2

DO/IO1

3

/WP/IO2

4

GND

W25Q32FVSSIQ_SO8

W25Q32FVSSIQ_SO8

SBA@

SBA@

5

/HOLD/IO3

+3VM

8

VCC

7

PCH_SPI_HOLD1#

6

PCH_SPI_CLK_R1

CLK

5

PCH_SPI_MOSI_1

DI/IO0

SML1Bus:EC/GPU/ThermalSensor/P‐sensor

+3VS

PU 2.2K at EC side (+3VS)

5

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

HSW MCP(4/11) CLK,SPI,SMBUS

HSW MCP(4/11) CLK,SPI,SMBUS

HSW MCP(4/11) CLK,SPI,SMBUS

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

1

SML1CLK

SML1DATA

for KSP4

2

6 1

Q2417A

Q2417A

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

3 4

Q2417B

Q2417B

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

EC_SMB_CK2 [21,37,39]

EC_SMB_DA2 [21,37,39]

850Tuesday, March 25, 2014

850Tuesday, March 25, 2014

850Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

PM/ GPIO/ DDI

4

3

2

1

D D

C C

B B

AC_PRESENTNeedpullhightoVCCDSW3_3

(IfnodeepSx,connecttoVCCSUS3_3)

Note:SUSACK#andSUSWARN#canbetiedtogetherifECdoesnotwanttoinvolve

inthehandshakemechanismfortheDeepSleepstateentryandexit.

CANbeNC,ifnotsupportDeepSx

T115@ T115@

SUSPWRDNACK

SYS_RESET#[10,38]

SYS_PWROK[39]

PCH_PWROK[39]

PCH_APWROK[39]

EC_RSMRST#[39]

SUSPWRDNACK[10,39]

PBTN_OUT#[39]

PCH_GPIO72[10]

PM_SLP_S0#[38]

SLP_WLAN#[10,34]

R135 0_0402_5%@R135 0_0402_5%@

R147 0_0402_5%NOSBA@R147 0_0402_5%NOSBA@

R146 0_0402_5%SBA@R146 0_0402_5%SBA@

R149

R149

10K_0402_5%

10K_0402_5%

1 2

1 2

1 2

1 2

PM_SLP_S0#

PU10k@page10

AC_PRESENT[10,39]

INVPWM[26,5]

ENBKL[39]

PCH_ENVDD[26]

GC6_FB_EN[21,22]

DGPU_PWR_EN[10,23]

DGPU_HOLD_RST#[10,18]

BT_OFF#[10,34]

PCH_GPIO55[10]

PCH_GPIO52[10]

PCH_GPIO54[10]

PCH_GPIO51[10]

PCH_GPIO53[10]

AC_PRESENT

R150 0_0402_5%R150 0_0402_5%

1 2

T27@ T27@

SUSACK#_R

SYS_RESET#

SYS_PWROK

PCH_PWROK

PCH_PWROK_R

PLT_RST#

EC_RSMRST#

SUSPWRDNACK

PBTN_OUT#

AC_PRESENT

PCH_GPIO72

SLP_WLAN#

PLT_RST#

EDP_BKCTL

GC6_FB_EN

DGPU_PWR_EN

DGPU_HOLD_RST#

BT_OFF#

PCH_GPIO55

PCH_GPIO52

PCH_GPIO54

PCH_GPIO51

PCH_GPIO53

U1H

U1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

1

C2223

C2223

100P_0402_50V8J

100P_0402_50V8J

@EMI@

@EMI@

2

ESD

U1I

@

U1I

@

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

BDW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

1 2

2

B

1

A

@

@

BDW_ULT_DDR3L

BDW_ULT_DDR3L

PCIE

PCIE

BDW_ULT_DDR3L

8 OF 19

8 OF 19

+3VS

MC74VHC1G08DFT2G_SC70-5

MC74VHC1G08DFT2G_SC70-5

5

U15

U15

P

Y

G

3

@

@

R155 0_0402_5%R155 0_0402_5%

eDP SIDEBAND

eDP SIDEBAND

4

12

R159

R159

100K_0402_5%

100K_0402_5%

DISPLAY

DISPLAY

DSWVRMEN

DPWROK

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

PLT_RST_BUF# [18,29,34,38,39,8]

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

DPWROK:TiredtoghterwithRSMRST#thatdonotsupportDeepSx

AW7

DSWODVREN

AV5

EC_RSMRST#

AJ5

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

PCH_PCIE_WAKE#

V5

PCH_GPIO32

AG4

PCH_GPIO61

AE6

SUSCLK

AP5

PM_SLP_S5#

AJ6

PM_SLP_S4#

AT4

PM_SLP_S3#

AL5

PM_SLP_A#

AP4

PM_SLP_SUS#

AJ7

PM_SLP_LAN#

DDI1_CTRL_DATA

DDI2_CTRL_CLK

DDI2_CTRL_DATA

DDI1_AUXN

DDI1_AUXP

T110 @T110 @

T112 @T112 @

DDI2_CTRL_CLK [27]

DDI2_CTRL_DATA [27]

DDI1_AUXN [32]

DDI1_AUXP [32]

DDI1_DP_HPD [32]

DDI2_HDMI_HPD [27]

EDP_HPD [26]

WAKE

PCH_PCIE_WAKE# [10]

PCH_GPIO32 [10]

PCH_GPIO61 [10]

T121 @T121 @

PM_SLP_S5# [38,39]

T116 @T116 @

PM_SLP_S4# [38,39]

PM_SLP_S3# [38,39]

PM_SLP_A# [38,39,40,46]

T117 @T117 @

T118 @T118 @

PH/PDforPCHJTAG

DDI2_CTRL_CLK

DDI1_CTRL_DATA

DDI2_CTRL_DATA

DDPB_CTRLDATA:PortBDetected

DDPC_CTRLDATA:PortCDetected

1:PortBorCisdetected

*

0:PortBorCisnotdetected

PorthaveinternalPD

RP34

RP34

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

+RTCVCC

R134

R134

330K_0402_5%

330K_0402_5%

DSWODVREN

1 2

12

R139

R139

330K_0402_5%

330K_0402_5%

@

@

DSWODVREN‐OnDieDSWVREnable

Enable(default)

H

*

Disable

L

+3VS

9 OF 19

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

A A

5

4

9 OF 19

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

for KSP4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

HSW MCP(5/11) PM,GPIO,DDI

HSW MCP(5/11) PM,GPIO,DDI

HSW MCP(5/11) PM,GPIO,DDI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

950Tuesday, March 25, 2014

950Tuesday, March 25, 2014

950Tuesday, March 25, 2014

0.1

0.1

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

GPIO/ LPIO

4

3

2

1

KB_RST#DOCK_PRSNT#

SERIRQ

PCH_OPIRCOMP

PCH_GPIO83

PCH_GPIO84

GPU_EVENT#

PCH_GPIO86

PCH_GPIO87

PCH_GPIO88

PCH_GPIO89

VOL_UP#

VOL_DOWN#

PCH_GPIO92

PCH_GPIO93

PCH_GPIO94

PCH_GPIO0

PCH_GPIO1

PCH_GPIO2

PCH_GPIO3

PCH_GPIO4

PCH_GPIO5

PCH_GPIO6

PCH_GPIO7

PCH_GPIO64

PCH_GPIO65

PCH_GPIO66

PCH_GPIO67

PCH_GPIO68

PCH_GPIO69

+1.05VS

12

R179

R179

1K_0402_1%

1K_0402_1%

1 2

R185 49.9_0402_1%R185 49.9_0402_1%

DGPU_THRMTRIP# [21]

KB_RST# [39]

SERIRQ [38,39]

GPU_EVENT# [21]

VOL_UP# [38]

VOL_DOWN# [38]

PCH_GPIO86

1 2

R710 1K_0402_1%@R710 1K_0402_1%@

1 2

R711 1K_0402_1%R711 1K_0402_1%

+3VS

GSPI0_MOSI/GPIO86:BootBIOSStrap

1:LPCBUS

0:SPIBUS(default)

*

PorthaveinternalPD

PCH_GPIO66

1 2

R189 4.7K_0402_5%@R189 4.7K_0402_5%@

+3VS

SDIO_D0/GPIO66:Top‐BlockSwapOverride

1:Enable

0:Disable

*

PorthaveinternalPD

+3VALW_PCH

D D

+3VS

C C

+3VS

1 2

R712 1K_0402_1%R712 1K_0402_1%

EC_WAKE#

GPIO15:TLSConfidentiality

1:IntelMETLSwithconfidentiality

0:IntelMETLSwithnoconfidentiality

*

PorthaveinternalPD

ID_PRSNT#ForZIUS1/S2only

1:Lenovo

0:NEC

Pullup/PulldownatPowerBoard

R707 10K_0402_5%UMA@R707 10K_0402_5%UMA@

1 2

R708 10K_0402_5%DIS@R708 10K_0402_5%DIS@

12

DGPU_PRSNT#

M/BType

1:UMA

0:dGPU

1 2

R193 10K_0402_5%R193 10K_0402_5%

+3VS +3VALW_PCH +3VS

MSATA_DEVSLP1

BDW_ULT_DDR3L

U1J

@

U1J

@

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

+3VS

PCH_GPIO76

PCH_GPIO12

EC_WAKE#

WWAN_PWRON#

PCH_GPIO17

ID_PRSNT#

PCH_GPIO27

PCH_GPIO28

PCH_GPIO26

PCH_GPIO56

PCH_GPIO57

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

PCH_GPIO47

PCH_GPIO48

DGPU_PRSNT#

PCH_GPIO50

PCH_GPIO71

PCH_GPIO13

PCH_GPIO14

PCH_GPIO25

PCH_GPIO45

PCH_GPIO46

WLAN_WAKE#

EC_SCI#

HDD_DEVSLP0

mSATA_DETEC#

MSATA_DEVSLP1

3G_OFF#

SPKR

DOCK_PRSNT#[32]

EC_WAKE#[39]

WWAN_PWRON#[35]

ID_PRSNT#[38]

WLAN_WAKE#[34]

EC_SCI#[39]

HDD_DEVSLP0[36]

mSATA_DETEC#[35]

MSATA_DEVSLP1[35]

3G_OFF#[35]

SPKR[28]

BDW_ULT_DDR3L

GPIO

GPIO

10 OF 19

10 OF 19

CPU/

CPU/

MISC

MISC

SERIAL IO

SERIAL IO

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PCH_GPIO14

PCH_GPIO58

DOCK_PRSNT#

RP29 10K_8P4R_5%RP29 10K_8P4R_5%

PCH_GPIO47

PCH_GPIO28

PCH_GPIO45

PCH_GPIO56

RP32 10K_8P4R_5%RP32 10K_8P4R_5%

PCH_GPIO26

PCH_GPIO57

PCH_GPIO13

RP27 10K_8P4R_5%RP27 10K_8P4R_5%

PCH_GPIO44

EC_SCI#

RP30 10K_8P4R_5%RP30 10K_8P4R_5%

PCH_GPIO73 [8]

PCH_GPIO41 [11]

USB_OC0# [11,32,33]

PCH_GPIO11 [8]

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

2014/01/09 2014/01/09

2014/01/09 2014/01/09

2014/01/09 2014/01/09

Deciphered Date

+3VALW_PCH

2

4

1 8

2 7

3 6

4 5

RP19 10K_8P4R_5%RP19 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP24 10K_8P4R_5%RP24 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP25 10K_8P4R_5%RP25 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP26 10K_8P4R_5%RP26 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP23 10K_8P4R_5%RP23 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP37 10K_8P4R_5%RP37 10K_8P4R_5%

PCH_GPIO0PCH_GPIO94

PCH_GPIO3

PCH_GPIO48

PCH_GPIO71

WWAN_PWRON#

SERIRQ

PCH_GPIO50

PCH_GPIO76

PCH_GPIO87

PCH_GPIO55

KB_RST#

mSATA_DETEC#

PCH_GPIO64

PCH_GPIO69

PCH_GPIO5

PCH_GPIO52 [9]

PCH_GPIO51 [9]

TS_PRSNC# [7]

PCH_GPIO36 [7]

PCH_GPIO19 [8]

PCH_GPIO32 [9]

PCH_GPIO23 [8]

PCH_GPIO18 [8]

PCH_GPIO55 [9]

PEG_CLKREQ# [18,8]

3

1 8

2 7

3 6

5

4 5

RP17 10K_8P4R_5%RP17 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP16 10K_8P4R_5%RP16 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP20 10K_8P4R_5%RP20 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP21 10K_8P4R_5%RP21 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP22 10K_8P4R_5%RP22 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP18 10K_8P4R_5%RP18 10K_8P4R_5%

B B

+3VALW_PCH

A A

PCH_GPIO93

PCH_GPIO92

PCH_GPIO4

PCH_GPIO7

PCH_GPIO6

PCH_GPIO1

PCH_GPIO68

PCH_GPIO84

VOL_DOWN#

VOL_UP#

PCH_GPIO17

PCH_GPIO88

PCH_GPIO2

PCH_GPIO65

PCH_GPIO67

DGPU_HOLD_RST# [18,9]

PCH_GPIO37 [7]

WLAN_CLKREQ# [34,8]

SYS_RESET# [38,9]

SLP_WLAN# [34,9]

PCH_GPIO53 [9]

PCH_SATALED# [7]

PCH_GPIO54 [9]

for KSP4

4 5

3 6

2 7

1 8

RP1 10K_8P4R_5%RP1 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP33 10K_8P4R_5%RP33 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP15 10K_8P4R_5%RP15 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP31 10K_8P4R_5%RP31 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP35 10K_8P4R_5%RP35 10K_8P4R_5%

PCH_GPIO83

PCH_GPIO89

3G_OFF#

HDD_DEVSLP0

PCH_GPIO46

PCH_GPIO25

PCH_GPIO27

WLAN_WAKE#

PCH_GPIO12

PCH_GPIO59

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

HSW MCP(6/11) GPIO,LPIO

HSW MCP(6/11) GPIO,LPIO

HSW MCP(6/11) GPIO,LPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B591P_SDV

LA-B591P_SDV

LA-B591P_SDV

Date: Sheet of

Date: Sheet of

Date: Sheet of

DGPU_PWR_EN [23,9]

AC_PRESENT [39,9]

BT_OFF# [34,9]

CR_CLKREQ# [38,8]

PCH_PCIE_WAKE# [9]

PCH_GPIO61 [9]

PCH_GPIO42 [11]

SUSPWRDNACK [39,9]

USB_OC3# [11,33]

PCH_GPIO72 [9]

1

0.1

0.1

10 50Tuesday, March 25, 2014

10 50Tuesday, March 25, 2014

10 50Tuesday, March 25, 2014

0.1

Vinafix.com

5

www.laptoprepairsecrets.com

4

3

2

1

PCIE/ USB

D D

BDW_ULT_DDR3L

U1K

@

U1K

@

PCIE_PRX_DTX_N5_L0[18]

PCIE_PRX_DTX_P5_L0[18]

PCIE_PTX_C_DRX_N5_L0[18]

PCIE_PTX_C_DRX_P5_L0[18]

PCIE_PRX_DTX_N5_L1[18]

PCIE_PRX_DTX_P5_L1[18]

dGPU

C C

WLAN

Card Reader

USB 2/3 (OneLink)

Carmera (3D Camera)

B B