5

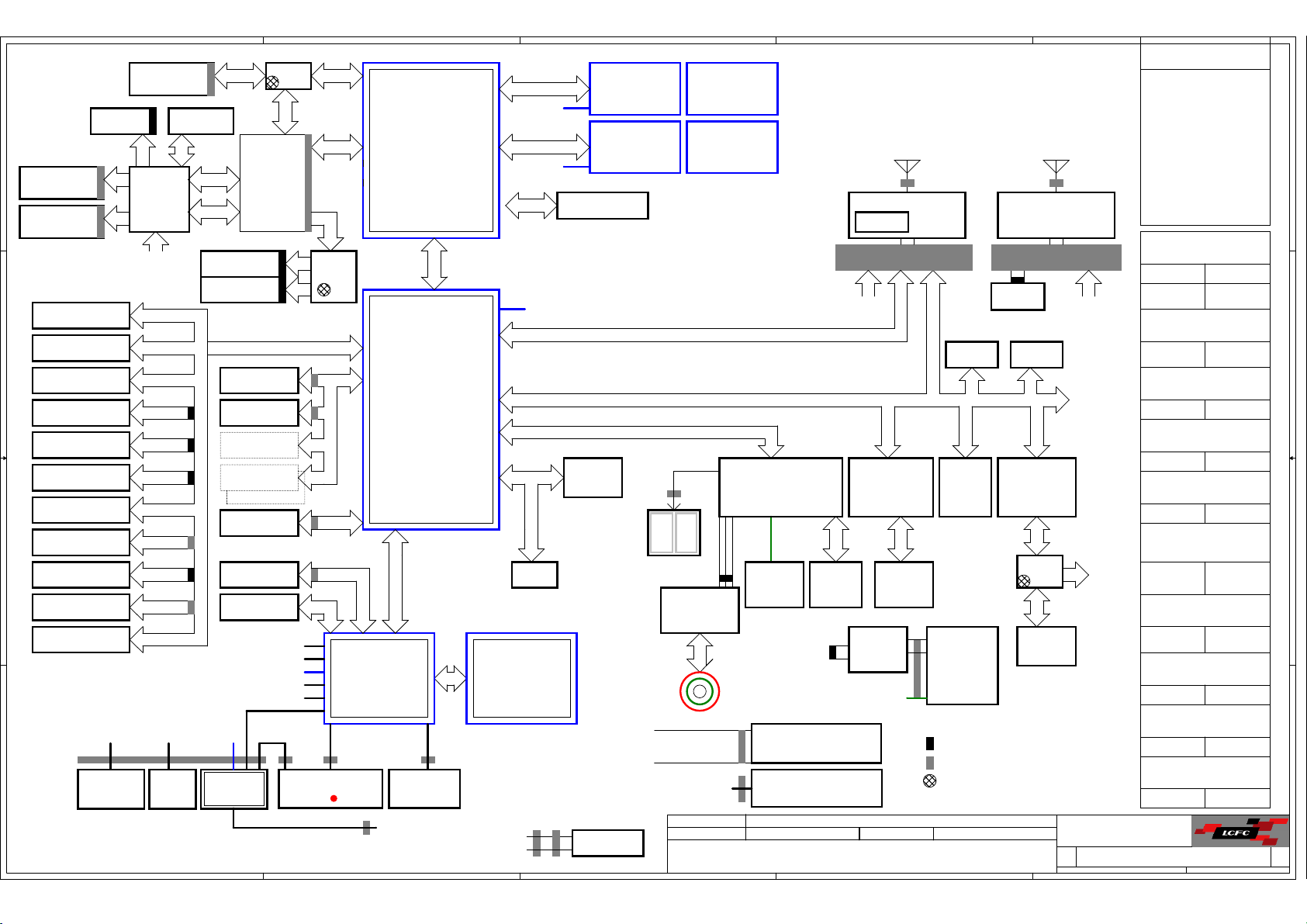

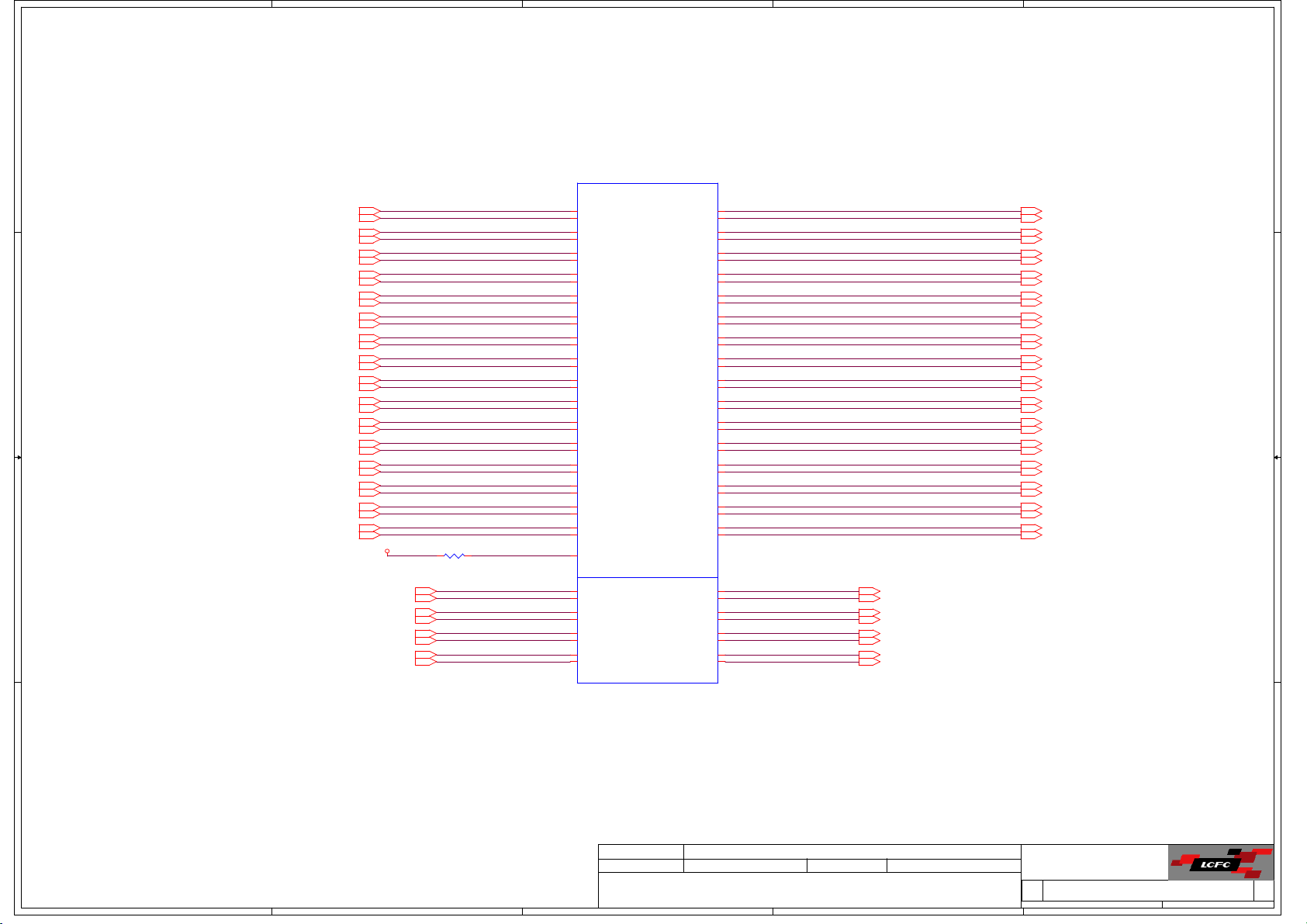

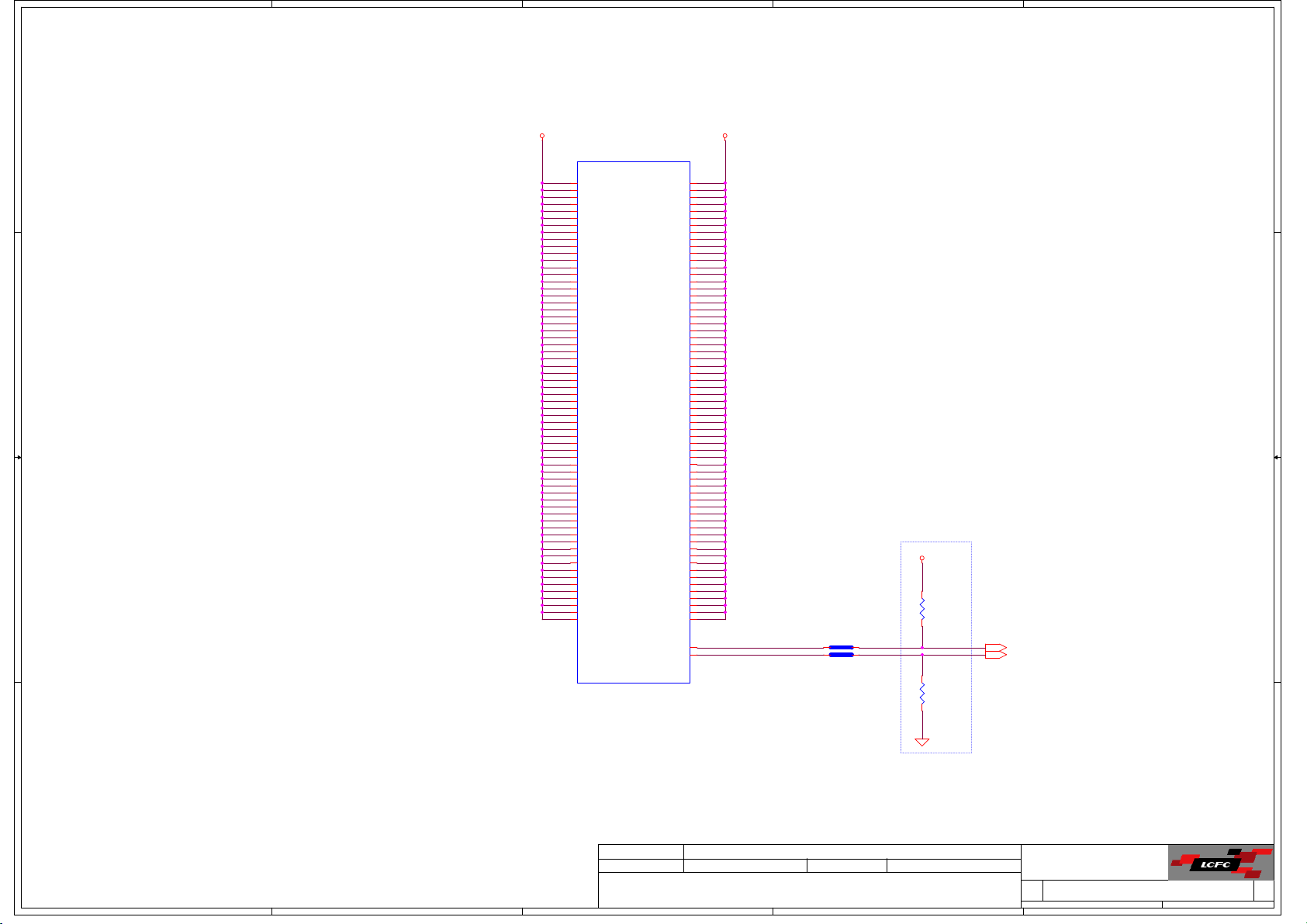

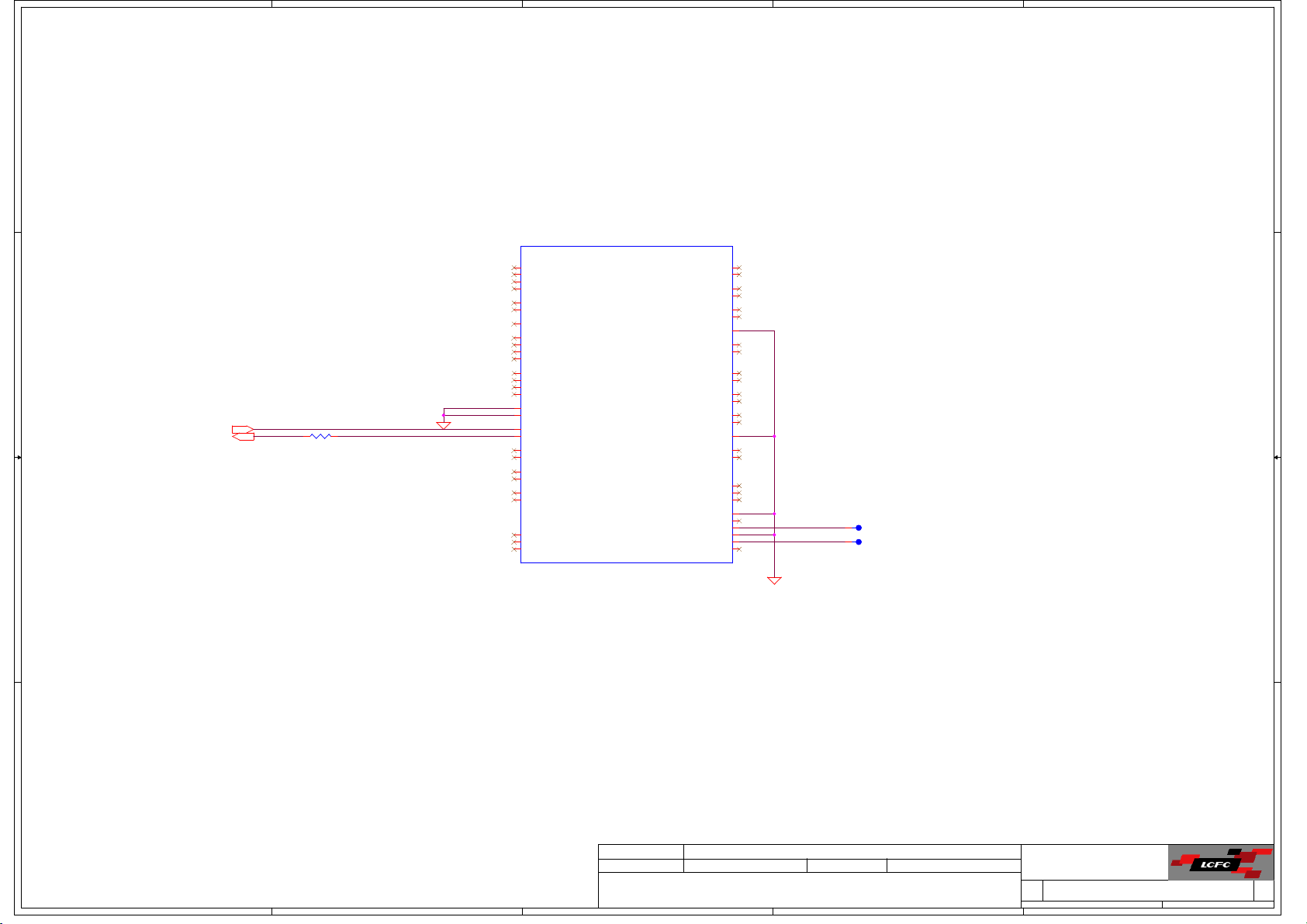

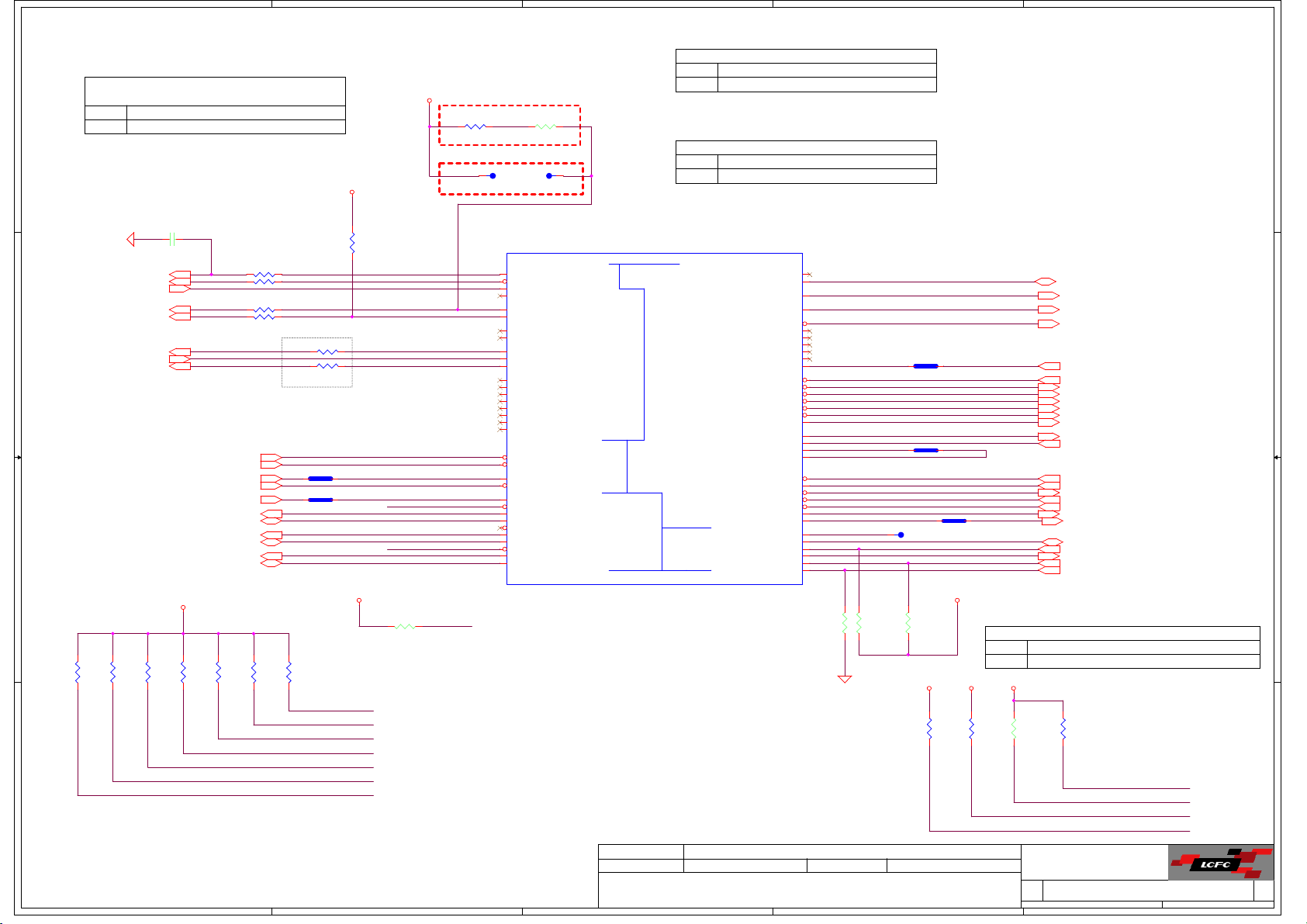

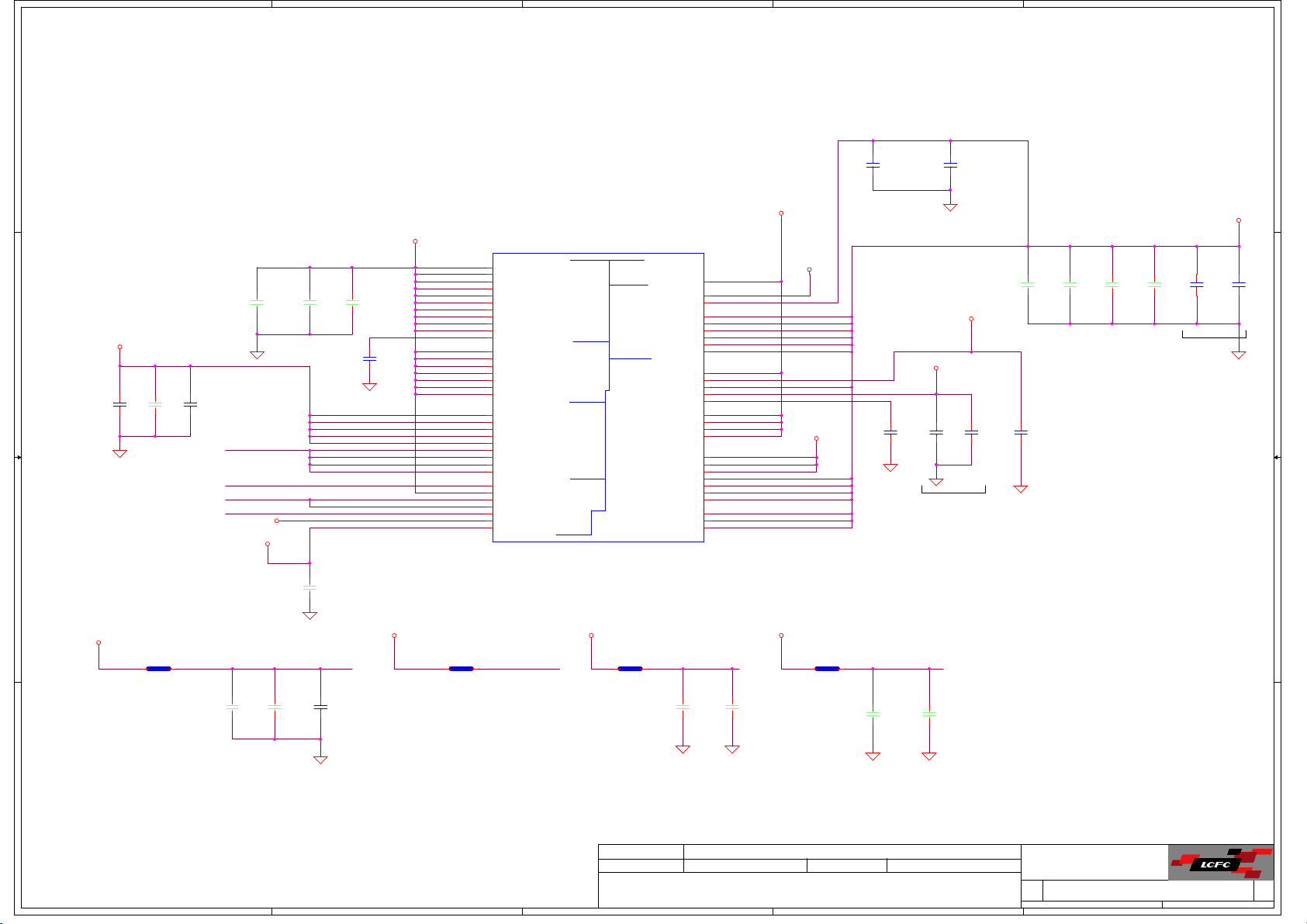

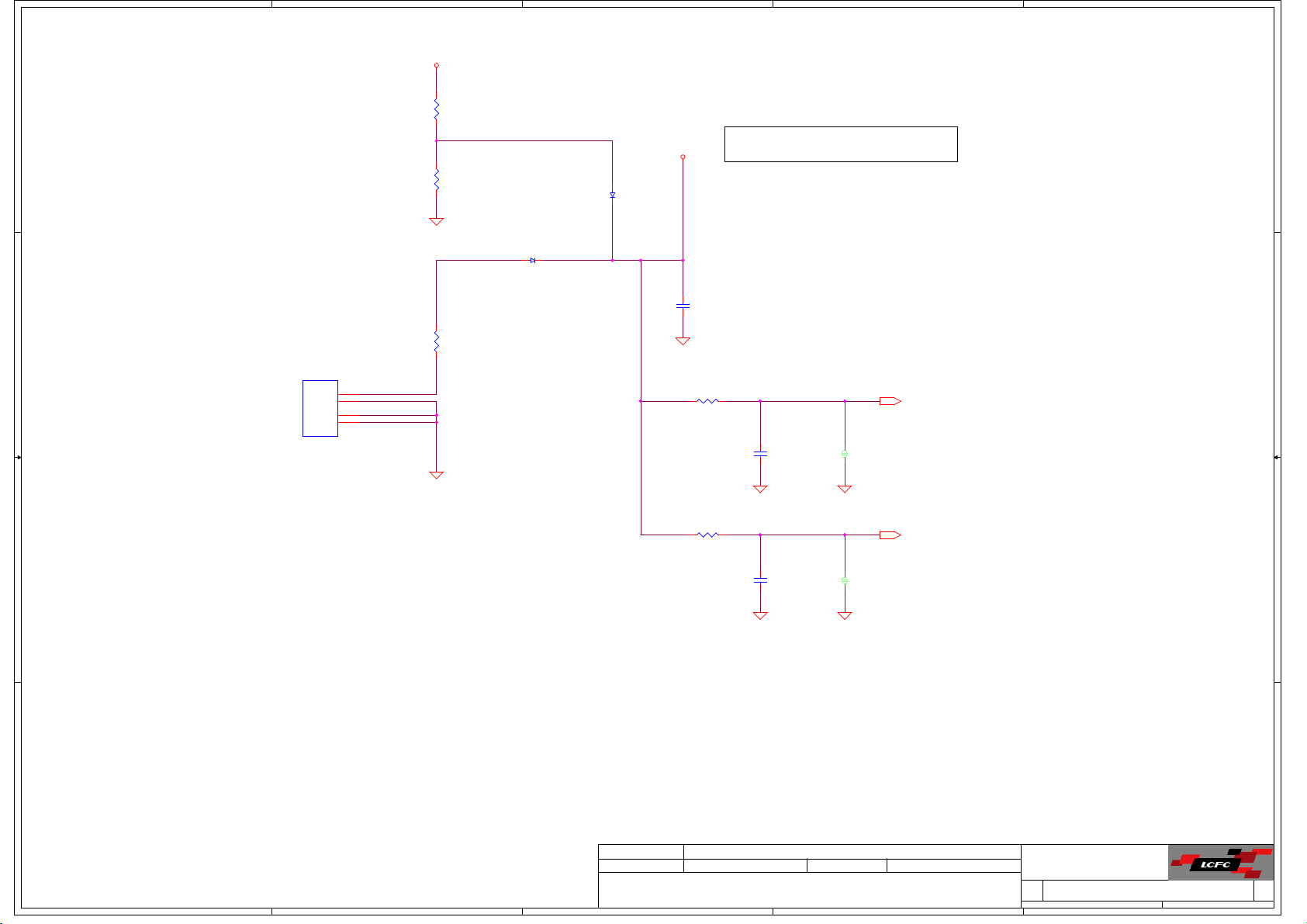

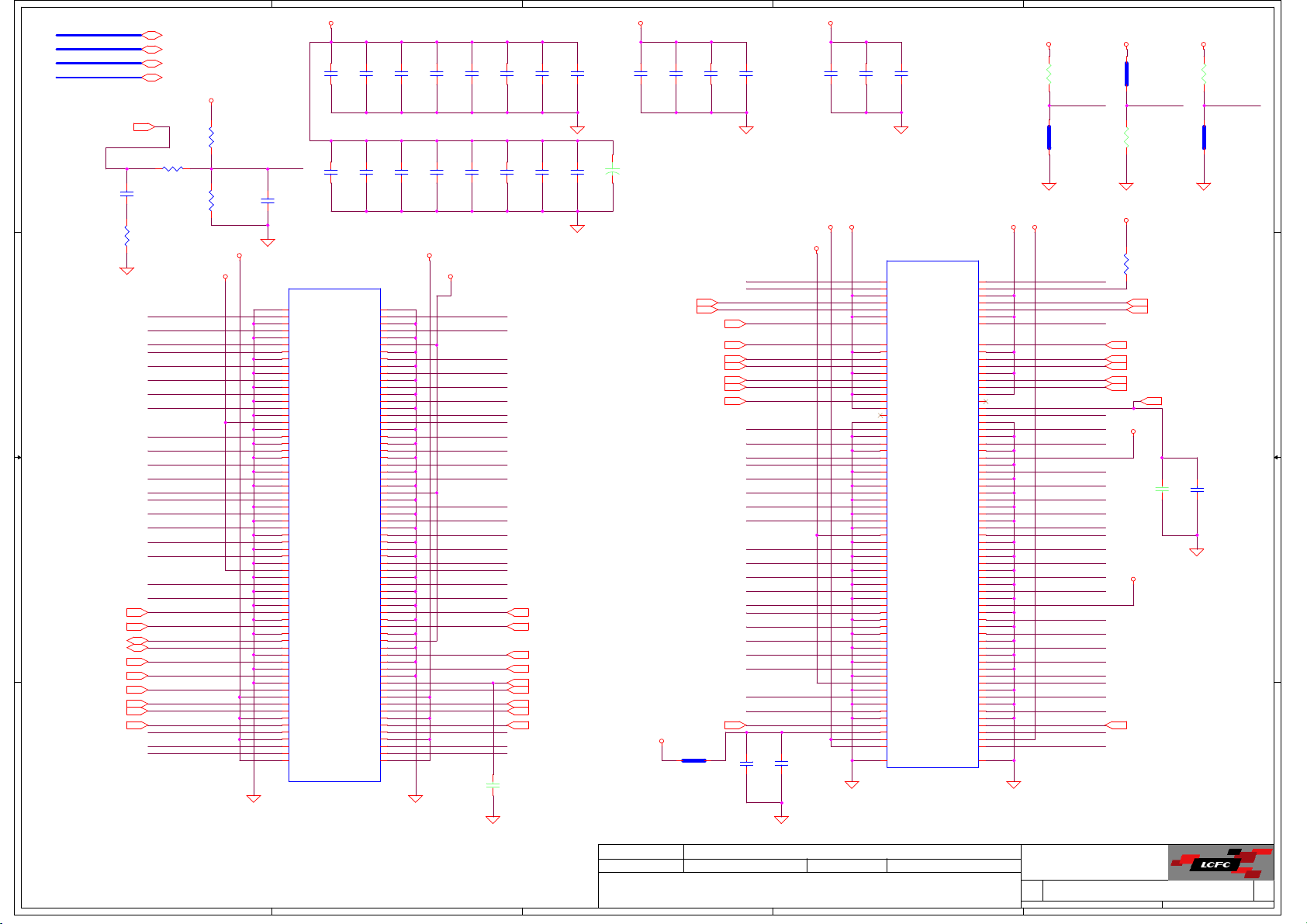

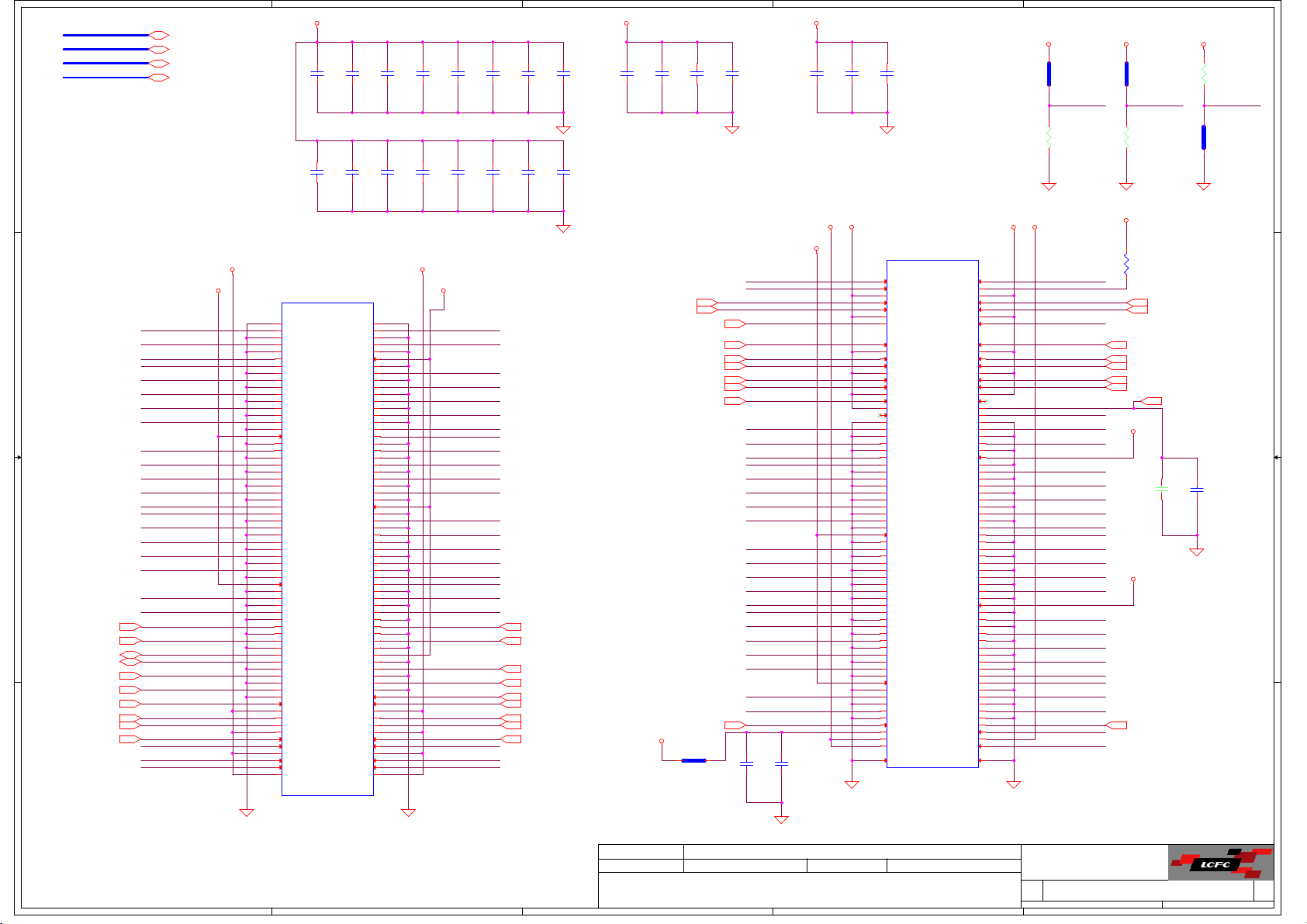

LCD CONN

eDP 17.3"

FHD/QFHD

45

Thunderbolt

46-51

PCI Expre ss x4

USB2.0 CH2

USB3.0 CH2

USB2.0 CH1

USB3.0 CH1

USB2.0 CH3

USB2.0 CH4

USB3.0 CH4

USB2.0 CH5

USB3.0 CH5

USB2.0 CH6

USB3.0 CH6

USB2.0 CH14

USB2.0 CH8

USB2.0 CH10

USB2.0 CH11

USB2.0 CH12

SPI Flash TBT

4Mbits (U15)

HDMI Conn.

D D

TBT-PWR SW

/USB Type-C

(port 1)

TBT-PWR SW

/USB Type-C

(port 2)

C C

B B

52

53

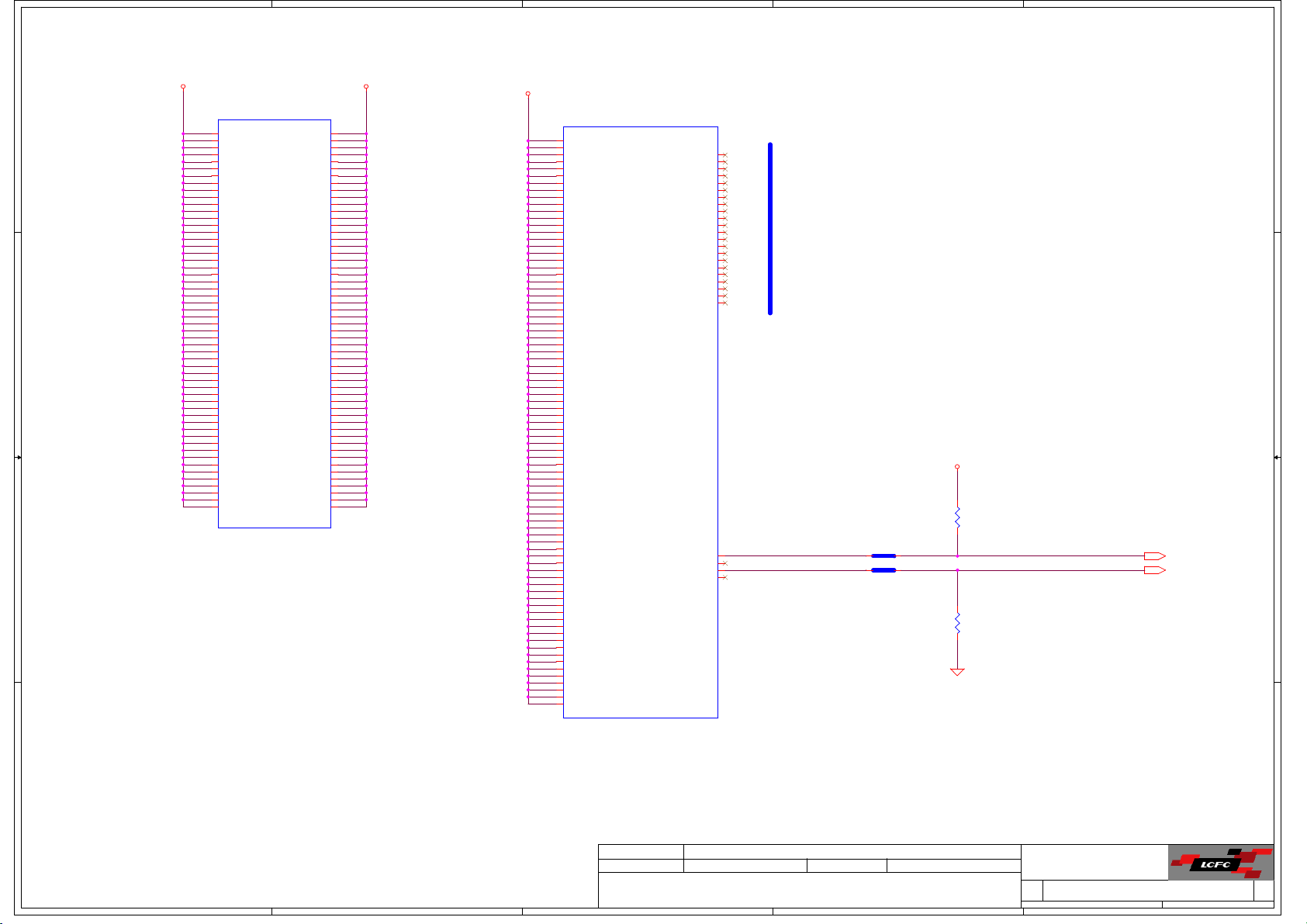

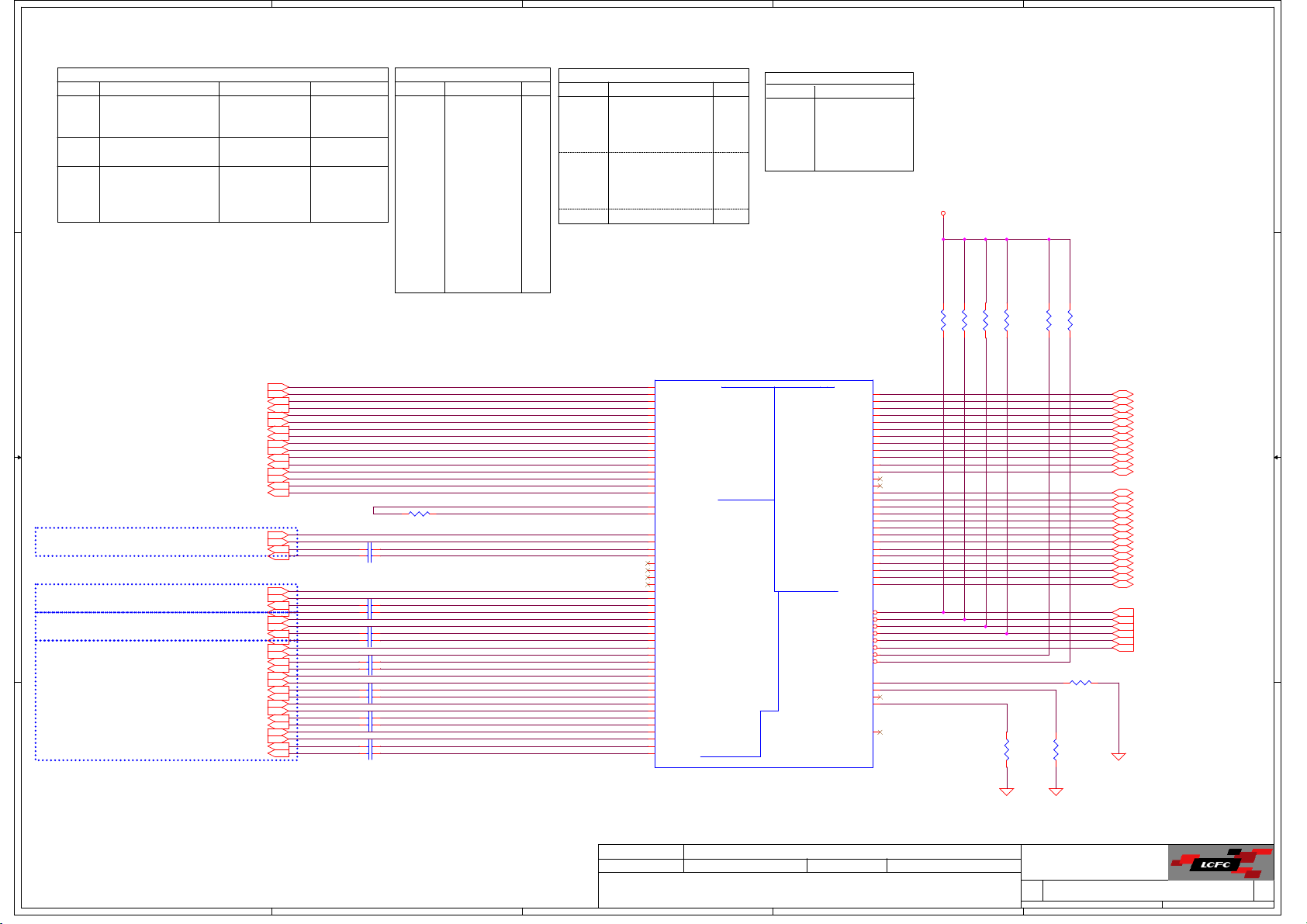

USB3.0

CONN (USB2)

USB3.0

AOU (USB1)

USB2.0 M.2

WWAN Slot

USB3.0

Docking

USB3.0

CONN (USB3)

USB3.0

CONN (USB4)

USB2.0 M.2

WLAN Slot (BT)

USB2.0 2D

Camera

USB2.0

Touch Panel

USB2.0

Smart Card Slot

USB2.0

Express Slot

Right

54

Left

54

61

74

Right

54

Right

54

61

40

40

64

64

eDPx4

42

46

DPx4

DPx4

Mini DisplayPort

DisplayPort

(Docking)

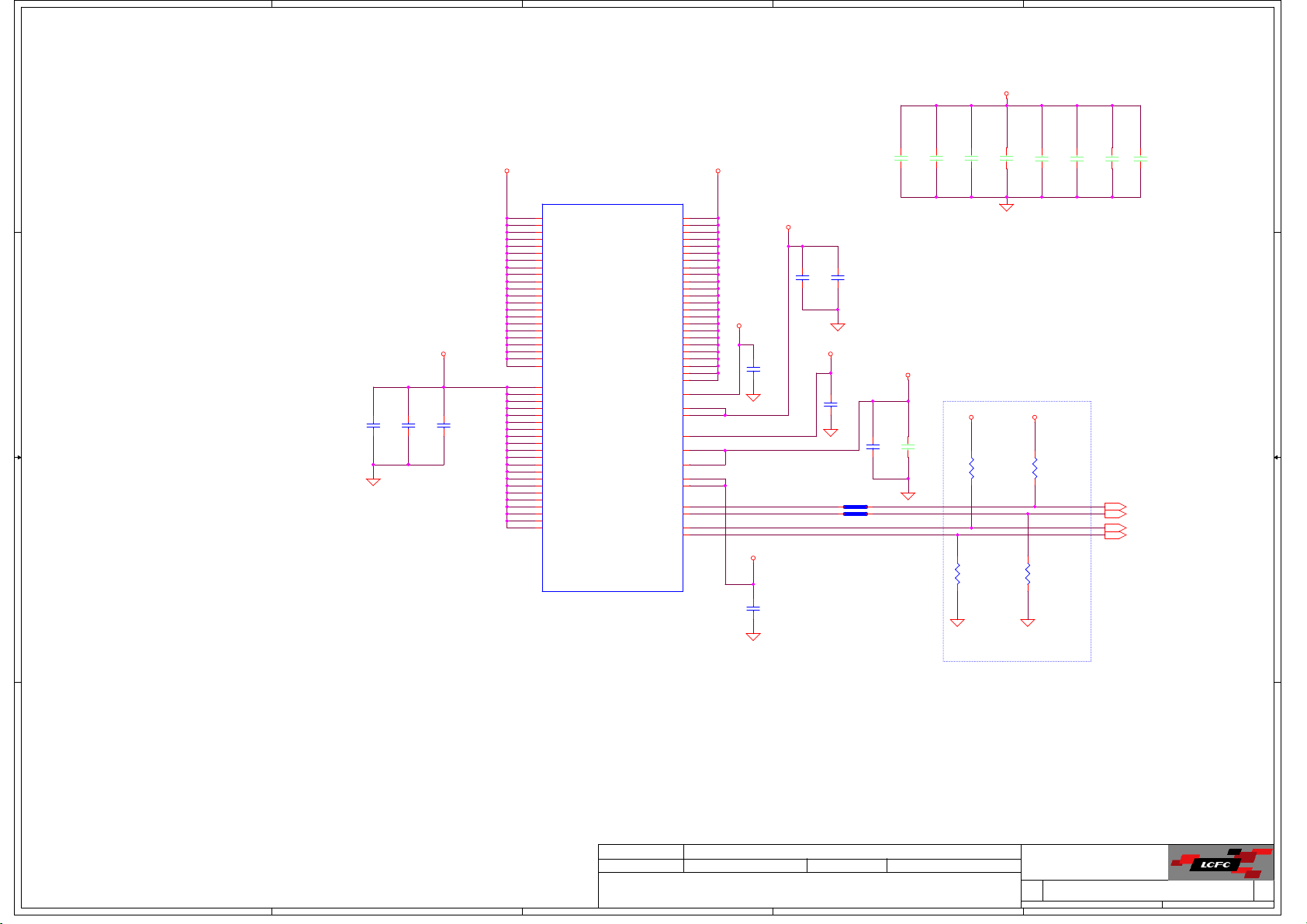

HDD CONN

SSD

ODD CONN

M.2 SLOT

SSD

M.2 SLOT

SSD

Optane Memory

RTC Battery

FAN

G-Sensor

LED for Camera

LED for ThinkPad Logos

USB2.0

Port 9

A

Fingerprint

Reader

USB2.0

Port 13

Color

Sensor

54

5

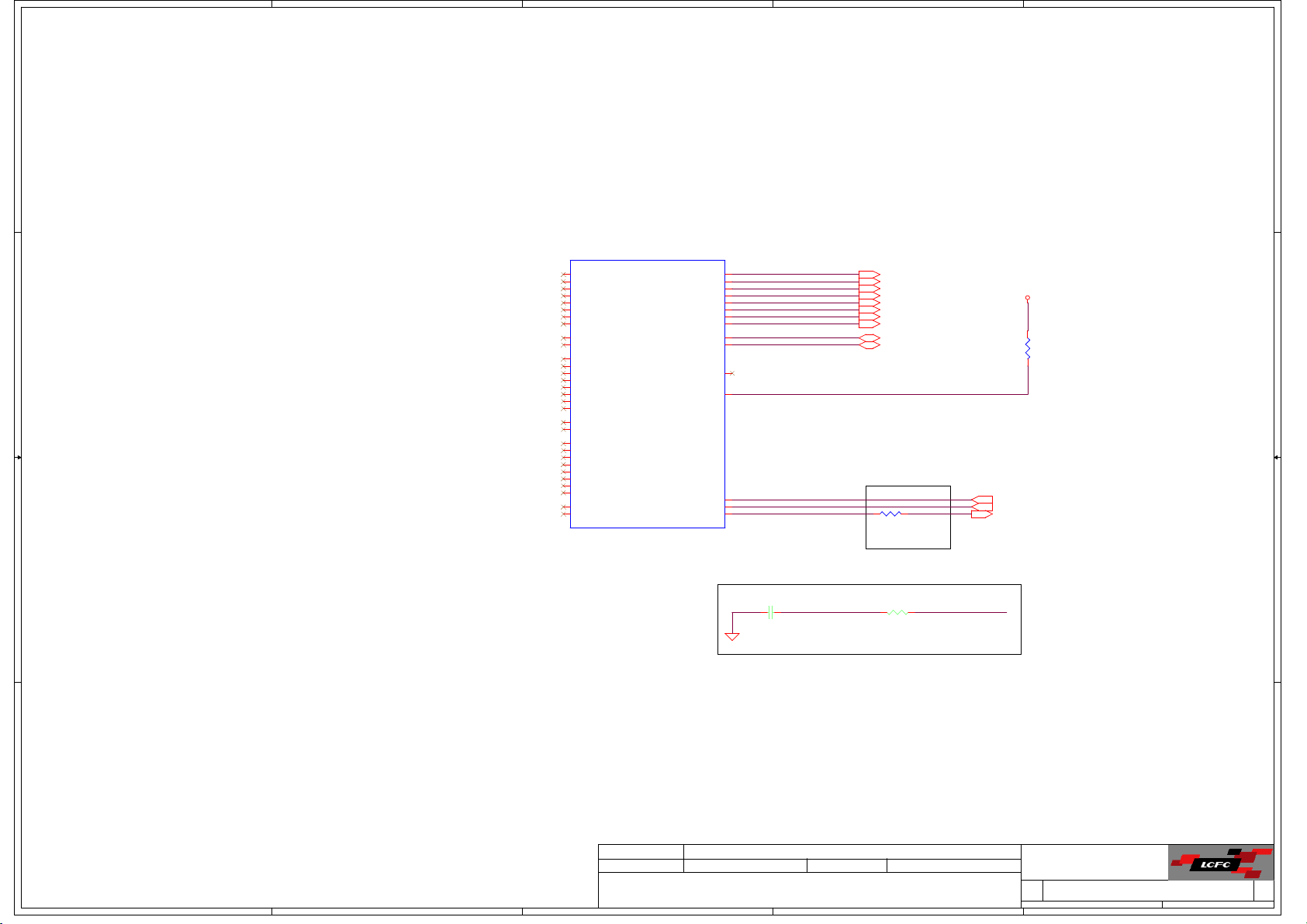

SM Bus

ClickPad

40

eDP

Mux

eDPx4

dGPU MXM

NVIDIA

N17M-Q3

N17EQ1/Q3//Q5

31

44

74

USB x 12 p orts

65

66

60

60

25

80

81

Thermal Sensor

PECI 3.0

SMB-MB/SB

CS15 Keyboard with

Numpad

41

eDPx4

PEG-16X

GEN3

DP Mux

SATA x4

CH2

CH3

CH0

CH4

Antenna

43

15

16

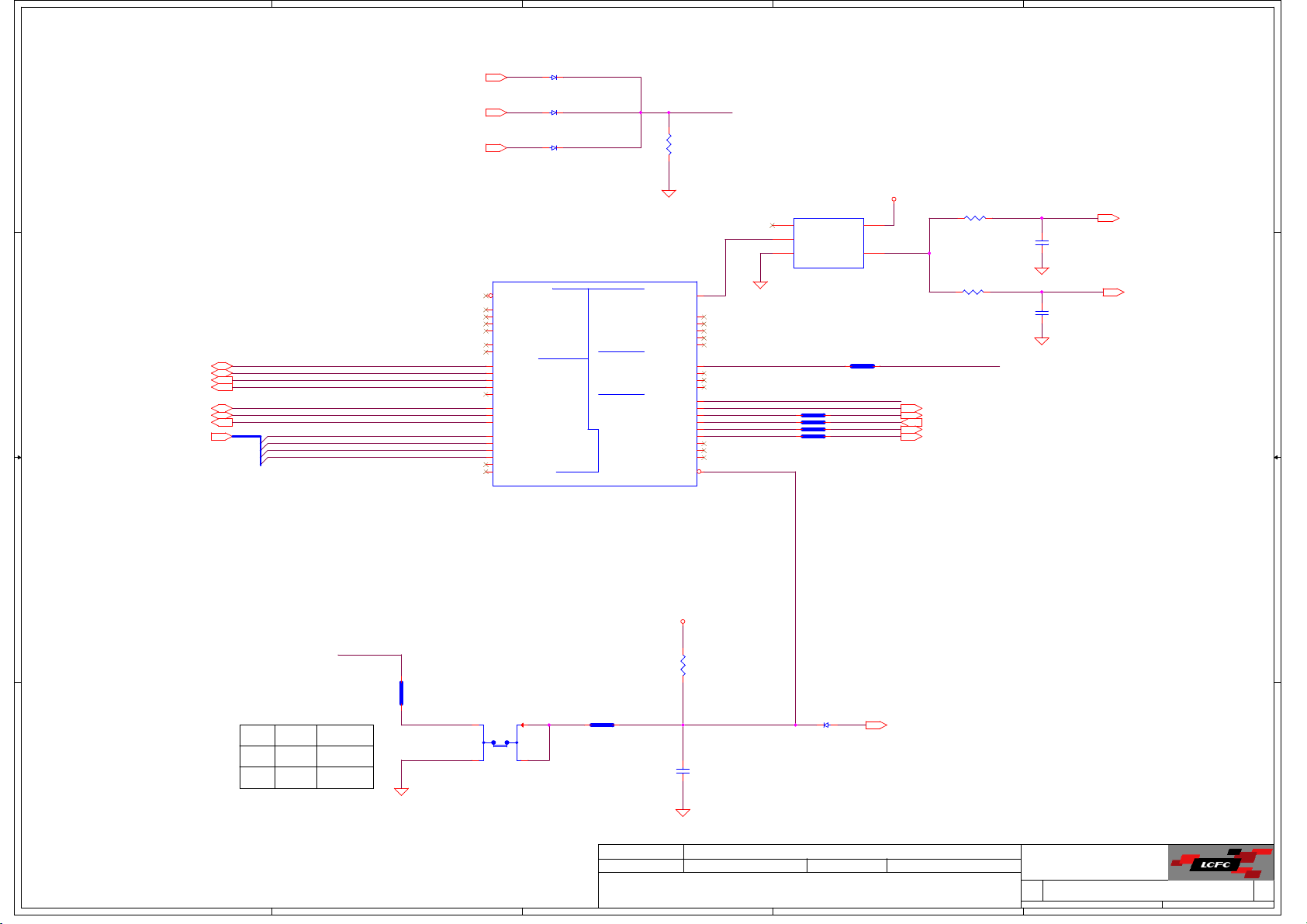

Embedded

Controller

MEC1653

4

Channel A

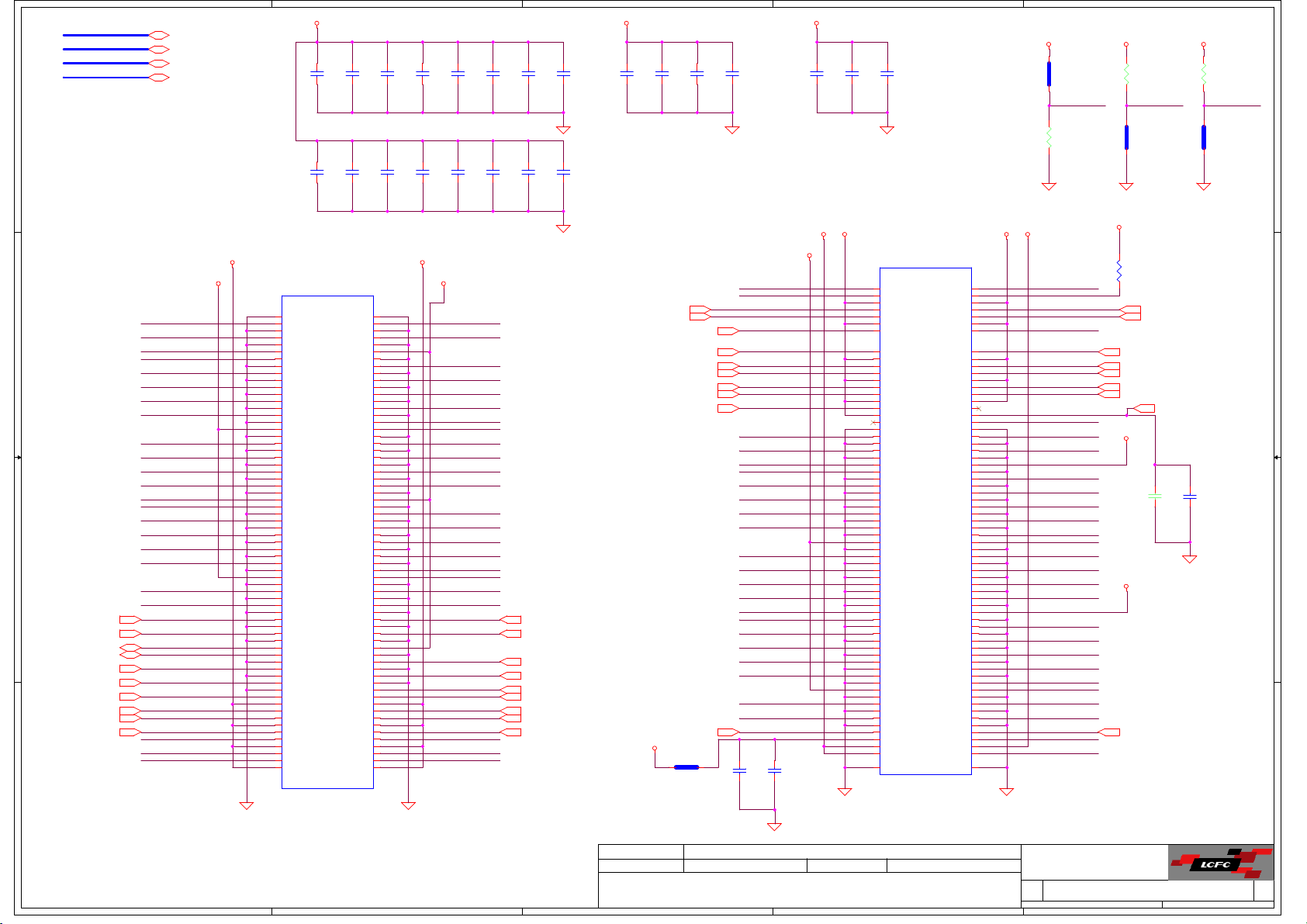

CPU

Intel

Kabylake_H

BGA1440

45W

3,4,5,6,7,8,9,10,11,12,13

DMI x4

DDR4 2400 MHz

SM Bus_B

Channel B

DDR4 2400 MHz

SM Bus_B

PCH

C-Link

Intel

Kabylake-H

vPro

14,15,16,17,18

19,20,21,22,23

LPC Bus 33MHz

75,76,77 84,85

Power Button

Subcard

7879

4

54

PCI Expre ss x7 ports

HDA

TPM 2.0

Lenovo

ASIC

ThinkEngine

USB Port 8

SM Bus

82

DDR4 / 1.2V

UNBUFFERED

DDR4

SO-DIMMA1

UNBUFFERED

DDR4

SO-DIMMB1

CPU XDP

SPI Flash

64Mbits

(SPI1)

Camera

Subcard

3

27 28

29

24

26

Stereo

Speaker

71

Microphone

Headphone

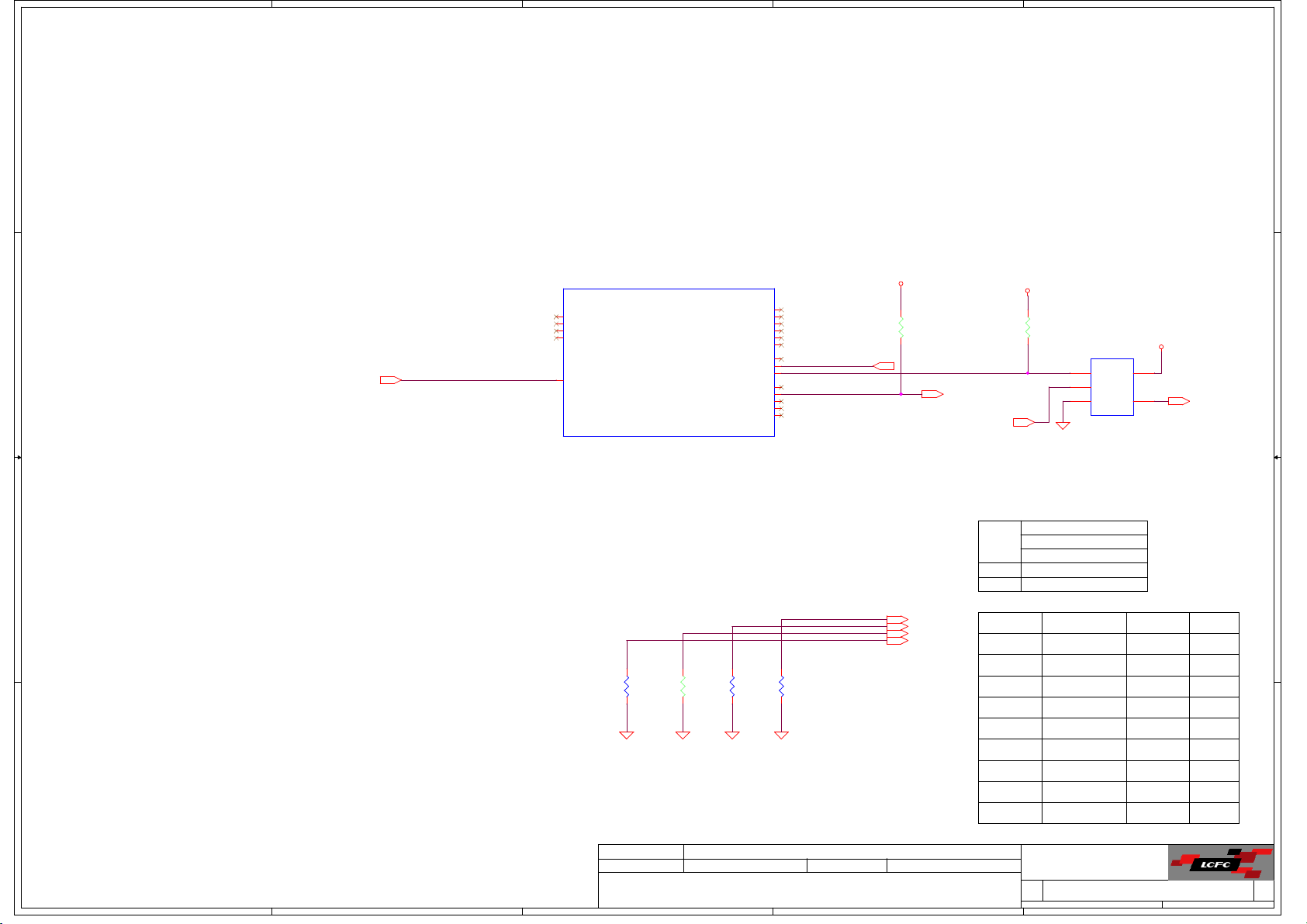

I/O SubCard Interface

USB 2.0 P8

SATA P3

LED for ThinkPad Logos

Security Cla ssification

Security Classi fication

Security Classi fication

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

40

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY LC FUTURE CENTE R NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY LC FUTURE CENTE R NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY LC FUTURE CENTE R NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

UNBUFFERED

DDR4

SO-DIMMA2

UNBUFFERED

DDR4

SO-DIMMB2

ALC3268 HDA

CODEC

Audio

(Docking)

67,68

68

Audio

Combo Jack

2

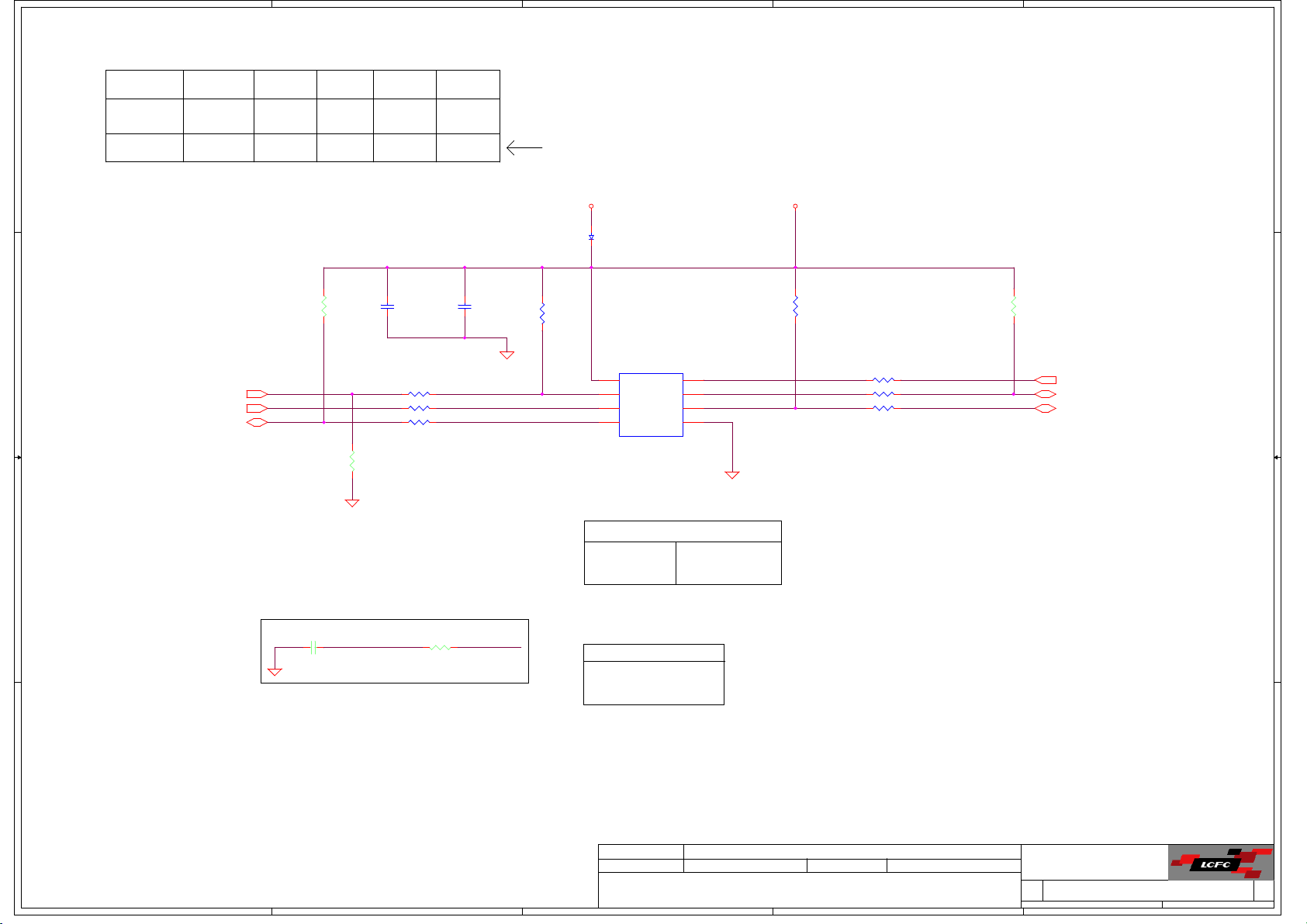

PY-Note Block Diagram

Project Code:

PCB(Raw Card):

Wireless LAN

30

Antenna

(M.2 WLAN Card)

Bluetooth

Type-A M.2 Card

USB

Port 14

Multi-Media

Controller

RTS5234s

67 62 64 56

I2S

74 40

AC-DC IN

Camera-(USB2)/LID SW

ODD Sub Card

LED for ThinkPad Logo

On A cover

2015/07/16

2015/07/16

2015/07/16

(UHS-II)

Internal

Mic

SD/MMC

Card Slot

DC/DC

Converter

40

40

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

I2C

DP710

1.0

61

Port 3

(X1)

M.2 SLOT

SSD

Port 13

(X1)

Express

Card Slot

63

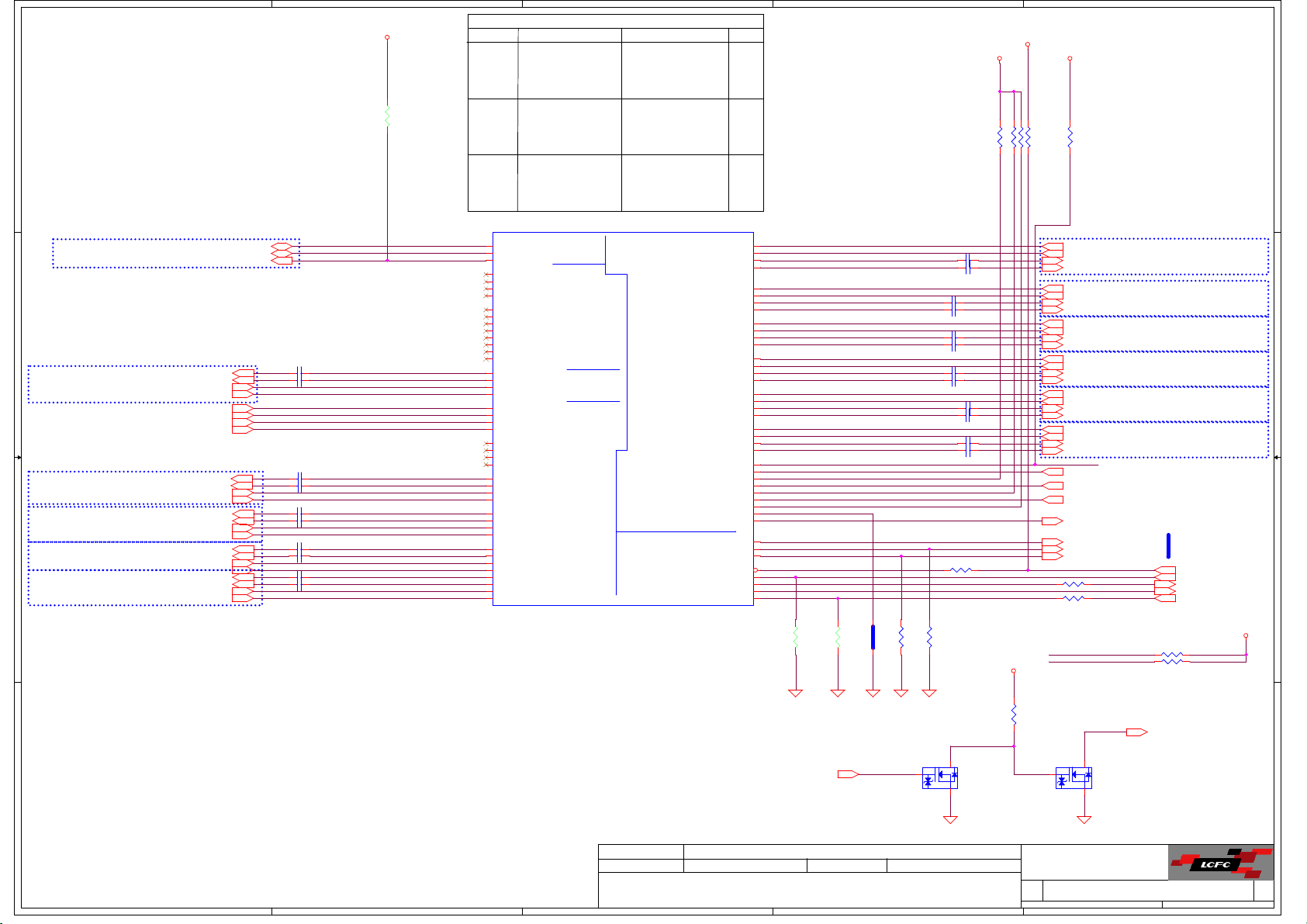

Main

86

Battery

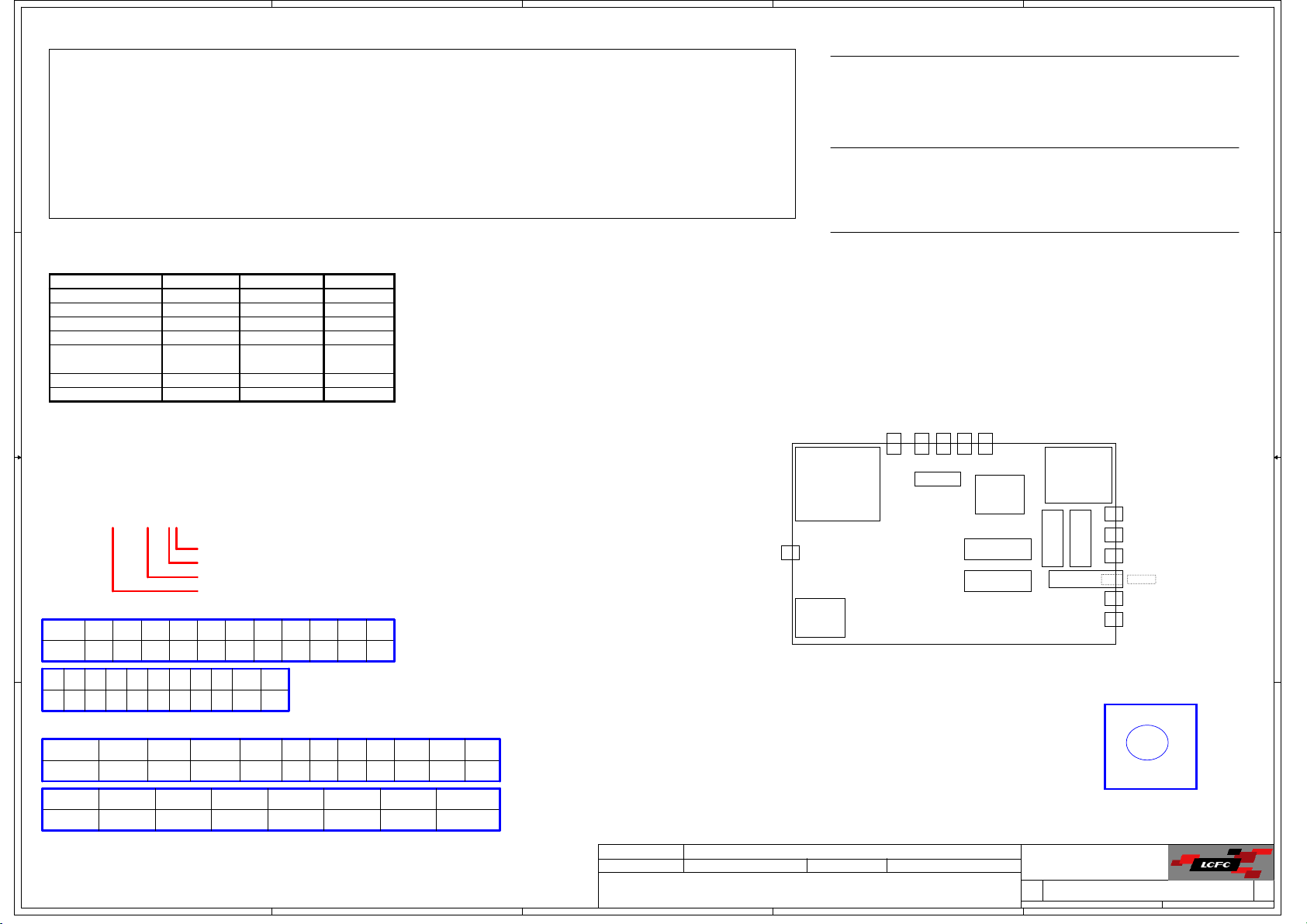

External Connector/Socket

Internal Connector/Socket

Internal Switch

2

SIM Card

Slot

60 60

Port 11

(X1)

Port 1

(X1)

Intel GbE PHY

JACKSONVILLE

88

2016/01/16

2016/01/16

2016/01/16

Type-B M.2 Card

1

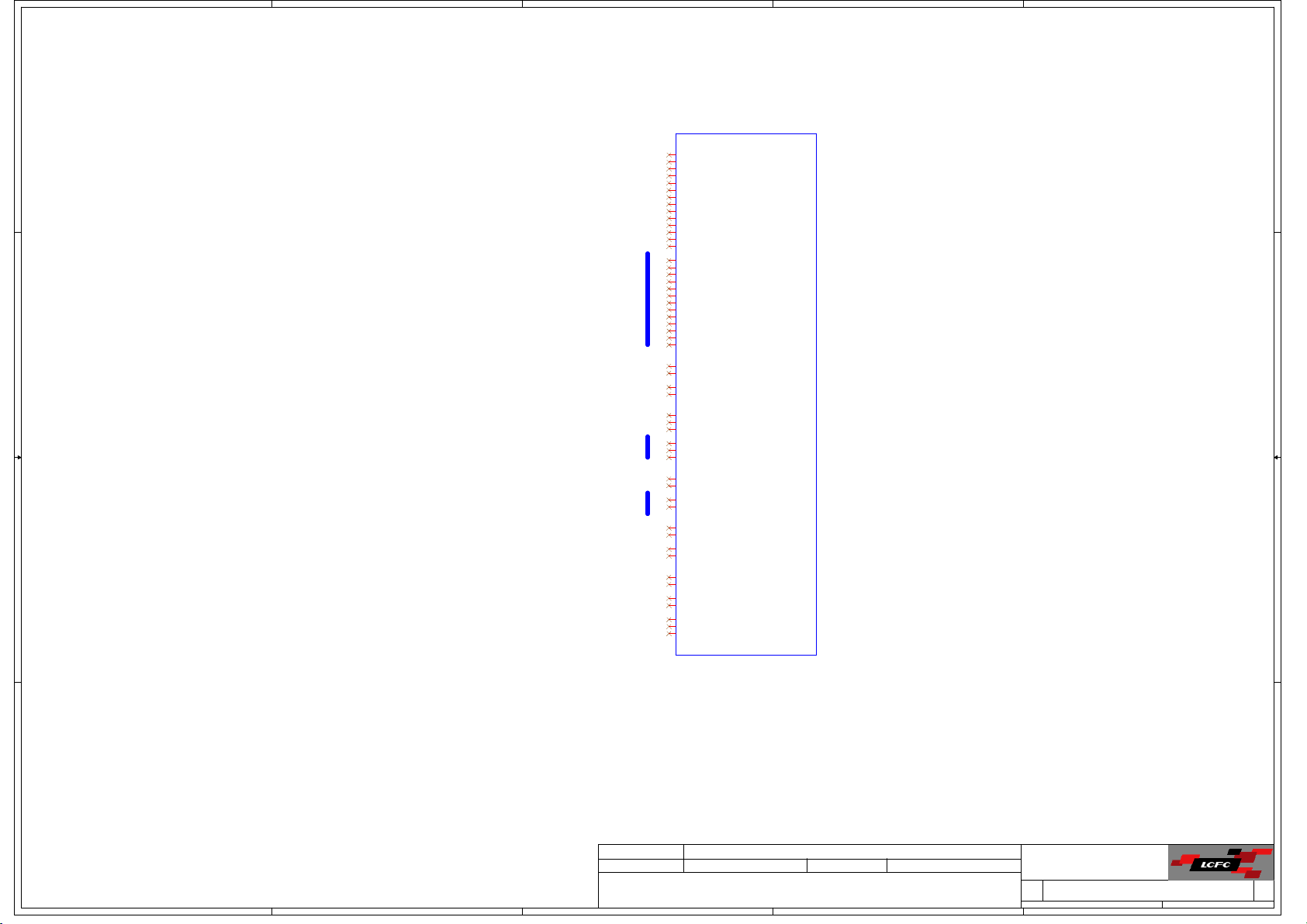

PCB Layer Stackup

L1:TOP

L2:GND

L3:Signal

L4:PWR

Wireless WAN

Antenna

L5:Signal

L6:Signal

L7:GND

L8:Signal

L9:GND

(M.2 WWAN Ca rd)

61

USB

Port 3

M.2 SLOT

SSD

Port 19

(X1

Thunderbolt

Port 4

(X1)

61

L10:BOTTOM

Battery Charger

BQ24780SRUYR

DOCK_PWR20 M-BAT-PWR

System DC/DC

TPS51285BRUKR

VINT20

CPU DC/DC

M: NCP81205 MNTXG

S: NCP81382MNTXG

VINT20

VCCCPUIO

NB681GD-C623-Z

VCC5M

VCC1R0_SUS

TPS51362RVER

VCC5M

VCC1R2A /VCC0R6 B

+SMDDR_VREF_DIMM

LAN

MUX

57

MAGNETICS

RJ45

58,59

Docking

TPS51716RUKR

VINT20

VCC1R8B

BD9B300MUV-E2

VCC5M

VCC2R5A

BD91364AMUU-Z E2

VCC5M VCC2R5A

VCCOPC/VC CEOPIO (44e)

NB681GD-C623-Z

NB681GD-C623-Z

VCC5M VCCOPC

VCC5M VCCEOPIO

VCCGTX (44e)

NCP81210MNTXG

VINT20 VCCGTX

Title

Title

Title

TITLE PAGE

TITLE PAGE

TITLE PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

1

88

OUTPUTSINPUTS

90

VCC5M

VCC3M

91

92,93,94

VCCCPUCORE

VCCGFXCORE_I

VCCSA

95

VCCCPUIO

96

VCC1R0_SUS

99

+SMDDR_VREF_DIMM

VCC0R6B

VCC1R2A

98

VCC1R8B

100

101

103

102

of

of

of

1111

1111

1111

0.1

0.1

0.1

A

5

4

3

2

1

TABLE: SYSTEM POWER STATE

Power state to be determined

D D

Schematics Mark Definition

BOM Structure 4+2 CPU

@

EMC@

RF@

C C

ME@

PRxxx,PCxxx,

PLxxx

42@

44e@

NO ASM

ASM

ASM

ASM

ASM

ASM

NO ASM

Any other mark like below is prohibited on Payton/Walter.

ESD@,EMI@,EMC_NS@,EMC_PX@,EMC_OPT@,CONN@,

4+4e CPU Note

NO ASM

ASM

ASM

ASM

ASM

NO ASM

EMC

RF

ME

Power

4+2 CPU

4+4e CPUASM

EC SMBus0 address

Device

Smart Battery

Addres s

0001 011X b

EC SMBus2 address

Device Address

Charge Controller

0001 0010

PCH SM Bus address

CH-A P

CH-A S

CH-B P

CH-B S

DDR DIMM0

DDR DIMM1

DDR DIMM2

DDR DIMM3

Addres sDevice

1001 0000b

1001 0001b

1001 0010b

1001 0011b

EC SMBus1 address

Device Address

G-Senor (LIS3DH)

G-Senor (KX023)

0011 000Xb

0011 110Xb

EC SMBus10 address

Device

Master VGA

Addres s

0x9E

PCH SM Bus0 address

Device

Intel Lan_I2 19

Addres s

0XC8

TABLE: SYSTEM COMPONENT PLACEMENT (AS OF 2014 Dec 8)

DCIN TBT-ATBT-BHDMIRJ45

CONN_NS@... RH,CH,LH(PCH related RLC)..

GPU FAN

Capacitor Naming Note

Ceramic Capacitors:

(FAN2)

DOCK

CPU

0.1U_0402_6.3VXX

Tolerance

B B

Temperature Characteristics

Rated Voltage

Package Size

Temperature Characteristics:

Symbol

Code Z5VZ5U Y5UZ5P Y5PY5V

01 32547698A

X5R NPOX7R X6SCOG

USBP1

(AOU)

DIMM

DIMM

SMARTCARD

CPU FAN

(FAN1)

M.2 SSD1

EXPRESSCARD

M.2 SSD2

mDP

USBP2

USBP5

SD CARD

USBP6

AUDIO

B

CFEDHGKJI

CJCHBJ SJSHCK UJ X5SSLUK

L

NOJ

Tolerance:

Symbol

A

Symbol P Q ZXV YS

AB DCGFJHMKN

+-0.05PF

5

+-0.25PF+-0.1PF +-1%+-0.5PF

+30,-10%+100,-0%Tolerance

+-2% +-3%Tolerance +-10%+-5% +-30%+-20%

+40,-20%+20,-10% +50,-20%+80,-20%

PCB_MB

XXX

PCB NM-B121

DAA00007D00

A

-30% ~ 10%

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

Blank

Blank

Blank

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

of

2111

2111

2111

0.1

0.1

0.1

5

4

3

2

1

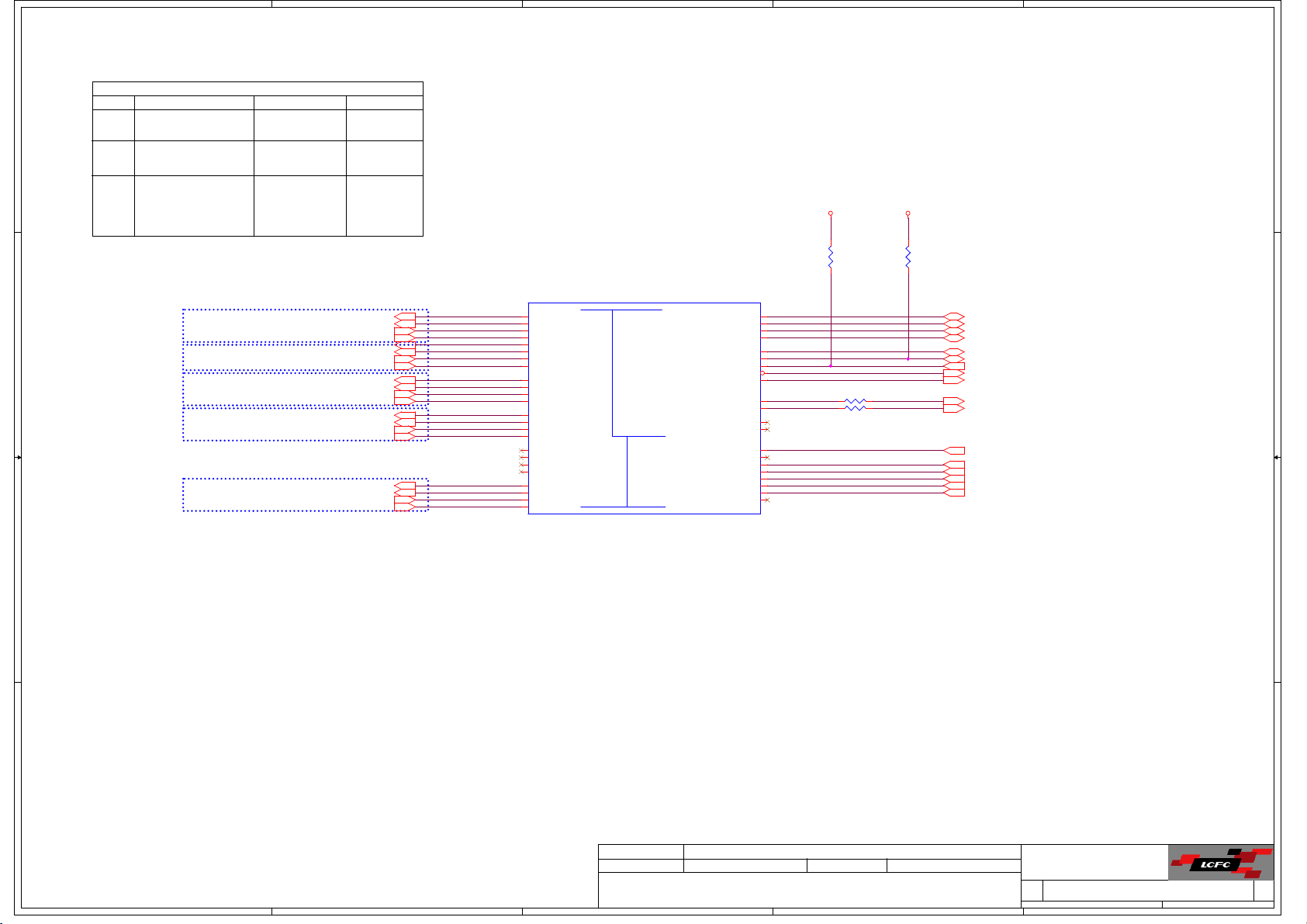

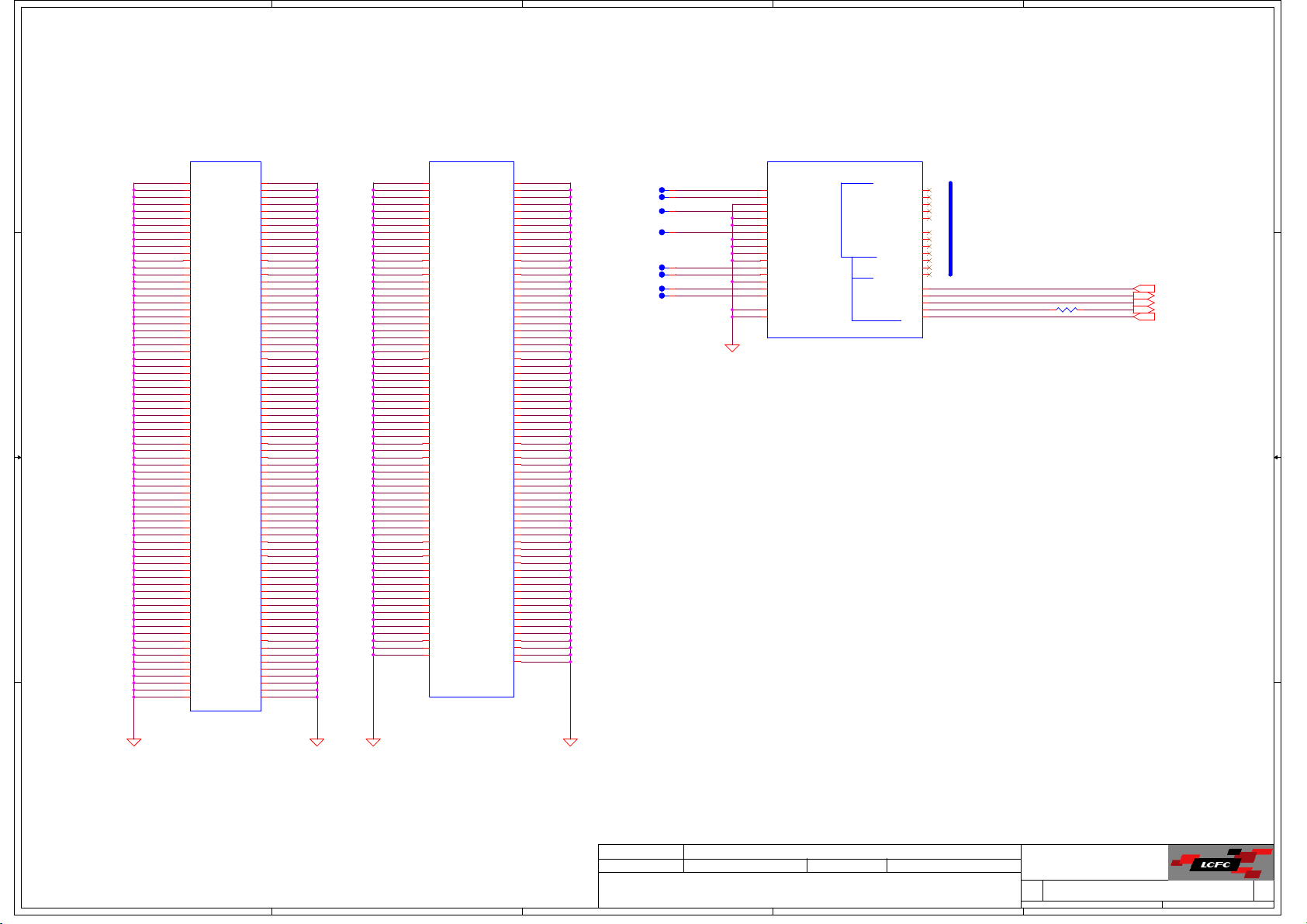

D D

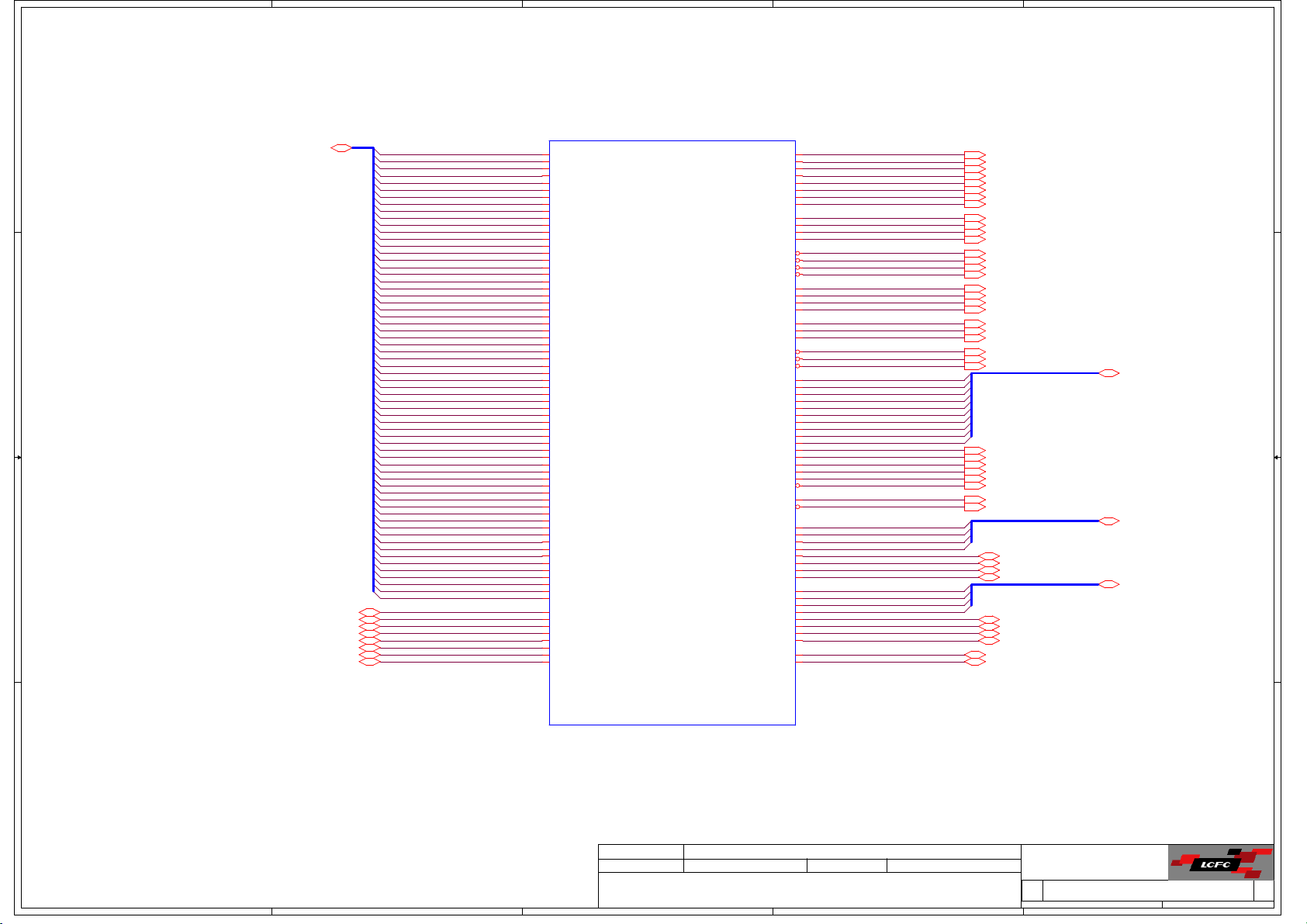

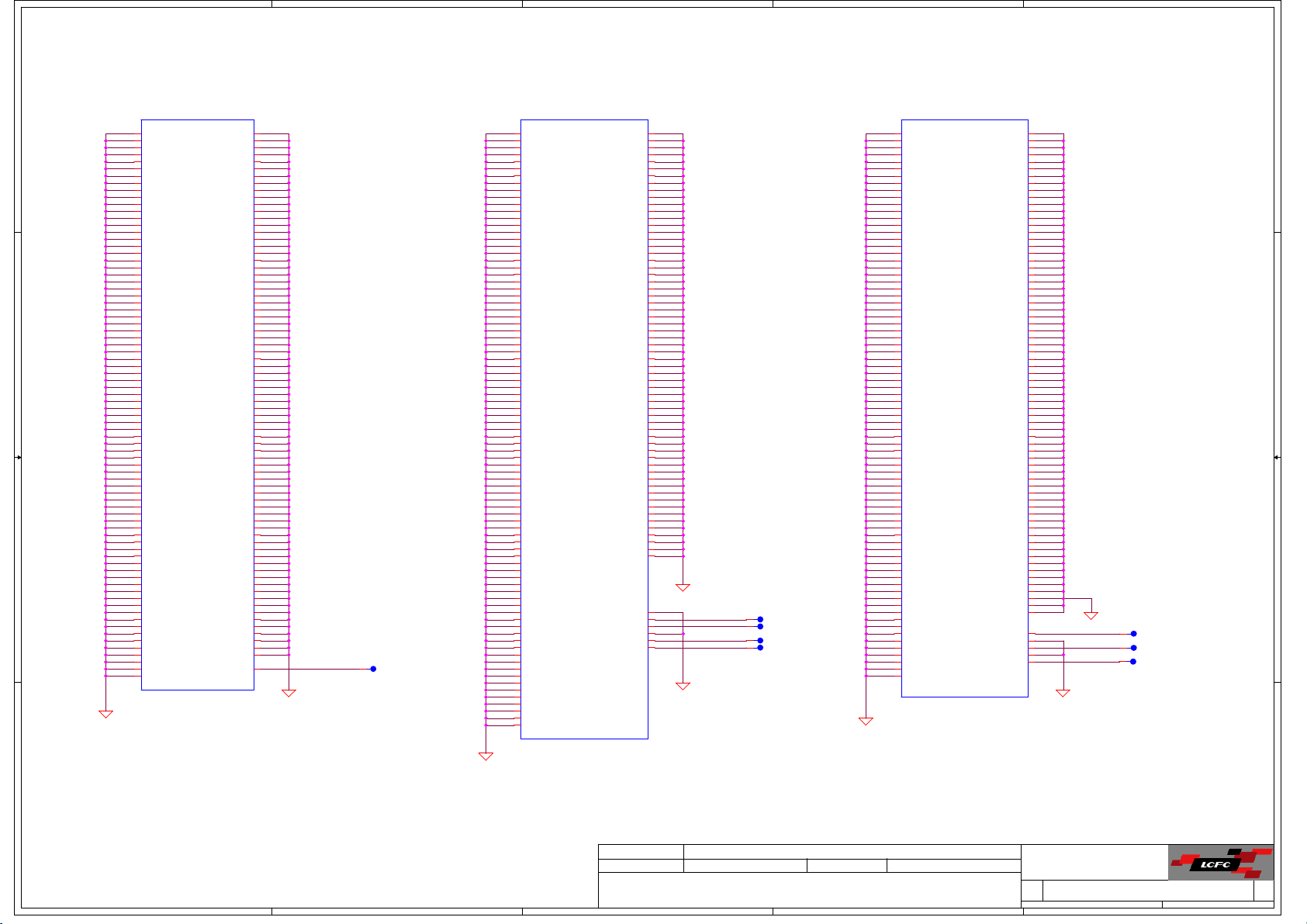

M_A_DQ[0..63]27,28

C C

B B

M_A_CB027,28

M_A_CB127,28

M_A_CB227,28

M_A_CB327,28

M_A_CB427,28

M_A_CB527,28

M_A_CB627,28

M_A_CB727,28

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_CB0

M_A_CB1

M_A_CB2

M_A_CB3

M_A_CB4

M_A_CB5

M_A_CB6

M_A_CB7

U1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

SKYLAKE_HALO

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

M_A_DDRCLK0_1066M

-M_A_DDRC LK0_1066M

-M_A_DDRC LK1_1066M

M_A_DDRCLK1_1066M

M_A_DDRCLK2_1066M

-M_A_DDRC LK2_1066M

M_A_DDRCLK3_1066M

-M_A_DDRC LK3_1066M

M_A_CKE0

M_A_CKE1

M_A_CKE2

M_A_CKE3

-M_A_CS0

-M_A_CS1

-M_A_CS2

-M_A_CS3

M_A_ODT0

M_A_ODT1

M_A_ODT2

M_A_ODT3

M_A_BA0

M_A_BA1

M_A_BG0

M_A_A16_RAS_N

M_A_A14_WE_N

M_A_A15_CAS_N

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10_AP

M_A_A11

M_A_A12

M_A_A13

M_A_BG1

-M_A_ACT

M_A_PARITY

-M_A_ALERT

-M_A_DQS0

-M_A_DQS1

-M_A_DQS2

-M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

-M_A_DQS4

-M_A_DQS5

-M_A_DQS6

-M_A_DQS7

M_A_DQS8

-M_A_DQS8

M_A_DDRCLK0_1066M 27

-M_A_DDRC LK0_1066M 27

-M_A_DDRC LK1_1066M 27

M_A_DDRCLK1_1066M 27

M_A_DDRCLK2_1066M 28

-M_A_DDRC LK2_1066M 28

M_A_DDRCLK3_1066M 28

-M_A_DDRC LK3_1066M 28

M_A_CKE0 27

M_A_CKE1 27

M_A_CKE2 28

M_A_CKE3 28

-M_A_CS0 27

-M_A_CS1 27

-M_A_CS2 28

-M_A_CS3 28

M_A_ODT0 27

M_A_ODT1 27

M_A_ODT2 28

M_A_ODT3 28

M_A_BA0 27,28

M_A_BA1 27,28

M_A_BG0 27,28

M_A_A16_RAS_N 27,28

M_A_A14_WE_N 27,28

M_A_A15_CAS_N 27,28

M_A_A10_AP 27,28

M_A_A11 27,28

M_A_A12 27,28

M_A_A13 27,28

M_A_BG1 27,28

-M_A_ACT 27,28

M_A_PARITY 27,28

-M_A_ALERT 27,28

M_A_DQS4 27,28

M_A_DQS5 27,28

M_A_DQS6 27,28

M_A_DQS7 27,28

-M_A_DQS4 2 7,28

-M_A_DQS5 2 7,28

-M_A_DQS6 2 7,28

-M_A_DQS7 2 7,28

M_A_DQS8 27,28

-M_A_DQS8 27,2 8

M_A_A[0..9] 27,28

-M_A_DQS[0..3] 27,28

M_A_DQS[0..3] 27,28

DDR CHANNEL

A

SKYLAKE-H-CPU_BGA1440

1 OF 14

DDR4 INTERLEAVE IMPLEMENTATION

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : DDR4 CH-A

CPU SKL-H : DDR4 CH-A

CPU SKL-H : DDR4 CH-A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet of

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

3111

3111

3111

A

0.1

0.1

0.1

5

4

3

2

1

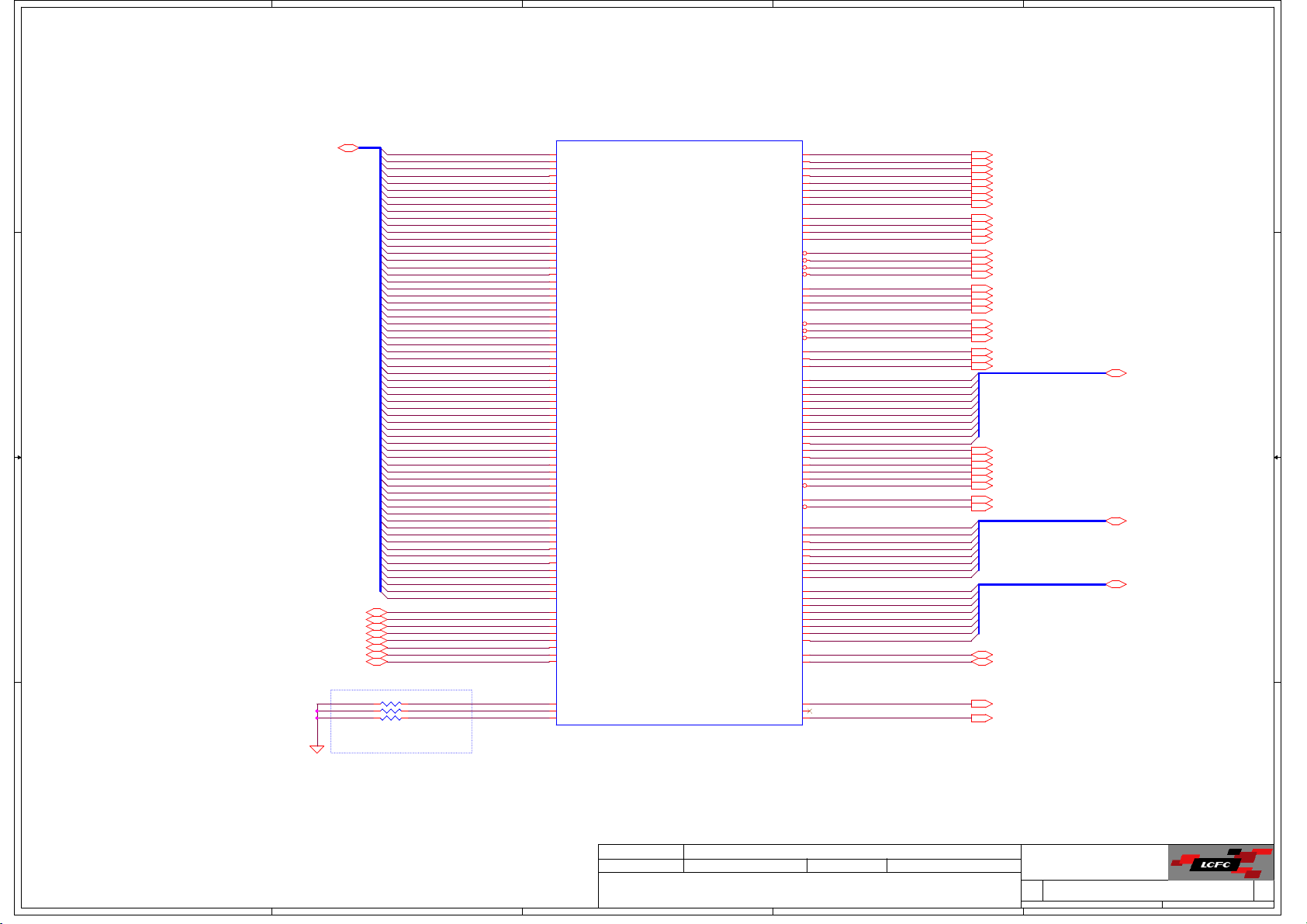

D D

M_B_DQ[0..63]29,30

C C

B B

M_B_CB029,30

M_B_CB129,30

M_B_CB229,30

M_B_CB329,30

M_B_CB429,30

M_B_CB529,30

M_B_CB629,30

M_B_CB729,30

1

2

R543 121_0402_1%

2

R544 75_0402_1%

R545 100_0402_1%

1

1

2

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_CB0

M_B_CB1

M_B_CB2

M_B_CB3

M_B_CB4

M_B_CB5

M_B_CB6

M_B_CB7

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

PLACE CLOSE TO CPU

U1B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKYLAKE-H-CPU_BGA1440

DDR CHANNEL B

SKYLAKE_HALO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

M_B_DDRCLK0_1066M

-M_B_DDRC LK0_1066M

-M_B_DDRC LK1_1066M

M_B_DDRCLK1_1066M

M_B_DDRCLK2_1066M

-M_B_DDRC LK2_1066M

M_B_DDRCLK3_1066M

-M_B_DDRC LK3_1066M

M_B_CKE0

M_B_CKE1

M_B_CKE2

M_B_CKE3

-M_B_CS0

-M_B_CS1

-M_B_CS2

-M_B_CS3

M_B_ODT0

M_B_ODT1

M_B_ODT2

M_B_ODT3

M_B_A16_RAS_N

M_B_A14_WE_N

M_B_A15_CAS_N

M_B_BA0

M_B_BA1

M_B_BG0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10_AP

M_B_A11

M_B_A12

M_B_A13

M_B_BG1

-M_B_ACT

M_B_PARITY

-M_B_ALERT

-M_B_DQS0

-M_B_DQS1

-M_B_DQS2

-M_B_DQS3

-M_B_DQS4

-M_B_DQS5

-M_B_DQS6

-M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS8

-M_B_DQS8

M_A_VREF_CA_CPU

M_B_VREF_DQ_CPU

M_B_DDRCLK0_1066M 29

-M_B_DDRC LK0_1066M 29

-M_B_DDRC LK1_1066M 29

M_B_DDRCLK1_1066M 29

M_B_DDRCLK2_1066M 30

-M_B_DDRC LK2_1066M 30

M_B_DDRCLK3_1066M 30

-M_B_DDRC LK3_1066M 30

M_B_CKE0 29

M_B_CKE1 29

M_B_CKE2 30

M_B_CKE3 30

-M_B_CS0 29

-M_B_CS1 29

-M_B_CS2 30

-M_B_CS3 30

M_B_ODT0 29

M_B_ODT1 29

M_B_ODT2 30

M_B_ODT3 30

M_B_A16_RAS_N 29,30

M_B_A14_WE_N 29,30

M_B_A15_CAS_N 29,30

M_B_BA0 29,30

M_B_BA1 29,30

M_B_BG0 29,30

M_B_A10_AP 29,30

M_B_A11 29,30

M_B_A12 29,30

M_B_A13 29,30

M_B_BG1 29,30

-M_B_ACT 29,30

M_B_PARITY 29,30

-M_B_ALERT 29,30

M_B_DQS8 29,30

-M_B_DQS8 29,3 0

M_A_VREF_CA_CPU 27

M_B_VREF_DQ_CPU 29

M_B_A[0..9] 29,30

-M_B_DQS[0..7] 29,30

M_B_DQS[0..7] 29,30

DDR_VREF_CA: Connected to VREF_CA on DIMM CH-A

DDR0_VREF_DQ: NC

A

DDR1_VREF_DQ: Connected to VREF_CA on DIMM CH-B

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : DDR4 CH-B

CPU SKL-H : DDR4 CH-B

CPU SKL-H : DDR4 CH-B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

of

4111

4111

4111

0.1

0.1

0.1

5

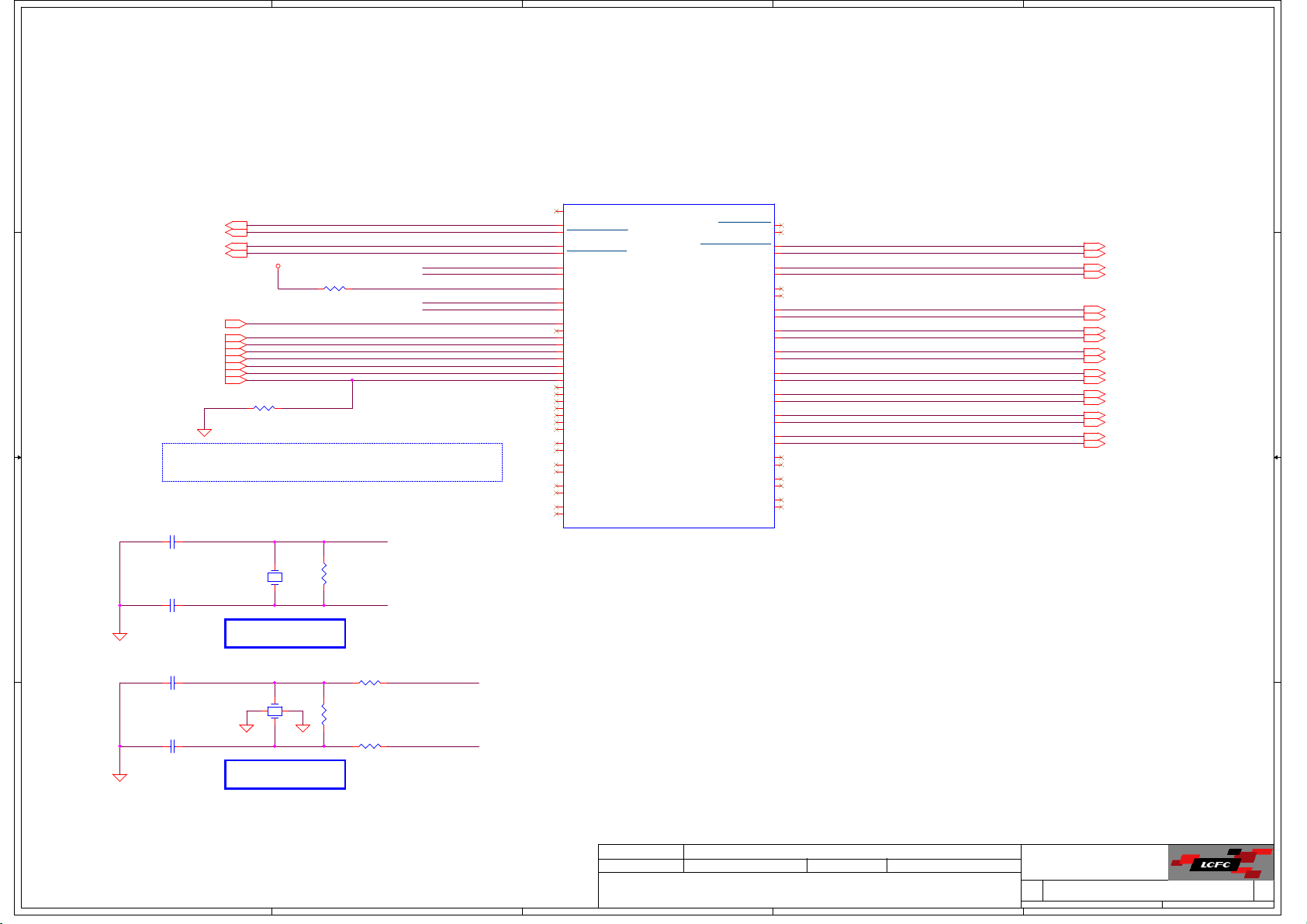

D D

4

3

2

1

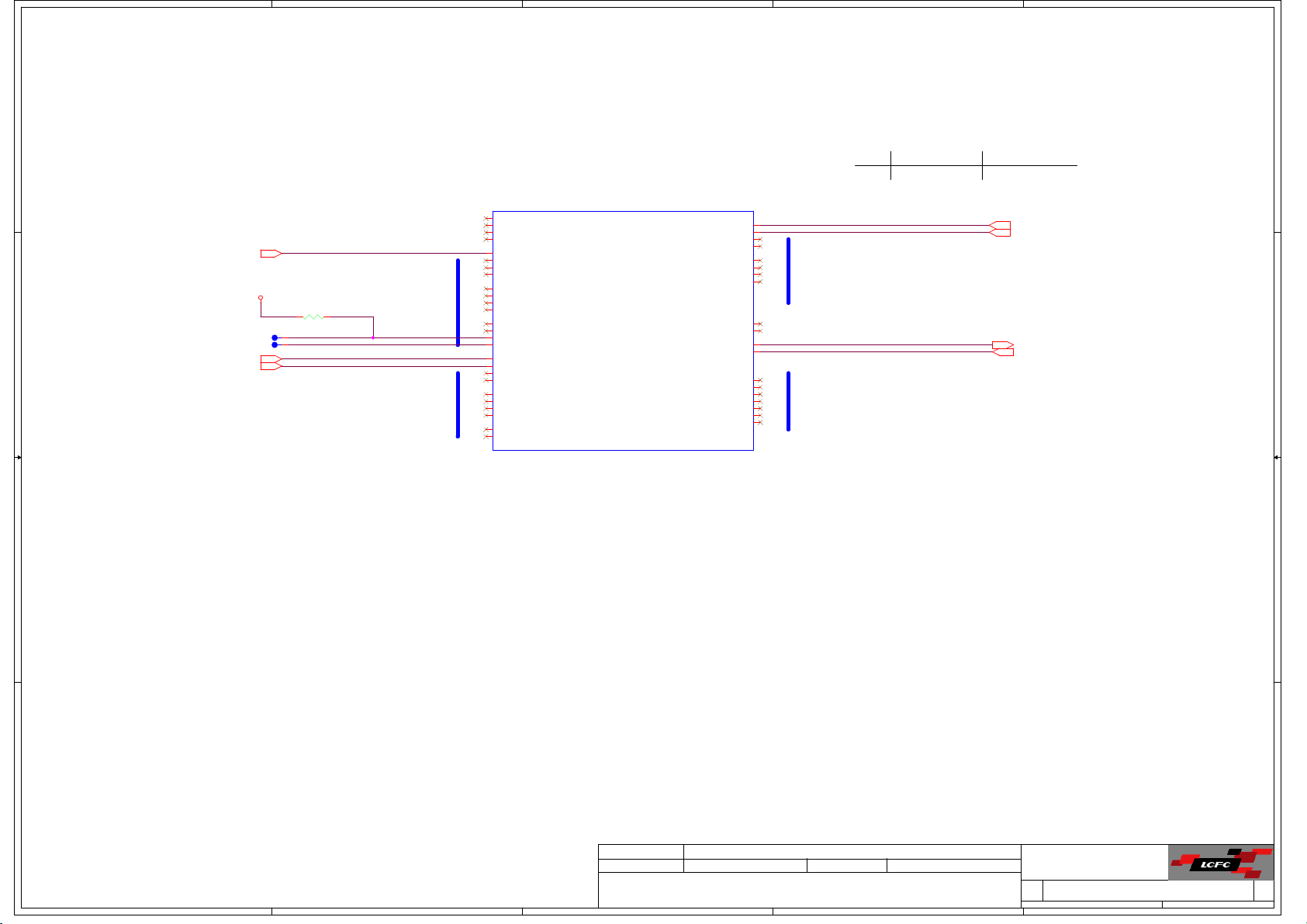

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

SKYLAKE_HALO

BGA1440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

DMI_RXP0 15

DMI_RXN0 15

DMI_RXP1 15

DMI_RXN1 15

DMI_RXP2 15

DMI_RXN2 15

DMI_RXP3 15

DMI_RXN3 15

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

PEG_TXP0 31

PEG_TXN0 31

PEG_TXP1 31

PEG_TXN1 31

PEG_TXP2 31

PEG_TXN2 31

PEG_TXP3 31

PEG_TXN3 31

PEG_TXP4 31

PEG_TXN4 31

PEG_TXP5 31

PEG_TXN5 31

PEG_TXP6 31

PEG_TXN6 31

PEG_TXP7 31

PEG_TXN7 31

PEG_TXP8 31

PEG_TXN8 31

PEG_TXP9 31

PEG_TXN9 31

PEG_TXP10 31

PEG_TXN10 31

PEG_TXP11 31

PEG_TXN11 31

PEG_TXP12 31

PEG_TXN12 31

PEG_TXP13 31

PEG_TXN13 31

PEG_TXP14 31

PEG_TXN14 31

PEG_TXP15 31

PEG_TXN15 31

U1C

VCCCPUIO

DMI_TXP015

DMI_TXN015

DMI_TXP115

DMI_TXN115

DMI_TXP215

DMI_TXN215

DMI_TXP315

DMI_TXN315

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_RXP4

PEG_RXN4

PEG_RXP5

PEG_RXN5

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

R1

1

24.9_0402_1%

PEG_COMP_W12mil

2

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

PEG_RXP031

PEG_RXN031

PEG_RXP131

PEG_RXN131

PEG_RXP231

PEG_RXN231

PEG_RXP331

PEG_RXN331

PEG_RXP431

PEG_RXN431

PEG_RXP531

PEG_RXN531

PEG_RXP631

C C

B B

PEG_RXN631

PEG_RXP731

PEG_RXN731

PEG_RXP831

PEG_RXN831

PEG_RXP931

PEG_RXN931

PEG_RXP1031

PEG_RXN1031

PEG_RXP1131

PEG_RXN1131

PEG_RXP1231

PEG_RXN1231

PEG_RXP1331

PEG_RXN1331

PEG_RXP1431

PEG_RXN1431

PEG_RXP1531

PEG_RXN1531

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

SKYLAKE-H-CPU_BGA1440

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : PEG/DMI

CPU SKL-H : PEG/DMI

CPU SKL-H : PEG/DMI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet of

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

5111

5111

5111

A

0.1

0.1

0.1

5

D D

4

3

2

1

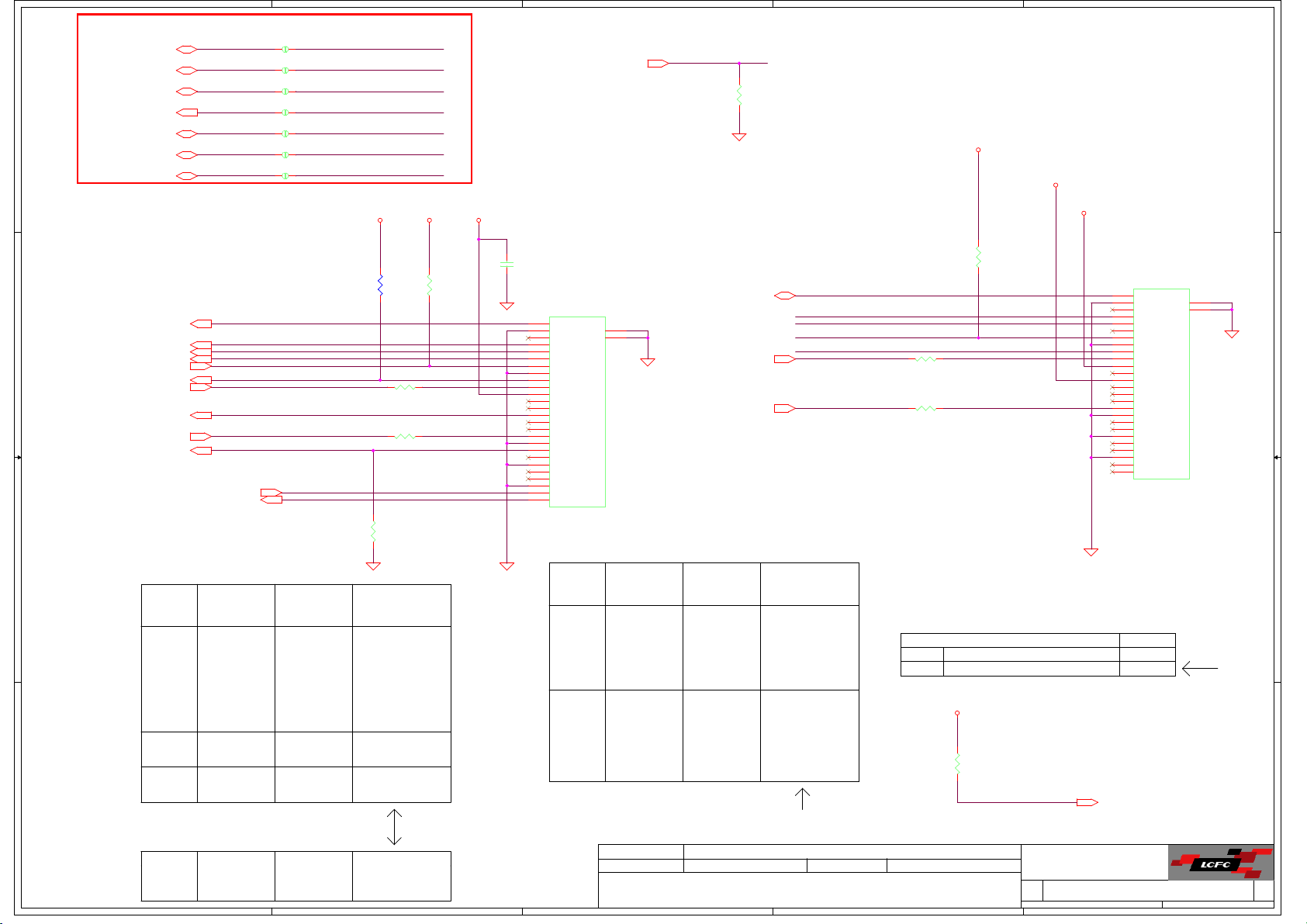

U1D

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

C C

B B

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

SKYLAKE-H-CPU_BGA1440

SKYLAKE_HALO

BGA1440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

EDP_TXP0_I

D29

EDP_TXN0_I

E29

EDP_TXP1_I

F28

EDP_TXN1_I

E28

EDP_TXN2_I

B29

EDP_TXP2_I

A29

EDP_TXN3_I

B28

EDP_TXP3_I

C28

EDP_AUXP_I

C26

EDP_AUXN_I

B26

A33

Leave EDP_DISP_UTIL NC

EDP_RCOMP_W20mil

D37

PROC_AUDIO_CLK_CPU

G27

PROC_AUDIO_SDO_CPU

G25

PROC_AUDIO_SDI_CPU_R

G29

2

1

C455

@

10P_0402_50V8-J

For EMC

EDP_TXP0_I 41

EDP_TXN0_I 41

EDP_TXP1_I 41

EDP_TXN1_I 41

EDP_TXN2_I 41

EDP_TXP2_I 41

EDP_TXN3_I 41

EDP_TXP3_I 41

EDP_AUXP_I 41

EDP_AUXN_I 41

1

2

R3 20_0402_1%

PLACE NEAR CPU

1 2

R638

@

33_0402_5%

PROC_AUDIO_CLK_CPU

VCCCPUIO

1

R2

24.9_0402_1%

2

PROC_AUDIO_CLK_CPU 17

PROC_AUDIO_SDO_CPU 17

PROC_AUDIO_SDI_CPU 17

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : DDI/EDP

CPU SKL-H : DDI/EDP

CPU SKL-H : DDI/EDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet of

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

6111

6111

6111

A

0.1

0.1

0.1

5

VCC3M

2

VCC1R2A

D D

C C

PROCPWRGD From PCH to CPU

RESET# From PCH to CPU

B B

CPUCORE_ON101,102,103,84,91

VCCST_PWRGD requirements (546884_SKL_H_PDG_Rev0_71)

1) Indication that the VCCST/VDDQ power supplies are stable and within specification.

(Table 41-1)

A

2) VCCST_PW RGD must go low during Sx pwr states, regardless of the voltage level of VCCST.

(Figure 41-1 Note 1)

3) VCCST_PW RGD should be equal or ealier than PCH_PW ROK.

(Table 41-5, tCPU16. See also 543016_SKL_PDG_UY_1_0)

4) VCCST_PW RGD is typically made from ALL_SYS_PWRGD

(CPUCORE_ON/VR_ON for CPU DCDC), not PCH_PWROK (CPUCORE_PWRGD).

(Figure 41-1)

1

1

2

3

2

1

5

VCC3B

R659

100K_0402_5%

@

Q55

DTC115TMT2L_VMT3

@

DDR_PG_CTRL

R77

10K_0402_5%

@

CPUCORE_ON

2

R774

100K_0402_5%

1

DDR_VTT_PG_CTRL

1

NC

2

A

2

G

VCC1R2A

1

5

U36

0.1U_0402_16V7-K

4

VCC3

Y

GND

SN74AUP1G07DCKR_SC-70

CPU_BCLK_100M20

-CPU_BCLK_ 100M20

CPU_PCI_BCLK_100M20

-CPU_PCI_BC LK_100M20

CPU_REFCLK_24M20

-CPU_REFCL K_24M20

-SVID_ALERT102,91

SVID_CLK102,91

SVID_DATA102,91

-PROCHOT102,76,91

PROCPWRGD_CPU17

-PCH_PLTRS T_PROC16

VCC3_SUS

2

R19

10K_0402_5%

1

1

D

Q1

LSK3541G1ET2L_VMT3

S

3

C709

2

VCCST_PWRGD VCCST_PWRGD_R

PM_SYNC16

PM_DOWN16

PECI16,76

-THERMTRIP16

Q1_Q2_R19

4

DDR_VTT_PG_CTRL 99

-SVID_ALERT

SVID_CLK

SVID_DATA

-PROCHOT

DDR_PG_CTRL

R14 220_0402_5%

R772 0_0402_5%

R773 0_0402_5%

R15 499_0402_1%

2

R586 60.4_0402_1%

1

R16 0_0402_5%

VCCST

R78

@

10K_0402_5%

VCC1R0_SUS

R20

@

10K_0402_5%

1 2

1

D

2

G

Q2

LSK3541G1ET2L_VMT3

S

3

4

1

1

1

1 2

1

2

12

VCCST

2

1

U36

TI

Supplier PN

SN74AUP1G07DCKR

NXP 74AUP1G07GW SA00007GU00

U1E

B31

BCLKP

A32

BCLKN

D35

PCI_BCLKP

C36

PCI_BCLKN

E31

CLK24P

D31

CLK24N

2

2

2

R1057

1K_0402_5%

-SVID_ALERT_ R

SVID_CLK_R

SVID_DATA_R

-PROCHOT_R

PROCPWRGD_CPU

-PCH_PLTRS T_PROC_R

Leave as NC

CPU_CATERR#

If VC CSTG is used inst ead of VCC1R0 _SUS,

VCCST_PWR GD will be off in sleep S0 bec ause

VCCSTG ma y be turned off when in sleep S0.

Currently, VCCSTG is still on in sleep S0,

but we may change logic to turn off VCCSTG in sleep S0.

(CT_20141216)

VCCST_PWRGD

BH31

VIDALERT#

BH32

VIDSCK

BH29

VIDSOUT

BR30

PROCHOT#

BT13

DDR_VTT_CNTL

H13

VCCST_PWRGD

BT31

PROCPWRGD

BP35

RESET#

BM34

PM_SYNC

BP31

PM_DOWN

BT34

PECI

J31

THERMTRIP#

BR33

SKTOCC#

BN1

PROC_SELECT#

BM30

CATERR#

SKYLAKE-H-CPU_BGA1440

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

SKYLAKE_HALO

BGA1440

3

5 OF 14

LCFC PN

SA00007F700

-SVID_ALERT

SVID_CLK

SVID_DATA

-PROCHOT

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

2015/07/16

2015/07/16

2015/07/16

2

R6

100_0402_5%

12

R9

1K_0402_1%

@

XDP_TDO 24

XDP_TDI 24

XDP_TMS 24

XDP_TCK 24

-XDP_TRST 24

-XDP_PREQ 24

-XDP_PRDY 24

VCCSTG

1 2

R7

1K_0402_1%

1

R10

1K_0402_1%

@

2

12

LOGIC

VCCST

2

DCI@

R18

51_0402_1%

1 2

LOGIC

LOGIC

R5

100_0402_5%

@

1

CFG3 24

2

R297

51_0402_1%

@

1

LOGIC

1 2

12

R8

1K_0402_1%

@

R4

56_0402_5%

1 2

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

BL32

BP28

BR28

BP30

BL30

BP27

BT25

CFG0

CPU_CFG1

CPU_CFG8

CPU_CFG9

CPU_CFG10

CPU_CFG11

CPU_CFG12

CPU_CFG13

CPU_CFG14

CPU_CFG15

CPU_CFG17

CPU_CFG16

CPU_CFG19

CPU_CFG18

CFG_RCOMP

TABLE

CFG[0] : Stall reset sequence after CPU PLL lock until de-asserted:

1 : No Stall

0 : Stall

CFG[2] : PEG Static Lane Reversal

1 : Normal Operation

0 : Lane Reversal

CFG[4] : eDP enable

1 : Disabled

0 : Enabled

CFG[6:5] : PEG Bifurcation, bus#:dev#:func#=0:1:0

11 : 1x16

CFG[7] : PEG Training

1 : PEG Train immediately following RESET# deassertion

0 : PEG Wait for BIOS for training

1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

IST_TRIG

CPU_BPM1

CPU_BPM2

CPU_BPM3

TP53 Test_Point_32MIL

1

TP37 Test_Point_32MIL

1

TP38 Test_Point_32MIL

1

TP39 Test_Point_32MIL

1

TP40 Test_Point_32MIL

1

TP41 Test_Point_32MIL

1

TP42 Test_Point_32MIL

1

TP43 Test_Point_32MIL

1

TP44 Test_Point_32MIL

1

TP45 Test_Point_32MIL

1

TP46 Test_Point_32MIL

1

TP47 Test_Point_32MIL

1

TP48 Test_Point_32MIL

1

1

1

1

2

R17

49.9_0402_1%

1

TP49 Test_Point_32MIL

TP50 Test_Point_32MIL

TP51 Test_Point_32MIL

TP52 Test_Point_32MIL

CFG[19:0] pin has internal Pull up to VCCCPUIO with 5-8 k ohm.

LOGIC

CFG[19:8] : Reserved

Title

Title

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : MISC/CLK/JTAG/ CFG

CPU SKL-H : MISC/CLK/JTAG/ CFG

CPU SKL-H : MISC/CLK/JTAG/ CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet of

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

R11

1K_0402_1%

1

12

R12

1K_0402_1%

@

7111

7111

7111

1

R13

1K_0402_1%

@

2

of

of

0.1

0.1

0.1

A

5

4

3

2

1

SKYLAKE_HALO

D D

C C

B B

U1F

Y38

VSS_1

Y37

VSS_2

Y14

VSS_3

Y13

VSS_4

Y11

VSS_5

Y10

VSS_6

Y9

VSS_7

Y8

VSS_8

Y7

VSS_9

W34

VSS_10

W33

VSS_11

W12

VSS_12

W5

VSS_13

W4

VSS_14

W3

VSS_15

W2

VSS_16

W1

VSS_17

V30

VSS_18

V29

VSS_19

V12

VSS_20

V6

VSS_21

U38

VSS_153

U37

VSS_22

U6

VSS_23

T34

VSS_24

T33

VSS_25

T14

VSS_26

T13

VSS_27

T12

VSS_28

T11

VSS_29

T10

VSS_30

T9

VSS_31

T8

VSS_32

T7

VSS_33

T5

VSS_34

T4

VSS_35

T3

VSS_36

T2

VSS_37

T1

VSS_38

R30

VSS_39

R29

VSS_40

R12

VSS_41

P38

VSS_42

P37

VSS_43

P12

VSS_44

P6

VSS_45

N34

VSS_46

N33

VSS_47

N12

VSS_48

N11

VSS_49

N10

VSS_50

N9

VSS_51

N8

VSS_52

N7

VSS_53

N6

VSS_54

N5

VSS_55

N4

VSS_56

N3

VSS_57

N2

VSS_58

N1

VSS_59

M14

VSS_60

M13

VSS_61

M12

VSS_62

M6

VSS_63

L34

VSS_64

L33

VSS_65

L30

VSS_66

L29

VSS_67

K38

VSS_68

K11

VSS_69

K10

VSS_70

K9

VSS_71

K8

VSS_72

K7

VSS_73

K5

VSS_74

K4

VSS_75

K3

VSS_76

K2

VSS_77

SKYLAKE-H-CPU_BGA1440

BGA1440

6 OF 14

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

NCTFVSS_1

BT32

BT26

BT24

BT21

BT18

BT14

BT12

BR36

BR34

BR29

BR26

BR24

BR21

BR18

BR14

BR12

BP34

BP33

BP29

BP26

BP24

BP21

BP18

BP14

BP12

BN34

BN31

BN30

BN29

BN24

BN21

BN20

BN19

BN18

BN14

BN12

BM38

BM35

BM28

BM27

BM26

BM23

BM21

BM13

BM12

BM9

BM6

BM2

BL29

BK29

BK15

BK14

BJ32

BJ31

BJ25

BJ22

BH14

BH12

BH9

BH8

BH5

BH4

BH1

BG38

BG13

BG12

BF33

BF12

BE29

BD9

BC34

BC12

BB12

C17

C13

BT9

BT5

BR7

BP7

BN9

BN7

BN4

BN2

BE6

C9

K1

J36

J33

J32

J25

J22

J18

J10

J7

J4

H35

H32

H25

H22

H18

H12

H11

G28

G26

G24

G23

G22

G20

G18

G16

G14

G12

G10

G9

G8

G6

G5

G4

F36

F31

F29

F27

F25

F23

F21

F19

F17

F15

F13

F11

F9

F8

F5

F4

F3

F2

E38

E35

E34

E9

E4

D33

D30

D28

D26

D24

D22

D20

D18

D16

D14

D12

D10

D9

D6

D3

C37

C31

C29

C27

CPU_NCTF_1

D38

1

TP17 Test_Point_22MIL

SKYLAKE_HALO

U1L

SKYLAKE-H-CPU_BGA1440

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

BGA1440

12 OF 14

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

NCTFVSS_2

NCTFVSS_3

NCTFVSS_4

NCTFVSS_5

NCTFVSS_6

NCTFVSS_7

C25

C23

C21

C19

C15

C11

C8

C5

BM29

BM25

BM18

BM11

BM8

BM7

BM5

BM3

BL38

BL35

BL13

BL6

BK25

BK22

BK13

BK6

BJ30

BJ29

BJ15

BJ12

BH11

BH10

BH7

BH6

BH3

BH2

BG37

BG14

BG6

BF34

BF6

BE30

BE5

BE4

BE3

BE2

BE1

BD38

BD37

BD12

BD11

BD10

BD8

BD7

BD6

BC33

BC14

BC13

BC6

BB30

BB29

BB6

BB5

C2

BT36

BT35

BT4

BT3

BR38

CPU_NCTF_9

CPU_NCTF_10

CPU_NCTF_7

CPU_NCTF_8

1

TP18 Test_Point_22MIL

1

TP19 Test_Point_22MIL

1

TP23 Test_Point_22MIL

1

TP24 Test_Point_22MIL

U1M

BB4

VSS_300

BB3

VSS_301

BB2

VSS_302

BB1

VSS_303

BA38

VSS_304

BA37

VSS_305

BA12

VSS_306

BA11

VSS_307

BA10

VSS_308

BA9

VSS_309

BA8

VSS_310

BA7

VSS_311

BA6

VSS_312

B9

VSS_313

AY34

VSS_314

AY33

VSS_315

AY14

VSS_316

AY12

VSS_317

AW30

VSS_318

AW29

VSS_319

AW12

VSS_320

AW5

VSS_321

AW4

VSS_322

AW3

VSS_323

AW2

VSS_324

AW1

VSS_325

AV38

VSS_326

AV37

VSS_327

AU34

VSS_328

AU33

VSS_329

AU12

VSS_330

AU11

VSS_331

AU10

VSS_332

AU9

VSS_333

AU8

VSS_334

AU7

VSS_335

AU6

VSS_336

AT30

VSS_337

AT29

VSS_338

AT6

VSS_339

AR38

VSS_340

AR37

VSS_341

AR14

VSS_342

AR13

VSS_343

AR5

VSS_344

AR4

VSS_345

AR3

VSS_346

AR2

VSS_347

AR1

VSS_348

AP34

VSS_349

AP33

VSS_350

AP12

VSS_351

AP11

VSS_352

AP10

VSS_353

AP9

VSS_354

AP8

VSS_355

AN30

VSS_356

AN29

VSS_357

AN12

VSS_358

AN6

VSS_359

AN5

VSS_360

AM38

VSS_361

AM37

VSS_362

AM12

VSS_363

AM5

VSS_364

AM4

VSS_365

AM3

VSS_366

AM2

VSS_367

AM1

VSS_368

AL34

VSS_369

AL33

VSS_370

AL14

VSS_371

AL12

VSS_372

AL10

VSS_373

AL9

VSS_374

AL8

VSS_375

AL7

VSS_376

AL4

VSS_377

SKYLAKE-H-CPU_BGA1440

SKYLAKE_HALO

BGA1440

13 OF 14

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

VSS_396

VSS_397

VSS_398

VSS_399

VSS_400

VSS_401

VSS_402

VSS_403

VSS_404

VSS_405

VSS_406

VSS_407

VSS_408

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

VSS_428

VSS_429

VSS_430

VSS_431

VSS_432

VSS_433

VSS_434

VSS_435

VSS_436

VSS_437

VSS_438

VSS_439

VSS_440

VSS_441

VSS_442

VSS_443

VSS_444

VSS_445

VSS_446

NCTFVSS_8

NCTFVSS_9

NCTFVSS_10

NCTFVSS_11

NCTFVSS_12

AK30

AK29

AK4

AJ38

AJ37

AJ6

AJ5

AJ4

AJ3

AJ2

AJ1

AH34

AH33

AH12

AH6

AG30

AG29

AG11

AG10

AG8

AG7

AG6

AF14

AF13

AF12

AF4

AF3

AF2

AF1

AE34

AE33

AE6

AD30

AD29

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AC38

AC37

AC12

AC6

AC5

AC4

AC3

AC2

AC1

AB34

AB33

AB6

AA30

AA29

AA12

A30

A28

A26

A24

A22

A20

A18

A16

A14

A12

A10

A9

A6

B37

B3

A34

A4

A3

CPU_NCTF_2

CPU_NCTF_3

CPU_NCTF_4

1

TP25 Test_Point_22MIL

1

TP26 Test_Point_22MIL

1

TP29 Test_Point_22MIL

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : GND

CPU SKL-H : GND

CPU SKL-H : GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet of

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

8111

8111

8111

A

0.1

0.1

0.1

5

4

3

2

1

D D

C C

B B

VCCCPUCORE

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_HALO

U1G

BGA1440

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

SKYLAKE-H-CPU_BGA1440

7 OF 14

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_SENSE

VSS_SENSE

VCCCPUCORE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

VCCCORE_SENSE_R

VSSCORE_SENSE_R

1 2

R750 0_0402_5%

1 2

R751 0_0402_5%

Near Processor pins

VCCCPUCORE

1

R21

100_0402_1%

2

1

R22

100_0402_1%

2

VCCCORE_SENSE 91

VSSCORE_SENSE 91

A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT CONTA INS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CEN TER.

3

2015/07/16

2015/07/16

2015/07/16

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/16

2016/01/16

2016/01/16

Title

CPU SKL-H : VCC

CPU SKL-H : VCC

CPU SKL-H : VCC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Wednesday, December 07, 2016

Date: Sheet

Date: Sheet

Date: Sheet

PAYTON

PAYTON

PAYTON

1

of

of

of

9111

9111

9111

A

0.1

0.1

0.1

5

4

3

2

1

VCCGFXCORE_I

SKYLAKE_HALO

D D

C C

B B

U1H

BG34

VCCGT_1

BG35

VCCGT_2

BG36

VCCGT_3

BH33

VCCGT_4

BH34

VCCGT_5

BH35

VCCGT_6

BH36

VCCGT_7

BH37

VCCGT_8

BH38

VCCGT_9

BJ37

VCCGT_10

BJ38

VCCGT_11

BL36

VCCGT_12

BL37

VCCGT_13

BM36

VCCGT_14

BM37

VCCGT_15

BN36

VCCGT_16

BN37

VCCGT_17

BN38

VCCGT_18

BP37

VCCGT_19

BP38

VCCGT_20

BR37

VCCGT_21

BT37

VCCGT_22

BE38

VCCGT_23

BF13

VCCGT_24

BF14

VCCGT_25

BF29

VCCGT_26

BF30

VCCGT_27

BF31

VCCGT_28

BF32

VCCGT_29

BF35

VCCGT_30

BF36

VCCGT_31

BF37

VCCGT_32

BF38

VCCGT_33

BG29

VCCGT_34

BG30

VCCGT_35

BG31

VCCGT_36

BG32