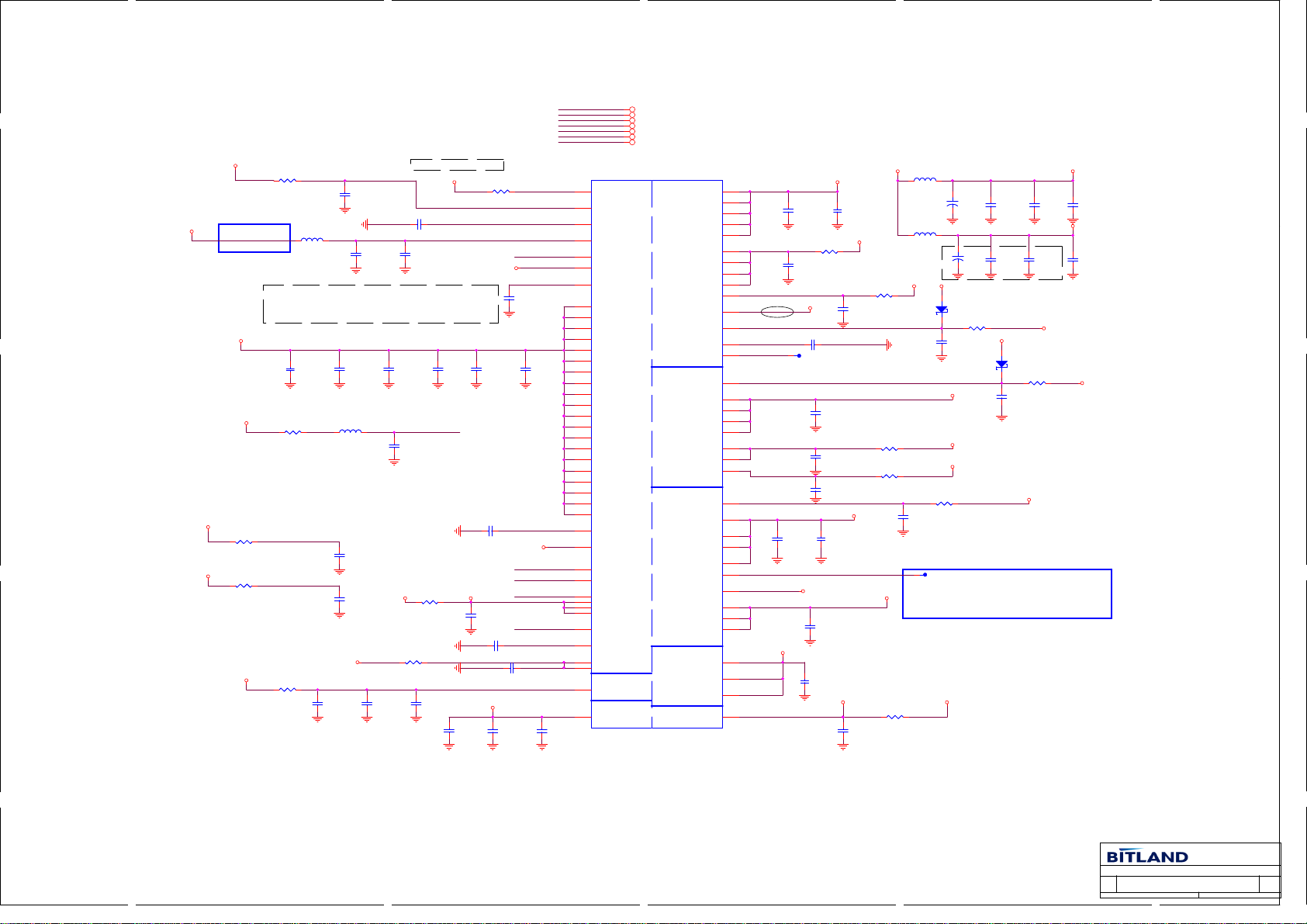

LENOVO N480 Schematics

5

D D

4

3

2

1

Bitland Confidential

N480 MB Schematics Document

C C

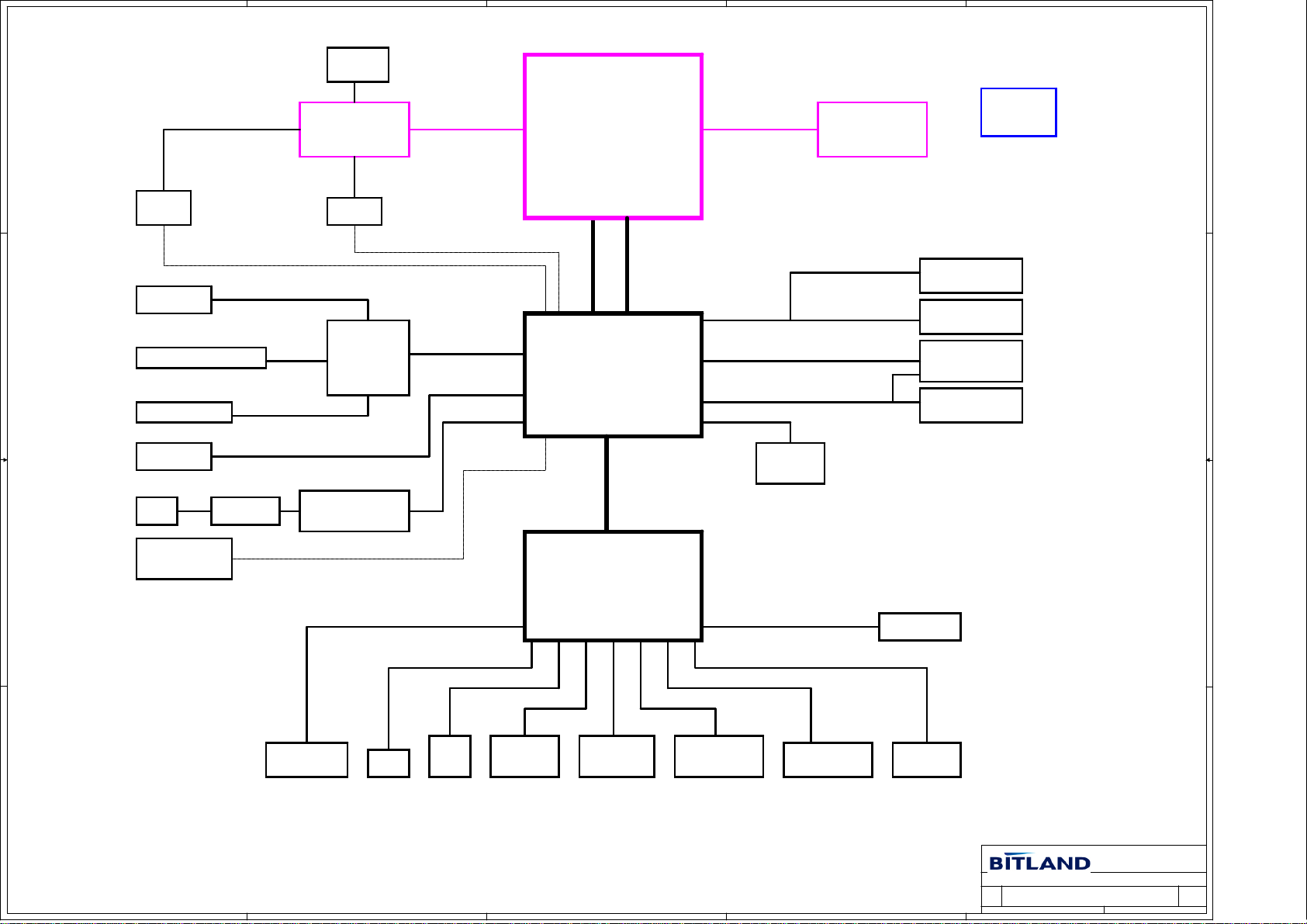

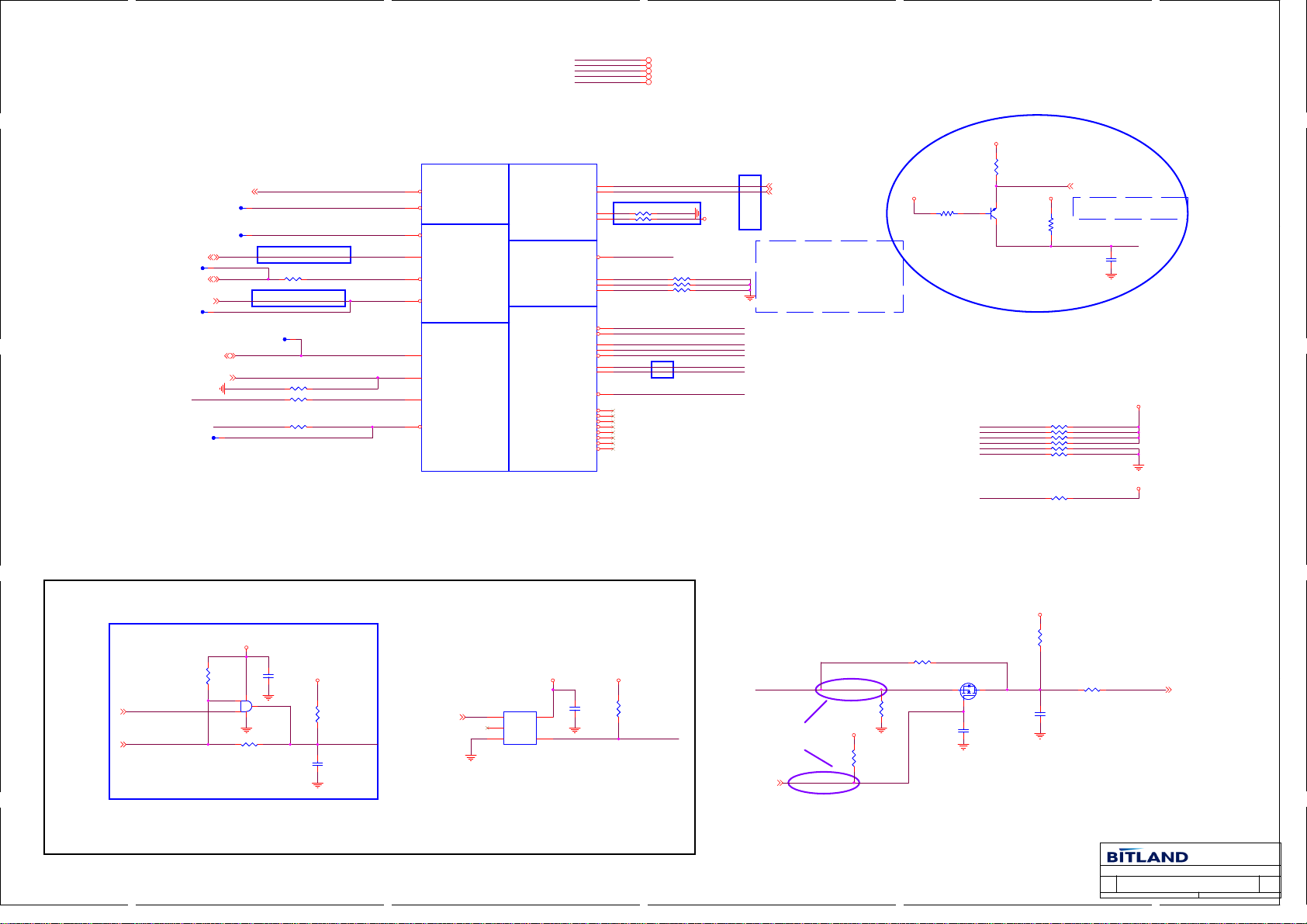

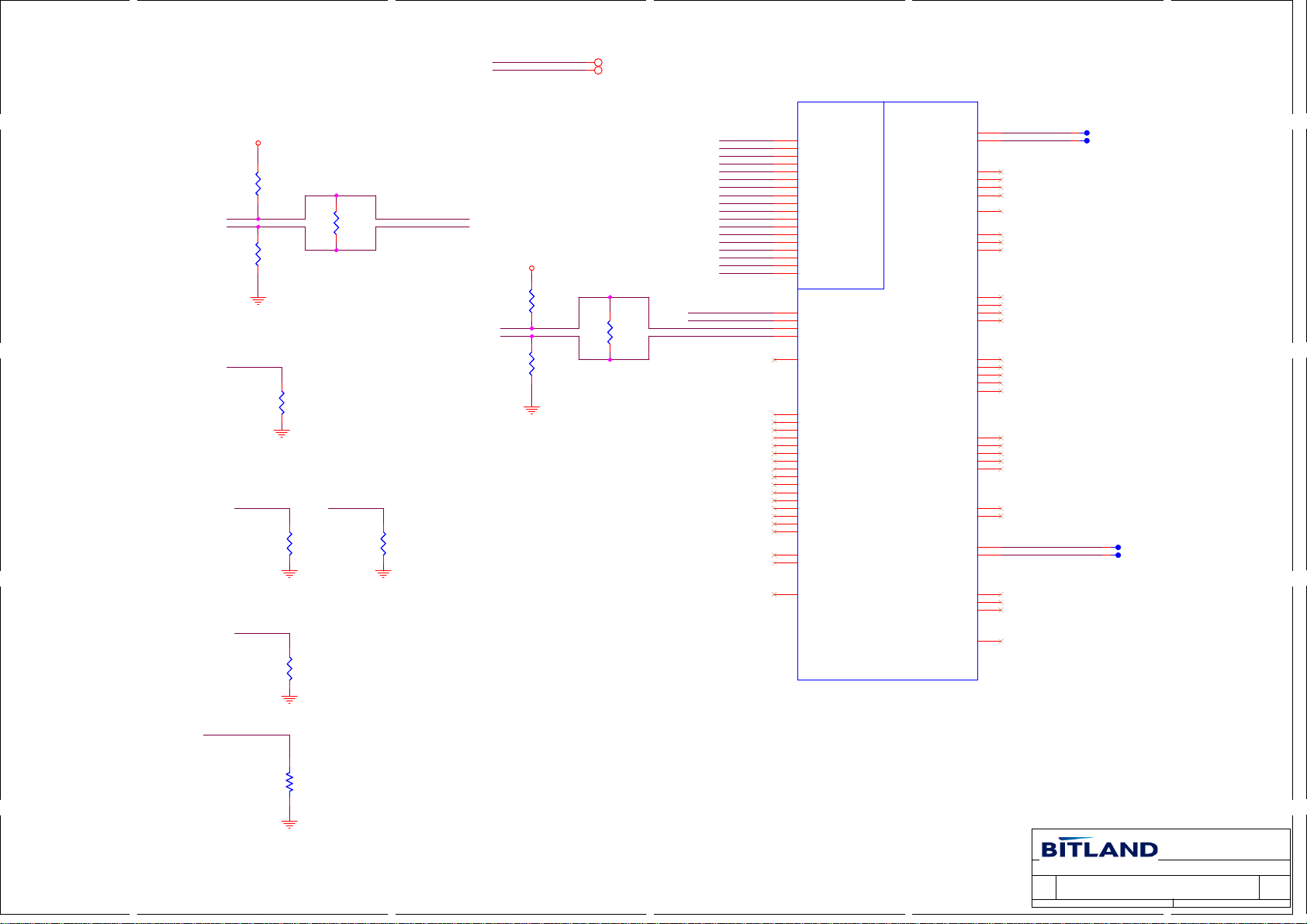

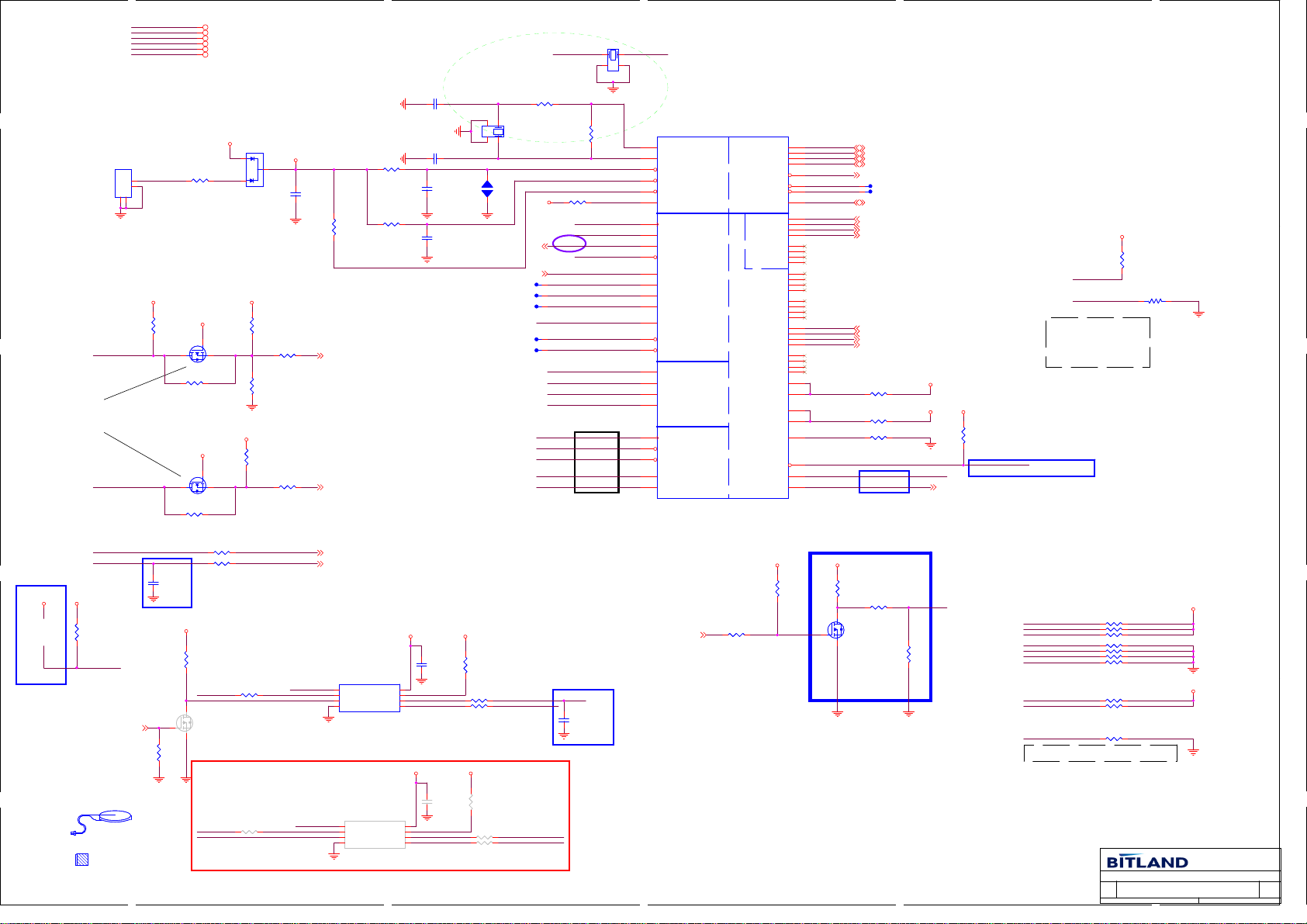

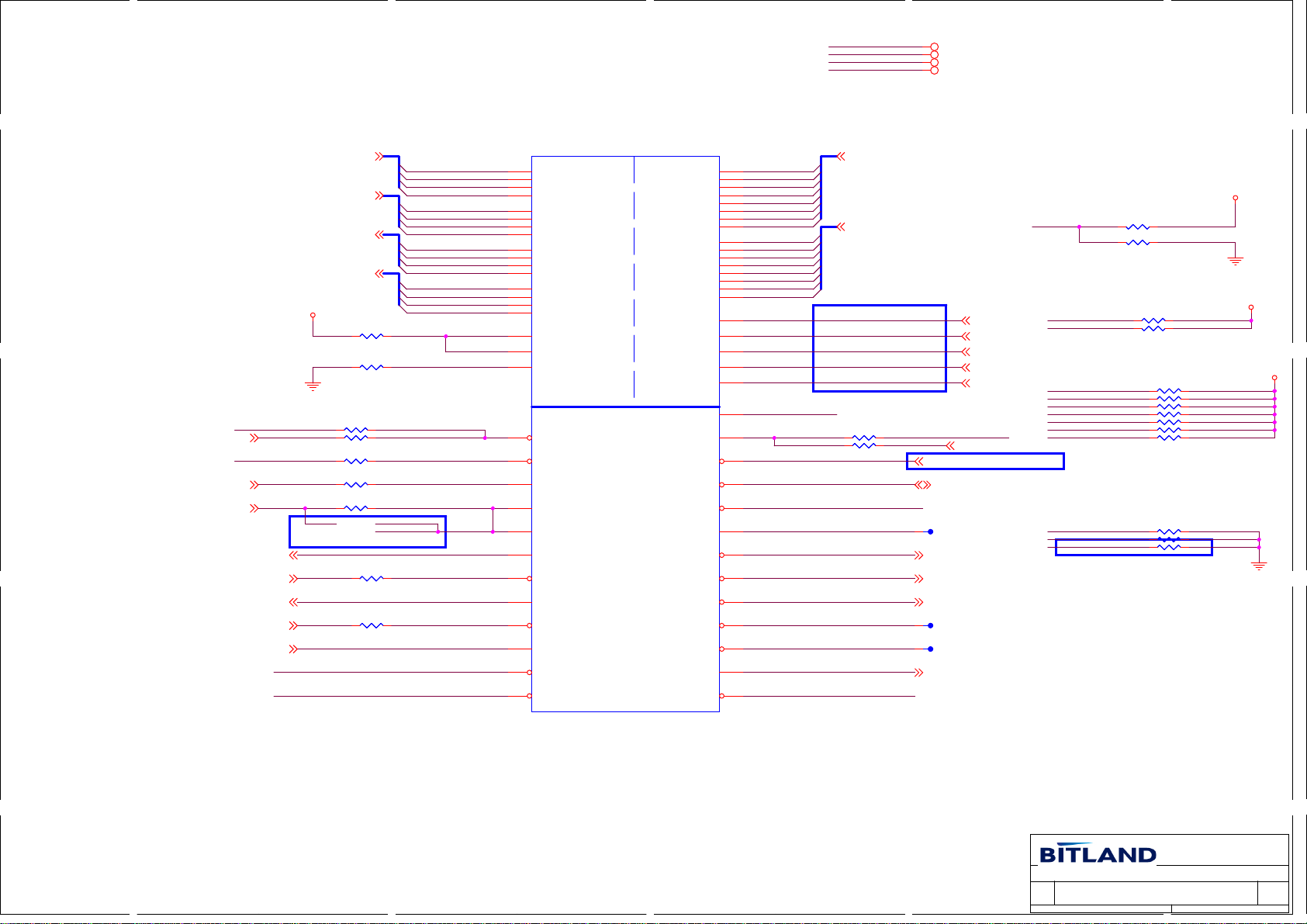

Intel Ivy Bridge/Sandy Bridge Processor with PantherPoint HM76/HM70+ DDRIII

MotherBoard version:BM5238 Rev1.2

B B

2012-04-09

A A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A3

A3

A3

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

5

4

3

2

Wednesday, September 12, 2012 64

Cover page

Cover page

Cover page

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

1

Rev

Rev

Rev

1.2

1.2

1.2

1

1

1

5

4

3

2

1

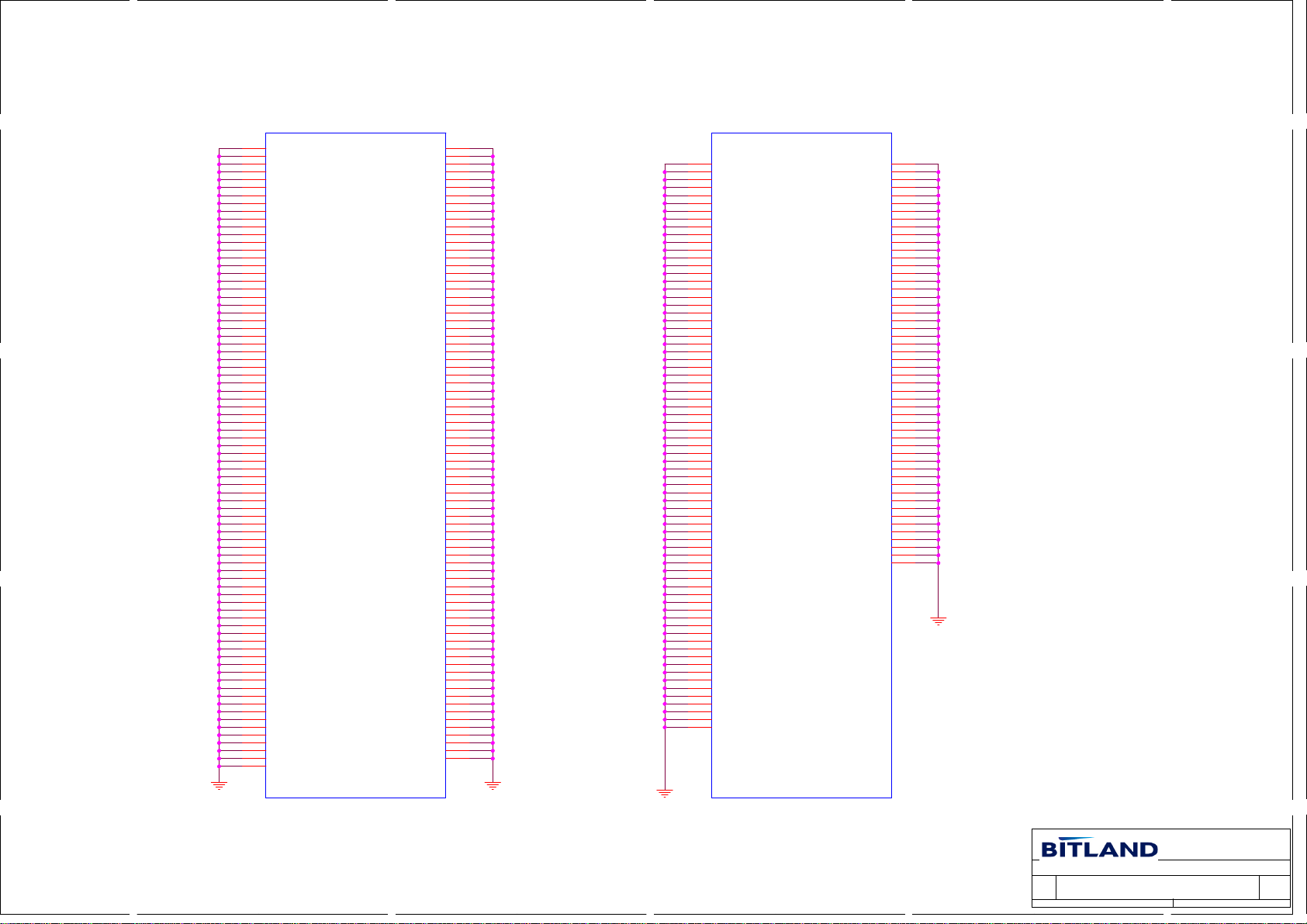

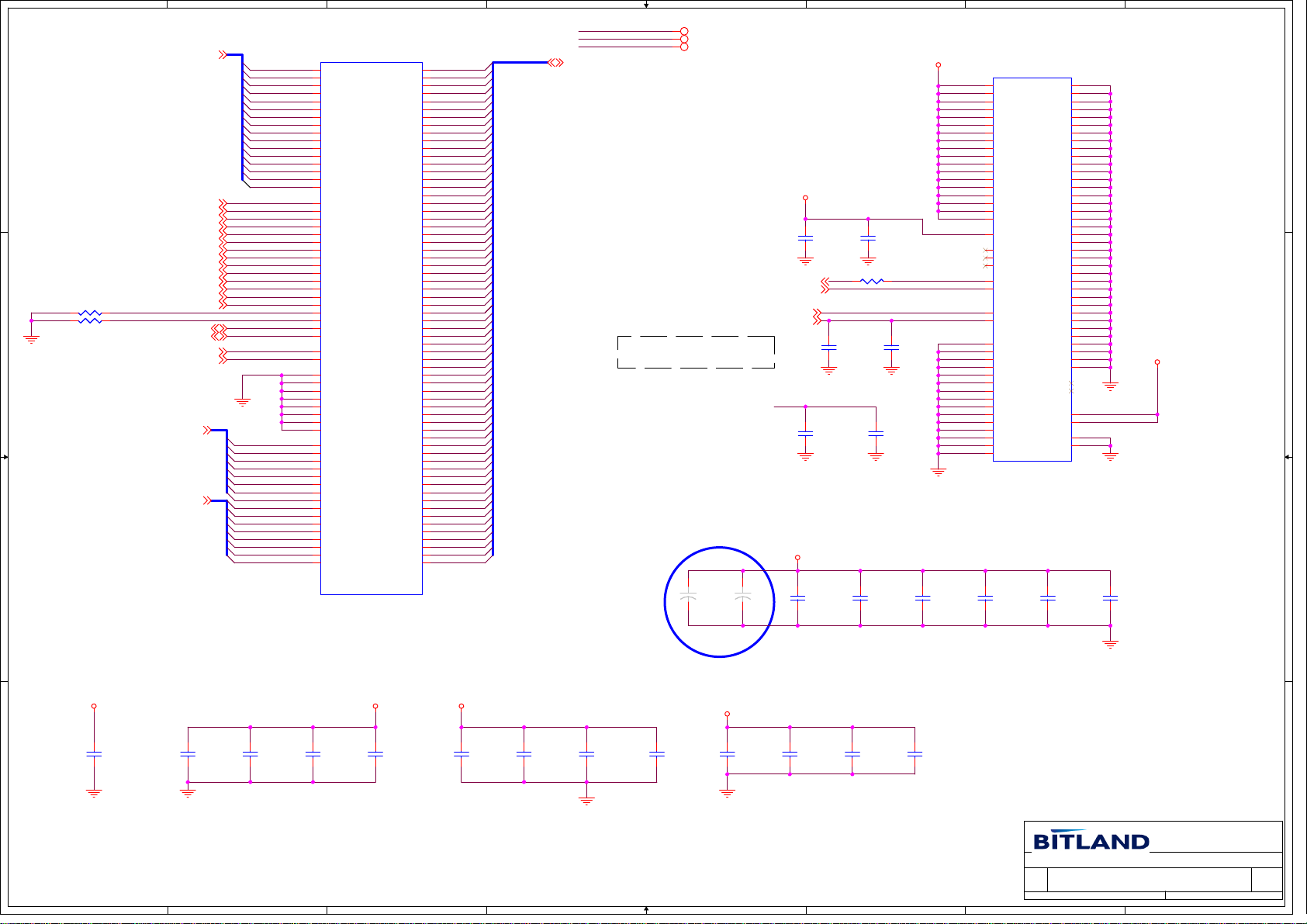

1G DDR3

P56

Ivy Processor

D D

LVDS

GPU

Robson-XT

PEG X16

Micro-FCPGA-988

(988-pin rPGA socket)

1600/1333 MHZ

37.5 mm X 37.5 mm

CRT

SO-DIMM 0

1600/1333 MHZ

DDR(III)

204 pin

P20

IMVP7

(2+1)

P42

LVDS

WXGA

P23 P22

VGA

P4-P10

CRT(Option)

LVDS(Option) FDI

Int. Speaker

1.5Walt

C C

Combo Jack x1

DB

Realtek

ALC269-VB6

P30

HDA

USB2.0

CPT/PPT

(USB x 14)

(PCIE x 8)

(SATA x 6)

989 mBGA

Internal Mic X1

PCIE

25 mm X 25 mm

DMI

PCIE

USB2.0

SPI

SATA3.0

SATA2.0

SATA

HDD

P34

SATA

ODD

P34

Harf Mini-Card

WLAN

P27

USB 2.0

CONNx3

P33

P11-P19

CAMERA

RJ45

P29

Transformer

RTL8105E

100M LAN

USB2.0(Option)

LPC

P31

Flash BIOS

32Mbitx2

P11

RTS5179

B B

2in1 Conn

P36

ITE

IT8518E

LQFP-128

P25

GPIO

Lid Switch

P25

GPIO

PS2

PWM/TACH

SPI

Keyboard

A A

5

P25 P37 P35

LED

P35 P35

4

FAN BATT CONN Power Button

Flash BIOS

512K bit

P26

3

SMBus0

Thermal Sensor

P32P32

Touchpad

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Date:

Date:

2

Date:

Notebook R&D Division

Block Diagram

Block Diagram

Block Diagram

N480

N480

N480

Sheet of

Sheet of

Sheet of

1

Rev

Rev

Rev

1.2

1.2

2

2

2

1.2

5

A

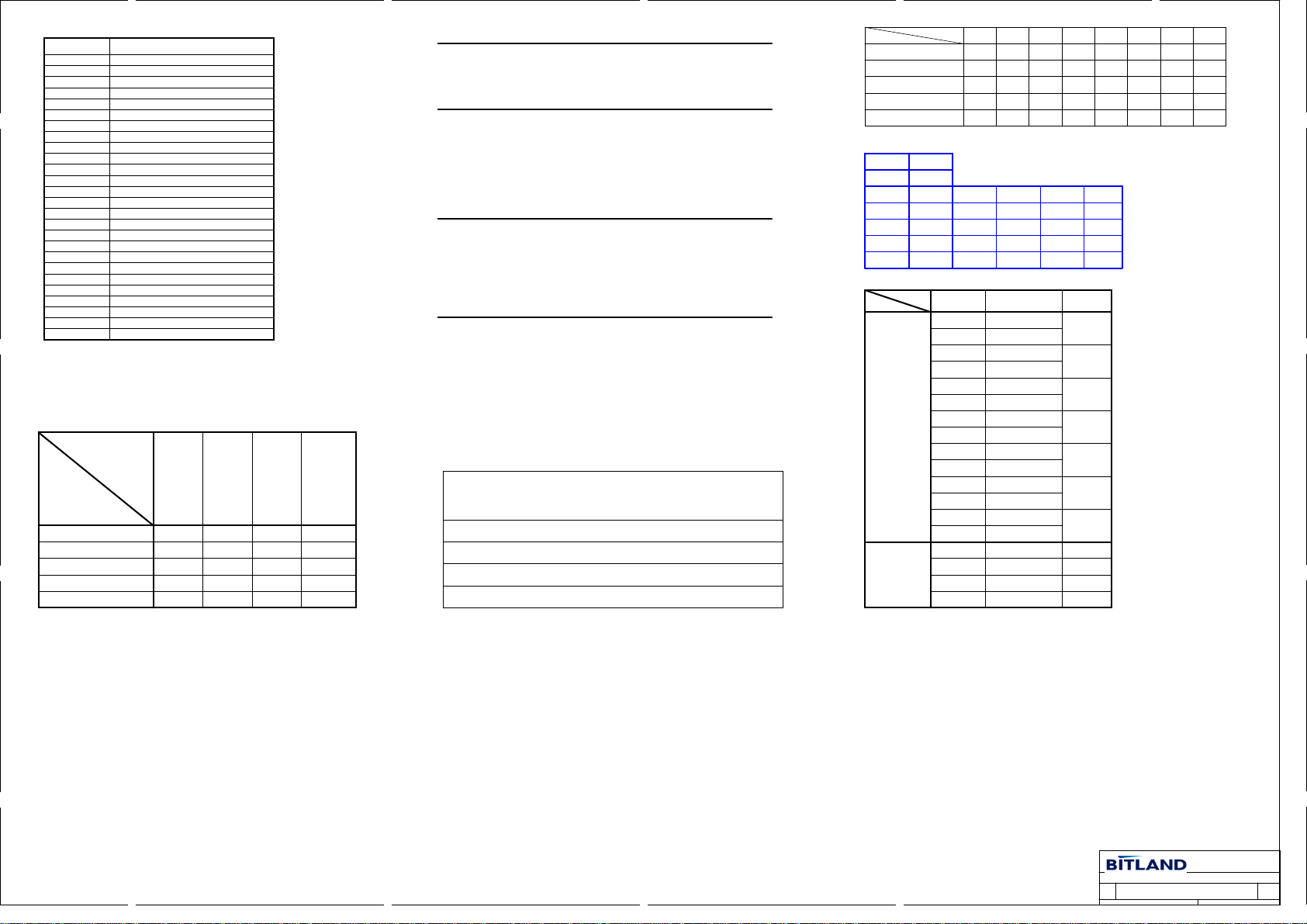

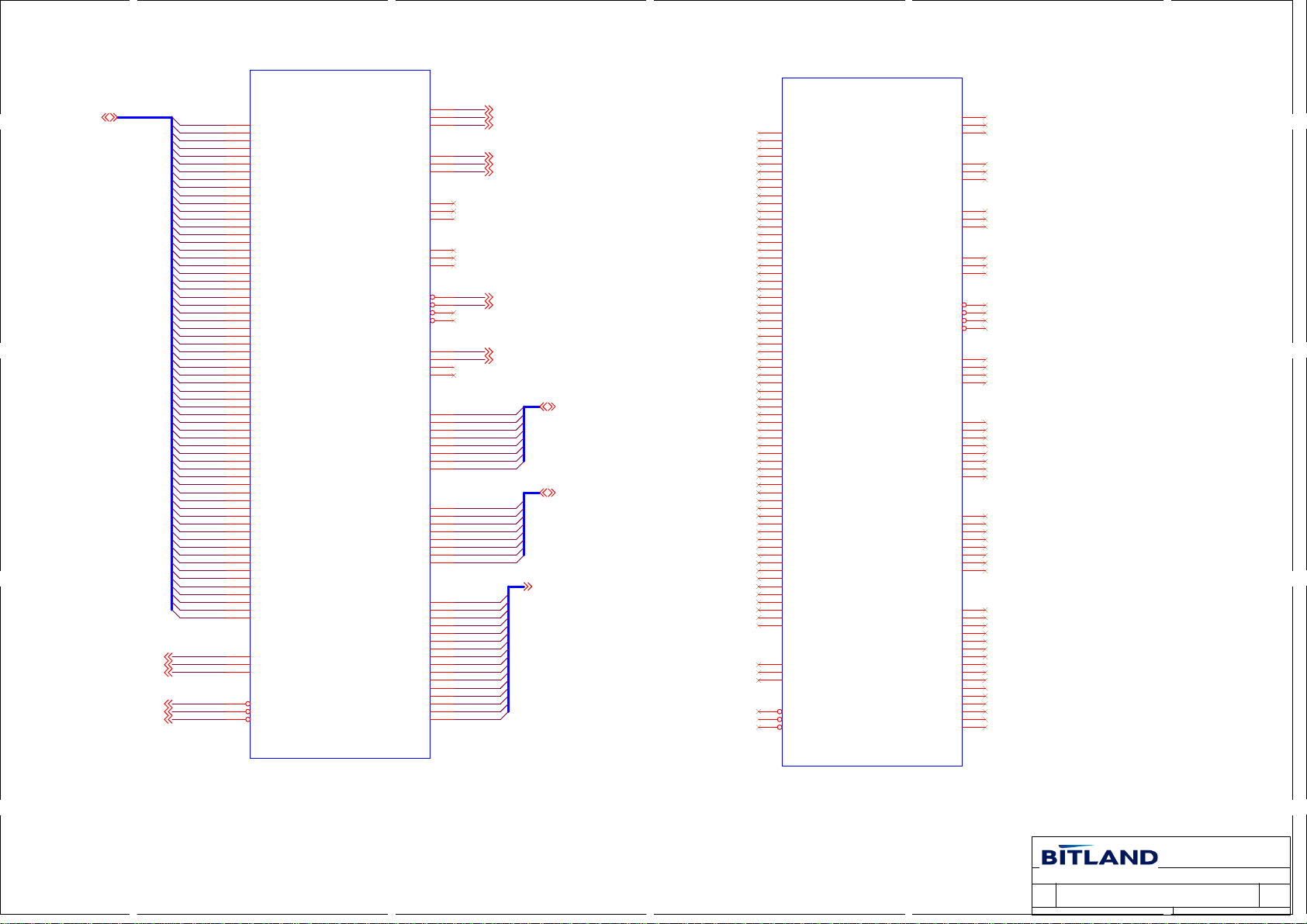

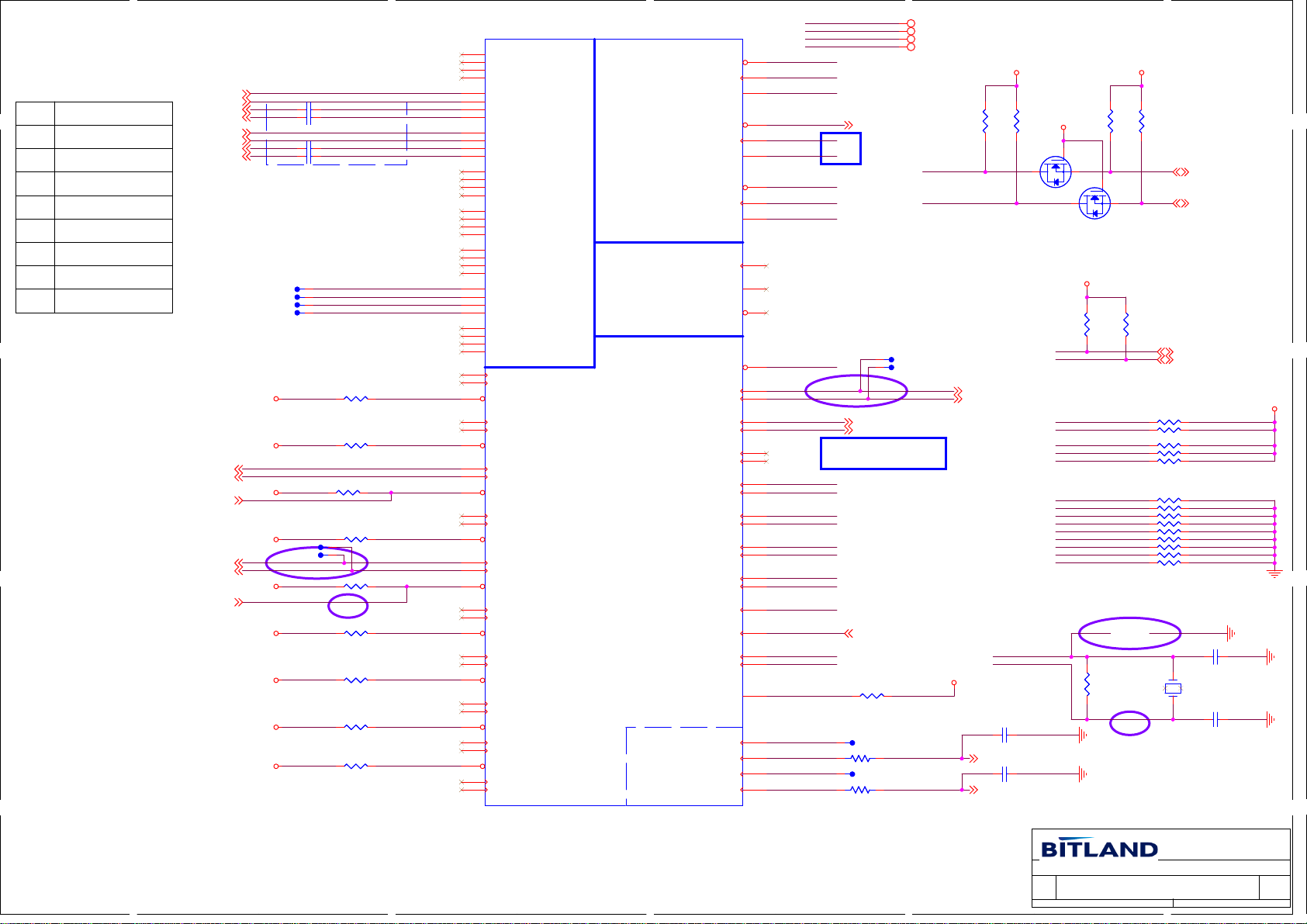

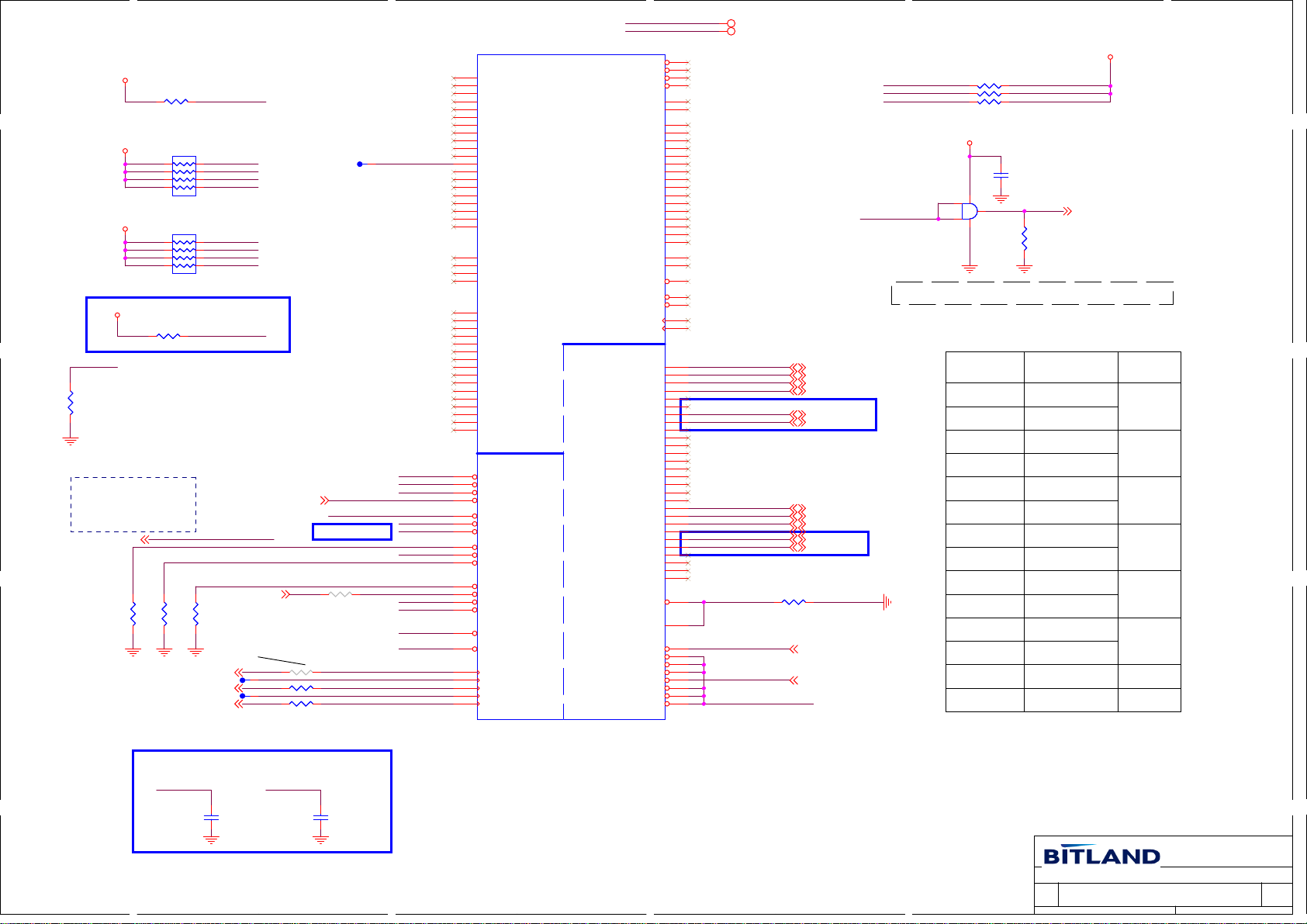

Power Annotations

Power Plane

AD+

DCBATOUT

VHCORE

+0_75V 0_75VRUN LDO power rail for DDR terminator

+1_05VRUN

D D

+1.0V_VCCP

+1_5VSUS 1.5V power rail for DDR

+1_5V_CPU 1.5V switched power rail

+1_8VRUN

+3VALW

+3VSUS

+V3.3M_LAN

+3VRUN

+5VALW

+5VSUS

+5VRUN 5V switched power rail

+3VALW_LDO

+5VALW_LDO

+VCCSA

GFXCORE

+VDDC

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.05V switched power rail

VCCP switched power rail

1.8V power rail for system

3.3V always on power rail

3.3V power rail for SB

3.3V power rail for LAN

3.3V switched power rail

5V always on power rail

5V switched power rail

3.3V power from TPS51125 LDO

5V power from TPS51125 LDO

SA voltage for CPU

GFXCORE voltage for CPU Graphic

CORE Power for discete GPU

C C

Voltage Rails

Power Plane

State

S0

S3

B B

S4&S5 (AC)

S3&S4 (Battery only)

S3&S4 (AC&Battery don't exist) OFF OFFOFFOFF

DCBATOUT

+3VALW_LDO

+5VALW_LDO

AD+

+3VALW

+V3.3M_LAN

+5VALW

ON

ON

ON

ON

+1_5VSUS

+3VSUS

+5VSUS

ON

ON

ON

+0_75V

+1_05VRUN

+1.05V_VCCP

+VCCSA

VHCORE

+1_5V_CPU

+1_8VRUN

+3VRUN

+5VRUN

GFXCORE

+VDDC

ON ON

ON

OFF

OFF

OFF

OFFOFFOFF

4

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

EC SM Bus1 address

Device

Smart Battery

Address Address

0001 011X b

3

EC SM Bus2 address

Device

Thermal Sensor for DDR&VR

1001 100X b

2

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

1

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +V*ALW +V*SUS +V*RUN Clock

ON

ON

ON

ON

ON

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

LOW

OFF

OFF

OFF

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

HIGHHIGHHIGH

HIGH

LOWLOWLOW

HIGH

BOARD ID Table

+ECVCC 3.3V 5%

R3863100K 5%

CPT/PPT SM Bus address

Device Address

DDR DIMM0

DDR DIMM1

Debug Port

1001 000Xb

1001 010Xb

1100 1000 b

Board ID

0

1

2

R387

0

8.2K 5%

18K 5%

33K 5%

V min V typ

0V

0.216V

0.436V

0.712V

0V

0.250V

0.503V

0.819V

V max Phase

0V

REV1.0

0.289V

REV1.1

0.538V

REV1.2

REV1.3

0.875V

USB Port Table

CPT/PPT SM Bus0 address

Device Address

SMBUS Control Table

SOURCE VGA BATT EC DIMM

SMB_EC_CK0

SMB_EC_DA0

SMB_EC_CK1

SMB_EC_DA1

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

IT8105E

+3VALW

IT8105E

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

+ECVCC

V

X

X

X

X V

+3VALW

CPT/PPT SM Bus1 address

EC

X V

WLAN

Thermal

WWAN

Sensor

X

X

X

X

V

X

+3VALW

X

X

X

AddressDevice

PCH GPU LAN

USB 2.0

USB 3.0

PORT-0

PORT-1

PORT-2

PORT-3

PORT-4

PORT-5

PORT-6

PORT-7

PORT-8

PORT-9

PORT-10

PORT-11

PORT-12

PORT-13

PORT-0

PORT-1

PORT-2

PORT-3

FunctionUSB PORT

Ext. Port(MB)

Ext. Port(MB)

Card reader

Ext. Port(DB)

BT

CAMERA

OC pin

OC#0

OC#1

OC#2

OC#3

OC#4

OC#5

OC#6

A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A2

A2

A2

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

5

4

3

2

Wednesday, September 12, 2012 64

NOTE LIST

NOTE LIST

NOTE LIST

1

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.2

1.2

1.2

3

3

3

5

A

4

+1_05VRUN 5,7,11,13,17,18,26,40,42,44,48,49,51,52

3

2

1

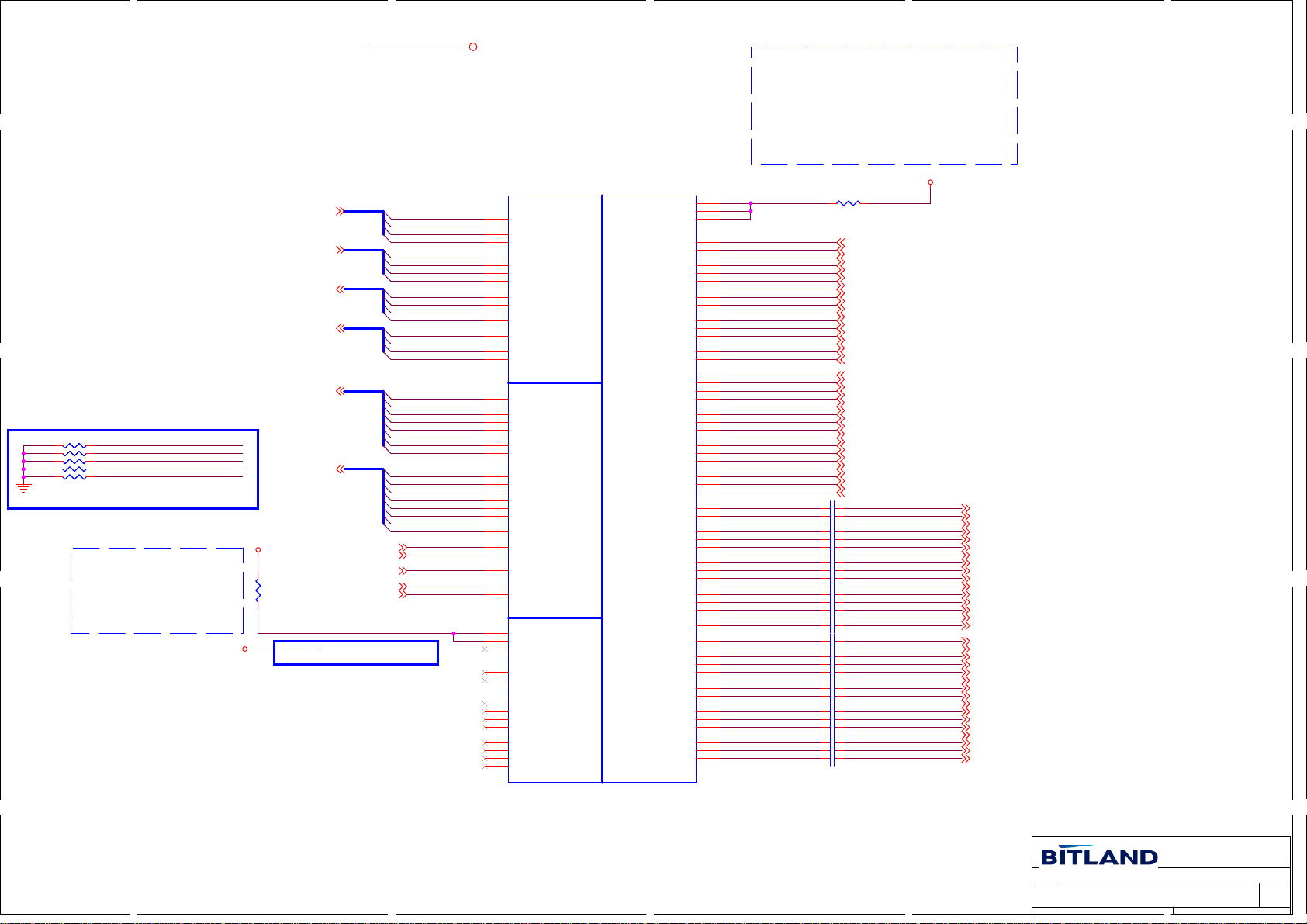

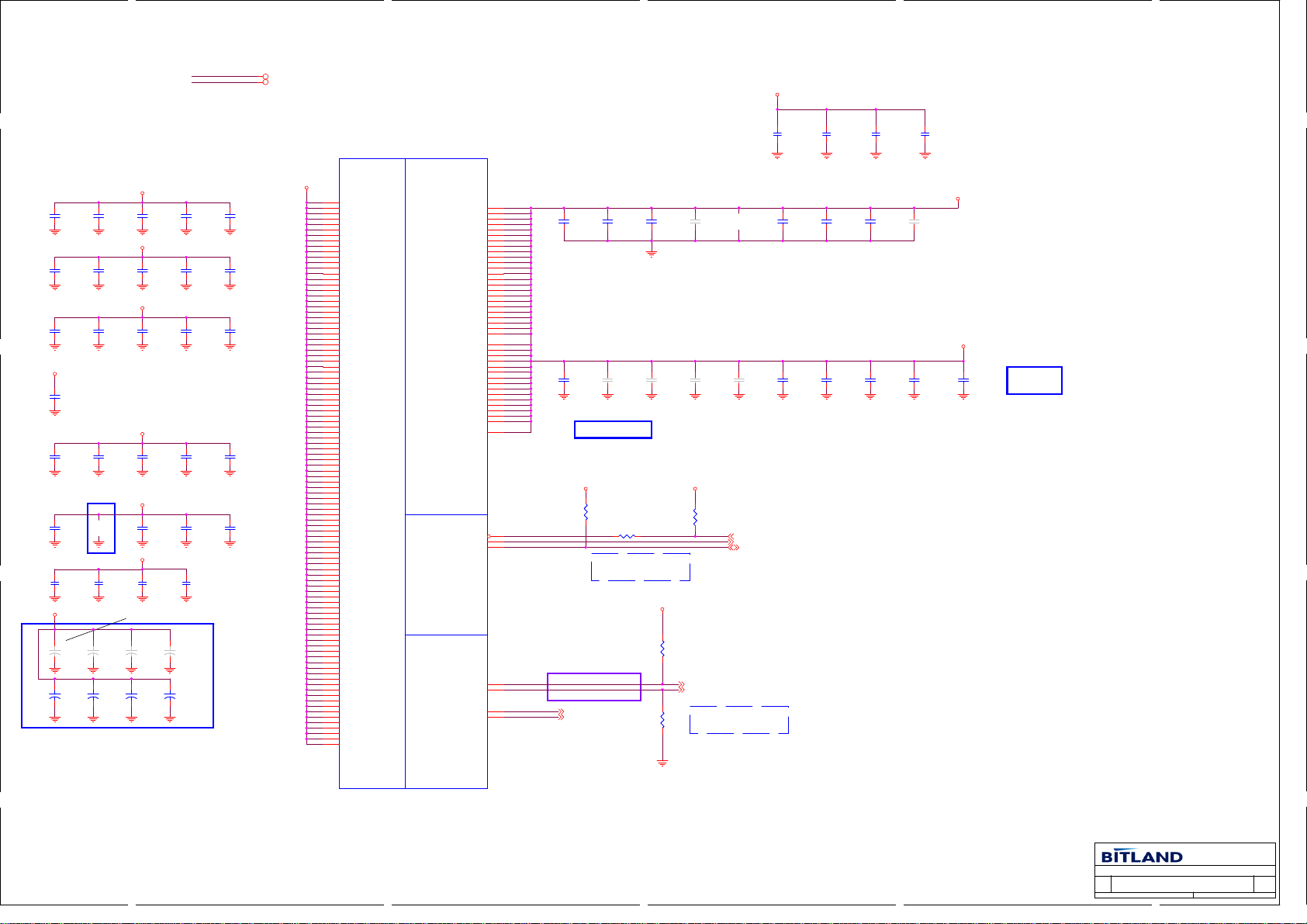

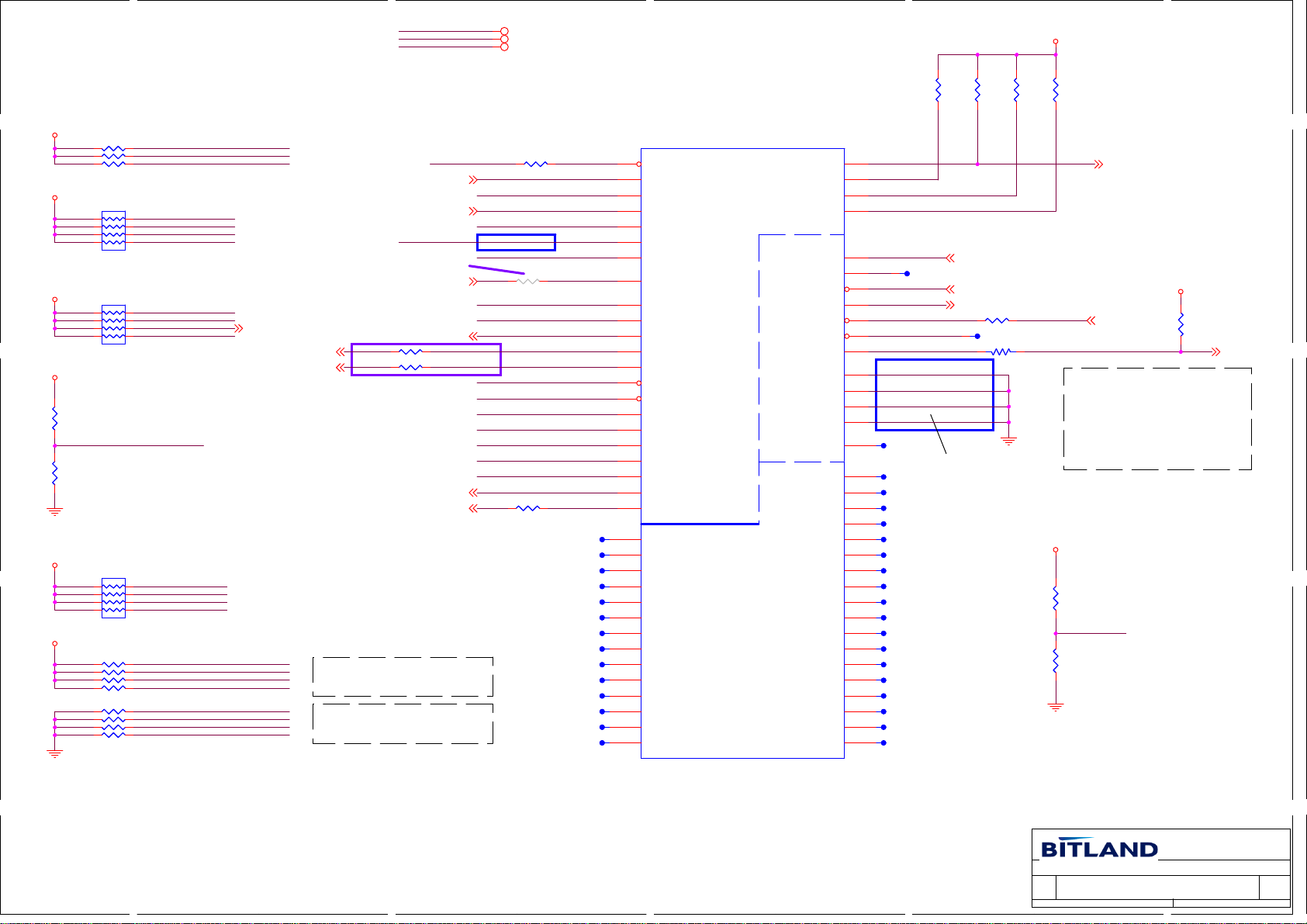

CAD NOTE: PEG_ICOMPI and RCOMPO signals

should be shorted and routed with

- max length = 500 mils

- typical impedance = 43 mohms

D D

PEG_ICOMPO signals should be routed with

- max length = 500 mils

- typical impedance = 14.5 mohms

+1_05VRUN

U55A

U55A

DMI_TXN[3:0]13

DMI_TXP[3:0]13

DMI_RXN[3:0]13

DMI_RXP[3:0]13

C C

FDI_TXN[7:0]13

add by lihong 0504

R7 1K_J R0402

R7 1K_J R0402

R8 1K_J R0402

R8 1K_J R0402

R40 1K_J R0402

R40 1K_J R0402

R41 1K_J R0402

R41 1K_J R0402

R42 1K_J R0402

R42 1K_J R0402

12

12

12

12

12

CAD NOTE: DP_COMPIO and

B B

ICOMPO signals

should be shorted near balls and

routed with

- typical impedance < 25 mohms

GPU

GPU

GPU

GPU

GPU

GPU

GPU

GPU

GPU

GPU

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

+1_05VRUN

+1_05VRUN

R2

R2

24.9_F

24.9_F

r0402

r0402

1 2

FDI_TXP[7:0]13

FDI_FSYNC013

FDI_FSYNC113

FDI_INT13

FDI_LSYNC013

FDI_LSYNC113

DP_COMP

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

del R3 lihong 0504

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_COMP

0.22uF->0.1uF lihong 0626

In order to support Gen 3 PCI Express Graphic,

the value of the AC coupling capacitor should be 180 - 265 nF.

As for Gen2 PCI Express ,the value of the AC coupling capacitor should be 100 - 220 nF

1 2

R1 24.9_F r0402R1 24.9_F r0402

GFX_RX0N_C 48

GFX_RX1N_C 48

GFX_RX2N_C 48

GFX_RX3N_C 48

GFX_RX4N_C 48

GFX_RX5N_C 48

GFX_RX6N_C 48

GFX_RX7N_C 48

GFX_RX8N_C 48

GFX_RX9N_C 48

GFX_RX10N_C 48

GFX_RX11N_C 48

GFX_RX12N_C 48

GFX_RX13N_C 48

GFX_RX14N_C 48

GFX_RX15N_C 48

GFX_RX0P_C 48

GFX_RX1P_C 48

GFX_RX2P_C 48

GFX_RX3P_C 48

GFX_RX4P_C 48

GFX_RX5P_C 48

GFX_RX6P_C 48

GFX_RX7P_C 48

GFX_RX8P_C 48

GFX_RX9P_C 48

GFX_RX10P_C 48

GFX_RX11P_C 48

GFX_RX12P_C 48

GFX_RX13P_C 48

GFX_RX14P_C 48

GFX_RX15P_C 48

1 2

C3510 0.1uF/10V,X5R GPUc0402C3510 0.1uF/10V,X5R GPUc0402

1 2

C3511 0.1uF/10V,X5R GPUc0402C3511 0.1uF/10V,X5R GPUc0402

1 2

C3512 0.1uF/10V,X5R GPUc0402C3512 0.1uF/10V,X5R GPUc0402

1 2

C3513 0.1uF/10V,X5R GPUc0402C3513 0.1uF/10V,X5R GPUc0402

1 2

C3514 0.1uF/10V,X5R GPUc0402C3514 0.1uF/10V,X5R GPUc0402

1 2

C3515 0.1uF/10V,X5R GPUc0402C3515 0.1uF/10V,X5R GPUc0402

1 2

C3516 0.1uF/10V,X5R GPUc0402C3516 0.1uF/10V,X5R GPUc0402

1 2

C3517 0.1uF/10V,X5R GPUc0402C3517 0.1uF/10V,X5R GPUc0402

1 2

C3502 0.1uF/10V,X5R GPUc0402C3502 0.1uF/10V,X5R GPUc0402

1 2

C3503 0.1uF/10V,X5R GPUc0402C3503 0.1uF/10V,X5R GPUc0402

1 2

C3504 0.1uF/10V,X5R GPUc0402C3504 0.1uF/10V,X5R GPUc0402

1 2

C3505 0.1uF/10V,X5R GPUc0402C3505 0.1uF/10V,X5R GPUc0402

1 2

C3506 0.1uF/10V,X5R GPUc0402C3506 0.1uF/10V,X5R GPUc0402

1 2

C3507 0.1uF/10V,X5R GPUc0402C3507 0.1uF/10V,X5R GPUc0402

1 2

C3508 0.1uF/10V,X5R GPUc0402C3508 0.1uF/10V,X5R GPUc0402

1 2

C3509 0.1uF/10V,X5R GPUc0402C3509 0.1uF/10V,X5R GPUc0402

1 2

C3518 0.1uF/10V,X5R GPUc0402C3518 0.1uF/10V,X5R GPUc0402

1 2

C3519 0.1uF/10V,X5R GPUc0402C3519 0.1uF/10V,X5R GPUc0402

1 2

C3520 0.1uF/10V,X5R GPUc0402C3520 0.1uF/10V,X5R GPUc0402

1 2

C3521 0.1uF/10V,X5R GPUc0402C3521 0.1uF/10V,X5R GPUc0402

1 2

C3522 0.1uF/10V,X5R GPUc0402C3522 0.1uF/10V,X5R GPUc0402

1 2

C3523 0.1uF/10V,X5R GPUc0402C3523 0.1uF/10V,X5R GPUc0402

1 2

C3524 0.1uF/10V,X5R GPUc0402C3524 0.1uF/10V,X5R GPUc0402

1 2

C3525 0.1uF/10V,X5R GPUc0402C3525 0.1uF/10V,X5R GPUc0402

1 2

C3526 0.1uF/10V,X5R GPUc0402C3526 0.1uF/10V,X5R GPUc0402

1 2

C3527 0.1uF/10V,X5R GPUc0402C3527 0.1uF/10V,X5R GPUc0402

1 2

C3528 0.1uF/10V,X5R GPUc0402C3528 0.1uF/10V,X5R GPUc0402

1 2

C3529 0.1uF/10V,X5R GPUc0402C3529 0.1uF/10V,X5R GPUc0402

1 2

C3530 0.1uF/10V,X5R GPUc0402C3530 0.1uF/10V,X5R GPUc0402

1 2

C3531 0.1uF/10V,X5R GPUc0402C3531 0.1uF/10V,X5R GPUc0402

1 2

C3532 0.1uF/10V,X5R GPUc0402C3532 0.1uF/10V,X5R GPUc0402

1 2

C3533 0.1uF/10V,X5R GPUc0402C3533 0.1uF/10V,X5R GPUc0402

GFX_TX0N_C 48

GFX_TX1N_C 48

GFX_TX2N_C 48

GFX_TX3N_C 48

GFX_TX4N_C 48

GFX_TX5N_C 48

GFX_TX6N_C 48

GFX_TX7N_C 48

GFX_TX8N_C 48

GFX_TX9N_C 48

GFX_TX10N_C 48

GFX_TX11N_C 48

GFX_TX12N_C 48

GFX_TX13N_C 48

GFX_TX14N_C 48

GFX_TX15N_C 48

GFX_TX0P_C 48

GFX_TX1P_C 48

GFX_TX2P_C 48

GFX_TX3P_C 48

GFX_TX4P_C 48

GFX_TX5P_C 48

GFX_TX6P_C 48

GFX_TX7P_C 48

GFX_TX8P_C 48

GFX_TX9P_C 48

GFX_TX10P_C 48

GFX_TX11P_C 48

GFX_TX12P_C 48

GFX_TX13P_C 48

GFX_TX14P_C 48

GFX_TX15P_C 48

MXM3.0 need put the CAP on the motherboard.

Close to the MXM Slot

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A3

A3

A3

Date:

Wednesday, September 12, 2012 64

Date:

Wednesday, September 12, 2012 64

Date:

Wednesday, September 12, 2012 64

CPU(DMI,DP,PEG,FDI)

CPU(DMI,DP,PEG,FDI)

CPU(DMI,DP,PEG,FDI)

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.2

1.2

1.2

4

4

4

A

5

A

4

3

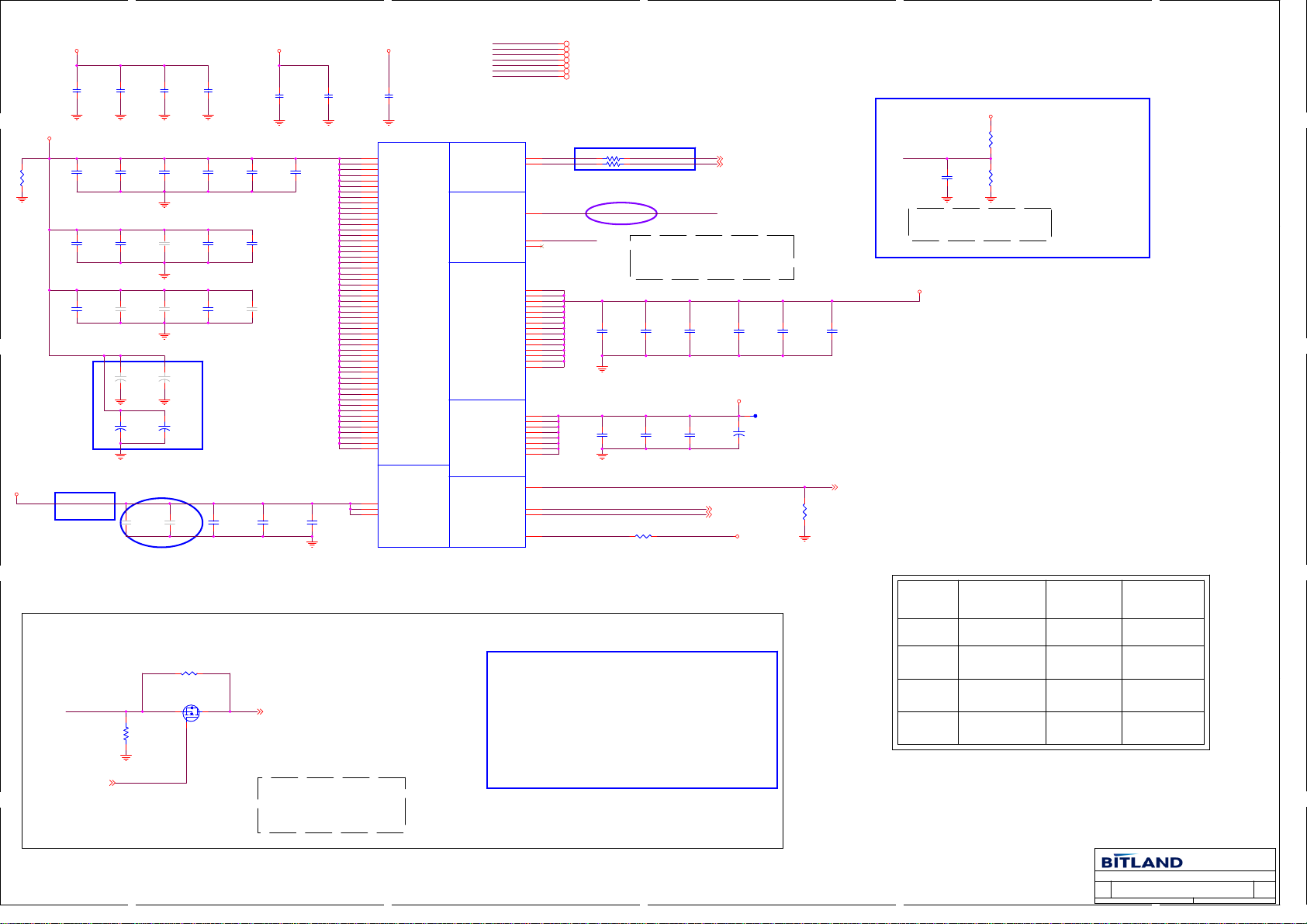

+3VALW 8,11,12,13,15,16,17,18,23,25,26,27,31,35,38,39,43,44,47

+1_5V_CPU 8,17,27,43,44,47,51,55,56,57

+3VRUN 11,12,13,14,15,16,17,18,20,22,23,25,26,27,30,31,32,34,35,36,39,40,41,42,43,44,47,48,49,51,53

+1_05VRUN 4,7,11,13,17,18,26,40,42,44,48,49,51,52

+1_5VSUS 8,20,39,43,57

2

1

D D

+3VALW

U55B

U55B

A28

BCLK

A27

BCLK#

A16

DPLL_REF_CLK

R43 1K_J R0402R43 1K_J R0402

A15

R45 1K_J R0402R45 1K_J R0402

refer to DG no eDP lihong 0504

R8

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TCK

TMS

TDO

TDI

AK1

A5

A4

AP29

AP27

AR26

AR27

AP30

AR28

AP26

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

DDR3_DRAMRST#_R

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_DBRESET#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PROCHOT#_R

H_PM_SYNC

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

DPLL_REF_CLK#

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

H_SNB_IVB#16

ictpad_c20

ictpad_c20

20MIL

20MIL

TP101

TP101

ictpad_c20

ictpad_c20

20MIL

20MIL

TP105

H_PECI25

1

TP107

TP107

1

TP106

TP106

ictpad_c20

ictpad_c20

H_PM_SYNC13

H_CPUPWRGD16

PM_SYS_PWRGD_BUFF

BUF_CPU_RST#

1

TP126

TP126

TP105

H_PROCHOT#

del R8 lihong 0503

ictpad_c20

ictpad_c20

20MIL

20MIL

H_PROCHOT#42

PM_THRMTRIP#16,26

ictpad_c20

ictpad_c20

20MIL

20MIL

C C

ictpad_c20

ictpad_c20

20MIL

20MIL

H_SNB_IVB#

1

SKTOCC#

1

H_CATERR#

1 2

56_J r0402

R459

R459

del R15 lihong 0504

20MIL

20MIL

56_J r0402

1

TP108

TP108

1 2

R29 10K_J r0402R29 10K_J r0402

1 2

R179 130_F r0402R179 130_F r0402

1 2

R636 43_F r0402R636 43_F r0402

H_CPUPWRGD

BUF_CPU_RST#_R

del RP1 RP2 refer to TCL lihong 0503

CLK_EXP_P 12

CLK_EXP_N 12

12

12

R10 140_F r0402R10 140_F r0402

R11 25.5_F r0402R11 25.5_F r0402

R12 200_F r0402R12 200_F r0402

1 2

1 2

1 2

+1_05VRUN

CAD NOTE: All DDR_COMP signals

should be routed such that :-

- max length = 500 mils

- trace width = 15mils and

- MB trace impedance < 68 mohms

(worst case resistance)

del R484 R485 lihong 0425

R5646 1K_J

R5646 1K_J

R0402

R0402

dengrl

The OD buffer serves two purposes:

1.Voltage level shifter - from 3.3 V (EC) to 1.05 V (Processor).

2.Improve the Prochot signal quality at the Processor.

R117

R117

10K_J

10K_J

r0402

r0402

12

1 2

1

3 2

XDP_TDO

XDP_TMS

XDP_TDI

XDP_PREQ#

XDP_TCK

XDP_TRST#

XDP_DBRESET#

Q3657

Q3657

LMBT3904LT1G

LMBT3904LT1G

SOT23-3

SOT23-3

R53 51_J r0402R53 51_J r0402

R52 51_J r0402R52 51_J r0402

R60 51_J r0402R60 51_J r0402

R65 51_J nsr0402R65 51_J nsr0402

R54 51_J r0402R54 51_J r0402

R59 51_J r0402R59 51_J r0402

R241 1K_J r0402R241 1K_J r0402

OVT_EC# 25

+1_05VRUN+1_05VRUN

CAD Note: Capacitor need to be placed

close to transistor

R6

R6

1K_J

1K_J

R0402

R0402

1 2

H_PROCHOT#

1 2

1 2

1 2

1 2

1 2

12

1 2

12

C2

C2

47PF/50V,NPO

47PF/50V,NPO

c0402

c0402

+1_05VRUN

+3VRUN

B B

+1_5VSUS

R21

+3VALW

12

C48

1

2

53

4

U4

U4

74AHC1G09GW

74AHC1G09GW

sot353

sot353

ns

ns

C48

0.1UF/10V,X5R

0.1UF/10V,X5R

c0402

c0402

ns

ns

+1_5V_CPU

R72

R72

200_F

200_F

r0402

r0402

1 2

PM_SYS_PWRGD_BUFF

C365

C365

18PF/50V,NPO

18PF/50V,NPO

c0402

c0402

1 2

ns

ns

+3VRUN +1_05VRUN

U12

U12

TC7SZ07F

TC7SZ07F

sot23-5

sot23-5

2

PLT_RST#

PLT_RST#15,25,26,27,31,48

1

A

NC

GND3Y

VCC

4

12

C3

C3

0.1UF/10V,X5R

0.1UF/10V,X5R

R785

c0402

c0402

1 2

R785

75_J

75_J

r0603

r0603

BUF_CPU_RST#

5

4

3

DDR3_DRAMRST#_R

del 0ohm R37 R69

lihong 0723

DRAMRST_CNTRL_PCH8,12

R66

R66

10K_J

10K_J

r0402

r0402

ns

ns

1 2

1P5S_1P8_0P75_PWRGD47

PM_DRAM_PWRGD13

R664 0_J r0402R664 0_J r0402

20111124 by dengrl

5

Q22 footprint SOT23_ld1_h43 -> sot23-3 lihong 0627

1 2

R36 0_J

R36 0_J

nsr0402

nsr0402

S

S

D

D

32

G

G

Q22

Q22

1

BSS138-7

BSS138-7

sot23-3

sot23-3

12

C1

C1

0.047UF/10V,X7R

0.047UF/10V,X7R

c0402

c0402

+3VALW

12

R30

R30

4.99K_F

4.99K_F

r0402

r0402

R132

R132

1K_J

1K_J

r0402

r0402

1 2

2

R21

1K_F

1K_F

r0402

r0402

1 2

R22 1K_F r0402R22 1K_F r0402

12

C332

C332

0.01UF/25V,X7R

0.01UF/25V,X7R

c0402

c0402

12

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A2

A2

A2

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

DDR3_DRAMRST# 20

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Notebook R&D Division

CPU(CLK,MISC,JTAG)

CPU(CLK,MISC,JTAG)

CPU(CLK,MISC,JTAG)

N480

N480

N480

Sheet of

Sheet of

Sheet of

1

Rev

Rev

Rev

1.2

1.2

1.2

5

5

5

A

5

A

U55C

U55C

4

3

U55D

U55D

2

1

AB6

SA_CK[0]

M_A_DQ[63:0]20

D D

C C

B B

M_A_BS020

M_A_BS120

M_A_BS220

M_A_CAS#20

M_A_RAS#20

M_A_WE#20

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

F10

M8

M9

M7

AJ5

AJ6

AJ8

AJ9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

N8

N7

N9

V6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CLK#[0]

SA_CLK#[1]

SA_CLK#[2]

SA_CLK#[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CKE[0]

SA_CK[1]

SA_CKE[1]

SA_CK[2]

SA_CKE[2]

SA_CK[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 20

M_CLK_DDR#0 20

M_CKE0 20

M_CLK_DDR1 20

M_CLK_DDR#1 20

M_CKE1 20

M_CS#0 20

M_CS#1 20

M_ODT0 20

M_ODT1 20

M_A_A[15:0] 20

M_A_DQS#[7:0] 20

M_A_DQS[7:0] 20

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

K9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

R6

J7

J8

J9

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

AE2

SB_CK[0]

SB_CKE[0]

SB_CK[1]

SB_CKE[1]

SB_CK[2]

SB_CKE[2]

SB_CK[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

SB_CLK#[0]

SB_CLK#[1]

SB_CLK#[2]

SB_CLK#[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A3

A3

A3

Date:

Wednesday, September 12, 2012 64

Date:

Wednesday, September 12, 2012 64

Date:

Wednesday, September 12, 2012 64

CPU(DDR3)

CPU(DDR3)

CPU(DDR3)

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.2

1.2

1.2

6

6

6

5

A

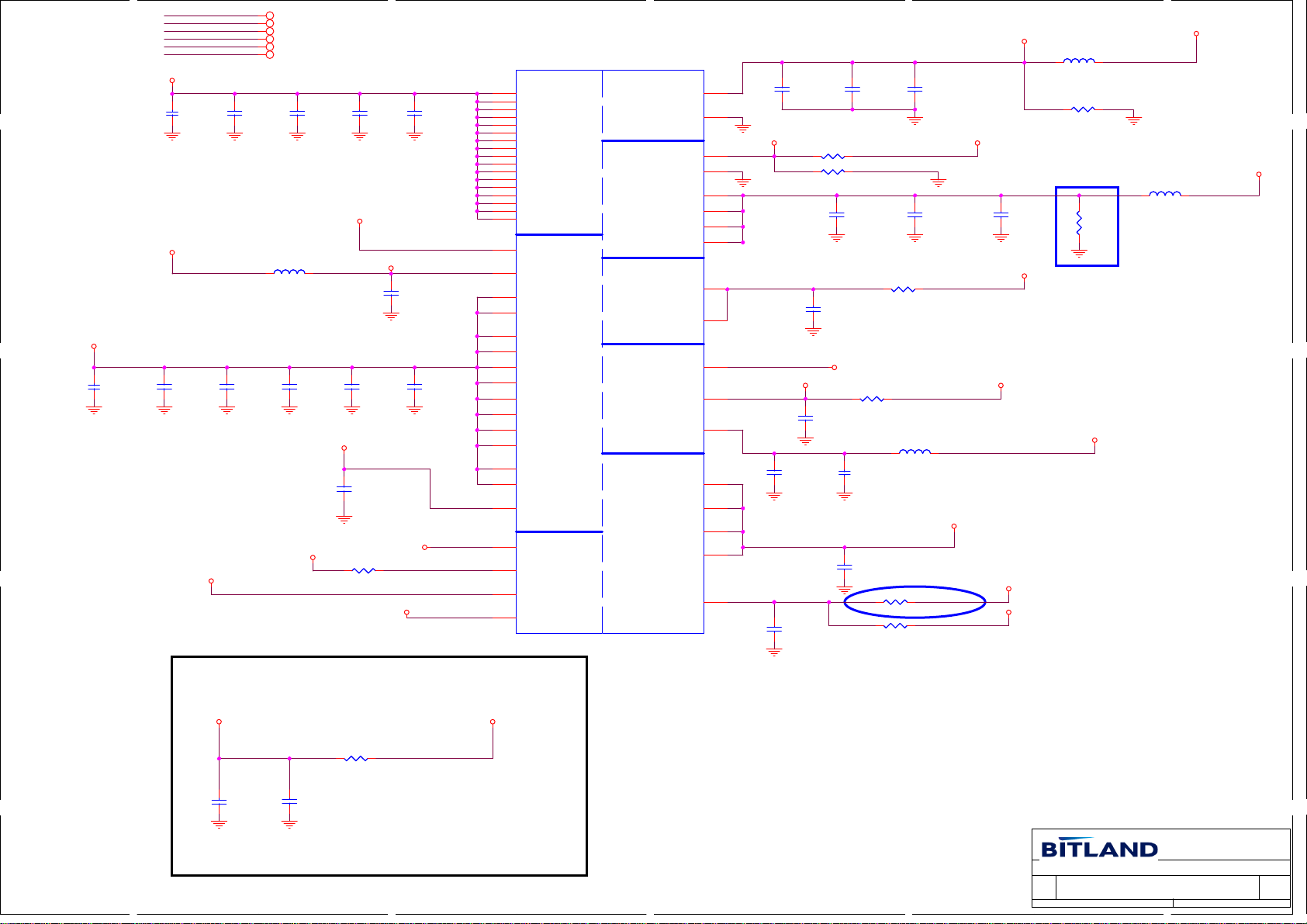

VHCORE 10,42

+1_05VRUN 4,5,11,13,17,18,26,40,42,44,48,49,51,52

4

3

+1_05VRUN

2

1

D D

POWER

POWER

U55F

U55F

94A

VHCORE

12

C14

C14

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C20

C20

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C23

C23

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C4

C4

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C12

C12

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C24

C24

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

VHCORE

12

VHCORE

12

C15

C15

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C21

C21

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C38

C38

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C5

C5

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C22

C22

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C77

C77

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C16

C16

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C13

C13

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C82

C82

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C C

VHCORE

12

C64

C64

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

VHCORE

12

12

C39

C39

C40

C40

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

c0805

c0805

del C44 Power suggest lihong 0517

VHCORE

12

C43

C43

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

VHCORE

B B

C3568

C3568

C3570

C3570

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

C0402_BGA

C0402_BGA

VHCORE

470uF(1002-00254) -> 330uF(1002-00252) lihong 0516

12

12

PC163

PC163

+

+

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

12

PC173

PC173

820uF/2.5V

820uF/2.5V

+

+

Ced_6d3x8

Ced_6d3x8

Decoupling capacitors for +Vcc_CORE rail

[10+1PH] 0805, 10uF (644066-099)

[16+3PH] 0805, 22uF (644066-070)

[4+2PH] 470uF, 4.5mohm ESR (699013-025)

+

+

12

+

+

PC164

PC164

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

PC174

PC174

820uF/2.5V

820uF/2.5V

Ced_6d3x8

Ced_6d3x8

12

+

+

12

+

+

PC187

PC187

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

PC175

PC175

820uF/2.5V

820uF/2.5V

Ced_6d3x8

Ced_6d3x8

12

C41

C41

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

12

C45

C45

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

C3574

C3574

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

+

+

12

+

+

12

12

PC188

PC188

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

PC176

PC176

820uF/2.5V

820uF/2.5V

Ced_6d3x8

Ced_6d3x8

C42

C42

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

C46

C46

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

C3581

C3581

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

C50

C50

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

12

C47

C47

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

colay lihong 0424

VHCORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

PEG AND DDR

PEG AND DDR

CORE SUPPLY

CORE SUPPLY

VSS_SENSE_VCCIO

SENSE LINES SVID

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

VCCP_SENSE

VSSP_SENSE

12

C6

C6

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C28

C28

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

del R39 refer to Compal lihong 0504

+1_05VRUN +1_05VRUN

H_CPU_SVIDALRT#

add R453 R454 lihong 0514

del R453 R454 lihong 0503

del R453 R454 lihong 0724

VCCP_SENSE 40

VSSP_SENSE 40

12

C7

C7

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C29

C29

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

12

R91

R91

130_F

130_F

r0402

r0402

1 2

R81 43_F r0402R81 43_F r0402

CAD Note: Place the PU

resistors close to CPU

12

12

VHCORE

C17

C17

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C30

C30

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

12

PR312

PR312

100_F

100_F

r0402

r0402

12

PR313

PR313

100_F

100_F

r0402

r0402

VCCSENSE 42

VSSSENSE 42

Remove C18

C7 NC->Stuff

lihong 0722

12

C8

C8

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

12

C32

C32

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

R89

R89

75_F

75_F

r0402

r0402

1 2

VR_SVID_ALERT# 42

VR_SVID_CLK 42

CAD Note: Place the PU

resistors close to CPU

12

C34

C34

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

VR_SVID_DATA 42

C3617

C3617

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

C9

C9

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C31

C31

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C3618

C3618

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

C10

C10

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C33

C33

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C3619

C3619

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

C19

C19

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

C35

C35

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

C3620

C3620

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

+1_05VRUN

8.65A

12

C11

C11

Decoupling capacitors for Vccp rail

22uF/6.3V,X5R

22uF/6.3V,X5R

[12+17PH] 0805, 22uF (644066-070)

c0805

c0805

[2+1PH] 330uF, 6mohm ESR (699013-021)

ns

ns

+1_05VRUN

12

C36

C36

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

12

Move PC95 PC214 to PWM side lihong 0518

C37

C37

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

PC95 PC214 colay in top side lihong 0509

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A2

A2

A2

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

5

4

3

2

Notebook R&D Division

CPU(POWER)

CPU(POWER)

CPU(POWER)

N480

N480

N480

Sheet of

Sheet of

Sheet of

1

7

7

7

A

Rev

Rev

Rev

1.2

1.2

1.2

5

A

4

3

2

1

GFXCORE +VCCSA

C3621

C3621

C3622

C3622

C3623

C3623

C3624

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

C0402_BGA

C0402_BGA

iGPU

iGPU

iGPU

iGPU

D D

GFXCORE

38A

12

C53

C53

22uF/6.3V,X5R

R3

R3

0_J

0_J

r0402

r0402

GPU

GPU

1 2

C C

+1_8VRUN

0.93A

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

C58

C58

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

C83

C83

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

del reserved PC229 PC304

Decoupling capacitors for +Vcc_gfxcore rail

[12+4PH] 0805, 22uF (644066-070)

[2+2PH] 470uF, 4.5mohm ESR (699013-025)

del R7 lihong 0503

B B

12

12

C54

C54

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

12

C59

C59

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

12

C315

C315

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

12

12

PC302

PC302

+

+

+

+

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

12

12

PC177

PC177

820uF/2.5V

820uF/2.5V

+

+

+

+

Ced_6d3x8

Ced_6d3x8

iGPU

iGPU

12

C196

C196

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

ns

ns

Co_lay

C88 ns lihong 0423

PC90(7343) C88(3528)->3528 0805 lihong 0502

C3624

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

C0402_BGA

C0402_BGA

iGPU

iGPU

iGPU

iGPU

12

C55

C55

C51

C51

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

c0805

c0805

iGPU

iGPU

iGPU

iGPU

12

C60

C60

C61

C61

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

c0805

c0805

iGPU

iGPU

ns

ns

12

C316

C316

C381

C381

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

c0805

c0805

iGPU

iGPU

ns

ns

470uF(1002-00254) ->

PC303

PC303

330uF/2V

330uF/2V

tc7343

tc7343

ns

ns

PC185

PC185

820uF/2.5V

820uF/2.5V

Ced_6d3x8

Ced_6d3x8

iGPU

iGPU

12

330uF(1002-00252) lihong 0516

colay lihong 0424

12

C90

C90

C197

C197

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

c0805

c0805

ns

ns

+1_5V_CPU

C3625

12

C56

C56

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

C89

C89

1uF/6.3V,X5R

1uF/6.3V,X5R

c0402

c0402

C3625

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

C3626

C3626

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

12

C52

C52

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

C62

C62

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

iGPU

iGPU

12

C63

C63

22uF/6.3V,X5R

22uF/6.3V,X5R

c0805

c0805

ns

ns

C91 C89 1uF/25V -> 1uF/6.3V

lihong 0502

12

C91

C91

1uF/6.3V,X5R

1uF/6.3V,X5R

c0402

c0402

C3628

C3628

0.1UF/10V,X5R

0.1UF/10V,X5R

C0402_BGA

C0402_BGA

U55G

U55G

AT24

VAXG1

AT23

VAXG2

AT21

VAXG3

AT20

VAXG4

AT18

VAXG5

AT17

VAXG6

AR24

VAXG7

AR23

VAXG8

AR21

VAXG9

AR20

VAXG10

AR18

VAXG11

AR17

VAXG12

AP24

VAXG13

AP23

VAXG14

AP21

VAXG15

AP20

VAXG16

AP18

VAXG17

AP17

VAXG18

AN24

VAXG19

AN23

VAXG20

AN21

VAXG21

AN20

VAXG22

AN18

VAXG23

AN17

VAXG24

AM24

VAXG25

AM23

VAXG26

AM21

VAXG27

AM20

VAXG28

AM18

VAXG29

AM17

VAXG30

AL24

VAXG31

AL23

VAXG32

AL21

VAXG33

AL20

VAXG34

AL18

VAXG35

AL17

VAXG36

AK24

VAXG37

AK23

VAXG38

AK21

VAXG39

AK20

VAXG40

AK18

VAXG41

AK17

VAXG42

AJ24

VAXG43

AJ23

VAXG44

AJ21

VAXG45

AJ20

VAXG46

AJ18

VAXG47

AJ17

VAXG48

AH24

VAXG49

AH23

VAXG50

AH21

VAXG51

AH20

VAXG52

AH18

VAXG53

AH17

VAXG54

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

POWER

POWER

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

VREFMISC

GRAPHICS

GRAPHICS

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

1.8V RAIL

1.8V RAIL

VCCIO_SEL

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

del PC90 C88 lihong 0509

add C196 C197 place near CPU lihong 0514

PROCESSOR DRIVEN Vref PATH WAS STUFFED BY DEFAULT:

1 2

R251 0_J

R251 0_J

nsr0402

nsr0402

删除Q42及预留的R252 R5385 lihong 0516

no DDR_WR_VREF01

GFXCORE 10,42

+1_5V_CPU 5,17,27,43,44,47,51,55,56,57

+1_5VSUS 5,20,39,43,57

+VCCSA 41

+1_8VRUN 16,17,40,43,44,47,49,51,52

+3VALW 5,11,12,13,15,16,17,18,23,25,26,27,31,35,38,39,43,44,47

+1_5V_CPU 5,17,27,43,44,47,51,55,56,57

add R532 R658 lihong 0514

del R532 R658 lihong 0503

AK35

AK34

AL1

B4

DDR_WR_VREF01

D1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

A19

Provides 1.0/1.05V selectable via VCCIO_SEL

refer EDS PR235 should NC for chief river lihong

1 2

R532 R04020_J iGPUR532 R04020_J iGPU

1 2

R658 R04020_J iGPUR658 R04020_J iGPU

12

C65

C65

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

12

C72

C72

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

VCCSA_SENSE

H_VCCP_SEL

PR235 100k_J nsr0402PR235 100k_J nsr0402

del 0ohm R470

lihong 0723

+V_SM_VREF_CNT

CAD Note: All traces starting with

+V_SM_VREF* and DDR_WR_VREF*

should have 20:20mils wherever possible

12

12

C66

C66

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

12

12

C73

C73

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

1 2

GFX_VCC_SENSE 42

GFX_VSS_SENSE 42

12

C67

C67

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

+VCCSA

4.5A

T

T

C74

C74

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

C139 ns lihong 0423

C139 7343->3528 in top side lihong 0424

VCCSA_SELECT0 41

VCCSA_SELECT1 41

12

C68

C68

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

实测电流值(SNB)0.3857A lihong 0720

1

20MIL

20MIL

TP130

TP130

12

Decoupling capacitors for +VccSA rail

C139

C139

[1PH] 0603, 10uF (602433-075)

220UF/2.5V

220UF/2.5V

+

+

[3] 0805, 10uF (644066-099)

TC3528

TC3528

[1] 330uF, 6mohm ESR (699013-021)

ns

ns

+3VALW

C69

C69

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

ictpad_c20

ictpad_c20

R515

R515

0_J

0_J

r0402

r0402

ns

ns

12

C70

C70

10uF/6.3V,X5R

10uF/6.3V,X5R

c0805

c0805

VCCSA_SENSE 41

+1_5V_CPU

12

C75

C75

0.1UF/10V,X5R

0.1UF/10V,X5R

c0402

c0402

1 2

1 2

max 5A

+V_SM_VREF_CNT

S3 circuit:- 1.5V input to IVB is gated

& IVB Read Vref 0.75V is gated

+1_5V_CPU

move C71 to Page39 lihong 0509

Function

SNB HIGH

IVB HIGH

xxVccSA_Select[1]

[[CPU PIN# C24

VID0 of VR ]]

0

0

PR128

PR128

1K_F

1K_F

r0402

r0402

PR139

PR139

1K_F

1K_F

r0402

r0402

dengrl

xxVccSA_Select[0]

[[CPU PIN# C22

VID1 of VR ]]

0

1

VCCSA VR Vout

0.90V

0.725V

S

S

D

D

DDR_WR_VREF01

R5384

R5384

1K_J

1K_J

r0402

r0402

ns

ns

1 2

DRAMRST_CNTRL_PCH5,12

5

32

G

G

Q41

Q41

AO3424

AO3424

1

sot23-3

sot23-3

DDR_WR_VREF01_B4 20,57

Q41 footprint sot23_ld1_lp20 -> sot23-3 lihong 0620

CAD Note: Route with min.

trace width of 10 mils

0.1uF capacitors need to be placed

as close as possible to voltage divider

The FETs are needed in order to avoid potential leakage while system is in S3 state

DRAMRST_CNTRL signal and FETs (with low Rdson) are required for S3 Power Reduction

Circuitry. If the S3 Power Reduction Circuit isn’t implemented than these FETs can be

unstuffed and R251 and R252 would have to be stuffed

4

3

SNB LOW

IVB LOW

2

1

1

0

1

0.80V

0.675V

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A2

A2

A2

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Notebook R&D Division

CPU(GRAPHICS POWER)

CPU(GRAPHICS POWER)

CPU(GRAPHICS POWER)

N480

N480

N480

Sheet of

Sheet of

Sheet of

1

A

Rev

Rev

Rev

1.2

1.2

1.2

8

8

8

5

A

4

3

2

1

D D

C C

B B

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

U55H

U55H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

M34

H33

H30

H27

H24

H21

H18

H15

H13

H10

G35

G32

G29

G26

G23

G20

G17

G11

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

L33

L30

L27

K35

K32

K29

K26

J34

J31

F34

F31

F29

U55I

U55I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS

VSS

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A3

A3

A3

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

CPU(GND)

CPU(GND)

CPU(GND)

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

A

Rev

Rev

Rev

1.2

1.2

1.2

9

9

9

5

A

4

3

GFXCORE 8,42

VHCORE 7,42

U55E

U55E

2

1

D D

C C

B B

GFXCORE

R200

R200

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

R198

R198

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

CFG2 1:(Default) Normal Operation; Lane # definition matches

socket pin map definition

CFG2 0:Lane Reversed

CFG2

12

R55

R55

1K_F

1K_F

r0402

r0402

ns

ns

CGF[6:5]

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG6 CFG5

12

R57

R57

1K_F

1K_F

r0402

r0402

ns

ns

CFG7 1: (Default) PEG Train immediately following xxRESETB de assertion

CFG7 0: PEG Wait for BIOS for training

CFG7

12

R62

R62

1K_F

1K_F

r0402

r0402

ns

ns

R184

R184

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

CAD NOTE:Floating for probe use,

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

12

R58

R58

1K_F

1K_F

r0402

r0402

ns

ns

VHCORE

R191

R191

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

R174

R174

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

VAXG_VAL_SENSE

R149

R149

49.9_F

49.9_F

r0402

r0402

ns

ns

1 2

VSSAXG_VAL_SENSE

TP_H_CPU_RSVD3

TP_H_CPU_RSVD4

CAD NOTE:Floating for probe use,

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

Ivy_Bridge_rPGA_Rev0p7

Ivy_Bridge_rPGA_Rev0p7

mpga989_mcp_skt_37-5mm_sq_HR

mpga989_mcp_skt_37-5mm_sq_HR

CFG

CFG

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RESERVED

RESERVED

RSVD_NCTF8

RSVD_NCTF9

RSVD_NCTF10

BCLK_ITP#

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD51

RSVD52

BCLK_ITP

KEY

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

CLK_XDP_ITP_P

CLK_XDP_ITP_N

1

1

TP45 20MIL ictv20_10TP45 20MIL ictv20_10

TP133 20MIL ictv20_10TP133 20MIL ictv20_10

1

TP40 20MIL ictv20_10TP40 20MIL ictv20_10

1

TP41 20MIL ictv20_10TP41 20MIL ictv20_10

CFG4

12

CGF4 1:Disabled; No Physical Display Port

R56

R56

1K_J

1K_J

attached to Embedded Display Port

r0402

r0402

ns

ns

CGF4 0:Enabled; An external Display Port device

is connected to the Embedded Display Port

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

A3

A3

A3

Date:

Date:

Date:

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

Wednesday, September 12, 2012 64

CPU(RESERVED)

CPU(RESERVED)

CPU(RESERVED)

Notebook R&D Division

N480

N480

N480

Sheet of

Sheet of

Sheet of

10

10

10

Rev

Rev

Rev

A

1.2

1.2

1.2

5

A

+ECVCC 25,26,35,37,38

VCCRTC 13,18,25

+3VRUN 5,12,13,14,15,16,17,18,20,22,23,25,26,27,30,31,32,34,35,36,39,40,41,42,43,44,47,48,49,51,53

+5VRUN 12,18,22,25,29,30,32,34,35,40,42,43

+3VALW 5,8,12,13,15,16,17,18,23,25,26,27,31,35,38,39,43,44,47

+1_05VRUN 4,5,7,13,17,18,26,40,42,44,48,49,51,52

D D

1

RTC1

2

3

4

CN1

CN1

cns2_1d25_r

cns2_1d25_r

85204-02001

85204-02001

+3VALW

12

R269

R269

1K_J

1K_J

r0402

r0402

C C

Q19 Q20 footprint SOT23_ld1_h43 -> sot23-3 lihong 0627

IHDA_SYNC

IHDA_SDATAO

D1 footprint sot23_ld1_lp20 -> sot23-3 lihong 0620

+ECVCC

1

VCCRTC

W=20mils

1 2

R75 1K_J r0402R75 1K_J r0402

2

D1

D1

LBAT54CLT1G

LBAT54CLT1G

sot23-3

sot23-3

3

12

C96

C96

1uF/6.3V,X5R

1uF/6.3V,X5R

c0402

c0402

INTVRMEN

H:Integrated VRM enable

L:Integrated VRM disable

INTVRMEN should always be pull high

+3VRUN

+5VRUN

1

3 2

D

D

Q19

Q19

BSS138-7

BSS138-7

sot23-3

sot23-3

1 2

R101 0_J nsr0402R101 0_J nsr0402

+5VRUN

1

3 2

D

D

Q20

Q20

BSS138-7

BSS138-7

sot23-3

sot23-3

1 2

R226 0_J nsr0402R226 0_J nsr0402

12

R237

R237

10K_J

10K_J

r0402

r0402

ns

+3VRUN

12

12

R239

R239

10K_J

10K_J

r0402

r0402

ns

ns

ns

1 2

R189 33_J r0402R189 33_J r0402

R455

R455

1M_J

1M_J

r0402

r0402

1 2

R223 33_J r0402R223 33_J r0402

G

G

S

S

G

G

S

S

12

HDA_CODEC_SYNC 30

HDA_CODEC_SDATAOUT 30

4

R79 0_J r0402R79 0_J r0402

VCCRTC

del 0ohm R82

lihong 0723

1

TP17

TP17

1

TP18

TP18

1

TP19

TP19

1

TP20

TP20

1

TP22

TP22

SPI_CLK

SPI_CS#0

SPI_CS#1

SPI_MOSI

SPI_MISO

CO- LAYOUT

12

1 2

1 2

R80 330K_F r0402R80 330K_F r0402

20110712

20110621

The traces inside this

1 2

C95 15PF/50V,NPO c0402C95 15PF/50V,NPO c0402

1 2

C98 15PF/50V,NPO c0402C98 15PF/50V,NPO c0402

1 2

R76 20K_F r0402R76 20K_F r0402

1 2

R77

R77

1M_J

1M_J

R78 20K_J r0402R78 20K_J r0402

r0402

r0402

CRB 20K

12

C97

C97

1uF/6.3V,X5R

1uF/6.3V,X5R

c0402

c0402

12

C99

C99

1uF/6.3V,X5R

1uF/6.3V,X5R

c0402

c0402

block should be wider.

RTC_32KX1

4

Y2

Y2

32.768KHZ

32.768KHZ

y_4p_smd8038

y_4p_smd8038

1

2 3

RTC_32KX2_R

21

GP1

GP1

OPEN_JUMP_OPEN2

OPEN_JUMP_OPEN2

OPEN2

OPEN2

HDA_SPKR30

HDA_CODEC_SDATAIN030

20MIL

20MIL

ictv20_10

ictv20_10

20MIL

20MIL

ictpad_c20

ictpad_c20

20MIL

20MIL

ictpad_c20

ictpad_c20

20MIL

20MIL

ictpad_c20

ictpad_c20

20MIL

20MIL

ictpad_c20

ictpad_c20

NOTE:Use one 33- Ω series-resistor per device if using

two SPI devices and place it close to the devices.

No series-resistor required if a single device is used.

Y6

Y6

y_4p_smd7014