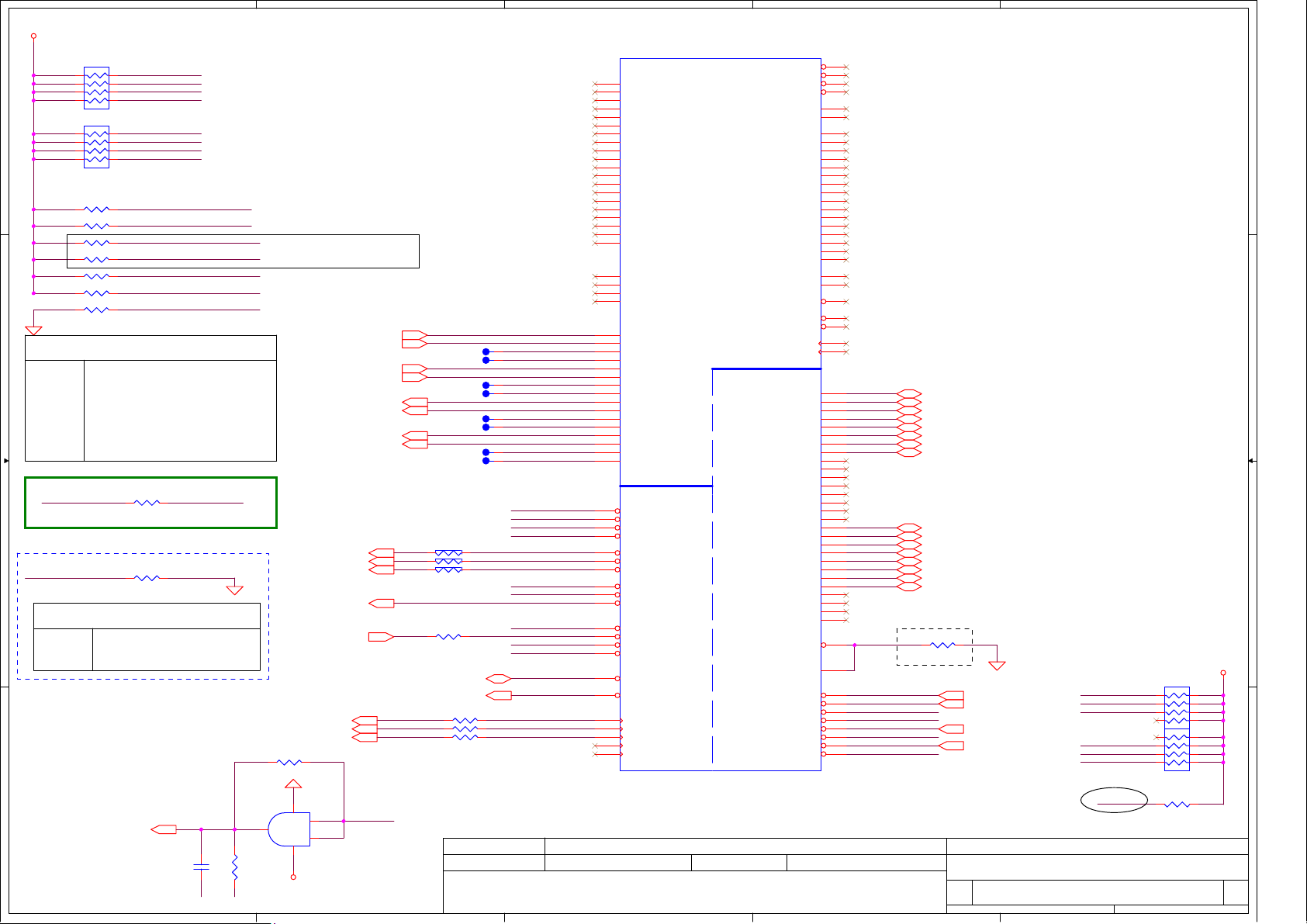

LENOVO G580 Schematics

A

B

C

D

E

1

1

Compal Confidential

2

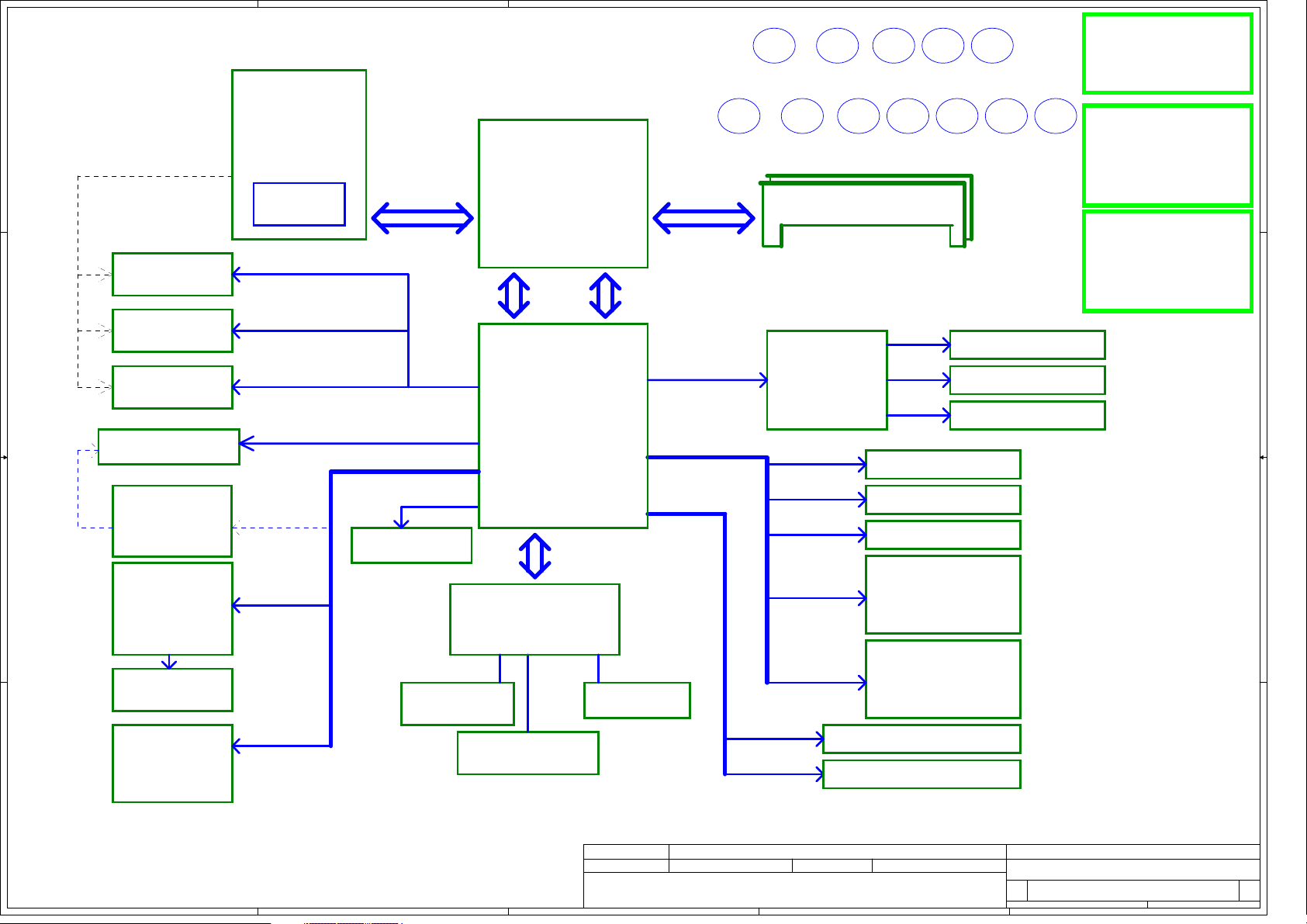

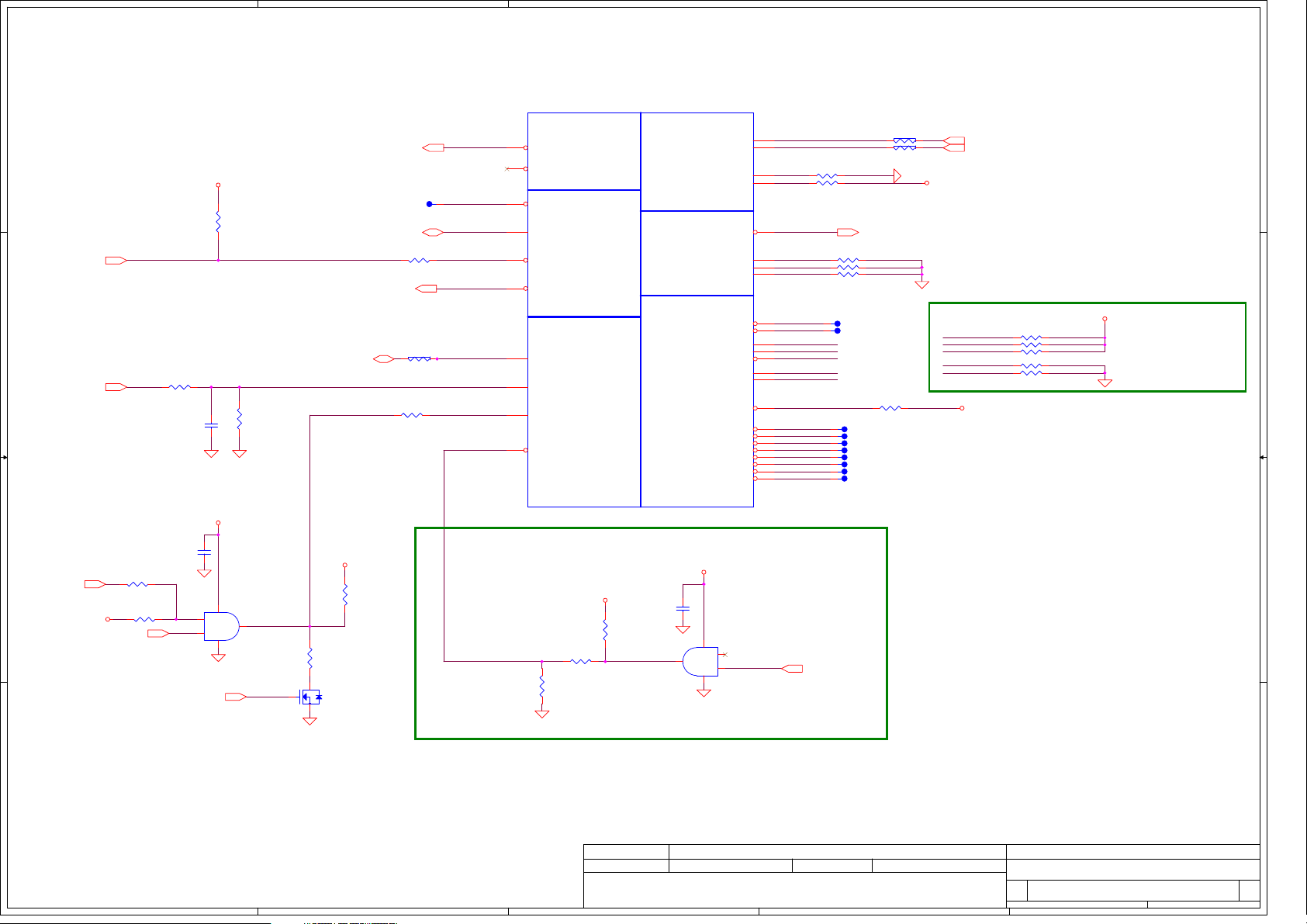

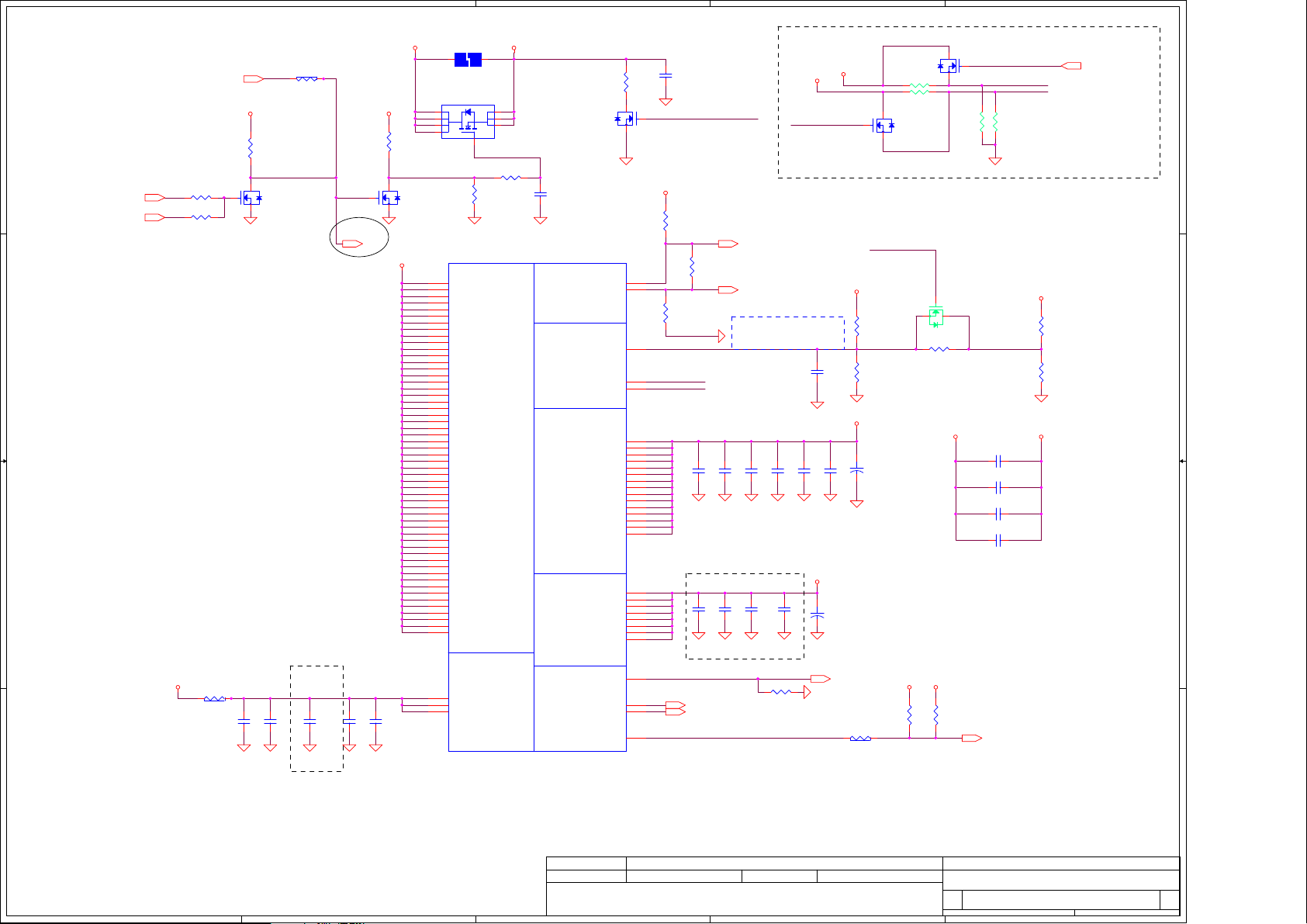

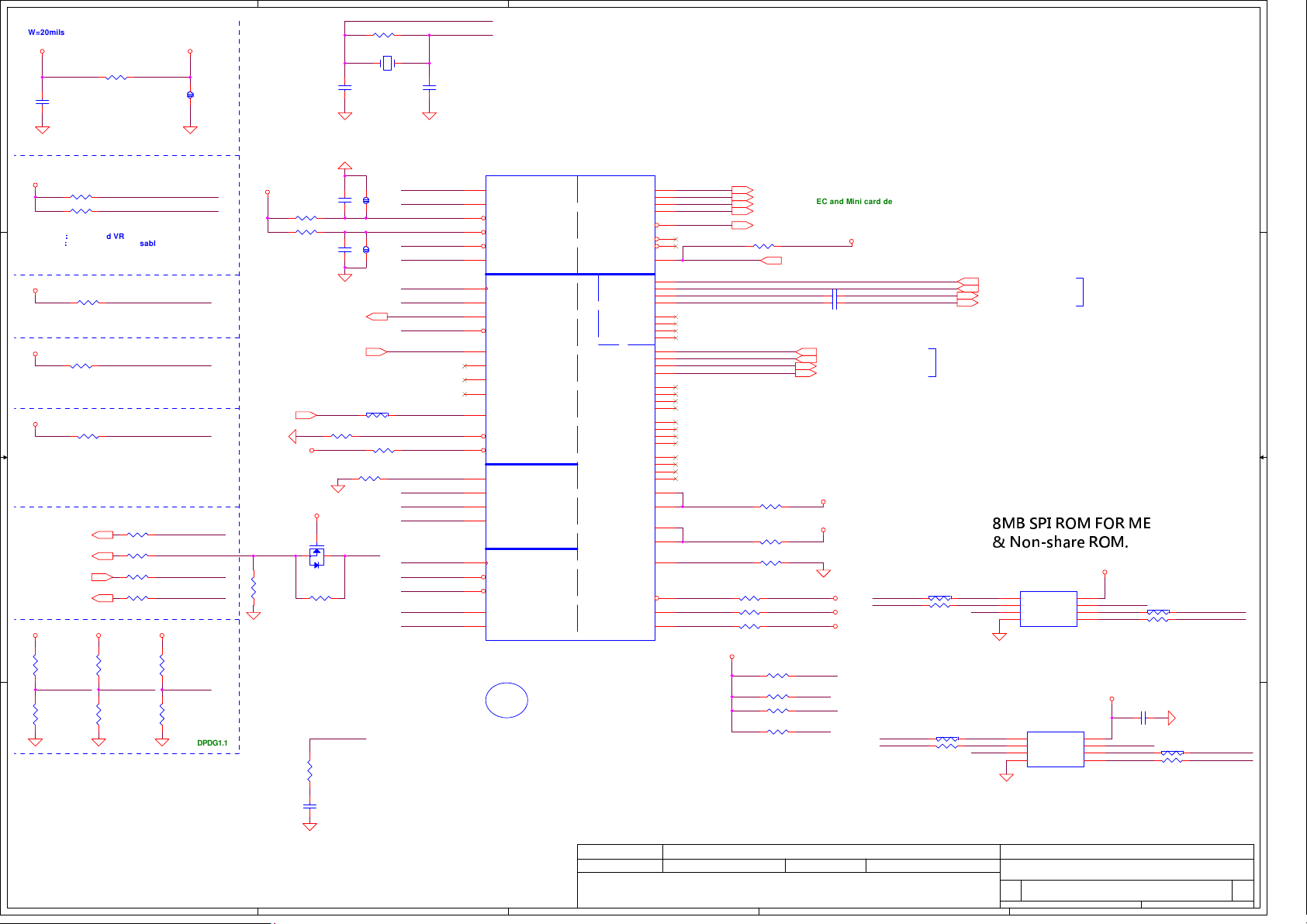

QIWG5/QIWG6 DIS M/B Schematics Document

Intel Ivy Bridge Processor with DDRIII + Panther Point PCH

nVIDIA N13X

2012-05-21

2

3

3

LA-7986P

REV:1.0

4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

LA-7986P

E

1 62Wedn esday, August 08, 2012

of

4

1.0

A

Compal confidential

File Name : QIWG5/QIWG6

1

HDMI

Connector

CRT

2

Connector

LVDS

Connector

USB3.0 *2(Left)

Option

USB3.0

Renesas

uPD720202

3

Arthros

AR8161(GLAN)

AR8162(10/100)

RJ-45

Connector

PCI Express

Mini Card Slot *1

WLAN

4

nVIDIA N13M-GE

VIDIA N13P-GL

n

VR A M 1 2 8* 1 6

Page35

Page34

P

age33

Page45

Page37

Page38

PCI-E(WLAN)

Page36

Page23-32

DD R3 *8

B

PCI-E x16

PCI-E x1 *6

SPIROM

BIOS

Page14

Touch Pad Int. KBD

Ivy Bridge

Socket-rPGA988B

37.5mm*37.5mm

100MHz

2.7GT/s

Panther Point

HM75 / HM76

EC

ENE KB9012

Page43

Thermal Sensor

EMC1403

Intel

Page5-11

FDI *8

Intel

FCBGA 989

25mm*25mm

Page14-22

LPC BUS

Page42

Page39

C

Dual Channel

DDR3 1066MHz(1.5V)

DDR3 1333MHz(1.5V)

DDR3 1600MHz(1.5V)

DMI *4

AZALIA

USB2.0 *14

SATA *6

Page43

ZZZ 5

LA7986

15@

DAZ_PCB

DAZ0N200501

D

ZZ Z

LA7986

14@

DAZ_PCB

DAZ0N100601

ZZZ 7

G6_DA@

DA_PCB

DA80000SU00

ZZZ 1

G5_DA@

DA_PCB

DA80000SU00

ZZZ 6

G6_DA@

DA_PCB

DA400016P10

ZZZ 2

G5_DA@

DA_PCB

DA400016P10

ZZZ 8

G6_DA@

DA_PCB

DA400016Q10

DDR3 SO-DIMM *2

BANK 0, 1, 2, 3

Up to 8GB

Audio Codec

Conexant

CX20671-21Z

Page41

Camera Conn.

BlueTooth Conn.

Mini Card Slot *1

Card Reader

Reltek

RTS5178 for SDR50

SDXC/MMC

USB2.0 *2(Right)

USB2.0 *2(Left)

SATA HDD

SATA ODD

ZZZ 3

G5_DA@

DA_PCB

DA400016Q10

ZZZ 9

G6_DA@

DA_PCB

DA400016R10

Page12-13

ZZZ 4

G5_DA@

DA_PCB

DA400018T10

ZZZ1 0

G6_DA@

DA_PCB

DA400016S10

2 channel speaker

Int. MIC x1

Audio Jacks

Page33

Page40

Page36

Page43

Page 43;44

Page45

Page40

P

age40

ZZZ1 1

G6_DA@

DA_PCB

DA400018T10

Page41

Page41

Page43

(Port 0/Port 1 support SATA3)

E

QIWG5

LS7986P CardReader/B

LS7982P USB/B

LS7983P PWR/B

QIWG6

LS7986P CardReader/B

LS7982P USB/B

LS7983P PWR/B

LS7984P LED/B

LS7985P ODD/B

QIWG9

LS7986P CardReader/B

LS7982P USB/B

L

S7983P PWR/B

LS8612P LED/B

LS7985P ODD/B

1

2

3

4

www.schematic-x.blogspot.com

A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet

Compal Electronics, Inc.

Block Diagram

LA-7986P

E

2 62Wedn esday, August 08, 2012

1.0

of

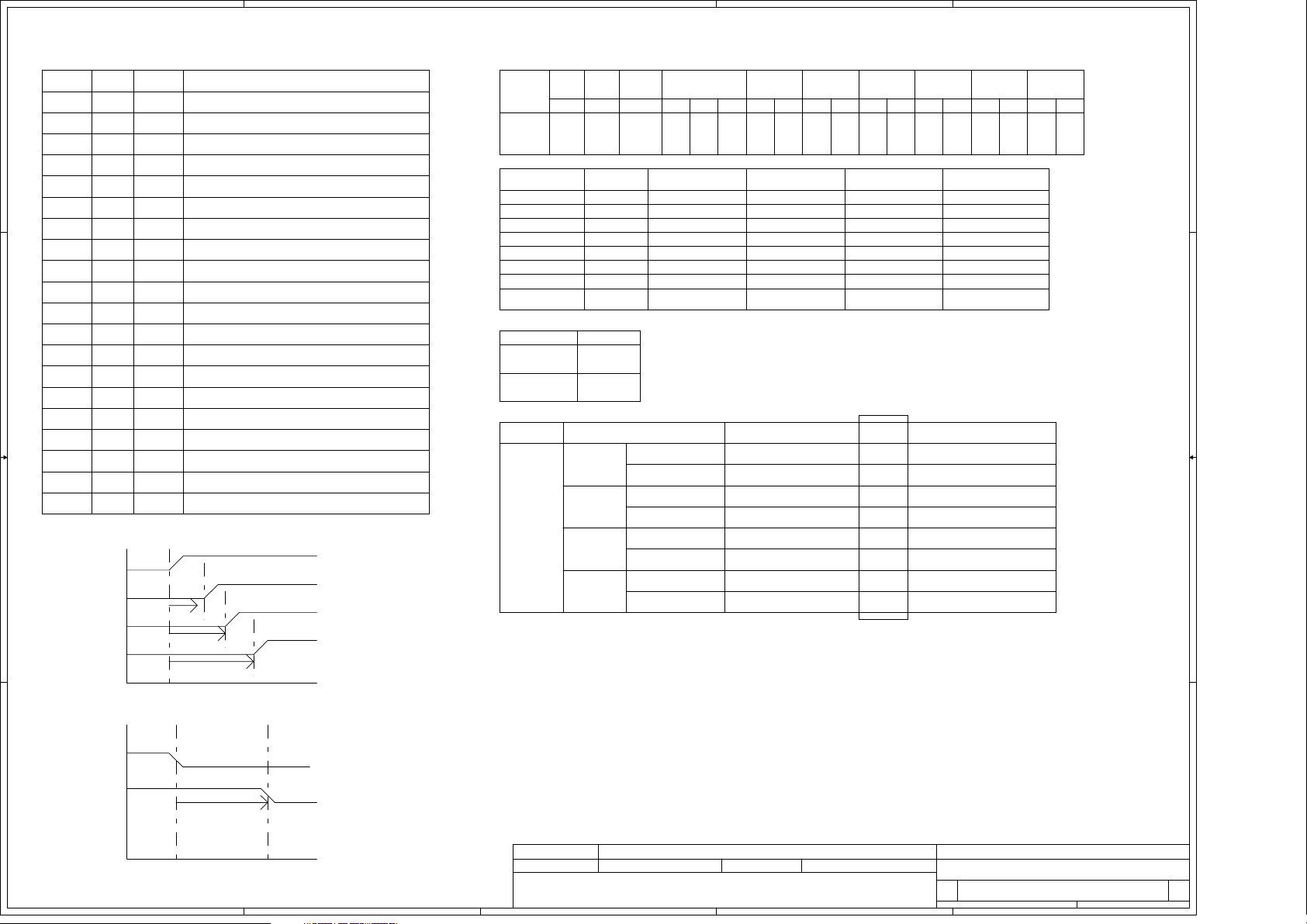

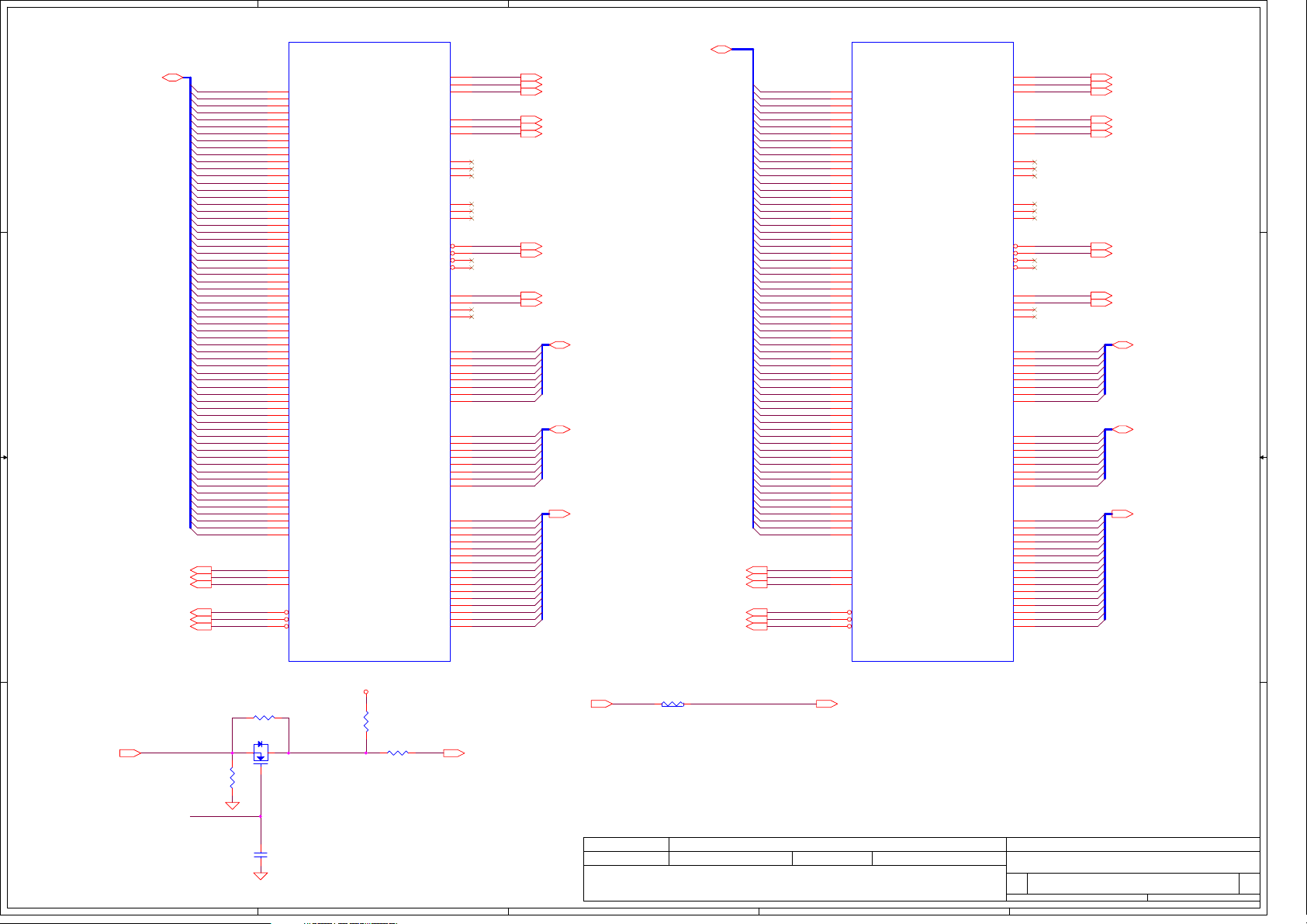

Voltage Rails

power

1

2

S5 S4/ Battery only

S5 S4/AC & Battery

do

n't exist

plane

State

S0

S3

S5 S4/AC

EC SM Bus1 address

Device

Smart Battery

PCH SM Bus address

Device Address

DDR D IMM0

3

DDR D IMM2

NV-GPU SM Bus address

Device Address

Internal thermal sensor

A

Address

000 1 011 X b

+B

O

O

O

O

X

100 1 000 Xb

100 1 010 Xb

100 1 111 Xb (0x9E )

B

+5VALW

+3VALW

+1.5V

+VCC_GFXCORE_AXG

O

O

O

X

O

X X

X

X X X

EC SM Bus2 address

Device

Thermal Sensor F75303M

Address

100 1_101 xb

+5VS

+3VS

+1.5VS

+V1.05S_VCCP

+VCC_CORE

+VGA_CORE

+1.8VS

+0.75VS

+1.05VS

OO

X

X

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

USB Port Table

USB 2.0

UHCI0

EHCI1

USB3.0

EHCI2

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

C

PCB Revision

0.1

Port

0

USB Port (Right Side CR-BD)

1

2

USB Port (Left Side)

3

USB Port (Left Side)

4

5

Camera

6

7

8

USB/B (Right Side USB-BD)

9

10

Mini Card(WLAN)

11

Card Reader

12

13

Blue Tooth

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

3 External

USB Port

D

STATE

Full ON

S1(P ower On Suspend)

S3 ( Suspend to RAM)

S4 ( Suspend to Disk)

S5 ( Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

USB 3.0

USB 3.0

E

SLP_S4#

SLP_S5#

HIGH HIGH HIGH H IGH

LOW

LOW

LOW

HIGH

LOWLOWLOW

LOW LOW LOW LOW

HIGHHIGHHIGH

HIGH

HIGH

+VALW

ON

ON

ON

ON

ON

+V

ONONON ON

ON

OFF

OFF

Board ID / SKU ID Table for AD channel

AD_BID

V typ

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

V

max

AD_BID

0 V 0 V

0.538 V

0.875 V

2.341 V

3.300 V

BOM Structure Table

BTO Item BOM Structure

N13P@ GPU:N13P-GL

HDMI HDMI@

Interna-Intel-USB3.0 IU3@

External-NEC-USB3.0 EU3@

Blue Tooth BT@

Connector ME@

45 LEVEL 45@

10/100 LAN 8162@

GIGA LAN GIGA@

LAN LDO Mode LDO@

LAN Switch mode SWR@

Cameara CMOS@

For QIWG5 (14") 14@

For QIWG6 (15") 15@

Unpop

G5/G6/G9(Low/Mid END)

G9 High-END

G9

G5/G6/G9(Low/Mid END) 15_nonBBH@

N13M@GPU:N13M-GE

@

nonBBH@

BBH@

G9 @

+VS

Clock

ON

LOW

OFF

OFF

OFF

OFF

OFF

OFF

Porject Phase

G-ser ies

MP

G-ser ies

PVT

G-ser ies

DVT

G-ser ies

EVT

Y-ser ies

EV

Y-ser ies

DVT

Y-ser ies

PVT

Y-ser ies

MP

1

T

2

3

SMBUS Control Table

SOURCE

4

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

KB9012

+3VALW

KB9012

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

VGA BATT KB9012 SODIMM

X V

+3VALW

X

X

X

V

+3VS

A

X

X

X

X

X

X

V

+3VS

X

X

V

+3VS

X

WLAN

WWAN

X

XX

V

+3VS

X

B

Thermal

Sensor

X

X

X

XX

V

+3VS

PCH

X

V

+3VS

X

X

XX X

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

Compal Secret Data

Deciphered Date

D

Title

Size Doc ument Number Re v

B

LA-7986P

Date: Sheet

Compal Electronics, Inc.

Notes List

of

3 62Wedn esday, August 08, 2012

E

4

1.0

5

4

3

2

1

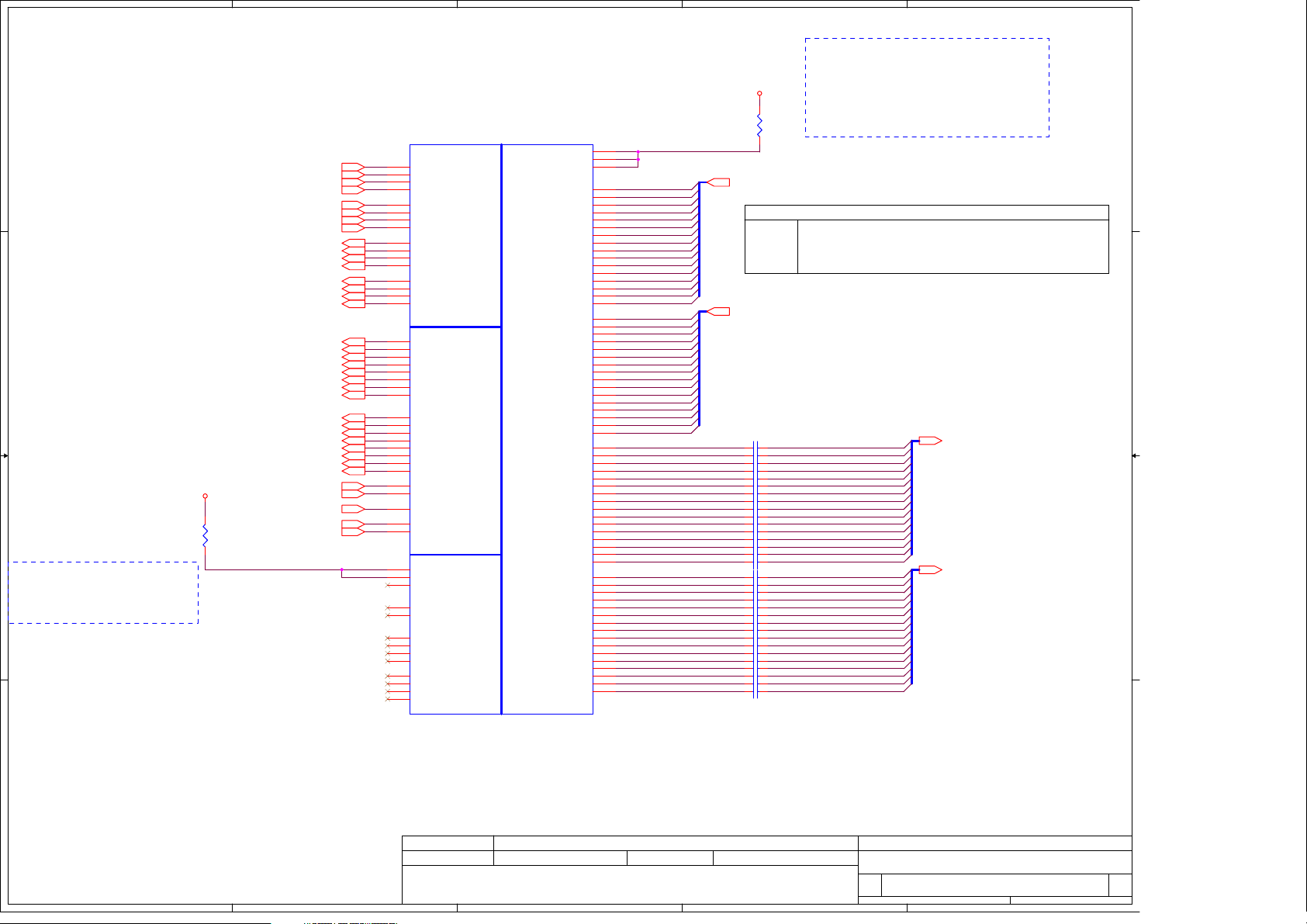

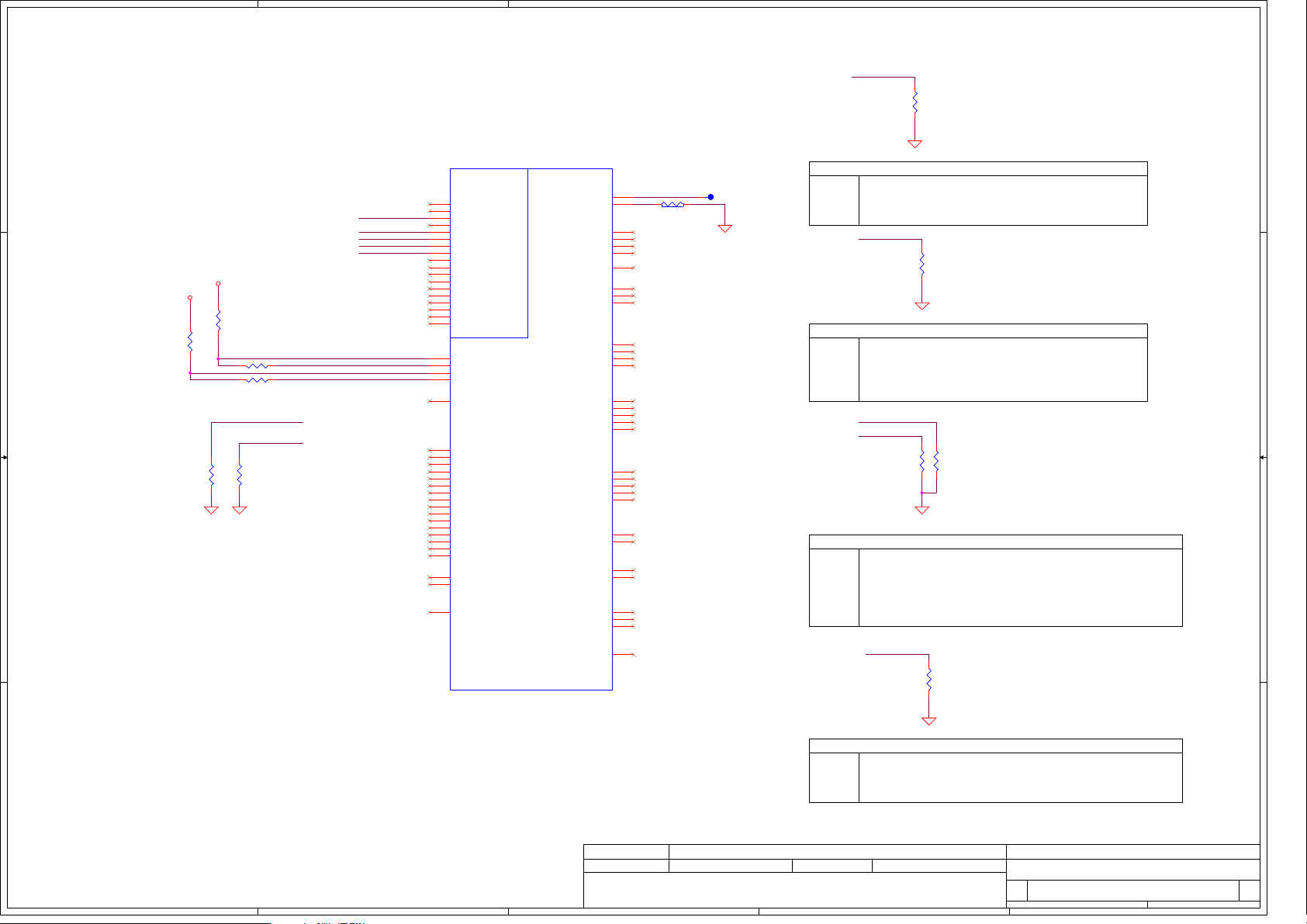

Hot pl ug detect for IFP link C

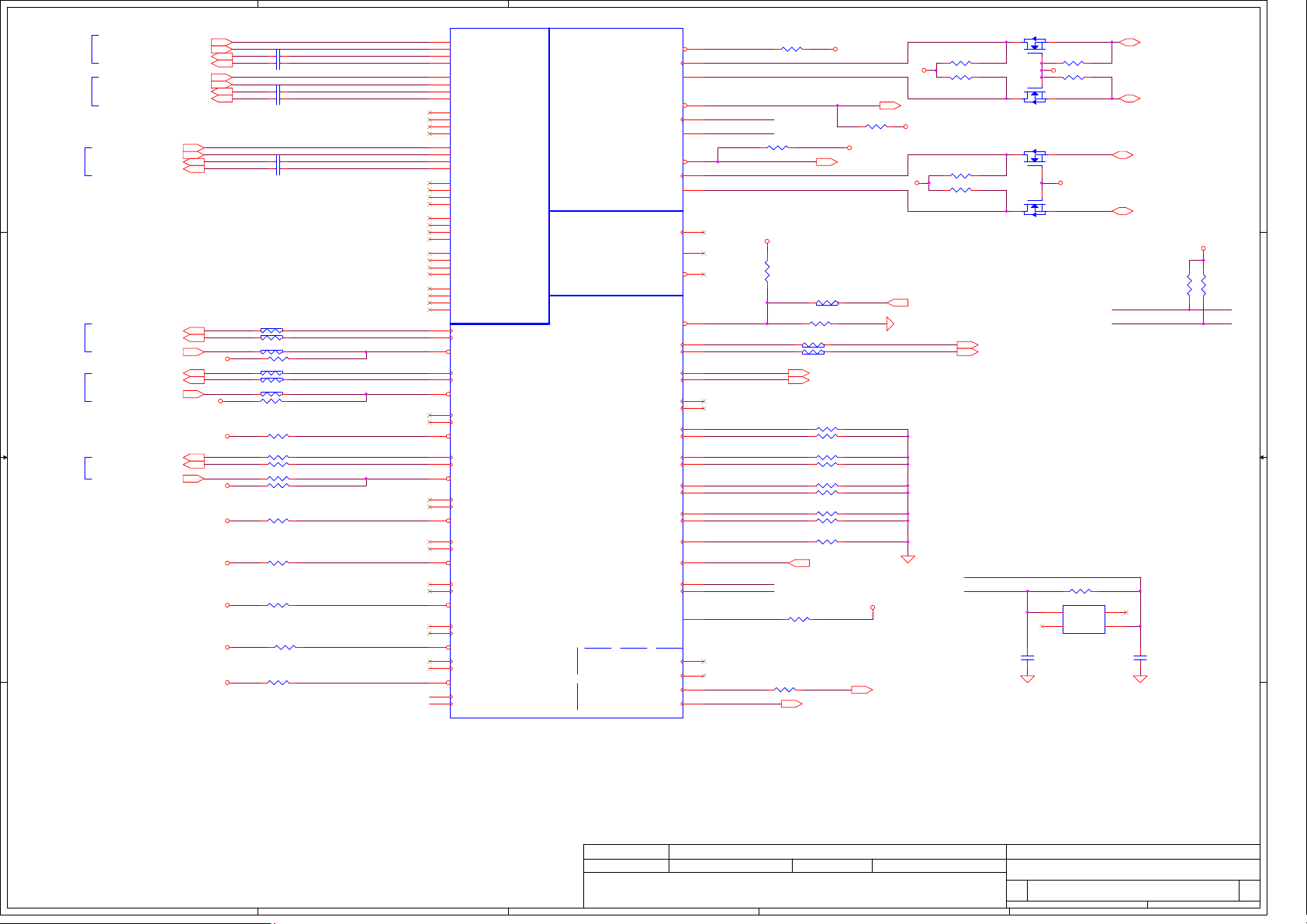

VGA and GDDR3 Voltage Rails (N13x GPIO)

GPIO I/O ACTIVE Function Description

GPIO0

D

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

C

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

B

+1.05 VS_VGA

OUT GPU VID4-

OUT

OUT

OUT

OUT

OUT

OUT

I/O

OUT

OUT

IN

OUT

OUT

IN

OUT

IN

IN

IN

+3VS_VG A

+VGA_ CORE

+1.5V S_VGA

-

GPU VID3OUT

Panel Back-Li ght b rightness(PWM capable)

H

Pan el Powe r Enable

H

Panel Back-Li ght On/Off (PWM)

H

GPU VID1

-

GPU VID2

-

N/A

Thermal Catast rophic Over Temperature

-

Therma l Alert

-

Memory VREF Control

-

GPU VID0-OUT

AC Pow er Det ect Input

GPU VID5-

N/A

Hot pl ug detect for IFP link C

N/A

N/A

Hot Pl ug Detect for IFPE

N/A

tNVVDD >0

tFBVDDQ >0

tPEX_VDD >0

(10K pull low)

Performance Mode P0 TDP at Tj = 102 C* (GDDR3)

PU Mem NVCLK

G

(4) (1,5) (6)

Products

N13P-GL

64bit

1GB

GDDR3

Physi cal

Stra pping pin

ROM_SCL K

(W) (W) (MHz)

TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD

ROM_SI

ROM_SO FB[0]

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

/MCLK NVVDD

TBD TBD

Power Rail

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

(V) (A) (W) (A) (W )

Logical

S

trapp ing Bit3

PCI_DEVID[4]

FB[1]

PCI_DEVID[3] PCI_DEVID[2] PCI_DEVID[1] PCI_DEVID[0]

SOR3_EXPOSED

RESERVED PCIE_SPEED_

FBVDD

Logical

Stra pping Bit 2

SUB_V ENDOR

USER[2] USER[1] USER[0]USER[3]

3GIO_PAD_CFG_ADR[2] 3GIO_PAD_CFG_ADR[1]3GIO_PAD_CFG_ADR[3]

SOR2_EXPOSED SOR1_EXPOSED

CHANGE_GEN3

Device ID

N13P-GL

(28nm)

N13M-GE

(28nm)

GPU STRAP2 STRAP1 ST RAP0

N13P-GL

N13M-GE

???

???

FB Memory (GDDR3)

Samsung

2500MHz

Hynix

2500MHz

Samsung

2500MHz

2500MHz

K4G10325FG-HC04

H5GQ1H24BFR-T2C

K4G20325FG-HC04

H5GQ2H24MFR-T2CHynix

ROM_SO

32Mx32

32Mx32 PD 15K

PD 10K

64Mx32

64Mx32

FBVDDQ PCI Express I/O and

(GPU+Mem)

(1.35V)(1.35V)

(A) (W) (W)(mA) (W) ( W) (W)(mA) (mA) (mA)

(1.05V)

Logical

Stra pping Bit 1

SLOT_CLK_CFG

RAM_CFG[1]RAM_CFG[3] RAM_CFG[2]

PLLVDD

Logical

Stra pping Bit 0

PEX_PLL_EN_TERM

AM_CFG[0]

R

VGA_D EVICESMB_A LT_ADDR

3GIO_PAD_CFG_ADR[0]

PCIE_MAX_SPEED DP_PLL_VDD33V

SOR0_EXPOSED

ROM_SCLK ROM_SI

PD 15K

PD 15K

PD 20KPD 10K PU 45K

PU 20K

PU 20K

PD 15K PD 35KPU 20KPD 10K PD 20K PU 45K

PD 15K PD 35KPU 20KPD 10K PD 20K PU 45K

X76

I/O and

PLLVDD

PD 35K

PD 35K

Other

(3.3V)(1.05V)(1.8V)

D

C

PU 45K

B

1. all power rail ramp up time should be larger than 40us

2. Optimus system VDD33 avoids drop down earlier than NVDD and FBVDDQ

A

1.all GPU power rails should be turned off within 10ms

5

Tpower-off <10ms

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

3

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet

Compal Electronics, Inc.

VGA Notes List

LA-7986P

4 62Wedn esday, August 08, 2012

1

of

A

1.0

5

D

C

24.9_04 02_1%

B

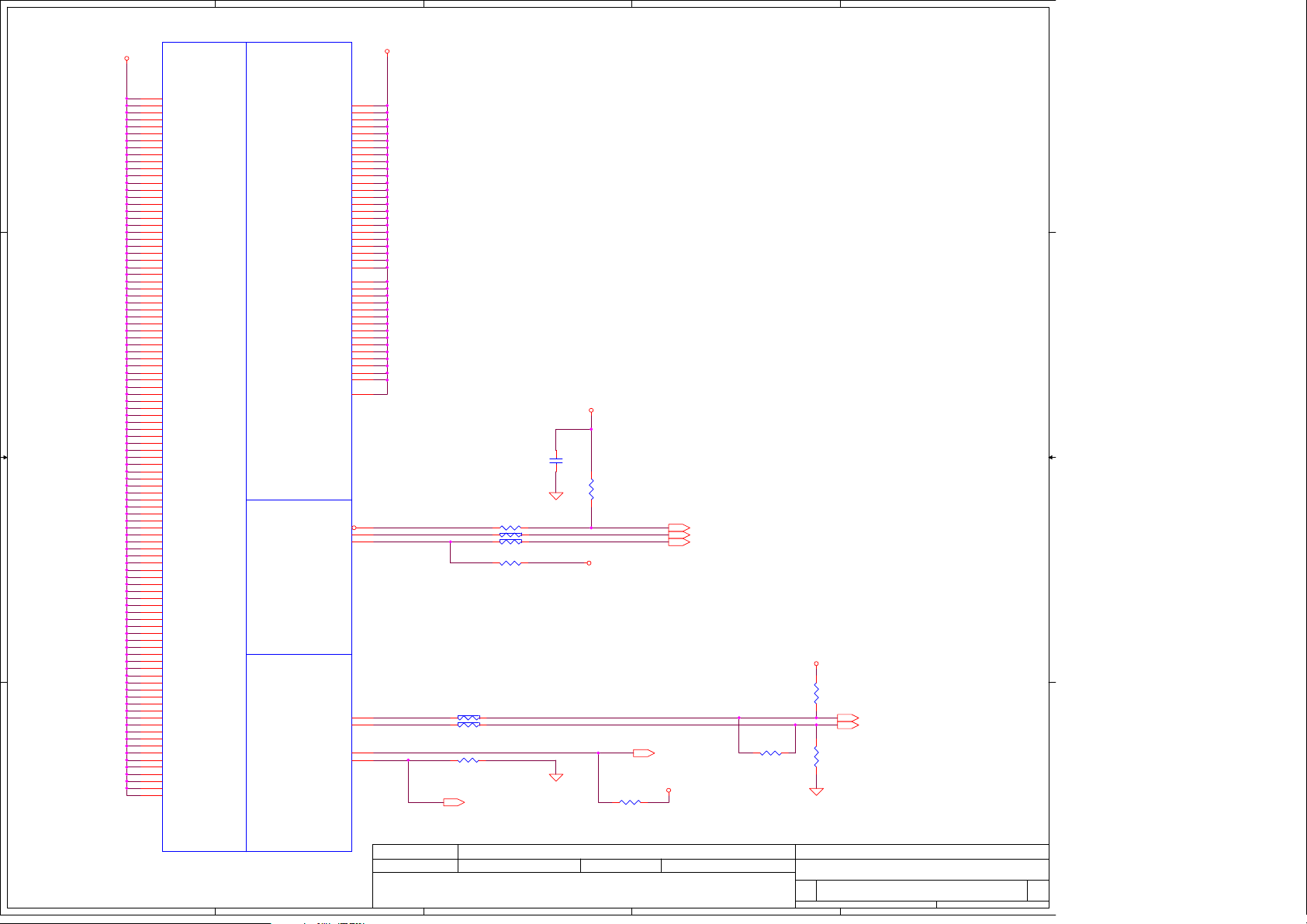

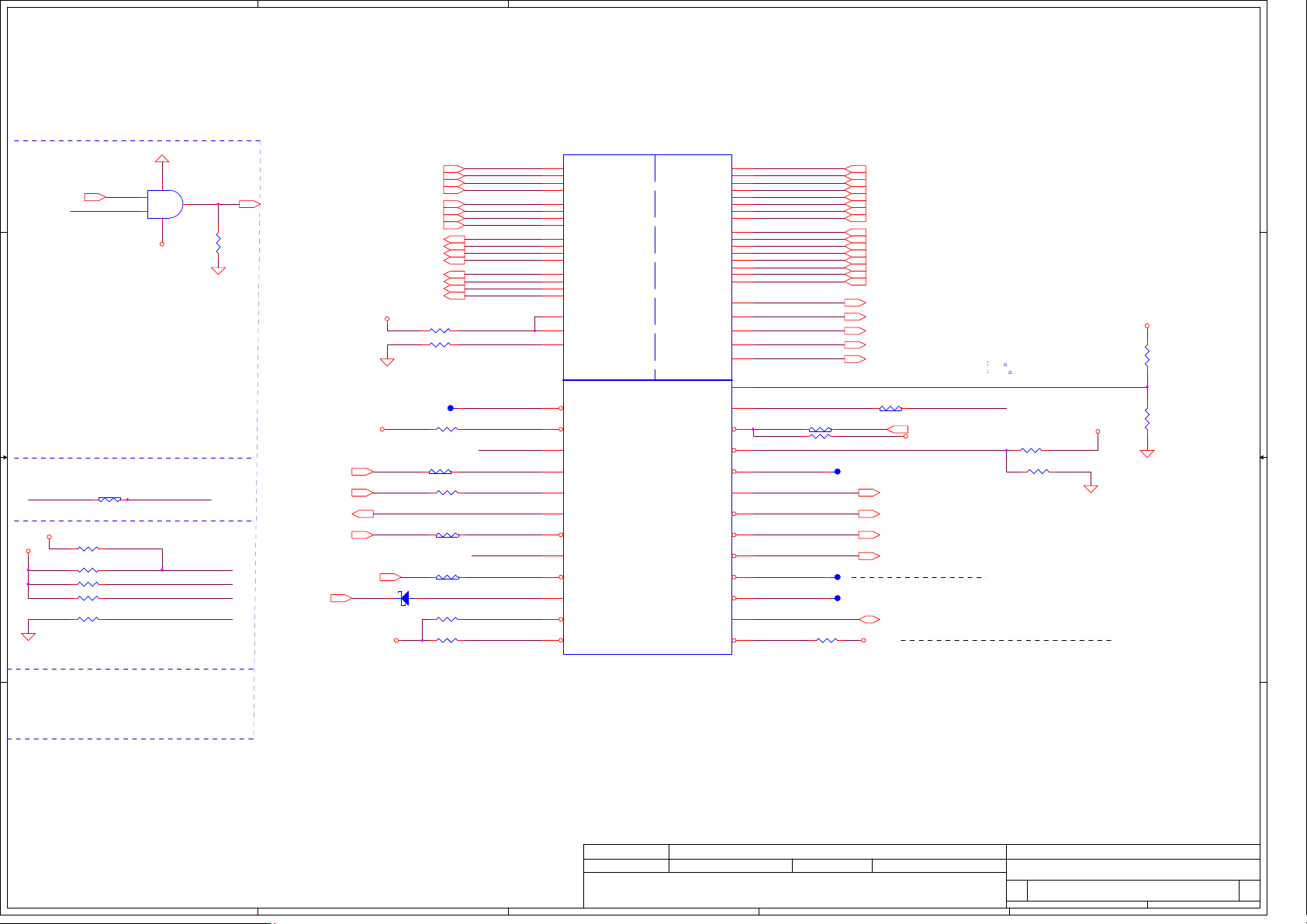

eDP_COMPIO and ICOMPO signals

should be short ed near balls

and routed with typical

impedance <25 mohms

+V1.05S _VCCP

1

R7

2

2

PEG_ICOM PI and RCOMPO signals should be

shorted and routed

with - max length = 500 mils - typical

impedance = 43 mohms

1

2

PEG_ICOM PO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

1: No rmal Opera tion; Lane # definition matches

socke t pin map definition

0:Lan e Reversed

*

PCIE_CTX_GR X_N15

PCIE_CTX_GR X_N14

PCIE_CTX_GR X_N13

PCIE_CTX_GR X_N12

PCIE_CTX_GR X_N11

PCIE_CTX_GR X_N10

PCIE_CTX_GR X_N9

PCIE_CTX_GR X_N8

PCIE_CTX_GR X_N7

PCIE_CTX_GR X_N6

PCIE_CTX_GR X_N5

PCIE_CTX_GR X_N4

PCIE_CTX_GR X_N3

PCIE_CTX_GR X_N2

PCIE_CTX_GR X_N1

PCIE_CTX_GR X_N0

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P0

PCIE_CTX_ GRX_N[0..15] <23>

PCIE_CTX_GR X_P[0..15] <23>

PEG_ICOMP I

PEG_ICOMP O

PEG_RCO MPO

PEG_RX# [0]

PEG_RX# [1]

PEG_RX# [2]

PEG_RX# [3]

PEG_RX# [4]

PEG_RX# [5]

PEG_RX# [6]

PEG_RX# [7]

PEG_RX# [8]

PEG_RX# [9]

PEG_RX# [10]

PEG_RX# [11]

PEG_RX# [12]

PEG_RX# [13]

PEG_RX# [14]

PEG_RX# [15]

PEG_RX[0 ]

PEG_RX[1 ]

PEG_RX[2 ]

PEG_RX[3 ]

PEG_RX[4 ]

PEG_RX[5 ]

PEG_RX[6 ]

PEG_RX[7 ]

PEG_RX[8 ]

PEG_RX[9 ]

PEG_RX[1 0]

PEG_RX[1 1]

PEG_RX[1 2]

PEG_RX[1 3]

PEG_RX[1 4]

PEG_RX[1 5]

PEG_TX# [0]

PEG_TX# [1]

PEG_TX# [2]

PEG_TX# [3]

PEG_TX# [4]

PEG_TX# [5]

PEG_TX# [6]

PEG_TX# [7]

PEG_TX# [8]

PEG_TX# [9]

PEG_TX# [10]

PEG_TX# [11]

PEG_TX# [12]

PCI EXPRESS* - GRAPHICS

PEG_TX# [13]

PEG_TX# [14]

PEG_TX# [15]

PEG_TX[0 ]

PEG_TX[1 ]

PEG_TX[2 ]

PEG_TX[3 ]

PEG_TX[4 ]

PEG_TX[5 ]

PEG_TX[6 ]

PEG_TX[7 ]

PEG_TX[8 ]

PEG_TX[9 ]

PEG_TX[1 0]

PEG_TX[1 1]

PEG_TX[1 2]

PEG_TX[1 3]

PEG_TX[1 4]

PEG_TX[1 5]

3

+V1.05S _VCCP

R1

24.9_0402_1%

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_COMP

PCIE_CRX_G TX_N15

PCIE_CRX_G TX_N14

PCIE_CRX_G TX_N13

PCIE_CRX_G TX_N12

PCIE_CRX_G TX_N11

PCIE_CRX_G TX_N10

PCIE_CRX_G TX_N9

PCIE_CRX_G TX_N8

PCIE_CRX_G TX_N7

PCIE_CRX_G TX_N6

PCIE_CRX_G TX_N5

PCIE_CRX_G TX_N4

PCIE_CRX_G TX_N3

PCIE_CRX_G TX_N2

PCIE_CRX_G TX_N1

PCIE_CRX_G TX_N0

PCIE_CRX_GTX_P15

PCIE_CRX_GTX_P14

PCIE_CRX_GTX_P13

PCIE_CRX_GTX_P12

PCIE_CRX_GTX_P11

PCIE_CRX_GTX_P10

PCIE_CRX_GTX_P9

PCIE_CRX_GTX_P8

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_P0

PCIE_CTX_GR X_C_N15

PCIE_CTX_GR X_C_N14

PCIE_CTX_GR X_C_N13

PCIE_CTX_GR X_C_N12

PCIE_CTX_GR X_C_N11

PCIE_CTX_GR X_C_N10

PCIE_CTX_GR X_C_N9

PCIE_CTX_GR X_C_N8

PCIE_CTX_GR X_C_N7

PCIE_CTX_GR X_C_N6

PCIE_CTX_GR X_C_N5

PCIE_CTX_GR X_C_N4

PCIE_CTX_GR X_C_N3

PCIE_CTX_GR X_C_N2

PCIE_CTX_GR X_C_N1

PCIE_CTX_GR X_C_N0

PCIE_CTX_GR X_C_P15

PCIE_CTX_GR X_C_P14

PCIE_CTX_GR X_C_P13

PCIE_CTX_GR X_C_P12

PCIE_CTX_GR X_C_P11

PCIE_CTX_GR X_C_P10

PCIE_CTX_GR X_C_P9

PCIE_CTX_GR X_C_P8

PCIE_CTX_GR X_C_P7

PCIE_CTX_GR X_C_P6

PCIE_CTX_GR X_C_P5

PCIE_CTX_GR X_C_P4

PCIE_CTX_GR X_C_P3

PCIE_CTX_GR X_C_P2

PCIE_CTX_GR X_C_P1

PCIE_CTX_GR X_C_P0

PCIE_CRX_G TX_N[0..15] <23>

PCIE_CRX_G TX_P[0..15] <23>

C1 0.1U_04 02_10V7KN13P@

1

C2 0.1U_04 02_10V7KN13P@

1

C3 0.1U_04 02_10V7KN13P@

1

C4 0.1U_04 02_10V7KN13P@

1

C5 0.1U_04 02_10V7KN13P@

1

C6 0.1U_04 02_10V7KN13P@

1

C7 0.1U_04 02_10V7KN13P@

1

C8 0.1U_04 02_10V7KN13P@

1

C9 0.1U_04 02_10V7K

1

C10 0.1U_04 02_10V7K

1

C11 0.1U_04 02_10V7K

1

C12 0.1U_04 02_10V7K

1

C13 0.1U_04 02_10V7K

1

C14 0.1U_04 02_10V7K

1

C15 0.1U_04 02_10V7K

1

C16 0.1U_04 02_10V7K

1

C17 0.1U_04 02_10V7KN13P@

1

C18 0.1U_04 02_10V7KN13P@

1

C19 0.1U_04 02_10V7KN13P@

1

C20 0.1U_04 02_10V7KN13P@

1

C21 0.1U_04 02_10V7KN13P@

1

C22 0.1U_04 02_10V7KN13P@

1

C23 0.1U_04 02_10V7KN13P@

1

C24 0.1U_04 02_10V7KN13P@

1

C25 0.1U_04 02_10V7K

1

C26 0.1U_04 02_10V7K

1

C27 0.1U_04 02_10V7K

1

C28 0.1U_04 02_10V7K

1

C29 0.1U_04 02_10V7K

1

C30 0.1U_04 02_10V7K

1

C31 0.1U_04 02_10V7K

1

C32 0.1U_04 02_10V7K

1

4

JCPU 1A

eDP_HPD

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0 ]

H19

FDI0_TX#[1 ]

E19

FDI0_TX#[2 ]

F18

FDI0_TX#[3 ]

B21

FDI1_TX#[0 ]

C20

FDI1_TX#[1 ]

D18

FDI1_TX#[2 ]

E17

FDI1_TX#[3 ]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMP IO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0 ]

E16

eDP_TX#[1 ]

D16

eDP_TX#[2 ]

F15

eDP_TX#[3 ]

TYCO_ 20136 20-2_IVY BRIDGE

DMI

Intel(R) FDI

eDP

DMI_CRX_PTX_N0<16>

DMI_CRX_PTX_N1<16>

DMI_CRX_PTX_N2<16>

DMI_CRX_PTX_N3<16>

DMI_CRX_PTX_P0<16>

DMI_CRX_PTX_P1<16>

DMI_CRX_PTX_P2<16>

DMI_CRX_PTX_P3<16>

DMI_CTX_PRX_N0<16>

DMI_CTX_PRX_N1<16>

DMI_CTX_PRX_N2<16>

DMI_CTX_PRX_N3<16>

DMI_CTX_PRX_P0<16>

DMI_CTX_PRX_P1<16>

DMI_CTX_PRX_P2<16>

DMI_CTX_PRX_P3<16>

FDI_CTX_PRX_ N0<16>

FDI_CTX_PRX_ N1<16>

FDI_CTX_PRX_ N2<16>

FDI_CTX_PRX_ N3<16>

FDI_CTX_PRX_ N4<16>

FDI_CTX_PRX_ N5<16>

FDI_CTX_PRX_ N6<16>

FDI_CTX_PRX_ N7<16>

FDI_CTX_PRX_P0<16>

FDI_CTX_PRX_P1<16>

FDI_CTX_PRX_P2<16>

FDI_CTX_PRX_P3<16>

FDI_CTX_PRX_P4<16>

FDI_CTX_PRX_P5<16>

FDI_CTX_PRX_P6<16>

FDI_CTX_PRX_P7<16>

FD I_FSY NC0<16>

FD I_FSY NC1<16>

FD I_INT<16>

FD I_LSYN C0<16>

FD I_LSYN C1<16>

EDP_COMP

1

D

C

B

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

Compal Secret Data

3

Deciphered Date

Title

PROCESSOR(1/7) DMI,FDI,PEG

Size D ocumen t Number Re v

Cust om

LA-7986P

2

Dat e: Sheet

1

o f

5 62We dnesda y, August 08 , 2012

A

1.0

5

4

3

2

1

D

H_SNB _IVB#<19>

+V1.05S_VCCP

H_CATERR #

H_PRO CHOT#_R

2

H_PM _SYNC_R

2

H_CPU PWRGD_R

PM_DRAM_PWR GD_R

2

BUF_C PU_RST#

BUF_C PU_RST#

H_THRMTRIP#<19>

@

R30

200_0402_5%

T48

H_PEC I<19,42>

R15

56_0402_5%

1

R22

1

0_0402_5%

R29

1

130_0402_5%

1

R9

62_0402_5%

H_PRO CHOT#<42,48>

C

H_CPU PWRGD<19>

B

SYS_PW ROK<16>

+3VS

PM_DRAM_PWR GD<16>

H_PROCH OT#

1

100P_0402_50V8J

EMI Reserve

0.1U_0402_16V4Z

R880

@

1

2

0_0402_5%

R161

1

2

10K_0402_5%

RUN_O N_CPU1.5VS3#<10>

2

H_PM _SYNC<16>

R260_0402_5%

2

2

R27

1

C549

@

C33

1

2

1

2

+3VALW

1

2

U1

5

P

B

4

O

A

G

74AHC1G09GW_TSSOP5

3

10K_0402_5%

PM_SYS _PWRGD_BUF

2

G

+1.5V_ CPU_VDDQ

1

@

R33

39_0402_5%

2

1

D

Q1

@

2N7002H_SOT23-3

S

3

1

2

JCPU1B

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWR OK

AR33

RESET#

TYCO_20 13620-2_IV Y BRIDGE

1

R35

@

0_0402_5%

2

+V1.05S_VCCP

1

R32

75_0402_5%

R34

2

43_0402_1%

1

2

SN74L VC1G07DCKR_SC70-5

MISCTHERMALPWR MANAGEMENT

CLOCKS

DDR3

JTAG & BPM

Buffered reset to CPU

C34

0.1U_0402_16V4Z

BUFO_ CPU_RST#

MISC

1

2

U2

4

Y

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

+3VS

5

1

P

NC

2

A

G

3

CLK_C PU_DMI_R

A28

CLK_C PU_DMII#_R

A27

A16

A15

R8

AK1

A5

A4

2

2

H_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR3 C ompensation Signals

XDP_P RDY#

AP29

XDP_PREQ#

AP27

XDP_TCK

AR26

TCK

XDP_TMS

AR27

TMS

XDP_TRST#

AP30

XDP_TDI

AR28

TDI

XDP_TDO

AP26

TDO

XDP_DBRESET#

AL35

XDP_BPM#0

AT28

XDP_BPM#1

AR29

XDP_BPM#2

AR30

XDP_BPM#3

AT30

XDP_BPM#4

AP32

XDP_BPM#5

AR31

XDP_BPM#6

AT31

XDP_BPM#7

AR32

PCH_PLTRST#

3V

PCH_PLTRST# <18>

R10;R11 put on U4 side

R10

@

0_0402_5%

1

0_0402_5%

R12 1K_0402_5%

1

R13 1K_0402_5%

1

H_DRAMRST# <7>

R16 140_0402_1%

1

2

R17 25.5_0402_1%

1

2

R18 200_0402_1%

1

2

T97

T98

R28 1K_0402_5%

2

T49

T90

T91

T92

T93

T94

T95

T96

2

1

2

@

R11

1

+V1.05S_VCCP

XDP_TMS

XDP_TDI

XDP_TDO

XDP_TCK

XDP_TRST#

CLK_C PU_DMI <15>

CLK_C PU_DMI# <15>

R20 51_0402_5%

2

R21 51_0402_5%

2

R23 51_0402_5%@

2

R24 51_0402_5%

2

R25 51_0402_5%

2

+3VS

D

+V1.05S_VCCP

1

1

1

1

1

PU/PD for JTAG signals

C

B

A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

PROCESSOR(2/7) PM,XDP,CLK

Size Doc ument Number Re v

Cus tom

LA-7986P

2

Date: Sheet

1

of

6 62Wedn esday, August 08, 2012

A

1.0

5

4

3

2

1

JCPU 1C

DDR_ A_D[0..63 ]<12>

D

C

B

DDR_A_BS 0<12>

DDR_A_BS 1<12>

DDR_A_BS 2<12>

DDR_A _CAS#<12>

DDR_A _RAS#<12>

DDR_A_W E#<12>

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D10

DDR_A _D11

DDR_A _D12

DDR_A _D13

DDR_A _D14

DDR_A _D15

DDR_A _D16

DDR_A _D17

DDR_A _D18

DDR_A _D19

DDR_A _D20

DDR_A _D21

DDR_A _D22

DDR_A _D23

DDR_A _D24

DDR_A _D25

DDR_A _D26

DDR_A _D27

DDR_A _D28

DDR_A _D29

DDR_A _D30

DDR_A _D31

DDR_A _D32

DDR_A _D33

DDR_A _D34

DDR_A _D35

DDR_A _D36

DDR_A _D37

DDR_A _D38

DDR_A _D39

DDR_A _D40

DDR_A _D41

DDR_A _D42

DDR_A _D43

DDR_A _D44

DDR_A _D45

DDR_A _D46

DDR_A _D47

DDR_A _D48

DDR_A _D49

DDR_A _D50

DDR_A _D51

DDR_A _D52

DDR_A _D53

DDR_A _D54

DDR_A _D55

DDR_A _D56

DDR_A _D57

DDR_A _D58

DDR_A _D59

DDR_A _D60

DDR_A _D61

DDR_A _D62

DDR_A _D63

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

C5

SA_DQ[0]

D5

SA_DQ[1]

D3

SA_DQ[2]

D2

SA_DQ[3]

D6

SA_DQ[4]

C6

SA_DQ[5]

C2

SA_DQ[6]

C3

SA_DQ[7]

F10

SA_DQ[8]

F8

SA_DQ[9]

SA_DQ[10]

G9

SA_DQ[11]

F9

SA_DQ[12]

F7

SA_DQ[13]

G8

SA_DQ[14]

G7

SA_DQ[15]

K4

SA_DQ[16]

K5

SA_DQ[17]

K1

SA_DQ[18]

J1

SA_DQ[19]

J5

SA_DQ[20]

J4

SA_DQ[21]

J2

SA_DQ[22]

K2

SA_DQ[23]

M8

SA_DQ[24]

SA_DQ[25]

N8

SA_DQ[26]

N7

SA_DQ[27]

SA_DQ[28]

M9

SA_DQ[29]

N9

SA_DQ[30]

M7

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

AJ5

SA_DQ[38]

AJ6

SA_DQ[39]

AJ8

SA_DQ[40]

SA_DQ[41]

AJ9

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

AL9

SA_DQ[46]

AL8

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

V6

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

RSVD_TP[10]

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A _DQS#0

DDR_A _DQS#1

DDR_A _DQS#2

DDR_A _DQS#3

DDR_A _DQS#4

DDR_A _DQS#5

DDR_A _DQS#6

DDR_A _DQS#7

DDR_A _DQS0

DDR_A _DQS1

DDR_A _DQS2

DDR_A _DQS3

DDR_A _DQS4

DDR_A _DQS5

DDR_A _DQS6

DDR_A _DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DD R0 <12>

M_CLK_DD R#0 <12>

DDR_CKE 0_DIMMA <12>

M_CLK_DD R1 <12>

M_CLK_DD R#1 <12>

DDR_CKE 1_DIMMA <12>

DDR_C S0_DIMMA# <12>

DDR_C S1_DIMMA# <12>

M_ODT0 <12>

M_ODT1 <12>

DDR_A _DQS#[0.. 7] <12>

DDR_ A_DQS[0.. 7] <12>

DDR_A _MA[0..15] <12>

DDR _B_D[0..6 3]<13>

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D10

DDR_B _D11

DDR_B _D12

DDR_B _D13

DDR_B _D14

DDR_B _D15

DDR_B _D16

DDR_B _D17

DDR_B _D18

DDR_B _D19

DDR_B _D20

DDR_B _D21

DDR_B _D22

DDR_B _D23

DDR_B _D24

DDR_B _D25

DDR_B _D26

DDR_B _D27

DDR_B _D28

DDR_B _D29

DDR_B _D30

DDR_B _D31

DDR_B _D32

DDR_B _D33

DDR_B _D34

DDR_B _D35

DDR_B _D36

DDR_B _D37

DDR_B _D38

DDR_B _D39

DDR_B _D40

DDR_B _D41

DDR_B _D42

DDR_B _D43

DDR_B _D44

DDR_B _D45

DDR_B _D46

DDR_B _D47

DDR_B _D48

DDR_B _D49

DDR_B _D50

DDR_B _D51

DDR_B _D52

DDR_B _D53

DDR_B _D54

DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B _D58

DDR_B _D59

DDR_B _D60

DDR_B _D61

DDR_B _D62

DDR_B _D63

DDR_B_BS 0<13>

DDR_B_BS 1<13>

DDR_B_BS 2<13>

DDR_B _CAS#<13>

DDR_B _RAS#<13>

DDR_B _WE#<13>

AM5

AM6

AR3

AN3

AN2

AN1

AN9

AN8

AR6

AR5

AR9

AJ11

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA10

JCPU 1D

AE2

SB_CLK[0]

AD2

DDR SYSTEM MEMORY B

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

SB_CS#[0]

SB_CS#[1]

RSVD_TP[17]

RSVD_TP[18]

SB_ODT[0]

SB_ODT[1]

RSVD_TP[19]

RSVD_TP[20]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B _DQS#0

DDR_B _DQS#1

DDR_B _DQS#2

DDR_B _DQS#3

DDR_B _DQS#4

DDR_B _DQS#5

DDR_B _DQS#6

DDR_B _DQS#7

DDR_B _DQS0

DDR_B _DQS1

DDR_B _DQS2

DDR_B _DQS3

DDR_B _DQS4

DDR_B _DQS5

DDR_B _DQS6

DDR_B _DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

C9

SB_DQ[0]

A7

SB_DQ[1]

D10

SB_DQ[2]

C8

SB_DQ[3]

A9

SB_DQ[4]

A8

SB_DQ[5]

D9

SB_DQ[6]

D8

SB_DQ[7]

G4

SB_DQ[8]

F4

SB_DQ[9]

F1

SB_DQ[10]

G1

SB_DQ[11]

G5

SB_DQ[12]

F5

SB_DQ[13]

F2

SB_DQ[14]

G2

SB_DQ[15]

J7

SB_DQ[16]

J8

SB_DQ[17]

K10

SB_DQ[18]

K9

SB_DQ[19]

J9

SB_DQ[20]

J10

SB_DQ[21]

K8

SB_DQ[22]

K7

SB_DQ[23]

M5

SB_DQ[24]

N4

SB_DQ[25]

N2

SB_DQ[26]

N1

SB_DQ[27]

M4

SB_DQ[28]

N5

SB_DQ[29]

M2

SB_DQ[30]

M1

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

AP3

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

AP2

SB_DQ[39]

AP5

SB_DQ[40]

SB_DQ[41]

AT5

SB_DQ[42]

AT6

SB_DQ[43]

AP6

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

AT8

SB_DQ[50]

AT9

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AA9

SB_BS[0]

AA7

SB_BS[1]

R6

SB_BS[2]

SB_CAS#

AB8

SB_RAS#

AB9

SB_WE#

M_CLK_DD R2 <13>

M_CLK_DDR#2 <13>

DDR_CKE 2_DIMMB <13>

M_CLK_DD R3 <13>

M_CLK_DDR#3 <13>

DDR_CKE 3_DIMMB <13>

DDR_CS2_D IMMB# <13>

DDR_CS3_D IMMB# <13>

M_ODT2 <13>

M_ODT3 <13>

DDR_B _DQS#[0.. 7] <13>

DDR_ B_DQS[0.. 7] <13>

DDR_B _MA[0..15] <13>

D

C

B

DRAMRST_CNTRL <10>

Deciphered Date

TYCO_20 13620-2_IV Y BRIDGE

2

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

LA-7986P

1

of

7 62Wedn esday, August 08, 2012

A

1.0

TYCO_20 13620-2_IV Y BRIDGE

R36

@

0_0402_5%

1

2

D

S

1

3

Q2

G

LBSS138LT1G_SOT-23-3

2

1

C35

0.047U 16V K X7R 0402

2

DDR3_ DRAMRST#_R

5

H_DRAMRST#

4.99K_0402_1%

2

R39

1

DRAMRST_CNTRL

H_DRAMRST#<6>

A

+1.5V

1

R37

1K_0402_5%

R38

2

1K_0402_5%

1

2

Eiffel used 0.01u

Module design used 0.047u

4

DRAM RST_CNTRL_PCH<15>

DDR3_DR AMRST# <12,13>

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

R40 0_0402_5%

3

R02

@

2

DRAMRST_CNTRL

2011/06/15 2012/07/11

Compal Secret Data

5

4

3

2

1

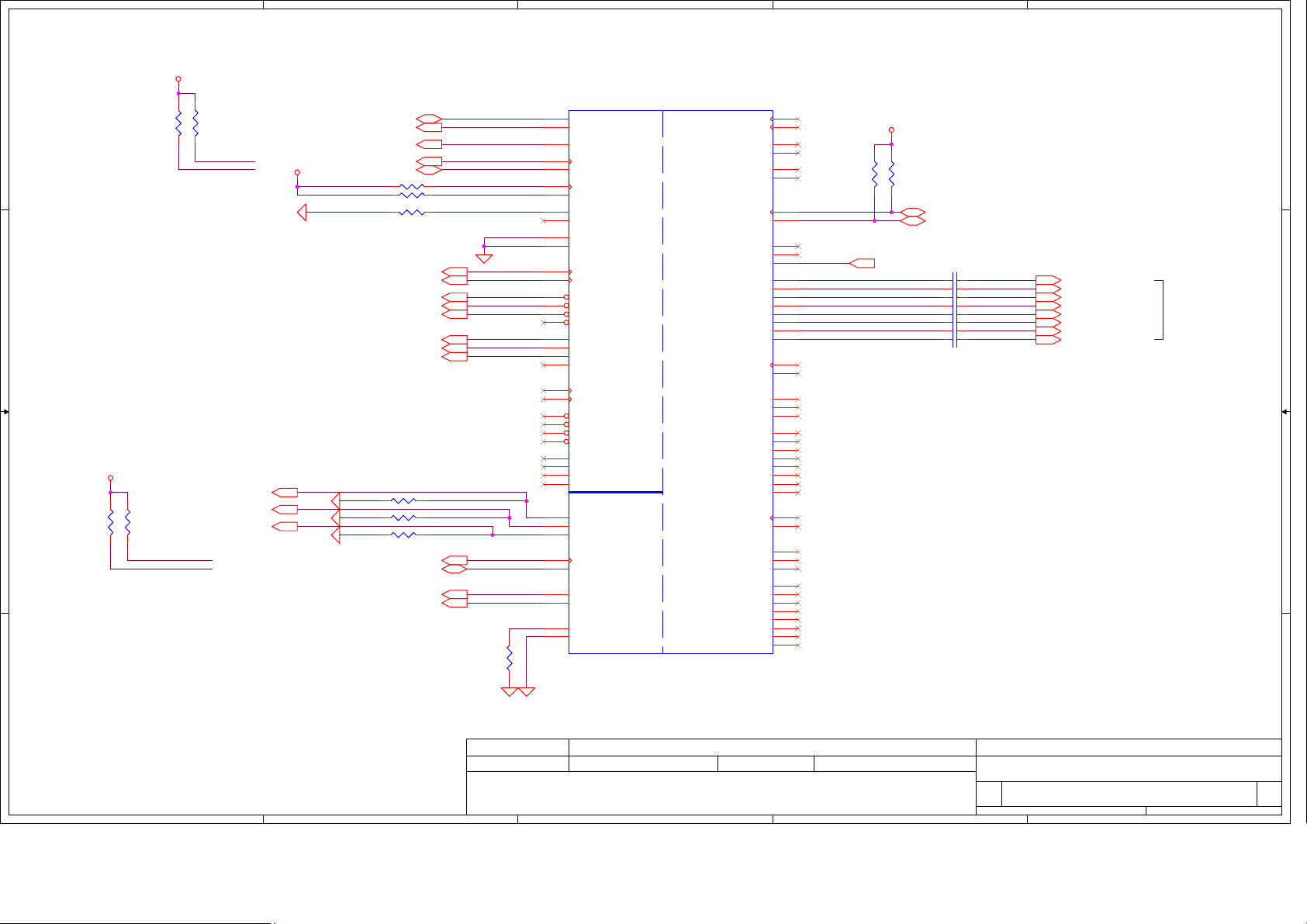

CFG Straps for Processor

CFG2

D

JCPU1E

RESERVED

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD_NCTF10

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

AK28

CFG[0]

AK29

CFG2

CFG4

CFG5

CFG6

CFG7

+VCC_GFXCORE_AXG

+VCC_C ORE

R253

C

49.9_0402_1%

2

R252

49.9_0402_1%

2

1

1

R82 100_0402_1%@

1

R88 100_0402_1%@

2

1

2

VCC_AXG_VAL_SENSE

VSS_AXG_VAL_SENSE

VCC_VAL_SENSE

VSS_VAL_SENSE

Nee d PWR a dd ne w cir cu it on 1.0 5V(r efer CRB )

VSS_AXG_VAL_SENSE

Check

R255

49.9_0402_1%

INTEL 12/28 recommand

to add RC120, RC121, RC122, RC123

B

Please place as close as JCPU1

2

1

VSS_VAL_SENSE

2

R257

49.9_0402_1%

1

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

TYCO_20 13620-2_IV Y BRIDGE

CFG

Interl reque st AH2 6 s hor t GND

check on EVT ph ase

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RSVD_NCTF9

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

KEY

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

R60 0_0402_5%

@

1

2

R02

PEG Static Lane Reversal - CFG2 is for the 16x

T13PAD

CFG2

*

Display Port Presence Strap

CFG4

*

N13M@

PCIE Port Bifurcation Straps

11: (Def aul t) x1 6 - Devic e 1 functi ons 1 and 2 disabled

CFG[6:5 ]

*

10: x8, x8 - Devi ce 1 funct ion 1 enab led ; func tion 2

01: Rese rve d - ( Device 1 function 1 disabled ; function

00: x8,x 4,x 4 - Devi ce 1 funct ions 1 and 2 enable d

1

R41

1K_0402_1%

2

1: N orma l O peration ; Lane # definition matches

sock et p in map def inition

0:La ne Revers ed

CFG4

1K_0402_1%

1

R42

@

1K_0402_1%

2

1 : Disa bled; No Physi cal Displa y Port

atta ched to Embe dded Displ ay Port

0 : Enab led ; An ext ernal Disp lay Port d evice is

conn ecte d to the Embed ded Displa y Port

CFG6

CFG5

1

1

R43

2

R44

@

1K_0402_1%

2

disabled

2 enabled)

CFG7

1

@

2

R45

1K_0402_1%

D

C

B

PEG DEFER TRAINING

1: ( Defa ult ) PEG Train imme diately fo llowing xx RESETB

CFG7

de as sertion

A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

Compal Secret Data

Deciphered Date

0: P EG W ait for BIOS for t raining

Title

PROCESSOR(4/7) RSVD,CFG

Size Doc ument Number Re v

Cus tom

LA-7986P

2

Date: Sheet

Compal Electronics, Inc.

1

8 62Wedn esday, August 08, 2012

A

1.0

of

5

4

3

2

1

+VCC_C ORE

JCPU 1F

QC=94A

DC=53A

D

C

B

A

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

POWER

CORE SUPPLY

PEG AND DDR

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

+V1.05S_VCCP

8.5A

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

H_CPU _SVIDALRT#

H_CPU _SVIDCLK

H_CPU _SVIDDAT

0.1U_0402_10V6K

R47 43_0402_5%

1

2

1

2

1

2

R50 130_0402_5%

1

2

C99

R480_0402_5% @

R490_0402_5% @

1

2

+V1.05S_VCCP

1

R46

75_0402_5%

2

+V1.05S_VCCP

VR_SVID_CLK

VR_SVID_ALR T# <55>

VR_SV ID_CLK <55>

VR_SVID_DAT <55>

0.1u F on po wer side

VCC_SENCE 100ohm +-1% pull-up to VCC near processor

Trace Impedance =27-33 ohm

Trace Length Matc < 25 mils

VCCS ENSE_R

AJ35

VSSSENSE_R

AJ34

B10

VSSIO_SENSE_L

A10

R74 & R79 put toget her

VSS_SENCE 100ohm +-1% pull-down to GND near processor

1

2

1

2

VSSIO_SENSE

R74

1

2

10_0402_1%

@

VSSIO_SENSE_L <53 >

R52 0_0402_5%@

R53 0_0402_5%@

R79

2

10_0402_1%

VCCIO_ SENSE <52,53>

+V1.05S_VCCP

1

series -resistors close to VR

+VCC_ CORE

1

R51

100_0402_1%

2

R66

1

100_0402_1%

1

@

R54

2

100_0402_1%

2

VCCSENS E <55>

VSSSENSE <55>

D

C

B

A

TYCO_20 13620-2_IV Y BRIDGE

5

4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

3

Compal Secret Data

Deciphered Date

Title

PROCESSOR(5/7) PWR,BYPASS

Size Doc ument Number Re v

Cus tom

LA-7986P

2

Date: Sheet

9 62Wedn esday, August 08, 2012

1

1.0

of

5

4

3

2

1

+1.5V

R668

@

1

SUSP<46,53,54>

R667

@

100K_0402_5%

2

2

R580_0402_5% @

G

2

R590_0402_5% @

+3VALW

1

2

RUN_O N_CPU1.5VS 3#

1

D

Q7

2N7002_SOT23

S

3

D

CPU1.5V_S3_ GATE<42,46,53>

SUSP#<25,42, 46,51,52,53,54>

C

B

1

1

0_0402_5%

@

2

Check

+VSB

1

R03

R56

82K_0402_5%

2

1

D

Q4

2

G

2N7002_SOT23

S

3

RUN_O N_CPU1.5VS3# <6>

+VCC_GFXCORE_AXG

@

1

PAD- OPEN 4x4m

U3

DMN3030LSS-13_S OP8L-8

8

7

6

5

RUN_O N_CPU1.5VS 3

JCPU 1G

AT24

VAXG1

AT23

VAXG2

AT21

VAXG3

AT20

VAXG4

AT18

VAXG5

AT17

VAXG6

AR24

VAXG7

AR23

VAXG8

AR21

VAXG9

AR20

VAXG10

AR18

VAXG11

AR17

VAXG12

AP24

VAXG13

AP23

VAXG14

AP21

VAXG15

AP20

VAXG16

AP18

VAXG17

AP17

VAXG18

AN24

VAXG19

AN23

VAXG20

AN21

VAXG21

AN20

VAXG22

AN18

VAXG23

AN17

VAXG24

AM24

VAXG25

AM23

VAXG26

AM21

VAXG27

AM20

VAXG28

AM18

VAXG29

AM17

VAXG30

AL24

VAXG31

AL23

VAXG32

AL21

VAXG33

AL20

VAXG34

AL18

VAXG35

AL17

VAXG36

AK24

VAXG37

AK23

VAXG38

AK21

VAXG39

AK20

VAXG40

AK18

VAXG41

AK17

VAXG42

AJ24

VAXG43

AJ23

VAXG44

AJ21

VAXG45

AJ20

VAXG46

AJ18

VAXG47

AJ17

VAXG48

AH24

VAXG49

AH23

VAXG50

AH21

VAXG51

AH20

VAXG52

AH18

VAXG53

AH17

VAXG54

J1

2

4

1

1

15K_0402_1%

R57

330K_0402_5%

@

2

+1.5V _CPU_VDDQ

1

AP4800

2

Id=9.6A

3

R02

R885

2

1

2

POWER

GRAPHICS

220_0402_5%

2N7002_SOT23

C97

0.047U_0603_25 V7K

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

DDR3 -1.5V RAILS

@

R55

@

Q3

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

1

2

1

D

G

S

3

AK35

AK34

AL1

B4

D1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

1

@

C92

0.1U_0402_10V 6K

2

RUN_O N_CPU1.5VS 3#

2

+VCC_GFXCORE_AXG

1

R616

10_0402_1%

2

1

R626

10_0402_1%

2

+V_SM_VREF_CNT

+V_D DR_REFA_R

+V_D DR_REFB_R

+VCCSA

1

R89

100_0402_1%

2

1

2

1

2

VCC_AXG_SENSE <55>

@

VSS_AXG_SENSE <55>

+V_SM_VREF should

have 2 0 mil t race width

C117

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

C118

10U_0603_6.3V6M

1

1

2

2

10U

C125

10U_0603_6.3V6M

10U_0603_6.3V6M

C124

1

1

2

2

Q6

1

D

LBSS138LT1G_SOT-23-3

+VREF_DQ_DI MMA

+VREF_DQ_DI MMB

DRAMR ST_CNTRL

LBSS138LT1G_SOT-23-3

R670

1

1

R671

1

D

2

G

S

3

Q9

@

@

S

3

0_0402_5%~D

2

0_0402_5%~D

2

1K_0402_1%

R353

2

G

@

M3 Cir cuit ( Processor Generated SO-DIMM VREF_DQ)

RUN_O N_CPU1.5VS 3

Q5- or ign al p art

AP2 30 2GN -HF _SOT23-3

SB5 23 020210

G

2

1

3

D

S

R61

@

1

0_0402_5%

+1.5V

PMV45EN_SOT23-3

Q5

@

2

C98

0.1U_0402_10V 6K

C119

C120

10U_0603_6.3V6M

1

2

C127

10U_0603_6.3V6M

C126

1

2

1

2

+1.5 V_CPU_VDDQ

C121

10U_0603_6.3V6M

1

1

2

2

+VCCSA

1

+

C128

330U_D2 _2.5VY_R9M

2

+1.5 V_CPU_VDDQ

1

R67

1K_0402_1%

2

1

R78

1K_0402_1%

2

1

C122

10U_0603_6.3V6M

+

C123

330U_2.5V_M

2

@

DRAMR ST_CNTRL

+V_D DR_REFA_R

+V_D DR_REFB_R

1

1

R64

1K_0402_1%

@

2

2

+V_SM_VREF

+1.5 V_CPU_VDDQ

C396

@

0.1U_0402_10V 6K

1

2

C129

@

0.1U_0402_10V 6K

1

2

C96

0.1U_0402_10V 6K

1

2

C95

0.1U_0402_10V 6K

1

2

+1.5V

1

R62

1K_0402_1%

2

1

R63

1K_0402_1%

2

DRAMRST _CNTRL <7>

D

@

C

@

B

SA RAIL

+1.8VS

R69 0_0805_5%

1

2

@

VCCIO_SEL

H23

C22

C24

A19

H_VCC SA_VID0 <52>

H_VCC SA_VID1 <52>

@

1

R68 0_0402_5%

10U

C154

22U_0805_6.3V6M

1

1

@

2

2

C130

10U_0603_6.3V6M

C345

22U_0805_6.3V6M

1

@

2

1

2

C131

1U_0402_6.3V6K

1.5A

+1.8VS_VCCP LL

C132

1U_0402_6.3V6K

1

2

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

TYCO _2013620-2_IVY BRIDGE

1.8V RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

2

H_VCCP_ SELH_VCCP_SELH_VCCP_S ELH_VCCP_SELH_VCCP_S ELH _VCCP_SELH_VCCP _SELH_VCCP_SELH_VCCP_ SELH_VCCP_SEL

+VCCSA_SENS E <52>

10K_0402_5%

@

1

2

R77 0_0402_5%

R02

+3VALW

+3VS

2

2

R75

R76

@

10K_0402_5%

1

1

VCCP _PWRCTRL <52>

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

Compal Secret Data

IVY Bridge drives VCCIO_SEL low

VCCP_PWRCTRL:0

Sandy Bridge is NC for A19

VCCP_PWRCTRL:1

Deciphered Date

2

Title

PROCESSOR(6/7) PWR

Size Doc ument Number Re v

Cust om

LA-7986P

Date : Sheet

1

of

10 62Wed nesday, August 08, 201 2

A

1.0

3

JC PU1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

TYC O_201 3620- 2_IVY BRIDGE

VSS

Compal Secret Data

2011/06/15 2012/07/11

3

Deciphered Date

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

4

AJ22

VSS81

AJ19

VSS82

AJ16

VSS83

AJ13

VSS84

AJ10

VSS85

AJ7

VSS86

AJ4

VSS87

AJ3

VSS88

AJ2

VSS89

AJ1

VSS90

AH35

VSS91

AH34

VSS92

AH32

VSS93

AH30

VSS94

AH29

VSS95

AH28

VSS96

AH25

VSS98

AH22

VSS99

AH19

VSS100

AH16

VSS101

AH7

VSS102

AH4

VSS103

AG9

VSS104

AG8

VSS105

AG4

VSS106

AF6

VSS107

AF5

VSS108

AF3

VSS109

AF2

VSS110

AE35

VSS111

AE34

VSS112

AE33

VSS113

AE32

VSS114

AE31

VSS115

AE30

VSS116

AE29

VSS117

AE28

VSS118

VSS

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

5

JCP U1H

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

D

C

B

A

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

TYC O_201 3620- 2_IVY BRIDGE

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

2

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

Compal Electronics, Inc.

Title

PROCESSOR(7/7) VSS

Size Docu ment Num ber R ev

Cus tom

LA-7986P

Dat e: Sheet

1

D

C

B

A

1.0

o f

11 62We dnesda y, Augus t 08, 2 012

1

+VR EF_D Q_DIMMA

D

C

B

A

R7 1

1K_ 0402_1%

+1.5 V

1

R7 0

1K_ 0402_1%

2

1

2

3

+1.5 V

1

2

1

R7 3

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Lay ou t N ote:

Pl ace near DIM M

+1.5 V

C1 38

10U_ 0603_ 6.3V6M

C1 39

C1 37

10U_ 0603_ 6.3V6M

1

@

@

2

Lay ou t N ote:

Pl ace near DIM M

+0.7 5VS

@

C1 50

1U_0 402_6 .3V6K

C1 51

1U_0 402_6 .3V6K

1

2

2011/06/15 2012/07/11

10U_ 0603_ 6.3V6M

1

2

C1 52

1U_0 402_6 .3V6K

1

2

1

1

2

2

@

C1 53

1U_0 402_6 .3V6K

1

1

2

2

Compal Secret Data

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

SDA

SCL

VTT2

4

+1.5 V

2

DD R_A _D4

4

DD R_A _D5

6

8

DD R_A_ DQS# 0

10

DD R_A _DQS 0

12

14

DD R_A _D6

16

DD R_A _D7

18

20

DD R_A _D12

22

DD R_A _D13

24

26

DD R_A_ DM1

28

DD R3_DR AMRS T#

30

32

DD R_A _D14

34

DD R_A _D15

36

38

DD R_A _D20

40

DD R_A _D21

42

44

DD R_A_ DM2

46

48

DD R_A _D22

50

DD R_A _D23

52

54

DD R_A _D28

56

DD R_A _D29

58

60

DD R_A_ DQS# 3

62

DD R_A _DQS 3

64

66

DD R_A _D30

68

DD R_A _D31

70

72

DDR_ CKE1 _DIM MA

74

76

DDR_ A_MA 15

78

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

DDR_ A_MA 14

DDR_A_MA 11

DDR_ A_M A7

DDR_A_MA6

DDR_ A_M A4

DDR_ A_M A2

DDR_ A_M A0

M _CLK_ DDR1

M _CLK_ DDR#1

DD R_A_ BS1

DD R_A_ RAS#

DDR_ CS0_ DIMM A#

M_OD T0

M_OD T1

DD R_A _D36

DD R_A _D37

DD R_A_ DM4

DD R_A _D38

DD R_A _D39

DD R_A _D44

DD R_A _D45

DD R_A_ DQS# 5

DD R_A _DQS 5

DD R_A _D46

DD R_A _D47

DD R_A _D52

DD R_A _D53

DD R_A_ DM6

DD R_A _D54

DD R_A _D55

DD R_A _D60

DD R_A _D61

DD R_A_ DQS# 7

DD R_A _DQS 7

DD R_A _D62

DD R_A _D63

SMB _DATA_S3

SMB _CLK_S 3

4

+0.7 5VS

0.

0. 65 A @0 . 75 V

65 A @0 . 75 V

0.0.

65 A @0 . 75 V65 A @0 . 75 V

DD R3_DR AMRS T# <7,13 >

DDR_ CKE1 _DIM MA <7>

M_ CLK_D DR1 <7>

M_C LK_DD R#1 <7>

DD R_A_B S1 <7>

DD R_A_ RAS# <7>

DDR_ CS0_ DIMM A# <7>

M_ODT 0 <7>

M_ODT 1 <7>

0.1U _0402 _10V6K

C1 35

1

2

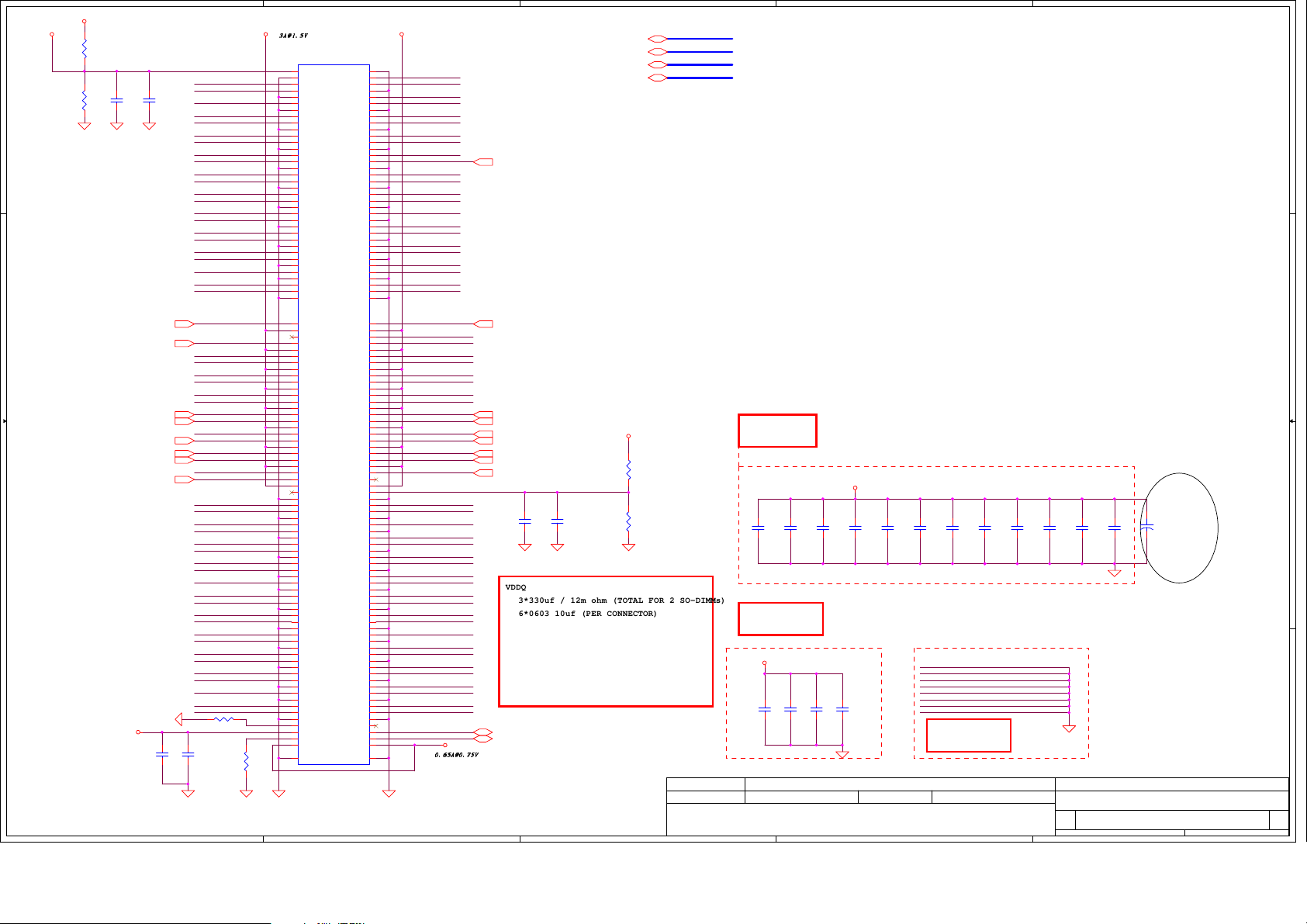

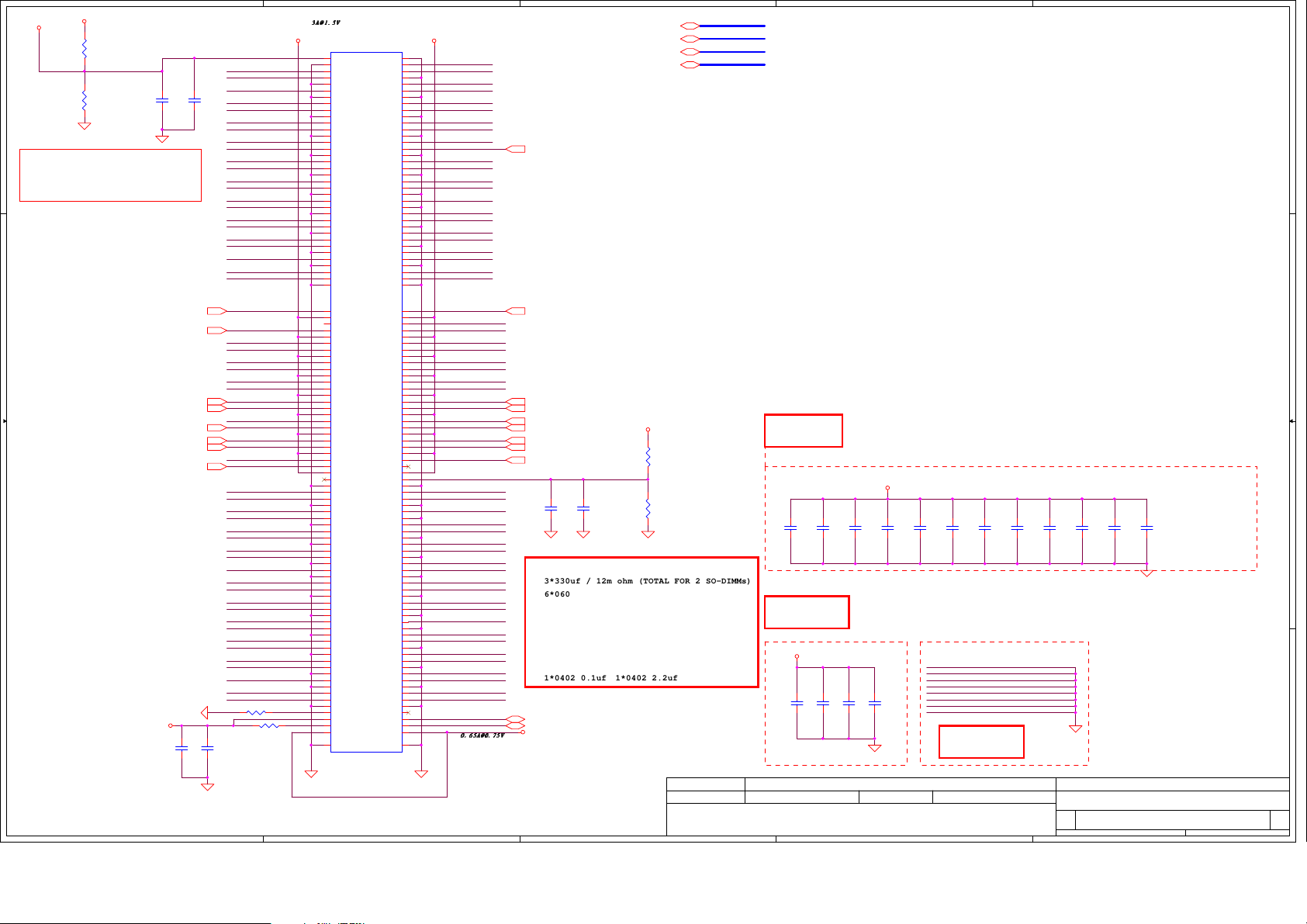

VDDQ(1 .5V) =

3*330u f / 12 m ohm (TOTAL FOR 2 SO-DIMMs)

6*0603 10uf (PER C ONNECTOR)

VTT(0. 75V) =

3*0805 10uf

VREF =

1*0402 0.1uf

VDDSPD (3.3V )=

1*0402 0.1uf 1*0402 2.2uf

SMB_ DATA_S3 < 13,15 ,36>

SMB _CLK_S3 < 13,15 ,36>

1

2

+VR EF_C A

2.2U _0603 _6.3V 4Z

C1 36

DD R_A _D[0 ..63]<7>

DD R_A _DQS [0..7 ]<7>

DD R_A_ DQS# [0..7 ]<7>

DDR_ A_MA [0.. 15]<7>

R7 2

1K_ 0402_1%

1K_ 0402_1%

4*0402 1uf

1*0402 2.2uf

5

+1.5 V

3A @

3A @ 1. 5 V

1. 5 V

3A @3A @

1. 5 V1. 5 V

DDR3 SO-DIMM A

2.2U _0603 _6.3V 4Z

C1 34

1

1

2

2

DDR_ CKE0 _DIM MA<7>

DD R_A_B S2<7>

M_ CLK_D DR0<7>

M_C LK_DD R#0<7>

DD R_A_B S0<7>

DD R_A_ WE#<7>

DD R_A_ CAS#<7>

DDR_ CS1_ DIMM A#<7>

+3VS

5

+VR EF_D Q_DIMM A

0.1U _0402 _10V6K

1

2

DD R_A _D0

C1 33

DD R_A _D1

DD R_A_ DM0

DD R_A _D2

DD R_A _D3

DD R_A _D8

DD R_A _D9

DD R_A_ DQS# 1

DD R_A _DQS 1

DD R_A _D10

DD R_A _D11

DD R_A _D16

DD R_A _D17

DD R_A_ DQS# 2

DD R_A _DQS 2

DD R_A _D18

DD R_A _D19

DD R_A _D24

DD R_A _D25

DD R_A_ DM3

DD R_A _D26

DD R_A _D27

DDR_ CKE0 _DIM MA

DD R_A_ BS2

DDR_ A_MA 12

DDR_ A_M A9

DDR_A_MA8

DDR_ A_M A5

DDR_ A_M A3

DDR_ A_M A1

M _CLK_ DDR0

M _CLK_ DDR#0

DDR_ A_MA 10

DD R_A_ BS0

DD R_A _WE#

DD R_A_ CAS#

DDR_ A_MA 13

DDR_ CS1_ DIMM A#

DD R_A _D32

DD R_A _D33

DD R_A_ DQS# 4

DD R_A _DQS 4

DD R_A _D34

DD R_A _D35

DD R_A _D40

DD R_A _D41

DD R_A_ DM5

DD R_A _D42

DD R_A _D43

DD R_A _D48

DD R_A _D49

DD R_A_ DQS# 6

DD R_A _DQS 6

DD R_A _D50

DD R_A _D51

DD R_A _D56

DD R_A _D57

DD R_A_ DM7

DD R_A _D58

DD R_A _D59

R8 1

1

2

10K _0402_5%

2.2U _0603 _6.3V 4Z

0.1U _0402 _10V6K

C1 55

C1 56

1

2

10K _0402_5%

1

2

JDI MM1

1

VREF_DQ

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

29

DQS1

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

R8 3

205

RESET#

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24