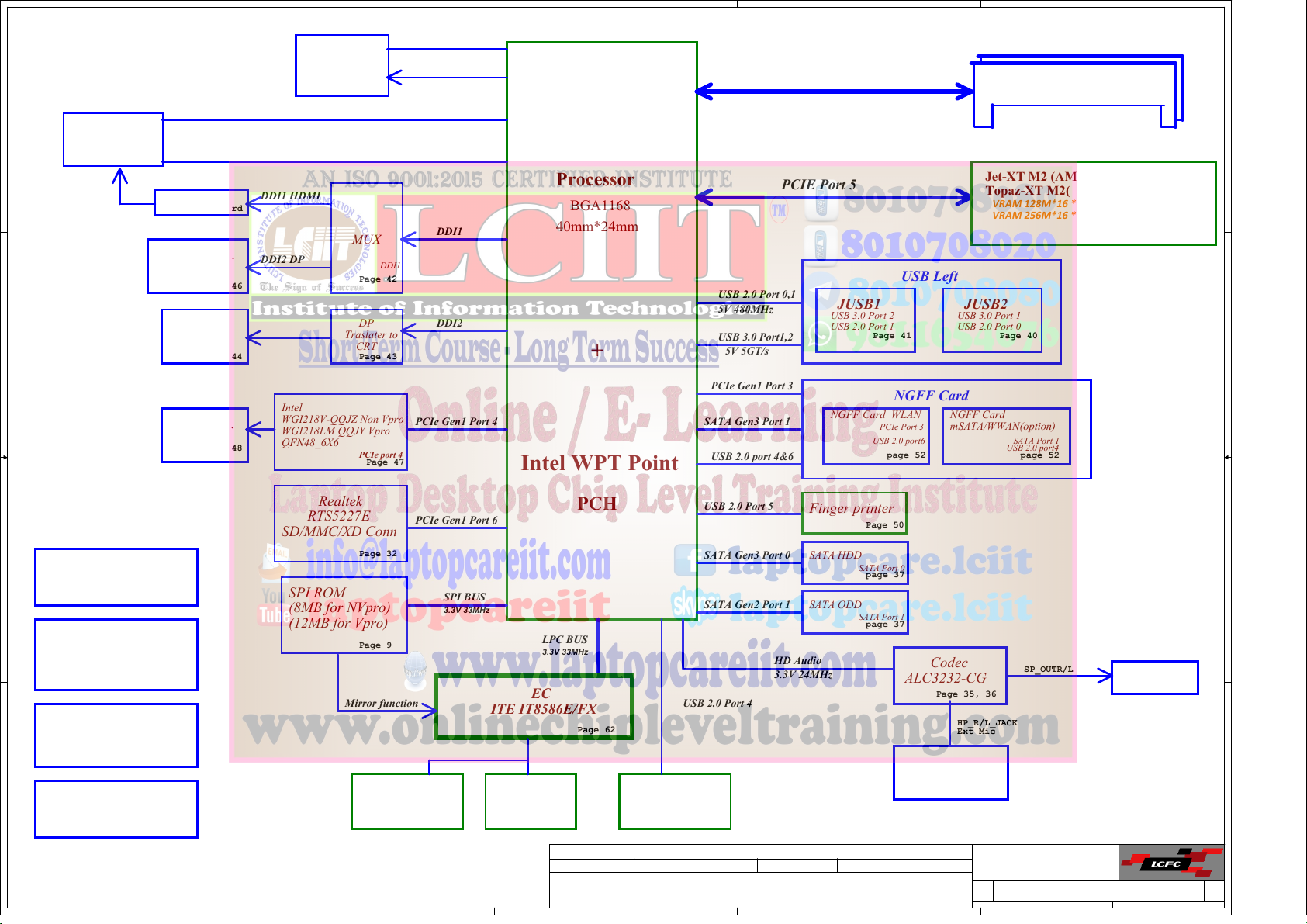

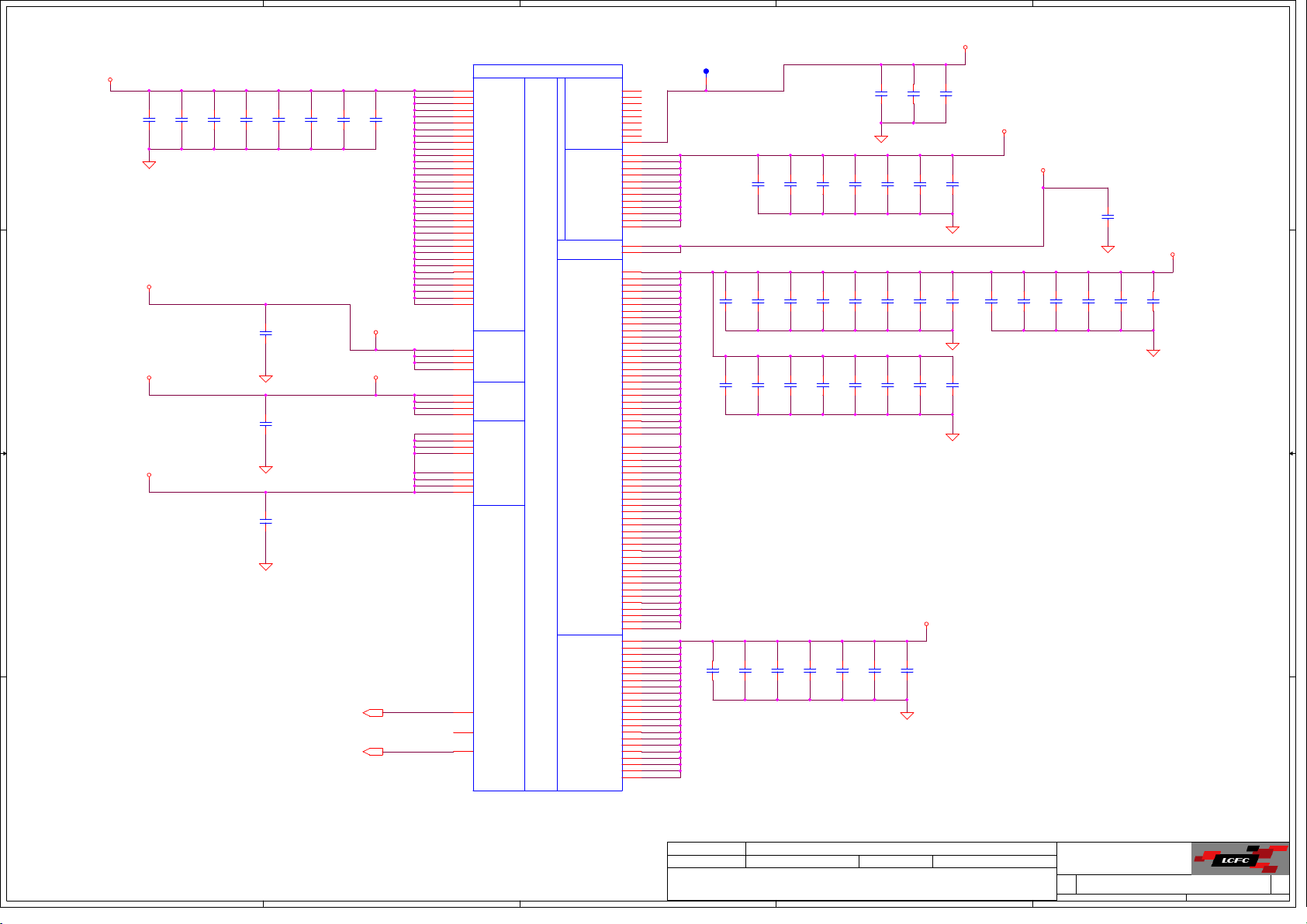

Lenovo E450C Schematic

A

1 1

B

C

D

E

LCFC Confidential

2 2

NM-A221 Rev1.0 Schematic

Intel Crescent Bay Processor with DDRIIIL + Wild Cat Point PCH

3 3

4 4

A

AMD Opal-XT/ Jet-XT

2013-09-07 Rev1.0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

B

C

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2014/09/07

2014/09/07

2014/09/07

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

E

1 81

1 81

1 81

1.0

1.0

1.0

A

B

C

D

E

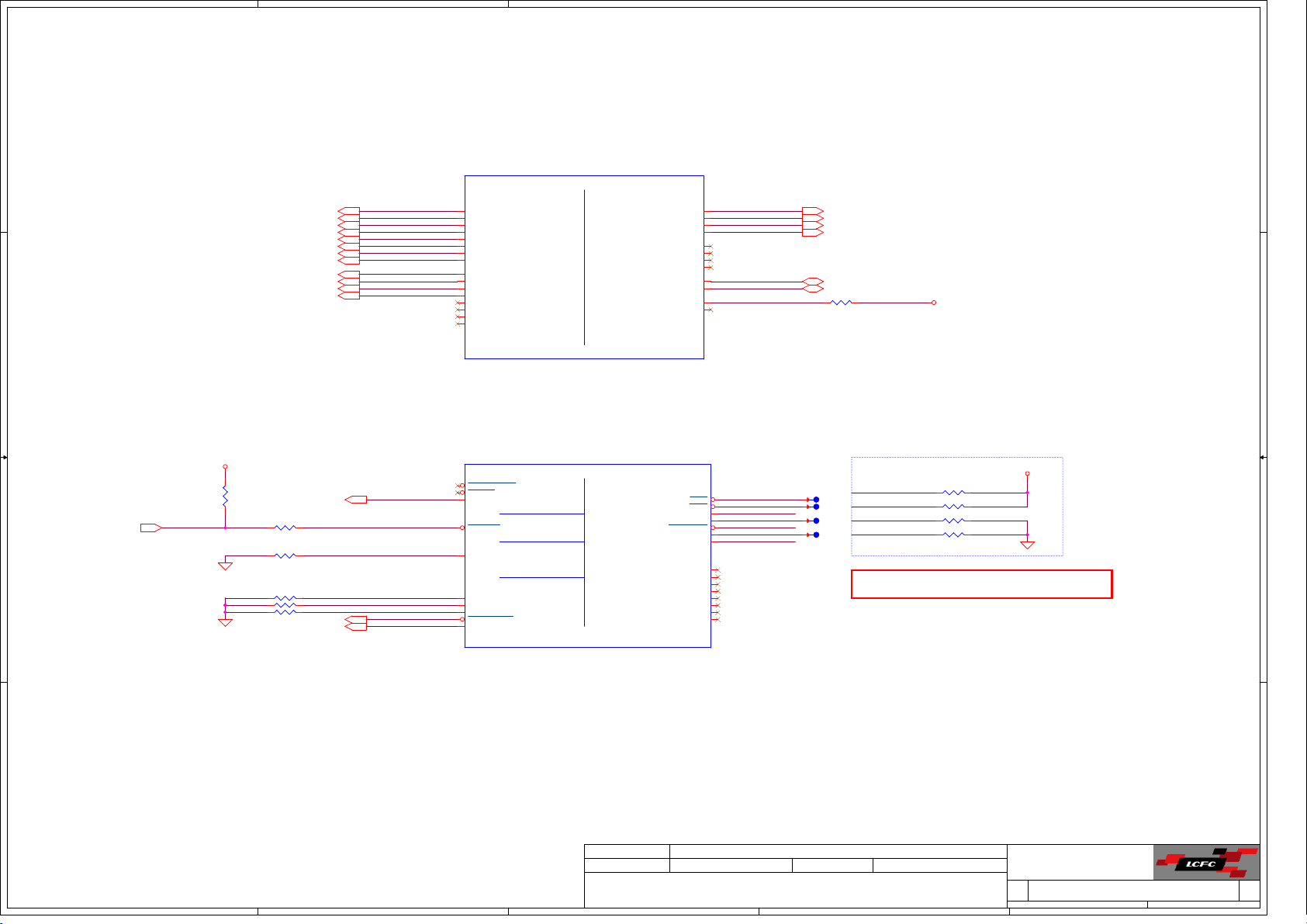

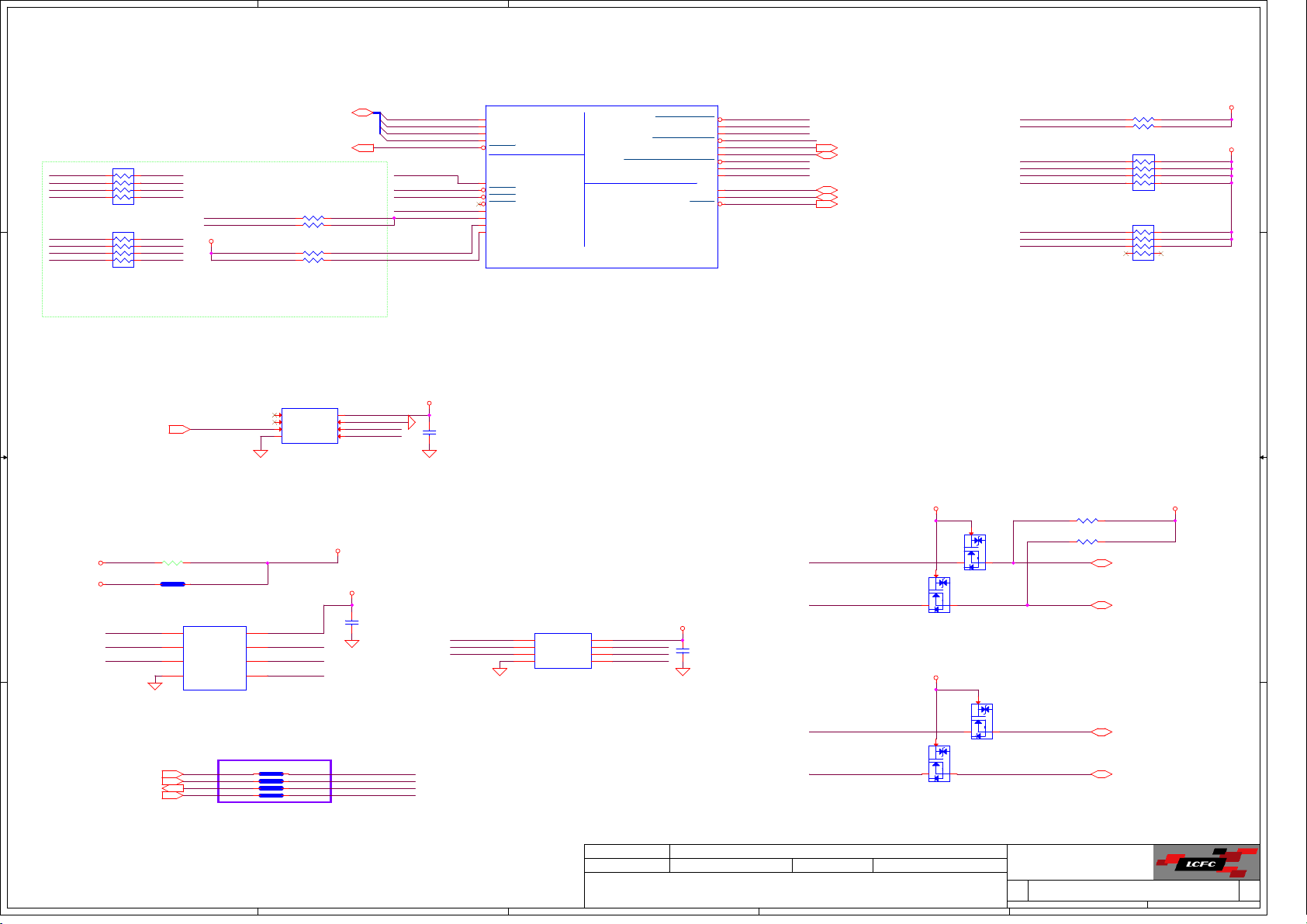

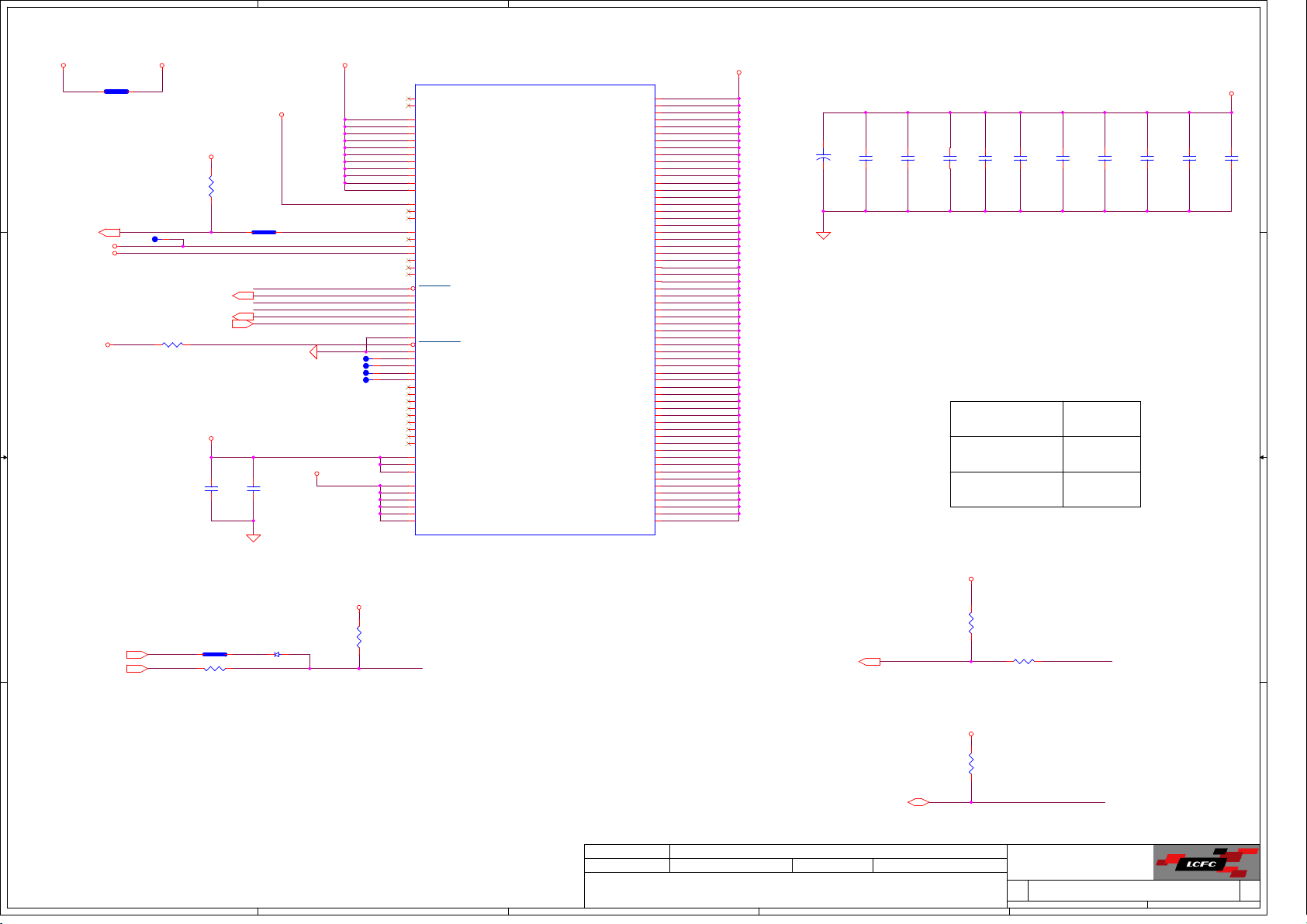

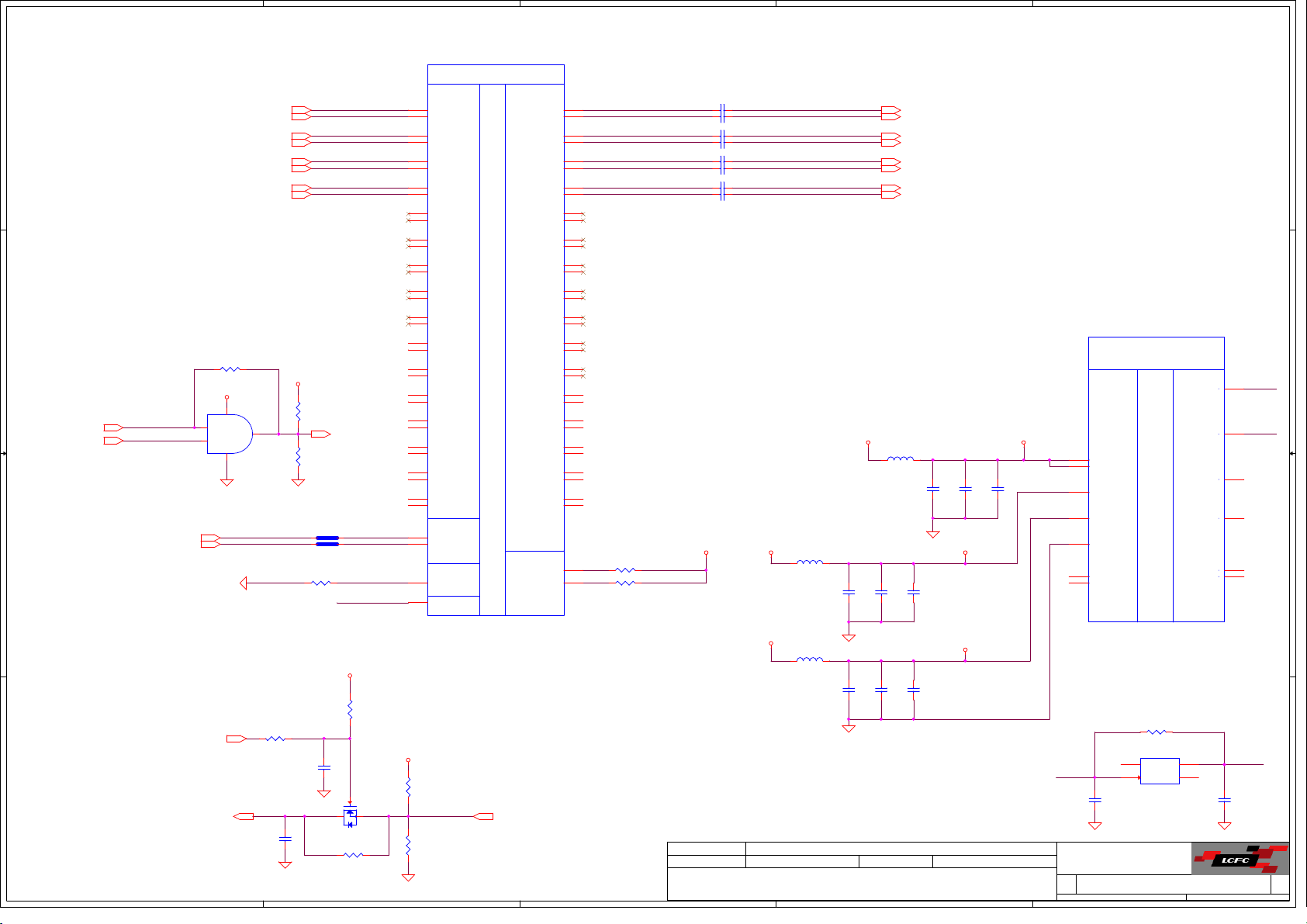

eDP Conn.

USB Port 7

DP Port 0

Page 38

1 1

5V 480MHzUSB 2.0 Port 2 & 3

USB 2.0 Port 7

DP Port0

OneLink board

Page 34

DP Repeater

On OneLink board

HDMI Conn.

Page 46

VGA Conn

2 2

RJ45 Conn.

Page 48

5V 5GT/sUSB 3.0 Port 4

DDI1 HDMI

DDI2 DP

Traslater to

CRT

Intel

WGI218V-QQJZ Non Vpro

WGI218LM QQJY Vpro

QFN48_6X6

MUX

Page 42

Page 43Page 44

PCIe port 4

Page 47

DDI1

DDI1

DDI2 DP

PCIe Gen1 Port 4

Broad Well

Intel

Crescent Bay

Processor

BGA1168

40mm*24mm

+

Intel WPT Point

Memory BUS (DDRIII)

1DPC (Interleaved)

1.35V DDRIIIL 1333/1600 MT/s

PCIE Port 5

USB 2.0 Port 0,1

5V 480MHz

USB 3.0 Port1,2

5V 5GT/s

PCIe Gen1 Port 3

SATA Gen3 Port 1

USB 2.0 port 4&6

JUSB1

USB 3.0 Port 2

USB 2.0 Port 1

NGFF Card WLAN

USB Left

Page 41

NGFF Card

PCIe Port 3

USB 2.0 port6

page 52

DDR3L-SO-DIMM X2

BANK 0, 1, 2, 3

UP TO 16G

Jet-XT M2 (AMD Radeon R5 M240)

Topaz-XT M2(AMD Radeon R5 M240)

VRAM 128M*16 *8

VRAM 256M*16 *8

JUSB2

USB 3.0 Port 1

USB 2.0 Port 0

Page 40

NGFF Card

mSATA/WWAN(option)

SATA Port 1

USB 2.0 port4

page 52

Page 18~19

PCIe port 5

Page 20~29

Realtek

RTS5227E

PCIe Gen1 Port 6

PCH

SD/MMC/XD Conn

Page 32

3 3

Power Circuit DC/DC

Page 65~70

One-Link Docking Board

&

SPI ROM

(8MB for NVpro)

(12MB for Vpro)

Page 9

SPI BUS

3.3V 33MHz

LPC BUS

3.3V 33MHz

USB3.0 Port3

Mirror function

Combon Jack Board

EC

ITE IT8586E/FX

Page 62

USB 2.0 Port 5

SATA Gen3 Port 0 SATA HDD

HD Audio

3.3V 24MHz

USB 2.0 Port 4

Finger printer

Page 50

SATA Port 0

page 37

SATA ODDSATA Gen2 Port 1

SATA Port 1

page 37

Codec

ALC3232-CG

Page 35, 36

HP_R/L_JACK

Ext Mic

SP_OUTR/L

SPK Conn.

Page 36

Combon Jack

4 4

Power Board

A

Thermal Sensor

Fintek F75303M

Page 55

B

Int.KBD

Page 51

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Touch Pad Conn

USB Port 4

Page 51

2013/09/07

2013/09/07

2013/09/07

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2014/09/07

2014/09/07

2014/09/07

Page 54

Title

Title

Title

XXXX

XXXX

XXXX

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

2 81

2 81

2 81

E

1.0

1.0

1.0

A

B

C

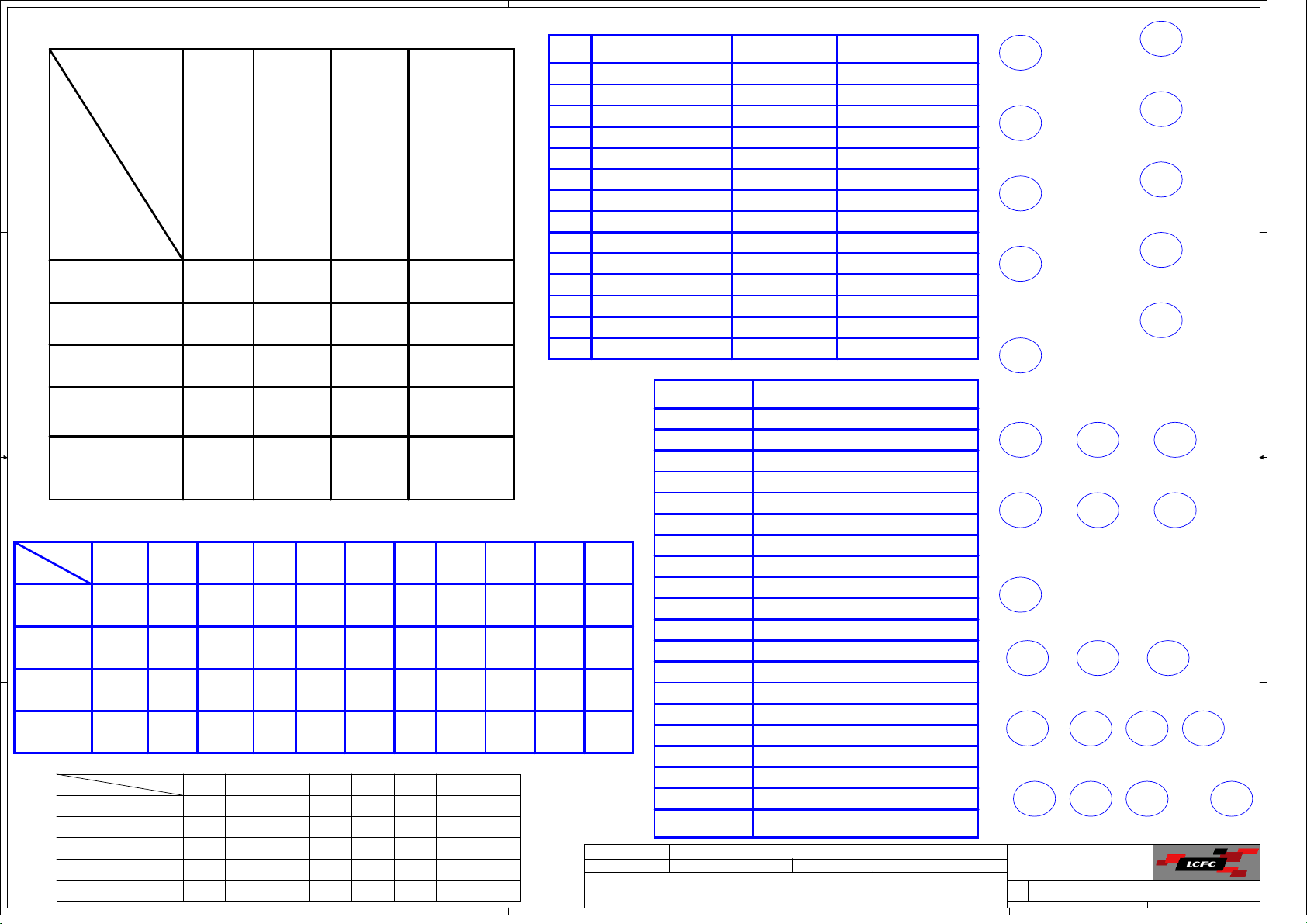

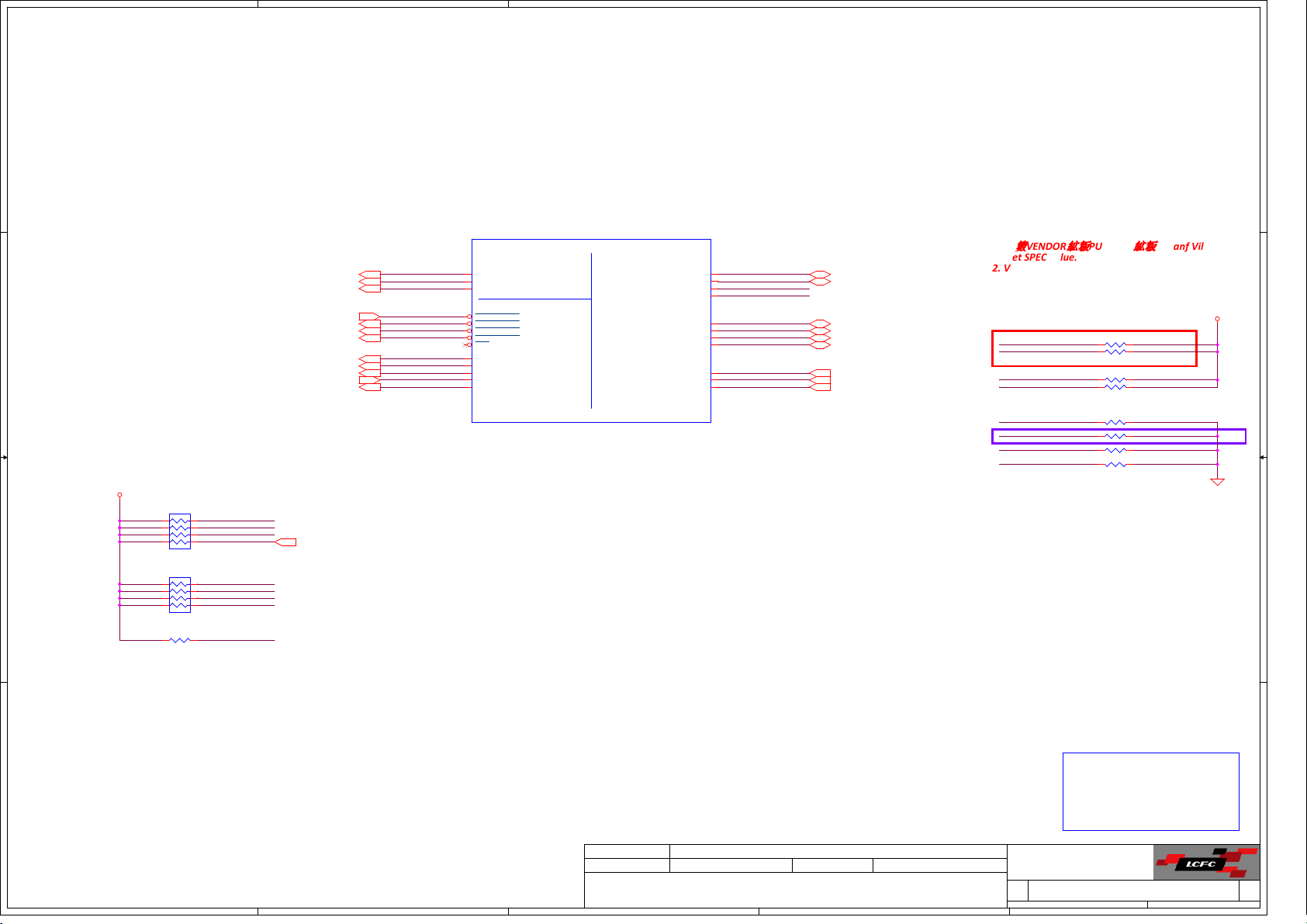

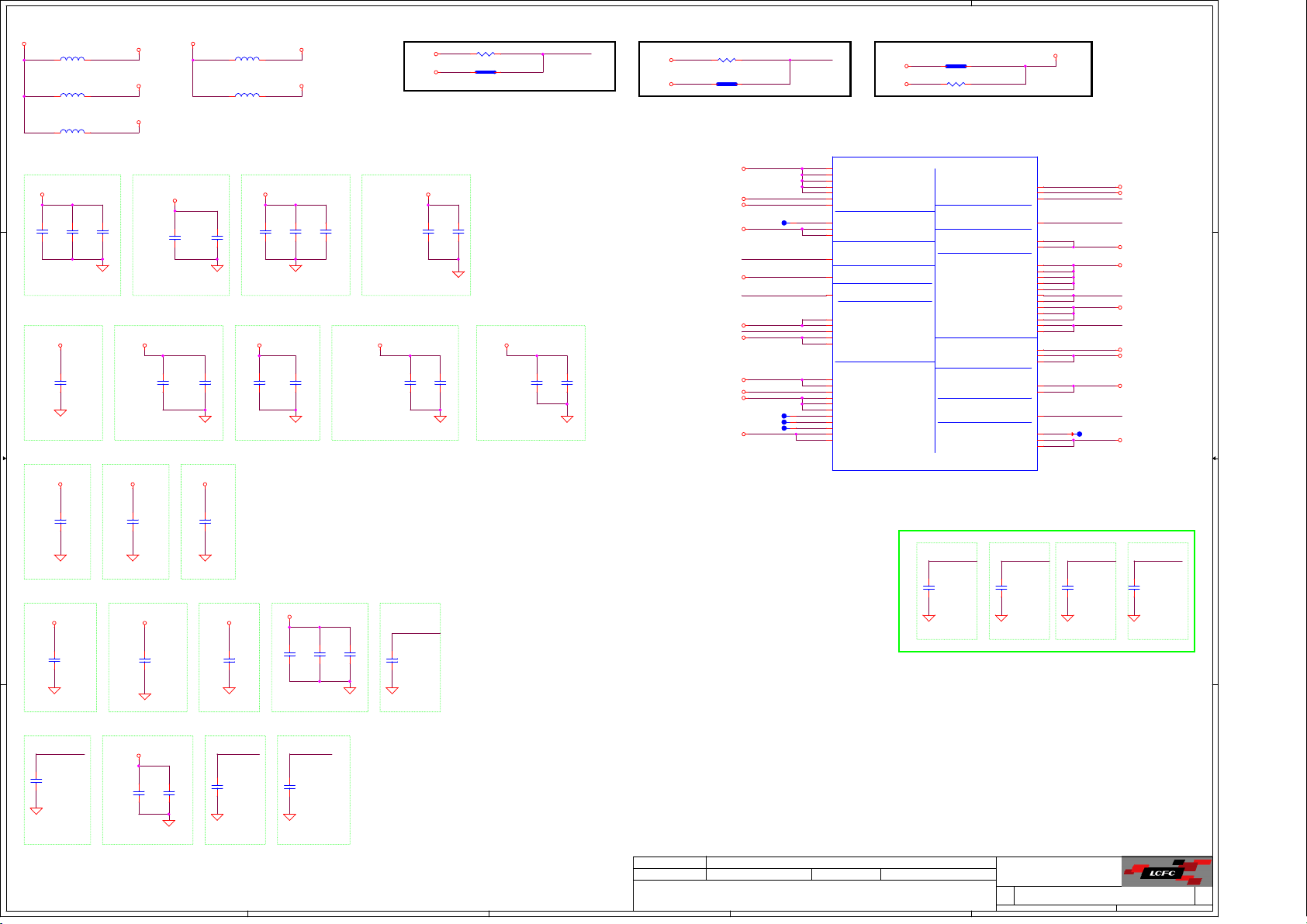

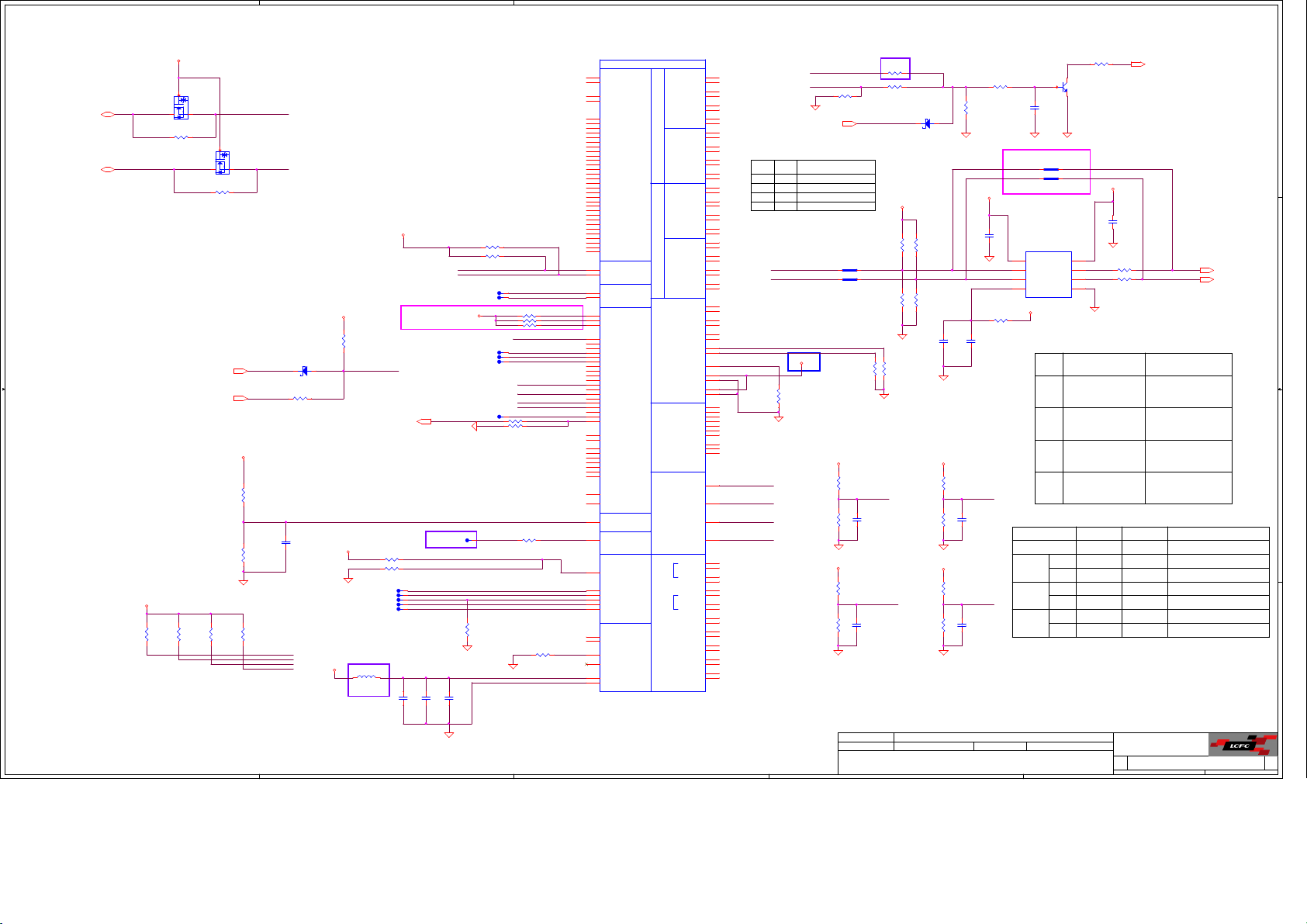

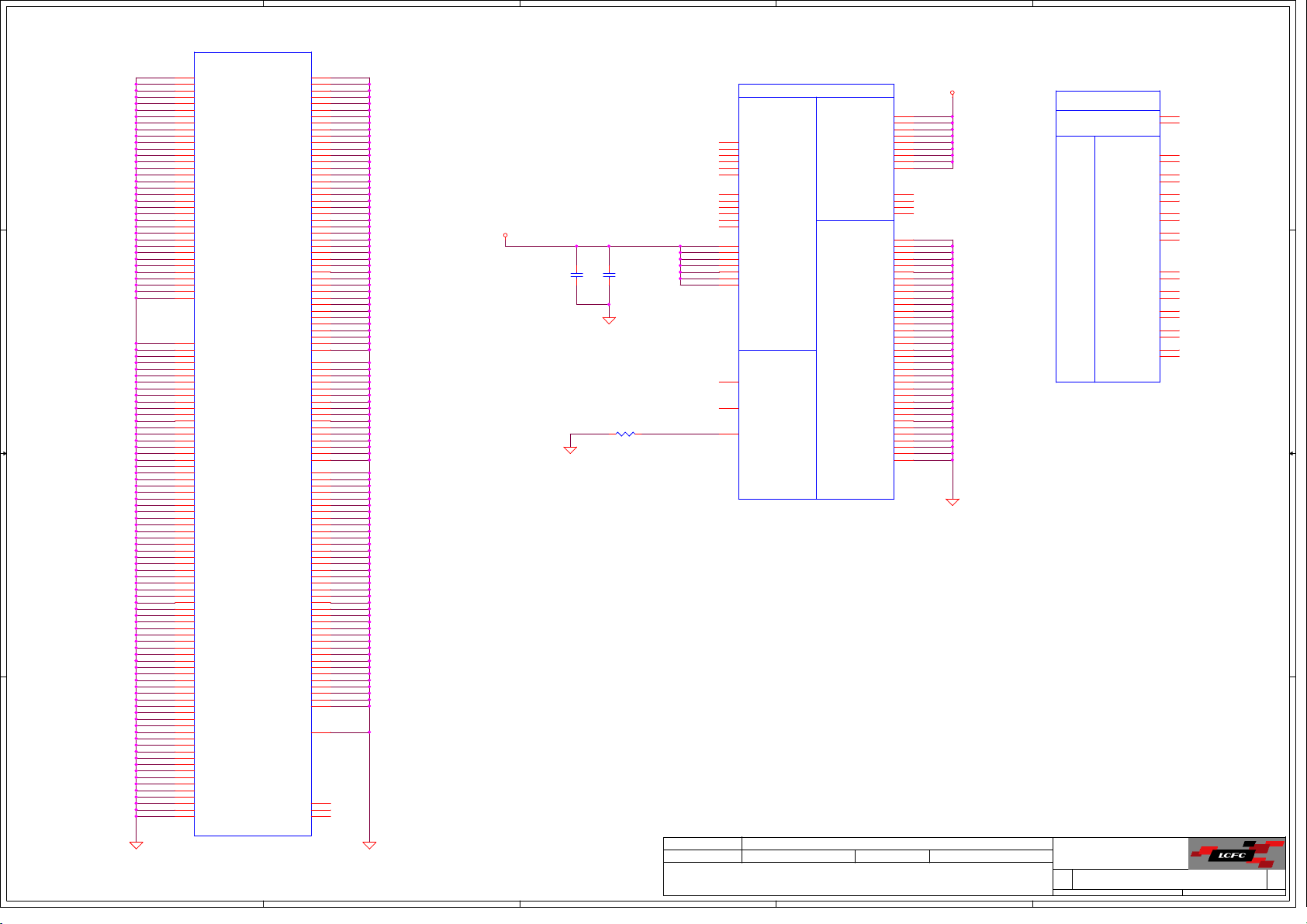

High Speed I/O port

Voltage Rails

Power Plane

1 1

State

S0

S3

2 2

S5 S4/AC Only

S5 S4

Battery only

S5 S4

AC & Battery

don't exist

SMBUS Control Table

3 3

PCH_SML0_CLK

PCH_SML0_DAT

PCH_SML1CLK

PCH_SML1DATA

EC_SMB_CK1

EC_SMB_DA1

PCH_SMBCLK

PCH_SMBDATA

4 4

SOURCE

+3V_PCH

+3V_PCH

IT8586E

+3VL

+3V_PCH

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

( O --> Means ON , X --> Means OFF )

+3VALW

B+

+5VALW

O

O O O

O

O

O

O

X X

X X

PCH

PCH

PCH

Main

VGA

+3VS +3VS

SIGNAL

A

LAN BATT SODIMM

V

+3V_PCH

V

X X X X X X

XX X X X X X X

V

+3VL

X X X X X

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

HIGH

LOWLOWLOW

LOW LOW LOW LOW

IT8586E

V

+3VS

HIGHHIGHHIGH

HIGH

HIGH

+5VS

+3VS

+1.5VS

+VCCSA

+V1.5S_VCCP

+CPU_CORE

+1.5V

OO

X

+VGA_CORE

+GFX_CORE

+1.8VS

+1.05VS

+0.75VS

+3.3VS_VGA

+1.5VS_VGA

+1.05VS_VGA

X

X

X

X

WLAN

WiMAX

V V

+3VS

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

B

X

Thermal

Sensor

V

ON ON

ON

OFF

OFF

OFF

PCH

+3V_PCH

LOW

OFF

OFF

OFF

I/O High Speed Signal

1

USB3 1

2

USB3 2

3

PCIE 1 / USB3 3

4

PCIE 2 / USB3 4

5

PCIE 3

6

PCIE 4

7

PCIE 5 L0

8

PCIE 5 L1

9

PCIE 5 L2

10

PCIE 5 L3

11

PCIE 6 L0 / SATA 3

12

PCIE 6 L1 / SATA 2

13

PCIE 6 L2 / SATA 1

14

PCIE 6 L3 / SATA 0

Configuration

USB3 1

USB3 2

NC

USB3 4

PCIE 3

PCIE 4

PCIE 5 L0

PCIE 5 L1

PCIE 5 L2

PCIE 5 L3

PCIE 6

SATA 2

SATA 1

SATA 0

BOM Structure Table

PCB@ For PCB load BOM

3G@

TPM@

NM14@

NM15@

UMA@

CP

Module

Charger

DIS@

X76@

M2G@

X

M1G@

S2G@

X

XXXXXXXX

V

+3VL

S1G@

ME@

TS@ Touch screen function

DEBUG@ For debug

VX X

+3VS

NVPRO@ For Non-VPRO function

VPRO@ For VPRO function

X76_S2G@

S2G@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2013/09/07

2013/09/07

2013/09/07

3G function(Option with TS@)

Trusted Platform Module (TPM)

14" SKU ID

15" SKU ID

UMA SKU ID

Optimus SKU ID

GPU VRAM Setting

Micron 256Mx16 VRAM

Micron 128Mx16 VRAM

Samsung 256Mx16 VRAM

Samsung 128Mx16 VRAM

ME Connector

For bypassBYPASS@

For mirror functionMIRROR@

For Samsung 2G VRAM

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Port assignment

On MB USB

On MB USB

NC

Docking USB

WLAN

LAN

GPU

GPU

GPU

GPU

Cardreader

mSATA

ODD

HDD

NOTEBOM Structure

2014/09/07

2014/09/07

2014/09/07

D

UC1

Haswell-ULT-CL8064701478202_SR16Q

SR16Q@

SA00005VY10

UC1

Broadwell-ULT-CL8065801674128_QG21

QG21@

SA000067H00

UC1

Broadwell-ULT-CL8065801675027_QG22

QG22@

SA000067I00

UC1

Haswell-ULT-CL8064701477400_SR1ED

SR1ED@

SA00005YW10

UV1

JET M2 XT

JET@

SA000066500

ZZZ7

X76_S2G@

K4W4G1646D-BC1A

X7603901003

ZZZ10

X76_S1G@

K4W2G1646Q-BC1A

X7603901004

UL1

VPRO@

WGI218LM-QQJY-B1_QFN48_6X6

SA00005TP10

UC1

BDW-3205U-1.5G

QGZ6@

SA000072M00

UC1

BDW-i3-2G

QH18@

SA000072H00

UC1

HSW I3 4030U

SR1EN@

SA000810100

Title

Title

Title

NOTE LIST

NOTE LIST

NOTE LIST

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Broadwell-1.6GHz ULV 15W 2+2U 1600 DDR ES2

ZZZ8

H5TC4G63AFR-11C

X7603901001

ZZZ11

H5TC2G63FFR-11C

X7603901005

UC1

BDW-3755U-1.7G

QGZ5@

SA000072J00

UC1

BDW-i3-2G

QGZ3@

SA000072P00

UC1

HSW I5 4210U

SR1EF@

SA000066Y20

Thursday, November 06, 2014

Thursday, November 06, 2014

Thursday, November 06, 2014

E

UC1

Broadwell-1.8GHz 15W 2+2U 1600 DDR ES2

QGH9@

SA000810900

UC1

QGHB@

SA000811100

UC1

Broadwell-1.6GHz 15W 2+2U 1333 DDR ES2

Haswell-CL8064701478404 QEAR D0

Haswell-CL8064701477600 QEAH D0 2.0G

QGHA@

SA000811000

UC1

QEAR@

SA00005YZ00

UC1

QEAH@

SA000066W00

X76_H2G@

X76_H1G@

ZZZ9

MT41J256M16HA-093G:E

X7603901002

ZZZ12

MT41J128M16JT-093G:K

X7603901006

UC1

BDW-i7-2.2G

QH15@

SA000072L00

UC1

BDW-i5-2G

QH17@

SA000072K00

UC1

HSW I3 4005U

SR1EK@

SA00005YZ20

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

E

X76_M2G@

X76_M1G@

UC1

BDW-3805U-1.9G

QGZ4@

SA000072N00

ZZZ1

NM-A221

PCB@

DAZ0TS00100

3 81

3 81

3 81

1.0

1.0

1.0

5

4

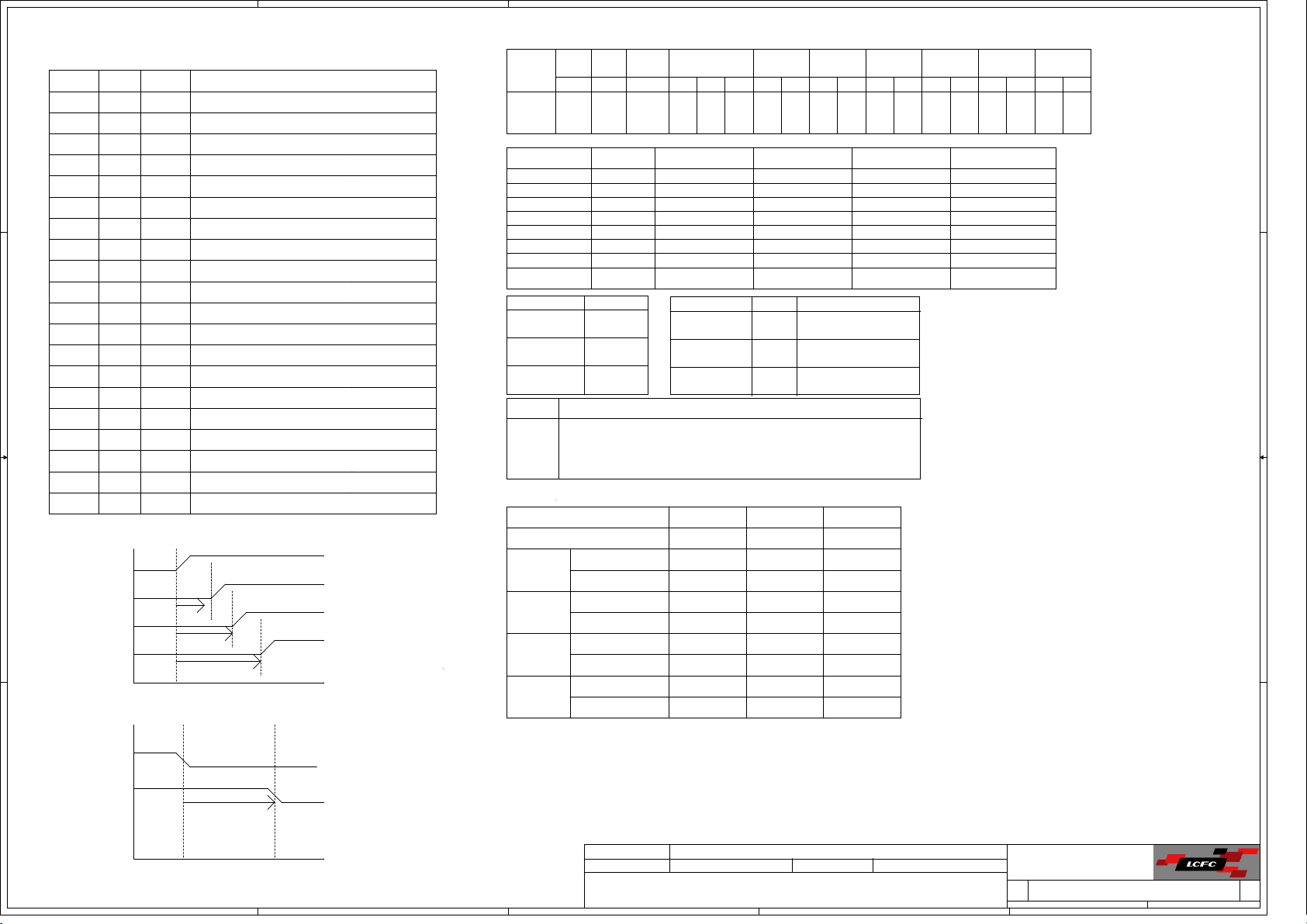

3

2

1

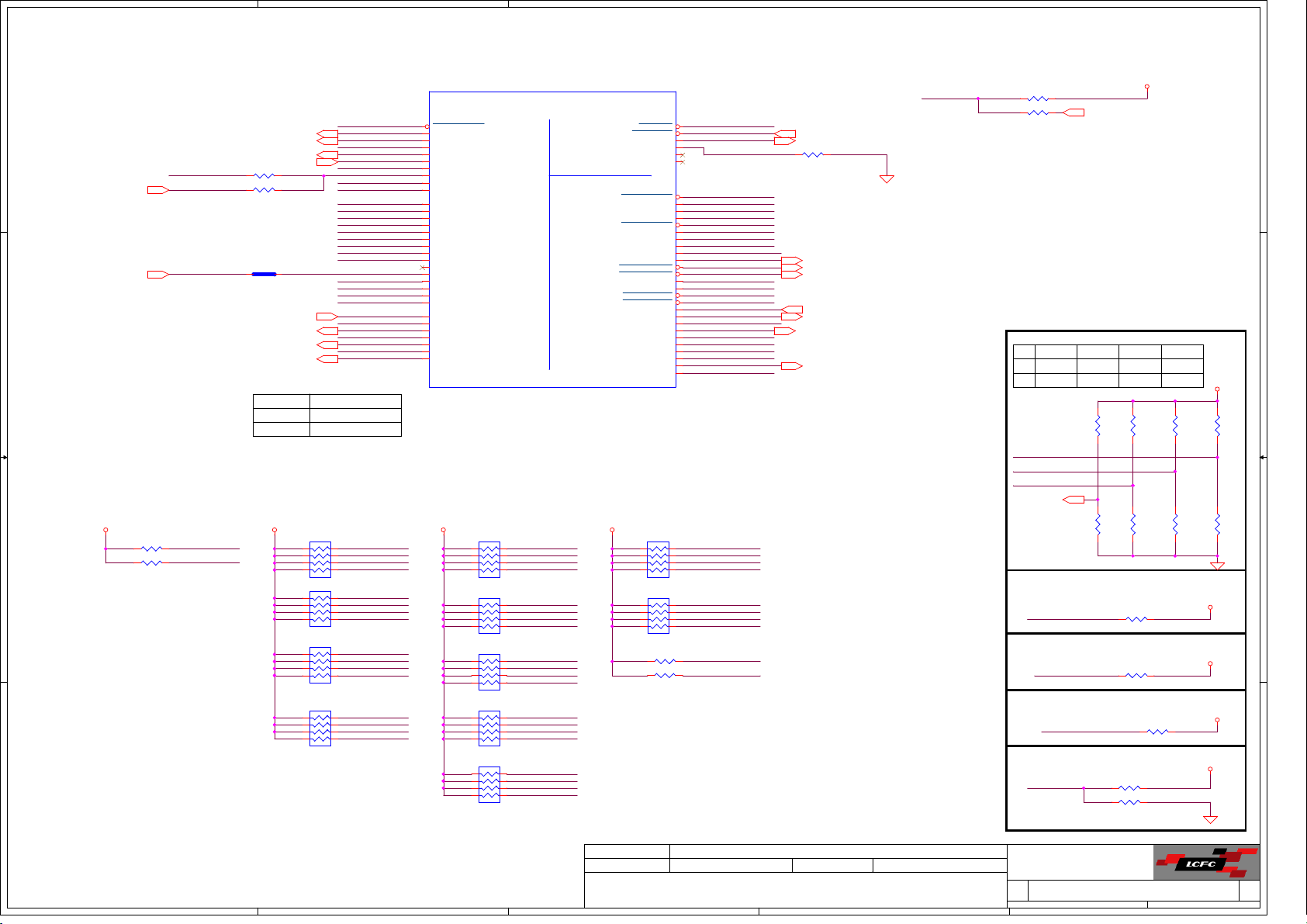

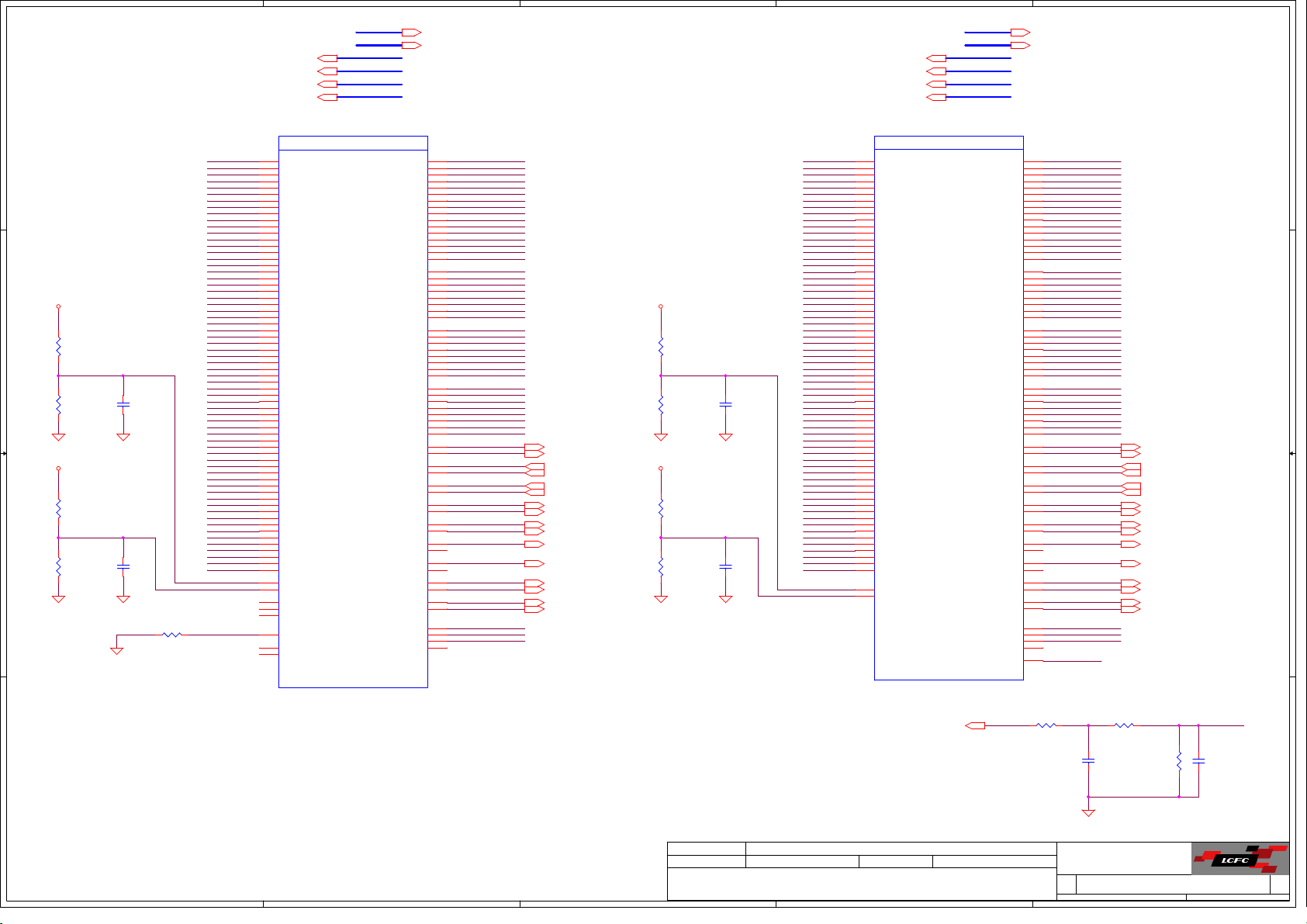

Hot plug detect for IFP link E

VGA and GDDR5 Voltage Rails (N13Px GPIO)

GPIO I/O ACTIVE Function Description

GPIO0

D D

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

C C

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

B B

+1.05VS_VGA

OUT GPU VID4-

OUT

OUT

OUT

OUT

OUT

OUT

I/O

OUT

OUT

IN

OUT

OUT

IN

OUT

IN

IN

IN

+3VS_VGA

+VGA_CORE

+1.5VS_VGA

-

GPU VID3OUT

VGA_BL_PWM

-

-

VGA_ENVDD

- VGA_ENBKL

GPU VID1

-

GPU VID2

-

DPRSLPVR_VGA

-

Thermal Catastrophic Over Temperature

-

GPIO9

-

Memory VREF Control

-

GPU VID0-OUT

AC Power Detect Input

GPU VID5-

FB_CLAMP_TOGGLE_REQ#

-

N/A (100K pull low)

FRMLCK#

-

N/A

-

dGPU_HDMI_HPD

HPD_IRQ

-

tNVVDD >0

tFBVDDQ >0

tPEX_VDD >0

1. all power rail ramp up time should be larger than 40us

(10K pull High)

Performance Mode P0 TDP at Tj = 102 C* (GDDR5)

GPU Mem NVCLK

Products

N13X

128bit

1GB

GDDR5

Physical

Strapping pin

ROM_SCLK

(4) (1,5) (6)

(W) (W) (MHz)

ROM_SI

ROM_SO FB[0]

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

/MCLK NVVDD

(V) (A) (W) (A) (W)

TBD TBDTBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD

Power Rail

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

Logical

Strapping Bit3

PCI_DEVID[4]

FB[1]

PCI_DEVID[3] PCI_DEVID[2] PCI_DEVID[1] PCI_DEVID[0]

SOR3_EXPOSED

RESERVED PCIE_SPEED_

Device ID

N13P-GT

(28nm)

0x0FDB

SMB_ALT_ADDR

(ROM_SO Bit 1)

FBVDD

Logical

Strapping Bit2

SUB_VENDOR

USER[2] USER[1] USER[0]USER[3]

3GIO_PAD_CFG_ADR[2] 3GIO_PAD_CFG_ADR[1]3GIO_PAD_CFG_ADR[3]

SOR2_EXPOSED SOR1_EXPOSED

CHANGE_GEN3

setting

0

1

ROM_SO ROM_SCLK

GPU

N13P-GT1

28nm

GPU

FB Memory (GDDR5)

Samsung

2500MHz

Hynix

2500MHz

Samsung

2500MHz

2500MHz

PU 25K

PU 45KPU 10K PD 10K

PU 25K PD 35KPU 45KPU 20K PD 10K PD 5K PD 10K

K4G10325FG-HC04

32Mx32

H5GQ1H24BFR-T2C

32Mx32 PD 35K

K4G20325FD-FC04

64Mx32

H5GQ2H24MFR-T2CHynix

64Mx32

PD 35K

N13P-GT

ROM_SI

PD 45K

PD 30K

PD 25K

FBVDDQ PCI Express I/O and

(GPU+Mem)

(1.35V)(1.35V)

(A) (W) (W)(mA) (W) (W) (W)(mA) (mA) (mA)

I2C Slave addrees ID

0x9E

0x9C

STRAP2STRAP1STRAP0

STRAP3

PU 5K PD 10K

(1.05V)

Logical

Strapping Bit1

SLOT_CLK_CFG

RAM_CFG[1]RAM_CFG[3] RAM_CFG[2]

PLLVDD

I/O and

PLLVDD

Logical

Strapping Bit0

PEX_PLL_EN_TERM

RAM_CFG[0]

VGA_DEVICESMB_ALT_ADDR

3GIO_PAD_CFG_ADR[0]

PCIE_MAX_SPEED DP_PLL_VDD33V

SOR0_EXPOSED

STRAP4

Master

Slave

Other

(3.3V)(1.05V)(1.8V)

Other Power rail

A A

+3VS_VGA

Tpower-off <10ms

1.all GPU power rails should be turned off within 10ms

2. Optimus system VDD33 avoids drop down earlier than NVDD and FBVDDQ

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

VGA NOTE

VGA NOTE

VGA NOTE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

4 81

4 81

4 81

1.0

1.0

1.0

5

D D

4

3

2

1

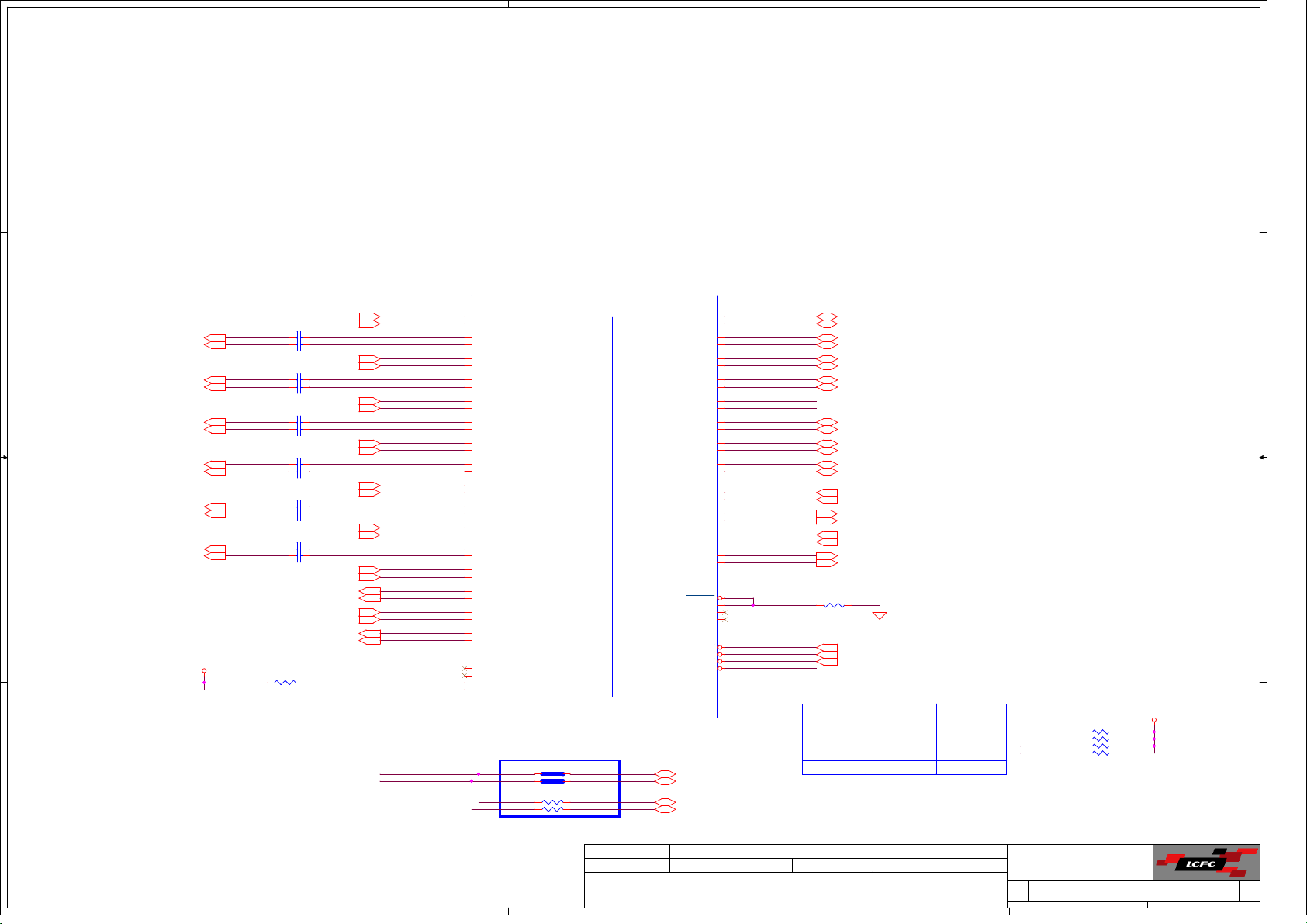

MISC

THERMAL

PWR

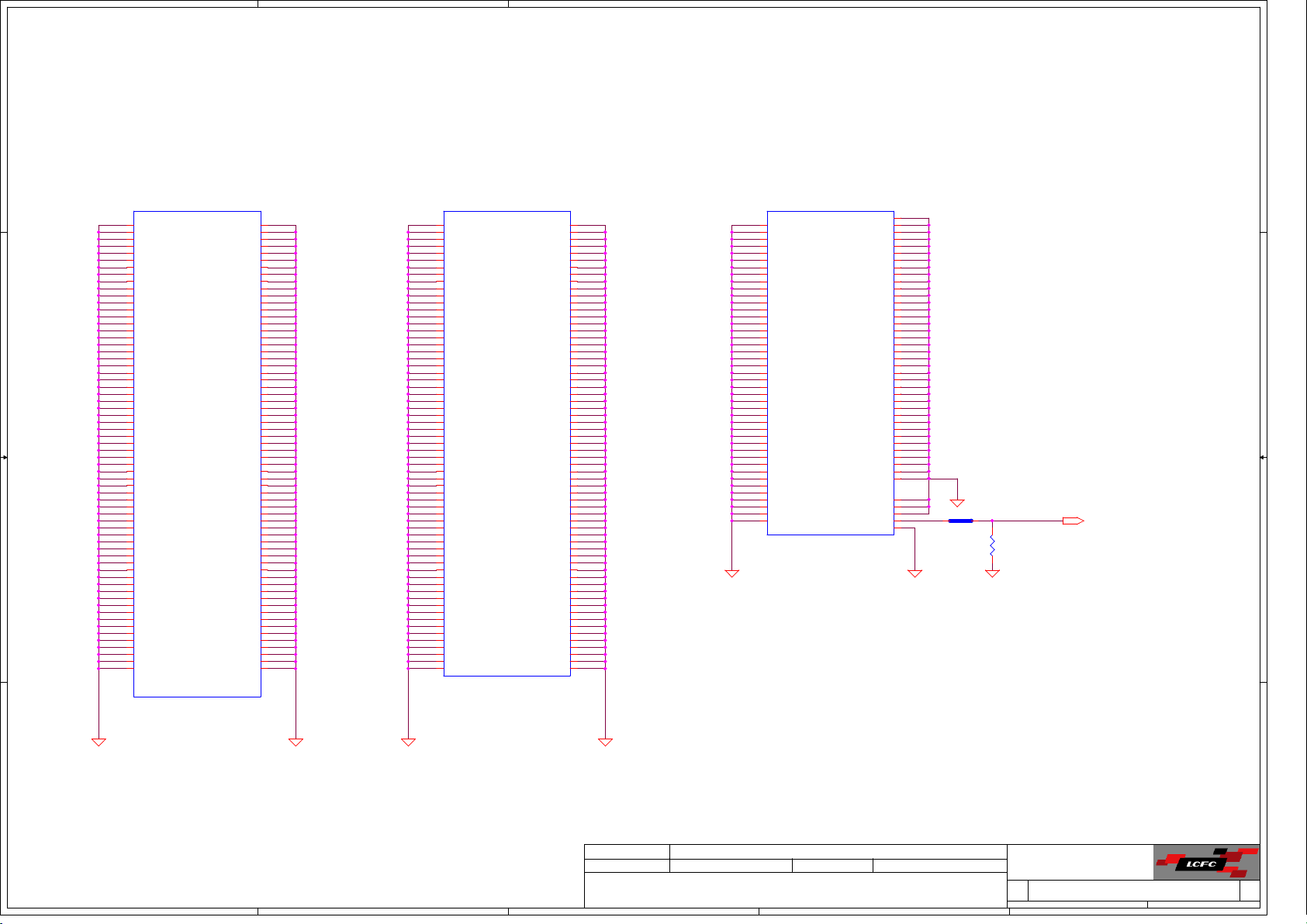

DDR3L

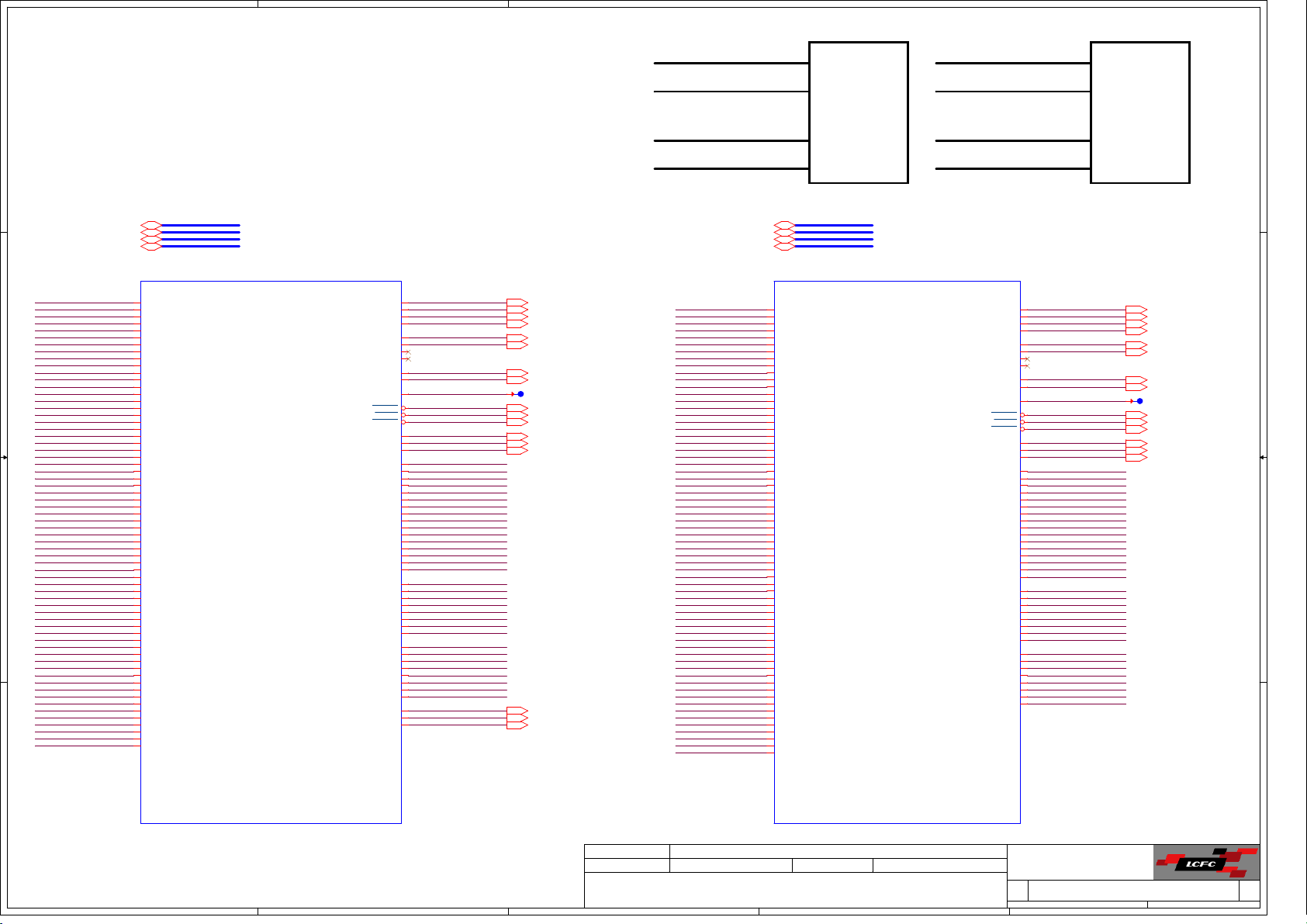

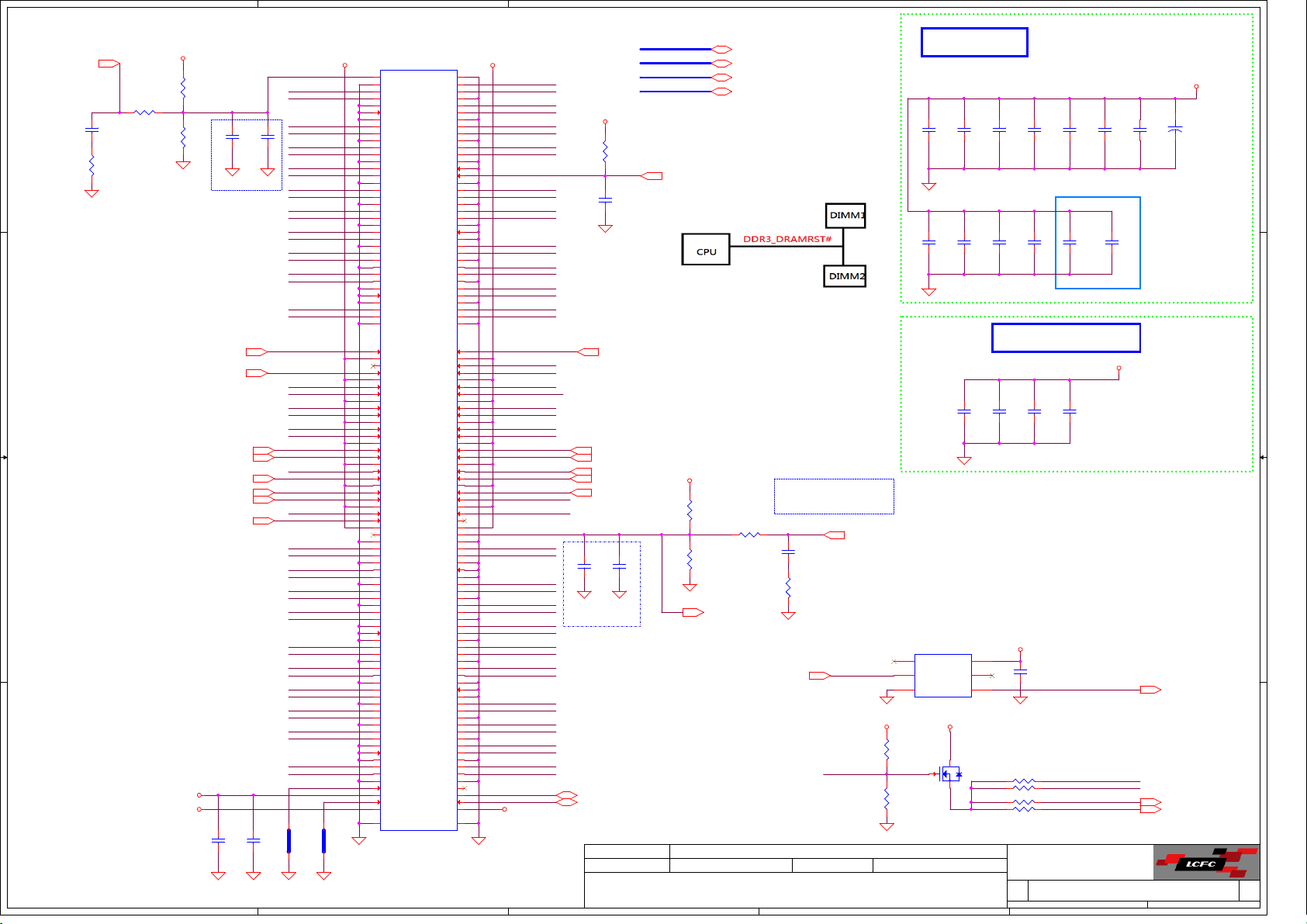

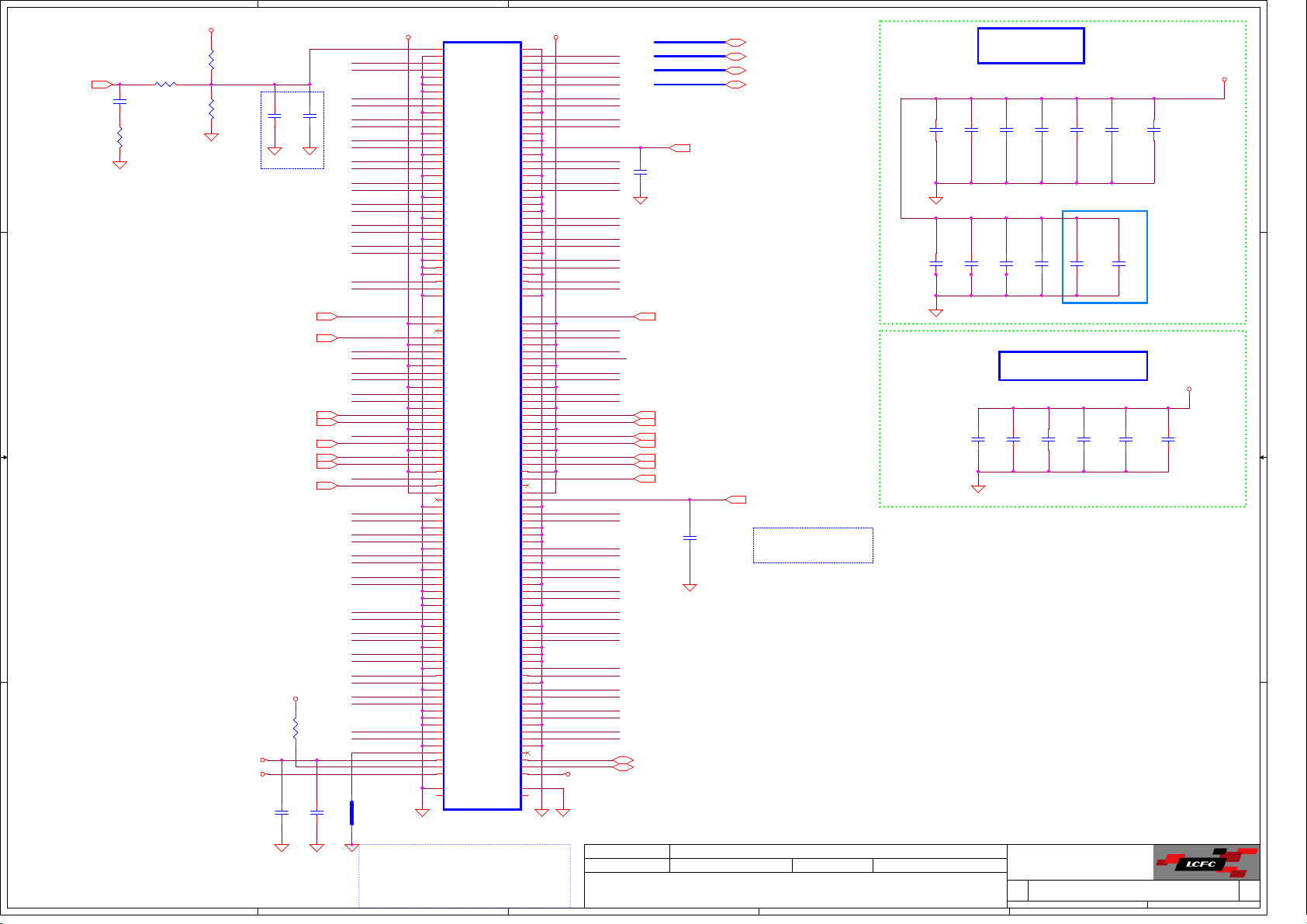

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

2 OF 19

QFSY@

C45

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDPDDI

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

CPU_EDP_TX0-

B46

CPU_EDP_TX0+

A47

CPU_EDP_TX1-

B47

CPU_EDP_TX1+

C47

C46

A49

B49

A45

CPU_EDP_AUX#

B45

CPU_EDP_AUX

D20

EDP_COMP

A43

CPU_EDP_TX0- <38>

CPU_EDP_TX0+ <38>

CPU_EDP_TX1- <38>

CPU_EDP_TX1+ <38>

CPU_EDP_AUX# <38>

CPU_EDP_AUX <38>

2

1

RC1 24.9_0402_1%

+VCCIOA_OUT

+1.05VS_VCCST

1 2

RC164 51_0402_1%XDP@

1 2

RC3 51_0402_1%XDP@

RC4 51_0402_1%

RC6 51_0402_1%@

2

1

2

1

JTAG

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

1

1

1

1

XDP_TDI

T1

XDP_TDO

T2

XDP_TCLK

T3

XDP_TRST#

T4

XDP PU/PD portion need to check agian.

UC1A

DDI1_MUX_TX0-<42>

DDI1_MUX_TX0+<42>

C C

+1.05VS_VCCST

12

RC2

62_0402_5%

VR_HOT#<62,67,73>

B B

VR_HOT#

DDI1_MUX_TX1-<42>

DDI1_MUX_TX1+<42>

DDI1_MUX_TX2-<42>

DDI1_MUX_TX2+<42>

DDI1_MUX_TX3-<42>

DDI1_MUX_TX3+<42>

DDI2_VGA_TX0-<43>

DDI2_VGA_TX0+<43>

DDI2_VGA_TX1-<43>

DDI2_VGA_TX1+<43>

H_PECI<62>

2

1

RC5 56_0402_5%

2

1

RC7 10K_0402_5%

1 2

RC8 200_0402_1%

1 2

RC9 120_0402_1%

1 2

RC10 100_0402_1%

DDR3_DRAMRST#<18,19>

DDR_PG_CTRL<18>

DDI1_MUX_TX0DDI1_MUX_TX0+

DDI1_MUX_TX1DDI1_MUX_TX1+

DDI1_MUX_TX2DDI1_MUX_TX2+

DDI1_MUX_TX3DDI1_MUX_TX3+

DDI2_VGA_TX0DDI2_VGA_TX0+

DDI2_VGA_TX1DDI2_VGA_TX1+

H_PECI

VR_HOT#_R

H_CPUPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR3_DRAMRST#

DDR_PG_CTRL

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

Broadwell-ULT_CL8064701614813_QFSY

SA000064600

UC1B

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

Broadwell-ULT_CL8064701614813_QFSY

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

BDW_DDI/EDP/XDP

BDW_DDI/EDP/XDP

BDW_DDI/EDP/XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

5 81

5 81

5 81

1.0

1.0

1.0

5

4

3

2

1

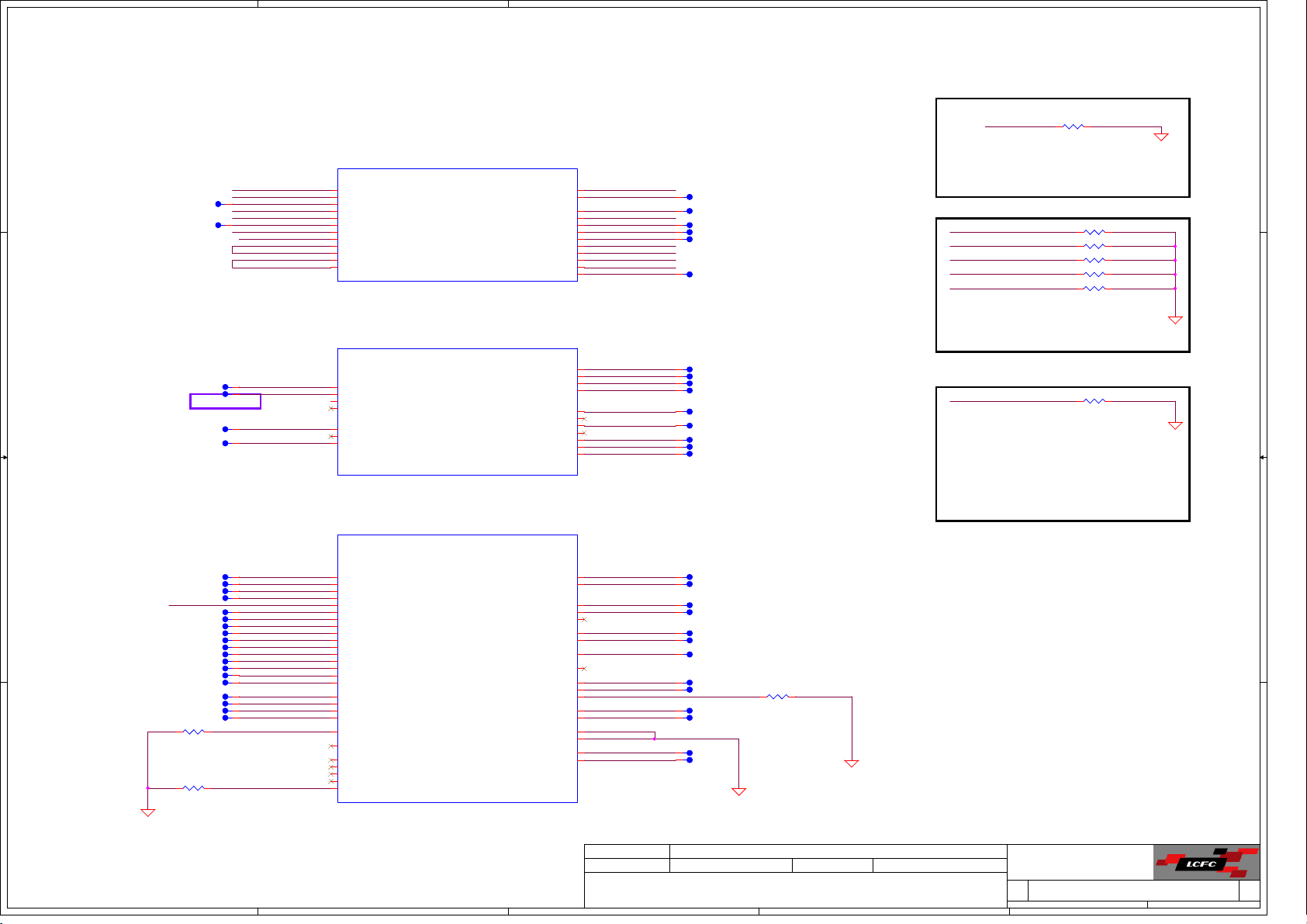

Interleaved (Butterfly Topology)

Broadwell Platform System Memory Interface

Document Number: 528378

BDW U DDR3L/DDR3L-RS SO-DIMM Interleaved Recommendations

D D

Channel A Byte 0 & 1

Channel B Byte 0 & 1

Channel A Byte 2 & 3

MCP

Channel A

Channel B Byte 2 & 3

DDR_A_D[0..63]<18> DDR_B_D[0..63]<19>

DDR_A_DQS#[0..7]<18>

DDR_A_DQS[0..7]<18>

DDR_A_MA[0..15]<18> DDR_B_MA[0..15]<19>

UC1C

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

C C

B B

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

SA_CLK_DDR#0

SA_CLK_DDR0

SA_CLK_DDR#1

SA_CLK_DDR1

DDRA_CKE0_DIMMA

DDRA_CKE1_DIMMA

DDRA_CS0_DIMMA#

DDRA_CS1_DIMMA#

DDRA_ODT0

DDR_A_RAS#

DDR_A_WE#

DDR_A_CAS#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_B_DQS#0

DDR_B_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_B_DQS#2

DDR_B_DQS#3

DDR_A_DQS0

DDR_A_DQS1

DDR_B_DQS0

DDR_B_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_B_DQS2

DDR_B_DQS3

SM_DIMM_VREFCA

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

SA_CLK_DDR#0 <18>

SA_CLK_DDR0 <18>

SA_CLK_DDR#1 <18>

SA_CLK_DDR1 <18>

DDRA_CKE0_DIMMA <18>

DDRA_CKE1_DIMMA <18>

DDRA_CS0_DIMMA# <18>

DDRA_CS1_DIMMA# <18>

1

T5

DDR_A_RAS# <18>

DDR_A_WE# <18>

DDR_A_CAS# <18>

DDR_A_BS0 <18>

DDR_A_BS1 <18>

DDR_A_BS2 <18>

SM_DIMM_VREFCA <18>

SA_DIMM_VREFDQ <18>

SB_DIMM_VREFDQ <19>

DDR_B_DQS#[0..7]<19>

DDR_B_DQS[0..7]<19>

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

UC1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

Channel A Byte 4 & 5

Channel B Byte 4 & 5

Channel A Byte 6 & 7

Channel B Byte 6 & 7

AM38

SB_CK#0

AN38

SB_CK0

AK38

SB_CK#1

AL38

SB_CK1

AY49

SB_CKE0

AU50

SB_CKE1

AW49

SB_CKE2

AV50

SB_CKE3

AM32

SB_CS#0

AK32

SB_CS#1

AL32

SB_ODT0

AM35

SB_RAS

AK35

SB_WE

AM33

SB_CAS

AL35

SB_BA0

AM36

SB_BA1

AU49

SB_BA2

AP40

SB_MA0

AR40

SB_MA1

AP42

SB_MA2

AR42

SB_MA3

AR45

SB_MA4

AP45

SB_MA5

AW46

SB_MA6

AY46

SB_MA7

AY47

SB_MA8

AU46

SB_MA9

AK36

SB_MA10

AV47

SB_MA11

AU47

SB_MA12

AK33

SB_MA13

AR46

SB_MA14

AP46

SB_MA15

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDR_A_DQS#4

DDR_A_DQS#5

DDR_B_DQS#4

DDR_B_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_B_DQS#6

DDR_B_DQS#7

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

SB_CLK_DDR#0

SB_CLK_DDR0

SB_CLK_DDR#1

SB_CLK_DDR1

DDRB_CKE0_DIMMB

DDRB_CKE1_DIMMB

DDRB_CS0_DIMMB#

DDRB_CS1_DIMMB#

DDRB_ODT0

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_A_DQS4

DDR_A_DQS5

DDR_B_DQS4

DDR_B_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_B_DQS6

DDR_B_DQS7

MCP

Channel B

SB_CLK_DDR#0 <19>

SB_CLK_DDR0 <19>

SB_CLK_DDR#1 <19>

SB_CLK_DDR1 <19>

DDRB_CKE0_DIMMB <19>

DDRB_CKE1_DIMMB <19>

DDRB_CS0_DIMMB# <19>

DDRB_CS1_DIMMB# <19>

1

T6

DDR_B_RAS# <19>

DDR_B_WE# <19>

DDR_B_CAS# <19>

DDR_B_BS0 <19>

DDR_B_BS1 <19>

DDR_B_BS2 <19>

A A

Broadwell-ULT_CL8064701614813_QFSY

5

3 OF 19

Broadwell-ULT_CL8064701614813_QFSY

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4 OF 19

2

2014/09/07

2014/09/07

2014/09/07

Title

Title

Title

BDW_DDR3L INT

BDW_DDR3L INT

BDW_DDR3L INT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

6 81

6 81

6 81

of

1.0

1.0

1.0

5

4

3

2

1

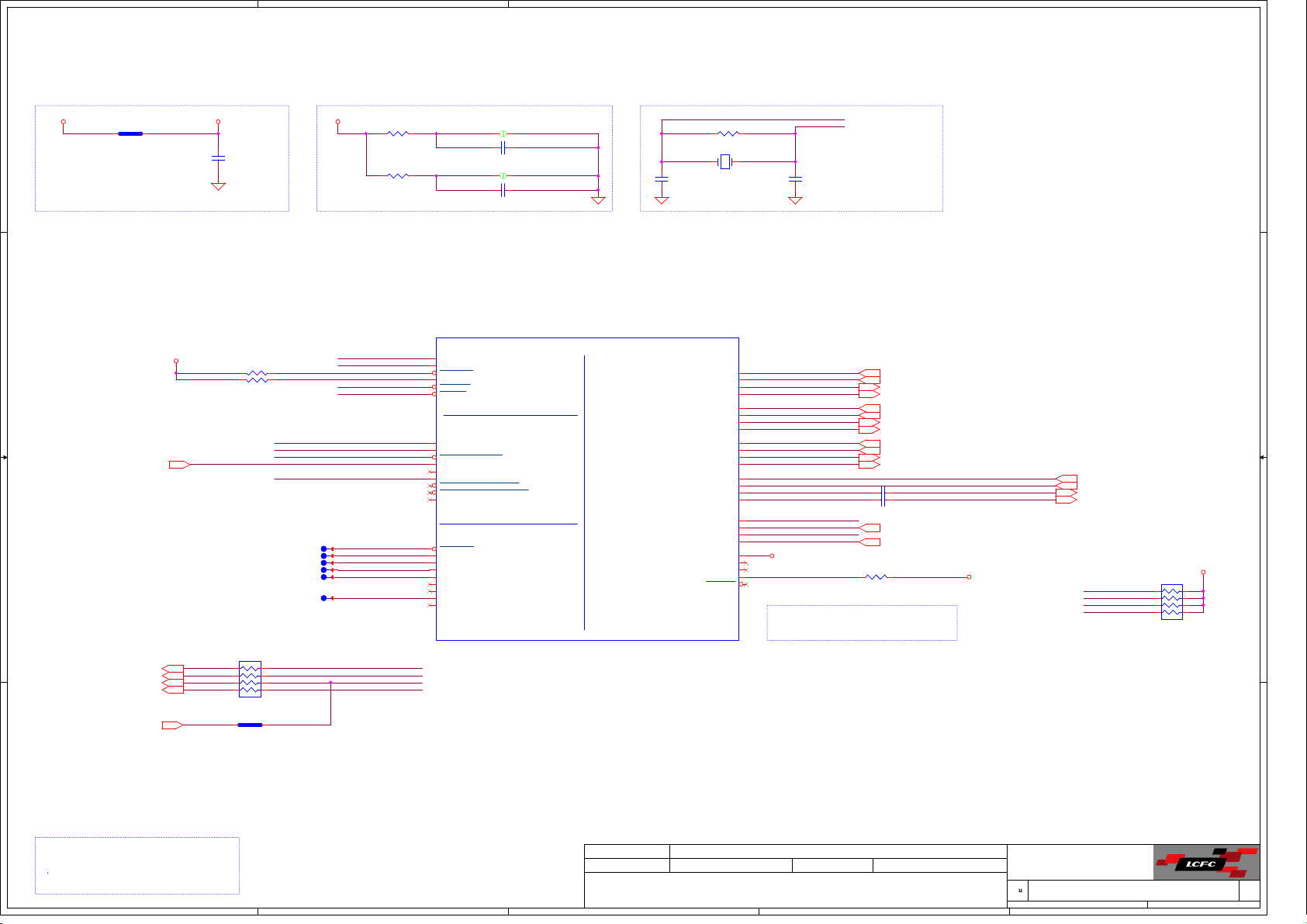

RTC External Circuit

D D

C C

B B

1 2

RC11 0_0402_5%

PCH_HDA_SDIN0<35>

PCH_HDA_RST#<35>

PCH_HDA_BCLK<35>

PCH_HDA_SDOUT<35>

PCH_HDA_SYNC<35>

ME_FLASH<62>

+RTCVCC+RTCBATT

1

CC2

@

1U_0402_10V6-K

2

+RTCVCC

1

RC16 1M_0402_5%

1 2

RC15 330K_0402_5%

RPC25

1

2

3

4

33_0804_8P4R_5%

SD30000370T

1 2

RC44 0_0402_5%

8

7

6

5

JCMOS, JME Setting, Need Under DDR Door

+RTCVCC

2

T8

T9

T10

T11

T12

T13

PCH_RTCX1

PCH_RTCX2

PCH_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST#

PCH_RTCRST#

HDA_BCLK

HDA_SYNC

HDA_RST#

PCH_HDA_SDIN0

HDA_SDOUT

1

PCH_JTAG_TRST#

1

PCH_JTAG_TCK

1

PCH_JTAG_TDI

1

PCH_JTAG_TDO

1

PCH_JTAG_TMS

1

PCH_JTAGX

HDA_RST#

HDA_BCLK

HDA_SDOUT

HDA_SYNC

1 2

1 2

RC12

20K_0402_5%

RC14

20K_0402_5%

JCMOS1 @

PCH_RTCRST#

PCH_SRTCRST#

UC1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD1

AC4

RSVD2

AE63

JTAGX

AV2

RSVD0

Broadwell-ULT_CL8064701614813_QFSY

1 2

1

CC1 1U_0402_10V6-K

JME1 @

1 2

1

CC5 1U_0402_10V6-K

2

2

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

5 OF 19

RTC Crystal

1

2

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

RC13

1

10M_0402_5%

YC1

2

1

32.768KHZ_12.5PF_9H03200042

CC3

12P_0402_50V8-J

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD3

RSVD4

SATA_RCOMP

SATALED

PCH_RTCX1

2

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

PCH_RTCX2

1

CC4

12P_0402_50V8-J

2

SATA_PRX_DTX_N0

SATA_PRX_DTX_P0

SATA_PTX_DRX_N0

SATA_PTX_DRX_P0

SATA_PRX_DTX_N1

SATA_PRX_DTX_P1

SATA_PTX_DRX_N1

SATA_PTX_DRX_P1

SATA_PRX_DTX_N2

SATA_PRX_DTX_P2

SATA_PTX_DRX_N2

SATA_PTX_DRX_P2

PCIE6_CRX_DTX_N

PCIE6_CRX_DTX_P

PCIE6_CTX_DRX_N

PCIE6_CTX_DRX_P

PCH_GPIO34

ODD_DETEC#

PCH_GPIO36

EC_SCI#

+1.05VS_PSATA3PLL

SATACOMP

1 2

CC23 0.1U_0402_10V7-K

1 2

CC24 0.1U_0402_10V7-K

1

RC22 3.01K_0402_1%

SATACOMP

SATA_PRX_DTX_N0 <37>

SATA_PRX_DTX_P0 <37>

SATA_PTX_DRX_N0 <37>

SATA_PTX_DRX_P0 <37>

SATA_PRX_DTX_N1 <37>

SATA_PRX_DTX_P1 <37>

SATA_PTX_DRX_N1 <37>

SATA_PTX_DRX_P1 <37>

SATA_PRX_DTX_N2 <52>

SATA_PRX_DTX_P2 <52>

SATA_PTX_DRX_N2 <52>

SATA_PTX_DRX_P2 <52>

ODD_DETEC# <37>

EC_SCI# <62>

2

HDD

ODD, only for 15"

SSD(NGFF)

PCIE6_CTX_C_DRX_N

PCIE6_CTX_C_DRX_P

Only for 15"

+1.05VS_PSATA3PLL

PCIE6_CRX_DTX_N <32>

PCIE6_CRX_DTX_P <32>

PCIE6_CTX_C_DRX_N <32>

PCIE6_CTX_C_DRX_P <32>

RPC1

PCH_GPIO34

PCH_GPIO36

ODD_DETEC#

EC_SCI#

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

Card Reader

+3VS

A A

INTVRMEN

*

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

Title

Title

RTC/HDA/SATA/PCIe/JTAG

RTC/HDA/SATA/PCIe/JTAG

RTC/HDA/SATA/PCIe/JTAG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

7 81

7 81

7 81

1.0

1.0

1.0

5

D D

4

3

2

1

UC1F

+3VS

WLAN

C C

LAN

VGA

CR

B B

1 2

RC29 10K_0402_5%DIS@

1

RC32 10K_0402_5%UMA@

CLK_PCIE_WLAN#<52>

CLK_PCIE_WLAN<52>

CLKREQ_PCIE2_WLAN#<52>

CLK_PCIE_LAN#<47>

CLK_PCIE_LAN<47>

CLKREQ_PCIE3_LAN#<47>

CLK_PCIE_VGA#<20>

CLK_PCIE_VGA<20>

CLKREQ_PCIE4_VGA#<20>

CLK_PCIE_CR#<32>

CLK_PCIE_CR<32>

CLKREQ_PCIE5_CR#<32>

+3VS

RPC2

1

2

3

4

10K_0804_8P4R_5%

+3VS

1 2

RC165 10K_0402_5%

1 2

RC166 10K_0402_5%

2

UMA@

DIS@

8

7

6

5

PCH_GPIO19

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

CLKREQ_PCIE2_WLAN#

CLK_PCIE_LAN#

CLK_PCIE_LAN

CLKREQ_PCIE3_LAN#

CLK_PCIE_VGA#

CLK_PCIE_VGA

CLKREQ_PCIE4_VGA#

CLK_PCIE_CR#

CLK_PCIE_CR

CLKREQ_PCIE5_CR#

CLKREQ_PCIE2_WLAN#

CLKREQ_PCIE3_LAN#

PCH_GPIO19

CLKREQ_PCIE5_CR#

CLKREQ_PCIE4_VGA#CLKREQ_PCIE4_VGA#

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

Broadwell-ULT_CL8064701614813_QFSY

HSW_ULT_DDR3L

CLOCK

SIGNALS

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD5

RSVD6

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

PCH_XTAL24_IN

PCH_XTAL24_OUT

DIFFCLK_BIASREF

MCP_TESTLOW1

MCP_TESTLOW2

MCP_TESTLOW3

MCP_TESTLOW4

PCH_PCI_CLK_R

CLK_PCI_TPM_R

MCP_TESTLOW3

MCP_TESTLOW4

MCP_TESTLOW1

MCP_TESTLOW2

RC23 3.01K_0402_1%

2

1

RC24 22_0402_5%

1 2

RC25 22_0402_5%TPM@

RPC4

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

+1.05VS_PLPTCLKPLL

2

1

CLK_PCI_EC <62>

CLK_PCI_TPM <56>

PCH_XTAL24_IN

PCH_XTAL24_OUTDISCRETE_PRESENCE

12P_0402_50V8-J

CC6

1

1

2

RC30

1 2

1M_0402_5%

YC2

1

24MHZ_10PF_8Y24000011

GND1

3

GND2

4

2

3

1

CC7

12P_0402_50V8-J

2

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

BDW_CLOCK/PM

BDW_CLOCK/PM

BDW_CLOCK/PM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

8 81

8 81

8 81

of

1.0

1.0

1.0

5

4

3

2

1

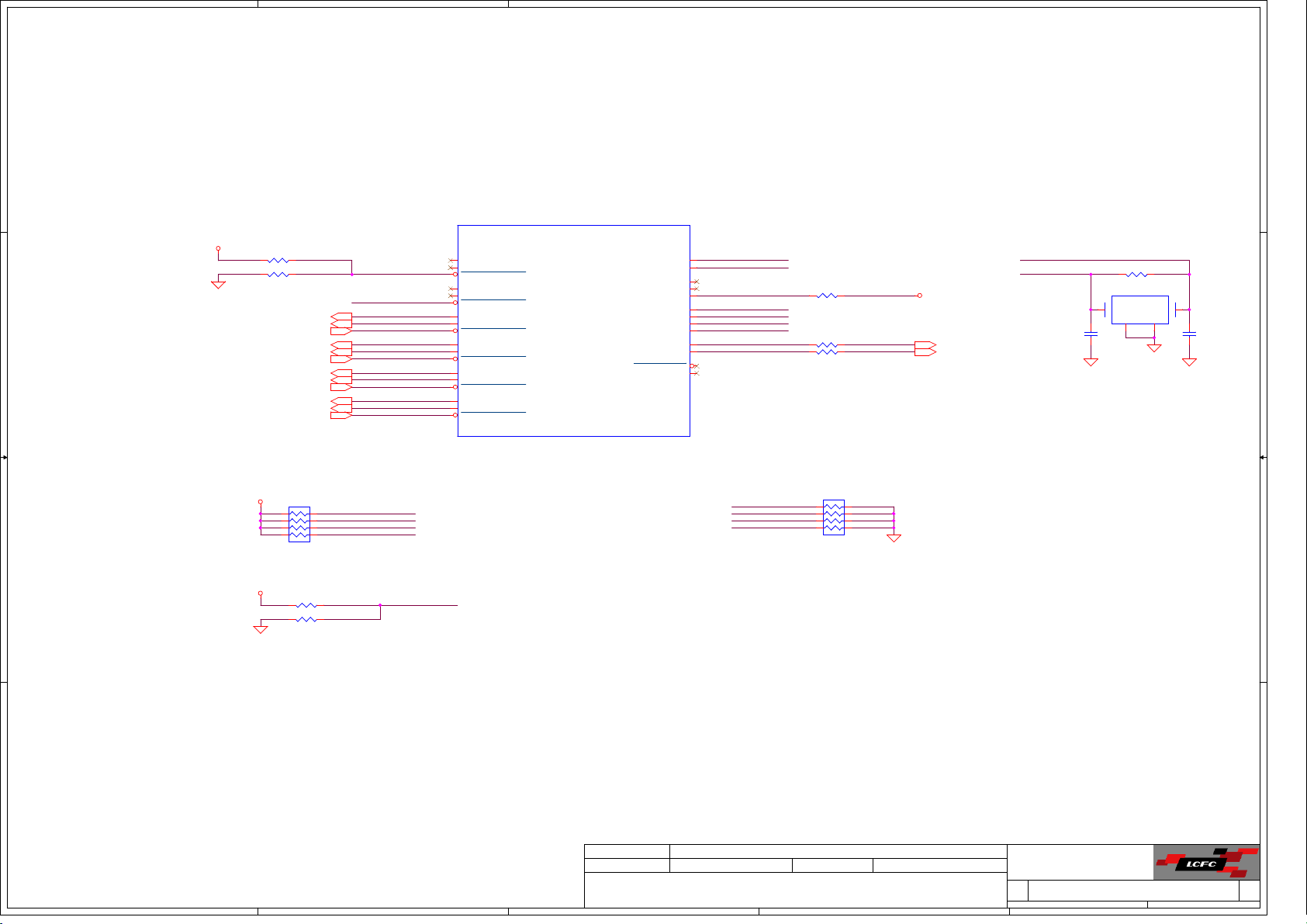

D D

RPC23

8

1

SPI_IO3_8MB SPI_IO3

SPI_CLK_8MB

SPI_SI_8MB

SPI_IO2_8MB

SPI_IO3_4MB SPI_IO3

SPI_CLK_4MB

SPI_SI_4MB

SPI_IO2_4MB

7

2

6

3

5

4

33_0804_8P4R_5%

SD30000370T

RPC24

8

1

7

2

6

3

5

4

33_0804_8P4R_5%

SD30000370T

VPRO@

SPI_CLK

SPI_SI

SPI_IO2

SPI_CLK

SPI_SI

SPI_IO2

+3V_SPI

SPI_SO_8MB

SPI_SO_4MB

LPC_AD[3:0]<56,62>

LPC_FRAME#<56,62>

1 2

RC100 33_0402_5%

RC101 33_0402_5%

RC117 1K_0402_5%

RC118 1K_0402_5%

1

1

1

VPRO@

2

2

2

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

SPI_CLK

SPI_CS0#_8MB

SPI_CS1#_4MB

SPI_SI

SPI_SO

SPI_IO2

SPI_IO3

UC1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

Broadwell-ULT_CL8064701614813_QFSY

HSW_ULT_DDR3L

LPC

SMBUS

SML1ALERT/PCHHOT/GPIO73

C-LINKSPI

7 OF 19

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

PCH_GPIO11

PCH_SMB_CLK

PCH_SMB_DATA

PCH_GPIO60

PCH_SML0_CLK

PCH_SML0_DAT

PCH_GPIO73

PCH_SML1CLK

PCH_SML1DATA

CL_CLK_WLAN

CL_DATA_WLAN

CL_RST_WLAN#

PCH_SML0_CLK <47>

PCH_SML0_DAT <47>

CL_CLK_WLAN <52>

CL_DATA_WLAN <52>

CL_RST_WLAN# <52>

PCH_SML0_CLK

PCH_SML0_DAT

PCH_SMB_CLK

PCH_SMB_DATA

PCH_SML1CLK

PCH_SML1DATA

PCH_GPIO11

PCH_GPIO60

PCH_GPIO73

1 2

RC92 499_0402_1%

1 2

RC93 499_0402_1%

RPC14

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

RPC15

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

SD300002P0T

+3V_PCH

+3V_PCH

Near UC4M1 and UC8M1

C C

Security ROM

USROM1

1

NC_1

2

NC_2

PLTRST#_NEAR<10,32,47>

PLTRST#_NEAR

3

PROT#

4

GND

PCA24S08AD_SO8

SA00004MK00/SA00004ML00

VCC

SCL

SDA

WP

8

7

6

PM_SMB_CLK

5

PM_SMB_DAT

M3 Support + Intel LAN PHY / Wireless LAN Solution

B B

+3VS

RC112 0_0402_5%

+3VM

SPI_CS0#_8MB

SPI_SO_8MB

SPI_IO2_8MB

1 2

1

2

3

4

UC8M1

CS#

VCC

HOLD#

DO

WP#

CLK

GND

W25Q64FVSSIQ_SO8

8

7

6

5

DI

2

1

RC110 0_0402_5%@

1

FSCE#<62>

SPI_FMOSI#<62>

SPI_FMISO<62>

A A

SPI_FSCK<62>

RE19 0_0402_5%

1 2

RE21 0_0402_5%

1 2

RE22 0_0402_5%

1 2

RE24 0_0402_5%

+3V_SPI

0.085 A

+3V_SPI

SPI_IO3_8MB

SPI_CLK_8MB

SPI_SI_8MB

2

+3V_SPI

+3V_SPI

1

CC25

0.1U_0402_10V7-K

2

SPI_CS0#_8MB

SPI_SI_8MB

SPI_SO_8MB

SPI_CLK_8MB

+3VS

1

CC22

0.1U_0402_10V6-K

2

SPI_CS1#_4MB

SPI_SO_4MB

SPI_IO2_4MB

UC4M1

1

CS#

2

HOLD#

DO

3

WP#

4

GND

W25Q32FVSSIQ_SO8

VPRO@

VCC

SM Bus

+3VS

PCH_SMB_CLK

PCH_SMB_DATA

8

+3V_SPI

7

SPI_IO3_4MB

6

SPI_CLK_4MB

CLK

5

SPI_SI_4MB

DI

+3V_SPI

1

CC26

VPRO@

0.1U_0402_10V7-K

2

PCH_SML1CLK EC_SMB_CK3

PCH_SML1DATA

6 1

D

5

QC1A

G

2N7002KDWH_SOT363-6

3 4

S

D

QC1B

2N7002KDWH_SOT363-6

+3VS

6 1

5

G

3 4

S

D

QC2B

2N7002KDWH_SOT363-6

DIMM1, DIMM2,

WLAN(@), CP, Security ROM

Touch Panel

2

G

S

RC106 4.7K_0402_5%

RC107 4.7K_0402_5%

PM_SMB_CLK

PM_SMB_DAT

GPU, EC, Thermal Sensor

2N7002KDWH

2

G

Vth= min 1V, max 2.5V

ESD 2KV

S

D

QC2A

2N7002KDWH_SOT363-6

EC_SMB_DA3

1 2

+3VS

1 2

PM_SMB_CLK <18,19,49>

PM_SMB_DAT <18,19,49>

EC_SMB_CK3 <21,34,55,62>

EC_SMB_DA3 <21,34,55,62>

Close to SPI ROM (UC8M1).

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

BDW_LPC/SPI/SM BUS

BDW_LPC/SPI/SM BUS

BDW_LPC/SPI/SM BUS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

9 81

9 81

9 81

of

1.0

1.0

1.0

5

4

3

2

1

D D

UC1H

2

1

SUSACK#<62>

PCH_SYSPWROK<62>

PCH_PWROK<62>

PCH_APWROK<78>

PLTRST#<20>

EC_RSMRST#<62>

SUSWARN#<62>

PBTN_OUT#<62>

AC_PRESENT<62>

C C

+3VALW +3V_PCH

B B

RPC18

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

SD300002P0T

RC37 0_0402_5%@

1 2

RC41 0_0402_5%

RC42 0_0402_5%

RC39 0_0402_5%@

AC_PRESENT

BATLOW#

PCIE_WAKE#

PCH_APWROK

1

VPRO@

1 2

2

SUSACK#_R

SYS_RESET#

PCH_SYSPWROK

PWROK

APWROK

PLTRST#

EC_RSMRST#

SUSWARN#_R

PBTN_OUT#

AC_PRESENT

BATLOW#

1

PCH_SLP_WLAN#

T17

+3VS

1

RC108 10K_0402_5%

1 2

RC51 8.2K_0402_5%

1

RC27 10K_0402_5%

1

RC28 100K_0402_1%@

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

Broadwell-ULT_CL8064701614813_QFSY

2

2

2

SYS_RESET#

CLKRUN#

EC_RSMRST#

EC_DPWROK_R

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

8 OF 19

1.05VS_PGOOD<14,62,70>

SUS_STAT/GPIO61

1 2

RC49 10K_0402_5%@

DSWVRMEN

DPWROK

WAKE

CLKRUN/GPIO32

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

DSWODVREN

AV5

EC_DPWROK_R

AJ5

PCIE_WAKE#

V5

CLKRUN#

AG4

SUS_STAT#

AE6

SUSCLK_32K

AP5

PM_SLP_S5#

AJ6

PM_SLP_S4#

AT4

PM_SLP_S3#

AL5

PM_SLP_A#

AP4

PCH_SLP_SUS#

AJ7

PCH_SLP_LAN#

1 2

RC125

@

10K_0402_5%

SUSWARN#_R

1

2

1

PCH_APWROK

CC40

@

.01U_0402_16V7-K

1 2

RC45 330K_0402_5%

CLKRUN# <56>

RC47 0_0402_5%@

SUSCLK_32K <52>

PM_SLP_S5# <62>

PM_SLP_S4# <62>

PM_SLP_S3# <62>

PM_SLP_A# <62>

PCH_SLP_SUS# <62>

T18

PLTRST#

100K_0402_5%

1

RC26

2

1

2

3

12

+RTCVCC

UC3

NC

IN_A

GND

TC7SG17FE_SON5

VCC

OUT_Y

LPC_PD# <56>

+3VALW

5

1

4

RC48 33_0402_5%

1 2

RC50 33_0402_5%

2

RC43 0_0402_5%

RC52 0_0402_5%@

RC33 100K_0402_5%@

1

CC8

@

1U_0402_10V6-K

2

2

1

2

1

1 2

1

CC9

100P_0402_50V8-J

2

1

CC82

100P_0402_50V8-J

2

EC_RSMRST#

EC_DPWROK <62>

+3VALW

PLTRST#_NEAR <32,47,9>

PLTRST#_FAR <52,56,62>

RC109

2

SUSWARN#_R

A A

APWROK

1

0_0402_5%

RC111

1 2

0_0402_5%

SUSACK#_R

PWROK

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

Title

Title

BDW_SYS PM

BDW_SYS PM

BDW_SYS PM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

10 81

10 81

10 81

1.0

1.0

1.0

5

D D

4

3

2

1

eDP SIDEBAND

PCIE

HSW_ULT_DDR3L

9 OF 19

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

PCH_MUX_CLK

PCH_MUX_DAT

PCH_VGA_CLK

PCH_VGA_DAT

PCH_MUX_AUX#

PCH_VGA_AUX#

PCH_MUX_AUX

PCH_VGA_AUX

PCH_MUX_HPD

PCH_VGA_HPD

CPU_EDP_HPD

PCH_MUX_CLK <42>

PCH_MUX_DAT <42>

PCH_MUX_AUX# <42>

PCH_VGA_AUX# <43>

PCH_MUX_AUX <42>

PCH_VGA_AUX <43>

PCH_MUX_HPD <42>

PCH_VGA_HPD <43>

CPU_EDP_HPD <38>

After testing, check if can un-stuff.

1.

籔籔籔籔

VENDOR

絋絋絋絋絋絋絋絋

PU

Τmeet SPEC value.

2. Vender fine tune recommend value.(Pass

Through Mode)

3. Vendor recommend use PU 4.7K ohm. (10/1)

Intel Spec is PU 2.2K ohm

PCH_MUX_CLK

PCH_MUX_DAT

PCH_VGA_CLK

PCH_VGA_DAT

PCH_MUX_HPD

PCH_VGA_HPD

CPU_EDP_HPD

ENBKL

, 絋絋絋絋絋絋絋絋

1 2

RC115 4.7K_0402_5%

1 2

RC116 4.7K_0402_5%

1

RC31 2.2K_0402_5%

1

RC40 2.2K_0402_5%

1

RC157 100K_0402_5%@

1

RC158 100K_0402_5%

1 2

RC159 100K_0402_5%

1 2

RC156 100K_0402_5%

2

2

2

2

Vih anf Vil

+3VS

UC1I

PCH_EDP_PWM<38>

ENBKL<62>

PCH_ENVDD<38>

C C

+3VS

1

2

3

4

B B

1

2

3

4

1 2

RC85 10K_0402_5%

RPC16

8

VGA_ON

7

DGPU_HOLD_RST#

6

BT_ON

5

CP_BYPASS

10K_0804_8P4R_5%

RPC17

8

PCH_TSOFF#

7

F4_LED#

6

F1_LED#

5

FN_LED#

10K_0804_8P4R_5%

DGPU_PWROK

UMA@

DGPU_PWROK<29,76>

VGA_ON<20,29,72,76,77>

DGPU_HOLD_RST#<20>

BT_ON<52>

PCH_TSOFF#<51>

FN_LED#<51>

F4_LED#<51>

PLANARID3<12>

F1_LED#<51>

CP_BYPASS <12,49>

PCH_EDP_PWM

ENBKL

PCH_ENVDD

DGPU_PWROK

VGA_ON

DGPU_HOLD_RST#

BT_ON

PCH_TSOFF#

FN_LED#

F4_LED#

PLANARID3

F1_LED#

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

Broadwell-ULT_CL8064701614813_QFSY

*

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

2013/09/07

2013/09/07

2013/09/07

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/09/07

2014/09/07

2014/09/07

Title

BDW_eDP SBAND/DDPx

BDW_eDP SBAND/DDPx

BDW_eDP SBAND/DDPx

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, November 06, 2014

Thursday, November 06, 2014

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, November 06, 2014

AITE1_NM-A221

AITE1_NM-A221

AITE1_NM-A221

1

11 81

11 81

11 81

1.0

1.0

1.0

5

4

3

2

1

+1.05VS_VCCST

H_THERMTRIP# <21>

GPIO18 PLANARID2

(GPIO50)

HSW

UMA

BDW

OPT

12

12

10K_0402_5%

10K_0402_5%

RC67

RC68

BDW@

12

12

10K_0402_5%

10K_0402_5%

RC72

RC71

HSW@

@

RC75 1K_0402_5%

2

@

RC76 1K_0402_5%

RC77 1K_0402_5%

2

1

@

RC80 1K_0402_5%

2

RC82 1K_0402_5%

1

@

12

1

PLANARID3

(GPIO51)

NA

PU

12

10K_0402_5%

RC69

12

10K_0402_5%

RC73

@

12

+3VS

*

10K_0402_5%

10K_0402_5%

+3V_PCH

+3VS

+3VS

+3VS

12

RC70

15NM@

12

RC74

14NM@

GPIO

RPC8

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

RPC9

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

RPC10

18

27

36

45

10K_0804_8P4R_5%

RPC11

8

1

7

2

6

3

5

4

4.7K_0804_8P4R_5%

RPC12

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

HSW_ULT_DDR3L

10 OF 19

ODD_DA#

PCH_GPIO83

PCH_GPIO69

PCH_GPIO89

PCH_GPIO76

ODD_EN

PCH_GPIO6

WWAN_DISABLE#

FW_GPIO

PCH_GPIO70

PCH_GPIO90

PCH_CMOS_ON

PCH_GPIO1

PCH_GPIO2

PCH_GPIO3

PCH_GPIO0

PCH_GPIO64

PCH_GPIO65

PCH_GPIO67

PCH_GPIO85

CPU/

MISC

SERIAL IO

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD7

RSVD8

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

+3VS

RPC20

10K_0804_8P4R_5%

RPC21

10K_0804_8P4R_5%

1

RC83 10K_0402_5%

1 2

RC84 10K_0402_5%

Intel recommend OPI_RCOMP PD 50 ohm 1%

D60

THRMTRIP#

V4

KBRST#

T4

SERIRQ

AW15

AF20

OPI_RCOMP

AB21

R6

PCH_GPIO83

L6

PCH_GPIO84

N6

PCH_GPIO85

L8

PCH_GPIO86

R7

PCH_GPIO87

L5

PCH_GPIO88

N7

PCH_GPIO89

K2

PCH_GPIO90

J1

PCH_GPIO91

K3

CP_RESET#

J2

CP_BYPASS

G1

TP_REST

K4

PCH_GPIO0

G2

PCH_GPIO1

J3

PCH_GPIO2

J4

PCH_GPIO3

F2

WWAN_DET#

F3

WWAN_DISABLE#

G4

PCH_GPIO6

F1

FW_GPIO

E3

PCH_GPIO64

F4

PCH_GPIO65

D3

PCH_GPIO66

E4

PCH_GPIO67

C3

PCH_CMOS_ON

E2

PCH_GPIO69

18

PCH_GPIO91

27

PCH_GPIO84

36

PCH_GPIO87

45

PCH_GPIO88

18

SERIRQ

27

KBRST#

36

WWAN_DET#

45

PCH_GPIO39

2

DEVSLP0

DEVSLP1

KBRST# <62>

SERIRQ <56,62>

1 2

RC55 49.9_0402_1%

CP_RESET# <49>

CP_BYPASS <11,49>

TP_REST <49>

WWAN_DET# <52>

WWAN_DISABLE# <52>

FW_GPIO <38>

PCH_CMOS_ON <38>

THRMTRIP#

Only for 15"

RC54

0_0402_5%

@

2

1

RC53 1K_0402_1%

1 2

Planar ID

PLANARID0

(GPIO48)

0

14"

1

15"

*

PLANARID0

PLANARID1

PLANARID2

PLANARID3<11>

GPIO15, Internal PD

1: INTEL ME TLS W Confidentiality

0: INTEL ME TLS WO Confidentiality

PCH_GPIO15

GPIO66, Internal 20K PD

1: Top-Block Swap Override EN

*0: Disable

PCH_GPIO66

GPIO81, No Reboot, Internal PD

1: Enabled No Reboot Mode

*0: Disable No Reboot Mode

PCH_BEEP

GPIO86, Internal PD

1: Enabled

*0: SPI ROM

PCH_GPIO86

UC1J

D D

Only for 15"

EC_WAKE#

RC167 0_0402_5%@

PCH_LAN_WAKE#<47>

EC_WAKE#<62>

C C

RC168 0_0402_5%@

RC169 0_0402_5%

1 2

1

1 2

ONEDOCK_DET#<34>

RF_OFF#<52>

LANPHYPC<47>

ODD_EN<37>

ODD_DA#<37>

2

DEVSLP0<37>

DEVSLP1<52>

PCH_BEEP<36>

PCH_GPIO76

RF_OFF#

LANPHYPC

PCH_GPIO15

ODD_EN

ODD_DA#

PCH_GPIO24

DS_WAKE#

PCH_GPIO28

PCH_GPIO26

PCH_GPIO56

PCH_GPIO57

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

PCH_GPIO47

PLANARID0

PLANARID1

PLANARID2

EC_WAKE_R#

PCH_GPIO14

PCH_GPIO25

PCH_GPIO45

PCH_GPIO46

ONEDOCK_DET#

PCH_GPIO10

DEVSLP0

PCH_GPIO70

DEVSLP1

PCH_GPIO39

PCH_BEEP

SATA Port

DEVSLP0

DEVSLP1

+3V_PCH+3VALW

2

1

RC90 10K_0402_5%

B B

A A

RC91 10K_0402_5%

2

1

DS_WAKE#

SATA Port 0

SATA Port 1

RPC5

18

27

36

45

10K_0804_8P4R_5%

RPC6

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

RPC7

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

RPC19

8

1

7

2

6

3

5

4

10K_0804_8P4R_5%

PCH_GPIO59PCH_GPIO25

PCH_GPIO56

PCH_GPIO47

PCH_GPIO44

PCH_GPIO58

PCH_GPIO57

PCH_GPIO10

ONEDOCK_DET#

RF_OFF#

PCH_GPIO46

EC_WAKE_R#

PCH_GPIO26

PCH_GPIO24

PCH_GPIO28

PCH_GPIO14

PCH_GPIO45

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12