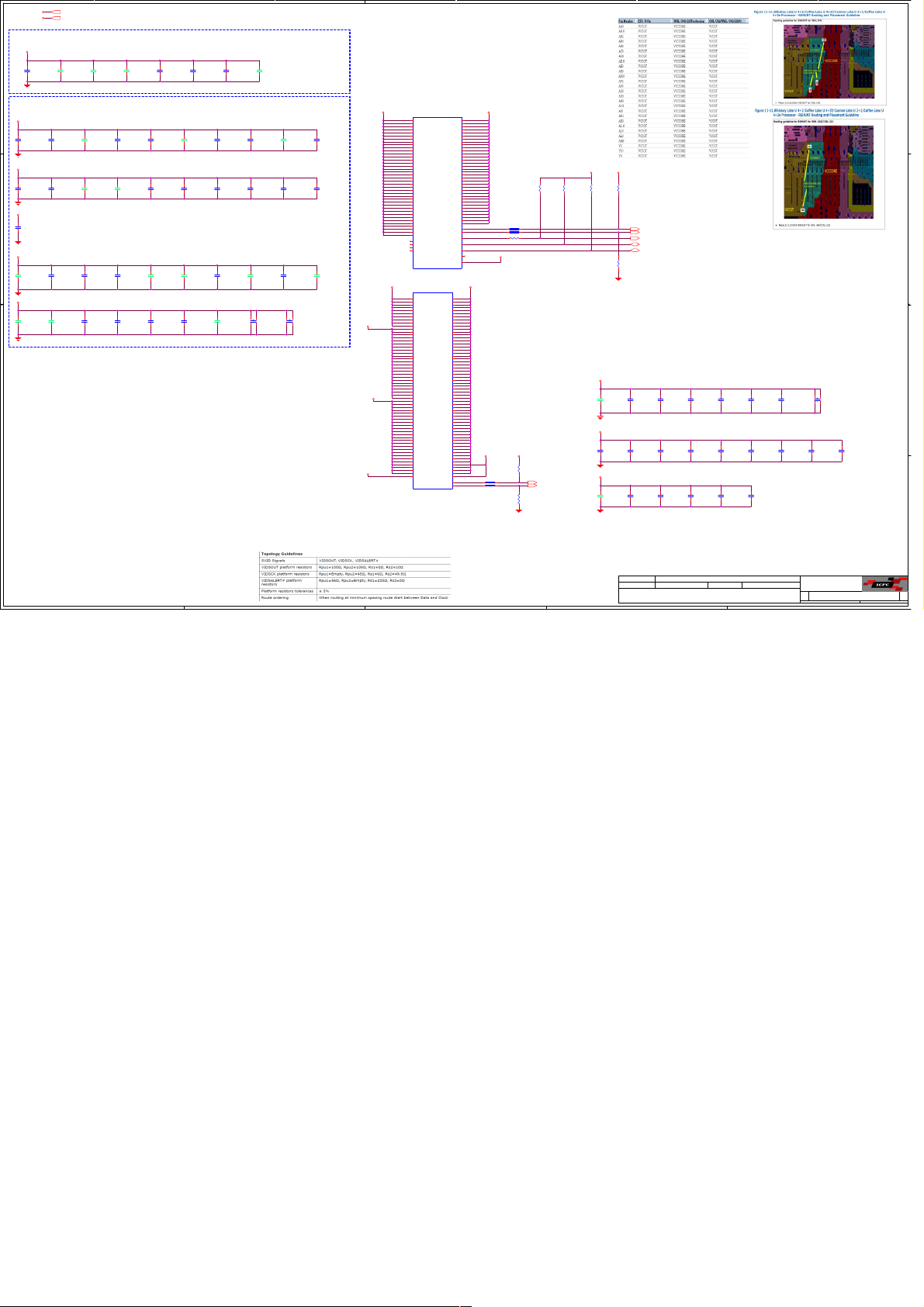

Lenovo E15 THINKPAD Schematic

A

VInafix.com

B

C

D

E

1 1

LCFC Confidential

Skids/Mudflap

2 2

NM-C421 Rev1.0 Schematic

3 3

E14/R14/E15/R15

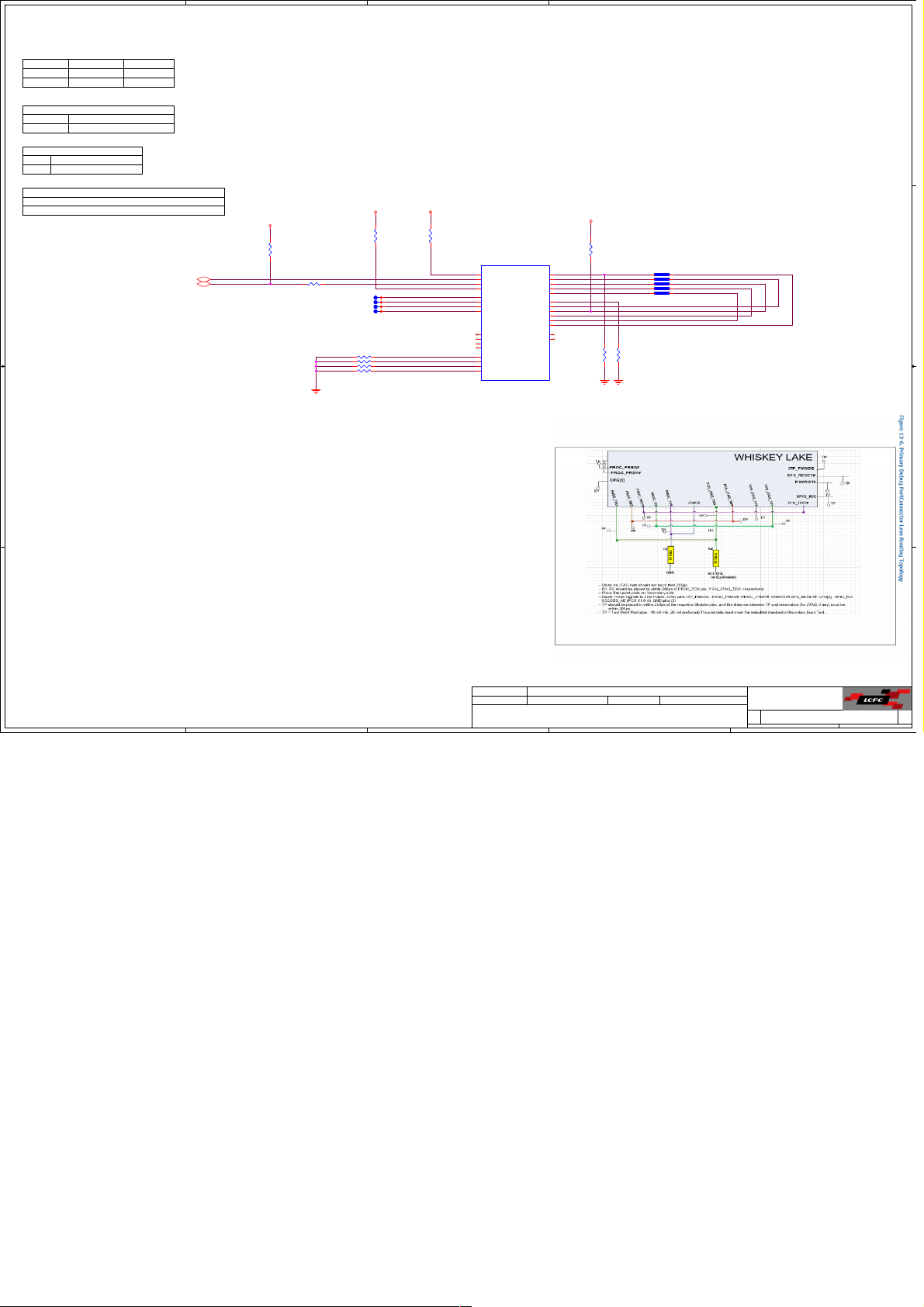

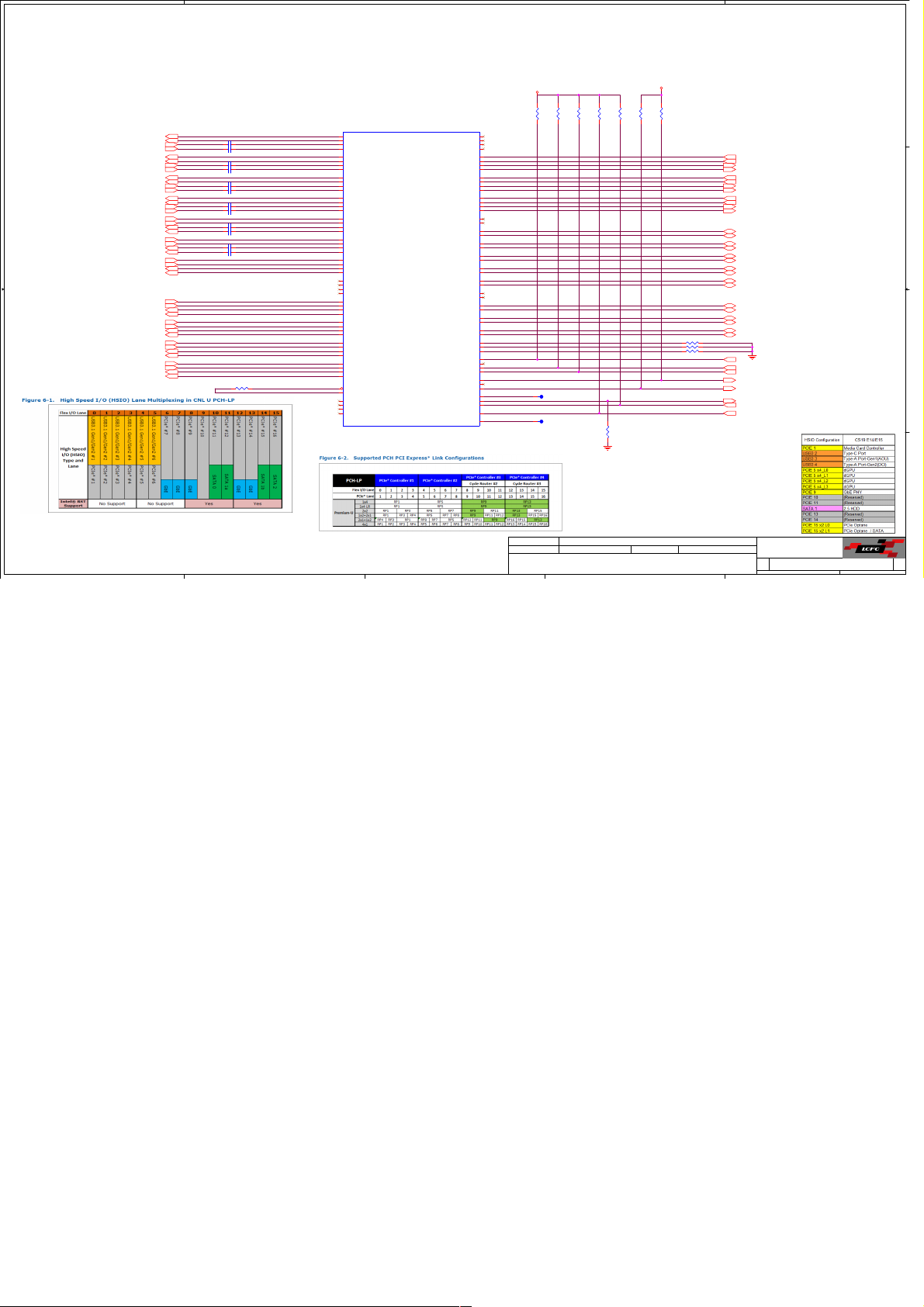

Intel Comet Processor with DDR4 + PCH

AMD R19M-P25 50/70

AMD

2019-07-05 Rev1.0

R19M-M25-50

4 4

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAYBE USED BY OR D ISCLOSED TOANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAYBE USED BY OR D ISCLOSED TOANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

MAYBE USED BY OR D ISCLOSED TOANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2016/01/12

2016/01/12

2016/01/12

D

Title

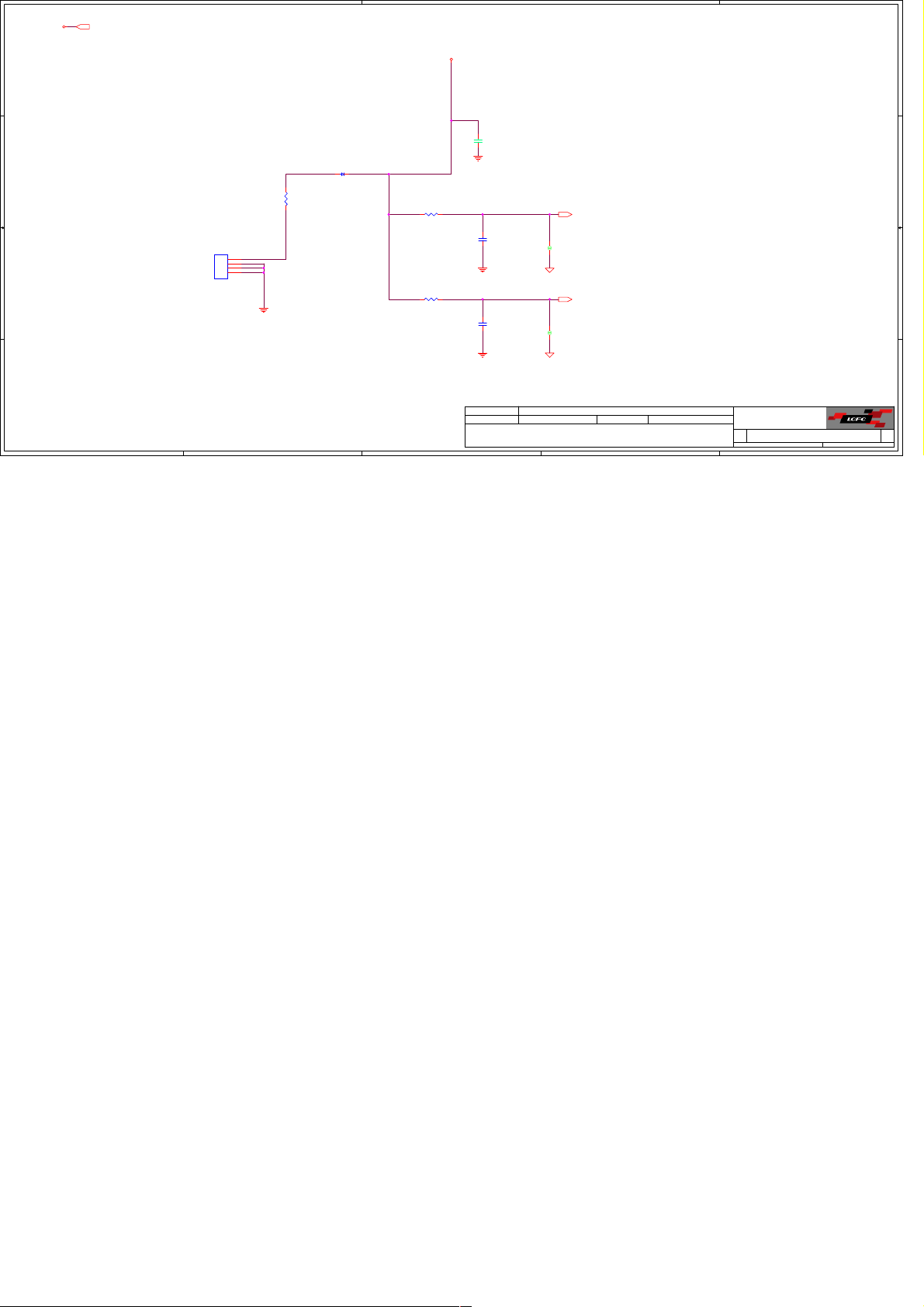

COVER PAGE

COVER PAGE

COVER PAGE

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number R

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

1 128

1 128

1 128

E

ev

0.1

0.1

0.1

A

VInafix.com

B

C

D

E

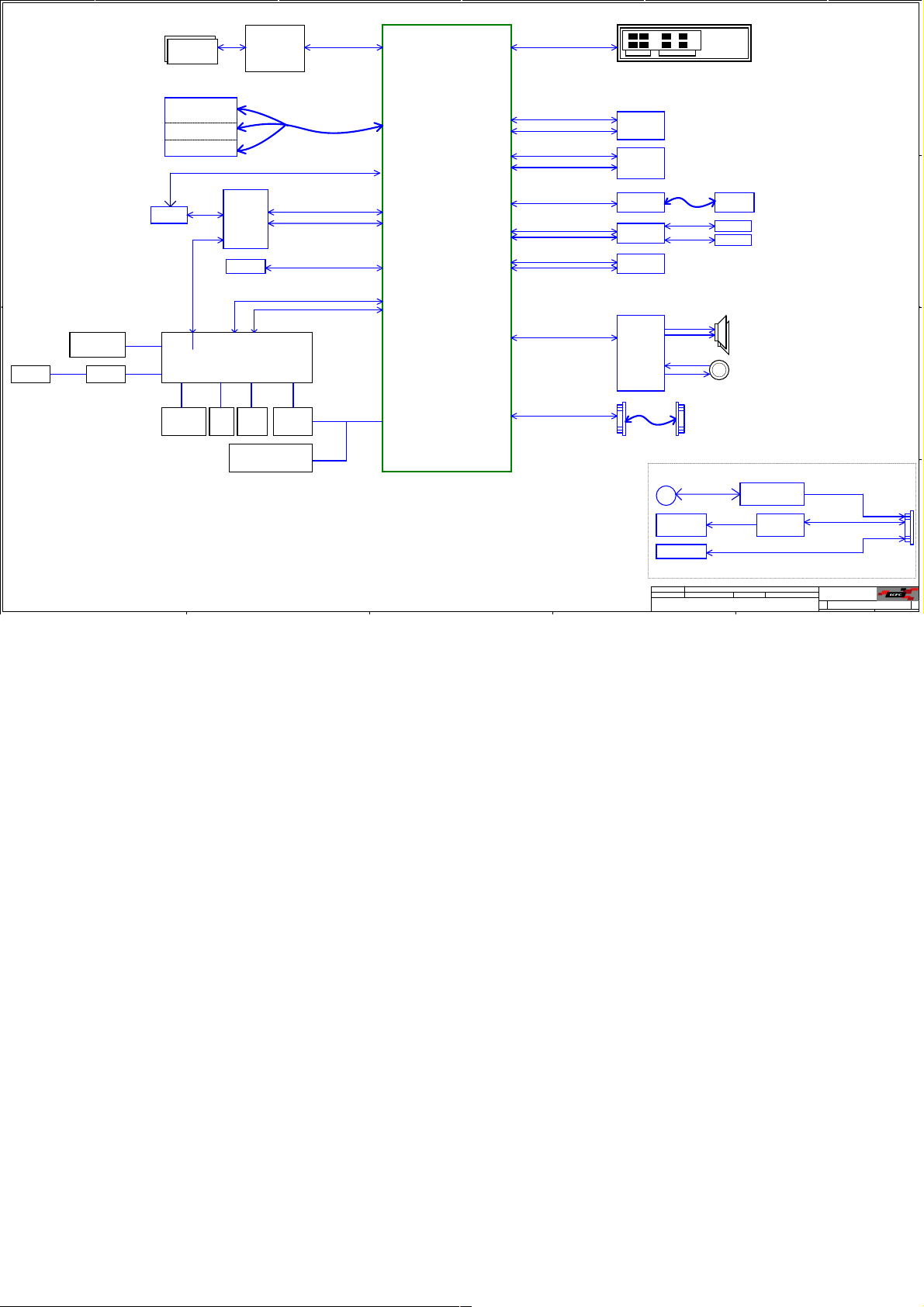

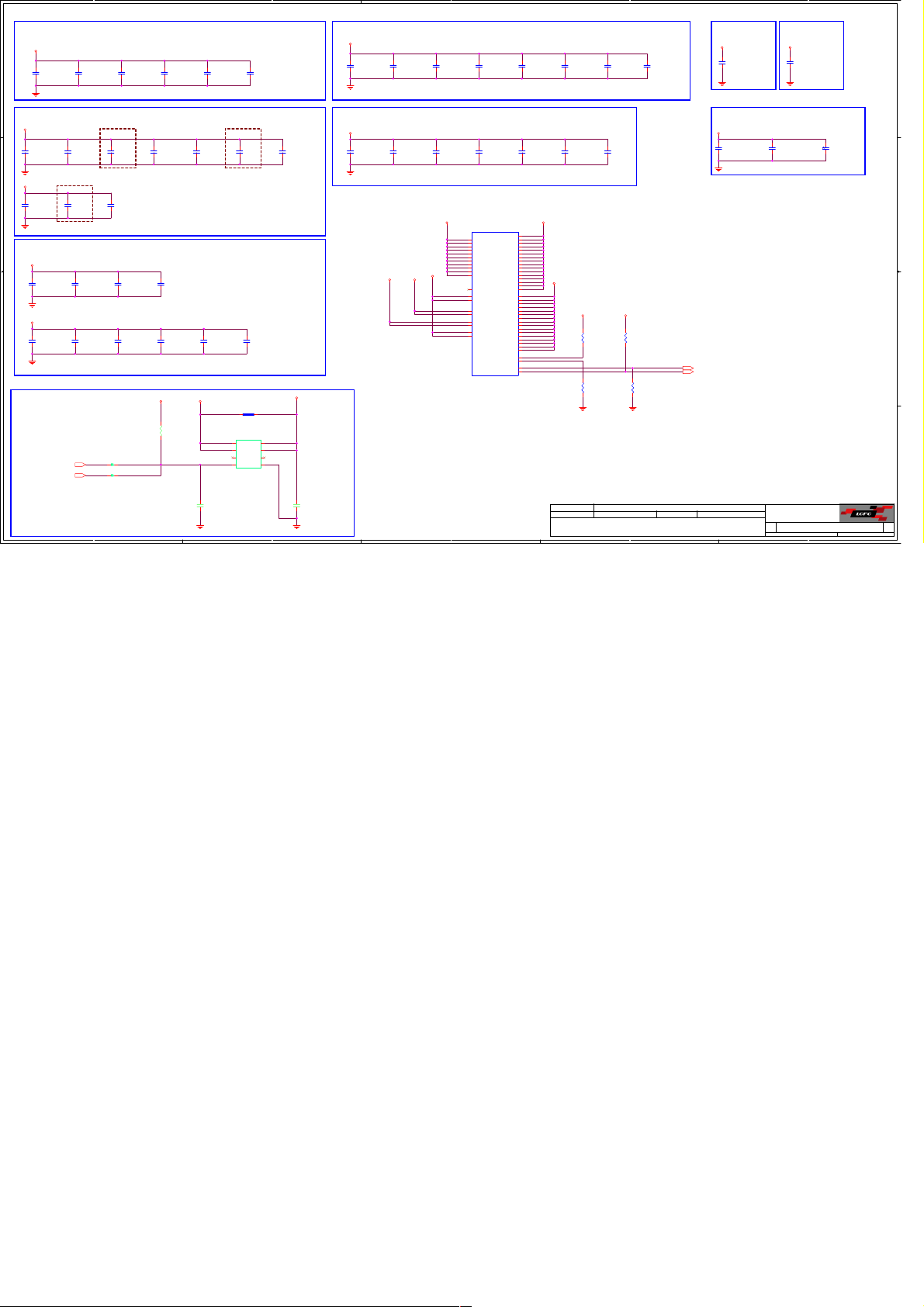

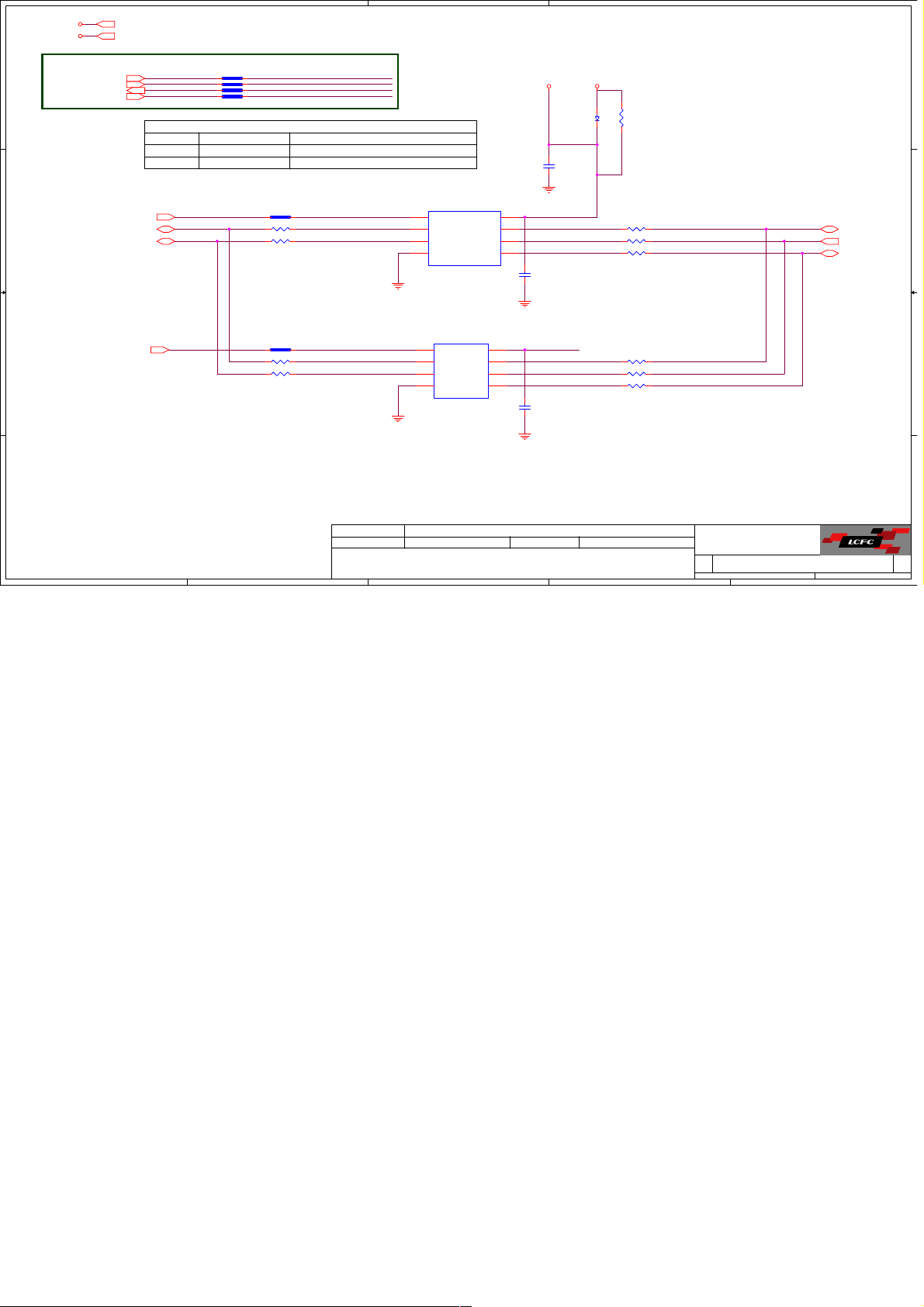

HDD FFC cable

Type M CONN

Type M CONN

(2CH 4W/4ohm)

MIC IN/GND

HP R/L

DDR4

2400 Mhz

SODIMM A

(PORT 5)

Page 33~34

HDD 2.5"HDD CONN

PCIE SSD

SATA SSD

2CH Speaker

Page 82

Univeral Jack

Page 79

power botton&Finger Print

MDI

USB 2.0 x 1

JYT

JYAA139A

Giga LAN

Realtek

R8111GUS

USB 2.0 x 1

PCIe x 1

(PCIE Lane 9)

IO_Board

(PORT 9)

GPU

DDR5

VRAM

GDDR5

Page 45

(PORT 6)

(PORT 8)

SMBus

PS2

DIS only (SWG)

15" LCD FHD

Touch Panel (Optional)

Camera(Digital MIC)

LENOVO LED Logo

USB

JUSB3(Type-C)

Page 63

SMBus

I2C

G-sensor

Fintek

LIS3DSHTR

Page 51

Page 51

Embedded Controller

ITE

IT8227E-256

FAN

1 1

2 2

Thermal Sensor

Fintek

F75303M

Page 92

Click PadTrack Point

3 3

Page 89Page 89 Page 85

AMD

(R19M-P25-70)

(R18M-M2-60)

eDP x 2

USB 2.0 x 1

LED signal

Type-C PD

CONTROLLER

RTS5455

Page 59

HDMI Conn.

Page 54

Int. K/B Matrix SPI BUS

Flash ROM

Int. KB

16+8M

TPM 2.0

M:ST ST33HTPH2E32AHC0

S:Nuvoton NPCT750LABYX

Page 37~44

PCIE x 4

(PCIE Lane 5~8)

eDP coxail Y cable(40 Pin)

USB2.0

(PORT 2)

USB3.0

DDI1

DDI2

LPC BUS

eSPI BUS(RES ERVED)

Mirror function

SPI BUS

Page 21Page 88Page 90Page 91

Page 98

(PORT 2)

Intel CPU

Comet Lake U

15W (UM A& DIS)

Comet Lake PCH-LP

10 USB 2.0/1.1 Ports

6 USB 3.0 Ports

3 SATA Ports

16 PCIE Ports

HD Audio

LPC I/F

ACPI 3.0

NON interleave

USB 2.0 x 1

U

SB 3.0 x 1

USB 2.0 x 1

USB 3.0 x 1

SATA x 1

PCIE x 4

SATA x 1

PCIE x 1

USB 2.0 x 1

CNVi(TBD)

HDA

DDR4 400MHz

(PORT 4)

(PORT 4)

(PORT 3)

(PORT 3)

(PCIE Lane 11)

(

PCIELane13~16)

(TBD)

(PCIE Lane 10)

(PORT 5)

Left-Front

JUSB2

USB 2.0 Port 1

USB 3.0 Port 2

Page 69

Left-Back

JUSB3(AOU)

USB 2.0 Port 1

USB 3.0 Port 2

Page 69

Page 96

M2 Slot for 2280

(

Type M CONN)

Page 64

NGFF Card WLAN

(Type E)

Page 66

HDA Codec

Synaptics

CX11880- 11Z

Page 78

40 PIN WTB Cable

MB_40 Pin conn IO_40 Pin conn

Page 73

TOUCH FPR

RJ45 Conn.

4 4

Page ??

JUSB4 (USB2.0)

Page ??

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2016/01/12

2016/01/12

2016/01/12

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

2 128

2 128

2 128

0.1

0.1

0.1

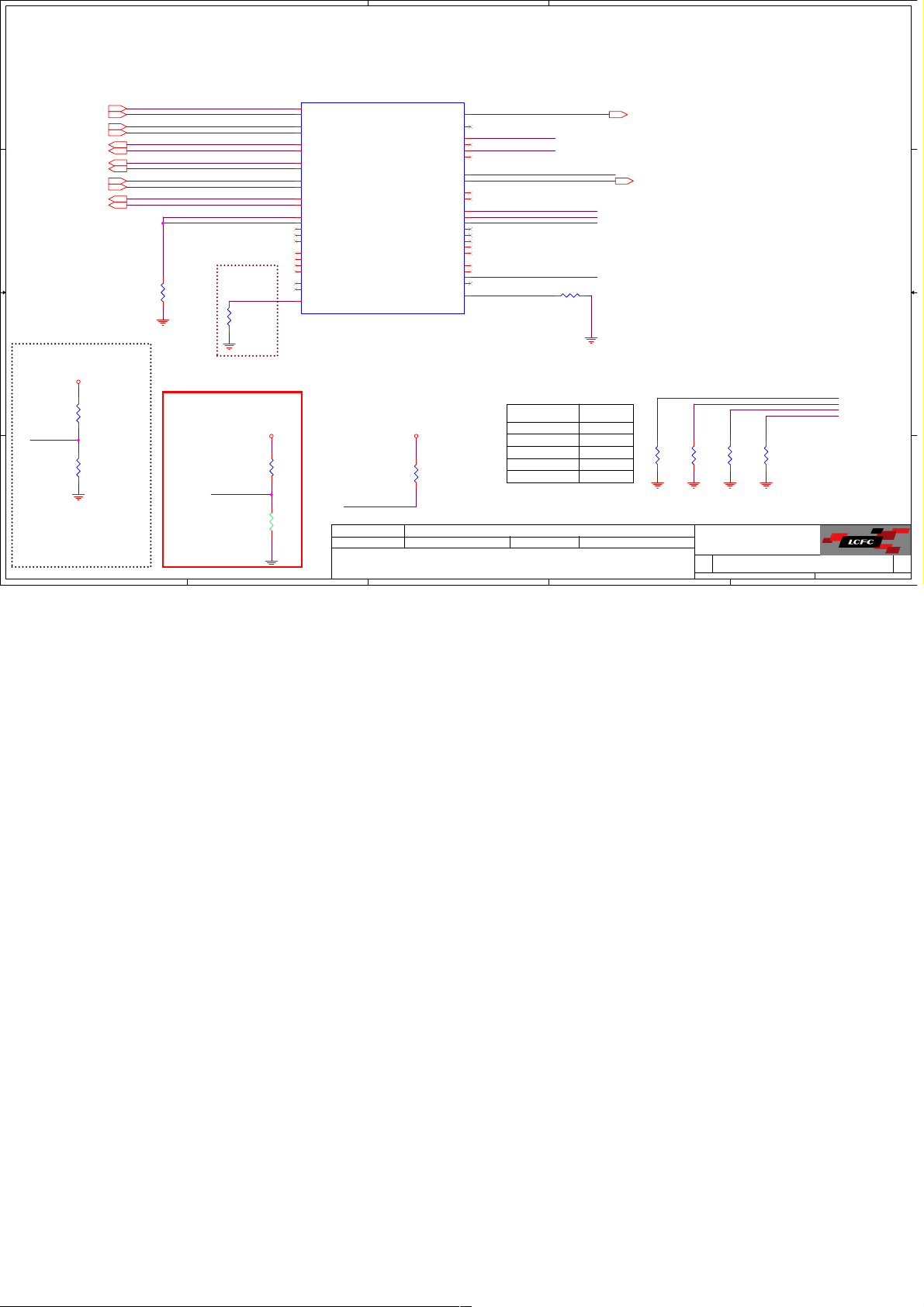

5

VInafix.com

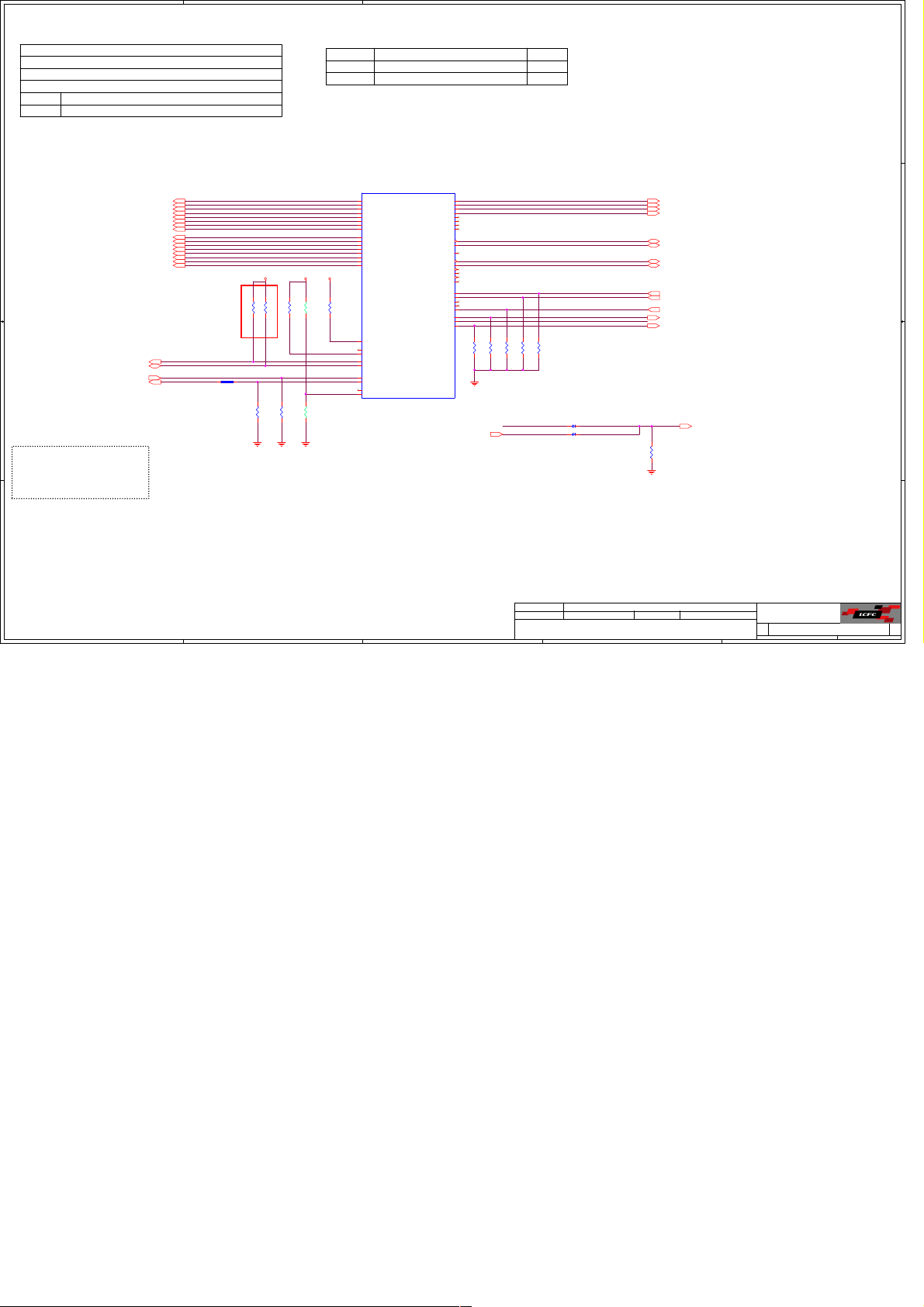

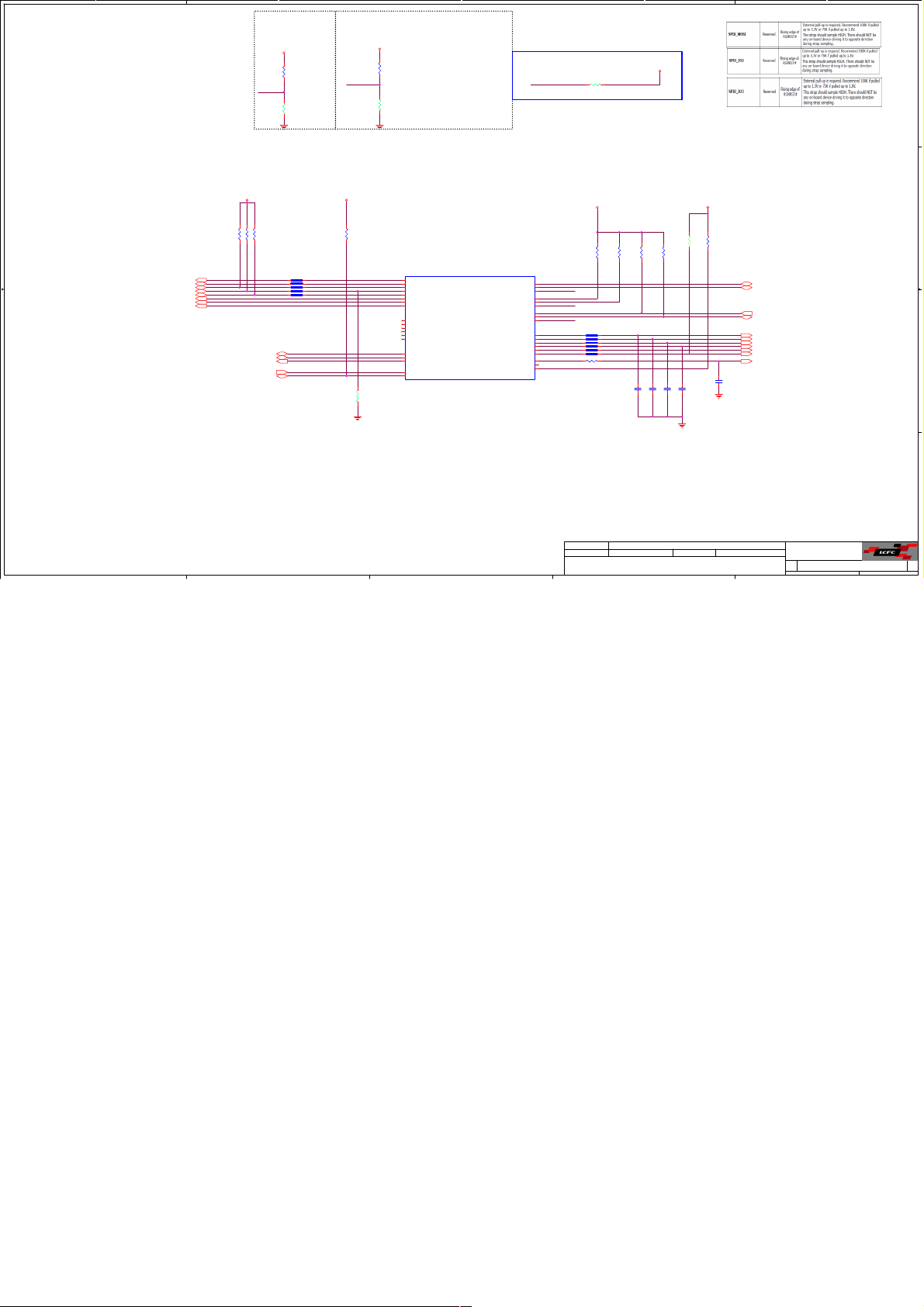

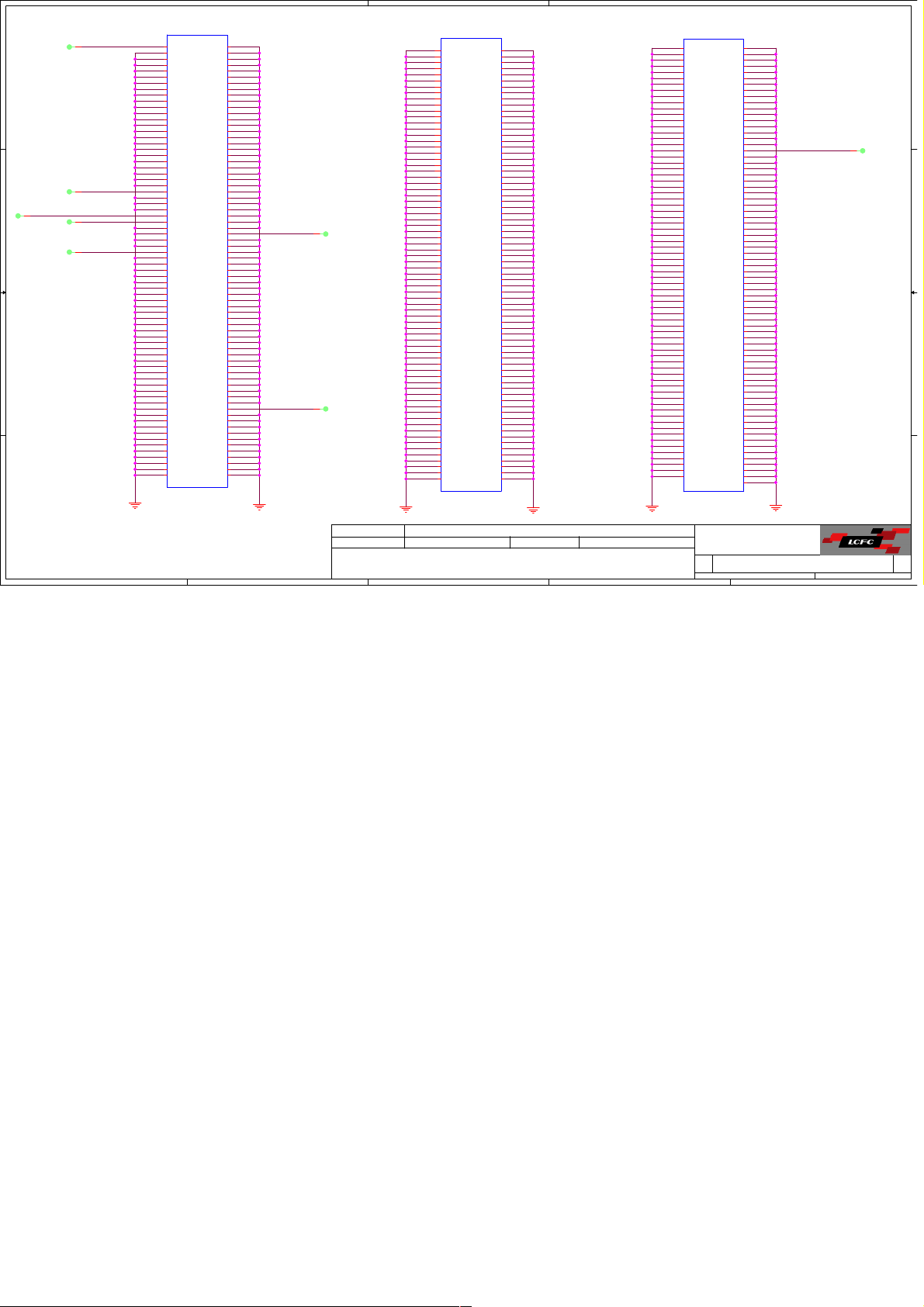

TABLE : Functional Strap

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD (DDP1 I2C / TBT LSX #0 PINS VCCIO CONFIGURATION)

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD (DDP2 I2C / TBT LSX #1 PINS VCCIO CONFIGURATION)

GPP_D10/DDP3_CTRLDATA/TBT_LSX2_RXD (DDP3 I2C / TBT LSX #2 PINS VCCIO CONFIGURATION)

D D

GPP_D12/DDP4_CTRLDATA/TBT_LSX3_RXD (DDP4 I2C / TBT LSX #3 PINS VCCIO CONFIGURATION)

HIGH

3.3V

1.8V

LOW

4

DP port

DDPB_CTRLDAT A

DDPC_CTRLDAT A

Pull up to 3.3 V with 2.2-k ohm ± 5% resistor

Pull up to 3.3 V with 2.2-k ohm ± 5% resistor

3

Enable Disable

no connect

no connect

2

1

DDIP1_0N

DDIP1_0N59

DDIP1_0P

DDIP1_0P59

DDIP1_1N

DDIP1_1N59

DDIP1_1P

HDMI

DDIP2_CTRLCLK54

DDIP2_CTRLDATA54

-GPU_RST37

GFX_PWR_EN50

DDIP1_1P59

DDIP1_2N

DDIP1_2N59

DDIP1_2P

DDIP1_2P59

DDIP1_3N

DDIP1_3N59

DDIP1_3P

DDIP1_3P59

DDIP2_2N

DDIP2_2N54

DDIP2_2P

DDIP2_2P54

DDIP2_1N

DDIP2_1N54

DDIP2_1P

DDIP2_1P54

DDIP2_0N

DDIP2_0N54

DDIP2_0P

DDIP2_0P54

DDIP2_3N

DDIP2_3N54

DDIP2_3P

DDIP2_3P54

Change to 2K for 15m test

DDIP2_CTRLCLK

DDIP2_CTRLDATA

-GPU_RST

GFX_PWR_EN

R0315 0_0201_SP

TX Net NAME:1R8VIDEO_AON_ON

VCC3B

VCC3_SUS

12

R03131/16W_2K_5%_0402

12

12

DIS@

12

12

R03111/20W_20K_5%_0201

R03011/20W_2.2K_5%_0201

R03141/16W_2K_5%_0402

@

1 2

GFX_PWR_EN_PCH

GPP_H17

12

12

R0309

DIS@

@

R0308

R0312

1/20W_1M_1%_0201

1/20W_1M_1%_0201

1/20W_20K_5%_0201

4

TYPE-C

C C

To VGA_CORE IC, RPC3.7

B B

eDP_RC OMP

Trace Width: 5 mils

Isolation Spacing: 25 mils

Resistor Value: 24.9 or 100 ohm 1%

Max Length: 600 mils

Pull-up to VCCIO through 24.9-ohm 1%resistor.

For CNL, it is 100 ohm 1%

Please refer to PDG Table 3-2.

Cited by 575412_WHL_U_PDG_Rev0.9

A A

5

AL5

AL6

AJ5

AJ6

AF6

AF5

AE5

AE6

AC4

AC3

AC1

AC2

AE4

AE3

AE1

AE2

VCCIO

12

R0307

1/20W_24.9_1%_0201

EDP_COMP

AM6

CC8

GPP_E19

CC9

CH4

CH3

CP4

CN4

CR26

CP26

UCPU1A

DDI1_TXN_0

DDI1_TXP_0

DDI1_TXN_1

DDI1_TXP_1

DDI1_TXN_2

DDI1_TXP_2

DDI1_TXN_3

DDI1_TXP_3

DDI2_TXN_0

DDI2_TXP_0

DDI2_TXN_1

DDI2_TXP_1

DDI2_TXN_2

DDI2_TXP_2

DDI2_TXN_3

DDI2_TXP_3

DISP_RCOMP

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

GPP_E19/DPPB_CTRLDATA

GPP_E20/DPPC_CTRLCLK

GPP_E21/DPPC_CTRLDATA

GPP_E22/DPPD_CTRLCLK

GPP_E23/DPPD_CTRLDATA

GPP_H16/DDPF_CTRLCLK

GPP_H17/DDPF_CTRLDATA

@

WHISKEYLAKE-U_BGA1528

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

1 of 20

12

12

2015/01/12

2015/01/12

2015/01/12

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_AUXN

EDP_AUXP

DDIP1_AUXN

DDIP1_AUXP

DDIP1_HPD

DDIP2_HPD

EDP_HPD

VGA_BLON

PANEL_POWER_ON_CPU

PANEL_BKLT_CTRL_CPU

1/20W_10K_5%_0201

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2

R0310

Deciphered Date

Deciphered Date

Deciphered Date

EDP_TXN0 51

EDP_TXP0 51

EDP_TXN1 51

EDP_TXP1 51

EDP_AUXN 51

EDP_AUXP 51

DDIP1_AUXN 59

DDIP1_AUXP 59

DDIP1_HPD 59

DDIP2_HPD 54

EDP_HPD 51

VGA_BLON 85

PANEL_BKLT_CTRL_CPU 51

1 2

PANEL_POWER_ON 51

2016/01/12

2016/01/12

2016/01/12

Title

Title

Title

CPU (1/16): DDI/TYPE-C

CPU (1/16): DDI/TYPE-C

CPU (1/16): DDI/TYPE-C

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

3 128

3 128

3 128

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

@

LCD_SELF_TEST_ON51,85

3

@

R0303

R0304

R0302

R0306

R0305

1 2

1 2

1 2

1 2

1 2

1/20W_100K_5%_0201

1/20W_100K_5%_0201

1/20W_100K_5%_0201

1/20W_100K_5%_0201

1/20W_100K_5%_0201

PANEL_POWER_ON_CPU PANEL_POWER_ON

LCD_SELF_TEST_ON

D0301 RB520CM-30T2R_VMN2M2

D0302 RB520CM-30T2R_VMN2M2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

0.1

0.1

0.1

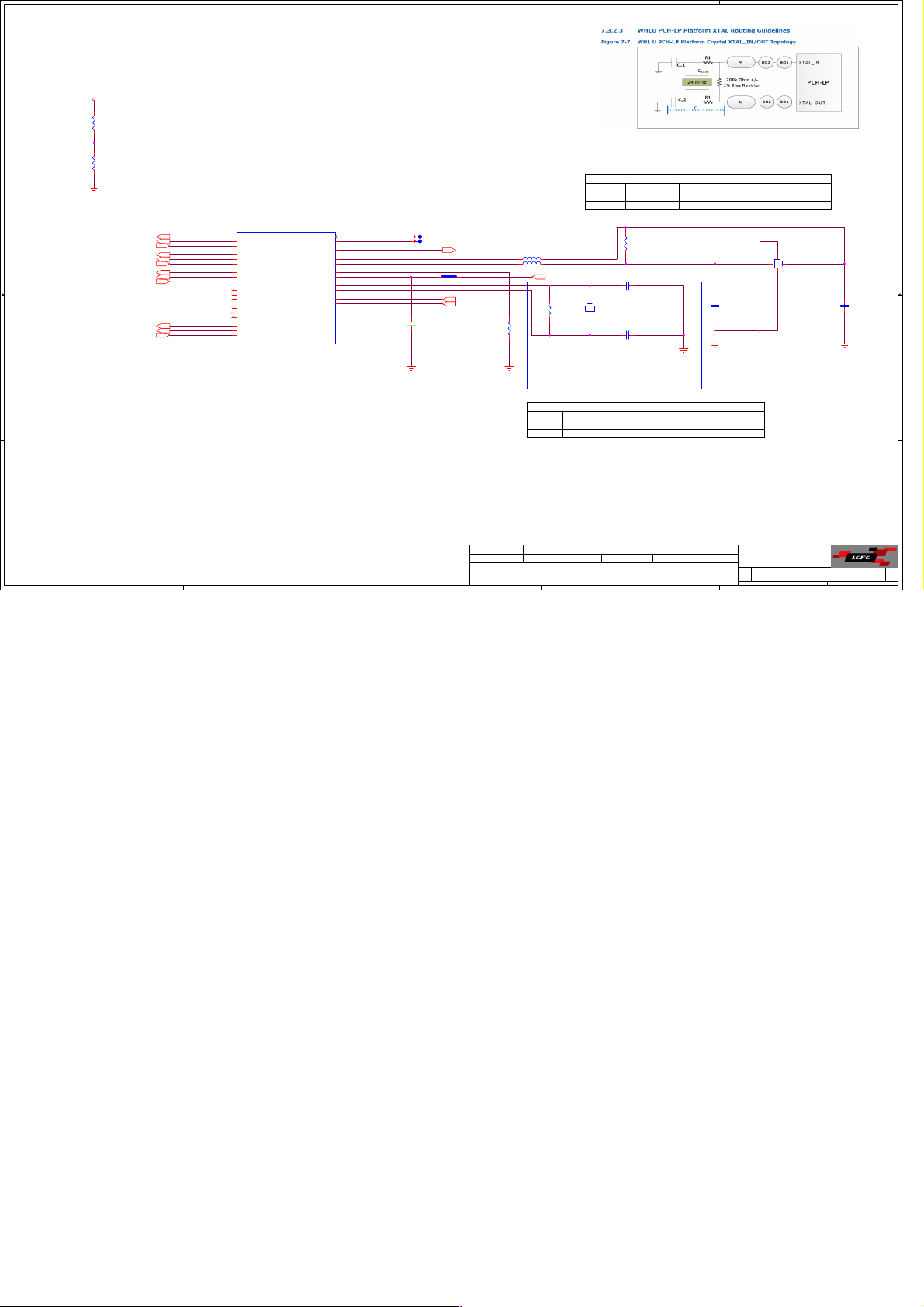

5

VInafix.com

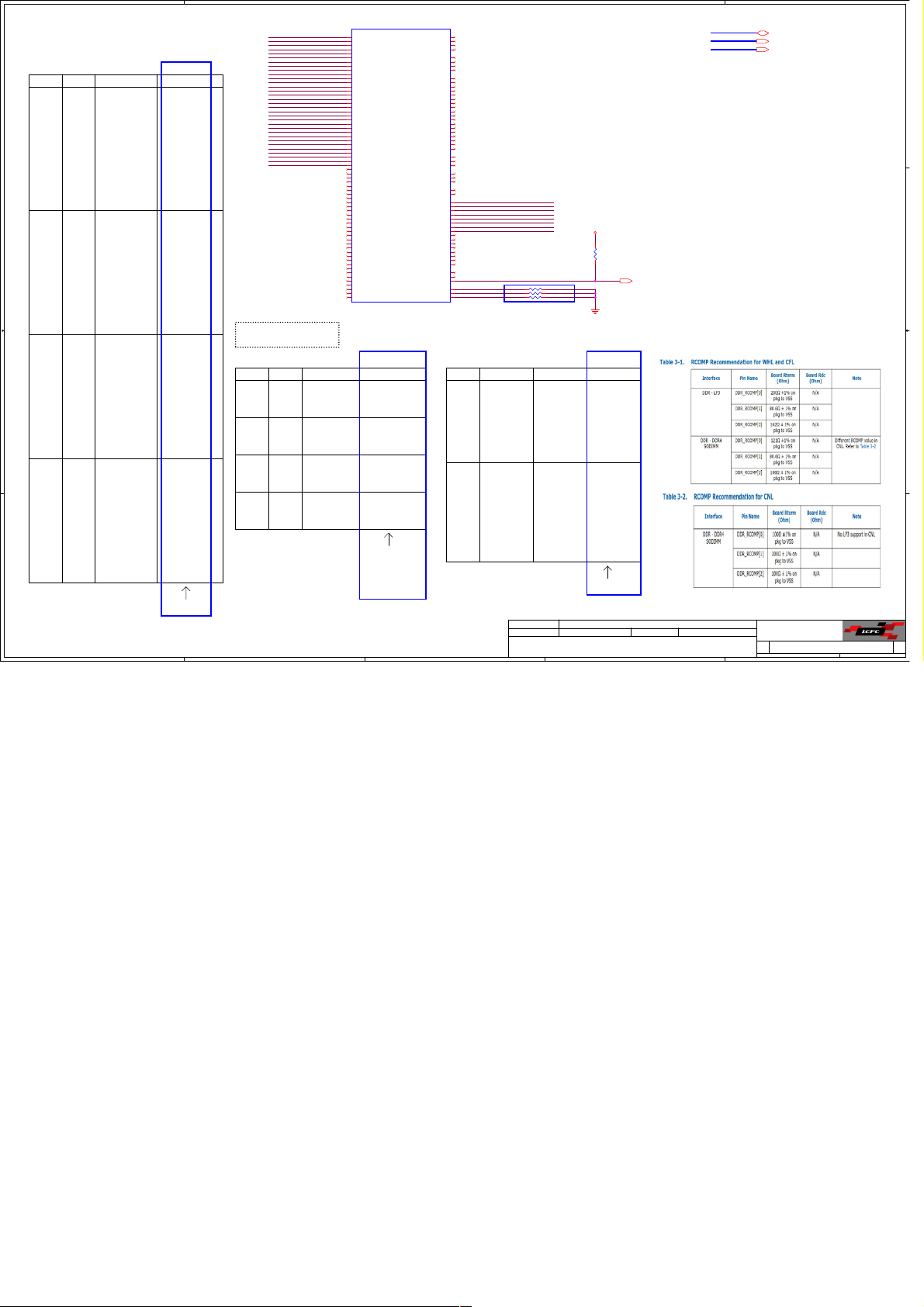

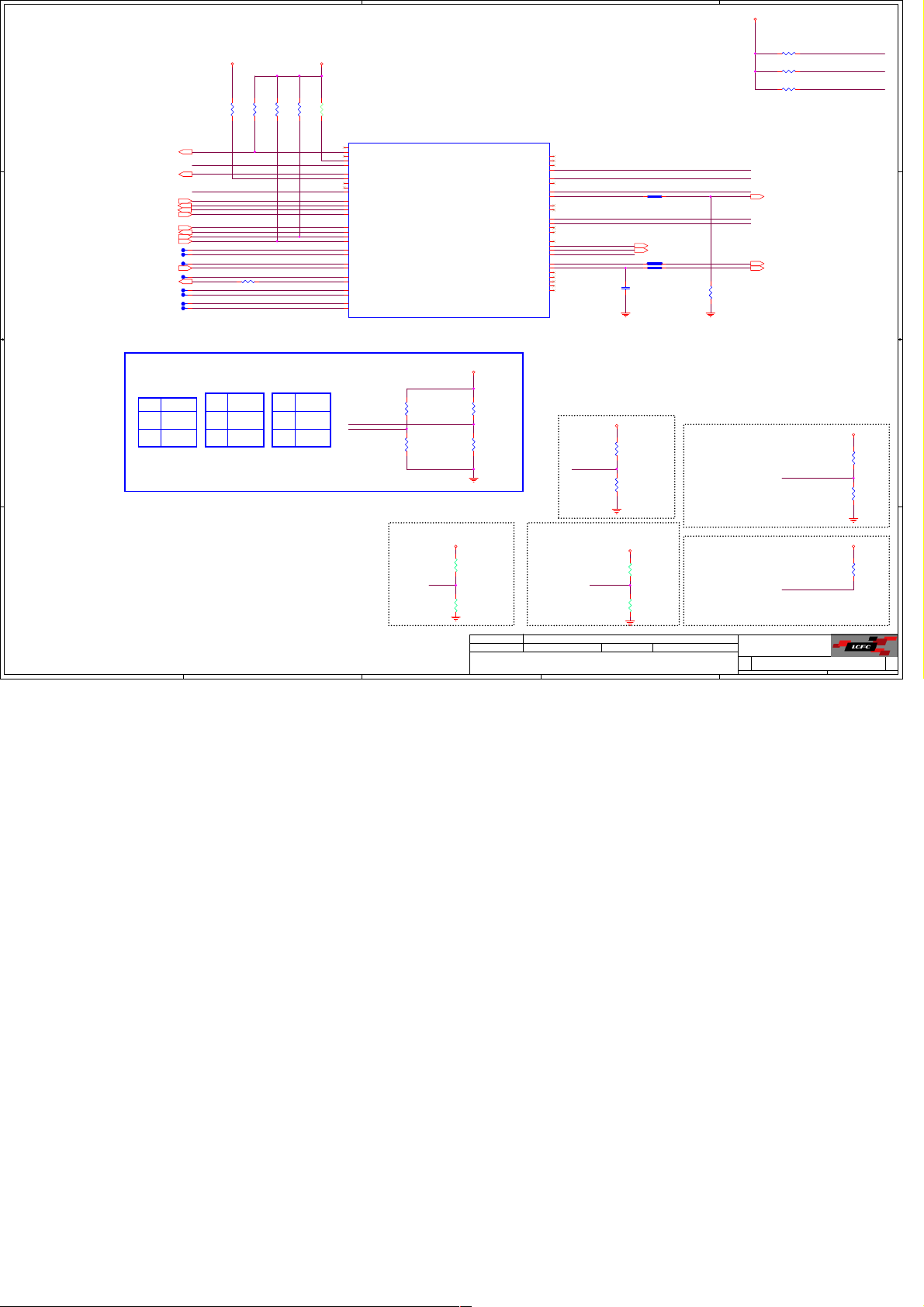

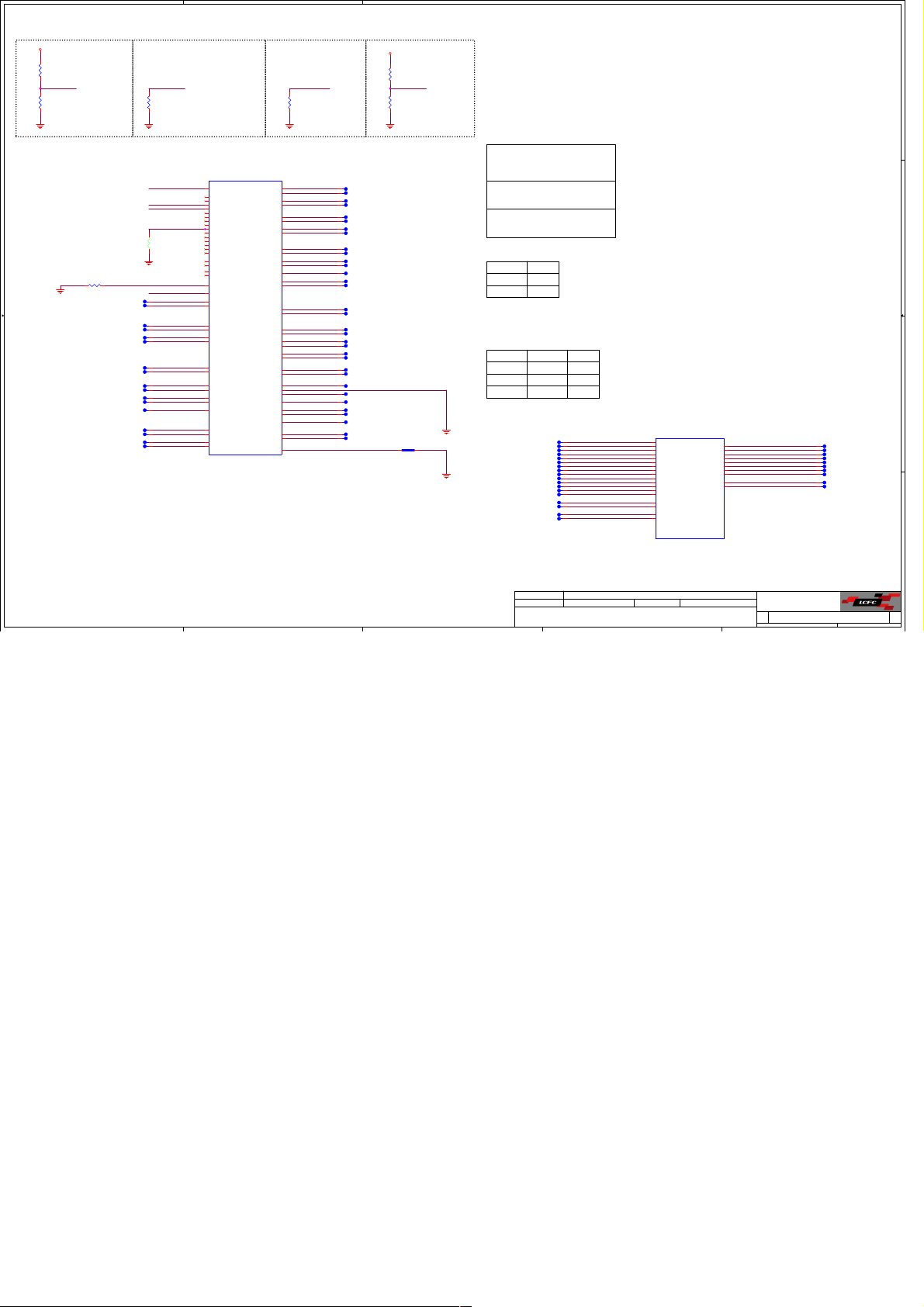

TABLE

Pin

D D

Block 0

C C

Block 2

Block 4

B B

Block 6

A A

A26

D26

D28

C28

B26

C26

B28

A28

B30

D30

B33

D32

A30

C30

B32

C32

H37

H34

K34

K35

H36

H35

K36

K37

N36

N34

R37

R34

N37

N35

R36

R35

AN35

AN34

AR35

AR34

AN37

AN36

AR36

AR37

AU35

AU34

AW35

AW34

AU37

AU36

AW36

AW37

BA35

BA34

BC35

BC34

BA37

BA36

BC36

BC37

BE35

BE34

BG35

BG34

BE37

BE36

BG36

BG37

Interleave

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

Non-Interleave

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR1_DQ[0]

DDR1_DQ[1]

DDR1_DQ[2]

DDR1_DQ[3]

DDR1_DQ[4]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

DDR1_DQ[8]

DDR1_DQ[9]

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

4

Block 0

Block 2

Block 4

Block 6

UCPU1B

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

DDR0_DQ_5/DDR0_DQ_5

B28

DDR0_DQ_6/DDR0_DQ_6

A28

DDR0_DQ_7/DDR0_DQ_7

B30

DDR0_DQ_8/DDR0_DQ_8

D30

DDR0_DQ_9/DDR0_DQ_9

B33

DDR0_DQ_10/DDR0_DQ_10

D32

DDR0_DQ_11/DDR0_DQ_11

A30

DDR0_DQ_12/DDR0_DQ_12

C30

DDR0_DQ_13/DDR0_DQ_13

B32

DDR0_DQ_14/DDR0_DQ_14

C32

DDR0_DQ_15/DDR0_DQ_15

H37

DDR0_DQ_16/DDR0_DQ_32

H34

DDR0_DQ_17/DDR0_DQ_33

K34

DDR0_DQ_18/DDR0_DQ_34

K35

DDR0_DQ_19/DDR0_DQ_35

H36

DDR0_DQ_20/DDR0_DQ_36

H35

DDR0_DQ_21/DDR0_DQ_37

K36

DDR0_DQ_22/DDR0_DQ_38

K37

DDR0_DQ_23/DDR0_DQ_39

N36

DDR0_DQ_24/DDR0_DQ_40

N34

DDR0_DQ_25/DDR0_DQ_41

R37

DDR0_DQ_26/DDR0_DQ_42

R34

DDR0_DQ_27/DDR0_DQ_43

N37

DDR0_DQ_28/DDR0_DQ_44

N35

DDR0_DQ_29/DDR0_DQ_45

R36

DDR0_DQ_30/DDR0_DQ_46

R35

DDR0_DQ_31/DDR0_DQ_47

AN35

DDR0_DQ_32/DDR1_DQ_0

AN34

DDR0_DQ_33/DDR1_DQ_1

AR35

DDR0_DQ_34/DDR1_DQ_2

AR34

DDR0_DQ_35/DDR1_DQ_3

AN37

DDR0_DQ_36/DDR1_DQ_4

AN36

DDR0_DQ_37/DDR1_DQ_5

AR36

DDR0_DQ_38/DDR1_DQ_6

AR37

DDR0_DQ_39/DDR1_DQ_7

AU35

DDR0_DQ_40/DDR1_DQ_8

AU34

DDR0_DQ_41/DDR1_DQ_9

AW35

DDR0_DQ_42/DDR1_DQ_10

AW34

DDR0_DQ_43/DDR1_DQ_11

AU37

DDR0_DQ_44/DDR1_DQ_12

AU36

DDR0_DQ_45/DDR1_DQ_13

AW36

DDR0_DQ_46/DDR1_DQ_14

AW37

DDR0_DQ_47/DDR1_DQ_15

BA35

DDR0_DQ_48/DDR1_DQ_32

BA34

DDR0_DQ_49/DDR1_DQ_33

BC35

DDR0_DQ_50/DDR1_DQ_34

BC34

DDR0_DQ_51/DDR1_DQ_35

BA37

DDR0_DQ_52/DDR1_DQ_36

BA36

DDR0_DQ_53/DDR1_DQ_37

BC36

DDR0_DQ_54/DDR1_DQ_38

BC37

DDR0_DQ_55/DDR1_DQ_39

BE35

DDR0_DQ_56/DDR1_DQ_40

BE34

DDR0_DQ_57/DDR1_DQ_41

BG35

DDR0_DQ_58/DDR1_DQ_42

BG34

DDR0_DQ_59/DDR1_DQ_43

BE37

DDR0_DQ_60/DDR1_DQ_44

BE36

DDR0_DQ_61/DDR1_DQ_45

BG36

DDR0_DQ_62/DDR1_DQ_46

BG37

DDR0_DQ_63/DDR1_DQ_47

WHISKEYLAKE-U_BGA1528

Pin

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

2 of 20

Interleave

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

TABLE

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/NC

DDR0_CKE_3/NC

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR1_DQSN[0]

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

3

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

Non-Interleave

-M_A_DDRCLK0_1066M

M_A_DDRCLK0_1066M

-M_A_DDRCLK1_1066M

M_A_DDRCLK1_1066M

M_A_CKE0

M_A_CKE1

-M_A_CS0

-M_A_CS1

M_A_ODT0

M_A_ODT1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

M_A_BS0

M_A_BS1

M_A_BG0

-M_A_ACT

M_A_BG1

-M_A_DQS0

M_A_DQS0

-M_A_DQS1

M_A_DQS1

-M_A_DQS4

M_A_DQS4

-M_A_DQS5

M_A_DQS5

-M_A_ALERT

M_A_PARITY

M_A_VREF_CA_CPU

DDR_PG_CTRL

TABLE

AB35

W36

AA37

AB34

AA36

V34

AA34

W34

V35

W35

AC32

AB32

AC31

Y32

W32

AC34

AB31

Y31

AC36

AC37

AC35

AA35

Pin

-M_A_DDRCLK0_1066M 33

M_A_DDRCLK0_1066M 33

-M_A_DDRCLK1_1066M 33

M_A_DDRCLK1_1066M 33

M_A_CKE0 33

M_A_CKE1 33

-M_A_CS0 33

-M_A_CS1 33

M_A_ODT0 33

M_A_ODT1 33

M_A_BS0 33

M_A_BS1 33

M_A_BG0 33

-M_A_ACT 33

M_A_BG1 33

-M_A_ALERT 33

M_A_PARITY 33

M_A_VREF_CA_CPU 33

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BA[2]

DDR0_MA[12]

DDR0_MA[11]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[13]

DDR0_CAS#

DDR0_WE#

DDR0_RAS#

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

2

Vendor

ROHM

TOSHIBA

ON

LPDDR3DDR3L

DDR0_CAA[0]

DDR0_CAA[1]

DDR0_CAA[2]

DDR0_CAA[3]

DDR0_CAA[4]

DDR0_CAA[5]

DDR0_CAA[6]

DDR0_CAA[7]

DDR0_CAA[8]

DDR0_CAA[9]

DDR0_CAB[0]

DDR0_CAB[1]

DDR0_CAB[2]

DDR0_CAB[3]

DDR0_CAB[4]

DDR0_CAB[5]

DDR0_CAB[6]

DDR0_CAB[7]

DDR0_CAB[8]

DDR0_CAB[9]

Not Used

Not Used

TABLE of BJT (Q0401)

VCC1R2A

2

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BG[0]

DDR0_MA[12]

DDR0_MA[11]

DDR0_ACT#

DDR0_BG[1]

DDR0_MA[13]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[16]

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

LCFC P/N

SB00000WC0J

SB000010700

SB000013J00

DDR_VTT_PG_CTRL

1

Q0401

DTC015TMT2L_VMT3

3

R0401

@

1/20W_10K_5%_0201

1 2

DDR4

M_A_DQ[63:0] 5,33

M_A_A[16:0] 33

-M_A_DQS[7:0] 5,33

M_A_DQS[7:0] 5,33

Description

S TR DTC015TMT2L NPN VMT3

S TR RN1131MFV NPN VESM

S TR DTC115TM3T5G NPN SOT-723-3

VCC3M

R0402

1/20W_100K_5%_0201

1 2

1

DDR_VTT_PG_CTRL 106

LOGIC

LOGIC

LOGIC

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2015/09/01

2015/09/01

2015/09/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/12/31

2016/12/31

2016/12/31

Title

CPU (2/16): DDR (1/2)

CPU (2/16): DDR (1/2)

CPU (2/16): DDR (1/2)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

4 128

4 128

4 128

1

0.1

0.1

0.1

5

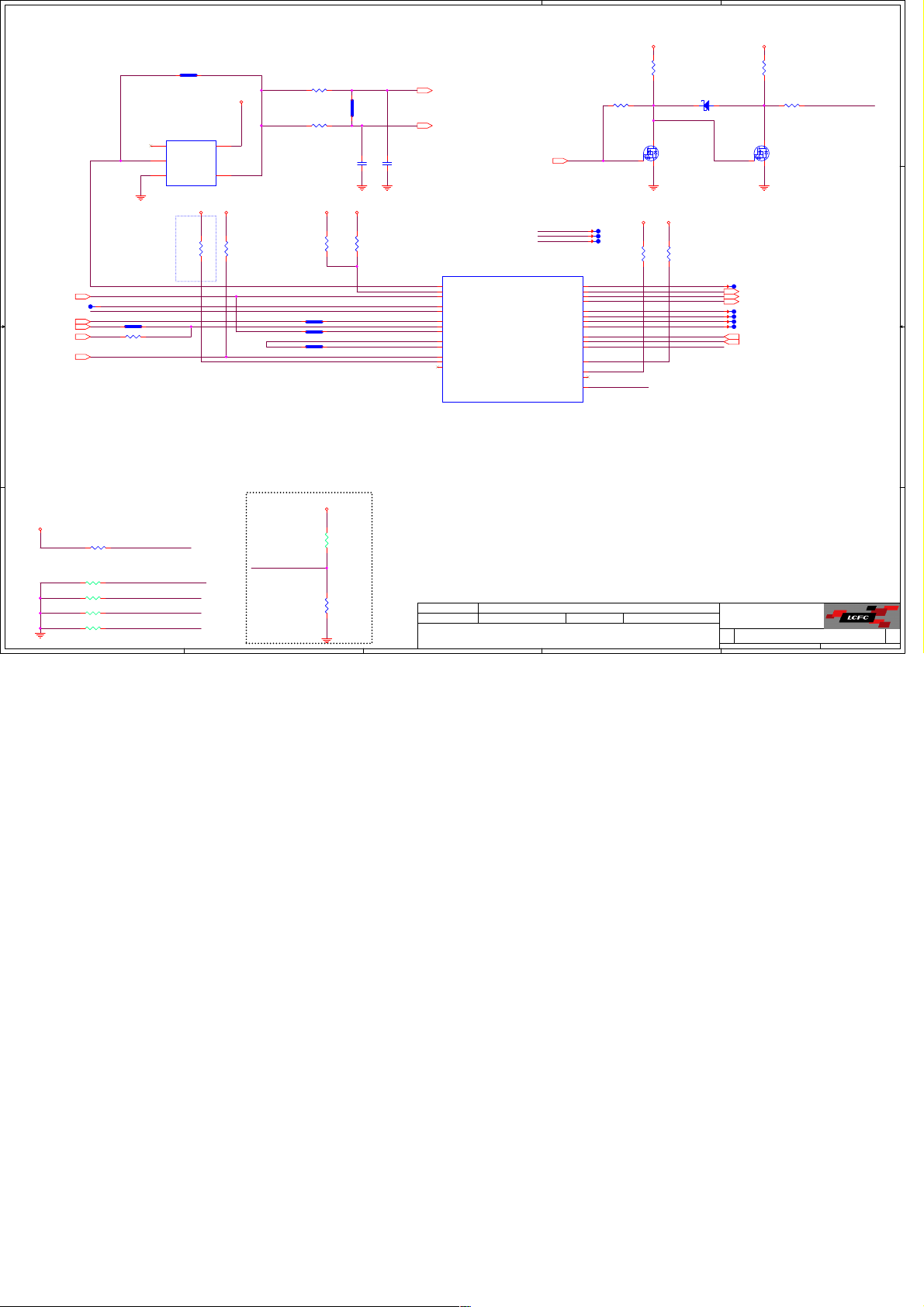

VInafix.com

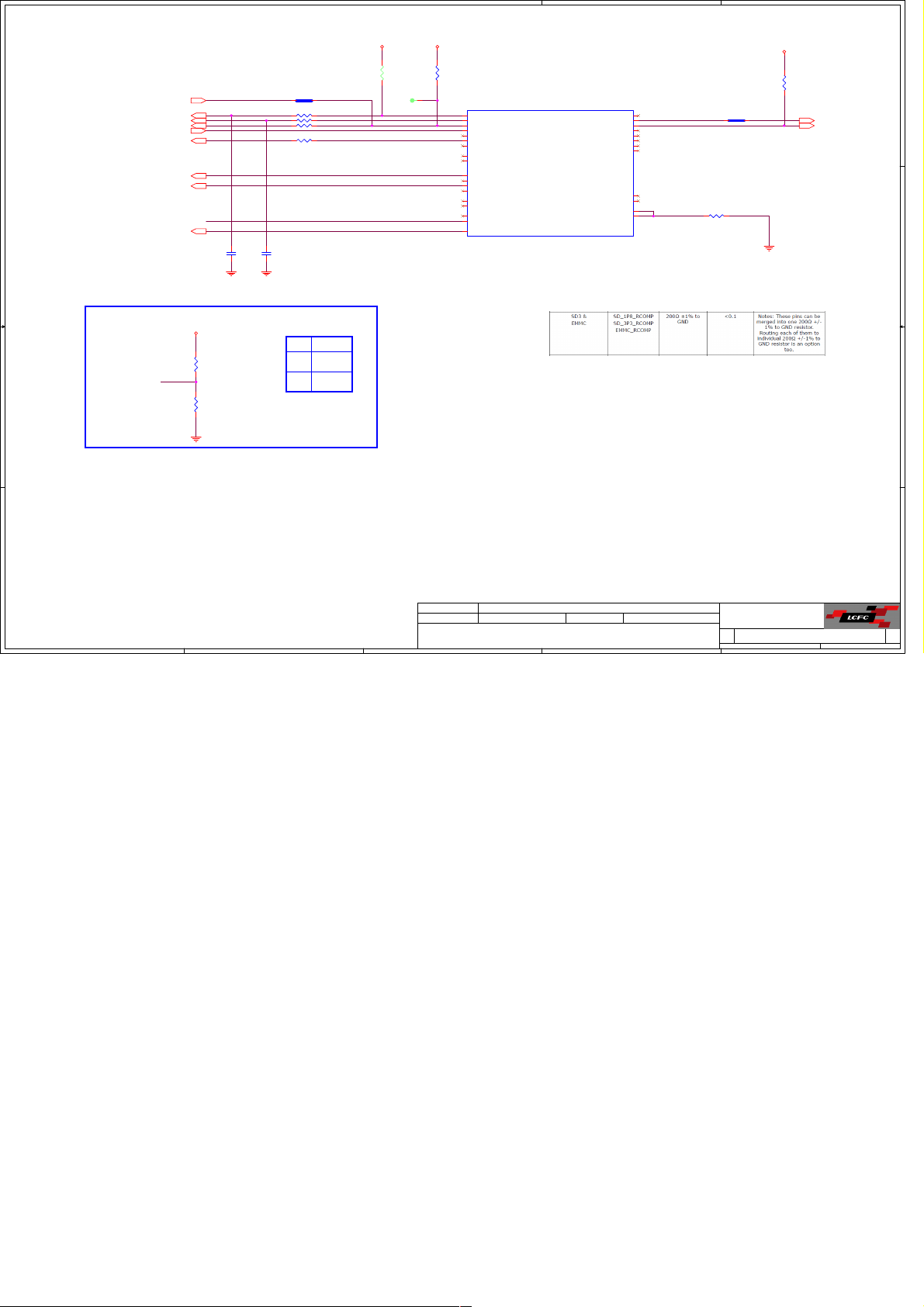

TABLE

Pin

D D

Block 1

C C

Block 3

Block 5

B B

Block 7

A A

J22

H25

G22

H22

F25

J25

G25

F22

D22

C22

C24

D24

A22

B22

A24

B24

G31

G32

H29

H28

G28

G29

H31

H32

L31

L32

N29

N28

L28

L29

N31

N32

AJ29

AJ30

AM32

AM31

AM30

AM29

AJ31

AJ32

AR31

AR32

AV30

AV29

AR30

AR29

AV32

AV31

BA32

BA31

BD31

BD32

BA30

BA29

BD29

BD30

BG31

BG32

BK32

BK31

BG29

BG30

BK30

BK29

Interleave

DDR1_DQ[0]

DDR1_DQ[1]

DDR1_DQ[2]

DDR1_DQ[3]

DDR1_DQ[4]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

DDR1_DQ[8]

DDR1_DQ[9]

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

Non-Interleave

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

4

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

[WHL PDG]for WHL DDR4 COMPENSATION

DDR_RCOMP[0] Pull down 121 ohm resistor

DDR_RCOMP[1] Pull down 80.6 ohm resistor

DDR_RCOMP[2] Pull down 100 ohm resistor

TABLE

Pin

H24

DDR1_DQSN[0]

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

Block 1

Block 3

Block 5

Block 7

UCPU1C

J22

DDR1_DQ_0/DDR0_DQ_16

H25

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

DDR1_DQ_4/DDR0_DQ_20

J25

DDR1_DQ_5/DDR0_DQ_21

G25

DDR1_DQ_6/DDR0_DQ_22

F22

DDR1_DQ_7/DDR0_DQ_23

D22

DDR1_DQ_8/DDR0_DQ_24

C22

DDR1_DQ_9/DDR0_DQ_25

C24

DDR1_DQ_10/DDR0_DQ_26

D24

DDR1_DQ_11/DDR0_DQ_27

A22

DDR1_DQ_12/DDR0_DQ_28

B22

DDR1_DQ_13/DDR0_DQ_29

A24

DDR1_DQ_14/DDR0_DQ_30

B24

DDR1_DQ_15/DDR0_DQ_31

G31

DDR1_DQ_16/DDR0_DQ_48

G32

DDR1_DQ_17/DDR0_DQ_49

H29

DDR1_DQ_18/DDR0_DQ_50

H28

DDR1_DQ_19/DDR0_DQ_51

G28

DDR1_DQ_20/DDR0_DQ_52

G29

DDR1_DQ_21/DDR0_DQ_53

H31

DDR1_DQ_22/DDR0_DQ_54

H32

DDR1_DQ_23/DDR0_DQ_55

L31

DDR1_DQ_24/DDR0_DQ_56

L32

DDR1_DQ_25/DDR0_DQ_57

N29

DDR1_DQ_26/DDR0_DQ_58

N28

DDR1_DQ_27/DDR0_DQ_59

L28

DDR1_DQ_28/DDR0_DQ_60

L29

DDR1_DQ_29/DDR0_DQ_61

N31

DDR1_DQ_30/DDR0_DQ_62

N32

DDR1_DQ_31/DDR0_DQ_63

AJ29

DDR1_DQ_32/DDR1_DQ_16

AJ30

DDR1_DQ_33/DDR1_DQ_17

AM32

DDR1_DQ_34/DDR1_DQ_18

AM31

DDR1_DQ_35/DDR1_DQ_19

AM30

DDR1_DQ_36/DDR1_DQ_20

AM29

DDR1_DQ_37/DDR1_DQ_21

AJ31

DDR1_DQ_38/DDR1_DQ_22

AJ32

DDR1_DQ_39/DDR1_DQ_23

AR31

DDR1_DQ_40/DDR1_DQ_24

AR32

DDR1_DQ_41/DDR1_DQ_25

AV30

DDR1_DQ_42/DDR1_DQ_26

AV29

DDR1_DQ_43/DDR1_DQ_27

AR30

DDR1_DQ_44/DDR1_DQ_28

AR29

DDR1_DQ_45/DDR1_DQ_29

AV32

DDR1_DQ_46/DDR1_DQ_30

AV31

DDR1_DQ_47/DDR1_DQ_31

BA32

DDR1_DQ_48/DDR1_DQ_48

BA31

DDR1_DQ_49/DDR1_DQ_49

BD31

DDR1_DQ_50/DDR1_DQ_50

BD32

DDR1_DQ_51/DDR1_DQ_51

BA30

DDR1_DQ_52/DDR1_DQ_52

BA29

DDR1_DQ_53/DDR1_DQ_53

BD29

DDR1_DQ_54/DDR1_DQ_54

BD30

DDR1_DQ_55/DDR1_DQ_55

BG31

DDR1_DQ_56/DDR1_DQ_56

BG32

DDR1_DQ_57/DDR1_DQ_57

BK32

DDR1_DQ_58/DDR1_DQ_58

BK31

DDR1_DQ_59/DDR1_DQ_59

BG29

DDR1_DQ_60/DDR1_DQ_60

BG30

DDR1_DQ_61/DDR1_DQ_61

BK30

DDR1_DQ_62/DDR1_DQ_62

BK29

DDR1_DQ_63/DDR1_DQ_63

WHISKEYLAKE-U_BGA1528

@

[WHL PDG]for CNL DDR4 COMPENSATION

DDR_RCOMP[0] Pull down 100 ohm resistor

DDR_RCOMP[1] Pull down 100 ohm resistor

DDR_RCOMP[2] Pull down 100 ohm resistor

Interleave

Non-Interleave

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP_7

3 of 20

LOGIC

DDR1_CKE_2/NC

DDR1_CKE_3/NC

NC/DDR1_ODT_1

NC/DDR1_MA_3

NC/DDR1_MA_4

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_COMP_0

DDR_COMP_1

DDR_COMP_2

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

TABLE

AF35

A

AE37

AE36

AC29

W29

AB28

AC28

W28

Y28

AK35

AK34

AJ35

AJ34

AJ37

AF34

AJ36

AG34

AG35

AG36

AG37

AE35

3

-M_A_DQS2

M_A_DQS2

-M_A_DQS3

M_A_DQS3

-M_A_DQS6

M_A_DQS6

-M_A_DQS7

M_A_DQS7

-DRAMRST

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

Pin

B29

1 2

R0501 1/20W_121_1%_0201

1 2

R0502 1/20W_80.6_1%_0201

1 2

R0503 1/20W_100_1%_0201

WHL RCOMP

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BA[2]

DDR1_MA[12]

DDR1_MA[11]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[13]

DDR1_CAS#

DDR1_WE#

DDR1_RAS#

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

LPDDR3DDR3L

DDR1_CAA[0]

DDR1_CAA[1]

DDR1_CAA[2]

DDR1_CAA[3]

DDR1_CAA[4]

DDR1_CAA[5]

DDR1_CAA[6]

DDR1_CAA[7]

DDR1_CAA[8]

DDR1_CAA[9]

DDR1_CAB[0]

DDR1_CAB[1]

DDR1_CAB[2]

DDR1_CAB[3]

DDR1_CAB[4]

DDR1_CAB[5]

DDR1_CAB[6]

DDR1_CAB[7]

DDR1_CAB[8]

DDR1_CAB[9]

Not Used

Not Used

VCC1R2A

12

R0504

1/20W_470_5%_0201

DDR4

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BG[0]

DDR1_MA[12]

DDR1_MA[11]

DDR1_ACT#

DDR1_BG[1]

DDR1_MA[13]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[16]

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

2

-DRAMRST 33

M_A_DQ[63:0] 4,33

-M_A_DQS[7:0] 4,33

M_A_DQS[7:0] 4,33

1

LOGIC

LOGIC

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2015/09/01

2015/09/01

2015/09/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/12/31

2016/12/31

2016/12/31

Title

CPU (3/16): DDR (2/2)

CPU (3/16): DDR (2/2)

CPU (3/16): DDR (2/2)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

5 128

5 128

5 128

1

0.1

0.1

0.1

5

VInafix.com

4

3

2

1

TABLE : GT3e RCOMP Resistor

CPU SKU

Pin A14 Reserved

Pin B14

D D

TABLE : Functional Strap

ITP_PMODE (DFX Test Mode)

HIGH

LOW

TABLE : Functional Strap

GPP_E6 (JTAG ODT Disable)

HIGH

LOW

TABLE : Functional Strap

GPP_H2/CNV_BT_I2S_SDO (eSPI Flash Sharing Mode)

HIGH

LOW

C C

B B

U43e

OPCE_RCOMP

OPC_RCOMP

DFX Test Mode Disabled (Default)

DFX Test Mode Enabled

Enabled

Disabled

Slave Attached Flash Sharing (SAFS) Enabled

Master Attached Flash Sharing (MAFS) Enabled (Default)

U42

Reserved

VCCSTG

R0603

1/20W_1K_5%_0201

1 2

PECI85

-PROCHOT85,102,108

PECI

-PROCHOT

R0601 1/20W_499_1%_0201

[WHL PDG FOR DCL DEBUG]

VCCST VCCST

R0605

1/20W_1K_5%_0201

1 2

12

TP0601

TP0602

TP0603

TP0604

1 2

R0606 1/20W_49.9_1%_0201

1 2

R0607 1/20W_49.9_1%_0201

1 2

R0608 1/20W_49.9_1%_0201

1 2

R0609 1/20W_49.9_1%_0201

1 2

-CATERR

-PROCHOT_CPU

-THRMTRIP

XDP_BPM#0

1

XDP_BPM#1

1

XDP_BPM#2

1

XDP_BPM#3

1

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

Follow the CRB

R0609, R0610 for WHL 4+3e

R0604

1/20W_49.9_1%_0201

BW25

UCPU1D

AA4

CATERR#

AR1

PECI

Y4

PROCHOT#

BJ1

THRMTRIP#

U1

BPM#_0

U2

BPM#_1

U3

BPM#_2

U4

BPM#_3

CE9

GPP_E3/CPU_GP0

CN3

GPP_E7/CPU_GP1

CB34

GPP_B3/CPU_GP2

CC35

GPP_B4/CPU_GP3

BP27

PROC_POPIRCOMP

PCH_OPIRCOMP

L5

RSVD35

N5

RSVD36

WHISKEYLAKE-U_BGA1528

@

4 of 20

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

PROC_PREQ#

PROC_PRDY#

T6

U6

Y5

T5

AB6

W6

U5

W5

P5

Y6

P6

W2

W1

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST

PCH_TCK_R

VCCSTG

1 2

R0610

1/20W_51_5%_0201

R0617

1/20W_100_5%_0201

R0602

@

1/20W_51_5%_0201

1 2

1 2

1 2

R0611 0_0201_SP

1 2

R0612 0_0201_SP

1 2

R0613 0_0201_SP

1 2

R0614 0_0201_SP

1 2

R0615 0_0201_SP

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

-XDP_TRST

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

CPU (4/16): MISC/JTAG

CPU (4/16): MISC/JTAG

CPU (4/16): MISC/JTAG

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

6 128

6 128

6 128

1

0.1

0.1

0.1

5

VInafix.com

D D

4

GPP_C5, Weak internal PD

Rising edge of RSMRST#

*L: LPC

H: eSPI

VCC3_SUS

R0719

1/20W_1K_5%_0201@

1 2

GPP_C5

12

R0720

@

1/20W_20K_5%_0201

GPP_C2, Internal PD 20K

L:Disable Intel ME Crypto TLS cipher suite (no confidentiality).

*H:Enable Intel ME Crypto Transport Layer Security (TLS) cipher

suite (with confidentiality).Support Intel AMT with TLS and

Intel SBA (Small Business Advantage) with TLS.

VCC3_SUS

R0711

1/20W_1K_5%_0201

1 2

GPP_C2

12

R0718

@

1/20W_20K_5%_0201

3

This signal has an internal pull-down.

0

= Disable IntelR DCI-OOB (Default)

FOR DCI USE

1 = Enable IntelR DCI-OOB

PCHHOT

1 2

R0717 1/20W_4.7K_5%_0201

2

VCC3_SUS

1

VCC3_SUS_SPI

C C

SPI_CLK21,98

SPI_MISO_IO121,98

SPI_MOSI_IO021,98

SPI_IO221

SPI_IO321

-SPI_CS0 For SPI

-SPI_CS1 For SPI

-SPI_CS2 For TPM

B B

A A

5

-SPI_CS021

-SPI_CS1_8MB21

-SPI_CS298

SPI_CLK

SPI_MISO_IO1

SPI_MOSI_IO0

SPI_IO2

SPI_IO3

R07231/20W_100K_5%_0201

1 2

1 2

R07211/20W_100K_5%_0201

R07221/20W_100K_5%_0201

1 2

C-LINK

CL_CLK_WLAN66

CL_DATA_WLAN66

-CL_RST_WLAN66

-KBRC85

IRQSER85

1 2

R0712 0_0402_SP

1 2

R0713 0_0402_SP

1 2

R0714 0_0402_SP

1 2

R0715 0_0402_SP

1 2

R0716 0_0402_SP

4

CL_CLK_WLAN

CL_DATA_WLAN

-CL_RST_WLAN

-KBRC

IRQSER

VCC3B

12

R07041/20W_8.2K_5%_0201

UCPU1E

CH37

R0712

SPI0_CLK

R0713

R0714

R0715

R0716

-SPI_CS0

-SPI_CS1_8MB

-SPI_CS2

R0705

1/20W_1K_5%_0201@

1 2

CF37

SPI0_MISO

CF36

SPI0_MOSI

CF34

SPI0_IO2

CG34

SPI0_IO3

CG36

SPI0_CS0#

CG35

SPI0_CS1#

CH34

SPI0_CS2#

CF20

GPP_D1/SPI1_CLK/BK1/SBK1

CG22

GPP_D2/SPI1_MISO_IO1/BK2/SBK2

CF22

GPP_D3/SPI1_MOSI_IO0/BK3/SBK3

CG23

GPP_D21/SPI1_IO2

CH23

GPP_D22/SPI1_IO3

CG20

GPP_D0/SPI1_CS0#/BK0/SBK0

CH7

CL_CLK

CH8

CL_DATA

CH9

CL_RST#

BV29

GPP_A0/RCIN#/TIME_SYNC1

BV28

GPP_A6/SERIRQ

WHISKEYLAKE-U_BGA1528

@

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 of 20

3

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

CK14

CH15

CJ15

CH14

CF15

CG15

CN15

CM15

CC34

CA29

BY29

BY27

BV27

CA28

CA27

BV32

BV30

BY30

VCC3_SUS

R0707

R0709

R0710

1 2

1 2

1 2

1/20W_499_1%_0201

1/20W_499_1%_0201

1/20W_4.7K_5%_0201

GPP_C2

GPP_C5

PCHHOT

1 2

R0725 0_0201_SP

1 2

R0726 0_0201_SP

1 2

R0727 0_0201_SP

1 2

R0728 0_0201_SP

1 2

R0729 0_0201_SP

1 2

R0730 0_0201_SP

LPCCLK_0

1 2

R0702 1/20W_22_1%_0201EMC@

1

1

C0702

@

@

2

2

27P_25V_J_NPO_0201

27P_25V_J_NPO_0201

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2015/01/12

2015/01/12

2015/01/12

2

VCC3B

12

R07241/20W_10K_5%_0201

@

R0708

1 2

1/20W_4.7K_5%_0201

1

1

C0703

C0704

C0705

@

@

2

2

27P_25V_J_NPO_0201

27P_25V_J_NPO_0201

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

12

R07031/20W_8.2K_5%_0201

SMB_CLK

SMB_DATA

EC_SCL2

EC_SDA2

1

EMC_NS@

C0701

22P_50V_J_NPO_0402

2

2016/01/12

2016/01/12

2016/01/12

SMB_CLK 93

SMB_DATA 93

EC_SCL2 93

EC_SDA2 93

LPC_AD0 85

LPC_AD1 85

LPC_AD2 85

LPC_AD3 85

-LPC_FRAME 85

-SUS_STAT 85

LPCCLK_EC_24M 85

DIMM1,CP

GPU,G-Sensor Thermal-Sensor、EC

D

EC and TPM Module debug port

Title

Title

Title

CPU (5/16): ESPI/SPI/SMBUS/C-LINK

CPU (5/16): ESPI/SPI/SMBUS/C-LINK

CPU (5/16): ESPI/SPI/SMBUS/C-LINK

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

Date: Sheet

Date: Sheet

Date: Sheet

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

1

7 128

7 128

7 128

of

of

of

0.1

0.1

0.1

5

VInafix.com

D D

Size CTL51

FPR_RESET73,85

TP0801@

TP0802@

TP0803@

TP0804@

TP0805@

TP0806@

TP0807@

TP0808@

Size CTL

(GPP_C19)

0 (GND Low)

-TPM_IRQ

GPP_B18

-WLAN_RF_KILL

GPP_B22

BRI_RSP_CNVI

RGI_DT_CNVI

BRI_DT_CNVI

RGI_RSP_CNVI

UART_RX

UART_TX

-EC_SCI

-EC_WAKE

1

1

1

Size CTL

1

1

1

1

GPP_H9

1

Graphics ID

Status

UMA

-TPM_IRQ98

-WLAN_RF_KILL66

FN, F1, F4 PD 100K, BIOS need output

"High" while act i v e

C C

BRI_RSP_CNVI66

RGI_DT_CNVI66

BRI_DT_CNVI66

RGI_RSP_CNVI66

UART_RX66,84

UART_TX66,84

-EC_SCI85

-EC_WAKE85

Panel ID

(Pin#7 Control)

Status

B B

15"

14" 1 (NC High)

A A

5

VCC3B

1 2

-DISCRETE_

PRESENCE

(GPP_D13)

0 (R0824)

1 (R0823)DIS

R0801

GPP_A11

1 2

1/16W_20K_1%_0402

4

R0806

1 2

1/20W_10K_5%_0201

12

R08281/20W_0_5%_0201 @

Graphics Control

Status

R18M

4

R0802

R0803

1 2

1/20W_10K_5%_0201

FPR_RESET_PCH

-DISCRETE_CTL

(GPP_D14)

0 (R0826)

1 (R0825)R19M

1/20W_10K_5%_0201

VCC3_SUS

@

1 2

R0804

1/20W_1K_5%_0201

GPP_B17

CC27

CC32

CE28

CE27

CE29

CA31

CA32

CC29

CC30

CA30

CK20

CG19

CJ20

CH19

CR12

CP12

CN12

CM12

CM11

CN11

CK12

CJ12

CF27

CF29

CH27

CH28

CJ30

CJ31

UCPU1F

WHISKEYLAKE-U_BGA1528

@

GPP_B15/GSPI0_CS0#

GPP_A7/PIRQA#/GSPI0_CS1#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS0#

GPP_A11/PME#/GSPI1_CS1#/SD_VDD2_PWR_EN#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_F5/CNV_BRI_RSP

GPP_F6/CNV_RGI_DT

GPP_F4/CNV_BRI_DT

GPP_F7/CNV_RGI_RSP

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_H4/I2C2_SDA

GPP_H5/I2C2_SCL

GPP_H6/I2C3_SDA

GPP_H7/I2C3_SCL

GPP_H8/I2C4_SDA

GPP_H9/I2C4_SCL

12

R0825

-DISCRETE_PRESENCE

-DISCRETE_CTL

1/20W_10K_5%_0201R19M@

12

R0826

R18M@

1/20W_10K_5%_0201

GPP_B22, Internal PD 20K

*L: SPI

H: LPC

GPP_B22 GPP_B18

3

GPP_D9/ISH_SPI_CS#/GSPI2_CS0#

GPP_D10/ISH_SPI_CLK/GSPI2_CLK

GPP_D11/ISH_SPI_MISO/GSPI2_MISO

GPP_D12/ISH_SPI_MOSI/GSPI2_MOSI

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_H10/I2C5_SDA/ISH_I2C2_SDA

GPP_H11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD

GPP_D14/ISH_UART0_TXD

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A12/ISH_GP6/BM_BUSY#/SX_EXIT_HOLDOFF#

6 of 20

VCC3B

12

R0823

1/20W_10K_5%_0201DIS@

12

R0824

UMA@

1/20W_10K_5%_0201

VCC3_SUS

12

R0809

@

1/20W_20K_5%_0201

12

R0810

@

1/20W_20K_5%_0201

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

CN22

CR22

CM22

CP22

CK22

CH20

CH22

CJ22

CJ27

CJ29

CM24

CN23

CM23

CR24

CG12

CH12

CF12

CG14

BW35

GPP_A18/ISH_GP0

BW34

GPP_A19/ISH_GP1

CA37

GPP_A20/ISH_GP2

CA36

GPP_A21/ISH_GP3

CA35

GPP_A22/ISH_GP4

CA34

GPP_A23/ISH_GP5

BW37

GPP_B18, Internal PD 20K

*L: Disable “ No Reboot” mode

H: Enable “ No Reboot” mode

2015/01/12

2015/01/12

2015/01/12

GPP_D12

GPP_D5

GPP_D7

-DISCRETE_PRESENCE

-DISCRETE_CTL

-LED_MUTE

-LED_MICMUTE

GPP_C15

TP4_RESET_PCH TP4_RESET

-LID_CLOSE_R

VCC3B

12

R0812

1/20W_10K_5%_0201@

GPP_D5

12

R0813

@

1/20W_10K_5%_0201

VCC3_SUS

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

1 2

R0805 0_0201_SP

-LED_MUTE 88

-LED_MICMUTE 88

1 2

R0821 0_0201_SP

1 2

R0827 0_0201_SP

1

EMC_NS@

C0801

10P_25V_J_NPO_0201

2

12

R0807

@

1/20W_1K_5%_0201

12

R0808

@

1/20W_20K_5%_0201

2016/01/12

2016/01/12

2016/01/12

2

R0817

1/16W_10K_5%_0402

1 2

@

R0818

1/16W_10K_5%_0402

1 2

@

R0819

1/16W_10K_5%_0402

1 2

@

PAD_DISABLE 89

TP4_RESET 88

-LID_CLOSE 51,73,85,89

GPP_D12

1

GPP_C15

-LED_MUTE

-LED_MICMUTE

VCC3B

PAD_DISABLEPAD_DISABLE_PCH

-LID_CLOSE

12

R0822

1/16W_100K_5%_0402

GPP_D12, External pull-up is required.

ecommend 100K if pulled up to 3.3V or 75K

R

if pulled up to 1.8V.

This strap should sample HIGH.

There should NOT be any on-board device driving it

to opposite direction during strap sampling.

GPP_D7, Reserved, Rising edge of DSW_PWROK

External pull-up is required. Recommend 100K.

This strap should sample HIGH.

There should NOT be any on-board device driving it

to opposite direction during strap sampling

Title

Title

Title

Size

Size

Size

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

GPP_D7

CPU (6/16): LPSS/ISH

CPU (6/16): LPSS/ISH

CPU (6/16): LPSS/ISH

Document Number Rev

Document Number Rev

Document Number Rev

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

1

VCC3_SUS

12

R0814

1/20W_100K_1%_0201

12

R0815

@

1/20W_10K_5%_0201

VCC3_SUS

12

R0816

1/20W_100K_1%_0201

8 128

8 128

8 128

0.1

0.1

0.1

5

VInafix.com

4

3

2

1

VCC3_SUS VCC3_SUS

R0903

1/20W_1K_5%_0201@

D D

C C

B B

ME_FLASH85

HDA_SYNC78

HDA_BCLK78

HDA_SDO78

HDA_SDIN078

-HDA_RST78

-CNV_RF_RESET66

CNV_CLKREQ66

PCH_SPKR83

ME_FLASH

HDA_BCLK

HDA_SDO HDA_SDO_CPU

-HDA_RST

EMC@

1

C0902

2

22P_25V_J_NPO_0201_MURATA

VCC3B

12

NTPM@

R0911

1/20W_10K_5%_0201

PLANARID4

12

TPM@

R0913

1/20W_10K_5%_0201

R0904 0_0402_SP

R0901 1/20W_33_5%_0201

R0907 1/20W_33_5%_0201EMC@

R0902 1/20W_33_5%_0201

R0908 1/20W_33_5%_0201

EMC@

1

C0901

2

22P_25V_J_NPO_0201_MURATA

TPM ID

1 2

1 2

1 2

1 2

1 2

Status

TPM

NTPM

PLANARID4

(GPP_D18)

0 (R0913)

1 (R0911)

1 2

Test_Point_20MIL

HDA_SYNC_CPUHDA_SYNC

HDA_BCLK_CPU

HDA_SDIN0

-HDA_RST_CPU

-CNV_RF_RESET

CNV_CLKREQ

PLANARID4

PCH_SPKR

R0905

1/20W_1K_5%_0201

1 2

TP0901

1

@

UCPU1G

BN34

HDA_SYNC/I2S0_SFRM

BN37

HDA_BCLK/I2S0_SCLK

BN36

HDA_SDO/I2S0_TXD

BN35

HDA_SDI0/I2S0_RXD

BL36

HDA_SDI1/I2S1_RXD/SNDW1_DATA

BL35

HDA_RST#/I2S1_SCLK/SNDW1_CLK

CK23

GPP_D23/I2S_MCLK

BL37

I2S1_SFRM/SNDW2_CLK

BL34

I2S1_TXD/SNDW2_DATA

CJ32

GPP_H1/I2S2_SFRM/CNV_BT_I2S_BCLK/CNV_RF_RESET#

CH32

GPP_H0/I2S2_SCLK/CNV_BT_I2S_SCLK

CH29

GPP_H2/I2S2_TXD/CNV_BT_I2S_SDI/MODEM_CLKREQ

CH30

GPP_H3/I2S2_RXD/CNV_BT_I2S_SDO

CP24

GPP_D19/DMIC_CLK0/SNDW4_CLK

CN24

GPP_D20/DMIC_DATA0/SNDW4_DATA

CK25

GPP_D17/DMIC_CLK1/SNDW3_CLK

CJ25

GPP_D18/DMIC_DATA1/SNDW3_DATA

CF35

GPP_B14/SPKR

WHISKEYLAKE-U_BGA1528

@

GPP_A17/SD_VDD1_PWR_EN#/ISH_GP7

7 of 20

GPP_G0/SD_CMD

GPP_G1/SD3_DATA0

GPP_G2/SD3_DATA1

GPP_G3/SD3_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_1P8_RCOMP

SD_3P3_RCOMP

CH36

-LED_CAPSLOCK_PCH

CL35

-LED_NUMBER

CL36

CM35

CN35

CH35

CK36

CK34

BW36

BY31

CK33

SD_RCOMP

CM34

1 2

R0915 0_0201_SP

1 2

R0906 1/20W_200_1%_0201

Table 3-1.RCOMP Recommendation for WHL and CFL

VCC3B

12

R0914

@

1/16W_10K_5%_0402

-LED_CAPSLOCK 85,88

-LED_NUMBER 88

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER TH IS SHEET NOR THE INFORMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2016/01/12

2016/01/12

2016/01/12

2

Title

CPU (7/16): AUDIO/SDXC

CPU (7/16): AUDIO/SDXC

CPU (7/16): AUDIO/SDXC

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

E14/E15 NM-C421E14/E15 NM-C421

Thursday, July 04, 2019

Thursday, July 04, 2019

Thursday, July 04, 2019

9 128

9 128

9 128

1

0.1

0.1

0.1

5

VInafix.com

4

3

2

1

D D

PCIE_RCOMP_N

PCIE_RCOMP_P

UCPU1H

BW9

PCIE5_RXN/USB31_5_RXN

BW8

PCIE5_RXP/USB31_5_RXP

BW4

PCIE5_TXN/USB31_5_TXN

BW3

PCIE5_TXP/USB31_5_TXP

BU6

PCIE6_RXN/USB31_6_RXN

BU5

PCIE6_RXP/USB31_6_RXP

BU4

PCIE6_TXN/USB31_6_TXN

BU3

PCIE6_TXP/USB31_6_TXP

BT7

PCIE7_RXN

BT6

PCIE7_RXP

BU2

PCIE7_TXN

BU1

PCIE7_TXP

BU9

PCIE8_RXN

BU8

PCIE8_RXP

BT4

PCIE8_TXN

BT3

PCIE8_TXP

BP5

PCIE9_RXN

BP6

PCIE9_RXP

BR2

PCIE9_TXN

BR1

PCIE9_TXP

BN6

PCIE10_RXN

BN5

PCIE10_RXP

BR4

PCIE10_TXN

BR3

PCIE10_TXP

BN10

PCIE11_RXN/SATA0_RXN

BN8

PCIE11_RXP/SATA0_RXP

BN4

PCIE11_TXN/SATA0_TXN

BN3

PCIE11_TXP/SATA0_TXP

BL6

PCIE12_RXN/SATA1A_RXN

BL5

PCIE12_RXP/SATA1A_RXP

BN2

PCIE12_TXN/SATA1A_TXN

BN1

PCIE12_TXP/SATA1A_TXP

BK6

PCIE13_RXN

BK5

PCIE13_RXP

BM4

PCIE13_TXN

BM3

PCIE13_TXP

BJ6

PCIE14_RXN

BJ5

PCIE14_RXP

BL2

PCIE14_TXN

BL1

PCIE14_TXP

BG5

PCIE15_RXN/SATA1B_RXN

BG6

PCIE15_RXP/SATA1B_RXP

BL4

PCIE15_TXN/SATA1B_TXN

BL3

PCIE15_TXP/SATA1B_TXP

BE5

PCIE16_RXN/SATA2_RXN

BE6

PCIE16_RXP/SATA2_RXP

BJ4

PCIE16_TXN/SATA2_TXN

BJ3

PCIE16_TXP/SATA2_TXP

CE6

PCIE_RCOMP_N

CE5

PCIE_RCOMP_P

CR28

GPP_H12/M2_SKT2/CFG_0

CP28

GPP_H13/M2_SKT2/CFG_1

CN28

GPP_H14/M2_SKT2/CFG_2

CM28

GPP_H15/M2_SKT2/CFG_3

WHISKEYLAKE-U_BGA1528

@

PCIE1_RXN/USB31_1_RXN

PCIE1_RXP/USB31_1_RXP

PCIE1_TXN/USB31_1_TXN

PCIE1_TXP/USB31_1_TXP

PCIE2_RXN/USB31_2_RXN/SSIC_1_RXN

PCIE2_RXP/USB31_2_RXP/SSIC_1_RXP

PCIE2_TXN/USB31_2_TXN/SSIC_1_TXN

PCIE2_TXP/USB31_2_TXP/SSIC_1_TXP

PCIE3_RXN/USB31_3_RXN

PCIE3_RXP/USB31_3_RXP

PCIE3_TXN/USB31_3_TXN

PCIE3_TXP/USB31_3_TXP

PCIE4_RXN/USB31_4_RXN

PCIE4_RXP/USB31_4_RXP

PCIE4_TXN/USB31_4_TXN

PCIE4_TXP/USB31_4_TXP

USB2_COMP

USB2_VBUSSENSE

GPP_E9/USB2_OC0#/GP_BSSB_CLK

GPP_E10/USB2_OC1#/GP_BSSB_DI

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#/SPI1_CS1#

8 of 20

USB2_1N

USB2_1P

USB2_2N

USB2_2P

USB2_3N

USB2_3P

USB2_4N

USB2_4P

USB2_5N

USB2_5P

USB2_6N

USB2_6P

USB2_7N

USB2_7P

USB2_8N

USB2_8P

USB2_9N

USB2_9P

USB2_10N

USB2_10P

USB2_ID

RSVD37

CB5

CB6

CA4

CA3

BY8

BY9

CA2

CA1

BY7

BY6

BY4

BY3

BW6

BW5

BW2

BW1

CE3

CE4

CE1

CE2

CG3

CG4

CD3

CD4

CG5

CG6

CC1

CC2

CG8

CG9

CB8

CB9

CH5

CH6

CC3

CC4

CC5

CE8

CC6

CK6

CK5

CK8

CK9

CP8

CR8

CM8

CN8

CM10

CP10

CN7

AR3

PCIE5_L0_RXN37

PCIE5_L0_RXP37

PCIE5_L0_TXN37

PCIE5_L0_TXP37

PCIE5_L1_RXN37

PCIE5_L1_RXP37

PCIE5_L1_TXN37

AMD GPU

C C

WLAN

2.5" SATA HDD

NVMe SSD

B B

A A

SATA SSD

PCIE5_L1_TXP37

PCIE5_L2_RXN37

PCIE5_L2_RXP37

PCIE5_L2_TXN37

PCIE5_L2_TXP37

PCIE5_L3_RXN37

PCIE5_L3_RXP37

PCIE5_L3_TXN37

PCIE5_L3_TXP37

PCIE9_RXN73

PCIE9_RXP73

PCIE9_TXN73

LAN

PCIE9_TXP73

PCIE10_RXN66

PCIE10_RXP66

PCIE10_TXN66

PCIE10_TXP66

PCIE11_L0_SATA0_RXN96

PCIE11_L0_SATA0_RXP96

PCIE11_L0_SATA0_TXN96

PCIE11_L0_SATA0_TXP96

NC

PCIE13_L3_RXN64

PCIE13_L3_RXP64

PCIE13_L3_TXN64

PCIE13_L3_TXP64

PCIE13_L2_RXN64

PCIE13_L2_RXP64

PCIE13_L2_TXN64

PCIE13_L2_TXP64

PCIE13_L1_RXN64

PCIE13_L1_RXP64

PCIE13_L1_TXN64

PCIE13_L1_TXP64

PCIE13_L0_SATA1_RXN64

PCIE13_L0_SATA1_RXP64

PCIE13_L0_SATA1_TXN64

PCIE13_L0_SATA1_TXP64

PCIE5_L0_RXN

PCIE5_L0_RXP

PCIE5_L0_TXN

1 2

C1000 0.22U_6.3V_K_X5R_0201

PCIE5_L0_TXP

1 2

C1001 0.22U_6.3V_K_X5R_0201

PCIE5_L1_RXN

PCIE5_L1_RXP

PCIE5_L1_TXN

1 2

C1002 0.22U_6.3V_K_X5R_0201

PCIE5_L1_TXP

1 2

C1003 0.22U_6.3V_K_X5R_0201

PCIE5_L2_RXN

PCIE5_L2_RXP

PCIE5_L2_TXN PCIE5_L2_TXN_C

1 2

C1004 0.22U_6.3V_K_X5R_0201

PCIE5_L2_TXP

1 2

C1005 0.22U_6.3V_K_X5R_0201

PCIE5_L3_RXN

PCIE5_L3_RXP

PCIE5_L3_TXN PCIE5_L3_TXN_C

1 2

C1006 0.22U_6.3V_K_X5R_0201

1 2

C1007 0.22U_6.3V_K_X5R_0201

PCIE9_RXN

PCIE9_RXP

PCIE9_TXN

1 2

C1010 0.1U_10V_K_X5R_0201

PCIE9_TXP

1 2

C1011 0.1U_10V_K_X5R_0201

PCIE10_RXN

PCIE10_RXP

PCIE10_TXN

1 2

C1008 0.1U_10V_K_X5R_0201

PCIE10_TXP

1 2

C1009 0.1U_10V_K_X5R_0201

PCIE11_L0_SATA0_RXN

PCIE11_L0_SATA0_RXP

PCIE11_L0_SATA0_TXN

PCIE11_L0_SATA0_TXP

PCIE13_L3_RXN

PCIE13_L3_RXP

PCIE13_L3_TXN

PCIE13_L3_TXP

PCIE13_L2_RXN

PCIE13_L2_RXP

PCIE13_L2_TXN

PCIE13_L2_TXP

PCIE13_L1_RXN

PCIE13_L1_RXP

PCIE13_L1_TXN

PCIE13_L1_TXP

PCIE13_L0_SATA1_RXN

PCIE13_L0_SATA1_RXP

PCIE13_L0_SATA1_TXN

PCIE13_L0_SATA1_TXP

1 2

R1007 1/20W_100_1%_0201

PCIE5_L0_TXN_C

PCIE5_L0_TXP_C

PCIE5_L1_TXN_C

PCIE5_L1_TXP_C

PCIE5_L2_TXP_C

PCIE5_L3_TXP_CPCIE5_L3_TXP

PCIE9_TXN_C

PCIE9_TXP_C

PCIE10_TXN_C

PCIE10_TXP_C

USB3P2_RXN

USB3P2_RXP

USB3P2_TXN

USB3P2_TXP

USB3P3_RXN

USB3P3_RXP

USB3P3_TXN

USB3P3_TXP

USB3P4_RXN

USB3P4_RXP

USB3P4_TXN

USB3P4_TXP

USBC_USB2N

USBC_USB2P