Page 1

VMP2

Power PC-based CPU Board

for VME Applications

Manual ID: 24855, Rev. Index 02

November 2002

The product described in this manual is

in compliance with all applied CE standards.

Page 2

Preface VMP2

Revision History

Manual/Product Title: VMP2

Manual ID Number: 24855

Rev.

Index

01 Initial Issue 00 Oct. 02

02 Chapter 5 replaced (new bootstrap loader) 00 Nov. 02

Brief Description of Changes Board Index

Date of

Issue

Imprint

Copyright © 2002 PEP Modular Computers GmbH. All rights

reserved. This manual may not be copied, photocopied, reproduced, translated or converted to any electronic or machinereadable form in whole or in part without prior written approval of

PEP Modular Computers GmbH.

Disclaimer:

PEP Modular Computers GmbH rejects any liability for the cor-

rectnesss and completeness of this manual as well as its suitability for any particular purpose.

This manual was realized by: TPD/Engineering, PEP Modular Computers GmbH.

ID 24855, Rev. 02Page 0 - 2 © 2002 PEP Modular Computers GmbH

Page 3

VMP2 Preface

Table of Contents

Revision History .................................................................................................. 0 - 2

Imprint ................................................................................................................. 0 - 2

Table of Contents .................................................................................................0 - 3

List of Tables ........................................................................................................0 - 9

List of Figures ....................................................................................................0 - 11

Proprietary Note ........... ..................................................................................... 0 - 15

Trademarks ....................................................................................................... 0 - 15

Explanation of Symbols .................................................................................... 0 - 16

For Your Safety ................................................................................................. 0 - 17

Two Year Warranty ........................................................................................... 0 - 19

Chapter

1. Introduction ................................................................................................... 1 - 3

1.1 Board Introduction .................................................................................. 1 - 4

1.2 Board Overview ..................................................................................... 1 - 5

1.3 VMP2 Main Specifications ..................................................................... 1 - 6

1.4 Applied Standards .................................................................................. 1 - 8

1.4.1 CE Compliance ................................................................................ 1 - 8

1.4.2 Mechanical Compliance ................................................................... 1 - 8

1.4.3 Environmental Tests ........................................................................ 1 - 8

1.5 Related Publications .............................................................................. 1 - 8

1.5.1 VME Systems/Boards ...................................................................... 1 - 8

1.5.2 PMC Add-on Modules/Carriers ........................................................ 1 - 8

Chapter

1

2

2. Functional Description .................................................................................. 2 - 3

2.1 Functional Block Diagram ...................................................................... 2 - 3

2.2 Front Panels ........................................................................................... 2 - 4

2.3 Board Layout .......................................................................................... 2 - 5

2.4 Main Features ........................................................................................ 2 - 6

ID 24855, Rev. 02 Page 0 - 3© 2002 PEP Modular Computers GmbH

Page 4

Preface VMP2

2.4.1 CPU .................................................................................................. 2 - 6

2.4.1.1 MPC8245 (Kahlua II) Features ................................................... 2 - 6

2.4.2 Memory ............................................................................................. 2 - 8

2.4.2.1 System Memory (DRAM) ............................................................ 2 - 8

2.4.2.2 Flash ........................................................................................... 2 - 8

2.4.2.3 EEPROM .................................................................................... 2 - 8

2.4.2.4 Memory Expansion Socket (DIL600) .......................................... 2 - 8

2.5 Board Interfaces ..................................................................................... 2 - 9

2.5.1 VME Interface and Connector Pinout ............................................... 2 - 9

2.5.1.1 VME Bus Connector CON1 Pinout ........................................... 2 - 10

2.5.2 Ethernet Interface and Connector Pinout ....................................... 2 - 11

2.5.2.1 Ethernet Connector CON8 Pinout ............................................ 2 - 11

2.5.3 Serial Interfaces and ConnectorPinout ........................................... 2 - 12

2.5.3.1 Pinouts of Serial Ports (RJ45 Connectors) ............................... 2 - 12

2.5.4 PCI Expansion Interface and Connector Pinout ............................. 2 - 13

2.5.4.1 PCI Expansion Connector (CON11) Pinout .............................. 2 - 14

2.5.5 Serial Interface Expansion Connector and Pinout .......................... 2 - 16

2.5.5.1 Serial Interface Expansion Connector CON3 Pinout ................ 2 - 16

2.5.6 Memory Expansion Interface .......................................................... 2 - 16

2.5.7 DEBUG Interface and Connector Pinout ........................................ 2 - 17

2.5.7.1 Debug Connector CON10 Pinout ............................................. 2 - 17

2.5.8 Digital Temperature Sensor (LM75) ............................................... 2 - 17

2.6 Special Board Features ........................................................................ 2 - 18

2.6.1 Watchdog Timer ............................................................................. 2 - 18

2.6.2 RTC (STC M41T56) ....................................................................... 2 - 18

2.6.3 Reset/Abort .................................................................................... 2 - 18

2.6.4 Front Panel LED’s .......................................................................... 2 - 19

Chapter

3. Installation ..................................................................................................... 3 - 3

3.1 Board Installation .................................................................................... 3 - 3

3.1.1 Front Panel I/O Connectors .............................................................. 3 - 4

3

ID 24855, Rev. 02Page 0 - 4 © 2002 PEP Modular Computers GmbH

Page 5

VMP2 Preface

Chapter

4. Configuration ................................................................................................ 4 - 3

4.1 Jumper Settings ..................................................................................... 4 - 3

4.1.1 Bootstrap Loader / Socket Jumper J1 .............................................. 4 - 3

4.1.2 RTC (Real-time clock) Calibration Output (J2) ................................ 4 - 3

4.1.3 Resistor Setting for Non-standard Socket Devices .......................... 4 - 4

4.1.4 RS485 Termination (Onboard Interface Only) ................................. 4 - 4

4.2 Pinouts ................................................................................................... 4 - 5

4.2.1 Flash Socket Type Selection ........................................................... 4 - 5

4.2.1.1 Socket Device Selection (Memory Expansion Socket IC8) ........ 4 - 5

4.2.2 Serial Interface Expansion Connector (CON3) ................................ 4 - 6

4.3 Board Address Map ............................................................................... 4 - 7

4.3.1 Address Map Overview .................................................................... 4 - 7

4.3.2 VME Address Area .......................................................................... 4 - 8

4.3.3 Onboard Device Addresses ............................................................. 4 - 9

4

4.3.4 Special Registers Overview ........................................................... 4 - 10

4.3.4.1 Board Control Registers ........................................................... 4 - 10

4.3.4.2 Board ID Register ..................................................................... 4 - 10

4.3.4.3 Software Compatibility ID ......................................................... 4 - 11

4.3.4.4 Memory Configuration Register ............................................... 4 - 12

4.3.4.5 Flash Bank Select Register ...................................................... 4 - 12

4.3.4.6 Watchdog Control Register ...................................................... 4 - 13

4.3.4.7 Control Register ....................................................................... 4 - 14

4.3.4.8 Event Register .......................................................................... 4 - 15

4.3.4.9 Board / Logic Revision Register ............................................... 4 - 16

4.3.4.10 UART A / Registers ................................................................ 4 - 17

4.3.4.11 UART B / Registers ................................................................ 4 - 18

4.3.5 IRQ Routing ................................................................................... 4 - 19

4.3.6 Real-time Clock .............................................................................. 4 - 20

4.3.7 EEPROM ....................................................................................... 4 - 21

4.3.8 Digital Temperature Sensor ........................................................... 4 - 21

ID 24855, Rev. 02 Page 0 - 5© 2002 PEP Modular Computers GmbH

Page 6

Preface VMP2

Chapter

5. NetBootLoader .............................................................................................5 - 3

5.1 General Operation ...................................................................................5 - 3

5.2 NetBootLoader Interfaces ........................................................................5 - 3

5.2.1 ABT (Abort) Switch ..........................................................................5 - 4

5.2.2 TERM Serial Interface .....................................................................5 - 4

5.2.3 SER0 Serial Interface ......................................................................5 - 4

5.2.4 Ethernet Interface ............................................................................5 - 4

5.3 NetBootLoader Functions ........................................................................5 - 4

5.3.1 NetBootLoader Control ...................................................................5 - 5

5.3.2 System Status Monitoring ...............................................................5 - 5

5.3.3 ftp Server Access ............................................................................5 - 6

5.3.4 FLASH Operation ............................................................................5 - 6

5.3.5 Motorola S-Records ........................................................................5 - 6

5.4 Operating the NetBootLoader ..................................................................5 - 7

5

5.4.1 Initial Setup .....................................................................................5 - 7

5.4.2 Accessing the NetBootLoader .........................................................5 - 7

5.4.3 NetBootLoader Configuration ..........................................................5 - 8

5.4.3.1 BW ..............................................................................................5 - 8

5.4.3.2 NET .............................................................................................5 - 8

5.4.3.3 PASSWD .....................................................................................5 - 8

5.4.3.4 PF ...............................................................................................5 - 9

5.4.4 telnet Login ......................................................................................5 - 9

5.4.5 FLASH Operations ..........................................................................5 - 9

5.4.5.1 FLASH Offsets ............................................................................5 - 9

5.4.5.2 Programming an Application .....................................................5 - 10

5.4.5.3 ftp Server Access ......................................................................5 - 10

5.4.5.4 Motorola S-Records ..................................................................5 - 10

5.4.6 Updating the NetBootLoader .........................................................5 - 11

5.4.6.1 Updating With an Image Loaded Via an ftp Server ...................5 - 11

5.4.6.2 Updating Via a Separate DIL FLASH ........................................5 - 11

ID 24855, Rev. 02Page 0 - 6 © 2002 PEP Modular Computers GmbH

Page 7

VMP2 Preface

5.4.7 Uploading a FLASH Area .............................................................5 - 12

5.5 Plug and Play ........................................................................................5 - 12

5.6 Porting an Operating System to the CPU Board ...................................5 - 12

5.7 Commands ............................................................................................5 - 13

Annex

A. VMP1-IO1 Module (Optional) ....................................................................... A - 3

A.1 Overview ................................................................................................ A - 3

A.2 Board Interfaces ..................................................................................... A - 4

A.3 Board Layout .......................................................................................... A - 5

A.4 VMP1-IO1 Front Panel ........................................................................... A - 6

A.5 Technical Specifications ........................................................................ A - 7

A.6 Board Installation ................................................................................... A - 8

A.7 Pinouts ................................................................................................. A - 10

A.7.1 Jn1 (CON4) Pin Assignment .......................................................... A - 10

A.7.2 Jn2 (CON5) Pin Assignment .......................................................... A - 11

A.8 Jumper Setting ..................................................................................... A - 12

Annex

A

B

B. VMP1-Post (Optional) ................................................................................... B - 3

Annex

C. Optoisolation RS485 Module (Optional) ....................................................... C - 3

Annex

D. JTAG Subsystem .......................................................................................... D - 3

ID 24855, Rev. 02 Page 0 - 7© 2002 PEP Modular Computers GmbH

C

D

Page 8

Preface VMP2

Annex

E. CP320-TR1 (Optional) ................................................................................. E - 3

Annex

Annex

Annex

Annex

Annex

F. CP320-TR2 (Optional) ................................................................................. F - 3

Annex

G. PMC-HDD1 Module (Optional) ..................................................................... G - 3

E

E

E

E

E

F

G

ID 24855, Rev. 02Page 0 - 8 © 2002 PEP Modular Computers GmbH

Page 9

VMP2 Preface

List of Tables

1-1 VMP2 Main Specifications...........................................................................1 - 6

2-1 Pin Assignment J1/P1 VME Connector CON1..........................................2 - 10

2-2 Ethernet RJ45 Connector CON8 Pin Assignment..................................... 2 - 11

2-3 Serial Port Connectors CON6 and CON7 Pin Assignment .......................2 - 12

2-4 PCI Expansion Connector Pinout..............................................................2 - 14

2-5 Serial Interface Expansion Connector (CON3) Pinout...............................2 - 16

2-6 Debug Interface Connector (CON10) Pinout.............................................2 - 17

4-1 Bootstrap Loader / Socket Jumper J1 Settings...........................................4 - 3

4-2 Resistor Setting for Various Non-standard Socket Devices ........................4 - 4

4-3 Jumper Settings for RS485 Termination......................................................4 - 4

4-4 DIL 32 Pinout for Various Devices...............................................................4 - 5

4-5 RS Expansion Connector Pinout.................................................................4 - 6

4-6 Board Control Registers............................................................................4 - 10

4-7 Board ID Register......................................................................................4 - 10

4-8 Software Compatibility ID.......................................................................... 4 - 11

4-9 Memory Configuration Register.................................................................4 - 12

4-10 Flash Bank Select Register .......................................................................4 - 12

4-11 Watchdog Control Register........................................................................4 - 13

4-12 Control Register.........................................................................................4 - 14

4-13 Event Register...........................................................................................4 - 15

4-14 Board Logic / Revision Register ................................................................4 - 16

4-15 General Register Set (THR/RHR, IER/ISR, MCR/MSR, LCR/LSR, SPR).4 - 17

4-16 Baud Rate Register Set (DLL/DLM)..........................................................4 - 17

4-17 Enhanced Register Set..............................................................................4 - 17

4-18 General Register Set (THR/RHR, IER/ISR, MCR/MSR, LCR/LSR, SPR).4 - 18

4-19 Baud Rate Register Set (DLL/DLM)..........................................................4 - 18

4-20 Enhanced Register Set..............................................................................4 - 18

4-21 Serial IRQ’s................................................................................................4 - 19

4-22 Register Map RTC M41T56.......................................................................4 - 20

5-1 NetBootLoader Control Commands...........................................................5 - 5

5-2 System Status Monitoring Commands.......................................................5 - 5

5-3 ftp Server Commands................................................................................5 - 6

ID 24855, Rev. 02 Page 0 - 9© 2002 PEP Modular Computers GmbH

Page 10

Preface VMP2

5-4 FLASH Operation Commands....................................................................5 - 6

5-5 Motorola S-Records Commands................................................................5 - 6

A-1 VMP1-IO1 Specifications............................................................................A - 7

A-2 Jn1, 32-bit PCI ..........................................................................................A - 10

A-3 Jn2, 32-bit PCI ...........................................................................................A - 11

A-4 IO1 Jumper Settings for Different Module Positions.................................A - 12

E-1 Duplex Configuration...................................................................................E - 3

E-2 Serial Port Pinout........................................................................................E - 3

E-3 CP320-TR1 Jumper Settings......................................................................E - 4

F-1 Serial Port Pinout........................................................................................ F - 4

G-1 Pinout of the PMC Connectors....................................................................G - 4

G-2 IDE Hard Disk Drive Connector Pinout.......................................................G - 5

ID 24855, Rev. 02Page 0 - 10 © 2002 PEP Modular Computers GmbH

Page 11

VMP2 Preface

List of Figures

2-1 Functional Block Diagram............................................................................2 - 3

2-2 Front Panels................................................................................................2 - 4

2-3 VMP2 Board (Front View)............................................................................2 - 5

2-4 VMP2 Board (Reverse View).......................................................................2 - 5

2-5 VME Connector CON1................................................................................2 - 9

2-6 Ethernet Connector CON8 ........................................................................ 2 - 11

2-7 Serial Port Connectors CON6 and CON7 .................................................2 - 12

2-8 PCI Expansion Connector CON11.............................................................2 - 13

2-9 Memory Expansion Connector IC8............................................................2 - 16

2-10 DEBUG Connector CON10 .......................................................................2 - 17

4-1 VMP2 Address Map.....................................................................................4 - 7

4-2 VME Address Area .....................................................................................4 - 8

4-3 VMP2 Device Address Map.........................................................................4 - 9

A-1 Board Layout (Front View)...........................................................................A - 5

A-2 VMP1-IO1 Front Panel ................................................................................A - 6

A-3 Installation Diagrams...................................................................................A - 9

B-1 Plan and Profile Views of VMP1-Post Module.............................................B - 4

C-1 View of underside of RS485 Module ...........................................................C - 3

D-1 JT AG Chain Illustration................................................................................D - 3

D-2 Resistor Positions on Reverse of VMP2 Board ..........................................D - 4

E-1 View of Underside of the CP320-TR1 Module.............................................E - 3

F-1 View of Underside of CP320-TR2 Module...................................................F - 4

G-1 PMC-HDD1 Module with Hard Disk Drive Attached................................... G - 3

ID 24855, Rev. 02 Page 0 - 11© 2002 PEP Modular Computers GmbH

Page 12

Preface VMP2

This page was intentionally left blank.

ID 24855, Rev. 02Page 0 - 12 © 2002 PEP Modular Computers GmbH

Page 13

VMP2 Preface

Preface

ID 24855, Rev. 02 Page 0 - 13© 2002 PEP Modular Computers GmbH

Page 14

Preface VMP2

This page was intentionally left blank.

ID 24855, Rev. 02 Page 0 - 14© 2002 PEP Modular Computers GmbH

Page 15

VMP2 Preface

Proprietary Note

This document contains information proprietary to PEP Modular Computers. It may not be

copied or transmitted by any means, disclosed to others, or stored in any retrieval system or

media without the prior written consent of PEP Modular Computers GmbH or one of its authorized agents.

The information contained in this document is, to the best of our knowledge, entirely correct.

However, PEP Modular Computers cannot accept liability for any inaccuracies or the consequences thereof, or for any liability arising from the use or application of any circuit, product,

or example shown in this document.

PEP Modular Computers reserves the right to change, modify, or improve this document or

the product described herein, as seen fit by PEP Modular Computers without further notice.

Trademarks

PEP Modular Computers, the PEP logo and, if occurring in this manual, “CXM” are trade

marks owned by PEP Modular Computers GmbH, Kaufbeuren (Germany). In addition, this

document may include names, company logos and trademarks, which are registered trademarks and, therefore, proprietary to their respective owners.

ID 24855, Rev. 02 Page 0 - 15© 2002 PEP Modular Computers GmbH

Page 16

Preface VMP2

Explanation of Symbols

CE Conformity

This symbol indicates that the product described in this manual is in

compliance with all applied CE standards. Please refer also to the

section “Applied Standards” in this manual.

Caution, Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60V)

when touching products or parts of them. Failure to observe the precautions indicated and/or prescribed by the law may endanger your

life/health and/or result in damage to your material.

Please refer also to the section “High Voltage Safety Instructions” on

the following page.

Warning, ESD Sensitive Device!

This symbol and title inform that electronic boards and their components are sensitive to static electricity. Therefore, care must be taken

during all handling operations and inspections of this product, in

order to ensure product integrity at all times.

Please read also the section “Special Handling and Unpacking

Instructions” on the following page.

Warning!

This symbol and title emphasize points which, if not fully understood

and taken into consideration by the reader, may endanger your health

and/or result in damage to your material.

Note...

This symbol and title emphasize aspects the reader should read

through carefully for his or her own advantage.

PEP Advantage

This symbol and title emphasize advantages or positive aspects of a

product and/or procedure.

ID 24855, Rev. 02Page 0 - 16 © 2002 PEP Modular Computers GmbH

Page 17

VMP2 Preface

For Your Safety

Your new PEP product was developed and tested carefully to provide all features necessary

to ensure its compliance with electrical safety requirements. It was also designed for a long

fault-free life. However, the life expectancy of your product can be drastically reduced by

improper treatment during unpacking and installation. Therefore, in the interest of your own

safety and of the correct operation of your new PEP product, you are requested to conform

with the following guidelines.

High Voltage Safety Instructions

Warning!

All operations on this device must be carried out by sufficiently skilled

personnel only.

Caution, Electric Shock!

Before installing your new PEP product into a system always ensure

that your mains power is switched off. This applies also to the installation of piggybacks.

Serious electrical shock hazards can exist during all installation,

repair and maintenance operations with this product. Therefore,

always unplug the power cable and any other cables which provide

external voltages before performing work.

Special Handling and Unpacking Instructions

ESD Sensitive Device!

Electronic boards and their components are sensitive to static elec-

tricity. Therefore, care must be taken during all handling operations

and inspections of this product, in order to ensure product integrity at

all times.

• Do not handle this product out of its protective enclosure while it is not used for operational purposes unless it is otherwise protected.

• Whenever possible, unpack or pack this product only at EOS/ESD safe work stations.

Where a safe work station is not guarante ed, it is imp ortant for the user to be electrically

discharged before touching the product with his/her hands or tools. This is most easily

done by touching a metal part of your system housing.

• It is particularly important to observe standard anti-static precautions when changing

piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC

or memory back-up, ensure that the board is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the board.

ID 24855, Rev. 02 Page 0 - 17© 2002 PEP Modular Computers GmbH

Page 18

Preface VMP2

General Instructions on Usage

• In order to maintain PEP’s product warranty, this product must not b e altered or modified

in any way. Changes or modifications to the device, which are not explicitly approved by

PEP Modular Computers and described in this manual or received from PEP Technical

Support as a special handling instruction, will void your warranty.

• This device should only be installed in or connected to systems that fulfill all necessary

technical and specific environmental requirements. This applies also to the operational

temperature range of the specific board version, which must not be exceeded. If batteries are present their temperature restrictions must be taken into account.

• In performing all necessary installation and application operations, please follow only

the instructions supplied by the present manual.

• Keep all the original packaging material for future storage or warranty shipments. If it is

necessary to store or ship the board please re-pack it as nearly as possible in the manner in which it was delivered.

• Special care is necessary when handling or unpacking the product. Please, consult the

special handling and unpacking instruction on the previous page of this manual.

ID 24855, Rev. 02Page 0 - 18 © 2002 PEP Modular Computers GmbH

Page 19

VMP2 Preface

Two Year Warranty

PEP Modular Computers grants the original purchaser of PEP products a TWO YEAR LIMITED

HARDWARE

granted or implied by anyone on behalf of PEP are valid unless the consumer has the express

written consent of PEP Modular Computers.

PEP Modular Computers warrants their own products, excluding software, to be free from

manufacturing and material defects for a period of 24 consecutive months from the date of

purchase. This warranty is not transferable nor extendible to cover any other users or longterm storage of the product. It does not cover products which have been modified, altered or

repaired by any other party than PEP Modular Computers or their authorized agents. Further-

more, any product which has been, or is suspected of being damaged as a result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been

damaged as a result of excessive current/voltage or temperature, or which has had its serial

number(s), any other markings or parts thereof altered, defaced or removed will also be

excluded from this warranty.

If the customer’s eligibility for warranty has not been voided, in the event of any claim, he may

return the product at the earliest possible convenience to the original place of purchase,

together with a copy of the original document of purchase, a full description of the application

the product is used on and a description of the defect. Pack the product in such a way as to

ensure safe transportation (see our safety instructions).

WARRANTY as d escribed in the fo llowing. However, no other warranties that may be

PEP provides for repair or replacement of any part, assembly or sub-assembly at their own

discretion, or to refund the original cost of purchase, if appropriate. In the event of repair,

refunding or replacement of any part, the ownership of the removed or replaced parts reverts

to PEP Modular Computers, and the remaining part of the original guarantee, or any new

guarantee to cover the repaired or replaced items, will be transferred to cover the new or

repaired items. Any extensions to the original guarantee are considered gestures of goodwill,

and will be defined in the “Repair Report” issued by PEP with the repaired or replaced item.

PEP Modular Computers will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than the above specified repair, replacement or refunding. In particular, all claims for damage to any system or process in which the product was

employed, or any loss incurred as a result of the product not functioning at any given time, are

excluded. The extent of PEP Modular Computers liability to the customer shall not exceed the

original purchase price of the item for which the claim exists.

PEP Modular Computers issues no warranty or representation, either explicit or implicit, with

respect to its products’ reliability, fitness, quality, marketability or ability to fulfil any particular

application or purpose. As a result, the products are sold “as is,” and the responsibility to

ensure their suitability for any given task remains that of the purchaser. In no event will PEP

be liable for direct, indirect or consequential damages resulting from the use of our hardware

or software products, or documentation, even if PEP were advised of the possibility of such

claims prior to the purchase of the product or during any period since t he da te of its purchase.

Please remember that no PEP Modular Computers employee, dealer or agent is authorized to

make any modification or addition to the above specified terms, either verbally or in any other

form, written or electronically transmitted, without the company’s consent.

ID 24855, Rev. 02 Page 0 - 19© 2002 PEP Modular Computers GmbH

Page 20

Preface VMP2

This page was intentionally left blank.

ID 24855, Rev. 02 Page 0 - 20© 2002 PEP Modular Computers GmbH

Page 21

VMP2

Introduction

Introduction

Chapter

1

ID 24855, Rev. 02

Page 1 - 1© 2002 PEP Modular Computers GmbH

Page 22

VMP2 Introduction

This page was intentionally left blank.

ID 24855, Rev. 02Page 1 - 2 © 2002 PEP Modular Computers GmbH

Page 23

VMP2 Introduction

1. Introduction

The VMP2 is a comprehensive computing platform which brings togethor the latest

advances in computing technology in a board designed for maximum performance, flexibility and versatility within a rugged compact format.

The design centered on realizing a board which addresses the need for increased computing capacity while at the same time reducing the size and number of system components in order to reduce space requirement s and optimize power dissipation.

The VMP2 is based on the MPC8245, a highly integrated microprocessor containing a

PowerPC MPC603e core. This is the 330 MHz version with a Floating Point Unit (FPU).

One of the prime advantages of utilizing the established and proven MPC603e core is

the associated broad infrastructure of support that has built up around it . All of the noteworthy third-party software tool vendors provide tools for the MPC8245.

An important feature of the board is the integration of a PCI bus within a VME-CPU

board. This connects the MPC8245 with the Fast Ethernet controller and the Tundra

Universe II PCI/VME bridge and also to the onboard 100-pin PCI expansion connector,

enabling the connection of the full range of PCI peripherals.

The VMP2 employs an OS-independent boot loader that enables the loading of any

operating system. This boot loader makes an update of the Flash content s and automatically downloads from Flash to SDRAM before booting the OS. For performance reasons the OS is started from the SDRAM.

The power of the board is greatly enhanced by means of the PCI expansion connector

which makes it possible to cascade one or two additional IO1 modules onto the board

resulting in a total package of either 8HP or 12HP. Both IO1 modules may be used to

carry PMC modules. Given the wide range of PMC modules now available, this feature

affords the user a very wide range of options. Additionally, one can substitute a module

designed to provide an even greater range of PCI peripherals in place of either of the

IO1 modules. These features enable, for example, the connection of the widest range of

system I/O components such as various field busses, Fast Ethernet and Ultra 2 SCSI, to

name just a few . The complete range of expansion possibilities is thus mad e available to

the user by the VMP2.

ID 24855, Rev. 02 Page 1 - 3© 2002 PEP Modular Computers GmbH

Page 24

VMP2 Introduction

1.1 B oard Introduction

The VMP2 is a VME PowerPC-based single-board computer specifically designed for

use in highly integrated platforms with solid mechanical interfacing for a wide range of

industrial environment applications.

Some of the VMP2’s outstanding features are:

• PowerPC MPC8245 Kahlua II (603E core with an integrated FPU,

combined with PCI interface and memory controller)

• 16 kB data cache

• 16 kB instruction cache

• up to 256 MB SDRAM (132 MHz) with optional ECC support

• up to 8 MB onboard Flash

• Fast Ethernet interface

• two serial I/O’s (RS232 / ESD protected and EMI compliant)

• Memory Expansion Socket e.g. Flash memory (up to 144 MB) or SRAM

• onboard PCI bus with expansion connector

• four counter/timers

• programmable watchdog timer

• real-time clock

• double-width version for PCI expansion

• Tundra Universe II VME-to-PCI Bridge

• compliance with VITA VME-S pecification ANSI / IEEE STD1014-1987 / IEC 821 and 297

ID 24855, Rev. 02Page 1 - 4 © 2002 PEP Modular Computers GmbH

Page 25

VMP2 Introduction

1.2 Board Overview

The VMP2 is a 3U VME CPU board featuring a powerful CPU (number cruncher). The

design is based on the new highly integrated Motorola PowerPC processor MPC8245,

which integrates a PCI interface and several peripherals inside one Chip.

Four standard memory configurations (32 MB, 64 MB, 128 MB and 256 MB SDRAM)

are available. Flash memory for integrating the initial bootloader and ROMable operating systems are provided . Additionally, NV SRAM or a Disk-On-Chip (by M-Systems)

can be placed on a DIL socket for special purposes.

The board controls the VMEbus through the Tundra UNIVERSE II PCI-VME bridge

which is an industrial standard for connecting the PCI bus to the VME. Improved VMEbus master and VMEbus slave performance with an increase of FIFO depth and optimized DMA transfer are some of the outstanding features of this device.

The VMP2 is also able to communicate with the environment through a Fast Ethernet

interface and two serial interfaces at the front side of the board. One of the serial interfaces is a RS232 full modem interface while the other is a software-configurable

RS232/RS485 port. These UARTS support baud rates up to 1.5 Mbps and are software

compatible with the 16550 UART from National Semiconductor. They contain 128 Byte

Transmit FIFO and 128 Byte Receive FIFO for reducing the bandwidth requirement of

the CPU.

The Ethernet is realized with the Intel 82559 with full duplex support at both 10/100

Mbps possible. This Fast Ethernet controller with an integrated 10/100 Mbps physical

layer device is the foremost solution for PCI board LAN designs. It combines low power

consumption with a small package design which is ideal for power and space constrained environments.

Anticipating the VMP2's use in data critical applications, the memory data path contains

a selectable in-line ECC controller which can provide SDRAM single-bit error correct or

double-bit error detect.

For mass data transmission a dual channel DMA controller is provided. It can be

programmed directly or through the use of descriptor chains located in memory. Data

can thus be moved from PCI to memory or vice versa, memory to memory, or PCI to

PCI.

The MPC8245 supports processor control and visibility through the JTAG/COP

(common on-chip processor) interface that is available on the VMP2. Utilizing third party

tools, the developer can access and control the processor. It also has standard IEEE

1149.1a-1993 compliant boundary scan capability. The ECC data path has a mechanism to manually inject errors into memory for use with maintenance and diagnostic

utilities. Furthermore a watch point and capture register on the internal bus and a set of

address attributes on the external memory and PCI buses facilitate debugging analysis.

VME interface

In addition to the standard functionality required by a VME CPU, the VMEbus interface

(Tundra Universe 2) provides:

• automatic First-Slot detection

• integral FIFO buffers for multiple transactions in both directions

• programmable DMA controller with linked list support.

• Mailbox

ID 24855, Rev. 02 Page 1 - 5© 2002 PEP Modular Computers GmbH

Page 26

VMP2 Introduction

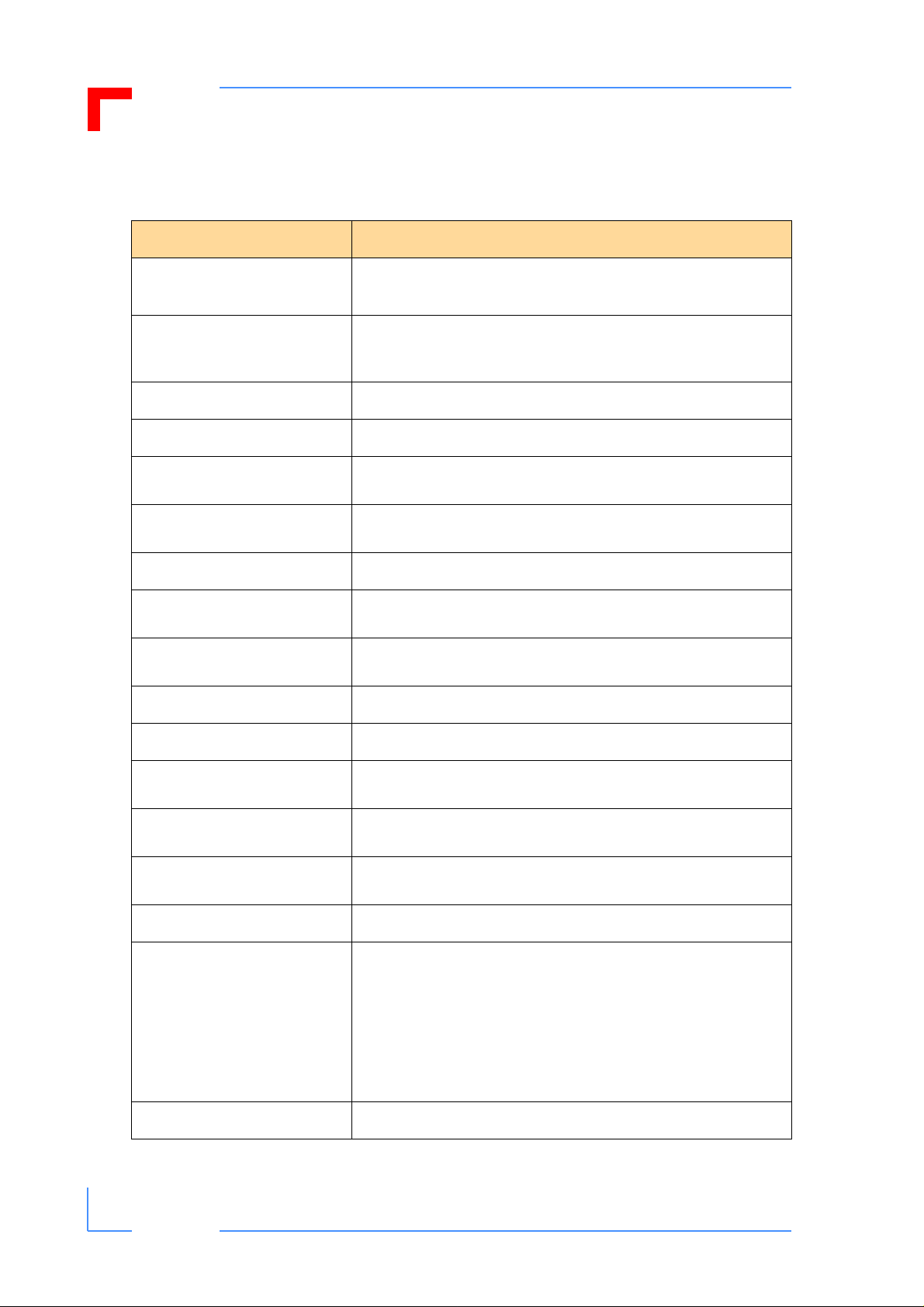

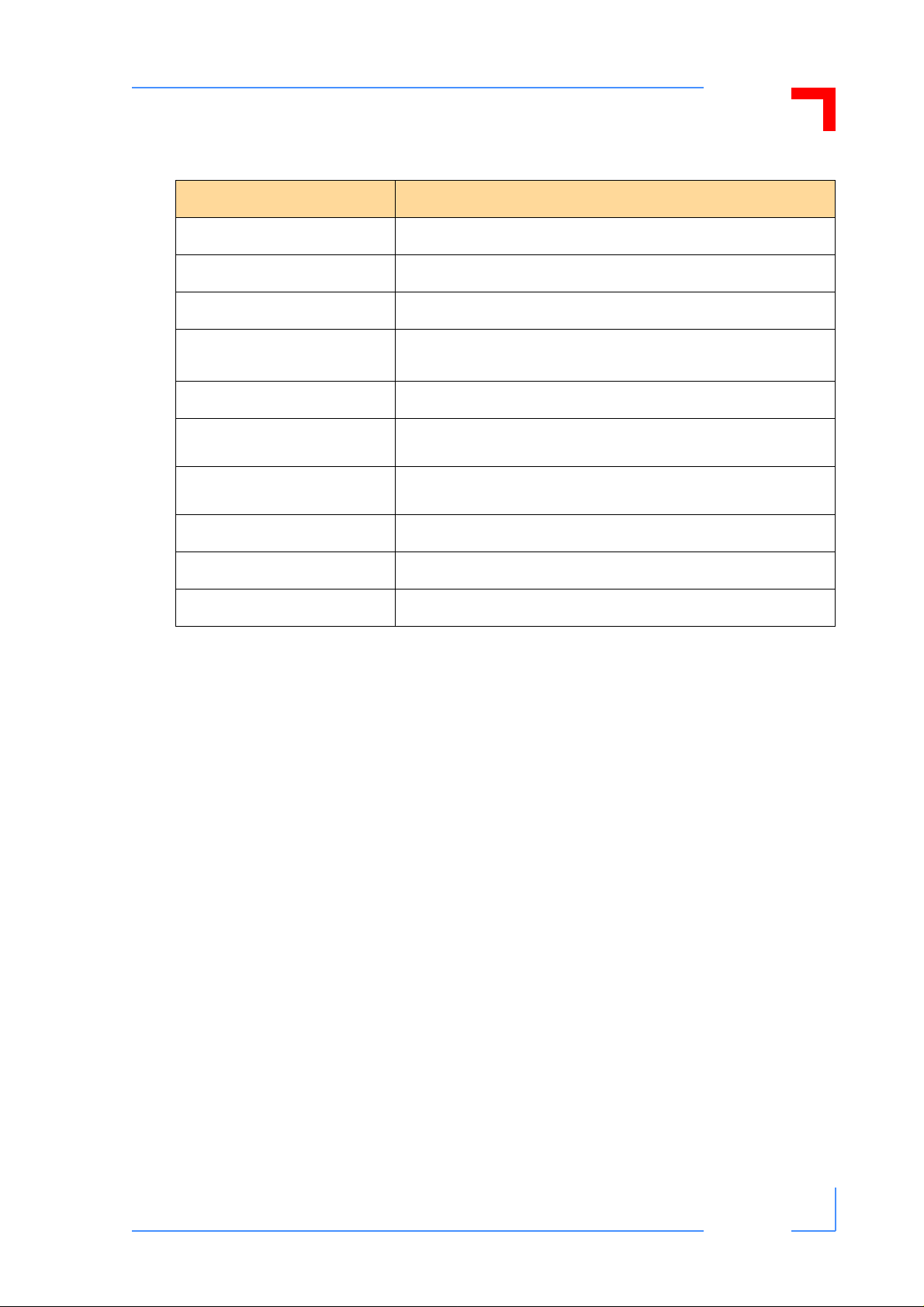

1.3 VMP2 Main Specifications

Table 1-1: VMP2 Main Specifications

VMP2 Specifications

Operating System

Support

VME Interface

Processor

Boot Device

Main Memory

Cache Structure

Flash

DIL600 Socket

PCI Expansion Connector

Ethernet

Initial boot loader with capability to load VxWorks and other

Real-time operating systems

ANSI/VITA 1-1994 for VME, approved April 10, 1995

Support for A24: D16/D8 master and A24: D16/D8 slave

interface

Motorola MPC8245, 330 MHz with integrated PCI interface

8 MB Flash for bootloader and ROMable OS/Socket

32 MB, 64 MB, 128 MB and 256 MB of onboard SDRAM with

ECC support available as standard

16K, 32 byte line, 4-way set associative instruction cache

16K, 32 byte line, 4-way set associative data cache

8 MB on-board Flash (soldered)

Socket for Flash extension by another 512 kB or addition of

Flash disk (M-System) with up to 144 MB

1 x Samtec SMT Board-to-Board connector 100-pin

order number: FLE - 15 - 01 - G - DV

10Base-T / 100Base-TX

SRAM

Serial Port

Watchdog

RTC

EEPROM

LED’s

Switches

256 or 512 kB NV SRAM on the DIL60 0 socket

16550 compatible Dual UART; 2 x RS-232 or

1 x RS232 + 1 x RS485

Watchdog generates Exception Condition / Reset or NMI

(software configurable)

backed up with GoldCap / Data retention for about 5 days /

backup battery possible

1 x 24LC16 for special purposes (8x256Byte)

6 LED’s:

red = general purpose

yellow = watchdog active

green = general purpose

green = Ethernet Link Integrity,

green = Ethernet Activity

green = Ethernet Speed

Two push-buttons (Reset and Abort)

ID 24855, Rev. 02Page 1 - 6 © 2002 PEP Modular Computers GmbH

Page 27

VMP2 Introduction

Table 1-1: VMP2 Main Specifications (Continued)

VMP2 Specifications

Debug Interface

VME Connector

Onboard Connectors

PCI Expansion Modules

Mechanical Conformance

Power Supply

Temperature Range

Humidity

Dimensions

Board Weight

JTAG/BDM

96-pin VME connector

2 x RJ45 for RS232, 1 x RJ45 for Ethernet

PMC carrier, future PCI based I/O board with

nd

VGA/SCSI/2

Conforms with IEEE 1101.10

5V in accordance with the VME Specification, 1.31 Amp

current (at 330 MHz)

–40°C to +85°C (operating)

–55°C to +125°C (storage)

0% to 95% non-condensing

100mm x 160mm single-height Eurocard

182 grams

Ethernet

ID 24855, Rev. 02 Page 1 - 7© 2002 PEP Modular Computers GmbH

Page 28

VMP2 Introduction

1.4 Applied Standards

1.4.1 CE Compliance

The PEP Modular Computers’ VME systems comply with the requirements of the following CE-relevant standards:

• Emission EN50081-1

• Immission EN50082-2

• Electrical Safety EN60950

1.4.2 Mechanical Compliance

• Mechanical Dimensions IEEE 1101.10

1.4.3 Environmental Tests

• Vibration IEC68-2-6

Random Vibration, Broadband IEC68-2-64 (3U boards)

• Permanent Shock IEC68-2-29

• Single Shock IEC68-2-27

1.5 R elated Publications

1.5.1 VME Systems/Boards

VME Specification, ANSI/VITA 1-1994 for VME, approved April 10, 1995

1.5.2 PMC Add-on Modules/Carriers

• Draft Standard for a Common Mezzanine Card Family, P1386/Draft 2.0

• Draft Standard Physical and Environment Layers for PCI Mezzanine Cards,

P1386.1/Draft 2.0

ID 24855, Rev. 02Page 1 - 8 © 2002 PEP Modular Computers GmbH

Page 29

VMP2

Functional Description

Functional Description

Chapter

2

ID 24855, Rev. 02

Page 2 - 1© 2002 PEP Modular Computers GmbH

Page 30

VMP2 Functional Description

This page was intentionally left blank.

ID 24855, Rev. 02Page 2 - 2 © 2002 PEP Modular Computers GmbH

Page 31

VMP2 Functional Description

2. Functional Description

2.1 Functional Block Diagram

Figure 2-1: Functional Block Diagram

PUSH

BUTTONS/

LED’S

SERIAL

INTERFACE

2 16550

compatible

SYSTEM

LOGIC

Serial IRQ

(Registry

Watchdog)

POWER

SUPPLY

2 DC/DC

RESET

GENERATION

FLASH

2 4MB

Port X (8 bit wide)

RTC

M41T56

FLASH

SOCKET

DIP600,

<52kB

CPU

Motorola

MPC 8245

200-332 MHz

Memory Bus

64-bit

SYSTEM

MEMORY

SDRAM

32 - 256 MB

DEBUG

JTAG/Test

interface

PCI

EXPANSION

CONNECTOR

EEPROM

I2C

FAST

ETHERNET

82559ER

PCI Bus

ID 24855, Rev. 02 Page 2 - 3© 2002 PEP Modular Computers GmbH

VME

INTERFACE

Tundra

Universe II

Page 32

VMP2 Functional Description

2.2 Front Panels

Figure 2-2: Front Panels

WUH WUH

ABRST

LNK.

SPEEDACT.

WUH

ABRST

LNK.

SPEEDACT.

VMP1VMP1

UH

W

VMP1-IO1

Standard VMP2 and

Standard with IO1 Module

KEY

LED colors

(for B&W monitors

and printouts):

U = green

W = yellow

H = red

ABRST

LNK.

VMP1

ABRST

VMP2 Optoisolated version

and Optoisolated version

with IO1 Module - note the

LNK.

SPEEDACT.

VMP1

SPEEDACT.

VMP1-IO1

different position of the

SER 0 connector

ID 24855, Rev. 02Page 2 - 4 © 2002 PEP Modular Computers GmbH

Page 33

VMP2 Functional Description

2.3 Board Layout

Figure 2-3: VMP2 Board (Front View)

1

LED

RJ45

GND

RTC

UART

X BUS

BUFFERS

ABORT

& RESET

(Serial)

RJ45

(Term.)

LOGIC

12

11

LED

ETHERNET

1

2

GOLDCAP

BATTERY

(Optional)

ETHERNET

216

CON10

115

JTAG

Figure 2-4: VMP2 Board (Reverse View)

SDRAM MEMORY

BANK 1

DC/DC DC/DC

CPU

1

2

CON11

PCI TO VME

PCI EXPANSION CONNECTOR

J1

BRIDGE

99

100

SDRAM MEMORY

BANK 2

R3

R8 R6R7

R11R12R13

MAGNIFIED

R3

R8 R6R7

R11R12R13

ID 24855, Rev. 02 Page 2 - 5© 2002 PEP Modular Computers GmbH

Page 34

VMP2 Functional Description

2.4 Main Features

The following descriptions provide an overview of the main features of the principa l functional blocks of the VMP2.

2.4.1 CPU

The VMP2 is based on the Motorola PowerPC processor MPC8245 which integrates a

large number of peripherals, such as a PCI interface, PCI arbiter, Interrupt Controller,

Memory Controller and multiple Timers. CPU speed is 330 MHz.

2.4.1.1 MPC8245 (Kahlua II) Features

Important features of the MPC8245 implemented on the VMP2 are as follows:

Peripheral logic

Memory interface

• Programmable timing supporting SDRAM (The VMP2 uses SDRAM at 132

MHz)

• High bandwidth bus (64-bit data bus) to SDRAM

• 2 memory banks with up to 128 MByte each

• Supports 64, 128 and 256 Mbit SDRAM

• Contiguous memory mapping

• 8-bit ROM interface

• Write buffering for PCI and processor accesses

• Supports ECC

• SDRAM data path buffer

• Low voltage transistor-to-transistor logic (LVTTL)

• Port X: 8-bit general-purpose I/O port using ROM controller

interface with address strobe

32-bit PCI interface operating up to 33 MHz on the VMP2

• PCI Specification Revision 2.1 compatible

• PCI 5.0-V tolerance

• Support for PCI-locked accesses to memory

• Support for accesses to all PCI address spaces

• Selectable big- or little-endian operation

• Store gathering of processor-to-PCI write and PCI-to-memory write accesses

• Memory prefetching of PCI read accesses

• Selectable hardware-enforced coherency

• PCI bus arbitration unit (five request/grant pairs)

ID 24855, Rev. 02Page 2 - 6 © 2002 PEP Modular Computers GmbH

Page 35

VMP2 Functional Description

PCI agent mode capability

• Address translation unit

• Internal configuration registers accessible from PCI

• Two-channel integrated DMA controller

• Supports direct mode or chaining mode (automatic linking of DMA transfers)

• Supports scatter gathering - read or write discontinuous memory

• Interrupt on completed segment, chain, and error

• Local-to-local memory

• PCI-to-PCI memory

• PCI-to-local memory

• Local-to-PCI memory

Message unit

• I2O message controller

• Two door-bell registers

• In-bound and out-bound messaging registers

I2C controller with full master/slave support

Embedded programmable interrupt controller (EPIC)

• Five hardware interrupts (IRQs) or 16 serial interrupts

• Four programmable timers

Integrated PCI bus and SDRAM clock generation

Programmable memory and PCI bus output drivers

Debug features

• Watchpoint monitor

• Address attribute and PCI attribute signals

• JTAG/COP - common onboard processor for in-circuit hardware debugging

• Performance monitor

603e core

High performance, superscalar 603e core

627 Dhrystone (2.1) MIPS

Integer unit (IU), floating point unit (FPU) (user enabled or disabled), load/store unit

(LSU), system register unit (SRU), and a branch processing unit (BPU)

16 kB instruction cache

16 kB data cache

Lockable L1 cache - entire cache or on a per-way basis

Dynamic power management

ID 24855, Rev. 02 Page 2 - 7© 2002 PEP Modular Computers GmbH

Page 36

VMP2 Functional Description

2.4.2 Memory

2.4.2.1 System Memory (DRAM)

The main memory of the VMP2 consists of SDRAM, ranging from 64 up to 256 MByte,

soldered onto the board for mechanical stability.

The VMP2 provides ECC support (optional) and a maximum memory speed of 132 MHz.

2.4.2.2 Flash

4 or 8 MB of soldered Flash memory accommodate the bootstrap loader software and

can be used to store ROMable operating systems or user data. This Flash memory is 8bit wide and windowed with window sizes of 512 kB.

2.4.2.3 EEPROM

A serial EEPROM is provided, organised into 8 blocks with 256 bytes per block

(24LC16). This EEPROM is connected to the I2C bus provided by the MPC8245.

2.4.2.4 Memory Expansion Socket (DIL600)

The VMP2 provides one 32-pin DIL socket on which to place SRAM, non-volatile SRAM

or other DIL600 devices on the board. Access to this Memory is controlled by the

onboard logic.

The following devices may be added to the VMP2 via the 32-pin DIL600 socket:

• Standard Flash memory of up to 512 kB, for example, the AMD29F010 and

AMD29F040

• The NV SRAM from Dallas Semiconductor. These devices are available in the

temperature range –40°C to +85°C for the industrial environment and guarantee

a minimum data retention of 10 years (e.g. DS1250Y-100).

• Disk-on-chip Flash memory. In order to achieve flexibility with low cost, the VMP2

Flash disk is not soldered but connected via a special module from M-Systems

(Disk-on-Chip 2000) which comes in the following sizes:

2 - 24 MB (dimensions 41.7 x 17.9 x 5.6mm);

4 - 144 MB (dimensions 42.0 x 18.3 x 11.8mm).

ID 24855, Rev. 02Page 2 - 8 © 2002 PEP Modular Computers GmbH

Page 37

VMP2 Functional Description

2.5 Board Interfaces

2.5.1 VME Interface and Connector Pinout

Figure 2-5: VME Connector CON1

The VME interface is based on the TUNDRA UNIVERSE II Bridge,

which includes the following features required for 3U VME systems:

• A24/A16 addressing modes capability

• D16/D8 data transfer capability

• Automatic First-Slot-Detection

• Single level BR3 arbitration release-when-done option

• FAIR VMEbus arbitration option

• ACFAIL NMI option

• SYSFAIL IRQ option

• System controller functions (SYSCLK, Bus monitor, Power monitor)

• Compatibility with PEP 3U VME system addressing schemes

• Compatibility with PEP VME backplane design and feature set

• Compatibility with PEP backplane transceiver logic

A table showing the pinout of the VME bus connector

appears on the following page.

PINROWS

ABC

1

32

ID 24855, Rev. 02 Page 2 - 9© 2002 PEP Modular Computers GmbH

Page 38

VMP2 Functional Description

2.5.1.1 VME Bus Connector CON1 Pinout

Table 2-1: Pin Assignment J1/P1 VME Connector CON1

Pin Number Pinrow A Pinrow B Pinrow C

1 D00 BBSY D08

2 D01 BCLR D09

3 D02 ACFAIL D10

4 D03 BG0IN D11

5 D04 BG0OUT D12

6 D05 BG1IN D13

7 D06 BG1OUT D14

8 D07 BG2IN D15

9 GND BG2OUT GND

10 SYSCLK BG3IN SYSFAIL

11 GND BG3OUT BERR

12 DS1 BR0 SYSRESET

13 DS0 BR1 LWORD

14 WRITE BR2 AM5

15 GND BR3 A23

16 DTACK AM0 A22

17 GND AM1 A21

18 AS AM2 A20

19 GND AM3 A19

20 IACK GND A18

21 IACKIN SERA A17

22 IACKOUT SERB A16

23 AM4 GND A15

24 A07 IRQ7 A14

25 A06 IRQ6 A13

26 A05 IRQ5 A12

27 A04 IRQ4 A11

28 A03 IRQ3 A10

29 A02 IRQ2 A09

30 A01 IRQ1 A08

31 -12V +5VSTDBY +12V

32 +5V +5V +5V

ID 24855, Rev. 02Page 2 - 10 © 2002 PEP Modular Computers GmbH

Page 39

VMP2 Functional Description

2.5.2 Ethernet Interface and Connector Pinout

Figure 2-6: Ethernet Connector CON8

The Ethernet interface is based on a PCI device

from Intel; the Ethernet Controller 82559ERS.

The main features of the Ethernet are as follows:

• integrated IEEE 802.3 10Base T and 100Base TX compatible PHY

• glueless 32-bit PCI master interface

• compatible with driver software of the 82558 and 82557

• full duplex support at both 10 and 100 Mbps

• IEEE 802.3u Auto-Negotiation support

• 4 kB transmit and 3 kB receive FIFO’s

2.5.2.1 Ethernet Connector CON8 Pinout

The connector used for the 100BaseTX Ethernet interface is an RJ45 connector.

The signals on this connector are as follows

Table 2-2: Ethernet RJ45 Connector CON8 Pin Assignment

Pin Number Signal

1TX+

1

8

2TX3RX+

4nc

5nc

6RX7nc

8nc

ID 24855, Rev. 02 Page 2 - 11© 2002 PEP Modular Computers GmbH

Page 40

VMP2 Functional Description

2.5.3 Serial Interfaces and ConnectorPinout

Figure 2-7: Serial Port Connectors CON6 and CON7

1

Two serial ports (RS-232) are provided by means of two 8pin RJ45 connectors.

8

The RS-232 serial interfaces named TERM and SER are 16C550 compliant and have

128-byte transmit and receive buffers. In addition to their other uses, the TERM port is

used to interface with the bootstrap loader and the SER port is used to download software.

Electrically, the two serial ports are identical and they provide a complete set of handshaking and modem control signals, maskable interrupt generation and data transfer of

up to 115.2 KBaud.

The upper serial interface (SER) can also be configured to act as an RS-485 interface.

The configuration of the interface is achieved by setting the RS_CTL bit in the Control

Register. Please refer to Table 4-14 in chapter 4.

Additionally, a module is available from PEP which provides an optoisolated half/full

duplex RS-485 interface. For this reason the onboard SER connector on the VMP2

baseboard is not equipped. Please contact PEP Support department for more information.

2.5.3.1 Pinouts of Serial Ports (RJ45 Connectors)

Table 2-3: Serial Port Connectors CON6 and CON7 Pin Assignment

RS485

Pin Number Signal

Signal Half-duplex Signal Full-duplex

1DSRNC-RxD

2 RTS NC NC

3 GND GND GND

4TXD+TRXD-TxD

5 RXD NC NC

6DCDNC+RxD

7CTS-TRXD+TxD

8 DTR NC NC

ID 24855, Rev. 02Page 2 - 12 © 2002 PEP Modular Computers GmbH

Page 41

VMP2 Functional Description

2.5.4 PCI Expansion Interface and Connector Pinout

Figure 2-8: PCI Expansion Connector CON11

1

PCI EXPANSION CONNECTORCON11

2

The PCI Expansion Connector provides the possibility to mount several transition

boards above the VMP2 for adding special functionality which is not provided on the

VMP2 main board or on the VME bus. All the PCI signals of the on board PCI bu s will be

routed to this connector, so that a complete PCI bus is provided on this connector. In

addition, almost the same number of ground and power pins (3.3V and 5V) as are on a

CPCI P1 or PMC connector are provided. Examples of transition boards are:

• PMC carrier

• PC-MIP carrier

• IO board with Graphic interface, second Ethernet interface, SCSI etc.

99

100

A table showing the pinout of the PCI Expansion Connector

appears on the following page.

ID 24855, Rev. 02 Page 2 - 13© 2002 PEP Modular Computers GmbH

Page 42

VMP2 Functional Description

2.5.4.1 PCI Expansion Connector (CON11) Pinout

Table 2-4: PCI Expansion Connector Pinout

Signal Pin Number Pin Number Signal

GND

1)

RST# 3 4

+3.3V

2)

CLK3 7 8

GND

1)

12SCL (I2C)

+3.3V

2)

56CLK2

GND

1)

910CLK4

INTB# 11 12 INTA#

INTD#1314INTC#

+5V

3)

GNT#3 17 18

+3.3V

2)

GND

1)

REQ#3 23 24

+5V

3)

15 16 GNT#2

+5V

3)

19 20 GNT#4

21 22 REQ#2

GND

25 26 REQ#4

1)

AD31 27 28 AD30

AD29 29 30

GND

1)

31 32 AD28

+5V

3)

AD27 33 34 AD26

AD25 35 36

+3.3V

2)

37 38 AD24

GND

1)

C/BE3# 39 40 SDA (I2C)

AD23 41 42

GND

1)

43 44 AD22

+3.3V

2)

AD21 45 46 AD20

AD19 47 48

+5V

3)

49 50 AD18

GND

1)

AD17 51 52 AD16

C/BE2# 53 54

GND

1)

55 56 FRAME#

IRDY# 57 58

+3.3V

2)

59 60 TRDY#

DEVSEL# 61 62

GND

1)

63 64 STOP#

LOCK# 65 66

+5V

3)

GND

GND

+3.3V

1)

1)

2)

Table continued on following page

ID 24855, Rev. 02Page 2 - 14 © 2002 PEP Modular Computers GmbH

Page 43

VMP2 Functional Description

Table 2-4: PCI Expansion Connector Pinout (Continued)

Signal Pin Number Pin Number Signal

PERR# 67 68

SERR# 69 70

+5V

3)

71 72 PAR

+5V

GND

3)

1)

C/BE1# 73 74 AD15

AD14 75 76

GND

1)

77 78 AD13

+3.3V

2)

AD127980AD11

AD10 81 82

GND

1)

83 84 AD9

GND

1)

AD8 85 86 C/BE0#

AD7 87 8 8

+3.3V

2)

89 90 AD6

+5V

3)

AD5 91 9 2 AD4

AD3 93 9 4

GND

1)

95 96 AD2

GND

1)

AD1 97 9 8 AD0

+12V

4)

99 100

-12V

5)

1) Ground

2) +3.3V

3) +5V

Key

4) +12V

5) -12V

ID 24855, Rev. 02 Page 2 - 15© 2002 PEP Modular Computers GmbH

Page 44

VMP2 Functional Description

2.5.5 Serial Interface Expansion Connector and Pinout

The serial interface expansion connector provides the capability to add different front

end interfaces to the UART B signals. For example, an opto-isolated RS422/485 module

(currently under development) may be plugged onto this connector.

2.5.5.1 Serial Interface Expansion Connector CON3 Pinout

Table 2-5: Serial Interface Expansion Connector (CON3) Pinout

Pin Number Function Function Pin Number

1GNDRTSB2

3REDE4

5RxDTxD6

7CTSDTR8

9SCLSDA10

11 +3.3V VCC 12

2.5.6 Memory Expansion Interface

Figure 2-9: Memory Expansion Connector IC8

A 32-pin DIL600 socket is provided in order to make possible the addition

of various memory expansion devices (with access time <120ns). The

devices which have been tested and approved for this connector are as follows:-

DIL type Flash memory (up to 512 kB)

DIL SRAM (up to 512 kB) e.g. Samsung KM684000BLP-7

NVSRAM (up to 512 kB) e.g. DALLAS DS1250Y-100)

Eprom (up to 512 kB) e.g. 27C040

M-Systems DiskOnChip 2000 (up to 288 MB)

Note:

For the pinout of this connector please see Chapter 4,

section 4.2.1

1

ID 24855, Rev. 02Page 2 - 16 © 2002 PEP Modular Computers GmbH

Page 45

VMP2 Functional Description

2.5.7 DEBUG Interface and Connector Pinout

Figure 2-10: DEBUG Connector CON10

A JTAG/BDM interface is provided on the VMP2 for software

debugging. The pinout of this connector is in accordance

with the pinout of the most commonly used emulator probes.

Note:

As shipped, only the Altera onboard logic may be detected by

means of the JTAG interface. If the JTAG interface requires to be

re-configured for software debugging, please contact Support at

PEP Modular Computers for assistance.

216

CON10

115

JT A G

2.5.7.1 Debug Connector CON10 Pinout

Table 2-6: Debug Interface Connector (CON10) Pinout

Signal Pin Number Pin Number Signal

TDO 1 2 NC

TDI 3 4 TRST#

NC 5 6 3.3V

TCK 7 8 NC

TMS 9 10 NC

SRESET# 11 12 NC

HRESET# 13 14 KEY (no pin)

CHKSTP#1516GND

2.5.8 Digital Temperature Sensor (LM75)

The VMP2 also provides an onboard digital temperature sensor with a thermal watchdog functionality (National Semiconductor LM75). This has various uses including, for

example, calibration of the onboard RTC over a wider temperature range.

ID 24855, Rev. 02 Page 2 - 17© 2002 PEP Modular Computers GmbH

Page 46

VMP2 Functional Description

2.6 Special Board Features

2.6.1 Watchdog Ti mer

A watchdog timer is available which (when enabled) on timeout forces either a nonmaskable interrupt (NMI) to be generated or causes a system reset to occur (refer to

chapter 4 for configuration details). It is also possible to generate , as a first step , an NMI

and then, as a second step, a system reset (in Cascade mode).The watchdog timing

has four possible settings: 0.5, 1.0, 1.5, and 2.0 seconds. After selecting the timeout

value and routing (NMI or reset) the watchdog can be enabled. Once enabled, the

watchdog must be continuously retriggered or a timeout will occur. When the watchdog

timer is enabled, it cannot be stopped or reprogrammed except by resetting the system.

The yellow watchdog LED (W) indicates the enabling status of the watchdog. Prior to

the watchdog being enabled it is off. After enabling it comes on and remains on until a

system reset occurs.

2.6.2 RTC (STC M41T56)

The Real Time Clock provides the following features:

• counters for seconds, minutes, hours, day, date, month and year.

• clock calibration by software

• low supply current for buffering with Gold Caps

• alternatively a battery may be placed on the board to buffer the RTC for a longer

time

• it is also possible to buffer the power supply for the RTC via the VME-5V-Standby

power line

• automatic leap year compensation

• precision: 35 ppm

• for greater precision or for temperature compensation the RTC can be adjusted in

in steps of +4.068 or –2.034 ppm

• for temperature compensation, the onboard temperature sensor (LM75) may be

used

2.6.3 Reset/Abort

There are also 2 push button switches with the function ABORT and RESET. The

RESET button reinitializes the board via hardware.

The ABORT button initiates the NMI. In addition it is latched into a bit in the System

Logic, the purpose of this is to differentiate between the NMI initiated from the ABORT

Button and the NMI initiated from the watchdog.

buttons on the Front Panel may be viewed in Figure 2-2.

The positions of the Abort and Reset

ID 24855, Rev. 02Page 2 - 18 © 2002 PEP Modular Computers GmbH

Page 47

VMP2 Functional Description

2.6.4 Front Panel LED’s

Three LED’s with the colors red, green and yellow are provided on the front panel

(please see Figure 2-2 on page 2-4) to give a quick indication of several key operating

conditions:

• The red LED (H) is general purpose.

• The yellow LED (W) indicates WATCHDOG ACTIVE

• The green LED (U) has been preset to light on initialisation of the board. After-

wards it is available for general purposes

The general purpose LED’s are programmable via a register in the System Logic.

3 additional LED’s, all green, are provided to indicate Ethernet working conditions:

• Ethernet Link Integrity

• Ethernet Activity

• Ethernet Speed

ID 24855, Rev. 02 Page 2 - 19© 2002 PEP Modular Computers GmbH

Page 48

VMP2 Functional Description

This page was intentionally left blank.

ID 24855, Rev. 02Page 2 - 20 © 2002 PEP Modular Computers GmbH

Page 49

VMP2

Installation

Installation

Chapter

3

ID 24855, Rev. 02

Page 3 - 1© 2002 PEP Modular Computers GmbH

Page 50

VMP2 Installation

This page was intentionally left blank.

ID 24855, Rev. 02Page 3 - 2 © 2002 PEP Modular Computers GmbH

Page 51

VMP2 Installation

3. Installation

The VMP2 has been designed for easy installation. However, the following importantstandard precautions must be observed. Some other important information is also set

out below.

3.1 Board Installation

Slot Selection

The VMP2 is designed so that it may be used in any free slot of a 3U VME Backplane.

It has an automatic first slot detection mechanism which configures it as a System Controller when placed in the far left slot.

When configured as the System Controller, it enables its system clock and arbiter in

order to control the entire VME bus.

Default setting of the serial Interfaces: 9600 Baud, 8N1

On initial startup a message of greeting comes up.

When the VMP2 is invoked for the first time, a Bootstrap loader startup messag e comes

up on the “term” serial port, which will provide you with some configuration information

on the system and a command prompt for entering bootstrap loader commands. For a

detailed description of these commands please see chapter 5 Bootstrap loader.

Caution!

Please switch off the VME system before installing the board in a

free slot. Failure to do so could endanger your life/health and may

damage your board or system.

Note:

Certain VME boards require bus master capability. If you are in

doubt whether such features are required for the board you intend

to install, please check your specific board and/or system documentation to make sure your system is provided with an appropriate free slot to insert the board.

ID 24855, Rev. 02 Page 3 - 3© 2002 PEP Modular Computers GmbH

Page 52

VMP2 Installation

ESD Equipment!

Your VMP2 board contains electrostatically sensitive devices.

Please observe the necessary precautions to avoid damage to

your board:

• Discharge your clothing before touching the assembly. Tools

must be discharged before use.

• Do not touch components, connector-pins or traces.

• If working at an anti-static workbench with professional discharging equipment, please do not omit to use it.

PEP Advantage

The VMP2 is designed to be bootstrapped from the Flash device

alone.

3.1.1 Front Panel I/O Connectors

Attention!

!

Due care should be exercised when connecting cabling in order to

avoid damage to your connected device and/or the VMP2 board.

For pinouts of the Front Panel connectors, please see Chapter 2:

Functional Description, sections 2.4.3.2 and 2.4.3.3

ID 24855, Rev. 02Page 3 - 4 © 2002 PEP Modular Computers GmbH

Page 53

VMP2

Configuration

Configuration

Chapter

4

ID 24855, Rev. 02

Page 4 - 1© 2002 PEP Modular Computers GmbH

Page 54

VMP2 Configuration

This page was intentionally left blank.

ID 24855, Rev. 02Page 4 - 2 © 2002 PEP Modular Computers GmbH

Page 55

VMP2 Configuration

4. Configuration

4.1 Jumper Settings

Please see Figures 2-3 and 2-4 in Chapter 2 to view the positions of the jumpers and

resistors on the board.

4.1.1 Bootstrap Loader / Socket Jumper J1

The Jumper J1 is used to select the memory position from which the VMP2 fetches its

boot code. It determines the address position of the onboard Flash window and the

Flash/SRAM expansion socket (DIL600, 32-pin).

Table 4-1: Bootstrap Loader / Socket Jumper J1 Settings

J1 Meaning Address Assignment

VMP2 fetches

Open

Closed

Note: The MPC8245 initially fetches its boot code from address 0xFFF0 0100!

boot code from

onboard Flash

VMP2 fetches

boot code from

socket

Socket: 0xFFF8 0000 - 0xFFFF FFFF

Onboard Flash window: 0xFFF0 0000 - 0xFFF7 FFFF

Socket: 0xFFF0 0000 - 0xFFF7 FFFF

Onboard Flash window: 0xFFF8 0000 - 0xFFFF FFFF

4.1.2 RTC (Real-time clock) Calibration Output (J2)

Frequency test output is used for calibration of the onboard RTC. The RTC provides a

512 Hz frequency test signal for calibration purposes. Please refer to the datasheet of

the ST M41T56 for detailed information (for position of J2 on the board please see figure

2-3).

Warning!

!

J2 must not be bridged.

ID 24855, Rev. 02 Page 4 - 3© 2002 PEP Modular Computers GmbH

Page 56

VMP2 Configuration

4.1.3 Resistor Setting for Non-standard Socket Devices

The default pinout of this socket is designed for use with standard DIL Flashes and MSystems DiskOnChip. As some devices have a different pinout, resistors must be set

accordingly (please see figure 2-4 for an illustration of these resistors on the board)

Table 4-2: Resistor Setting for Various Non-standard Socket Devices

Used Socket Devices R3 R6 R7 R8 R11 R12 R13

Flash (default) Open Open Open Set Set Open Set

DiskOnChip (default) Open Open Open Set Set Open Set

NVSRAM Open Open Set Open Set Set Open

4 Mbit EPROM Set Set Open Open Open Open Set

Note: All resistors are 0 ohm

4.1.4 RS485 Termination (Onboard Interface Only)

When the VMP2 is using the onboard RS485 interface and is the last on the RS485 bus,

then the RS485 interface must provide termination resistance. The purpose of J3 is to

enable this line termination resistor (130 R).

Table 4-3: Jumper Settings for RS485 Termination

Termination J3

ON Set

OFF Open

Additionally, the correct idle line potential must be provided at one location within the

RS485 bus. J4 and J5 are used for this purpose. Pullup/Pulldown resistors are 380 Ohm

each.

Note:

Ensure that the reference potential for the RS485 signals are set

in one location only on the bus.

ID 24855, Rev. 02Page 4 - 4 © 2002 PEP Modular Computers GmbH

Page 57

VMP2 Configuration

4.2 Pinouts

4.2.1 Flash Socket Type Selection

4.2.1.1 Socket Device Selection (Memory Expansion Socket IC8)

A range of different memory devices may be used on the DIL32 socket (e.g. Flashes,

NVSRAM, M-Systems Disk-On-Chip, EPROM etc.).

Table 4-4: DIL 32 Pinout for Various Devices

Pin

10

11

12

13

4Mbit

Flash

1 A18 NC A18 VPP VCC VCC VCC VCC 32

2

3

4

5

6

7

8

9

A16 NC A16 A16 A18 A15 WE_ WE 31

A15 NC A14 A15 A17 A17 NC A17 30

A12 A12 A12 A12 A14 WE NC A14 29

A7 A7 A7 A7 A13 A13 NC A13 28

A6 A6 A6 A6 A8 A8 A8 A8 27

A5 A5 A5 A5 A9 A9 A9 A9 26

A4 A4 A4 A4 A11 A11 A11 A11 25

A3 A3 A3 A3 OE_ OE_ OE_ OE_ 24

A2 A2 A2 A2 A10 A10 A10 A10 23

A1 A1 A1 A1 CE_ CE_ CE_ CE_ 22

A0 A0 A0 A0 D7 D7 D7 D7 21

D0 D0 D0 D0 D6 D6 D6 D6 20

Disk

OnChipNVSRAM

4Mbit

Eprom

4Mbit

EpromNVSRAM

Disk

OnChip

4Mbit

Flash

Pin

14

15

16

ID 24855, Rev. 02 Page 4 - 5© 2002 PEP Modular Computers GmbH

D1 D1 D1 D1 D5 D5 D5 D5 19

D2 D2 D2 D2 D4 D4 D4 D4 18

GND GND GND GND D3 D3 D3 D3 17

Page 58

VMP2 Configuration

4.2.2 Serial Interface Expansion Connector (CON3)

Table 4-5: RS Expansion Connector Pinout

Pin Number Function Function Pin Number

1GNDRTSB2

3REDE4

5RxDTxD6

7CTSDTR8

9SCLSDA10

11 +3.3V VCC 12

ID 24855, Rev. 02Page 4 - 6 © 2002 PEP Modular Computers GmbH

Page 59

VMP2 Configuration

4.3 Board Address Map

4.3.1 Address Map Overview

The following figures illustrate the address mapping of the VMP2. Where the first figure

describes the overall map, the second figure provides a more detailed map of the uppermost address area. The upper area address map depends on the configuration of the

VMP2 memory expansion sockets and the requirements of the application.

Figure 4-1: VMP2 Address Map

BANK 0 BANK 0 0xFFFF FFFF

0xFFF0 0100

Reset Entry J1 IN J1 OUT

0x8000 0000

0xFFE0 0000VMP2 UPPER AREA

Reserved

0xFF00 0000

PCI Interrupt Ack 0xFEF0 0000

Configuration DATA 0xFEE0 0000

Configuration Address

0xFEC0 00000xFEC0 0000

PCI

Reserved

0x7C00 0000

Reserved

0x4000 0000

0x0000 0000

ID 24855, Rev. 02 Page 4 - 7© 2002 PEP Modular Computers GmbH

DRAM

Page 60

VMP2 Configuration

4.3.2 VME Address Area

Figure 4-2: VME Address Area

0x8FFF FFFF

currently unused

0x8800 0000

VME A24/D16

0x8700 0000

currently unused

0x8501 0000

VME A16/D16

0x8500 0000

currently unused

0x8400 0000

VME USER2

0x8300 0000

VME USER1

0x8200 0000

currently unused

0x8000 0000