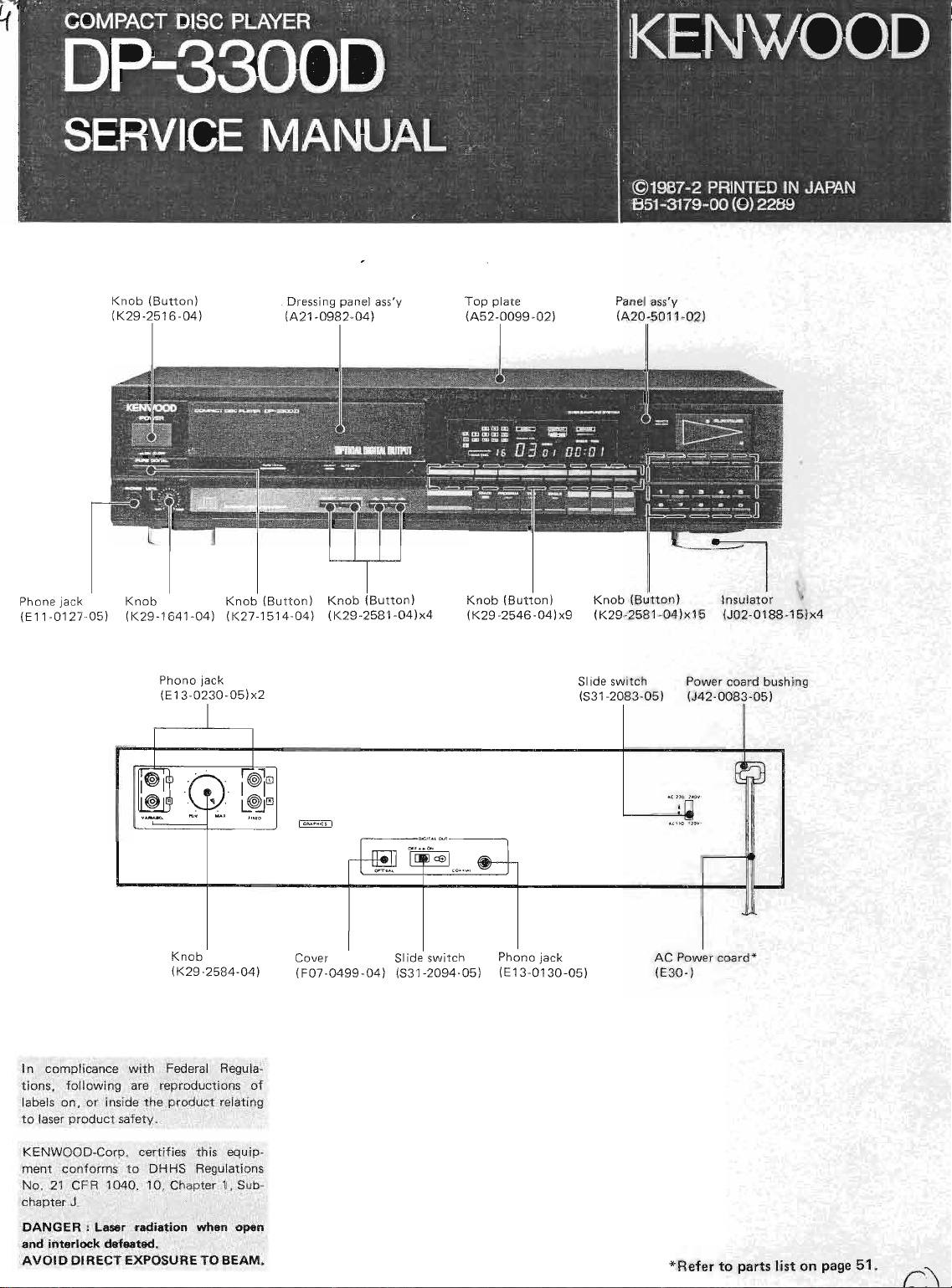

Page 1

Knob

(

K29

(Button)

-251

6

-04)

plate

Top

(A52-0099-02)

Panel

ass'y

{A20-501

1-021

jack

Phone

(E11-0127-05)

complicance

In

tions, f ollowing are

labels on, or inside

product

to laser

Knob

(K29-1641-04) (K27-1514-O4l

with

safety.

jack

Phono

(E

1 3-023O-05)x2

Knob

lK29-2584-o4l

Federal

reproductions

product

the

Knob

Begula-

of

relating

{Button)

Knob

lK29-25a1-O4lx4

Cover Slide

(

F07-0499

(Button)

-04)

(S31

(Buttonl

Knob

(K29-2546-04)x9 (K29-2581-04)x15

jack

switch

-2094-05)

Phono

(E

13-0130-05)

Knob

switch Power

Slide

(s31-2083-05) (J42-0083-051

(Button)

AC

{E30- }

Power

latJr

lnsu

(J02-01

88

coard bushing

coard*

-1

\

5lx4

K€NWOOD-Corp. certifies this eguin.

ment conforms to DHHS Regulations

No.

21 CFB

chapter

DANGER

and int€rlock

AVOID DIRECT

J.

1040.

10,

:

r8diltion when opon

Lasor

dofeatsd.

EXPOSURE

Chapter

1,

Sub-

TO BEAM,

*Refer

to

parts

list

on

Page

51

.

Page 2

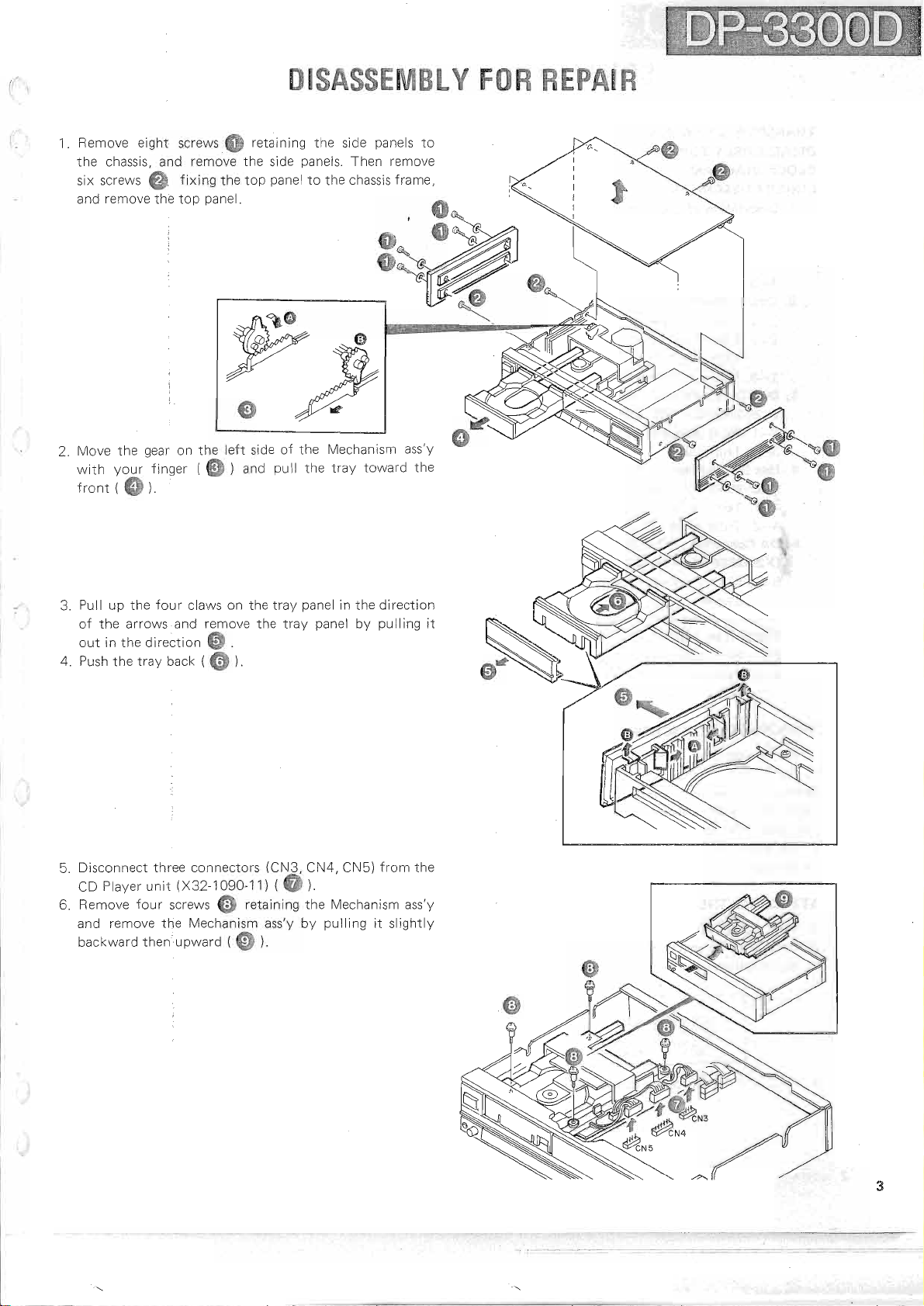

DISASSEMBLY FOR

HEPAIR

Remove

1.

the chassis, and

six screws

and remove the top

Move

2.

with

tront

eight

the

your

(

@

@

gear

finger

).

screws

remove

tixing

panel.

on the

(

@

db

retaining

the side

the top

left side

and

)

the side

panels.

panel

to the

of

the Mechanism

the tray

Putt

panels

to

remove

Then

chassis frame,

ass'y

toward

the

\a@

@

Pull up the

of the arrows and remove the tray

in

ouT

Push

4.

Disconnect three

5.

plaver

CD

Remove

and remove the

backward

four

ciirection @ .

the

tray back

the

unit

four

thenrupward

claws on the tray

(

)

G!

connectors

(X32-1090-11)

screws

Mechanism

@

(

GF

retaining

ass'y by

).

(CN3,

(G

panel

in the

panel

by

CN4, CN5)

).

Mechanism ass'y

the

pulling

direction

pulling

from

it slightly

it

the

Page 3

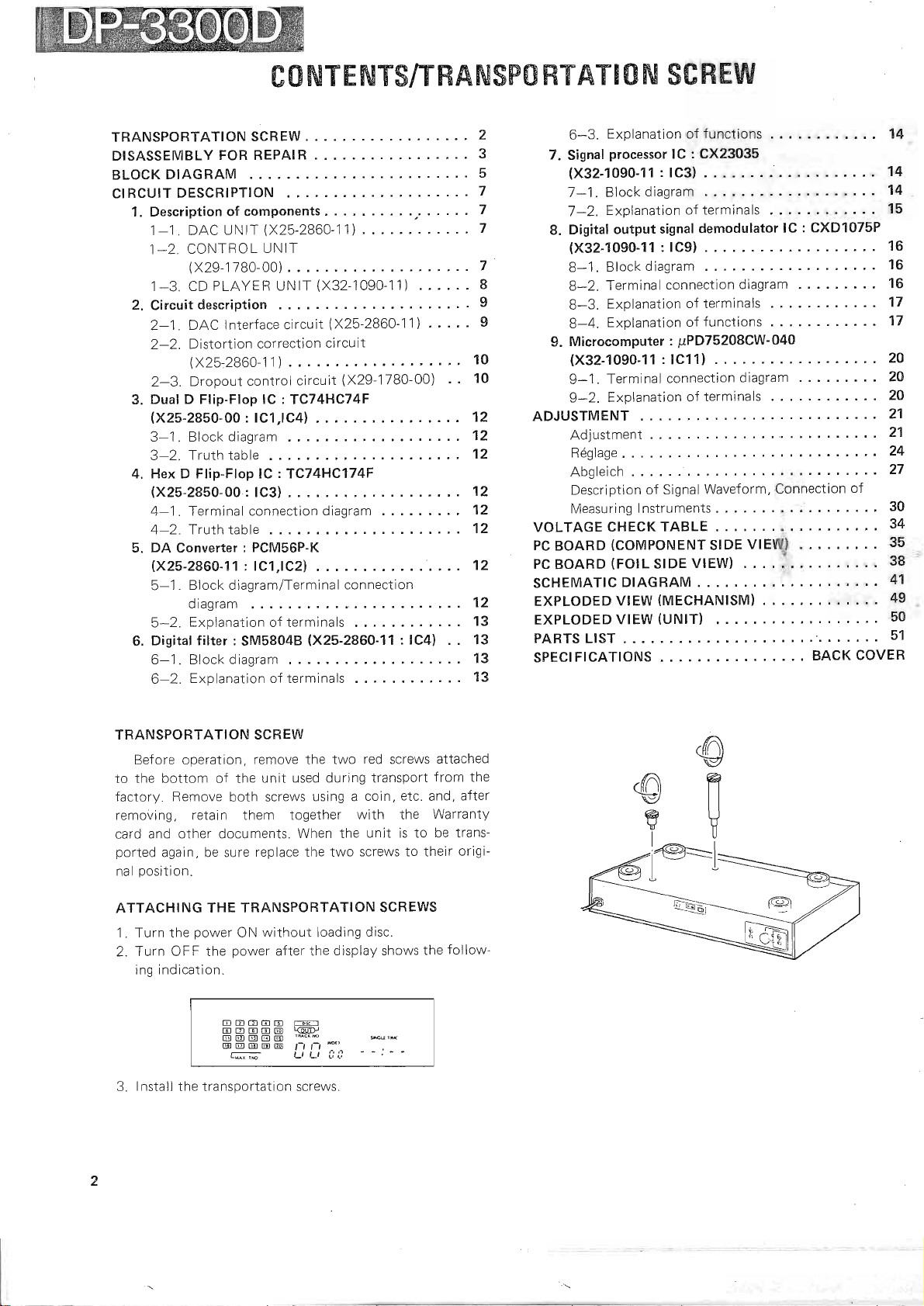

NTENTS/THANSPO

CO

RTATI

O

N

SCREW

TRANSPORTATION

DISASSEMBLY

BLOCK

CIRCUIT

DIAGRAM

DESCRIPTION

1. Description

1-1 . DAC UN

CONTROL

1_2.

(x29-1780-00).

1-3. CD

2, Circuit

2-1. DAC

2-2.

Dual D Flip-Ffop lC : TC74HC74F

(X25-2850-00

3-1 .

3-2. Truth table .

4.

4-1 . Terminal

4-2. Truth

5.

description

Distortion

lx25=2860-11)....

Dropout

2-3.

Block diagram

Hex D Flip-Flop lC : TC74HC174F

(X25-2850-00

DA

Converter

(X25-2860-1

5-1 . Block

li^^-^u tout dI l

ExJtanation

S-2.

Digitalfifter:

Block diagram

6-1 .

Explanation of termlnals

6-2.

SCREW

FOR REPAIR

of components

(X25-2860-1

rT

UNIT

PLAYER UNIT

lnterface

table .

1 z lCl,lC2l

diagram/Terminal connection

circuit

correction

control

:

lCl,lC4)

: lC3)

connection diagram

PCM56P-K

:

of terminals

SM58O4B

. .

.

1) . . .

. ..

(X32-1090-11)

(X25-286O-11)

circuit

(X29-1780-00)

circuit

(X25-2860-11

.....

. . .

: lC4)

. .

. .

.

2

3

5

7

7

7

7

8

9

9

10

10

12

12

12

12

12

12

12

12

13

13

13

13

Explanationof

6-3.

7.

8.

processor

Signal

(X32-1090-11

7-1. Block

7-2.

Digital

diagram

Explanation

output

(X32-1090-11

diagram

Block

B-1 .

Terminal

B-2.

Explanation

8-3.

Explanation

8-4.

Microcomputer

9.

(X32-1090'11

Terminal

9-1 .

Explanation

9-2.

ADJUSTMENT

Adjustment

Q6nlrna

I rEgrqgs

Abgleich

Description

Measuring

VOLTAGECHECKTABLE

Pc

BoARD

...

of Signal

Instruments

(CoMPONENT

pcBoARD(FO|LSIDEVIEW)

SCHEMATIC

EXPLODEDVIEW(MECHANISM)

EXPLODEDVIEW(UNIT)

PARTS LIST .

SPECIFICATIONS

DIAGRAM

functions

: GX23035

lG

:lC3).

of terminals

demodulator

signal

: lC9) .

connection

of terminals

of

:

PPD75208CW-040

: lCl1)

connection

of terminals

diagram

functions . .

diagram

Waveform,

vtEvQ

slDE

.....

....

.

: CXDl075P

lC

.

.

. .

Connection

...... 14

...20

of

...

. . . .

....

...49

COVER

BACK

14

14

15

16

16

16

17

17

20

20

21

21

24

27

30

34

1?

38

41

50

51

-

TRANSPOBTATION SCREW

Before

to the

factory. Remove both

removing,

card and other

ported

nal

ATTACHING

Turn the

1.

Turn OFF the

2.

3.

operation,

bottom of the

retain

again, be

position.

THE TRANSPORTATION

power

inq indication.

Install the transportation screws.

remove the two

unit used

screws

together

them

documents.

replace the

sure

without loading

ON

power

after

E] E] E] E] tr)

I!]E)EElE)

u@gE@

EgUE@

@

t@r

L, L, i.[]

When the

,-l l-t

red

screws

during transport

using a

the display

coin, etc. and,

with the

unit is to be trans-

two screws

SCREWS

disc.

shows the

*'

attached

from

Warranty

to their

follow-

the

after

origi-

Page 4

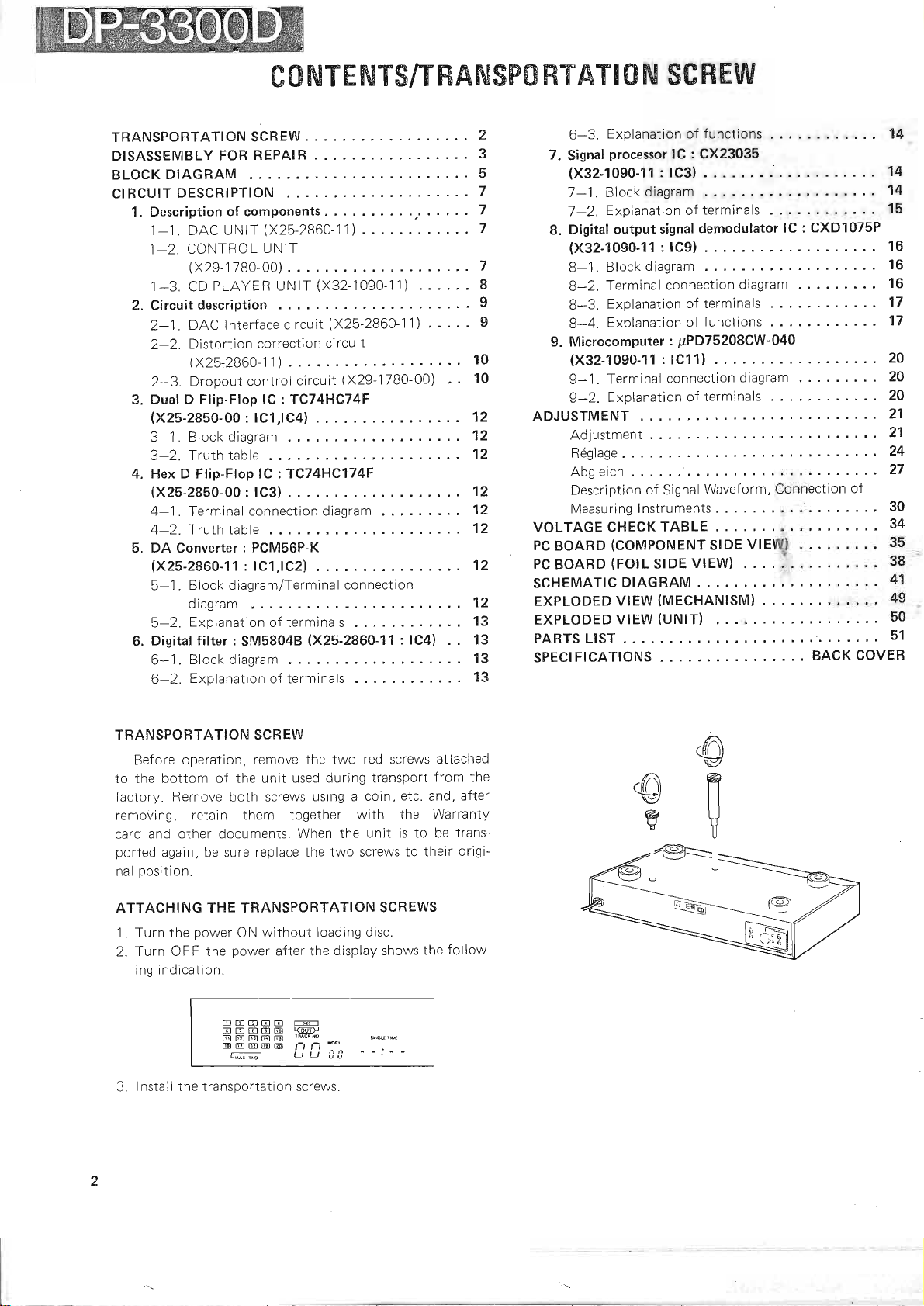

NTE NTS/THAI\ISPO

CO

RTATI

O

N

SCREW

TRANSPORTATION

DISASSEMBLY

BLOCK

CIBCUIT

DIAGRAM

DESCRIPTION

1. Description

DAC UN|T

1-1.

CONTROL

1_2.

(x29-1780-00).

'r-3.

cD

2.

Circuit

2-1. DAC

2-2.

Dual D Ff ip-Flop lC : TC74HC74F

3.

(X25-2850-00

3-1 . Block

3-2. Truth table .

4.

4-'l . Terminal connection

4-2.

5.

description

Dislort"ion

(x25,2860-1

Dropout

2-3.

Hex D Flip-Flop lC :

(X25-2850-00

Truth table .

DA

Converter

(X25-286O-11

5-1 . Block

di^^-^ulqqldlll

ExJlanation

5-2.

Digitalfifter :

6-1 . Block

Explanation of terminals

6-2.

SCREW

FOB REPAIR

of components

(X25-2860-11)

UNIT

PLAYER UNIT

lnterface

diagram

diagram/Terminal connection

diagram

circuit

correction

1 ) . .

control

: lCl,lC4)

TC74HC174F

: lC3)

r PCM56P-K

:

lCl,lC2)

of termrnats

SM58O4B

. .

....

. ..

(X32-1090-11)

(X25-2860-11)

ci rcuit

. .

(X29-1780-00)

circuit

diagram

(X25-2860-11

.....

' . . .

: lC4)

. .

.

.

2

3

5

7

7

7

7

I

9

9

10

10

12

12

12

12

12

12

12

12

13

13

13

13

Explanationof

6-3.

7.

8.

processor

Signal

(X32-1090-11

7-1. Block

7-2.

Digital

diagram

Exolanation

output

(X32-1090-11

diagram

Block

B-1 .

Terminal

B-2.

Explanation

8-3.

Explanation

8-4.

Microcomputer

9.

(X32-1090.11

Terminal

9-1 .

Explanation

9-2.

ADJUSTMENT

Adjustment

P6nlano

I rE9rqgs

Abgleich

Description

Measuringlnstruments

VOLTAGECHECKTABLE

Pc

BOABD

...

of Signal

(coMPoNENr

pcBoARD(FO|LSIDEVIEW)

SCHEMATIC

EXPLODEDVIEW(MECHANISM)

EXPLODEDVIEW(UNIT)

PARTS LIST .

SPECIFICATIONS

DIAGRAM

functions

: CX23035

lC

:lC3).

of terminals

demodulator

signal

: lC9) .

connection

of terminals

of

:

PPD75208CW-040

: lCl1)

connection

of terminals

diagram

functions . . .

diagram

Waveform,

vtEvQ

slDE

....-

....

.

: CXDl075P

lC

. . .

Connection

...... 14

...20

of

...30

...

. . .

....

...49

COVER

BACK

14

14

15

16

16

16

17

17

20

20

21

21

24

27

34

1?

38

41

50

51

-

TRANSPORTATION SCREW

Refnre nnpr:ti.}n remove

to the

factory.

remoVing,

card and other documents.

ported

nal

ATTACHING THE

1. Turn

2. Turn

3.

vPv, u!,v',, ' v

bottom of the

Remove both screws

retain

again, be

position.

power

the

OFF the

inq indication.

lnstall the transportation screws.

unit used

together

them

replace the two

sure

TRANSPORTATION

without loading

ON

power

after

ElEtElElCt C@

@gltEtrtE)

ID ID IEI

E0@tD@@

c;;;

r@r

E

L, L,

the two

during

using a coin,

with the

When the

the display

*^

,-rr-r

ili.]

red

scfews

transport

etc. and, after

unit is

screws to

SCBEWS

disc.

shows the

attached

from

the

Warranty

to be trans-

origi-

their

follow-

/^\

((Lr)

\Y/

@

v

I

@

fl

U

Page 5

DISASSEMBLY

FOR REPAIR

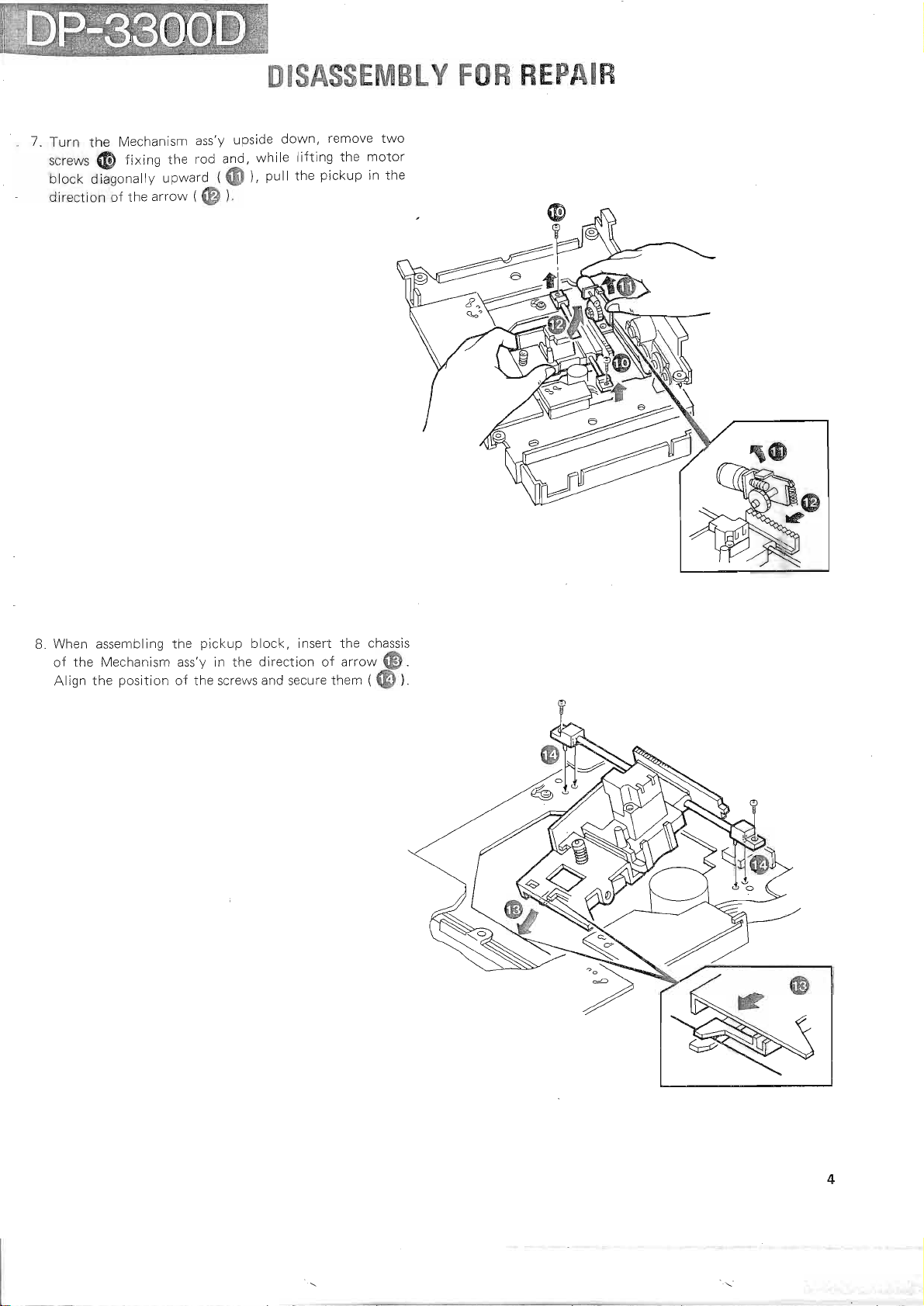

7.

Turn the

screws

block

direction of

Mechanism

tixing the

@

diigonally

arrow

the

ass'y

rod

upward

(

(D

upside

and,

((E

)

while

pull

)'

down,

lifting

the

remove

the motor

pickup

two

in the

When assembling

8.

of the Mechanism ass'y

Align the

position

pickup

the

of the screws and secure them

block,

in the direction of arrow @ .

insert the chassis

(

(E

).

Page 6

(cx20109)

rcl

^_J-F-

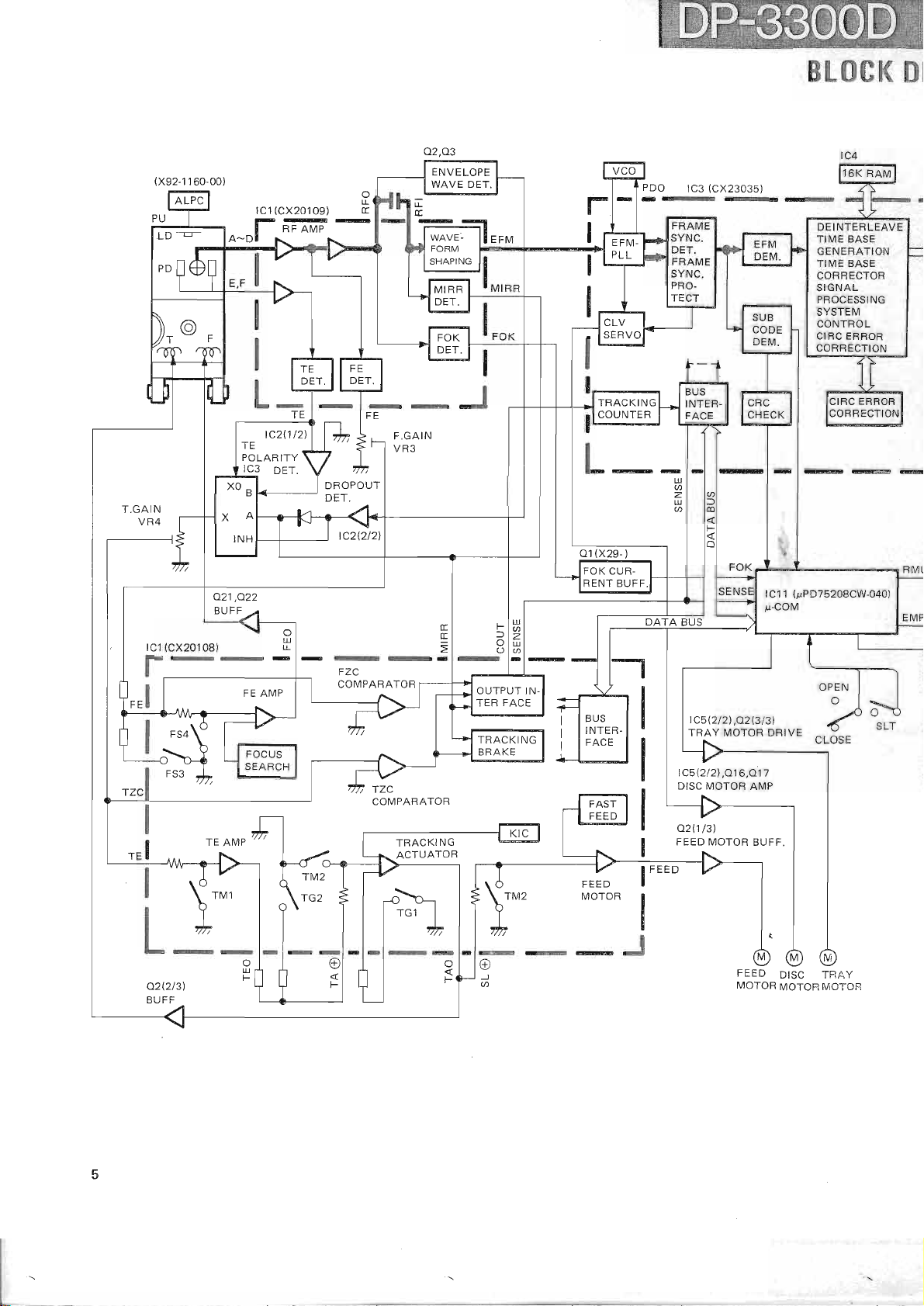

BLOCK

ENVELOPE

WAVE DET,

u-

(r

PDO

----

tc3

FFIAME

SYNC.

DET.

FRAME

SYNC.

PBO.

TECT

BUS

INTER"

FACE

(cx23035)

DEINTERLEAVE

BASE

TIME

GENERATION

TIME BASE

CORRECTOB

SIGNAL

PBOCESSING

SYSTEM

CONTROL

CIRC ERROR

CORRECTION

DI

tc1

r--

I

,rl

(cx20108)

^\-

'r'

|

|

I

-l--

rl

ll

I

'v7,

F

OUTPUT IN.

TER FACE

TRACKING

BFIAKE

E_J

@

J

U'

(x29-

01

FEED

MOTOB

E-

)

FEED

I

I

U

z

U

o

tc5l2t2l,o2l3l3l

MOTOR DRIVE

TBAY

FEED

MOTOR

GC-

CLOSE

DISC

MOTOR

OPEN

TRAY

MOTOR

NT

JLI

Page 7

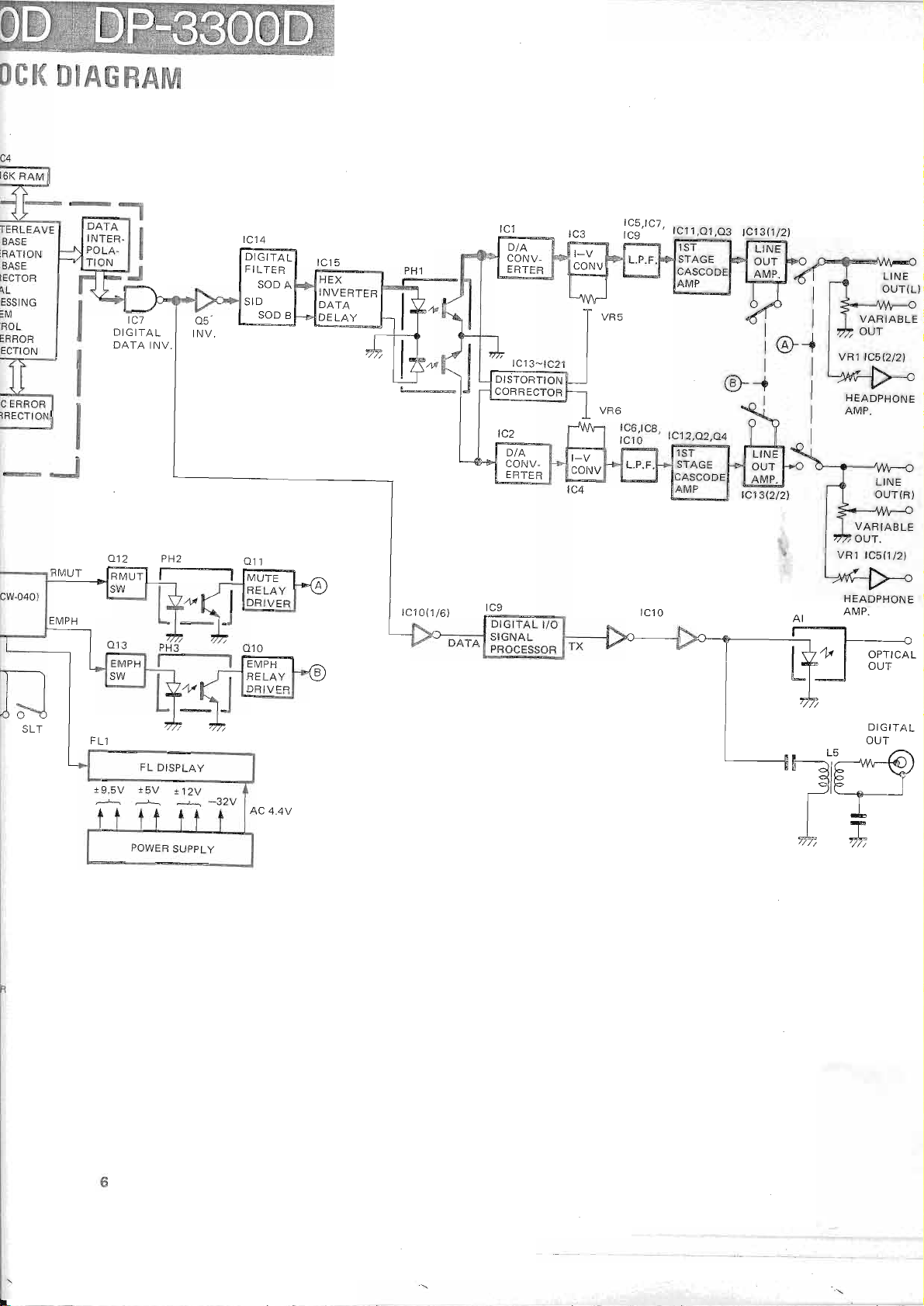

OCK

OIAG

BAM

TER LEAVE

OAJE

iRATION

BASE

iECTOR

qL

ESSING

EM

'FOL

ERHOR

ECTION

ERROR

C

IRECTI

:1

DATA

INTER.

POLA-

TION

DIGITAL

DATA INV.

Q13

DIGITAL

FI

LTER

SOD

SID

tc7

ol

1

rc

l1-fllffiej-@

L

I-'U

+rh

PH3

010

tcs,tc7,

tc9

A

lc13-tc21

tc6,tc8,

lc10

rc10(1/6)

f

c1 1,ol,o3

\c12,o2,A4

tc13l1l2l

tcls(2121

HEADPHONE

AMP.

LINE

OUT(R)

VARIABLE

OUT.

HEADPHONE

AMP.

ti

FL

DISPLAY

/v

t12V

--r-

-32V

DIGITAL

OUT

t--- -.,l'--'w.-6)

-AIBY

qtb

r-Jl\---a____J

tl

l-

IT

,7v

,ln

I

Page 8

DESCRIPTION

Operation/Condition/Compatibility

Converts digital

: Converts

11/21

(2121

: Generates

(General

a GIC

Forms

the 1st

stage of output

Amplifier device

Digital filter

Inverts

(-) power

(

+

)

Used in

Used in

Used in

Interface

Interface between

Interface

Used

Begulated

De-emphasis

Muting

Emphasis

Muting

Used for

Supplies

Determines

amp of 1

Feference

output

Used for

Used for

Determines

with

the logic

for

DAC.

power

for

DAC.

distortion corrector

distortion

distortion

between digital filter

between

in cascode

power

power

relav driver

relay driver.

photocoupler

photocoupler

supplying voltage

potential

potential

the

st staqe of

power

amp.

ga

I C 1

6 a

countermeasure

short-circuiting

the operating voltage

lC1 7 against counter-withstanding

value

into agalog

DAC current

offset voltage {or

lmpedance Converterl with

of output

4-fold oversampling.

of digital filter

corrector circuit.

corrector circuit.

DAC and X32

DAC and

1

stage of

for constant-voltage

supply

for

supply

driver.

driver.

to the cascode stage of

output amp.

for

supply

i nst cou nte

counter-electromotive

quantity.

input into voltage.

amp.

amp,

output and delays

circuit

and DAC

(Emphasis).

(Muting).

X32

st stage

differential

photocoupler

to the

of constant-current

constant-voltage

r-withstan-d i ng vol

against

static electricity.

of transistor

distortion correction.

LPF.

final

in the

o.f

output

stage.

(Used

for

amp.

circuit of ist

amp. of 1st

output.

lst stage of

circuit

circuit of 1st

taqe.

voltaqe

SW 014

voltage.

data.

data).

stage

of output amp.

staqe of output

'r

output amp

of differential

stage of

of relav.

amp.

1.

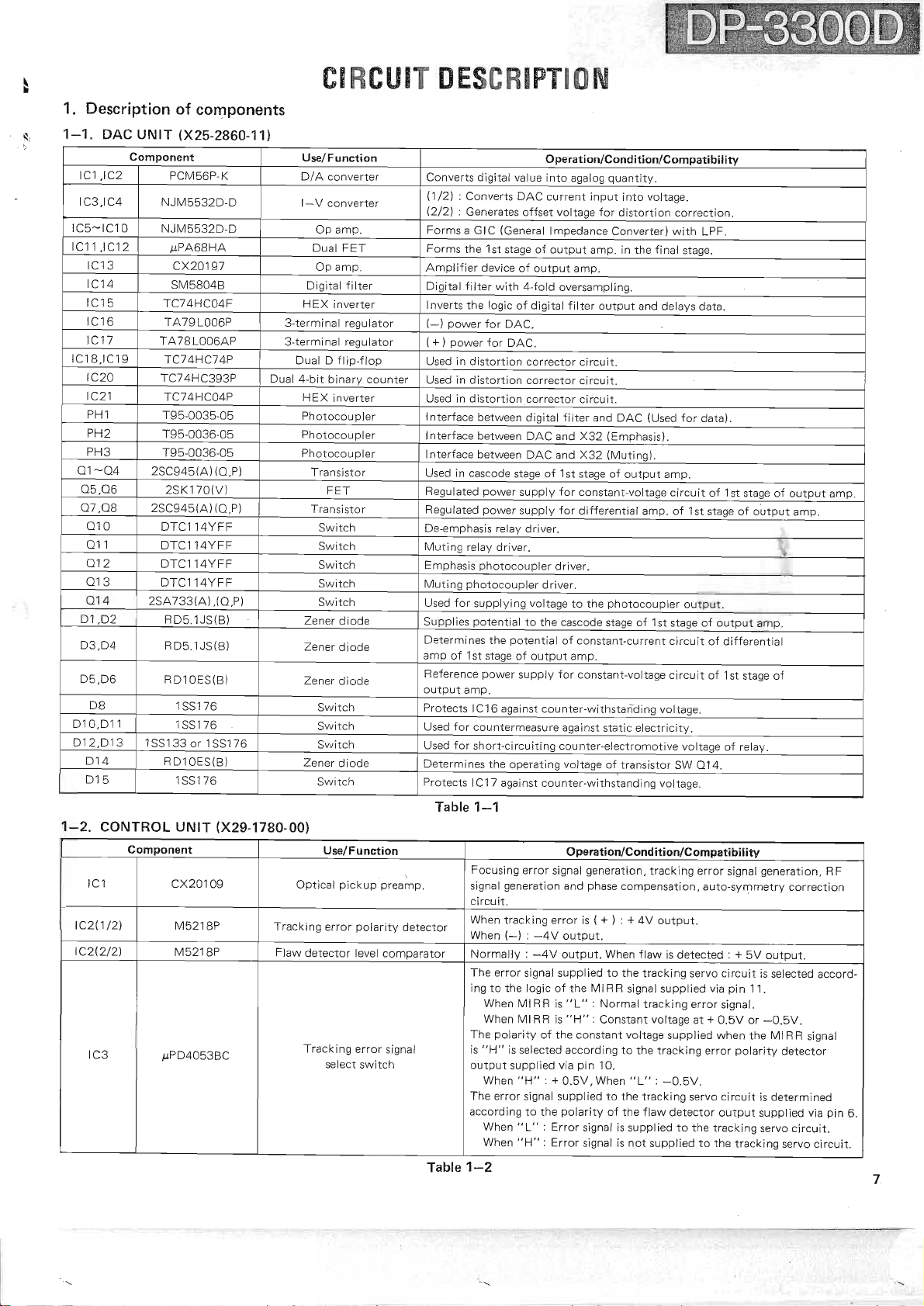

Description

1-1.

DAC UNIT

Component

lcl

,lc2

tc3,rc4

tc5-rc10

tc

,1c12

LIJ

a1A

L t3

Lto

c't7

tc

8,tc19

tc20

NJM5532D.D

NJM5532D-D

TATSLOO6AP

TC74HC393P

tc21

PH1

PH2

PH3

-o4

01

05.06

07,Q8

01 0

1

Q1

012

n1?

014

D1

.D2 RD5,iJS{B)

D3,D4

D5,D6 RDl

D8

D 10,D1 1

D12.D13

ut4

Litc

T95-0035-05

T95-0036-05

T95-0036-05

2SC945(A)(O,P)

2SC945(A)(O.P)

DTCl

DTC] 14YFF

DTC1 14YFF

DTC1 1

2SA733(A),(O,P)

iSS133

of

components

(x25-2860-11)

PCM56P.K

pPA6SHA

cx20197

SM5804B

TC74HCO4F

TA79LO06P

TC74HC74P

TC74HCO4P

25K170(V)

14YFF

4YFF

RD5.1JS(B)

OES(B)

tSst/u

tsSt/t)

or 1SS176

RDl

OES(B}

1

76

SS1

CIRCUIT

Use/Function

D/A converter

l-V converter

Op amp Forms

FET

Dual

Op amp

Digital filter

HEX

inverter

3-terminal reoulator

3-terminal regulator

Dual D flip-flop

Dual 4-bit binary

HEX

inverler

Photocoupler

Photocoupler

Photocoupler

Transistor

FET

Tra

nsistor Regulated

Switch

Switch

Switch

Switch

Switch

Zener

diode

Zener

diode

Zener

diode

Switch Protects

Switch

Switch

Zener

diode

Switch Protects

counter

Table 1-1

1-2.

CONTBOL

Component

tcl

tc20/21

tc2l2l2l

ILJ pPD4053BC

l-,

a(

t:

t

ji

(X29-1780-00)

UN|T

cx201 09

M5218P

M5218P

Use/Function

pickup

Optical

Tracking error

Flaw

detector

Tracking error

select switch

preamp.

polarity

detector

level comparator

signal

Table

Focusing

signal

ci

When

When

Normally :

The error

ing to the logic

The

is

output supplied via

The error

according

error

generation

rcu i t.

tracking

(-)

When

When

polarity

"H"

When

When

When

signal

error

-4V

:

-4V

signal supplied to the

of the

MIRR

is

MIRR

is

of the constant voltage

is selected according

"H"

+

:

signal supplied to the tracking

to the

"L"

:

Error

"H":

Error

1-2

Operatiory'Cond

generation,

phase

and

(

is

+

tracking error

compensation,

+

:

4V output.

)

output.

output. When flaw

MIRR

"L"

:

"H"

:

pin

0.5V. When

polarity

signal is

signal is not

tracking servo circuit

signal supplied

Normal

tracking error

Constant voltage

to the

1O.

"L"

flaw

of the

supplied to the tracking

supplied

ition/Compatibil

signal

auto-symmetry

detected :

is

supplied

tracking error

-0.5V.

:

detector

+

pin

via

signal.

at + 0.5V

when the Ml

polarity

servo circuit

output

to

the

tracking

ity

generation,

correction

5V

output.

is selected

11.

-0.5V.

or

R R

detector

is determined

supplied via

servo circuit.

servo

RF

accord-

signal

pin

circuit.

6.

7

Page 9

CIRCUIT

DESCRIPTION

atl

a2

o3

Dl

,D2

D3,D4

D5

1-3. CD

rc12-lC'l

Gomponenl

25C945(A)(o,P)

2SC945(A)(o,P)

2Sc945(A)(o,P)

or

1SS176

or

1SS176

or

1SS176

M51

UNIT

951 ASL

PLAYER

cxK581

TCT4HCOOP

TC74HC08P

cxDl

5

TC74HC74P

STA341

DTA1

2SC1923(R,O)

2SA733(A)(O,P)

2SC945(A),(O,P)

2SA992(F,E )

2SC1845(E,F

25 K246(Y,G

2SA733(A)(O,P)

25K246(Y,G

RF siqnal

RF siqnal

1SS131

'l

SS131

1SS131

(X32'1090'11)

6M

075P

R

R

Current

)

)

)

M

24EN

Use/Function

current

FOK

enveloPed

enveloped

Switch

Switch

Switch

gate

AND

output

Digital

modulator

withstanding

3-terminal

3-terminal

amPl

gital

transistor

Di

transistor

Dioital

buffer

(switch)

signal

lC

regulator

transistor

if ier

switch

switch

detector

deteclor

buff.

"H"

Goes

Detects

Detects

lC2l2l2l

When

the negative

vent

When lC2ll/21

vent the

When the

the

turns

1-2

Table

Generates

search

servo.

Generates

EFM

Signal

012\

l2l2l

11l2J

l2l2l

Digital

Controls

Converts

transmission

lC9

Controls

Interface

+

-5V

+

Error

Digital

For loqic

Current

ci

Used

the

microprocessor

decoder,

processor

compensator

: PLL

:

CLY

: CLV

: TraY

data

digital

digital

demodulation

disPlaY,

circuit

resulated

5V

requlated

regula'ted

5V

oI

amp

data

inversion

buffer

itrv.

rcu

prevent

to

motor

disc

inversion

digital

lnverts

Discharges

Supplies

An

Controts

Controls

-5V

emitter-follower

SWs

potential

Eliminates

-5V

Turns

supply

Power

Operation/Condition/Compatibility

from

output

is

a signal

when

+

envelope

side

the

the + side

negative

envelope

output

potential

output

potential to

flaw detector

MIBR

signal

pulses

for

correction/intetpolut!9n

(16K).

RAM

compensator

compensator

circuit

driver

circuit.

inverter

supply

signal

data

audio

signal

key-inPut

between

for

voltase

for digital

voltage

voltage

x12V constant

circuit

inverter

usi

for tracking

operation

driven'

not

is

level

and

high speed

at

data

-5V

to

DAC

DAC

unit

used

07

and

Q6

base

at

motor

of

offset

for laser

constant-voltage

the

in

of RF signal.

RF signal.

of

be

to

be applied

goes

level

"H".

servo,

pulse.

(LPF

(LPF

(amp.)'

DAc'

to

Sony/Philips

pulse

-4V,

applied

-4V,

transformer

becomes

becomes

also

focusing

reset

circuit

circuit

silsui{

into

amp,

microprocessor

a449lel9-!!!-!i!91

and

for servo

unit

line.

-disital

SW.

actuator,

of eye-pattern

of MON

shifting

and

to 0V.

for

supplying

Q8'

of

circuit

driver

ON/OFF

"H"

+

+

PLL lines'

regulated

feed

amplifies

pickup'

the

(Small

(Large

switches

the

to

switches

the

to

detecting

by

tracking

PLL cit'

citcuit,

amP.1.

shifter).

level

digital

servo

and

9!ql!

circuit

motor

center

ortp,4-|1on'

+

to

5V

while

regulated

constant)

time

constant)

time

function

pin

of lC3'

6

function

pin

10 of lC3'

flaw,

a

feed

and

servo

foimat

l/O

driver'

lC.

if:919y

DAC'

for

motor

tray

and

sampling

circuit

9I?9991

current'

the

unit'

DAC

me19!l1l99q9d'

power supply

laser

to

to

the

to

m

g'

or

w

Table

1-3

Page 10

($

rs

D6,D7

Dl

2-Di

D1

D1

8-D20

D21

D22

D23

D24

o14

ut3

Cl

7

o

019

o20

421

422

o23

o24

D,I

D2

D3

D4

D5

D8

no

Dl0

Dl1

6.D17

Component

2SC945(A)(O.P)

2SA1

z>L5240

2SA1286

25C945(A)(O,P)

2SA733(A)(O,P)

2SC945(A)(O,P)

2S,A1286

2SD1

z>u I

258941

rJJt/o

1

1

1

RD6.8ES(82)

DSM1A1

RD8.2ES(B)

1

SS1 76

BD2.7ES(B}

RD6.2JS(82)

5

rJJ

1

SS1

1

SS1 76

RD5.6ES(82)

1B4841

1B4B'41

1

SV1 47

286

266

zoo

SS1 76

SSl 76

SS1 76

| /O

76

(P)

CIRCUIT

Use/Function

Ripple

filter

Ripple filter

Current

buffer

Current

buffer

Switch

Switch

Switch

Current buffer

Current

buffer

Bipple

filter

Ripple

filter

Switch

Switch

Switch

Switch

Zener

diode

Rectif

ier diodes

Zener

diode

Switch

Switch

Zener

diode

Switch

Switch

Switch

Zener

diode

Bectif

ier diode

Fectifier

diode

Vari-cap

BESCHIPTION

Operation/Condition/Compatibility

Transistor

for FLdrivers

Transistor

Current

Current

Inverts

Connects

Control

Current

Current

Transistor

Transistor

Preiigital

Diode

Time-constant

Used

searching,

Provides

circuit

Used

Used to

Diode

OFF.

Used

Provides

Diode

Qiode

Diode

Provides

fiectifier

Rectifier

Vari-cap

Table 1-3

ripple

ripple filter

buffer

buffer

the

logic

rhe low

used

SW

buffer

buffer

ripple

ripple filter

SW.

SW used for

prevent

to

etc.

reference

for

FL

driver

for

voltage

maintain FL

SW used

to

decrease

reference

SW used for

used for

connected

SW

reference

diode

diode

in VCO

filter

for

constant-voltage

(lC12to

lCs

for

disc

for

disc

of

muting

to set

for focus

for focus

filter for

key

for

SW

variation

potential

multiplyinS

to

interrupt

r12V

potential

countermeasure

countermeasure

potential

bridge

bridge

circuit

lClb).

for

constant-voltage

motor driver

motor

driver circuit.

pre-digital

potential

r12V

SW.

regulated

actuator

actuator

+

12V regulated

-12V

lor

scanning

quick

discharge

of MUTE

for

(1C12

lCs

rectifier.

disp

ay erase

optical

power

DAC

for

to

limir

SW.

for

for

servo

for

DAC

PLL.

of

circuit.

in DAC unit

driver

driver

regulated

in test mode.

and EMpH

constant-voltage

to lC15).

potential

output

quickly

r1

2V regulated

against

against

-5V

laser

and

digital

line.

regulated

power

laser

to GND.

unit

power

DAC

circuit.

circuit-

DAC

unit

DAC unit

ot

C4E.

while

when

static

static electricity.

oower.

lines.

power

digital

regutated

the

digital

power

DAC

electricity

VDD

supply circuit

supply

circuit.

tOV.

to

powersupply

supply circuit

audio

data

during

V6p

supply

output

sw

is turned

power

OFF.

supply

in digital

circuit.

is oFF.

circuit.

output.

Ftu

FIJ'

r;

$Bi

;v

2.

Circuit

2-1.

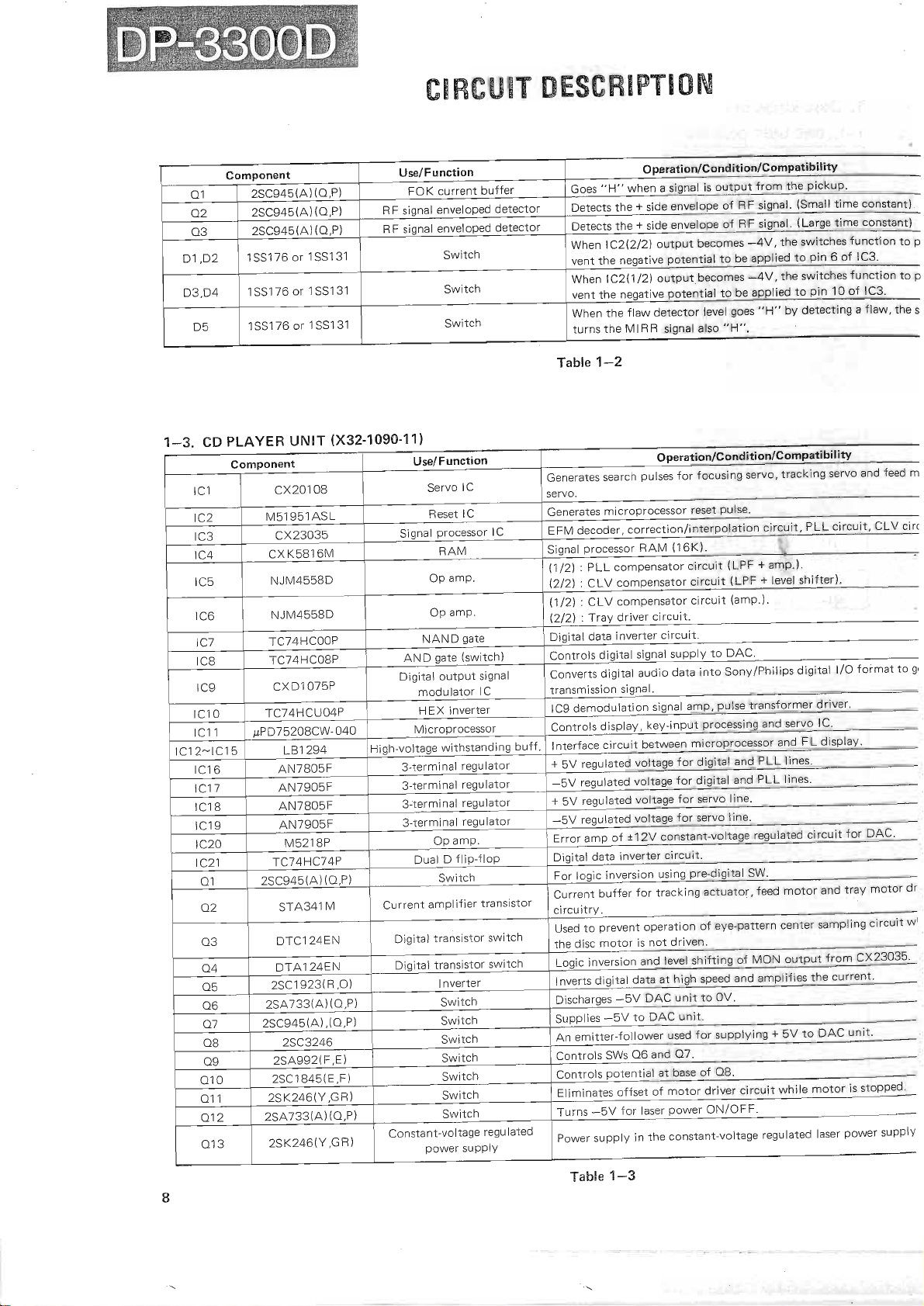

The

separated

description

DAC

Interface

digital

by transmitting

photocouplers.

speed

type,

the

lag

of

approx.

inverter

176.5kH2

is used

used for

(X25-2860-11)

circuit

line

and

analog

DAC

Although

the

photocoupler

20ns.

To

compensate

with

BCK

and

LATCH

signal.

line

of

the

digital

audio

photocouplers

outputs

are

stili

for

two

inverters

Dp-3300D

data

using

of

the high_

include

this

are

a time

delay,

used

with

are

an

tc14

(Digital

filter)

Fig.2-1

T

DAC

Interface

circuit

DAC

to DATA

DAC

to DATA

DAC

tO BCK

DAC

to LATCH

(Lch}

(Rch)

Page 11

CIRCUIT

DESCRIPTION

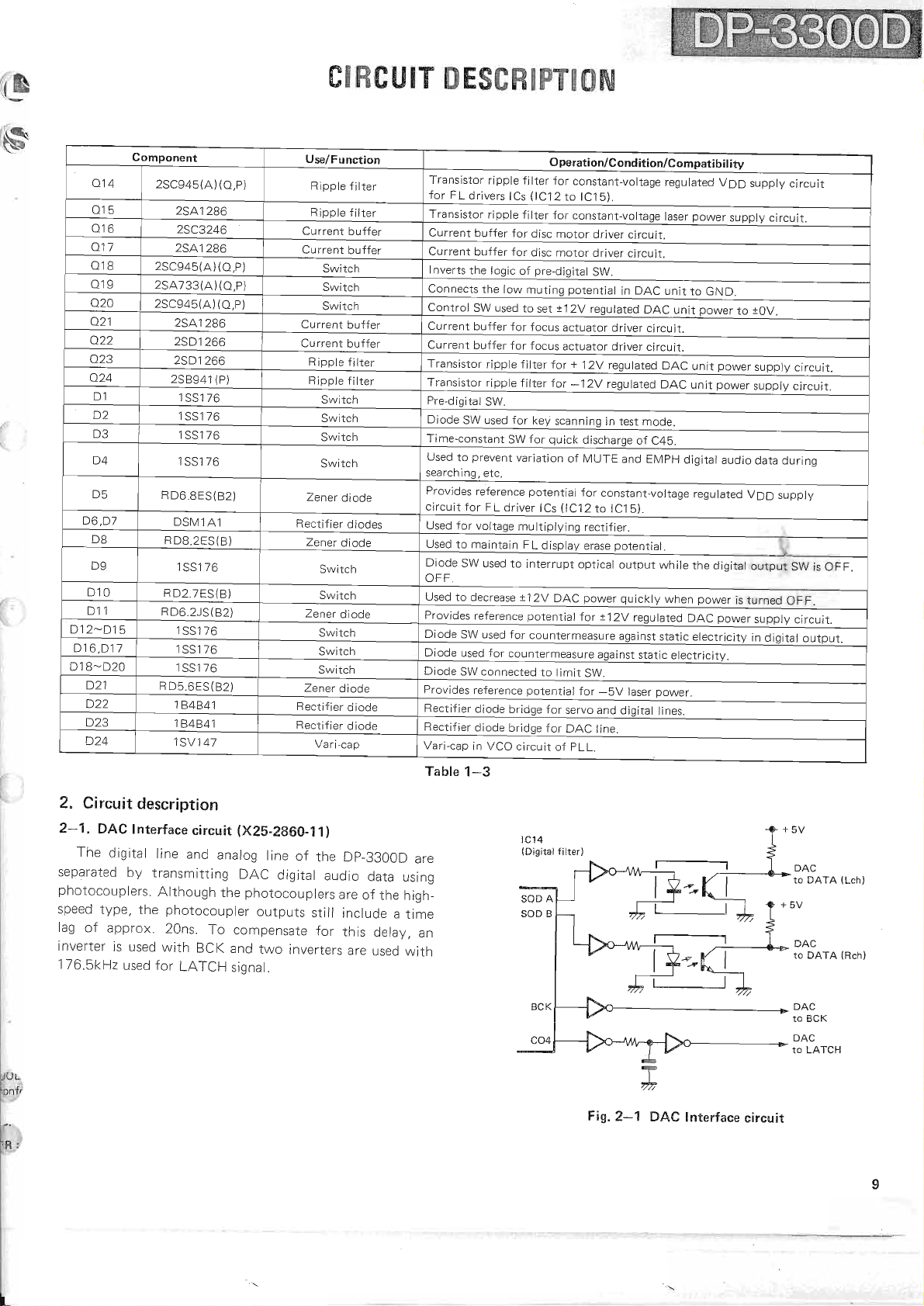

2-2.

Distortion correction

Fig.

In

circuit

data's

delays the logic

tion,

The DAC

the circuit which compensates

of

rent value corresponding to the

circuit

R3.

to

OP1 is used to add/subtract

the

from

current corresponding to the 1 sth bit

DAC according to the logic

passes

value of the 1sth bit is

ponding

CLK

4.2336

MHz

DATA

LATCH

176.4kH2

2-2, D-FF1,

which extracts the data logic

1sth bit which is immediately

by DATA.

please

refer to the timing

has been designed to accept the

consists

error

the

through OPi so that the

of

semi-fixed

corresponding to the

D/A

converted

to

the

(n-1)th

1sth bit

circuit

D-FF2,

current. Therefore,

eliminated. lf

not output

is

DATA

(X25-2860-11)

and

BC1

of the digital audio

after

For

chart in

resistor VR1 and

of

details of the opera-

the

Fig.2-3.

for

the

value

of the

the current compensating

value

of the

is output

15th bit, the current

the

error corresponding to the

the

from

{n)th

form

BC2

MSB, and

the

connection

error

of the cur-

MSB. The

resistors R1

15th Oit to/

when the

from

current corres-

DAC,

the

DATA

the

the

the

Fig. 2-2

output from

current is not applied to the

from

the DAC.

OP1 becomes

Distortion correction

0V, so that

D/A converted

the compensation

circuit

current output

C

D

2-3. Dropout controller

TE

i of

TE

passes

process

X

With

conventional

pin

from

CN3. However,

is shaped,

through

are as

[(n-1]thl

servo systems, tracking

17

of

TE

CX2O'I

with the DP-3300D,

the shape of waveform

lC3. The operations

follows.

15 losic

DATA

DATA

(X29-1780-00)

circuit

89

1slosic

Fig. 2-3 Timing

are output directlyat

and waveforms in this

)thl

t(n-1

chart of

error

signal

the waveform of

varies while

TE

distortion

pin

it

X

DATA

coruection

@

IE

circuit

15 tosic

DATA

DATA

[(n]thl

15 logic

logic

15

n;r

rcgl

[(n

[(n

+

+

1)th]

fE

f

1)th]

I

\

10

Fig.

2-4

Dropout

controller circuit

Page 12

is

$

C!RCUIT

o

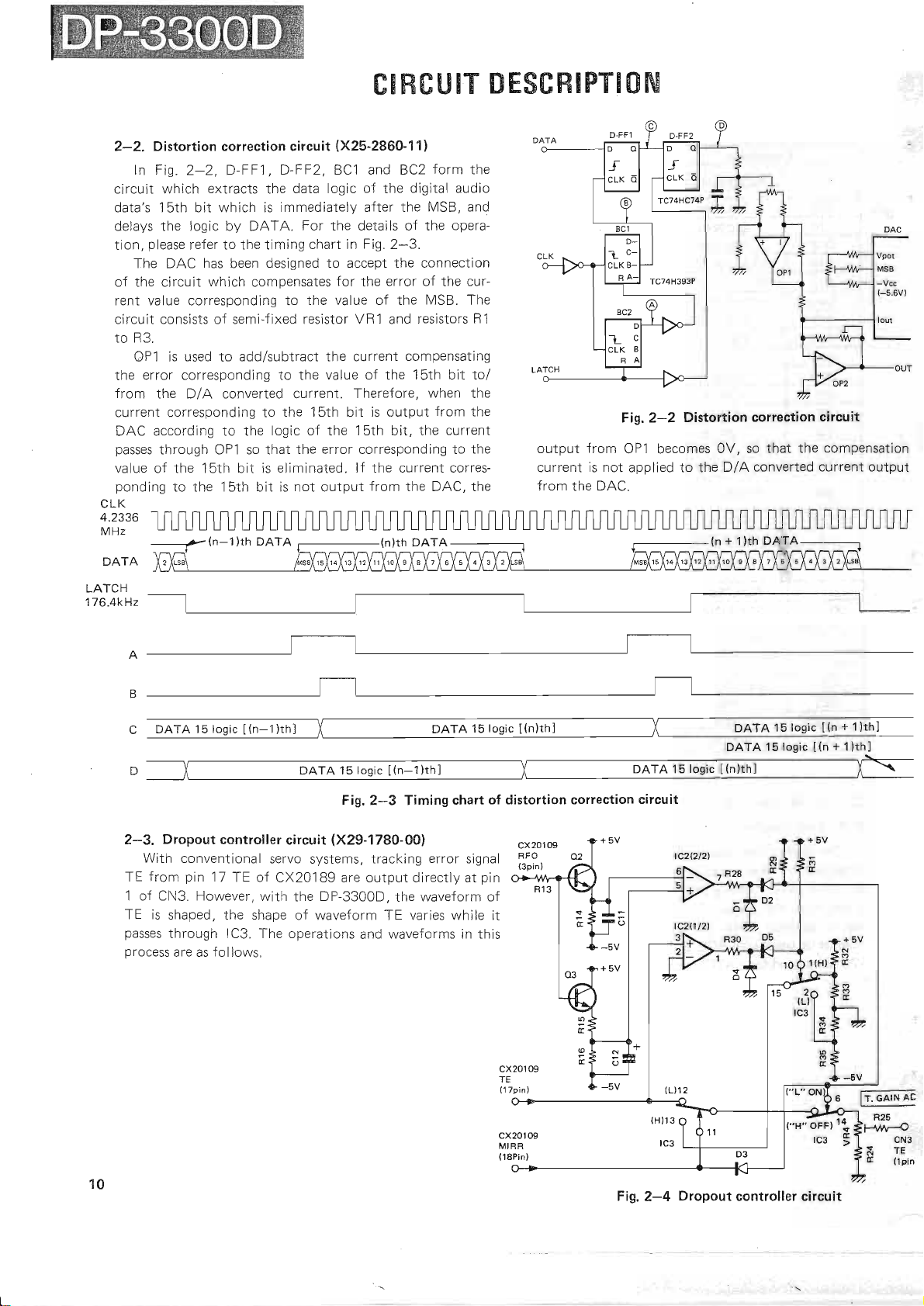

In

lf

the

03 have different

for

large time constant is divided by

waveform becomes as shown by the dotted line

(b).

form

Therefore,

by the

line,

(Fig.2-5(c))

This signal

pin

and VR4 and R24

error

TE is 0V only

waveform as shonw in

CN3

period.

over it. TE of

tion of MIRR.

of

case

the disc contains a

RF

signal

tracking

With signals that

becomes as

solid

and

When lC3

6.

signal

pin

However, as the

disc

the

may lack the

time constants, but they are both

positive

the

shown by the solid line

at

the

line

drops below the level

the output

is

shaped by D1 and D2, and applied to lC3

pin

set

does not

while

"H"

1

.

level

goes

CN3

contains scratch:

scratch

envelope. When

have

point

trom

goes

6

TE

to GND level so that the tracking

go

to the

"H"

Fig.

is

also applied to MIRR

control of lC3

GND

as shown in

positive

a small time constant, the wave-

of the scratch. the level shown

lC2(212)

"H",

lC3 sets the SW to OPEN,

next

is applied to lC3

2-5(e)

level

envelope. 02 and

side

the signal

R15

and R16, the signal

in

the same

by the dotted

shown

pin

7 will be inverted.

This means that

stage.

pin

is output as

via

pin

6

regardless

Fig.2-5(al

used

with

in Fig.

2-5

figure.

6, and the

from

TE

D3 at this

priority

has

varia-

of the

DESCRIPTICIIU

,

a

RFO

OV

o2

emitter

tc2l2l2l

pin

7 output

OV

OV

tc212l2l

pin

7 output

tc3

pinoinput

lc3

pin

14 output

'

bv

.

FnHrt*.1*F-{fift}.|r{ilrttlF

{-l

ll

I I

Fis.2-5

+5v

(b)

(c)

-4V

(d)

(e}

?

I

o

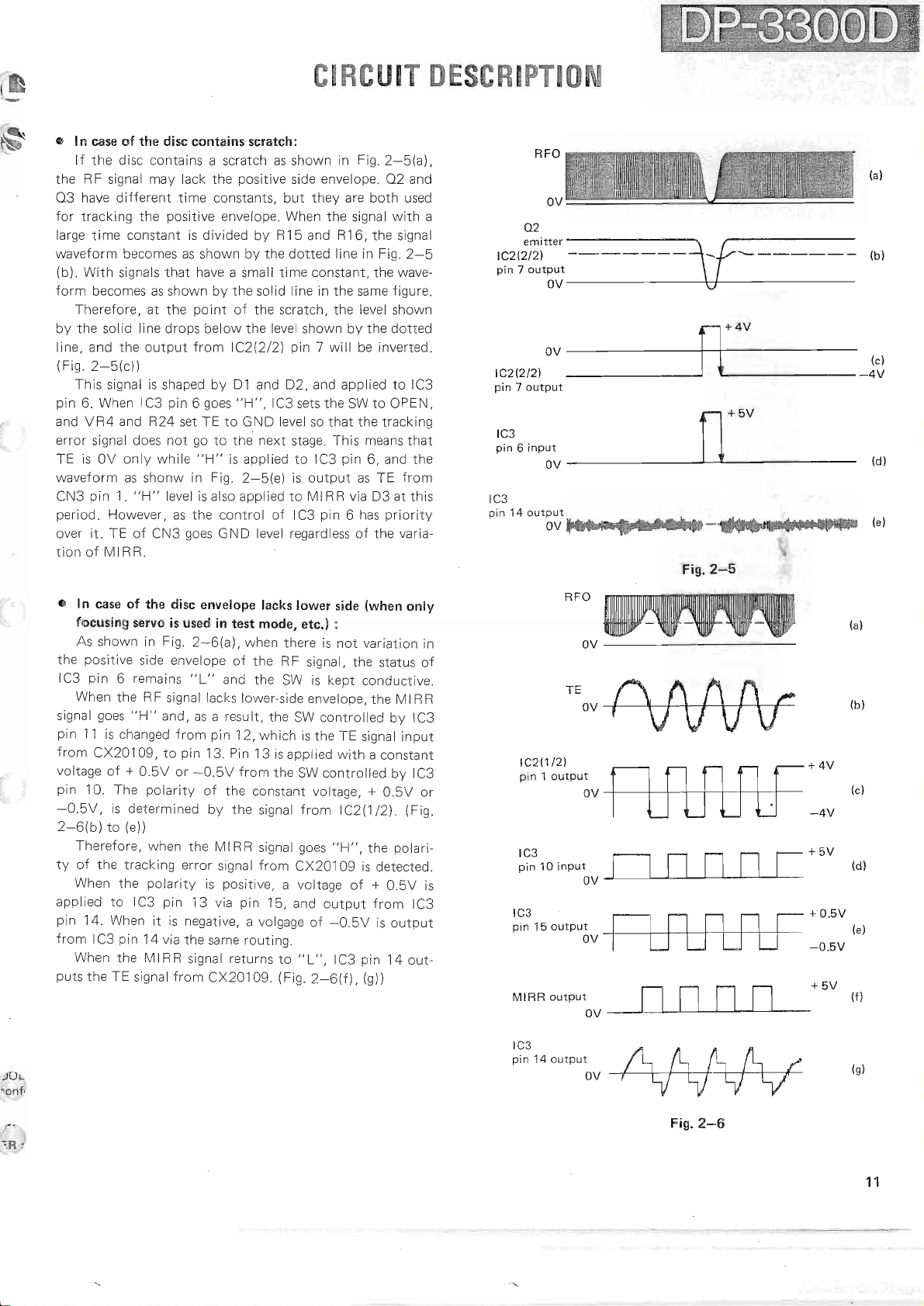

In

case of

focusing

As

shown in

positive

the

pin

lC3

signal

pin

from

voltage

pin

-0.5V,

2-6(b)

ty

applied

pin

from

puts

6 remains

When

the RF

goes

11

is changed from

CX20109,

of + 0.5V

10.

The

is determined

(e))

to

Therefore,

of

the tracking error

When

the

to

14. When

pin

lC3

When

the MIRR

the TE

disc

the

servo

side envelope

"H"

polarity

when

polarity

lC3

it

14 via

signalfrom

envelope

is used

in test

Fig.

2-6(a),

"L"

signal

lacks lower-side

and,

as a

pin

pin

to

13. Pin

-0.5V

or

of

by

the MIRR

is

pin

13 via

negative,

is

the

same routing.

signal rerurns

CX20109.

lacks

lower

mode,

when

there

of the RF

and

the

SW is kept

result,

the

'l

2,

from

the constant

the signal from

signal

positive,

pin

a volgage

SW controlled

which

13 is

applied

the SW

goes

signal

from

CX20l09

a voltage

15,

and

"L",lC3

Lo

(Fig.

(when

side

etc.) :

is not variation

signal,

the status of

conductive.

envelope,

is the

controlled

voltage,

output from

of

2-6(f),

the MIRR

TE

signal

with

a constant

+

lC2(112ir.

"H",

the

is detected.

of + 0.bV

-0.5V

is

pin

(S))

only

in

lC3

by

input

by lC3

0.5V or

(Fig.

polari-

lC3

output

I4

out-

is

RFO

OV

","n/v\Y

tc2l1l2l

'l

pin

output

OV

lC3

pin

input

10

lC3

outPutu

15

Pin

MrRRoutput

OVa

I I

ffi

n n n

n

t-

t-

+4V

-4V

=

5V

+

0.5V

-o.uu

+5v

(a)

(b)

(c)

(d)

t"'

(rl

F,,

ie-nJ,

:{-;

l?nt,oou,ou,

A f- tl- /l- /

ovm

Fis.

(s)

2-6

11

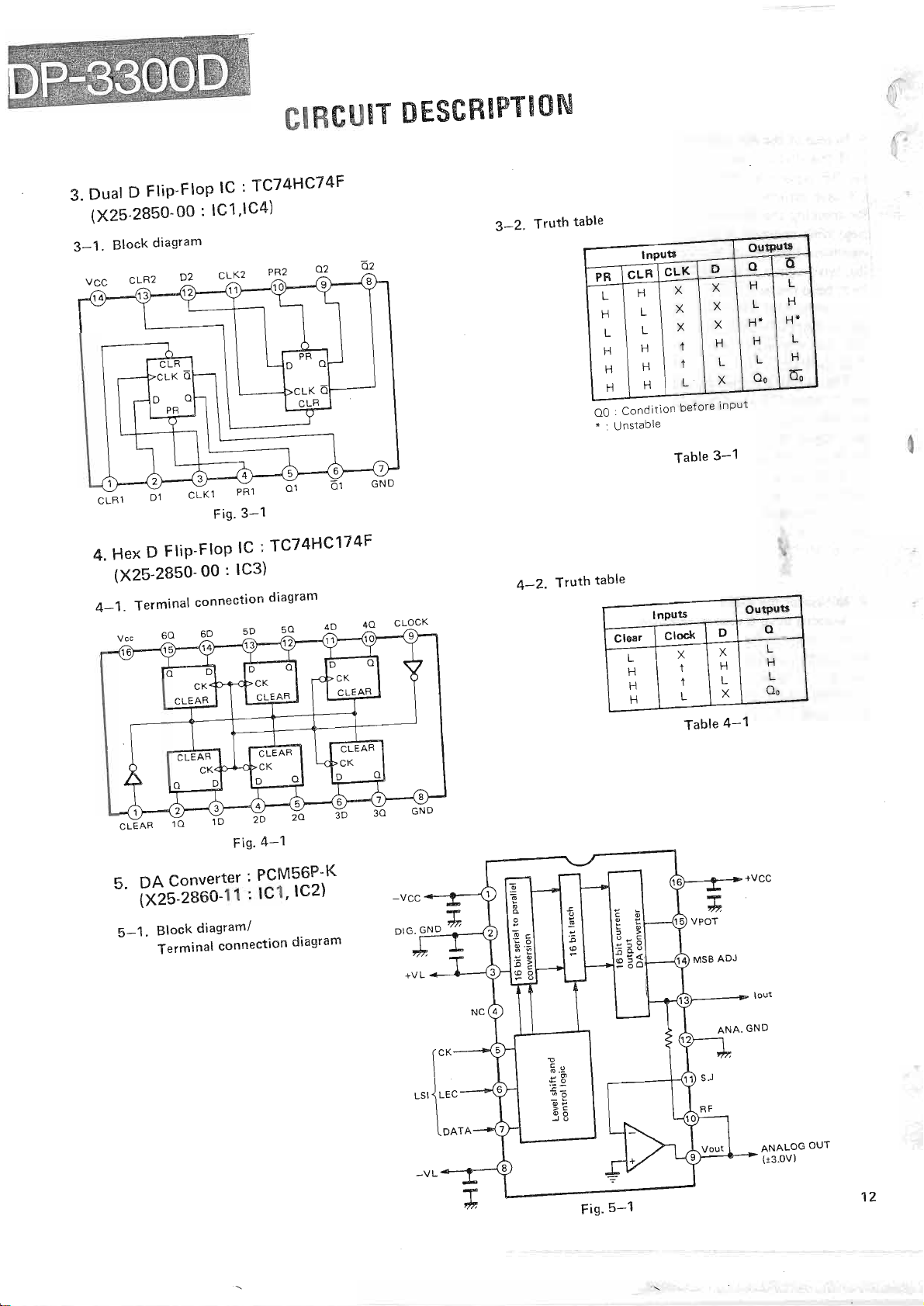

Page 13

CIRCUIT

DESCRIPTION

d:

\l

4'

\i

D

Duaf

3.

(X25-2850-

Block

3-1.

CLR1

Hex

4.

lX25-285O-00:

Terminal

.

4-1

vcc

FliP-FloP

diagram

Dl

FliP-FloP

D

60

lC:TC74HC74F

lC1'lC4)

:

O0

CLKT

CLK1

Fig'

Fis.

connection

6-D

PRl

3-1

3-1

TC74HC174F

:

lC

lG3)

diagram

P X

3-2.

Truth

4-2.

table

Truth

: Condition

O0

table

before

Table

L

H

H+

L

H

G

inPut

3-1

\.

ru

CLEAR

5. DA

"'

10

Converter

ifisl-iebo-rr

diagram/

Block

.

5-1

Terminal

connection

4-1

Fis'

PCM56P-K

:

lc1,lcz)

:

diagram

cK-

LEC'

(OAT

Table

4-1

ANALOG

(r3.0vl

OUT

Fis.

5-1

12

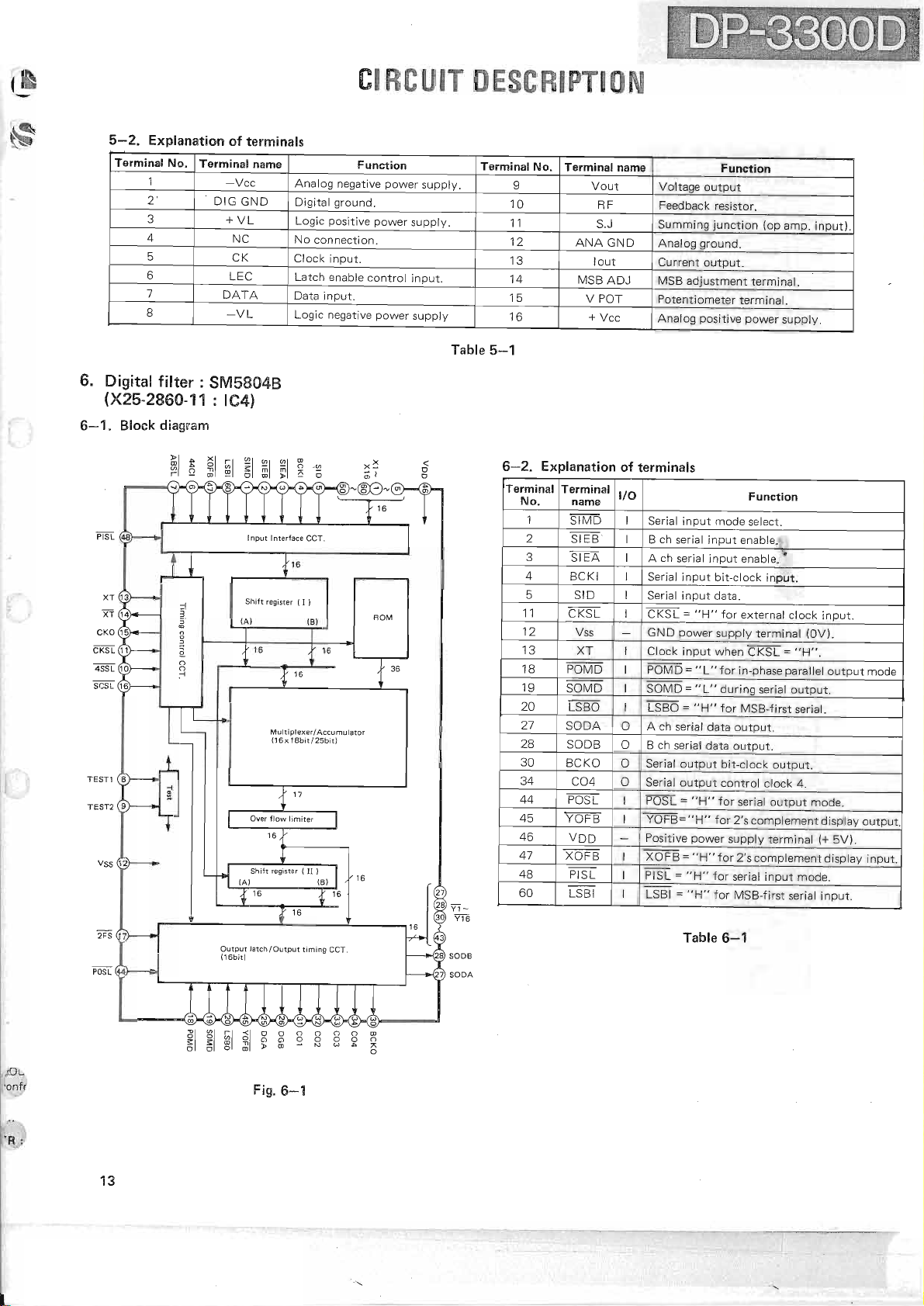

Page 14

r3

s^

5-2.

Explanation

6.

Terminal

Digital

No.

1

2'

6

I

filter

(X25-2860-11

6-1. Block

diagram

of terminals

Terminal

:

name

-Vcc

DIG

GND

+VL

NC

CK

LEC

DATA

SMS804B

:

lC4)

cf

Function

Analog

negative

ground.

Digital

positive

Logic

No connection.

Clock input.

Latch enable

Data input.

Logic negative

control

RculT

power

supply.

power

supply.

inout.

power

supply

Table

0EscRtPTt0tu

Terminal No.

I

10

tl

12

IJ

l4

tc

to *

5-1

Terminal

Vout

HF

el

ANA GND

I out

MSB

ADJ

POT

V

Vcc

name

Voltage

Feedback

Summing

Analog

Current

MSB

Potentiometer

Analog

Function

output

resistor.

junction

ground.

output.

adjustment

terminal.

positive

(op

terminal.

power

amp.

input)

supply.

XT

;-T

cKo

CKSL

lssf

scsL

FlESletBlfitfitEc

Mu!tiplexer/Accumulator

{16x18bit/25bitl

xI

Explanation

6-2.

Terminal

No.

A

5

11

12

18 POMD

19

tn

27

28

30

44 FdST

45

46

47

48

60

rerminal

name

S-two

EB

SI

siEa

BCKI

SID I

CKSL

Vss

XT

SOMD

LSBO

SODA

SODB

BCKO

co4 O

YOFB

VDD

XOFB

PISL

LSBI I

of

terminals

alo

Serial

B ch

,A ch

I Serial

Serial input data

I

ERSI

GND

Clock input

POMD

SOMD

o

ch

A

o B ch

o Serial

Serial

FOS-L

TOFB="U"

Positive

XOFB

I PISL

LSBI

Function

input mode

serial inout enable.r

serial input enable.'

input bit-clock

"H"

=

power

"L"

=

"

=

serial

serial

output

output

"H"

=

power

"H"

=

"H"

=

"H"

=

select.

for

external

supply

terminal

when

e KSf

for

in-phase

during

L"

data

data

serial

outout.

output.

bit-clock

control

for

serial outpur

for

2's comptement

supply

for

2's complement

for

serial

for

MSB-first

input.

outpur.

clock

terminal

input

clock

inout.

(0V).

"H"

=

parallel

output

output.

4.

mooe.

display

(+

display

mode.

serial input.

mode

outpur

5V).

input.

"0L

iq.nf

tii':::

'B;:t

13

Outpur lslch/Output

glElglflrac

timin€ CCT.

oOO@

oooo

No5x

Fis.6-1

Table 6-1

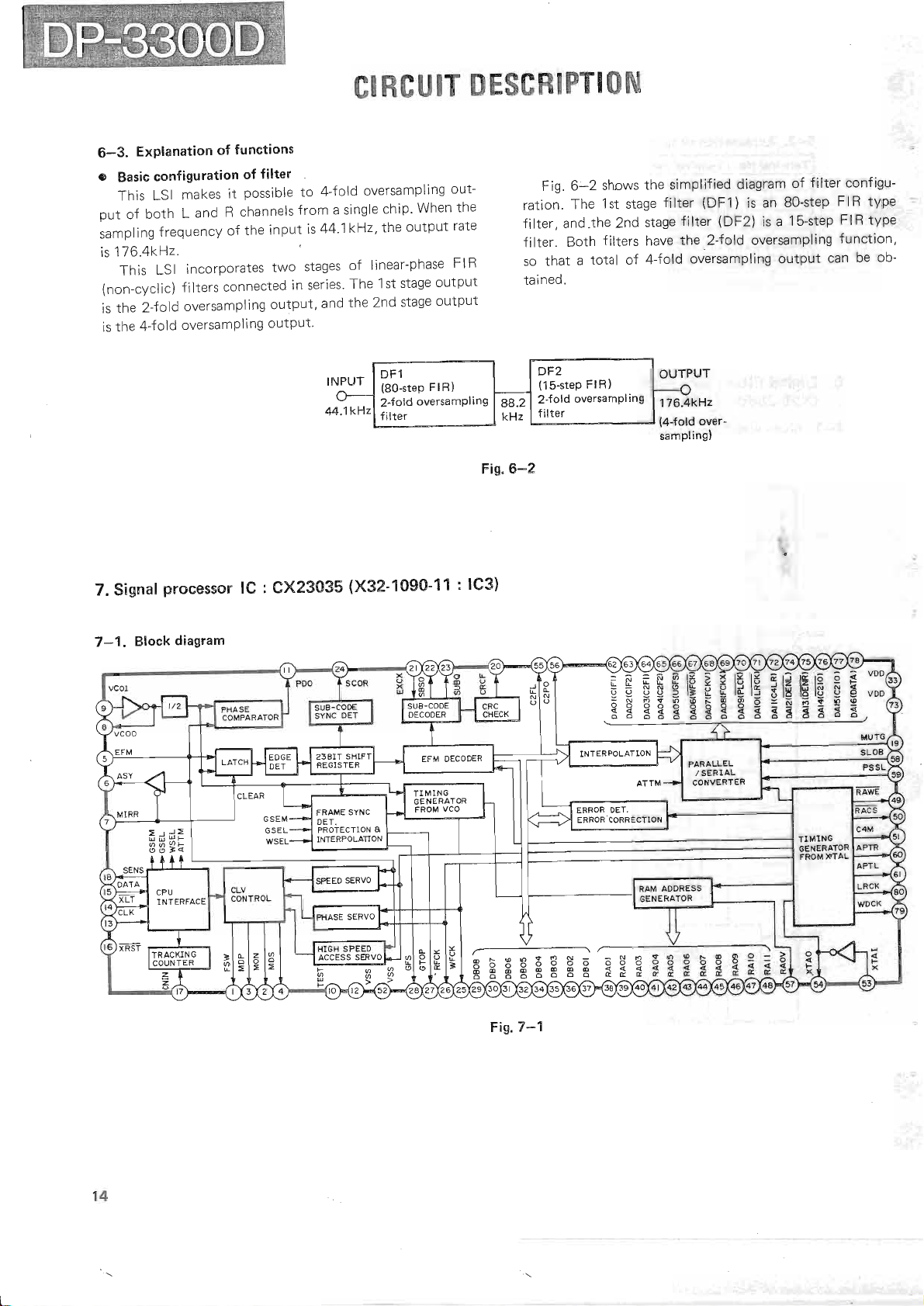

Page 15

CIRCUIT

functions

Explanation

6-3.

o

put

sampling

is

(non-cyclic) filters

isthe2-foldoversamplingoutput,andthe2ndstageoutput

is

configuration

Basic

LSI

This

both

of

frequency

176.4kH2.

LSI

This

4-fold

the

of

filter

of

possible

it

makes

channels

R

and

L

input

the

of

incorporates

connected

oversampling

two

output'

4-fold

to

a single

from

44'1kHz,

is

stages

in series'

oversampling

When

chip'

output

the

linear-phase

of

stage

1st

The

DESCRIPTION

out-

the

rate

FIR

output

Fig.6-2

Fig. 6-2

ration.

filter,

filter.

that

so

tained.

shows

lst

The

and.the

filters

Both

total

a

the

stage

stage

2nd

have

of 4-fold

simplified diagram

(DFl)

filter

filter

the.2-fold

oversampling

OUTPUT

176.4kH2

(4-fold

over-

sampling)

is an

(DF2)

is

oversampling

filter

of

8O-step

15-step

a

output

configu-

FIR

FIR

function,

be ob-

can

type

type

7. Signal

Block

7-1.

processorlC:

diagram

CX23035

(X32-1090-11 : lC3)

Fig.

ERROR DET.

€RROR

EEEHa

7-1

RHgFHsBEEaE

Eg s

99I

;NF

CORRECTION

s

I'

-t

=o

aa

o6

t003uu'

lSUEuoo

eo9

383,

14

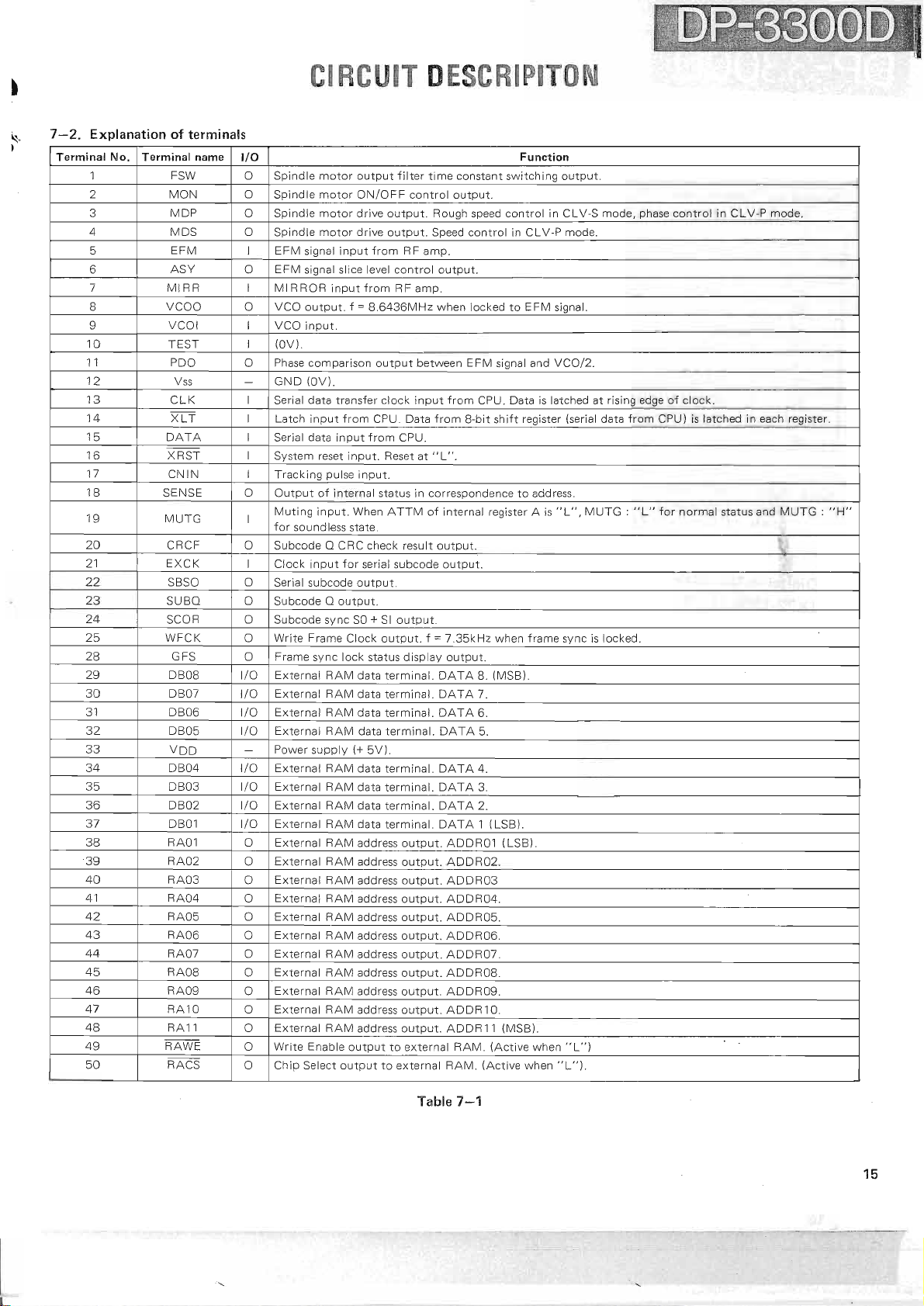

Page 16

CIRCIJIT

DESCRIPITOru

7-2. Explanation

\.

)

Terminal

'39

)L

1Tl

t-

of terminals

No.

Terminal name

1

FSW

2 MON

?

4 MDS

5

MDP o Spindle motor drive output. Rough

EFM EFM

6 ASY o

7 MI

RR IMIBROR

8 vcoo o VCO output. f

vcol VCO

10

11

12

tc

14

15

to XRST

i8

19

20

t1

zz

23

25 WFCK

28 GFS

29

30 DBOT

5t

5Z

33

34 DB04 t/o External RAM

35 DBO3 tlo External

JO

37 DBOl tlo External RAM

38

40 RAO3

41 RA04

4Z

44 RAOT

46 BAO9

47

48 FlA I I

49 RAWE

50 BACS

TEST

PDO

Vss GND

CLK

V'T

DATA

CNIN Tracking

SENSE o Output of

MUTG

CRCF o

EXCK

SBSO o Serial subcode output.

SUBQ o Subcode Q output.

SCOR o Subcode sync

DBOS tlo External FAM data

DB06 t/o

DBOS

VDD

DB02 t/o External RAM

RAOl

FA02

RAOS o External

FAO6

FAOS

RA1

O o External RAM

vo

o Spindle

o Spindle motor ON/OFF control

o Spindle motor drive output.

o

o

o

/o

/o

o

n

o

o External FAM

o External RAM

o External RAM

O External RAM address

o

o External RAM

o Write Enable

o Chip

motor

signal input from RF amp.

EFM

signal

slice

input

input.

tov).

Phase

comparison outpu't between

(OV)

data

Serial

Latch input

Serial

System

Muting

for

Subcode O CRC

Clock

Write

Frame

Exlernal

External

Exlernal

Power

External

External RAM address

External

External

transfer clock input from

from

data

input

reset input. Feset at

pulse

internal status in

input.

soundless state.

for

input

Frame

lock

sync

FAM data

BAM data

FAM data terminal.

supplV

RAM data

FAM address

RAM

FAM

BAM address

Select output to external

filter

output

level control output.

from RF amp.

=

8.6436MH2 when locked to

CPU. Data from

from

input.

When

check

serial subcode output.

SO + Sl

Clock output.

status display output.

(+

5V).

data

data terminal. DATA 2.

data terminal. DATA 1

address output. ADDR03

address output. ADDR04.

address

address output. ADDR06.

address output. ADDR07,

time constant switching output.

output.

speed

control

Speed

EFM

B-bit shift

CPU.

"L"

correspondence

ATTM of

terminal. DATA 8.

terminal. DATA 7.

terminal. DATA 6.

terminal. DATA 4.

terminal. DATA 3.

internal register A is

result output

output.

=

f

7.35kHz when

DATA 5.

output. ADDROl

output. ADDR02.

output.

ADDR05.

output. ADDR08.

output. ADDR09.

address

output. ADDF10.

address output. ADDR1l

output to external RAM.

RAM.

Table 7-1

Function

control

in CLV-P

EFM

signal

CPU. Data

register

to address,

frame

(MSB).

(LSB).

(LSB).

(MSB).

(Active

(Active

when

mode.

(serial

"L",

sync

"L")

"L")

mode,

data

MUTG

is locked.

in CLV-S

sional.

andVCO12.

is latched at rising

when

phase

control

edge

of clock.

from

CPU) is latched in

"L"

:

Ior

normal

CLV-P mode

in

each

and

status

register.

MUTG :

"H"

r ;';

15

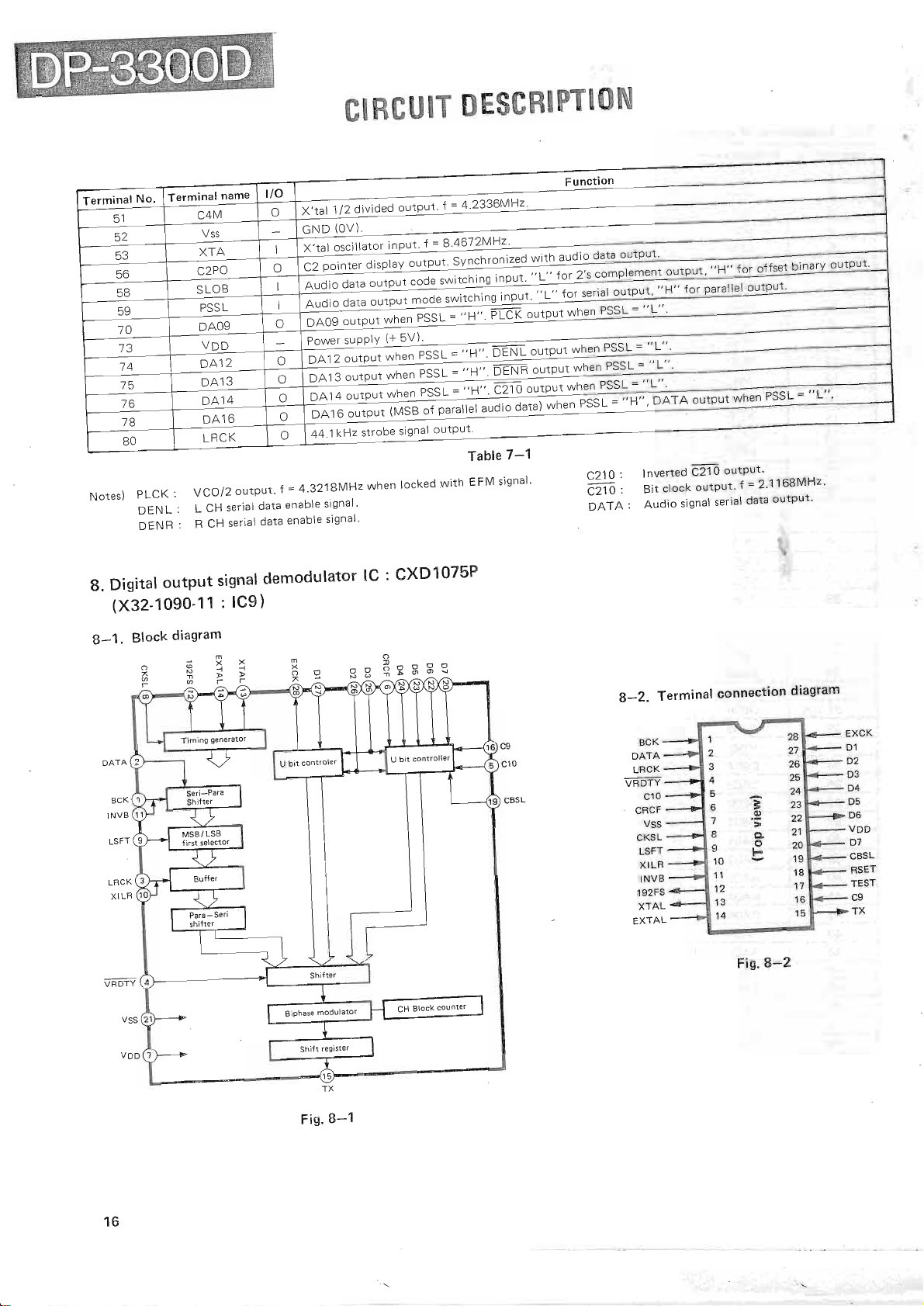

Page 17

Terminal

Terminal

No.

51

52

53

56

58

59

70

-14

75

76

7A

80

Notes)

8.

PLCK

DENL

DENR

Digital

output

(X32-1090-11

name

c4M

Vss

XTA

c2PO

SLOB

DA09

VDD

DA12

DA13

DA14

DA1

LRCK

YCOt2output'

:

CH

: L

R CH

:

signal

: lC9)

l/o

o

I

n

o

o

n

6

o

o

=

t

enable

data

serial

serial

data

enable

demodulator

CIBCUIT

ilffiid"o

f*ut

(OV).

GND

I'.JlIiiu,*

" *

r*.

c

Audio

9ata

oala

A!1i:

suPPlY

Power

outPu

DA12

outpur

DA16

44.1kt12

4'3218w{zwhen

signal'

signat'

outP"

inp"'

"\"d"yJ,

o"lp']

oi:P:;Uf'

(+

5V)'

srgl

strooe

locked

CXD1075P

:

lC

DESCRIPTION

:

=

+'23gonllHt'

t

-

-

=

e'aoz2MH''

+

-!-,1

!"]i^ r,:;;i:;;i;;i;;;

with

*T:

"

Table

EFM

r:

::i

ffiI.tout

NtrNIP

7-1

signal'

ii

;;t;;

li

', ,

iffiilH::;

;::i:;

;;;;;;i;i

when

rt when

C21O:

Tzro

DATA

o*

1=

PSSL

PSSL

,

:

"*"

"*,

"1"

"L"

=

-

lnverted

clock

Bit

Audio

parutt"' ou*out'

to'

o'tPut'

dZT-0

output'

serial

signal

=

2'116BMHz'

f

outpur'

data

t

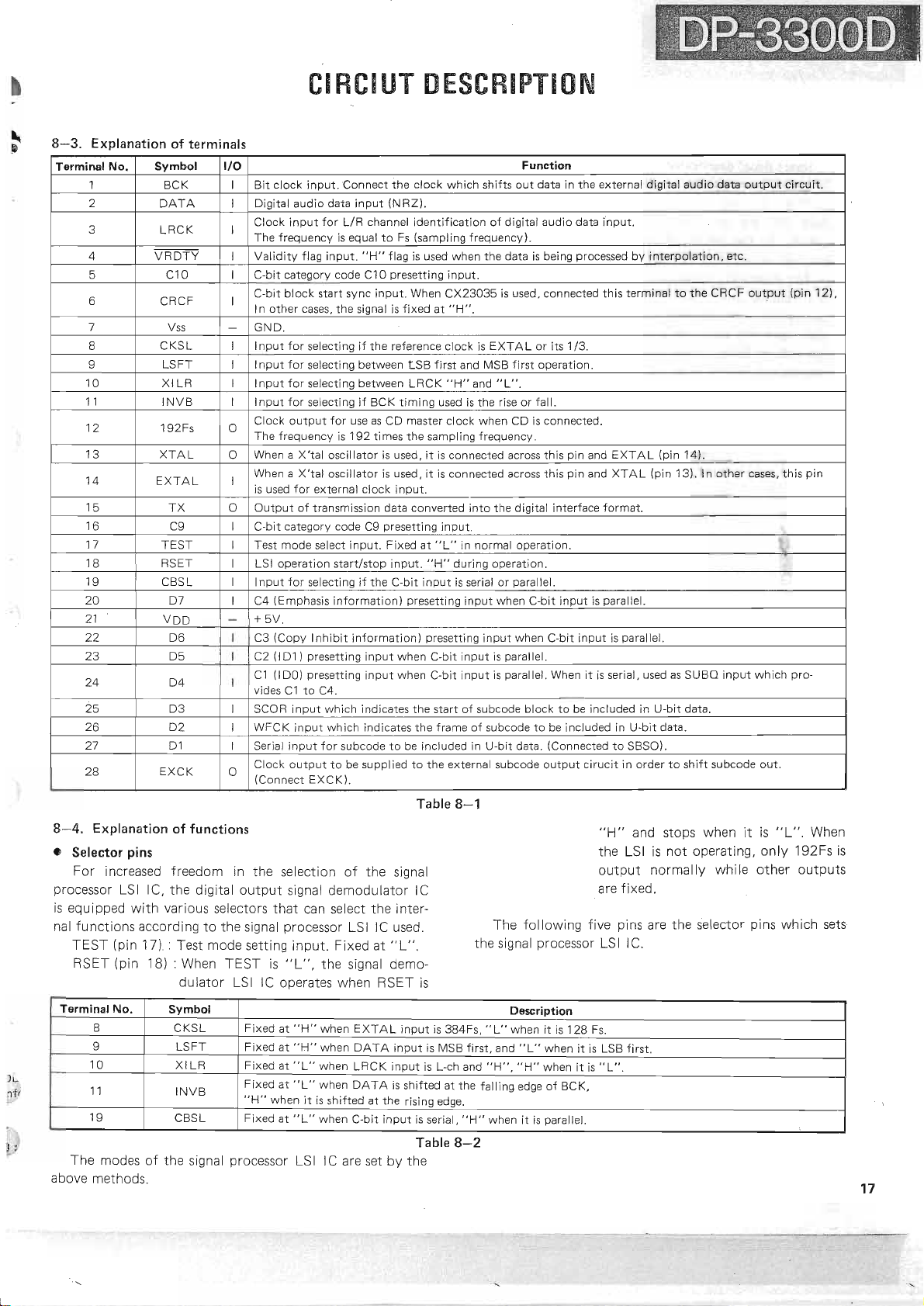

8-1

Block

.

diagram

9x

ii

-f

o

flcsse

8-2.

DATA

LRCK

VRDTY

CFCF

CKSL

I92FS

EXTAL

Terminal

BCK

cl0

vss

LSFT

XILR

INVB

XTAL

connection

t

2

4

o

6

9

10

I

111

I

112

| 13

lra

Fig.8-2

diagram

?I

241

231

221

21

20

19

18

17

't6

15

EXCK

D1

02

D3

D4

D5

D6

VDD

D7

CBSL

RSET

TEST

c9

TX

16

Fig.

8-1

Page 18

!

\

8-3. Explanation

p

Terminal

8-4. Explanation

o

Selector

For

processor

is

equipped with various

functions

nal

TEST

RSET

Terminal No,

)u

eTt

l:

The

above

CIRCIUT

of terminals

No. Symbol

BCK

DATA Digital audio data input

LFICK

4 VRDTY I Validity flag input.

5 cl0

6

LNUT I

7 Vss

8 CKSL Input for

Y

10 XI

11

12

IJ

14

15

to

't

8

IY

20

LSFT Input for

LR lnput

INVB lnput

ts,zrs

XTAL

EXTAL

TX

ItrJt

RSET

CBSL Input

D7 C4

21 VDD

22

ZJ

.A

UO

D5

D4

25 I

26 D2 WFCK

27 D1

28

EXCK

of

pins

increased

LSI

freedom

lC,

the

according

(pin'i

(pin

I CKSL

10

11

IY

modes

:

7)

Test mode setting

:When

18)

Symbol

LSFT

XI

INVB

CBSL Fixed

of the signal

methods.

vo

I

Bit clock input. Connect

Clock input

I

The

C-bit category code C1 0

I

C-bit

I n other cases, the siqnal is fixed at

GND.

Clock output

U

The

When a X'tal

o

When

is used for external

o Output of transmission data converted

C-bit

Test

LSI

+

I

C3

C2

C1

I

vides

SCOR input which indicates the start of subcode block to be included in U-bit

Serial

Clock output to be supplied to the external subcode output

{Connect

functions

in the

output

digital

selectors that

to the

signal

TEST is

dulator

tsl lC operates when RSET

Fixed

Fixed

LB Fixed at

Fixed

"H"

processor

for

frequency

block

L/R channel identification of digital audio data input.

is

start

selecting if the reference clock

selecting between LSB

for

selecting between LRCK

for

selecting if BCK timing used

for

frequency

a X'tal oscillator

category

mode

operation

for

{Emphasis

is

oscillator is used. it

code C9

select inDut.

start/stop input.

selecting if the

information)

5V.

(Copy

Inhibit information)

(lD1)

presetting

(lD0)

presetting

C1 to C4.

which

input

for

input

subcode

EXCK).

selection of the signal

signal demodulator lC

can

select

processor

Fixed

input.

"L",

the signal

"H"

at

when

"H"

at

when

"L"

when

"L"

at

when

when

it

is shifted at the

"L"

at

when C-bit input

LSI lC are

DESCRIPTION

the clock

(NRZ).

equal

to

"H"

Fs

flaq

presetting

sync input. When

use as

CD

192

times the sampling frequency.

used, it is connected

is

clock input.

presetting

Fixed

C-bit

input when

when

input

indicates the

to be

the inter-

lC used.

LSI

"L".

at

demo-

EXTAL

DATA

input is MSB

LBCK

input is L-ch and

DATA

is shifted at

by

set

which shifts

(sampling

is used when the

master clock

at

input

presettinq

included

Table

frequency).

input.

CX23035 is

"H".

firsr

and MSB

"H"

is the

connected acrossthis

is

into

input.

"L"

in normal operation.

"H"

during operation

is serial

input

presettinq

C-bit input

C-bit input is

frame of

8-1

is

input

is 384Fs,

first,

the

risinq edqe.

is serial,

"H"

Table 8-2

the

and

in U-bit data.

Function

out data

data

the external digital audio data output

in

processed

being

is

used, connected this terminal

EXTAL or its 1/3.

is

first

operation.

"L"

fall

rise or

when CD

input when C-bit input is

the

"L"

falling edge of BCK,

is connected.

pin

across this

the digital interface

parallel.

or

when

parallel.

is

parallel.

subcode

The

signal

Doscription

when

"L"

and

"H"."H"

when it is

pin

input is

C-bit

When it

to be

included

(Connected

following five

processor

it is 128 Fs

when

it is LSB

when

it is

parallel.

and

and XTAL

cirucit

by

interpolation,

EXTAL

(pin

format.

parallel.

parallel.

serial, used as

is

in U-bit data.

to SBSO).

in order to shift

"H"

and stops

LSI is not

the

output

are

LSI

"L"

norrnally

fixed.

pins

are the selector

lC.

first.

etc.

to the CBCF output

(pin

14)

13). In other cases, this

input which

SUBO

data.

subcode out.

when it is

operating, only

while other outputs

pins

circuit.

(pin

12),

pin

pro-

"L".

When

192Fs is

which sets

17

Page 19

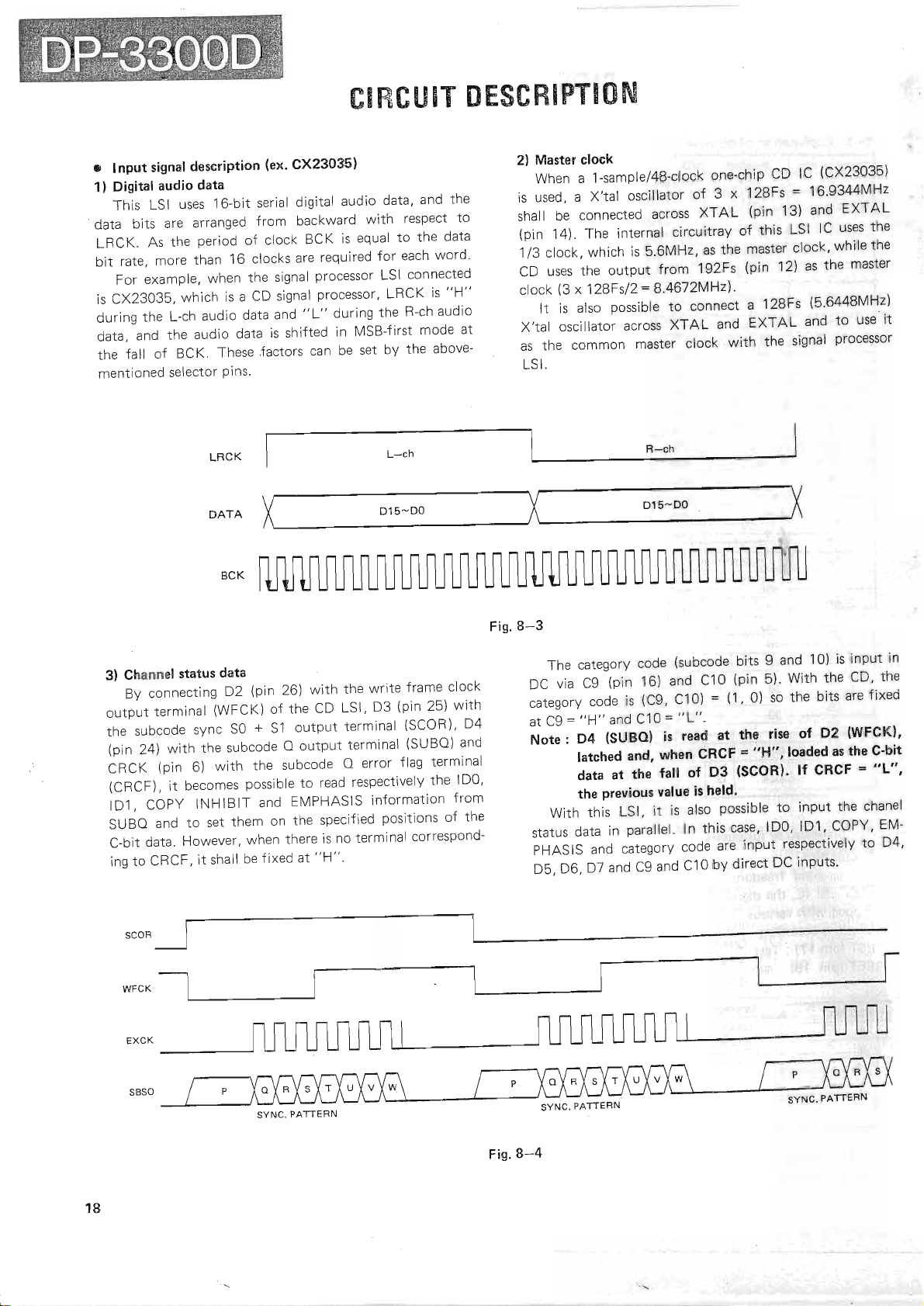

o

1)

data

LRCK.

bit

is

during

data,

the

mentioned

signal

Input

Digiul

LSI

This

bits

As

more

rate,

example,

For

CX23035,

the

and

of BCK.

fall

description

audio

uses

arranged

are

the

than

which

L-ch

audio

the

selector

data

16-bit

period

16

when

is

audio

data

These

Pins.

LRCK

DATA

(ex,

CX23035)

digital

serial

from backward

BCK

clock

of

required

are

clocks

processor LSI

signal

the

processor, LRCK

signal

CD

a

data

"L"

and

is shifted

Jactors

can

CIRCUIT

data'

audio

respect

with

to the

equal

is

each

for

connected

R-ch

the

during

by

mode

the

MSB-first

in

be set

DESCRIPTION

the

and

to

data

word'

"H"

is

audio

at

above-

Master

2)

When

used, a

is

shall

(pin

1/3

CD

clock

It is

X'tal

the

as

LSI.

clock

a 1-sample/48-clock

oscillator

X'tal

connected

be

The internal

14).

which

clock,

the

uses

(3

12BFsl2

x

also

oscillator

common

across

5.6MHz,

is

output

=

possible

across

master

one-chip

x

3

of

XTAL

circuitray

the

as

192Fs

from

8.4672MH21.

connect

to

clock

and

with

XTAL

CD

128Fs

(pin

this

of

master

(pin

128Fs

a

EXTAL

the

(CX23035)

lC

=

16'9344MH2

EXTAL

and

13)

uses

lC

LSI

clock'whilethe

master

the

as

12)

(5'6448MH2)

use

to

and

processor

signal

the

it

Channel

3)

connecting

By

output

the

terminal

subcode

24\

lpin

CRCK

(CRCF),

COpv

iot,

SUBO

data.

C-bit

cRCF,

to

ing

WFCK

status

(wFcK)

sync

the

with

(pin

and

with

6)

it becomes

lNHlBlT

set

to

However,

shall

it

BCK

data

(pin

D2

+

S0

subcode

the

possible

and

them

when

f

be

with

26)

cD

the

of

output

51

O output

subcode

read

to

EMPHASIS

specified

the

on

is no

there

a|"H"

ixed

frame

write

the

(pin

D3

LSl,

terminal

terminal

O

respectively

terminal

'

(SCOR)'

(SUBO)

flag

error

information

positions

correspond-

clock

with

25)

D4

and

terminal

lD0'

the

from

the

of

Fig.8-3

DC

category

at

Note

status

PHASIS

The

C9

With

D5,

category

Cg

via

code

"H"

=

D4

:

latched

data

the

this

data

and

D7

D6,

code

(pin

16)

(C9,

is

C10

and

(SUBO)

and,

the

at

Previous

LSl,

parallel.

in

category

C9

and

it

(subcode

and

C10)

"L"'

=

read

is

CRCF

when

of

fall

is

value

also

is

In

code

C10

and

(pin

CiO

=

(1'

at

D3

held'

possible

case'

this

are

direct

bv

and

9

bits

5)'

so

0)

rise

the

"H"'

=

(SCORI'

to

lDO'

respectively

input

DC

input

is

10)

CD'

the

With

are

bits

the

(WFCK)'

D2

of

the

as

loaded

CRCF

lf

the

input

lD1' COPY'

inputs'

in

the

fixed

C'bit

"L"

=

chanel

EM-

D4'

to

'

18

EXCK

SBSO

SYNC.

PATTERN

Fig.

8-4

Page 20

I

CIRCUIT

DESCRIPTION

User-definable

\

3

4)

The U-bit

code. Similarly to C-bit data,

imposed

signal

D3{SCOR}

D4(suBol

D2{WFCK)

lnternal

register

by

demodulator LSl.

CRCF

data

data

supplying

reserved

is

for

inch:ding the CD

the CD

the CD LSI output directly to the

-rr-r

v

lp0(1lv

subcode

rTr l-r l-rz- r l-r l-r r-r l-r l-

lp1(1)

rD0{0), rD1

can be

vcopy(1xEMp(1)\____

(0),

coPY{o}, EMP(ol

sub-

super-

When

(pin

25), EXCK

CD LSl, it

(pin

D1

27).

WFCK

outputs

is input to D2

28) is output. When

{pin

SBSO

rootzlXrortzlrcopvtztY

X

rD0(1

(pin

(subcode

(1

lDl

1,

26) and

data),

COPY(1

),

SCOR to D3

EXCK

is input

which

is

euptztv

Er,rP(l

),

input

)

to

to

Fis.8-5

Pu

NU

r.'

5) Validity

For

LRCK to VRDTY

flag

validity flag,

apply

(pin

4)

as shown in Fig.

the

flag

synchronized

g-6.

LFCK

DATA

VNDTY

Fis.8-6

t3

i;.',li |

:'r:

;i;:r:r,:.1

19

Page 21

CIRCUIT

DESCRIPTION

9.

Microcomputer:

9-1.

Terminal

9-2.

Terminal

connectiondiagram

Explanation

No.

5

6

7 SUBO O data

8 O

I

10

11

1a

IJ RMUTE

14

i5 DI RC

tb MUTG

'1

8

19 OPN SW

20 CLS SW

11 -aA

25 DATA

zo XLT

27 CLK

28 LDC o Laser ON/OFF

30

JI x2

32 Vss GND.

35

36

38

JY

40-51

AA

55 PK

56

57

5B

59

60

-63

61

64

pPDTS2OBCW-O4O

o

'od

(X32-1090-11

HB .-.

E s9 c irg i*

9 9 a o

e

: l0l1)

u 3 E

33S68ESEE333$689e5€9$SSE9gSDgggs

FNO{o@F@OFF_

f,8eHX

zi

a=

OFNO:P9:P9RFN&SRRRRRSES

gbe

H

6o

?Eg:Eiil""uevn!:sErrs

of terminals

Terminal name

-Pa

Pd

SENSE

WFCK

RCI Remote

SCOR O data sync

FOK

GFS

EMPH

SLT SW

-K4

Ki

XRTS

X1

OPNM o Tray open/close signal output. Normally OPNM

CLSM o

INV

R ESET

G1-G'1 2

PI

VLOAD

VPRE

Pj

Pi

KO

Pq-Pe

VDD

t/o

o

F L tube

segment

SENSE sisnal

readout

data

O

input

dara

CRC OK

control siqnal input.

Focus OK

EMF

sync

o Relay muting

Emphasis

o

o DIRC signal output

MUTG

o

siqnal output

Start limit SW signal

Tray open SW signal input

Tray close SW signal input

Main unit key

o Control data signal output

display

input

clock input

(from

("H")

signal

("H")

input

("H")

OK

ON/OFF

ON/OFF

inputs.

outputs.

(from

CX23035, CX20108).

(from

CX23035).

input

(from

input

(from

(from

input

('L"l"H"l

('L"l"H"l

(to

CX20109).

for mutins

(SW

input

(SW

(SW

(to

o Control data Iatch siqnal output

o Control

o Control reset

o

o

o

o

o

o

o

o

o

data clock

oscillation X'tal connection

Clock

(Oscillation

For opening,

lnvert

ON/OFF

Reset

signal input.

FL tube

FL

GND.

GND.

FL tube

Key

F

+

digit display output.

tube

segment

segment display

output

sense

L tube

segmen-t display output

5V.

signal output

('H"

output

signal

f requency

OPNM

('H"

display output.

signal.

sisnal

/"L"1

(to

=

4.1 94MHz).

"H"

:

and CLSM

/"L"\signal

output.

CX23035).

(from

CX23035).

CX23035).

CX2O109)

CX23035).

signal

output.

signal

ON/OFF

"L").

:

ON

"L")

:

ON

"L")

:

ON

CX23035, CX20108).

(to

CX23035, CX20108).

(to

CX23035,

output.

CX23035,

ter.minals

output.

3

D 3 3

Function

output.

('H"/"L"| (to

CX20108).

CX20108).

"L".

For

:

s 6

s

CX23035).

"L"

:

and CLSM

closing, OPNM

z=aizz

"L".

:

"L"

:

and CLSM

Fig.9-1

"H".

:

Table

9-1

20

Page 22

F;

w

p

I

ADJUSTMENT

1. Adjustment

t

l.

No.

YCO

LASEB

(Yhen

o be defective

RF

4 IEST

SETT

q

TANCENT

sErT I t{c

FOCUS

o

OFFSET

AD

J

7

8

9

l0

t1

T.

BALANCO

AD

J

TA],{GENT

AND FOCUS

OFFSET

AD

UST}ll ENTS

J

T.

BALA

II{E ADJUST]ilENT

FOCUS

,4 DJ

TRACI(

IDJ USTIjE],{T

ITI}I

ADJUSTMENT

POYER

CIIECI{

PU

seems

OFFSET

CH EC(

}I{ODI

I NG

I,{L

I NG

COARSE

UST}i1ENT

ERROR

COARSE

USTII ENT

IAL

I

}iG

F I NE

ERROR

NC E

CA ] N

UST}lENT

JNG

GA Il{

I NPUT

SETT I IiGS

Place

test di

Type

ol the

tray,

and colnplete

Ioading.

Place

test dis

Type

on

the tray,

and conp

loading.

Place

test

Type

on

the

tray,

and

complete

loading.

Place

test

Type

on

the

tray,

and conpl

Ioading.

Place

test dis

Type

the

tray,

loading.

test

Type 4

the

tray,

corl)pl

loading.

a

on

the

and con-

loading.

700H2,

Vrns

2 of

CN2

-1780

a

test

on

the

and coln-

loading.

lrnrs to

4 of

CN2

-1780

-00

4

test

-00.

on

and conpl

Place

on

and

Place

disc

tray

plete

Appiy

0.4

in

x29

Place

disc

tray

plete

Apply 900H2,

0.4

tin

.tr29

f-counter

(Gl'lD)

and

Place

on

an osci I

pin

of

X29-1780-00.

the oscilloscope's

GND

4

4

I et

dis

4

disr

4

ete

ete

dis

ete

to

of

of

Short-circuit

the

of X32-1090-i1(A/4)

an

osciiloscope

to

e

ol X29-1090-00.

an

osci

to

of

X29-1090-00.

Connect

CHI

to

CN4

of

and

to

an

osci

to

of X29-1780-00.

Connect

CH1

to

CN4

of

and connect

to

LOnnect

pin

to

of

I29

and

oscilloscope

AC

Connec!

pin

to

of X29-1780

and

an osc i I loscope

AC vo

OUTPUT

SETT I IiCS

Connect

an

across

TP1

of )(32-1090-11

(PLC()

TP10

an

opt ical

power

|Ileter

pickup.

the

Con

nec

t

loscope

(RF)

2

Connec

TPl

to

connector

of CNl0

Con

nec

pin

of

CN4

Con nec

I loscope

pin 2 (RF)

of

CN4

oscilloscope

pin 2 (RF)

X29-1780-00,

connect

pin 3 (TE).

Colnec

I loscope

pin

of CN4

osci I loscope

pin 2 (RF)

X29

pin 3 (TE).

1 of CN2

-1780

connect

voltlireter.

5

connec

I

tneter.

of

t

(GND).

t

(RF)

2

t

CH2

t

(RF)

2

-1780

CH2

L_f.f

-00,

L.P.F

of CN2

-00,

t

to

Cll4

(A/4)

of

of

-00,

or

or

PLA

SETT I I,{GS

Tray

or stop

-open.

Tray

Connect

1090-11

O

set

TP8

(A/4)

During

the CHECK

Tray opens

the LD

is

Tray open,

or stop

Turn

P0}{Efi

then 0N

Press

CIIECK key.

Ihe

laser

ttill

be

(Test

Press

CHEC(

The laser

will

be focused.

(Test

Press

CHECK

The I aser

vill be

(Test

Press

(Tracing ,till

PLAY

(Test

Press

CIIDCI(

(Focusing

y

on I

(Test

Turn POilER

then 0N again.

press

Then

o start

nornal

Nornal

play

YBR

open,

mode

of X32-

to G}lD

test mode,

key

0N

and

turned 0N.

mode.

S[ OFF

again.

focused.

node)

key.

mode)

key.

focused.

node)

key.

start

node)

key.

servo

rnode)

mode)

Sll OFF

PLAY key

play.

AL

I G l{}lENT

P0l

l,lTS

Turn

core

coil

of

of L2 of

x32-1090-11

$/4).

Hex

recessed

scre,r

below

nechanism

Turn

YR2 of

)(29-1780-00.

Turn

VB1 of

)(29-1?80-00.

YR2 of

x29-1780-00,

hex

recessed

scretr

below

nechanism.

l/RI

Turn

x2

Turn

I

-l

-00

780

VR3

of

of

x29-1'i80-00.

Turn

VR4 of

x29-1780-00.

AL I OlI FOR

4.32MHz

0(

if

p{

100

the

and

the

T.ERR0R

synmetrical

below

Turn

to

Adjust

to approx.

-0.70

Check

display

The

displfy

shal

l be 03\0,

anplitude

ilaximum

Adjust

arnpiitude

(V). (Photo

0

YR2 and

ampl

so

recessed screw

to obtain

Adjust

voltneter

Adjust

voltneter

opt itrrun

Adjust so

T.ERROR

sYnnelrical

below

arnplitude

(V). (Photo

0

so

that

or

indicate

so

that

oscilloscope

40 rnVrms.

or oscilloscope

indicate

40 mVrns.

from

200

zI

(v).

that

is 01

oo

naxinum.

itude.

that

is

above and

5)

hex

alternately

waveforn

that

is

above and

the

5)

AC

the AC

FIG,

(a)

(b)

(c)

(d)

(e)

(e)

(f)

(e)

(f)

(s)

(s)

21

:

Page 23

I2

Effective

2.

No,

1

5

,{DJUSTIIENT

DAC

I

keys

Input