Page 1

SERVICE MANUAL

DVD AUDIO/VIDEO PLAYER

XV-D9000

Area Suffix

J ------------- U.S.A.

XV-D9000

Contents

Safety precautions ------------------------ 1-2

Preventing static electricity ------------- 1-3

Dismantling and assembling

the traverse unit ----- 1-4

Important for laser products ------------ 1-5

Importance admistering point

on the safety ----- 1-6

Disassembly method -------------------- 1-7

Method of initializing EEPROM

and display of jitter value ----- 1-18

Description of major ICs ---------------- 1-19

This service manual is printed on 100% recycled paper.

COPYRIGHT 2001 VICTOR COMPANY OF JAPAN, LTD.

No.A0004

Mar. 2001

Page 2

XV-D9000

1. This design of this product contains special hardware and many circuits and components specially

for safety purposes. For continued protection, no changes should be made to the original design

unless authorized in writing by the manufacturer. Replacement parts must be identical to those

used in the original circuits. Services should be performed by qualified personnel only.

2. Alterations of the design or circuitry of the product should not be made. Any design alterations of

the product should not be made. Any design alterations or additions will void the warranty

and will further relieve the manufacture of responsibility for personal injury or property damage

resulting therefrom.

3. Many electrical and mechanical parts in the products have special safety-related characteristics.

These characteristics are often not evident from visual inspection nor can the protection afforded

by them necessarily be obtained by using replacement components rated for higher voltage,

wattage, etc. Replacement parts which have these special safety characteristics are identified in

the Parts List of Service Manual. Electrical components having such features are identified by

shading on the schematics and by ( ) on the Parts List in the Service Manual. The use of a

substitute replacement which does not have the same safety characteristics as the recommended

replacement parts shown in the Parts List of Service Manual may create shock, fire, or other

hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the

like to be separated from live parts, high temperature parts, moving parts and/or sharp edges

for the prevention of electric shock and fire hazard. When service is required, the original lead

routing and dress should be observed, and it should be confirmed that they have been returned

to normal, after reassembling.

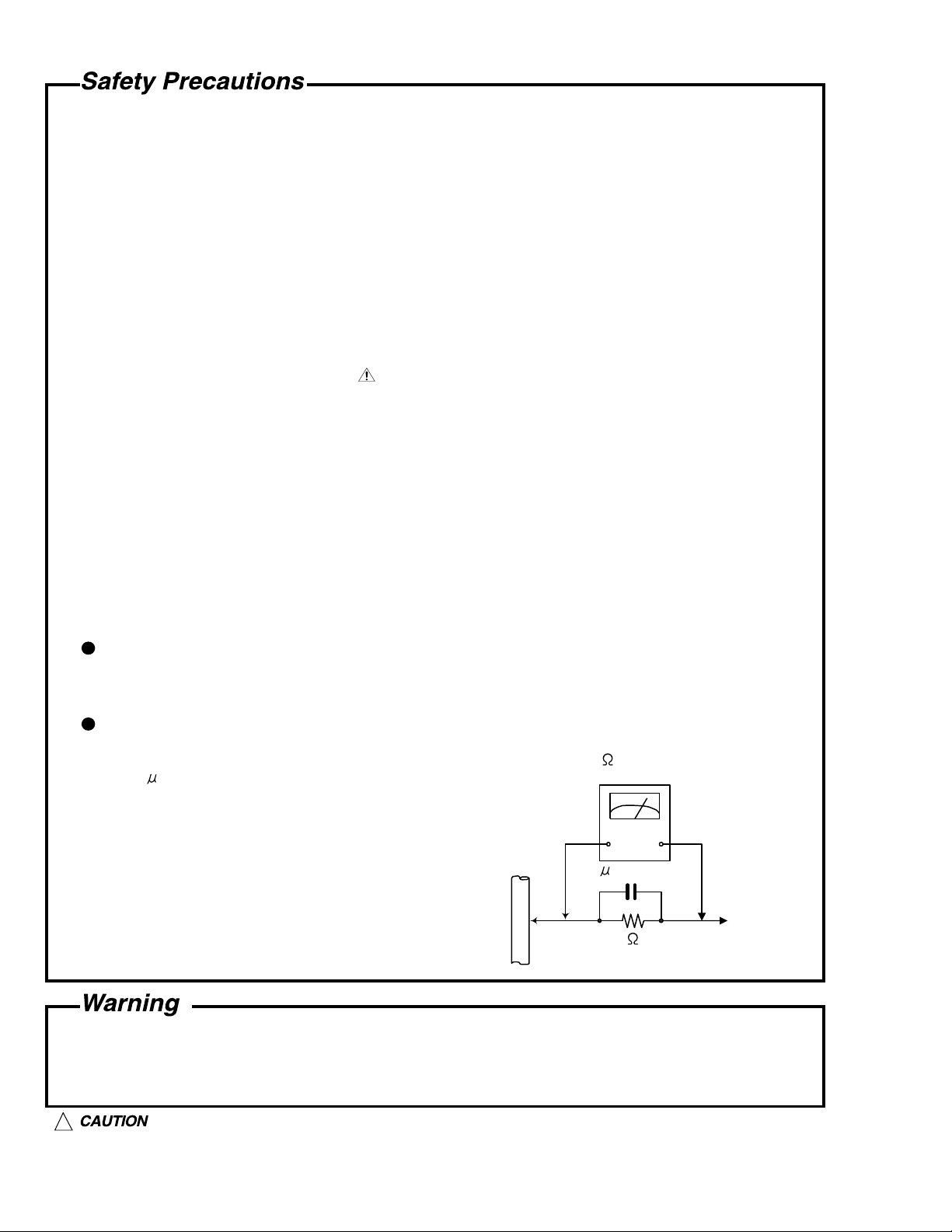

5. Leakage current check (Electrical shock hazard testing)

After reassembling the product, always perform an isolation check on the exposed metal parts of

the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control

shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure

the leakage current from each exposed metal parts of the cabinet , particularly any exposed

metal part having a return path to the chassis, to a known good earth ground. Any leakage

current must not exceed 0.5mA AC (r.m.s.)

Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms

per volt or more sensitivity in the following manner. Connect a 1,500 10W resistor paralleled by

a 0.15 F AC-type capacitor between an exposed

metal part and a known good earth ground.

Measure the AC voltage across the resistor with the

AC voltmeter.

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

Move the resistor connection to each exposed

metal part, particularly any exposed metal part

having a return path to the chassis, and measure

the AC voltage across the resistor. Now, reverse

the plug in the AC outlet and repeat each

measurement. voltage measured Any must not

0.15 F AC TYPE

1500 10W

Place this

probe on

each exposed

metal part.

exceed 0.75 V AC (r.m.s.). This corresponds to 0.5

Good earth ground

1. This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

3. Repairs must be made in accordance with the relevant safety standards.

4. It is essential that safety critical components are replaced by approved parts.

5. If mains voltage selector is provided, check setting for local voltage.

!

Burrs formed during molding may be left over on some parts of the chassis. Therefore,

pay attention to such burrs in the case of preforming repair of this system.

1-2

Page 3

XV-D9000

Preventing static electricity

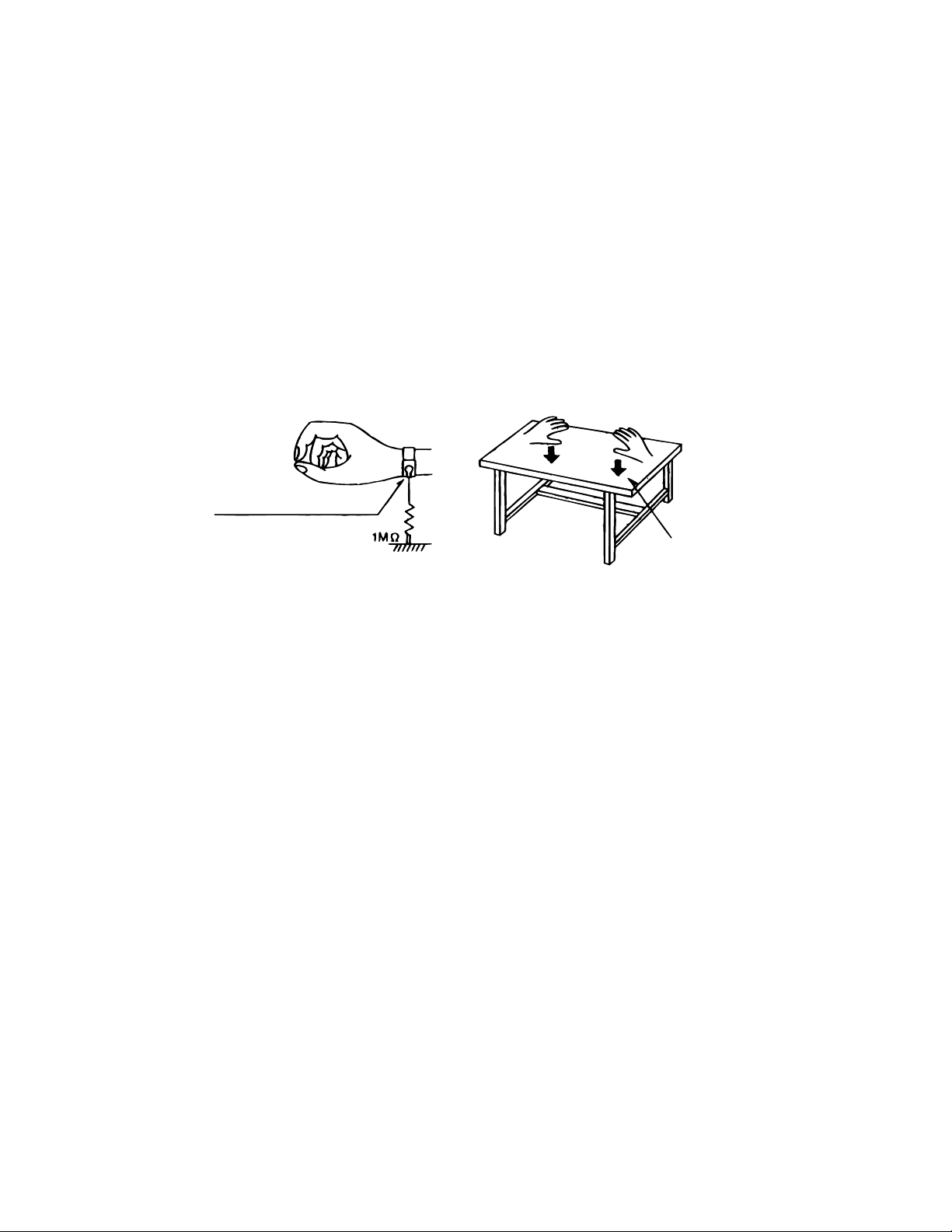

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players.

Be careful to use proper grounding in the area where repairs are being performed.

1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over

it before placing the traverse unit (optical pickup) on it.

1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

(caption)

Anti-static wrist strap

Conductive material

(conductive sheet) or iron plate

1.1.3. Handling the optical pickup

1. In order to maintain quality during transport and before installation, both sides of the laser diode on the

replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition.

(Refer to the text.)

2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power

source can easily destroy the laser diode.

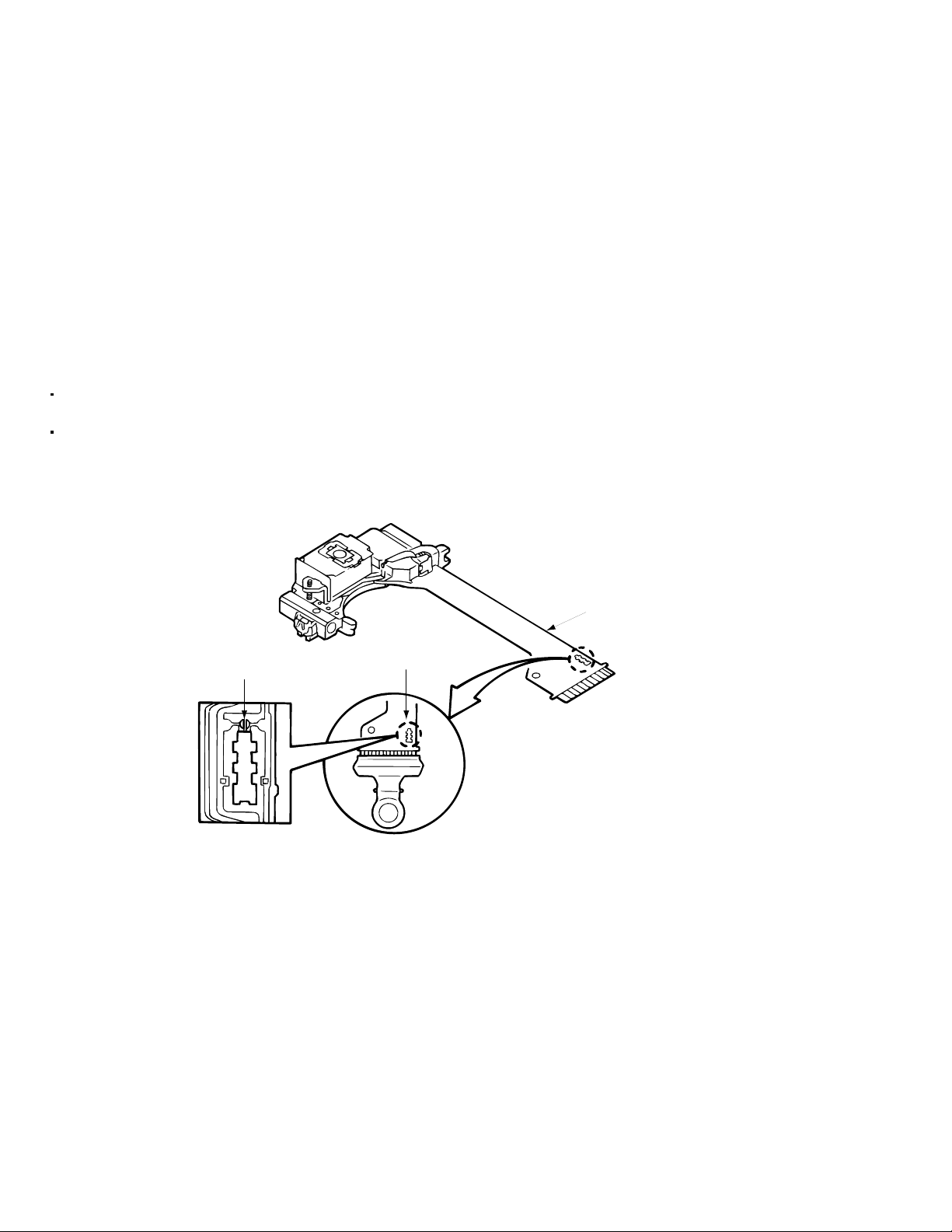

1.2. Handling the traverse unit (optical pickup)

1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific

details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse

unit. Be careful not to take too long a time when attaching it to the connector.

3. Handle the flexible cable carefully as it may break when subjected to strong force.

4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

1-3

Page 4

XV-D9000

Dismantling and assembling the traverse unit

1. Notice regarding replacement of optical pickup

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing

repairs to the optical pickup or connected devices.

(Refer to the section regarding anti-static measures.)

1. Do not touch the area around the laser diode and actuator.

2. Do not check the laser diode using a tester, as the diode may easily be destroyed.

3. It is recommended that you use a grounded soldering iron when shorting or removing the laser diode.

Recommended soldering iron: HAKKO ESD-compatible product

4. Solder the land on the optical pickup's flexible cable.

Note : Short the land after shorting the terminal on the flexible cable using a clip, etc., when using an

ungrounded soldering iron.

Note : After shorting the laser diode according to the procedure above, remove the solder according

to the text explanation.

Short circuit land

Laser pick-up unit

Flexible cable

Shorting

Shot with the clip

1-4

Page 5

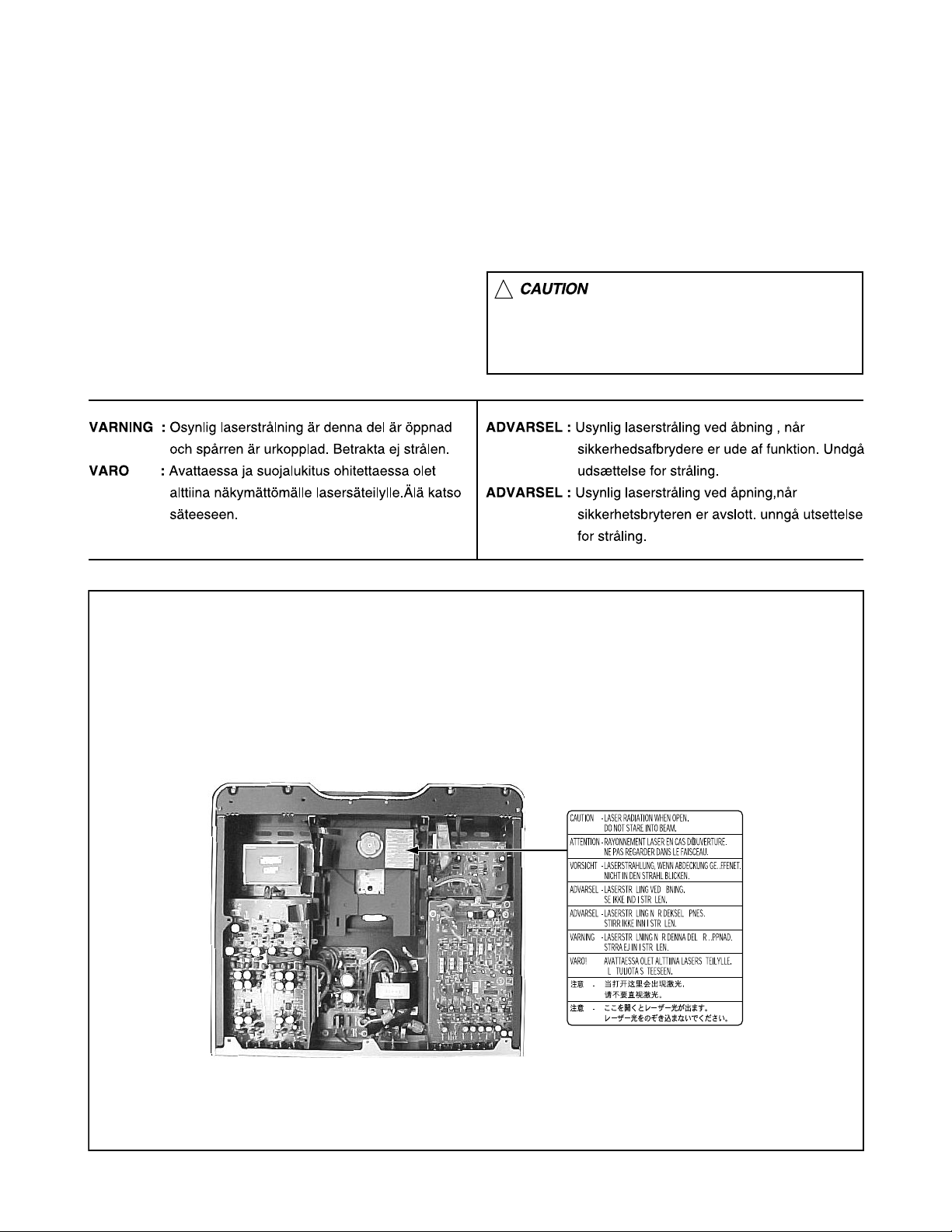

Important for Laser Products

XV-D9000

1.CLASS 1 LASER PRODUCT

2.DANGER : Invisible laser radiation when open and inter

lock failed or defeated. Avoid direct exposure to beam.

3.CAUTION : There are no serviceable parts inside the

Laser Unit. Do not disassemble the Laser Unit. Replace

the complete Laser Unit if it malfunctions.

4.CAUTION : The compact disc player uses invisible laser

radiation and is equipped with safety switches which

prevent emission of radiation when the drawer is open and

the safety interlocks have failed or are de

feated. It is dangerous to defeat the safety switches.

5.CAUTION : If safety switches malfunction, the laser is able

to function.

6.CAUTION : Use of controls, adjustments or performance of

procedures other than those specified herein may result in

hazardous radiation exposure.

!

Please use enough caution not to

see the beam directly or touch it

in case of an adjustment or operation

check.

REPRODUCTION AND POSITION OF LABELS

WARNING LABEL

1-5

Page 6

XV-D9000

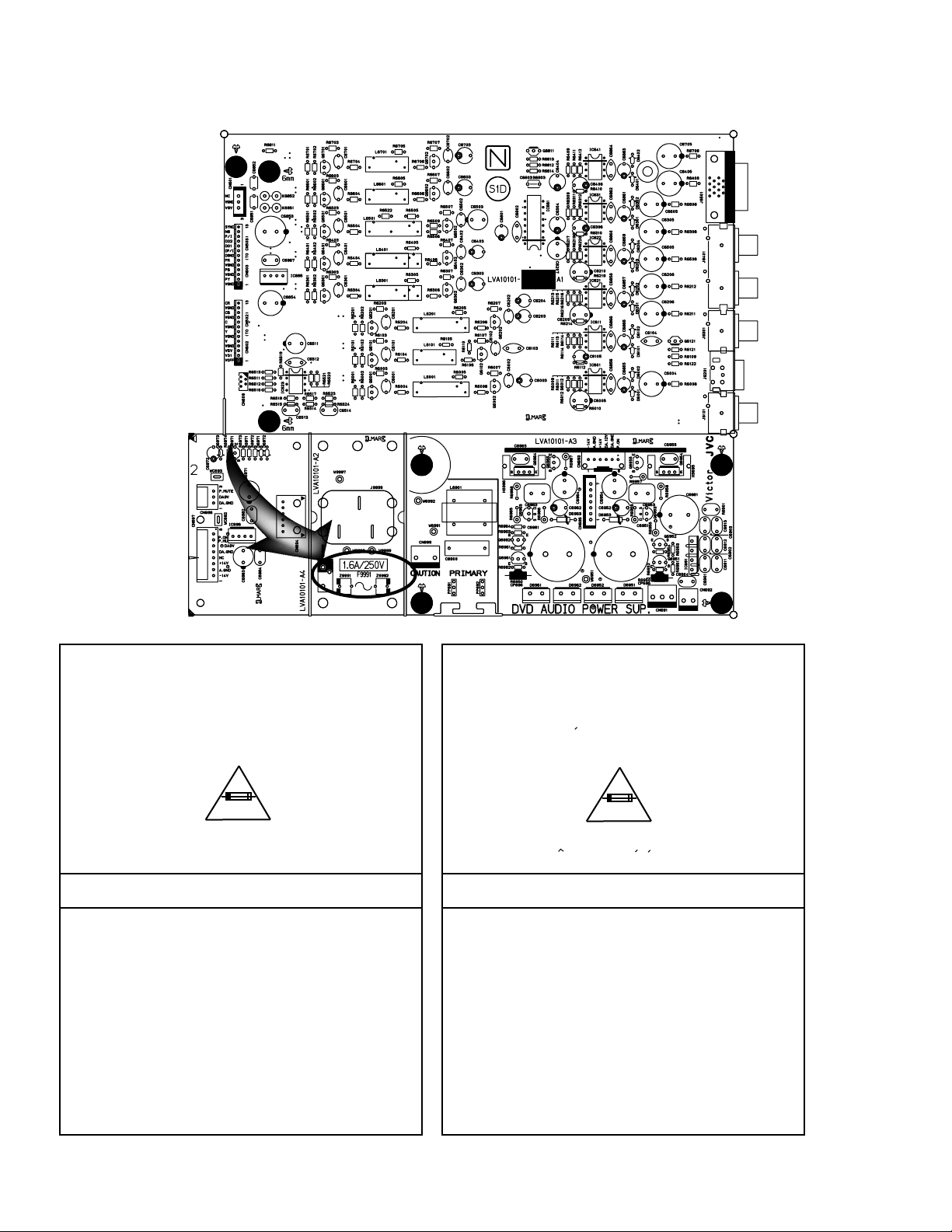

Importance Admistering point on the Safety

Full Fuse Replacement Marking

Graphic symbol mark

(This symbol means fast blow type fuse.)

should be read as follows ;

FUSE CAUTION

FOR CONTINUED PROTECTION AGAINST RISK

OF FIRE, REPLACE ONLY WITH SAME TYPE

AND RATING OF FUSES ;

F9991 : 1.6 A / 250 V

Marquage Pour Le Remplacement

Complet De Fusible

Le symbole graphique (Ce symbole signifie

fusible de type a fusion rapide.)

doit etre interprete comme suit ;

PRECAUTIONS SUR LES FUSIBLES

POUR UNE PROTECTION CONTINUE CONTRE

DES RISQUES D'INCENDIE, REMPLACER

SEULEMENT PAR UN FUSIBLE DU MEME TYPE ;

F9991 : 1.6 A / 250 V

1-6

Page 7

XV-D9000

Disassembly method

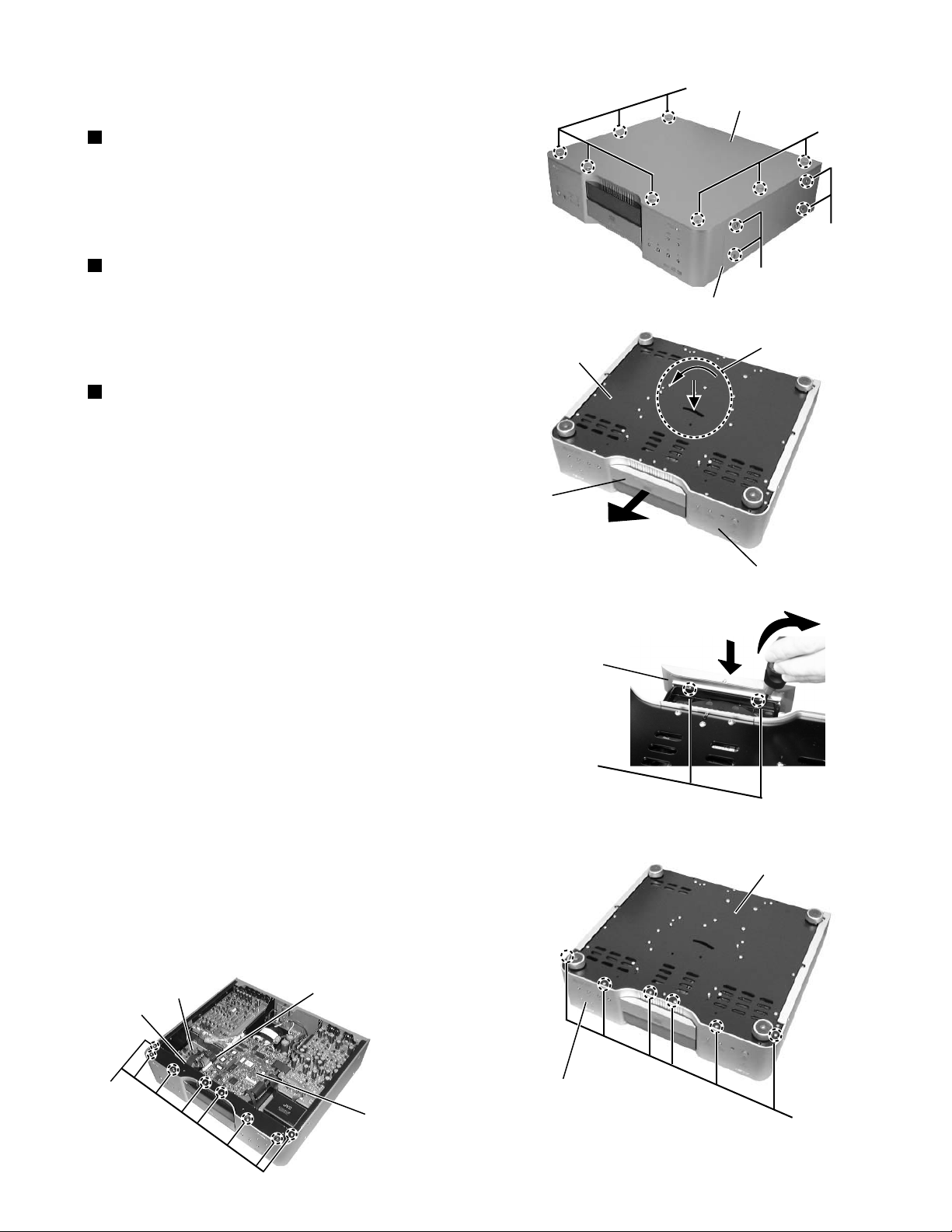

<Main body>

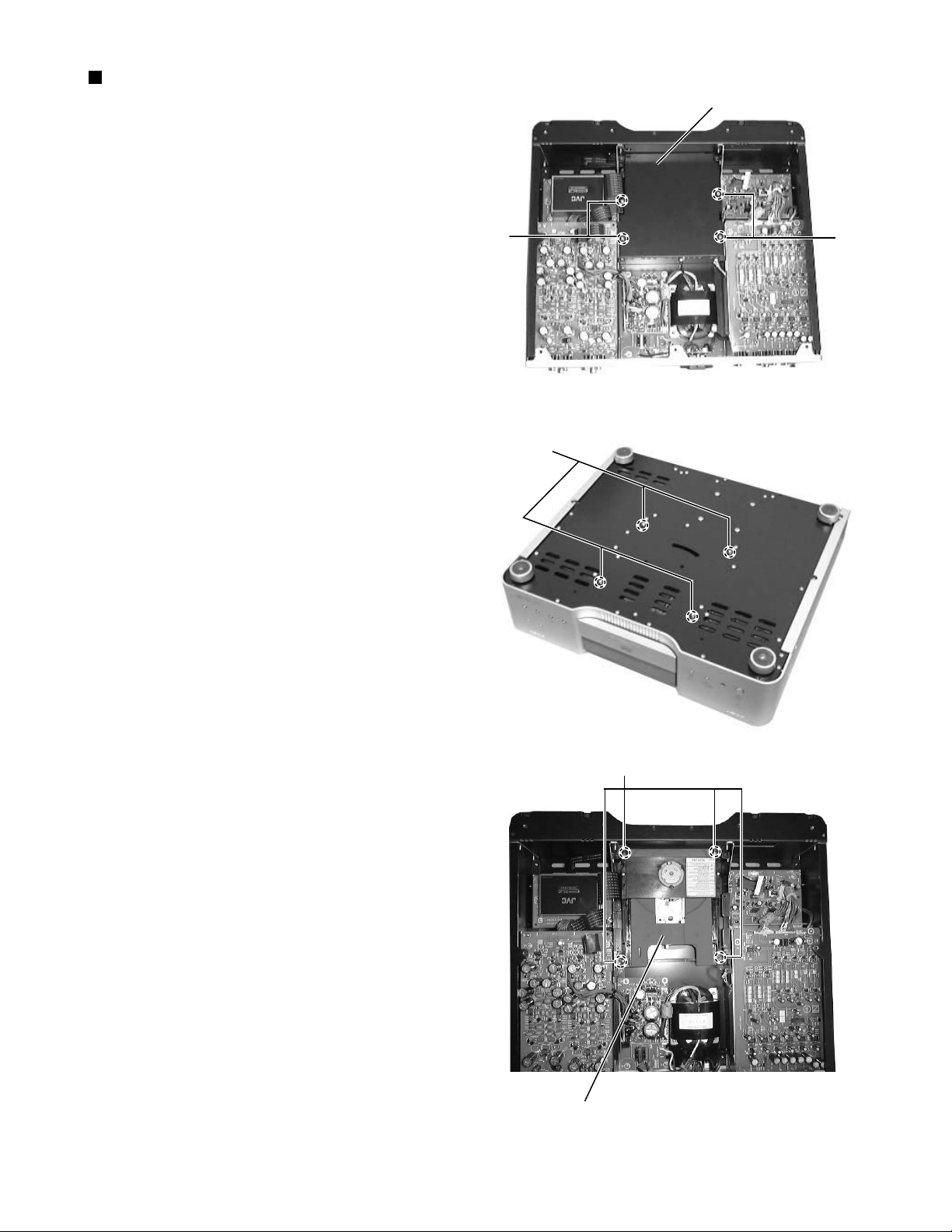

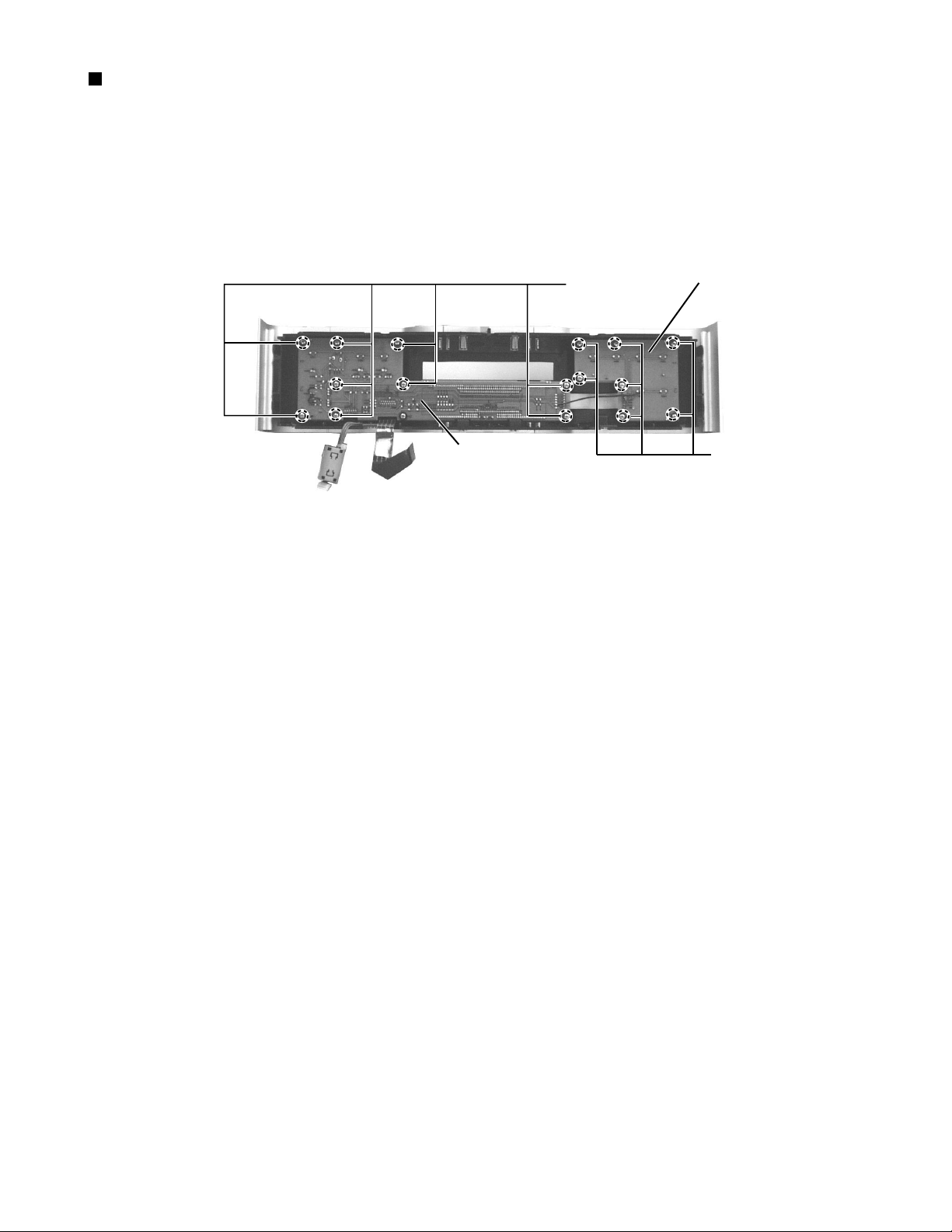

Removing the top panel(See Fig.1)

1.Remove the eight screws A by hexagonal driver

attaching the top panel.

2.A top panel is lifted up and it is removed.

Removing the side panel(See Fig.1)

1.Remove the four screws B by hexagonal driver

attaching the side panel.

2.The left side also similarly removes the side panel.

Removing the front panel assembly

(See Fig.1~5)

*Prior to performing the following procedure, remove

the top panel.

1.The bottom of the main body is done up.

2.A minus driver is inserted in the incision part at the

center of the bottom, the bar in the interior of the

incision part is moved in the direction of the arrow of

Figure 2, and the tray is drawn out forward.

Fig.1

Bottom plate

Tr ay

Fig.2

A

Top panel

Side panel

Front panel assembly

A

B

B

Incision part

3.Hook a which connects the tray covers to the tray is

removed by a minus driver etc. , the tray cover is

pushed downward, and removes.

4.Remove the six screws C attaching the front panel

assembly.

5.The top of the main body is done up.

6.Remove the eight screws D attaching the front panel

assembly from the upper side of main body.

7.Disconnect the wire from connector CN507 on the main

board and CN981 on the power supply board.

8.It comes off when the front panel assembly is drawn out

forward.

Power supply

board

CN981

CN507

Tray cover

Hook a

Fig.3

Bottom plate

D

Main board

Fig.5

Front panel assembly

Fig.4

C

1-7

Page 8

XV-D9000

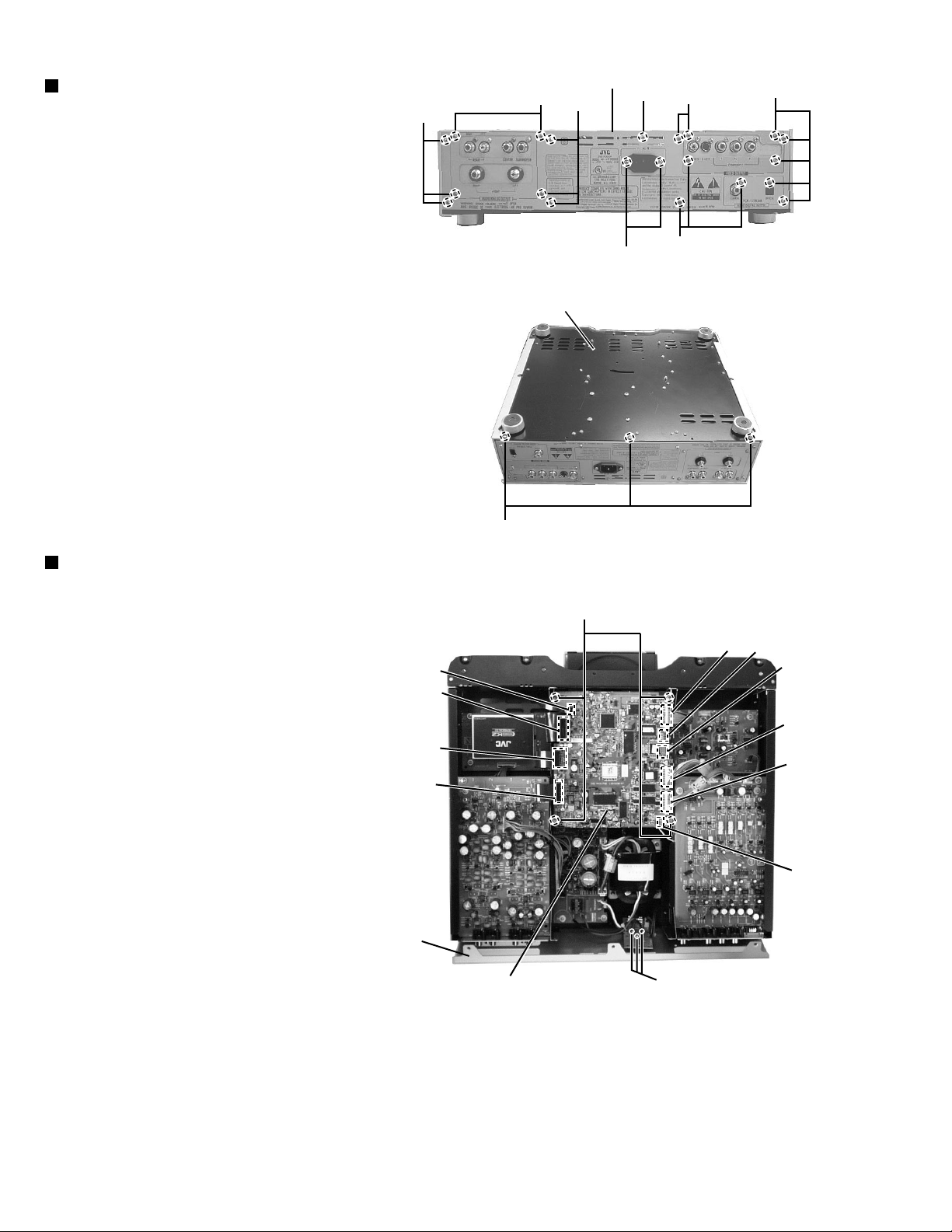

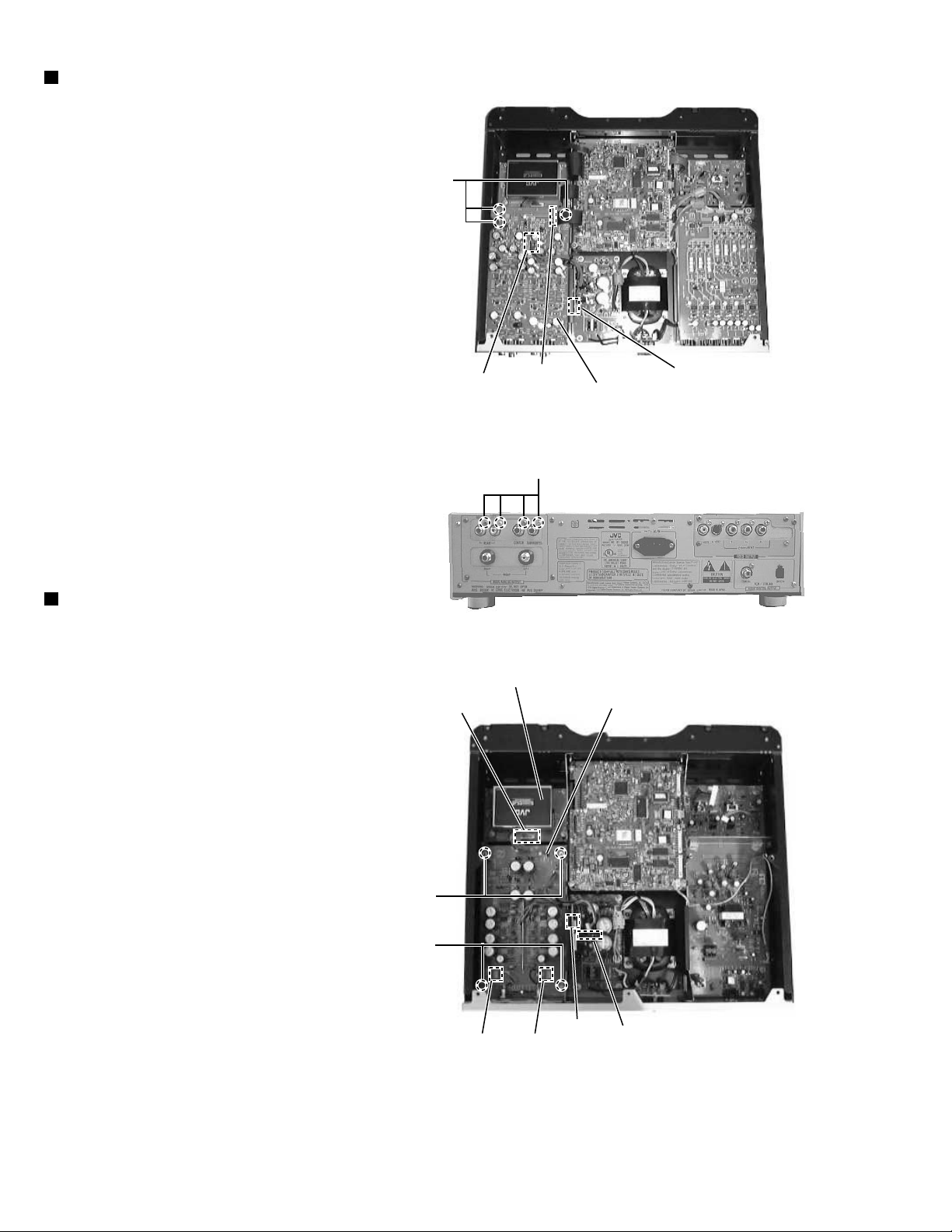

Removing the rear cover(See Fig.6~8)

*Prior to performing the following procedure,

remove the top panel.

1.Remove the eighteen screws E attaching the

rear cover from back of the main body.

2.Remove the three screws F attaching the

bottom plate from back of the main body.

3.Solder on the power supply board is removed

by three places.(See Fig.8)

4.Remove the two screws G attaching the

AC socket and one screw G' attaching the

power supply board.

Rear cover

G'

E

E

E

Fig.6

G

E

E

E

Bottom plate

Removing the main board(See Fig.8)

*Prior to performing the following procedure,

remove the top panel.

1.Remove the four screws H attaching the

main board.

2.Disconnect the connector from CN101,CN103

CN504,CN505,CN501,CN502,CN503,CN506

CN507 on the main board.

Rear cover

CN103

CN101

CN504

CN505

F

Fig.7

H

CN501

CN507

CN509

CN503

CN502

CN506

1-8

Main board

Fig.8

Solder parts

Page 9

XV-D9000

Removing the DVD mechanism assembly

(See Fig.9~11)

*Prior to performing the following procedure, remove

the top panel and main board.

1.Remove the four screws I attaching the DVD

mechanism assembly cover, and DVD mechanism

assembly cover lifted up and it is removed.

2.The bottom of the main body is done up.

3.Remove the four nut J attaching the DVD mechanism

assembly

4.The top of the main body is done up.

5.Remove the four screws K attaching the DVD

mechanism assembly.

6.It is removed while lifting the DVD mechanism

assembly backward while noting the card wire.

DVD Mechanism

assembly cover

I

Fig.9

J

I

Fig.10

K

DVD Mechanism assembly

Fig.11

1-9

Page 10

XV-D9000

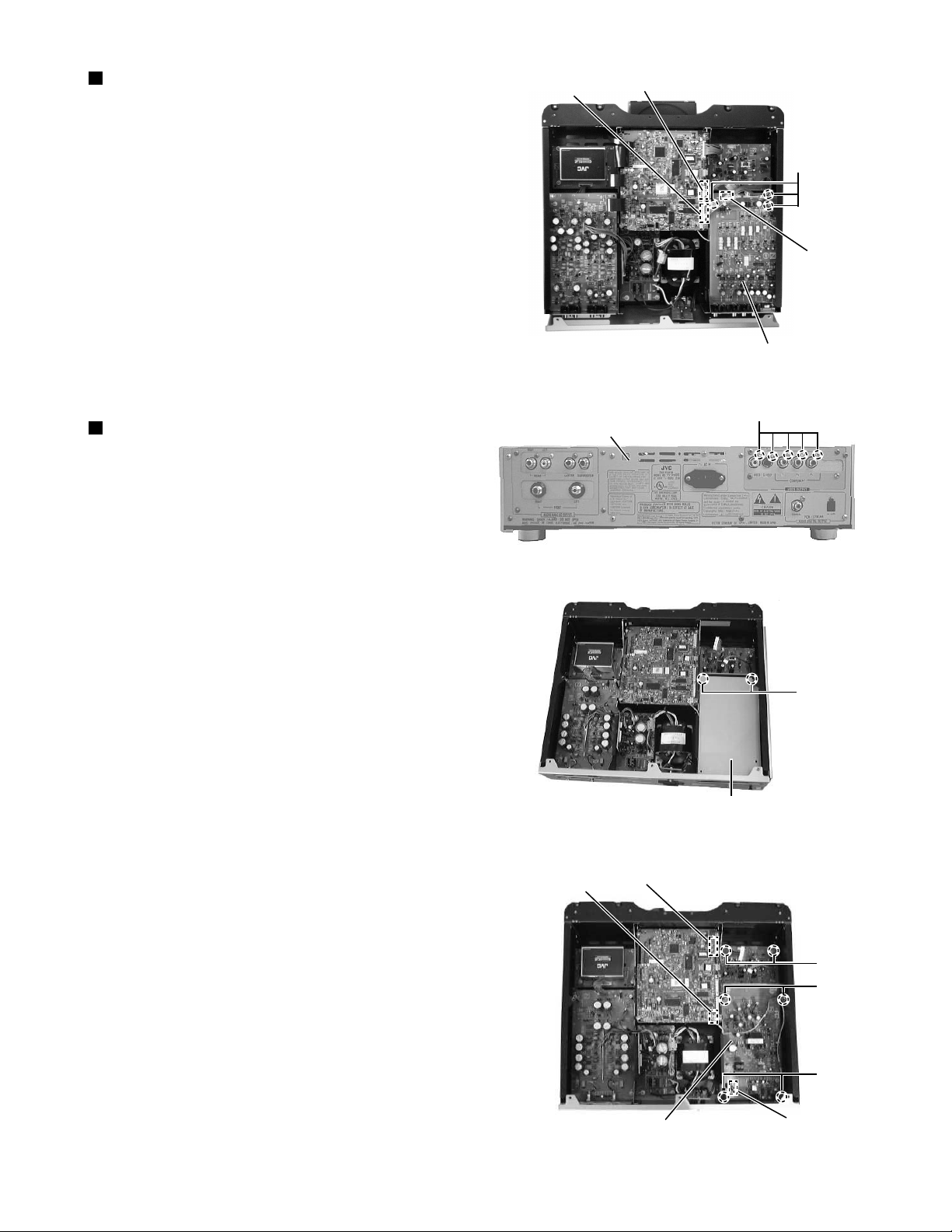

Removing the audio(rear L/R) board

(See Fig.12~13)

*Prior to performing the following procedure, remove

the top panel and rear cover.

1.Remove the three screws L attaching the

audio(rear L/R) board.

2.Remove the four screws M attaching the

audio(rear L/R) board from back of the body.

3.Disconnect the card wire from CN761 and

connector from CN751 on the audio(rear L/R)

board.

4.Disconnect the connector from CN697 on the

audio power board.

Removing the audio(front L/R) board

(See Fig.14)

L

CN751

CN761 CN697

Audio-analog

(rear L/R)board

Fig.12

M

Fig.13

*Prior to performing the following procedure,

remove the top panel and rear cover.

1.Remove the audio(rear L/R) board(upper step).

2.Remove the two screws N of the pillar which

supports audio(rear L/R) board(upper step).

3.Remove the two screws O attaching the

audio(front L/R)board(lower step).

4.Disconnect the connector from CN721 and

CN722 on the audio signal(front) output

terminal.

5.Disconnect the connector from CN695 and

CN696 on the DVD audio power board.

6.Disconnect the connector from CN741 on the

signal processing board.

Signal processing board

CN741

N

O

CN722

CN696

CN721

Audio-analog

(front L/R)board

CN695

Fig.14

1-10

Page 11

XV-D9000

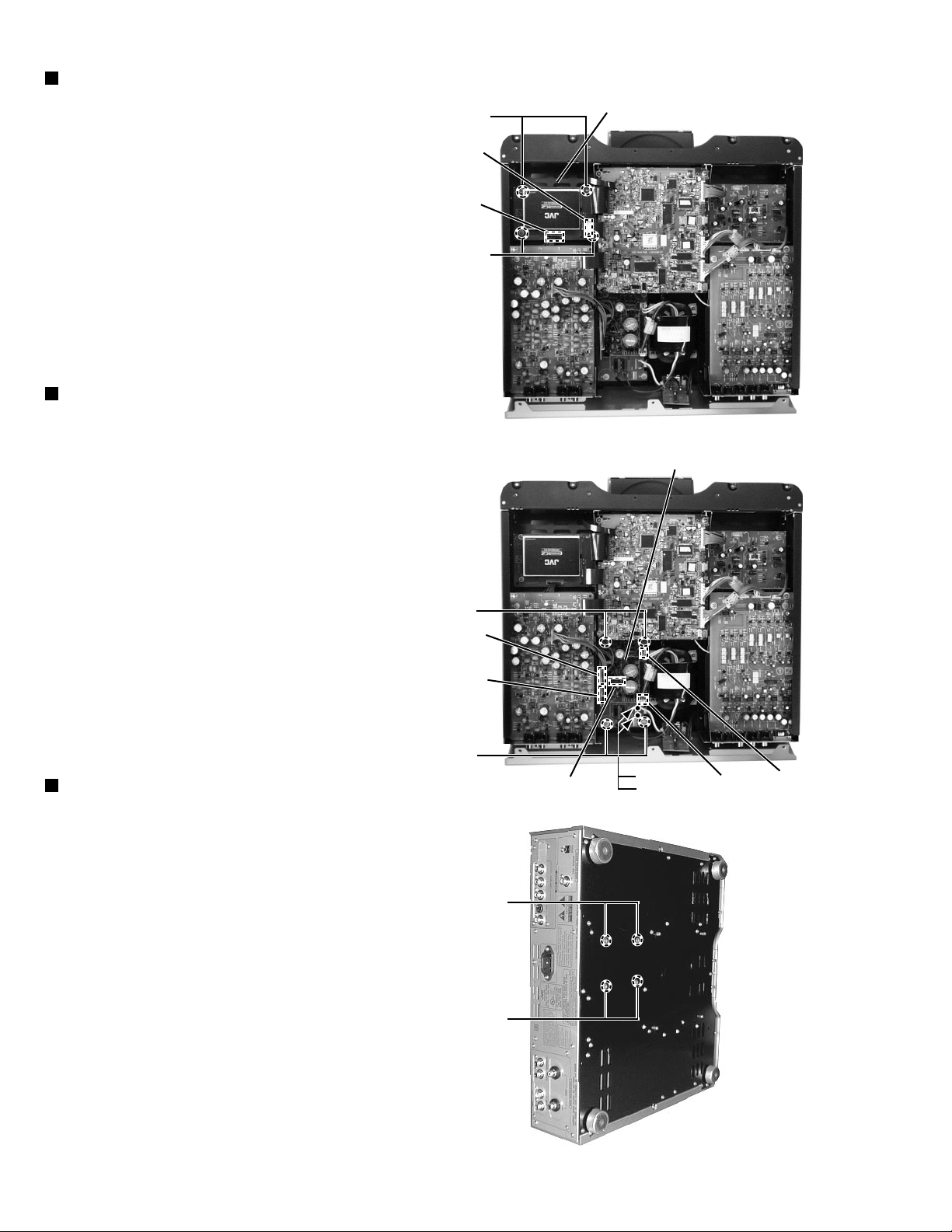

Removing the video signal board(See Fig.15,16)

*Prior to performing the following procedure,

remove the top panel and rear cover.

1.Remove the three screws P attaching the

video signal board.

2.Remove the five screws Q attaching the video

signal board from back of the body.

3.Disconnect the connector from CN502 and CN503

on the main board.

4.Disconnect the connector from CN601 on the

video signal board.

Removing the power supply board

(See Fig.17,18)

*Prior to performing the following procedure,

remove the top panel, rear cover and video

signal board.

1.Remove the two screws S attaching the power

supply board cover and it is remove.

CN502

Rear cover

CN503

Fig.15

Fig.16

P

CN601

Video signal board

Q

2.Remove the two screws T of the pillar which

supports power supply board cover.

3.Remove the four screws U attaching the power

supply board.

4.Disconnect the connector from CN991 on the

power supply board.

5.Disconnect the connector from CN501 and CN506

on the main board.

CN506

Fig.17

CN501

S

Power supply board cover

U

T

Power supply board

Fig.18

U

CN991

1-11

Page 12

XV-D9000

Removing the signal processing board

(See Fig.19)

*Prior to performing the following procedure,

remove the top panel.

1.Remove the four screws V attaching the signal

processing board.

2.Disconnect the connector from CN711 and

CN741 on the signal processing board.

Removing the audio-power supply board

(See Fig.20)

*Prior to performing the following procedure,

remove the top panel and rear cover.

V

Signal processing board

CN711

CN741

V

Fig.19

Audio-power supply board

1.Remove the four screws W attaching the audio power supply board.

2.Disconnect the connector from CN691,CN692,CN695,

CN696,CN697 on the audio-power supply board.

3.The solder(PP691 and PP692) of wire connected

with power transformer is removed.

Removing the power transformer

(See Fig.21)

*Prior to performing the following procedure,

remove the top panel.

1.Disconnect the connector from CN691 and CN692 on

the audio-power supply board.

2.The solder(PP691 and PP692) of wire connected

with power transformer is removed.

W

CN696

CN697

W

X

PP692

PP691

Fig.20

CN691CN695

CN692

3.Remove the four screws X attaching the power transformer

from bottom of the body.

<ATTENTION>

Please the power transformer must become unstable and put

up the main body sideways, and work while supporting the

power transformer by one of hands when you remove the screw

of the power transformer.

1-12

X

Fig.21

Page 13

Removing the operation switch board/

FL and operation switch board(See Fig.22)

1.Remove the front panel assembly.(See Fig.1~5)

2.Remove the ten screws Y attaching the FL and operation switch board.

3.Remove the seven screws Z attaching the operation switch board.

XV-D9000

FL and operation

switch board

Fig.22

Y

Operation switch board

Z

1-13

Page 14

XV-D9000

<Removing DVD mechanism unit>

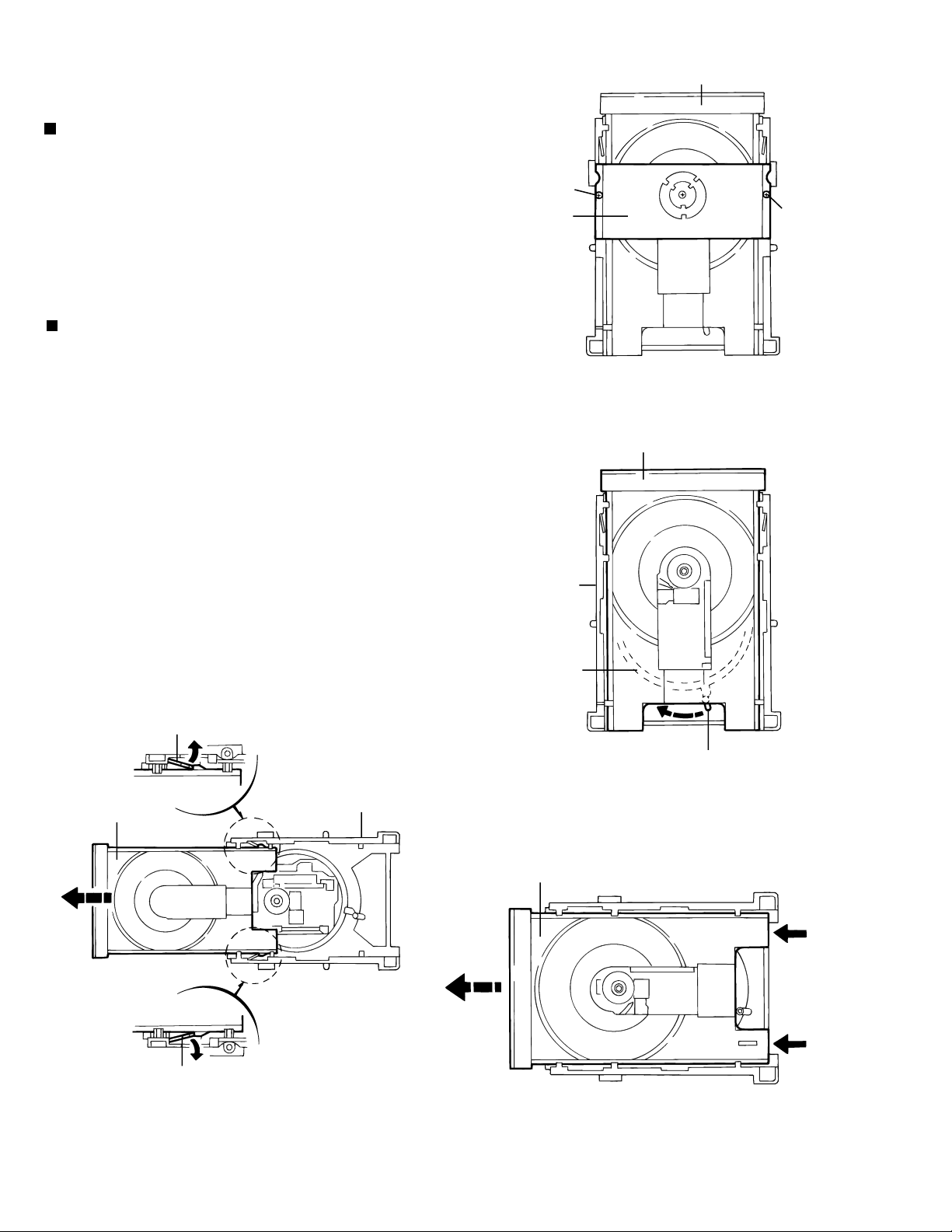

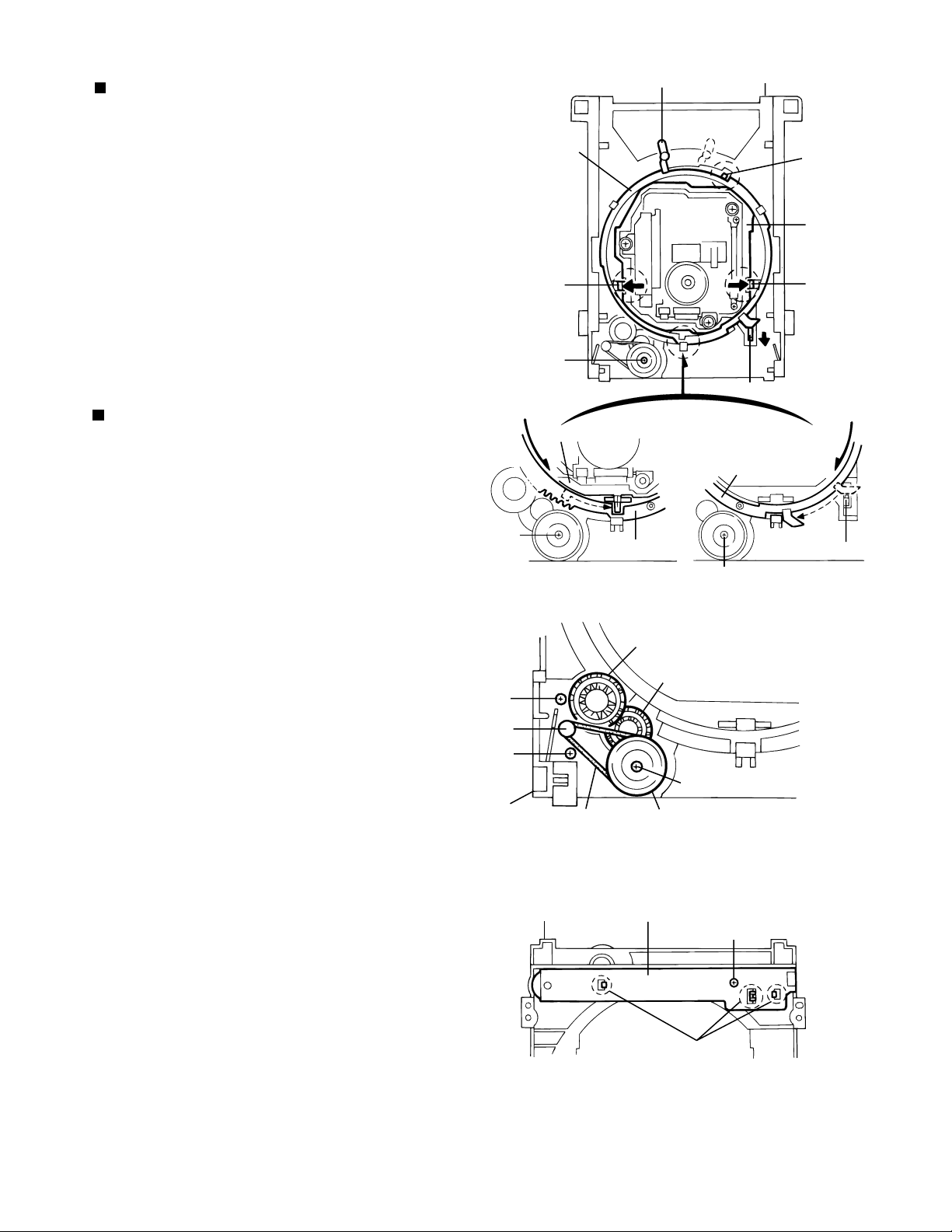

Removing the clamper base (See Fig.1)

* Remove the top cover.

* Remove the DVD mechanism unit.

1. Remove the two screws A attaching the clamper base.

Removing the loading tray (See Fig.2~4)

* Remove the clamper base.

1. Turn the up-down cam lever clockwise (in the direction

of the arrow in Fig.2) to lower the position of the mechanism.

2. Manually set the loading tray to the fully-open position.

3. Stretch the tray stoppers on both sides of the loading

base outward and pull out the tray.

Clamper base

Loading tray

A

A

Fig.1

Loading tray (front side)

Tray stopper

Loading tray

Loading base

Up-down cam

Lever

Fig.2

Loading base

Loading tray

Push

Push

1-14

Tray stopper

Fig.4

Fig.3

Page 15

XV-D9000

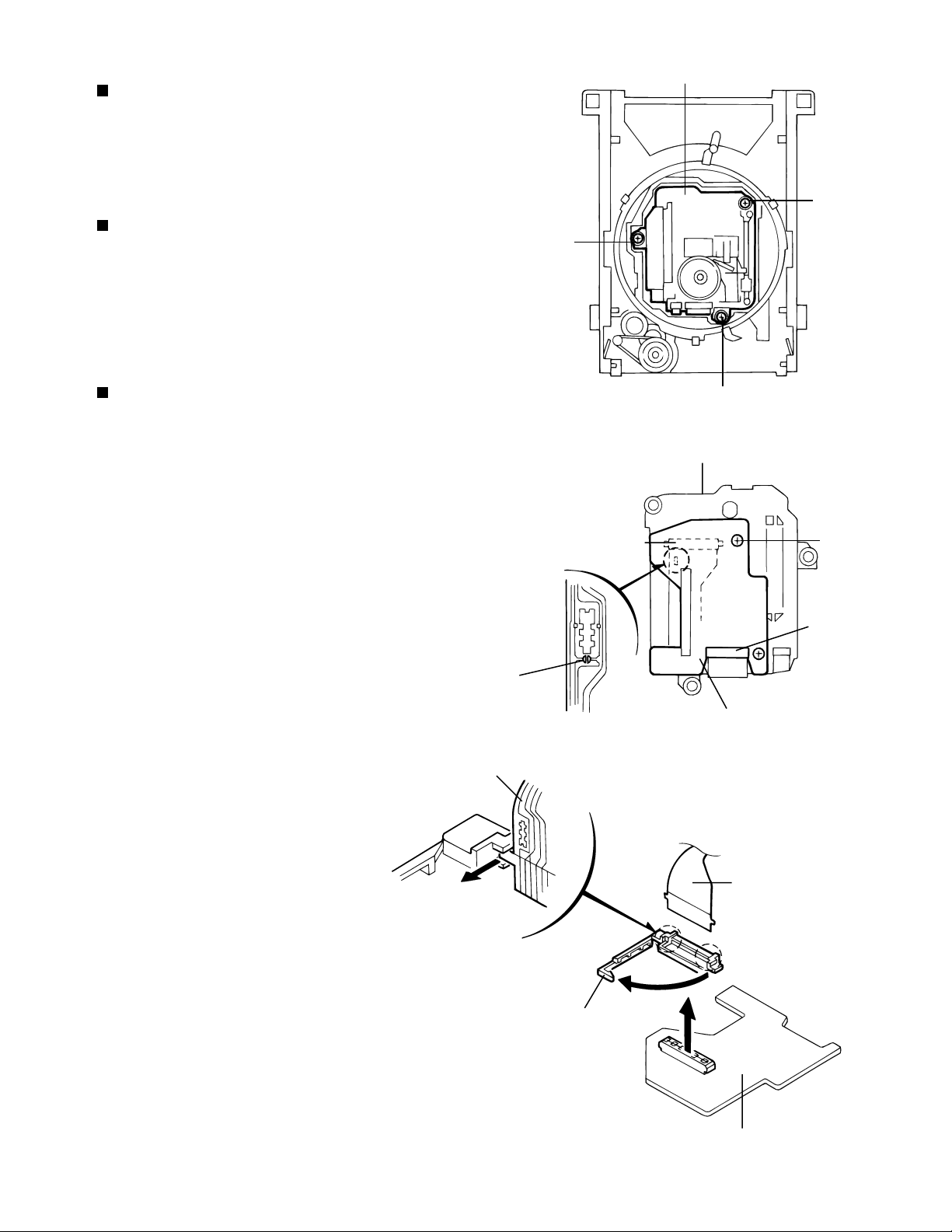

Removing the traverse mechanism unit (See Fig.5)

* Remove the loading tray.

1. Remove the three screws B attaching the traverse

mechanism unit.

Protecting the optical pickup

* Solder the flexible ground point on the optical pickup

when replacing the pickup or before detaching the

mechanism control board. When assembling the unit,

remove the solder last.

Removing the mechanism control board

(See Fig.6~7)

* Remove the traverse unit. (Can be detached without

detaching the T-mechanism unit.)

1. Remove the two screws C attaching the mechanism

control base from the bottom of the traverse unit.

2. Pull out the CN12 connector and detach the

mechanism control board.

3. Remove the card wire from the CN13 connector

on the mechanism control board.

4. Pull out the FPC holder from the CN12 connector

on the reverse side of the mechanism control board

and remove the flexible harness, referring to Fig.7.

B

Enlargement

Traverse mechanism unit

B

Fig.5

Traverse mechanism unit

CN12

B

C

CN13

Connection area

(Solder the flexible

ground point)

Flexible harness

3

Enlargement

FPC holder

Fig.7

Mechanism control board

Fig.6

Flexible harness

2

1

CN12

Mechanism control board

1-15

Page 16

XV-D9000

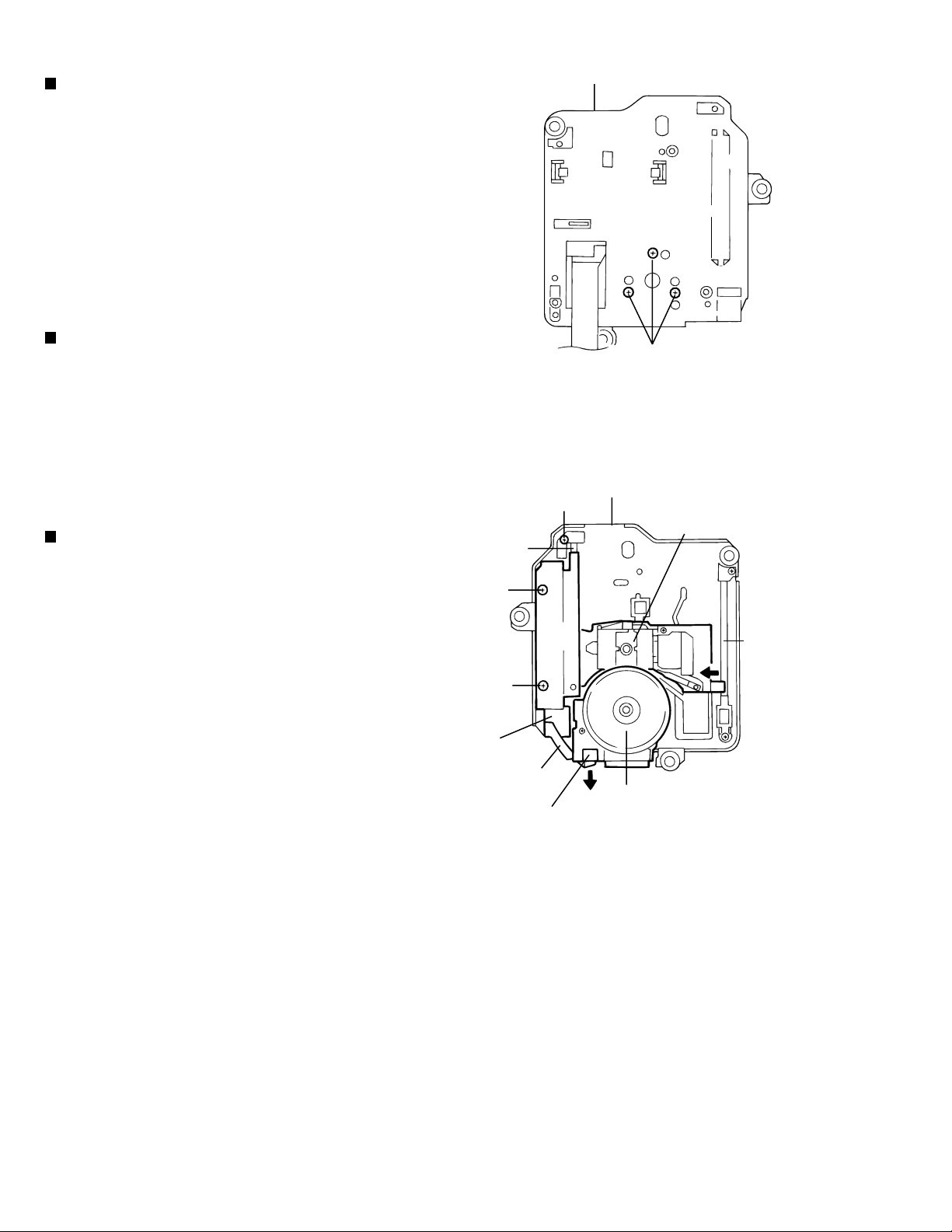

Removing the turntable and spindle motor assembly

(See Fig.8~9)

* Remove the traverse mechanism unit.

* Solder the flexible ground point on the optical pickup.

(See Fig.6)

* Remove the mechanism control board.

1. Remove the flexible harness from the feed motor

connector on the spindle motor board assembly.

2. Remove the three screws D attaching the spindle motor

from the bottom of the traverse chassis.

Removing the feed motor unit (See Fig.9)

* Remove the traverse mechanism unit.

* Remove the mechanism control board.

1. Remove the FPC from the feed motor connector

on the turntable spindle motor board.

2. Remove the two screws E attaching the feed motor unit.

Removing the optical pickup unit (See Fig.9)

* Remove the traverse mechanism unit.

Guide shaft b

* Remove the mechanism control board.

* Remove the feed motor unit.

1. Remove the screw F attaching the guide shaft holder at b,

then simultaneously remove the guide shaft at B and the

optical pickup unit. While doing so, slide the unit

horizontally away from the guide shaft at a.

Traverse chassis

D

Fig.8

Traverse mechanism unit

F

Pick-up assembly

E

Guide

shaft a

E

Feed motor assembly

Flexible harness

Feed motor connector

Turn table/spindle motor unit

Fig.9

1-16

Page 17

XV-D9000

Removing the loading mechanism parts

(See Fig.10~11)

* Remove the clamper base.

* Remove the disk tray.

1. Turn the lever counterclockwise until it stops (position 1),

while pushing the switch lever in the direction of the

arrow and pushing up the pawl at a using a screwdriver.

2. Stretch the two pawls at b outward using a screwdriver

and remove the chassis.

3. Turn the lever clockwise (position 2) to remove the

up-down cam.

4. Remove the pulley gear and the pulley gear belt after

removing the screw G attaching the pulley gear.

5. Pull out drive gear 2 then drive gear 1.

(1)When detaching

Removing the loading motor board

the chassis.

(See Fig.11~12)

* Remove the clamper base.

* Remove the disk tray.

1. Remove the loading belt.

2. Remove the two screws H attaching the loading motor.

3. Remove the screw at I and the three pawls at c fixing

the loading motor base from the reverse side of the

loading base.

Up-down

Pawl b

chassis.

G

cam

G

Lever

1

Up-down cam

Fig.10

Loading base

2

Pawl a

Chassis

Pawl b

Switch lever

(2)When detaching

the up-down cam.

Up-down cam

Switch lever

G

H

Loading motor unit

Loading base

H

Loading belt

Loading base

Drive gear 1

Drive gear 2

G

Pulley gear

Fig.11

Loading motor board

I

Pawl c

Fig.12

1-17

Page 18

XV-D9000

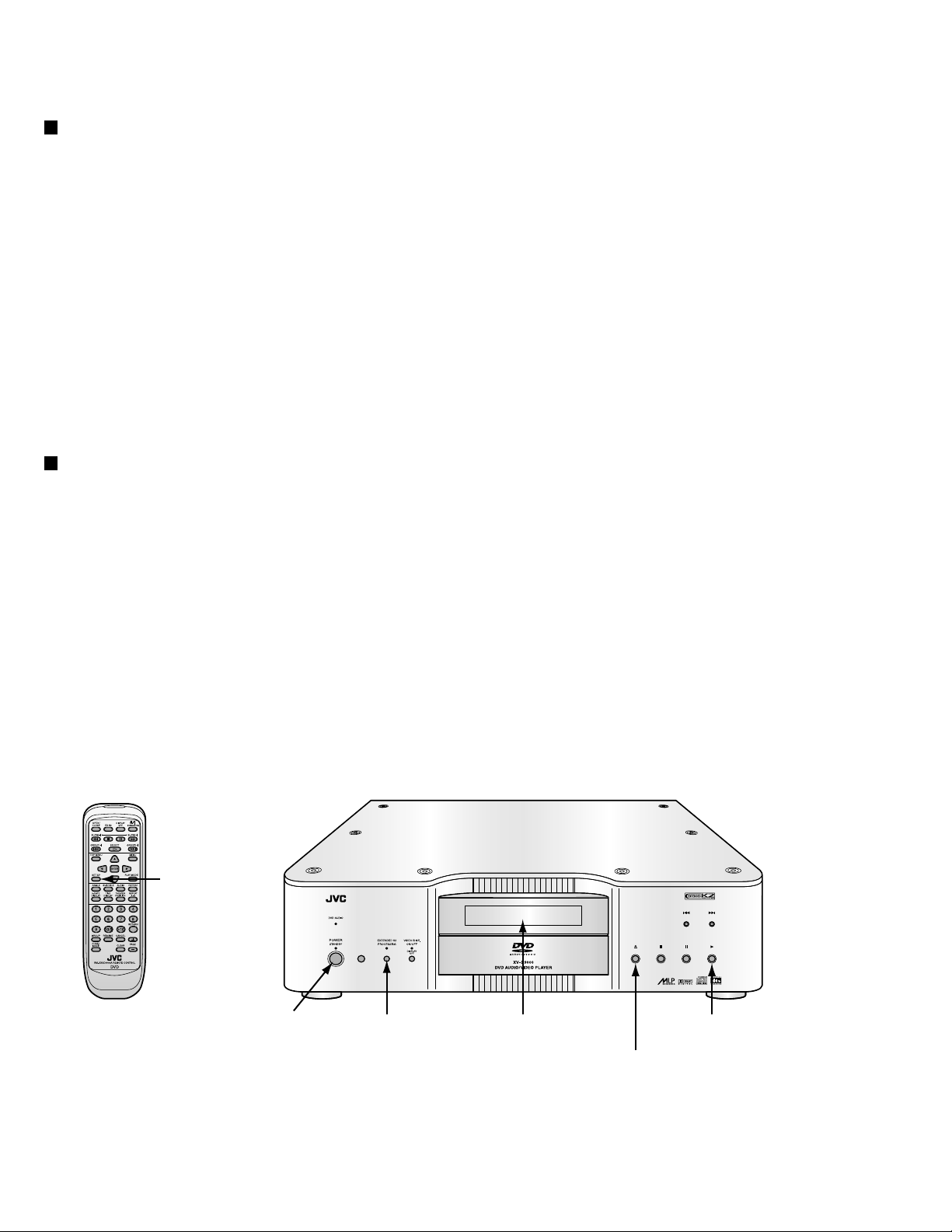

Method of initializing EEPROM and display of jitter value

Initializing EEPROM

Please initialize EEPROM when you exchange Microcomputer(IC401,IC402) and

optical pick-up by the undermentioned method.

1. It is confirmed that there is no disk in the tray.

2. The power supply plug is inserted while pushing the PLAY key and the OPEN/CLOSE key to the main body.

3. It is displayed in the FL display part as "TEST JC1".

4. The EX K2 key is pushed.

5. The POWER key is pushed if displayed in the FL display part as "EFP****".

(**** is a check sum of device key display. )

6.When normally entering the state of the power standby, initialization is normal and completion.

Jitter value (We will separately inform of the method of adjusting jitter.)

1. It is confirmed that there is no disk in the tray.

2. The power supply plug is inserted while pushing the PLAY key and the OPEN/CLOSE key to the main body.

3. It is displayed in the FL display part as "TEST JC1".

4. Press the OPEN/CLOSE key to move the tray outward.

Put the test disc (VT-501) on the tray and press OPEN/CLOSE key.

The tray should move inward (NOTE:Don't push to close the tray directly by hand etc,)

5.Keeps pushing SETUP key to remote controller for ten seconds or more.

6.Press the PLAY key of the main body.

Remote controller Main body

SETUP key

1-18

POWER/

STANDBY key

EX K2 key FL Display PLAY key

OPEN/CLOSE key

Page 19

Description of major ICs

ADV7123KST50(IC359):Video DAC

VAA

XV-D9000

BLANK

SYNK

R9-R0

G9-G0

B9-B0

10

10

10

PSAVE

CLOCK

Pin Function (1/2)

Pin No.

Symbol

1~10

11

12

13

14~23

24

CLOCK

25,26

27

28

29,30

31

32

33

34

35

36

37

38

39~48

DATA

REGISTER

DATA

REGISTER

DATA

REGISTER

POWER-DOWN

MODE

GND

G0~G9

BLANK

SYNC

VAA

B0~B9

GND

IOB

IOB

VAA

IOG

IOG

IOR

IOR

COMP

VREF

RSET

PSAVE

R0~R9

10

10

10

RSET COMP

DAC

DAC

I/O

Green pixel data input terminal (TTL compatible)

I

Composite blank control input terminal (TTL compatible)

I

Composite sync control input (TTL compatible)

I

Analog power supply terminal

Blue pixel data input terminal (TTL compatible)

I

Clock signal input (TTL compatible)

I

Connect to ground

-

O

O

O

O

O

O

I/O

Differential blue current output (high impedance current source)

Blue current output

Analog power supply terminal

Differential green current output (high impedance current source)

Green current output

Differential red current output (high impedance current source)

Red current output

Compensation pin

Voltage reference input for DAC or voltage reference output (1.235V)

A resistor connected between this pin and ground

I

Power save control pin

I

Red pixel data input (TTL compatible)

I

DAC

REFERENCE

BLANK AND

SYNK LOGIC

IOR

IOR

IOG

IOG

IOB

IOB

VOLTAGE

VREF

CIRCUIT

Function

1-19

Page 20

XV-D9000

AN8706FHQ (IC101) : Front end processor

1.Pin layout

CBDOSL

CSAG

DCAGC

AGCG

PEAK

BOTTOM

RFENVFCBOOST

OFTR

BDO

JITOUT

GND3

75747372717069686766656463626160595857565554535251

RBCA

RFINP

RFINN

VCC2

GND2

VREF2

RFON

RFOP

TS

DCRF

FS

VIN6

VIN5

VCC1

VIN1

VIN2

VIN3

VIN4

VREF4

DIFP

DIFN

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

AN8706FHQ

CBDOFS

TESTSG

COFTFS

COFTSL

FUPDN

ITDLI

VCOIN

PLFLT

PLFLT2

FCPO

PCPO

VCC3

CAPA

DTRD

IDGT

VCC5

50

RDCKP

49

RDCKN

48

RDTP

47

RDTN

46

GND5

45

GND4

44

VCC4

43

DTMONN

42

DTMONP

41

DSLFLT

40

DSLO

39

FLTOUT

38

DCFLT

37

VREF3

36

VPWBDO

35

VPWOFT

34

IDDLY

33

DBAL

32

GND1

31

VREF1

30

TKCNT

29

TKCFLT

28

TEOUT

27

TEI

26

RSCL

2.Block diagram

Head Amp.

SSD Signal

Head Amp.

DPD Signal

12345678910111213141516171819202122232425

TG

LPCOA

LDONB

LDONA

LPC1

VHARF

RFOUT

FS/TS

POFLT

TGBAL

PTH

TBAL

FBAL

FGCTL

FEN

VREFL

FEOUT

PULIN

VREFC

VREFH

TGTETKCNTTBALFBALFE

SEN

SCK

STDI

FC/Boost

AGC Cont

TKCNT

FE(SSD)

FE BAL

AGC EQ

MU

TE(DPD)

TE BAL

TG(DPD)

LPC(Amp)

VREF reg

STNBY

XTRON

MTRON

RFIN

ROMRAM

RF ENV

DFLTOP/NRFENV

DSL

BDO Det

OFTR Det

INTERFACE

PLL

JITTER Det

SYNC

JITOUT

CLK

DATA

DSLOUT

BDO

OFTR

1-20

OPTICAL HEAD

(650nm)

TGBAL CPU STNBY MTRON

SERVO PROCESSOR

Head Amp.

Page 21

XV-D9000

3.Pin function

Pin No. Symbol I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

LDONB

LDONA

LPCOA

VHARF

TGBAL

FGCTL

FEOUT

VREFL

VREFC

VREFH

STNBY

XTRON

MTRON

ROMRAM

TEOUT

TKCFLT

TKCNT

VREF1

VPWOFT

VPWBDO

VREF3

DCFLT

FLTOUT

DSLFLT

DTMONP

DTMONN

RDCKN

RDCKP

LPC1

POFLT

PTH

TBAL

TG

FBAL

FEN

PULIN

SEN

SCK

STDI

RSCL

TEI

GND1

DBAL

IDDLY

DSLO

VCC4

GND4

GND5

RDTN

RDTP

Functions

I

Laser ON (CD Head) terminal

I

Laser ON (DVD Head) terminal

O

Laser drive output terminal

I

Laser PIN input terminal

O

VHALF voltage output terminal

I

Tangential phase balance control terminal

O

Track detection Threshold value level terminal

I

Track detection Threshold value level terminal

I

Tracking balance control terminal

O

Tangential phase error signal output terminal

I

Focus amplifier Gain control terminal

I

Focus balance control terminal

O

Focus error signal output terminal

I

Focus error output amplifier reversing input terminal

O

VREFL voltage output terminal

O

VREFC voltage output terminal

O

VREFH voltage output terminal

I

DSL,PLL drawing mode switch terminal

I

SEN(Cereal data input terminal)

I

SCK(Cereal data input terminal)

I

STDI(Cereal data input terminal)

I

Standby mode control terminal

I

Tracking OFF holding input terminal

I

Monitor output ON/OFF switch terminal

I

ROM RAM switch terminal

O

Standard current source terminal

I

Tracking error output Amp reversing input terminal

O

Tracking error signal output terminal

O

Track count detection filter terminal

O

Track count output terminal

O

VREF1 voltage output terminal

O

Earth terminal 1

I

Data slice offset adjustment terminal

I

Data slice delay adjustment terminal

I

OFTR detection level setting terminal

I

BDO detection level setting terminal

O

VREF3 voltage output terminal

O

Capacity connection terminal for data slice input filter

O

Filter amplifier output terminal

O

Data slice single data output terminal

O

Constant filter terminal when data is sliceddelly

O

PLL differential motion 2 making to value edge signal monitor output (+)

O

PLL differential motion 2 making to value edge signal monitor output (-)

I

Power terminal 4 (5V)

O

Earth terminal 4

O

Earth terminal 5

O

PLL differential motion making to synchronization RF signal reversing output

O

PLL differential motion making to synchronization RF signal rotation output

O

PLL differential motion making synchronization clock reversing output

O

PLL differential motion making synchronization clock rotation output

AN8706FHQ (1/2)

1-21

Page 22

XV-D9000

3.Pin function

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

VCC5

IDGT

DTRD

CAPA

VCC3

PCPO

FCPO

PLFLT2

PLFLT

VCOIN

ITDLI

FUPDN

GND3

JITOUT

BDO

OFTR

BOOST

FC

RFENV

BOTTOM

PEAK

AGCG

DCAGC

CSAG

CBDOSL

CBDOFS

RBCA

TESTSG

RFINP

RFINN

VCC2

GND2

VREF2

COFTFS

COFTFL

RFON

RFOP

TS

DCRF

FS

VIN6

VIN5

VCC1

VIN1

VIN2

VIN3

VIN4

VREF4

DIFP

DIFN

I/OPin No. Symbol Functions

Power terminal 5 (3.3V)

I

Data slice part address part gate signal input terminal (For RAM)

I

Data slice data read signal input terminal(For RAM)

I

Data slice CAPA(Address)signal input terminal (For RAM)

I

Power terminal 3 (5V)

I

PLL phase gain set terminal

O

PLL frequency gain set terminal

O

PLL low region filter terminal

O

PLL high region filter terminal

O

PLL VCO input terminal

I

PLL jitter free current ripple removal filter terminal

O

PLL frequency control input terminal

I

Earth terminal 3

O

Detection signal output of jitter

O

BDO output terminal

O

OFTR output terminal

O

Booth control terminal for filter

I

FC control terminal for filter

I

RF envelope output terminal

O

Bottom envelope detection filter terminal

O

Peak envelope detection filter terminal

O

AGC amplifier gain control terminal

O

AGC amp filter terminal

O

Sag cancellation circuit filter terminal

O

BDO detection capacitor terminal

O

BDO detection capacitor terminal

O

BCA detection level setting terminal

O

TEST signal input terminal

I

RF signal positive moving input terminal

I

RF signal reversing input terminal

I

Power terminal 2 (5V)

I

Earth terminal 2

O

VREF2 voltage output terminal

O

OFTR detection capacitor terminal

O

OFTR detection capacitor terminal

O

RF signal output terminal P

O

RF signal output terminal N

O

All addition amplifier (DVD) output terminal

O

All addition amplifier capacitor terminal

O

All addition amplifier (CD) output terminal

O

Focus input of external division into two terminal

I

Focus input of external division into two terminal

I

Power terminal 1 (5V)

I

External division into four (DVD/CD) RF input terminal 1

I

External division into four (DVD/CD) RF input terminal 2

I

External division into four (DVD/CD) RF input terminal 3

I

External division into four (DVD/CD) RF input terminal 4

I

VREF4 voltage output terminal

O

RF signal (RAM) output terminal P

O

RF signal (RAM) output terminal N

O

AN8706FHQ(2/2)

1-22

Page 23

BA5983FM-X (IC271) : 4CH DRIVER

1.Block diagram

27

28

Vcc

25

26

10k

20k

24

23 22

10k

20k

XV-D9000

21

20

19

Vcc

STAND BY

CH4

10k

10k

18

Level Shift

17 16

10k

10k

10k

10k

15

10k

10k

Level Shift

10k

10k

1

2

3

5

4

10k

10k

6

7

2.Pin function

Pin No. Pin No.

10

11

12

13

14

Symbol Symbol

1

BIAS IN

2

OPIN1(+)

3

OPIN1(-)

4

OPOUT1

5

OPIN2(+)

6

OPIN2(-)

7

OPOUT2

8

9

GND

STBY1

PowVcc1

VO2(-)

VO2(+)

VO1(-)

VO1(+)

I/O I/O

Input for Bias-amplifier

I

Non inverting input for CH1 OP-AMP

I

Inverting input for CH1 OP-AMP

I

Output for CH1 OP-AMP

O

Non inverting input for CH2 OP-AMP

I

Inverting input for CH2 OP-AMP

I

Output for CH2 OP-AMP

O

Substrate ground

-

Input for CH1/2/3 stand by control

I

Vcc for CH1/2 power block

-

Inverted output of CH2

O

Non inverted output of CH2

O

Inverted output of CH1

O

Non inverted output of CH1

O

Function

15

16

17

18

19

20

21

22

23

24

25

26

27

28

STAND BY

CH1/2/3

89

VO4(+)

VO4(-)

VO3(+)

VO3(-)

PowVcc2

STBY2

GND

OPOUT3

OPIN3(-)

OPIN3(+)

OPOUT4

OPIN4(-)

OPIN4(+)

PreVcc

Vcc

10

Level Shift

Level Shift

10k

10k

11

10k

10k

10k

10k

12

13

14

Function

O

Non inverted output of CH4

O

Inverted output of CH4

O

Non inverted output of CH3

O

Inverted output of CH3

-

Vcc for CH3/4 power block

I

Input for Ch4 stand by control

-

Substrate ground

O

Output for CH3 OP-AMP

I

Inverting input for CH3 OP-AMP

I

Non inverting input for CH3 OP-AMP

O

Output for CH4 OP-AMP

I

Inverting input for CH4 OP-AMP

I

Non inverting input for CH4 OP-AMP

-

Vcc for pre block

10k

10k

1-23

Page 24

XV-D9000

IS61LV256-12T(IC163,IC164,IC165,IC173):32k X 8 Low voltage CMOS Static RAM

1.Pin layout 2.Block diagram

OE 22

A11 23

A9 24

A8 25

A13 26

WE 26

VCC 28

A14 1

A12 2

A7 3

A6 4

A5 5

A4 6

A3 7

A10

21

CE

20

I/O7

19

I/O6

18

I/O5

17

I/O4

16

I/O3

15

GND

14

I/O2

13

I/O1

12

I/O0

11

A0

10

A1

9

A2

8

A0-A14

VCC

GND

I/O0-I/O7

DECODER

I/O

DATA

CIRCUIT

256 X 1024

MEMORY ARRAY

COLUMN I/O

3.Pin function

Pin No. Symbol I/O

1

2

3~10

11~13

14

15~19

20

21

22

23

24,25

26

27

28

A14

A12

A7~A0

I/O0~I/O2

GND

I/O3~I/O7

CE

A10

OE

A11

A9,A8

A13

WE

VCC

Function

I

Address input

I

Address input

I

Address input

I/O

Data I/O

-

Connects with the ground

I/O

Data I/O

I

Chip enable input

I

Address input

I

Output enable input

I

Address input

I

Address input

I

Address input

I

Write enable input

-

Power supply terminal

CE

OE

WE

CONTROL

CIRCUIT

1-24

Page 25

JCE8011(IC551):Graphic controller

XV-D9000

Pin No. Symbol

1~8

9

10

11

12

13

14

15

16~23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39~46

47

48

49

50

51

52

53

54~61

62

63~70

71

72

73~82

83

84~93

94

95

96

97

98

99

100

VD0~7

VCLKI

HSYNCI

VSYNCI

VCC

VCLKO

HSYNCO

VSYNCO

DOUT0~7

TEST

RESETB

GND

NTB

DTSF0

DTSF1

VIDEG

DOSF0

DOSF1

XVRST

F1

HBL

VBL

VOEDG

VCC

FRD7~0

GND

FRCK

FWCK

FREB

FWEB

FRRSTB

FWRSTB

FWD7~0

VCC

CHD7~0

GND

CHOEB

CHA19~10

VCC

CHA9~0

GND

ACK

CS1B

CS2B

SCK

RXD

TXD

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Function

DVD Image signal input (Multi plex data Y,Cr,Cb)

I

Dot clock signal input (27MHz)

I

The horizontal synchronous signal input

I

Vertical synchronous signal input

I

Power supply

Dot clock signal output (27MHz)

'H' blanking output

'V' blanking output

Digital data output

Test terminal (Uses as GND usually)

System reset signal

I

Connect to GND

Mode switching NTSC(low) / PAL(high)

I

Taking timing shift of VD input

I

Taking timing shift of VD input

I

Taking edge specification of VD input (0:up , 1:down)

I

Timing shift input of output data

I

Timing shift input of output data

I

Non connect

Field Identification signal output

'H' blanking output

'V' blanking output

Output timing setting of DOUT (0:up , 1:down)

I

Power supply

Field memory read data input

I

Connect to GND

Field memory read clock

Field memory write clock

Field memory read enable

Field memory write enable

Field memory read address reset

Field memory write address reset

Field memory write data output

Power supply

Character ROM data

I

Connect to GND

Character ROM output enable

Character ROM address output

Power supply

Character ROM address output

Connect to GND

-

Serial data chip select for graphic control

I

Serial data chip select for encoder control

I

Serial clock input

I

Serial input data

I

Serial output data

1-25

Page 26

XV-D9000

JCV8005-2(IC471):CPPM

1.Pin layout

80 51

81

50

100

1 30

2.Pin function

Pin No. I/O

1

2

3~10

11

12

13~20

21

22

23

24

25

26

27

28

29

30

31

32

33~36

37

38~41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

31

Symbol

VDD

GND

HDATA0~7

VDD

GND

HADDR0~7

VDD

GND

NCS

NRD

NWR

NIRQ

WAIT

NRESET

VDD

GND

VDD

GND

STD7~4_OUT

GND

STD3~0_OUT

VDD

GND

REQ_IN

DACK_OUT

STCLK_OUT

SYNC_OUT

STERROUT

VDD

GND

VDD

GND

NG_RD

NG_WR

G_WITODC

G_CSDEC

G_WITDEC

VDD

-

-

I/O

-

I

-

I

I

I

O

O

I

-

-

-

-

O

-

O

-

-

I

O

O

O

-

-

-

-

-

I

I

I

I

I

-

JCV8005-2 1/2

Description

Power supply

Connect to ground

Data input/output terminal (both by 8 bits)

Power supply

Connect to ground

8 bit address bus to internal address (connect to host)

Power supply

Connect to ground

Chip select signal from host

Data read signal from host

Data write signal from host

Interrupt of request to host

Wait demand to host

Reset signal from host

Power supply

Connect to ground

Power supply

Connect to ground

Data output to DVD decoder (8 bits)

Connect to ground

Data output to DVD decoder (8 bits)

Power supply

Connect to ground

Request signal for forwarding control by decoder

Output signal to decoder which shows effective data

Data strobe signal to decoder

Sector sink signal to decoder

Non connect

Power supply

Connect to ground

Power supply

Connect to ground

Glue logic input signal from host

Glue logic input signal from host

Glue logic input signal from front end

Glue logic input signal from host

Glue logic input signal from decoder

Power supply

1-26

Page 27

XV-D9000

2.Pin function

Pin No. I/O

59

60

61

62

63

64

65

66,67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90~93

94

95~98

99

100

Symbol

GND

WAIT1

WAIT2

WAITIN

VDD

GND

TEST_IN

NC

VDD

GND

CLKOCTL

NC

OSCI

OSCO

NC

VDD

GND

33OUT

16OUT

VDD

GND

VDD

GND

STERR_IN

SYNC_IN

STCLK_IN

DACK_IN

REQ_OUT

VDD

GND

STD0~3_IN

GND

STD4~7_IN

VDD

GND

JCV8005-2 2/2

Description

-

O

I

-

I

-

-

I

I

O

-

-

-

O

O

-

-

-

I

I

I

I

O

-

I

I

-

-

Connect to ground

Glue logic output signal to host

Non connect

Glue logic input signal (connect to 27 pin)

Power supply

Connect to ground

Connect to ground

Non connect

Power supply

Connect to ground

Input terminal for crystal-oscillator circuit on/off control

Non connect

Crystal oscillation terminal (input side)

Crystal oscillation terminal (output side)

Non connect

Power supply

Connect to ground

Oscillation output terminal

Oscillation output terminal

Power supply

Connect to ground

Power supply

Connect to ground

Presence of data error from front end

Sector sink signal from front end

Data clock signal from front end

Signal which shows effective data from front end

Request signal for forwarding control to front end

Power supply

Connect to ground

Data input from front end (8 bits)

Connect to ground

Data input from front end (8 bits)

Power supply

Connect to ground

1-27

Page 28

XV-D9000

M27C1602CZ(IC402,IC553):16M ROM

1.Pin layout

44

WE

A19

A18

A8

A7

A6

A5

A4

A3

10

A2

11

A1

12

CE

13

VSS

14

OE

15

D0

16

D8

17

D1

18

D9

19

D2

20

D10

21

D3

22

D11

2.Pin function

1

2

3

4

5

6

7

8

9

WP

43

A20

42

A9

41

A10

40

A11

39

A12

38

A13

37

A14

36

A15

35

A16

34

A17

33

BYTE

32

VSS

31

A0

30

D7

29

D14

28

D6

27

D13

26

D5

25

D12

24

D4

23

VCC

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

Symbol

WE

A19

A18

A8

A7

A6

A5

A4

A3

A2

A1

CE

VSS

OE

D0

D8

D1

D9

D2

D10

D3

D11

I/O I/OFunction Function

Write enable

I

Address bus 19

I

Address bus 18

I

Address bus 8

I

Address bus 7

I

Address bus 6

I

Address bus 5

I

Address bus 4

I

Address bus 3

I

Address bus 2

I

Address bus 1

I

Chip enable

I

Connect to GND

Output enable

I

Data bus 0

O

Data bus 8

O

Data bus 1

O

Data bus 9

O

Data bus 2

O

Data bus 10

O

Data bus 3

O

Data bus 11

O

Pin No.

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Symbol

VCC

D4

D12

D5

D13

D6

D14

D7

A0

VSS

BYTE

A17

A16

A15

A14

A13

A12

A11

A10

A9

A20

WP

-

Power supply +3.3V

O

Data bus 4

O

Data bus 12

O

Data bus 5

O

Data bus 13

O

Data bus 6

O

Data bus 14

O

Data bus 7

I

Address bus 0

-

Connect to GND

I

Data width selection input

I

Address bus 17

I

Address bus 16

I

Address bus 15

I

Address bus 14

I

Address bus 13

I

Address bus 12

I

Address bus 11

I

Address bus 10

I

Address bus 9

I

Address bus 20

-

Non connect

1-28

Page 29

M30622EC-FP(IC451):System controller

1.Pin layout

100 ~ 81

1

80

XV-D9000

~

30

~

51

31 ~ 50

2.Key Matrix

KEY IN 2

DISPLAY OFF

PAUSE

PLAY

KEY OUT 0

KEY OUT 1

KEY OUT 2

KEY IN 0

POWER

OPEN/CLOSE

KEY IN 1

K2

STOP

3.Pin Function (1/2)

Pin No. Pin No.

Symbol Symbol

1

FLDAT

2

FLSCK

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

CS4

VLINEOFF

EEPEI

EEPEO

EECK

GND

GND

EECS

POWERON

RESET

XOUT

VSS

XIN

VCC

NMI

REQ

REMO

VSYNC

TRAYIN

BUSY

SS1

SS2

HREQ1

HREQ2

OSDCS2

OSDCK

OSDDI

OSDDO

MDSPOUT

MDSPIN

MDSPCK

I/O I/O

FL driver data output

O

FL driver clock output

O

VFPIC chip select output

O

Video line OFF control

O

EEPROM set data input

I

EEPROM set data output

O

EEPROM clock signal output

O

Connect to ground

Connect to ground

EEPROM chip select

O

Power on signal output

O

Reset signal input

I

Clock signal output

O

Connect to ground

Clock signal input

I

Power supply +5V

Non connect

Request signal input

I

Remote control signal input

I

Video sync input

I

Tray close detection signal

I

Busy signal output

O

Selection output for DSP1

O

Selection output for DSP2

O

Request signal input for DSP1

I

Request signal input for DSP2

I

OSD Chip select signal

O

OSD Clock signal

O

OSD Data input

I

OSD Data output

O

Data output for DSP

O

Data input for DSP

I

Clock signal output for DSP

O

Function

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

CPURST

S2UDT

U2SDT

SCLK

DSPRST

BANK

ACK

TRAYOUT

OSDCS1

OSDCS3

ENCDRST

K2RESET

VS1

VCD

MULTI/2CH

96K/48K

DDCLK

DDDATA

DDCS1

DDCS2

K2ONOFF

192K/48K

GAINSL

GAINSR

GAINNC

GAINLFE

MLPSEL2

MLPSEL1

VCC

MLPSEL0

VSS

Function

O

CPU Reset signal output

O

Communication data output

for unit micon

I

Communication data input

From unit micon

I

System clock signal input

O

Reset signal output for DSP

O

OSDROM switch output

I

OSD active input

O

Tray open detection signal

O

OSD Chip select

O

Encoder Chip select

O

Encoder reset

O

K2 Reset signal output

O

S1 Switch output

O

Video mode switch output

-

Non connect

-

Non connect

O

Clock signal output for DAC

O

Data output for DAC

O

Chip select output for front CH

O

Chip select output for rear CH

O

K2 power control output

O

Switch output of front CH lpffc

O

Gain switch output of rear Lch

O

Gain switch output of rear Rch

O

Gain switch output of center CH

O

Gain switch output of LFE CH

Master clock switch output of DSP

O

Master clock switch output of DSP

O

Power supply +5V

-

Master clock switch output of DSP

O

Connect to ground

-

1-29

Page 30

XV-D9000

3.Pin Function (2/2)

Pin No.

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Symbol

K2LATCH

PLLSEL1

PLLSEL0

LMUTE

CMUTE

SMUTE

FMUTE

K2SCK

K2DATA

K2CS

FLCS

FLPOR

STANDBYIND

AUDIOIND

PROGSCL

PROGSDA

PROGPWA

PROGRST

D60P60I

DOUT1

DOUT2

KEYO2

KEYO1

KEYO0

KEYI2

KEYI1

KEYI0

DEVIDE-MCK

AICCTRL

IECZIVA

IECDSP

AVSS

VDFF

VREF

AVCC

GND

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

M30622EC-FP

Function

Latch output for K2

Switch output for PLL

Switch output for PLL

Sub woofer mute output

Center mute output

Surround mute output

Front mute output

Clock signal output for K2

Data output for K2

Chip select output to K2

Chip select output for FL driver

Reset signal output for FL driver

STANDBY indicator control signal output

AUDIO indicator control signal output

Clock signal output for progressive

Data output for progressive

ON/OFF output for progressive

Reset signal output for progressive

D terminal control signal output

D terminal aspect ratio output

D terminal aspect ratio output

Key matrix output 2

Key matrix output 1

Key matrix output 0

I

I

I

-

I

-

-

Key matrix input 2

Key matrix input 1

Key matrix input 0

Clock control output for DSP

Clock control output for DSP

Digital output control signal output

Digital output control signal output

Connect to ground

Control signal output for video power

Internal AD reference input

Power supply +5V

Connect to ground

1-30

Page 31

M66004SP(IC802):FL DRIVER

1.Block diagram

FLCS

14

FLCK

15

16

FLDATA

Serial

reception

circuit

Vcc Vcc2

19 60

Display code

register

(8bit 16)

control circuit

Code/Command

RAM write

CGROM

(35bit 160)

DecoderDecoder

(35bit 16)

CGRAM

Segment output circuit

Output port

(2bit)

23

31

33

59

17

18

XV-D9000

SEG35

SEG27

SEG26

SEG00

P1

P0

13

RESET

XIN

21

XOUT

20

2.Pin function

Pin.No.

1

2~12

13

14

15

16

17

18

19

20

21

22

23

24~31

32

33~59

60

61~64

Clock

generation

circuit

FLOFFIND

S34~S27

D15~D12

Display

register

Symbol

D11

D10~D0

POR

CS

SCK

SDATA

K2IND

VCC1

XOUT

XIN

VSS

S35

VP

S26~S0

VCC2

control

code select

Display

controller

22 32

Vss

I/O

Non connect

-

FL digit control signal output.

O

FL Driver chip select.

I

Chip select signal input.

I

Shift clock signal input.

I

Serial data input.

I

Indicator control signal output.

O

Indicator control signal output.

O

Power supply for internal logic.

-

Clock signal output.

O

Clock signal input.

I

Connect to GND.

-

Non connect.

-

FL Segment control signal output.

O

Power supply.

-

FL Segment control signal output.

O

Power supply for grid output and segment output.

-

Non connect

-

Function

Digit

output

circuit

Vp

12

61

64

1

DIG11

DIG00

DIG15

DIG12

1-31

Page 32

XV-D9000

MBM29LV2TC9TN(IC357):2Mbit Flash memory

1.Pin layout

N.C.

N.C.

RESET

N.C.

N.C.

RY/BY

N.C.

N.C.

A15

A14

A13

A12

A11

A10

A9

A8

WE

A

A6

A5

A4

A3

A2

A1

7

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A16

BYTE

Vss

DQ

15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

Vcc

11

DQ

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE

Vss

CE

A

0

2.Pin function

Symbol Pin function

A-1,A0~A16

DQ0~DQ15

CE

OE

WE

RY/BY

RESET

Address inputs

Data inputs / outputs

Chip enable

Output enable

Write enable

Ready / busy output

Hardware reset pin / Temporary sector

unprotection

BYTE

N.C.

Vss

Vcc

Selects 8-bit or 16-bit mode

Non connect

Connect to ground

Power supply

3.Block diagram

Vcc

Vss RY/BY

WE

BYTE

RESET

CE

OE

A0~A16

A-1

RY/BY

Buffer

State

Control

Command

Register

Low Vcc Detector

Program Voltage

Generator

Timer for

program/erase

Erase voltage

generator

STB

Chip enable

output enable

logic

Y-Decoder

X-Decoder

Address Latch

STB

DQ0~DQ15

Input/Output

buffers

Data latch

Y-Gating

Cell matrix

1-32

Page 33

XV-D9000

MC44724AVFU (IC554) : VIDEO ENCODER

1.Terminal layout 2.Block diagrams

64 ~ 49

1

~

16

17 ~ 32

3.Pin function

No. Symbol

1

CVBS/Cb/B1

2

CVBS/Cb/B1

3

CVBS/Cb/B1Vdd

4

Y/G1

5

Y/G1

6

Y/G1/Vdd

7

C/Cr/R1

8

C/Cr/R1

9

C/Cr/R1Vdd

10

DAVss

11

TBIAS1

12

Vref1

13

DAVdd

14

Vref2

15

TBIAS2

16

NC

17

CVBS/Cb/B2

18

CVBS/Cb/B2

19

CVBS/Cb/B2Vdd

20

Y/G2

21

Y/G2

22

Y/GVdd

23

C/Cr/R2

24

C/Cr/R2

25

C/Cr/R2Vdd

26

ChipA

27

TEST

28

DVdd

29

CLOCK

30

DVss

31

Reset

32

PAL/NTSC

48

~

33

I/O

O

Analog composite drive signal (+)

O

Analog composite drive signal (-)

-

Power supply for CVBS/Cb/B DAC1

O

Analog brightness signal/G drive signal (+)

O

Analog brightness signal/G drive signal (-)

-

Power supply for Y/G DAC

O

Analog chroma signal (+)

O

Analog chroma signal (-)

-

Power supply for C/Cr/RDAC

-

Connect to ground for DAC

O

Standard BIAS for DAC1

-

Standard voltage for DAC1

-

Power supply for DAC

-

Standard voltage for DAC2

O

Standard BIAS for DAC2

-

Non connect

O

Analog composite drive signal (+)

O

Analog composite drive signal (-)

-

Power supply for CVBS/Cb/B DAC2

O

Analog brightness signal/G drive signal (+)

O

Analog brightness signal/G drive signal (-)

-

Power supply for Y/G DAC

O

Analog chroma signal (+)

O

Analog chroma signal (-)

-

Power supply for C/Cr/RDAC2

-

Chip address selection

I

Connect to test pin

-

Digital ground

I

Clock signal input (27MHz)

-

Power supply for digital circuit

I

Reset signal input L:ON

I

Selection NTSC/PAL NTSC:L PAL:H

DVdd

DVss

DVIA[7:0]

DVIB[7:0]

A/B_sel

TP

Clock

ChipA

Reset

PAL/NTSC

Function

H.V

DEMAX

Y

cb

cr

12C / SPI

SO

SDA/SI

C/Fsync/VBI

Sync_ generator

CGMS,

wss gen

0

off_set

0

0

sub carrier

SEL

SCL/SCK

No. Symbol

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

F/Vsync

CCwss gen

Modulator

gen

SO

SDA/SI

SCL/SCK

SEL

DVdd

DVss

DVIN7

DVIN6

DVIN5

DVIN4

DVIN3

DVIN2

DVIN1

DVIN0

TVIN

EXT

F/Vsyac

Chsyac

DATST

TP8

TP7

TP6

TP5

DVss

DVdd

TP4

TP3

TP2

TP1

TP0

DLVdd

DLVss

Hsync

RGB

matrix

Y/G2Vdd

C/Cr/R2Vdd

CVBS/Cb/B2Vdd

Copy,

protection

bus

0

+

0

+

0

0

0

Output Selector

0

DAC BIAS DAC DAC DAC

DAC

DAC

BIAS

TEST

bus

TEST

I/O

-

Non connect

I

SPI Mode : Serial data input

I

Serial clock input

I

Power supply for serial data,chip select,digital

--

Power supply for digital circuit

--

Digital ground

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I

VIDEO mute on Reset(0:nomal, 1:mute)

I/O

Frame output / VBI information input

I/O

Frame / Vertical, synchronous I/O

I/O

The horizontal, synchronous I/O

I

Data input

I/O

Multiplex data input

I/O

Multiplex data input

I/O

Multiplex data input

I/O

Multiplex data input

-

Ground for digital circuit

-

Power supply for digital circuit

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

-

Power supply for D/A converter

-

Ground for D/A converter

DAVss

DAVdd

Function

Y/G1Vdd

CVBS/Cb/B1Vdd

C/Cr/R1Vdd

Y/G1

Y/G1

CVBS/Cb/B1

CVBS/Cb/B1

C/Cr/R1

C/Cr/R1

Vref1

iBIAS1

Y/G2

Y/G2

CVBS/Cb/B2

CVBS/Cb/B2

C/Cr/R2

C/Cr/R2

Vref2

Ibias

1-33

Page 34

XV-D9000

MN102LP25G(IC401):UNIT CPU

Pin No. Pin No.

Symbol Symbol

1

WAIT

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

RE

MUTE

WEM

CS0

CS1

CS2

CS3

TCLOSE

TOPEN

LSIRST

WORD

A0

A1

A2

A3

VDD

SYSCLK

VSS

XI

XO

VDD

OSCI

OSCO

MODE

A4

A5

A6

A7

A8

A9

A10

A11

VDD

A12

A13

A14

A15

A16

A17

A18

A19

VSS

A20

TXSEL

TMPSN

ADPD

-

-

TRVSW

I/O I/O

Micon wait signal input

I

Read enable

O

Driver mute

O

Write enable

O

Non connect

O

Chip select for ODC

O

Chip select for ZIVA

O

Chip select for outer ROM

O

Tray close signal output

O

Tray open signal output

O

LSI reset

I

Bus selection input

O

Address bus 0 for CPU

O

Address bus 1 for CPU

O

Address bus 2 for CPU

O

Address bus 3 for CPU

O

Power supply

System clock signal output

O

Power supply

Non connect

Non connect

Power supply

Clock signal input(13.5MHz)

I

Non connect

CPU Mode selection input

I

Address bus 4 for CPU

O

Address bus 5 for CPU

O

Address bus 6 for CPU

O

Address bus 7 for CPU

O

Address bus 8 for CPU

O

Address bus 9 for CPU

O

Address bus 10 for CPU

O

Address bus 11 for CPU

O

Power supply

Address bus 12 for CPU

O

Address bus 13 for CPU

O

Address bus 14 for CPU

O

Address bus 15 for CPU

O

Address bus 16 for CPU

O

Address bus 17 for CPU

O

Address bus 18 for CPU

O

Address bus 19 for CPU

O

Power supply

Address bus 20 for CPU

O

TX Select signal

Connect to ground

Non connect

Non connect

Non connect

Detection switch of traverse

I

inside

Function

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

SWCLOSE

SWOPEN

ADSCEN

VDD

EFPEN

SLEEP

BUSY

REQ

CIRCEN

TEHC

VSS

EECS

EECK

EEDI

EEDO

VDD

SCLK0

S2UDT

S2SDT

CPSCK

SDIN

SDOUT

-

-

NMI

ADSCIRQ

ODCIRQ

DECIRQ

CSSIRQ

ODCIRQ2

ADSEP

RST

VDD

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

TEST8

VSS

D0

D1

D2

D3

D4

D5

D6

D7

Function

Detection switch of tray close

I

Detection switch of tray open

I

Serial enable signal for ADSC

O

Non connect

Serial enable signal for FEP

O

Standby signal for FEP

O

Communication busy

I

Communication Request

O

Serial I/F chip selection

O

To front end processor

O

Power supply

Chip select signal for EEPROM

O

Clock signal for EEPROM

O

Input data for EEPROM

I

Output data for EEPROM

O

Power supply

Communication clock

I

Communication input data

I

Communication output data

O

Clock for ADSC serial

O

ADSC serial data input

I

ADSC serial data output

O

Non connect

Non connect

Non connect

Interrupt input of ADSC

I

Interrupt input of ODC

I

Interrupt input of ZIVA

I

O

Non connect

I

Address data selection input

I

Reset input

I

Power supply

Test signal 1 input

I

Test signal 2 input

I

Test signal 3 input

I

Test signal 4 input

I

Test signal 5 input

I

Test signal 6 input

I

Test signal 7 input

I

Test signal 8 input

I

Power supply

Data bus 0 of CPU

I/O

Data bus 1 of CPU

I/O

Data bus 2 of CPU

I/O

Data bus 3 of CPU

I/O

Data bus 4 of CPU

I/O

Data bus 5 of CPU

I/O

Data bus 6 of CPU

I/O

Data bus 7 of CPU

I/O

1-34

Page 35

MN103007BGA (IC301) : Optical disc controller

1.Pin layout

DMARQ

NIOWR

VSS

NIORD

IORDY

NDMACK

5VDD

INTRQ

IOCS16

DA1

VSS

NPDIAG

DA0

DA2

VDD

NCS1FX

NCS3FX

NDASP

NTRYCL

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

HDD15

HDD0

HDD14

5VDD

HDD1

HDD13

HDD2

VSS

HDD12

VDD

HDD3

HDD11

HDD4

HDD10

5VDD

HDD5

HDD9

VSS

HDD6

HDD8

HDD7

5VDD

NRESET

MASTER

NINT0

NINT1

WAITOOC

NMRST

DASPST

VDD

OSCO2

OSCI2

UATASEL

VSS

PVSSDRAM

PVDDDAM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

3738394041424344454647484950515253545556575859606162636465666768697071

MN103007BGA

126

5VDD

125

NEJECT

VSS

124

123

MONI0

MONI1

122

121

MONI2

MONI3

120

119

SDATA

SCLOCK

118

117

VDD

116

FAT0

115

DAT1

114

DAT2

113

DAT3

112

CHCK4

XCLDCK

111

110

72

SUBC

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

SBCK

VSS