Page 1

22009200302

TH-A75

SERVICE MANUAL

DVD DIGITAL CINEMA SYSTEM

TH-A75

SP-WA75

VCR/DBS

FM/AM

AUDIO

ANGLE

TOP MENU

MENU

DSP

SURROUND

CONTROL

VCR

123

+

S.WFR

Ð

TV

456

SLEEP

789

+

SURR-L

SETTING

Ð

10

TV RETURN

ADJUST

ON

SCREEN

ENTER

CHOICE

CHANNEL/ZOOM

TV/VIDEO MUTING

/REW

PLAY

TUNING

DOWN UP

O.T.

STOP

REPLAY

REC

MEMORY

DIMMER

RMÐSTHA75U

DVD CINEMA SYSTEM

TV AUDIO

DVD

SUBTITLE

RETURN DIGEST

OFF

+

CENTER

Ð

+

S-BACK

Ð

0

FM MODE

VOLUMETV VOL

DECODE

EFFECT

SURR-R

CATV/DBS

PROGRESSIVE

FF/

PAUSE

STROBE

VCR 1

VCR

SOUND

TEST

+

Ð

+10

100+

AUDIO/

TV/VCR

VFP

STANDBY

COMPACT

DIGITAL¥EX

SUPER VIDEO

PRO LOGIC

SP-XSA75

PROGRESSIVE

SP-XCA75

SOURCE

VOLUME

PHONES

XV-THA75

Area Suffix

US ---------------- Singapore

UP --------------------- Korea

UT -------------------- Taiwan

UX ------------ Saudi Arabia

TABLE OF CONTENTS

1 Important Safety Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

2 Disassembly method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

3 Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

4 Description of major ICs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

COPYRIGHT © 2003 VICTOR COMPANY OF JAPAN, LTD.

No.22009

2003/02

Page 2

TH-A75

Important Safety Precautions

1.1 Safety Precautions

(1) This design of this product contains special hardware and

many circuits and components specially for safety purposes.

For continued protection, no changes sho uld be made to the

original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those

used in the original circuits. Services should be performed by qualified personnel only.

(2) Alterations of the design or circuitry of the product should

not be made. Any design alterations of the product should

not be made. Any design alterations or additions will void

the manufacturers warranty and will further relieve the

manufacture of responsibility for personal injury or property

damage resulting therefrom.

(3) Many electrical and mechanical parts in the products have

special safety-related characteristics. These characteristics are often not evident from v isual inspecti on nor can th e

protection afforded by them necessarily be obtained by using replacement components rated for highe r voltage, w a tt age, etc. Replacement parts which have these special safety

characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by ( ) on the

Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the

Parts List of Service Manual may create shock , fire, or other hazards.

(4) The leads in the products are routed and dressed with ties,

clamps, tubings, barriers and the like to be separated from

live parts, high temperature parts, moving parts and/or

sharp edges for the prevention of electric shock and fire

hazard. When service is required, the original lead routing

and dress should be observed, and it should be confirmed

that they have been returned to normal, after reassembling.

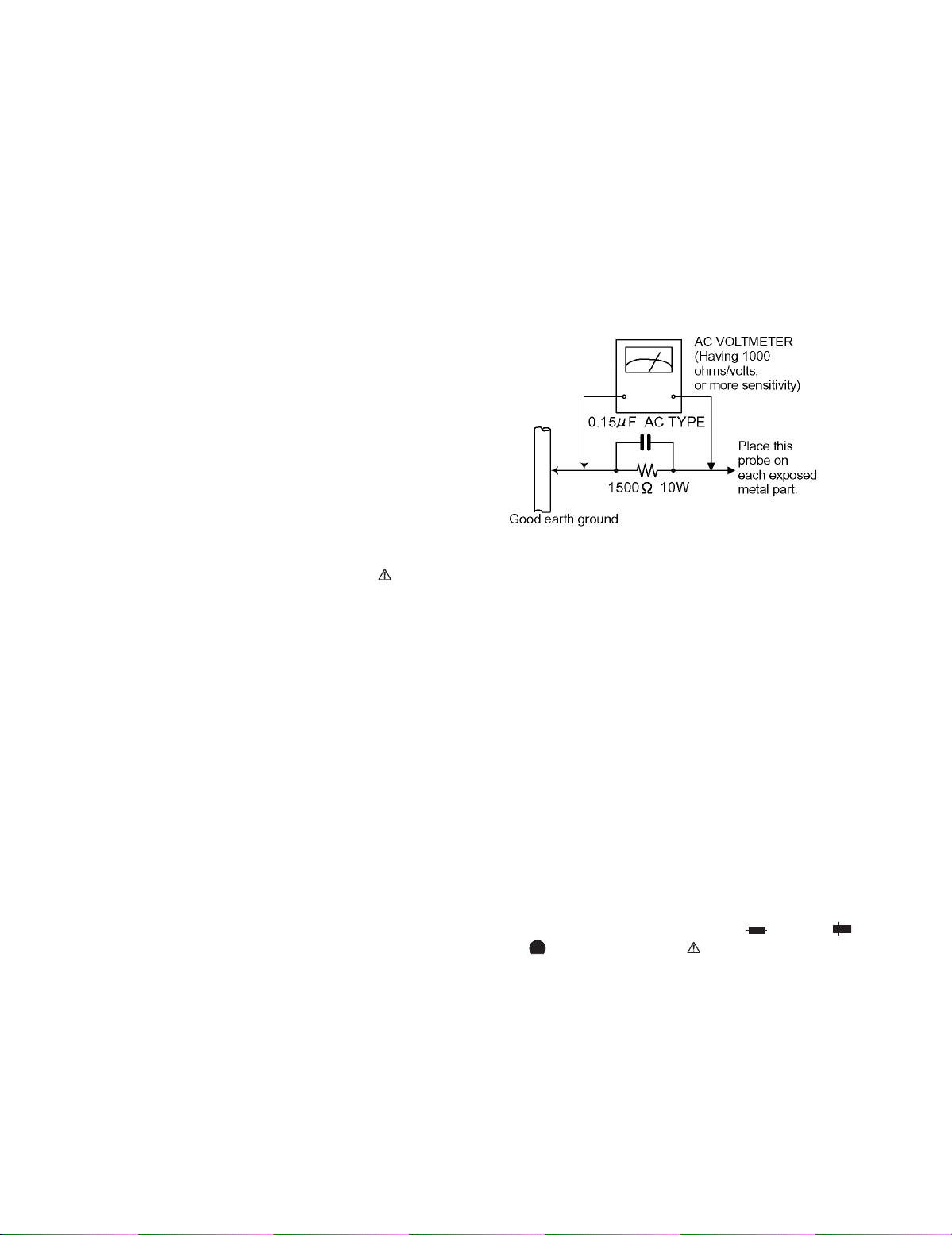

(5) Leakage shock hazard testing)

After reassembling the product, always perform an isolat ion

check on the exposed metal parts of the product (antenna

terminals, knobs, metal cabinet, screw heads, headphone

jack, control shafts, etc.) to be sure the product is safe to

operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

• Plug the AC line cord directly into the AC outlet. Using a

"Leakage Current Tester", measure the leakage current

from each exposed metal parts of the cabinet, partic ularly any exposed metal part having a return path to the

chassis, to a known good earth ground . Any leakage current must not exceed 0.5mA AC (r.m.s.).

• Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC

voltmeter having, 1,000 ohms per volt or more sensitivity in

the following manner. Connect a 1,500 ohm 10W resistor

paralleled by a 0.15 µF AC-type capacitor between an

SECTION 1

exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC

voltmeter.

Move the resistor connection to each exposed meta l part,

particularly any exposed metal part having a return path to

the chassis, and measure the AC voltage across the resistor.

Now, reverse the plug in the AC outlet and repeat each

measurement. Voltage measured any must not exceed 0.75

V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

1.2 Warning

(1) This equipment has been designed and manufactured to

meet international safety standards.

(2) It is the legal responsibility of the repairer to ensure that

these safety standards are maintained.

(3) Repairs must be made in accordance with the relevant

safety standards.

(4) It is essential that safety critical components are replaced

by approved parts.

(5) If mains voltage selector is provided, check setting for local

voltage.

1.3 Caution

Burrs formed during molding may be left over on some parts

of the chassis.

Therefore, pay attention to such burrs in the case of preforming repair of this system.

1.4 Critical parts for safety

In regard with component parts appearing on the silk-screen

printed side (parts side) of the PWB diagrams, t he p arts th at are

printed over with black such as the resistor ( ), diode ( )

and ICP ( ) or identified by the " " mark nearby are critical

for safety.

When replacing them, be sure to use the parts of the same type

and rating as specified by the manufacturer. (Except the JC version)

1-2 (No.22009)

Page 3

TH-A75

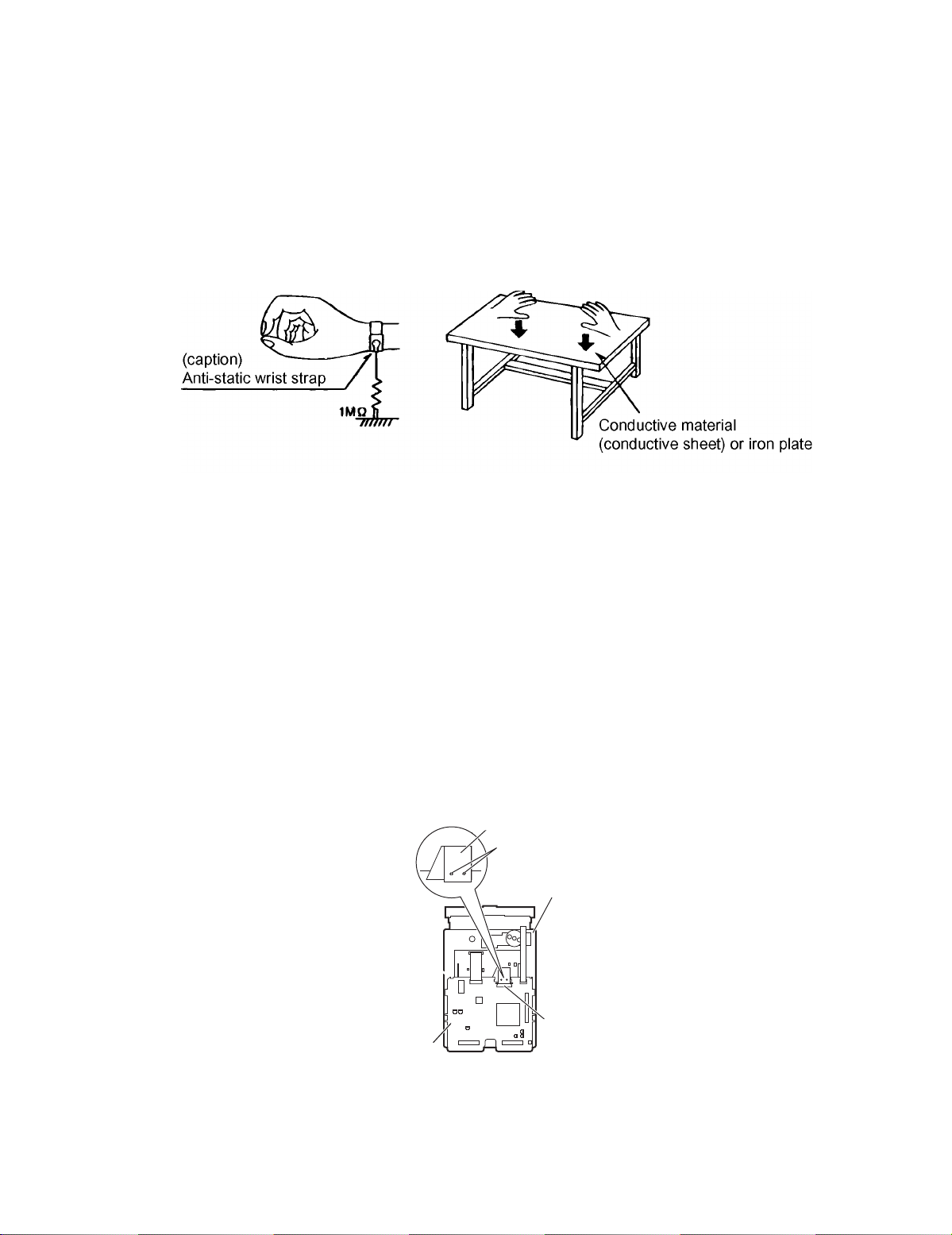

1.5 Preventing static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

1.5.1 Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players.

Be careful to use proper grounding in the area where repairs are being performed.

(1) Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the

traverse unit (optical pickup) on it.

(2) Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

(3) Handling the optical pickup

• In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical

pickup are shorted. After replacement, return the shorted parts to their original condition.

(Refer to the text.)

• Do not use a tester to check the condition of the laser diode in the optical pic kup. The tester's internal powe r source can easily

destroy the laser diode.

1.6 Handling the traverse unit (optical pickup)

(1) Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

(2) Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, re f e r t o the replace-

ment procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time

when attaching it to the connector.

(3) Handle the flexible ca ble carefully as it may break when subjected to strong force.

(4) I t is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it.

1.7 Attention when traverse unit is decomposed

*Please refer to "Disassembly method" in the text for the DVD pickup unit.

• Apply solder to the short land sections before the flexible wire is disconnected from the connector CN101 on the DVD servo board.

(If the flexible wire is disconnected without applying solder, the DVD pickup may be destroyed by static electricity.)

• In the assembly, be sure to remove solder from the short land sections after connecting the flexible wire.

DVD servo board

Flexible wire

Short land sections

DVD mechanism assembly

CN101

(No.22009)1-3

Page 4

TH-A75

1.8 Important for laser products

(1) CLASS 1 LASER PRODUCT

(2) DANGER : Invisible laser radiation when open and inter

lock failed or defeated. Avoid direct exposure to beam.

(3) CAUTION : There are no serviceable parts inside the

Laser Unit. Do not disassemble the Laser Unit. Replace the

complete Laser Unit if it malfunctions.

(4) CAUTION : The compact disc player uses invisible laser

radiation and is equipped with safety switches which

prevent emission of radiation when the drawer is open and

the safety interlocks have failed or are de feated.

It is dangerous to defeat the safety switches.

(5) CAUTION : If safety switches malfunction, the laser is able

to function.

(6) CAUTION : Use of controls, adjustments or performance of

procedures other than those specified herein may result in

hazardous radiation exposure.

CAUTION

Please use enough caution not to see the beam directly

or touch it in case of anadjustment or operation check.

VARNING

Osynlig laserstrålning är denna del är öppnad och spårren är

urkopplad. Betrakta ej strålen.

VARO

Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle. Älä katso säteeseen.

REPRODUCTION AND POSITION OF LABELS

CLASS 1

LASER PRODUCT

ADVARSEL

Usynlig laserstråling ved åbning, når sikkerhedsafbrydere er

ude af funktion. Undgå udsasttelse for stråling.

ADVARSEL

Usynlig laserstråling ved åpning, når sikkerhetsbryt eren er avslott. unngå utsettelse for stråling.

WARNING LABEL

1-4 (No.22009)

Page 5

SECTION 2

r

Disassembly method

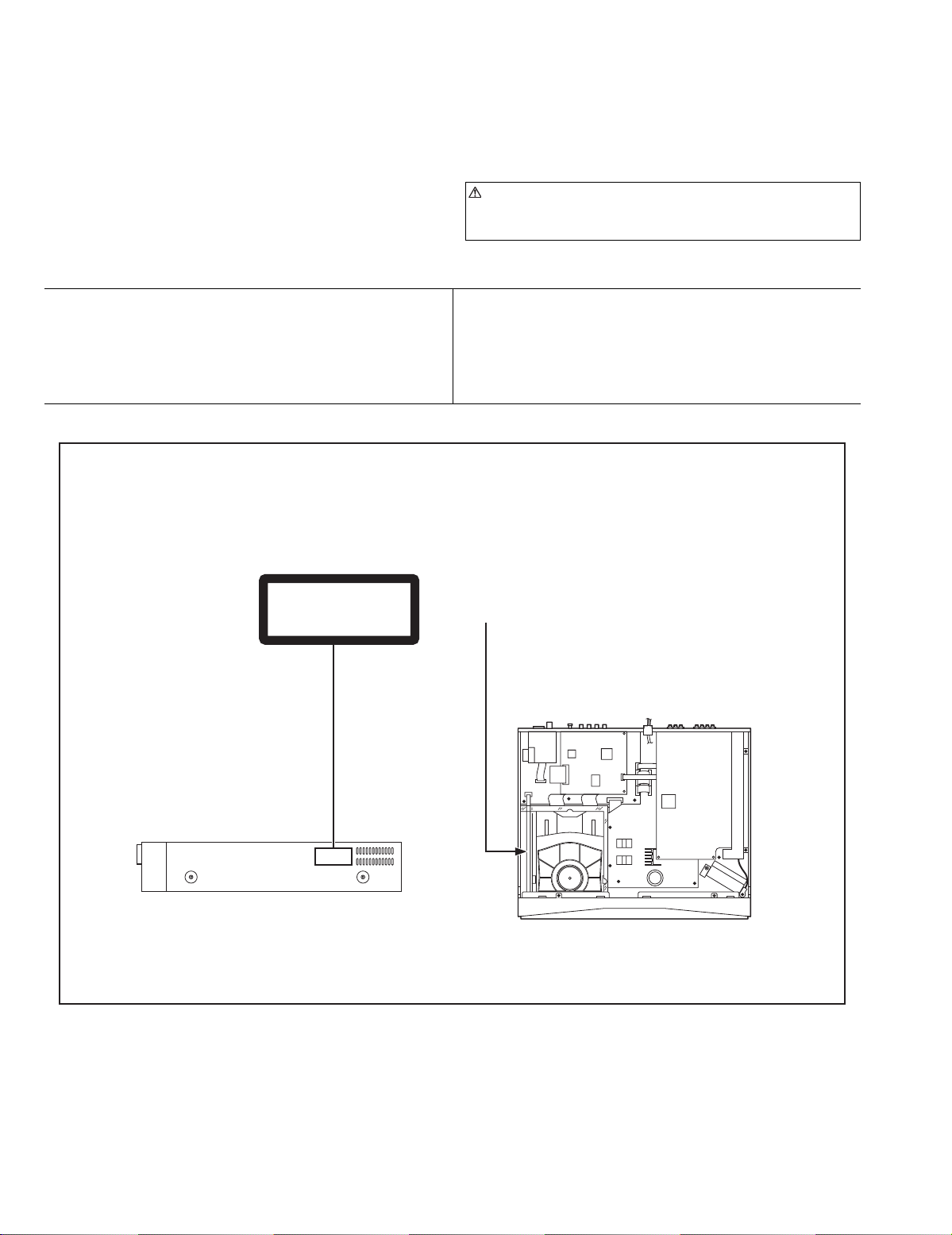

2.1 Main body section

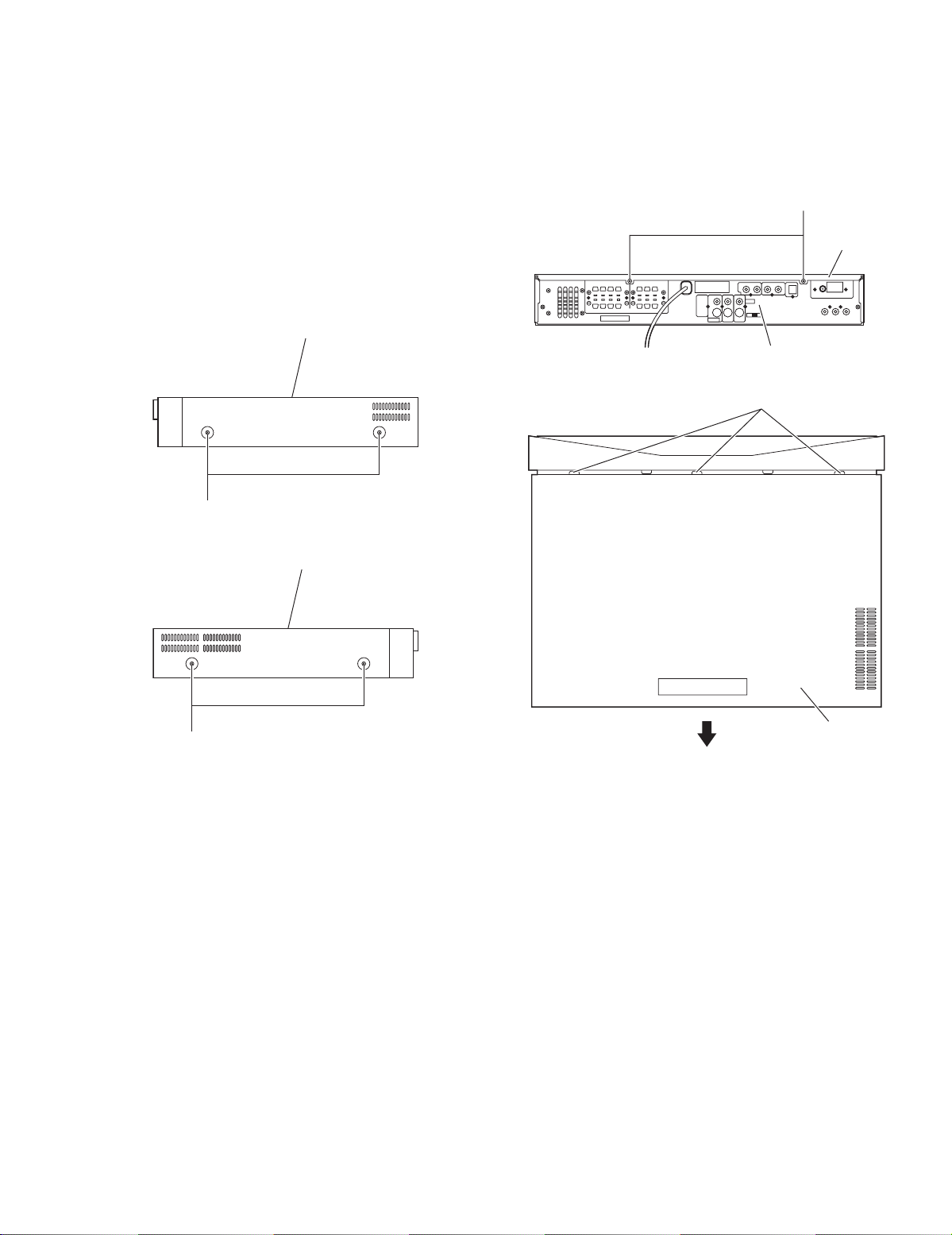

2.1.1 Removing the top cover (See Figs.1 to 4.)

(1) From the right and left sides of the main body, remove the

four screws A attaching the top cover. (See Figs.1 and 2.)

(2) From the back side of the main body, remove the two

screws B attaching the top cover. (See Fig.3.)

(3) Lift the rear section of the top cover, slide the top cover

slightly in the direction of the arrow. (See Fig.4.)

(4) Disengage the engagement sections a of the top cover

from the main body. (See Fig.4.)

Top cover

TH-A75

B

Top cove

Rear panel

Fig.3

a

A

A

Fig.1

Top cover

Top cover

Fig.4

Fig.2

(No.22009)1-5

Page 6

TH-A75

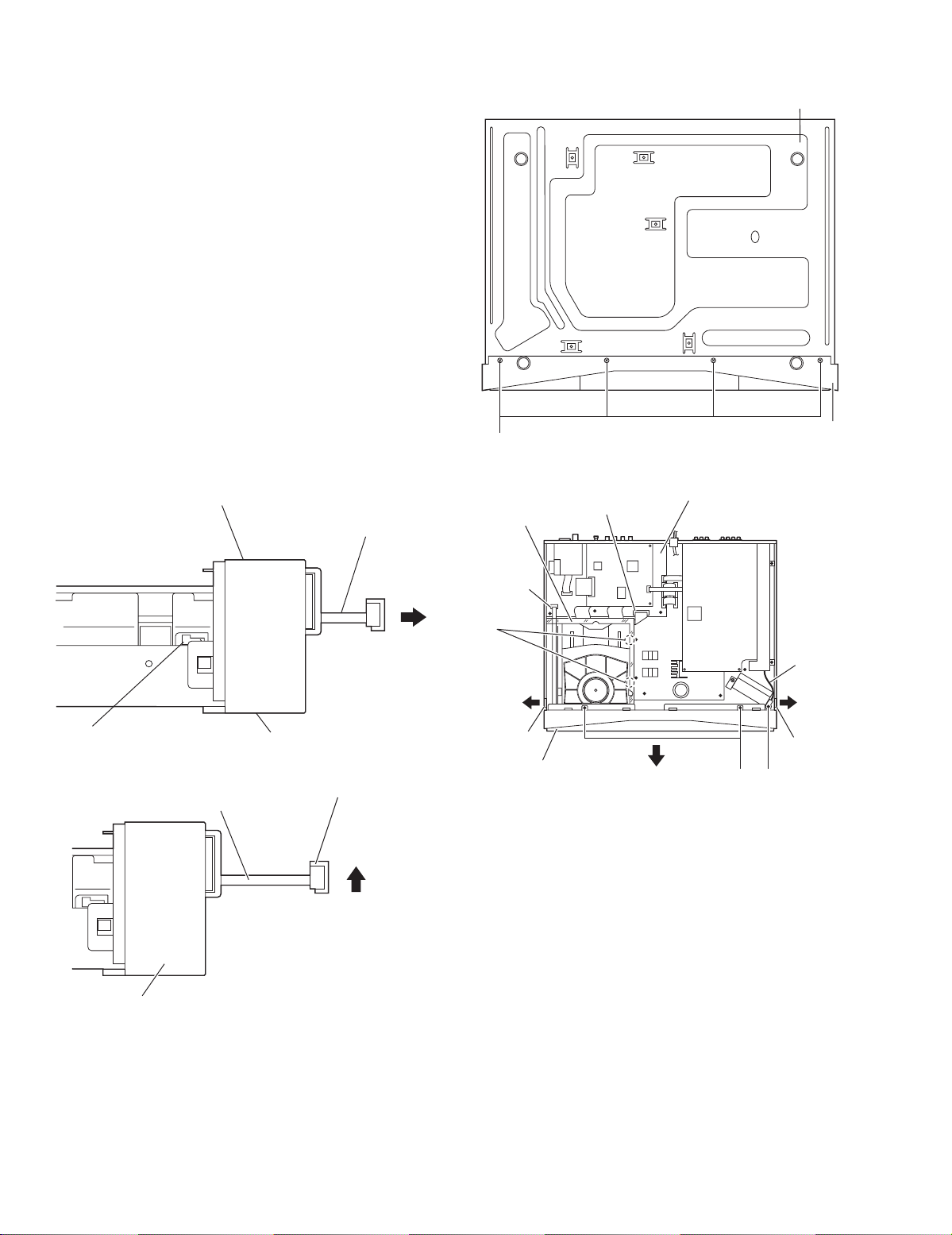

2.1.2 Removing the front panel assembly (See Figs.5 to 8.)

• Remove the top cove r.

(1) From the left side of the main body, push the section b of

the slide cam using the screw driver, etc. (See Fig.5.)

(2) Pull out the tray. (See Fig.5.)

(3) Push the tray fitting assembly of the tray in the direction of

the arrow and then remove the tray fitting assembly. (See

Fig.6.)

(4) Return the tray into the DVD mechanism assembly.

(5) From the bottom side of the main body, remove the four

screws C attaching the front panel assembly. (See Fig.7.)

(6) From the top side of the main body, remove the two screws

D attaching the front panel assembly. (See Fig.8.)

(7) Disconnect the card wires from the connectors CN206 and

CN207 on the main board. (See Fig.8.)

(8) Remove the screw E attaching the lug wire. (See Fig.8.)

(9) While opening the hooks c to the right and left sides of the

front panel assembly in the direction of the arrow 1, remove

the front panel assembly i n the direction of the arrow 2.

(See Fig.8.)

Reference:

In the assembly, through the card wire in the barrier and

then hold the card wire to the sections d of the barrier.

(See Fig.8.)

Front panel assembly

Tray

C

Barrier

Chassis base

Front panel assembly

Fig.7

Main board

CN207

Slide cam

Front panel assembly

Tray

Fig.5

Fig.6

b

Tray fitting assembly

CN206

d

1

Hook c

Front panel assembly

2

Fig.8

Lug wire

1

Hook c

D E

1-6 (No.22009)

Page 7

TH-A75

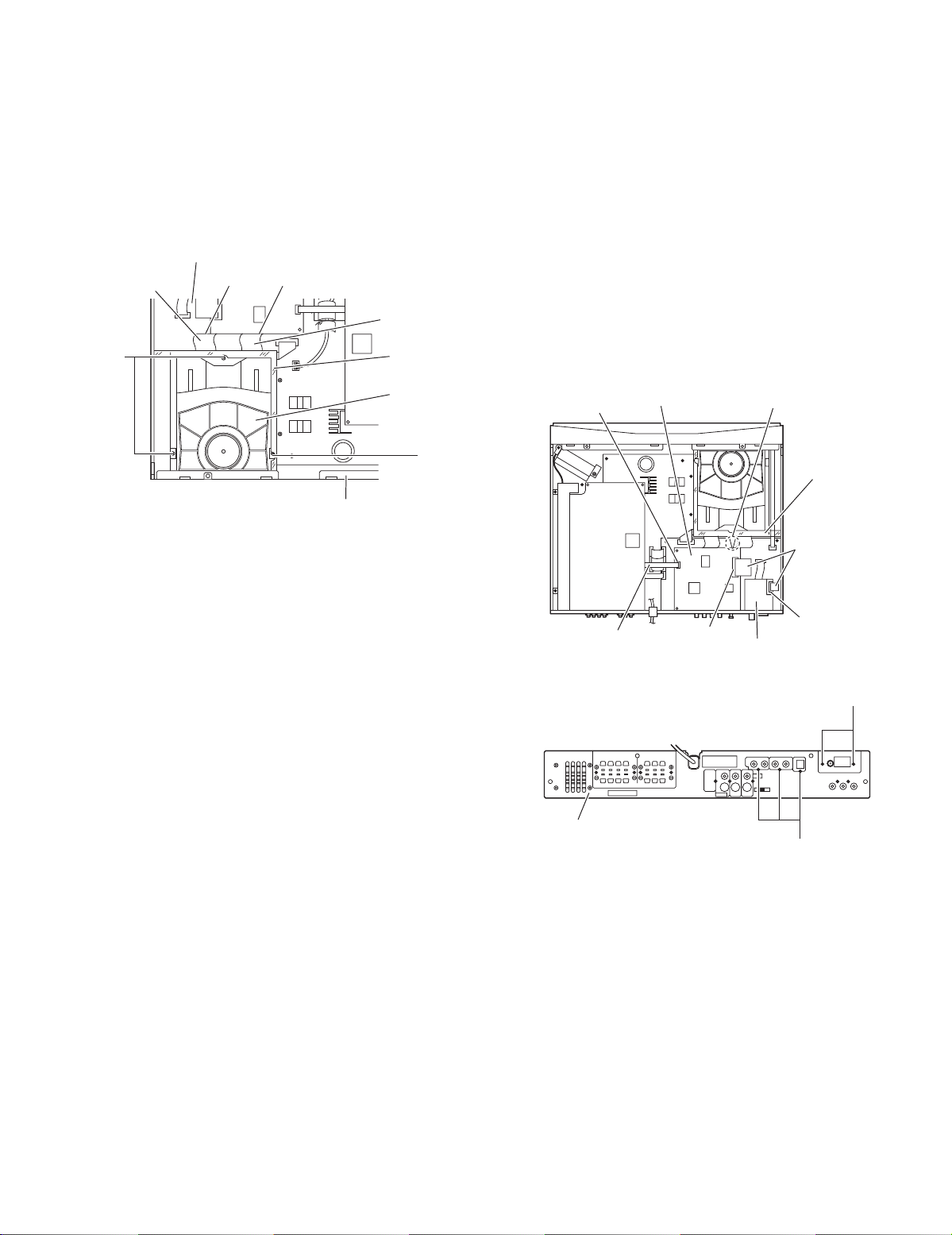

2.1.3 Removing the DVD mechanism assembly ( See Fig.9.)

• Remove the top cove r.

• Remove the front panel assembly.

(1) From the top side of the main body, remove the barrier.

(2) Disconnect the card wires from the connectors CN208 and

CN209 on the main board.

(3) Remove the three screws F attaching the DVD mechanism

assembly.

(4) Take out the DVD mechanism assembly from the chassis

base.

Main board

Card wire

F

CN209 CN208

Card wire

Barrier

DVD

mechanism

assembly

F

Chassis base

Fig.9

2.1.4 Removing the DSP board (See Figs.10 and 11.)

• Remove the top cover.

(1) From the top side of the main body, disconnect the card

wires from the connectors CN591 and CN592 on the DSP

board. (See Fig.10.)

(2) From the back side of the main body, remove the three

screws G attaching the DSP board. (See Fig.11.)

(3) Remove the DSP board from the section e of the barrier,

take out the DSP board. (See Fig.10.)

Reference:

When attaching the DSP board, hang the DSP board to

the section e of the ba rrier. (See Fig.10.)

2.1.5 Removing the tuner (See Figs.10 and 11.)

• Remove the top cover.

(1) From the top side of the main body, disconnect the card

wire from the connector CN1 on the tuner. (See Fig.10.)

(2) From the back side of the main body, remove the two

screws H attaching the tuner. (See Fig.11.)

CN592

DSP board

e

Barrier

Card wires

Card wire

Rear panel

CN591

Fig.10

Fig.11

CN1

Tuner

H

G

(No.22009)1-7

Page 8

TH-A75

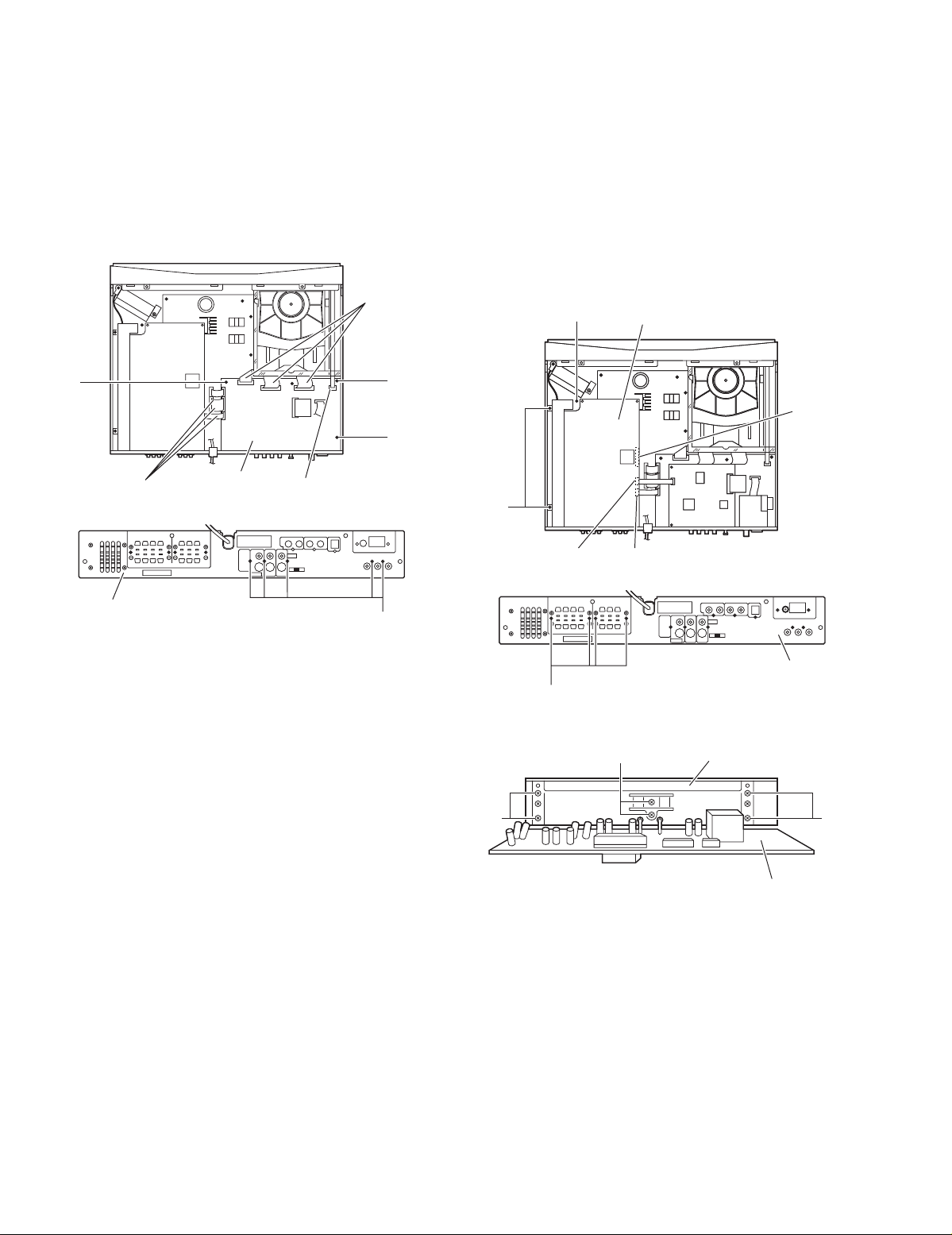

2.1.6 Removing the main board (See Figs.12 and 13.)

• Remove the top cove r.

• Remove the DSP board.

• Remove the tune r.

(1) From the top side of the main body, disconnect the card

wires from the connectors (CN201, CN202, CN204,

CN206-CN209) on the main board. (See Fig.12.)

(2) Remove the screw J and two screws K attaching the main

board. (See Fig.12.)

(3) From the back side of the main body, remove the five

screws L attaching the main board. (See Fig.13.)

Card wires

J

CN207

CN202

CN201

CN204

CN208

CN209

K

K

Card wires

Main board

Fig.12

CN206

2.1.7 Removing the amplifier board (See Figs.14 to 16.)

• Remove the top cover.

(1) From the top side of the main body, disconnect the card

wires from the connectors CN701 and CN702 on the amplifier board (See Fig.14.)

(2) Remove the three screws M attaching the amplifier board.

(See Fig.14.)

(3) From the back side of the main body, remove the four

screws N attaching the amplifier board. (See Fig.15.)

(4) Disconnect the connector CN703 on the amplifier board,

take out the amplifier board. (See Fig.14.)

(5) Remove the six screws P attaching the heat sink t o the am-

plifier board. (See Fig.16.)

M

Amplifier board

CN703

M

Rear panel

Fig.13

L

N

P

CN702CN701

Fig.14

Rear panel

Fig.15

Heat sink

PP

Amplifier board

Fig.16

1-8 (No.22009)

Page 9

TH-A75

t

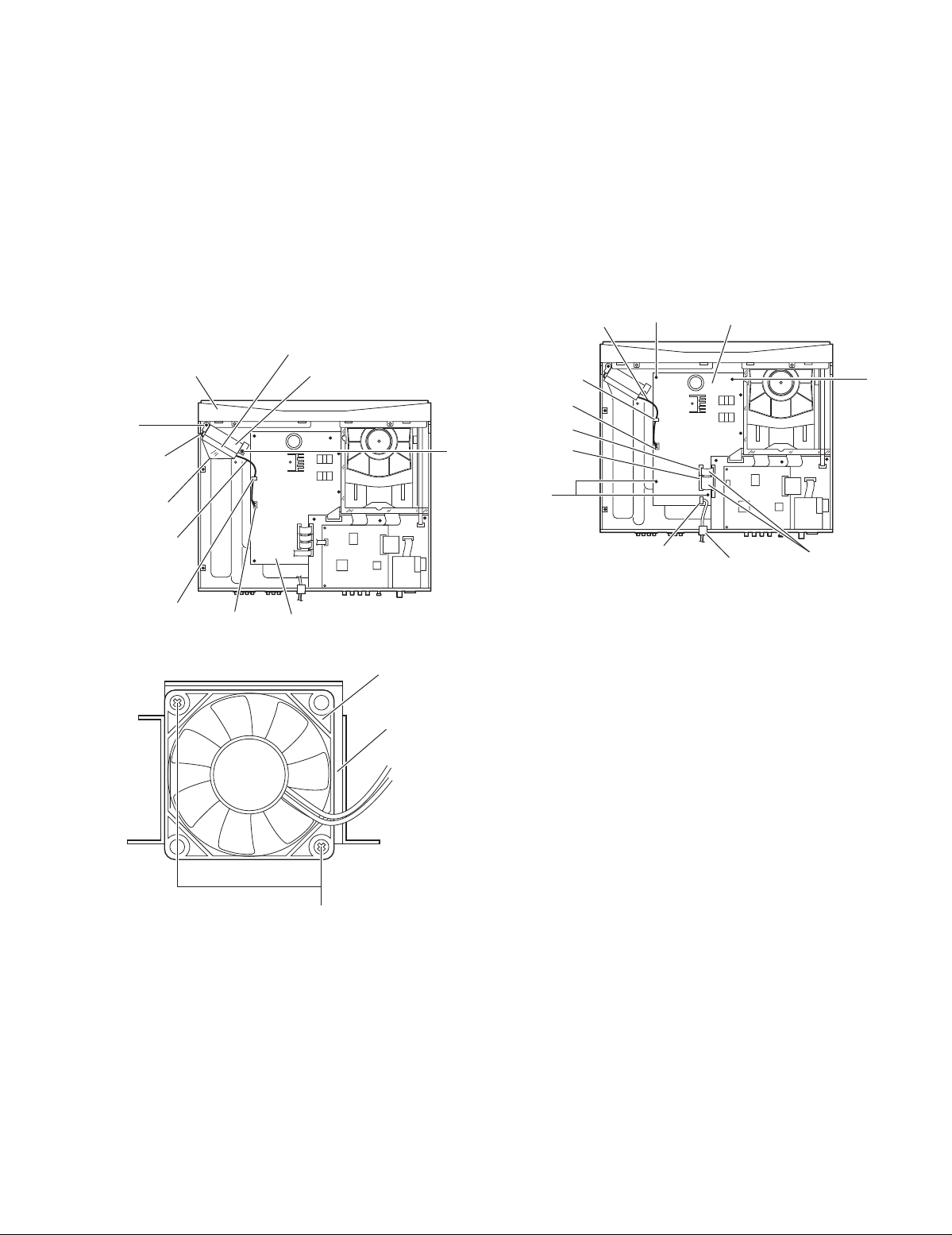

2.1.8 Removing the fan motor (See Figs.17 and 18.)

• Remove the top cove r.

• Remove the amplifier board.

(1) From the top side of the main body, remove the fan cover.

(See Fig.17.)

(2) Remove the tie band banding the fan motor wire and then

disconnect the fan motor wire from the connector CN174

on the power board. (See Fig.17.)

(3) Remove the screw Q and screw R attaching the fan brack-

et. (See Fig.17.)

(4) Remove the two screws S attaching the fan motor to the

fan bracket. (See Fig.18.)

Reference:

When attaching the screw Q, attach the lug wire of the

front panel assembly at the same time.

Fan motor

Front panel assembly

Fan bracket

Q

Lug wire

Fan cover

R

2.1.9 Removing the power board (See Fig.19.)

• Remove the top cover.

• Remove the amplifier board.

(1) From the top side of the main body, disconnect the card

wires from the connectors CN172 and CN173 on the power

board.

(2) Remove the tie band banding the fan motor wire and then

disconnect the fan motor wire from the connector CN174

on the power board.

(3) Disconnect the power cord from the connector CN101 on

the power board.

(4) Remove the screw T and three screws U attaching the

power board.

Fan motor wire

Tie band

CN174

CN173

CN172

T

Power board

U

U

Fan motor wire

Tie band

CN174

Power board

Fig.17

S

Fig.18

Fan motor

Fan bracke

CN101

Power cord

Fig.19

Card wires

(No.22009)1-9

Page 10

TH-A75

V

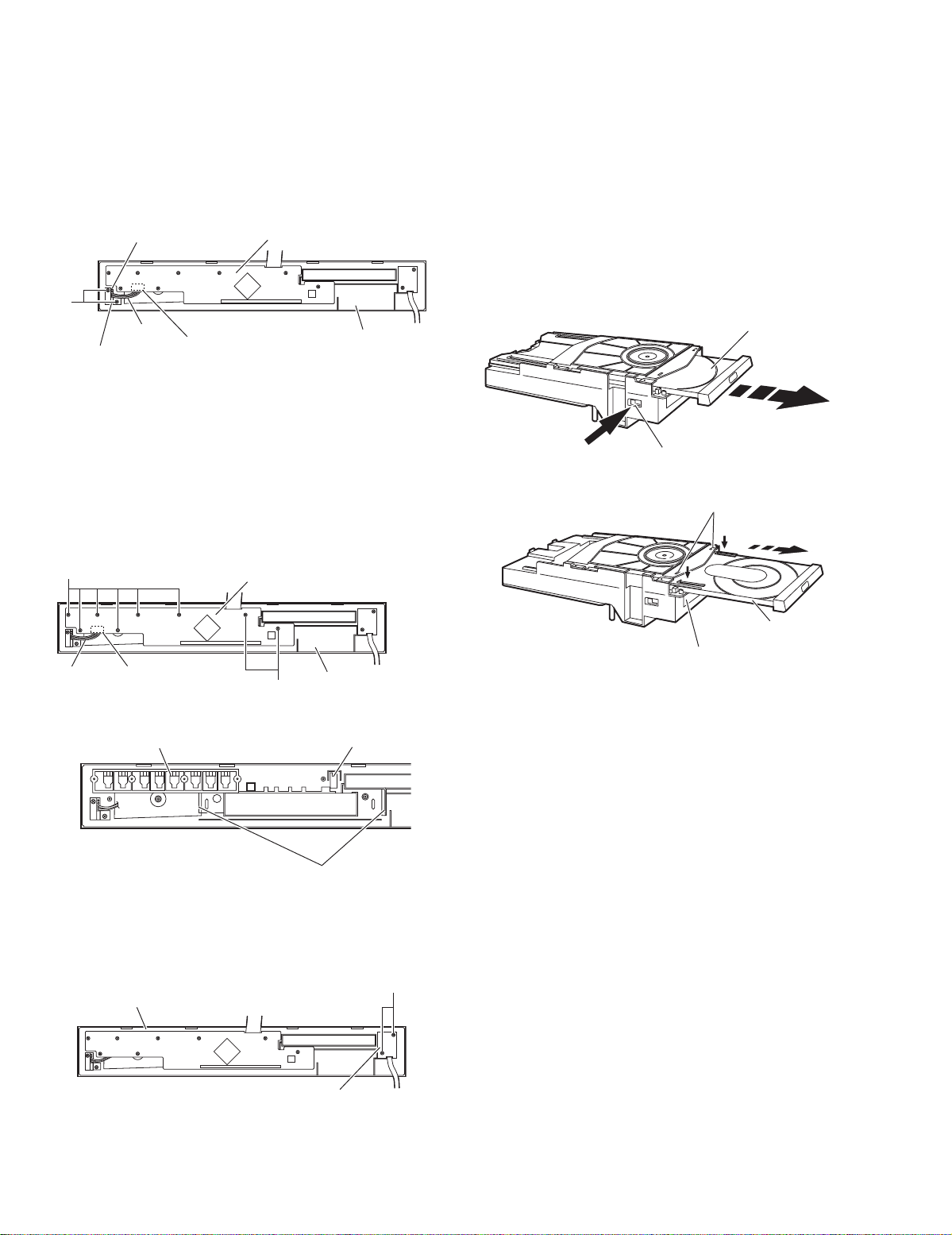

2.2 Front panel assembly section

• Remove the top cove r.

• Remove the front panel assembly.

2.2.1 Removing the jack board (See Fig.1.)

(1) From the inside of the front panel assembly, disconnect the

wire from the connector CN403 on the switch board.

(2) Remove the two screws V attaching the jack holder, take

out the jack board together the jack holder.

Jack board

Wire

Jack holder

2.2.2 Removing the switch board (See Figs.2 and 3.)

(1) From the inside of the front panel assembly, disconnect the

wire from the connector CN403 on the switch board. (See

Fig.2.)

(2) Remove the eight screws W attaching the switch board,

take out the switch board. (See Fig.2.)

Reference:

In the assembly, attach the switch board after attaching

the push buttons and light lens as before. (See Fig.3.)

CN403

W

Switch board

Front panel assembly

Fig.1

Switch board

2.3 DVD mechanism section

• Remove the top cover.

• Remove the DVD mechanism assembly.

2.3.1 Removing the tray (See Figs.1 and 2.)

(1) From the left side of the DVD mechanism assembly, push

the slide cam in th e direction o f the arrow 1 and then pull

out the tray in the direction of the arrow 2. (See Fig.1.)

(2) Push the tray stoppers a in the direction of the arrow 3, pull

out the tray in the direction of the arrow 4. (See Fig.2.)

2.3.2 Attaching the tray (See Fig.2.)

When attaching the tray, insert the tray to the rail of the DVD

mechanism assembly and then pus h the tr ay in th e DVD mechanism assembly.

Tray

2

1

Slide cam

Fig.1

Tray stoppers a

3

4

Wire

CN403

Front panel assembly

W

Fig.2

Push button Push button

Light lens

Fig.3

2.2.3 Removing the standby board (See Fig.4.)

From the inside of the front panel assembly, remove the two

screws X attaching the standby board.

X

Front panel assembly

Tray

DVD mechanism assembly

Fig.2

1-10 (No.22009)

Standby board

Fig.4

Page 11

TH-A75

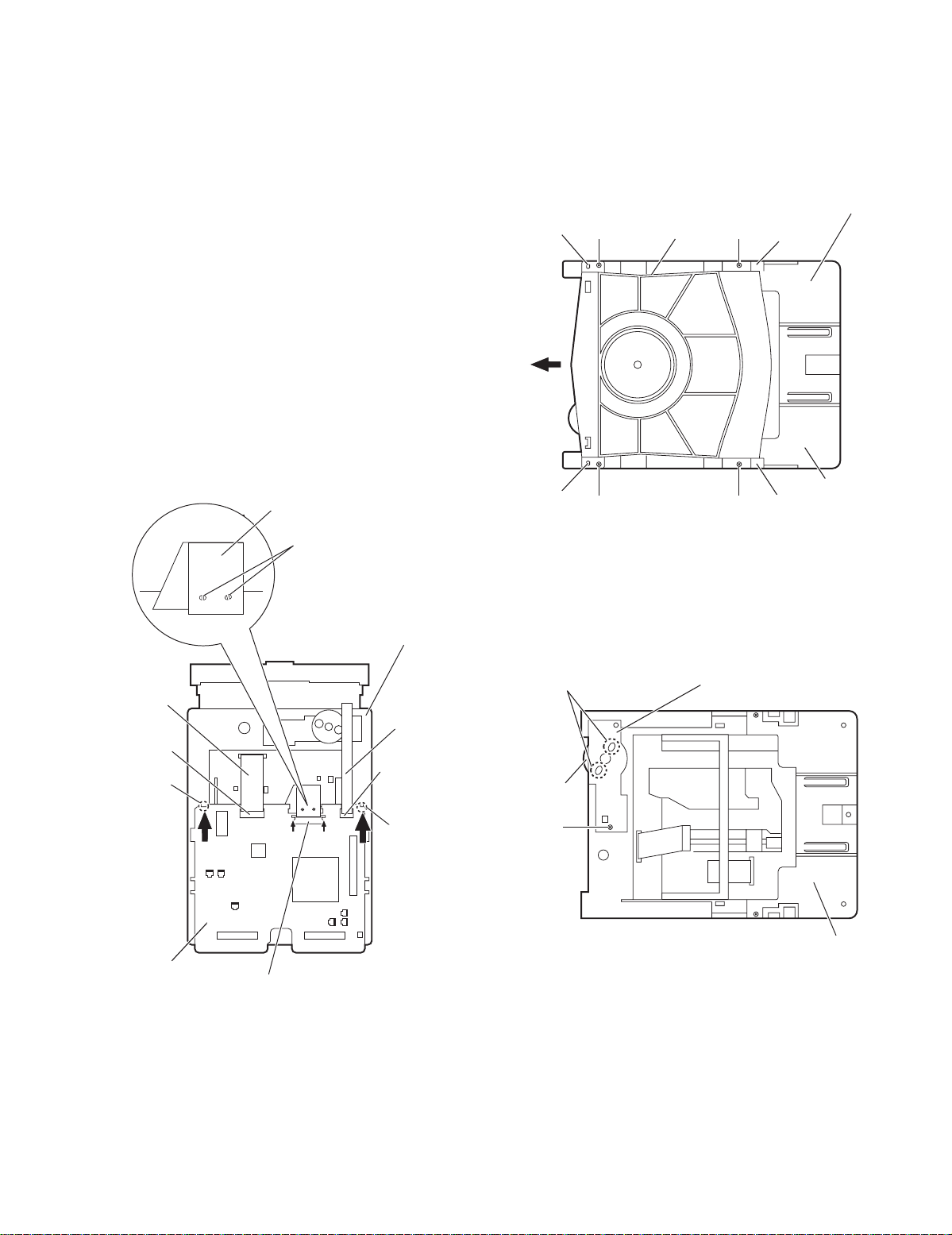

2.3.3 Removing the tray (See Fig.3.)

(1) From the bottom side of the DVD mechanism assembly,

disconnect the card wires from the connectors CN201 and

CN202 on the DVD servo board.

Caution:

Be sure to solder the short land sections b on th e flexible

wire before disconnecting the flexible wire from connector CN101 on the DVD servo board.

If the flexible wire is disconnected without attaching solder, the DVD pickup unit may be destroyed by static

electricity.

(2) Release the locks of the connector CN101 (in the direction

of the arrow 1) on the DVD servo board, disconnect the

flexible wire.

(3) Release the locks of the connector CN101 on the DVD ser-

vo board in the direction of the arro w 1, disconnect the flexible wire.

Caution:

In the assembly, be sure to remove solders from the

short land sections b after connecting the flexib le wire to

the connector CN101 on the DVD servo board.

(4) While pushing the claw c of the DVD mechanism assembly

in the direction of the arrow 2, remove the DVD servo board

in an upward direction.

Flexible wire

Short land sections b

DVD mechanism assembly

Card wire

2.3.4 Removing the clamper base (See Fig.4.)

(1) From the top side of the DVD mechanism assembly, re-

move the four screws A attaching the clamper base.

(2) Remove the clamper base from the bosses d of the loading

base in an upward direction, remove the clamper base

from the sections e while sliding it in the direc tion of th e arrow.

DVD mechanism assembly

Boss d

Boss d

2.3.5 Removing the tray drive board (See Fig.5.)

• Remove the clamper base.

(1) From the bottom side of the DVD mechanism assembly, re-

move the solders from the soldered sections f on the tray

drive board.

(2) Remove the screw B attaching the tray drive board to the

DVD mechanism assembly.

Soldered sections f

Clamper base

AA

A A

Fig.4

Tray drive board

Section e

Loading base

Section e

CN201

Claw c

DVD servo board

2 22

11

CN101

Fig.3

Card wire

CN202

Claw c

Motor

B

DVD mechanism assembly

Fig.5

(No.22009)1-11

Page 12

TH-A75

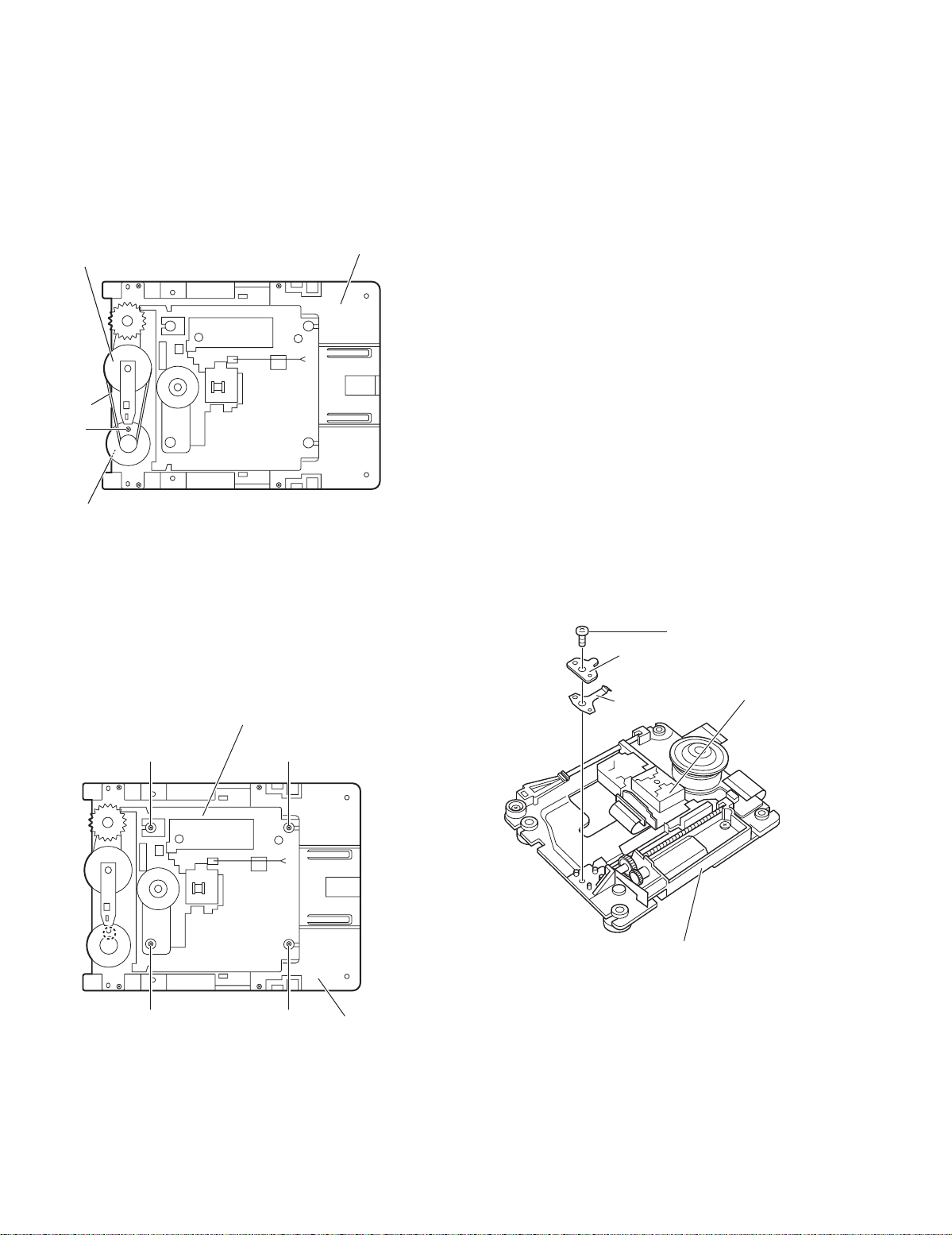

2.3.6 Removing the motor (See Fig.6.)

• Remove the clamper base.

• Remove the tray drive board.

(1) From the top side of the DVD mechanism assembly, re-

move the belt of the pulley gear.

Note:

Take care not to attach grease on the belt.

(2) Remove the screw C attaching the motor to the DVD mech-

anism assembly.

DVD mechanism assembly

Pulley gear

Belt

C

Motor

Fig.6

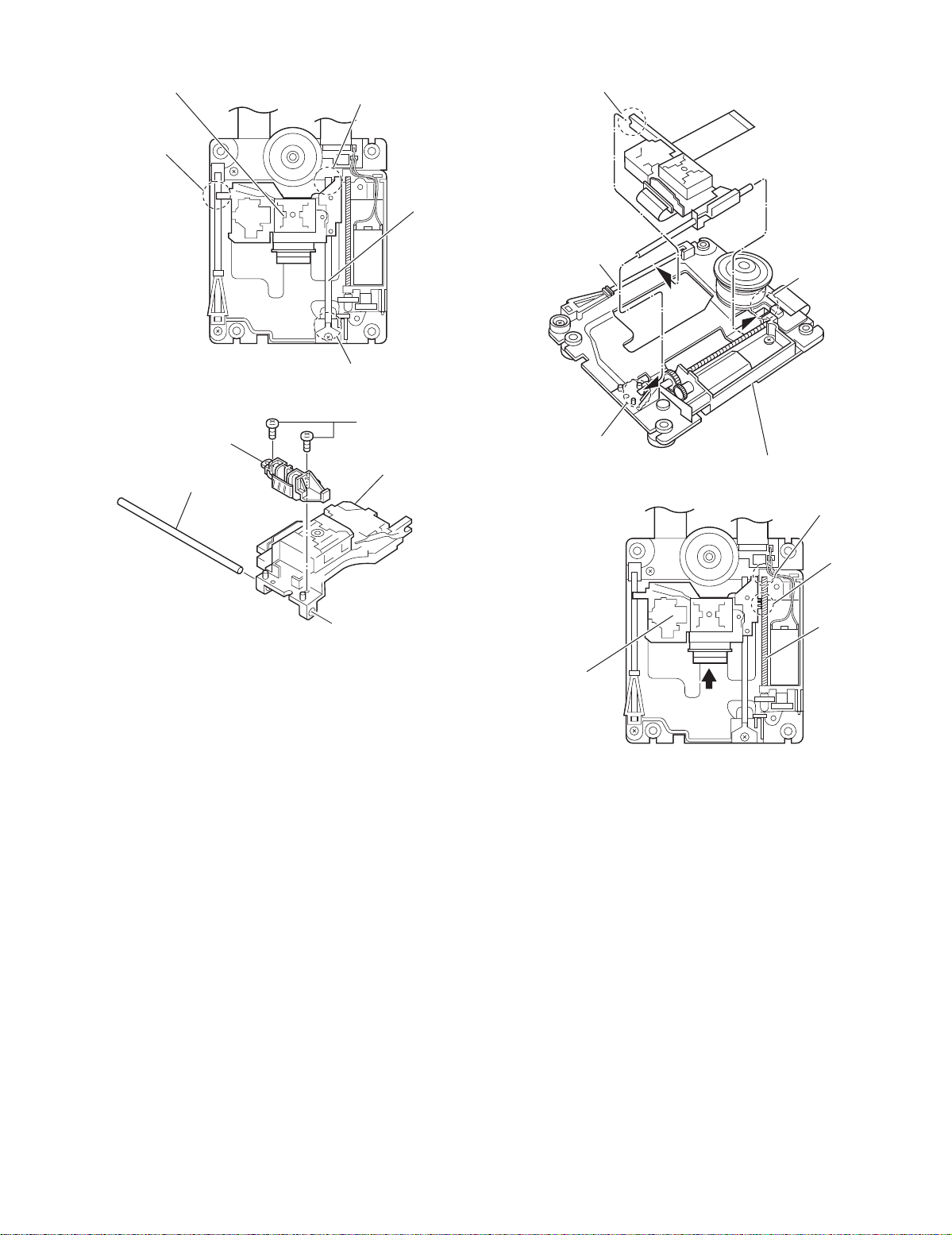

2.3.7 Removing the DVD traverse mechanism assembly

(See Figs.7.)

• Remove the DVD servo board.

• Remove the clamper base.

(1) From the top side of the DVD mechanism assembly, re-

move the four screws D attaching the DVD traverse mechanism assembly to the loading base.

(2) Take out the DVD traverse mechanism assembly from the

loading base.

DVD traverse mechanism assembly

2.3.8 Removing the DVD pickup unit (See Figs.8 to 10.)

• Remove the DVD servo board.

• Remove the clamper base.

• Remove the DVD traverse mechanism assembly.

(1) From the top side of the DVD traverse mechanism assem-

bly, remove the screw E a ttaching the plate and torsion

spring. (See Fig.8.)

(2) Remove the shaft from the section g and then remove the

shaft from the section h. (See Fig.9.)

(3) Disengage the section i of the DVD pickup unit and then re-

move the DVD pickup unit with the shaft.

(4) Pull the shaft out of the DVD pickup unit.

(5) Remove the two screws F attaching the SW. actuator.

2.3.9 Attaching the DVD pickup unit (See Figs.8,10 to 12)

Reference:

Refer to the explanation of "Removing the DVD pickup unit" on

the preceding page.

(1) Attach the SW. actuator and shaft to the DVD pickup unit.

(See Fig.10.)

(2) Engage the section i of the DVD pickup unit to the shaft of

the DVD traverse mechanism assembly first, and set the

both ends of the shaft of the DVD pickup unit in the sections

g and h of the DVD traverse mechanism assembly. (See

Fig.11.)

(3) Slide the DVD pickup unit all the way in the direction of the

arrow. (See Fig.12.)

(4) Mesh the lead screw to the section j of DVD pickup unit and

then set the end of the lead screw to the section k. (See

Fig.12.)

(5) Attach the torsion spring. (See Fig.8.)

(6) Attach the plate. (See Fig.8.)

E

Plate

Torsion spring

DVD pickup unit

1-12 (No.22009)

D D

DD

Fig.7

Loading base

DVD traverse mechanism assembly

Fig.8

Page 13

TH-A75

t

w

DVD pickup unit

Section i

SW. actuator

Shaft

Fig.9

Section h

Section g

F

DVD pickup unit

Shaf

Section

Shaft

Section

i

Section h

DVD traverse mechanism assembly

Fig.11

Section k

Fig.10

Section j

Lead scre

DVD pickup unit

Fig.12

(No.22009)1-13

Page 14

TH-A75

r

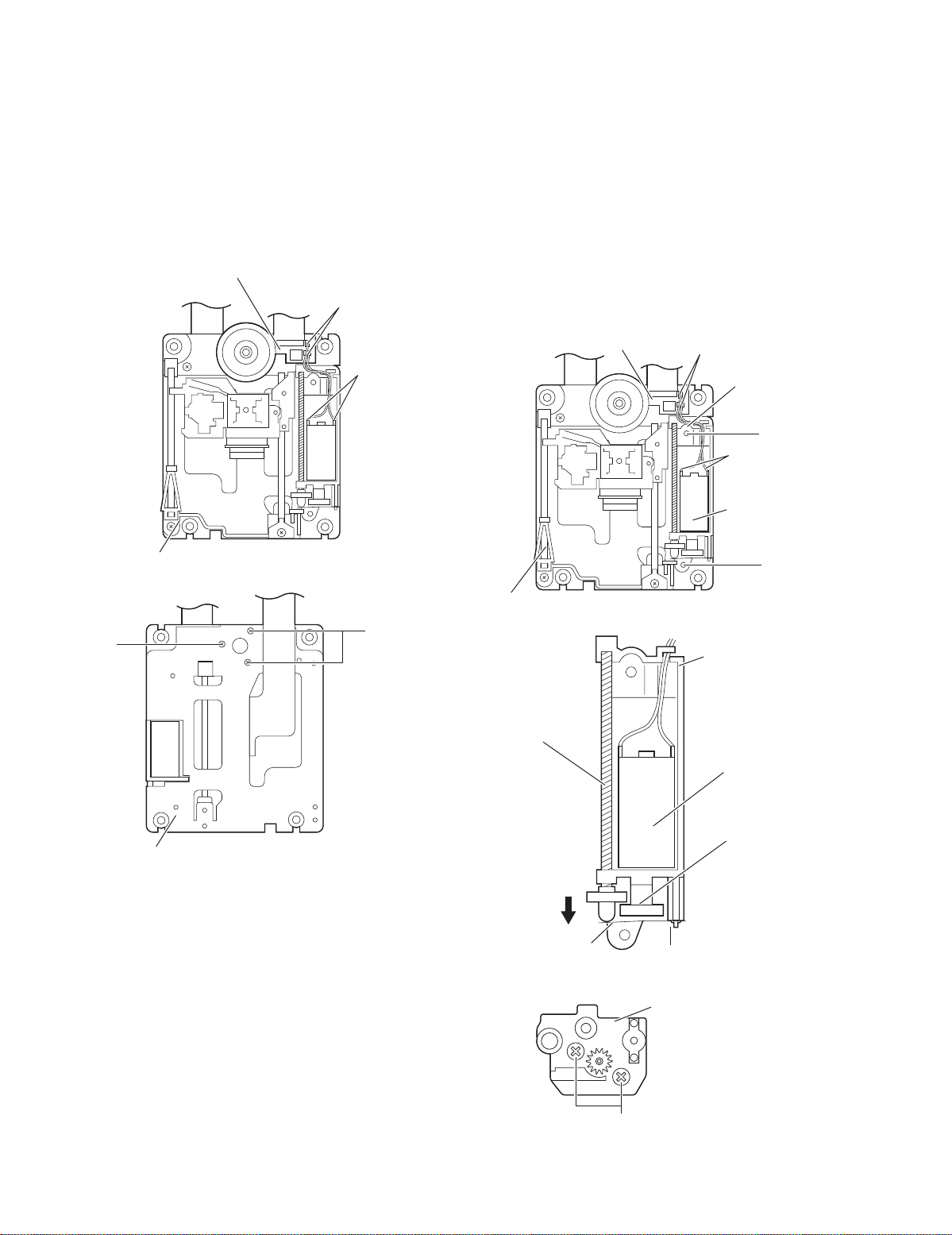

2.3.10 Removing the spindle motor board (See Figs.13 and

14.)

• Remove the DVD servo board.

• Remove the clamper base.

• Remove the DVD traverse mechanism assembly.

(1) From the top side of the DVD traverse mechanism assem-

bly, remove the feed motor wire that is soldered to the spi ndle motor board. (See Fig.13.)

(2) From the bottom side of the DVD traverse mechanism as-

sembly, remove the three screws G attaching the spindle

motor board. (See Fig.14.)

Spindle motor board

Remove the solders.

Feed moto

wire

2.3.11 Removing the feed motor (See Figs.15 to 17.)

• Remove the DVD servo board.

• Remove the clamper base.

• Remove the DVD traverse mechanism assembly.

(1) From the top side of the DVD traverse mechanism assem-

bly, remove the feed motor wire that is soldered to the spi ndle motor board. (See Fig.15.)

(2) Remove the screws H attaching the feed holder assembly

and then take out the feed holder assembly. (See Fig.15.)

(3) Remove the screw J attaching the thrust spring. (See

Fig.16.)

(4) Remove the feed gear and lead screw in the direction of the

arrow. (See Fig.16.)

(5) Remove the two screws K attaching the feed motor. (See

Fig.17.)

Spindle motor board

Remove the solders.

Feed holder assembly

H

Feed motor

wire

Feed motor

DVD traverse mechanism assembly

Fig.13

G

DVD traverse mechanism assembly

Fig.14

H

DVD traverse mechanism assembly

Fig.15

G

Feed holder assembly

Lead screw

Feed motor

Feed gear

Thrust spring

J

Fig.16

Feed holder assembly

1-14 (No.22009)

K

Fig.17

Page 15

SECTION 3

Adjustment

3.1 Test mode

(1) The AC cord is connected after pushing the STOP key and the EJECT key of a main body.

(2) Change to test mode, FL indicate "TEST ??". (?? is version)

At this time, TV monitor indicate the firm number " ".

(3) Press PAUSE key of the main body, EEPROM initialize is start.

FL indicate "RDS", EEPROM initialize is complete.

(4) Release the test mode by power to off.

3.2 Up grade

3.2.1 How to UPGRADE

(1) Power to on then mode to DVD.

(2) Set the recorded disc.

(Down loaded the up grade program "TH-A75 -Firmware Update Procedure" from Audio Products DIV.

Technological Material of JS-Net .)

(3) FL indicate "UPGRADE", press cursol key of the remote controller.

(4) TV monitor indication the UPGRADE condition.

(5) Upgrade is complete, disc is automatically eject then finish the upgrade.

TH-A75

3.2.2 After UPGRADE

After upgrade, it is should done the EEPROM initialize and confirm the firm number.

(1) Tray close then release the AC cord.

(2) The AC cord is connected after pushing the STOP key and the EJECT key of a main body.

(3) Change to test mode, FL indicate "TEST ??". (?? is version)

In this time, confrim the TV monitor indicate the firm number "114".

(4) EEPROM initialize start by press the PAUSE key of main body.

FL indicate "RDS", EEPROM initialize is complete.

(5) Release the test mode by power to off.

(No.22009)1-15

Page 16

TH-A75

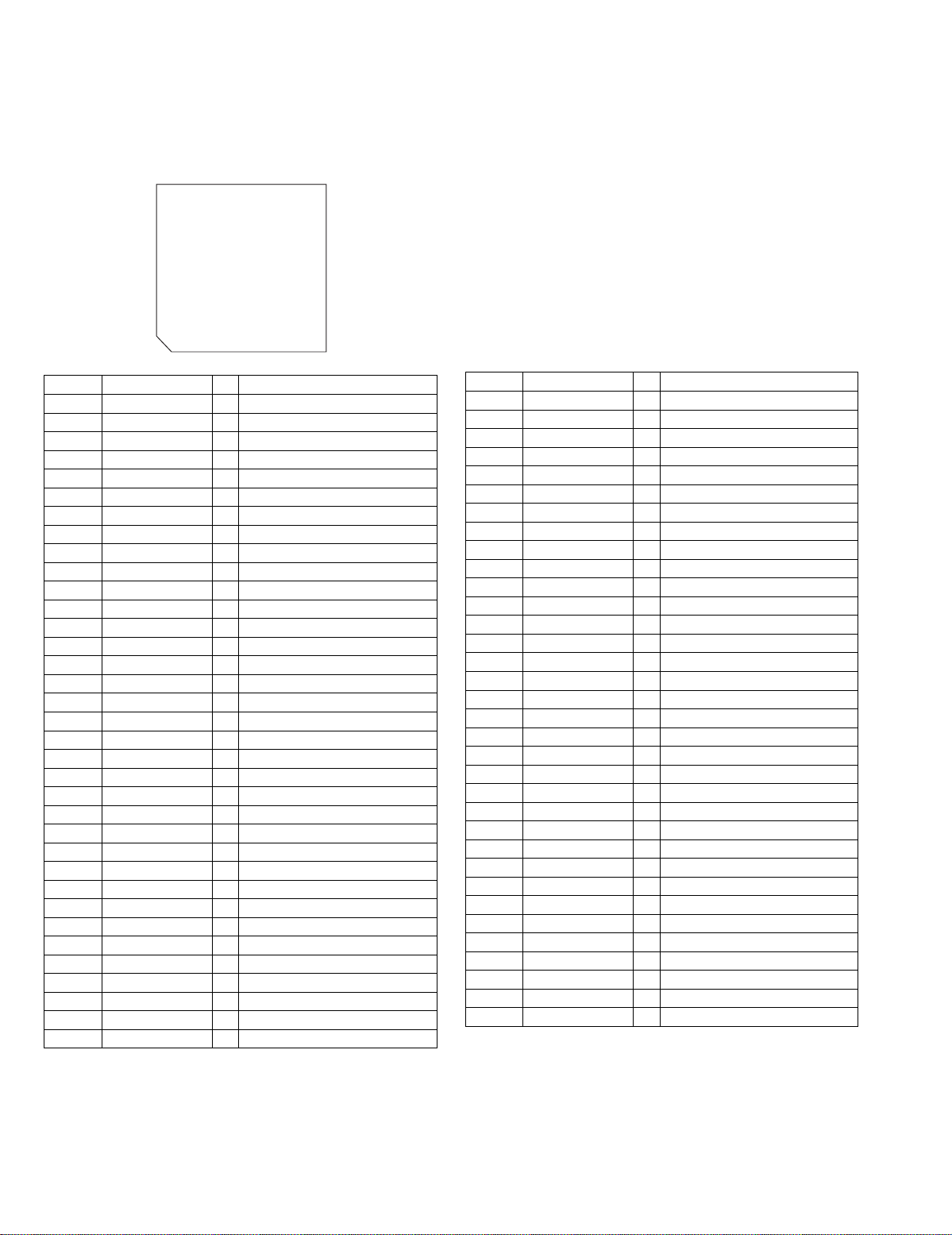

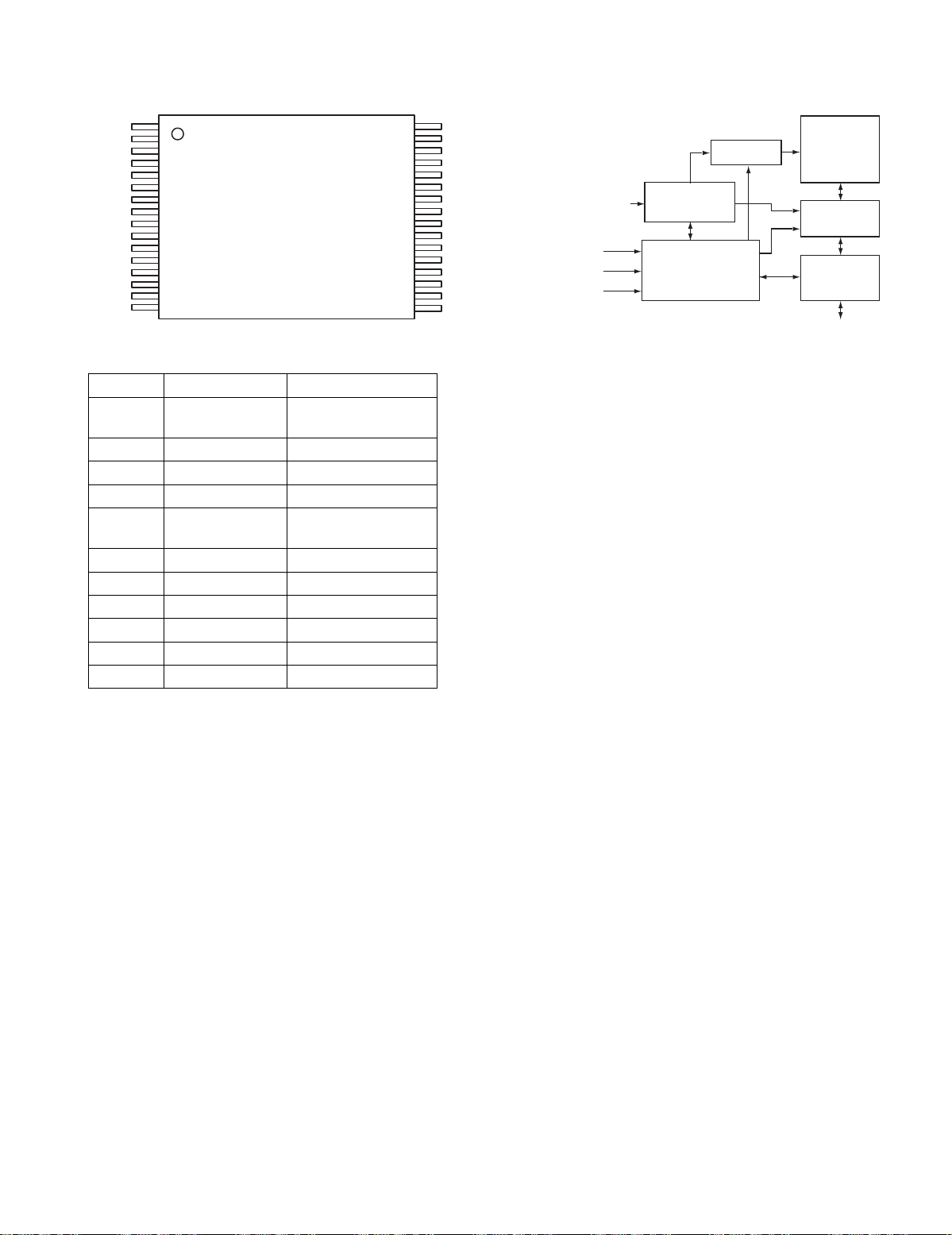

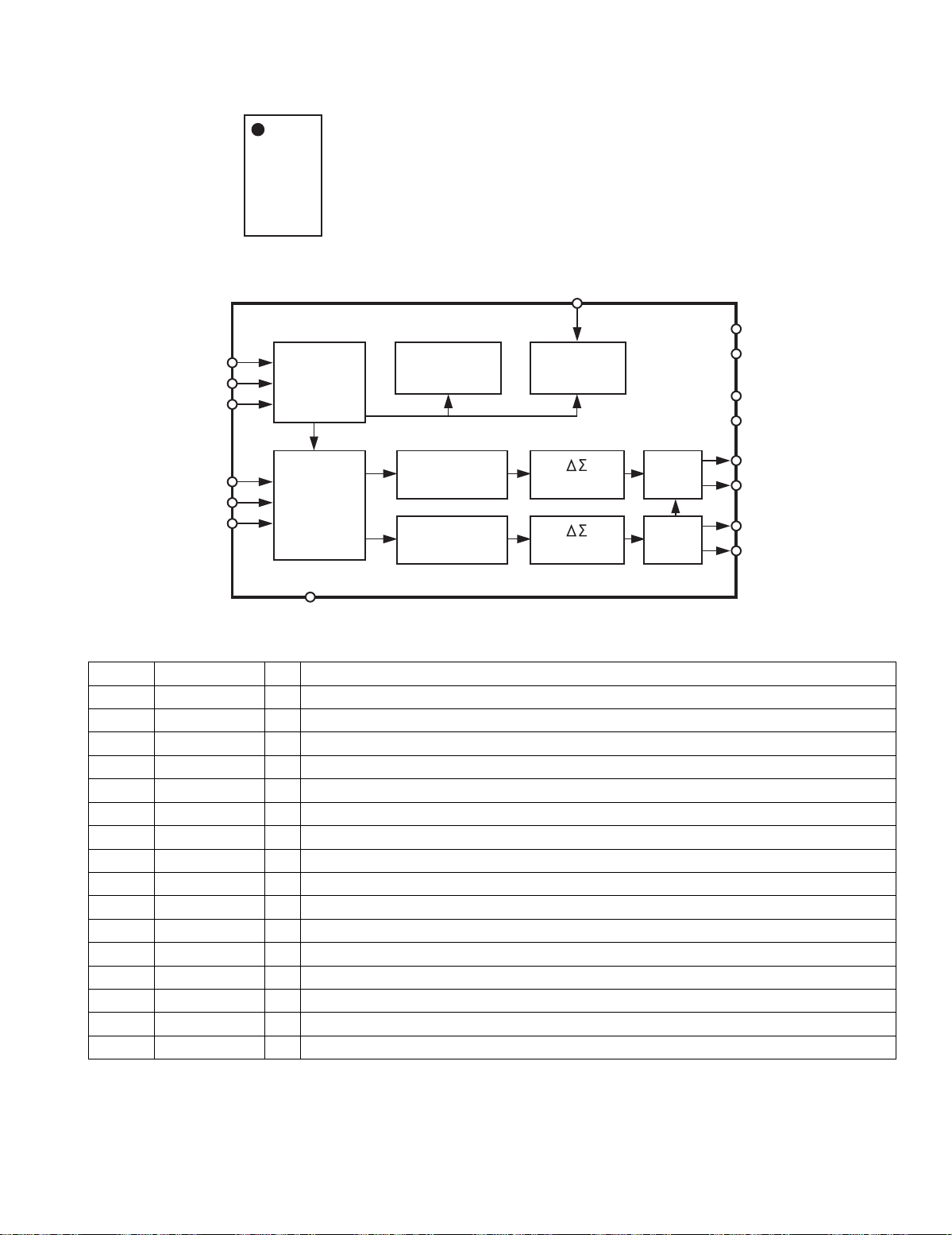

4.1 UPD784215AGC194 (IC531) : CPU

• Pin layout

75 ~ 51

SECTION 4

Description of major ICs

76

~

100

1 ~ 25

• Pin function

Pin No. Symbol I/O Function

1~8 - - Not use

9VDD-+3.0V

10 X2 I Main system clock input

11 X1 I Main system clock input

12 VSS - GND

13 XT2 - OPEN

14 XT1 I Connect to VSS

15 RESET I Reset for Flash write

16 - - Not use

17 INT0 I Error input0 (detect UNLOCK)

18 INT1 I Error input1 (detect Non Audio)

19 DZF I GND

20~22 - - Not use

23 AVDD - The same potential as VDD

24 AV REF0 - The same potential as VSS

25 - - Not use

26 CS1 I Chip select input port

27 CS2 I Chip select input port

28 CS3 I Chip select input port

29 CS4 I Chip select input port

30~32 - - Not use

33 AVSS - The same potential as VSS

34, 35 - - Not use

36 AV REF1 - The same potential as VDD

37 RX O For flash write

38 TX O For flash write

39 - - Not use

40 DSP_COM I Command (serial 1)

41 DSP_STS O Status (Serial 1)

42 DSP_CLK I Clock (Serial 1)

43 DSP_RDY I Ready

44 - - Not use

45 MIDIO_IN I Data in (Serial 0)

46 MIDIO_OUT O Data out (Serial 0)

47 MICK O Clock (Serial 0)

50

~

26

Pin No. Symbol I/O Function

48 HREQ I HREQ

49 SS O Sla ve select

50,51 - - Not use

52 DSP_RST O DSP RESET

53 - - Not use

54 DA_CS O Chip select output

55 - - Not use

56 PD/DA O Power down output (RESET)

57 PD O Power down output (RESET)

58~63 - - Not use

64 CODEC_D-OUT O Data out

65 CODEC_D-IN I Data in

66 CODEC_CLK O Clock

67 CODEC_CS O Chip select output

68 DEBUG1 O Debug out port

69 DEBUG2 O Debug out port

70 DEBUG3 O Debug out port

71 GEBUG4 O Debug out port

72 GND - GND

73~75 - - Not use

76 EQ O EQ

77 CTR_TONE O Center tone

78 3D O 3D-Phonic

79, 80 - - Not use

81 VDD - +3.0V

82, 83 - - Not use

84 ANA/T.TUNE O ANALOG./T.TONE

85 LFE.MIX O LFE MIX CONTROL

86 LEF_OUT O LFE OUT CONTROL

87 - - Not use

88 S.MUTE O S.MUTE

89~93 - - Not use

94 TEST O Usual "VSS"

95~100 - - Not use

1-16 (No.22009)

Page 17

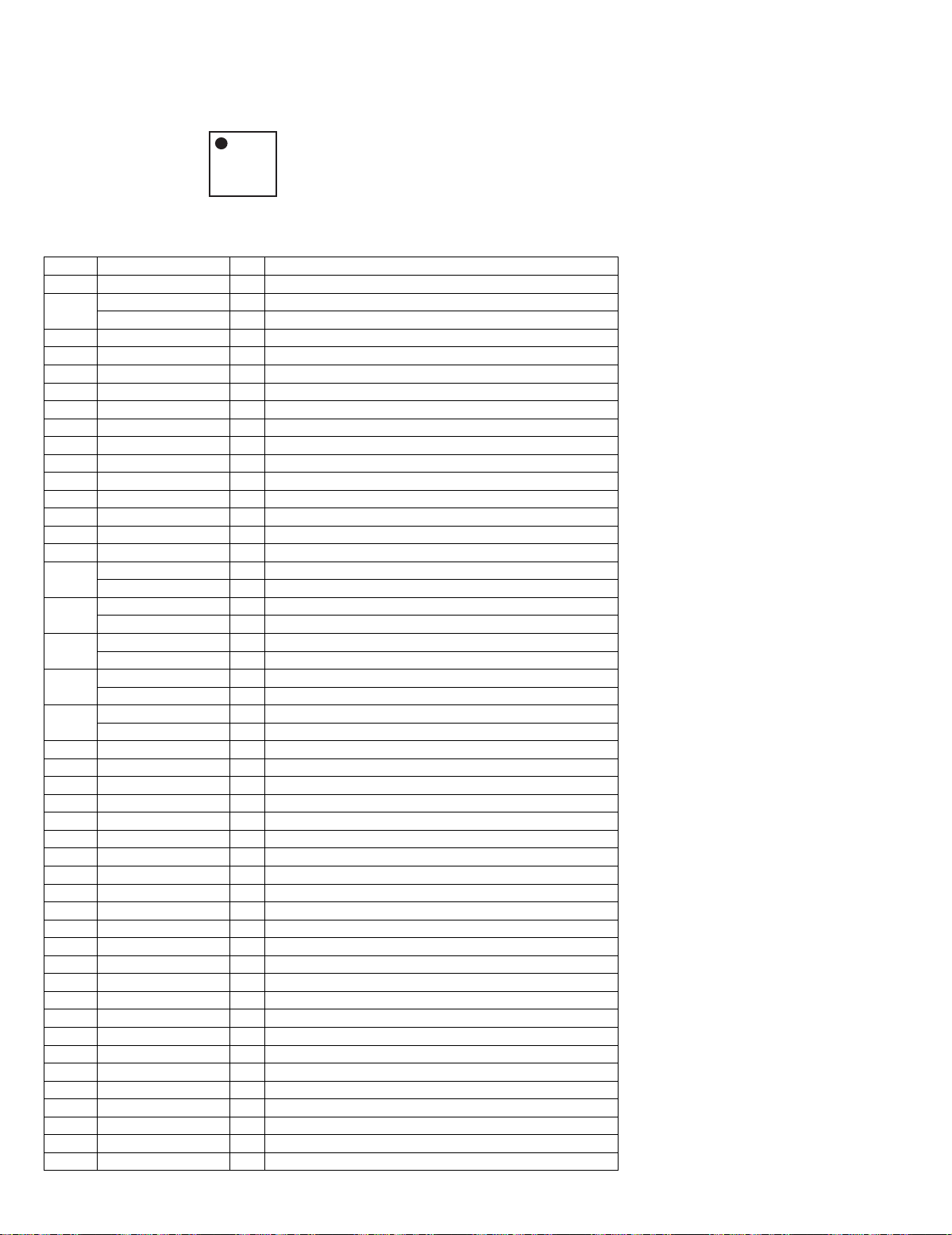

4.2 39VF0207CWHQ01 (IC524) : 2 Mbit multi-purpose flash memory

• Pin layout • Block diagram

A11

A9

A8

A13

A14

A17

WE#

V

DD

NC

A16

A15

A12

A7

A6

A5

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Top view

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

OE#

A10

CE#

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

A3

Memory Address

CE#

OE#

WE#

• Pin function

Pin No. Symbol Function

1 - 6 A11,A9,A8

Address inputs

A13,A14,A17

7 WE# Write enable

8 VDD Power supply

9 NC Not connect

10 - 20 A16,A15,A12

Address inputs

A7 - A0

21 - 23 DQ0 - DQ2 Data inputs/outputs

24 VSS Ground

25 - 29 DQ3 - DQ7 Data inputs/outputs

30 CE# Chip enable

31 A10 Address input

32 OE# Output enable

X-Decoder

Address Buffers

and

Latches

Control Logic

SuperFlash

Memory

Y-Decoder

I/O Buffers

and

Data Latches

DQ7 - DQ0

TH-A75

(No.22009)1-17

Page 18

TH-A75

4.3 AK4586VQ (IC511) : A/D, D/A Converter

• Pin layout

44 - 34

11 - 1

12 - 22

23 - 33

• Pin function

Pin No. Symbol I/O Function

1 XTO O X'tal output pin

2 XTI I X'tal input pin

EXTCLK I External master clock input pin

3 TVDD - Output buffer power supply pin, 2.7V~5.5V

4 VDSS - Digital Ground pin, 0V

5 DVDD - Digital pow er supp ly pin, 4.5V~5 .5V

6 TX O Transmit channel (through data) output pin

7 MCKO O Master clock outp ut pin

8 LRCK I/O Input/Output channel clock pin

9 BICK I/O Audio serial data clock pin

10 SDTO O Audio serial data output pin

11 SDTI1 I DAC1 audio serial data input pin

12 SDTI2 I DAC2 audio serial data input pin

13 SDTI3 I DAC3 audio serial data input pin

14 INT0 O Interrupt 0 pin

15 INT2 O Interrupt 1 pin

16 CDTO O Control data output pin in 4-wire serial control mode

CAD1 I Chip address 1 pin in I2C bus control mode

17 CDTI I Control data input pin in 4-wire serial control mode

SDA I/O Control data input/output pin in I2C bus control mode

18 CCLK I Control data clock pin in 4-wire serial control mode

SCL I Control data clock pin in I2C bus control mode

19 CSN I Chip select pin in 4-wire serial control mode

CAD0 I Chip address 0 pin in I2C bus control mode

20 DZF2 O Zero input detect 2 pin

OVF O Analog input ove rflow detect pin

21 AVSS - Analog ground pin, 0V

22 AVDD - Analog power supply pin, 4.5V~5.5V

23 VREFH I Positive voltage reference input pin, AVDD

24 VCOM O Common voltage output pin, AVDD/2

25 DZF1 O Zero input detect 1 pin

26 LOUT3 O DAC3 Lch analog output pin

27 ROUT3 O DAC3 Rch analog output pin

28 LOUT2 O DAC2 Lch analog output

29 ROUT2 O DAC2 Rch analog output pin

30 LOUT1 O DAC1 Lch analog output pin

31 ROUT1 O DAC1 Rch analog output pin

32 LIN I Lch analog input pin

33 RIN I Rch analog input pin

34 PCDD - PLL power supply pin, 4.5V~5.5V

35 R - External resistor pin

36 PVSS - Pll ground pin, 0V

37 RX4 I Receiver channel 4 pin (internal biased pin)

38 SLAVE I Slave mode pin

39 RX3 I Receiver channel 3 pin (internal biased pin)

40 TST I Test pin

41 RX2 I Receiver channel 2 pin (internal biased pin)

42 I2C I Control mode select pin

43 RX1 I Receiver channel 1 pin (internal biased pin)

44 PDN I Power-Down & Reset pin

1-18 (No.22009)

Page 19

• Block diagram

CSN

CCLK

CDTI

TH-A75

CDTO

LIN

RIN

LOUT1

ROUT1

LOUT2

ROUT2

LOUT3

ROUT3

ADC HPF

ADC HPF

DAC DATTLPF

DAC DATTLPF

DAC DATTLPF

DAC DATTLPF

DAC DATTLPF

DAC DATTLPF

Audio

I/F

MCLK

SDOUT

BICK

LRCK

SDIN1

SDIN2

SDIN3

uP I/F

Clock

Recovery

DAIF

Decoder

DEM

X'tal

Oscillator

Clock

Generator

Input

Selector

XTI

XTO

MCKO

TX

RX1

RX2

RX3

RX4

SDOUT

BICK

LRCK

SDIN1

SDIN2

SDIN3

(No.22009)1-19

Page 20

TH-A75

4.4 MM74HCT32MTC-X (IC521) : Quad 2 input OR gate

• Pin layout & Block diagram

• Truth table

11A

21B

31Y

42A

52B

62Y

7

14

13

12

11

10

9

8GND

V

4B

4A

4Y

3B

3A

3Y

CC

(TOP VIEW)

4.5 74LCX373MTC-X (IC512,IC513) : Octal D-type latch

• Pin layout • Truth table

20

19

18

17

16

15

14D2

13

12

11

VCC

Q7

D7

D6

Q6

Q5

D5

D4

Q4

LE

1OE

2Q0

3D0

4D1

5Q1

6Q2

7

8D3

9Q3

10GND

(TOP VIEW)

INPUTS OUTPUT

ABY

LLL

LHH

HLH

HHH

INPUTS OUTPUT

OE

LE D Y

HXXZ

LLXQn

LHLL

LHHH

X: Don't care

Z: High impedance

Qn: Q outputs are latched at the time when t he LE input is tak-

en to a low logic level.

•Block diagram

D0

3

D

Q

L

2

Q0

OE

11

LE

1

D1

4

D2

7

D

Q

L

5

Q1

D3

8

D

Q

L

6

Q2

D4

13

D

Q

L

9

Q3

D5

14

D

Q

L

12

Q4

D6

17

D

Q

L

15

Q5

D7

18

D

D

Q

L

16

Q

L

19

Q6

Q7

1-20 (No.22009)

Page 21

4.6 AK4382AVT-X (IC512) : D/A Converter

• Pin layout

1

2

3

4

5

6

7

8

• Block diagram

CSN

CCLK

16

15

14

13

12

11

10

9

uP

Interface

CDTI

De-empahsis

Control

MCLK

Clock

Divider

TH-A75

VDD

VSS

DZFL

DZFR

8X

LRCK

BICK

SDTI

Audio

Data

Interface

Interpolator

8X

Interpolator

Modulator

Modulator

PDN

• Pin function

Pin No. Symbol I/O Function

1 MCLK I Master Clock Input Pin

2 BICK I Audio Serial Data Clock Pin

3 SDTI I Audio Serial Data Input Pin

4 LRCK I L/R Clock Pin

5 PDN I Power-Down Mode Pin

6 CSN I Chip Select Pin

7 CCLK I Control Data Input Pin

8 CDTI I Control Data Input Pin

9 AOUTR- O Rch Negative Analog Output Pin

10 AOUTR+ O Rch Positive Analog Output Pin

11 AOUTL- O Lch Negative Analog Output Pin

12 AOUTL+ O Lch Positive Analog Output Pin

13 VSS - Ground Pin

14 VDD - Power Supply Pin

15 DZFR O Rch Data Zero Input Detect Pin

16 DZFL O Lch Data Zero Input Detect Pin

SCF

SCF

AOUTL+

AOUTL-

AOUTR+

AOUTR-

(No.22009)1-21

Page 22

TH-A75

4.7 AK93C65AF-X (IC510) : EEPROM

• Pin layout

PE

VCC

CS

SK

•Block diagram

DI

CS

1

2

3

4

8 PIN SOP

INSTRUCTION

REGISTER

NC

8

GND

7

DO

6

5

INSTRUCTION

DECODE,

CONTROL

AND

CLOCK

GENERATION

DI

DO

DATA

REGISTER

16

R/W AMPS

AND

AUTO ERASE

16

EEPROM

4096bit

ADD.

BUFFERS

DECODER

256 x 16

SK

PE

• Pin function

Pin no. Symbol Function

1 PE Program enable (With built-in pull-up resistor)

2 VCC Power supply

3 CS Chip selection

4 SK Cereal clock input

5 DI Cereal data input

6 DO Cereal data output

7 GND Ground

8 NC No connection

NOTE :

The pull-up resistor of the PE pin is about 2.5Mohm (VCC=5V)

VREF

VPP SW

VPP

GENERATOR

1-22 (No.22009)

Page 23

4.8 AN8703FH-V (IC101) : Frontend processor for DVD

• Pin layout

64 49

1

48

TH-A75

16

33

17 32

• Pin function

Pin No.

Symbol I/O Description

1 LPC1 I Laser input terminal (DVD)

2 LPC01 O Laser drive signal output terminal (DVD)

3 LPC2 I Laser input terminal (CD)

4 LPC02 O Laser drive signal output terminal (CD)

5

VFOSHORT

6 TBAL I Tracking balance control terminal

7 FBAL I Focus balance control terminal

8 POFLT O Track detection threshold level terminal

9 DTRD I Data slice part data read signal input ter-

10 IDGT I Data slice part address part gate signal

11 STANDBY I Standby mo de control te rm in al

12 SEN I SEN(Serial data input terminal)

13 SCK I SCK(Ser ial data input terminal)

14 STDI I STDI(Serial data input terminal)

15 RSCL I Standard electric current terminal

16 JLINE I Electric curr ent setting terminal of JLine

17 TEN I Reversing input terminal of tracking error

18 TEOUT O Tracking error signal output terminal

19 AGCBAL I Offset adjusting terminal 1

20 AS OUT O Full adder signal output terminal

21 FEN I Focus error output amplifier reversing in-

22 FEOUT O Focus error signal output terminal

23 AGCOFST I Offset adjusting terminal 2

24 MON - Non connect

25 AGCLVL O Output amplitude adjustment for DRC

26 GND2 - Connect to GND

27 VREF2 O VREF2 voltage output termina l

28 VCC2 - Power supply terminal 5V

29 VHALF O VHALF voltage output termina l

30 DFLTON O Reversing output terminal of filter AMP.

31 DFLTOP O Filter AMP. output terminal

32 DCFLT I Capacity connection terminal for filter

I VFOSHORT control terminal

minal(For RAM)

input terminal( For RAM)

output AMP.

put terminal

output

Pin No.

Symbol I/O Description

33 GND3 - Connect to GND

34 RFDIFO - Non connect

35 RFOUT - Connect to TP103

36 VCC3 - Power supply terminal 3.3V

37 RFC O Filter for RF delay correction AMP.

38 DCRF O All addition amplifier capacitor terminal

39 OFTR O OFTR output terminal

40 BDO O BDO output terminal

41 RFENV O RF envelope output terminal

42 BOTTOM O Bottom envelope detection filter terminal

43 PEAK O Peak envelope detection filter terminal

44 AGCG O AGC amplifier gain control terminal

45 AGCO O AGC amplifier level control terminal

46 TESTSG I TEST signal input terminal

47 RFINP I RF signal positive input terminal

48 RFINN I RF signal negative input terminal

49 VIN5 I Internal four-partition (CD) RF input 1

50 VIN6 I Internal four-partition (CD) RF input 2

51 VIN7 - Internal four-partition (CD) RF input 3

52 VIN8 - Internal four-partition (CD) RF input 4

53 V I N9 I External two-partition (DVD) RF input 2

54 VIN10 I External two-partition (DVD) RF input 1

55 VCC1 - Power supply terminal 5V

56 VREF1 O VREF1 voltage output terminal

57 VIN1 I Internal four-partition (DVD) RF input 1

58 VIN2 I Internal four-partition (DVD) RF input 2

59 VIN3 I Internal four-partition (DVD) RF input 3

60 VIN4 I Internal four-partition (DVD) RF input 4

61 GND1 - Connect to GND

62 VIN11 I 3 beam sub input terminal 2 (CD)

63 VIN12 I 3 beam sub input terminal 1 (CD)

64 HDTYPE O HD Type selection

(No.22009)1-23

Page 24

TH-A75

4.9 BA6664FM-X (IC251) : Motor driver

• Pin layout

1

NC

2

A3

3

NC

4

A2

5

NC

6

NC

7

A1

29 30

8

GND

9

H1+

10

H1-

11

H2+

12

H2-

13

H3+

14

H3-

•Block diagram

RNF

28

VM

27

GSW

26

Vcc

25

FG

24

PS

23

EC

22

ECR

21

FR

20

FG2

19

SB

18

CNF

17

BR

16

VH-

15

GND

H1+

H1-

H2+

H2-

H3+

H3-

R

NF

28

VM

27

26

25

24

23

22

21

20

19

18

17

16

15

GSW

VCC

FG

PS

EC

ECR

FR

FG2

SB

CNF

BR

VH

TL

DRIVER

GAIN

CONTROL

CURRENT

SENSE AMP

TSD

GAIN

SWITCH

VCC

+ -

A3

2

A2

4

A1

7

8

9

10

11

12

13

HALL AMP

+

-

+

-

+

+

-

+

+

-

R

D Q

CK Q

PS

TOROUE

SENSE AMP

+

-

VCC

VCC

SHORT BRAKE

BRAKE MODE

14

Hall Bias

1-24 (No.22009)

Page 25

• Pin function

Pin No. Symbol I/O Description

1 NC - Non connect

2 A3 O Output 3 for spindle motor

3 NC - Non connect

4 A2 O Output 2 for spindle motor

5 NC - Non connect

6 NC - Non connect

7 A1 O Output 1 for spindle motor

8 GND - Connect to ground

9 H1+ I Positive input for hall input AMP 1

10 H1- I Negative input for hall input AMP 1

11 H2+ I Positive input for hall input AMP 2

12 H2- I Negative input for hall input AMP 2

13 H3+ I Positive input for hall input AMP 3

14 H3- I Negative input for hall input AMP 3

15 VH I Hall bias terminal

16 BR - Non connect

17 CNF - Capacitor connection pin for phase compensation

18 SB I Short brake terminal

19 FG2 - Non connect

20 FR - Non connect

21 ECR I Torque control standard voltage input terminal

22 EC I Torque control voltage input terminal

23 PS O Start/stop switch (power save terminal)

24 FG O FG signal output terminal

25 VCC - Power supply for signal division

26 GSW O Gain switch

27 VM - Power supply for driver division

28 RNF O Resistance connection pin for output current sense

29 - Connect to ground

30 - Connect to ground

TH-A75

(No.22009)1-25

Page 26

TH-A75

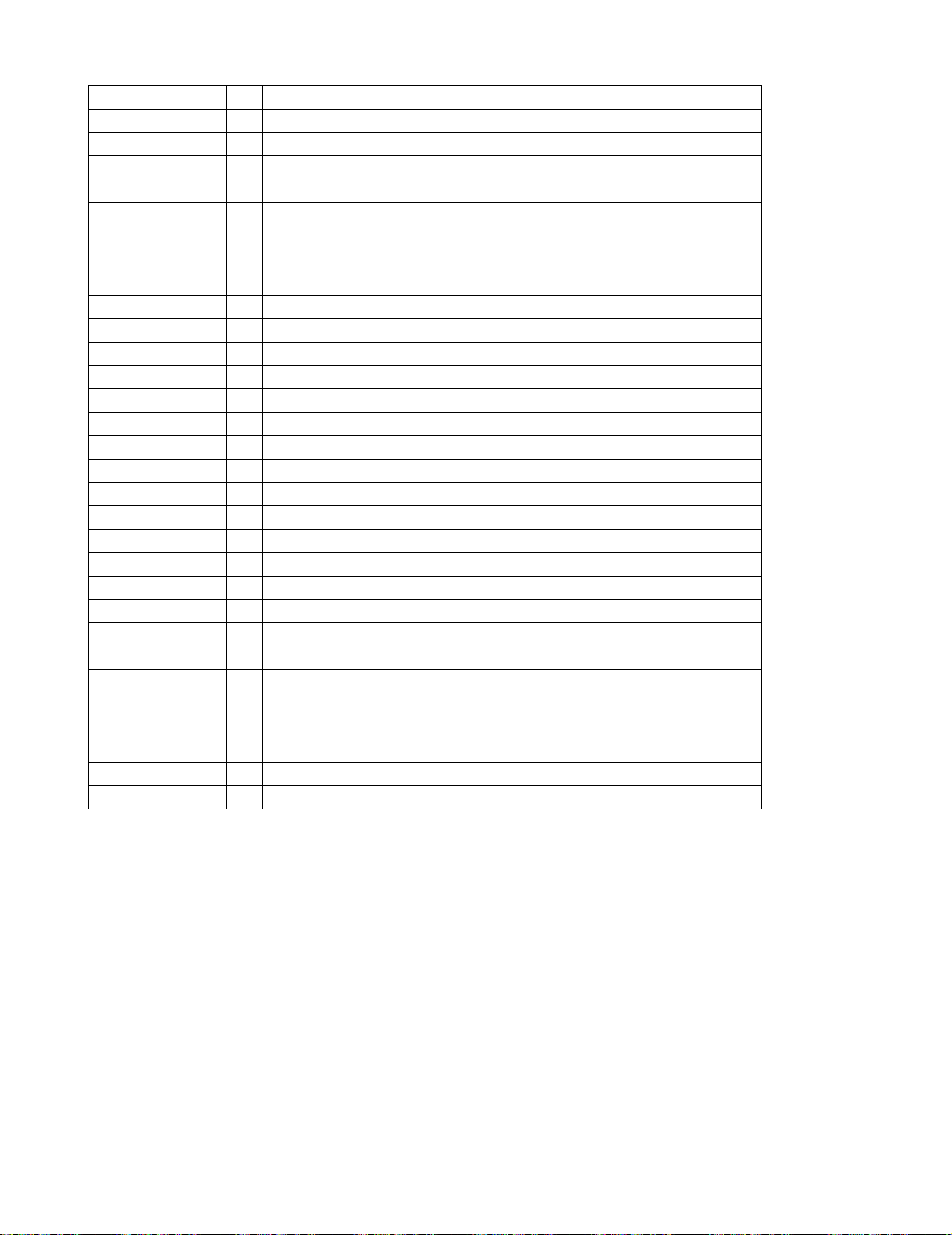

4.10 BA15218F-XE (IC251/IC540/IC544/IC546/IC548/IC557/IC560/IC562/IC564/IC566/IC711/IC712) : Dual operational amplifier

• Pin layout

OUT1 1

-IN1 2

+IN1 3

VEE 4

•Block diagram

Vcc

-IN

+IN

1

2

R1

Q5

Q1

Q2

D1

Q3 Q4

8 Vcc

7 OUT2

6 -IN2

5 +IN2

C2

R5

Q6

Q9

Q8

Q10

Q7

R7

Q11

R6

Q12

R8

Q18Q13

OTHER

CH

Q19

Q17Q16

VEE

C1

R3R2

R4

Q14 Q15Q114

R9

OUTPUT

1-26 (No.22009)

Page 27

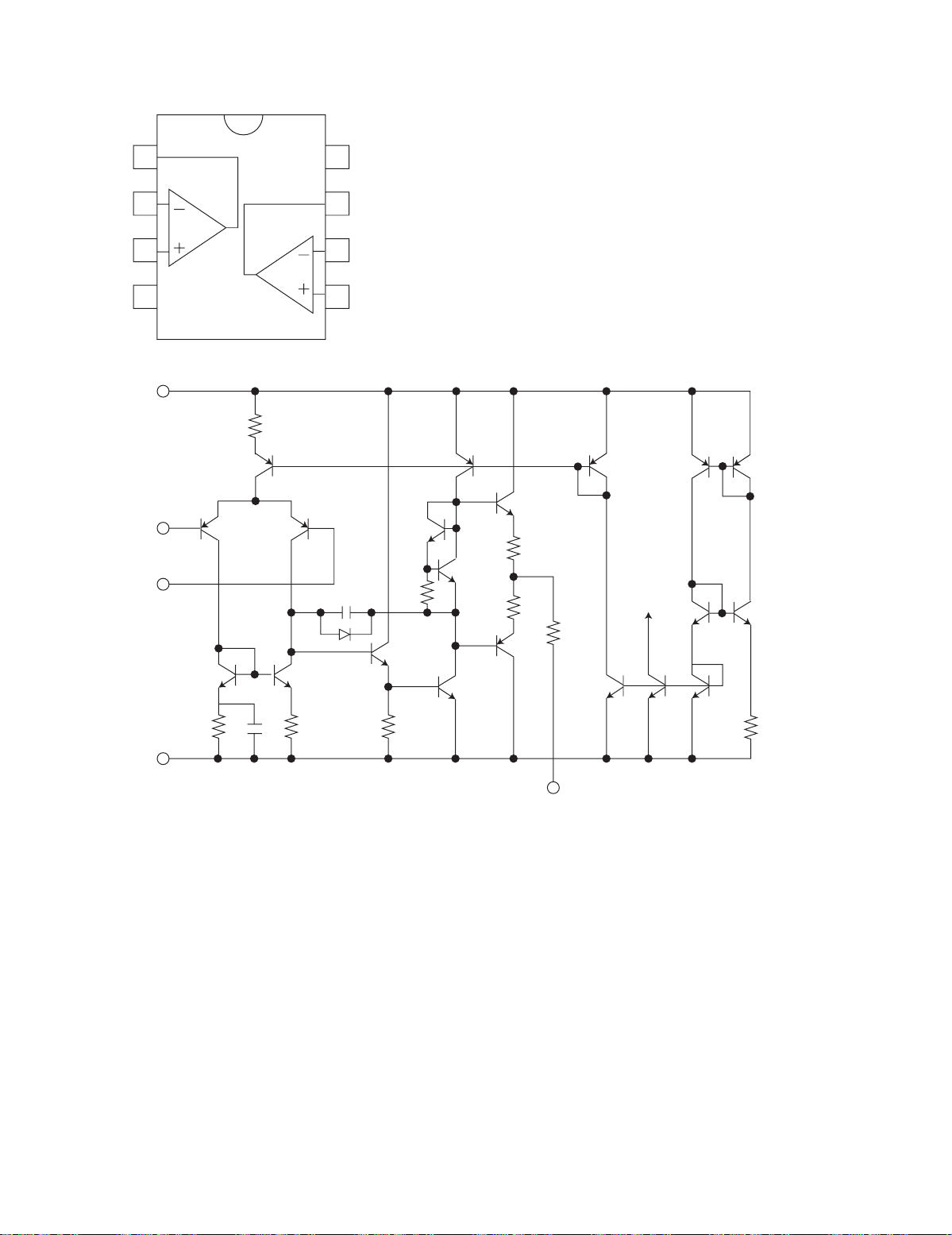

4.11 BA5983FM-X (IC201) : 4-channel driver

• Block diagram

27

26

25

28

Vcc

10k

24

20k

23 22 30

10k

20k

21

STAND BY

CH4

20

Vcc

19

10k

10k

18

Level Shift

17 16

10k

10k

10k

10k

TH-A75

15

10k

10k

Level Shift

10k

10k

1

2

3

5

4

10k

6

• Pin function

Pin No. Symbol I/O Description

1 BIAS IN I Input for Bias-amplifier

2 OPIN1(+) I Non inverting input for CH1 OP-AMP

3 OPIN1(-) I Inverting input for CH1 OP-AMP

4 OPOUT1 O Output for CH1 OP-AMP

5 OPIN2(+) I Non inverting input for CH2 OP-AMP

6 OPIN2(-) I Inverting input for CH2 OP-AMP

7 OPOUT2 O Output for CH2 OP-AMP

8 GND - Substrate ground

9 STBY1 I Input for CH1/2/3 stand by control

10 PowVcc1 - Vcc for CH1/2 power block

11 VO2(-) O Inverted output of CH2

12 VO2(+) O Non inverted output of CH2

13 VO1(-) O Inverted output of CH1

14 VO1(+) O Non inverted output of CH1

15 VO4(+) O Non inverted output of CH4

Level Shift

10k

10k

Level Shift

10k

10k

10k

10k

10k

10k

10k

STAND BY

CH1/2/3

729 891011121314

Vcc

Pin No. Symbol I/O Description

16 VO4(-) O Inverted output of CH4

17 VO3(+) O Non inverted output of CH3

18 VO3(-) O Inverted output of CH3

19 PowVcc2 - Vcc for CH3/4 power block

20 STBY2 I Input for Ch4 stand by control

21 GND - Substrate ground

22 OPOUT3 O Output for CH3 OP-AMP

23 OPIN3(-) I Inverting input for CH3 OP-AMP

24 OPIN3(+) I Non inverting input for CH3 OP-AMP

25 OPOUT4 O Output for CH4 OP-AMP

26 OPIN4(-) I Inverting input for CH4 OP-AMP

27 OPIN4(+) I Non inverting input for CH4 OP-AMP

28 PreVcc - Vcc for pre block

29 - Connect to ground

30 - Connect to ground

(No.22009)1-27

Page 28

TH-A75

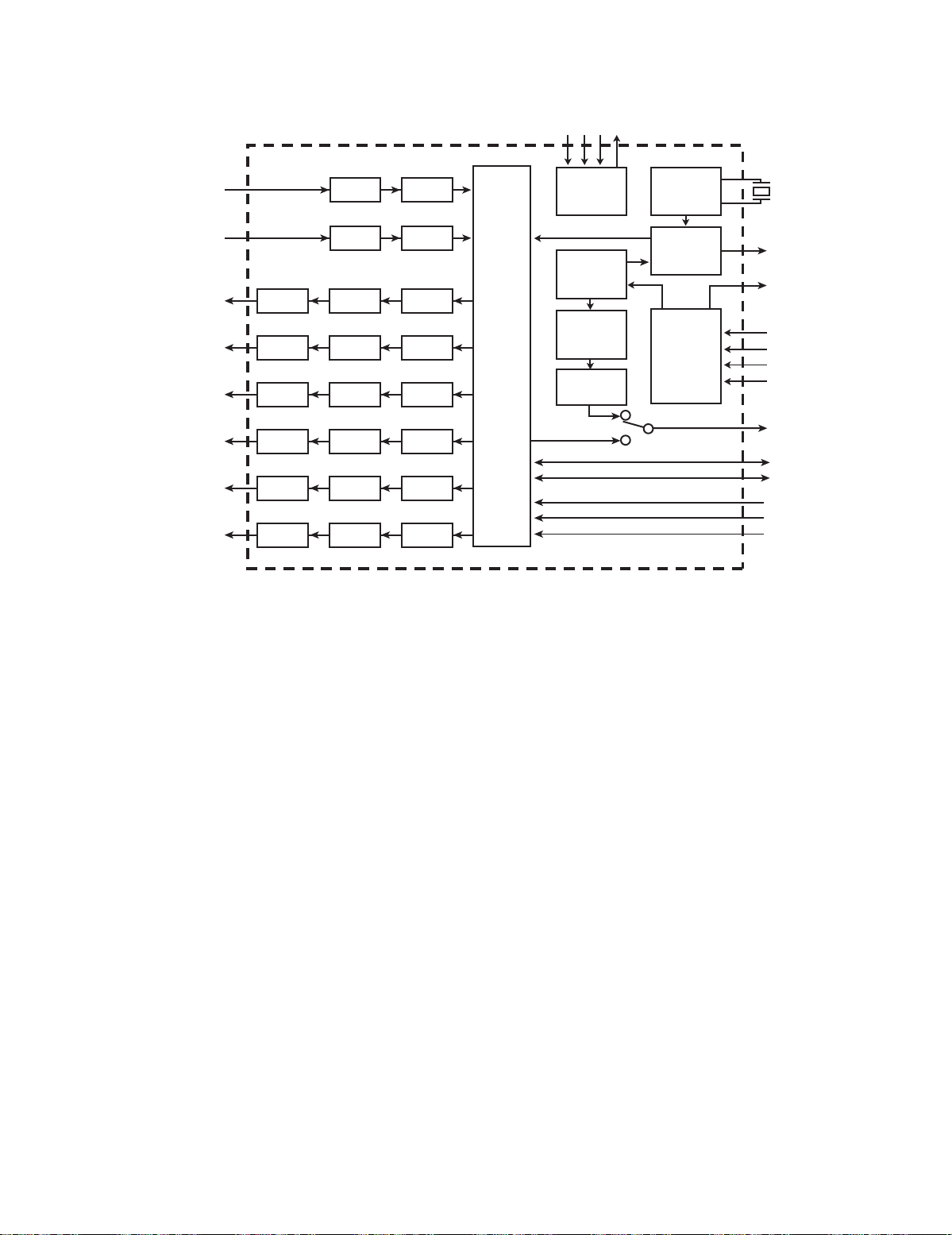

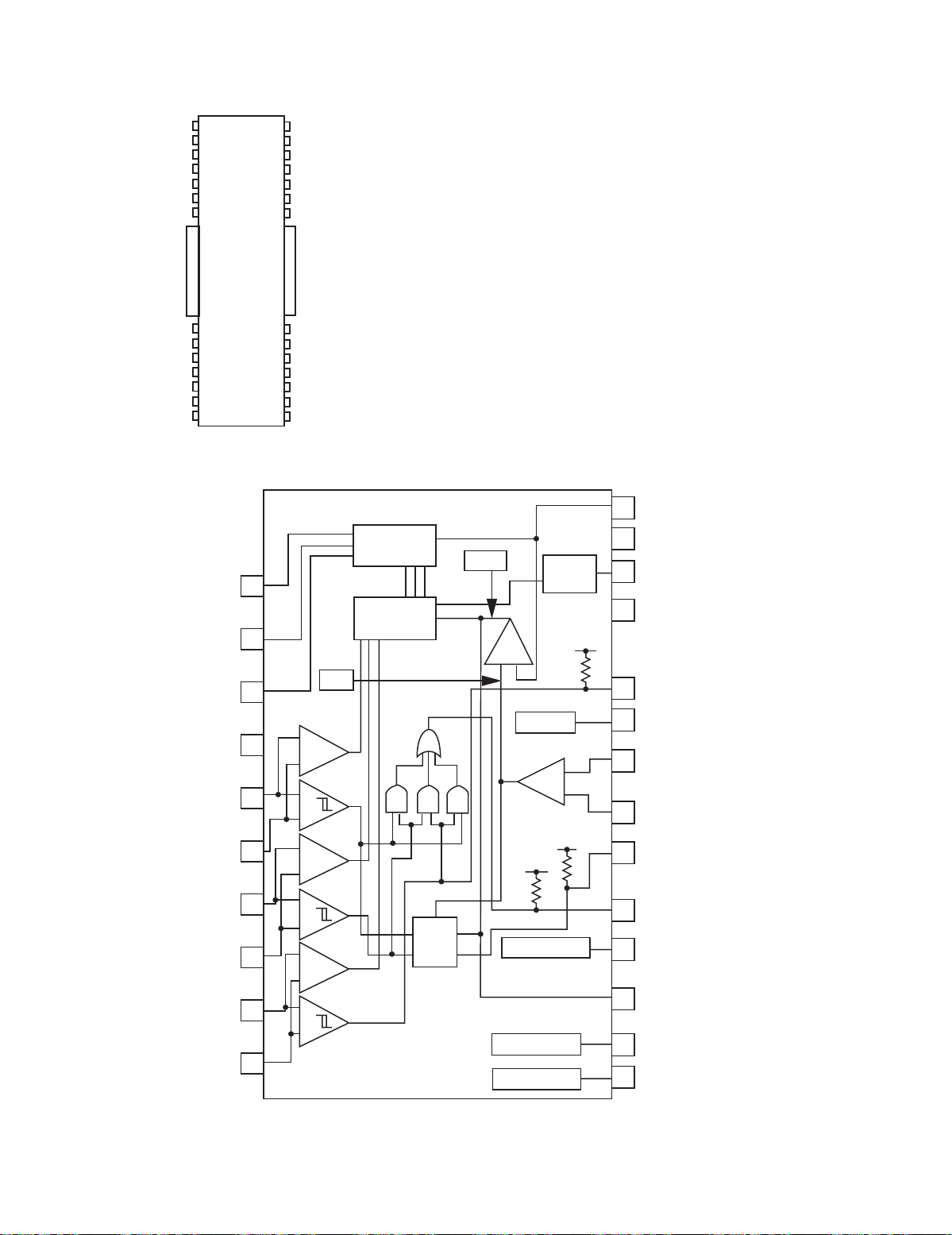

4.12 DSPC56367PV150 (IC521) : DSP

• Pin layout

144 109~

1~36

37 72~

•Block diagram

1

TRIPLE

TMER

(SPDIF Tx)

INTER-FA

INTERNAL

2

DAX

CE

GENERATION

SIX CHANNELS

DATA

BUS

INTER-

ADDRESS

UNIT

DMA UNIT

16

HOST

FACE

108 ~ 73

8

ESAI

INTER-

FACE

ESAI_1

PERIPHERAL

EXPANSION AREA

PIO_EB

4

6

24-BIT

DSP56300

Core

SHI

INTER-

FACE

5

MEMORY EXPANSION AREA

PROGRAM

RAM

/INSTR.

CACHE

3K x 24

PROGRAM

ROM

40K x 24

Bootstrap

DDB

YDB

XDB

PDB

GDB

PM_EB

YAB

XAB

PAB

DAB

X MEMORY

RAM

13K x 24

ROM

32K x 24

XM_EB

Y MEMORY

RAM

7K x 24

ROM

8K x 24

YM_EB

EXTERNAL

ADDRESS

SWITCH

DRAM &

SRAM BUS

INTERFACE

I-CACHE

EXTERNAL

DATA BUS

SWITCH

BUS

&

18

ADDRESS

10

CONTROL

24

DATA

1-28 (No.22009)

PLL

CLOCL

GENERAT

EXTAL

RESET

PINT/NMT

PROGRAM

INTERRUPT

CONTOROLLER

PROGRAM

DECODE

CONTOROLLE

MODA/IRQA

MODB/IRQB

MODC/IRQC

MODD/IRQD

PROGRAM

ADDRESS

GEBERATOR

DATA ALU

24X24+56>56BIBT MAC

TWO 56BIT ACCUMULATORS

BARREL SHIFTER

24 BITS BUS

POWER

GNGMNT

JTAG

OnCE

4

TW

Page 29

• Pin function

Pin No Symbol I/O Function

1 SCK/SCL I/O SPI serial clock / I2C serial clock

2SS

3 HREQ

4 SDO0/SDO0_1 O Serial data output 0

5 SDO1/SDO1_1 O Serial data output 1

6 SDO2/SDI3/SDO2_1/SDI3_1 O Serial data output 2 / Serial data input 3

7 SDO3/SDI2/SDO3_1/SDI2_1 O Serial data output 3 / Serial data input 2

8 VCCS - SHI,ESAI,ESAI_1,DAX and Timer power

9 GNDS - SHI,ESAI,ESAI_1,DAX and Timer ground

10 SDO4/SDI1 O Serial data output 4 / Serial data input 1

11 SDO5/SDI0 O Serial data output 5 / Serial data input 0

12 FST I/O Frame sync for transmitter

13 FSR I/O Frame sync for receiver

14 SCKT I/O Transmitter serial clock

15 SCKR I/O Receiver serial clock

16 HCKT I/O High frequency clock for transmitter

17 HCKR I/O High frequency clock for receiver

18 VCCQL - Quite core (Low) power

19 GNDQ - Quite ground

20 VCCQH - Quite external (High) power

21 HDS/HWR I Host data strobe / Host write data

22 HRW/HRD I Host read write / Host read data

23 HACK/HRRQ I Host acknowledge / Receive host request

24 HOREQ/HTRQ O Host request / Transmit host request

25 VCCS - SHI,ESAI,ESAI_1,DAX and Timer power

26 GNDS - SHI,ESAI,ESAI_1,DAX and Timer ground

27 ADO O Digital audio data output

28 ACI I Audio clock input

29 TIO0 I/O Timer 0 schmitt-trigger input/output

30 HCS/HA10 I Host chip select / Host address 10

31 HA9/HA2 I Host address 9 / Host address input 2

32 HA8/HA1 I Host address 8 / Host address input 1

33 HAS/HA0 I Host address strobe / Host address input 0

34~37 HAD7~HAD4 I/O Host address/Data

38 VCCH - Host power

39 GNDH - Host ground

40~43 HAD3~HAD0 I/O Host address/Data

44 RESET

45 VCCP - PLL power

46 PCAP I PLL capacitor

47 GNDP - PLL ground

48 SDO5_1/SDI0_1 I/O Serial data output 5_1 / Serial data input 0_1

49 VCCQH - Quite external (High) power

50 FST_1 I/O Frame sync for transmitter

51 AA2 O Address attribute or Row address strobe

52 CAS

53 SCKT_1 I/O Transmitter serial clock_1

54 GNDQ - Quite ground

55 EXTAL I External clock input

56 VCCQL - Quite core (Low) power

57 VCCC - Bus control power

58 GNDC - Bus control ground

/HA2 I SPI slave select / I2C slave address 2

I/O Host request

I Reset

O Column address strobe

TH-A75

(No.22009)1-29

Page 30

TH-A75

Pin No Symbol I/O Function

59 FSR_1 I/O Frame sync for receiver

60 SCKR_1 I/O Receiver serial clock_1

61 PINIT/NMI

62 TA

63 BR

64 BB

65 VCCC - Bus control power

66 GNDC - Bus control ground

67 WR O Write enable

68 RD

69,70 AA1,AA0 O Address attribute or row address strobe

71 BG

72,73 A0,A1 O Data bus

74 VCCA - Address bus power

75 GNDA - Address bus ground

76~79 A2~A5 O Data bus

80 VCCA - Address bus power

81 GNDA - Address bus ground

82~85 A6~A9 O Data bus

86 VCCA - Address bus power

87 GNDA - Address bus ground

88,89 A10,A11 O Data bus

90 GNDQ - Quite ground

91 VCCQL - Quite core (Low) power

92~94 A12~A14 O Data bus

95 VCCQH - Quite core (High) power

96 GNDA - Address bus ground

97~99 A15~A17 O Data bus

100~102 D0~D2 I/O Data bus

103 VCCD - Data bus power

104 GNDD - Data bus ground

105~110 D3,D8 I/O Data bus

111 VCCD - Data bus power

112 GNDD - Data bus ground

113~118 D9~D14 I/O Data bus

119 VCCD - Data bus power

120 GNDD - Data bus ground

121~125 D15~D19 I/O Data bus

126 VCCQL - Quite core (Low) power

127 GNDQL - Quite core (Low) ground

128 D20 I/O Data bus

129 VCCD - Data bus power

130 GNDD - Data bus ground

131~133 D21~D23 I/O Data bus

134 MODD/IRQD

135 MODC/IRQC

136 MODB/IRQB

137 MODA/IRQA

138 SDO4_1/SDI1_1 I/O Serial data output 4_1 / Serial data input 1_1

139~142 TDO,TDI,TCK,TMS O/I Test data output,Test data input,Test clock,Test mode select

143 MOSI/HA0 I/O SPI master-out-sleve-in / I2C slave address 0

144 MISO/SDA I/O SPI master-in-slave-out / I2C data and acknowkedge

I PLL initial / Nonmaskable interrupt

I Transfer acknowledge

O Bus request

I/O Bus busy

O Read enable

I Bus grant

I Mode select D / External interrupt request D

I Mode select C / External interrupt request C

I Mode select B / External interrupt request B

I Mode select A / External interrupt request A

1-30 (No.22009)

Page 31

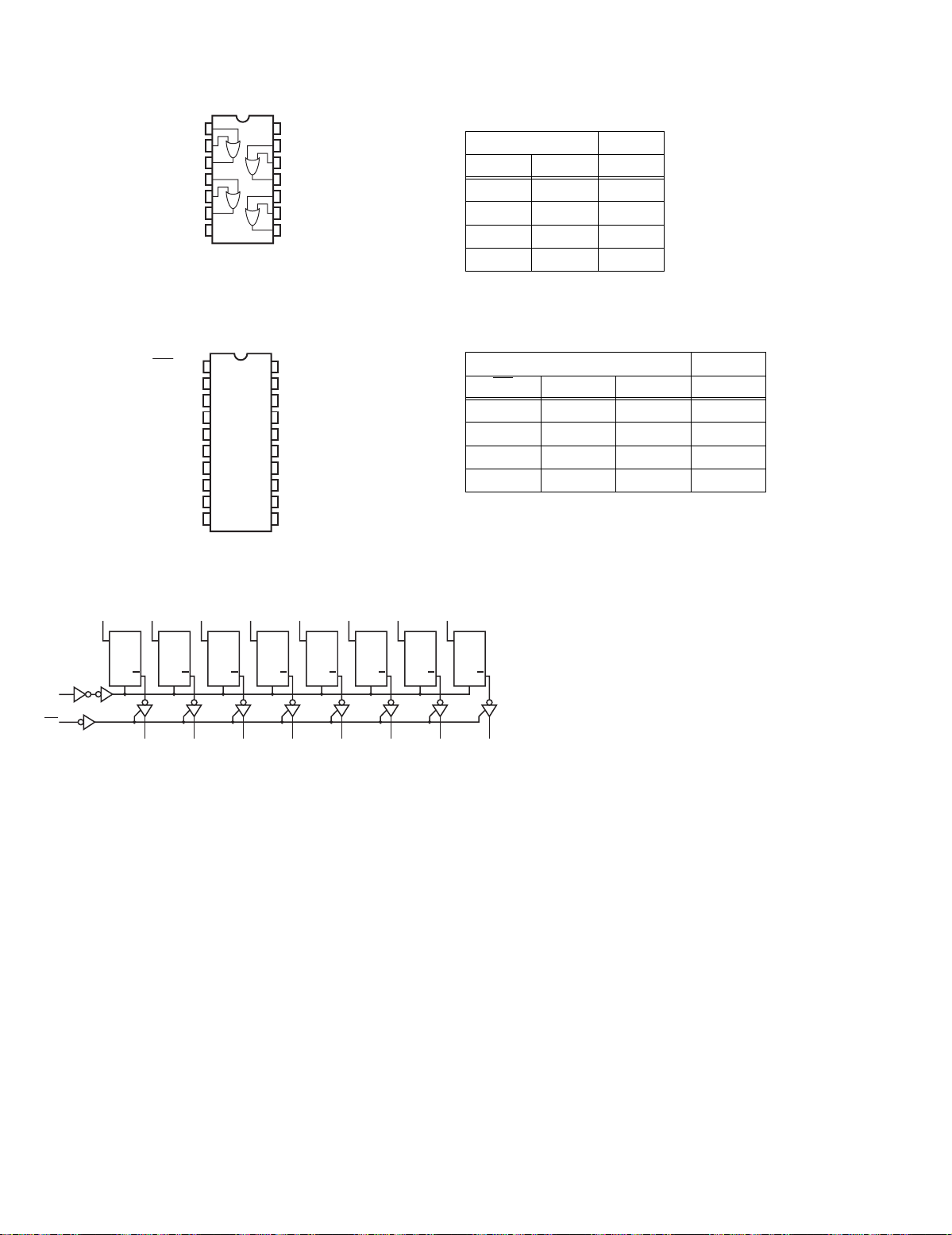

4.13 BA7603F-X (IC211/IC221) : Video signal switcher

• Pin layout & Block diagram

IN1a

GND

IN2b

Vcc

OUTb

IN1b

GND

IN1c

16 15 14 13 12 11 10 9

SWa

SWb

12345678

SWc

TH-A75

CTL OUTPUT

HIN2

LIN1

SWa,SWb,SWc: Clamp inputs

IN2a

CTLa

GND

OUTa

OUTb

OUTc

CTLc

IN2c

4.14 BD4740G-W (IC272) : Reset

• Pin layout • Block diagram

54

Vcc Vout

NC SUB GND

123

Vref

Vcc

5

3

GND

4

Vout

(No.22009)1-31

Page 32

TH-A75

A

4.15 K4S643232E-TC60 (IC505) : 512K x 32 bit x 4 banks synchronous DRAM

• Pin layout

1

86

•Block diagram

43

CLK

DD

Address Register

LCKE

44

Bank Select

Row Buffer

Refresh Counter

LRAS

LCBR

LRAS LCBR LWE

CLK CKE CS

LCAS

Row Decoder

Col. Buffer

Timing Register

RAS CAS

Data Input Register

512K x 32

512K x 32

512K x 32

512K x 32

Column Decoder

Latency & Burst Length

Programming Register

LWCBR

WE DQM

Sense AMP

LDQM

LWE

LDQM

I/O Control

DQi

Output Buffer

1-32 (No.22009)

Page 33

• Pin function

Pin No. Symbol Function

1 VDD Power for the input buffers and core logic.

2 DQ0 Data input/output are multiplexed on the same pin.

3 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

4,5 DQ1,DQ2 Data inputs/outputs are multiplexed on the same pins.

6 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

7,8 DQ3,DQ4 Data inputs/outputs are multiplexed on the same pins.

9 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

10,11 DQ5,DQ6 Data inputs/outputs are multiplexed on the same pins.

12 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

13 DQ7 Data input/output are multiplexed on the same pin.

14 N.C This pin is recommended to be left no connection on the device.

15 VDD Power for the input buffers and core logic.

16 DQM0 Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active.

17 WE

18 CAS

19 RAS

20 CS

21 N.C This pin is recommended to be left no connection on the device.

22,23 BA0,BA1 Selects bank to be activated during row address latch time.

24,25~27 A10,A0 - A2 Row/column addresses are multiplexed on the same pins.

28 DQM2 Makes data output Hi-Z, tSHZ after the clock and masks the output.

29 VDD Power for the input buffers and core logic.

30 N.C This pin is recommended to be left no connection on the device.

31 DQ16 Data input/output are multiplexed on the same pin.

32 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

33,34 DQ17,DQ18 Data inputs/outputs are multiplexed on the same pins.

35 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

36,37 DQ19,DQ20 Data inputs/outputs are multiplexed on the same pins.

38 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

39,40 DQ21,DQ22 Data inputs/outputs are multiplexed on the same pins.

41 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

42 DQ23 Data input/output are multiplexed on the same pin.

43 VDD Power for the input buffers and core logic.

44 VSS Ground for the input buffers and core logic.

45 DQ24 Data input/output are multiplexed on the same pin.

46 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

47,48 DQ25,DQ26 Data inputs/outputs are multiplexed on the same pins.

49 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

50,51 DQ27,DQ28 Data inputs/outputs are multiplexed on the same pins.

52 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQM.

Selects bank for read/write during column address latch time.

Row address : RA0 ~ RA10, Column address : CA0 ~ CA7

Blocks data input when DQM active.

TH-A75

(No.22009)1-33

Page 34

TH-A75

Pin No. Symbol Function

53,54 DQ29,DQ30 Data inputs/outputs are multiplexed on the same pins.

55 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

56 DQ31 Data input/output are multiplexed on the same pin.

57 N.C This pin is recommended to be left no connection on the device.

58 VSS Ground for the input buffers and core logic.

59 DQM3 Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active.

60~66 A3 - A9 Row/column addresses are multiplexed on the same pins.

Row address : RA0 - RA10, Column address : CA0 - CA7

67 CKE Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disables input buffers for power down mode.

68 CLK Active on the positive going edge to sample all inputs.

69,70 N.C This pin is recommended to be left no connection on the device.

71 DQM1 Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active.

72 VSS Ground for the input buffers and core logic.

73 N.C This pin is recommended to be left no connection on the device.

74 DQ8 Data input/output are multiplexed on the same pin.

75 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

76,77 DQ9,DQ10 Data inputs/outputs are multiplexed on the same pins.

78 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

79,80 DQ11,DQ12 Data inputs/outputs are multiplexed on the same pins.

81 VDDQ Isolated power supply for the output buffers to provide improved noise immunity.

82,83 DQ13,DQ14 Data inputs/outputs are multiplexed on the same pins.

84 VSSQ Isolated ground for the output buffers to provide improved noise immunity.

85 DQ15 Data input/output are multiplexed on the same pin.

86 VSS Ground for the input buffers and core logic.

1-34 (No.22009)

Page 35

4.16 GP1FA351RZ (J5521) : Fiber optic receiver

• Pin layout

4.17 GP1UM271XK (IC402) : IR detecting unit for remote control

• Block diagram

AMP

AMP

AMP

AMP

Comp & Output circuit

R

TH-A75

V

CC

V

OUT

GND

L

Amp

B.P.FLimiter

Demodulator

4.18 IS63LV102410K-X (IC525/IC526/IC527) : SRAM

• Pin layout • Block diagram

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A16

A15

A14

A13

OE

I/O7

I/O6

GND

Vcc

I/O5

I/O4

A12

A11

A10

A9

A8

A0-A16

VCC

GND

I/O0-I/O7

CE

OE

WE

A0

A1

A2

A3

CE

I/O0

I/O1

Vcc

GND

I/O2

I/O3

WE

A4

A5

A6

A7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

• Pin function

Pin No. Symbol I/O Function

1-4 A0-A3 I Address inputs

5CE

I Chip enable input

6,7 I/O0,I/O1 I/O Bidirectional ports

8Vcc-Power

9GND-Ground

10,11 I/O2,I/O3 I/O Bidirectional ports

12 WE

I Write enable input

Pin No. Symbol I/O Function

13-21 A4-A12 I Address inputs

22,23 I/O4,I/O5 I/O Bidirectional ports

24 Vcc - Power

25 GND - Ground

26,27 I/O6,I/O7 I/O Bidirectional ports

28 OE

29-32 A13-A16 I Address inputs

Integrator

Comparator

GND Vcc Vout

DECODER

I/O

DATA

CIRCUIT

CONTROL

CIRCUIT

128K X 8

MEMORY ARRAY

COLUMN I/O

I Output enable input

(No.22009)1-35

Page 36

TH-A75

4.19 LA73054-X (IC231) : Video driver

• Pin layout & Block diagram

36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19

75

DRIVER

LPF

2Step

Amp1

C_OFFSET

DC_CTL

CLAMP

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

75

DRIVER

LPF1

2Step

Amp2

Y/C

MIX

75

DRIVER

LPF1

2Step

Amp3

CLAMP

SYNC

SEP

PEDESTAL

CLAMP

• Pin function

Pin No. Symbol I/O Function

1 VCC1 - V CC except for 75ohm driver

2 COMPOSITE.IN I Input composite

3 SQUEEZE.SW I Selecting squeeze mode

4 LETTER-BOX.SW I Selecting letter-box mode

5 MUTE-SW-1 I Composite/S signal mute selection

6 C-IN I Input Chroma signal

7 GND11 - Composite/S GND except for 75ohm driver

8 Y-IN-1 I Input Y signal

9 YC-MIX.SW I Selecting of doing Y/C-MIX or not

10 SIGNAL-IN.SW I Selection of a kind of signal

11 Y-IN-2 I Input component Y or baseband signal

12 MUTE-SW-2 I Component signal mute selection

13 LPF.SW I Selection of a kind of component LPF

14 CB.IN I Input component or baseband signal

15 AMP.SW-2 I Selecting amplifier gain for component signal

16 CR.IN I Input component or baseband signal

17 GND12 - Component GND except for 75ohm driver

18 REG O Capacitor terminal for regulator

19 DRIVE.SW-2 I 2drive/1drive select for component signal

20 GND26 - CR-GND for 75ohm driver

21 CR.OUT O 75ohm driver output of pin16 input

22 GND25 - CB-OUT for 75ohm driver

23 CB.OUT O 75ohm driver output of pin14 input

24 VCC22 - Component Vcc for 75ohm driver

25 Y-OUT-2 O 75ohm driver output of pin11 input

26 GND24 - Component Y out for 75ohm driver

27 GND23 - Y out for 75ohm driver

28 Y-OUT-1 O 75ohm driver output of pin8 input

29 GND22 - Chroma out for 75ohm driver

30 C-DC.OUT O DC voltage output for S1,S2

31 C-OUT O 75ohm driver output of pin6 input

32 GND21 - Composite out for 75ohm driver

33 COMPOSITE-OUT O 75ohm driver output of pin2 input

34 VCC21 - Composite/S Vcc for 75ohm driver

35 DRIVE.SW-1 I 2drive/1drive select for composite/S signal

36 AMP.SW-1 I Selecting amplifier gain for composite/S signal

75

DRIVER

2Step

Amp4

LPF1LPF2

CLAMP

75

DRIVER

LPF1LPF2 LPF1LPF2

2Step

Amp5

PEDESTAL

CLAMP

75

DRIVER

2Step

Amp6

PEDESTAL

CLAMP

VCC

REG

1-36 (No.22009)

Page 37

4.20 LM1117MP1.8-X (IC511) : Regulator

A

• Pin layout • Block diagram

Top view

TH-A75

VIN

DJ/GND

OUTPUT

INPUT

Thermal

Limit

Current

Limit

GND (FIXED OUTPUT)

ADJ.(ADJUSTABLE OUTPUT)

VOUT

Substrate

(No.22009)1-37

Page 38

TH-A75

A

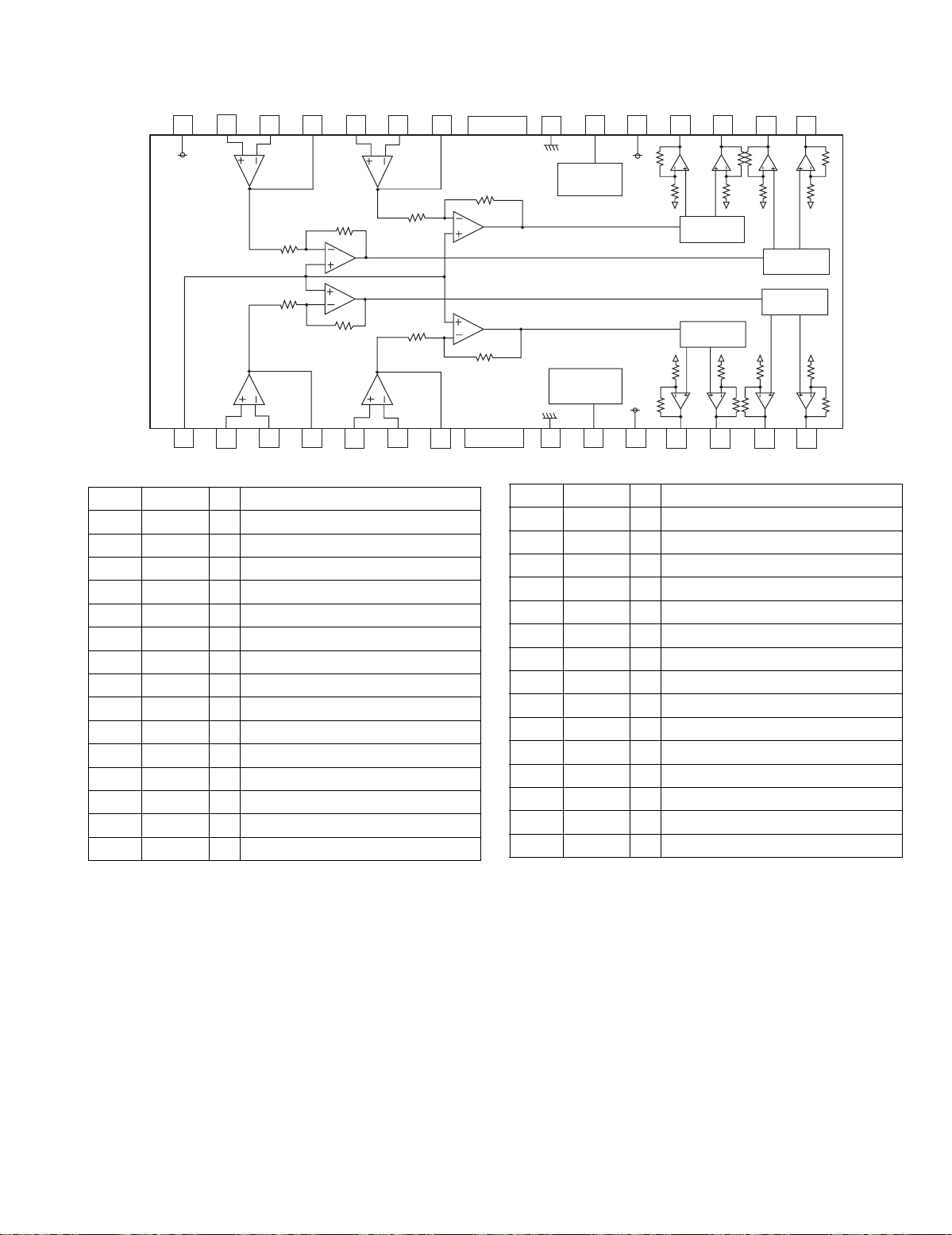

4.21 M61516FP (IC551) : Sound controller

• Pin layout & Block diagram

TONEOUT R

FRVIN FROUT

40

39

FROUT

SROUT

38

37

SBOUT

SWOUT

36

35

COUT

34

SBLOUT

SLOUT

33

32

FLOUT

OUTGND

31

30

AVC C

29

DGND

CLOCK

28

27

DATA

26

LATCH

25

TRE R

BASS R2

BASS R1

FRIN2

SRIN2

SBRIN2

SWIN2

CIN2

SBLIN2

SLIN2

FLIN2

VOLGND3

VOLGND4

BALANCE L/+

BALANCE L/-/LOUD L

INGND

BALANCE R/-/LOUD R

BALANCE R/+

REC R4

REC R3

REC R2

REC R1

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

BALNCE/LOUDNESS

58

50K 50K 50K 50K

59

60

61

62

TONE OUTPUT

SELECTOR

FRONT INPUT

SELECTOR

BALNCE/LOUDNESS

CHANGE SW

A

LOUDNESS TAP

B

CHANGE SW

REC SW

REC SW

REC SW

REC SW

OUTPUT GAIN

-

+

TONE

BASS/TRE

10K

+

-

Lch

10K

BALANCE OUTPUT

Rch

10K

+

10K

INPUT GAIN

CONTROL

CONTROL

50K

+

-

50K

FL VOL

LOUDNESS

TAP B

-

+

50K

SR VOL

SBR VOL SBL VOL SL VOLSW VOL C VOL

-

+

50K

OUTPUT GAIN

CONTROL

50K

+

-

50K

LOUDNESS

TAP A

+-+-+-+-+

50K 50K 50K 50K 50K

+

-

INPUT

SELECTOR

INPUT

SELECTOR

FL VOL

-

+

MCU

I/F

ZERO CROSS

DETECTOR &

TIMER DETECTOR

TONE OUTPUT

+

SELECTOR

TONE

BASS/TRE

FRONT INPUT

SELECTOR

INPUT GAIN

CONTROL

-

+

50K

-

REC SW

REC SW

REC SW

REC SW

50K 50K 50K 50K

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

DVDD

TINT

VOLGND2

FLVIN

TNEOUT

TREL

BASS L2

BASS L1

FRIN1

SRIN1

SBRIN1

SWIN1

CIN1

SBLIN1

SLIN1

FLIN1

VOLGND1

REC L4

REC L3

REC L2

REC L1

INLJ

1-38 (No.22009)

INRJ

INRI

63

64

65

INRH

66

INRG

67

INRF

68

INRE

69

INRD

70

INRC

71

INRB

72

INRA

73

VEE

74

INLA

75

INLB

76

INLC

77

INLD

78

INLE

79

INLF

80

INLG

2

INLI

1

INLH

Page 39

• Pin function

Pin No. Symbol Function

1~3 INLH,INLI,INLJ Lch input

4~7 REC L1,REC L2,REC L3,REC L4 REC output

8 VOLGND1 Analog GND for vol.

9~12 FLIN1,SLIN1,SBLIN1,CIN1 FLch,SLch,SBLch,Cch input

13~16 SWIN1,SBRIN1,SRIN1,FRIN1 SWch,SBRch,SRch,FRch input

17,18 BASS L1,BASS L2 Tone path frequency characteristic setup

19 TRE L Treble frequency characteristic setup

20 TONEOUT L Tone output

21 FLVIN FL vol. input

22 VOLGND2 Analog GND for vol.

23 TIM1 Timer setup

24 DVDD Internal logic circuit Power supply terminal

25,26,27 LATCH,DATA,CLOCK Latch,Data,Clock input for serial data transmission

28 DGND Internal logic circuit GND terminal

29 AVCC Internal analog cicuit power supply terminal (+)

30 OUTGND analog GND

31~34 FLOUT,SLOUT,SBLOUT,COUT FLch,SLch,SBLch,Cch output

35~38 SWOUT,SBROUT,SROUT,FROUT SWch,SBRch,SRch,FRch output

39 FRVIN FR vol.input

40 TONEOUT R Tone output

41 TRE R Treble frequency characteristic setup

42,43 BASS R1,BASS R2 Tone path frequency characteristic setup

44~47 FRIN2,SRIN2,SBRIN2,SWIN2 FRch,SRch,SBRch,SWch input

48~51 CIN2,SBLIN2,SLIN2,FLIN2 Cch,SBLch,SLch,FLch input

52,53 VOLGND3,VOLGND4 Analog GND for vol.

54 BALANCE L/+ Lch balance output for ADC

55 BALANCE L/- LOUD L Lch loudness frequency setup

56 INGND Analog GND

57 BALANCE R/+ Rch balance output for ADC

58 BALANCE R/- LOUD R Rch loudness frequency setup

59~62 REC R1,REC R2,REC R3,REC R4 REC input

63~66 INRJ,INRI,INRH,INRG Rch input

67~70 INRF,INRE,INRD,INRC Rch input

71,72 INRB,INRA Rch input

73 AVEE Internal analog circuit power supply terminal (-)

74~77 INLA,INLB,INLC,INLD Lch input

78~80 INLE,INLF,INLG Lch input

TH-A75

(No.22009)1-39

Page 40

TH-A75

4.22 MM1561KF-X (IC593) : Regulator

• Pin layout

756

(TOP VIEW)

1

234

•Block diagram

VIN

7

Cont

5

GND

3

• Pin function

Pin No. Symbol Function

1 Vo Output pin

2 NC Not connect

3 GND Ground

4 Cn Noise decrease pin

5 CONT Control pin

Bias

Thermal

shutdown

Driver

Current

limiter

Cn

Vo

1

Reference

4

CONT

H

L

Output

ON

OFF

6 Sub Substrate pin, The 6pin must be connected to GND.

7 VIN Input pin

1-40 (No.22009)

Page 41

4.23 MM1563DF-X (IC592) : Regulator

• Pin layout

756

(TOP VIEW)

1

234

• Block diagram

VIN

7

Bias

Cont

5

Thermal

shutdown

GND

3

• Pin function

Pin No. Symbol Function

1 Vo Output pin

2 NC Not connect

3 GND Ground

4 Cn Noise decrease pin

5 CONT Control pin

Driver

Current

limiter

Cn

TH-A75

Vo

1

Reference

4

CONT

H

L

Output

ON

OFF

6 Sub Substrate pin, The 6pin must be connected to GND.

7 VIN Input pin

(No.22009)1-41

Page 42

TH-A75

4.24 MN101C49GKR (IC271) : System micom

• Pin layout

100 76

1

75

25

51

26 50

• Pin function

Pin No. Symbol I/O Function

1 VREF- - Connect to ground

2 NTSEL(RGB--SEL) I NTSC/PAL discrimination (RGB/YC switching discrimination) signal

3 VCR-S/C I VCR S/Composite detection signal

4 DBS-S/C I DBS S/Composite detection signal

5 TH-DET I Heat sink temp. detection

6 SAFETY1 I Short det ection signal

7 VERSION I Version select switch signal

8 KEY-IN1 I Key input1 (AD)

9 KEY-IN2 I Key input2 (AD)

10 VREF+ - Reference power supply

11 VDD - Power supply

12 OSC2 O Oscillator output (8MHz)

13 OSC1 I Oscillator input (8MHz)

14 GND - Ground

15,16 NC - Not used

17 GND - Ground

18 DI-DO O Panel serial communication data output

19 NC - Not used

20 DI-CK O Panel serial communica tion clock output

21 S2UDT/TX (DATA OUT) O Serial communication data output for PANTERA

22 S2UDT/RX (DATA IN) I Serial communication data input for PANTERA

23 SCLK/CLK I Serial communication clock for PANTERA

24 INTP O Transmit request for PANTERA communication

25 CPU-RESET O Reset signal for PANTERA

26 CS I Receive request for PANTE RA communication (Interruption)

27 REMOCON I Remote control signal input (interruption)

28 PROTECT I Speaker protect detection

29 RDS ST I RDS communication strobe (Interruption)

30 NC - Not used

31 GND - Ground

32 VDD2/FLASH-VDD - VDD for Flash write

33 RESET-IN/RST I System control micom reset input

34 DSP-RST O DSP micom reset signal output

35 DSP-RDY O DSP micom ready signal

36 AVC-OUT O AV compulink signal output

37 AVC-IN I AV compulink signal input

38~40 NC - Not used

41 VPP/FLASH-VSS - VPP for Flash write

42 DSP-COM O DSP serial communication data output

43 DSP-STAT I DSP serial communication data input

44 DSP-CLK O DSP serial communication clock

45 VOL-DATA O VOLUME serial communication data output

46 VOL-LATCH O VOLUME serial communication strobe

47 VOL-CLK O VOLUME serial communication clock

1-42 (No.22009)

Page 43

Pin No. Symbol I/O Function

48 NC - Not used

49 INT/PROG O Video driver filter select

50 RELAT-CTL O Speaker control

51 BASS O Bass boost control

52,53 NC - Not used

54 VIDEO-MUTE1 O Video driver mute1 control

55 VIDEO-MUTE2 O Video driver mute2 control

56 VIDEO-YCMIX O Video driver YCMIX control