Page 1

SERVICE MANUAL

DVD DIGITAL CINEMA SYSTEM

Area suffix

TH-A30

US -------------- Singapore

UB ------------- Hong Kong

UW -- Brazil,Mexico,Peru

UG - Turkey,South Africa,

Egypt

A ------------------ Australia

TH-A30

SP-XSA30 2

STANDBY/ON

AUDIO

VCR

TV

TV/VIDEO PROGRESSIVE

TV CHANNEL

DISPLAY

STEP

AUDIO/

SUBTITLE

TV VOLUME

FM MODE

VCR

DVD FM/AM AUX

CONTROL

TUNER PRESET

DOWN UP

FF

REW

VCR CHANNEL

TUNING

B.SEARCH F.SEARCH

ENTER

VOLUME

MUTING

TOP MENU

MENU

RETURN

STANDB

RM-STHA30U

DVD CINEMA SYSTEM

Y

STANDBY/ON

AUDIO/FM MOD

D

SP

Contents

Safety precautions

Preventing static electricity

Important for laser products

SP-XA30 3

E

V

OLUME

SOURCE

DVD DIGITAL CINEMA

SYSTEM TH-A

30

DIGITAL

XV-THA30 SP-WA30

1-2

1-3

1-4

Disassembly method

Wiring connection

Description of major ICs

1-5

1-12

1-13~28

COPYRIGHT 2002 VICTOR COMPANY OF JAPAN, LTD.

No.21172

Dec. 2002

Page 2

TH-A30

1. This design of this product contains special hardware and many circuits and components specially for safety

purposes. For continued protection, no changes should be made to the original design unless authorized in

writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services

should be performed by qualified personnel only.

2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product

should not be made. Any design alterations or additions will void the manufacturer`s warranty and will further

relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

3. Many electrical and mechanical parts in the products have special safety-related characteristics. These

characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily

be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which

have these special safety characteristics are identified in the Parts List of Service Manual. Electrical

components having such features are identified by shading on the schematics and by ( ) on the Parts List in

the Service Manual. The use of a substitute replacement which does not have the same safety characteristics

as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or

other hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be

separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of

electric shock and fire hazard. When service is required, the original lead routing and dress should be

observed, and it should be confirmed that they have been returned to normal, after re-assembling.

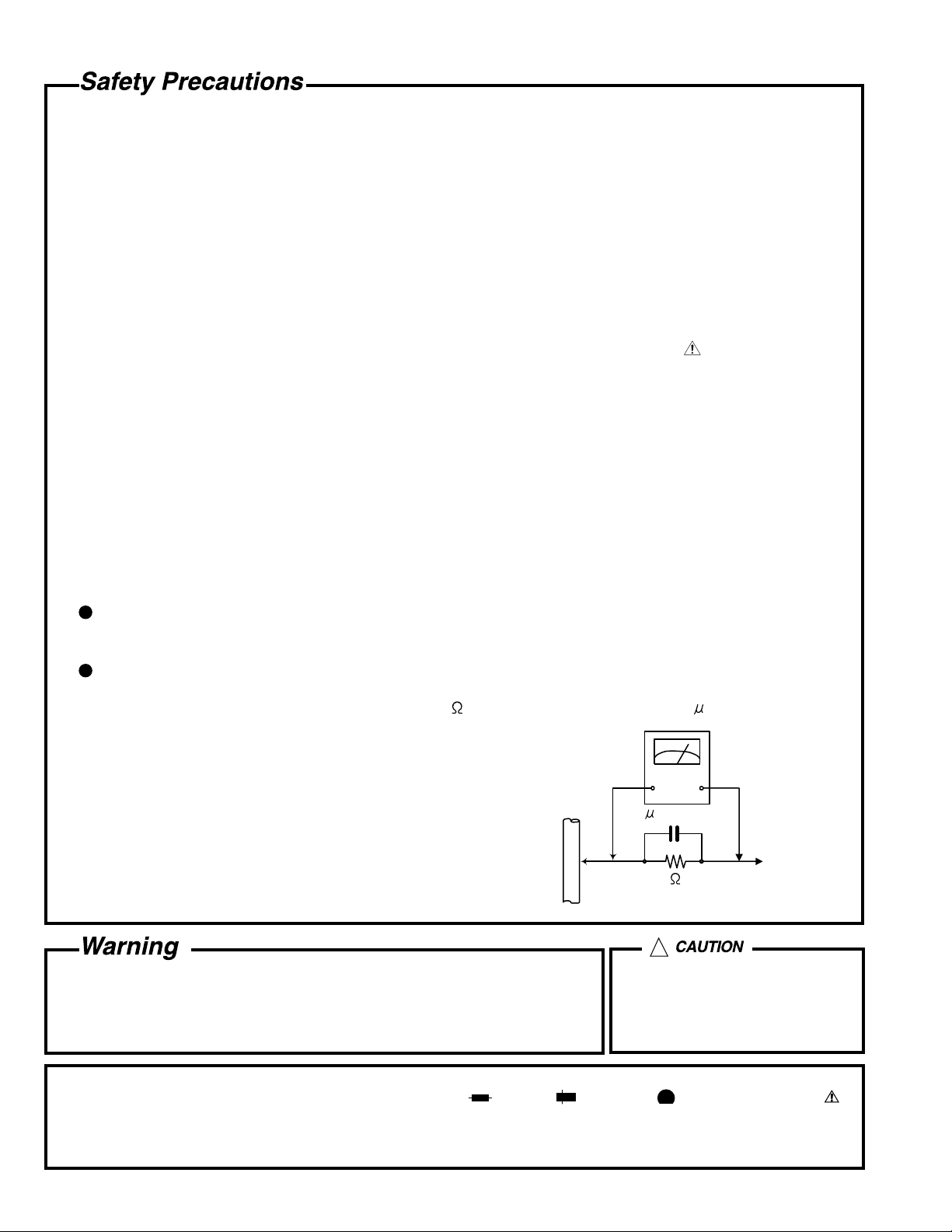

5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product

(antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the

product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage

current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return

path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more

sensitivity in the following manner. Connect a 1,500 10W resistor paralleled by a 0.15 F AC-type capacitor

between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC

voltmeter.

Move the resistor connection to each exposed metal part,

particularly any exposed metal part having a return path to

the chassis, and meausre the AC voltage across the resistor.

Now, reverse the plug in the AC outlet and repeat each

measurement. Voltage measured any must not exceed 0.75 V

AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

0.15 F AC TYPE

1500 10W

Good earth ground

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

Place this

probe on

each exposed

metal part.

!

1. This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

3. Repairs m ust be made in accordance with the relevant safety standards.

4. It is essential that safety critical components are replaced by approved parts.

5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may

be left over on some parts of the

chassis. Therefore, pay attention to

such burrs in the case of

preforming repair of this system.

In regard with component parts appearing on the silk-screen pr inted side (parts side) of the PWB diagrams, the

parts that are printed over with black such as the resistor ( ), diode ( ) and ICP ( ) or identified by the " "

mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

1-2

Page 3

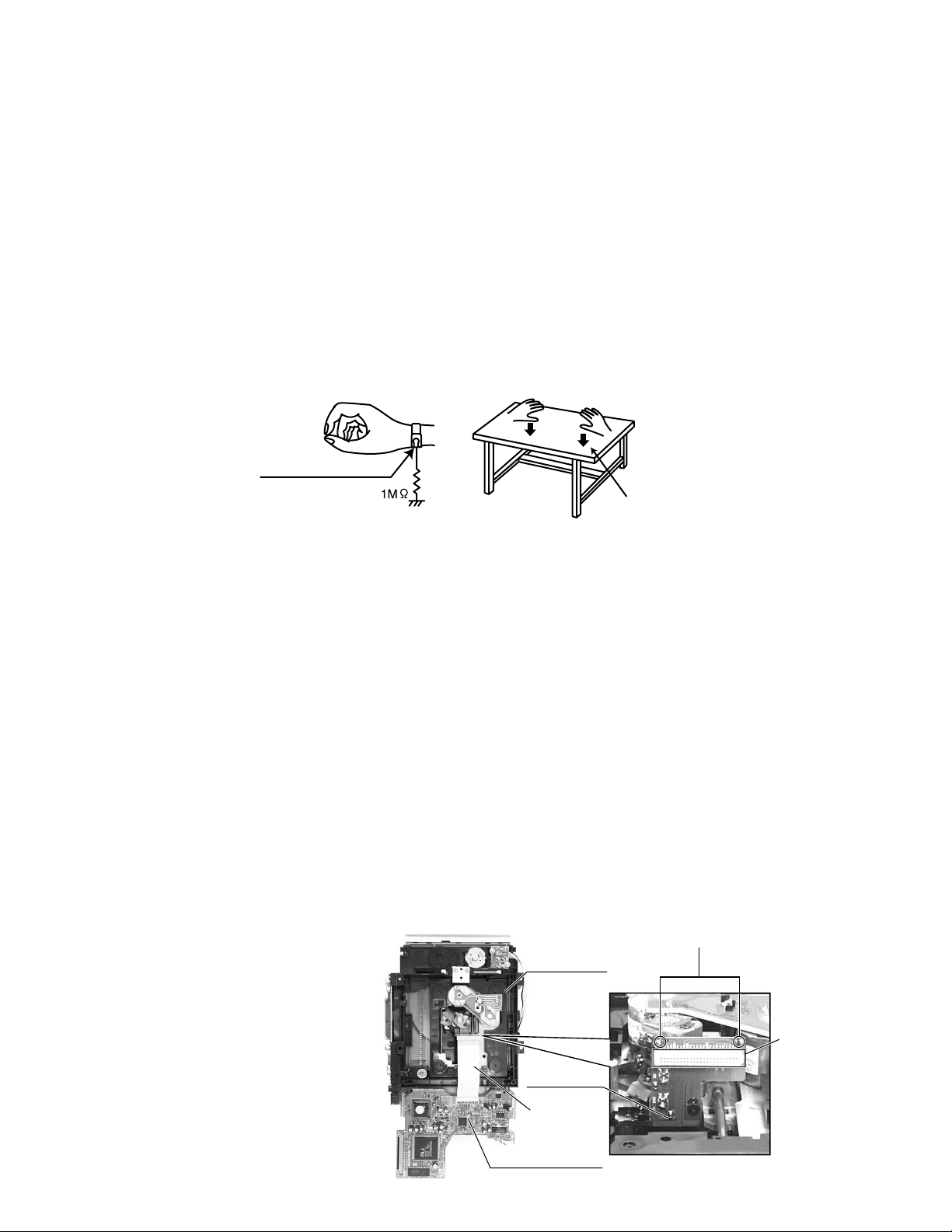

Preventing static electricity

TH-A30

1.Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

2.About the earth processing for the destruction prevention by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as CD players.

Be careful to use proper grounding in the area where repairs are being performed.

2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over

it before placing the traverse unit (optical pickup) on it.

2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

(caption)

Anti-static wrist strap

Conductive material

(conductive sheet) or iron plate

3. Handling the optical pickup

1. In order to maintain quality during transport and before installation, both sides of the laser diode on the

replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition.

(Refer to the text.)

2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power

source can easily destroy the laser diode.

4.Handling the traverse unit (optical pickup)

1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific

details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse

unit. Be careful not to take too long a time when attaching it to the connector.

3. Handle the flexible cable carefully as it may break when subjected to strong force.

4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it.

Attention when traverse unit is decomposed

*Please refer to "Disassembly method" in the text for pick-up and how to detach the substrate.

Solder is put up before the card

1.

wire is removed from connector

on the pick up board as shown in

Figure.

(When the wire is removed

without putting up solder, the CD

pick-up assembly might destroy.)

Please remove solder after

2.

connecting the card wire with

when you install picking up

in the substrate.

DVD mechanism assembly (bottom side)

DVD loading

mechanism

Pick up board

Card wire

Short land

(These two points are

soldered respectively,

and are made to

short-circuit)

Connector

DVD loader board

1-3

Page 4

TH-A30

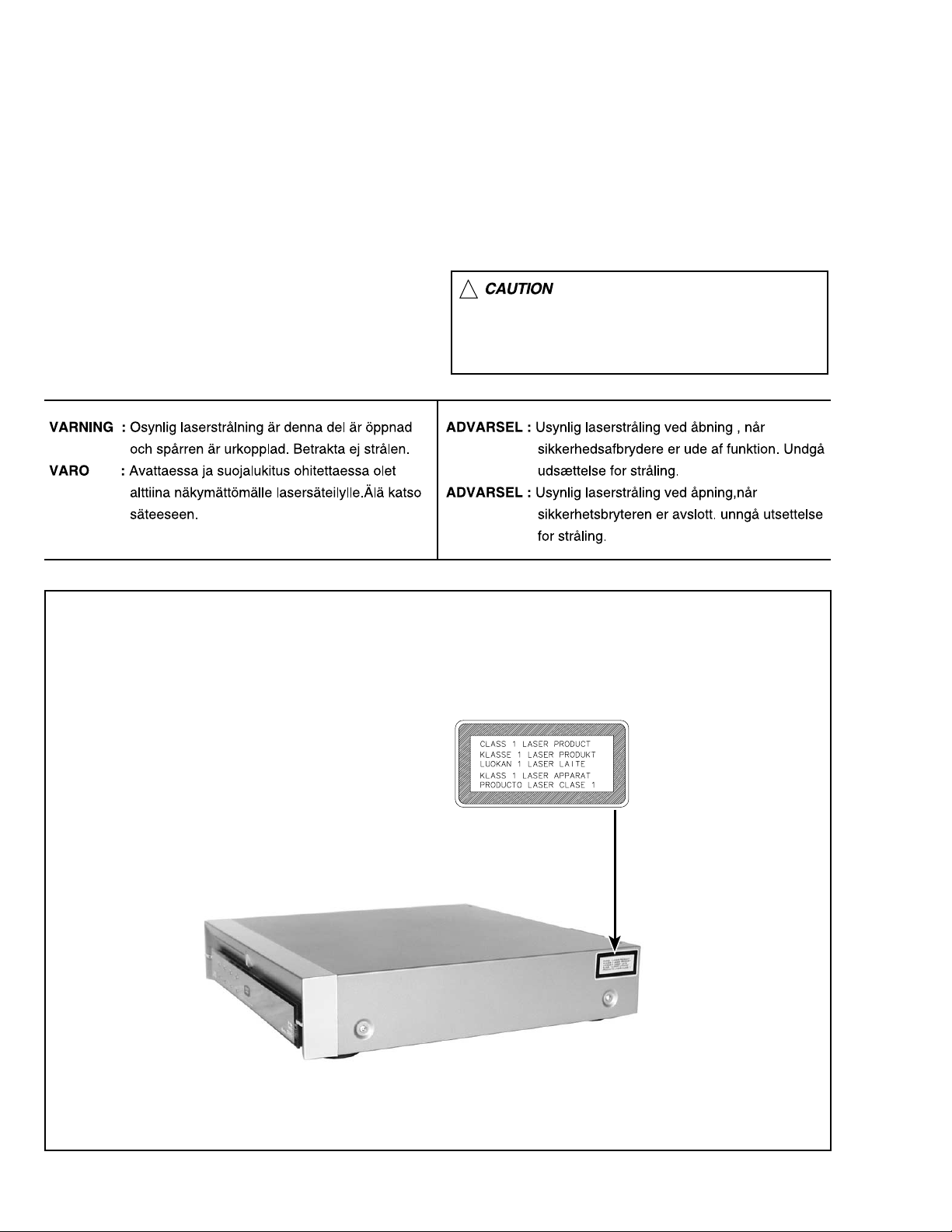

Important for laser products

1.CLASS 1 LASER PRODUCT

2.DANGER : Invisible laser radiation when open and inter

lock failed or defeated. Avoid direct exposure to beam.

3.CAUTION : There are no serviceable parts inside the

Laser Unit. Do not disassemble the Laser Unit. Replace

the complete Laser Unit if it malfunctions.

4.CAUTION : The compact disc player uses invisible laser

radiation and is equipped with safety switches which

prevent emission of radiation when the drawer is open and

the safety interlocks have failed or are de

feated. It is dangerous to defeat the safety switches.

5.CAUTION : If safety switches malfunction, the laser is able

to function.

6.CAUTION : Use of controls, adjustments or performance of

procedures other than those specified herein may result in

hazardous radiation exposure.

!

Please use enough caution not to

see the beam directly or touch it

in case of an adjustment or operation

check.

REPRODUCTION AND POSITION OF LABELS

CLASS 1

LASER PRODUCT

1-4

Page 5

TH-A30

Disassembly method

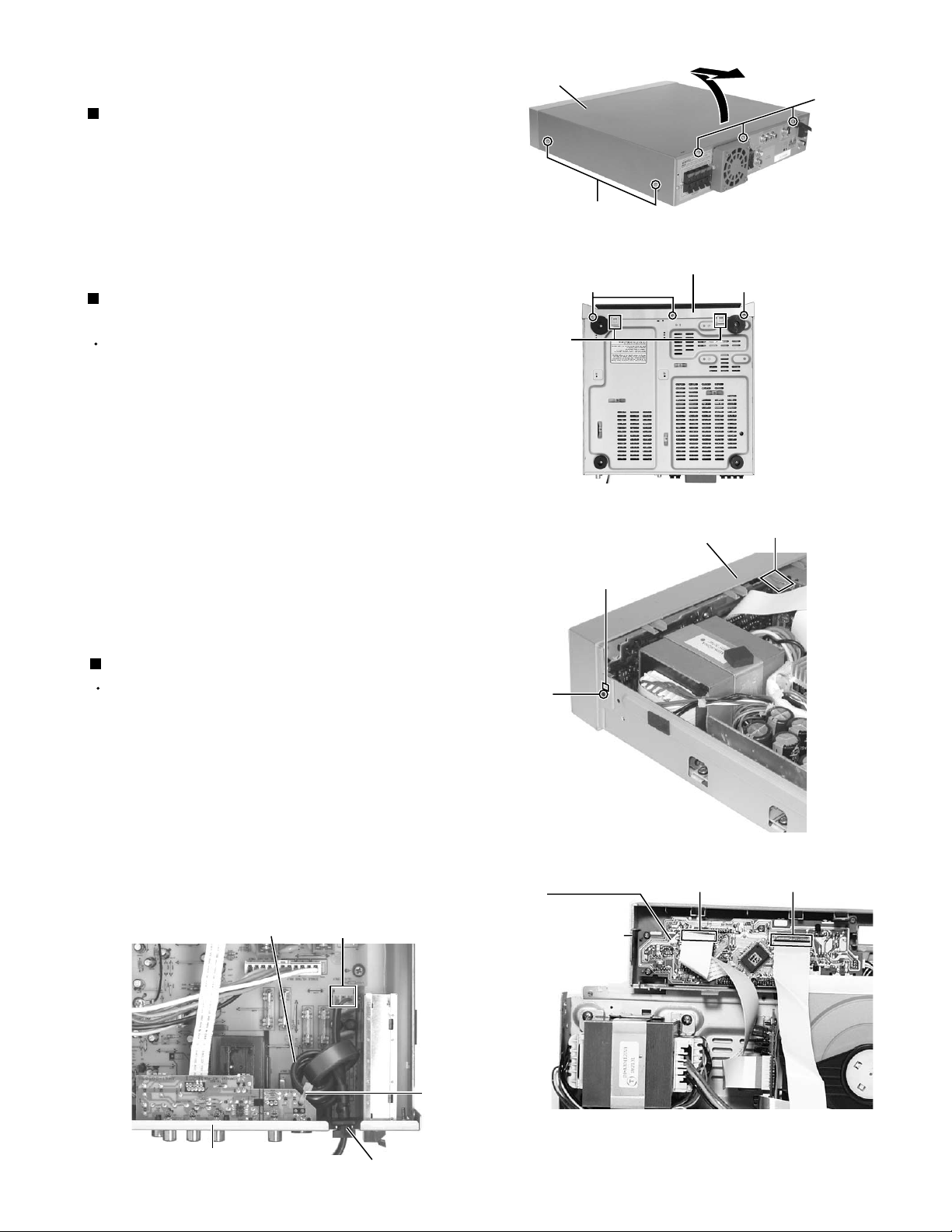

Removing the top cover (See Fig.1)

1.

Remove the four screws A attaching the top cover

on both sides of the body.

2.

Remove the three screws B on back of the body.

3.

Remove the top cover from behind in the direction of

the arrow while pulling both sides outward.

Removing the front panel assembly

(See Fig.2A, 2B and 3)

Prior to performing the following procedure, remove

the top cover.

1.

Remove the three screws C attaching the front panel

assembly on bottom of the body.

2.

Remove the two screws D attaching the front panel

assembly on both sides of the body.

3.

Remove the claw1, claw2 and claw3, and detach the

front panel assembly toward the front.

Top cover

Claw1

(bottom side)

B

A

(both sides)

Front panel assembly

Fig.1

CC

Fig.2A

Front panel assembly

Claw3

4.

Disconnect the card wire from the connector FCW1

and FCW2 on the display board.

Removing the power cord (See Fig.4)

Prior to performing the following procedure, remove

the top cover.

1.

Cut off the tie band fixing the power cord.

2.

Disconnect the power cord from the connector

ACW1 on the main board and pull up the cord

stopper upward.

Notes : The power cord is exchangeable.

Power cord

ACW1

Claw2

(both sides)

D

(both sides)

Display board

Front panel assembly

(Inner side)

Fig.2B

FCW1FCW2

Rear panel

Fig.4

Tie band

Power cord

stopper

Fig.3

1-5

Page 6

TH-A30

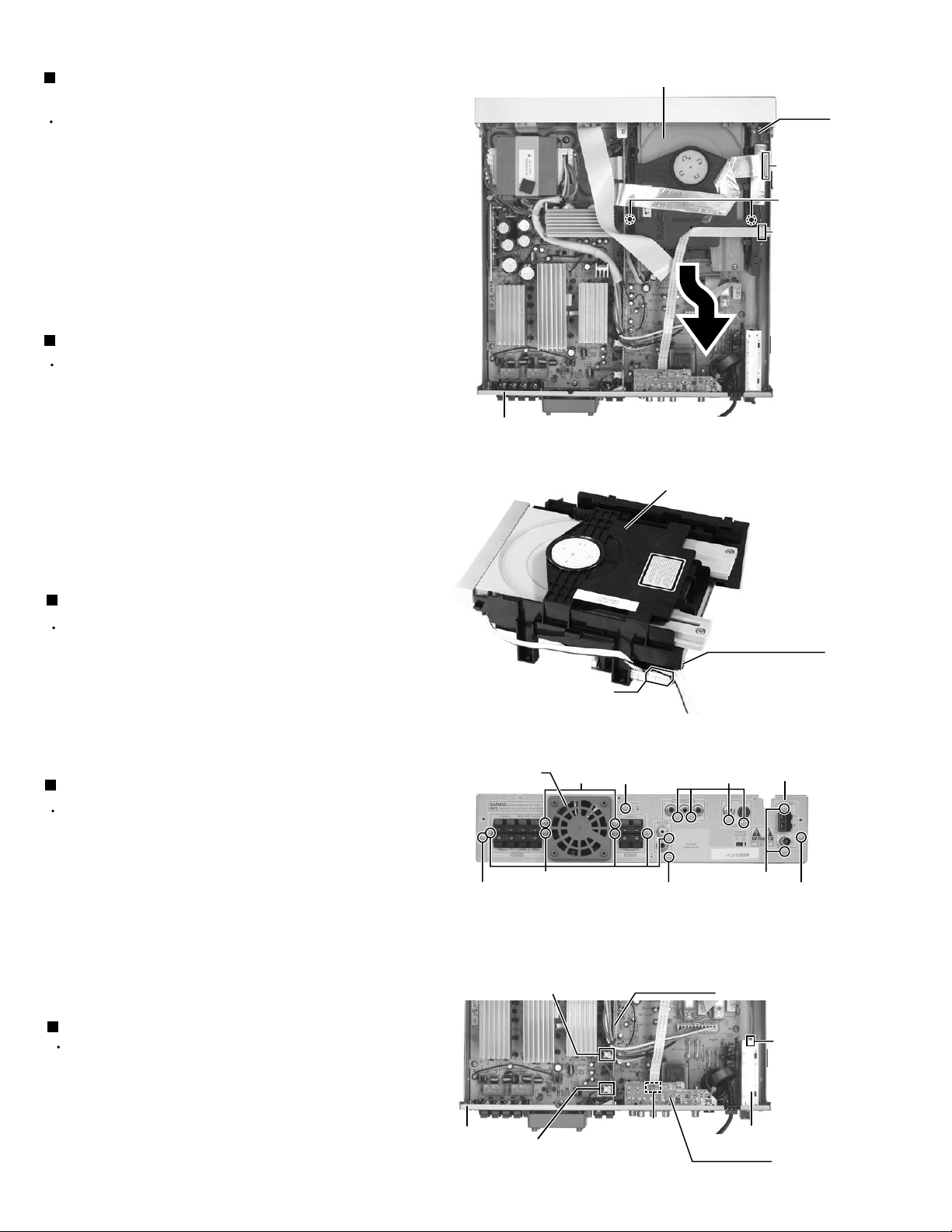

Removing the DVD mechanism assembly

(See Fig.5 and 6)

Prior to performing the following procedure, remove

the top cover.

1.

Disconnect the card wire from the connector J14 and

J21 on the DVD MPEG board.

2.

Remove the two screws E attaching the DVD

mechanism assembly and pull up with drawing out.

3.

Disconnect the harness from the connector DJ6 on

the DVD loader board.

Removing the rear panel (See Fig.7 and 8)

Prior to performing the following procedure, remove

the top cover and power cord stopper.

1.

Disconnect the harness from the connector J9 on the

DSP board.

2.

Remove the two screws F, four screws G, one screw

I and five screws J attaching the each board to the

rear panel.

Rear panel

DVD mechanism assembly

Fig.5

DVD mechanism

assembly

DVD

MPEG

board

J14

E

J21

3.

Remove the three screws K attaching the rear panel

on back of the body.

Removing the tuner pack (See Fig.7 and 8)

Prior to performing the following procedure, remove

the top cover.

1.

Disconnect the card wire from the connector CON01

on the tuner pack.

2.

Remove the two screws F attaching the tuner pack

to the rear panel.

Removing the jack board (See Fig.7 and 8)

Prior to performing the following procedure, remove

the top cover.

1.

Disconnect the card wire from the connector VW2 on

the jack board.

2.

Disconnect the harness from the connector J10 on

the DSP board.

3.

Remove the four screws G attaching the jack board

to the rear panel.

Fan motor

DSP board)

DJ6

J10 (on the

Fig.6

Fig.7

DSP board

DVD loader board

Rear panel

GHI

KKK

FJ

Removing the fan motor (See Fig.7 and 8)

Prior to performing the following procedures, remove

the top cover .

1.

Disconnect the harness from the connector J9 on the

DSP board .

2.

Removing the two screws H attaching the fan motor

to the rear panel.

1-6

Rear panel

J9(on the

DSP board)

Fig.8

VW2

CON01

Tuner pack

Jack board

Page 7

TH-A30

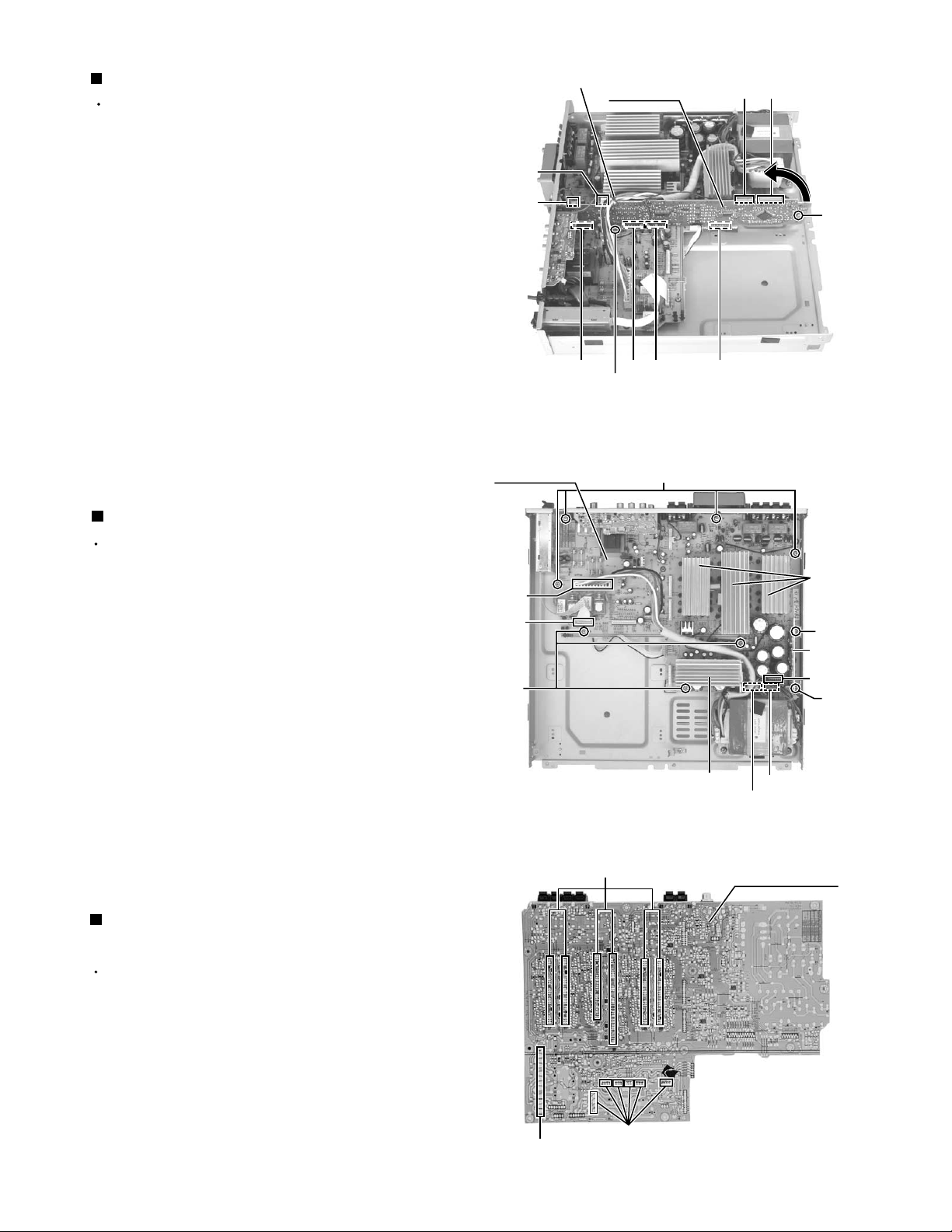

Removing the DSP board (See Fig.9)

Prior to performing the following procedure, remove

the top cover, front panel assembly, DVD

mechanism assembly and jack board.

1.

Remove the harness band fixing the harness.

2.

Disconnect the harness from the connector J9 and

J10 on the DSP board.

3.

Disconnect the card wire from the connector J1 and

J3 on the DSP board.

4.

Remove the one screw L attaching the DSP board.

5.

Remove the screw M1 and remove the earth wire.

6.

Remove the one screw I attaching the DSP board to

the rear panel (see fig.7).

7.

Pull up the DSP board from the front side upwards

disconnecting the connector J2, J5, J6 and J7.

Removing the main board (See Fig.10)

Prior to performing the following procedure, remove

the top cover, front panel assembly, power cord,

DVD mechanism assembly, jack board and DSP

board.

1.

Disconnect the card wire from the connector CW8 on

the main board.

2.

Disconnect the harness from the connector ACW2,

ACW3, ACW4 and ACW5 on the main board.

Harness band

J10

J9

(Rear panel side)

Main board

ACW2

CW8

M2

J6

M1

(fixing the

earth wire)

DSP board

J5 J7

Fig.9

M2

J2

J1J3

L

(Front panel side)

Heat sink1

M2

Heat sink2

ACW3

M2

3.

Remove the five screws J attaching the speaker

terminals and jack to the rear panel (see fig.7).

4.

Remove the nine screws M2 attaching the main

board.

5.

When the rear panel is not removed, pull up the

main board from front side.

Removing the power transistor & power IC

(See Fig.10 to 12)

Prior to performing the following procedure, remove

the top cover, front panel assembly, DVD

mechanism assembly, jack board, DSP board and

main board.

1.

After removing the solder part 1 soldered to the main

board, remove each screw and remove the heat sink

from the power transistor.

2.

After removing the solder part 2 soldered to the main

board, remove each screw and remove the heat sink

from the power IC.

Heat sink3

Fig.10

(Each power transistor is fixed)

Solder part 1

Solder part 3

Solder part 2

(Power IC is fixed)

(Power IC is fixed)

Fig.11

ACW5

ACW4

Main board

(Reverse side )

1-7

Page 8

TH-A30

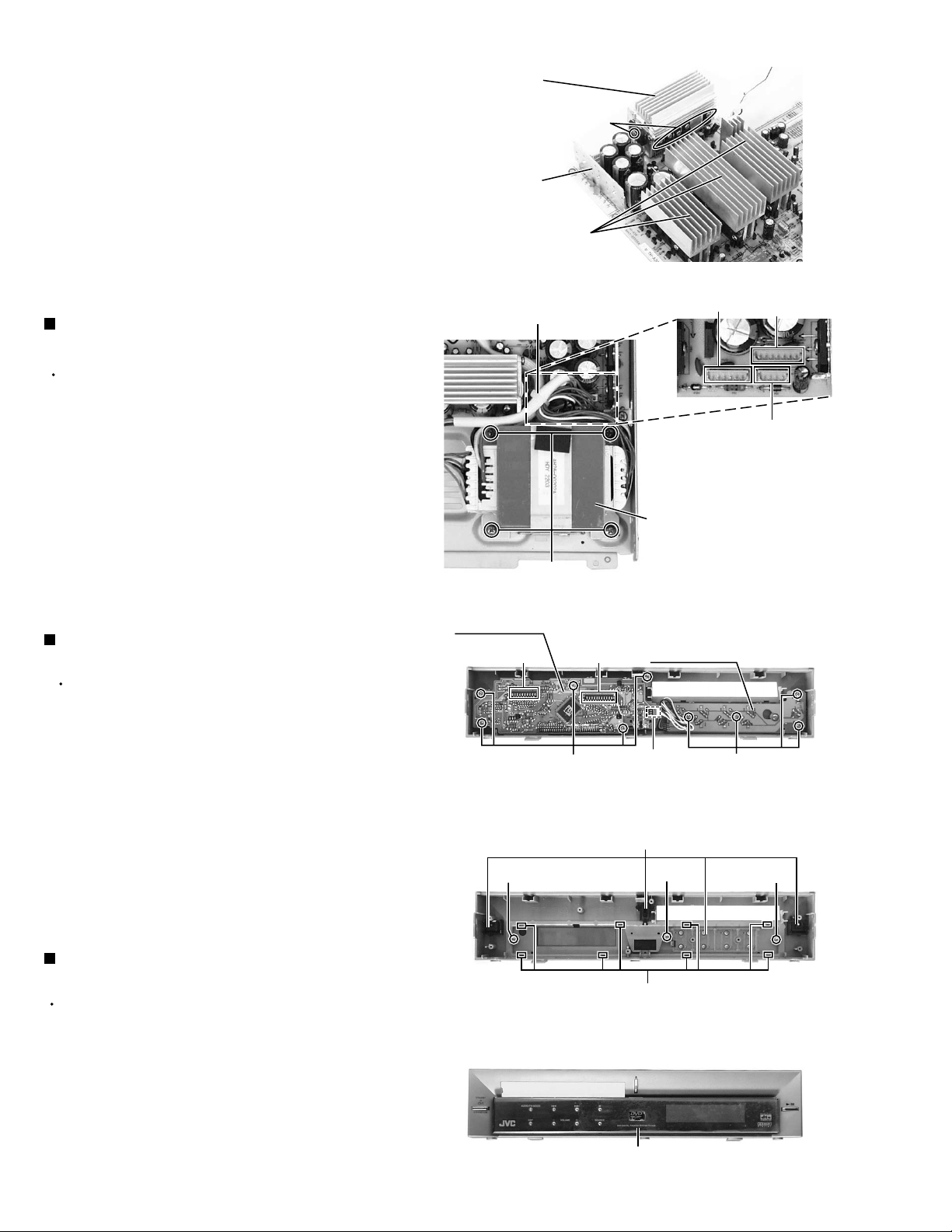

3.

The power ICs fixed to the heat sink 3 can be

removed individually that it is easy to remove

screws (in meaning that a screw driver reaches). It is

not necessary to remove whole like abovementioned 1. and 2. .

After removing each screw which is fixing each

power IC to the heat sink 3, the solder part 3 to

which it corresponds on the main board is removed.

In addition, probably, the way after removing the

whole will be safe when a screw driver does not

reach too.

Removing the power transformer

(See Fig.13)

Prior to performing the following procedure, remove

the top cover.

1.

Cut off the tie band fixing the harness, if needed.

2.

Disconnect the harness from the connector ACW2

(see fig.10), ACW3, ACW4 and ACW5 on the main

board.

3.

Remove the four screws N attaching the power

transformer.

<Front panel assembly section>

Removing the display board & switch

board (See Fig.1 and 2)

Prior to performing the following procedure, remove

the top cover and the front panel assembly.

Heat sink 3

(to which power

IC is attached)

Heat sink 2

(to which power

IC is attached)

Heat sink 1

(to which power

transistor is attached)

Tie band

Display board

FCW2

N

Screws

FCW1

Fig.12

ACW4 ACW3

ACW5

Power

transformer

Fig.13

Front panel assembly

(inner side)

Switch board

1.

Disconnect the card wire from the connector FCW1

and FCW2 on the display board.

2.

Remove the five screws A attaching the display

board on the inner of the front panel assembly.

3.

Remove the four screws B attaching the switch

board on the inner of the front panel assembly.

4.

Disconnect the harness from connector FW2 on the

display board, if needed.

Removing the front window

(See Fig.2 and 3)

Prior to performing the following procedure, remove

the top cover, front panel assembly, display board

and switch board.

Remove the switch buttons, if needed.

1.

Remove the three screws C attaching the front

2.

window on the front panel.

Remove the eight claws fixing the front window on

3.

the front panel.

1-8

A

FW2

B

Fig.1

Front panel assembly

(inner side)

Switch button

CCC

Claw

Fig.2

Front panel assembly

Front window

Fig.3

(front side)

Page 9

TH-A30

y

y

)

y

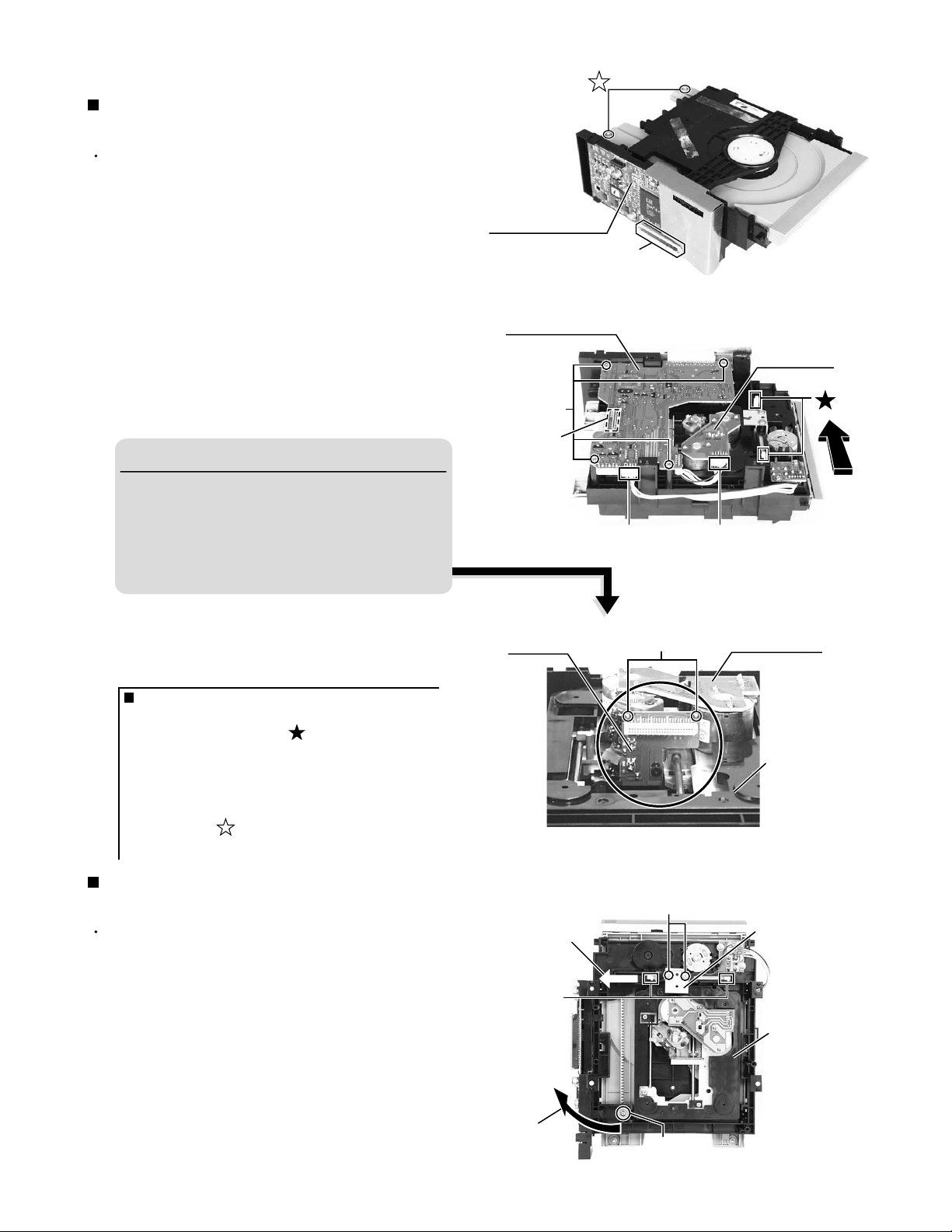

<DVD mechanism assembly section>

Removing the DVD loader board

(See Fig.1 to 3)

Prior to performing the following procedure, remove

the top cover and DVD mechanism assembly.

1.

Disconnect the card wire from the connector J6 on

the DVD MPEG board.

2.

Disconnect the harness from the connector on the

motor board.

3.

Disconnect the harness from the connector MJ5 on

the DVD loader board.

4.

Remove the four screws A attaching the DVD loader

board to DVD mechanism assembly.

CAUTION!! (see fig.3)

Before removing the card wire which

connects the pickup board and DVD loader

board, solder the two soldering parts and

make it short-circuit.

Moreover, while having removed the card

wire, don't remove these solder.

DVD MPEG board

DVD loader board

A

RCN1

J6

MJ5

DVD mechanism assembl

Fig.1

DVD mechanism assembl

Motor board

Connector

Fig.2

(top side)

(bottom side

5.

Disconnect the card wire from the connector RCN1

on the DVD loader board.

ONE POINT

How to eject the DVD tray manually

(see fig.2)

The white lever of the mark is moved in

the direction of the arrow. Then, the tray will

be opened.

Moreover, the tray is separable from a DVD

mechanism assembly by removing two

screws of the mark (see fig.1) and drawing

out the tray.

Removing the DVD loading mechanism

(See Fig.4)

Prior to performing the following procedure, remove

the top cover, DVD mechanism assembly and DVD

loader board.

1.

Remove the two screws B and remove the bracket.

2.

Remove the one screw C fixing the DVD loading

mechanism.

Pick up

board

Lever

Soldering parts

X

Motor board

Fig.3

DVD mechanism assembl

B

DVD loading

mechanism

(bottom side)

Bracket

DVD loading

mechanism

3.

Move the lever in the direction of the arrow X.

4.

Remove the DVD loading mechanism from the DVD

mechanism assembly by moving it in the direction of

the arrow Y.

Y

C

Fig.4

1-9

Page 10

TH-A30

m

)

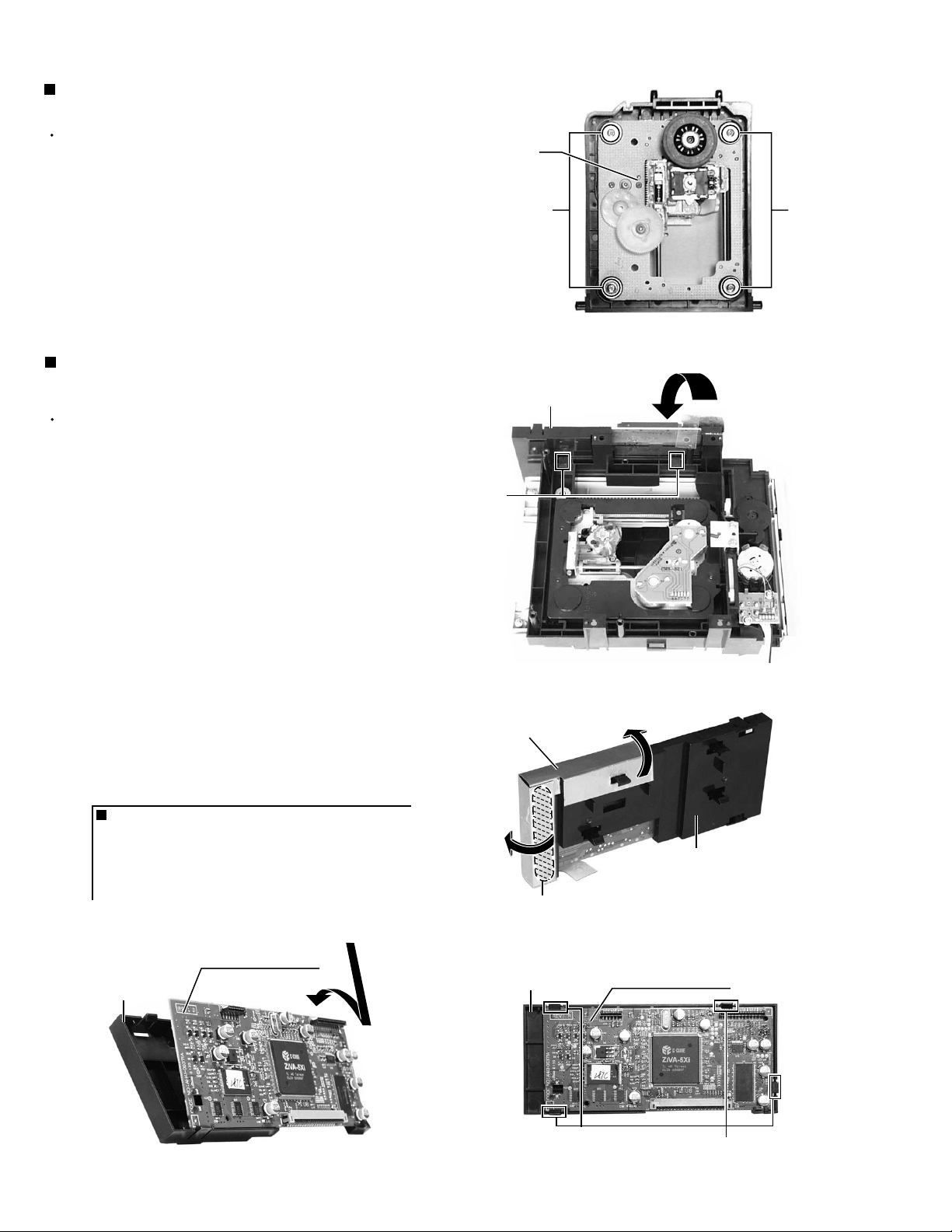

Removing the DVD traverse mechanism

(See Fig.5)

Prior to performing the following procedure, remove

the top cover, DVD mechanism assembly, DVD

loader board and DVD loading mechanism.

1.

Remove the four screws D attaching the DVD

traverse mechanism to DVD loading mechanism.

Removing the holder & DVD MPEG board

(See Fig.6 to 8)

Prior to performing the following procedure, remove

the top cover, DVD mechanism assembly and DVD

loader board.

1.

Remove the two claws1, and remove the holder from

the DVD mechanism assembly as it is pushed down.

DVD traverse

mechanism

Claw1

D

Holder

DVD loading mechanis

(top side

D

Fig.5

2.

Remove the shield cover from the holder.

3.

Remove the four claws2 and remove the DVD

MPEG board from the holder.

ONE POINT

When inserting DVD MPEG board in

holder. (see fig.9)

Insert in after uniting with a lower claws,

when inserting DVD MPEG board in holder.

DVD MPEG board

Holder

Shield cover

adhesive

couple-face tape

Holder

DVD mechanism assembly

Fig.6

Holder

(reverse side)

(bottom side)

Fig.7

DVD MPEG board

1-10

Fig.9

Claw2

Fig.8

Page 11

TH-A30

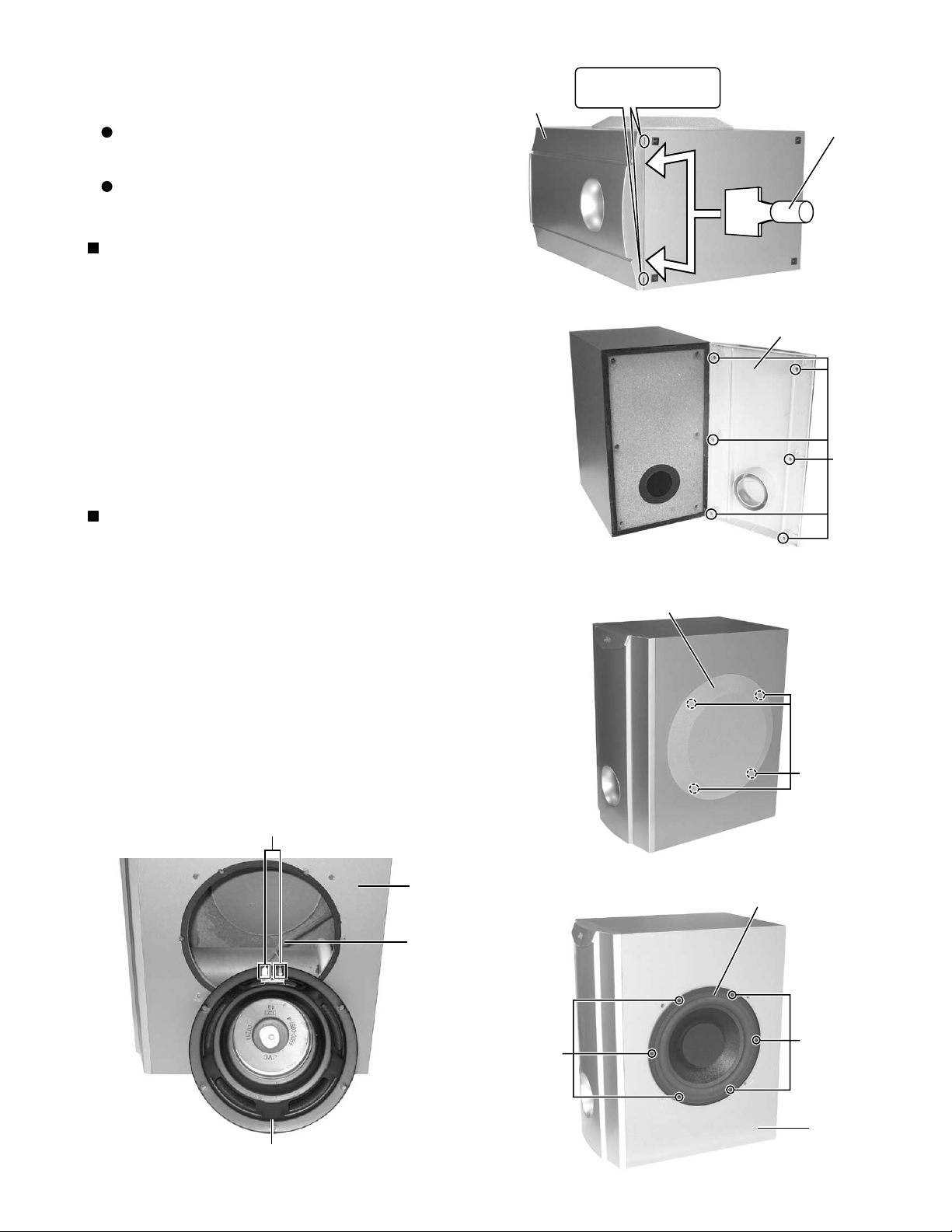

<Speaker section>

[SP-XA30 / Satellite speaker]

It is exchange in a unit.

[SP-XSA30 / Rear satellite speaker]

It is exchange in a unit.

[SP-WA30 / Subwoofer]

Removing the front panel

(See Fig.1 and 2)

1.

Remove the six bosses and remove the front panel.

Notes: It will be good to use the tool with a flat tip, since it

is hard to remove. Please take care not to damage the

cabinet at this time.

Removing the speaker unit

(See Fig.3 to 5)

1.

Remove the four bosses and remove the net

assembly.

Notes: It will be good to use the tool with a flat tip, since it

is hard to remove. Please take care not to damage the

cabinet at this time.

Front panel

One point

These slots are used.

Fig.1

Fig.2

Net assembly

Woofer (Bottom side)

The tool with

a flat tip

Front panel

(inner side)

Boss

2.

Remove the six screws A attaching the speaker unit

to the cabinet.

3.

Disconnect the code from the two terminals of the

speaker unit.

Terminals

Cabinet

Code

Speaker unit (reverse side)

Fig.5

A

Boss

Fig.3

Speaker unit

A

Cabinet

Fig.4

1-11

Page 12

TH-A30

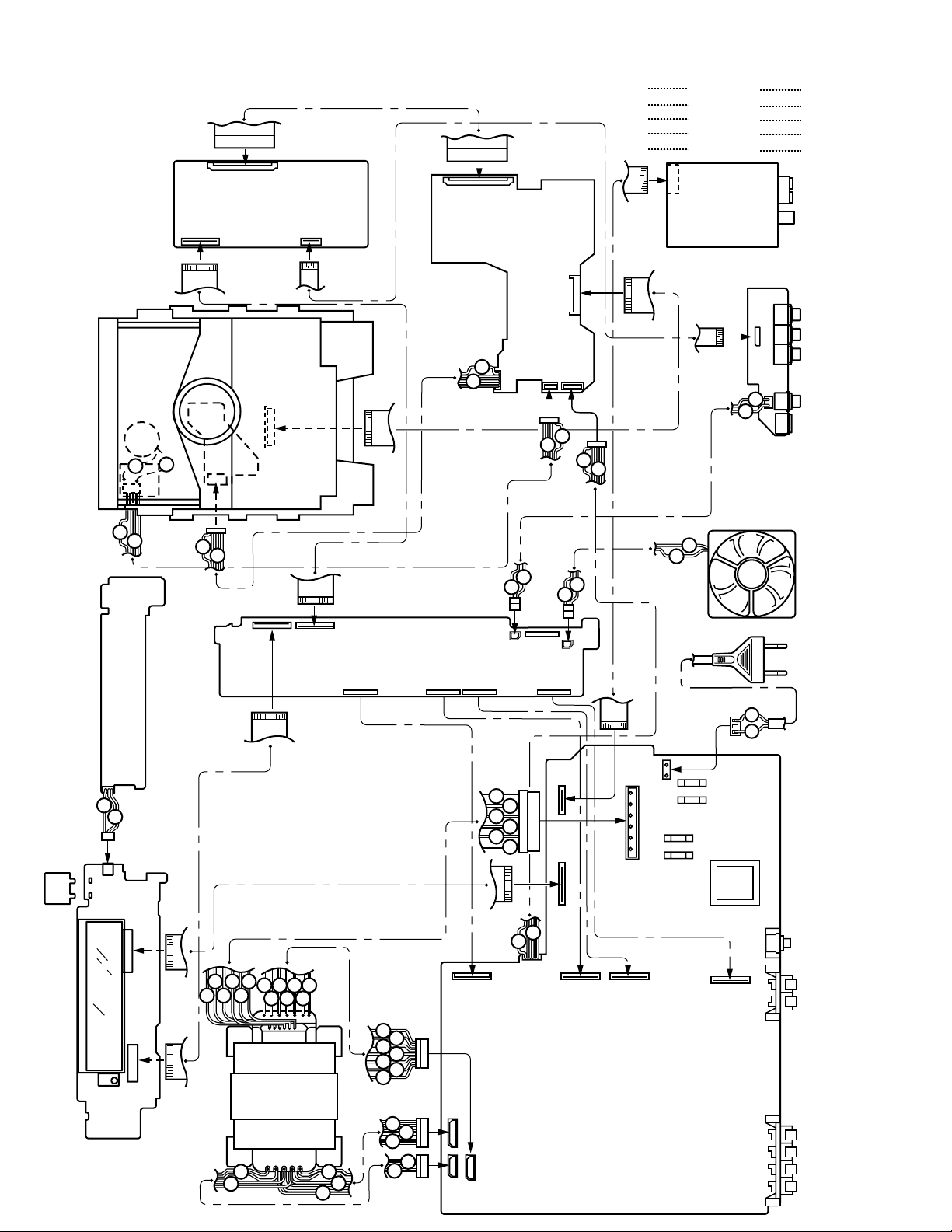

Wiring connection

J6

J14

2

0

0

9

SWITCH BOARD

0

9

J1

J21

J3

3809-001273

DVD MPEG

BOARD

DSP BOARD

J2

3809-001295

9

AH39-00368A

J7

DJ3

0

J5

3809-001305

DVD LOADER BOARD

MJ5

MJ4

9

0

4

J8

J10

J6

RCN1

DJ6

0

0

2

0

J9

Color codes are shown below.

1 Brown

2 Red

3 Orange

4 Yellow

5 Green

CON01

3809-001234

9

3809-001274

0

2

AH39-00291A

6 Blue

7 Violet

8 Gray

9 White

0 Black

TUNER PACK

VW2

J10-1

4

0

JACK BOARD (V-OUT)

1-12

FW3

AH39-00176A

0

FW2

DISPLAY BOARD

1

6

AFU1

3809-001335

9

3809-001334

FCW1

0

3

FCW2

8

2

9

POWER TRANCE

1

62305

4

6

4

1

1

6

0

5 32

4

2

9

0

1

0

9

2

6

9

2

4

PW3

ACW4

ACW3

ACW5

8

30

9

0

PW4

CW8

FCW1-1

CW7

MAIN BOARD

ACW1

ACW2

CW6

AFU2

AFU4

AFU3

PT1

CW5

Page 13

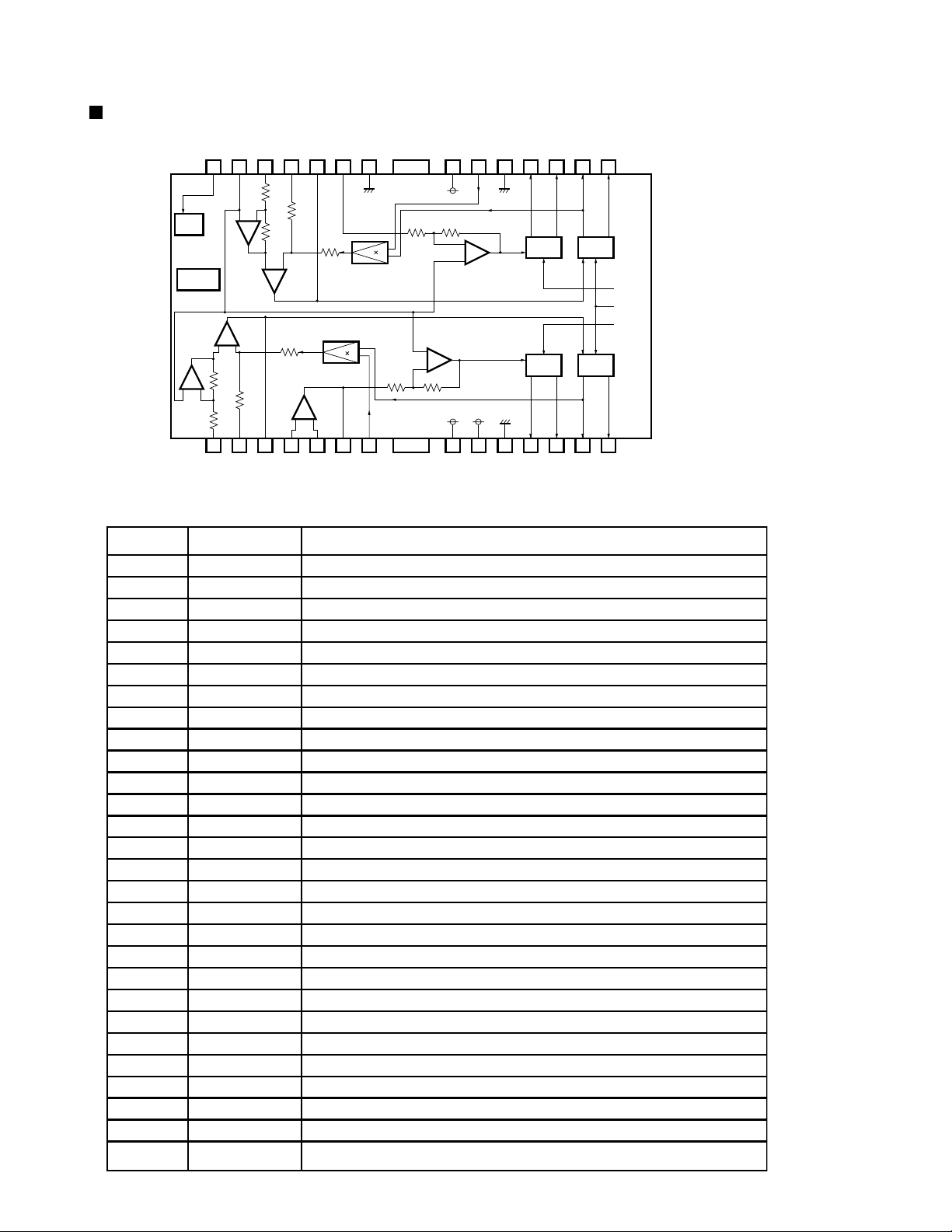

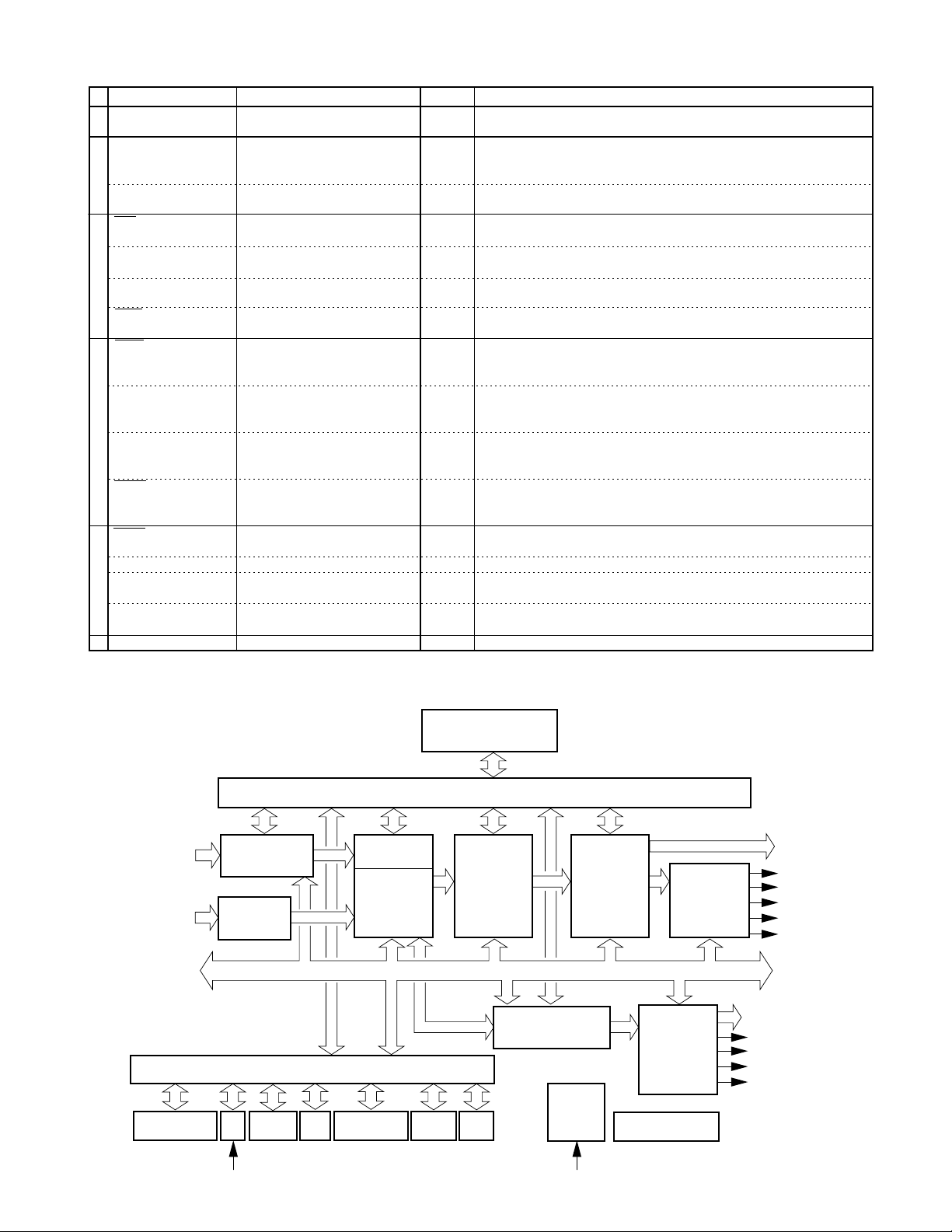

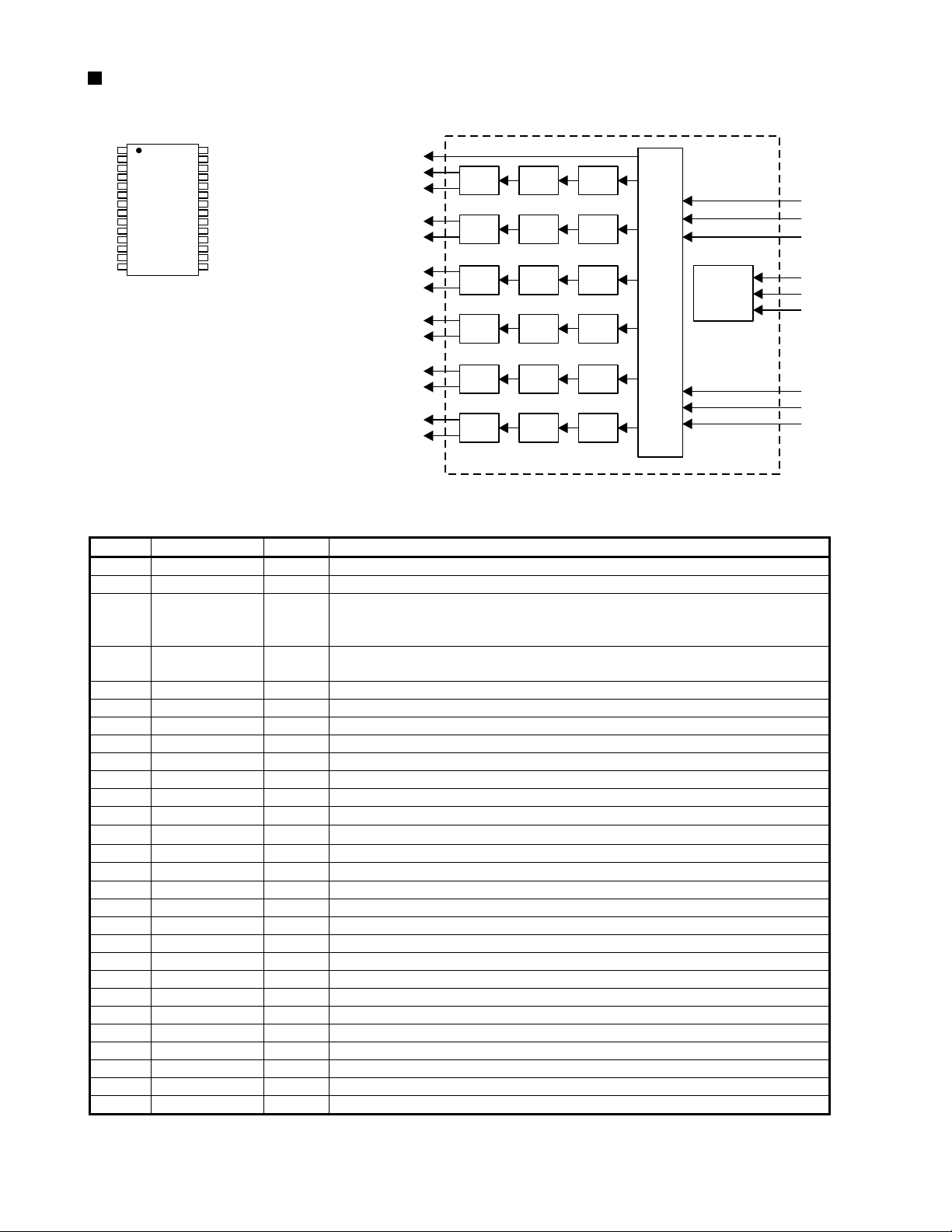

Description of major ICs

BA5954 (MU9) : Motor driver

1. Block diagram

TH-A30

STAND

SHUT DOWN

2. Pin function

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

-BY

THERMAL

-

+

28 2227 26

+

-

+

-

20k

7.5k

10k

1

Symbol

VINFC

CFCerr1

CFCerr2

VinSL +

VinSL -

VOSL

VNFFC

VCC

PVcc1

PGND

VOSL -

VOSL +

VOFC VOFC +

VOTK +

VOTK VOLD +

VOLD -

PGND

VNFTK

PVcc2

PreGND

VinLD

CTKerr2

CTKerr1

VinTK

BIAS

STBY

10k

20k

+

-

7.5k

3

25 24 23

7.5k

7.5k

DET.AMP.

-

+

4 5 6

PreGND

DET.AMP.

2

72

10k

2

10k 25k

21 1520 19

PVCC2

15k

+

-

V

CC

8 149 10

-

+

PVCC1

PGND

PGND

18 17 16

LOADING

DRIVER

SLED

DRIVER

11 12 13

ACTUATOR

DRIVER

ACTUATOR

DRIVER

Function

Focus driver input

Capacitor connection terminal for error amplifier filter

Capacitor connection terminal for error amplifier filter

Operational amplifier input for thread driver (+)

Operational amplifier input for thread driver (-)

Operational amplifier output for thread driver

Focal driver return terminal

Pre VCC, thread driver part power VCC

Power

Loading driver part power VCC

Thread driver part output (-)

Thread driver part output (+)

Focus driver part output (-)

Focus driver part output (+)

Tracking driver output (+)

Tracking driver output (-)

Loading driver output (+)

Loading driver output (-)

Power GND

Tracking driver return terminal

Actuator driver part power VCC

Pre GND

Loading driver input

Capacitor connection terminal for error amplifer filter

Capacitor connection terminal for error amplifer filter

Tracking driver input

Bias input

Standby terminal

PVCC1

PV

CC

V

CC

2

1-13

Page 14

TH-A30

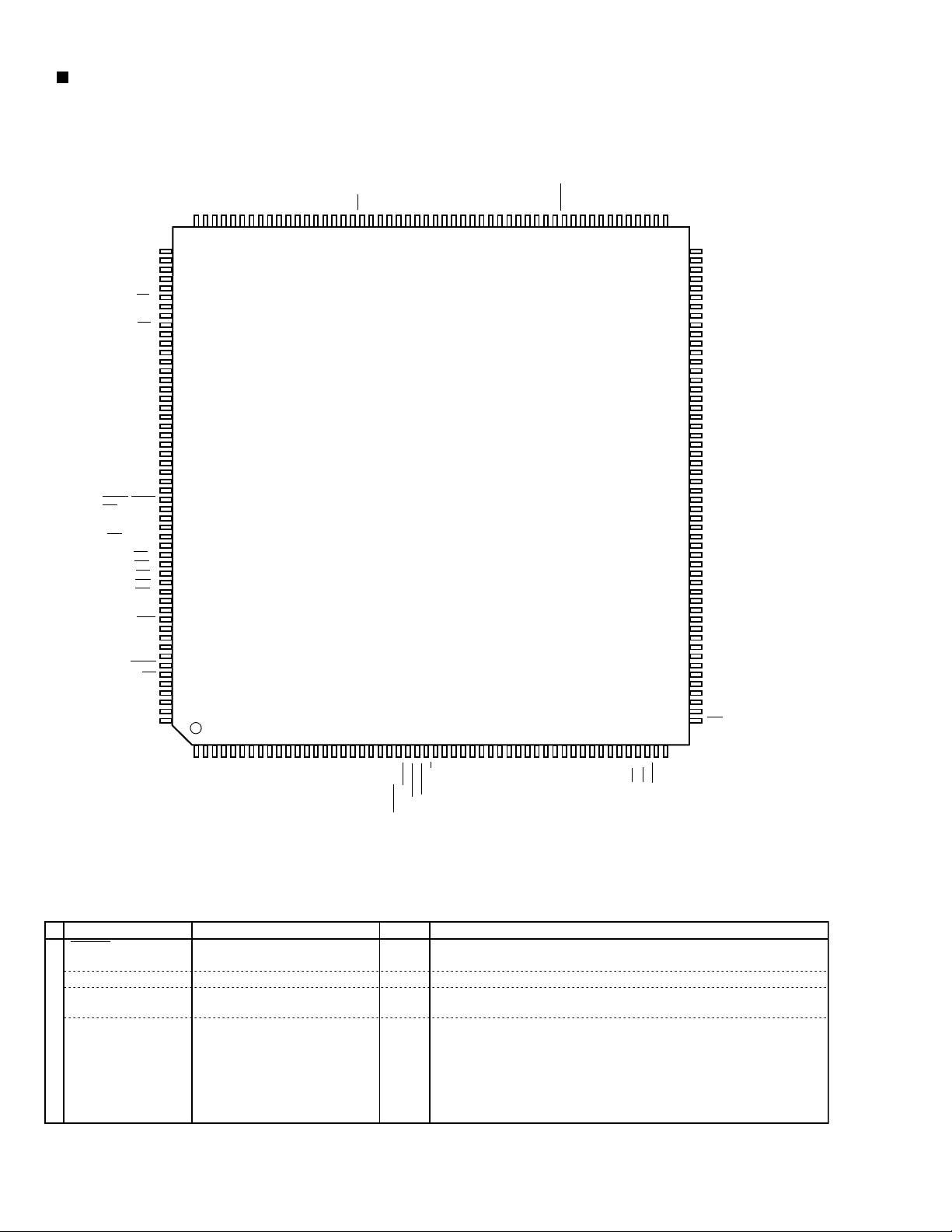

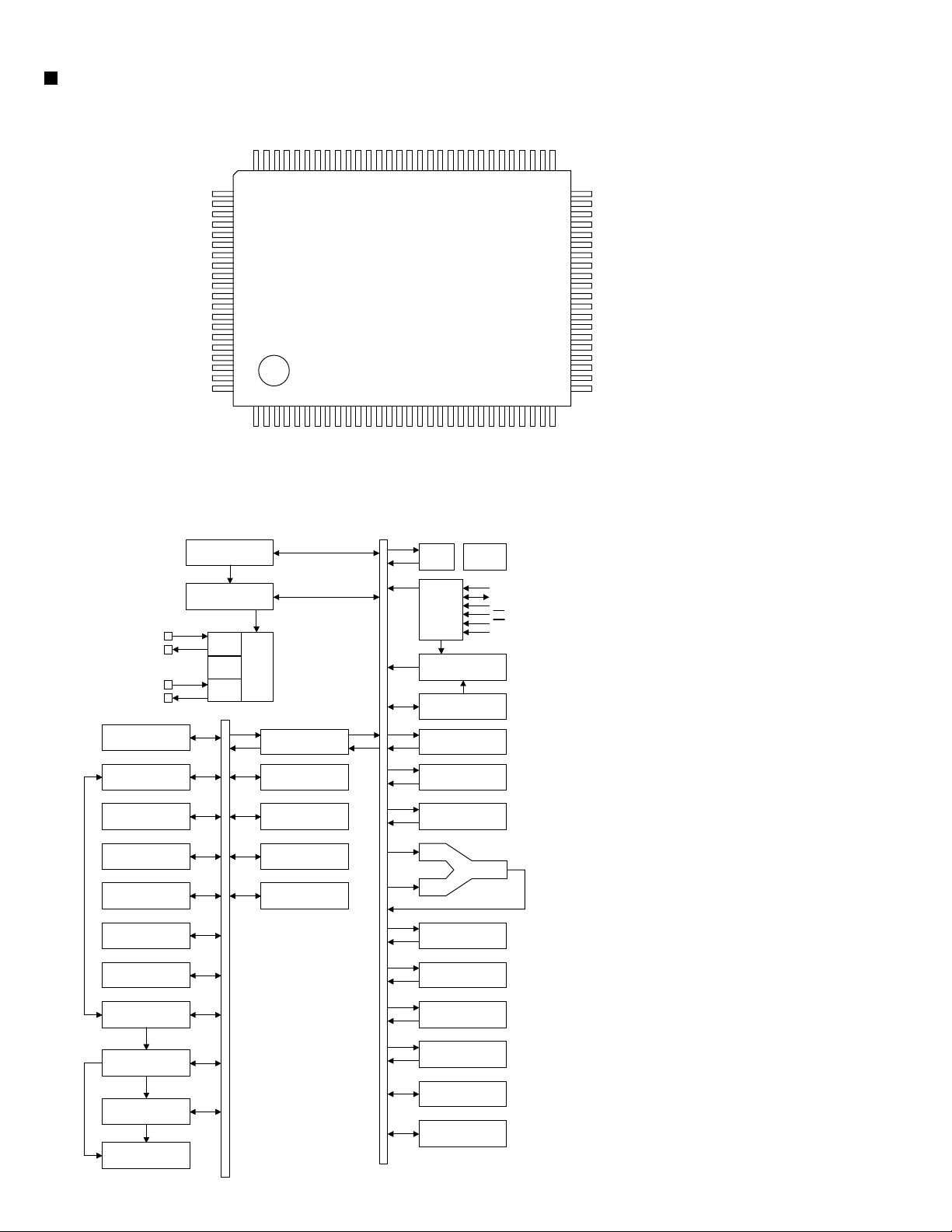

ZiVA-5 (U8) : DVD controller

1. Pin layout

DA-IEC958

DA-DATA3

DA-DATA2

156

155

154

2

C_CL

I

I

2

C_DA

RTS1

RXD1

TXD1

CTS1

VSS

VSS

VDDC

SD-EN

VSS

VDD_5

HCS4

HCS3

HCS2

HCS1

HCS0

VSS

TRST

TDO

TMS

TCK

RESET

ALE

VSS

VDDC

HAD3

HAD2

VSS

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

TDI

200

201

202

203

204

205

206

207

208

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

DAI-DATA

DAI-BCK/SYSCLKBP

DAI-LRCK/IEC958BP

VDD_3.3

SD-DATA7

SD-DATA6

SD-DATA5

SD-DATA4

SD-DATA3

SD-DATA2

SD-DATA1

SD-DATA0

SD-REQ

VDD_3.3

SD-ERROR

SD-CLK

VSYNC/HIRQ1

RTS2/SPI_CLK

RXD2/SPI_MISO

TXD2/SPI_MOSI

CTS2/SPI_CS

VDD_3.3

VSS

153

VDD_3.3

DA-DATA1

152

151

DA-DATA0

DA-BCK

DA-LRCK

150

149

148

DA-XCK

VSS

147

146

VDDC

145

A_VSS1

A_VDD1

144

143

A_VDD2

A_VSS2

142

141

XVDD

140

XTAL/VCLK216BP

XTAL

XVSS

VSS_RREF

VDAC_RREF

VDD_RREF

139

138

137

136

135

134

VDAC_DVDD

VDAC_DVSS

VDAC_0

VDAC_VDD0

133

132

131

130

VDAC_0B

VDAC_1

VDAC_VDD1

129

128

127

VDAC_1B

VDAC_2

VDAC_VDD2

126

125

124

VDAC_2B

VDAC_3

VDAC_VDD3

123

122

121

VDAC_3B

VDAC_4

VDAC_VDD4

120

119

118

VDAC_4B

HSYNC/IRQ2

VDATA0

117

116

115

VDATA1

VDATA2

114

113

VSS

112

VDD_3.3

VDATA3

111

110

109

VDATA4

VDATA5

VDATA6

108

107

VDATA7

VCLK

106

105

104

103

102

101

100

52

VDD_3.3

VSS

MDATA31

MDATA30

MDATA29

MDATA28

99

VDD_3.3

98

MDQM3

97

VSS

96

MDATA27

95

MDATA26

94

MDATA25

93

MDATA24

92

MDATA23

91

MDATA22

90

MDATA21

89

MDATA20

88

VDD_3.3

87

MDQM2

86

VSS

85

MDATA19

84

MDATA18

83

MDATA17

82

MDATA16

81

VDDC

80

VSS

79

MDATA15

78

MDATA14

77

MDATA13

76

MDATA12

75

VDD_3.3

74

MDQM1

73

VSS

72

MDATA11

71

MDATA10

70

MDATA9

69

MDATA8

68

MDATA7

67

MDATA6

66

MDATA5

65

MDATA4

64

VDD_3.3

63

MDQM0

62

VSS

61

MDATA3

60

MDATA2

59

MDATA1

58

MDATA0

57

MCLK

56

VDD_3.3

55

VSS

54

MWE

53

BA1

HA1

HAD15

VDD_3.3

HAD14

HAD13

HAD12

HAD11

HAD9

HAD10

HAD8

HAD7

VDD_3.3

VSS

HAD6

HAD5

HAD4

HAD3

HAD2

HAD1

VDD_3.3

VSS

HAD0

HDTACK/WAIT

HIRQ0

UDS/UWE

R/W

IRRX1

LDS/LWE

VSS

VDDC

VSS

VDD_3.3

MADDR9

MADDR8

MADDR7

MADDR6

MADDR5

MADDR4

MADDR3

MADDR2

MADDR1

MADDR0

VSS

VDD_3.3

MADDR10

MADDR11

BA0

MCS0

MCS1

MRAS

MCAS

2. Pin function (1/4)

1

Name

RESET

Pin No.

202

Description

Type

Active Low Reset. Assert for at least 5-milliseconds in the presence of

I

clock to reset the entire chip.

VCLK

XOUT

105

138

Video clock that outputs 27 MHz.

I/O

Crystal output. When the internal DCXO is used, a 13.5 MHz crystal

O

should be con-nected between this pin and the XIN pin.

XIN/bypass clk_216

139

Crystal input. When the internal DCXO is used, a 13.5 MHz crystal should

I

be con-nected between this pin and the XOUT pin. When an external

oscillator or VCXO is used, its output should be connected to this pin.

System Services

When configured for an external bypass clock, a 216 MHz clock should be

connected to this pin. The frequency of an external VCXO can be either 27

or 13.5 MHz.

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

1-14

Page 15

2. Pin function (2/4)

Name

VNW

VDDP

VDD25

XVDD

VDD

VDD_VDAC[4:0]

VDAC_DVDD

A_VDD[2:1]

VDAC_REFVDD

GNDP

GND

Power and GroundHost Interface

GND25

VDAC_DVSS

AVSS[2:1]

VDAC_REFVSS

XVSS

HCS[4:2]/GPIO[41:43]

HCS[1:0]

HA[3:1]

HA[15:0]

HDTACK/WAIT

HIRQ0

HUDS/UWE

HLDS/LWE

HREAD

ALE

MCS[1:0]

MCAS

MRAS

MDQM[3:0]

MA[11:0]

MD[31:0]

MWE

SDRAM Interface

MCLK

BA[1:0]

HSYNC/HIRQ2/

GPIO1[9]

VCLK

VDATA[7:0]/GPIO[1:7]

VSYNC/HIRQ1/

GPIO36

Digital Video Input/Output

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

12, 20, 111, 152, 167, 181, 196

32, 44, 55, 63, 74, 87, 98, 104

13, 21, 112, 153, 166, 180, 195, 208

31, 43, 54, 61, 72, 85, 96, 103

Pin No.

189

140

30, 80, 145, 173, 205

118, 121, 124, 127, 130

133

142, 143

134

29, 79, 146, 172, 204

132

141, 144

136

137

190-192

193, 192

206, 207, 2

3-11, 14-19, 22

23

24

25

26

27

203

50, 49

52

51

97, 86, 73, 62

46, 45, 33-42

102-99, 95-88, 84-81,

78-75, 71-64, 60-57

53

56

47, 48

116

105

106-110, 113-115

184

Type

Power

Power

Power

Power

Power

Power

Power

Ground

Ground

Ground

Ground

Ground

Ground

Ground

O

I

I/O

I/O

I/OD

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

I/O

O

O

O

I/O

I/O

I/O

I/O

1

Description

5-V supply voltage for 5V-tolerant I/O signals.

3.3-V supply voltage for I/O signals

3.3-V supply voltage for SDRAM I/O signals

3.3V Crystal interface power

1.8-V supply voltage for core logic

Analog Video DAC Power

3.3V Digital supply for 5 DACs

3.3-V Analog PLL Power

3.3V Analog Video Reference Voltage

Ground for I/O signals

Ground for core logic

Ground for SDRAM I/O signals

Digital VSS for DACs

Analog PLL Ground

Video Analog Ground

Crystal interface ground

Host chip select. Host asserts HCS to select the controller for a read or

write operation. The falling edge of this signal triggers the read or write

operation. General Purpose I/Os 41, 42, and 43, respectively.

Host chip select. Host asserts HCS to select the controller for a read or

write operation. The falling edge of this signal triggers the read or write

operation.

Host (muxed address) address bus. 3-bit address bus selects one of eight

host inter-face registers. These signals are not muxed in ATAPI master

mode.

HA[15:0] is the 16-bit (muxed address and data) bi-directional host data

bus through which the host writes data to the decoder Code FIFO. MSB of

the 32-bit word is writ-ten first. The host also reads and writes the decoder

internal registers and local SDRAM/ROM via HA[7:0]. These signals are

not muxed for ATAPI master mode.

Host Data Transfer Acknowledge.

Host interrupt. Open drain signal, must be pulled-up via 4.7k to 3.3 volts.

Driven high for 10 ns before tristate.

Host Upper Data Strobe. Host high byte data, HA[15:8], is valid when this

pin is active.

Host Lower Data Strobe. Host low byte data, HA[7:0], is valid when this pin

is active.

Read/write strobe

Address latch enable

Memory chip select.

Active LOW SDRAM Column Address Strobe.

Active LOW SDRAM Row Address Strobe.

These pins are the bytes masks corresponding to MD[7:0], [15:8], [23:16]

and [31:24]. They allow for byte reads/writes to SDRAM.

SDRAM Address

SDRAM Data

SDRAM Write Enable. Specifies transaction to SDRAM: read (=1) or

write (=0)

SDRAM Clock

SDRAM bank select

Horizontal sync. The decoder begins outputting pixel data for a new

horizontal line after the falling (active) edge of HSYNC.

Host Interrupt Request 2

General Purpose I/O 9

Video clock. Clocks out data on input. VDATA[7:0].

Clock is typically 27 MHz.

Video data bus. Byte serial CbYCrY data synchronous with VCLK. At

powerup, the decoder does not drive VDATA. During boot-up, the

decoder uses configuration parameters to drive or 3-state VDATA.

General Purpose I/Os [1:7]

Vertical sync. Bi-directional, the decoder outputs the top border of a new

field on the first HSYNC after the falling edge of VSYNC. VSYNC can

accept vertical synchroni-zation or top/bottom field notification from an

external source. (VSYNC HIGH = bot-tom field. VSYNC LOW = Top field)

Active Low Host Interrupt Pin

General Purpose I/O 36

TH-A30

1-15

Page 16

TH-A30

2. Pin function (3/4)

Name

SDDATA[7]/VDATA2[7]

/HDMARQ/GPIO24

SDDATA6/VDATA2[6]

/HXCVR_EN/GPIO25

SDDATA5/VDATA2[5]

HDMACK/GPIO26

SDDATA4/VDATA2[4]/

GPIO27

SDDATA3/

VDATA2[3]/GPIO28

SDDATA2/

VDATA2[2]/GPIO29

SDDATA1/

Parallel DVD/CD or Serial CD Interface

VDATA2[1]/GPIO30

SDDATA0/

VDATA2[0]/GPIO31

SDCLK

SDERROR

SDEN/GPIO33

SDREQ/GPIO32

VDAC_[4B:0B]

VDAC_4

VDAC_3V

DAC_2

VDAC_1

VDAC_0

VDAC_REF

VCLK

Analog Video OutputAudio InterfaceDigital Mic In

ADATA[3:0]/GPIO[4:1]

BCK

LRCK

XCK

IEC958/GPIO14

DAI_DATA/GPIO15

DAI_BCK/

BYPASS_SYSCLK/

GPIO16

DAI_LRCK/

IEC958BP/GPIO17

Pin No.

168

169

170

171

174

175

176

177

183

182

179

178

117, 120, 123, 126, 129

119

122

125

128

131

135

105

155, 154, 151, 150

149

148

147

156

157

158

159

Type

I

I

I

I

O

Analog O

Analog O

Analog O

Analog O

Analog O

Analog O

Analog I

I/O

O

O

O

I/O

O

I

I

I

1

Description

Compressed data from DVD DSP. Bit 7. In parallel mode, bit 7 is the first

(earliest in time) bit in the bitstream, while bit 0 is the last bit.

Video Data Bus 2, Bit 7

Host DMA Request

General Purpose I/O 24

Compressed data from DVD DSP. Bit 6.

Video Data Bus 2, Bit 6

ATAPI Transceiver Enable

General Purpose I/O 25

Compressed data from DVD DSP. Bit 5.

Video Data Bus 2, Bit 5

Host DMA Acknowledge

General Purpose I/O 26

Compressed data from DVD DSP. Bit 4.

Video Data Bus 2, Bit 4

General Purpose I/O 27

Compressed data from DVD DSP. Bit 3.

Video Data Bus 2, Bit 3

General Purpose I/O 28

Compressed data from DVD DSP. Bit 2.

Video Data Bus 2, Bit 2

General Purpose I/O 29

Compressed data from DVD DSP. Bit 1.

Video Data Bus 2, Bit 1

General Purpose I/O 30

In serial mode, bit 0 should be used as the input, with the unused bits

either used as GPIOs or tied to ground.

Video Data Bus 2, Bit 0

General Purpose I/O 31

Data clock. The maximum frequency is 25 MHz for parallel mode, and

???? MHz for serial mode. The polarity of this signal is programmable.

Error in input data. This signal carries the error bit associated with the

channel data type (if set, the byte is corrupted).

Data enable. Assertion indicates that data on SDDATA[7:0] is valid.

The polarity of this signal is programmable.

General Purpose I/O [33]

Bitstream request. controller asserts SDREQ to indicate that the bitstream

input buffer has available space.

General Purpose I/O 32

Video DAC Bias Bits[4:0]

DAC video output format: R, V, C, or CVBS. Macrovision encoded.

DAC video output format: B, U, C, or CVBS. Macrovision encoded.

DAC video output format: G or Y. Macrovision encoded.

DAC video output format: C. Macrovision encoded.

DAC video output format: CVBS or Y. Macrovision encoded.

Video DACs Reference Resistor. Connecting to pin 136 through

a 1.18K+/- 1% resis-tor is required.

System clock that drives internal PLLs. ZiVA-5 27-MHz TTL oscillator.

(See descrip-tion of VCLK for Digital Video Output.) Also optional video

clock for internal PLLs or external encoder.

PCM Data Out. Eight channels. Serial audio samples relative to BCK

and LRCK. General Purpose I/Os [4:1]

PCM Bit Clock. BCK can be either 48 or 32 times the sampling frequency

PCM Left Clock. Identifies the channel for each sample. The polarity is

programma-ble.

Audio External Frequency clock input or output. BCK and LRCK are

derived from this clock.

PCM data out (IEC-958 format ) or compressed data out

(IEC-1937 format). General Purpose I/O [14]

PCM data input.

General Purpose I/O [15]

PCM input bit clock.

BYPASS_SYSCLK: Alternate function TBS.

General Purpose I/O [16]

PCM left/right clock.

IEC958 input bypass

General Purpose I/O [17]

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

1-16

Page 17

2. Pin function (4/4)

Name

IRRX1/GPIO0

IR

IDC_CL/GPIO18

IDC

IDC_DA/GPIO19

RTS1/GPIO20

RXD1/GPIO21

TXD1/GPIO22

UART1UART2JTAG

CTS1/GPIO23

RTS2/SPI_CLK/

GPIO37

RXD2/SPI_MISO/

GPIO38

TXD2/SPI_MOSI/

GPIO39

CTS2/SPI_CS/

GPIO40

TRST

TDO

TDI/GPI0

TMS/GPI1

TCK

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

Pin No.

28

160

161

162

163

164

165

185

186

187

188

197

198

199

200

201

1

Type

Description

I

IR Remote Receive. This input connects to an integrated (photo diode,

band pass, demodulator) IR receiver. General Purpose I/O 0

I/O

Serial clock signal for IDC data transfer. It should be pulled up to the

positive supply voltage, depending on the device) using an external

pull-up resistor. General Purpose I/O [18]

Serial data signal for IDC data transfer. It should be pulled up to the supply

voltage using an external pull-up resistor. General Purpose I/O [19]

O

Ready to send, UART1

General Purpose I/O [20]

I

Receive data, UART1

General Purpose I/O [21]

O

Transmit data, UART1

General Purpose I/O [22]

I

Clear to send, UART1

General Purpose I/O [23]

O

Ready to send, UART2

Serial Peripheral Interface Clock

General Purpose I/O [37]

I

Receive data, UART2

Serial Peripheral Interface - Master Input/Slave Output

General Purpose I/O [38]

O

Transmit data, UART2

Serial Peripheral Interface - Master Output/Slave Input

General Purpose I/O [39]

I

Clear to send, UART2

Serial Peripheral Interface ????

General Purpose I/O [40]

I

Test reset. BST reset - resets the TAP controller.

This signal must be pulled low.

O

Test data Out. BST serial data output.

I

Test data In. BST serial data chain input.

General Purpose Input pin 0.

I

Test mode select. Controls state of test access port (TAP) controller.

General Purpose Input pin 1.

I

Test clock. Boundary scan test (BST) serial data clock.

TH-A30

3. Block diagram

Parallel/serial

DVD Interface

I2S Stereo In

32-128Mbit

SDRAM

SDRAM Controller

Track Buffer

Processor

Audio

Decryption

ZiVA

A/V Core

Graphics

Engine

Input Unit

System Control Bus

Bus Interface Unit

IR GPIO SPI UART1&2ASYNC BUS IDC

ATAPI

Interlaced/

Progressive

SPARC

Microprocessor

Phase

Lock

Loop

Video

Encoder

JTAG Interface

Five 10-bit

Audio

Output

Unit

Video

DACs

CCIR 656

Digital Video

Composite

Y/R

C

Cr/Pr/G

Cb/Pb/B

IEC 958/1937

Downmix

Left/right

Center/subwoofer

Left/ right/surround

Remote Control

13.5 MHz Crystal

1-17

Page 18

TH-A30

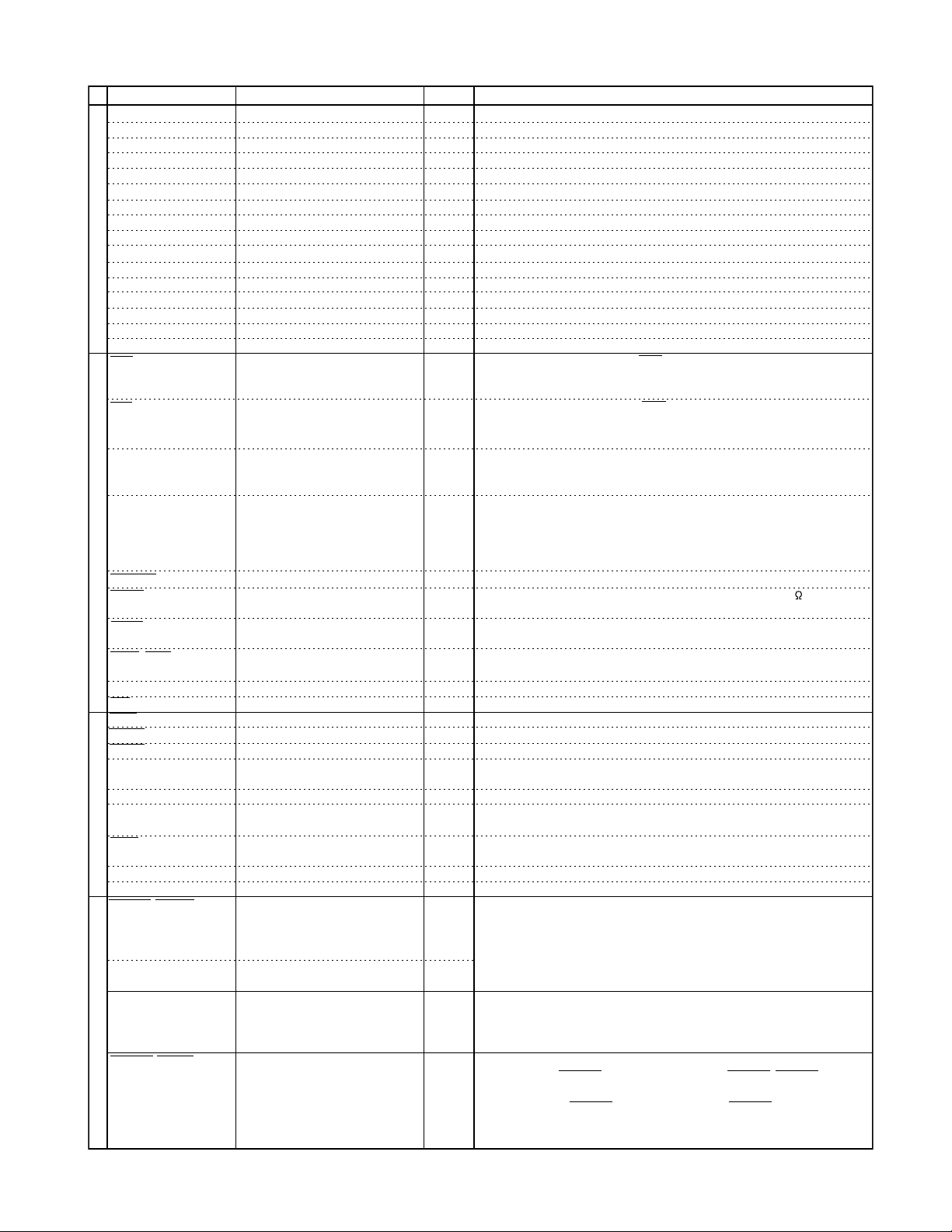

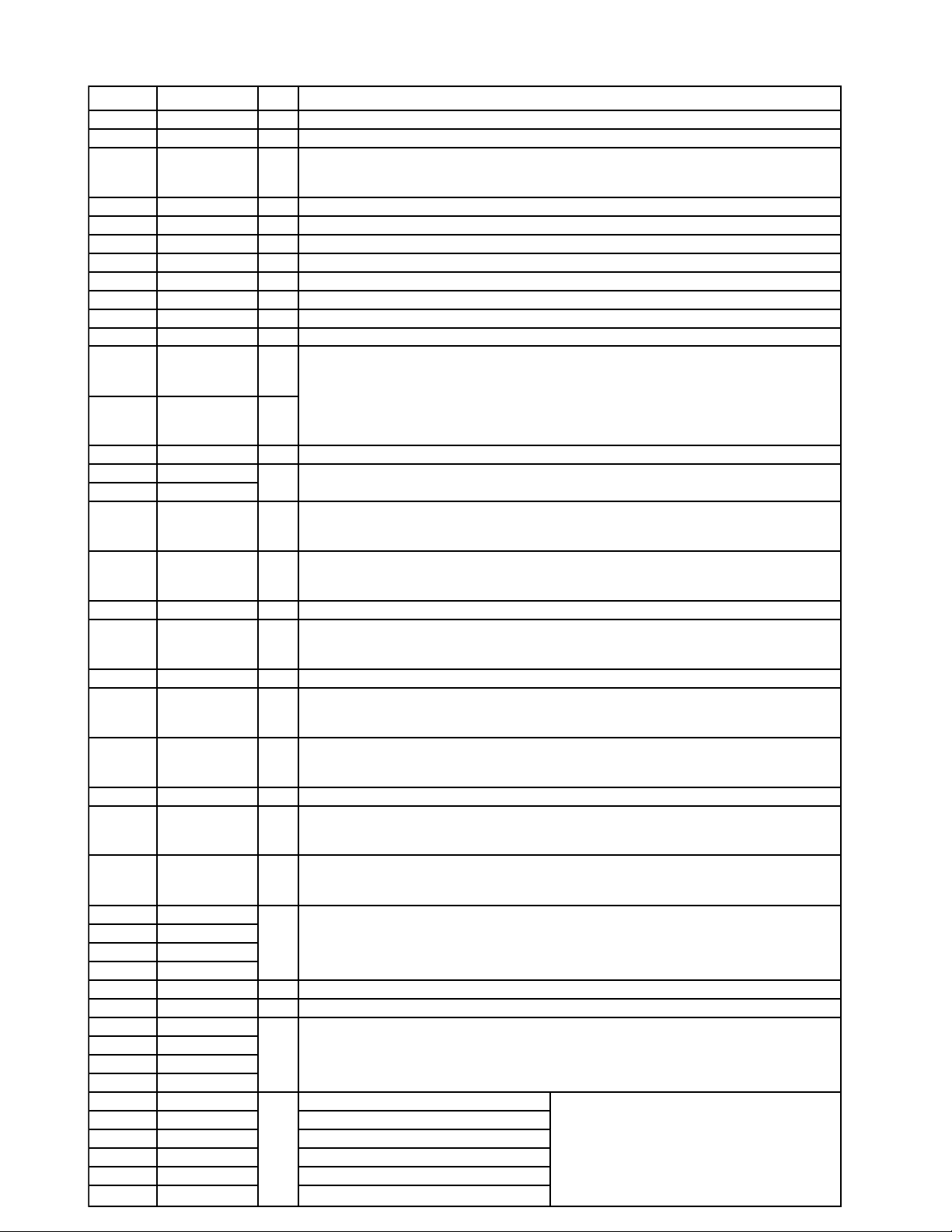

LC86P6548 (UIC1) : Microcontroller

1.Pin layout

S47/PF7

S46/PF6

S45/PF5

S44/PF4

S43/PF3

S42/PF2

S41/PF1

S40/PF0

VDD4

S39/PE7

S38/PE6

S37/PE5

S36/PE4

S35/PE3

S34/PE2

S33/PE1

S32/PE0

S31/PD7

S30/PD6

S29/PD5

S28/PD4

S27/PD3

S26/PD2

S25/PD1

S24/PD0

S23/PC7

S22/PC6

S21/PC5

S20/PC4

VP

2.Block diagram

S48/PG0

S49/PG1

S50/PG2

S51/PG3

P00

P01

P02

P03

VSS2

VDD2

P04

P05

P06

P07

P10/SO0

P11/SI0/SB0

P12/SCK0

P13/SO1

P14/SI1/SB1

P15/SCK1

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Interrupt Control

Standby Control

CF

RC

X’ta

l

8079787776757473727170696867666564636261605958575655545352

1234567891011121314151617181920212223242526272829

P30

P31

P32

P33

P34

P35

P36

P16/BUZ

P17/PWM0

Clock

Generator

P37

P70/INT0

RES

XT1/P74

CF1

VSS1

XT2/P75

CF2

VDD1

P80/AN0

IR

PLA

PROM

Control

PROM(48KB)

P81/AN1

P82/AN2

P83/AN3

PC

P84/AN4

P85/AN5

P86/AN6

A15-A0

D7-D0

TA

CE

OE

DAS

P87/AN7

P71/INT1

EC

P72/INT2/T0I

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

S0/T0

P72/INT3/T0I

S19/PC3

S18/PC2

S17/PC1

S16/PC0

VDD3

S15/T15

S14/T14

S13/T13

S12/T12

S11/T11

S10/T10

S9/T9

S8/T8

S7/T7

S6/T6

S5/T5

S4/T4

S3/T3

S2/T2

S1/T1

Base Time

SI

O0

O1

SI

Timer 0

er 1

Tim

ADC

INT0-3

Noise Filter

SIO Auto

transmissio

RAM

128 by

VFD

Controller

High voltage O

r

matic

s

te

utput

Bus Interface

n

Port 1

Port 3

Port 7

Port 8

ACC

B Register

C Register

PSW

RAR

RAM

Stack Poi nter

Port 0

Watchdog Timer

1-18

Page 19

3. Pin function

Pin No.

1

2

3

to

10

11

12

13

14

15

16

17

18

19

to

22

23

to

26

27

28

29

30

to

36

37

to

45

46

47

to

50

51

52

to

63

64

to

71

72

73

to

80

81

to

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

P16/BUZ

P17/PWM0

P70/INT0

XT1/P74

XT2/P75

P80/AN0

P83/AN3

P84/AN4

P87/AN7

P71/INT1

P72/INT2/T0I

P72/INT3/T0I

S15/T15

S16/PC0

P19/PC3

S20/PC4

S31/PD7

S32/PE0

S39/PE7

S40/PF0

S47/PF7

S48/PG0

S51/PG3

P10/SO0

P11/SI0/SB0

P12/SCK0

P13/SO1

P14/SI1/SB1

P15/SCK1

Symbol

P30

to

P37

RES

VSS1

CF1

CF2

VDD1

to

to

S0/T0

to

S6/T6

S7/T7

to

VDD3

to

VP

to

to

VDD4

to

to

P00

P01

P02

P03

VSS2

VDD2

P04

P05

P06

P07

Function

I/O

Buzzer output

I/O

Timer 1 output (PWM0 output)

I/O

8bit input/output port

I/O

Input/output in bit unit

15V withstand at N-channel open drain output

INT0 input /HOLD release/N-channel Tr. ouptput forwatchdog timer

I/O

Reset pin

I

32.768kHz crystal oscillation terminal XT1

I

32.768kHz crystal oscillation terminal XT2

I

Power pin (-)

Input pin for the ceramic resonator oscillation

I

Output pin for the ceramic resonator oscillation

O

Power pin (+)

4-bit input port

I

Input /output in bit unit

O

INT1 input/HOLD release input

I

INT2 input/timer 0 event input

I

Output for VFD display controller segment/timing incommon

O

Output for VFD dis;lay controller segment/timing withinternal pull-down

O

resistor in common

Internal pull-down resistor output

Power pin (+)

Output for VFD display controller

I/O

High voltage input port PC0 to PC3

Power pin (+) for the VFD output pull-down resist

Output for VFD display controller

I/O

High voltage input port PC4 to PC7, PD0 to PD7

Output for VFD displaya controller segment

I/O

High voltage input port PE0 to PE7

Power pin (+)

Output for VFD displaya controller segment

I/O

High voltage input port PF0 to PF7

Output for VFD displaya controller segment

I/O

High voltage I/O port PG0 to PG3

8-bit input/output port. Input for port0 interrupt.

I/O

Input/output in nibble unit

Input for HOLD release

15V withstand at N-channel open drain output

Power pin (-)

Power pin (+)

8-bit input/output port. Input for port0 interrupt.

I/O

Input/output in nibble unit

Input for HOLD release

15V withstand at N-channel open drain output

SIO0 data output

I/O

SIO0 data input/bus input/output

SIO0 clock input/output

SIO1 data output

SIO1 data input/bus input/output

SIO1 clock input/output

8-bit input/output port

Input/output can be specified in a bit unit

TH-A30

1-19

Page 20

TH-A30

SST39VF800A (U6) : 8M Flash memory

1. Pin layout

A15

A14

A13

A12

A11

A10

A9

A8

NC

NC

WE#

NC

NC

NC

NC

A18

A17

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

2. Block diagram

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

X-Decoder

A16

NC

Vss

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

VDD

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

Vss

CE#

A0

EEPROM

Cell Array

Memory Address

3. Pin function

Symbol

AMS- A0

DQ15- DQ0

Data Input/Output

CE#

OE#

WE#

VDD

Vss

NC

Address Buffer & Latches

CE#

OE#

WE#

Pin name

Address Inputs

Chip Enable

Output Enable

Write Enable

Power Supply

Ground

No Connection

Y-Decoder

Control Logic

I/O Buffers & Data Latches

DQ15-DQ0

Function

To provide memory addresses. During Sector-Erase AMS-A11 address lines will

select the sector. During Block-Erase AMS-A15 address lines will select the block.

To output data during Read cycles and receive input data during Write cycles. Data is

internally latched during a Write cycle. The outputs are in tri-state when OE# or CE# is

high.

To activate the device when CE# is low.

To gate the data output buffers.

To control the Write operations.

To provide power supply voltage: 2.7-3.6V

Unconnected pins.

1-20

Page 21

AK4355 (U6) : DAC

3

1.Pin layout 2.Block diagram

TH-A30

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

DZF

LOUT1+

LOUT1-

ROUT1+

ROUT1-

LOUT2+

LOUT2-

ROUT2+

ROUT2-

LOUT3+

LOUT3-

ROUT3+

ROUT3-

SCF

SCF

SCF

SCF

SCF DAC

SCF DAC

3.Pin function

Pin No. Symbol I/O Function

1 VREF I Positive Voltage Reference Input Pin

2DZF OZ

3 PDN I Power-Down Mode Pin

4 MCLK I Master Clock Input Pin

5 BICK I

6 SDTI1 I

7 SDTI2 I

8 SDTI3 I

9 LRCK I

10 CSN I C

11 CCLK I

12 CDTI I

13 DVDD - D

14 DVSS - D

15 ROUT3- O

16 ROUT3+ O

17 LOUT3- O

18 LOUT3+ O

19 ROUT2- O

20 ROUT2+ O

21 LOUT2- O

22 LOUT2+ O

23 ROUT1- O

24 ROUT1+ O

25 LOUT1- O

26 LOUT1+ O

27 AVSS 28 AVDD -

Note: All input pins should not be left floating.

ero Input Detect Pin

When at “L”, the AK4355 is in the power-down mode and is held in reset.

The AK4355 should always be reset upon power-up.

An external TTL clock should be input on this pin.

Audio Serial Data Clock Pin

DAC1 Audio Serial Data Input Pin

DAC2 Audio Serial Data Input Pin

DAC3 Audio Serial Data Input Pin

L/R Clock Pin

hip Select Pin

Control Clock Pin

Control Data Input Pin

igital Power Supply Pin

igital Ground Pin

DAC3 Rch Negative Analog Output Pin

DAC3 Rch Positive Analog Output Pin

DAC3 Lch Negative Analog Output Pin

DAC3 Lch Positive Analog Output Pin

DAC2 Rch Negative Analog Output Pin

DAC2 Rch Positive Analog Output Pin

DAC2 Lch Negative Analog Output Pin

DAC2 Lch Positive Analog Output Pin

DAC1 Rch Negative Analog Output Pin

DAC1 Rch Positive Analog Output Pin

DAC1 Lch Negative Analog Output Pin

DAC1 Lch Positive Analog Output Pin

Analog Ground Pin

Analog Power Supply Pin

DAC

DAC

DAC

DAC

DATT

DATT

DATT

DATT

DATT

DATT

Audio

I/F

Control

Register

MCLK

LRCK

BICK

CSN

CCLK

CDTI

SDTI1

SDTI2

SDTI

1-21

Page 22

TH-A30

M62463AFP (U11) : Surround decoder

1. Pin layout

RLC3

RLC7

RLC4

RLC1

RLC2

RLC5

PSC4

PSC1

PSC5

PSC2

48

47

46

45

44

43

42

41

40

39

PSC6

38

37

PSC3

DBC3

36

DBC2

35

34

DBC1

BNR IN

33

49

RLC8

50

RLC6

LT

RT

LIN

RIN

ABcc

VREF

IREF

NGC3

NGC2

NGC1

51

52

53

54

55

56

57

58

59

60

61

62

63

64

LBPF2

LBPF1

RBPF2

RBPF1

2. Block diagram

1 2 3 4 5 6 7 8 9

LOUT

ROUT

CVOLOUT

SOUT

COUT

CVOLIN

SVOLIN

SVOLOUT

10

CMC

11

AGND

VREFD

12

13

DVdd

MICIN

14

15

DATA

SCK

16

REQ

32

FBIN

31

LPF2 OUT

30

LPF2 IN2

29

LOF2 IN1

28

DAINT OUT

27

DAINT IN

26

DACONT

25

ADCONT

24

ADINT OUT

23

ADINT IN

22

LPF1 OUT

21

LPF1 IN2

20

LPF1 IN1

19

DSEL OUT

18

MICOUT

17

DVss

LIN

RIN

MICIN

57

58

12

L+R

2

SW6

L-R

1

2

NOISE

SEQUENCER

INPUT

BALANCE

SW4

1

2

3

4

MICVOL

MICOUT

ADAPTICVE

MATRIX

SELECTOR

S'

Digital Delay

10Kbit SRAM

LPF

A/D

SW5

Logic

F.B.VOL

CENTER

MODE

CONTROL

WIDE

NORMAL

PHANTOM

OFF

D/A

LPF

L

R

C

Modified BNR

PROLOGIC

PROLOGIC

SW3

BY-PASS

SPACE

SURROUND

SPACE

SURROUND

+

MUTE

BY-PASS

+/-

MUTE

MASTER

VOLUME

1

2

MASTER

VOLUME

MCU

Interface

DATA SCK REQ

SW1

2

3

2

3

SW2

161514333132201918

1

LOUT

1

4

1

ROUT

2

4

5

4

CVOLOUT

3

SVOLOUT

8

7

6

1-22

Page 23

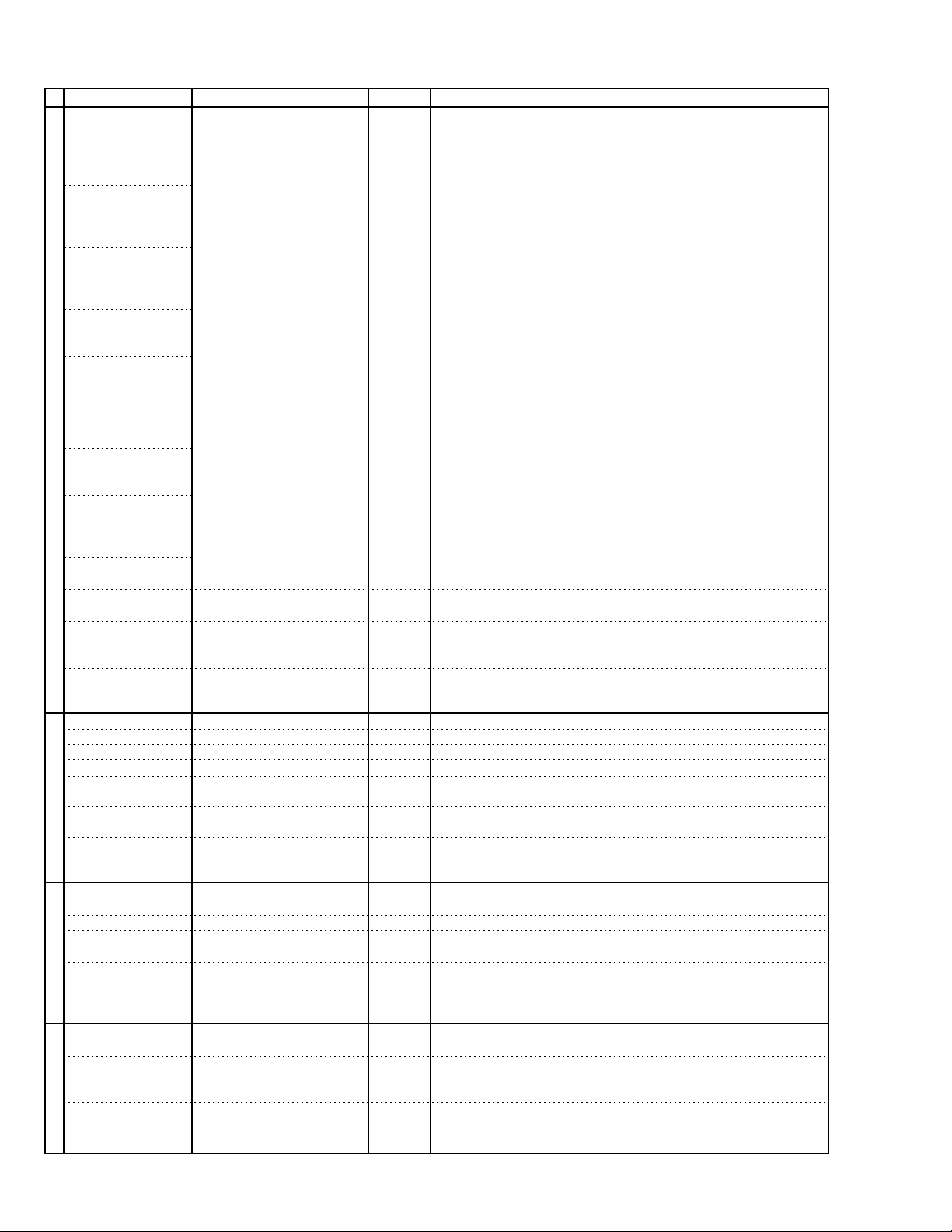

SP3721A (RU1) : DVD anlog front end chip

1.Pin layout

64-49

TH-A30

16-1

17-32

33-48

2.Pin function

Pin No.

1,2

3,4

5-8

9

10

11-14

15,16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51,52

53,54

55

56

57

58

59,60

61,62

63

64

Symblo

DVDRFP,VDVDRFN

PD1,PD2

A2,B2,C2,D2

CP

CN

A,B,C,D

E,F

CDTE

VCI2

NC

VNB

DVDPD

DVDLD

CDPD

CDLD

LDON#

VC

VCI

VPB

MIRR

MP

MB

FDCHG#

MLPF

MEVO

MIN

PI

DFT

TPH

MEV

MEI

TE

FE

CE

LCN

LCP

SCLK

SDATA

SDEN

HOLD1

VNA

FNP,FNN

DIP,DIN

RX

BYP

SIGO

VPA

AIP,AIN

ATOP/ATON

CDRF

CDRFDC

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

I/O

O

I/O

O

O

O

Function

RF Signal Inputs

I

CD Photodetector Interface Inputs

I

Photo Detector Interface Inputs

I

Differential Phase tracking LPF pin

Differential Phase tracking LPF pin

Photo Detector Interface Inputs

I

CD trackin Error Inputs

I

CD Tracking

Reference Voltage Input

No Connct

Ground

APC Input

I

APC ouput

APC Input

I

APC output

APC Output On/Off

I

Reference Voltage output

Reference Voltage Input

Power

Mirror Detect Output

MIRR signal Peak hold pin

MIRR signal Bottom hold pin

Low Impedance Enalle

I

MIRR signal LPF pin

SIGO Bottom Envelope Output

RF signal Input for Mirror

I

Pull-in Signal Output

Defect Output

PI Top Hold pin

Sigo Bottom Envelope pin

Mirror Envelope Input

I

Tracking Error Signal Output

Focusing Error Signal Output

Center Error Signal Output

Center Error LPF pin

Center Error LPF pin

Serial Clock

I

Serial Data

Serial Data Enable

I

Hold Control

I

Ground

Differential Normal Output

Analog inputs for RF Single Buffer

I

Reference Resistor Input

Single Ended Normal Output

Power

AGC Amplifier Inputs

I

Differential Attenuator Output

RF Signal Input

I

CD RF signal Output

1-23

Page 24

TH-A30

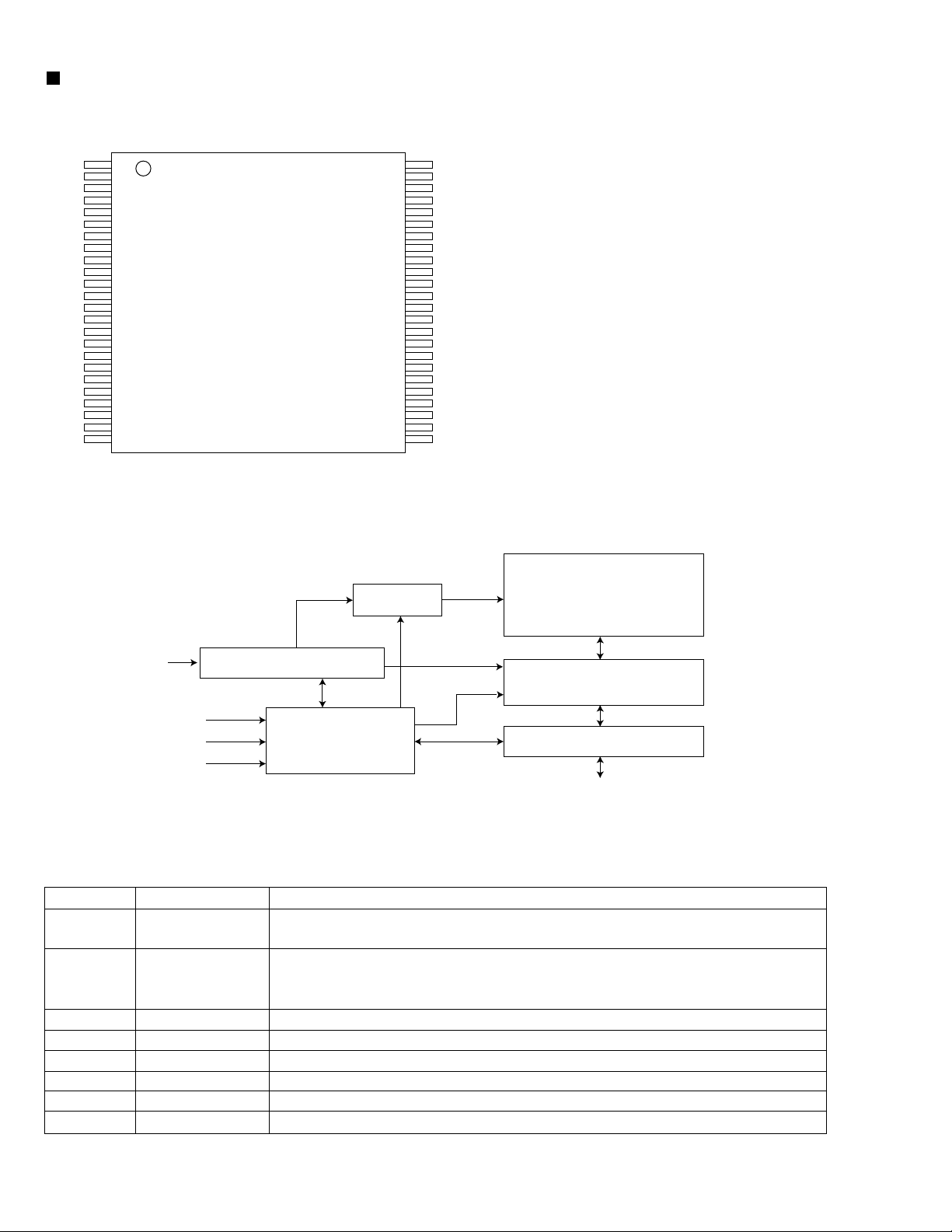

M12L64164A (AU13, AU14) : SDRAM

1.Pin layout

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

VDD

LDQM

CAS

RAS

A10/AP

VDD

WE

CS

A13

A12

A0

A1

A2

A3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

VSS

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

VSS

2.Pin function

Symbol

CLK

CS

CKE

A0 ~ A11

A12 , A13

RAS

CAS

WE

L(U)DQM

DQ0 ~ DQ15

VDD / VSS

VDDQ / VSSQ

NC

Function

System Clock

Chip Select

Clock Enable

Address

Bank Select Address

Row Address Strobe

Column Address Strobe

Write Enable

Data Input / Output Mask

Data Input / Output

Power Supply / Ground

Data Output Power / Ground

No Connection

3.Block diagram

CLK

CKE

Address

CS

RAS

CAS

WE

Clock

Generator

Bank

D

C

Bank

Bank

B

Row

Address

Mode

Regist

Buffer

er

&

Refresh

Counter

Row Decoder

Column

Address

Bank A

Sense Amplifie

Column Decod e

r

L(U)DQM

r

Buffer

&

Refresh

Control Logic

Counte

Command Decoder

r

Dat a Control Circui

t

Lat ch Circuit

Input & Output

DQ

Buffer

1-24

Page 25

TH-A30

BA4560 (AIC2, IC5, IC6, IC7, U1, U3, U5, U9, U13)

1.Pin layout

OUT1

– IN1

+ IN1

V

1

2

1ch

+

–

3

EE

4

2ch

+

V

CC

8

OUT2

7

– IN2

6

–

+ IN2

5

74LVT573 (U10, U11, U12) : Latch

OE

D0

D1

D2

D3

D4

D5

D6

D7

GND

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Vcc

O0

O1

O2

O3

O4

O5

O6

O7

LE

Symbol

D0-D7

LE

OE

O0-O7

Function

Data Inputs

Latch Enable Input

Output Enable Input

3-STATE Latch Outputs

: Dual op amp.

3. Truth table1. Pin layout 2. Pin function

H:HIGH Voltage Level

L:LOW Voltage Level

Z:High Impedance

X:Immaterial

O0:Previous O0 before HIGH to LOW transition of Latch Enable

Inputs Outputs

LE

X

H

H

L

OE

H

L

L

L

Dn

On

X

L

H

X

Z

L

H

O0

FAN8082 (U10) : DC motor driver

1.Pin layout

GND

1

V

O1

2

V

CTL

3

V

IN1

4

3. Pin function

12V

3V

4V

5V

6SV

7PV

8V

GND

O1

CTL

IN1

IN2

CC

CC

O2

V

8

PV

7

SV

5

V

6

I/O

O Output 1

I Motor speed control

I Input 1

I Input 2

- Supply voltage (Signal)

- Supply voltage (Power)

O Output 2

O2

CC

CC

IN2

Ground

2. Block diagram

GND

V

V

CTL

V

O1

IN1

1

2

DRIVER OUT

PRE DRIVER

3

4

TSD

LOGIC SWITCH

BIAS

8

V

O2

7

PV

CC

6

SV

CC

5

V

IN2

FunctionPin No. Symbol

1-25

Page 26

TH-A30

74HCT245 (U15) : Transceiver

1.Pin layout 2.Truth table

ENABLE

Vcc G B1 B2 B3 B4 B5 B6 B7 B8

20 19 18 17 16 15 14 13 12 11

1 2 3 4 5 6 7 8 9 10

DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

Control

G

LL

LH

H

H = HIGH Level

L = LOW Level

X = Irrelevant

Inputs

DIR 245

X

Operation

B data to A bus

A data to B bus

isolation

M5705 (DU3) : DVD-ROM controller

1.Block diagram

M5703/M5707

RF

Amp

M

Motor

Driver

Data

Separator

Digital

Servo

DVD-DSP

CD-DSP

4M DRAM

RAM

Arbiter

Target

Search

ATAPI

&

MPEG

I/F

C3 ECC

EDC

MCU

ROM

PC

MPEG

DEC.

1-26

Page 27

BA7612F (VIC3) : Video signal switcher

TH-A30

1. Block diagram

1

IN1

CTLA

CTLB

IN2

MUTE

2

LOGIC

3

4

8

V

OUT

75Ω6dB

7

CC

V

6

IN3

5

GND

2. Truth table

CTL A

L (OPEN)

L (OPEN)

HIN3

HHMUTE

TDA7440D (U2) : Audio processor

1. Terminal layout 2. Block diagram

4

RIN3

RIN2

RIN1

MUXO-L

IN(L)

MUXO-R

IN(R)

BIN(R)

BOUT(R)

BIN(L)

1

2

3

4

LIN1

5

LIN2 VS

6

LIN3

LIN4

7

8

9

10

11

12

13

14

28

RIN4

LOUT

27

ROUT

26

AGND

25

24

CREF

23

SDA

22

SCL

21

DGND

20

TRE(R)

19

18

TRE(L)

PS1

17

16

LP

BOUT(L)

15

LIN1

LIN2

LIN3

LIN4

RIN1

RIN2

RIN3

RIN4

100K

5

100K

6

100K

7

100K

3

100K

2

100K

1

100K

28

100K

CTL B

L (OPEN)

HIN2

L (OPEN)

MUXO-L IN(L)

8 9 18 14

G

0/30dB

2dB STEP

G

INPUT MULTIPLEXER

+ GAIN

VOLUME

VOLUME

10 11 19 12 13 23

MUXO-R IN(R)

OUT

IN1

TRE(L)

TREBLE

I2CBUS DECODER + LATCHES

TREBLE

TRE(R)

BIN(L)

BASS

BASS

R

B

R

B

BOUT(L)

15

BOUT(R)BIN(R)

SPKR ATT

LEFT

SPKR ATT

RIGHT

V

REF

SUPPLY

CREF

27

LOUT

21

SCL

22

SDA

20

DGND

26

ROUT

24

VS

25

AGND

W29EE512 (DU5) : Flash memory

1. Pin layout

4 3 2 1 32 31 30

5

A7

6

A6

7

A5

8

A4

9

A3

10

A2

11

A1

12

A0

13

DQ0

14 15 16 17 18 19 20

A12

A15NCNC

DQ1

DQ2

GND

VccWENC

DQ3

DQ4

DQ5

29

28

27

26

25

24

23

22

21

DQ6

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

2. Block diagram

V

DD

Vss

CS

OE

WE

A0

A15

CONTROL

DECODER

OUTPUT

BUFFER

CORE

ARRY

DQ0

DQ7

3. Pin function

Symbol

A0~A15

DQ0~DQ7

CE

OE

WE

Vcc

GND

NC

Function

Address input

Data I/O

Chip enable

Output enable

Write enable

Power

Ground

No connect

1-27

Page 28

TH-A30

TDA7449L (U7, U12) : Audio processor

1.Pin layout 2.Block diagram

CREF

PGND

ROUT

LOUT

R_IN2

R_IN1

L_IN1

L_IN2

MUXOUT(L) 10 MUXOUT(R)

1

2

V

S

3

4

5

6

7

8

9 N.C.

SDA20

SCL

19

DIG_GND

18

N.C.

17

N.C.

16

N.C.

15

N.C.

14

N.C.

13

12

11

L-IN1

L-IN2

R-IN1

R-IN2

8

100K

9

100K

7

100K

6

100K

G

0/30dB

2dB STEP

G

INPUT MULTIPLEXER

+ GAIN

MUXOUTL

10

VOLUME

I2CBUS DECODER + LATCHES

VOLUME

11 1

MUXOUTR

SPKR ATT

LEFT

SPKR ATT

RIGHT

V

REF

SUPPLY

CREF

5

19

20

18

4

2

3

LOUT

SCL

SDA

DIG_GND

ROUT

V

S

AGND

D98AU868

TL3472 (RU2) : Op. amp.

1.Pin layout

V

CC±

1OUT

1IN±

1IN+

/GND

1

2

3

4

8

7

6

5

V

CC+

2OUT

2IN±

2IN+

1-28

Page 29

< MEMO >

TH-A30

1-29

Page 30

TH-A30

VICTOR COMPANY OF JAPAN, LIMITED

AUDIO & COMMUNICATION BUSINESS DIVISION

PERSONAL & MOBILE NETWORK BUSINESS UNIT. 10-1,1chome,Ohwatari-machi,Maebashi-city,371-8543,Japan

(No.21172)

Printed in Japan

200212

Page 31

SCHEMATIC DIAGRAMS

DVD DIGITAL CINEMA SYSTEM

Area suffix

TH-A30

STANDBY/ON

AUDIO

VCR

TV

TV/VIDEO PROGRESSIVE

TV CHANNEL

DISPLAY

STEP

AUDIO/

SUBTITLE

TV VOLUME

FM MODE

DVD FM/AM AUX

TUNER PRESET

DOWN UP

REW

VCR CHANNEL

TUNING

B.SEARCH F.SEARCH

ENTER

VOLUME

TOP MENU

MENU

RETURN

RM-STHA30U

DVD CINEMA SYSTEM

TH-A30

US -------------- Singapore

UB ------------- Hong Kong

CD-ROM No.SML200212

UW -- Brazil,Mexico,Peru

UG - Turkey,South Africa,

Egypt

A ------------------ Australia

SP-XSA30 2

VCR

CONTROL

FF

MUTING

STANDB

Y

STANDBY/ON

AUDIO/FM MOD

D

SP

E

V

OLUME

SOURCE

DVD DIGITAL CINEMA

XV-THA30 SP-WA30

SP-XA30 3

SYSTEM TH-A

30

DIGITAL

Contents

Block diagrams

Standard schematic diagrams

Printed circuit boards

COPYRIGHT 2002 VICTOR COMPANY OF JAPAN, LTD.

2-1

2-2

2-6~10

No.21172SCH

Dec. 2002

Page 32

TH-A30

In regard with component parts appearing on the silk-screen pr inted side (par ts side) of

the PWB diagrams, the parts that are printed over with black such as the resistor ( ),

diode ( ) and ICP ( ) or identified by the " " mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

Page 33

TH-A30

Block diagrams

Main section

TUNER

VFD

FCW2

J1 CW8

DVD mecha block section

Front L-ch

6

(35W)

AUX1

L

R

IC5

POWER

AMP.

Front R-ch

6

(35W)

CW5

J6

Center

6

(35W)

IC7

POWER

U13

Sub Woofer

4

(110W)

AMP.

Rear L-ch

6

(35W)

IC6

POWER

J5

AMP.

CW6

Rear R-ch

6

(35W)

Main

Parallel/Serial

DVD Interface

416C256

4M DRAM

DU3

DVD ROM CONTROLLER

M5701/ M5705

M6759

MICOM

&

ATAPI

BCA

I/F

MPEG

RAM

DATA

SEPARATOR

C3 ECC

ARBITER

DVD-D SP

EDP

MCU I/F

TARGET

CD-DSP

DIGITAL

SEARCH

SERVO

64M SDRAM

W986432DH-7

SWITCHING

BUFFER

Analog

Video

Output

VIDEO OUT

BA7612

BUFFER

SIGNAL

KSA812

(Refer to "Main section.")

Audio

AMP PARTS

Output

(Refer to "Main section.")

U8

MPEG DECODER

ZIVA5

S-VIDEO

S_VIDEO_Y/C

UIC1

MICOM

COMPONENT OUT

VIDEO

VIC3

VIDEO SW

VIDEO_Y1,U,Y

VIDEO_COMPO

VW2

Front

V Signal

U11

PROLOGIC IC

Phase

JTAG

Interface

Lock

Loop

13.5MHZ Crystal

DACs

Digital Video

RL

U7

FUNCTION IC

RR

ERROR