Page 1

SCHEMATIC DIAGRAMS

DVD DIGITAL THEATER SYSTEM

TH-A25

CD-ROM No.SML200403

SOUND

DVD DIGITAL CINEMA

SYSTEM TH-A

STANDBY

STANDBY/ON

Since the printed circuit board of DVD was changed, the schematic diagram

and printed circuit boad which were changed are published.

25

SOURCE

VOLUME

Area suffix

J ----------------------------- U.S.A.

C -------------------------- Canada

Contents

Standard schematic diagrams ---------------------------------- 2-1

Printed circuit board ----------------------------------------------- 2-5

COPYRIGHT 2004 VICTOR COMPANY OF JAPAN, LTD.

No.MB141BSCH

2004/3

Page 2

In regard with component parts appearing on the silk-screen printed side (parts side) of

the PWB diagrams, the parts that are printed over with black such as the resistor ( ),

diode ( ) and ICP ( ) or identified by the " " mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

Page 3

8

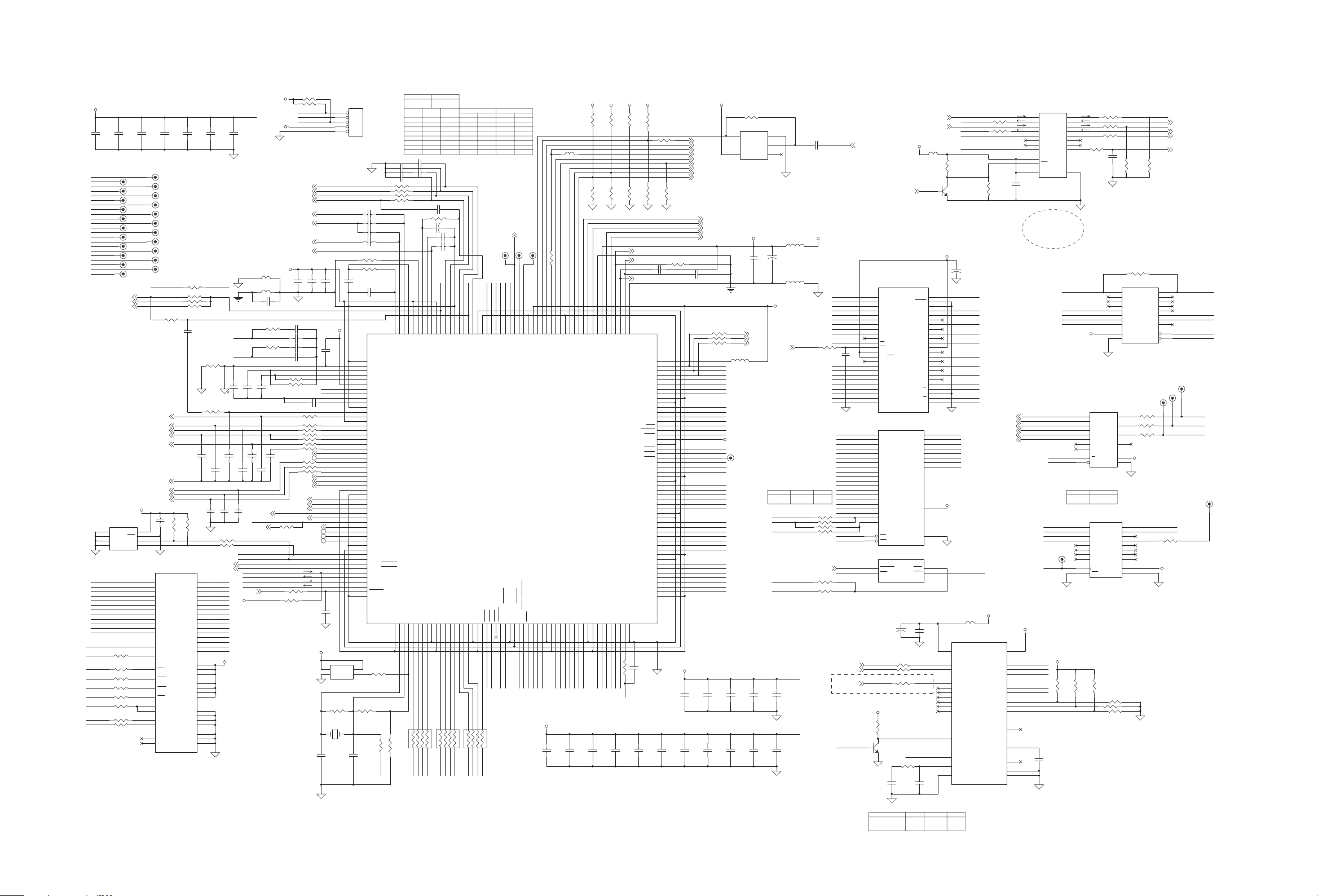

Standard schematic diagrams

SDRAM (MIC7)

VCC33

PIN 1 PIN 3 PIN 9 PIN 14 PIN 27 PIN 43 PIN 49

BC2

BC1

0.1U

SBAD

XFLAG0

XFLAG1

XFLAG2

XFLAG3

RFO

TESTAD

DA

RFRP

DIP

DIN

TRACK

FOCUS

SLEGP

SLEGN

SPINDLE

MIRR

TEI

FEI

CEI

SPDON

SFGIN

1

2

3

4 5

EGND

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

DSCK

DOE#

CS0#

RAS0#

CAS#

DWE#

DQM

RAS1#

RAS2#

BEFR_OP2

ATR_OP2

MIC6

S0

S1

S2

GND SDA

MR67 33

MR69 33

MR71 33

MR72 33

MR73 33

MR76 33

MR77 33

MR78 33

0.1U

MIRR2

24C02A

TP1

FLAG0

TP3

FLAG2

TP5

RFO

TP7

DA

TP9

DIP

TP11

STRACK

TP13

SSLEGP

TP18

SSPINDLE

TP20

TEI

TP22

CEI

TP24

FGIN

VCC33

VCC

WC

SCL

BC3

0.1U

SPINDLE3

SVREF152

8

7

6

23

24

25

26

29

30

31

32

33

34

22

35

38

37

19

18

17

16

15

39

20

21

36

40

BC4

0.1U

TP32

SBAD

TP2

FLAG1

TP4

FLAG3

TP6

TESTAD

TP8

RFRP

TP10

DIN

TP12

SFOCUS

TP14

SSLEGN

TP19

MIRR

TP21

FEI

TP23

XSPDON

MR22 0

MR26 0

MR27 R

MR28 R

MR30 33K

OPEN

OPEN3

SPINDLE

FOCUS

FOCUS3

SLEGN

SLEGN3

TRACK

TRACK3

SVREF15

SCSJ

SCSJ2

SDATA

SDATA2

SCLK

SCLK2

BC8

MR49

0.1U

1K

EGND

MIC8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

CLK

CKE

CS

RAS

CAS

WE

DQML

DQMH

BA0

BA1

NC

NC

4Mx16 SDRAM (9ns)

VCCQ

VCCQ

VCCQ

VCCQ

VSSQ

VSSQ

VSSQ

VSSQ

DECOUPLING CAPACITORS

BC6

BC5

0.1U

0.1U

MIRRASVREF15

RFRP

TESTAD

MC24

1U

MR32 0(2012)

PLLGND

RFGND

MR25 0

MC32

0.015U

MC36

0.22U

MC39

33P

MR50

1K

RFGND

MR55 33

MR56 33

HSYNC4

VSYNC4

DB0

2

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

VCC

VCC

VCC

VSS

VSS

VSS

DB1

4

DB2

5

DB3

7

DB4

8

DB5

10

DB6

11

DB7

13

DB8

42

DB9

44

DB10

45

DB11

47

DB12

48

DB13

50

DB14

51

DB15

53

VCC33

1

14

27

3

9

43

49

6

12

46

52

28

41

54

EGND

MC40

33P

EGND

MC33

C

EGND

MGND

MC28

0.1U

MIRRA

A5V

BC7

0.1U

TR1

TR2

MC41

33P

AUX0

AUX1

RESET#4

MC37

560P

AUX4

AUX5

AUX6

AUX7

L25 CIC21

L23 L

C30 C

MC29

47P

MC34

560P

OUTSW3

RS232_DET

MOCTL2

VCC33

A5V

EGND

RS232 CONNECTOR 2.54MM

RF33V

MR29 R

MR31 1.2K

MR33 10K

MR34 5.1K

MC30

0.1U

DA

MC35

0.015U

MC38

0.1U

HOMESW3

MR53

RESET#

MR89 100

MR59 4.7K(OPEN)

RR1 4.7K(SD)

RR2 4.7K(SD)

STXD

RS232_DET

SRXD

SBAD2

FEI2

CEI2

TEI2

DIP2

RFO2

DIN2

SVREF212

MC17

MC18

0.1U

0.1U

RFGND

MC22

C

MC23

C

MC25

0.047U

MC27

560P

MC31

0.1U

MR38 6.8K

MR39 6.8K

MR40 6.8K

MR41 R

MR42 5.1K

MR43 6.8K

MR44 6.8K

SFGIN3

SPHOI

MR45 33

MR46 33

MR47 33

SDEFCT2

SLDC2

SPDON3

INSW3

CLOSE3

DVD/CD2

FR3

0

GPIO2

GPIO1

GPIO0

HSYNC

MC47

0.1U

VCC33

EGND

MC45

24P

EGND

SBAD

FEI

CEI

TEI

DIP

RFO

DIN

SVREF21

MC19

0.1U

PLL33V

MC26

0.1U

TR1

TR2

SLEGP

SFGIN

1

XSCSJ

XSDATA

XSCLK

DEFCT

SLDC

SPDON

FR

1

1

1

EGND

1

2

GNQ

X1 33.33MHZ(DA)

MR74 100K

X2

27MHz

MC20

C

V

JJ1(SD)

SERVO MCU

1

2

DEBUG

3

HEADER

4

5

RFGND

MC8

4700P

MC9

C

MC11

C

MC13

4700P

MR19 68K

MR21 20K

MC21

6800P

157

AVSS_DS

158

AVSS_PL

159

XSPDOFTR1

160

XSFDO

161

XSFTROPI

162

AVDD3_PL

163

XSPLLFTR1

164

XSPLLFTR2

165

XSVREF0

166

XSAWRC

167

AVSS_DA

168

XSRFRPCTR

169

XSTRAY

170

AVDD3_DA

171

XSSPINDLE

172

XSFOCUS

173

XSSLEGP

174

XSSLEGN

175

XSTRACK

176

XSTESTDA

177

XSFGIN

178

XSPHOI

179

SXCSJ

180

XSDATA

181

XSCLK

182

XSDFCT

183

XSLDC

184

XSSPDON

185

VD33

186

VS33

187

XGPIO[9]

188

XGPIO[8]

189

XGPIO[7]

190

XGPIO[6]

191

XGPIO[5]

192

XGPIO[4]

193

XGPIO[3]

194

XGPIO[2]

195

XGPIO[1]

196

XGPIO[0]

197

VSS

198

VDD

199

AUX0

200

AUX1

201

AUX2/ HSYNC

202

AUX3/ VSYNC

203

AUX4

204

AUX5

205

AUX6

206

AUX7

207

RESET

208

VS33

4

3

MR70

MR75

33(OPEN)

100(DVI)

MR65

MC44

27P

PLL3(pin124)

CLK SOURCE

CRSTAL OSC

1

DCLK INPUT

0

PLL2

PLL1

PLL0

MULTI

139

XSTEXI

Frequency

114.75

4.5

5

bypass

4

4.25

4.75

5.5

6

137

138

VSS

VDD

121.5

NA

135

27

NA

101.25

108

121.5

114.75

NA

128.25

94.5

148.5

108

162

3

DRV

TP16

TP15

SRXD

STXD

XFLAG2

XFLAG1

XFLAG3

XFLAG0

129

130

131

132

133

134

135

136

XSLG

XSIP2

XSIP1

XSWBL

XSFLAG[0]

XSFLAG[1]

XSFLAG[2]

XSFLAG[3]

ML4 CIM10

MCLKMCL

TP17

MR60 33

UDAC1

TSD1

TSD3

TBCK

TWS

TSD2

TSD0

115

116

117

118

119

120

121

122

123

124

125

126

127

128

VS33

XSWBLCLK

VS33

VD33

TSD2

TSD3

TBCK

MCLK

SPDIFIN

TWS/SEL_PLL2

TSD0/SEL_PLL0

TSD1/SEL_PLL1

SPDIF/SEL_PLL3

TWS

0

0

0

0

1

1

1

1

MC4

1000P

MC6

1000P

MR10 3.3K

MR11 3.3K

MR16 3.3K

MR17 3.3K

152

153

154

155

156

XSIPIN

XSRFIP

XSRFIN

XSDSSLV

TSD1

0

0

1

1

0

0

1

1

MC3

1000P

MC5

1000P

MR18 10K

MC10 10U/16V

SVREF21

SVREF09

SVREF15

148

149

150

151

XSIREF

AVDD3_DS

XSVREF[21]

XSVREF[09]

XSVREF[15]

TSD0

DEFAULT S-CHIP DEFAULT S-CHIP

0

4.25

1

reserved

bypass

0

1

3.75

4.5

0

reserved

1

3.5

0

1

4

MC7

0.1U

MC12

1U

MC14

1U

RFRP

TESTAD

140

141

142

143

144

145

146

147

XSFEI

XSTEI

XSCEI

XSSBAD

XSRFRP

AVSS_AD

AVDD3_AD

XSTESTAD

ES66x8

VD33

XIN

XOUT

DCLK

DMA0

DMA1

DMA2

DMA3

VS33

VD33

DMA4

DMA5

DMA6

DMA7

DMA8

DMA9

DMA10

VS33

VD33

DMA11

DCAS

DCS0

DCS1

DRAS0

DBANK0/ DRAS1

VSS

VDD

DBANK1/ DRAS2

DCKE/DOE/TDMTSC

DWE

DB0

DB1

DB2

VS33

VD33

DB3

DB4

DB5

DB6

DB7

BC14

0.1U

DB15

DB3

DB5

DB7

DB4

DB6

DB15

DB14

BC15

0.1U

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

33(DA)

DCLK_DVI

XOUT

DCLK

XIN

DMA5

DMA2

DMA3

DMA0

DMA1

DMA6

DMA4

4.7K

MR94

RN1 10x4

1 8

2 7

3 6

4 5

1 8

2 7

3 6

MA1

MA6

MA4

MA0

MA2

MA5

MA3

CAS#

RAS0#

CS0#

DMA7

DMA11

DMA8

DMA10

DMA9

10x4

RN3

RN2 10x4

1 8

2 7

3 6

4 5

4 5

MA10

MA11

MA7

MA8

MA9

DB1

DB2

DB0

DWE#

RAS1#

RAS2#

DOE#

VCC33

CDAC1

114

YUV0/UDAC

DB14

MR4

MR12

YDAC1

113

YUV2/CDAC

VS33

YUV5/YDAC

VD33

GNDV

112

VS33_DA

DB13

DB13

BC16

0.1U

1.2K(OPEN)

1.2K

VCC33V

111

DB12

EGND

VDAC1

110

VD33_DA

DB12

DB11

MR5

MR13

FDAC1

109

YUV7/FDAC

YUV6/VDAC

DB11

DB10

DB10

1.2K(OPEN)

1.2K

EGND

COMP

DATA1

RSET

106

107

108

YUV4/RSET

YUV3/COMP

RBCK/TDMCLK

DB9

DB8

MR66 33

DB8

DB9

DSCK

BC17

0.1U

VCC33VCC33 VCC33

VCC33

MR6

MR7

1.2K(OPEN)

MR91 0(OPEN)

1.2K

MR14

MR15

RSET 4

DATA1 4

MC15 0.1U

DATA3 4

VS33_PL2

MIC4

105

VS33_PL

YUV1/VREF

VD33_PLL

RWS/TDMFS

RSD/TDMDR

LD7

LD6

LD5

LD4

VD33

VS33

LD3

LD2

LD1

LD0

LOE

LWRLL

LCS3

VDD

VSS

LCS2

LCS1

LCS0

LA0

LA1

LA2

VD33

VS33

LA3

LA4

LA5

LA6

LA7

LA8

VDD

VSS

LA9

LA10

LA11

LA12

LA13

LA14

LA15

VD33

VS33

LA16

LA17

LA18

LA19

LA20

LA21

DQM

VD33

DSCK

VS33

52

MC50

27P

BC18

0.1U

1.2K(OPEN)

1.2K

1.2K

MR84

EGNDEGNDEGND

UDAC

CDAC

YDAC

VDAC

5DAC

MR20 390

MC16 0.1U

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

EGND

BC19

0.1U

VCC20

SPDIF

TBCK 4

MCLK 4

MCLK_DIR

TSD3 4

TSD2 4

TSD1 4

TSD0 4

TWS 4

BC9

0.1U

BC20

0.1U

VCC33

UDAC 4

CDAC 4

YDAC 4

VDAC 4

5DAC 4

R5 R

R6 R

R4 R

VD33_PL1

TDMFS

TDMCLK

TDMDR

LD7

LD6

LD5

LD4

LD3

LD2

LD1

LD0

LOE#

WRLL#

LCS3#

LCS2#

LCS1#

LCS0

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LA18

LA19

LA20

LA21

DQM

BC10

0.1U

BC21

0.1U

MR61 100K(OPEN)

MQ1

5

VCC

TC7S04F(OPEN)

VCC33V

C2

0.1U

VGND

TWS 4

TBCK 4

RSD 4

ML2

CIC21

VCC20

TP49

BC11

0.1U

BC22

0.1U

RXD

RXD4

DQ15/A_1

MIC5

CLK/CE1

VCC

GND

A5V

BYTE

GND

DQ14

DQ13

DQ12

DQ11

DQ10

GND

D0

D1

D2

D3

D4

D5

D6

D7

ACK4

ML1

CIC21

Q2

1

R1103(OPEN)

2 3

VCC33

48

A16

47

46

45

44

DQ7

43

42

DQ6

41

40

DQ5

39

38

DQ4

37

VCC

36

35

DQ3

34

33

DQ2

32

DQ9

31

DQ1

30

DQ8

29

DQ0

28

G

27

26

E

EGND

LD0

13

LD1

14

LD2

15

LD3

17

LD4

18

LD5

19

LD6

20

LD7

21

A5V

32

16

EGND

34

GNDOUT

2

IN A

1

NC

RESET#4

INSTALL

R51, R54

R48, R52

WRLL#

LA18

LA19

LA20

LCS2#

EGND

C1

100U/6.3V

VCC33

L1CIC21

L2

CIC21

MC42

0.047U(OPEN)

VCC33

12

12

EGND

RESET#

MR90 100

TYPE

REMOVE

EPROM

R48, R52

FLASH

R51, R54

MR48 OPEN

MR51 0(EM)

MR52 OPEN

MR54 0(EM)

RESET#4

MR57 0(EM)

MR58 OPEN

SPDIF_IN

LA16

LA15

LA14

LA13

LA12

LA11

LA10

LA9

LA20

WRLL#

LA19

LA18

LA8

LA7

LA5

LA4

LA3

LA2

RESET#

WRLL#

EGND

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LA13

LA14

LA15

LA16

LA17

LCS3#

LOE#

SPDIF_IN 4

MC48

0.1U

RESET#4

MIC3

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

NC

10

NC

11

W

12

RP

13

VPP

14

DU/WP

15

NC

16

NC

17

A17

18

A7

19

A6

20

A5

21

A4

22

A3

23

A2

24 25

A1 A0

A29L160

12

A0

11

A1

10

A2

9

A3

8

A4

7

A5

6

A6

5

A7

27

A8

26

A9

23

A10

25

A11

4

A12

28

A13

29

A14

3

A15

2

A16

30

A17

31

A18

1

A19

22

CE

24

OE

27C040/080-90(EM)

MIC7

1 4

RESET

2 3

WE ADDR/CE1

ROM EMULATOR SOCKET

AUX5

ACK

AUX7

DCLK_DVI

SPDIF

MR95

10K(OPEN)

47U/6.3V(OPEN)

EGND

LA17

LA0

LD7

LD6

LD5

LD4

LD3

LD2

LD1

LD0LA6

LOE#

LCS3#

LA1

LA21

PC4

MR2 100

MR68 100

MR96

0

MC2

0.1U

SPSYNC

TWS4

SPCLK

TBCK4

SPDAT

RSD4

MIC1

2

A1

3

A2

4

A3

5

A4

6

A5

7

A6

8

A7

9

A8

1

DIR

19

OE

20

GND

+5V

74HCT245

ACK : AUX6

TXD : AUX7

RXD : AUX4

STB : AUX5

MCLK LINE SHIELD

ANASYNC

SPCLK

ANACLK

SPDAT

ANDAT

SELECT0

SELECT1

DVD DRIVE EXPANSION

LD0

LD1

LD2

LD3

LCS1#

MR1 1K

18

B1

17

TP38

B2

B3

B4

B5

B6

B7

B8

MR3 1K

16

15

MR8 100

14

13

12

MR9 33(OPEN)

11

MC1

47P(OPEN)

10

EGND

EGND

MCLK_DIR SPMCLK

LD4

LD5 EMPH

LD6

LD7

VCC33

SELECT0

HIGH

LOW

EGND

18

16

14

12

20

10

EGND

U17

2

1A

1Y

3

1B

5

2A

2Y

6

2B

11

3Y

3A

10

3B

14

4A

4Y

13

4B

1

A/B

VCC33

15

G

EGND

74LVX157

AUDIO

SPDIF

ANALOG

OPIC3

3

Q1

D1

4

Q2

D2

7

Q3

D3

8

Q4

D4

13

Q5

D5

14

Q6

D6

17

Q7

D7

18

Q8

D8

11

CLK

PL33

1 10

OE

GND

74LVX374

9

7

5

3

MR92

2.7K(OPEN)

OPIC2

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

PL33

GND

4

7

9

12

16

8

EGND

2

5

6

9

12

15

16

19

20

R40

33(OPEN)

74LVX244

R105 33

R106 33

R107 33

VCC33

SELECT0

SELECT1

CCLK

AUX4

STB

AUX6

TXD

MR93

2.7K(OPEN)

2

1A1

4

1A2

6

1A3

8

1A4

11

2A1

13

2A2

15

2A3

17

2A4

1

1G

19

2G

RWS

33(OPEN)

EGND

TDMCLK

R57

VCC33

STB 4

TXD 4

DVICLK 4

OPT_OUT 4

TDMDR

ERR

SELECT0

LCS1#

TDMFSSPSYNC

TDMCLK

TDMDR

EAUX40

TP4

4-PIN EXTENSION FOR ROM EMULATOR INTERFACE

A5V

BC12

0.1U

BC23

0.1U

EGND

EGND

BC13

0.1U

BC24

0.1U

SPDIF_IN4

SELECT1

AUX0

AUX1

GND_SHIELD

AUX0

AUX1

VCC33

1

2 3

EGND

PLL LOCK TIMS

60ms(Z VER)

35ms(R VER)

PRODUCTION

C38

47U/6.3V

R44 33

R45 33

R47 33

R55

1K

Q1

R1103

EGND

ASL1

6

1

28

4

12

13

14

15

26

9

11

8

7

CR

2.2nF

47nF

4.7nF

CIC21

VA+

SDA/CDOUT

SCL/CCLK

RXP0

RXP1

RXP2

RXP3

RXP4

RXP6

RST

RERR

FILT

AGND

OPIC1

AD1/CDINRXP5

CS8415A - SOIC

CS8415A-CS

C56

0.1U

EGND

RXP0SPDIF_IN

SPRST

ERR

1.2K

R58

C58

C59

0.1U

4700P

CF

RF

0.47uF

0.4K

0.1uF

1.2K

0.047uF

3K

OLRCK

OSCLK

SDOUT

RMCK

OMCK

AD0/CS

EMPH

RXN0

DGND

VCC33

23

VL+

17

16

18

10

21

2

2725

3

19

INT

5

20

U

24

H/S

22

SPSYNC

SPCLK

SPDAT

SPMCLK

MCLK_DIR

AD0

AD1

EMPH

EGND

C57

0.01U

VCC33

R48

R49

4.7K

R50

4.7K

R51 4.7K(OPEN)

R53 4.7K(OPEN)

R54 4.7K(OPEN)

EGND

4.7K

2-1

Page 4

DCN1

SW

NC

DVD_LD

DVD_PD

DVD_VR

VCC

VREF

GND

F

E

A

B

C

RF

D

NC-

CD_LD

CD_PD

CD_VR

GND

T+

F+

FT-

*P/U PIN

HEADER-SMD_24P-0.5m/m_AN_BL

RCN1

24

E

23

D

22

A

21

RF

20

B

19

C

18

F

17

VCC

16

VREF

15

GND

14

T+

13

T-

12

F+

11

F-

TP41

TP

RL1

CIM10

RL2

CIM10

GND

DVDLD

DVDVR

DVDPD

GND

CDLD

CDVR

CDPD

VCC

2SB1197

CDD1

TP43

TP

TP42

TP

RQ5

2SB1197

CDD1

10

9

8

7

6

5

4

3

2

1

RR28

10(2012)

RQ1

RR36

10(2012)

BODY_GND

SMD_24P_FFC_AN_1M/M_DC

DVDLDO

CDLDO

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

RF50V

RF50V

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

RFGND

RFGND

23

RR42

47K

23

RR40

220_DC

1

RR43

47K

1

E

D

A

PUHRF

B

C

F

TRACK+

TRACKFOCUS+

FOCUS-

RC21

100U/6.3V

RC26

1000P

RC27

100U/6.3V

RC28

1000P

SW1(CD/DVD)

DVDLDO

DVDPD

DVDVR

A,B,C,D,E,F, LINE

TRACK+ 3

TRACK- 3

FOCUS+ 3

FOCUS- 3

DVDLDO

DVDPD

CDLDO

CDPD

RR41

560_DC

TP39

TP

RR32

1K

RD1

1

B

3

C

2

B

DAP202K

TP40

TP

RR37

1K

CDLD

F

E

A

B

C

PUHRF

D

CDLDO

CDPD

CDVR

TRACK+

FOCUS+

FOCUSTRACK-

DVDLD

RFGND

RF50V

RFGND

RFGND

RC1

RR11

SVREF211

RC43

0.1U

RFGND

0.1U_BL

R

RF50V

LINK

MEVO

SVREF151

MVREF2

RC44

0.1U

DR46 R

DR48 R

SVREF15

RC2

0.01U

RC4

0.01U

RC6

1

RR29

1K_BL

0

AA2

RC29 27P(OPEN)

DPD

DVDVR

2 3

1

220(BL)

R1103_BL

RQ2

RFGND

820P

RFGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CPD

RR10 1.2K

1

RR12 1.2K

RF50V

RR30 10K_BL

RQ3

1

2 3

R1103_BL

RFGNDRFGND

DR57 0

RIC3

1

1OUT

2

1IN-

3

1IN+

4 5

GND 2IN+

TL3472

BC26

0.1U

DVDFRP

DVDRFN

A2

B2

C2

D2

CP

CN

D

C

B

A

CD_D

CD_C

CD_B

CD_A

TP46

TP

SW1(CD/DVD)

RR33

10K_BL

BEFR_OP 1

SVRER15# 3

ATR_OP 1

VCC

2OUT

2IN-

646362616059585756555453525150

171819202122232425262728293031

8

7

6

PUHRF

RC8

27P

CC2

RC19 27P(OPEN)

DLD

1

1

RR34

1K_BL

RR35

DR41 0

DC18 33P(OPEN)

TP45

TP

RFGND

BB2

RC30 27P(OPEN)

CLD

1

DR53

DD2

2200P

RC12

RC13 2200P

2200P

RC14

2200P

RC16

C

B SBA

A

D

DC19

C

RC17 120P

CC

DD

AA TP27

BB

E1

DVD/CD1

DR45 10K(OPEN)

DR47 470K(OPEN)

DR52

R

RFGND

F1

F

E

MVREF2

DVDLD

CDLD

DVDPD

CDPD

RF50V

RR26

10K_BL

DC20

0.47U(OPEN)

RC20 27P(OPEN)

MVR2

RF50V

AIP

AIN

VPA

ATOP

RFDC

RFSIN

RFAC

ATON

ES6603

CD_F

CD_E

VPBVCDVDLD

CDLD

DVDPD

CDPD

BC25 0.1U

RFGND

CDVR

RR31

100(BL)

TP44

TP

RQ4

1

R1103_BL

2 3

RFGND

MGND

DR55

22K

MVCC

MGND

RF50V

DR49

1.5K

DR54

22K

BYP

VNB

DIN

LDON

DR44

4.7K

RR39

1M

DR50

1.5K

RC3

470P

RC5

470P

RC7

0.1U

RC9

0.01U

RR8 12K

RIC1

49

RX

DIP

FNP

VNA

FNN

MEV

SDEN

SDATA

SCLK

V33

LCP

LCN

MNTR

CE

FE

TE

V25

V125

TPH

DFT

LINK

MIRRMPMB

MLPF

MIN

MEVO

32

RC22

0.22U

RC23

150P

RC25

0.01U

D5V

L7 CIC21

1 2

L8 CIC21

1 2

DGND RFGND

DR56 100

DR42 10K

DR43

10K

PI

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RF50V

RC24

33000P

MGND

RFGND

RF33V

123

MOCTL

1

DR65

DC:R/BL:0

RC11

0.1U

RC15

0.047U

SVREF15#

RC18

0.1U

RFGND

RR27 0

RF50V

TOP

TO-223

MOCTL 1

LOAD+/DCMO+ 3

LOAD-/DCMO- 3

RFGND

RF50V

SCSJ

SDATA

SCLK

CE

FE

TE

RC45

1U

LINK

MEVOMVREF2

TP28

MIRR

REG1

AIC1117A-33CY

C10

0.1U

DIN 1

DIP 1

RFO 1

RF50V

MIRR 1

SLDC 1

TP33

SDATA

TP34

SCSJ

TP25

MNTR

CEI 1

FEI 1

TEI 1

SBAD 1

SVRER15# 3

TP26

DEFCT

LINK-

3.3V

23

VOUTVIN

4

TAB

ADJ

1

TP35

SCLK

SDEFCT 1

D5V

L4 CIC21

1 2

1 2

L5 CIC21

DGND

SCSJ 1

SDATA 1

SCLK 1

L6 CIC21

1 2

RR38 3.3 (2012)

DGND

100U/6.3V

L9

1 2

CIC21

RF50V

RF33V

RFGND

PLLGND

C8

0.1U

RFGND

PC1

100U/6.3V

PC3

47U/6.3V

C7

C9

1U

PLL33V

C11

470P

2-2

Page 5

MVCC

DR33

390_BL

W

11

W

V

U

VH+

Hu+

HuHv+

Hv-

Hw+

HwVH-

CN1

HEADER_SMD_11P_AN_1m/m_BL

CN3

4

3

2

1

V

10

U

9

8

Hu+

7

Hu-

6

Hv+

5

Hv-

4

Hw+

3

Hw-

2

VH-

1

HOMESW

SLED+

SLED-

*2002.05.08

(+5V)

SLED+,- PATTERN 0.4 m/m

HEADER_2m/m_SMD_AN_4P_BL

B/L _ MOTOR_OPTION

HEADER_2m/m_SMD_AN_6P_DC

MJ4

1

2

3

4

5

6

LOAD-/DCMOLOAD+/DCMO+

HOMESW

MGND

DC _ MOTOR_OPTION

HEADER_2m/m_AN_SMD_5P

DCLOAD-

5

DCLOAD+

CN2

4

3

2

1

DR63 100

DR64 100

MGND

1-CD_3-CD OPTION

L24 L

C31 C

MAIN GND

MVCC

DR51

47K

SLED+

SLED-

DR36

47K

DR40 0(OPEN)

PATTERN 0.4 m/m

LOADER SLED

CONNECTOR

HOMESW 1

MGND

HOMESW

HOMESW 1

1

MVCC

(+5V)

OUTSW

DR37

INSW

47K

1

1

DR39 0(OPEN)

MGND

SVRER15#2

OUTSW 1

INSW 1

FOCUS-2 TRACK- 2

FOCUS+2

PATTERN 0.4 m/m

+8V_M

DR1 1(2012)_BL

DR2 1(2012)_BL

47K_BL

DR5

DC6

0.1U

DR6 33_BL

DR7

DR8 0(BL)

100K_BL

DR10

R(BL)

DR9 390_BL

SFGIN

SSPDON

SMOTOR

MGND

MVCC

DC1

0.1U_BL

MGND MGND

MGND

FR

VH-

SFGIN 1

SPDON 1

SPINDLE 1

SVRER15# 2

FR 1

VH-

1

DC2

PM5V

100U/16V_BL

DR3

0(2012)_BL

MVCC

C3

0.1U(BL)

(+5V)

47U/6.3V(BL)

MGND

TOP

123

R1

CIC21

C14

0.1U

TO-223

+8V_M

MGND

AIC1117ACY-5.0(OPEN)

C15

100U/16V(OPEN)

REG2

3

OUT

IN

GND

1

MVCC

2

C13

0.1U

1 2

C12

220U/6.3V

L10

CIC21

D5V

+8V

C4

D5V connector

Hu+

Hu-

Hv+

Hv-

Hw+

Hw-

DRIC1

FAN8423D_BL

1

NC

2

A3

3

NC

4

A2

5

NC

6

NC

7

A1

8

GND

9

H1+

10

H1-

11

H2+

12

H2-

13

H3+

14

H3-

FIN

FIN

29

30

MGND MGND

DC4

1U_BL

DC7

0.1U_BL

DC8

0.1U_BL

DC9

0.1U_BL

DC5

1U_BL

H3

H2

H1

MGND

W

DC3

V

U

1U_BL

RNF

VM1

VCC

FG_1X

PS(S/S)

ECR

DIR

FG_3X

CNF

NC

EC

SB

NC

VH

28

27

26

25

24

23

22

21

20

19

18

17

16

15

DC10

0.1U_BL

DCLOAD+- PATTERN 0.4 m/m

DR58

MVCC

10K

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DIC1

BA5954FP

VINFC

CFCERR1

CFCERR2

VINSL+

VINSL-

VOSL

VNFFC

VCC

PVCC1

PGND

VOSL-

VOSL+

VOFC-

VOFC+

GND

29

MGND

CTKERR1

CTKERR2

GND

30

DR17

33

FOCUS1

DR18 12K

SLEGN1

DC14

0.1U

MGND

+8V_M

SLED-

SLED+

FOCUS-

FOCUS+

DR13 10K

DR15 47K

DC11

100P

DR20 3.3K

DR21

6.8K

FOCUS-

DR29 1(2012)

DR31 1(2012) DR32 1(2012)

DC13

4700P

MGND

DC15

0.1U

1

DR59

4.7K

STBY

BIAS

VINTK

VINLD

PREGND

PVCC2

VNFTK

PGND

VOLD-

VOLD+

VOTK-

VOTK+

MGND

23

RQ6

KSA812

28

27

DR16 10K

26

DR19 47K

25

24

23

22

21

20

19

18

17

16

15

1

DR60

2 3

100K

DC21

1U

DR14 10K

DC12

100P

+8V_M

DC16

0.1U

MGND

DR30 1(2012)

DR12

RQ7

R1103

3

DR22 0(OPEN)

DR23 0_DC

DC Only

10K

DD1

B

C

B

DAP202K

TRACK 1

OPEN

LOAD-/DCMO-

LOAD+/DCMO+

TRACK-

TRACK+

DR61 0

1

DR62 0(OPEN)

2

OPEN 1

SPINDLE 1

PATTERN 0.4 m/m

DRV 1

RSTM 4

DR34 R

DZD1

DC:5.6V/BL:4.7V

MGND

LOAD-/DCMO- 2

LOAD+/DCMO+ 2

TRACK+ 2

DCLOAD+

DR28 1K

RIC2

1

GND

2

V01

3

VCTL

4

VIN1

FAN8082_

RIC4

1

GND

2

V01

3

VCTL

4

VIN1

FAN8082_SOP

VO2

PVCC

SVCC

VIN2

VO2

PVCC

SVCC

VIN2

8

7

6

5

SOP

8

7

6

5

DCLOAD-

+8V_M

0.1U

DC17

MGND

DR35 1K

DR38

CLOSE

1K

1

OPEN

1

CLOSE 1

OPEN 1

MGND

2-3

Page 6

MCLK_DSP

ACK1

TXD1

RXD1

STB1

RESET#

C27

0.1U(DSP)

AGND

DPRST

DPL2_CLK

DPL2_DAT

TSD0

TSD01

TSD1

TSD11

TSD2

TSD21

RSD

RSD1

MCLK

MCLK1

AL26 CIM10(DSP)

TBCK1

TWS

TWS1

A5V

AGND

ACK

TXD

RXD

PR18 1K(DSP)

AC1

0.1U(DAC)

EGND

AR8 75(DAC)

AR10 75(DAC)

AR11 75(DAC)

AR12 33(DAC)

AR13 220(DAC)

AR16 75(DAC)

AR17 75(DAC)

L13 CIC21

1 2

L17

1 2

CIC21

TWS1

MCLK_DSP

TBCK1

RSD1

TSD01

TSD11

TSD21

TSD31

PR14 100(DSP)

PR15 100(DSP)

PR16 100(DSP)

PR17 100(DSP)

E5V

A5V

E5G

AGND

AC2

47U/6.3V(DAC)

C18

27P(DAC)

EGND

C21

27P(DAC)

EGND

AD2

3.6V(DAC)(OPEN)

1K(DAC)

C19

27P(DAC)

C22

27P(DAC)

AC16

0.1U(DAC)

AF_GND

REG3

AIC1117ACE_ADJ

C5

0.1U

PC2

10U/16V

AR4

C20

27P(DAC)

VOUTVIN

1

4

TOP

123

DSP

OPTION

ACN3

1

TWS

2

GND

3

MCLK

4

GND

5

TBCK

6

GND

7

RSD

8

TSD0

9

TSD1

10

TSD2

11

TSD3

12

ACK

13

TXD

14

RXD

15

STB

16

RESET

17

+5V

18

GND

19

A5V

20

GND

HEADER 20_SMD_1M/M_AN_DSP

10U/16V(DAC)

3.5V

TAB

ADJ

TO-252

UDAC1

DATA11

CDAC1

DATA31

RSET1

YDAC1

VDAC1

5DAC1

HSYNC1

VSYNC1

20

11

12

10

15

16

17

13

14

18

19

7

AC17

23

4

D11_FID

RESET

SCLK

SDATA

CS

SD11

SD12

SD13

SDATA_OUT

MCLK

D_SCLK

D_LRCLK

CAP

EGND

220

PR19

390

DVI_RST

DVICLK1

PR4 390(DVI)

PR5 390(DVI)

PR6 390(DVI)

PR7 390(DVI)

PR8 390(DVI)

PR9 390(DVI)

PR10 390(DVI)

PR11 390(DVI)

PR12 390(DVI)

PR13 390(DVI)

AD1

AR1

AIC1

1SS355(DAC)

9

AVdd

10(2012)(DAC)

21

DVdd

STAC9460(DAC)

DVss

22

AVss

8

AR21

0.1U(DAC)(2012)

AF_GND

300mA

C23

0.1U

PR20

DVI_DAT

DVI_CLK

FID

1

DGND

HEADER 20_SMD_0.5M/M_AN_DVI

DIFF_GND

DAC_LF

DAC_RF

DAC_LR

DAC_RR

DAC_CTR

DAC_LFE

VCC33

PC6

220U/6.3V

DVI

OPTION

ACN4

1

RST#

2

DGND

3

SDA

4

SCL

5

DGND

6

D1_FID

7

D1_CLK

8

DGND

9

DATA0

10

DATA1

11

DATA2

12

DATA3

13

DATA4

14

DATA5

15

DATA6

16

DATA7

17

DGND

18

HSYNC

19

VSYNC

20

DGND

DIFF_L

DIFF_R

MIC_R

MIC_L

ACN1

1

DPL2_CTL

2

DAC_CS

3

DPL2_CLK

4

DPL2_DAT

5

DPL2_RES

6

GND

7

ACK

8

TXD

9

RXD

10

STB

11

RESET

12

DT/ES

13

DT/CEN

14

F/L

15

AUGND

16

F/R

17

+12V

18

R/L

19

AUGND

20

R/R

21

-12V

22

CENTER

23

AUGND

24

S/W

HEADER 24_SMD_1M/M_ST_DAC

CONNECTOR_2m/m_SMD_ST_8P

PCN1

8

EVR5G

7

EVR5V

6

DGND

5

D5V

4

AGND

3

A5V

2

MGND

1

M8V

ACN2

1

COMP

2

S_C

3

V_GND

4

S_Y

5

Y/G

6

V_GND

7

Pr/R

8

Pb/B

9

VGND

10

OPT_OUT

11

OPTGND

12

OPTIN

13

OPTGND

14

F_R

15

+5V

16

F_L

17

SGND

18

AUX_L

19

SGND

20

AUX_R

HEADER 20_SMD_1M/M_AN

AJ2

1

2

AC20

AF_GND

AC11

10U/16V(DAC)

E5VE5V

DIFF_L

E5G

DIFF_R

AIC1(STAC9460)

AC6

1000P(DAC)

AC9

1000P(DAC)

AF_GND

AF_GND

AR3

100(DAC)

AR5

100(DAC)

AUX_L

AUX_R

DAC_LF

DAC_RF

AC12

10U/16V(DAC)

AC14

10U/16V(DAC)

DAC_LFO

AR14

100K(DAC)

DAC_RFO

AR18

100K(DAC)

DAC_LR

DAC_RR

AR2 3.3(2012)(DAC)

AF_GND

AC7

47U/6.3V(DAC)

AC10

0.1U(DAC)

DAC_LF

DAC_RF

DAC_LRTBCK

DAC_RR

DAC_CTR

DAC_LFE

AC4

100U/6.3V(DAC)

0.1U(DAC)(2012)

AF_GND

AC3

0.1U(DAC)

3

4

5

6

Vref

2

1

28

27

26

25

24

23

(AR8,AR17)

A5V

L12

1 2

CIC21

CDAC1

5DAC1

AD3

1SR154

CDAC

5DAC

CDAC1

5DAC1

AD4

1SR154

VR13

330(AV)

VGND

VR18

330(AV)

VGND

1

VR6

75(AV)

1

VR10

75(AV)

EGND

1

1

REG4

AIC1117ACE_ADJ

PC8

0.1U

PC11

10U/16V

VID+5V

VR3

330(AV)

23

VQ2

KSA812(AV)

VID+5V

VR8

330(AV)

23

VQ4

KSA812(AV)

VOUTVIN

TAB

ADJ

1

V/R1

1

VIDEO_U/B

Pb/B

COMP1

1

S_C/COMPO

A5V

AGND

2.0V

STAC9460

350mA

23

4

470

PR1

PR3

270

YDAC1

Pb/B

L16

1 2

10uH(AV)

L19

1 2

CIC21(AV)

YDAC

C26

0.1U(AV)

PC9

0.1U

VCC20

EGNDEGNDEGND

YDAC1

VID+5V

+

C24

100U/6.3V(AV)

VGND

DAC_CTR

PC10

220U/6.3V

VR12

330(AV)

1

VGND

VR17

330(AV)

NTSC

PALCCVBS

AC18

VID+5V

23

VID+5V

23

VGND

VR2

330(AV)

VQ1

KSA812(AV)

VR7

330(AV)

VQ5

KSA812(AV)

DAC_CTRO

AF_GND

AR22

100K(DAC)

S/Y1

1

S_VIDEO_Y

1

Y/G1

VIDEO_Y/G

Y/G

10U/16V(DAC)

1

VR5

75(AV)

1

5DAC VDAC YDAC CDAC UDAC

CVBS

CVBSYGPbBPrR

DAC_LFE

VDAC

VDAC1

C/CVBS

UDACSTB

UDAC1

AC13

10U/16V(DAC)

AC15

10U/16V(DAC)

AC19

10U/16V(DAC)

VR19

330(AV)

VDAC1

1

VGND

VR14

330(AV)

UDAC1

1

VR4

75(AV)

1

VR11

75(AV)

1

RSTM3

RESET#1

DVI_CLK

DVI_DAT

DVI_RST

DPL2_CLK

DPL2_DAT

DPRST

AR15

100K(DAC)

AF_GNDAF_GND

AR19

100K(DAC)

AF_GNDAF_GND

DAC_LFEO

AR23

100K(DAC)

AF_GND

VID+5V

VR9

330(AV)

23

VID+5V

23

VGND

MR85 0(DVI)

MR86 0(DVI)

MR87 0(DVI)

DAC_LRO

DAC_RRO

VQ6

KSA812(AV)

VR1

330(AV)

VQ3

KSA812(AV)

RST#1

COMP2

1

CVBS

U/B1

1

VIDEO_V/R

Pr/R

C16

0.1U(DAC)

C17

0.1U

EGND

COMP

EGND

1

DPRST1

1

AR6 1K

AR25

2.7K

AF_GND

E5V

D5V

A5V

+8V

VGND

A5V

ACK

ACK1

TXD

TXD1

RXD

RXD1

STB

STB1

DAC_LFO

DAC_RFO

DAC_LRO

DAC_RRO

DAC_CTRO

DAC_LFEO

E5G

DGND

AGND

MGND

S_C/COMPO

S_VIDEO_Y

VIDEO_Y/G

OPT_OUT1

GND_SHIELD

SPDIF_IN1

AUX_L

AL21 CIC21

AUX_R

EGNDAF_GND

MR88 1K(DAC)

AL24 CIM10(DAC)

AL2 CIM10(DAC)

AL3 CIM10(DAC)

MR79 100

MR80 100

MR81 100

MR82 100

AL4 CIM10(DAC)

AL5 CIM10(DAC)

AL6 CIM10(DAC)

AL7 CIM10(DAC)

AL8 CIM10(DAC)

AL9 CIM10(DAC)

AL1 CIM10(DAC)

AL10 CIM10(DAC)

AL11 CIM10(DAC)

AL12 CIM10(DAC)

AL13 CIM10(DAC)

COMP

VIDEO_V/R

VIDEO_U/B

SPDIF_IN

PC12 0.1U

PC13 0.1U

PC14 0.1U

PC15 0.1U

PC16 0.1U

PC17 0.1U

PC18 0.1U

CVBS

AL140

Y/G

AL15

0

Pr/R

Pb/B

AL160

AL23CIM10(OPEN)

AL17CIM10

AR24100

AL18CIM10

AL19CIC21

AL20

CIM10

AL22

CIM10

HEADER_2MM_DIP_ST_2P

2-4

Page 7

Printed circuit board

(Forward side)

2-5

Page 8

(Reverse side)

2-6

Page 9

< MEMO >

Page 10

VICTOR COMPANY OF JAPAN, LIMITED

AV & MULTIMEDIA COMPANY AUDIO/VIDEO SYSTEMS CATEGORY 10-1,1chome,Ohwatari-machi,Maebashi-city,371-8543,Japan

(No.MB141BSCH)

Printed in Japan

WPC

Loading...

Loading...