Page 1

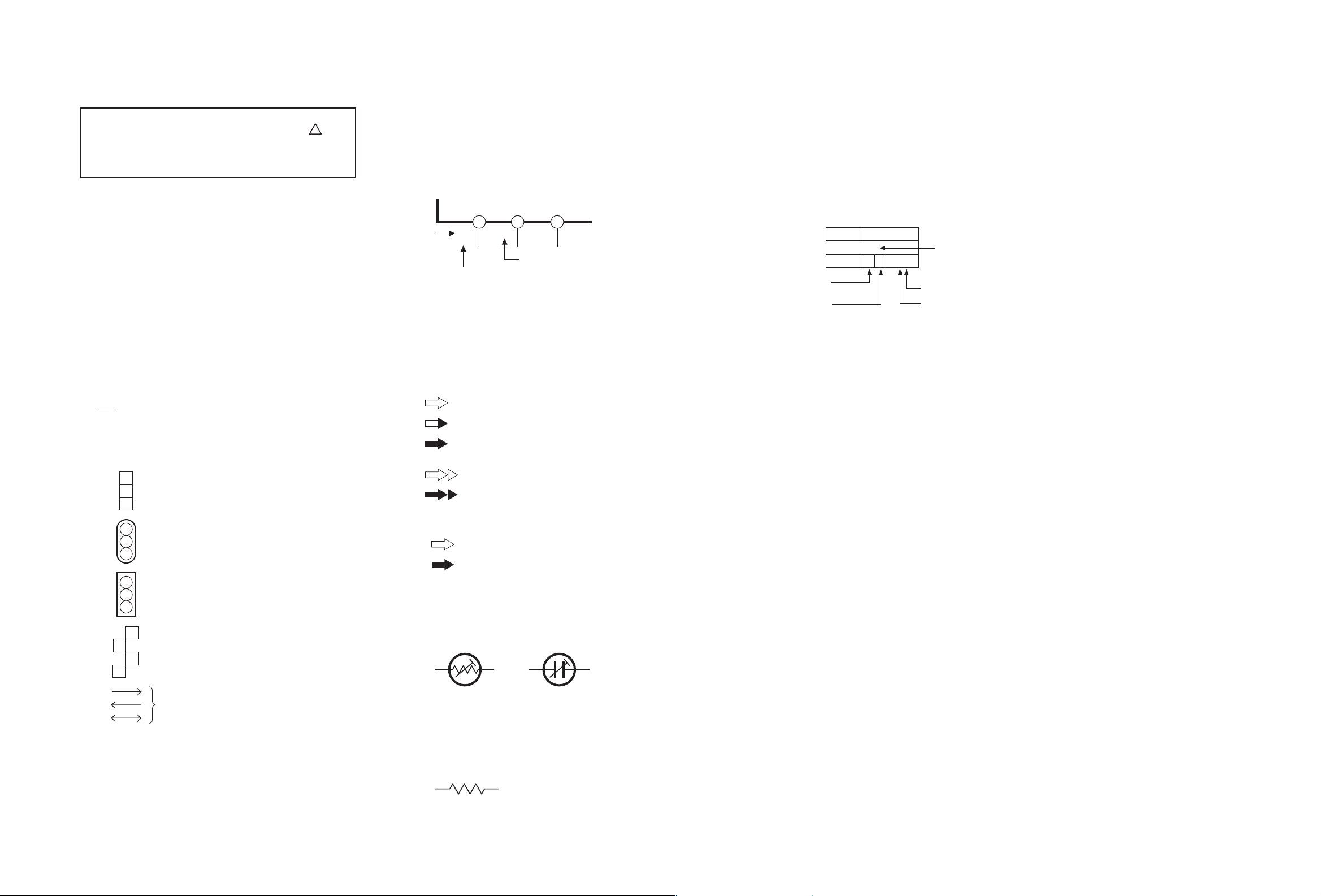

SCHEMATIC DIAGRAMS

DVD / HDD & Mini DV VIDEO RECORDER

200

SR-DVM70AG, SR-DVM70EU

CD-ROM No.SML200504

CABLE/SAT

DVD

TV

STANDBY/ON

DVD

TV/CBL/SAT

TV

AV

TV

VIDEO

DV HDD DVD

TV

PR

AUX

CANCEL

MEMO/MARK

PROGRAMME

EDITDUBBING

LIVE

NAVIGATIONTOPMEN U

ENTER

RETURN

MENU

NEXTPREVIOUS

SLOWSLOW PLAY/SELECT

CLEAR

PAUSEREC

STOP/

JUMP

RECMODE

DISPLAY

ONSCREEN

REMAIN

VPS/PDC

AUDIO

SUBTITLE

ANGLE

LIVECHECK

SETUP

PROGRESSIVE

OPERATE

EJECTEJECTDISPLAY

DV/HDD/DVD RECMODE INSTANTREPLAY AUDIODUB. INSERT

SAT

SCAN

S-VIDEO

VIDEO(MONO)L - AUDIO - R

INF-1

INPUTSELECT

RECDVDRECHDDRECDV

RECPAUSEPLAY

FFREWSTOP

DVIN / OUT

(AG model)

SR-DVM70AG, SR-DVM70EU [D4MC29]

(EU model)

COPYRIGHT © 2005 Victor Company of Japan, Limited.

No.YD049SCH

2005/4

Page 2

Page 3

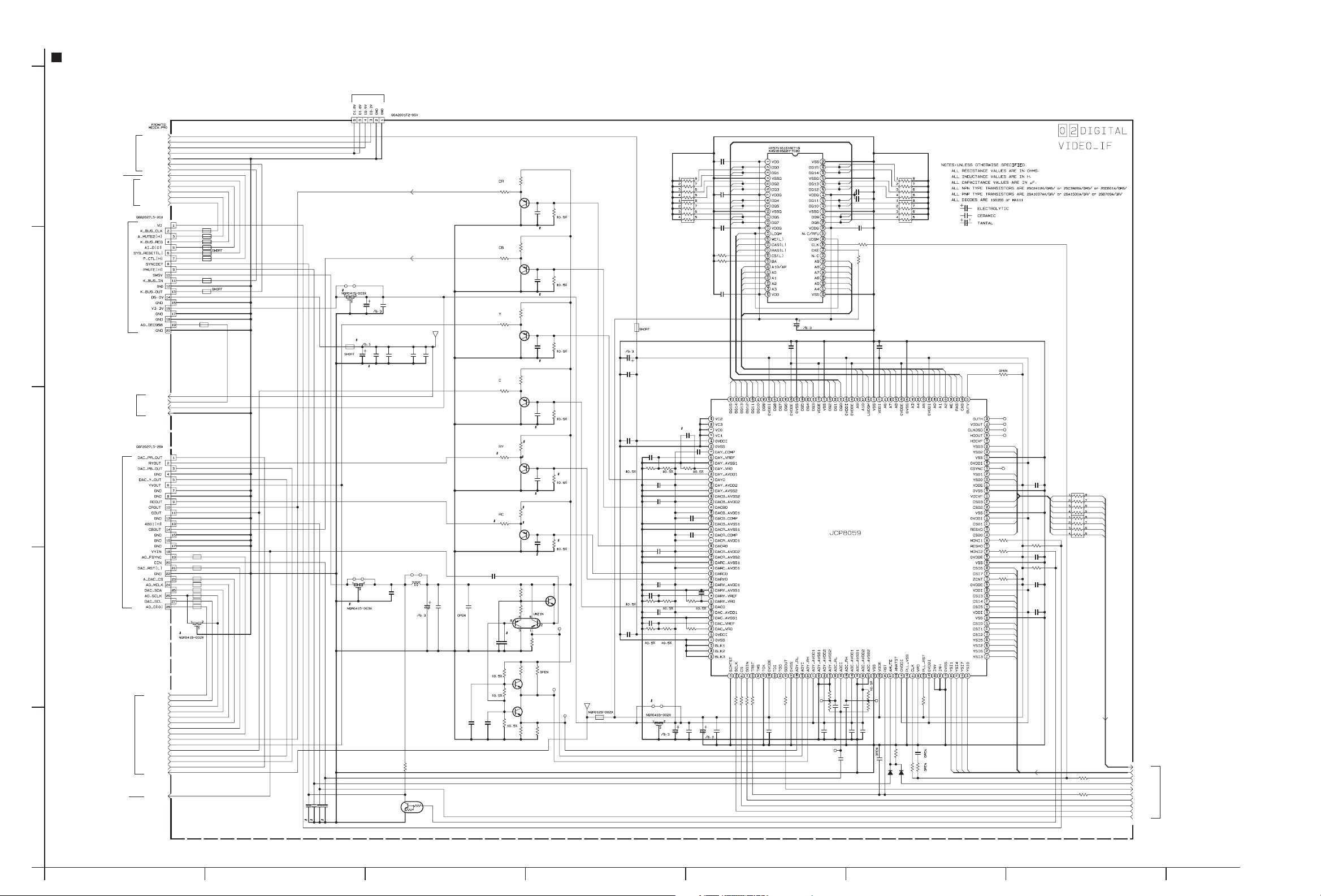

CHARTS AND DIAGRAMS

NOTES OF SCHEMATIC DIAGRAM

Safety precautions

The Components indentified by the symbol are

critical for safety. For continued safety, replace safety

critical components only with manufacturer's recommended parts.

1. Units of components on the schematic diagram

Unless otherwise specified.

1) All resistance values are in ohm. 1/6 W, 1/8 W (refer to

parts list).

Chip resistors are 1/16 W.

K: KΩ(1000Ω), M: MΩ (1000KΩ)

2) All capacitance values are in µF, (P: PF).

3) All inductance values are in µH, (m: mH).

4) All diodes are 1SS133, MA165 or 1N4148M (refer to parts

list).

Note: The Parts Number, value and rated voltage etc. in

the Schematic Diagram are for references only.

When replacing the parts, refer to the Parts List.

2. Indications of control voltage

AUX : Active at high.

AUX or AUX(L) : Active at low.

!

4. Voltage measurement

1) Regulator (DC/DC CONV) circuits

REC : Colour bar signal.

PB : Alignment tape (Colour bar).

— : Unmeasurable or unnecessary to measure.

2) Indication on schematic diagram

Voltage indications for REC and PB mode on the schematic diagram are as shown below.

REC mode

12 3

2.5

(5.0)

PB mode

1.8

PB and REC modes

(Voltage of PB and REC modes

are the same)

Note: If the voltages are not indicated on the schematic

diagram, refer to the voltage charts.

5. Signal path Symbols

The arrows indicate the signal path as follows.

NOTE : The arrow is DVC unique object.

Playback signal path

Playback and recording signal path

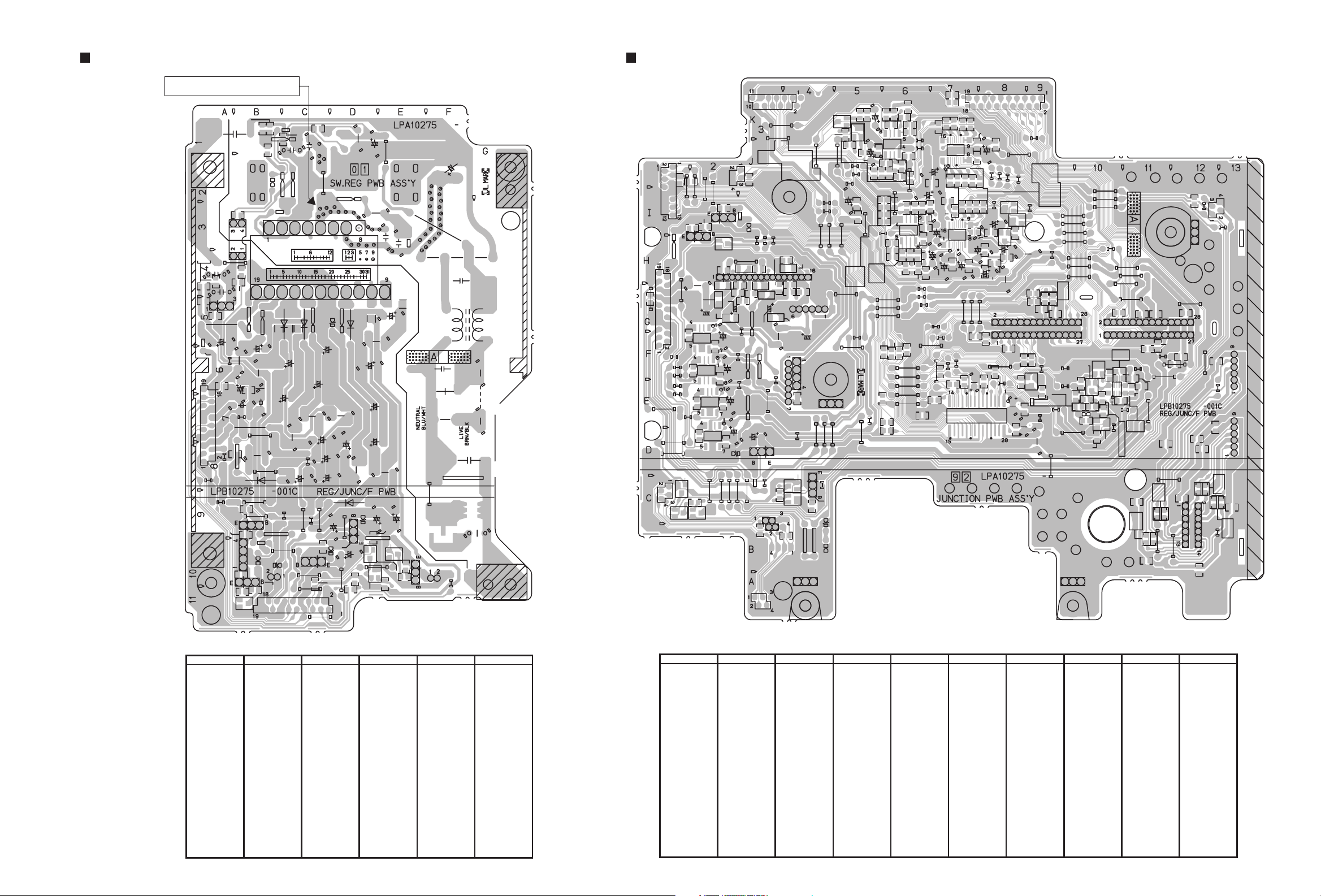

CIRCUIT BOARD NOTES

1. Foil and Component sides

1) Foil side (B side) :

Parts on the foil side seen from foil face (pattern face)

are indicated.

2) Component side (A side) :

Parts on the component side seen from component face

(parts face) indicated.

rts location are indicated by guide scale on the circuit board.

2. Parts location guides

Parts location are indicated by guide scale on the circuit board.

REF No.

IC101 B C 6 A

(A : Component side)

D : Discrete component)

B : Foil side

C : Chip component

Note: For general information in service manual, please

refer to the Service Manual of GENERAL INFORMATION Edition 4 No. 82054D (January 1994).

LOCATION

IC

Category : IC

Horizontal “A” zone

Vertical “6” zone

3. Interpreting Connector indications

1

2

Removable connector

3

1

2

Wire soldered directly on board

3

1

Non-removable Board connector

2

3

1

2

4

Board to Board

3

Connected pattern on board

The arrows indicate signal path

Note: For the destination of each signal and further line

connections that are cut off from the diagram,

refer to "BOARD INTERCONNECTIONS"

Recording signal path

(including E-E signal path)

Capstan servo path

Drum servo path

(Example)

R-Y

Playback R-Y signal path

Y

Recording Y signal path

6. Indication of the parts for adjustments

The parts for the adjustments are surrounded with the circle

as shown below.

7. Indication of the parts not mounted on the circuit board

“OPEN” is indicated by the parts not mounted on the circuit

board.

R216

OPEN

2-1 2-2

Page 4

BOARD INTERCONNECTIONS

CN852

CN951

Page 2-25

SHEET 11

CN5305

Page 2-5

SHEET 1

CN5001

CN5302

5

CN903

CN3501

CN3701 CN2601

CN1503

CN501

CN3014

CN5301

CN5402

CN3901

CN701

CN901

CN2602 CN8001

CN3103

CN7123

CN7107

CN7102

CN5304CN5501

CN7124

CN7105

CN7106

CN5303

CN1405

CN5403

CN902

REG Page 2-5 SHEET 1

ON SCREEN Page 2-19 SHEET 8

VIDEO SW DV Page 2-21 SHEET 9

VIDEO SW VDR Page 2-23 SHEET 10

TERMINAL I/O Page 2-25 SHEET 11

AUDIO I/O Page 2-27 SHEET 12

SYSCON Page 2-29 SHEET 13

TUNER Page 2-31 SHEET 14

CN5404CN1001

FW851

4

CN1502

REG Page 2-35 SHEET 16

DV MSD Page 2-37 SHEET 17

DV MAIN Page 2-39 SHEET 18

DV I/O Page 2-41 SHEET 19

DV VIDEO OUT Page 2-43 SHEET 20

AUDIO AD/DA Page 2-47 SHEET 22

3

CN1501

CN4001

2

CN3104

CN7201

Page 2-33

SHEET 15

CN3102

CN7001

Page 2-33

SHEET 15

CN7002

REG Page 2-5 SHEET 1

VIDEO Page 2-49 SHEET 23

AUDIO AD/DA Page 2-51 SHEET 24

CN7103

CN7127

CN5504

CN5503

Page 2-33

SHEET 15

1

VIDEO IF Page 2-7 SHEET 2

FLASH MEMORY Page 2-9 SHEET 3

MEDIA PROCESSOR Page 2-11 SHEET 4

DDR SDRAM Page 2-13 SHEET 5

1394 PHY Page 2-15 SHEET 6

ATAPI IF Page 2-17 SHEET 7

A

BCDEFG

2-3 2-4

p10688001a_rev0

Page 5

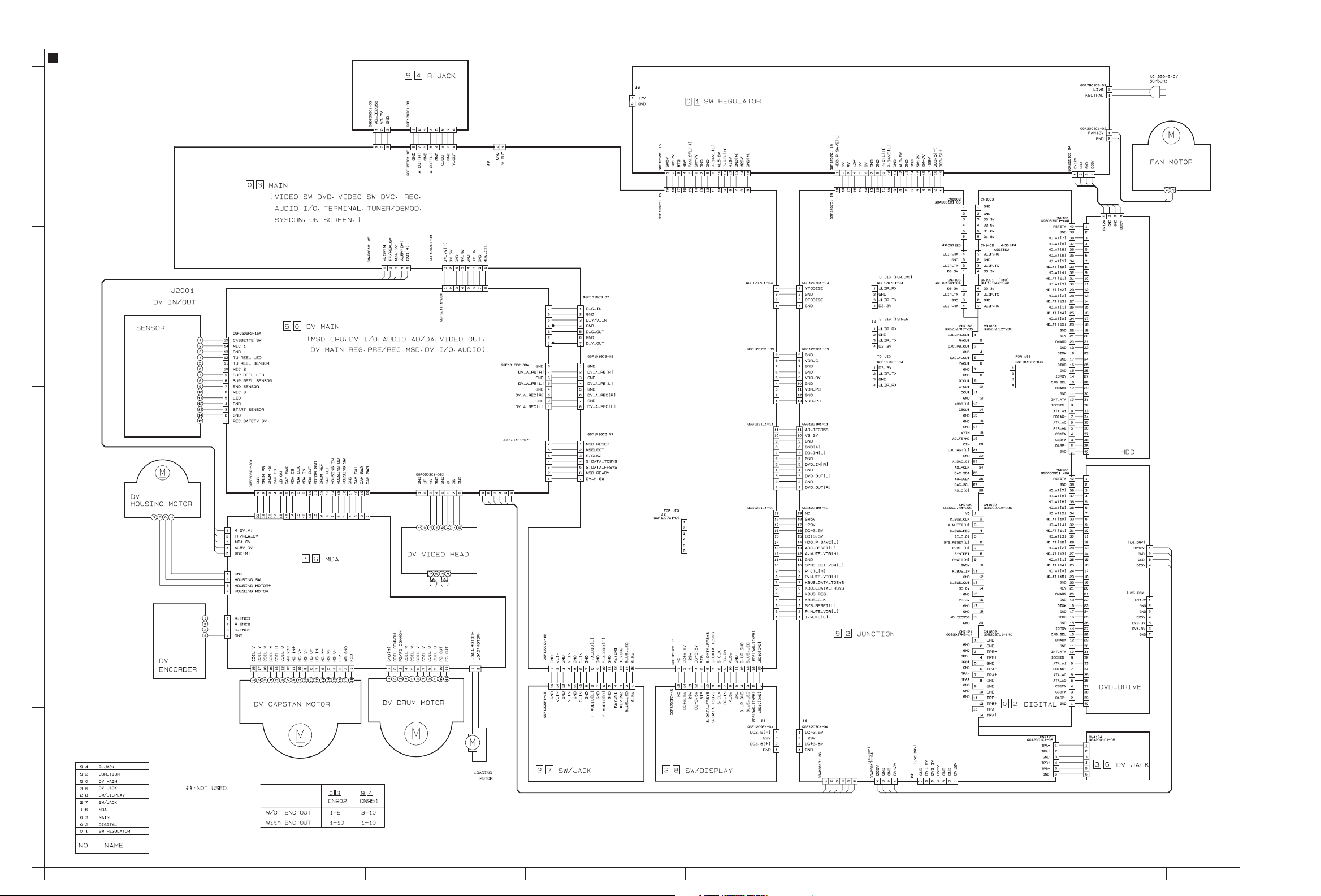

SW.REG, MAIN(REG) AND JUNCTION(REG) SCHEMATIC DIAGRAM

B5509

TO MAIN(VIDEO SW)

SHEET 10

TO MAIN(AUDIO I/O)

SHEET 12

TO MAIN(TUNER)

SHEET 14

TO MAIN(TERMINAL I/O)

SHEET 11

TO MAIN(TERMINAL I/O)

SHEET 11

GND

P.CTL[H]

AL5.8V

P.SAVE[L]

SW-7V

FAN_CTL[

45V

BT2

SW12V

SW5V

CN5403

TO MAIN(TUNER)

SHEET 14

TO MAIN(AUDIO I/O)

SHEET 12

TO MAIN(TUNER) SHEET 14

TO MAIN(SYSCON) SHEET 13

TO MAIN(VIDEO SW) SHEET 10

TO MAIN(TERMINAL I/O) SHEET 11

TO MAIN(AUDIO I/O) SHEET 12

MDA

CN5404

TO DV MAIN(REG)

CN1001

SHEET 16

TO

D3.3V

JUNCTION(VIDEO)

D2.5V

SHEET 23

CN5502

TO DIGITAL(VIDEO IF)

CN1003

SHEET 2

TO

SW5V[2]

JUNCTION(VIDEO)

D5V

SHEET 23

CN5503

NOT

USED

CN5504

DVD

V3.3V

TO

JUNCTION(VIDEO)

SHEET 23

TO MAIN(TERMINAL)

GND

SHEET 11

SW12V

TO MAIN(AUDIO I/O)

SW-7V

SHEET 12

-29V

DC[-]

DC[+]

TO

JUNCTION(VIDEO)

SHEET 23

TO MAIN(SYSCON)

SHEET 13

TO MAIN(TERMINAL I/O) SHEET 11

TO MAIN(SYSCON) SHEET 13

TO MAIN(SYSCON) SHEET 13

TO MAIN(TUNER) SHEET 14

D5302

IC5501

10

C5524

C5501

1

C5504

1

C5507

1

D5508

µ

IC5502

IC5503

C5525

1

100

CN5305

CN5301

CN5302

CN5303

C5502

C5527

10

C5505

100

C5508

100

R5513

C5506

10k

470p

470p

C5509

MAIN(REG)

30

CN5402

CP5401

1.5A

!

D5401

R5403

470

D5404

IC5401

R5401

R5402

2.2k

C5401

100

Q5403

10k

C5404

470p

Q5401

Q5402

C5402

100

B5401

R5404

10k

!

CP5402

1.5A

D5403

D5402

B5402

R5405

10k

Q5509

R5514

270

C5518 C5520 C5522C5517

470 1 11

C5503

470p

IC5506

C5526

10

C5528

R5501 R5503R5502

330 5.6k470

Q5504 Q5502

D5505

D5501

C5513

1

R5507

5.6k 12k

R5508 R5510

3.3k

C5519

470

D5504

IC5505

D5502 D5503

Q5507

100

C5514

C5515

470p

R5509

12k

470

C5521

Q5501

C5403

C5516

100

R5506

470

C5523

10

C5531

10

C5532

10

L5502

C5534

10

C5405

100

C5529

C5530

B5501

1

5

D5214

!

!

CN5001

4

3

DANGEROUS VOLTAGE

!

F5001

VA5001

B5001

GROUND POINT FOR

PRIMARY VOLTAGE

R5001

4.7M

SG5001

C5005

100p

VA5003

!

LF5002

R5103

680k

C5002

!

C5001

0.068

IC5101

R5106

3.9k

R5107

680

R5108

0.33

C5105

470p

D5001

!

0.022

C5104

470p

D5104

C5004

C5003

D5103

C5106

0.01

!

PC5101

R5301

220

R5109

R5101

68k

C5103

27

D5106

C5107

220p

GROUND POINT FOR

SECONDARY VOLTAGE

!

47

D5101

R5105

D5105

R5102

1.2k

R5104

1k

!

R5302

4.7k

R5303

R5304

1.5k

6.8k

C5301

0.15

C5302

R5305

IC5301

0.033

24k

R5306

3.9k

!

T5001

C5102

4700p

C5101

100p

68

2

D5211

L5208

33

µ

C5211

180

D5202

D5213

D5203

D5301

D5205

D5204

D5207

D5212

L5207

33

µ

D5209

C5208

1200

C5207

680

D5208

L5206

33

µ

C5308

100

D5210

CP5301

!

C5209

18

C5315

0.01

!

C5210

1.5A

220

L5203

µ

33

C5309

47

R5308

1.2k

C5202

4.7

L5201

33

µ

L5202

C5204

680

C5205

1200

C5307

100

R5326

47

R5325

15

!

CP5302

C5304

33

µ

100

C5203

C5303

100

680

L5204

C5305

33

µ

100

L5205

33

µ

C5316

C5306

100

C5206

1200

2.0A

Q5305

R5312

10k

C5310

2.2

L5301

Q5306

D5304

B5306

L5302

D5305

QUY460-125H

R5309

1k

R5313

10k

C5311

100

D5303

D5306

R5314

470

C5312

100

B5307

Q5303

TO JUNCTION(VIDEO)

CN5304

R5315

100

SHEET 23

HDD_P.SAVE[L]

B5303

Q5313

R5327

10k

R5328

470

Q5304

Q5307

R5316

10k

Q5308

R5317

1k

29

JUNCTION(REG)

CN5501

D5307

Q5315

B5304

R5329

10k

Q5314

R5330

470

B5301

D5513

QUY160-100Y

L5501

Q5505

Q5506

1k

R5504

R5505

2.2k

Q5503

B5503

B5502

R5511

10k

D5512

Q5510

B5506

B5504

B5302

R5512

470

D5511

B5510

R5323

1.2k

R5324

1.2k

Q5508

C5533

10

1

p10687001a_rev0

SHEET 1

A

BCD EFG

2-5 2-6

Page 6

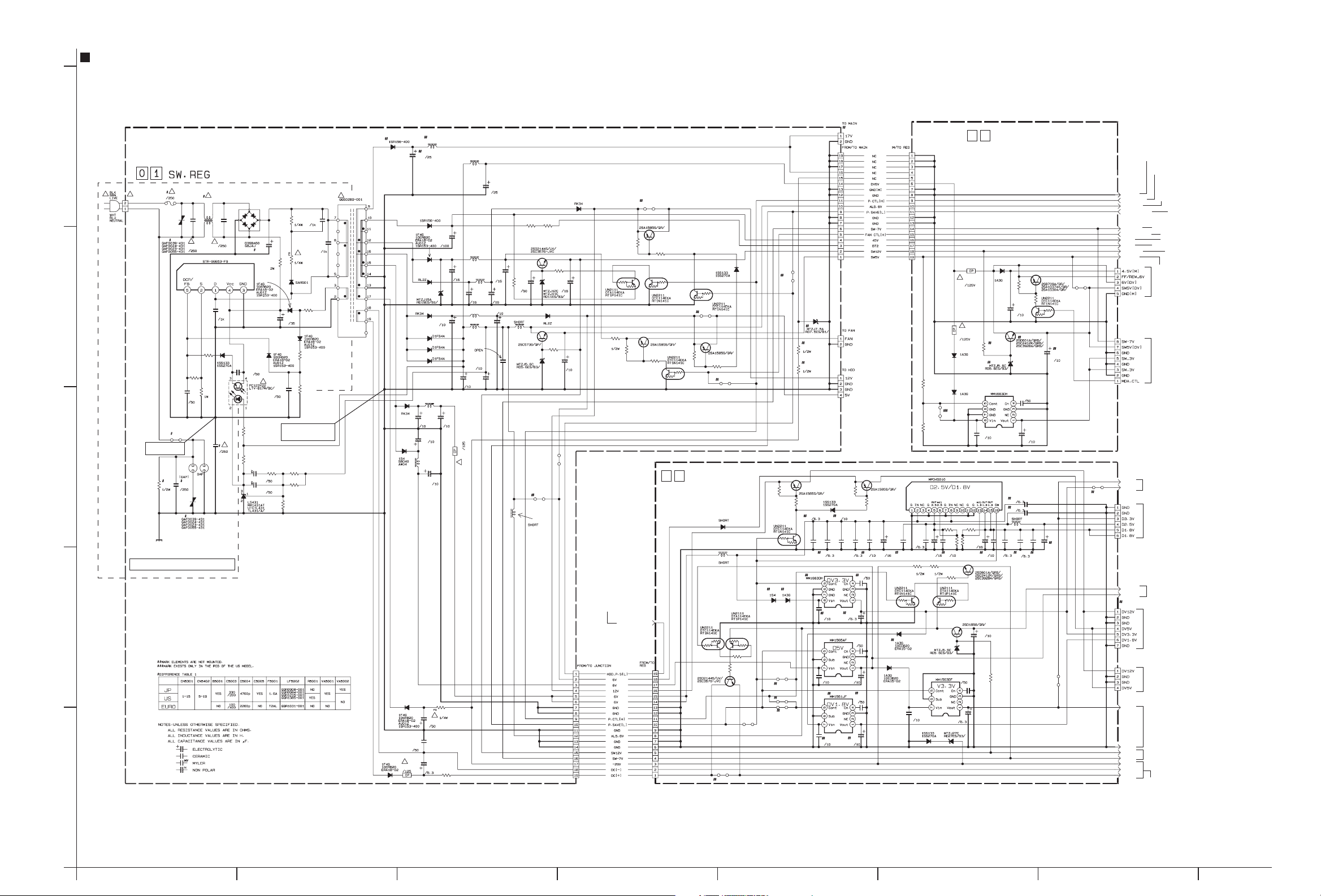

DIGITAL(VIDEO IF) SCHEMATIC DIAGRAM

VDDI1.8

DIGI3.3V

K_BUS_OUT

K_BUS_IN

P_CTL[H]

SYS_RESET[L]

AI_D[0]

K_BUS_REQ

A_MUTE2[H]

K_BUS_CLK

CN1002

AO_IEC958

CN1001

AO_D[0]

SPI_CLK

AO_SCLK

SPI_MOSI

AO_MCLKO

A_DAC_CS

DAC_RST[L]

AO_FSYNC

DAC_CVBS_OUT

DAC_SY_OUT

DAC_SC_OUT

DAC_Y_OUT

DAC_PB_OUT

DAC_PR_OUT

EPG_V_IN

D2.5V

D1.8V

GND

K1002

K1003

K1004

K1005

K1006

K1007

K1008

K1009

K1010

D5.0V

V3.3V

GND

K1011

K1012

K1013

K1014

K1015

K1016

K1017

K1018

LC1004

D3.3V

5

TO MEDIA PROCESSOR

TO ATAP I I F

TO MEDIA PROCESSOR

TO JUNCTION(VIDEO)

4

TO MEDIA PROCESSOR

3

TO JUNCTION(VIDEO)

2

TO MEDIA PROCESSOR

1

TO FLASH MEMORY

SHEET 4

SHEET 7

SHEET 4

CN7109

SHEET 23

SHEET 4

CN7108

SHEET 23

SHEET 4

SHEET 3

TO SW.REG

CN5502

SHEET 1

CN1003

C1042

0.1

C1093

B1001

LC1003

10k

C1043

0.1

C1044

RA1004

C1058

R1021

3.3k

R1024

2.7k

0.1

0.1

C1034

C1035

0.1

0.1

0.1

R1046

3.3k

0.1

C1094

0.1

R1054

3.3k

C1001

22

0.1

10k

R1030

10k

R1031

10k

C1045

0.1

DQ15

DQ14

0.1

0.1

C1033

0.1

0.1

0.01

C1062

R1028

2.7k

R1027

2.7k

R1013

C1002

C1003

C1004

0.1

0.1

10

R1036

1k

R1035

Q1002

0Ω

2SA1037AK/QR/-X

R1037

100

C1070

R1039

1k

R1038

Q1003

2SA1037AK/QR/-X

0Ω

R1040

R1042

1k

R1045

1k

1k

R1053

1k

R1066

100

R1067

120

C1071

C1072

C1073

C1074

C1075

Q1009

2SC2412K/QRS

Q1008

R1059

470

R1062

TL1098

R1065

120

100

K1019

R1043

150

R1047

220

R1051

270

R1055

180

TL1097

D3.3V

TL1099

C1095

10

C1096

0.1

C1036

0.1

C1032

0.1

R1022

1.5k

C1038

C1039

C1060

C1090

R1050

1.5k

C1091

C1092

0.1

R1071

1.5k

K1020

B1008

LC1001

C1067

C1066

0.1

47

C1080

C1078

0.1

47

K1001

C1079

0.1

B1007

C1069

LC1002

0.1

C1053

C1049

C1048

C1050

0.1

D5.0V

C1082

0.1

C1083

0.1

B1004

L1004

µ

10

C1052

C1051

10

R1034

10k

Q1001

C1063

0.1

R1041

Q1004

0Ω

2SA1037AK/QR/-X

R1044

Q1005

0Ω

2SA1037AK/QR/-X

R1049

R1048

Q1006

0Ω

2SA1037AK/QR/-X

R1052

Q1007

0Ω

2SA1037AK/QR/-X

C1065

4.7

R1056

2.2k

R1057

33

C1076

C1077

0.1

R1068

2.2k

Q1010

R1069

2SC2412K/QRS

2.2k

Q1011

2SC2412K/QRS

R1070

1.2k

C1098C1097

0.10.1

IC1002

C1041

10

DQ5

DQ4

DQ3

C1007 C1008 C1009

0.1 0.1 0.1

TL1091

22k

R1060 R1002

TL1092

DQ15

DQ14

DQ13

DQ12

C1047

0.1

C1088

DQ11

0.1

DQ10

DQ9

DQ8

C1046

0.1

R1033

470

27M_SDRAM

R1032

10k

A9

A8

A7

A6

A5

A4

DQ2

DQ1

DQ0

A9

AP

IC1001

0.1

0.1

0

C1017

C1018

C1019

0.01

RA1005RA1003

10k

RA1006

10k

C1026

0.1

R1010

UDQM

A6A7A8

TL1093

220

R1001

22k

R1061

R1009

C1022

D1001 1SS355-X

10k

1SS355-X

D1002

R1018

A3

27M_8059

0Ω

A0A1A2

A4

A5

WE

RAS

CAS

TL1031

TL1032

TL1033

TL1034

YSO3

YSO2

TL1035

YSO1

C1020

YSO0

CSO3

CSO2

CSO1

CSO0

R1006

R1004

VO_D[14]

VO_D[15]

R1003

VO_D[11]

VO_D[12]

VO_D[13]

VO_D[8]

VO_D[9]

VO_D[10]

VO_D[5]

VO_D[2]

VO_D[6]

VO_D[3]

0

R1072

VO_D[1]

VO_D[4]

VO_D[7]

R1020 C1023

VO_D[0]

0.1

R1007

0

10k

0

R1005

10k

C1014

0.1

0

C1012

0.1

RA1001

0

YSO3

YSO2

YSO1

YSO0

CSO3

CSO2

CSO1

CSO0

0.1

C1015

VI_D[9]

VI_D[8]

VI_D[7]

VI_D[6]

VI_D[5]

VI_D[4]

VI_D[3]

VI_D[2]

RA1002

0

VI_D[2-9]

VI_D[2-9]

VO_D[0-15]

R1019

0

R1017

0

VO_D[0-15]

VIDEO_27M

VIDEO_MUTE[H]

VIDEO_RXD

VIDEO_RST[L]

SPI_MOSI

VIDEO_CS

SPI_CLK

480I[H]

TO

MEDIA PROCESSOR

SHEET 4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

UDQM

WE

CAS

RAS

AP

A0

A1

A2

A3

C1030

0.1

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

000

R1015

R1014

0

0

R1012

R1029

C1005

0.1

p10657001a_rev0

SHEET 2

A

BCDEFG

2-7 2-8

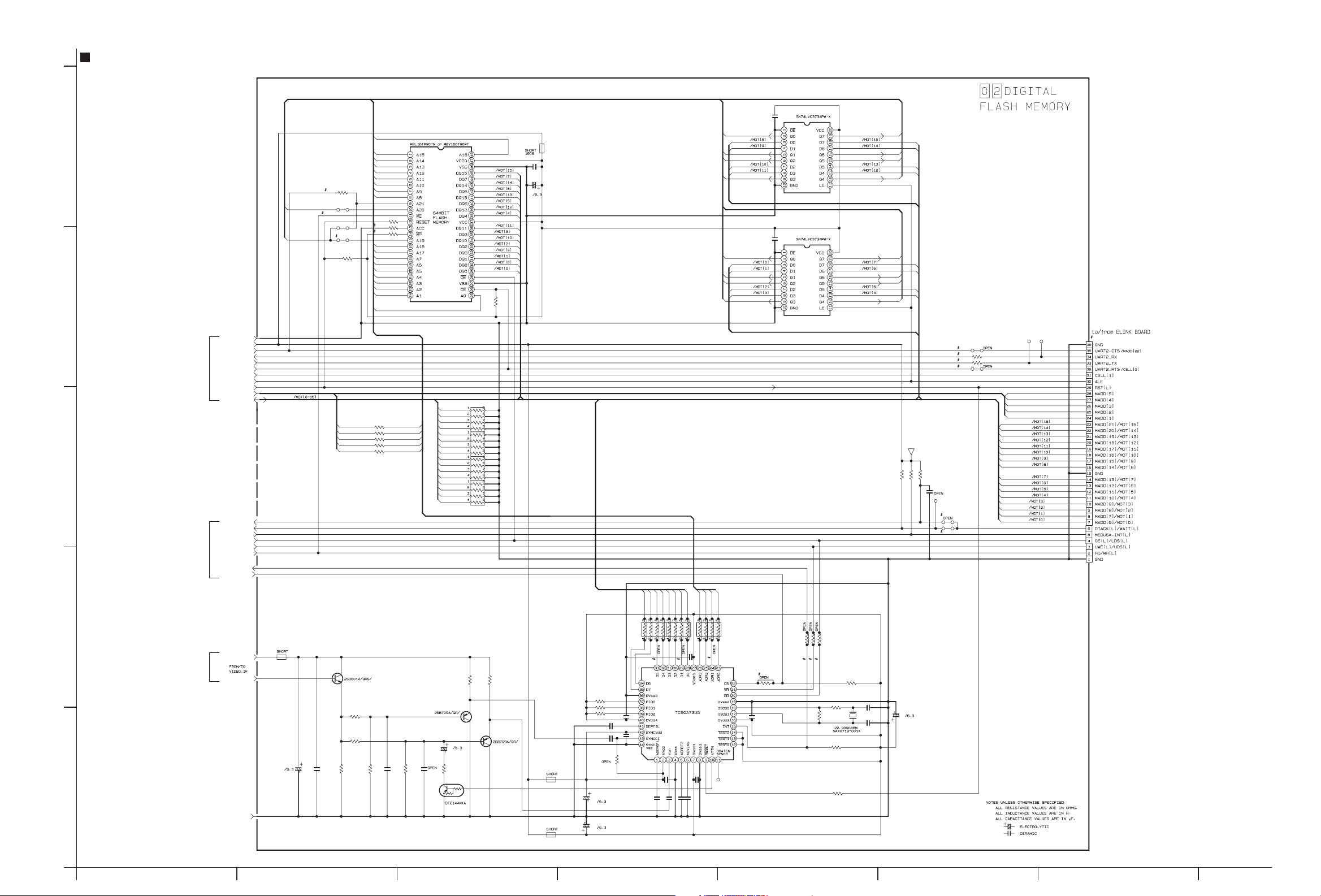

Page 7

DIGITAL(FLASH MEMORY) SCHEMATIC DIAGRAM

5

R1216

LH_AR[21]

B1203

B1202

R1225

B1204

10k

LH_AR[20]

4

R1222

R1223

R1224

LH_AR[16]

LH_AR[15]

LH_AR[14]

LH_AR[13]

LH_AR[12]

LH_AR[11]

LH_AR[10]

LH_AR[9]

LH_AR[19]

LH_AR[18]

LH_AR[8]

LH_AR[7]

LH_AR[6]

LH_AR[5]

LH_AR[4]

LH_AR[3]

LH_AR[2]

LH_AR[1]

C1207

IC1203

0.1

LH_AR[14]

IC1201

0Ω

4.7k

4.7k

LH_AR[17]

MADD[21]

MADD[13]

MADD[20]

MADD[12]

MADD[19]

MADD[11]

MADD[18]

MADD[10]

MADD[17]

MADD[9]

MADD[16]

MADD[8]

MADD[15]

MADD[7]

MADD[14]

MADD[6]

R1226

4.7k

K1201

47100

C1203

0.1

C1204

MADD[14]

MADD[15]

LH_AR[15]

LH_AR[16]

MADD[16]

MADD[17]

LH_AR[17]

C1206

IC1202

0.1

LH_AR[6]

MADD[6]

MADD[7]

LH_AR[7]

LH_AR[8]

MADD[8]

MADD[9] MADD[10]

LH_AR[9]

LH_AR[21]

MADD[21]

MADD[20]

LH_AR[20]

LH_AR[19]

MADD[19]

MADD[18]

LH_AR[18]

LH_AR[13]

MADD[13]

MADD[12]

LH_AR[12]

LH_AR[11]

MADD[11]

LH_AR[10]

TL1216

MADD[5]

MADD[4]

MADD[3]

MADD[2]

MADD[1]

MADD[21]

MADD[20]

MADD[19]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

MADD[13]

MADD[12]

MADD[11]

MADD[10]

MADD[9]

MADD[8]

MADD[7]

MADD[6]

TL1215

GND

D3.3V

MADD[22]

TO MEDIA PROCESSOR

SHEET 4

3

TO MEDIA PROCESSOR

SHEET 4

UART2_RX

UART2_TX

E5_RESET[L]

MADD[1-5]

MADD[6-21]

DTACK[L]

WAIT[L]

ELINK_INT[L]

OE[L]/LDS[L]

UWE[L]/UDS[L]

RD/WR[L]

EPG_INT[L]

CS[0]

CS[1]

CS[3]

ALE

MADD[1-5]

MADD[6-21]

MADD[1]

MADD[2]

MADD[3]

MADD[4]

MADD[5]

R1217

R1218

R1219

R1220

R1221

LH_AR[1]

100

LH_AR[2]

100

LH_AR[3]

100

LH_AR[4]

100

LH_AR[5]

100

MADD[21]

MADD[20]

MADD[19]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

MADD[13]

MADD[12]

MADD[11]

MADD[10]

MADD[9]

MADD[8]

MADD[7]

MADD[6]

RA1201

10k

RA1202

10k

RA1203

10k

RA1204

10k

MADD[12]

MADD[13]

MADD[10]

MADD[11]

MADD[9]

MADD[7]

MADD[8]

MADD[6]

LH_AR[3]

LH_AR[4]

LH_AR[1]

LH_AR[2]

4.7k

R1229

D3.3V

4.7k

R1230

4.7k

R1231

C1208

TL1217

B1207

B1208

B1205

R1227

R1228

B1206

100

100

CN1202

2

TO VIDEO IF

SHEET 2

D5.0V

EPG_V_IN

1

GND

A

K1241

Q1241

R1246R1245 C1244C1243

2.7K6.8K

Q1242

Q1243

C1245

47

R1241

2.7K

R1242

3.3K

C1241

47

C1242

0.1

R1243

820

R1244

270P5.6K

R1248R1247

680680

Q1244

K1242

K1243

R1258

3.3K

R1259

3.3K

R1260

3.3K

C1259 C1254

C1260

0.001

C1261

0.22

R1261

C1246

47

C1247

47

BCD EFG

RA1243

0.1

C1262

0.1

0.1

C1248

2-9 2-10

C1250

0.22

C1249

C1258

RA1242

RA1241

0.1

R1253

IC1241

0.1

0.1

0.1

C1253

TL1241

0.1

0.1

C1251

C1252

R1257

R1256

R1251

1M

R1255

R1252

470

R1250

3.3K

R1249

R1254

10K

C1256

22p

X1241

C1255

22p

0Ω

C1257

22

p10659001a_rev0

SHEET 3

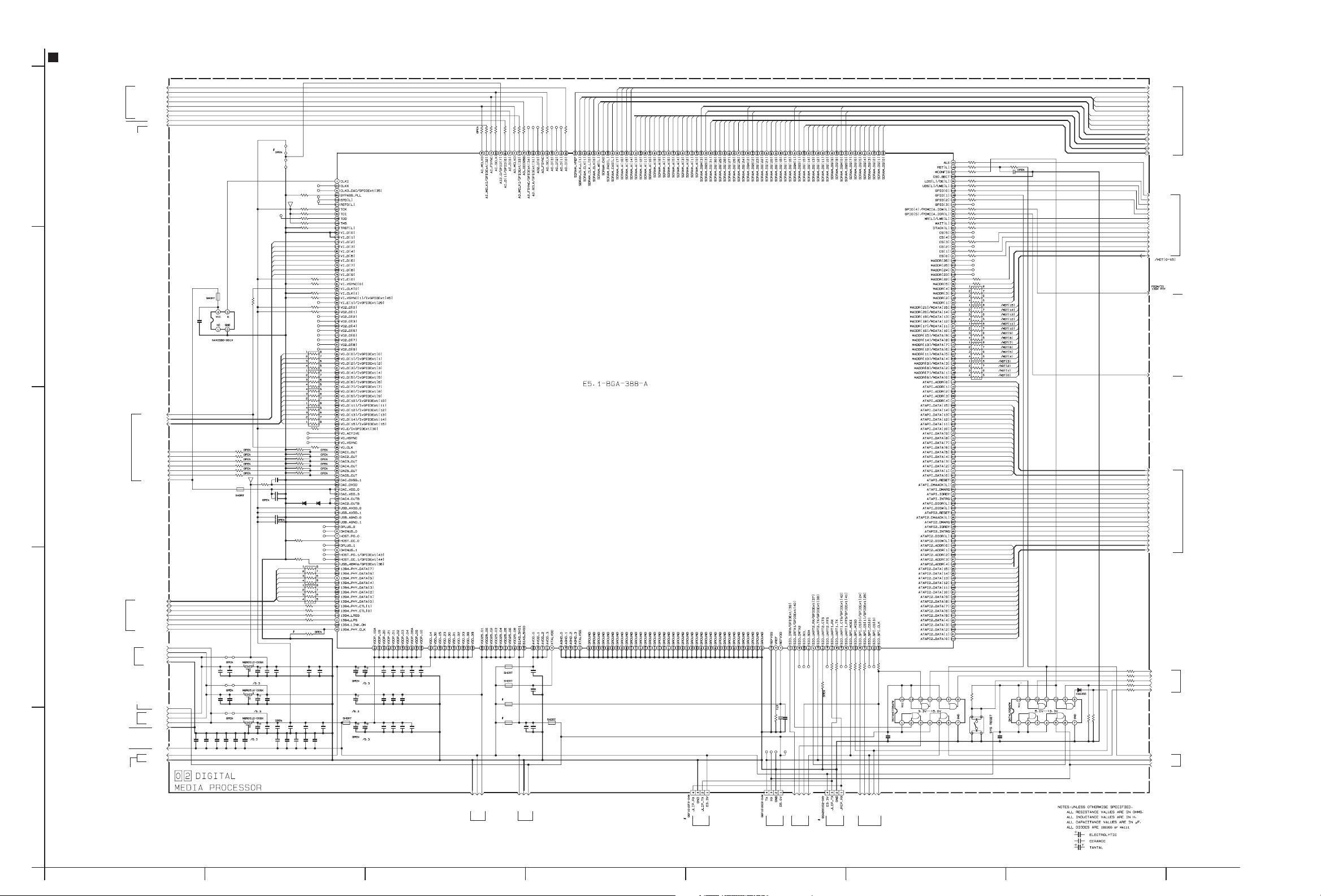

Page 8

DIGITAL(MEDIA PROCESSOR) SCHEMATIC DIAGRAM

5

4

3

2

TO VIDEO IF SHEET 2

1394 PHY SHEET 6

ATAPI IF SHEET 7

1

TO VIDEO IF

SHEET 2

TO 1394 PHY

SHEET 6

TO VIDEO IF

SHEET 2

TO 1394 PHY

SHEET 6

TO VIDEO IF

SHEET 2

TO VIDEO IF SHEET 2

TO ATAPI IF SHEET 7

TO VIDEO IF

TO ATAPI IF

SHEET 7

TO VIDEO IF

SHEET 2

SHEET 2

TO VIDEO IF

SHEET 2

VIDEO_MUTE[H]

PHY_DATA[0-7]

A

AO_D[0]

AO_SCLK

AO_FSYNC

AO_IEC958

AO_MCLKO

AI_D[0]

PHY_CNA

480I[H]

B1404

B1405

TL1402

TL1437

R1408

1k

VI_D[2]

VI_D[3]

VI_D[4]

VI_D[5]

VI_D[6]

VI_D[7]

VI_D[8]

VI_D[9]

VO_D[0]

VO_D[1]

VO_D[2]

VO_D[3]

VO_D[4]

VO_D[5]

VO_D[6]

VO_D[7]

VO_D[8]

VO_D[9]

VO_D[10]

VO_D[11]

VO_D[12]

VO_D[13]

VO_D[14]

VO_D[15]

TL1403

TL1404

R1409

10k

R1410

10k

R1411

100

R1412

10k

R1413

10k

R1414

1k

R1415

1k

R1416

1k

R1417

1k

TL1489

R1494

10k

R1495

10k

TL1452

TL1453

TL1454

TL1455

TL1456

TL1457

TL1458

TL1459

RA1401

100

RA1402

100

RA1403

100

RA1404

100

100

R1419

TL1412

TL1490

TL1491

100

R1420

R1485

R1486

R1487

R1488

R1489

R1490

D1402D1401

TL1413

TL1414

TL1415

1k

TL1417

TL1418

TL1419

100

TL1420

RA1405

100

RA1406

100

R1428

100

R1429

100

R1430

100

R1431

100

R1432

C1417

C1418

0.1

C1461

0.1

C1416

0.1

C1473C1472C1471C1469C1468C1467C1466C1465C1464 C1470

C1474

0.1

0.10.10.10.10.10.10.10.10.1 0.1

C1419

C1421

0.1

C1463

0.1

C1420C1404

SSTL2_VDD

K1401

C1425C1424C1423

C1422

0.10.10.1

0.10.11047

C1430C1429C1428C1427

C1439

C1438C1437C1436C1434 C1435

0.1

0.10.10.110

GND

TO DDR SDRAM

SHEET 5

D3.3V

TL1407

V3.3V

K1407

C1450

0.1

VIDEO_27M

VI_D[2-9]

VI_D[2-9]

VO_D[0-15]

VO_D[0-15]

DAC_CVBS_OUT

DAC_SY_OUT

DAC_SC_OUT

DAC_Y_OUT

DAC_PB_OUT

DAC_PR_OUT

V3.3V

PHY_CTL[1]

PHY_CTL[0]

PHY_LINK_ON

PHY_DATA[0-7]

PHY_LREQ

PHY_LPS

PHY_CLK

DIGI3.3V

D2.5V

D1.8V

GND

D5.0V

D5.0V

D1.8V

D2.5V K1405

DIGI3.3V

GND

GND

D3.3V

VDDI1.8

GND

R1402

0Ω

X1401

R1421

R1422

R1423

R1424

R1425

R1426

VDDI1.8

K1408

B1401

C1402

C1401

0.10.1

B1402

C1409

C1408

0.1

0.1

B1403

C1452

0.1

R1493

0Ω

C1453

0.1

C1454 1SS355-X 1SS355-X

0.1

C1455

C1456

R1491

R1427

PHY_DATA[7]

PHY_DATA[6]

PHY_DATA[5]

PHY_DATA[4]

PHY_DATA[3]

PHY_DATA[2]

PHY_DATA[1]

PHY_DATA[0]

LC1401

C1406

C1405

0.1

0.1

LC1402

C1411

C1412

0.1

100 0.10.10.110

LC1403

C1415

C1413 C1414

47 0.1

BCDEFG

SDRAM_A[14-17]

SDRAM_CLK_L[1]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK[0]

SDRAM_WE_L

SDRAM_CKE

0Ω

0Ω

100

100

270

100

100

R1478

R1479

R1476

R1480

R1481

R1483

D3.3V

SSTL2_VDD

R1482

R1477

K1402

C1442

0.1

K1403

K1404

C1445

0.1

GND

D3.3V

TO ATAPI IF

SHEET 7

TL1434

C1444

0.1

D5.0V

100

100

100

R1474

R1475

R1473

TL1432

TL1438

TL1439

TL1440

TL1433

C1446

0.1

SDRAM_CLK_L[1]

K1406

SDRAM_CAS_L

SDRAM_RAS_L

SDRAM_CKE

SDRAM_WE_L

SDRAM_CLK[0]

SDRAM_CLK_L[0]

SDRAM_CLK[1]

IC1401

DMN8652-BOL

SDRAM_A[17]

SDRAM_A[16]

SDRAM_A[15]

SDRAM_A[14]

SDRAM_A[13]

SDRAM_A[12]

SDRAM_A[11]

SDRAM_A[10]

SDRAM_A[9]

SDRAM_A[8]

SDRAM_A[7]

SDRAM_A[6]

SDRAM_A[5]

SDRAM_A[4]

SDRAM_A[3]

SDRAM_A[2]

CN1405

SDRAM_A[1]

SDRAM_A[0]

NOT

USED

SDRAM_DQS[3]

SDRAM_DQM[3]

SDRAM_DQ[31]

SDRAM_DQ[30]

SDRAM_DQ[28]

SDRAM_DQ[29]

SDRAM_DQ[26]

SDRAM_DQ[27]

SDRAM_DQ[24]

SDRAM_DQ[25]

SDRAM_DQS[2]

SDRAM_DQM[2]

SDRAM_DQ[22]

SDRAM_DQ[23]

CN1403

NOT

USED

SDRAM_DQ[20]

SDRAM_DQ[21]

TL1494

TL1495

SDRAM_DQ[18]

SDRAM_DQ[19]

1.18k

0.1

C1447

R1401

TL1493

SDRAM_DQS[1]

SDRAM_DQM[1]

SDRAM_DQ[16]

SDRAM_DQ[17]

TL1436

0.01

C1448

TL1492

A_MUTE2[H]

VIDEO_RST[L]

TO

VIDEO IF

SHEET 2

SDRAM_DQ[14]

SDRAM_DQ[15]

TL1441

TL1442

SPI_CLK

SPI_MOSI

SDRAM_DQ[10]

SDRAM_DQ[11]

SDRAM_DQ[12]

SDRAM_DQ[13]

TL1422

R1492

CN1402

JUNCTION

(VIDEO)

SHEET 23

SDRAM_DQ[8]

SDRAM_DQ[9]

100

100

R1434

R1435

TO

SDRAM_DQ[6]

SDRAM_DQ[7]

SDRAM_DQM[0]

SDRAM_DQS[0]

100

0Ω

R1436

R1437

TL1423

TL1424

TO VIDEO IF

SDRAM_DQ[2]

SDRAM_DQ[3]

SDRAM_DQ[4]

SDRAM_DQ[5]

100

100

TL1448

R1438

R1439

TL1425

A_DAC_CS

VIDEO_CS

SPI_MOSI

VIDEO_RXD

SHEET 2

SDRAM_DQ[0]

SDRAM_DQ[1]

100

R1440

SPI_CLK

100

R1471

R1469

R1468

R1467

R1466

R1465

R1464

TL1485

R1462

R1461

R1460

R1459

R1458

TL1484

TL1483

R1455

TL1481

R1453

R1452

TL1480

TL1479

TL1478

TL1477

R1451

R1450

RA1411

100

RA1410

100

RA1409

100

RA1408

100

RA1407

100

IC1404

R1472R1470

0Ω1k

C1459

1k

100

100

100

100

100

100

100

100

100

100

100

100

CS[1]

100

CS[0]

MADD[22]

100

MADD[5]

100

MADD[4]

MADD[3]

MADD[2]

MADD[1]

MADD[21]

MADD[20]

MADD[19]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

MADD[13]

MADD[12]

MADD[11]

MADD[10]

MADD[9]

MADD[8]

MADD[7]

MADD[6]

ATA_ADD[0]

ATA_ADD[1]

ATA_ADD[2]

ATA_ADD[3]

ATA_ADD[4]

ATA_DAT[15]

ATA_DAT[14]

ATA_DAT[13]

ATA_DAT[12]

ATA_DAT[11]

ATA_DAT[10]

ATA_DAT[9]

ATA_DAT[8]

ATA_DAT[7]

ATA_DAT[6]

ATA_DAT[5]

ATA_DAT[4]

ATA_DAT[3]

ATA_DAT[2]

ATA_DAT[1]

ATA2_ADD[0]

ATA2_ADD[1]

ATA2_ADD[2]

ATA2_ADD[3]

ATA2_ADD[4]

ATA2_DAT[15]

ATA2_DAT[14]

ATA2_DAT[13]

ATA2_DAT[12]

ATA2_DAT[11]

ATA2_DAT[10]

ATA2_DAT[9]

ATA2_DAT[8]

ATA2_DAT[7]

ATA2_DAT[6]

ATA2_DAT[5]

ATA2_DAT[4]

ATA2_DAT[3]

ATA2_DAT[2]

ATA2_DAT[1]

ATA2_DAT[0]

R1441

10k

IC1405

S1401

C1458C1457

0.10.1

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM_DQM[0-3]

SDRAM_DQS[0-3]

SDRAM_A[0-13]

SDRAM_DQ[16-31]

SDRAM_DQ[0-15]

MADD[1-5]

MADD[6-21]

ATA_ADD[0-4]

ATA_DAT[0-15]ATA_DAT[0]

ATA2_ADD[0-4]

ATA2_DAT[0-15]

D1403

4.7k

4.7k

R1443

R1444

SDRAM_A[14-17]

SDRAM_VREF

SDRAM_CLK_L[1]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK[0]

SDRAM_WE_L

SDRAM_CKE

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM_DQM[0-3]

SDRAM_DQS[0-3]

SDRAM_A[0-13]

SDRAM_DQ[16-31]

SDRAM_DQ[0-15]

ALE

OE[L]/LDS[L]

UWE[L]/UDS[L]

ELINK_INT[L]

EPG_INT[L]

RD/WR[L]

WAIT[L]

DTACK[L]

CS[3]

CS[1]

CS[0]

MADD[22]

MADD[1-5]

MADD[6-21]

PHY_RESET[L]

DAC_RST[L]

ATA_ADD[0-4]

ATA_DAT[0-15]

ATA_RESET

ATA_DMAACK[L]

ATA_DMARQ

ATA_IORDY

ATA_INTRQ

ATA_DIOR[L]

ATA_DIOW[L]

ATA2_RESET

ATA2_DMAACK[L]

ATA2_DMARQ

ATA2_IORDY

ATA2_INTRQ

ATA2_DIOR[L]

ATA2_DIOW[L]

ATA2_ADD[0-4]

ATA2_DAT[0-15]

100

R1445

100

R1446

R1447

100

R1448

100

100

R1449

K_BUS_CLK

K_BUS_REQ

SYS_RESET[L]

K_BUS_OUT

K_BUS_IN

E5_RESET[L]

UART2_TX

UART2_RX

TO DDR SDRAM

SHEET 5

TO

FLASH MEMORY

SHEET 3

TO 1394 PHY

SHEET 6

TO VIDEO IF

SHEET 2

TO ATAP I I F

SHEET 7

TO VIDEO IF

SHEET 2

TO

FLASH MEMORY

SHEET 3

p10658001a_rev0

SHEET 4

2-11 2-12

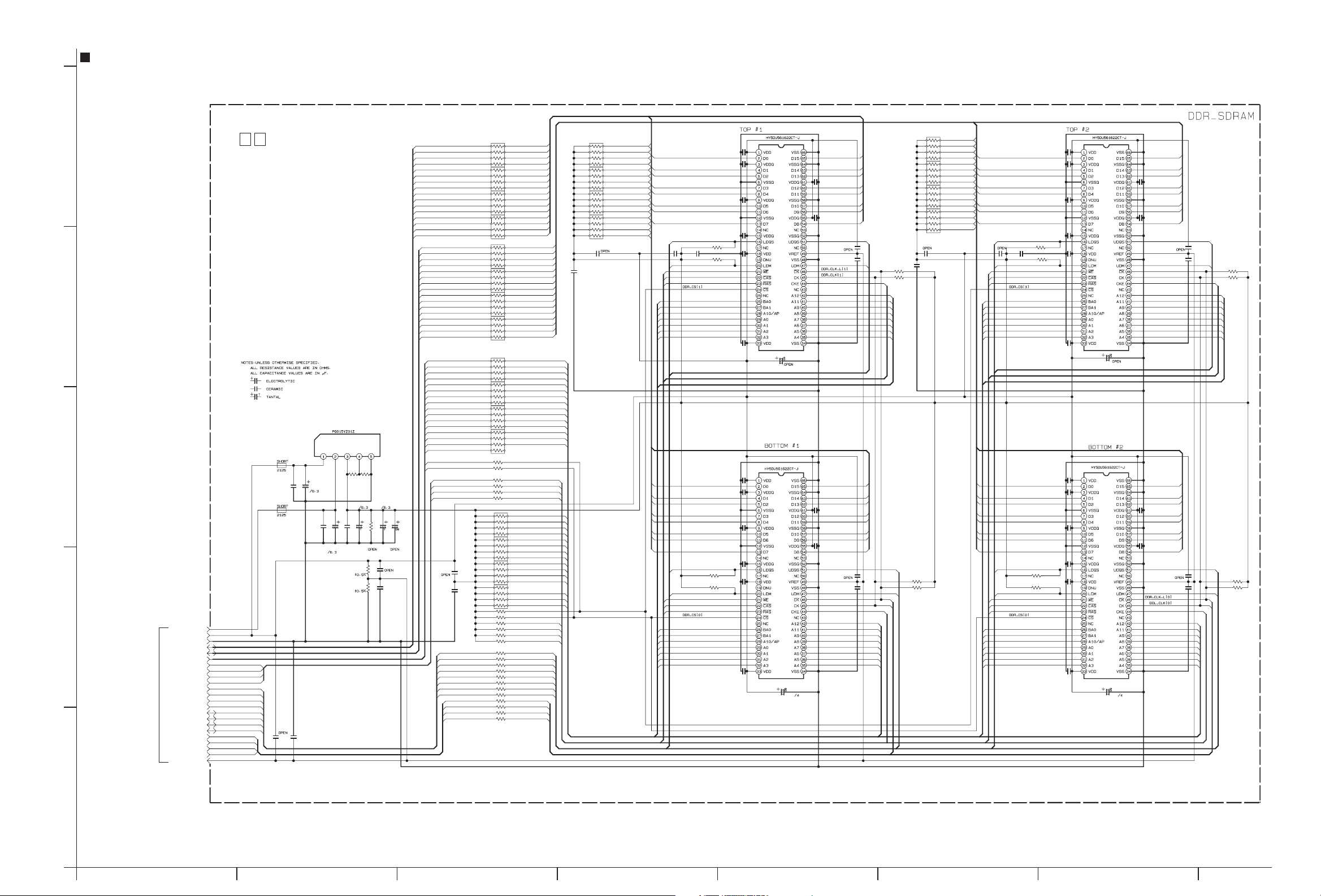

Page 9

DIGITAL(DDR SDRAM) SCHEMATIC DIAGRAM

5

4

3

2

MEDIA PROCESSOR

SHEET 4

TO

SSTL2_VDD

SDRAM_DQ[0-15]

SDRAM_DQ[16-31]

SDRAM_A[0-17]

SDRAM_CKE

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM_WE_L

SDRAM_DQM[0]

SDRAM_DQM[1]

SDRAM_DQM[2]

SDRAM_DQM[3]

SDRAM_DQS[0]

SDRAM_DQS[1]

SDRAM_DQS[2]

SDRAM_DQS[3]

SDRAM_CLK[0]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK_L[1]

SDRAM_VREF

D3.3V

C1604

IC1604IC1604

IC1602IC1602IC1602

IC1602

DDR_DQ[31]

DDR_DQ[30]

DDR_DQ[29]

C1633

0.1

DDR_DQ[28]

DDR_DQ[27]

DDR_DQ[26]

DDR_DQ[25]

C1632

0.1

DDR_DQ[24]

DDR_DQS[3]

DDR_DQM[3]

DDR_CLK_L[0]

DDR_CLK[0]

DDR_CKE

DDR_A[12]

DDR_A[11]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_DQ[16]

DDR_DQ[17]

DDR_DQ[18]

C1617

0.1

DDR_DQ[19]

DDR_DQ[20]

DDR_DQ[21]

DDR_DQ[22]

C1616

0.1

DDR_DQ[23]

DDR_DQS[2]

DDR_DQM[2]

DDR_CKE

DDR_A[12]

DDR_A[11]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[4]

C1661

C1662

C1657

C1658

0.1

0.1

R1628

R1627

R1631

R1632

100

100

100

100

IC1603IC1603 IC1604IC1603

IC1603 IC1604

20

DIGITAL(DDR_SDRAM)

IC1701

K1702

C1703 C1704

0.1 100

K1701

C1701

0.1

D3.3V

SSTL2_VDD

GND

GND

SDRAM_DQ[0-15]

SDRAM_DQ[16-31]

SDRAM_A[0-17]

SDRAM_CKE

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM_WE_L

SDRAM_DQM[0]

SDRAM_DQM[1]

SDRAM_DQM[2]

SDRAM_DQM[3]

SDRAM_DQS[0]

SDRAM_DQS[1]

SDRAM_DQS[2]

SDRAM_DQS[3]

SDRAM_CLK[0]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK_L[1]

SDRAM_VREF

C1653

C1654

0.1

C1702

R1701 R1702

270 1k

C1708

C1710

47

47

R1705

C1705

C1706

0.1

C1709

C1707

100

0.1

R1703

2.2k

R1704

2.2k

SDRAM_DQ[0]

SDRAM_DQ[1]

RA1609

SDRAM_DQ[2]

SDRAM_DQ[3]

SDRAM_DQ[4]

SDRAM_DQ[5]

SDRAM_DQ[6]

SDRAM_DQ[7]

SDRAM_DQ[8]

SDRAM_DQ[9]

SDRAM_DQ[10]

SDRAM_DQ[11]

SDRAM_DQ[12]

SDRAM_DQ[13]

SDRAM_DQ[14]

SDRAM_DQ[15]

SDRAM_DQ[16]

SDRAM_DQ[17]

SDRAM_DQ[18]

SDRAM_DQ[19]

SDRAM_DQ[20]

SDRAM_DQ[21]

SDRAM_DQ[22]

SDRAM_DQ[23]

SDRAM_DQ[24]

SDRAM_DQ[25]

SDRAM_DQ[26]

SDRAM_DQ[27]

SDRAM_DQ[28]

SDRAM_DQ[29]

SDRAM_DQ[30]

SDRAM_DQ[31]

C1645

C1646

0.1

22

RA1610

22

RA1611

22

RA1612

22

RA1613

22

RA1614

22

RA1615

22

RA1616

22

SDRAM_A[0]

RA1625

SDRAM_A[1]

22

SDRAM_A[2]

SDRAM_A[3]

SDRAM_A[4]

RA1626

SDRAM_A[6]

22

SDRAM_A[8]

SDRAM_A[11]

SDRAM_A[5]

RA1627

SDRAM_A[7]

22

SDRAM_A[9]

SDRAM_A[12]

SDRAM_A[10]

RA1628

SDRAM_A[15]

22

SDRAM_A[14]

SDRAM_A[13]

SDRAM_A[16]

SDRAM_A[17]

SDRAM_CKE

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM_WE_L

R1641

R1642

R1601

R1602

R1603

R1604

RA1629

100

RA1630

100

RA1631

100

RA1632

100

R1643

R1644

R1605

R1606

R1607

R1608

SDRAM_DQM[0]

SDRAM_DQM[1] DDR_A[5]

SDRAM_DQM[2]

SDRAM_DQM[3]

SDRAM_DQS[0]

SDRAM_DQS[1]

SDRAM_DQS[2]

SDRAM_DQS[3]

SDRAM_CLK[0]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK_L[1]

R1653

R1654

R1655

R1656

R1657

R1658

R1659

R1660

R1613

R1614

R1615

R1616

22

22

22

22

22

22

DDR_CS[1]

DDR_CS[0]

100

100

100

100

100

100

22

22

22

22

22

22

22

22

22

22

22

22

DDR_DQ[0]

DDR_DQ[1]

DDR_DQ[2]

DDR_DQ[3]

DDR_DQ[4]

DDR_DQ[5]

DDR_DQ[6]

DDR_DQ[7]

DDR_DQ[8]

DDR_DQ[9]

DDR_DQ[10]

DDR_DQ[11]

DDR_DQ[12]

DDR_DQ[13]

DDR_DQ[14]

DDR_DQ[15]

DDR_DQ[16]

DDR_DQ[17]

DDR_DQ[18]

DDR_DQ[19]

DDR_DQ[20]

DDR_DQ[21]

DDR_DQ[22]

DDR_DQ[23]

DDR_DQ[24]

DDR_DQ[25]

DDR_DQ[26]

DDR_DQ[27]

DDR_DQ[28]

DDR_DQ[29]

DDR_DQ[30]

DDR_DQ[31]

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

DDR_A[4]

DDR_A[6]

DDR_A[8]

DDR_A[11]

DDR_A[5]

DDR_A[7]

DDR_A[9]

DDR_A[12]

DDR_A[10]

DDR_BA[1]

DDR_BA[0]

DDR_CKE

DDR_RAS_L

DDR_CAS_L

DDR_WE_L

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

DDR_A[4]

DDR_A[5]

DDR_A[6]

DDR_A[7]

DDR_A[8]

DDR_A[9]

DDR_A[11]

DDR_A[12]

DDR_A[10]

DDR_BA[1]

DDR_BA[0]

DDR_RAS_L

DDR_CAS_L

DDR_WE_L

DDR_DQM[0]

DDR_DQM[1]

DDR_DQM[2]

DDR_DQM[3]

DDR_DQS[0]

DDR_DQS[1]

DDR_DQS[2]

DDR_DQS[3]

DDR_CLK[0]

DDR_CLK[1]

DDR_CLK_L[0]

DDR_CLK_L[1]

DDR_CKE

RA1617

100

RA1618

100

RA1619

100

RA1620

100

DDR_DQ[0]

DDR_DQ[1]

DDR_DQ[2]

DDR_DQ[3]

DDR_DQ[4]

DDR_DQ[5]

DDR_DQ[6]

DDR_DQ[7]

DDR_DQ[8]

DDR_DQ[9]

DDR_DQ[10]

DDR_DQ[11]

DDR_DQ[12]

DDR_DQ[13]

DDR_DQ[14]

DDR_DQ[15]

C1641 C1650

C1642

0.1

RA1621

R1622

R1621

RA1622

RA1623

RA1624

R1629

R1630

100

100

100

100

100

100

C1626

R1620

R1618

R1619

0.1

R1617

0.1

C1621

0.1

C1622

0.1

C1623

0.1

100

C1627

0.1

100

C1628

0.1

C1603

IC1601

IC1601IC1601

IC1601

C1610

0.1

C1605

0.1

C1606

0.1

C1607

0.1

100

C1611

0.1

100

C1612

0.1

C1601 C1602

220 220

DDR_DQ[15]

DDR_DQ[14]

DDR_DQ[13]

C1625

0.1

DDR_DQ[12]

DDR_DQ[11]

DDR_DQ[10]

DDR_DQ[9]

C1624

0.1

DDR_DQ[8]

DDR_DQS[1]

DDR_DQM[1]

DDR_CKE

DDR_A[12]

DDR_A[11]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

C1609

0.1

C1608

0.1

DDR_CLK_L[1]

C1659

C1660

0.1

DDR_DQ[0]

DDR_DQ[1]

DDR_DQ[2]

DDR_DQ[3]

DDR_DQ[4]

DDR_DQ[5]

DDR_DQ[6]

DDR_DQ[7] DDR_DQ[24]DDR_DQ[8]

DDR_DQS[0]

C1655

C1656

0.1

DDR_DQM[0]

DDR_CLK[1]

DDR_CKE

DDR_A[12]

DDR_A[11]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_DQ[0]

DDR_DQ[1]

DDR_DQ[2]

DDR_DQ[3]

DDR_DQ[4]

DDR_DQ[5]

DDR_DQ[6]

DDR_DQ[7]

DDR_DQS[0]

C1649 C1651 C1643

0.1

DDR_DQM[0]

DDR_WE_L

DDR_CAS_L

DDR_RAS_L

DDR_BA[0]

DDR_BA[1]

DDR_A[10]

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

DDR_DQ[15]

DDR_DQ[14]

DDR_DQ[13]

DDR_DQ[12]

DDR_DQ[11]

DDR_DQ[10]

DDR_DQ[9]

DDR_DQS[1]

DDR_DQM[1]

DDR_WE_L

DDR_CAS_L

DDR_RAS_L

DDR_BA[0]

DDR_BA[1]

DDR_A[10]

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

C1652

0.1

100

100

DDR_DQ[16]

DDR_DQ[17]

DDR_DQ[18]

DDR_DQ[19]

DDR_DQ[20]

DDR_DQ[21]

DDR_DQ[22]

DDR_DQ[23]

DDR_DQ[24]

DDR_DQ[25]

DDR_DQ[26]

DDR_DQ[27]

DDR_DQ[28]

DDR_DQ[29]

DDR_DQ[30]

DDR_DQ[31]

DDR_DQ[16]

DDR_DQ[17]

DDR_DQ[18]

DDR_DQ[19]

DDR_DQ[20]

DDR_DQ[21]

DDR_DQ[22]

DDR_DQ[23]

DDR_DQS[2]

C1644

DDR_DQM[2]

DDR_WE_L

DDR_CAS_L

DDR_RAS_L

DDR_BA[0]

DDR_BA[1]

DDR_A[10]

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

DDR_DQ[31]

DDR_DQ[30]

DDR_DQ[29]

DDR_DQ[28]

DDR_DQ[27]

DDR_DQ[26]

DDR_DQ[25]

DDR_DQS[3]

R1626

R1624

DDR_DQM[3]

DDR_WE_L

DDR_CAS_L

DDR_RAS_L

DDR_BA[0]

DDR_BA[1]

DDR_A[10]

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[3]

R1625

0.1

R1623

C1634

0.1

C1629

0.1

C1630

0.1

C1631

0.1

100

C1635

0.1

100

C1636

0.1

C1618

0.1

C1613

0.1

C1614

0.1

C1615

0.1

100

C1619

0.1

100

C1620

0.1

1

p10614001a_rev0

SHEET 5

A

BCD EFG

2-13 2-14

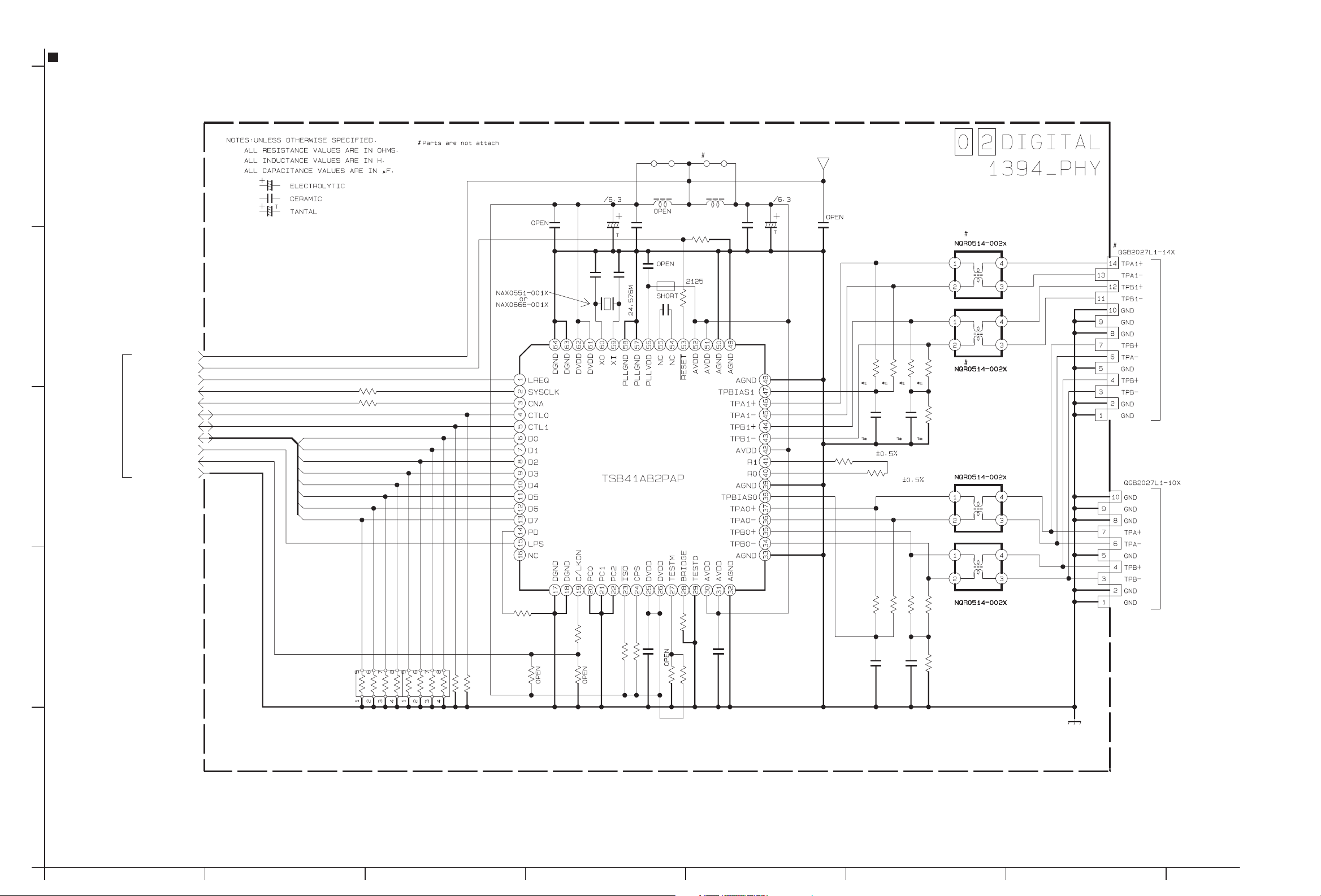

Page 10

DIGITAL(1394 PHY) SCHEMATIC DIAGRAM

5

4

MEDIA PROCESSOR

3

TO

SHEET 4

D3.3V

PHY_RESET[L]

PHY_LREQ

PHY_CLK

PHY_CNA

PHY_CTL[0]

PHY_CTL[1]

PHY_DATA[0-7]

PHY_LPS

PHY_LINK_ON

GND

PHY_DATA[0-7]

R1801

R1802

PHY_DATA[0]

PHY_DATA[1]

PHY_DATA[2]

PHY_DATA[3]

PHY_DATA[4]

PHY_DATA[5]

PHY_DATA[6]

PHY_DATA[7]

0Ω

0Ω

C1813

X1801

12p

C1809

1801_X0

12p

C1808

1801_XI

IC1801

C1805

0.1

C1810

K1801

C1807

0.1

R1820

10k

0Ω

R1822

B1801B1802

L1801L1802 C1804

0.1

10

µ

D3.3V

C1803C1806

1010

C1814

T1804T1804

R1819

TPA0+

TPA0-

TPB0+

TPB0-

R1823

C1815

750

R1818

T1804T1804

TPA1+

TPA1-

TPB1+

TPB1-

56

56

56

56

R1826

R1825

R1824

5.1k

5.6k

270p

C1816

R1827

156

T1803T1803

T1803T1803

T1802T1802

T1802T1802

TPA+

TPA-

TPB+

CN1802

CN1801

TO JUNCTION(VIDEO)

CN7121

SHEET 23

NOT

USED

TPB-

56

56

565.1k

R1805

2

10k

10k

RA1801

10k

RA1802

10k

R1803

R1804

0Ω

R1806

R1808 R1807

10k

10k

R1809

390k

R1810

0.1

C1811

R1812

1k

R1821

R1811

0Ω

0.1

C1812

TPBIAS0

R1813

1

C1801

R1814

R1815

270p

C1802

R1816R1817

T1801T1801

T1801T1801

GND

1

p30128001a_rev0

SHEET 6

A

BCDEFG

2-15 2-16

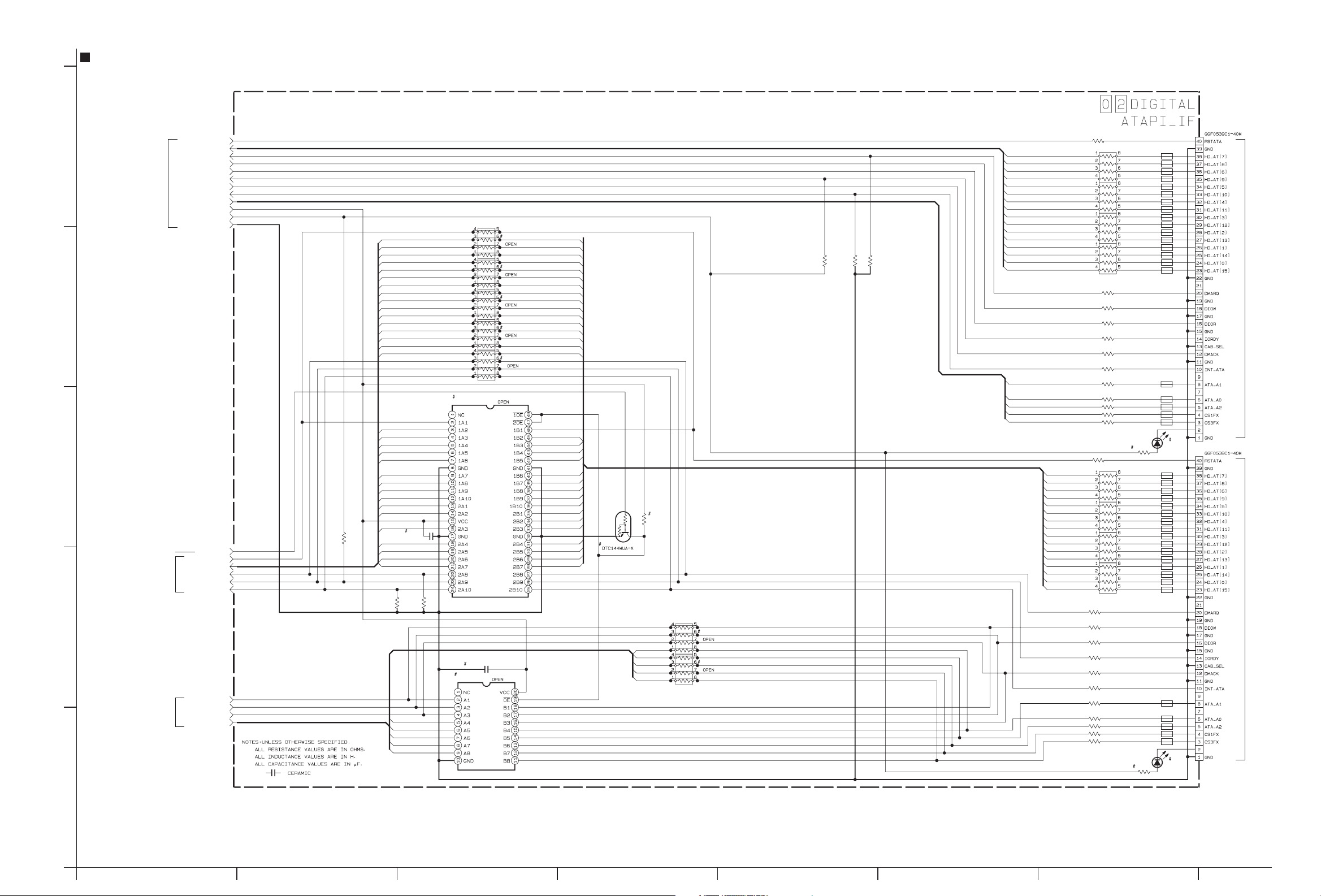

Page 11

DIGITAL(ATAPI IF) SCHEMATIC DIAGRAM

5

TO MEDIA PROCESSOR

4

3

TO MEDIA PROCESSOR

2

TO MEDIA PROCESSOR

1

SHEET 4

TO VIDEO IF

SHEET 2

SHEET 4

SHEET 4

ATA2_RESET

ATA2_DAT[0-15]

ATA2_DMARQ

ATA2_DIOW[L]

ATA2_DIOR[L]

ATA2_IORDY

ATA2_DMAACK[L]

ATA2_INTRQ

ATA2_ADD[0-4]

P_CTL[H]

ATA_RESET

ATA_DAT[0-15]

ATA_DMARQ

ATA_IORDY

ATA_INTRQ

ATA_DIOW[L]

ATA_DIOR[L]

ATA_DMAACK[L]

ATA_ADD[0-4]

D5.0V

D3.3V

GND

ATA2_DAT[0-15]

ATA2_ADD[0-4]

D5.0V

D3.3V

GND

ATA_DAT[0-15]

ATA_ADD[0-4]

4.7k

R2203

ATA_DAT[7]

ATA_DAT[8]

ATA_DAT[6]

ATA_DAT[9]

ATA_DAT[5]

ATA_DAT[10]

ATA_DAT[4]

ATA_DAT[11]

ATA_DAT[3]

ATA_DAT[12]

ATA_DAT[2]

ATA_DAT[13]

ATA_DAT[1]

ATA_DAT[14]

ATA_DAT[0]

ATA_DAT[15]

R2201

10k

ATA_DAT[7]

ATA_DAT[8]

ATA_DAT[6]

ATA_DAT[9]

ATA_DAT[5]

ATA_DAT[10]

ATA_DAT[4]

ATA_DAT[11]

ATA_DAT[3]

ATA_DAT[12]

ATA_DAT[2]

ATA_DAT[13]

ATA_DAT[1]

ATA_DAT[14]

ATA_DAT[0]

ATA_DAT[15]

C2201

0.1

R2202

5.6k

ATA_ADD[0]

ATA_ADD[1]

ATA_ADD[2]

ATA_ADD[3]

ATA_ADD[4]

IC2201

CD4052BM-X

C2202

IC2202

RC4558D-X

R2104

33

82

22

22

82

22

82

33

33

33

33

33

RA2101

33

RA2102

33

RA2103

33

RA2104

33

RA2208

33

RA2209

33

RA2210

33

RA2211

33

R2116

R2216

K2101

K2102

K2103

K2104

K2105

K2106

K2107

K2108

K2109

K2110

K2111

K2112

K2113

K2114

K2115

K2116

K2117

K2118

K2119

K2120

K2121

D2101

220

K2201

K2202

K2203

K2204

K2205

K2206

K2207

K2208

K2209

K2210

K2211

K2212

K2213

K2214

K2215

K2216

K2217

K2218

K2219

K2220

K2221

D2201

220

ATA2_DAT[7]

ATA2_DAT[8]

ATA2_DAT[6]

ATA2_DAT[9]

ATA2_DAT[5]

ATA2_DAT[10]

ATA2_DAT[4]

ATA2_DAT[11]

ATA2_DAT[3]

ATA2_DAT[12]

ATA2_DAT[2]

RA2201

R2101 R2102R2103

4.7k 10k 5.6k

RA2202

RA2203

RA2204

RA2205

ATA_DAT[7]

ATA_DAT[8]

ATA_DAT[6]

ATA_DAT[9]

ATA_DAT[5]

ATA_DAT[10]

ATA_DAT[4]

ATA_DAT[11]

ATA_DAT[3]

ATA_DAT[12]

ATA_DAT[2]

ATA_DAT[13]

ATA_DAT[1]

ATA_DAT[14]

ATA_DAT[0]

ATA_DAT[15]

0.1

Q2201

2SC2412K/QRS/

R2217

22k

ATA_ADD[0]

ATA_ADD[1]

ATA_ADD[2]

ATA_ADD[3]

ATA_ADD[4]

RA2206

RA2207

ATA2_DAT[13]

ATA2_DAT[1]

ATA2_DAT[14]

ATA2_DAT[0]

ATA2_DAT[15]

ATA2_ADD[1]

ATA2_ADD[0]

ATA2_ADD[2]

ATA2_ADD[3]

ATA2_ADD[4]

R2204

ATA_DAT[7]

ATA_DAT[8]

ATA_DAT[6]

ATA_DAT[9]

ATA_DAT[5]

ATA_DAT[10]

ATA_DAT[4]

ATA_DAT[11]

ATA_DAT[3]

ATA_DAT[12]

ATA_DAT[2]

ATA_DAT[13]

ATA_DAT[1]

ATA_DAT[14]

ATA_DAT[0]

ATA_DAT[15]

R2205

R2206

R2207

R2208

R2209

R2210

R2211

R2212

R2213

R2214

R2215

R2105

R2106

R2107

R2108

R2109

R2110

R2111

R2112

R2113

R2114

R2115

33

82

22

22

82

22

82

33

33

33

33

33

CN2101

HDD

CN2201

DVD

p20437001a_rev0

SHEET 7

A

BCD EFG

2-17 2-18

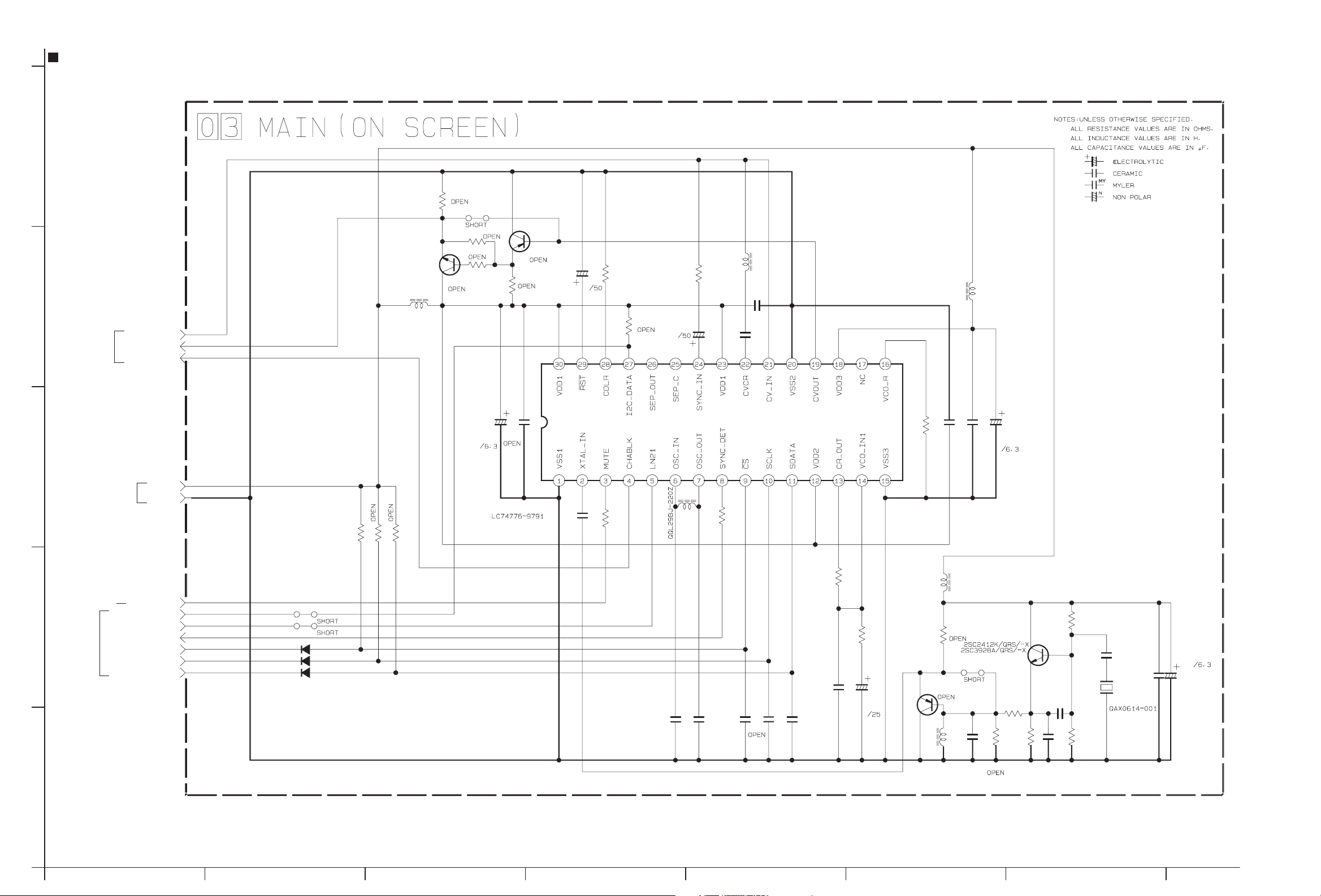

Page 12

MAIN(ON SCREEN) SCHEMATIC DIAGRAM

5

4

TO VIDEO SW DV

SHEET 9

V_TO_OSD

DV_V_OUT

CHARA_DATA

L201

1

µ

R225

B206

R223

R224

Q208

2SC2412K/QRS

Q207

2SA1037AK/QR

R212

C222

1

R216

10K

R220

R213

0Ω

C218

1

L206

22

C217

56p

µ

C209

0.47

L204

10

µ

3

TO VIDEO SW DV

2

TO SYSCON

SHEET 9

TO SYSCON

SHEET 13

SHEET 13

TO SYSCON

SHEET 13

SYNC_DET2[H]

S.DATA_FRSYS

SW5V

GND

P.MUTE[L]

I2C_DATA2

I2C_CLK2

OSD_CS

S.CLK

B204

B203

D201

D202

D203

1.5kΩ

100

100

10k

R202

NRSA63J-152X

NRSA63J-101X

NRSA63J-101X

R203

R204

C201

220

C202

IC201

C236

0.01

R226

1k

L203

C215

B231

C225

220

Q232

R233

470

R234

820

C232

820p

R236

3.3k

C237

18p

X231

C233

0.1

C234

100

C214

R211

0.22 0.22

5.6K

R208

2.2k

R209

6.8k

L231

µ

10

R231

R210

1.8k

Q231

C213C212

4.70.1

C210

33p33p

C208C207C206

C211

100p100p

C235

R232

C231L232

150p8.2

µ

0.001

R235

k

10

1

p30132001a_rev0

SHEET 8

A

BCDEFG

2-19 2-20

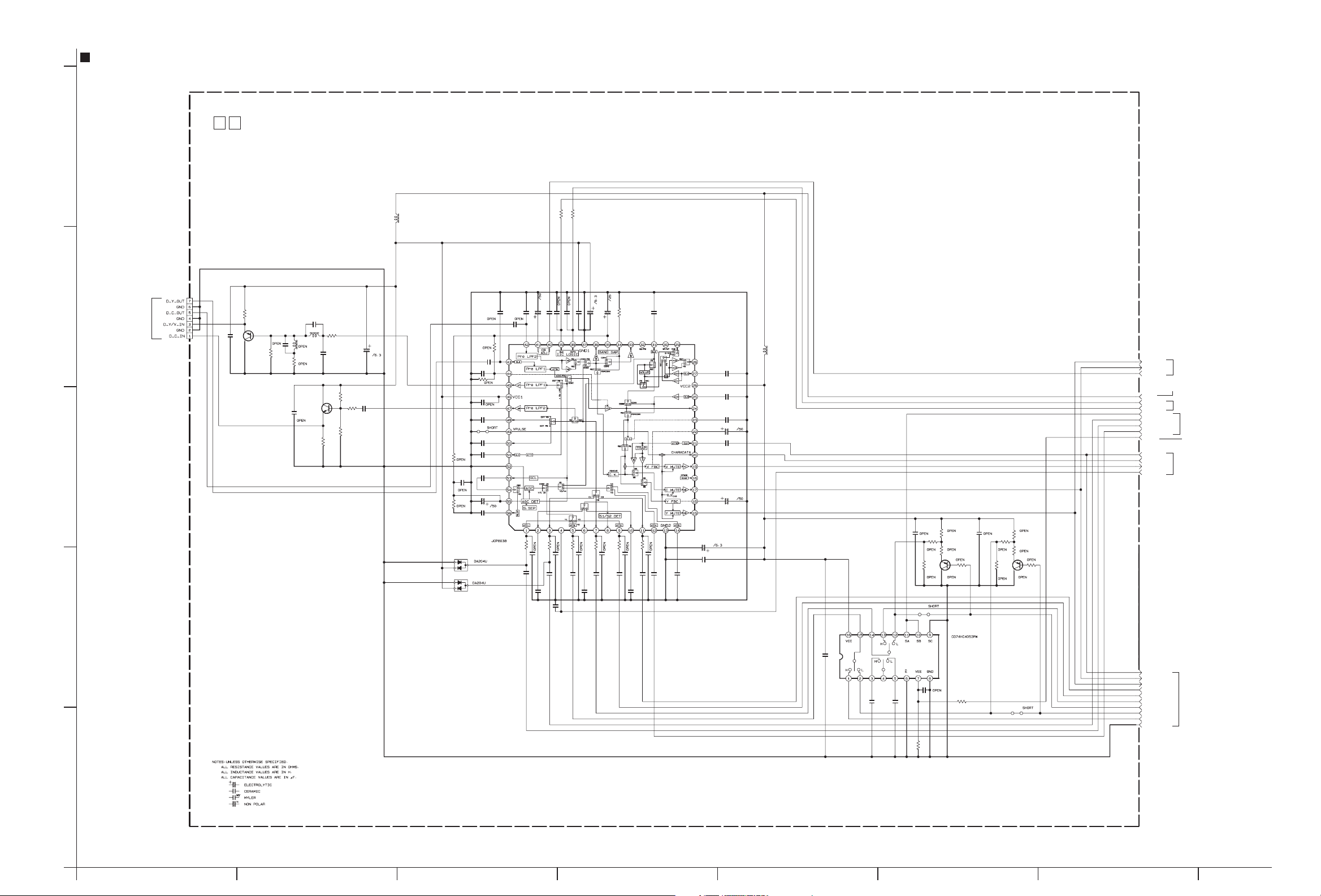

Page 13

MAIN(VIDEO SW DV) SCHEMATIC DIAGRAM

30

5

MAIN(VIDEO SW DV)

0`

L502

10

µ

0`

R511

R512

4

3

2

TO DV MAIN

(DV VIDEO OUT)

CN3501

SHEET 20

CN501

47

C531

C532

R504

0Ω

C507

C508

µ

1

C529

C528

C530

10

0.01

R507

R505

0`

0`

C511

C509

C513

C512

µ

1

0.01

C510 C515

0.01

C527

0.01

R510

3.3k

L501

10

µ

DV_Y_OUT

C526

0.01

C525

0.01

C524

0.01

C523

2.2

C522

1

µ

C521

2.2

R557

C501

R509

0`

C514

C517

C518

C516

0.01

0.01

1µ0.01

C519

47

C502

0.1

C560

0.1

C567

R558

R559

Q512

R560

B503

C566

R556

IC502

R552

R554

R553

R551

Q511

R555

TO VIDEO SW VDR

DV_C_OUT

SHEET 10

fSC

TO SYSCON

SHEET 13

SW5V

TO TERMINAL(I/O) SHEET 11

I2C_DATA2

I2C_CLK2

TO SYSCON SHEET 13

TO_DV_DUB[L]

FRONT_C_IN

FRONT_Y_IN

FRONT_V_IN

SW-7V

DV_V_OUT

CHARA_DATA

V_TO_OSD

P.MUTE[L]

TO SYSCON

SHEET 13

TO

VIDEO SW VDR

SHEET 10

TO ON SCREEN

SHEET 8

C534

C533

0.01

R542

1k

Q505

2SB709A/QR

C547

0.01

C548

R518

1.8k

C549

10p

L504

R521

33

µ

270

L503

C550

82p

R519

Q503

2SD601A/QRS

C555

R526

1k

R527

5.6k

R529

2.2k 0.01

R528

5.6k

C557

47

C556

C536

R513

1

C552

C537

0.01

R514

C538

C539

0.01

B501

C540

0.01

C541

0.01

R515

C543

0.1

C544

C545

2.2

R516

C546

0.01

IC501

D502

D501

4.7

C535

C551

0.1

R503

R501

0`

0`

C504

C506

0.01

C503

µ

1

C505

0.01

C520

0.01

DV_V_OUT

DV_C_OUT

C562

0.01

C563

0.01

C561

R531

8.2k

R532

10k

B502

DV_Y_OUT

REAR1_C_IN

REAR1_YV_IN

REAR2_C_IN

TO_DV_DUB_C

TO_DV_DUB_Y

REAR2_YV_IN

GND

TO TERMINAL(I/O)

SHEET 11

1

p10695001a_rev0

SHEET 9

A

BCD EFG

2-21 2-22

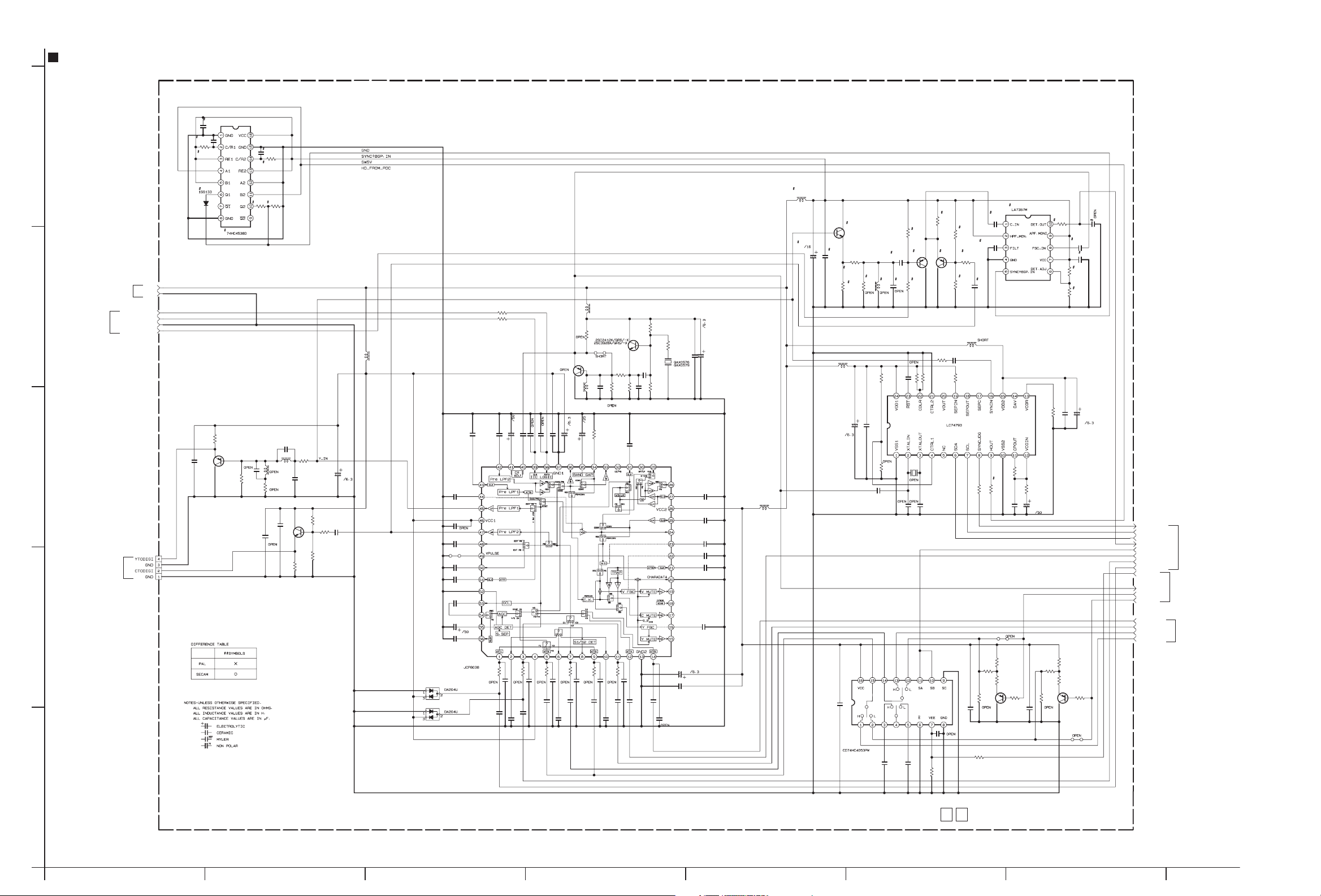

Page 14

MAIN(VIDEO SW VDR) SCHEMATIC DIAGRAM

C636

0.1

C637

5

470p

R638

12k

C635

470p

R635

12k

4

TO SYSCON

SHEET 13

3

TO JUNCTION(VIDEO)

TO RE G

SHEET 1

CN7123

SHEET 23

I2C_DATA_A/V

I2C_CLK_A/V

SEPA_IN[H]

CN701

SW5V

D631

R637

R636

10k

22k

IC631

GND

R711

0Ω

R712

GND

L702

10

µ

R717

1k

Q701

C747

0.01

2SB709A/QR

C748

R718

1.8k

L703

R719

C755

0.1

C751

C749

10p

L704 R721

µ

33

Q703

2SD601A/QRS/-X

R726

1k

270

C750

82p

R727

5.6k

R729

2.2k 0.01

R728

5.6k

C765

47

C756

C736

0.01

C737

0.01

C738

C739

0.01

B701

C740

0.01

C741

0.01

C743

0.1

0Ω

C734

C731

C732

C733

C730

0.01

4.7

C735

0.01

0.01

L706

10

µ

R746

3.3k

C769

820p

820

C768

R747

0.001

10k

100

R748

C771

C772

0

0.1

X701

C726

0.01

C725

0.01

C724

0.01

C723

0.01

C722

0.01

µ

10

2SD601A/QRS/-X

B702

R743C767L707

150p8.2

R710

3.3k

Q706

R744

470

R745

C727

0.01

R742

Q705

47

C728

C729

L601

10

µ

IC601

R606

Q601

C602

47

C601 C609

0.01

R602

R601

560

L621

10

µ

C621 C622

220

µ

10

L701

C604

0.01

0

R603

L602 C603

R621

10k

C623

1

0.1

R626

C631

0.01

C625 C626

R604

22k

Q602 Q603

R605

5.6k

R622

10K

R623

X621

1.2k

R624

C624

0

1

R625

0

IC621

C606

0.01

R607

10k

C607

0.01

R620

0

R608

C605

22k

0.01

L622

R629

10k

R628

R627

0

0

C627

0.056

R612

R631

5.6k

R630

2.7k

C628

4.7

C611

0Ω

C608

0.01

0.01

R609

2.2k

R610

8.2k

C630

220

C629

0.22

SYNC_DET1[H]

I2C_CLK2

I2C_DATA2

SECAM_DET[H]

TO_VDR_DUB[L]

FRONT_V_IN

FRONT_C_IN

FRONT_Y_IN

SW-7V

fSC

DV_C_OUT

DV_Y_OUT

TO SYSCON

SHEET 13

TO VIDEO SW DV

SHEET 9

C745

2

2.2

C746

0.01

IC701

D701

D702

R703

R701

C704

C703

1

R704

0Ω0Ω

0Ω

C707

C708

1

C706

0.01

C705

0.01

R707

R706

0Ω

0Ω

C714 C717C709

C711

C713

C712

1

0.01

C710 C715

0.01 0.01

R709

0Ω

C716

0.01

C718 C719

11

C720

C721

0.01

B704

R757

470

R759

C701

47

C702

0.1

C773

0.01

C774

IC702

C775 C776

0.01 0.01

R732

10k

0Ω

R758

470

R756 R751

0Ω 0Ω

Q712

2SB709A/QR/-X

C778 C777

0.01 0.01

R731

8.2k

R752

470

R754

0Ω

R753

470

R755R760

Q711

2SB709A/QR/-X

B703

TU_VIDEO

REAR1_C_IN

REAR2_C_IN

IF_SEL_YV_IN

TO TERMINAL(I/O)

SHEET 11

1

MAIN(VIDEO SW VDR)

30

p10694001a_rev0

SHEET 10

A

BCDEFG

2-23 2-24

Page 15

MAIN(TERMINAL I/O) SCHEMATIC DIAGRAM

MAIN(TERMINAL I/O)

30

5

R902

22k

Q901

2SD601A/QRS/

R901

10k

R903

18k

TO_DV_DUB_Y

TO_DV_DUB_C

TO

REAR2_C_IN

CN7107

SHEET 23

REAR2_YV_IN

REAR1_YV_IN

TO

REAR1_C_IN

DV_Y_OUT

DV_C_OUT

CN901

0.1

C945

C947

0.01

VIDEO SW DV

4

SHEET 9

JUNCTION(VIDEO)

3

Q902

2SD601A/QRS/

C948

0.01

R919

130

R914

100

10

µ

R909

75

Q903

R904

470k

IC903

C946

0.1

R932

R931

8.2k

10k

D901

R910

75

C901

470

C950

10

C951

10

C952

10

J902

75

75

R912

R911

R999

10K

L901

R915

µ

10

L902

C902 C903

C904 C905

330p 330p

330p 330p

L904

75

L905

R913

C941 C940

C939

11

C937

1

C942

4.7

100

L903

µ

1

470p

470p

470p

470p

C908

C909

C906

C907

L931

10

4.7

4.7

10

µ

µ

µ

L932

µ

10

C910

C911

C934

C935

0.01

0.01

Q907

2SB709A/QR

R918

C913

C912

C996

0.01

C966

C930

C932

0.01

0.1

1k

Q904

R990

27k

Q932

2SB709A/QR/

R991

47k

IC901

L914

D902

180`

QRE141J-181Y

R992 R993

1k 39k

C956

47

C960

0.01

C953

1

µ

C954

C955

L916

Q908

2SB709A/QR

R920

0Ω

Q933

2SB709A/QR/

C997

0.01

1

C957

100p

1

2SB709A/QR/

1

C959

R921

1K

B903

Q909

L917

10

µ

R994

10k

µ

R982

1

1k

C969

47k

R983

Q936

39k

R984

L918

10

µ

R922

75

J901

D903

Q944

L919

10

µ

C963

47

R971

R925

R924

R923

68

75

C914

470

75

C915

330

B904

R945R944

C964

0.01

330330

R939

Q912

100

2SB709A/QR/

R940

100

R926

75

C917C916

330330

Q913

2SB709A/QR/

C918 C919

330p 330p

C968

0.01

L906

L907

L909

L910

R965 R966

330 5.6k

Q941

2SB709A/QR/

0`0`0`

R941

10

10

C920 C921

330p 330p

470p

C922

R967

5.6k

Q942

IC902

R942

R943

100

µ

R927

R928

µ

100

L908

µ

0.22

470p

470p

470p

C924

C925

C923

4.7

4.7

C967

47

C926

C927

L933

10

µ

µ

µ

L934

µ

10

C929

C928

R968

3.3k

R969

100

Q943

R972

C981

R985

470

75

C982

R986

330

75

C983

R987

330

75

C965

0.01

J905

2

TO VIDEO SW DV

TO VIDEO SW VDR SHEET 10

TO VIDEO SW VDR

1

TO REG

SHEET 1

TO SYSCON

SHEET 13

TO REG

SHEET 1

TO VIDEO SW DV SHEET 9

TO TUNER SHEET 14

TO VIDEO SW VDR

SHEET 10

TO TUNER

SHEET 14

SHEET 9

TO TUNER SHEET 14

TO VIDEO SW DV

SHEET 9

SHEET 10

TO SYSCON

SHEET 13

TO AUDIO I/O

SHEET 12

A

TO SYSCON

SHEET 13

REAR1_C_IN

REAR2_C_IN

I2C_DATA2

IF_SEL_YV_IN

AV1_YC_IN[H]

DEC_A.OUT[L]

DEC_A.OUT[R]

A.IN1[L]

A.IN1[R]

A.IN2[L]

A.IN2[R]

LINE_OUT[L]

LINE_OUT[R]

AD_IEC958

RGB[H]

SW-7V

P50_I/O

SCR[H]

P.ON_P

SW12V

SW5V

RF_VIDEO

I2C_CLK2

TU_VIDEO

DV_V_OUT

A.GND

V3.3V

R953

R973

Q914

100

C961

C962

47

0.01

R937

100

C944

47

D904

GND

GND

C971

0.01

L920

10

µ

2SB709A/QR/

Q915

R975

2SB709A/QR/

100

C973

C972

47

470

R976R974

330330

R961

470

R960

470

K851

K852

B851

B852

B853

L852

C857

µ

1

0.1

C858 C859R857

100

0.1100k

CN902

J851

FW851

CN951

CN852

L935

10

µ

C991 C992

47 0.01

C852C851

0.1100

R851

4.7

R956

100

Q921

2SB709A/QR

R957

330

IC851

C993

R954

100

R955

100

C951

C853

4.7

R852

R854

560

82

R853

560

R877

560

75

470

L952

C952

C953

L953

C954

C955

C956

0.1

R952

75

R951

0.01

75

L851

10

R855

µ

1

C855

330p

C854

150p

R856

10

C856

0.1

K853

J953

J952

J952

J952

J951

J852

J852

p10693001a_rev0

SHEET 11

BCD EFG

2-25 2-26

Page 16

MAIN(AUDIO I/O) SCHEMATIC DIAGRAM

5

TO TERMINAL I/O

4

3

SHEET 11

TO TUNER

SHEET 14

A.IN2[R]

A.IN2[L]

A.IN1[R]

A.IN1[L]

DEMOD[R]

DEMOD[L]

R2201

1k

IC2201

GND

R2662

R2663

R2664

R2665

R2666

R2667

47k

47k

47k

47k

47k

47k

C2602

0.01

C2601

0.01

R2606

3.3k

R2607

1k

R2603

1k

R2602

3.3k

R2601

100

IC2601

R2605

100

R2604

27k

R2608

27k

R2610 R2611

10k 10k

R2202 R2203

10k 10k

R2609

1k

B2601

IC2602

B2602

R2612

1k

R2613 R2614

10k 10k

IC2202

IC2603

R2204

100

R2205

100

IC2604

R2615

100

R2616

100

IC2607

1

C2605

1

C2606

Q2204

4.7

C2607

4.7

C2608

Q2202

R2208

4.7k

R2209

4.7k

Q2201

R2210

1k

Q2203

1

1

10

C2609

C2610

C2611

R2634R2633

10k10k

R2207

47k

C2201

10

C2202

10

R2206

47k

CN2601

CN2602

AD_IEC958

V3.3V

A.GND

DEC_A.OUT[R]

DEC_A.OUT[L]

LINE_OUT[R]

LINE_OUT[L]

RF_AUDIO

GND

TO DV MAIN

(AUDIO AD/DA)

CN3701

SHEET 21

TO JUNCTION

(AUDIO AD/DA)

CN8001

SHEET 24

TO TERMINAL I/O

SHEET 11

TO TUNER

SHEET 14

2

TO JUNCTION(REG)

TO SYSCON

SHEET 13

1

SHEET 1

AL5.8V

DVD_A_INSEL1

DVD_A_INSEL2

DVD_A_INSEL3

DEC_SEL

DVC_A_INSEL1

DVC_A_INSEL2

A.OUTSEL1

A.OUTSEL2

A.MUTE_DVC[H]

A.MUTE[L]

F.AUDIO[R]

F.AUDIO[L]

A

SW12V

SW-7V

SW5V

GND

R2651

R2652

R2655 R2656 R2657

47k 47k 47k

0Ω

0Ω

C2651 C2653C2652 C2654

47 47

R2658R2659 R2660 R2661

47k 47k 47k 47k

IC2301

R2301

12k

R2303

12k

R2305

100

R2304 R2302

180 180

R2306 R2310

R2307

2.2k

10k

C2301

10

R2308

220k

R2309

2.2k

C2302

10

C2306 C2305

47

10k

R2311

100

C2303

10

C2304

10

R2312

8.2k

R2653

10k

R2654

15k

D2601

1SS133-T2

R2631

27k

R2632

1k

Q2605

Q2603

Q2604

R2622 R2623

10k 10k

R2621

1k

IC2605

IC2606

R2624

470

R2625

470

C2604

10

C2603

10

R2627

10K

R2628

10K

Q2601

Q2602

R2629

4.7k

R2630

4.7k

p10686001a_rev0

SHEET 12

BCDEFG

2-27 2-28

Page 17

MAIN(SYSCON) SCHEMATIC DIAGRAM

5

TO VIDEO SW VDR

TO VIDEO SW DV

TO VIDEO SW VDR

TO VIDEO SW DV

TO VIDEO SW VDR

4

TO VIDEO SW DV

TO TERMINAL I/O

3

VIDEO SW VDR

TO VIDEO SW DV

TO

SHEET 10

SHEET 9

SHEET 10

SHEET 9

SHEET 10

SHEET 9

SHEET 10

TO ON SCREEN

SHEET 8

SHEET 9

TO REG

SHEET 1

TO ON SCREEN

SHEET 8

SHEET 11

TO

JUNCTION

(VIDEO)

CN7102

SHEET 23

SEPA_IN[H]

I2C_DATA_A/V

I2C_CLK_A/V

SECAM_DET[H]

I2C_DATA2

I2C_CLK2

SYNC_DET1[H]

TO_VDR_DUB[L]

FRONT_V_IN

FRONT_Y_IN

FRONT_C_IN

TO_DV_DUB[L]

I2C_DATA2

I2C_CLK2

TO REG

SHEET 1

P.SAVE[L]

FAN_CTL[H]

P.CTL[H]

CN3103

CN3102

GND

SW5V

SW12V

AL5.8V

R7204

10

Q7201

C7203

L7201

µ

100

C7202

330

100

220

R7202

R7203

4.7k

0101K

000

000

R3091

R3050

R3051

R3089

R3052

R3053

R3087

470

R3054

0

R3086

1k

R3055

R3249

R3250

R3255

R3246

R3244

C3017

C3018

C3021

C3020

C3019

IC3004

R3081

R3080

R3079

R3078

R3077

R3076

R3075

R3074

R3073

R3072

R3063

R3061

R3060

R3057

TP3906

3.3k

3.3k

3.3k

C3032

1

C3034

C3037

10k

X3002

100

R3229

1M

C3036

C3025

C3024

10k

C3028 C3029

R3240

R3239

10k

10k

10k

10k

10k

0.1

C3022

4.7k

4.7k

C3035

12p

18p

10p

22p

0

0

1k

0

0

0

0

0

0

0

TP3904

R3071

B3001

R3069

0.1

C3050

TP3905

X3001

TP3903

R3062

0

0

R3259

10k

TP3908

TP3907

B3971

B3962

1k

R3258

R3257

R3256

R3223

R3224

1k

2.2k

C3054

0.1

R3066

4.7k

Q3901

R3225

0.01

C3026

470

R3230

4.7k

B3966

R3226

470

IC3002

S-80827CNNB-G-W

CN3901

R3231

C3031

1

1k

C3030

47

C3027

10k

R3313

10k

R3314

10k

R3315

R3097

0

R3044

R3096

1

C3016

R3095

TP3901

000

R3046

R3094

TP3902

R3047

0

R3092

R3093

0047000

R3049

R3048

0.1

C3033

C3038

C3039

47

R3205

100k

45V

GND

B3002

L3001

R3204

D3010

4.7k

BT3001

D3003

R3203

4.7k

0.22

µ

R3206

1k

C3010 C3011

CN3002

Q3004

D3004

10ED820

R3207

1k

4700

R3201

470k

R3202

330k

D3005

10ED820

470

D3002

C3042

C3014

47

C3015

1

6.8k

R3018

R3218 C3041

4.7k

C3007

R3011

R3014

R3015

R3017

R3019

R3020

R3021

R3022

R3024

R3025

R3027

R3028

0.01

C3051

C3049

1

1k

1k

100k

1k

1k

1k

1k

1k

1k

1k

0

1k

001k1k1k1k1k

R3029

0.0027

R3031

R3032

R3033

R3034

R3035

R3036

R3037

IC3001

BU2090FS-X

0

0

R3038

R3039

1k

R3040

1k

R3041

C3055

0.1

R7205

J7201

100

CN3104

TO SW/JACK

CN7201

SHEET 15

F.AUDIO[L]

F.AUDIO[R]

A.MUTE_DVC[H]

A.MUTE[L]

DVD_A_INSEL1

DVD_A_INSEL2

DVD_A_INSEL3

DEC_SEL

DVC_A_INSEL1

DVC_A_INSEL2

A.OUTSEL1

A.OUTSEL2

P.MUTE[L]

OSD_CS

I2C_DATA2

I2C_CLK2

SYNC_DET2[H]

S.CLK

S.DATA_FRSYS

P.ON_P

SCR[H]

AV1_YC_IN[H]

P50_I/O

RGB[H]

TU_V_MUTE[H]

TU_I2C_DATA

TU_I2C_CLK

SW_2

SW_1

AFC

RF_AGC

TO AUDIO I/O

SHEET 12

TO

ON SCREEN

SHEET 8

TO

TERMINAL I/O

SHEET 11

TO TUNER

SHEET 14

2

DV MAIN(DV MSD)

1

SW/DISPLAY

CN7001

SHEET 15

TO

CN503

SHEET 17

IC3301

TO

10k

CN3014

R3234

R3233

R3247

10k

R3248

Q3011

B3012

Q3014

Q3013

B3011

Q3007

Q3009

D3008

10k

D3007

10k

Q3012

C3301

0.1

C3302

C3303

Q3010

p10690001a_rev0

SHEET 13

A

BCD EFG

2-29 2-30

Page 18

MAIN(TUNER) SCHEMATIC DIAGRAM

5

L6701

SHORT

C6752C6751

OPEN270

R6001

47

R6002

OPEN

L6002

SHORT

Q6001

100

L6004

OPEN

L6001

OPEN

L6005

1

µ

4

B6003

OPEN

B6005

R6054

OPEN

B6009

OPEN

R6080

10k

B6001

B6002

B6004

B6006

B6007

B6008

TU6001

3

2

L6003

C6002

0.01

C6001

100

µ

1

C6012

C6014

C6054

R6053

C6053

C6013

R6052

C6052

R6050

C6055

C6056

R6020

C6020

R6021

C6021

C6007

C6008

C6005

C6006

D6002

C6027

C6028

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

1k

OPEN

1k

OPEN

OPEN

C6721

C6720

R6721

C6722

C6723

C6719

10

C6724

0.01

10

K6707

R6707

5.6k

OPEN

600

C6718

OPEN

R6720

5.6k

2.2

C6701

K6706

600

C6717

2.2

R6716

47

600

K6701

600

0

C6706

OPEN

0.01

K6702

47p

C6707

8p

C6708

IC6701

0.0022

C6716

8p

C6709

X6701

R6031

100

12k

R6715

K6708

12k

0.0022

C6715

2.2

R6713

C6714

R6712R6714

1k1k

R6711

C6713

D6701

C6712

K6705

R6710

600

C6753

R6709

K6704

600

C6711

C6710

K6703

R6708

600

R6719

10k

600

R6030

3.3k

100k

0.22

OPEN

OPEN

OPEN

OPEN

L6702

SHORT

0

1k

10k

GND

AL5.8V

SW5V

SW12V

BT2

DEMOD[L]

GND

DEMOD[R]

RF_AUDIO

TO REG

SHEET 1

TO AUDIO I/O

SHEET 12

C6037R6032

103.3k

R6033

1.5k

1

TO SYSCON

SHEET 13

TU_I2C_CLK

TU_I2C_DATA

TU_V_MUTE[H]

RF_AGC

SW_1

SW_2

AFC

C6032

OPEN

Q6031

UN2211-X

Q6030

2SB709A/QR

TU_VIDEO

GND

RF_VIDEO

TO TERMINAL I/O

SHEET 11

p10685001a_rev0

SHEET 14

A

BCDEFG

2-31 2-32

Page 19

SWITCH JACK, SWITCH DISPLAY AND JACK SCHEMATIC DIAGRAM

5

S7033 S7035S7034

S7014 S7013

1SS133

1SS133

1SS133

D7012

D7013

D7014

S7032

S7024

1SS133

D7005

S7025

S7012

1SS133

D7004

IC7002

1SS133

D7003

S7023

S7004S7015

R7213

15k

R7212

4.7k

R7211

10k

S7213

S7212

S7211

C7211

0.01

C7201

QUY153-050Y

L7204

D7203D7202

L7202

0.01

C7202

C7203

100p

C7205

100p

L7203

100p

0.01

C7204

100p

R7202 J7201

75

µ

µ

L7201

J7201

J7201

J7204

D7204

R7206R7207

7575

Q7002

UN221L

R7016

C7006

220

Q7003

UN221L

CN7001

TO MAIN(SYSCON)

CN3102

SHEET 13

R7215

4.7k

R7214

10k

S7215

S7214

C7212

0.01

C7206

0.01

4

C7001

C7008

0.1 220

10k

R7009

1k

R7015

4.7k

R7005

1k

R7007

4.7k

R7006

10k

R7002

10k 33k

R7001 R7014

IC7001

D7031

3

C7002

0. 1