Page 1

MX-DVA9/MX-DVA9R

SERVICE MANUAL

COMPACT COMPONENT SYSTEM

MX-DVA9/MX-DVA9R

Contents

Area suffix

MX-DVA9R

B -------------------------- U.K.

EN ------- Northern Europe

SP-MXG79 CA-MXDVA9/CA-MXDVA9R SP-MXG79

Area suffix

MX-DVA9

A ------------------------- Australia

US ---------------------- Singapore

(SP-DSC99TN)

Center unit Speaker unit

CA-MXDVA9/CA-MXDVA9R SP-MXDVA9/SP-MXDVA9R

SP-MXG79(Front speaker)

SP-DSC99TN(Center speaker)

SP-DSS99TN(Surround speaker)

(SP-DSS99TN)

UW ---------- Brazil,Mexico,Peru

UJ --------------------- U.S.Military

UG - Turkey,South Africa,Egypt

UN ----------------------------Asean

Safety Precautions

Preventing static electricity

Precautions for service

Important for laser products

Disassembly method

COPYRIGHT 2001 VICTOR COMPANY OF JAPAN, LTD.

1-2

1-4

1-5

1-6

1-7

Adjustment method

Flow of functional operation until Toc read

Maintenance of laser pickup

Replacement of laser pickup

Description of major ICs

1-28

1-34

1-35

1-35

1-36

No.21040

Oct. 2001

Page 2

MX-DVA9/MX-DVA9R

1. This design of this product contains special hardware and many circuits and components specially for safety

purposes. For continued protection, no changes should be made to the original design unless authorized in

writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services

should be performed by qualified personnel only.

2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product

should not be made. Any design alterations or additions will void the manufacturer`s warranty and will further

relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

3. Many electrical and mechanical parts in the products have special safety-related characteristics. These

characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily

be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which

have these special safety characteristics are identified in the Parts List of Service Manual. Electrical

components having such features are identified by shading on the schematics and by ( ) on the Parts List in

the Service Manual. The use of a substitute replacement which does not have the same safety characteristics

as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or

other hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be

separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of

electric shock and fire hazard. When service is required, the original lead routing and dress should be

observed, and it should be confirmed that they have been returned to normal, after re-assembling.

5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product

(antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the

product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage

current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return

path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more

sensitivity in the following manner. Connect a 1,500 10W resistor paralleled by a 0.15 F AC-type capacitor

between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC

voltmeter.

Move the resistor connection to each exposed metal part,

particularly any exposed metal part having a return path to

the chassis, and meausre the AC voltage across the resistor.

Now, reverse the plug in the AC outlet and repeat each

measurement. Voltage measured any must not exceed 0.75 V

AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

0.15 F AC TYPE

1500 10W

Good earth ground

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

Place this

probe on

each exposed

metal part.

!

1. This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

3. Repairs must be made in accordance with the relevant safety standards.

4. It is essential that safety critical components are replaced by approved parts.

5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may

be left over on some parts of the

chassis. Therefore, pay attention to

such burrs in the case of

preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the

parts that are printed over with black such as the resistor ( ), diode ( ) and ICP ( ) or identified by the " "

mark nearby are critical for safety.

When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer.

(Except the J and C version)

1-2

Page 3

MX-DVA9/MX-DVA9R

(U.K only)

1. This design of this product contains special hardware and many circuits and components specially

for safety purposes. For continued protection, no changes should be made to the original

design unless authorized in writing by the manufacturer. Replacement parts must be identical to

those used in the original circuits.

2. Any unauthorised design alterations or additions will void the manufacturer's guarantee ; furthermore the

manufacturer cannot accept responsibility for personal injury or property damage resulting therefrom.

3. Essential safety critical components are identified by ( ) on the Parts List and by shading on the

schematics, and must never be replaced by parts other than those listed in the manual. Please note

however that many electrical and mechanical parts in the product have special safety related

characteristics. These characteristics are often not evident from visual inspection. Parts other than

specified by the manufacturer may not have the same safety characteristics as the recommended

replacement parts shown in the Parts List of the Service Manual and may create shock, fire, or

other hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the

like to be separated from live parts, high temperature parts, moving parts and/or sharp edges

for the prevention of electric shock and fire hazard. When service is required, the original lead

routing and dress should be observed, and it should be confirmed that they have been returned

to normal, after re-assembling.

1. Service should be performed by qualified personnel only.

2. This equipment has been designed and manufactured to meet international safety standards.

3. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

4. Repairs must be made in accordance with the relevant safety standards.

5. It is essential that safety critical components are replaced by approved parts.

6. If mains voltage selector is provided, check setting for local voltage.

!

Burrs formed during molding may be left over on some parts of the chassis. Therefore,

pay attention to such burrs in the case of preforming repair of this system.

1-3

Page 4

MX-DVA9/MX-DVA9R

Preventing static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players.

Be careful to use proper grounding in the area where repairs are being performed.

1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over

it before placing the traverse unit (optical pickup) on it.

1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

(caption)

Anti-static wrist strap

Conductive material

(conductive sheet) or iron plate

1.1.3. Handling the optical pickup

1. In order to maintain quality during transport and before installation, both sides of the laser diode on the

replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition.

(Refer to the next page.)

2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power

source can easily destroy the laser diode.

1.2. Handling the traverse unit (optical pickup)

1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

2. For specific details, refer to the replacement procedure in the text. Be careful not to take too long a time

when attaching it to the connector.

3. Handle the flexible cable carefully as it may break when subjected to strong force.

4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

1-4

Page 5

Precautions for service

Handling of Traverse Unit and Laser Pickup

1. Do not touch any peripheral element of the pickup or the actuator.

2. The traverse unit and the pickup are precision devices and therefore must not be subjected to

strong shock.

3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the

internal power supply of the tester.)

4. When replacing the pickup, after mounting a new pickup, remove the solder on the short land

which is provided at the center of the flexible wire to open the circuit.

5. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the

characteristics of the optical block.

Do not change the setting of these half-fixed resistors for laser power adjustment.

Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing

or the human body. Before repairing peripheral elements of the traverse

unit or pickup, be sure to take the following electrostatic protection:

MX-DVA9/MX-DVA9R

1. Wear an antistatic wrist wrap.

2. With a conductive sheet or a steel plate on the workbench on which

the traverse unit or the pick up is to be repaired, ground the sheet

or the plate.

When you remove the traverse mechanism from the servo control substrate

The laser diode of pick-up might be destroyed by static electricity and set switch (S11) on the pick-up board

on "SHORT" side, please before removing the card wire from connector (CN10).

Moreover, please set switch (S11) on "OPEN" side after assembling and inserting the card wire in

connector (CN10) without fail at times.

Traverse

mechanism

CN10

CN12

SWITCH S11

SHORT

OPEN

When you remove the pick-up from the traverse mechanism

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before

extracting a flexible wire from connector (CN12).

Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12).

Soldering part

Pick-up

Traverse

mechanism

1-5

Page 6

MX-DVA9/MX-DVA9R

Important for laser products

1.CLASS 2 LASER PRODUCT

2.DANGER : Invisible laser radiation when open and inter

lock failed or defeated. Avoid direct exposure to beam.

3.CAUTION : There are no serviceable parts inside the

Laser Unit. Do not disassemble the Laser Unit. Replace

the complete Laser Unit if it malfunctions.

4.CAUTION : The compact disc player uses invisible

laserradiation and is equipped with safety switches

whichprevent emission of radiation when the drawer is

open and the safety interlocks have failed or are de

feated. It is dangerous to defeat the safety switches.

5.CAUTION : If safety switches malfunction, the laser is able

to function.

6.CAUTION : Use of controls, adjustments or performance of

procedures other than those specified herein may result in

hazardous radiation exposure.

!

Please use enough caution not to

see the beam directly or touch it

in case of an adjustment or operation

check.

REPRODUCTION AND POSITION OF LABELS

WARNING LABEL

CLASS 2

LASER PRODUCT

1-6

Page 7

MX-DVA9/MX-DVA9R

Disassembly method

<Main body>

Removing the metal cover

(See Fig.1 to 3)

1.

Remove the six screws A on the back of the body.

2.

Remove the two screws B on both sides of the

body.

3.

Remove the metal cover from the body by lifting the

rear part of the cover.

CAUTION:

Do not break the front panel tab fitted to

the metal cover.

A

A

Metal cover

Metal cover

A

Fig.1

B

Fig.2

Metal cover

Fig.3

B

1-7

Page 8

MX-DVA9/MX-DVA9R

Removing the DVD mechanism assembly

(See Fig.4 to 7)

Prior to performing the following procedure, remove

the metal cover.

1.

Disconnect the card wire from connector CN542 on

the main board on the right side of the body.

2.

Disconnect the wire from CN501 on the DVD servo

board in the lower part of the DVD mechanism

assembly, on the left side of the body.

3.

Remove the screw F from the rear panel on the

back of the body. Disconnect the earth terminal

extending from the DVD changer mechanism

assembly and attached to the terminal on the

antenna board.

Remove the two screws C on top of the body and

the two screws D on back of the body.

Remove the DVD changer mechanism from behind

upward while pulling the front panel assembly and

the rear panel outward.

C

Main board

CN542

Rear panel

Front panel assembly

C

DVD changer

mechanism assembly

Fig.4

DVD changer mechanism assembly

CN501

Rear panel

Front panel assembly

REFERENCE:

6.

Disconnect the card wire from connector CN540 and

CN541 on the inner side of the main board on the

right side of the body, and remove the DVD

mechanism assembly.

REFERENCE:

REFERENCE:

At this point, the two card wires in the

lower part of the DVD mechanism

assembly is still connected.

To prevent damage to the DVD changer

mechanism assembly, make sure to pull

both the front panel assembly and the rear

panel outward enough to remove the DVD

changer mechanism assembly.

To prevent damage to the DVD fitting, be

sure to pull both the rear panel and the

front panel assembly enough to remove

the DVD changer mechanism assembly.

Fig.5

Tuner board

DVD changer mechanism assembly

Main board

CN542

CN541

CN540

Front panel assembly

Fig.6

Rear panel

F

Earth terminal

Rear panel

Tuner board

D

1-8

DVD changer mechanism assembly

Fig.7

Page 9

MX-DVA9/MX-DVA9R

Removing the front panel assembly

(See Fig.8 to 12)

Prior to performing the following procedure, remove

the metal cover and DVD changer mechanism

assembly.

1.

Disconnect the card wires from connector CN500,

CN505 and CN510 on the main board respectively.

2.

Remove the wire clamp and disconnect the wire from

connector CN703 on the amplifier board.

3.

Disconnect the wire from connector CN220 on the

transformer board.

4.

Remove the plastic rivet attaching the main board to

the front assembly on the right side of the body.

5.

Remove the two screws E on the bottom of the

body.

6.

Release the two joints a on the lower right and left

sides of the body using a screwdriver, and remove

the front panel assembly toward the front.

Power amplifier board (2)

CN703

Wire clamp

Fig.8

Plastic rivet

Main board

CN500

CN505

CN510

Front panel

assembly

Transformer board

CN220

Front panel assembly

Front panel assembly

Fig.9

Main board

E

(Bottom)

Fig.10

Joint a

Front panel assembly

Fig.12

Front panel assembly

Fig.11

Joint a

1-9

Page 10

MX-DVA9/MX-DVA9R

Removing the tuner board

(See Fig.13 and 14)

Prior to performing the following procedure, remove

the metal cover.

1.

Disconnect the card wire from connector CN1 on the

tuner board on the right side of the body.

2.

Remove the plastic rivet fixing the tuner board.

3.

Remove the two screws F on the back of the body.

CAUTION:

When reassembling, connect the earth

terminal which is extending from the

DVD changer mechanism assembly and

attached to the tuner board, to the inner

side of the rear panel.

Removing the rear cover / rear panel

(See Fig.15 to 17)

Plastic rivet

Joints b

CN1

Tuner board

Fig.13

G

Rear panel

F

Rear panel

Joints b

Prior to performing the following procedure, remove

the metal cover and the DVD changer mechanism

assembly, the tuner board.

1.

Remove the screw G attaching the rear cover on the

back of the body.

2.

Push each tab of the four joints b in the direction of

the arrow and release.

3.

Remove the fourteen (A/B/EN) or sixteen(US/UJ/UG/

UN/UW) screws F attaching the rear panel.

4.

Disengage the joints c on each lower side of the rear

panel using a screwdriver and remove the rear panel

backward.

Rear cover

F

F

F

F

Fig.14

Fig.15-1

Rear panel

F

F

Rear panel

F

Joint c

Rear panel

Fig.17

1-10

Rear panel

Fig.16

Joint c

F

F

F

FF

Fig.15-2

Page 11

MX-DVA9/MX-DVA9R

Removing the main board

(See Fig.18 and 19)

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly, the rear panel and the antenna board.

1.

Disconnect the card wire from connector CN500,

CN505, CN510 and the wire from CN513 on the

main board respectively.

2.

Remove the plastic rivet and the screw H attaching

the main board on the right side of the body.

3.

Disconnect connector CN521 on the main board

from the analog output board outward. Disconnect

connector CN530 and CN531 in the lower part of the

main board from the regulator board upward.

Main board

CN513

Analog output board

Plastic rivet

CN510

CN505

CN500

Fig.18

Main board

CN521

Front panel assembly

Analog output board

CN520

Removing the speaker board

(See Fig.20)

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly and the rear panel.

REFERENCE:

1.

Disconnect connector CN287 on the speaker board

from the regulator board.

It is not necessary to remove the main

board.

H

CN287

CN530

Fig.19

Speaker board

Fig.20

CN531

Regulator board

1-11

Page 12

MX-DVA9/MX-DVA9R

Removing the power board / power cord

(See Fig.21)

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly and the rear panel.

1.

Disconnect the wire from connector CN218 and

CN219(only US/UJ/UG/UN/UW) on the power board.

Move the power cord stopper upward and remove.

2.

Disconnect connector CN213 on the power board

3.

from the regulator board.

Remove the two wire clamps fixing the power cord

4.

and disconnect the power cord from connector

CN250 on the power board.

Removing the analog output board / fan

(See Fig.22 to 24)

CN218

CN219

Power board

CN250

Power cord

Power cord stopper

Analog output board

Wire clamp

CN213

Fig.21

CN370

Wire clamp

CN371

Wire clamps

Main board

CN513

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly, the rear panel and the antenna board.

1.

Disconnect the wire from connector CN513 on the

main board.

2.

Remove the two wire clamps fixing the wire on the

analog output board.

3.

Disconnect the wire extending from the fan from

connector CN705 on the power amplifier board (2).

4.

Disconnect connector CN370 (only US/UJ/UG/UN/

UW) CN371 on the analog output board from the

main board. Disconnect connector CN372 and

CN373 on the analog output board from the power

amplifier board (1) and the power amplifier board (2)

respectively upward.

5.

Remove the two screws I and the fan from the fan

bracket.

Main board

CN370

Fan

CN371

Power amplifier board (2)

CN705

Fig.22

Analog output board

CN372

CN373

Fig.23

Analog output board

1-12

Fan bracket

I

Fan

Fig.24

Page 13

MX-DVA9/MX-DVA9R

Removing the power amplifier board (1)

/ power amplifier board (2) / heat sink

(See Fig.25 to 27)

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly, the rear panel, the antenna board and the

analog output board.

1.

Disconnect the wire from connector CN513 on the

main board.

2.

Remove the wire clamp on the power amplifier board

(1).

3.

Disconnect the wire from connector CN703 on the

power amplifier board (2).

4.

Disconnect connector CN310 on the power amplifier

board (1) and CN701 on the power amplifier board

(2) from the regulator board upward. The heat sink is

detached with the power amplifier board (1) and the

power amplifier board (2).

Main board

CN513

Power amplifier

board (2)

Heat sink

CN701

Power amplifier board (1)

CN703

CN310

Fig.25

Power amplifier board (2)

Wire clamp

Power amplifier

Regulator board

board (1)

Heat sink

5.

Remove the four screws J attaching the power

amplifier board (1) to the heat sink.

6.

Remove the four screws K attaching the power

amplifier board (2) to the heat sink.

Power amplifier board (1)

Heat sink

K

J

J

Fig.26

Power amplifier board (2)

K

Fig.27

1-13

Page 14

MX-DVA9/MX-DVA9R

Removing the power transformer assembly

(See Fig.28 and 29)

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly and the rear panel.

1.

Disconnect the wire from connector CN218 and

CN219(only US/UJ/UG/UN/UW) on the power board.

2.

Remove the two wire clamps on the power amplifier

board (1) and power board.

3.

Disconnect the wire from connector CN204 on the

regulator board.

4.

Disconnect the wire from connector CN220 on the

transformer board.

5.

Remove the four screws L attaching the power

transformer assembly.

Removing the regulator board

(See Fig.30)

CN219

Power board

CN218

Power transformer assembly

Wire clamps

Wire clamp

L

Transformer board

CN220

Fig.28

L

Regulator board

L

Regulator board

CN204

CN204

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly, the rear panel, the antenna board, the

main board, the analog output board, the power

board, the power amplifier board (1), the power

amplifier board (2) and the speaker board.

1.

Disconnect the wire from connector CN204 on the

regulator board.

2.

Remove the two screws M.

L

Power transformer assembly

M

Power transformer assembly

L

Fig.29

Fig.30

CN220

Regulator board

M

CN204

1-14

Page 15

MX-DVA9/MX-DVA9R

<Front panel assembly>

Prior to performing the following procedure, remove

the metal cover, the DVD changer mechanism

assembly and the front panel assembly.

Removing the cassette mechanism

assembly (See Fig.31)

1.

Disconnect the card wire from connector CN306 on

the head amplifier & mechanism control board.

2.

Remove the seven screws N attaching the cassette

mechanism assembly.

Removing the display system control

board (See Fig.32 to 34)

1.

Remove the four screws O attaching the stay

bracket.

Head amplifier

& mechanism control board

CN306

N

N

Cassette mechanism

assembly

O

N

N

N

Fig.31

O

2.

Disconnect the card wires from connector CN316

and CN881 on the display system control board.

3.

Remove the six screws P attaching the display

system control board.

4.

If necessary, disconnect the wire from connector

CN870 on the front side of the display system control

board and unsolder FW915.

Display system control board

CN316

P

FW915

(Solding)

P

CN881

CN911

Fig.32

CN870

P

Display system control board

Fig.33

CD eject board

Stay bracket

P

P

FW915

FW915

Display system control board

Fig.34

1-15

Page 16

MX-DVA9/MX-DVA9R

Removing the CD eject board

(See Fig.35)

1.

Remove the three screws Q attaching the DVD eject

board.

2.

If necessary, unsolder FW915 on the DVD eject

board.

Removing the preset / tuning switch

board (See Fig.36 and 37)

Prior to performing the following procedure, remove

the display system control board.

1.

Pull out the preset knob on the front panel.

2.

Remove the five screws R attaching the preset /

tuning switch board.

3.

If necessary, unsolder FW901 on the preset / tuning

switch board.

Removing the operation switch board

(See Fig.37 and 38)

Prior to performing the following procedure, remove

the display system control board and the preset /

tuning switch board.

DVD eject board

FW915

(Solding)

Q

Preset / tuning switch board

FW915

(Solding)

Preset knob

Q

Fig.35

R

R

Fig.36

Operation switch board

Surround mode knob

Surround woofer

level knob

1.

Pull out the volume knob on the front panel and

remove the nut. Pull out the surround mode knob

and the surround woofer level knob toward the front.

Pull out the mic level knob toward the front.

(only US/UJ/UG/UN/UW)

2.

Remove the eleven (A/B/EN) or thirteen (US/UJ/UG/

UN/UW) screws S attaching the operation switch

board.

3.

Release each tab of the seven joints g retaining the

Joints g

S

Joint g

S

Operation

switch board

S

Joint g

Joints g

S

S

S

Fig.38-2

S

Joint g

Joint g

Joint g

Joints g

Volume knob

S

S

Joints g

S

Fig.37

S

Fig.38-1

Nut

S

Mic level knob

S

Joint g

S

Operation

switch board

1-16

Page 17

<Speaker unit section>

Removing the side cover (See Fig.1)

1.

Remove the six screws A on the side of the body.

Removing the squawker speaker

(See Fig.2)

Prior to performing the following procedure, remove

the side cover.

1.

Remove the four screws B on the side of the body.

2.

Disconnect the red and black wires from the speaker

terminals on the squawker speaker.

MX-DVA9/MX-DVA9R

A

A

Side cover

A

A

Fig.1

B

Removing the front cover (See Fig.3 to 5)

Prior to performing the following procedure, remove

the side cover.

1.

Pull out the saran net toward the front while

disengaging the four joints a.

2.

Remove the two screws C and D respectively.

3.

Remove the front cover toward the front and

disconnect the yellow and black wires from the two

tweeter speaker terminals.

CC

Front cover

Squawker speaker

B

Fig.2

DD

Fig.4

Joints a

Joints a

Saran net

Fig.3

1-17

Page 18

MX-DVA9/MX-DVA9R

Removing the woofer speaker (See Fig.6)

Prior to performing the following procedure, remove

the side cover and the front cover.

Tweeter speaker

Fig.5

1.

Remove the four screws E on the front of the body.

2.

Pull out the woofer speaker toward the front and

disconnect the wire (yellow and black,blue and

black) from the two speaker terminals.

Removing the tweeter speaker

(See Fig.7)

Prior to performing the following procedure, remove

the side cover and the front cover.

1.

Remove the two screws F attaching the tweeter

speaker on the back of the front cover.

E

E

Woofer speaker

Fig.6

F

Tweeter speaker

1-18

Front cover

Fig.7

Page 19

DVD Changer Mechanism Section

Removing the DVD Servo control

board

1.

Remove the Metal cover.

2.

Remove the DVD changer mechanism assembly.

3.

From bottom side the DVD changer mechanism

assembly, remove the one screw 1 retaining the DVD

Servo control board.

Ciconnect the card wire,From the connectors CN101

4.

and CN102, on the DVD Servo control board.

Disengage the two engagements "A" , remove the DVD

5.

Servo control board.

Removing the DVD tray assembly

(See Fig.2~4)

Remove the front panel assembly.

1.

Remove the DVD changer mechanism assembly.

2.

Remove the DVD Servo control board.

3.

Remove the screw 2 retaining the Disc stopper

4.

(See Fig.3).

Remove the three screws 3 retaining the T.bracket

5.

(See Fig.3).

From the clamper base section "C" , remove both of the

6.

edges fixing the rod(See Fig.2 and 3).

Remove the screw 4 retaining the clamper assembly

7.

(See Fig.3).

From the left side face of the chassis assembly, remove

8.

the one screw 5 retaining both of the return spring and

lock lever(See Fig. 4).

By removing the pawl at the section "D" fixing the return

9.

spring, dismount the return spring(See Fig.4).

Remove the three lock levers(See Fig.4).

10.

Disc stopper

T.Braket

MX-DVA9/MX-DVA9R

1

DVD servo control baord

CN102

CN101

AA

Fig.1

Clamper base

B

Rod

C

T.Braket

Fig.2

D

3

B

C

Clamper ass'y

Fig.3

2

3

Lod stopper

(C/J version only)

3

4

Return spring

5

Lock lever

Fig.4

1-19

Page 20

MX-DVA9/MX-DVA9R

11.

Check whether the lifter unit stopper has been caught

into the hole at the section "E" of DVD tray assembly

as shown in Fig.5.

Make sure that the driver unit elevator is positioned as

12.

shown in Fig.6 from to the second or fifth hole on the

left side face of the DVD Traverse mechanism

assembly.

[Caution]

13.

14.

15.

Chassis assembly

In case the driver unit elevator is not at above

position, set the elevator to the position as

shown in Fig.7 by manually turning the pulley

gear as shown in Fig.8.

Manually turn the motor pulley in the clockwise

direction until the lifter unit stopper is lowered from the

section "E" of DVD tray assembly(See Fig.8).

Pull out all of the three stages of DVD tray assembly in

the arrow direction "F" until these stages stop

(See Fig.6).

At the position where the DVD tray assembly has

stoppend, pull out the DVD tray assembly while

pressing the two pawls "G and G' " on the back side of

DVD tray assembly(See Fig.9). In this case, it is easy

to pull out the assembly when it is pulled out first from

the stage DVD tray assembly.

Fig.5

Stopper

E

DVD tray

assembly

Refer to Fig.7

Pulley gear

Pawl

DVD tray assembly

G

F

Drive unit of elevator

Fig.7Fig.6

DVD tray assembly

Motor pulley

Fig.8

1-20

Pawl ,

G

Fig.9

G'

Page 21

MX-DVA9/MX-DVA9R

Removing the DVD mechanism

assembly(See Fig.10)

1.2.While turning the cams R1 and R2 assembly in the

arrow direction "H" . align the shaft "I" of the DVD

mechanism assembly to the position shown in Fig.10.

Remove the four screw 6 retaining the DVD

mechanism assembly.

Removing the DVD mechanism

(See Fig.11 and 12 )

For dismounting only the DVD machanism without

1.

removing the DVD mechanism assembly, align the shaft

"J" of the DVD mechanism assembly to the position

shown Fig.11 while turning the cam R1 and R2

assembly in the arrow direction "K" .

By raising the DVD mechanism assembly in the arrow

2.

direction "L" , remove the assembly from the lifter unit

(See Fig.12).

Cam R1, R2 assembly

Cams R1, R2 assembly

Arrow

H

I

6

6

CD mechanism assembly

10

6

6

Fig.10

CD mechanism

Arrow

K

J

Lifter unit

Fig.11

Fig.12

Arrow

L

1-21

Page 22

MX-DVA9/MX-DVA9R

Removing the actuator motor boad

(See Fig.14, 15)

1.

Absord the four soldered positions "M" of the right and

left motors with a soldering absorber(See Fig.14).

2.

Remove the two screws 7 retaining the actuator motor

board(See Fig.14).

Remove the two screws 8 retaining the tray select

3.

switch board(See Fig.15).

Removing the can unit

(See Fig.15~18 )

1.

Remove the CD mechanism assembly.

2.

While turning the cam gear L, align the pawl "N"

position of the drive unit to the notch position(Fig.15) on

the cam gear L.

Pull out the drive unit and cylinder gear(See Fig.17).

3.

While turning the cam gear L, align the pawl "O"

4.

position of the select lever to the notch position(Fig.18)

on the cam gear L.

Remove the four screws 9 retaining the cam unit(cam

5.

gear L and cams R1/R2 assembly)(See Fig.18).

M

Motor L

Actuator motor board

Fig.14

7

Motor R

M

7

Chassis assembly

CN801

Fig.15

CN802

Drive unit

Tray select

switch board

Cylinder gear

CN804

Drive unit

N

8

Cam gear L

9

Cam gear L

Fig.16

Cams R1, R2 assembly

9

Cam unit

9

1-22

Fig.17

O

Select lever

Fig.18

Page 23

MX-DVA9/MX-DVA9R

Removing the actuator motor and belt

(See Fig.19~22)

1.

Remove the two screws 10 retaining the gear bracket

(See Fig.19).

2.

While pressing the pawl "P" fixing the gear bracket in

the arrow direction, remove the gear bracket

(See Fig.19).

From the notch "Q section" on the chassis assembly

3.

fixing the edge of gear bracket, remove and take out the

gear bracket(See Fig. 20).

Remove the belts respectively from the right and left

4.

actuator motor pulleys and pulley gears(See Fig. 19).

After turning over the chassis assembly, remove the

5.

actuator motor while spreading the four pawls "R" fixing

the right and left actuator motors in the arrow

direction(See Fig. 21).

[Note]

When the chassis assembly is turned over under

the conditions wherein the gear bracket and belt

have been removed, then the pulley gear as well

as the gear, etc. constituting the gear unit can

possibly be separated to pieces. In such a case,

assemble these parts by referring to the assembly

and configuration diagram in Fig. 22.

Pully gear

Gear bracket

Belt

Motor pulley

10

Fig.19

Actuator motor

Pulley gear

Belt

Motor pulley

10

Pawl

P

Chassis assembly

Q

Gear bracket

Fig.20

Assembly and Configuration Diagram

Pulley gear

R

R

Fig.21

Pulley gear

Gear B

Cylinder gear

Gear B

Gear C

Select gear

Gross gear L

Fig.22

Gross gear U

Gear C

1-23

Page 24

MX-DVA9/MX-DVA9R

Removing the cams R1/R2 assembly

and cam gear L(See Fig.23)

Remove the slit washer fixing the cams R1 and R2

1.

assembly.

By removing the two pawls "S" fixing the cam R1,

2.

separate R2 from R1.

Remove the slit washer fixing the cam gear L.

3.

Pull out the cam gear L from the C.G. base assembly.

4.

Removing the C.G. base assembly

(See Fig.23 and 24)

Remove the three screws 11 retaining the C.G. base

assembly.

[Caution]

To retassemble the cylinder gear, etc.with the

cam unit (cam gear and cans R1/R2 assembly),

gear unit and drive unit, align the position of the

pawl "N" on the drive unit to that o f the notch

on the cam gear L. Then, make sure that the

gear unit is engaged by turning the cam gear L

(See Fig. 24).

Slit washer

Cam gear L

11

Slit washer

Cam R2

Pawl

S

Cam R1

Cam switch board

C.G. base assembly

Pawl

S

Notch

Pawl

N

Cylinder

gear

Drive unit

Fig.23

Cam gear L

Cam R1, R2 assembly

Gear unit

Gear bracket

Fig.24

1-24

Page 25

MX-DVA9/MX-DVA9R

< Cassette Mechanism Section >

Removing the Playback,Recording and Eraser

Heads (See Fig.1~3)

1. While shifting the trigger arms seen on the right

side of the head mount in the arrow direction,turn

the flywheel R in counterclockwise direction until

the head mount has gone out with a click

(See Fig. 1).

2. When the flywheel R is rotated in counterclockwise

direction, the playback head will be turned in

counterclockwise direction from the position in

Fig.2 to that in Fig.3.

3. At this position, disconnect the flexible P.C.board

(outgoing from the playback head) from the

connector CN301 on the head amp. and mechanism

control P.C. board.

4. After dismounting the FPC holder,remove the

flexible P.C.board.

5. Remove the flexible P.C.board from the chassis

base.

6. Remove the spring "a" from behind the playback

head.

7. Loosen the reversing azimuth screw retaining the

playback head.

8. Take out the playback head from the front of the

head mount.

9. The recording and eraser heads should also be

removed similarly according to Steps 1~8 above.

Reassembling the Playback, Recording

and Eraser Heads (See Fig.2,3)

Cassette mechanism

Fig.1

Playback/Recording &

eraser head

Flexible

P.C.board

CN301

Head amplifier & mechanism

control P.C. board

Fig.2

Flywheel R

Trigger armHead mount

(Mechanism A side)

Spring "a"

Trigger arm

Flywheel R

(Mechanism A side)

1. Reassemble the playback head from the front of

the head mount to the position as shown in Fig.3.

2. Fix the reversing azimuth screw.

3. Set the spring a from behind the playback head.

4. Attach the flexible P.C.board to the chassis base,

and fix it with the FPC holder as shown in Fig.3.

5. The recording and eraser heads should also be

reassembled similarly according to Steps 1~4

above.

Playback head

Spring "a"

FPC holder

Fig.3

Reversing azimuth

screw

Head

mount

Flexible

P.C.board

CN302

Head amplifier &

mechanism control

P.C. board

(Mechanism B side)

1-25

Page 26

MX-DVA9/MX-DVA9R

Removing the head Amp.and Mechanism

Control P.C.Board (See Fig. 4)

1.Remove the cassette mechanism assembly.

2.After turning over the cassette mechanism

assembly,remove the five screws "A" retaining

the head amp. and mechanism control P.C.

board

3.Disconnect the connectors CN303 and CN304

on the P.C.Board and the connectors CN1 on

both the right and left side reel pulse

P.C.Boards.

4.When necessary, remove the 4pin parallel

wire soldered to the main motor

Removing the Capstan Motor Assembly

1.Remove the six screws "B" retaining capstan

motor assembly (See Fig. 5).

2.While raising the capstan motor, remove the

capstan belts A and B respectively from the

motor pulley (See Fig. 6).

A

Flexible

board

Head amplifier &

mechanism control board

AA

CN304

CN302 CN301

Flexible

board

CN303

Fig.4

BB

Capstan motor

assembly

AA

Caution 1: Be sure to handle the capstan

belts so carefully that these belts

will not be stained by grease and

other foreign matter. Moreover,

these belts should be hand while

referring to the capstan belt

hanging method.

Capstan

belt A

BBBB

Fig.5

Capstan motor

Capstan

belt B

Capstan

belt A

Fig.7 Fig.6

1-26

Capstan

belt B

Motor pulley

Page 27

MX-DVA9/MX-DVA9R

Removing the Capstan Motor (See Fig. 8)

From the joint bracket, remove the two screws "C"

retaining the capstan motor.

Removing the Flywheel (See Fig. 9,10)

1.Remove the head amp. and mechanism control

P.C.Board.

2.Remove the capstan motor assembly.

3.After turning over the cassette mechanism, remove

the slit washers "a" and "b" fixing the capstan shafts

R and L, and pull out the flywheels R and L respectively

from behind the cassette mechanism.

C

Capstan motor

Joint

bracket

C

Fig.8

Flywheel R Flywheel L

Flywheel R Flywheel L

Fig.10

Removing the Reel Pulse P.C.Board and Solenoid

(See Fig. 11)

1.Remove the five pawls (c,d,e,f,g) retaining

the reel pulse P.C.Board.

2.From the surface of the reel pulse P.C.Board parts,

remove the two pawls "h" and "i" retaining the solenoid.

hi

Solenoid

c

a

d

Slit

washer "a"

Fig.9

e

f

b

Slit

washer "b"

g

Reel pulse board

Solenoid

Fig.11

1-27

Page 28

MX-DVA9/MX-DVA9R

Adjustment method

Measurement instruments required

for adjustment

1. Low frequency oscillator,

This oscillator should have a capacity to output 0dBs

to 600ohm at an oscillation frequency of 50Hz-20kHz.

2. Attenuator impedance : 600ohm

3. Electronic voltmeter

4. Frequency counter

5. Wow flutter meter

6. Test tape

VT712 : For Tape speed and wow flutter ( 3kHz)

VT724 : For Reference level (1kHz)

VT703L : For Head angle(10kHz)

Because of frequency-mixed tape with 63,1k,10k and

14kHz(250nWb/m -24dB).

Use this tape together with a filter.

7. Blank tape

TAPE : AC-225

8. Torque gauge : For play and back tension

Forward ; TW2111A, Reverse ; TW2121A

Fast Forward and Rewind ; TW2231A

9. Test disc

: CTS-1000(12cm),GRG-1211(8cm)

10. Jitter meter

Radio input signal

AM modulation frequency : 400Hz

Modulation factor : 30%

FM modulation frequency : 400Hz

Frequency displacement : 22.5kHz

Frequency Range

A/B/EN

AM 522kHz~1629kHz

FM 87.5MHz~108MHz

US/UJ/UG/UN/UW

AM 531kHz~1602kHz

FM 87.5MHz~108MHz

Standard measurement positions of volume

and switch

Power : Standby (Light STANDBY Indicator)

Sub woofer VOL. : Minimum

Sound mode : OFF

Main VOL. : 0 Minimum

Traverse mecha set position : Disc 1

Mic MIX VOL : MAX

ECHO : OFF

Measurement conditions

Power supply voltage

AC120V(60Hz)

Measurement

output terminal : Speaker out

:TP101(Mesuring for TUNER/DECK/CD)

:Dummy load 6ohm

Precautions for measurement

1. Apply 30pF and 33kohm to the IF sweeper output

side and 0.082 F and 100kohm in series to

the sweeper input side.

2. The IF sweeper output level should be made as

low as possible within the adjustable range.

3. Since the IF sweeper is a fixed device, there is

no need to adjust this sweeper.

4. Since a ceramic oscillator is used, there is no need

to perform any MPX adjustment.

5. Since a fixed coil is used, there is no need to adjust

the FM tracking.

6. The input and output earth systems are separated.

In case of simultaneously measuring the voltage

in both of the input and output systems with an

electronic voltmeter for two channels, therefore,

the earth should be connected particularly.

7. In the case of BTL connection amplifier, the minus

terminal of speaker is not for earthing. Therefore,

be sure not to connect any other earth terminal

to this terminal. This system is of an OTL system.

1-28

Page 29

DVD section

TEST MODE FOR DVD a INITIALISE THE DVD UNIT BOARD

a) Insert A/C Power Cord

b) At standby mode press Stop Button and CANCEL/DEMO button.

Wait 4 seconds & for the display of " TEST VERSION REGION " i.e. TEST JC 1

c) Press the 'ENTER' button on remocon. The FL panel will display 'EEPROM'.

Plug out and plug in again the power cord. Repeat the process 1(a) and 1(b) again.

Confirm that the Area Code and Region Code is correctly display as below.

MX-DVA9/MX-DVA9R

Are Code FL indicate of Area Code in Test mode

Region Code.

J/C

UJ

UG/UX

US/UN/UP

UT

UW

E/EN/B

A

EE

JC

JC

2U

3U

UT

4U

E

A

EE

1

1

2

3

3

4

2

4

5

Note: Please plug out and plug in the power cord from A/C supply before continue the next test.

Adjustment

Jig setup

1. Remove the rubber cushion from each of the four

corners of the traverse mechanism.

(When installing be sure not to make a mistake with

the cushion colors).

2. Install the jig stud.

3. Make a jig clamp. (Remove the clamp from the set

and assemble it as shown in the diagram below.

Green rubber

cushion

Blue rubber

cushion

Note:

How to handle the pickup

To protect the pickup from electro-static damage,

make sure to hold it by the die-cast chassis (optical

base). And make sure that pickup lens do not touch

the top cover.

How to prepare a clamp

Remove the claws

from the 3 locations

Jig stud

Disassemble the clamp

and holder

Installing the

4 jig studs

Blue rubber

cushion

Combine the clamp

and holder to become

a jig clamp.

1-29

Page 30

MX-DVA9/MX-DVA9R

Integrated wiring for adjustment

1. Place a board on top of the unit and put the

changer on it. Then carry out the wiring of the

main unit.

2. Connect a extension cable to the traverse

mechanism for adjustment and then connect

them to the changer.

3. Remove the solder of the short-circuited

flexible wire. Then remove the short-circuited

pin from the traverse mechanism

4. Connection is completed.

Adjustment preparation

1. The 3 adjustment locations

2. 1.4 mm hexagonal wrench

3. Set the VT-501 or the VT502 test disc.

FL jitter display

1. Connect the power cable while pressing the

(OPEN/CLOSE) button of DISC1 and

(PLAY) button simultaneously.

--- The DISC no. " " is displayed on

the FL indicator.

2. Press the 3D-PHONIC key button of remote

controller to commence initialization.

3. When the key (PLAY) is pressed the jitter

value is displayed.

4. Adjust the jitter value to minimum by using the

adjust screw.

a). Turn the adjustment screw ( A and B )

clockwise half.

b). Return the adjustment screw ( A and B ) to

former position.

c). Turn the adjustment screw ( A and B )

counterclockwise half.

d). Set the adjustment screw ( A and B ) to the

position of best jitter at three positions.

Next, do it similar to the above-mentioned in

adjustment screw A and C.

Extension cord

QUQ605-4040AJ

Adjustment location

(Adjust screw C )

Adjustment location

(Adjust screw A )

Jig ass'y clamp adjustment

Stud

JIGXVM555

Hexagonal wrench

(Adjust screw B )

Test disc

1-30

3 locations

for adjustment

Adjust by using

a hexagonal

wrench

Page 31

Arrangement of adjusting positions

MX-DVA9/MX-DVA9R

Cassette mechanism section (Mechanism A section)

Head azimuth

adjusting screw

(Forward side)

Playback

head

Head azimuth

adjusting screw

(Reverse side)

Cassette mechanism section (Back side)

Head azimuth

adjusting screw

(Forward side)

Playback, recording and eraser

heads or playback head

Head azimuth

adjusting screw

(Reverse side)

Cassette Mechanism Unit Section

Tape speed ADJ

Bias ADJ L

Bias ADJ R

1-31

Page 32

MX-DVA9/MX-DVA9R

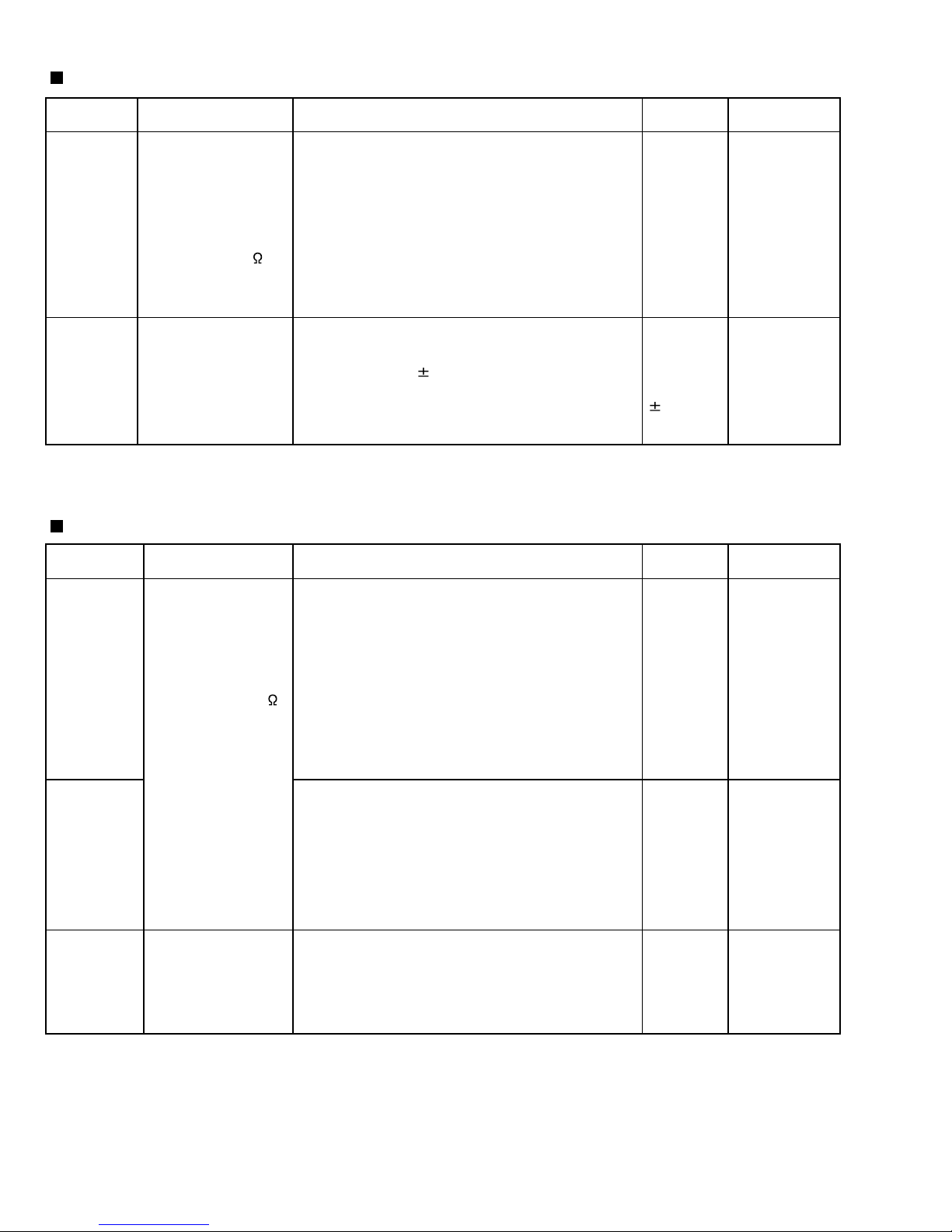

Tape recorder section

Items Measurement

Confirmation

of head angle

Confirmation

of tape speed

conditions

Test tape

:VT703L(10kHz)

Measurement

output terminal

:Speaker terminal

Speaker R

(Load resistor:6 )

:Headphone terminal

Test tape

:VT712(3kHz)

Measurement

output terminal

:Headphone terminal

1.Playback the test tape VT703L(10kHz).

2.With the playback mechanism or recording &

playback mechanism, adjust the head azimuth

screw so that the forward and reverse output

levels become maximum.After adjustment,lock

the head azimuth at least by half a turn.

3.In either case,this adjustment should be

performed in both the forward and reverse

directions with the head azimuth screw.

<Constant speed>

Adjust VR301 so that the frequency counter reading

becomes 3,000Hz 60Hz when playing back the

test tape VT712(3kHz)with the playback mechanism

or playback and recording mechanism after ending

forward winding of the tape.

Reference values for confirmation items

Items Measurement

Double tape

speed

conditions

Test tape

:VT703L(10kHz)

Measurement

output terminal

:Speaker terminal

Speaker R

(Load resistance:6 )

measurement

output terminal

:Headphone terminal

After setting to the double speed motor, confirm

that the frequency counter reading becomes

4,800+400/-300Hz when the test tape VT712

(3kHz) has been play back with the playback

mechanism.

Measurement method

Measurement method

Standard

values

Maximum

output

Tape speed

of decks

(A and B)

:3,000Hz

60Hz

Standard

values

4,800+400/

-300Hz

Adjusting

positions

Adjust the head

azimuth screw

only when the

head has been

changed.

VR301

Adjusting

positions

Playback

mechanism side

Difference

between the

forward and

reverse speed.

P.mecha and

R/P mecha

speed

Wow & flutter

Test tape

:VT712(3kHz)

Measurement

output terminal

:Headphone terminal

When the test tape VT712(3kHz) has been played

back with the playback mechanism or recording and

playback mechanism at the beginning of forward

winding, the frequency counter reading of the

difference between both of the mechanisms should

be 6.0Hz or less.

When the test tape VT712(3kHz) has been played

back with the playback mechanism or recording and

playback mechanism at the beginning of forward

winding the frequency counter reading of wow &

flutter should be 0.25% or less(WRMS).

1-32

60Hz or

less

with in

0.25%

JIS(WTD)

Both the playback

and recording &

playback

mechanism

Both the playback

and recording &

playback

mechanism

Page 33

Electrical performance

Items Measurement

Adjustment of

recording bias

current

(Reference

value)

conditions

*Mode : Forward or

reverse mode

*Recording mode

*Test tape

: AC-225

Measurement output

terminal

:Both recording and

headphone terminals

Measurement method

1.With the recording and playback mechanism,

load the test tapes(AC-225 to TYP ),and set the

mechanism to the recording and

pausing conditions in advance.

2.After connecting 100 in series to the recorder

head,measure the bias current with a valve

voltmeter at both of the terminals.

3.After resetting the [PAUSE] mode,start recording.

At this time,adjust VR101 for LcH and VR201 for

RcH so that the recording bias current values

become 4.0 A (TYP ).

Standard

values

AC-225

:4.20 A

MX-DVA9/MX-DVA9R

Adjusting

positions

LcH

:VR101

RcH

:VR201

Adjustment of

recording and

playback

frequency

characteristics

Reference frequency

:1kHz and 10kHz

(REF:-20dB)

Test tape

:TYP AC-225

Measurement input

terminal

:OSC IN

1.With the recording and playback mechanism,load

the test tape(AC-225 to TYP ),and set the

mechanism to the recording and pausing condition

in advance.

2.While repetitively inputting the reference frequency

signal of 1kHz and 10kHz from OSC IN, record and

playback the test tape.

3.While recording and playing back the test tape in

TYP ,adjust VR101 for LcH and VR201 for RcH

so that the output deviation between 1kHz and

10kHz becomes -1dB 2dB.

Reference values for electrical function confirmation items

Items Measurement

Recording

bias frequency

conditions

*Recording and

playback side forward

or reverse

*Test tape

:TYP AC-225

*Measurement

terminal BIAS TP on

P.C.board

1.While changing over to and from BIAS 1 and 2,

confirm that the frequency is changed.

2.With the recording and playback mechanism.

load the test tape (AC-225 to TYP ),and set the

mechanism to the recording and pausing

conditions in advance.

3.Confirm that the BIAS TP frequency on the

P.C.board is 100kHz 6kHz.

Measurement method

Output

deviation

between

1kHz and

10kH

:-1dB 2dB

Standard

values

100kHz

+9kHz

-7kHz

LcH

:VR101

RcH

:VR201

Adjusting

positions

Eraser current

(Reference

value)

*Recording and

playback side forward

or reverse

*Recording mode

*Test tape

:AC-225

Measurement terminal

Both of the eraser

head

1.With the recording and playback mechanism,

load the test tapes(AC-225 to TYP ),and set the

mechanism to the recording and pausing condition

in advance.

2.After setting to the recording conditions,connect

1M in series to the eraser head on the recording

and playback mechanism side,and measure the

eraser current from both of the eraser terminal.

TYP

:75mA

1-33

Page 34

MX-DVA9/MX-DVA9R

Flow of functional operation until TOC read

Power ON

Play Key

Slider turns REST

SW ON.

Automatic tuning

of TE offset

Check Point

Confirm that the voltage at the pin5

of CN801 is "H"\"L"\"H".

Tracking error waveform at TOC reading

Approx.3sec

Tracking

servo

off states

Automatic measurement

of TE amplitude and

automatic tuning of

TE balance

VREF

pin 25 of

IC601(TE)

Approx

1.8V

Disc states

to rotate

Tracking

servo

on states

Disc to be

braked to stop

TOC reading

finishes

500mv/div

2ms/div

Fig.1

Laser ON

Detection of disc

Automatic tuning of

Focus offset

Automatic measurement of

Focus S-curve amplitude

Disc is rotated

Focus servo ON

(Tracking servo ON)

Automatic measurement of

Tracking error amplitude

Automatic tuning of

Tracking error balance

Check that the voltage at the

pin40 of IC651 is + 5V?

Confirm that the Focus error

S-cuve signal at the pin28 of

IC651 is approx.2Vp-p

Confirm that the signal from

pin24 IC651 is 0V as a

accelerated pulse during

approx.400ms.

Confirm the waveform of

the Tracking error signal.

at the pin 25 of IC601 (R604)

(See fig-1)

1-34

Automatic tuning of

Focus error balance

Automatic tuning of

Focus error gain

Automatic tuning of

Tracking error gain

TOC reading

Play a disc

Confirm the eys-pattern

at the lead of TP1

Page 35

MX-DVA9/MX-DVA9R

Maintenance of laser pickup

(1) Cleaning the pick up lens

Before you replace the pick up, please try to

clean the lens with a alcohol soaked cotton

swab.

(2) Life of the laser diode

When the life of the laser diode has expired,

the following symptoms will appear.

1. The level of RF output (EFM output : ampli

tude of eye pattern) will below.

Is the level of

RFOUT under

1.25V 0.22Vp-p?

YES

O.K

NO

Replace it.

Replacement of laser pickup

Turn off the power switch and, disconnect the

power cord from the ac outlet.

Replace the pickup with a normal one.(Refer

to "Pickup Removal" on the previous page)

Plug the power cord in, and turn the power on.

At this time, check that the laser emits for

about 3seconds and the objective lens moves

up and down.

Note: Do not observe the laser beam directly.

Play a disc.

Check the eye-pattern at TP1.

Finish.

(3) Semi-fixed resistor on the APC PC board

The semi-fixed resistor on the APC printed circuit board which is attached to the pickup is used to adjust the laser

power. Since this adjustment should be performed to match the characteristics of the whole optical block, do not

touch the semi-fixed resistor.

If the laser power is lower than the specified value, the laser diode is almost worn out, and the laser pickup should

be replaced.

If the semi-fixed resistor is adjusted while the pickup is functioning normally, the laser pickup may be damaged

due to excessive current.

1-35

Page 36

MX-DVA9/MX-DVA9R

Description of major ICs

MN102L62GEJ (IC401) : Unit CPU

1.Terminal layout

~

100 76

1

~

75

~

25

26 50

51

~

2.Pin function

Pin No. Pin No.

Symbol Symbol

1

WAIT

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

RE

SPMUTE

WEN

CS0

CS1

CS2

CS3

DRVMUTE

SPKICK

LSIRST

WORD

A0

A1

A2

A3

VDD

SYSCLK

VSS

XI

XO

VDD

OSCI

OSCO

MODE

A4

A5

A6

A7

A8

A9

A10

A11

VDD

A12

A13

A14

A15

A16

A17

A18

A19

VSS

A20

TXSEL

HAGUP

CD/DVD

ADPD

HMFON

TRVSW

I/O I/O

Micon wait signal input

I

Read enable

O

Spindle muting output to IC251

O

Write enable

O

Non connect

Chip select for ODC

O

Chip select for ZIVA

O

Chip select for outer ROM

O

Driver mute

O

Spin kick (Non connect)

O

LSI reset

O

Bus selection input

O

Address bus 0 for CPU

O

Address bus 1 for CPU

O

Address bus 2 for CPU

O

Address bus 3 for CPU

O

Power supply

System clock signal output

O

Ground

Not use (Connect to vss)

Non connect

Power supply

Clock signal input(13.5MHz)

I

Clock signal output(13.5MHz)

O

CPU Mode selection input

I

Address bus 4 for CPU

O

Address bus 5 for CPU

O

Address bus 6 for CPU

O

Address bus 7 for CPU

O

Address bus 8 for CPU

O

Address bus 9 for CPU

O

Address bus 10 for CPU

O

Address bus 11 for CPU

O

Power supply

Address bus 12 for CPU

O

Address bus 13 for CPU

O

Address bus 14 for CPU

O

Address bus 15 for CPU

O

Address bus 16 for CPU

O

Address bus 17 for CPU

O

Address bus 18 for CPU

O

Address bus 19 for CPU

O

Ground

Address bus 20 for CPU

O

TX Select

O

O

Foucs balance & leaser power select

O

Power up out put

O

O

Detection switch of traverse

I

inside

Function

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

FGIN

TRS

ADSCEN

VDD

FEPEN

SLEEP

BUSY

REQ

CIRCEN

HSSEEK

VSS

EPCS

EPSK

DPDI

EPDO

VDD

SCLKO

S2UDT

U2SDT

CPSCK

SDIN

SDOUT

-

-

NMI

ADSCIRQ

ODCIRQ

DECIRQ

WAKEUP

ODCIRQ2

ADSEP

RST

VDD

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

TEST8

VSS

D0

D1

D2

D3

D4

D5

D6

D7

Function

Serial enable signal for ADSC

O

Power supply

Serial enable signal for FEP

O

Standby signal for FEP

O

Communication busy

I

Communication Request

O

CIRC command select

O

Non connect

Ground

EEPROM chip select

O

EEPROM clock

O

EEPROM data input

I

EEPROM data output

O

Power supply

Communication clock

I

Communication input data

I

Communication output data

O

Clock for ADSC serial

O

ADSC serial data input

I

ADSC serial data output

O

Not use

Not use

Not use

Interrupt input of ADSC

I

Interrupt input of ODC

I

Interrupt input of ZIVA

I

Not use

O

Interruption of system control

I

Address data selection input

I

Reset input

I

Power supply

Test signal 1 input

I

Test signal 2 input

I

Test signal 3 input

I

Test signal 4 input

I

Test signal 5 input

I

Test signal 6 input

I

Test signal 7 input

I

Test signal 8 input

I

Ground

Data bus 0 of CPU

I/O

Data bus 1 of CPU

I/O

Data bus 2 of CPU

I/O

Data bus 3 of CPU

I/O

Data bus 4 of CPU

I/O

Data bus 5 of CPU

I/O

Data bus 6 of CPU

I/O

Data bus 7 of CPU

I/O

1-36

Page 37

AN8702FH(IC101):Frontend processor

1.Pin layout

HDTYPE

VIN12

646362616059585756555453525150

VIN11

GND1

VIN4

VIN3

VIN2

VIN1

VREF1

VCC1

VIN10

VIN9

VIN8

VIN7

VIN6

VIN5

49

MX-DVA9/MX-DVA9R

2.Pin function

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

Symbol

PC1

PC01

PC2

PC02

TGBAL

TBAL

FBAL

POFLT

DTRD

IDGT

STANDBY

SEN

SCK

STDI

RSEL

JLINE

TEN

TEOUT

ASN

ASOUT

FEN

FEOUT

VSS

TG

VDD

GND2

VREF2

VCC2

VHALF

DFLTON

DFLTOP

DSFLT

GND3

1

PC1

2

PC01

3

PC2

4

PC02

5

TGBAL

6

TBAL

7

FBAL

8

POFLT

9

DTRD

10

IDGT

SEN

SCK

STDI

RSEL

JLINE

11

12

13

14

15

16

171819202122232425262728293031

TEN

TEOUT

STANDBY

I/O Description

Input for Laser current monitor

I

Laser power control output for DVD

O

Photo detector fo CD

I

Laser power control output for CD

O

Tangential phase balance control terminal

I

Tracking balance control terminal

I

Focus balance control terminal

I

Track detection threshold level terminal

O

Data slice part data read signal input terminal

I

(For RAM)

Data slice part address part gate signal input

I

terminal( For RAM)

Standby mode control terminal

I

SEN(Serial data input terminal)

I

SCK(Serial data input terminal)

I

STDI(Serial data input terminal)

I

I

DVD and CD selection

J-line setting output (FEP)

I

Tracking error output amplifier reversing input terminal

I

Tracking error signal output terminal

O

Off set adjustment terminal for DRC

I

All added signal output terminal

O

Focus error output amplifier reversing input terminal

I

Focus error signal output terminal

O

Connect to GND

-

Tangential phase error signal output terminal

O

Power supply terminal 3V

-

Connect to GND

-

VREF2 voltage output terminal

O

Power supply terminal 5V

-

VHALF voltage output terminal

O

Filter amplifier reversing output terminal

O

Filter amplifier output terminal

O

Connected capacitor terminal for filter output

O

Connect to GND

-

AN8702FH

FEN

ASN

FEOUT

ASOUT

VSS

TG

VDD

Pin No.

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

48

RFINN

RFINP

47

TESTSG

46

AGCO

45

AGCG

44

43

PEAK

42

BOTTOM

41

RFENV

40

BDO

39

OFTR

38

DCRF

37

RFC

36

VCC3

35

RFOUT

34

RFDIFO

33

GND3

32

VCC2

GND2

VREF2

VHALF

DFLTON

DSFLT

DFLTOP

Symbol I/O Description

RF operation output terminal

RFDIFO

RFOUT

VCC3

RFC

DCRF

OFTR

BDO

RFENV

BOTTOM

PEAK

AGCG

AGCO

TESTSG

RFINP

RFINN

VIN5

VIN6

VIN7

VIN8

VIN9

VIN10

VCC1

VREF1

VIN1

VIN2

VIN3

VIN4

GND1

VIN11

VIN12

HDTYPE

O

RF output terminal

O

Power supply terminal 5V

-

I Filter for RF amplifier

All addition amplifier capacitor terminal

O

OFTR output terminal

O

BDO output terminal

O

RF envelope output terminal

O

Bottom envelope detection filter terminal

O

Peak envelope detection filter terminal

O

AGC amplifier gain control terminal

O

AGC amplifier level control terminal

O

TEST signal input terminal

I

RF signal positive input terminal

I

RF signal negative input terminal

I

RF input of external division into 4 terminal for CD

I

RF input of external division into 4 terminal for CD

I

I

RF input of external division into 4 terminal for CD

RF input of external division into 4 terminal for CD

I

I

RF input of external division into 2 terminal for DVD

I

RF input of external division into 2 terminal for DVD

Power supply terminal 5V

-

VREF1 voltage output terminal

O

External division into four (DVD/CD) RF input

I

terminal1

External division into four (DVD/CD) RF input

I

terminal2

External division into four (DVD/CD) RF input

I

terminal3

External division into four (DVD/CD) RF input

I

terminal4

Connect to GND

-

3 beem sub input terminal for CD

I

I

3 beem sub input terminal for CD

HD type switching

I

1-37

Page 38

MX-DVA9/MX-DVA9R

MN101C35DEG(IC810):System controller

Pin function

Pin No.

1

2

3

4~7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49~51

52~64

65~88

89~99

100

Symbol

D DATA

DCLK

DACOCS

DI/DO/CS/SK

VDD

OSC2

OSC1

VSS

XI

XO

MMOD

VREF-

POWER SW

NTSEL

RGB/YC SW

S/COMPO

AIN0

AIN2

TEST0

TEST1

VREF+

RGBSEL

RESET

AVCO

AVCI

POWERON

TCLOSE

YOPEN

/LMMUTE

SWOPEN

SWUPDN

REMO

NC

REQ

NC

S2UDT

U2SDT

SCLK

BUSY

CPURST

NC

VS3

VS1

MUTE

STANDBYIND

NC

1G~13G

S1~S24

NC

VPP

I/O

O

O

O

-

-

O

I

-

-

-

-

I

I

-

I

I

-

-

-

O

I

O

I

O

O

O

O

I

I

I

-

I

-

O

I

O

O

O

O

O

O

O

O

O

-

-

DAC control data

DAC control clock

DAC control chip select

Non connect

Power supply +B 5V

Oscillation terminal 8MHz

Oscillation terminal 8MHz

Connect to ground

Unused, Connect with ground

Unused

Connect to ground

Connect to ground

Key input (power)

NTSC/PAL switch input

Un used

Un used

Key input (S831~S835)

Key input (open/close)

Un used

Un used

Power supply +B 5V

RGB select control (H:RGB L:other)

Reset input

AV COMPULINK output

AV COMPULINK input

Power ON output

Tray close control output

Tray open control output

Tray muting output (L:muting)

Detection switch of tray open/close (L:open/close)

Detection switch of traverse mechanism up/down (H:UP L:DOWN)

Remote control interruption

Non connect

Communication between unit microcomputers request

Non connect

Communication between unit microcomputers DATA output

Communication between unit microcomputers DATA input

Communication between unit microcomputers CLK

Communication between unit microcomputers BUSY

Unit microcomputers reset

Non connect

S3 control (H:standby L:power ON)

S1 control

Muting output

LED control signal output (standby)

Non connect

FL grid control signal output

FL segment control signal output

Non connect

-VDISP (apply -35V)

Description

1-38

Page 39