IXYS IXDD415SI Datasheet

IXDD415SI

Dual 15 Ampere Low-Side Ultrafast MOSFET Driver

Features

• Built using the advantages and compatibility

of CMOS and IXYS HDMOSTM processes

• Latch-Up Protected

• High Peak Output Current: Dual 15A Peak

• Wide Operating Range: 8V to 30V

• Rise And Fall Times of <3ns

• Minimum Pulse Width Of 6ns

• Ability to Disable Output under Faults

• High Capacitive Load

Drive Capability: 4nF in <5ns

• Matched Rise And Fall Times

• 32ns Input To Output Delay Time

• Low Output Impedance

• Low Supply Current

Applications

• Driving RF MOSFETs

• Class D or E Switching Amplifier Drivers

• Multi MHz Switch Mode Power Supplies (SMPS)

• Pulse Generators

• Acoustic Transducer Drivers

• Pulsed Laser Diode Drivers

• DC to DC Converters

• Pulse Transformer Driver

General Description

The IXDD415 is a dual CMOS high speed high current gate

driver specifically designed to drive MOSFETs in Class D and E

HF RF applications, as well as other applications requiring

ultrafast rise and fall times or short minimum pulse widths.

Each output of the IXDD415 can source and sink 15A of peak

current while producing voltage rise and fall times of less than

3ns. The outputs of the IXDD415 may be paralleled, producing a

single output of up to 30A with comparable rise and fall times.

The input of the driver is compatible with TTL or CMOS and is

fully immune to latch up over the entire operating range.

Designed with small internal delays, cross conduction/current

shoot-through is virtually eliminated in the IXDD415. Its features

and wide safety margin in operating voltage and power make

the IXDD415 unmatched in performance and value.

The IXDD415 has two enable inputs, ENA and ENB. These

enable inputs can be used to independently disable either of the

outputs, OUTA or OUTB, for added flexibility. Additionally, the

IXDD415 incorporates a unique ability to disable the output

under fault conditions. When a logical low is forced into the

Enable inputs, both final output stage MOSFETs (NMOS and

PMOS) are turned off. As a result, the output of the IXDD415

enters a tristate mode and achieves a Soft Turn-Off of the

MOSFET when a short circuit is detected. This helps prevent

damage that could occur to the MOSFET if it were to be

switched off abruptly due to a dv/dt over-voltage transient.

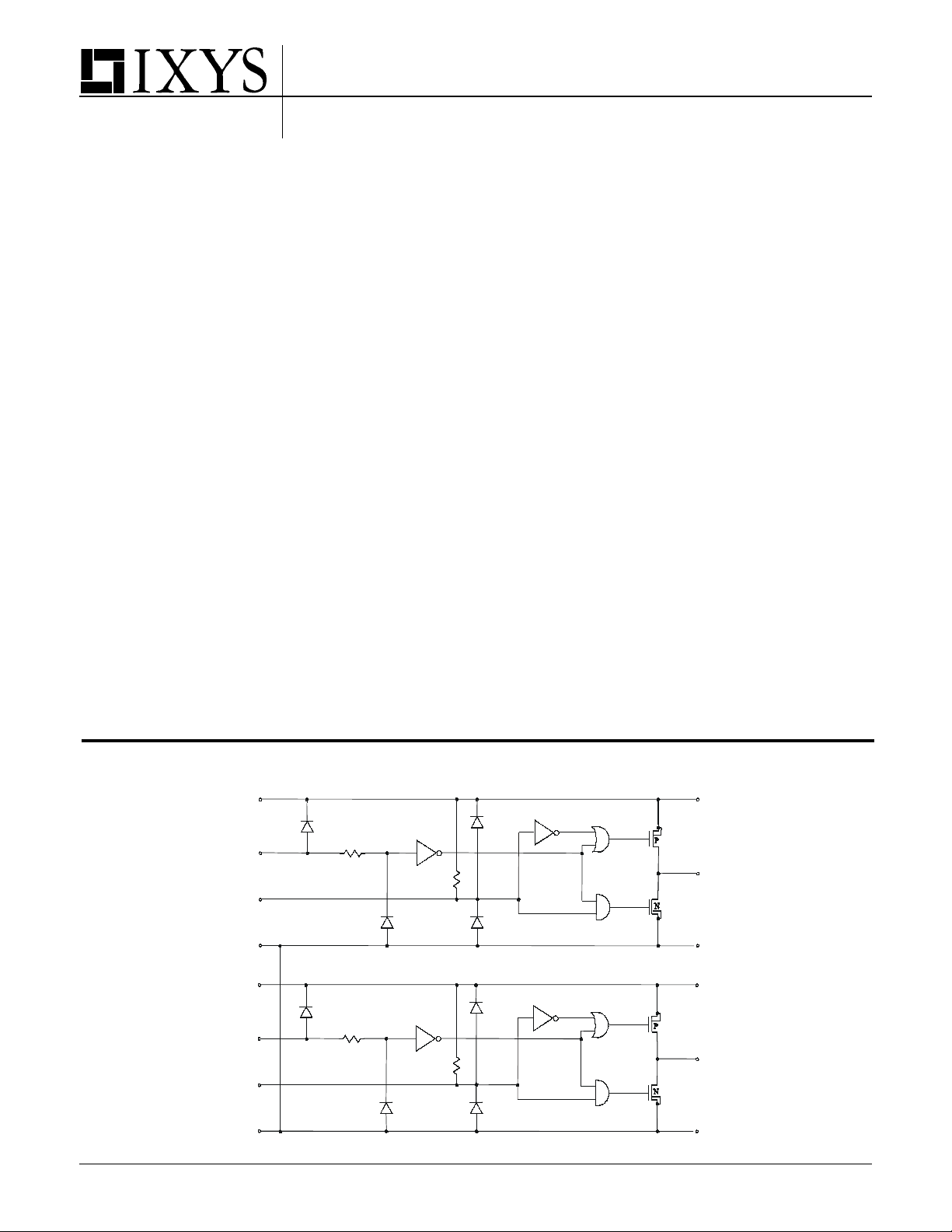

Figure 1 - Functional Diagram

Vcc (1, 2)

INA (7)

ENA (6)

GND (25, 26)

Vcc (11, 12)

INB (8)

ENB (9)

The IXDD415 is available in a 28 pin SO package (IXDD415SI),

incorporating DEI's patented

(1)

RF layout techniques to minimize

stray lead inductances for optimum switching performance.

(1)

DEI U.S. Patent #4,891,686

Vcc (3, 4)

200k

200k

OUTA (22, 23, 24)

GND (27, 28)

Vcc (13, 14)

OUTB (19, 20, 21)

GND (15, 16)

Copyright © IXYS CORPORATION 2001 Patent Pending

GND (17, 18)

First Release

IXDD415SI

Absolute Maximum Ratings

Parameter Value

Supply Voltage 30V

All Other Pins -0.3V to VCC + 0.3V

Power Dissipation

T

T

AMBIENT

≤25 oC

CASE

≤25 oC

(Note 1) Operating Ratings

Parameter Value

Maximum Junction Temperature

Operating Temperature Range

1W

12W

Thermal Impedance (Junction To Case)

28 Pin SOIC (SI) (θJC)

150oC

-40oC to 85oC

0.75oC/W

Derating Factors (to Ambient)

28-Pin SOIC

Storage Temperature

Soldering Lead Temperature

(10 seconds maximum)

0.1W/oC

-65oC to 150oC

300oC

Electrical Characteristics

Unless otherwise noted, TA = 25 oC, 4.5V ≤ V

All voltage measurements with respect to GND. IXDD415 configured as described in Test Conditions.

Symbol Parameter Test Conditions Min Typ Max Units

V

IH

High input voltage 3.5 V

VIL Low input voltage 0.8 V

VIN Input voltage range -5 V

IIN Input current

VOH High output voltage V

VOL Low output voltage 0.025 V

ROH Output resistance

@ Outp u t High

ROL Output resistance

@ Outp u t L o w

I

Peak output current VCC = 15V, each output

PEAK

I

Continuous output

DC

curre nt

V

EN

V

High En input voltage 2/3 Vcc V

ENH

V

Low En input voltage 1/3 Vcc V

ENL

f

Maximum frequency CL=1.0nF Vcc=15V, max CW frequency

MAX

tR Rise time

tF Fall time

t

ONDLY

t

OFFDLY

P

Minimum pulse width FWHM CL=1nF

Wmin

t

Enable to output low

ENOL

Enable voltage range -0.3 Vcc + 0.3 V

(1)

C

(1)

C

On-time propagation

Off-time propagation

delay

delay

(1)

(1)

delay time

t

Enable to output high

ENOH

delay time

t

Disable to output low

DOLD

Disable delay time

t

Disable to output high

DOHD

Disable delay time

VCC Power supply voltage 8 15 30 V

ICC Power supply current V

(1)

Refer to Figures 2a and 2b

Specifications Subject To Change Without Notice

≤ 25V .

CC

+ 0.3 V

CC

0V ≤ V

I

= 10mA , V

OUT

I

= 10mA , V

OUT

IN

≤ V

CC

= 15V

CC

= 15V 0.8 1.2

CC

-10 10

- 0.025 V

CC

0.8 1.2

µA

Ω

Ω

15 A

2 A

45 MHz

limit e d by pac kag e p ow e r diss ip a t io n

=1nF Vcc=15V VOH=2 V to 12 V

L

=4nF Vcc=15V VOH=2 V to 12 V

C

L

=1nF Vcc=15V VOH=2 V to 12 V

L

=4nF Vcc=15V VOH=2 V to 12 V

C

L

C

=4nF Vcc=15V 32 38 ns

L

C

=4nF Vcc=15V 29 35 ns

L

2.5

4.5

2.0

3.5

5.0

+3V to +3V C

=1nF

L

7.0

ns

ns

ns

ns

ns

ns

Vcc=15V 80 ns

Vcc=15V 170 ns

Vcc=15V 30 ns

Vcc=15V 30 ns

IN

V

IN

V

IN

= 3.5V

= 0V

= + VCC

1 0 3

10

10

mA

µA

µ

A

2

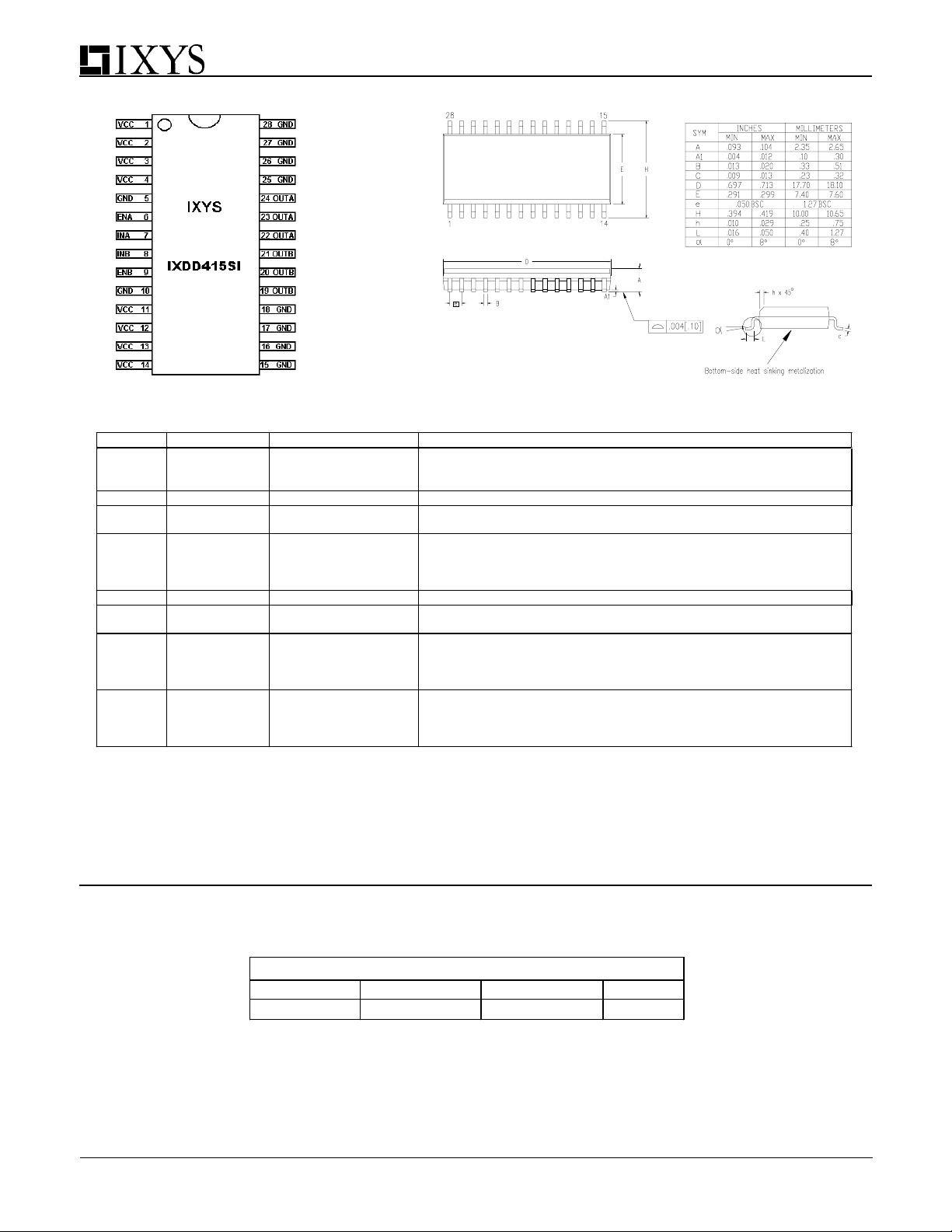

Pin Configurations And Package Outline

NOTE: Bottom-side heat sinking metalization is connected to ground

Pin Description

PIN # SYMBOL FUNCTION DESCRIPTION

1-4

11-14

7 INA Input Input signal-TT L or CM O S com patible.

6 ENA Enable

22-24 OUTA

8 INB Input Input signal-TT L or CM O S com patible.

9 ENB Enable

19-21 OUTB Output

5,10

15-18

25-28

VCC Supply Voltage

Output

GND Ground

Positive power-supply voltage input. This pin provides power

to the entire chip. The range for this voltage is from 8V to

30V.

The system enable pin. This pin, when driven low, disables

the chip, forcing high impedance state to the output.

Driver Output. For application purposes, this pin is

connected to the Gate of a MOS FET. In some app lications,

a low-impedance series resistor may be required between

this o u tp u t a nd the M OSFET Gate .

The system enable pin. This pin, when driven low, disables

the chip, forcing high impedance state to the output.

Driver Output. For application purposes, this pin is

connected to the Gate of a MOS FET. In some app lications,

a low-impedance series resistor may be required between

this o u tp u t a nd the M OSFET Gate .

The system ground pins. Internally connected to all circuitry,

these pins provide ground reference for the entire chip. All of

these pins should be connected to a low noise analog

ground plane for optim um performance.

IXDD415SI

Note 1: Operating the device beyond parameters with listed “Absolute Maximum Ratings” may cause permanent

damage to the device. Typical values indicate conditions for which the device is intended to be functional, but do not

guarantee specific performance limits. The guaranteed specifications apply only for the test conditions listed.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD procedures

when handling and assembling this component.

Ordering Information

Part Number Package Type Temp. Range Grade

IXDD415SI 28-Pin SOIC

-40°C to +85°C

3

Industrial

Loading...

Loading...