IT8712F

Environment Control – Low Pin Count Input / Output

(EC - LPC I/O)

Preliminary Specification V0. 81

ITE TECH. INC.

Specification subject to Change without notice, AS IS and for reference only. For purchasing, please

contact sales representatives.

Please note that the IT8712F V0.81 is applicable to I version and future versions.

Copyright 2004 ITE Tech. Inc.

This is Preliminary document release. All specifications are subject to change without notice.

The material contained in this document supersedes all previous documentation issued for the related

products included herein. Please contact ITE Tech. Inc. for the latest docum ent(s). All sales are subject to

ITE’s Standard Terms and Conditions, a copy of which is included in the back of this document.

All sales are subject to IT E’s Standard Term s and Conditions, a copy of which is included in the bac k of this

document.

ITE, IT8712F is a trademark of ITE Tech. Inc.

Intel is claimed as a trademark by Intel Corp.

Microsoft and Windows are claimed as trademarks by Microsoft Corporation.

PCI is claimed as a trademark by the PCI Special Interest Group.

IrDA is claimed as a trademark by the Infrared Data Association.

All other trademarks are claimed by their respective owners.

All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE Tech. Inc. Phone: (02) 29126889

Marketing Department Fax: (02) 2910-2551, 2910-2552

8F, No. 233-1, Bao Chiao RD., Hsin Tien,

Taipei County 231, Taiwan, R.O.C.

If you have any marketing or sales questions, please contact:

P.Y. Chang, at ITE Taiwan: E-mail: p.y.chang@ite.com.tw, Tel: 886-2-29126889 X6052,

Fax: 886-2-29102551

To find out more about ITE, visit our World Wide Web at:

http://www.ite.com.tw

Or e-mail itesupport@ite.com.tw for more product information/services

y

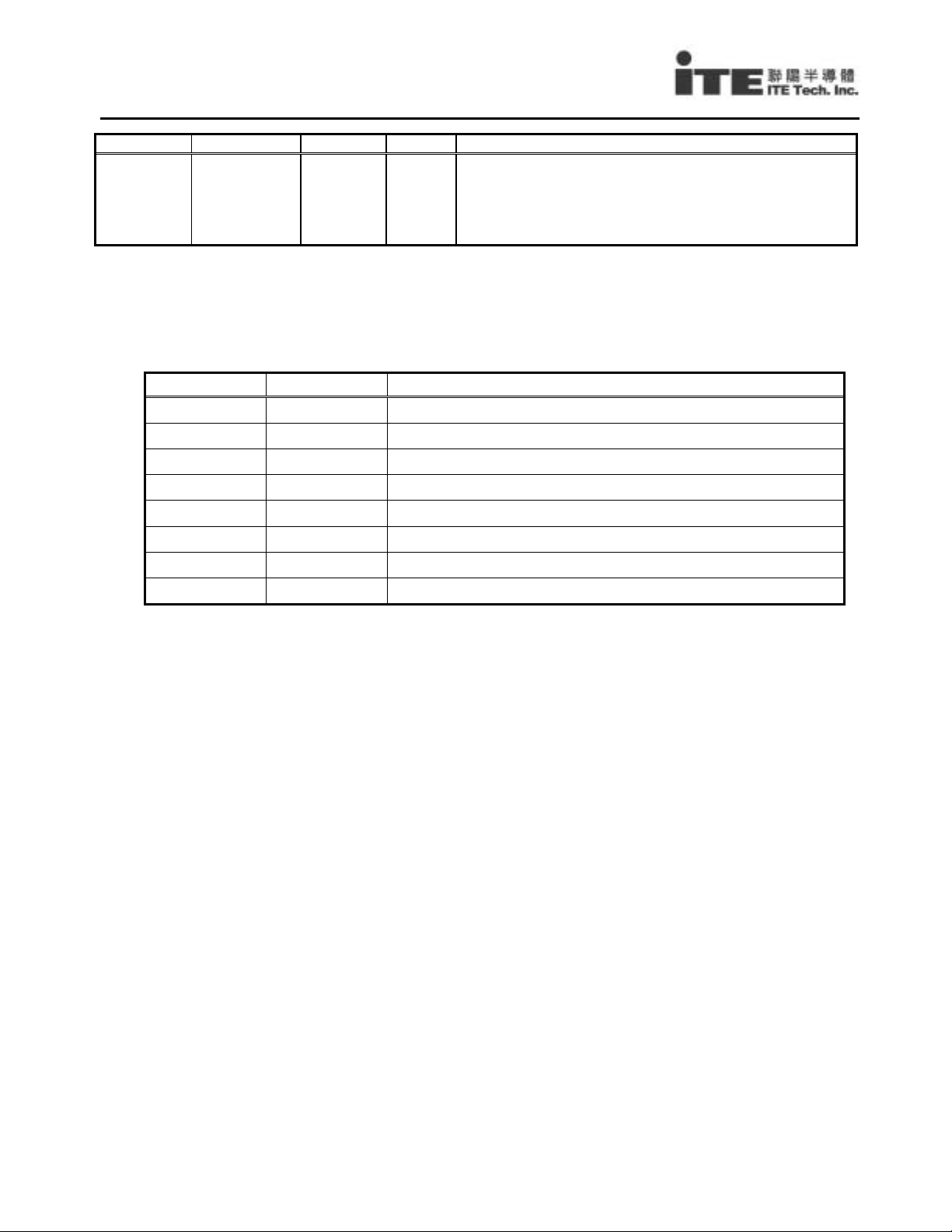

Revision Histor

Revision History

Section Revision Page No.

5

9 In section 9.5.2.1.11, the description of bit 7 and 6 was revised. 77

In section 9.5.2.1.13, the description of bit 7-3 was revised. 78

In table 5-5, JP5 was revised to JP6.

Added a paragraph in the end of section 9.5.3.6: “Enhanced interrupt

mode”. When the enhanced interrupt mode is enabled…

Figure 9-5 was revised.

12, 13

90

www.ite.com.tw IT8712F V0.81

1

Contents

CONTENTS

1. Features ................................................................................................................................................1

2. General Description ....................................................................................................................................... 3

3. Block Diagram................................................................................................................................................5

4. Pin Configuration............................................................................................................................................7

5. IT8712F Pin Descriptions...............................................................................................................................9

6. List of GPIO Pins .........................................................................................................................................21

7. Power On Strapping Options and Special Pin Routings .............................................................................. 23

8. Configuration ..............................................................................................................................................25

8.1 Configuring Sequence Description....................................................................................................25

8.2 Description of the Configuration Registers........................................................................................ 27

8.2.1 Logical Device Base Address............................................................................................... 32

8.3 Global Configuration Registers (LDN: All).........................................................................................34

8.3.1 Configure Control (Index=02h).............................................................................................34

8.3.2 Logical Device Number (LDN, Index=07h)...........................................................................34

8.3.3 Chip ID Byte 1 (Index=20h, Default=87h)............................................................................. 34

8.3.4 Chip ID Byte 2 (Index=21h, Default=12h)............................................................................. 34

8.3.5 Configuration Select and Chip Version (Index=22h, Default=07h).......................................34

8.3.6 Clock Selection Register (Index=23h, Default=00h) ............................................................34

8.3.7 Software Suspend (Index=24h, Default=00h, MB PnP) ....................................................... 35

8.3.8 GPIO Set 1 Multi-Function Pin Selection Register (Index=25h, Default=01h) ..................... 35

8.3.9 GPIO Set 2 Multi-Function Pin Selection Register (Index=26h, Default=00h) ..................... 36

8.3.10 GPIO Set 3 Multi-Function Pin Selection Register (Index=27h, Default=00h) .....................36

8.3.11 GPIO Set 4 Multi-Function Pin Selection Register (Index=28h, Default=40h) .....................37

8.3.12 GPIO Set 5 Multi-Function Pin Selection Register (Index=29h, Default=00h) .....................37

8.3.13 Extended 1 Multi-Function Pin Selection Register (Index=2Ah, Default=00h) ..................... 38

8.3.14 Logical Block Lock Register (Index=2Bh, Default=00h)....................................................... 39

8.3.15 Extended 2 Multi-Function Pin Selection Register (Index=2Ch, Default=1Fh)..................... 39

8.3.16 Test 1 Register (Index=2Eh, Default=00h)........................................................................... 40

8.3.17 Test 2 Register (Index=2Fh, Default=00h)...........................................................................40

8.4 FDC Configuration Registers (LDN=00h) .........................................................................................41

8.4.1 FDC Activate (Index=30h, Default=00h)............................................................................... 41

8.4.2 FDC Base Address MSB Register (Index=60h, Default=03h).............................................. 41

8.4.3 FDC Base Address LSB Register (Index=61h, Default=F0h) .............................................. 41

8.4.4 FDC Interrupt Level Select (Index=70h, Default=06h) .........................................................41

8.4.5 FDC DMA Channel Select (Index=74h, Default=02h)..........................................................41

8.4.6 FDC Special Configuration Register 1 (Index=F0h, Default=00h) .......................................41

8.4.7 FDC Special Configuration Register 2 (Index=F1h, Default=00h) .......................................42

8.5 Serial Port 1 Configuration Registers (LDN=01h) ............................................................................. 43

8.5.1 Serial Port 1 Activate (Index=30h, Default=00h) .................................................................. 43

8.5.2 Serial Port 1 Base Address MSB Register (Index=60h, Default=03h) ...................................43

8.5.3 Serial Port 1 Base Address LSB Register (Index=61h, Default=F8h) .................................... 43

8.5.4 Serial Port 1 Interrupt Level Select (Index=70h, Default=04h).............................................43

8.5.5 Serial Port 1 Special Configuration Register 1 (Index=F0h, Default=00h)...........................43

8.5.6 Serial Port 1 Special Configuration Register 2 (Index=F1h, Default=50h)...........................44

8.5.7 Serial Port 1 Special Configuration Register 3 (Index=F2h, Default=00h)...........................44

8.5.8 Serial Port 1 Special Configuration Register 4 (Index=F3h, Default=7Fh)........................... 44

8.6 Serial Port 2 Configuration Registers (LDN=02h) ............................................................................. 45

8.6.1 Serial Port 2 Activate (Index=30h, Default=00h) .................................................................. 45

www.ite.com.tw IT8712F V0.81

i i

IT8712F

8.6.2 Serial Port 2 Base Address MSB Register (Index=60h, Default=02h) ...................................45

8.6.3 Serial Port 2 Base Address LSB Register (Index=61h, Default=F8h) .................................... 45

8.6.4 Serial Port 2 Interrupt Level Select (Index=70h, Default=03h).............................................45

8.6.5 Serial Port 2 Special Configuration Register 1 (Index=F0h, Default=00h)...........................45

8.6.6 Serial Port 2 Special Configuration Register 2 (Index=F1h, Default=50h)...........................46

8.6.7 Serial Port 2 Special Configuration Register 3 (Index=F2h, Default=00h)...........................46

8.6.8 Serial Port 2 Special Configuration Register 4 (Index=F3h, Default=7Fh)........................... 46

8.7 Parallel Port Configuration Registers (LDN=03h) ............................................................................. 47

8.7.1 Parallel Port Activate (Index=30h, Default=00h) ..................................................................47

8.7.2 Parallel Port Primary Base Address MSB Register (Index=60h, Default=03h) ...................... 47

8.7.3 Parallel Port Primary Base Address LSB Register (Index=61h, Default=78h) ..................... 47

8.7.4 Parallel Port Secondary Base Address MSB Register (Index=62h, Default=07h) .................47

8.7.5 Parallel Port Secondary Base Address LSB Register (Index=63h, Default=78h) ................ 47

8.7.6 Parallel Port Interrupt Level Select (Index =70h, Default=07h)............................................47

8.7.7 Parallel Port DMA Channel Select (Index=74h, Default=03h)..............................................47

8.7.8 Parallel Port Special Configuration Register (Index=F0h, Default=03h) .............................. 48

8.8 Environment Controller Configuration Registers (LDN=04h)............................................................49

8.8.1 Environment Controller Activate Register (Index=30h, Default=00h)................................... 49

8.8.2 Environment Controller Base Address MSB Register (Index=60h, Default=02h) .................. 49

8.8.3 Environment Controller Base Address LSB Register (Index=61h, Default=90h) ................... 49

8.8.4 PME Direct Access Base Address MSB Register (Index=62h, Default=02h) ........................ 49

8.8.5 PME Direct Access Base Address LSB Register (Index=63h, Default=30h) ......................... 49

8.8.6 Environment Controller Interrupt Level Select (Index=70h, Default=09h)............................49

8.8.7 APC/PME Event Enable Register (PER) (Index=F0h, Default=00h).................................... 49

8.8.8 APC/PME Status Register (PSR) (Index=F1h, Default=00h)...............................................50

8.8.9 APC/PME Control Register 1 (PCR 1) (Index=F2h, Default=00h) .......................................50

8.8.10 Environment Controller Special Configuration Register (Index=F3h, Default=00h).............51

8.8.11 APC/PME Control Register 2 (PCR 2) (Index=F4h, Default=00h) ....................................... 51

8.8.12 APC/PME Special Code Index Register (Index=F5h) ..........................................................51

8.8.13 APC/PME Special Code Data Register (Index=F6h) ........................................................... 51

8.9 KBC (keyboard) Configuration Registers (LDN=05h) .......................................................................52

8.9.1 KBC (keyboard) Activate (Index=30h, Default=01h or 00h) ................................................. 52

8.9.2 KBC (keyboard) Data Base Address MSB Register (Index=60h, Default=00h)................... 52

8.9.3 KBC (keyboard) Data Base Address LSB Register (Index=61h, Default=60h).................... 52

8.9.4 KBC (keyboard) Command Base Address MSB Register (Index=62h, Default=00h).......... 52

8.9.5 KBC (keyboard) Command Base Address LSB Register (Index=63h, Default=64h)........... 52

8.9.6 KBC (keyboard) Interrupt Level Select (Index=70h, Default=01h) ....................................... 52

8.9.7 KBC (keyboard) Interrupt Type (Index=71h, Default=02h)................................................... 53

8.9.8 KBC (keyboard) Special Configuration Register (Index=F0h, Default=00h)............................. 53

8.10 KBC (mouse) Configuration Registers (LDN=06h)...........................................................................53

8.10.1 KBC (mouse) Activate (Index=30h, Default=00h) ................................................................ 53

8.10.2 KBC (mouse) Interrupt Level Select (Index=70h, Default=0Ch).............................................. 53

8.10.3 KBC (mouse) Interrupt Type (Index=71h, Default=02h)....................................................... 53

8.10.4 KBC (mouse) Special Configuration Register (Index=F0h, Default=00h)............................54

8.11 GPIO Configuration Registers (LDN=07h)........................................................................................ 55

8.11.1 SMI# Normal Run Access Base Address MSB Register (Index=60h, Default=00h)............ 55

8.11.2 SMI# Normal Run Access Base Address LSB Register (Index=61h, Default=00h)............. 55

8.11.3 Simple I/O Base Address MSB Register (Index=62h, Default=00h) .................................... 55

8.11.4 Simple I/O Base Address LSB Register (Index=63h, Default=00h) ..................................... 55

8.11.5 Panel Button De-bounce Base Address MSB Register (Index=64h, Default=00h)..............55

8.11.6 Panel Button De-bounce Base Address LSB Register (Index=65h, Default=00h)...............55

8.11.7 Panel Button De-bounce Interrupt Level Select Register (Index=70h, Default=00h)........... 55

8.11.8 Watch Dog Timer Control Register (Index=71h, Default=00h) ............................................55

www.ite.com.tw IT8712F V0.81

ii

Contents

8.11.9 Watch Dog Timer Configuration Register (Index=72h, Default=00h)................................... 56

8.11.10 Watch Dog Timer Time-Out Value Register (Index=73h, Default=00h)............................... 56

8.11.11 GPIO Pin Set 1, 2, 3, 4 and 5 Polarity Registers (Index=B0h, B1h, B2h, B3h and B4h,

Default=00h)......................................................................................................................... 56

8.11.12 GPIO Pin Set 1, 2, 3, 4 and 5 Pin Internal Pull-up Enable Registers (Index=B8h, B9h, BAh,

BBh and BCh, Default=00h).................................................................................................56

8.11.13 Simple I/O Set 1, 2, 3, 4 and 5 Enable Registers (Index=C0h, C1h, C2h, C3h and C4h,

Default=01h, 00h, 00h, 40h, and 00h).................................................................................. 56

8.11.14 Simple I/O Set 1, 2, 3, 4 and 5 Output Enable Registers (Index=C8h, C9h, CAh, CBh and

CCh, Default=01h, 00h, 00h, 40h, and 00h)......................................................................... 57

8.11.15 Panel Button De-bounce Control Register (Index=D0h, Default=00h)................................. 57

8.11.16 Panel Button De-bounce Set 1, 2, 3, 4 and 5 Enable Registers (Index=D1h, D2h, D3h, D4h

and D5h, Default=00h) ......................................................................................................... 57

8.11.17 IRQ3-7, 9-12 and 14-15 External Routing Input Pin Mapping Registers (Index=E3h-E7h,

E9h-ECh and EEh-EFh, Default=00h)..................................................................................57

8.11.18 SMI# Control Register 1 (Index=F0h, Default=00h).............................................................57

8.11.19 SMI# Control Register 2 (Index=F1h, Default=00h).............................................................58

8.11.20 SMI# Status Register 1 (Index=F2h, Default=00h)...............................................................58

8.11.21 SMI# Status Register 2 (Index=F3h, Default=00h)...............................................................58

8.11.22 SMI# Pin Mapping Register (Index=F4h, Default=00h)........................................................ 58

8.11.23 Hardware Monitor Thermal Output Pin Mapping Register (Index=F5h, Default=00h) .........59

8.11.24 Hardware Monitor Alert Beep Pin Mapping Register (Index=F6h, Default=00h).................. 59

8.11.25 Keyboard Lock Pin Mapping Register (Index=F7h, Default=00h) ........................................ 59

8.11.26 GP LED Blinking 1 Pin Mapping Register (Index=F8h, Default=00h) .................................. 59

8.11.27 GP LED Blinking 1 Control Register (Index=F9h, Default=00h)........................................... 59

8.11.28 GP LED Blinking 2 Pin Mapping Register (Index=FAh, Default=00h).................................... 59

8.11.29 GP LED Blinking 2 Control Register (Index=FBh, Default=00h) .......................................... 60

8.11.30 VID Input Register (Index=FCh, Default=--h).......................................................................60

8.11.31 VID Output Register (Index=FDh, Default=00h)................................................................... 60

8.12 MIDI Port Configuration Registers (LDN=08h).................................................................................. 61

8.12.1 MIDI Port Activate (Index=30h, Default=00h).......................................................................61

8.12.2 MIDI Port Base Address MSB Register (Index=60h, Default=03h)........................................ 61

8.12.3 MIDI Port Base Address LSB Register (Index=61h, Default=00h)......................................... 61

8.12.4 MIDI Port Interrupt Level Select (Index=70h, Default=0Ah).................................................61

8.12.5 MIDI Port Special Configuration Register (Index=F0h, Default=00h)................................... 61

8.13 Game Port Configuration Registers (LDN=09h) ............................................................................... 62

8.13.1 Game Port Activate (Index=30h, Default=00h) ....................................................................62

8.13.2 Game Port Base Address MSB Register (Index=60h, Default=02h)...................................... 62

8.13.3 Game Port Base Address LSB Register (Index=61h, Default=01h)....................................... 62

8.14 Consumer IR Configuration Registers (LDN=0Ah) ........................................................................... 63

8.14.1 Consumer IR Activate (Index=30h, Default=00h)................................................................. 63

8.14.2 Consumer IR Base Address MSB Register (Index=60h, Default=03h).................................. 63

8.14.3 Consumer IR Base Address LSB Register (Index=61h, Default=10h)................................... 63

8.14.4 Consumer IR Interrupt Level Select (Index=70h, Default=0Bh)...........................................63

8.14.5 Consumer IR Special Configuration Register (Index=F0h, Default=00h)............................. 63

9. Functional Description..................................................................................................................................65

9.1 LPC Interface....................................................................................................................................65

9.1.1 LPC Transactions.................................................................................................................65

9.1.2 LDRQ# Encoding..................................................................................................................65

9.2 Serialized IRQ...................................................................................................................................65

9.2.1 Continuous Mode .................................................................................................................65

9.2.2 Quiet Mode...........................................................................................................................66

www.ite.com.tw IT8712F V0.81

iii iii

IT8712F

9.2.3 Waveform Samples of SERIRQ Sequence.......................................................................... 66

9.2.4 SERIRQ Sampling Slot......................................................................................................... 67

9.3 General Purpose I/O ......................................................................................................................... 68

9.4 Advanced Power Supply Control and Power Management Event (PME#).......................................70

9.5 Environment Controller .....................................................................................................................71

9.5.1 Interfaces..............................................................................................................................71

9.5.2 Registers .............................................................................................................................. 71

9.5.2.1 Address Port (Base+05h, Default=00h):.................................................................. 71

9.5.2.2 Register Description ................................................................................................75

9.5.2.2.1 Configuration Register (Index=00h, Default=18h)............................ 75

9.5.2.2.2 Interrupt Status Register 1 (Index=01h, Default=00h) ..................... 76

9.5.2.2.3 Interrupt Status Register 2 (Index=02h, Default=00h) ..................... 76

9.5.2.2.4 Interrupt Status Register 3 (Index=03h, Default=00h) ..................... 76

9.5.2.2.5 SMI# Mask Register 1 (Index=04h, Default=00h)............................76

9.5.2.2.6 SMI# Mask Register 2 (Index=05h, Default=00h)............................76

9.5.2.2.7 SMI# Mask Register 3 (Index=06h, Default=00h)............................76

9.5.2.2.8 Interrupt Mask Register 1 (Index=07h, Default=00h).......................77

9.5.2.2.9 Interrupt Mask Register 2 (Index=08h, Default=00h).......................77

9.5.2.2.10 Interrupt Mask Register 3 (Index=09h, Default=00h).......................77

9.5.2.2.11 VID Register (Index=0Ah) ................................................................ 77

9.5.2.2.12 Fan Tachometer Divisor Register (Index=0Bh, Default=09h).......... 77

9.5.2.2.13 Fan Tachometer 16-bit Counter Enable Register (Index=0Ch,

Default=00h) .....................................................................................................78

9.5.2.2.14 Fan Tachometer 1-3 Reading Registers (Index=0Dh-0Fh).............. 78

9.5.2.2.15 Fan Tachometer 1-3 Limit Registers (Index=10h-12h) .................... 78

9.5.2.2.16 Fan Controller Main Control Register (Index=13h, Default=00h).....78

9.5.2.2.17 FAN_CTL Control Register (Index=14h, Default=50h) .................... 79

9.5.2.2.18 FAN_CTL1 PWM Control Register (Index=15h, Default=00h or 40h).

.....................................................................................................79

9.5.2.2.19 FAN_CTL2 PWM Control Register (Index=16h, Default=00h or 40h).

.....................................................................................................80

9.5.2.2.20 FAN_CTL3 PWM Control Register (Index=17h, Default=00h or 40h).

.....................................................................................................80

9.5.2.2.21 Fan Tachometer 1-3 Extended Reading Registers (Index=18h-1Ah)..

.....................................................................................................80

9.5.2.2.22 Fan Tachometer 1-3 Extended Limit Registers (Index=1Bh-1Dh)... 80

9.5.2.2.23 VIN7-VIN0 Voltage Reading Registers (Index=27h-20h)................. 80

9.5.2.2.24 VBAT Voltage Reading Register (Index=28h)..................................80

9.5.2.2.25 TMPIN3-1 Temperature Reading Registers (Index=2Bh-29h)......... 81

9.5.2.2.26 VIN7-0 Low Limit Registers (Index=3Fh, 3Dh, 3Bh, 39h, 37h, 35h,

33h, 31h) .....................................................................................................81

9.5.2.2.27 TMPIN3-1 High Limit Registers (Index=44h, 42h, 40h) ................... 81

9.5.2.2.28 TMPIN3-1 Low Limit Registers (Index=45h, 43h, 41h)....................82

9.5.2.2.29 ADC Voltage Channel Enable Register (Index=50h, Default=00h).. 82

9.5.2.2.30 ADC Temperature Channel Enable Register (Index=51h,

Default=00h) .....................................................................................................82

9.5.2.2.31 TMPIN3-1 Thermal Output Limit Registers (Index=54h-52h,

Default=7Fh) ..................................................................................................... 82

9.5.2.2.32 Thermal Diode Zero Degree Adjust 1 Register (Index=56h,

Default=56h) .....................................................................................................82

9.5.2.2.33 Thermal Diode Zero Degree Adjust 2 Register (Index=57h,

Default=56h) .....................................................................................................82

9.5.2.2.34 Vendor ID Register (Index=58h, Default=90h).................................82

www.ite.com.tw IT8712F V0.81

iv

Contents

9.5.2.2.35 Thermal Diode Zero Degree Adjust 3 Register (Index=59h,

Default=56h) .....................................................................................................83

9.5.2.2.36 Code ID Register (Index=5Bh, Default=12h) ................................... 83

9.5.2.2.37 Beep Event Enable Register (Index=5Ch, Default=00h).................. 83

9.5.2.2.38 Beep Frequency Divisor of Fan Event Register (Index=5Dh,

Default=00h) .....................................................................................................83

9.5.2.2.39 Beep Frequency Divisor of Voltage Event Register (Index=5Eh,

Default=00h) .....................................................................................................83

9.5.2.2.40 Beep Frequency Divisor of Temper ature Event Register (I ndex=5Fh,

Default=00h) .....................................................................................................83

9.5.2.2.41 FAN_CTL3-1 SmartGuar dian Automatic Mode Temperature Lim it of

OFF Registers (Index=70h, 68h, 60h, Default=7Fh) .............................................83

9.5.2.2.42 FAN_CTL3-1 SmartGuar dian Automatic Mode Temperature Lim it of

Fan Start Registers (Index=71h, 69h, 61h, Default=7Fh)......................................84

9.5.2.2.43 FAN_CTL3-1 SmartGuar dian Automatic Mode Temperature Lim it of

Full Speed Registers (Index=72h, 6Ah, 62h, Default=7Fh) ................................... 84

9.5.2.2.44 FAN_CTL3-1 SmartGuar dian Automatic Mode Start PW M Registers

(Index=73h, 6Bh, 63h, Default=00h)...................................................................... 84

9.5.2.2.45 FAN_CTL3-1 SmartGuardian Automatic Mode Control Registers

(Index=74h, 6Ch, 64h, Default=00h)...................................................................... 84

9.5.2.2.46 FAN_CTL3-1 SmartGuar dian Automatic Mode Temperature Lim it of

Full-Speed-OFF Registers (Index=75h, 6Dh, 65h, Default=7Fh)..........................85

9.5.2.2.47 Fan Tachometer 4-5 Reading LSB Registers (Index=80h,82h)....... 85

9.5.2.2.48 Fan Tachometer 4-5 Reading MSB Registers (Index=81h,83h)...... 85

9.5.2.2.49 Fan Tachometer 4-5 Limit LSB Registers (Index=84h,86h)............. 85

9.5.2.2.50 Fan Tachometer 4-5 Limit MSB Registers (Index=85h,87h)............ 85

9.5.2.2.51 FAN_CTL4 PWM Control Register (Index=88h, Default=00h) ........85

9.5.2.2.52 FAN_CTL5 PWM Control Register (Index=89h, Default=00h) ........85

9.5.2.2.53 FAN_CTL5-4 SmartGuar dian Automatic Mode Temperature Lim it of

OFF Registers (Index=98h, 90h, Default=7Fh) .....................................................86

9.5.2.2.54 FAN_CTL5-4 SmartGuar dian Automatic Mode Temperature Lim it of

Fan Start Registers (Index=99h, 91h, Default=7Fh)..............................................86

9.5.2.2.55 FAN_CTL5-4 SmartGuar dian Automatic Mode Temperature Lim it of

Full Speed Registers (Index=9Ah, 92h, Default=7Fh) ........................................... 86

9.5.2.2.56 FAN_CTL5-4 SmartGuar dian Automatic Mode Start PW M Registers

(Index=9Bh, 93h, Default=00h).............................................................................. 86

9.5.2.2.57 FAN_CTL5-4 SmartGuardian Automatic Mode Control Registers

(Index=9Ch, 94h, Default=00h).............................................................................. 86

9.5.2.2.58 FAN_CTL5-4 SmartGuar dian Automatic Mode Temperature Lim it of

Full-Speed-OFF Registers (Index=9Dh, 95h, Default=7Fh) ..................................87

9.5.3 Operation..............................................................................................................................87

9.5.3.1 Power On RESET and Software RESET................................................................. 87

9.5.3.2 Starting Conversion ................................................................................................. 87

9.5.3.3 Voltage and Temperature Inputs.............................................................................88

9.5.3.4 Layout and Grounding ............................................................................................. 89

9.5.3.5 Fan Tachometer ......................................................................................................89

9.5.3.6 Interrupt of the EC ...................................................................................................89

9.5.3.7 FAN Controller FAN_CTL’s ON-OFF and SmartGuardian Modes .......................... 91

9.6 Floppy Disk Controller (FDC)............................................................................................................92

9.6.1 Introduction........................................................................................................................... 92

9.6.2 Reset....................................................................................................................................92

9.6.3 Hardware Reset (LRESET# Pin)..........................................................................................92

9.6.4 Software Reset (DOR Reset and DSR Reset).....................................................................92

www.ite.com.tw IT8712F V0.81

v v

IT8712F

9.6.5 Digital Data Separator ..........................................................................................................92

9.6.6 Write Precompensation........................................................................................................92

9.6.7 Data Rate Selection.............................................................................................................. 92

9.6.8 Status, Data and Control Registers......................................................................................93

9.6.8.1 Digital Output Register (DOR, FDC Base Address + 02h) ...................................... 93

9.6.8.2 Tape Drive Register (TDR, FDC Base Address + 03h)...........................................93

9.6.8.3 Main Status Register (MSR, FDC Base Address + 04h).........................................93

9.6.8.4 Data Rate Select Register (DSR, FDC Base Address + 04h)................................. 95

9.6.8.5 Data Register (FIFO, FDC Base Address + 05h) ....................................................96

9.6.8.6 Digital Input Register (DIR, FDC Base Address + 07h)...........................................96

9.6.8.7 Diskette Control Register (DCR, FDC Base Address + 07h)................................... 96

9.6.9 Controller Phases.................................................................................................................97

9.6.9.1 Command Phase.....................................................................................................97

9.6.9.2 Execution Phase......................................................................................................97

9.6.9.3 Result Phase............................................................................................................ 97

9.6.9.4 Result Phase Status Registers................................................................................97

9.6.10 Command Set ....................................................................................................................100

9.6.11 Data Transfer Commands..................................................................................................110

9.6.11.1 Read Data.............................................................................................................. 110

9.6.11.2 Read Deleted Data ................................................................................................111

9.6.11.3 Read a Track .........................................................................................................111

9.6.11.4 Write Data.............................................................................................................. 111

9.6.11.5 Write Deleted Data ................................................................................................ 111

9.6.11.6 Format A Track...................................................................................................... 111

9.6.11.7 SCAN.....................................................................................................................112

9.6.11.8 VERIFY..................................................................................................................113

9.6.12 Control Commands ............................................................................................................113

9.6.12.1 READ ID ................................................................................................................114

9.6.12.2 Configure ...............................................................................................................114

9.6.12.3 RE-CALIBRATE..................................................................................................... 114

9.6.12.4 SEEK .....................................................................................................................115

9.6.12.5 RELATIVE SEEK...................................................................................................115

9.6.12.6 DUMPREG............................................................................................................. 115

9.6.12.7 LOCK..................................................................................................................... 115

9.6.12.8 VERSION............................................................................................................... 115

9.6.12.9 SENSE INTERRUPT STATUS.............................................................................. 116

9.6.12.10 SENSE DRIVE STATUS .......................................................................................116

9.6.12.11 SPECIFY................................................................................................................ 116

9.6.12.12 PERPENDICULAR MODE..................................................................................... 117

9.6.12.13 INVALID.................................................................................................................118

9.6.13 DMA Transfers ...................................................................................................................118

9.6.14 Low Power Mode................................................................................................................ 118

9.7 Serial Port (UART) Description ....................................................................................................... 119

9.7.1 Data Registers....................................................................................................................119

9.7.2 Control Registers: IER, IIR, FCR, DLL, DLM, LCR and MCR............................................119

9.7.3 Status Registers: LSR and MSR ........................................................................................ 125

9.7.4 Reset..................................................................................................................................127

9.7.5 Programming...................................................................................................................... 127

9.7.6 Software Reset................................................................................................................... 127

9.7.7 Clock Input Operation......................................................................................................... 127

9.7.8 FIFO Interrupt Mode Operation..........................................................................................128

9.8 Smart Card Reader.........................................................................................................................129

9.8.1 Features ............................................................................................................................. 129

www.ite.com.tw IT8712F V0.81

vi

Contents

9.8.2 Operation............................................................................................................................129

9.8.3 Connection of IFD to ICC Socket ....................................................................................... 129

9.8.4 Baud Rate Relationship Between UART and Smart Card Interface .................................. 130

9.8.5 Waveform Relationship......................................................................................................130

9.8.6 Clock Divider ......................................................................................................................130

9.8.7 Waveform Example of Activation/Deactivation Sequence ................................................. 131

9.8.8 ATR and PTS Structure...................................................................................................... 132

9.8.9 Smart Card Operating Sequence Example........................................................................133

9.9 Parallel Port..................................................................................................................................... 134

9.9.1 SPP and EPP Modes .........................................................................................................134

9.9.2 EPP Mode Operation.......................................................................................................... 136

9.9.3 ECP Mode Operation .........................................................................................................137

9.10 Keyboard Controller (KBC)..............................................................................................................143

9.10.1 Host Interface .....................................................................................................................144

9.10.2 Data Registers and Status Register ................................................................................... 144

9.10.3 Keyboard and Mouse Interface ..........................................................................................145

9.10.4 KIRQ and MIRQ .................................................................................................................145

9.11 Consumer Remote Control (TV Remote) IR (CIR)......................................................................... 146

9.11.1 Overview............................................................................................................................. 146

9.11.2 Features ............................................................................................................................. 146

9.11.3 Block Diagram .................................................................................................................... 146

9.11.4 Transmit Operation............................................................................................................. 147

9.11.5 Receive Operation.............................................................................................................. 147

9.11.6 Register Descriptions and Address....................................................................................147

9.11.6.1 CIR Data Register (DR).........................................................................................148

9.11.6.2 CIR Interrupt Enable Register (IER) ......................................................................148

9.11.6.3 CIR Receiver Control Register (RCR) ................................................................... 149

9.11.6.4 CIR Transmitter Control Register 1 (TCR1) ..........................................................150

9.11.6.5 CIR Transmitter Control Register (TCR2) .............................................................151

9.11.6.6 CIR Baud Rate Divisor Low Byte Register (BDLR)................................................ 154

9.11.6.7 CIR Baud Rate Divisor High Byte Register (BDHR)..............................................154

9.11.6.8 CIR Transmitter Status Register (TSR).................................................................154

9.11.6.9 CIR Receiver FIFO Status Register (RSR)............................................................155

9.11.6.10 CIR Interrupt Identification Register (IIR)............................................................... 155

9.12 Game Port Interface........................................................................................................................156

9.12.1 Game Port (Base+0h) ........................................................................................................156

9.13 MIDI Interface.................................................................................................................................. 156

9.13.1 MPU-401 Register Interface...............................................................................................156

9.13.2 Operation............................................................................................................................ 157

10. DC Electrical Characteristics .....................................................................................................................158

11. AC Characteristics (VCC = 5V ± 5%, Ta = 0°C to + 70°C)........................................................................161

11.1 Clock Input Timings ........................................................................................................................161

11.2 LCLK (PCICLK) and LRESET Timings ........................................................................................... 161

11.3 LPC and SERIRQ Timings..............................................................................................................162

11.4 Serial Port, ASKIR, SIR and Consumer Remote Control Timings..................................................163

11.5 Modem Control Timings..................................................................................................................163

11.6 Floppy Disk Drive Timings ..............................................................................................................164

11.7 EPP Address or Data Write Cycle Timings..................................................................................... 165

11.8 EPP Address or Data Read Cycle Timings..................................................................................... 166

11.9 ECP Parallel Port Forward Timings ................................................................................................166

11.10 ECP Parallel Port Backward Timings.............................................................................................167

11.11 RSMRST#, PWROK1/2, and ACPI Power Control Signals Timings..............................................167

www.ite.com.tw IT8712F V0.81

vii vii

IT8712F

12. Package Information.................................................................................................................................. 169

13. Ordering Information..................................................................................................................................171

www.ite.com.tw IT8712F V0.81

viii

Contents

FIGURES

Figure 7-1. IT8712F Special Applications Circuitry for Intel ICH.......................................................................23

Figure 9-1. Start Frame Timing ......................................................................................................................... 66

Figure 9-2. Stop Frame Timing .........................................................................................................................66

Figure 9-3. General Logic of GPIO Function..................................................................................... ................69

Figure 9-4. Application Example. Resistor should provide approximately 2V at the Analog Inputs.................. 88

Figure 9-5. Temperature Interrupt Response Diagram.....................................................................................90

Figure 9-6. SmartGuardian Automatic Mode.....................................................................................................91

Figure 9-7. Smart Card Reader Application ....................................................................................................129

Figure 9-8. 9600 Baud Rate Example.............................................................................................................130

Figure 9-9. Waveform Example of IFD ...........................................................................................................131

Figure 9-10. Keyboard and Mouse Interface...................................................................................................143

Figure 9-11. CIR Block Diagram .....................................................................................................................146

Figure 11-1. Clock Input Timings .................................................................................................................... 161

Figure 11-2. LCLK (PCICLK) and LRESET Timings....................................................................................... 161

Figure 11-3. LPC and SERIRQ Timings..........................................................................................................162

Figure 11-4. Serial Port, ASKIR, SIR and Consumer Remote Control Timings.............................................. 163

Figure 11-5. Modem Control Timings..............................................................................................................163

Figure 11-6. Floppy Disk Drive Timings .......................................................................................................... 164

Figure 11-7. EPP Address or Data Write Cycle Timings.................................................................................165

Figure 11-8. EPP Address or Data Read Cycle Timings................................................................................. 166

Figure 11-9. ECP Parallel Port Forward Timings ............................................................................................ 166

Figure 11-10. ECP Parallel Port Backward Timings........................................................................................167

TABLES

Table 4-1. Pins Listed in Numeric Order.............................................................................................................8

Table 5-1. Pin Description of Supplies Signals....................................................................................................9

Table 5-2. Pin Description of LPC Bus Interface Signals....................................................................................9

Table 5-3. Pin Description of MIDI Interface Signals......................................................................................... 10

Table 5-4. Pin Description of Game Port Signals.............................................................................................. 10

Table 5-5. Pin Description of Hardware Monitor Signals

Table 5-6. Pin Description of Fan Controller Signals ........................................................................................13

Table 5-7. Pin Description of Infrared Port Signals ........................................................................................... 14

Table 5-8. Pin Description of Serial Port 1 Signals............................................................................................14

Table 5-9. Pin Description of Serial Port 2 Signals............................................................................................15

Table 5-10. Pin Description of Parallel Port Signals..........................................................................................16

Table 5-11. Pin Description of Floppy Disk Controller Signals.......................................................................... 17

Table 5-12. Pin Description of Smart Card Reader Interface Signals...............................................................17

www.ite.com.tw IT8712F V0.81

Note1

............................................................................11

ix ix

IT8712F

Table 5-13. Pin Description of Keyboard Controller Signals .............................................................................19

Table 5-14. Pin Description of Miscellaneous Signals ......................................................................................19

Table 6-1. General Purpose I/O Group 1 (Set 1) .............................................................................................. 21

Table 6-2. General Purpose I/O Group 2 (Set 2) .............................................................................................. 21

Table 6-3. General Purpose I/O Group 3 (Set 3) .............................................................................................. 21

Table 6-4. General Purpose I/O Group 4 (Set 4) .............................................................................................. 22

Table 6-5. General Purpose I/O Group 5 (Set 5) .............................................................................................. 22

Table 7-1. Power On Strapping Options............................................................................................................ 23

Table 8-1. Global Configuration Registers ........................................................................................................27

Table 8-2. FDC Configuration Registers ........................................................................................................... 27

Table 8-3. Serial Port 1 Configuration Registers...............................................................................................27

Table 8-4. Serial Port 2 Configuration Registers...............................................................................................28

Table 8-5. Parallel Port Configuration Registers...............................................................................................28

Table 8-6. Environment Controller Configuration Registers.............................................................................. 28

Table 8-7. KBC(Keyboard) Configuration Registers.......................................................................................... 29

Table 8-8. KBC(Mouse) Configuration Registers..............................................................................................29

Table 8-9. GPIO Configuration Registers..........................................................................................................30

Table 8-10. GPIO Configuration Registers........................................................................................................31

Table 8-11. MIDI Port Configuration Registers .................................................................................................32

Table 8-12. Game Port Configuration Registers ............................................................................................... 32

Table 8-13. Consumer IR Configuration Registers ........................................................................................... 32

Table 8-14. Base Address of Logical Devices................................................................................................... 32

Table 9-1. Address Map on the LPC Bus.......................................................................................................... 71

Table 9-2. Environment Controller Registers .................................................................................................... 72

Table 9-3. Digital Output Register (DOR)..........................................................................................................93

Table 9-4. Tape Drive Register (TDR) .............................................................................................................. 93

Table 9-5. Main Status Register (MSR) ............................................................................................................94

Table 9-6. Data Rate Select Register (DSR).....................................................................................................95

Table 9-7. Data Register (FIFO)........................................................................................................................ 96

Table 9-8. Digital Input Register (DIR) ..............................................................................................................96

Table 9-9. Diskette Control Register (DCR)......................................................................................................96

Table 9-10. Status Register 0 (ST0)..................................................................................................................97

Table 9-11. Status Register 1 (ST1)..................................................................................................................98

Table 9-12. Status Register 2 (ST2)..................................................................................................................99

Table 9-13. Status Register 3 (ST3)..................................................................................................................99

Table 9-14. Command Set Symbol Descriptions ............................................................................................ 100

Table 9-15. Command Set Summary..............................................................................................................102

Table 9-16. Effects of MT and N Bits .............................................................................................................. 110

Table 9-17. SCAN Command Result .............................................................................................................. 112

www.ite.com.tw IT8712F V0.81

x

Contents

Table 9-18. VERIFY Command Result ...........................................................................................................113

Table 9-19. Interrupt Identification................................................................................................................... 116

Table 9-20. HUT Values.................................................................................................................................. 116

Table 9-21. SRT Values..................................................................................................................................116

Table 9-22. HLT Values ..................................................................................................................................117

Table 9-23. Effects of GAP and WG on FORMAT A TRACK and WRITE DATA Commands....................... 117

Table 9-24. Effects of Drive Mode and Data Rate on FORMAT A TRACK and WRITE DATA Commands ..117

Table 9-25. Serial Channel Registers.............................................................................................................. 119

Table 9-26. Interrupt Enable Register Description ..........................................................................................120

Table 9-27. Interrupt Identification Register ....................................................................................................121

Table 9-28. FIFO Control Register Description...............................................................................................122

Table 9-29. Receiver FIFO Trigger Level Encoding........................................................................................122

Table 9-30. Baud Rates Using (24 MHz ÷ 13) Clock ...................................................................................... 123

Table 9-31. Line Control Register Description ................................................................................................124

Table 9-32. Stop Bits Number Encoding.........................................................................................................124

Table 9-33. Modem Control Register Description...........................................................................................125

Table 9-34. Line Status Register Description..................................................................................................125

Table 9-35. Modem Status Register Description............................................................................................. 126

Table 9-36. Reset Control of Registers and Pinout Signals............................................................................127

Table 9-37. SCRCLK Selections.....................................................................................................................130

Table 9-38. Parallel Port Connector in Different Modes.................................................................................. 134

Table 9-39. Address Map and Bit Map for SPP and EPP Modes ...................................................................134

Table 9-40. Bit Map of the ECP Registers ......................................................................................................137

Table 9-41. ECP Register Definitions..............................................................................................................137

Table 9-42. ECP Mode Descriptions...............................................................................................................138

Table 9-43. ECP Pin Descriptions...................................................................................................................138

Table 9-44. Extended Control Register (ECR) Mode and Description............................................................140

Table 9-45. Data Register READ/WRITE Controls.........................................................................................144

Table 9-46. Status Register.............................................................................................................................144

Table 9-47. List of CIR Registers .................................................................................................................... 147

Table 9-48. Modulation Carrier Frequency......................................................................................................152

Table 9-49. Receiver Demodulation Low Frequency (HCFS = 0)...................................................................153

Table 9-50. Receiver Demodulation High Frequency (HCFS = 1)..................................................................154

www.ite.com.tw IT8712F V0.81

xi xi

1. Features

Low Pin Count Interface

− Comply with Intel Low Pin Count Interface

Specification Rev. 1.0

− Supports LDRQ#, SERIRQ protocols

− Supports PCI PME# Interfaces

ACPI & LANDesk Compliant

− ACPI V. 1.0 compliant

− Register sets compatible with “Plug and Play

ISA Specification V. 1.0a”

− LANDesk 3.X compliant

− Supports 12 logical devices

Enhanced Hardware Monitor

− Built-in 8-bit Analog to Digital Converter

− 3 thermal inputs from remote thermal resistor

or thermal diode or diode-connected transistor

− 8 voltage monitor inputs (VBAT is measured

internally.)

− 1 chassis open detection input with low power

Flip-Flop backed by the battery

− Watch Dog comparison of all monitored values

− Provides VID0 – VID5 support for the CPU

Fan Speed Controller

− Provides fan on-off and PWM control

− Supports 5 programmable Pulse Width

Modulation (PWM) outputs

− 128 steps of PWM modes

− Monitors 5 fan tachometer inputs

SmartGuardian Controller

− Provides programmable fan speed automatic

control

− Supports mix-and-match for temperature inputs

and fan speed control outputs

− Overrides fan speed controller during

catastrophic situations

− Provides over temperature beep tone warning

Two 16C550 UARTs

− Supports two standard Serial Ports

− Supports IrDA 1.0/ASKIR protocols

− Supports Smart Card Reader protocols

Features

Smart Card Reader

− Compliant with Personal Computer Smart Card

(PC/SC) Working Group standard

− Compliant with smart card (ISO 7816) protocols

− Supports card present detect

− Supports Smart Card insertion power-on

feature

− Supports one programmable clock frequency,

and 7.1 MHz and 3.5 MHz (Default) card clocks

Consumer Remote Control (TV remote) IR

with power-up feature

IEEE 1284 Parallel Port

− Standard mode -- Bi-directional SPP compliant

− Enhanced mode -- EPP V. 1.7 and V. 1.9

compliant

− High speed mode -- ECP, IEEE 1284 compliant

− Back-drive current reduction

− Printer power-on damage reduction

− Supports POST (Power-On Self Test) Data

Port

Floppy Disk Controller

− Supports two 360K/ 720K/ 1.2M/ 1.44M/ 2.88M

floppy disk drives

− Enhanced digital data separator

− 3-Mode drives supported

− Supports automatic write protection via

software

Keyboard Controller

− 8042 compatible for PS/2 keyboard and mouse

− 2KB of custom ROM and 256-byte data RAM

− GateA20 and Keyboard reset output

− Supports any key, or 2-5 sequential keys, or 1-

3 simultaneous keys keyboard power-on events

− Supports mouse double-click and/or mouse

move power on events

− Supports Keyboard and Mouse I/F hardware

auto-swap

www.ite.com.tw IT8712F V0.81

1

ITPM-PN-200415

Specifications subject to Change without Notice By Joseph, 4/20/2004

IT8712F

Game Port

− Built-in 558 quad timers and buffer chips

− Supports direct connection of two joysticks

Dedicated MIDI Interface

− MPU-401 UART mode compatible

38 General Purpose I/O Pins

− Input mode supports either switch de-bounce or

programmable external IRQ input routing

− Output mode supports 2 sets of programmable

LED blinking periods

External IRQ Input Routing Capability

− Provides IRQ input routing through GPIO input

mode

− Programmable registers for IRQ routing

ITE innovative automatic power-failure

resume and power button de-bounce

Dedicated Infrared pins

VCCH and Vbat S upported

Built-in 32.768 KHz Oscillator

Single 24/48 MHz Clock Input

+5V Power Supply

128-pin QFP

Watch Dog Timer

− Time resolution 1 minute or 1 second,

maximum 255 minutes or 255 seconds

− Output to KRST# when expired

www.ite.com.tw IT8712F V0.81

2

General Description

2. General Description

The IT8712F is a Low Pin Count Interfac e-based highly integrated Super I/O. The IT 8712F provides the m ost

commonly used legacy Super I/O functionality plus the latest Environm ent Control initiatives, such as H/W

Monitor, Fan Speed Controller, ITE’s “SmartGuardian” function and Smart Card Reader Interface. The

device’s LPC interface complies with Intel “LPC Interface Specification Rev. 1.0”. The IT8712F is ACPI &

LANDesk compliant.

The IT8712F features the enhanced hardware monitor providing 3 thermal inputs from remote thermal

resistors, or thermal diode or diode-connected transistor (2N3094). The device also provides the ITE

innovative intelligent automatic Fan ON/OFF & speed control functions (SmartGuardian) to protect the system,

reducing the system noise and power consum ption. It also features a PC/SC and ISO 7816 compliant Sm art

Card Reader.

The IT8712F contains one gam e port which supports 2 joysticks, 1 MIDI port, and 1 Fan Speed Contr oller.

The fan speed controller is responsible to control 5 fan speeds through three 128 steps of Pulse Width

Modulation (PWM) output pins and to monitor five FANs’ Tachometer inputs. It also features two 16C550

UARTs, one IEEE 1284 Parallel Port, one Floppy Disk Controller and one 8042 Keyboard Controller.

The IT8712F has integrated 12 logical devices. One high-performance 2.88MB floppy disk controller, with

digital data separator, supports two 360K/ 720K/ 1.2M/ 1.44M/ 2.88M floppy disk drives. One multi-mode highperformance parallel port featur es the bi-directional Standard Parallel Por t (SPP), the Enhanced Parallel Port

(EPP V. 1.7 and EPP V. 1.9 are supported), and the IEEE 1284 com pliant Extended Capabilities Port (ECP).

Two 16C550 standard compatible enhanced UART s perf orm asynchronous comm unication, and als o support

either IR or MIDI interfaces. One game port with built-in 558 quad timers and buffer chips supports direct

connection of 2 joysticks. T he device also features one MPU-401 UART m ode compatible MIDI port, one f an

speed controller responsible for controlling / monitor ing 5 f ans and 5 G PIO por ts (38 G PIO pins ) . T he IT8712F

also has an integrated 8042 compatible Keyboard Controller with 2KB of programmable RO M for customer

application.

These 12 logical devices can be individually enabled or disabled via software configuration registers. The

IT8712F utilizes power-saving circuitry to reduce power consumption, and once a logical device is disabled the

inputs are gated inhibit, the outputs are tri-state, and the input c lock is disabled. T he device requires a single

24/48 MHz clock input and operates with +5V power supply. The IT8712F is available in 128- pin QFP (Quad

Flat Package).

www.ite.com.tw IT8712F V0.81

3

www.ite.com.tw IT8712F V0.81

4

3. Block Diagram

F

/

I

SERIRQ

C

P

L

CLKRUN#

LDRQ#

Block Diagram

24 / 48 MHz

OSC.

Serial Port I/F

IR I/F

SCR I/F

Serial Port I/F

Parallel Port

I/F

Floppy

Drive I/F

Clock

Gen.

16C550

UART 1

IrDA 1.0 /

ASKIR

Smart Card

Reader

16C550

UART 2

IEEE1284

Parallel

Port

Floppy

Disk

Controller

LPC Interface

& Plug-and-Play

Registers

s

u

B

e

c

a

f

r

e

t

n

I

l

a

r

t

n

e

C

Keyboard

Controller

MPU-401

UART

mode

Consumer

I/R

Game

Port

General

Purpose

I/O

Fan

Speed

Controller

PME#

Mouse I/F

Keyboard I/F

MIDI I/F

CIR I/F

Joystick I/F

I/O Ports

Fan I/F

8-bit

ADC

Monitored

Voltages

Environment Controller

Fan

Tachometers

Thermal

Resistor

Thermal

Diode

www.ite.com.tw IT8712F V0.81

5

This page is intentionally left blank.

www.ite.com.tw IT8712F V0.81

6

4. Pin Configuration

DTR2#/JP4

RTS2/JP5

DSR2#

VCC

SOUT2/JP6

SIN2

FAN_TAC1

FAN_CTL1

FAN_TAC2/GP52

FAN_CTL2/GP51

FAN_TAC3/GP37

FAN_CTL3/GP36

VID5/GP35

VID4/GP34

GNDD

VID3/GP33

VID2/GP32

VID1/GP31

FAN_CTL4/JSBB2/GP27

FAN_CTL5/JSBB1/GP26

FAN_TAC4/JSBCY/GP25

FAN_TAC5/JSBCX/GP24

RESETCON#/CIRTX/GP15

PCIRST1#/SCRRST/GP14

PWROK1/SCRPFET#/GP13

PCIRST2#/SCRIO/GP12

PCIRST3#/SCRCLK/GP11

VID0/GP30

JSAB2/GP23

JSAB1/GP22

JSACY/GP21

JSACX/GP20

MIDI_OUT/GP17

MIDI_IN/GP16

VCC

VIDVCC

LRESET#

LDRQ#

PD6

PD7

GNDD

DCD1#

RI1#

CTS1#

DTR1#/JP1

RTS1#/JP2

DSR1#

SOUT1/JP3

SIN1

DCD2#

RI2#

CTS2#

115

116

117

118

119

120

121

122

123

124

125

126

127

128

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39404142434445464748495051525354555657

IT8712F

128-QFP

PD5

114

PD4

113

PD3

112

PD2

111

PD1

110

ERR#

AFD#

STB#

PD0

109

106

107

108

58

5960616263

Pin Configuration

ACK#

SLIN#

INIT#

104

105

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

BUSY

PE

SLCT

VCC

VIN0

VIN1

VIN2

VIN3/ATXPG

VIN4

VIN5

VIN6

VIN7/PCIRSTIN#

VREF

TMPIN1

TMPIN2

TMPIN3

GNDA

RSMRST#/CIRRX/GP55

PCIRST4#/SCRPSNT#/GP10

MCLK

MDAT

KCLK

KDAT

GP40

PWROK2/GP41

GP53

PSON#/GP42

PANSWH#/GP43

GNDD

PME#/GP54

PWRON#/GP44

PSIN/GP45

IRRX/GP46

VBAT

COPEN#

VCCH

IRTX/GP47

DSKCHG#

LAD0

LAD1

LAD2

LAD3

GA20

CLKIN

PCICLK

GNDD

MTRA#

DENSEL#

MTRB#/THRMO#

PCIRST5#/CLKRUN#/GP50

SERIRQ

LFRAME#

KRST#

DRVA#

DRVB#

DIR#

STEP#

HDSEL#

WDATA#

WGATE#

RDATA#

TRK0#

WPT#

INDEX#

Top View

www.ite.com.tw IT8712F V0.81

7

IT8712F

Table 4-1. Pins Listed in Numeric Order

Pin Signal Pin Signal Pin Signal Pin Signal

1 DTR2#/JP4 33

2 RTS2#/JP5 34

PCIRST2#/SCRIO

/GP12

PCIRST3#/SCRC

LK/GP11

65 DSKCHG# 97 VIN1

66 IRTX/GP47 98 VIN0

3 DSR2# 35 VCC 67 VCCH 99 VCC

4 VCC 36 VIDVCC 68 COPEN# 100 SLCT

5 SOUT2/JP6 37 LRESET# 69 VBAT 101 PE

6 SIN2 38 LDRQ# 70 IRRX/GP46 102 BUSY

7 FAN_TAC1 39 SERIRQ 71 GP45 103 ACK#

8 FAN_CTL1 40 LFRAME# 72 PWRON#/GP44 104 SLIN#

9 FAN_TAC2/GP52 41 LAD0 73 PME#/GP54 105 INIT#

10 FAN_CTL2/GP51 42 LAD1 74 GNDD 106 ERR#

11 FAN_TAC3/GP37 43 LAD2 75 PANSWH#/GP43 107 AFD#

12 FAN_CTL3/GP36 44 LAD3 76 PSON#/GP42 108 STB#

13 VID5/GP35 45 KRST# 77 GP53 109 PD0

14 VID4/GP34 46 GA20 78 PWROK2/GP41 110 PD1

15 GNDD 47 PCICLK 79 GP40 111 PD2

16 VID3/GP33 48

PCIRST5#/CLKR

UN#/GP50

80 KDAT 112 PD3

17 VID2/GP32 49 CLKIN 81 KCLK 113 PD4

18 VID1/GP31 50 GNDD 82 MDAT 114 PD5

19 VID0/GP30 51 DENSEL# 83 MCLK 115 PD6

FAN_CTL4/JSBB

20

2/GP27

FAN_CTL5/JSBB

21

1/GP26

FAN_TAC4/JSBC

22

Y/GP25

FAN_TAC5/JSBC

23

X/GP24

52 MTRA# 84

53 MTRB#/THRMO# 85

54 DRVA# 86 GNDA 118 DCD1#

55 DRVB# 87 TMPIN3 119 RI1#

PCIRST4#/

SCRPSNT#/GP1

0

RSMRST#/CIRRX

/GP55

116 PD7

117 GNDD

24 JSAB2/GP23 56 WDATA# 88 TMPIN2 120 CTS1#

25 JSAB1/GP22 57 DIR# 89 TMPIN1 121 DTR1#/JP1

26 JSACY/GP21 58 STEP# 90 VREF 122 RTS1#/JP2

27 JSACX/GP20 59 HDSEL# 91 VIN7/PCIRSTIN# 123 DSR1#

28 MIDI_OUT/GP17 60 WGATE# 92 VIN6 124 SOUT1/JP3

29 MIDI_IN/GP16 61 RDATA# 93 VIN5 125 SIN1

RESETCON#/CIR

30

TX/GP15

PCIRST1#/SCRR

31

ST/GP14

PWROK1/SCRPF

32

ET#/GP13

62 TRK0# 94 VIN4 126 DCD2#

63 INDEX# 95 VIN3/ATXPG 127 RI2#

64 WPT# 96 VIN2 128 CTS2#

www.ite.com.tw IT8712F V0.81

8

Pin Descriptions

5. IT8712F Pin Descriptions

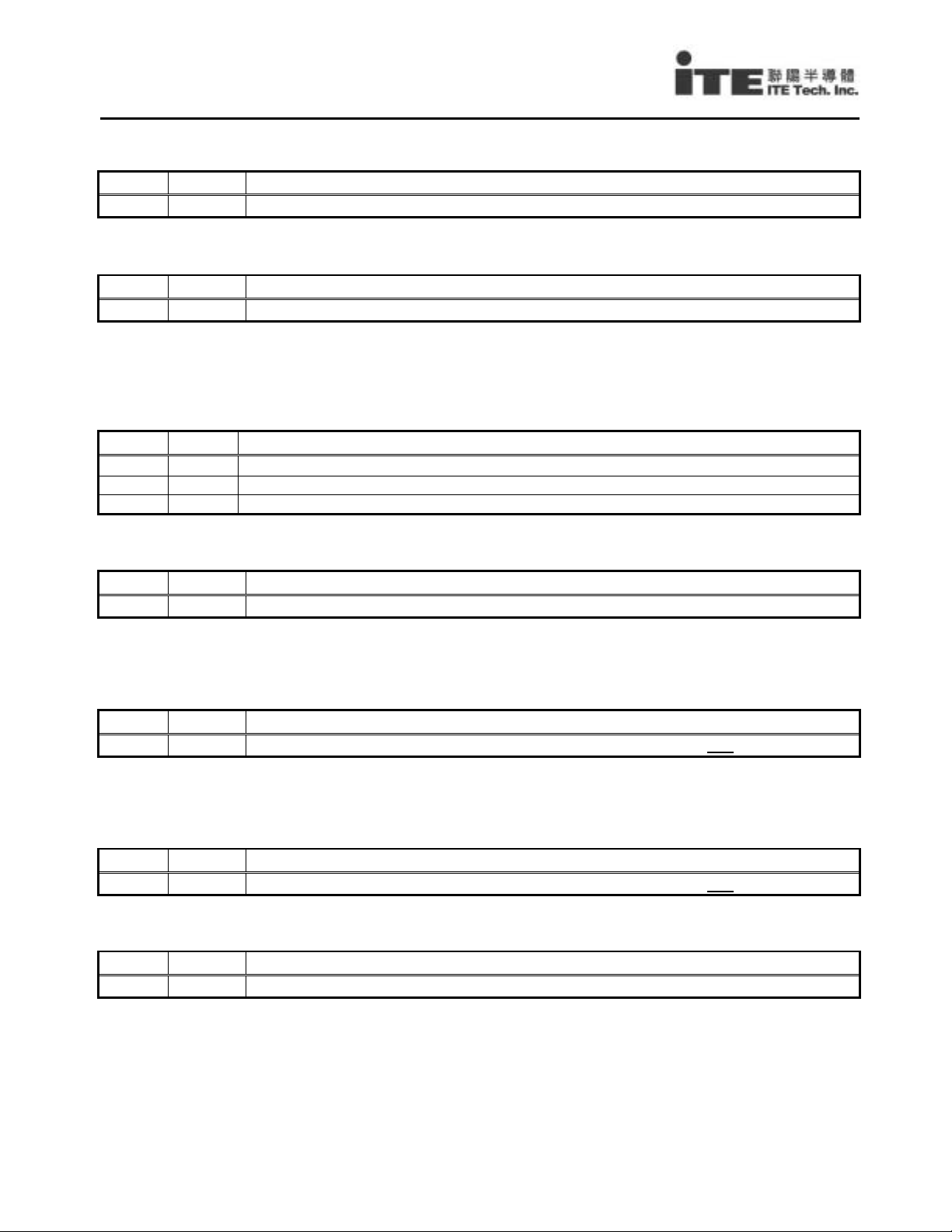

Table 5-1. Pin Description of Supplies Signals

Pin(s) No. Symbol Attribute Power Description

4, 35, 99 VCC

67 VCCH

69 VBAT

36 VIDVCC

15, 50,

GNDD

PWR PWR PWR PWR GND -

74, 117

86 GNDA

GND -

Table 5-2. Pin Description of LPC Bus Interface Signals

Pin(s) No. Symbol Attribute Power Description

37 LRESET#

38 LDRQ#

39 SERIRQ

40 LFRAME#

41 – 44 LAD[0:3]

47 PCICLK

48 PCIRST5#/CLK

RUN#/GP50

DI VCC

DO16 VCC

DIO16 VCC

DI VCC

DIO16 VCC

DI VCC

DO16/DIO

D16/

VCC

DIOD16

73 PME#/GP54

DOD8/

VCCH

DIOD8

+5V Power Supply.

+5V VCC Help Supply.

+3.3V Battery Supply.

VID power supply. (1.2 or 3.3V)

Digital Ground.

Analog Ground.

LPC RESET #.

LPC DMA Request #.

An encoded signal for DMA channel select.

Serial IRQ.

LPC Frame #.

This signal indicates the start of LPC cycle.

LPC Address/Data 0 - 3.

4-bit LPC address/bi-directional data lines. LAD0 is the LSB

and LAD3 is the MSB.

PCI Clock.

33 MHz PCI clock input for LPC I/F and SERIRQ.

PCI Reset 5 # / Clock Run # / General Purpose I/O 50.

• The first function of this pin is PCI Reset 5 #. It is a

buffer output of LRESET# if bit1 of Index 2Ch is 0. It

will be (LRESET# AND PCIRSTIN#) if bit1 of Index

2Ch is 1.

• The second function of this pin is the clock run #.

This is an open-drain output and also an input. The

IT8712F uses this signal to request starting (or speed

up) the clock. CLKRUN# also indicates the clock

status.

• The third function of this pin is the General Purpose

I/O 50.

• The function configuration of this pin is decided by

the software configuration registers.

Power Management Event # / General Purpose I/O 54.

• The first function of this pin is the power

management event #. It supports the PCI PME#

interface. This signal allows the peripheral to request

the system to wake up from the D3 (cold) state.

• The second function of this pin is the General

Purpose I/O Port 5 Bit 4.

• The function configuration of this pin is determined by

programming the software configuration registers.

www.ite.com.tw IT8712F V0.81

9

IT8712F

Table 5-3. Pin Description of MIDI Interface Signals

Pin(s) No. Symbol Attribute Power Description

28 MIDI_OUT/

GP17