ITE IT8511E, IT8511G, IT8511TE Schematics

IT8511E/TE/G

Embedded Controller

Preliminary Specification 0.4.1

ITE TECH. INC.

Specification subject to Change without notice, AS IS and for reference only. For purchasing, please contact sales representatives.

Copyright © 2006 ITE Tech. Inc.

This is Preliminary document release. All specifications are subject to change without notice.

The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE Tech. Inc. for the latest document(s). All sales are subject to ITE’s Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8511E/TE/G is a trademark of ITE Tech. Inc.

All other trademarks are claimed by their respective owners.

All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE Tech. Inc. |

Phone: (02) 2912-6889 |

Marketing Department |

Fax: (02) 2910-2551, 2910-2552 |

8F, No. 233-1, Bao Chiao RD., Hsin Tien, |

|

Taipei County 231, Taiwan, R.O.C. |

|

If you have any marketing or sales questions, please contact:

P.Y. Chang, at ITE Taiwan: E-mail: p.y.chang@ite.com.tw, Tel: 886-2-29126889 X6052, Fax: 886-2-29102551

To find out more about ITE, visit our World Wide Web at:

http://www.ite.com.tw

Or e-mail itesupport@ite.com.tw for more product information/services

Revision History

|

Section |

|

|

|

Revision |

|

|

Page No. |

|

7 |

|

• In section 7.5.4 Alternate Function Selection, the followings were revised: |

181 |

|

|||||

|

|

|

1. |

The “output driving” of GPIOB3-4 was revised to “4“. |

|

|

|

||

|

|

|

2. |

The “output driving” of GPIOC1-2 was revised to “4“ and GPIOE7 was |

|

|

|

||

|

|

|

|

revised to “4“. |

|

|

|

||

|

|

|

3. |

GPIOE0-3 don’t support neither “pull-up” nor “pull-down”. |

|

|

|

||

|

|

|

4. |

The “default pull” of GPIOI7 was revised to “Up“. |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

www.ite.com.tw |

1 |

IT8511E/TE/G V0.4.1 |

Contents

1. |

Features |

CONTENTS |

|

1 |

|

|

|

||||

2. |

General Description ....................................................................................................................................... |

|

3 |

||

3. |

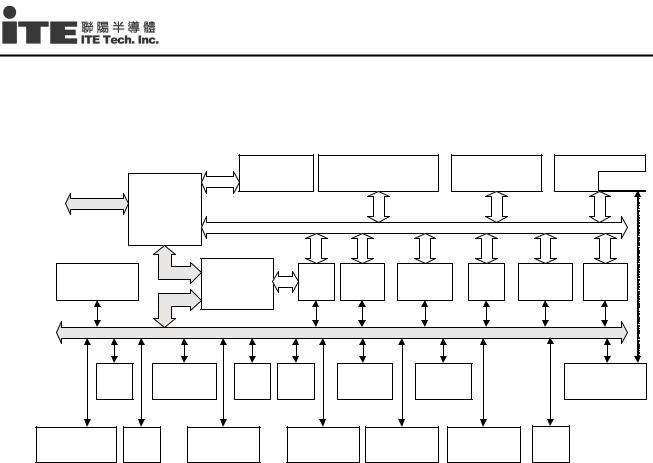

System Block Diagram................................................................................................................................... |

|

5 |

||

|

3.1 |

Block Diagram..................................................................................................................................... |

|

5 |

|

|

3.2 |

Host/EC Mapped Memory Space ....................................................................................................... |

|

6 |

|

|

3.3 |

EC Mapped Memory Space................................................................................................................ |

|

9 |

|

|

3.4 |

Register Abbreviation........................................................................................................................ |

|

10 |

|

4. |

Pin Configuration ......................................................................................................................................... |

|

11 |

||

|

4.1 |

Top View ........................................................................................................................................... |

|

11 |

|

5. |

Pin Descriptions ........................................................................................................................................... |

|

17 |

||

|

5.1 |

Pin Descriptions ................................................................................................................................ |

|

17 |

|

|

5.2 |

Chip Power Planes and Power States.............................................................................................. |

|

23 |

|

|

5.3 |

Pin Power Planes and States ........................................................................................................... |

|

24 |

|

|

5.4 |

PWRFAIL# Interrupt to INTC ........................................................................................................... |

|

28 |

|

|

5.5 |

Reset Sources and Types................................................................................................................. |

|

29 |

|

|

|

5.5.1 Relative Interrupts to INTC................................................................................................... |

|

29 |

|

|

5.6 |

Chip Power Mode and Clock Domain............................................................................................... |

|

30 |

|

|

5.7 |

Pins with Pull, Schmitt-Trigger or Open-Drain Function ................................................................... |

|

34 |

|

|

5.8 |

Power Consumption Consideration .................................................................................................. |

|

35 |

|

6. |

Host Domain Functions................................................................................................................................ |

|

37 |

||

|

6.1 |

Low Pin Count Interface.................................................................................................................... |

|

37 |

|

|

|

6.1.1 |

Overview............................................................................................................................... |

|

37 |

|

|

6.1.2 |

Features ............................................................................................................................... |

|

37 |

|

|

6.1.3 Accepted LPC Cycle Type ................................................................................................... |

|

37 |

|

|

|

6.1.4 |

Debug Port Function ............................................................................................................ |

|

38 |

|

|

6.1.5 |

Serialized IRQ (SERIRQ) ..................................................................................................... |

|

39 |

|

|

6.1.6 Relative Interrupts to WUC................................................................................................... |

|

39 |

|

|

|

6.1.7 |

LPCPD# and CLKRUN#....................................................................................................... |

|

39 |

|

|

6.1.8 |

Check Items.......................................................................................................................... |

|

39 |

|

6.2 |

Plug and Play Configuration (PNPCFG)........................................................................................... |

|

40 |

|

|

|

6.2.1 |

Logical Device Assignment .................................................................................................. |

|

42 |

|

|

6.2.2 Super I/O Configuration Registers ....................................................................................... |

|

43 |

|

|

|

6.2.2.1 Logical Device Number (LDN)................................................................................. |

|

43 |

|

|

|

6.2.2.2 Chip ID Byte 1 (CHIPID1)........................................................................................ |

|

43 |

|

|

|

6.2.2.3 Chip ID Byte 2 (CHIPID2)........................................................................................ |

|

43 |

|

|

|

6.2.2.4 Chip Version (CHIPVER)......................................................................................... |

|

43 |

|

|

|

6.2.2.5 Super I/O Control Register (SIOCTRL) ................................................................... |

|

43 |

|

|

|

6.2.2.6 Super I/O IRQ Configuration Register (SIOIRQ)..................................................... |

|

44 |

|

|

|

6.2.2.7 Super I/O General Purpose Register (SIOGP)........................................................ |

|

44 |

|

|

|

6.2.2.8 Super I/O Power Mode Register (SIOPWR) ........................................................... |

|

44 |

|

|

|

6.2.3 Standard Logical Device Configuration Registers................................................................ |

|

45 |

|

|

|

6.2.3.1 Logical Device Activate Register (LDA)................................................................... |

|

45 |

|

|

|

6.2.3.2 I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

45 |

||

|

|

6.2.3.3 I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

45 |

||

|

|

6.2.3.4 I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

46 |

||

|

|

6.2.3.5 I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

46 |

||

|

|

6.2.3.6 Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

46 |

||

|

|

6.2.3.7 Interrupt Request Type Select (IRQTP) .................................................................. |

|

46 |

|

|

|

6.2.3.8 DMA Channel Select 0 (DMAS0) ............................................................................ |

|

47 |

|

|

|

6.2.3.9 DMA Channel Select 0 (DMAS1) ............................................................................ |

|

47 |

|

|

|

6.2.4 System Wake-Up Control (SWUC) Configuration Registers ............................................... |

|

47 |

|

|

|

6.2.4.1 Logical Device Activate Register (LDA)................................................................... |

|

48 |

|

www.ite.com.tw |

i |

IT8511E/TE/G V0.4.1 |

|||

IT8511E/TE/G |

|

|

|

6.2.4.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

48 |

|

6.2.4.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

48 |

|

6.2.4.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

48 |

|

6.2.4.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

48 |

|

6.2.4.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

48 |

|

6.2.4.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

48 |

6.2.5 KBC / Mouse Interface Configuration Registers .................................................................. |

|

49 |

|

6.2.5.1 |

Logical Device Activate Register (LDA)................................................................... |

|

49 |

6.2.5.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

49 |

|

6.2.5.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

49 |

|

6.2.5.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

49 |

|

6.2.5.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

50 |

|

6.2.5.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

50 |

|

6.2.5.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

50 |

6.2.6 KBC / Keyboard Interface Configuration Registers.............................................................. |

|

50 |

|

6.2.6.1 |

Logical Device Activate Register (LDA)................................................................... |

|

50 |

6.2.6.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

50 |

|

6.2.6.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

51 |

|

6.2.6.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

51 |

|

6.2.6.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

51 |

|

6.2.6.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

51 |

|

6.2.6.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

51 |

6.2.7 Shared Memory/Flash Interface (SMFI) Configuration Registers ........................................ |

|

51 |

|

6.2.7.1 |

Logical Device Activate Register (LDA)................................................................... |

|

52 |

6.2.7.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

52 |

|

6.2.7.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

52 |

|

6.2.7.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

52 |

|

6.2.7.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

52 |

|

6.2.7.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

52 |

|

6.2.7.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

52 |

6.2.7.8 |

Shared Memory Configuration Register (SHMC) .................................................... |

|

53 |

6.2.8 Real Time Clock (RTC) Configuration Registers ................................................................. |

|

53 |

|

6.2.8.1 |

Logical Device Activate Register (LDA)................................................................... |

|

53 |

6.2.8.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

53 |

|

6.2.8.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

54 |

|

6.2.8.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

54 |

|

6.2.8.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

54 |

|

6.2.8.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

54 |

|

6.2.8.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

54 |

6.2.8.8 |

RAM Lock Register (RLR) ....................................................................................... |

|

54 |

6.2.8.9 |

Date of Month Alarm Register Offset (DOMAO) ..................................................... |

|

55 |

6.2.8.10 |

Month Alarm Register Offset (MONAO) .................................................................. |

|

55 |

6.2.8.11 |

P80L Begin Index (P80LB) ...................................................................................... |

|

55 |

6.2.8.12 |

P80L End Index (P80LE)......................................................................................... |

|

55 |

6.2.8.13 |

P80L Current Index (P80LC) ................................................................................... |

|

55 |

6.2.9 Power Management I/F Channel 1 Configuration Registers................................................ |

|

56 |

|

6.2.9.1 |

Logical Device Activate Register (LDA)................................................................... |

|

56 |

6.2.9.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

56 |

|

6.2.9.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

56 |

|

6.2.9.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

56 |

|

6.2.9.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

57 |

|

6.2.9.6 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

57 |

|

6.2.9.7 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

57 |

6.2.10 Power Management I/F Channel 2 Configuration Registers................................................ |

|

57 |

|

6.2.10.1 |

Logical Device Activate Register (LDA)................................................................... |

|

57 |

6.2.10.2 |

I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) ........................ |

58 |

|

www.ite.com.tw |

ii |

IT8511E/TE/G V0.4.1 |

|

|

|

|

|

|

Contents |

|

|

|

|

||||

6.2.10.3 |

I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0]) ............................ |

58 |

||||

6.2.10.4 |

I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) ........................ |

58 |

||||

6.2.10.5 |

I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[7:0]) ............................ |

58 |

||||

6.2.10.6 |

I/O Port Base Address Bits [15:8] for Descriptor 2 (IOBAD2[15:8]) ........................ |

58 |

||||

6.2.10.7 |

I/O Port Base Address Bits [7:0] for Descriptor 2 (IOBAD2[7:0]) ............................ |

58 |

||||

6.2.10.8 |

Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)................... |

59 |

||||

6.2.10.9 |

Interrupt Request Type Select (IRQTP) .................................................................. |

|

59 |

|||

6.2.11 |

Programming Guide ............................................................................................................. |

|

|

|

60 |

|

6.3 Shared Memory Flash Interface Bridge (SMFI) ................................................................................ |

|

62 |

||||

6.3.1 |

Overview............................................................................................................................... |

|

|

|

62 |

|

6.3.2 |

Features ............................................................................................................................... |

|

|

|

62 |

|

6.3.3 |

Function Description............................................................................................................. |

|

|

|

62 |

|

6.3.3.1 |

Supported Flash |

...................................................................................................... |

|

62 |

||

6.3.3.2 |

Host to M Bus Translation ....................................................................................... |

|

62 |

|||

6.3.3.3 |

Memory Mapping ..................................................................................................... |

|

62 |

|||

6.3.3.4 |

Host-Indirect Memory .......................................................Read/Write Transaction |

|

63 |

|||

6.3.3.5 |

EC-Indirect Memory ..........................................................Read/Write Transaction |

|

63 |

|||

6.3.3.6 |

Locking Between .................................................................Host and EC Domains |

|

64 |

|||

6.3.3.7 |

Host Access Protection............................................................................................ |

|

64 |

|||

6.3.3.8 |

Response to a Forbidden ............................................................................Access |

|

64 |

|||

6.3.3.9 |

Scratch SRAM ......................................................................................................... |

|

|

|

64 |

|

6.3.3.10 |

DMA for Scratch ...........................................................................................SRAM |

|

66 |

|||

6.3.3.11 |

Trusted ROM/RAM .................................................................................................. |

|

66 |

|||

6.3.3.12 |

Flash Programming ............................via Host LPC Interface with Scratch SRAM |

66 |

||||

6.3.4 |

EC Interface Registers ......................................................................................................... |

|

|

|

67 |

|

6.3.4.1 |

FBIU Configuration ....................................................................Register (FBCFG) |

|

68 |

|||

6.3.4.2 |

Flash Programming .............................................Configuration Register (FPCFG) |

|

68 |

|||

6.3.4.3 |

Flash EC Code Banking ...............................................Select Register (FECBSR) |

|

69 |

|||

6.3.4.4 |

Flash Memory Size ........................................................Select Register (FMSSR) |

|

70 |

|||

6.3.4.5 |

Shared Memory .................................EC Control and Status Register (SMECCS) |

|

71 |

|||

6.3.4.6 |

Shared Memory ............................................Host Semaphore Register (SMHSR) |

|

71 |

|||

6.3.4.7 |

Shared Memory ........EC Override Read Protect Registers 0-1 (SMECORPR0-1) |

72 |

||||

6.3.4.8 |

Shared Memory .......EC Override Write Protect Registers 0-1 (SMECOWPR0-1) |

72 |

||||

6.3.4.9 |

Host Control 2 Register .......................................................................(HCTRL2R) |

|

72 |

|||

6.3.4.10 |

Trusted ROM Register ............................................................................(TROMR) |

|

73 |

|||

6.3.4.11 |

EC-Indirect Memory ...........................................Address Register 0 (ECINDAR0) |

|

73 |

|||

6.3.4.12 |

EC-Indirect Memory ...........................................Address Register 1 (ECINDAR1) |

|

73 |

|||

6.3.4.13 |

EC-Indirect Memory ...........................................Address Register 2 (ECINDAR2) |

|

73 |

|||

6.3.4.14 |

EC-Indirect Memory ...........................................Address Register 3 (ECINDAR3) |

|

73 |

|||

6.3.4.15 |

EC-Indirect Memory ......................................................Data Register (ECINDDR) |

|

73 |

|||

6.3.4.16 |

Scratch SRAM |

0 ........................................ |

Address Low Byte Register (SCAR0L) |

|

74 |

|

6.3.4.17 |

Scratch SRAM |

0 ................................... |

Address Middle Byte Register (SCAR0M) |

|

74 |

|

6.3.4.18 |

Scratch SRAM |

0 ....................................... |

Address High Byte Register (SCAR0H) |

|

74 |

|

6.3.4.19 |

Scratch SRAM |

1 ........................................ |

Address Low Byte Register (SCAR1L) |

|

74 |

|

6.3.4.20 |

Scratch SRAM |

1 ................................... |

Address Middle Byte Register (SCAR1M) |

|

74 |

|

6.3.4.21 |

Scratch SRAM |

1 ....................................... |

Address High Byte Register (SCAR1H) |

|

74 |

|

6.3.4.22 |

Scratch SRAM |

2 ........................................ |

Address Low Byte Register (SCAR2L) |

|

75 |

|

6.3.4.23 |

Scratch SRAM |

2 ................................... |

Address Middle Byte Register (SCAR2M) |

|

75 |

|

6.3.4.24 |

Scratch SRAM |

2 ....................................... |

Address High Byte Register (SCAR2H) |

|

75 |

|

6.3.4.25 |

Scratch SRAM |

3 ........................................ |

Address Low Byte Register (SCAR3L) |

|

75 |

|

6.3.4.26 |

Scratch SRAM |

3 ................................... |

Address Middle Byte Register (SCAR3M) |

|

75 |

|

6.3.4.27 |

Scratch SRAM |

3 ....................................... |

Address High Byte Register (SCAR3H) |

|

75 |

|

6.3.4.28 |

Scratch SRAM |

4 ........................................ |

Address Low Byte Register (SCAR4L) |

|

76 |

|

6.3.4.29 |

Scratch SRAM |

4 ................................... |

Address Middle Byte Register (SCAR4M) |

|

76 |

|

6.3.4.30 |

Scratch SRAM |

4 ....................................... |

Address High Byte Register (SCAR4H) |

|

76 |

|

6.3.5 |

Host Interface Registers....................................................................................................... |

|

|

76 |

||

www.ite.com.tw |

|

|

|

iii |

IT8511E/TE/G V0.4.1 |

|

IT8511E/TE/G

6.3.5.1 Shared Memory Indirect Memory Address Register 0 (SMIMAR0) ........................ |

76 |

|||

6.3.5.2 Shared Memory Indirect Memory Address Register 1 (SMIMAR1) ........................ |

77 |

|||

6.3.5.3 Shared Memory Indirect Memory Address Register 2 (SMIMAR2) ........................ |

77 |

|||

6.3.5.4 Shared Memory Indirect Memory Address Register 3 (SMIMAR3) ........................ |

77 |

|||

6.3.5.5 Shared Memory Indirect Memory Data Register (SMIMDR) |

................................... |

77 |

||

6.3.5.6 Shared Memory Host Semaphore Register (SMHSR) ............................................ |

|

77 |

||

6.3.5.7 M-Bus Control Register (MBCTRL) ......................................................................... |

|

78 |

||

6.4 System Wake-Up Control (SWUC) ................................................................................................... |

|

79 |

||

6.4.1 |

Overview............................................................................................................................... |

|

79 |

|

6.4.2 |

Features ............................................................................................................................... |

|

79 |

|

6.4.3 |

Functional Description.......................................................................................................... |

|

79 |

|

6.4.3.1 |

Wake-Up Status....................................................................................................... |

|

79 |

|

6.4.3.2 |

Wake-Up Events...................................................................................................... |

|

80 |

|

6.4.3.3 |

Wake-Up Output Events.......................................................................................... |

|

81 |

|

6.4.3.4 Other SWUC Controlled Options............................................................................. |

|

81 |

||

6.4.4 |

Host Interface Registers....................................................................................................... |

|

83 |

|

6.4.4.1 Wake-Up Event Status Register (WKSTR) ............................................................. |

|

83 |

||

6.4.4.2 Wake-Up Event Enable Register (WKER)............................................................... |

|

84 |

||

6.4.4.3 Wake-Up Signals Monitor Register (WKSMR) ........................................................ |

|

84 |

||

6.4.4.4 Wake-Up ACPI Status Register (WKACPIR) .......................................................... |

|

85 |

||

6.4.4.5 Wake-Up SMI Enable Register (WKSMIER)........................................................... |

|

85 |

||

6.4.4.6 Wake-Up IRQ Enable Register (WKIRQER)........................................................... |

|

86 |

||

6.4.5 |

EC Interface Registers ......................................................................................................... |

|

86 |

|

6.4.5.1 SWUC Control Status 1 Register (SWCTL1) .......................................................... |

|

86 |

||

6.4.5.2 SWUC Control Status 2 Register (SWCTL2) .......................................................... |

|

87 |

||

6.4.5.3 SWUC Control Status 3 Register (SWCTL3) .......................................................... |

|

88 |

||

6.4.5.4 SWUC Host Configuration Base Address Low Byte Register ............(SWCBALR) |

88 |

|||

6.4.5.5 SWUC Host Configuration Base Address High Byte Register ..........(SWCBAHR) |

88 |

|||

6.4.5.6 SWUC Interrupt Enable Register (SWCIER)........................................................... |

|

88 |

||

6.4.5.7 SWUC Host Event Status Register (SWCHSTR).................................................... |

|

89 |

||

6.4.5.8 SWUC Host Event Interrupt Enable Register (SWCHIER) ..................................... |

|

90 |

||

6.5 Keyboard Controller (KBC) ............................................................................................................... |

|

91 |

||

6.5.1 |

Overview............................................................................................................................... |

|

91 |

|

6.5.2 |

Features ............................................................................................................................... |

|

91 |

|

6.5.3 |

Functional Description.......................................................................................................... |

|

91 |

|

6.5.4 |

Host Interface Registers....................................................................................................... |

|

92 |

|

6.5.4.1 KBC Data Input Register (KBDIR)........................................................................... |

|

93 |

||

6.5.4.2 KBC Data Output Register (KBDOR) ...................................................................... |

|

93 |

||

6.5.4.3 KBC Command Register (KBCMDR) ...................................................................... |

|

93 |

||

6.5.4.4 KBC Status Register (KBSTR) ................................................................................ |

|

93 |

||

6.5.5 |

EC Interface Registers ......................................................................................................... |

|

94 |

|

6.5.5.1 KBC Host Interface Control Register (KBHICR)...................................................... |

|

94 |

||

6.5.5.2 KBC Interrupt Control Register (KBIRQR)............................................................... |

|

95 |

||

6.5.5.3 KBC Host Interface Keyboard/Mouse Status Register (KBHISR)........................... |

96 |

|||

6.5.5.4 KBC Host Interface Keyboard Data Output Register (KBHIKDOR) ........................ |

96 |

|||

6.5.5.5 KBC Host Interface Mouse Data Output Register (KBHIMDOR) ............................ |

96 |

|||

6.5.5.6 KBC Host Interface Keyboard/Mouse Data Input Register (KBHIDIR) ................... |

97 |

|||

6.6 Power Management Channel (PMC)................................................................................................ |

|

98 |

||

6.6.1 |

Overview............................................................................................................................... |

|

98 |

|

6.6.2 |

Features ............................................................................................................................... |

|

98 |

|

6.6.3 |

Functional Description.......................................................................................................... |

|

98 |

|

6.6.3.1 |

General Description................................................................................................. |

|

98 |

|

6.6.3.2 |

Compatible Mode..................................................................................................... |

|

99 |

|

6.6.3.3 |

Enhanced PM mode .............................................................................................. |

|

100 |

|

6.6.3.4 |

PMC2EX ................................................................................................................ |

|

101 |

|

6.6.4 |

Host Interface Registers..................................................................................................... |

|

102 |

|

www.ite.com.tw |

|

iv |

IT8511E/TE/G V0.4.1 |

|

|

|

|

Contents |

|

|

|

|

|

6.6.4.1 |

PMC Data Input Register (PMDIR)........................................................................ |

102 |

|

6.6.4.2 |

PMC Data Output Register (PMDOR)................................................................... |

103 |

|

6.6.4.3 |

PMC Command Register (PMCMDR) ................................................................... |

103 |

|

6.6.4.4 |

Status Register (PMSTR) ...................................................................................... |

103 |

6.6.5 |

EC Interface Registers ....................................................................................................... |

104 |

|

|

6.6.5.1 |

PM Status Register (PMSTS)................................................................................ |

104 |

|

6.6.5.2 |

PM Data Out Port (PMDO) .................................................................................... |

105 |

|

6.6.5.3 |

PM Data Out Port with SCI (PMDOSCI)................................................................ |

105 |

|

6.6.5.4 |

PM Data Out Port with SMI (PMDOSMI)............................................................... |

105 |

|

6.6.5.5 |

PM Data In Port (PMDI)......................................................................................... |

106 |

|

6.6.5.6 |

PM Data In Port with SCI (PMDISCI) .................................................................... |

106 |

|

6.6.5.7 |

PM Control (PMCTL) ............................................................................................. |

106 |

|

6.6.5.8 |

PM Interrupt Control (PMIC).................................................................................. |

107 |

|

6.6.5.9 |

PM Interrupt Enable (PMIE) .................................................................................. |

107 |

|

6.6.5.10 |

PM Interrupt Enable (PMIE) .................................................................................. |

108 |

|

6.6.5.11 |

16-byte PMC2EX Mailbox 0-15 (MBXEC0-15)...................................................... |

108 |

6.7 Trusted Mobile KBC (TMKBC)........................................................................................................ |

109 |

||

6.7.1 |

Overview............................................................................................................................. |

109 |

|

6.7.2 |

Features ............................................................................................................................. |

109 |

|

6.7.3 |

Functional Description........................................................................................................ |

109 |

|

6.7.4 |

Host Interface Registers..................................................................................................... |

109 |

|

|

6.7.4.1 |

TMKBC Vendor ID Register (TVENDID) ............................................................... |

109 |

|

6.7.4.2 |

TMKBC Device ID Register (TDEVID) .................................................................. |

110 |

|

6.7.4.3 |

TMKBC Version Register (TVER) ......................................................................... |

110 |

|

6.7.4.4 |

Generic Capabilities Reporting Register (CAP) .................................................... |

110 |

|

6.7.4.5 |

TMKBC Revision ID Register (TREVID)................................................................ |

110 |

|

6.7.4.6 |

Configuration Register (CNF) ................................................................................ |

111 |

|

6.7.4.7 |

Control Register (CNT).......................................................................................... |

111 |

|

6.7.4.8 |

IRQ Capabilities Reporting Register (IRQCAP) .................................................... |

112 |

|

6.7.4.9 |

Status Register (STS)............................................................................................ |

112 |

|

6.7.4.10 |

Extended Status Register (EXTSTS) .................................................................... |

112 |

|

6.7.4.11 |

Interrupt Trigger Enable Register (INTTRIG) ........................................................ |

113 |

|

6.7.4.12 |

TMKBC Data Input Register (TDATIN).................................................................. |

113 |

|

6.7.4.13 |

TMKBC Data Output Register (TDATOUT)........................................................... |

113 |

6.7.5 |

EC Interface Registers ....................................................................................................... |

114 |

|

|

6.7.5.1 |

EC Side Configuration Register (ECCON) ............................................................ |

114 |

|

6.7.5.2 |

Status Control Register (STSCON) ....................................................................... |

114 |

|

6.7.5.3 |

EC Data Input Register (EDATIN) ......................................................................... |

115 |

|

6.7.5.4 |

EC Data Output Register (EDATOUT) .................................................................. |

115 |

|

6.7.5.5 |

EC Buffer Status Register (EBUFSTS) ................................................................. |

115 |

|

6.7.5.6 |

EC Status Register (ESTS) ................................................................................... |

115 |

|

6.7.5.7 |

EC Vendor ID Low Register (EVENL) ................................................................... |

116 |

|

6.7.5.8 |

EC Vendor ID High Register (EVENH).................................................................. |

116 |

|

6.7.5.9 |

EC Device ID Low Register (EDEVL).................................................................... |

116 |

|

6.7.5.10 |

EC Device ID High Register (EDEVH) .................................................................. |

116 |

|

6.7.5.11 |

EC Version Low Register (EVERL) ....................................................................... |

116 |

|

6.7.5.12 |

EC Version High Register (EVERH)...................................................................... |

117 |

|

6.7.5.13 |

EC Revision ID Register (EREVID) ....................................................................... |

117 |

6.8 Real-Time Clock (RTC)................................................................................................................... |

118 |

||

6.8.1 |

Overview............................................................................................................................. |

118 |

|

6.8.2 |

Feature |

............................................................................................................................... |

118 |

6.8.3 |

Functional Description........................................................................................................ |

118 |

|

|

6.8.3.1 |

Timekeeping .......................................................................................................... |

118 |

|

6.8.3.2 |

Update Cycles ....................................................................................................... |

118 |

|

6.8.3.3 |

Interrupts................................................................................................................ |

118 |

|

6.8.3.4 |

P80L ...................................................................................................................... |

119 |

www.ite.com.tw |

v |

IT8511E/TE/G V0.4.1 |

|

IT8511E/TE/G

6.8.4 |

Host Interface Registers..................................................................................................... |

119 |

|

|

6.8.4.1 RTC Bank 0 Register............................................................................................. |

121 |

|

|

6.8.4.1.1 |

Seconds Register (SECREG) ....................................................... |

121 |

|

6.8.4.1.2 |

Seconds Alarm 1 Register (SECA1REG) ...................................... |

121 |

|

6.8.4.1.3 |

Minutes Register (MINREG) ......................................................... |

122 |

|

6.8.4.1.4 |

Minutes Alarm 1 Register (MINA1REG) ........................................ |

122 |

|

6.8.4.1.5 |

Hours Register (HRREG)............................................................... |

122 |

|

6.8.4.1.6 |

Hours Alarm 1 Register (HRA1REG)............................................. |

122 |

|

6.8.4.1.7 |

Day Of Week Register (DOWREG) ............................................... |

122 |

|

6.8.4.1.8 |

Date Of Month Register (DOMREG).............................................. |

123 |

|

6.8.4.1.9 |

Month Register (MONREG) ........................................................... |

123 |

|

6.8.4.1.10 |

Year Register (YRREG)................................................................. |

123 |

|

6.8.4.1.11 |

RTC Control Register A (CTLREGA)............................................. |

123 |

|

6.8.4.1.12 |

RTC Control Register B (CTLREGB)............................................. |

124 |

|

6.8.4.1.13 |

RTC Control Register C (CTLREGC) ............................................ |

125 |

|

6.8.4.1.14 |

RTC Control Register D (CTLREGD) ............................................ |

126 |

|

6.8.4.1.15 |

Date of Month Alarm 1 Register (DOMA1REG) |

............................. 126 |

|

6.8.4.1.16 |

Month Alarm 1 Register (MONA1REG) ......................................... |

126 |

|

6.8.4.2 RTC Bank 1 Register............................................................................................. |

126 |

|

|

6.8.4.2.1 |

Seconds Alarm 2 Register (SECA2REG) ...................................... |

126 |

|

6.8.4.2.2 |

Minutes Alarm 2 Register (MINA2REG) ........................................ |

126 |

|

6.8.4.2.3 |

Hours Alarm 2 Register (HRA2REG)............................................. |

127 |

|

6.8.4.2.4 |

Date of Month Alarm 2 Register (DOMA2REG) |

............................. 127 |

|

6.8.4.2.5 |

Month Alarm 2 Register (MONA2REG) ......................................... |

127 |

|

6.8.4.3 RTC I/O Register ................................................................................................... |

127 |

|

|

6.8.4.3.1 |

RTC Index Register of Bank 0 (RIRB0) ......................................... |

127 |

|

6.8.4.3.2 |

RTC Data Register of Bank 0 (RDRB0)......................................... |

127 |

|

6.8.4.3.3 |

RTC Index Register of Bank 1 (RIRB1) ......................................... |

128 |

|

6.8.4.3.4 |

RTC Data Register of Bank 1 (RDRB1)......................................... |

128 |

7. EC Domain Functions................................................................................................................................ |

|

131 |

|

7.1 8032 Embedded Controller (EC)..................................................................................................... |

131 |

||

7.1.1 |

Overview............................................................................................................................. |

|

131 |

7.1.2 |

Features ............................................................................................................................. |

|

131 |

7.1.3 |

General Description............................................................................................................ |

|

131 |

7.1.4 |

Functional Description....................................................................................................... |

131 |

|

7.1.5 |

Memory Organization ......................................................................................................... |

|

132 |

7.1.6 |

On-Chip Peripherals........................................................................................................... |

|

133 |

7.1.7 |

Timer / Counter................................................................................................................... |

|

135 |

7.1.8 Idle and Doze/Sleep Mode ................................................................................................. |

144 |

||

7.1.9 EC Internal Register Description........................................................................................ |

144 |

||

|

7.1.9.1 Port 0 Register (P0R) ............................................................................................ |

145 |

|

|

7.1.9.2 Stack Pointer Register (SPR) ................................................................................ |

145 |

|

|

7.1.9.3 Data Pointer Low Register (DPLR)........................................................................ |

145 |

|

|

7.1.9.4 Data Pointer High Register (DPHR) ...................................................................... |

145 |

|

|

7.1.9.5 Data Pointer 1 Low Register (DP1LR)................................................................... |

145 |

|

|

7.1.9.6 Data Pointer 1 High Register (DP1HR) ................................................................. |

145 |

|

|

7.1.9.7 Data Pointer Select Register (DPSR).................................................................... |

145 |

|

|

7.1.9.8 Power Control Register (PCON)............................................................................ |

146 |

|

|

7.1.9.9 Timer Control Register (TCON)............................................................................. |

146 |

|

|

7.1.9.10 Timer Mode Register (TMOD) ............................................................................... |

147 |

|

|

7.1.9.11 Timer 0 Low Byte Register (TL0R) ........................................................................ |

147 |

|

|

7.1.9.12 Timer 1 Low Byte Register (TL1R) ........................................................................ |

147 |

|

|

7.1.9.13 Timer 0 High Byte Register (TH0R)....................................................................... |

147 |

|

|

7.1.9.14 Timer 1 Low Byte Register (TH1R) ....................................................................... |

148 |

|

|

7.1.9.15 Clock Control Register (CKCON) .......................................................................... |

148 |

|

|

7.1.9.16 Port 1 Register (P1R) ............................................................................................ |

148 |

|

www.ite.com.tw |

vi |

IT8511E/TE/G V0.4.1 |

|

|

|

|

|

|

Contents |

|

|

|

|

|

|

|

7.1.9.17 |

Serial Port Control Register (SCON) ..................................................................... |

|

149 |

|

|

7.1.9.18 |

Serial Port Buffer Register (SBUFR) ..................................................................... |

|

149 |

|

|

7.1.9.19 |

Port 2 Register (P2R) ............................................................................................ |

|

149 |

|

|

7.1.9.20 |

Interrupt Enable Register (IE)................................................................................ |

|

150 |

|

|

7.1.9.21 |

Port 3 Register (P3R) ............................................................................................ |

|

150 |

|

|

7.1.9.22 |

Interrupt Priority Register (IP)................................................................................ |

|

151 |

|

|

7.1.9.23 |

Status Register (STATUS) ................................................................................... |

|

151 |

|

|

7.1.9.24 |

Timer 2 Control Register (T2CON)........................................................................ |

|

151 |

|

|

7.1.9.25 |

Timer Mode Register (T2MOD) ............................................................................. |

|

152 |

|

|

7.1.9.26 |

Timer 2 Capture Low Byte Register (RCAP2LR) .................................................. |

|

152 |

|

|

7.1.9.27 |

Timer 2 Capture High Byte Register (RCAP2HR)................................................. |

|

152 |

|

|

7.1.9.28 |

Timer 2 Low Byte Register (TL2R) ........................................................................ |

|

152 |

|

|

7.1.9.29 |

Timer 2 High Byte Register (TH2R)....................................................................... |

|

153 |

|

|

7.1.9.30 |

Program Status Word Register (PSW).................................................................. |

|

153 |

|

|

7.1.9.31 |

Watch Dog Timer Control Register (WDTCON).................................................... |

|

153 |

|

|

7.1.9.32 |

Accumulator Register (ACC) ................................................................................. |

|

154 |

|

|

7.1.9.33 |

B Register (BR)...................................................................................................... |

|

154 |

|

|

7.1.10 |

Programming Guide ........................................................................................................... |

|

154 |

|

|

7.1.10.1 |

Code Snippet of Entering Idle/Doze/Sleep Mode.................................................. |

|

154 |

|

|

7.1.10.2Code snippet of Copying Flash Content to Scratch ROM 4 (MOVC-MOVX by PIO) |

||||

|

|

......................................................................................................................................... |

|||

|

|

................................................................................................................................... |

|

|

155 |

|

7.1.10.3 |

Code snippet of Copying Flash Content to Scratch ROM (DMA) |

......................... 156 |

||

7.2 |

Interrupt Controller (INTC) .............................................................................................................. |

|

157 |

||

|

7.2.1 |

Overview............................................................................................................................. |

|

157 |

|

|

7.2.2 |

Features ............................................................................................................................. |

|

157 |

|

|

7.2.3 |

Functional Description........................................................................................................ |

|

157 |

|

|

7.2.3.1 |

Power Fail Interrupt ............................................................................................... |

|

157 |

|

|

7.2.3.2 |

ROM Match Interrupt ............................................................................................. |

|

157 |

|

|

7.2.3.3 |

Programmable Interrupts....................................................................................... |

|

157 |

|

|

7.2.4 |

EC Interface Registers ....................................................................................................... |

|

158 |

|

|

7.2.4.1 |

Interrupt Status Register 0 (ISR0) ......................................................................... |

|

159 |

|

|

7.2.4.2 |

Interrupt Status Register 1 (ISR1) ......................................................................... |

|

159 |

|

|

7.2.4.3 |

Interrupt Status Register 2 (ISR2) ......................................................................... |

|

160 |

|

|

7.2.4.4 |

Interrupt Status Register 3 (ISR3) ......................................................................... |

|

160 |

|

|

7.2.4.5 |

Interrupt Enable Register 0 (IER0) ........................................................................ |

|

160 |

|

|

7.2.4.6 |

Interrupt Enable Register 1 (IER1) ........................................................................ |

|

161 |

|

|

7.2.4.7 |

Interrupt Enable Register 2 (IER2) ........................................................................ |

|

161 |

|

|

7.2.4.8 |

Interrupt Enable Register 3 (IER3) ........................................................................ |

|

161 |

|

|

7.2.4.9 |

Interrupt Edge/Level-Triggered Mode Register 0 (IELMR0).................................. |

|

161 |

|

|

7.2.4.10 |

Interrupt Edge/Level-Triggered Mode Register 1 (IELMR1).................................. |

|

162 |

|

|

7.2.4.11 |

Interrupt Edge/Level-Triggered Mode Register 2 (IELMR2).................................. |

|

162 |

|

|

7.2.4.12 |

Interrupt Edge/Level-Triggered Mode Register 3 (IELMR3).................................. |

|

162 |

|

|

7.2.4.13 |

Interrupt Polarity Register 0 (IPOLR0)................................................................... |

|

162 |

|

|

7.2.4.14 |

Interrupt Polarity Register 1 (IPOLR1)................................................................... |

|

163 |

|

|

7.2.4.15 |

Interrupt Polarity Register 2 (IPOLR2)................................................................... |

|

163 |

|

|

7.2.4.16 |

Interrupt Polarity Register 3 (IPOLR3)................................................................... |

|

163 |

|

|

7.2.4.17 |

Interrupt Vector Register (IVCT)............................................................................ |

|

163 |

|

|

7.2.4.18 |

8032 INT0# Status (INT0ST)................................................................................. |

|

164 |

|

|

7.2.4.19 |

Power Fail Register (PFAILR) ............................................................................... |

|

164 |

|

|

7.2.5 |

INTC Interrupt Assignments ............................................................................................... |

|

165 |

|

|

7.2.6 |

Programming Guide ........................................................................................................... |

|

167 |

|

7.3 |

Wake-Up Control (WUC) ................................................................................................................ |

|

168 |

||

|

7.3.1 |

Overview............................................................................................................................. |

|

168 |

|

|

7.3.2 |

Features ............................................................................................................................. |

|

168 |

|

|

7.3.3 |

Functional Description........................................................................................................ |

|

168 |

|

www.ite.com.tw |

|

vii |

IT8511E/TE/G V0.4.1 |

||

IT8511E/TE/G

7.3.4 |

EC Interface Registers ....................................................................................................... |

168 |

|

|

7.3.4.1 |

Wake-Up Edge Mode Register (WUEMR1) .......................................................... |

168 |

|

7.3.4.2 |

Wake-Up Edge Mode Register (WUEMR2) .......................................................... |

169 |

|

7.3.4.3 |

Wake-Up Edge Mode Register (WUEMR3) .......................................................... |

169 |

|

7.3.4.4 |

Wake-Up Edge Mode Register (WUEMR4) .......................................................... |

169 |

|

7.3.4.5 |

Wake-Up Edge Sense Register (WUESR1).......................................................... |

169 |

|

7.3.4.6 |

Wake-Up Edge Sense Register (WUESR2).......................................................... |

170 |

|

7.3.4.7 |

Wake-Up Edge Sense Register (WUESR3).......................................................... |

170 |

|

7.3.4.8 |

Wake-Up Edge Sense Register (WUESR4).......................................................... |

170 |

|

7.3.4.9 |

Wake-Up Enable Register (WUENR1).................................................................. |

171 |

|

7.3.4.10 |

Wake-Up Enable Register (WUENR2).................................................................. |

171 |

|

7.3.4.11 |

Wake-Up Enable Register (WUENR3).................................................................. |

171 |

|

7.3.4.12 |

Wake-Up Enable Register (WUENR4).................................................................. |

171 |

7.3.5 |

WUC Input Assignments .................................................................................................... |

172 |

|

7.3.6 |

Programming Guide ........................................................................................................... |

173 |

|

7.4 Keyboard Matrix Scan Controller .................................................................................................... |

174 |

||

7.4.1 |

Overview............................................................................................................................. |

174 |

|

7.4.2 |

Features ............................................................................................................................. |

174 |

|

7.4.3 |

EC Interface Registers ....................................................................................................... |

174 |

|

|

7.4.3.1 |

Keyboard Scan Out Low Byte Data Register (KSOL) ........................................... |

174 |

|

7.4.3.2 |

Keyboard Scan Out High Byte Data 1 Register (KSOH1)..................................... |

174 |

|

7.4.3.3 |

Keyboard Scan Out Control Register (KSOCTRL)................................................ |

174 |

|

7.4.3.4 |

Keyboard Scan Out High Byte Data 2 Register (KSOH2)..................................... |

175 |

|

7.4.3.5 |

Keyboard Scan In Data Register (KSIR) ............................................................... |

175 |

|

7.4.3.6 |

Keyboard Scan In Control Register (KSICTRLR).................................................. |

175 |

7.5 General Purpose I/O Port (GPIO) ................................................................................................... |

176 |

||

7.5.1 |

Overview............................................................................................................................. |

176 |

|

7.5.2 |

Features ............................................................................................................................. |

176 |

|

7.5.3 |

EC Interface Registers ....................................................................................................... |

176 |

|

|

7.5.3.1 |

General Control Register (GCR) ........................................................................... |

176 |

|

7.5.3.2 |

Port Data Registers A-M (GPDRA-GPDRM)......................................................... |

177 |

|

7.5.3.3 |

Port Data Mirror Registers A-M (GPDMRA-GPDMRM) ........................................ |

177 |

|

7.5.3.4 |

Port Control n Registers (GPCRn, n = A0-I7)........................................................ |

178 |

|

7.5.3.5 |

Output Type Registers A-I (GPOTA-GPOTI)......................................................... |

180 |

7.5.4 |

Alternate Function Selection .............................................................................................. |

181 |

|

7.5.5 |

Programming Guide ........................................................................................................... |

186 |

|

7.6 EC Clock and Power Management Controller (ECPM) .................................................................. |

187 |

||

7.6.1 |

Overview............................................................................................................................. |

187 |

|

7.6.2 |

Features ............................................................................................................................. |

187 |

|

7.6.3 |

EC Interface Registers ....................................................................................................... |

187 |

|

|

7.6.3.1 |

Clock Frequency Select Register (CFSELR) ........................................................ |

187 |

|

7.6.3.2 |

Clock Gating Control 1 Register (CGCTRL1R) ..................................................... |

187 |

|

7.6.3.3 |

Clock Gating Control 2 Register (CGCTRL2R) ..................................................... |

188 |

|

7.6.3.4 |

Clock Gating Control 3 Register (CGCTRL3R) ..................................................... |

189 |

|

7.6.3.5 |

PLL Control (PLLCTRL) ........................................................................................ |

189 |

|

7.6.3.6 |

Auto Clock Gating (AUTOCG)............................................................................... |

189 |

7.7 SM Bus Interface (SMB) ................................................................................................................. |

191 |

||

7.7.1 |

Overview............................................................................................................................. |

191 |

|

7.7.2 |

Features ............................................................................................................................. |

191 |

|

7.7.3 |

Functional Description........................................................................................................ |

191 |

|

|

7.7.3.1 |

SMBUS Master Interface....................................................................................... |

191 |

|

7.7.3.2 |

SMBUS Porting Guide........................................................................................... |

192 |

7.7.4 |

EC Interface Registers ....................................................................................................... |

196 |

|

|

7.7.4.1 |

Host Status Register (HOSTA).............................................................................. |

196 |

|

7.7.4.2 |

Host Control Register (HOCTL)............................................................................. |

197 |

|

7.7.4.3 |

Host Command Register (HOCMD) ...................................................................... |

198 |

www.ite.com.tw |

viii |

IT8511E/TE/G V0.4.1 |

|

|

|

|

Contents |

|

|

|

|

7.7.4.4 |

Transmit Slave Address Register (TRASLA) ........................................................ |

198 |

|

7.7.4.5 |

Data 0 Register (D0REG)...................................................................................... |

198 |

|

7.7.4.6 |

Data 1 Register (D1REG)...................................................................................... |

198 |

|

7.7.4.7 |

Host Block Data Byte Register (HOBDB).............................................................. |

198 |

|

7.7.4.8 |

Packet Error Check Register (PECERC)............................................................... |

199 |

|

7.7.4.9 |

SMBUS Pin Control Register (SMBPCTL) ............................................................ |

199 |

|

7.7.4.10 |

Host Control Register 2 (HOCTL2)........................................................................ |

199 |

|

7.7.4.11 |

4.7 μs Low Register (4P7USL) .............................................................................. |

200 |

|

7.7.4.12 |

4.0 μs Low Register (4P0USL) .............................................................................. |

200 |

|

7.7.4.13 |

300 ns Register (300NSREG) ............................................................................... |

200 |

|

7.7.4.14 |

250 ns Register (250NSREG) ............................................................................... |

200 |

|

7.7.4.15 |

25 ms Register (25MSREG).................................................................................. |

200 |

|

7.7.4.16 |

45.3 μs Low Register (45P3USLREG) .................................................................. |

201 |

|

7.7.4.17 |

45.3 μs High Register (45P3USHREG)................................................................. |

201 |

|

7.7.4.18 |

4.7 μs And 4.0 μs High Register (4p7A4P0H) ....................................................... |

201 |

|

7.8 PS/2 Interface ................................................................................................................................. |

|

202 |

|

7.8.1 |

Overview............................................................................................................................. |

202 |

|

7.8.2 |

Features ............................................................................................................................. |

202 |

|

7.8.3 |

Functional Description........................................................................................................ |

202 |

|

7.8.3.1 |

Hardware Mode Selected ...................................................................................... |

202 |

|

7.8.3.2 |

Software Mode Selected ....................................................................................... |

203 |

|

7.8.4 |

EC Interface Registers ....................................................................................................... |

203 |

|

7.8.4.1 |

PS/2 Control Register 1-4 (PSCTL1-4) ................................................................. |

203 |

|

7.8.4.2 |

PS/2 Interrupt Control Register 1-4 (PSINT1-4).................................................... |

204 |

|

7.8.4.3 |

PS/2 Status Register 1-4 (PSSTS1-4)................................................................... |

204 |

|

7.8.4.4 |

PS/2 Data Register 1-4 (PSDAT1-4)..................................................................... |

205 |

|

7.9 Digital To Analog Converter (DAC)................................................................................................. |

206 |

||

7.9.1 |

Overview............................................................................................................................. |

206 |

|

7.9.2 |

Feature |

............................................................................................................................... |

206 |

7.9.3 |

Functional Description........................................................................................................ |

206 |

|

7.9.4 |

EC Interface Registers ....................................................................................................... |

206 |

|

7.9.4.1 |

DAC Control Register (DACCTRL)........................................................................ |

206 |

|

7.9.4.2 |

DAC Data Channel 0~3 Register (DACDAT0~3) .................................................. |

207 |

|

7.9.4.3 |

DAC Power Down Register (DACPDREG) ........................................................... |

207 |

|

7.10 Analog to Digital Converter (ADC) .................................................................................................. |

208 |

||

7.10.1 |

Overview............................................................................................................................. |

208 |

|

7.10.2 |

Features ............................................................................................................................. |

208 |

|

7.10.3 |