Page 1

IT6506 Programming Guide

Ver 1.02

Tseng Jau-Chih

ITE Tech. INC.

Last Update Date: 2013/11/12

Page 2

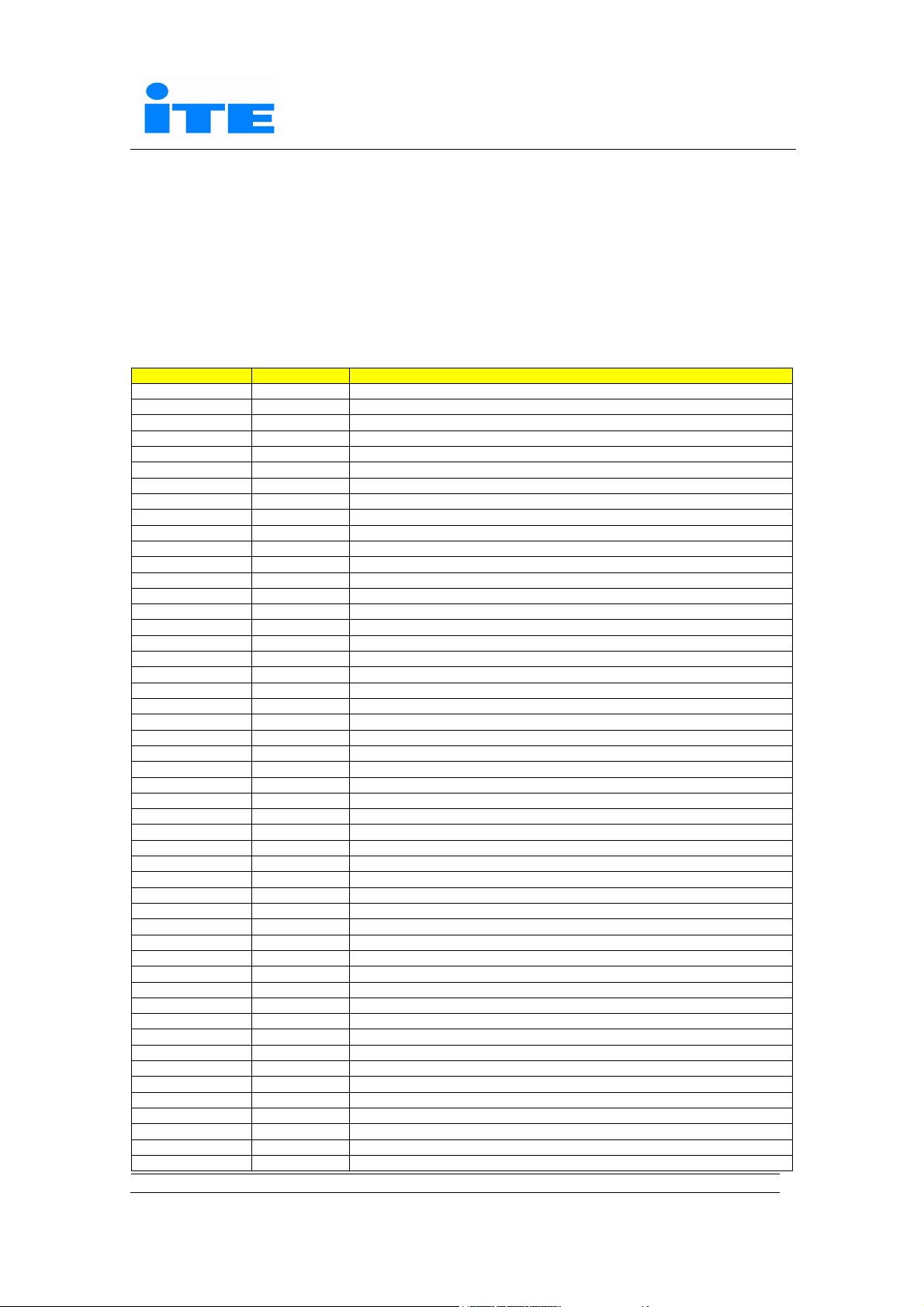

History

Page 3

Index

Chap 1 Introduce .......................................................................................................... 1

Chap 2 IT6506 Initial ..................................................................................................... 4

Initial Register Setting ................................................................................................................... 4

Chap 3 Event of IT6506 ................................................................................................ 6

Chap 4 Link Configuration ............................................................................................ 8

Hot Plug ........................................................................................................................................ 8

System status................................................................................................................................ 8

IT6506 Capacity Configuring ......................................................................................................... 8

Detecting a Tx ............................................................................................................................... 8

Training ......................................................................................................................................... 8

Train Fail ....................................................................................................................................... 8

Chap 5 Video Programming .......................................................................................... 9

Video Input Readback ................................................................................................................... 9

Video Output Programming ......................................................................................................... 10

Output RGB444 video ............................................................................................................. 11

Output YCbCr444 video .......................................................................................................... 11

Output YCbCr422 video sync seperated ................................................................................. 11

Output YCbCr422 video sync embedded ................................................................................ 12

Output YCbCr422 video sync embedded CCIR656 ................................................................ 12

Color Converting ..................................................................................................................... 13

Enable Video Output ................................................................................................................... 14

Chap 6 Audio Programming........................................................................................ 15

Audio Input Information ............................................................................................................... 15

Configure Audio Output ............................................................................................................... 16

Audio Error .................................................................................................................................. 16

Chap 9 Registers ........................................................................................................ 19

Bank 0 : reg05[3] = ‘0’, reg05[0] = ‘0’ .......................................................................................... 19

Bank 1 : Reg05[3][0] = ‘0’ ‘1’ ....................................................................................................... 31

Bank 2 : (reg5[3] = ‘1’, reg5[0] = ‘0’) ............................................................................................ 37

-i

Page 4

IT6506 PROGRAMMING GUIDE

Chap 1 Introduce

The IT6506 is a high-performance DisplayPort 1.1a receiver, fully compliant with DisplayPort

1.1a,

HDCP 1.3 specifications. The IT6506 with its Deep Color capability (up to 36-bit) ensures

robust reception of high-quality uncompressed video content, along with state-of-the-art

uncompressed and compressed digital audio content.

Aside from the various video output formats supported, the IT6506 also receives and provides

up to 8 channels of I2S digital audio outputs, with sampling rate up to 192kHz and sample size

up to 24 bits, facilitating direct connection to industry-standard low-cost audio DACs. Also, an

S/PDIF output is provided to support up to compressed audio of 192kHz frame rate.

Each IT6506 comes preprogrammed with an unique HDCP key, in compliance with the HDCP

1.3 standard so as to provide secure transmission of high-definition content. Users of the

IT6506 need not purchase any HDCP keys or ROMs.

Features

• Compliance with DisplayPort Specification V1.1a at 1.62/2.7 Gbps data rate (Low bit

rate/High bit rate)

• Support flexible 1/2/4 lanes configurations; Full 10.8Gbps data rate support(4 lanes at

2.7Gbps)

• Support DPCD Rev.1.1

• Support HDCP 1.3 with HDCP key embedded

• Support Spread Spectrum Clocking up to 0.5% down-spread to reduce EMI

• Support Source Connection Detection through AUX channel DC levels

• Support up to WQXGA(2560X1600) VESA display format

• Support Digital Video Output in 18/24/30/36(deep color) bits format with separate

Sync control

• Support Pixel component format with RGB; YCbCr 422; YCbCr 444

• Support Bit depth per color with 6/8/10/12 bits

• Bi-direction Color Space Conversion (CSC) between RGB and YCbCr color spaces

with programmable coefficients.

• Up/down sampling between YCbCr 4:4:4 and YCbCr 4:2:2

• Dithering for conversion from 12-bit component to 10-bit/8-bit

• S/PDIF interface supporting PCM, Dolby Digital, DTS digital audio up to 192kHz frame

rate

• Support 8-channel, uncompressed LPCM I2S audio with sample rates of 32~192 kHz

and sample sizes of 16~24 bits

• Automatic Audio Error detection with soft mute function, preventing annoying harsh

output sound due to audio error or hot-unplug

ITE Tech. INC.

-1- 2013/11/12

Page 5

IT6506 PROGRAMMING GUIDE

2

• Automatic loss of signal detection for Link management

• Intelligent, programmable power management

• 144-pin LQFP (20mm x 20mm) package

Pin Diagram

RX3N

RX3P

RX2N

RX2P

AVCC

AGND

VSYNC

QB35

OVSS

OVDD

SCL K

WS

I2S0

I2S1

I2S2

I2S3

OVD D

OVS S

MCL K

SPD IF

IVD D

IVD D

IVSS

HPD

QB2

QB3

QB4

QB5

QB6

QB7

QB8

QB9

OVD D

OVS S

QB1 0

QB1 1

IVDD

IVSS

DDC SCL

DDC SDA

QB1 4

QB1 5

QB1 6

QB1 7

QB1 8

QB1 9

ASPGND

INT#

PCADR

PCSCL

SYSRSTN

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

QB21

QB20

ENTEST

PCSDA

OVDD

QB26

OVSS

QB23

QB22

PGND

ASPVCC

XTALIN

XTALOUT

6263646566676869707172

Displayport RX Chip

119118117116115114113112111110109

QB27

IVDD

IVSS

QB28

AVCC

PVCC

DVSS18

DVDD18

IT6506

LQFP-144

(Top View)

QB29

QB30

QB31

QB32

QB33

QB34

EMEM_VPP

DCAUXN

AGND

RX1N

RX1P

RX0N

RX0P

DVDD18

PGND

PVCC

AVCC

DVSS18

HSYNC

IVDD

PCLK

IVSSDEQA0

QA1

QA4

QA2

QA3

DCAUXP

RXAUXP

RXAUXN

37383940414243444546474849505152535455565758596061

36

QA35

35

QA34

34

QA33

33

QA32

32

OVSS

31

OVDD

30

QA31

29

QA30

28

QA29

27

QA2 8

26

IVSS

25

IVDD

24

QA27

23

QA26

22

QA25

21

QA24

20

QA23

19

QA22

18

QA21

17

QA20

16

OVSS

15

OVD D

14

QA19

13

QA18

12

QA17

11

QA16

10

IVSS

9

IVDD

8

QA15

7

QA14

6

QA13

5

QA12

4

QA11

3

QA10

2

QA9

1

QA8

QA5

144143142141140139138137136135134133132131130129128127126125124123122121120

OVDD

OVSS

QA6

QA7

IT6506 provides internal register accessed via PCSCL (pin 71) and PCSDA (pin 70) with slave

address 0xB0 where PCADR (pin68) is low, or 0xB2 where PCADR (pin68) is high under

100KHz speed.

The terms listed in the below table are using in future chapters:

Term Description Example

RegXX Where XX is a hexadecimal number, to indicate the

internal register accessed with subaddress XX of

2

I

C, and in bank 0.

ITE Tech. INC.

-2- 2013/11/12

Reg05 – access with I

address 0xB0/0xB2,

sub-address 0x05.

C slave

Page 6

IT6506 PROGRAMMING GUIDE

Reg1XX

Reg2XX Where XX is a hexadecimal number, to indicate the

The register 0x00~0x0F are common for all banks, and the bank switching using as following:

bank 0 – reg05[3][0] = ‘0’ ‘0’

bank 1 – reg05[3][0] = ‘0’ ‘1’

bank 2 – reg05[3][0] = ‘1’ ‘0’

Where XX is a hexadecimal number, to indicate the

internal register accessed with subaddress XX of

I2C, and in bank 1.

internal register accessed with subaddress XX of

I2C, and in bank 2.

Reg1C0 – access with I2C

slave address 0xB0/0xB2,

sub-address 0xC0.

ITE Tech. INC.

-3- 2013/11/12

Page 7

IT6506 PROGRAMMING GUIDE

Reg Bit Mask

Bit Value

0xEA 0xFF 0xFF

0xEA 0xFF 0x10

0xEB 0xFE 0xFE

0x1B3

0xFE 0xFE

0x1B3

0xFE 0x00

0x1B2

0xFF 4

0x1B2

0x05 1

0x1B5

0xFF 0x14

0x1B7

0xFF 0x33

0x1B8

0xFF 0x03

0x1CD

0xFF 0x80

0x1D2

0xFF 0x88

0x1D3

0xFF 0x69

0xEA 0x05 0x05

0xEA 0x05 0x04

0xEE 0x01 0x01

0x21 0xFF 0x0A

0x22 0xFF 0x64

0x2F 0xFF 0x7B

0xFD 0x05 4

0x31 0x40 0x40

0x32 0xFF 0xFF

0xB2 0x41 1

0xB7 0xFF 0x10

0xB8 0xFF 0x08

0xB9 0xFF 0x10

0xBA 0xFF 0x08

0xBB 0xFF 0x30

0xBC 0xFF 0x60

0xBD 0xF0 0x00

0xC0 0xFF 0x00

0xC1 0xBF 0xBF

0xC2 0xFF 0x8C

0xC3 0xFF 0x7A

0xCC 0xFF 0xC5

0xCD 0xFF 0xA8

0xE3 0x80 0x80

0xEB 0x8F 0xF

0xEC 0x26 0x26

0xEF 0x24 0x24

0xF1 0x40 0x40

0xFC 0xFF 0x21

0xD2 0xFF 0xE0

0xF6 0xFF 0x4C

0x1A5

0xFF 0xC8

0x1A2

0x10 0x00

0x1B1

0x04 0x04

0x1B1

0x78 0x00

0x170

0x0C 0x04

0xE4 0xFF 0

x00

Chap 2 IT6506 Initial

IT6506 initial can be separated into two parts. The first part is to reset the physical layer of

IT6506. The second part is to reset the logical part of IT6506.

Initial Register Setting

The following table is the setting sequence for each step. The Bit Mask means the bit to

update on each step, and the Bit Value means the updating part of each step.

ITE Tech. INC.

-4- 2013/11/12

Page 8

IT6506 PROGRAMMING GUIDE

0xE6 0xFF 0x00

0xE9 0xFF 0x00

0xE5 0xFF 0x07

0xE7 0xFF 0xFF

0xE8 0xFF 0xFF

0xC9 0x09 0x09

0xED 0xC0 0x80

0xEE 0x02 0x00

0xEE 0xFC 0xFC

0xC9 0x10 0x10

0xF7 0x01 0x00

ITE Tech. INC.

-5- 2013/11/12

Page 9

IT6506 PROGRAMMING GUIDE

Reg Name

Bit Descrioption

Type

Reserved

7:6 ------------------------------------------

RO

IntGroup5

5

Group Reg0Ch Int

RO

IntGroup4

4

Group Reg0Bh Int

RO

IntGroup3

3

Grou

p Reg0Ah Int

RO

IntGroup2

2

Group Reg09h Int

RO

IntGroup1

1

Group Reg08h Int

RO

IntGroup0

0

Group Reg07h Int

RO

Reg Name

Bit Descr

ioption

Type

LSVBIDInt

7

VBID majority error interrupt

W1C

LSNAudInt

6

NAud majority error interrupt

W1C

LSMAudInt

5 Ma

ud majority error interrupt

W1C

LSMVidInt

4

Mvid majority error interrupt

W1C

RegAFUflow

3 Audio fifo under flow

RO

RegAFOf

low 2 A

udio fifo over flow

RO

RegVFUflow

1

video fifo under flow

RO

RegVFOflow

0

video fifo over flow

RO

LSAudMuteEnd

7

Audio mute end interrupt

W1C

LSAudMuteStart

6

Audio mute start

interrupt

W1C

LSVidMuteEnd

5

Video mute end interrupt

W1C

L

SVidMuteStart

4

Video mute start interrupt

W1C

AutoAudMute

3 Write 1 will gen

REGHWMuteAACClr

W1C

RefAuxURLen

2

AUX receive un

-

support length interrupt

W1C

RefAuxURCmd

1

AUX receive un

-

support command interrupt

W1C

RefAuxSynErr

0

AUX receive sync l

ength error interrupt

W1C

LSNoSPDInfo

7

No SPD InfoFrame interrupt

W1C

LSNoMpegInfo

6

No Mpeg InfoFrame interrupt

W1C

LSNoAudInfo

5

No Audio InfoFrame interrupt

W1C

LSNoAVIInfo

4

No AVI InfoFrame interrupt

W1C

LSL3ECCInt

3

Lane 3 (2 nibble erro

r) ECC interrupt

W1C

LSL2ECCInt

2

Lane 2 (2 nibble error) ECC interrupt

W1C

LSL1ECCInt

1

Lane 1 (2 nibble error) ECC interrupt

W1C

LSL0ECCInt

0

Lane 0 (2 nibble error) ECC interrupt

W1C

RefL3SymUnLkIRQ

7

Lane 3 Symbol lose lock interrupt

W1C

Re

fL2SymUnLkIRQ

6

Lane 2 Symbol lose lock interrupt

W1C

RefL1SymUnLkIRQ

5

Lane 1 Symbol lose lock

interrupt

W1C

RefL0SymUnLkIRQ

4

Lane 0 Symbol lose lock interrupt

W1C

RefLnkTrnFalIRQ

3

Link Training fail interrupt

W1C

RefSymUnAlgnIRQ

2

Symbol lose a

lignment interrupt

W1C

RefLnkTrnDnIRQ

1

Link Training done interrupt

W1C

RefLnkTrnStrIRQ

0

Link Training start interrupt

W1C

RefAuthDnIRQ

7

Authentication done interrupt

W1C

RefAuthStartIRQ

6

Authentication start interrupt

W1C

RefLCFailIRQ

5 Link Integrity Check fail interrupt

W1C

RefRiRdyIRQ

4

R0 ready interrupt

W1C

RefAksvFailIRQ

3

Illegal Aksv interrrupt

W1C

RefHPDRstNIRQ

2

HPD Reset interrupt

W1C

RefD3EntryInt

1

DPCD 00600h[1:0] have been changed to 10

W1C

RefD0En

tryInt 0 DPCD 00600h[1:0] have been changed to 01

W1C

0C Reserved

7

------------------------------------------

RO

Chap 3 Event of IT6506

The events of IT6506 will activate the bits in reg06, where each bit corresponded to a group of

event shows in the table reg07~reg0C.

06

The event of IT6506 shows on the register Reg07~Reg0C, as the following table, where write

to one will clear the bits.

07

08

09

0A

0B

from other values

ITE Tech. INC.

from other values

-6- 2013/11/12

Page 10

IT6506 PROGRAMMING GUIDE

LSNewGenPkt

6

New Mpeg InfoFrame interrupt

W1C

LSNewSPDInfo

5

New SPD InfoFrame interrupt

W1C

LSNewMpegInfo

4

New Mpe

g InfoFrame interrupt

W1C

LSNewAudInfo

3

New Audio InfoFrame interrupt

W1C

LSNewAVIInfo

2

New AVI InfoFrame interrupt

W1C

LSNewVidFormat

1

New Video format interrupt

W1C

RefI2CHangInt

0

I2C may hanging ( stay the same state too

W1C

LSL32

NibbleErr

7

Lane 3 ECC 2 nibble error

W1C

LSL22NibbleErr

6

Lane 2 ECC 2 nibble error

W1C

LSL12NibbleErr

5

Lane 1 ECC 2 nibble error

W1C

LSL02NibbleErr

4

Lane 0 ECC 2 nibble error

W1C

LSL31NibbleErr

3

Lane 3 ECC 1 nibble error

W1C

LSL21NibbleErr

2

Lane 2 ECC 1 nibble error

W1C

LSL11NibbleErr

1

Lane 1 ECC 1 nibble error

W1C

LSL01NibbleErr

0

Lane 0 ECC 1 nibble error

W1C

Reg Name

Bit Description

Type Defa

ult

E4 RegIntMask

[7:0] 7:0 Interrupt Mask [7:0]

R/W 11111111

E5 RegIntMask

[15:8]

7:0 Interrupt Mask [15:8]

R/W 11111111

E6 RegIntMask

[23:16]

7:0 Interrupt Mask [23:16]

R/W 1111

1111

E7 RegIntMask

[31:24]

7:0 Interrupt Mask [31:24]

R/W 11111111

E8 RegIntMask

[39:32]

7:0 Interrupt Mask [39:32]

R/W 11111111

E9 RegIntMask[47]

7

Reserved For

future

use R/W 1

RegIntMask[46:40]

6:0 For Resister 0C[6:0]

R/W 1111111

long )

0D

Where interrupt mask is in RegE4~RegE9, and the bits are one-to-one mapping to

reg07~reg0C:

For register 07 ( one to one mapping )

Value

For register 08

For Register 09

For Register 0A

For Register 0B

ITE Tech. INC.

-7- 2013/11/12

Page 11

IT6506 PROGRAMMING GUIDE

reg name bit description

type

Reserved

7:6 ------------------------------------------

RegLnkTrnFail

5

Link Training fail status

RO

RegTxSense

4

Tx Sense status

RO

RegTxPwrSense

3

Tx power is on

RO

RegTxConnected

2

Tx is connected

RO

RegLnkTrnDn

1

Link Training done status

RO

RegLnkTrnBusy

0

Link Training busy status

RO

Feature

Reg Setting

Acceptable Maximum Lane Number

4

lanes –

SSC reg22[6] =

‘1’ for

enabling

Enhance Framing

reg22[5] =

‘1’ for enabling

Chap 4 Link Configuration

Hot Plug

IT6506 can determine the HPD to Tx side with regC9[4] = ‘1’ for plugged and ‘0’ for unplugged.

Trigger HPD interrupt with reg1F[6] to notify DP source device.

System status

The following register regC8 shows the system status of IT6506:

C8

The system state transition can refer these bits to judge the status transition.

IT6506 Capacity Configuring

Set DP sink capability with the following table:

reg22[2:0] = ‘100’

2 lanes –

reg22[2:0] = ‘010’

1 lane –

reg22[2:0] = ‘001’

Detecting a Tx

regC8[4] = ‘1’, means a DP 1.1a transmitter connected.

Training

When DisplayPort transmitter start link training, regC8[0] will be read back as ‘1’. If training

done, regC8[1] = ‘1’ until next training start or fail.

After training done, the video and audio can be measuring.

Train Fail

Detecting a training fail in regC8[4] = ‘1’, the training fail.

ITE Tech. INC.

-8- 2013/11/12

Page 12

IT6506 PROGRAMMING GUIDE

Reserved

7:6 ------------------------------------------

RO

RegAudStable

5 Audio output stable

RO

RegVidStable

4

video output stable

RO

10 RegPClkCnt

[7:0] 7:0 PCLKCnt = the tick count of PCLK under 1024T of

RO

Reserved

7:6 RO

RegAudStable

5 Audio output stable

RO

RegVidStable

4

video output stable

RO

RegPClkCnt

[11:8]

3:0 RO

Reg Name

bit Description

Type

97 LSHTotal

[7:0] 7:0 H total [7:0]

RO

98 LSHTotal

[15:8]

7:0 H total [15:8]

RO

99 LSHStart

[7:0] 7:0 H start [7:0] from H

sync start edge to H active start edge

RO

9A LSHStart

[15:8]

7:0 H start [15:8] from Hsync start edge to H active start edge

RO

9B LSHWidth

[7:0] 7:0 M

ain stream attribute data

- H active width [7:0]

RO

9C LSHWidth

[15:8]

7:0 M

ain stream attribute data

-H active width [15:8]

RO

9D LSVTotal

[7:0] 7:0 M

ain stream attribute data

-

V total [7:0]

RO

9E LSVTotal

[15:8]

7:0 M

ain stream attribute data

-

V total [15:8]

RO

LSVStart

[7:0] 7:0 M

ain stream attribute data

-

V start [7:0] from Vsync start

RO

LSVStart

[15:8]

7:0 M

ain stream attribute data

-

V start [15:8] from Vsync start

RO

A1 LSVHeight

[7:0] 7:0 M

ain stream attribute data

-

V active height [7:0]

RO

A2 LSVHeight

[15:8]

7:0 M

ain stream attribute data

-

V active height [15:8]

RO

A3 LSHSyncWidth

[7:0] 7:0 M

ain stream attribute data

-

H Sync Width [7:0]

RO

LSHSyncPolarity

7 Main stream attribute data

-

H Sync polarity

RO

LSHSyncWidth

[14:8]

6:0 M

ain stream attribute data

-

H Sync Width[14:8]

RO

A5 LSVSy

ncWidth

7:0 M

ain stream attribute data

-

V Sync Width [7:0]

RO

LSVSyncPolarity

7 Main stream attribute data

-

VSync polarity

RO

LSVSyncWidth

6:0 M

ain stream attribute data

-

V Sync Width[7:0]

RO

LSVdBPC

7:5 M

ain stream attribute data

-Bit depth per

color / component

RO

LSVdYUVColor

4 Main stream attribute data

-

YCbCr Colorietry

RO

Chap 5 Video Programming

If DP connection are built and trained, the video will be sent from DP source. Video and audio

input status are present in reg11:

11

Video Input Readback

And begin to program the video output and pass the video parameter defined in the following

registers:

Input Video Pixel Clock is in reg11[3:0]|10[7:0]

27MHz reference clock.

PCLK = 27MHz*1024/PCLKCnt

11

If RegPclkCnt = 186, PCLK = 27MHz * 1024/186 = 148.6MHz

Input Video status registers:

9F

A0

A4

A6

A7

edge to V active start edge

edge to V active start edge

000 = 6 bits

001 = 8 bits

010 = 10 bits

011 = 12 bits

100 = 16 bits

101, 110, 111 = Reserved

ITE Tech. INC.

0: ITU-R BT601-5

1: ITU-R BT709-5

-9- 2013/11/12

Page 13

IT6506 PROGRAMMING GUIDE

LSVdRange

3 Main stream attribute data

-Dynamic range

RO

LSVdPxlFormat

2:1 M

ain stream attribute data

-Component format

RO

LSCLKSync

0 Main stream attribute data

-

Synchronous clock

RO

Reserved

7:3 ------------------------------------------

RO

LSStereoVdAttr

2:1 M

ain stream attribute data

-

Stereo video attribute

RO

LSVdIFrameEven

0 Main stream attribute data

-

Interlaced vertical total even

RO

Name

bit Description

Type Default

Reg_LMSwap

7

1: swap output direction(MSB/LSB)

R/W 0

Reg_O16Bit

6 ‘1’

: YCbCr422 output only 16bit width

R/W 0

Reg_OUTBit

5:4 00: output 8 bits per color channel

R/W 00

Reg_ColorDepth

3:2 00: output 8 bits 444 format

R/W 01

Reg_PCLKDiv2

1 ‘1’: output half PCLK

R/W 0

Reg_ChgSyncPol

0 ‘1’: output H/V sync indicated by reg171[2]/reg171[3]

R/W 0

Reg_PGEn

7

reserved

R/W 0

Reg_DNFreeGo

6 ‘1’: Dither free go.

R/W 0

Reg_EnUdFilt

5 ‘1’: Enable 444

↔

422 up/down filter

R/W 0

Reg_EnDither

4 ‘1’: Enable Dither

R/W 0

Reg_VSyncPol

3 ‘1’: Set V sync polarity as positive while reg170[0] as

‘1’

R/W 0

Reg_HSyncPol

2 ‘1’: Set H sync polarity as positive while reg170[0] as

‘1’

R/W 0

Reg_ChSwap

1 ‘1’: Swap output R/B(Cr/Cb) channel

R/W 0

Reg_RBSwap

0 ‘1’: Swap input R/B(Cr/Cb

) channel

R/W 0

0: VESA range ( from 0 to the maximum )

1: CEA range

00: RGB

01: YCbCr 4:2:2

10: YCbCr 4:4:4

11: Reserved

0: Link clock and stream clock asynchronous

1: Link clock and stream clock synchronous

00: No stereo video transported

01: for progressive vide, the next frame is RIGHT eye, for

interlaced video, TOP field is RIGHT eye and BOTTOM field is

LEFT eye

A8

10: reserved and must not be used

11: for progressive video, the next frame is LEFT eye, for

interlaced video, TOP field is LEFT eye and BOTTOM field is

RIGHT eye

0: number of lines per interlaced frame ( consisting of two

fields ) is an odd number

1: number of lines per interlaced frame ( consisting of two

fields ) is an even number

Video Output Programming

Video output path control registers are listed in the following table:

Reg

‘0’: YCbCr422 output is 24/20 bit width.

01:output 10 bits per color channel

10:output 12 bits per color channel

170

171

11: reserved

01: output 10 bits 444 format

10: output 12 bits 444 format

‘0’: keep the original sync polarity.

‘0’: Set V sync polarity as negative while reg170[0] as ‘1’

‘0’: Set YH sync polarity as negative while reg170[0] as ‘1’

Value

To determine the output color mode, the setting are listed as following:

ITE Tech. INC.

-10- 2013/11/12

Page 14

bit Value

Reg_LMSwap

7 0

Reg_O16Bit

6 0

Reg_OUTBit

5:4

Reg_ColorDepth

3:2

Reg_PCLKDiv2

1 0

Reg_ChgSyncPol

0 0

Reg_PGEn

7 0

Reg_DNFreeGo

6 x

Reg_EnUdFilt

5 x

Reg_EnDither

4 x

Reg_VSyncPol

3 x

Reg_

HSyncPol

2 x

Reg_ChSwap

1 x

Reg_RBSwap

0 x

176 Reg_SyncEmb

3 0

18F Reg_OutDDR

7 0

Reg_2x656Clk

6 0

Reg_656FFRst

5 0

Reg_EnAVMuteRst

4 0

Reg_CSCSel

3:2 00 / 02

Reg_OutColMod

1:0 00

bit Va

lue

Reg_LMSwap

7 0

Reg_O16Bit

6 0

Reg_OUTBit

5:4

Reg_ColorDepth

3:2

Reg_PCLKDiv2

1 0

Reg_ChgSyncPol

0 0

176 Reg_SyncEmb

3 0

Reg_PGEn

7 0

Reg_DNFreeGo

6 x

Reg_EnUdFilt

5 x

Reg_EnDither

4 x

Reg_VSyncPol

3 x

Reg_HSyncPol

2 x

Reg_ChSwap

1 x

Reg_RBSwap

0 x

18F Reg_OutDDR

7 0

Reg_2x656Clk

6 0

Reg_656FFRst

5 0

Reg_EnAVMuteRst

4 0

Reg_CSCSel

3:2 00 / 03

Reg_OutColMod

1:0 10

bit Value

170 Reg_LMSwap

7 0

Output RGB444 video

The output value should be:

170

171

IT6506 PROGRAMMING GUIDE

Output YCbCr444 video

The output value should be:

170

171

Output YCbCr422 video sync seperated

The output value should be:

ITE Tech. INC.

-11- 2013/11/12

Page 15

IT6506 PROGRAMMING GUIDE

Reg_O16Bit

6 x

Reg_OUTBit

5:4 00

Reg_ColorDepth

3:2 00

Reg_PCLKDiv2

1 0

Reg_ChgSyncPol

0 0

176 Reg_SyncEmb

3 0

Reg_PGEn

7 0

Reg_DNFreeGo

6 x

Reg_EnUdFilt

5 x

Reg_EnDither

4 x

Reg_VSyncPol

3 x

Reg_HSyncPol

2 x

Reg_ChSwap

1 x

Reg_RBSwap

0 x

18F Reg_OutDDR

7 0

Reg_2x656Clk

6 0

Reg_656FFRst

5 0

Reg_EnAVMuteRst

4 0

Reg_CSCSel

3:2 00 / 03

Reg_OutColMod

1:0 01

bit Value

Reg_LMSwap

7 0

Reg_O16Bit

6 0

Reg_OUTBit

5:4 00

Reg_ColorDepth

3:2 00

Reg_PCLKDiv2

1 0

Reg_ChgSyncPol

0 0

176 Reg_SyncEmb

3 1

Reg_PGEn

7 0

Reg_DNFreeGo

6 x

Reg_EnUdFilt

5 x

Reg_EnDither

4 x

Reg_VSyncPol

3 x

Reg_HSyncPol

2 x

Reg_ChSwap

1 x

Reg_RBSwap

0 x

18F

Reg_OutDDR

7 0

Reg_2x656Clk

6 0

Reg_656FFRst

5 0

Reg_EnAVMuteRst

4 0

Reg_CSCSel

3:2 00 / 02

Reg_OutColMod

1:0 00

bit Value

Reg_LMSwap

7 0

Reg_O16Bit

6 0

Reg_OU

TBit 5:4 00

Reg_ColorDepth

3:2 00

Reg_PCLKDiv2

1 0

Reg_ChgSyncPol

0 0

Reg_PGEn

7 0

Reg_DNFreeGo

6 x

Reg_EnUdFilt

5 x

171

Output YCbCr422 video sync embedded

The output value should be:

170

171

Output YCbCr422 video sync embedded CCIR656

The output value should be:

170

171

ITE Tech. INC.

-12- 2013/11/12

Page 16

IT6506 PROGRAMMING GUIDE

Reg_EnDither

4 x

Reg_VSyncPol

3 x

Reg_HSyncPol

2 x

Reg_ChSwap

1 x

Reg_RBSwap

0 x

176 Reg_SyncEmb

3 1

18F Reg_Out

DDR 7 0

Reg_2x656Clk

6 1

Reg_656FFRst

5 0

Reg_EnAVMuteRst

4 0

Reg_CSCSel

3:2 00 / 02

Reg_OutColMod

1:0 00

Reg Name

bit description

Type default

173 Reg_YOffSet

7:0

R/W 00000000

174 Reg_COffSet

7:0

R/W 00000000

175 Reg_RGBOffSet

7:0

R/W 00000000

190 Reg_Matrix11V

[7:0] 7:0 CSC matrix 11 low byte

R/W 10110010

Reserved

7:6 ----------------------------

--------------

RO

Reg_Matrix11V

[13:8]

5:0 CSC matrix 11 high bits

R/W 000100

192 Reg_Matrix1

2V[7:0] 7:0 CSC matrix 12 low byte

R/W 01100100

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix1

2V[13:8]

5:0 CSC matrix 12 high bi

ts R/W 000010

194 Reg_Matrix1

3V[7:0] 7:0 CSC matrix 13 low byte

R/W 11101001

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix1

3V[13:8]

5:0 CSC matrix 13 high bits

R/W 000000

196 Reg_Matrix

21V[7:0] 7:0 CSC matrix 21 low byte

R/W 10010011

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix

21V[13:8]

5:0 CSC matrix 21 high bits

R/W 011100

198 Reg_Matrix

22V[7:0] 7:0 CSC matrix 22 low byte

R/W 00010110

Reserved

7:6 ------------------------------------

------ RO

Reg_Matrix

22V[13:8]

5:0 CSC matrix 22 high bits

R/W 000100

19A Reg_Matrix

23V[7:0] 7:0 CSC matrix 23 low byte

R/W 01010110

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix

23V[13:8]

5:0 CSC matrix 23 high bits

R/W 0

11111

19C Reg_Matrix

31V[7:0] 7:0 CSC matrix 31 low byte

R/W 01001001

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix

31V[13:8]

5:0 CSC matrix 31 high bits

R/W 011101

19E Reg_Matrix

32V[7:0] 7:0 CSC matrix 32 low byte

R/W 10011

111

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix

32V[13:8]

5:0 CSC matrix 32 high bits

R/W 011110

1A0 Reg_Matrix

33V[7:0] 7:0 CSC matrix 33 low byte

R/W 00010110

Reserved

7:6 ------------------------------------------

RO

Reg_Matrix

33V[13:8]

5:0 CSC matrix 33 high bits

R/W 000100

Color space converting table

RGB to YUV

YUV to RGB

RGB to YUV

RGB to YUV 709

YUV to RGB

YUV to RGB

reg 16~ 235

0 ~ 255

16~ 235

0 ~ 255

16~ 235

0 ~ 255

16~ 235

0 ~ 255

Reg_CSCSel[1:0]

18F[3:2]

10 10 10 10 11 11 11 11

Reg_YoffSet[7:0]

173 0x00 0x10 0x00 0x10 0x00 0x10 0x00 0x10

Reg_CoffSet[7:0]

174 0x80 0x80 0x80 0x80 0x80 0x80 0x80 0x80

Reg_RGBOffSet[7

:0] 175

0x00 0x10 0x00 0x10 0x00 0x10 0x00 0x10

Reg_Matrix11V[13:0]

190 0xB2 0x09 0xB8 0xE5 0x00 0x4F 0x00 0x4F

191 0x04 0x04 0x05 0x04 0x08 0x09 0x08 0x09

Color Converting

If the input color and output color need a color space convert, the convert matrix are defined in

the following registers:

191

193

195

197

199

19B

19D

19F

1A1

To setting the matrix, depends the input color and output color mapping:

601

601

709

ITE Tech. INC.

-13- 2013/11/12

Page 17

IT6506 PROGRAMMING GUIDE

Reg_Matrix12V[13:0]

192 0x64 0x0E 0xB4 0x78 0x6A 0x81 0x53 0xBA

193 0x02 0x02 0x01 0x01 0x3A 0

x39 0x3C 0x3B

Reg_Matrix13V[13:0]

194 0xE9 0xC8 0x93 0x81 0x4F 0xDF 0x89 0x4B

195 0x00 0x00 0x00 0x00 0x3D 0x3C 0x3E 0x3E

Reg_Matrix21V[13:0]

196 0x93 0x0E 0x49 0xCE 0x00 0x4F 0x00 0x4F

197 0x3C 0x3D 0x3C 0x3C 0x08 0x09 0x08 0x09

Reg_Matrix22V[13:0]

198 0x18 0x84 0x18 0x84 0xF7 0xC2 0x51 0x56

199 0x04 0x03 0x04 0x03 0x0A 0x0C 0x0C 0x0E

Reg_Matrix23V[13:0]

19A 0x56 0x6E 0x9F 0xAE 0x00 0x00 0x00 0x00

19B 0x3F 0x3F 0x3F 0x3F 0x00 0x00 0x00 0x00

Reg_Matrix31V[13:0]

19C 0x49 0xAC 0xD9 0x49 0x00 0x4F 0x00 0x4F

19D 0x3D 0x3D 0x3C 0x3D 0x08 0x09 0x08 0x09

Reg_Matrix32V[13:0]

19E 0x9F 0xD0 0x10 0x33 0x00 0x00 0x00 0x00

19F 0x3E 0x3E 0x3F 0x3F 0x00 0x00 0x00 0x00

Reg_Matrix33V[13:0]

1A0 0x18 0x84 0x18 0x84 0xDB 0x1E 0x87 0xE7

1A1 0x04 0x03 0x04 0x03

0x0D 0x10 0x0E 0x10

Enable Video Output

Set Reg35[3] as zero to enable video output.

To enable video IO, regEB[5:4] = ‘00’

To enable video data output, in single pixel mode, regEE[7:2] = ‘111000’; if under dual pixel

mode, regEE[7:2] = ‘000000’ .

ITE Tech. INC.

-14- 2013/11/12

Page 18

IT6506 PROGRAMMING GUIDE

reg Name

bit description

type Default

88 LSAudStrID

7:0 Audio stream packet ID

RO

LSAudStrCType

6:3 Audio s

tream coding type

RO

LSAudStrChCnt

2:0 Audio stream channel count

RO

RegWs_sel

7

I2S word select switch

R/W 0

RegACINC

6 R/W 0

RegMCLKSel

5:4

R/W 01

RegARDec

3:2

R/W 00

RegAPLLGain

1:0

R/W 01

RegI2s_m

ode 7:6 I2S mapping mode select

R/W 00

RegAudVolCtrl

5:4 A

udio

volume

control

R/W 00

RegHWAudMuteClrMode

3 Audio hardware mute clear enable

R/W 0

RegBiphasemode

2 SPDIF output enable

R/W 0

RegHWMuteClr

1 Audi

o hardware mute clear

R/W 0

RegHWMuteEn

0 Audio hardware mute enable

R/W 0

RegI2S_CH3SEL

7:6 I2S channel 3 output source select

R/W 11

RegI2S_CH

2

SEL 5:4 I2S channel 2 output source select

R/W 10

RegI2S_CH

1

SEL 3:2 I2S channel 1 output source sele

ct R/W 01

RegI2S_CH

0

SEL 1:0 I2S channel 0 output source select

R/W 00

RegHWMuteRate

[7:0] 7:0 A

udio hardware mute rate low byte

R/W 001000

RegI2s_width

7:3 I2S

word length select

R/W 11000

RegHWMuteRate

[10:8]

2:0 A

udio hardware mute rate high

bits R/W 000

Reserved

7:6 ------------------------------------------

RO

RegFSdec

3:0 Sample frequency indicated in

IEC60958

-

3 p11

RO

Chap 6 Audio Programming

RegEA[2] = ‘0’, the audio program is available.

The audio related registers are listed as following table:

Audio Control Register

89

0: left -> right, 1:right->left

F6

00:i2s, 01:right, 10:left, 11:raw 60958

F7

F8

F9

FA

FB

bit 24~27

Sample frequency of software indicated

27..24

--------

0000 44.1 KHz

1000 88.2 KHz

1100 176.4 KHz

0110 24 Khz

0010 48Khz

1010 96Khz

1110 192KHz

0011 32KHz

0000 sampling frequency not indicated.

.

00

The output value can be decided in the initial stage, and only enable audio output while the

audio stable in Reg35[1].

Audio Input Information

Audio is stable when reg10[5] = ‘1’. If no audio stable, and no overflow/underflow interrupt

arriving, there is no audio.

If audio input change or invalid, the audio FIFO overflow/underflow interrupt responds in

reg07[3][2]. When audio change and invalid, reset audio (regEA[2] = ‘1’) and wait for audio

input stable again.

ITE Tech. INC.

-15- 2013/11/12

Page 19

IT6506 PROGRAMMING GUIDE

Audio channel number is presented on reg89[2:0], and sample frequency is presented on

regFB[3:0].

Configure Audio Output

When audio input is available, following the steps described below to configure audio output.

1. regEA[2] = ‘0’.

2. reg1B1[2] = ‘0’

3. reg1B3[2] = ‘1’, regEA[2] = ‘1’

4. reg1B3[2] = ‘0’, regEA[2] = ‘0’

5. If mini mode, set regF5[7] = ‘1’, otherwise, set is as ‘0’.

6. Enable audio output from IT6505:

• If require SPDIF output, set regEB[3] = ‘0’.

• If require I2S for 5~8 channel audio, set regEB[2][1] = ‘0’ ‘0’

• If only require I2S audio with 1~4 channel, set regEB[2][1] = ‘1’ ‘0’

Audio Error

If audio input have error, audio will be automatic mute by IT6506. The interrupt of audio

overflow/underflow will be activated. When audio error, reset the audio circuit with regEA[2] =

‘1’, then reprogram the audio with previous sequence.

ITE Tech. INC.

-16- 2013/11/12

Page 20

IT6506 PROGRAMMING GUIDE

DPCD

Name

Count Reg

Reg

Funcgtion

68000

BKSV 5 130

HDCP register

s are located in DPCD address

68005

R0’ 2 135

68007

AKSV 5 137

6800C

An 8

13C

68014

V’ H1 4 144

224

The V' calculation should do the SHA

-

1 calculation via software.

68018

V’ H2 4 148 228

6801C

V’ H3 4 14C 22C

6

8020 V’ H4 4

150 230

68024

V’ H5 4 154 234

68028

BCaps

1

158

bit 1 – REPEATER

68029

BStatus

1

159

bit 2 –

link ingtegrity_fail

– loss of cipher s

ynchronizationi.

Bstatus[2], LINK_INTEGRITY_FAILURE, is indicated by the HW.

Bstatus[1], R0'_AVALILABLE, is indicated by the HW.

6802A

BInfo 1 15A 238

bit 11

– MAX_CASCADE_EXCEEDED

6802C

KSV

15 15C

Reg Name

Type Description

1E3 invM0[7:0]

R/O

1E4 invM0[15:8]

R/O

1E5 invM0[23:16]

R/O

1E6 invM0[31:24]

R/O

1E7 invM0[39:32]

R/O

1E8 invM0[47:40]

R/O

1E9 invM0[55:48]

R/O

1EA invM0[63:56]

R/O

210~214

KSV0 R/W

215~219

KSV1 R/W

21A~21E

KSV2 R/W

21F~223

KSV3 R/W

224~237

VH

R/W

Offset

map

Mod

225

226

227

229

22A

22B

22D

22E

22F

231

232

233

235

236

237

0x68000~0x6803A, which are mapping to IT6504 bank 1

register 30~6A.

Those registers are read only, and the register should update by

other registers.

No hardware way to calculate.

The calculation of V' (reg224~reg237) need KSVList

(reg15C~reg16A),

RegCF[2] RegSetRepeater = this bit

bit 0 – HDCP_CAPABLE

RegB2[0] RegCPDesired

bit 1 – R0 Available

bit 0 – Ready – HDCP repeater KSV FIFO ready.

Bstatus[0], READY, is programed by RegCF[1], RegSetVReady.

239

FIFO

bit [10:8] – DEPTH

bit [7] – MAX_DEV_EXCEEDED

bit[6:0] – Downstream counter

RegCF[0] – CPReady set.

RegCF[1] – write ‘1’ to trigger 68029[0] as ‘1’, and need to clear immediatly.

inverse of M0

ITE Tech. INC.

-17- 2013/11/12

Page 21

IT6506 PROGRAMMING GUIDE

238 bInfo[7:0]

R/W

239 bInfo[15:0]

R/W

ITE Tech. INC.

-18- 2013/11/12

Page 22

IT6506 PROGRAMMING GUIDE

Default

00 DevNum_L

7:0 D

evice number low byte

RO 06

01 DevNum_H

7:0 Device number high byte

RO 05

02 RevNum

7:0 Revision number

RO B0

Reserved

7:4 RO

RegBankSel[1]

3

Select the register bank bit[1]

R/W 0

RegLCForce

2 Program

ming the DPCD 100

– 107 value through uP

R/W

RegEDIDWP

1 R/W 1

RegBankSel

0 S

elect the register bank bit[0]

Reserved

7:6 RO

IntGroup5

5

Group Reg0Ch Int

RO

IntGroup4

4

Group Reg0Bh Int

RO

IntGroup3

3

Group Reg0Ah Int

RO

IntGroup2

2

Group Reg09h Int

RO

IntGroup1

1

Group Reg08h Int

RO

IntGroup0

0

Group Reg07h Int

RO

LSVBIDInt

7

VBID majority error interrupt

W1C

LSNAudInt

6

NAud majority error interrupt

W1C

LSMAudInt

5 Ma

ud majority error interrupt

W1C

LSMVidInt

4 Mvid majority error interrupt

W1C

RegAFUflow

3 Audio fifo under flow

RO

RegAFOflow

2 Audio fifo over flow

RO

RegVFUflow

1

video fifo under flow

RO

RegVFOflow

0

video fifo over flow

RO

LSAudMuteEnd

7

Audio mute end interrupt

W1C

LSAudMuteS

tart 6 Audio mute start

interrupt

W1C

LSVidMuteEnd

5

Video mute end interrupt

W1C

LSVidMuteStart

4

Video mute start interrupt

W1C

AutoAudMute

3 Write 1 will gen

REGHWMuteAACClr

W1C

RefAuxURLen

2

AUX receive un

-

support length interrupt

W1C

Re

fAuxURCmd

1

AUX receive un

-

support command interrupt

W1C

RefAuxSynErr

0

AUX receive sync length error interrupt

W1C

LSNoSPDInfo

7

No SPD InfoFrame interrupt

W1C

LSNoMpegInfo

6

No Mpeg InfoFrame interrupt

W1C

LSNoAudInfo

5

No Audio InfoFrame i

nterrupt

W1C

LSNoAVIInfo

4

No AVI InfoFrame interrupt

W1C

LSL3ECCInt

3

Lane 3 (2 nibble error) ECC interrupt

W1C

LSL2ECCInt

2

Lane 2 (2 nibble error) ECC interrupt

W1C

LSL1ECCInt

1

Lane 1 (2 nibble error) ECC interrupt

W1C

LSL0ECCInt

0

Lane

0 (2 nibble error) ECC interrupt

W1C

0A RefL3SymUnLkIRQ

7

Lane 3 Symbol lose lock interrupt

W1C

Chap 9 Registers

W1C:Write 1 Clear

R1C:Read Clear

RO:Read Only

R/W:Read and Write

Note: There are two register banks in IT6506 register table, for Bank1 registers selection, the

reg0x05[0]=0. For Bank2 registers selection, the reg0x05[0]=1.

Bank 0 : reg05[3] = ‘0’, reg05[0] = ‘0’

Reg Register Name Bit Definition Type

1: enable force linktrain configuration set

05

06

07

0: disable

00: select bank 0

01: select bank 1

10: select bank 2

R/W 0

Value

08

09

ITE Tech. INC.

-19- 2013/11/12

Page 23

RefL2SymUnLkIRQ

6

Lane 2 Symbol lose lock interrupt

W1C

RefL1SymUnLkIRQ

5

Lane 1 Symbol lose lock

interrupt

W1C

RefL0SymUnLkIRQ

4

Lane 0 Symbol lose

lock interrupt

W1C

RefLnkTrnFalIRQ

3

Link Training fail interrupt

W1C

RefSymUnAlgnIRQ

2

Symbol lose alignment interrupt

W1C

RefLnkTrnDnIRQ

1

Link Training done interrupt

W1C

RefLnkTrnStrIRQ

0

Link Training start interrupt

W1C

RefAuthDnIRQ

7

Authentication done interrupt

W1C

RefAuthStartIRQ

6

Authentication start interrupt

W1C

RefLCFailIRQ

5

Link Integrity Check fail interrupt

W1C

RefRiRdyIRQ

4

R0 ready interrupt

W1C

RefAksvFailIRQ

3

Illegal Aksv interrrupt

W1C

RefHPDRstNIRQ

2

HPD Reset interrupt

W1C

RefD3EntryInt

1

DPCD 00600h[1:0] have been changed to 10 from

W1C

RefD0EntryInt

0

DPCD 00600h[1:0] have been changed to 01 from

W1C

Reserved

7 RO

RefI2CHangInt

6

I2C may hanging ( stay the s

ame state too long )

W1C

LSNewVidFormat

5

New Video format interrupt

W1C

LSNewGenPkt

4

New Mpeg InfoFrame interrupt

W1C

LSNewSPDInfo

3

New SPD InfoFrame interrupt

W1C

LSNewMpegInfo

2

New Mpeg InfoFrame interrupt

W1C

LSNewAudInfo

1

New Audio

InfoFrame interrupt

W1C

LSNewAVIInfo

0

New AVI InfoFrame interrupt

W1C

LSL32NibbleErr

7

Lane 3 ECC 2 nibble error

W1C

LSL22NibbleErr

6

Lane 2 ECC 2 nibble error

W1C

LSL12NibbleErr

5

Lane 1 ECC 2 nibble error

W1C

LSL02NibbleErr

4

Lane 0 ECC

2 nibble error

W1C

LSL31NibbleErr

3

Lane 3 ECC 1 nibble error

W1C

LSL21NibbleErr

2

Lane 2 ECC 1 nibble error

W1C

LSL11NibbleErr

1

Lane 1 ECC 1 nibble error

W1C

LSL01NibbleErr

0

Lane 0 ECC 1 nibble error

W1C

Reserved

7:6 RO

RegDEless

5 RO

RegDEover

4 RO

LSVBIDErr

3

VBID mahority error

W1C

LSNaudErr

2

Naud majority error

W1C

LSMaudErr

1

Maud majority error

W1C

LSMvidErr

0

Mvid majority error

W1C

10 RegPClkCnt

[7:0] 7:0 PCLKCnt = the tick count of PCLK under 1024T of

RO

Reserved

7:6 RO

RegAudStable

5 Audio output stable

RO

RegVidStable

4

video output stable

RO

RegPClkCnt

[11:8]

3:0 RO

Reserved

7 RO

RefHPDIRQTrg

6

Trigger HPD interrrupt

W1P

RefDDCT

rg 5 Trigger EMemory

DDC

accessing

W1P

RefAbortDDCTrg

4

Trigger

EMemory abort DDC accessing

W1P

RefRdBksvTrg

3

Trigger Bksv reading

W1P

RefSinkSpecIRQ

2 Trigger the Sink_Specific_IRQ in DPCD

W1P

RefAutoTestReq

1

Trigger

the Automated_test_request in DPCD

W1P

RefRmtCtlCmdPd

0 Trigger the remote_ctrl_cmd_pending in DPCD

W1P

RegDPCDRev

7:0 DPCD revision number

R/W 00010001

RegMaxLinkR

ate 7:0 Maximum link rate of main link lanes

R/W 00001010

IT6506 PROGRAMMING GUIDE

0B

other values

other values

0C

0D

0E

11

1F

20

21

27MHz reference clock.

PCLK = 27MHz*1024/PCLKCnt

( map to DPCD 201h[6] )

( map to DPCD 201h[1] )

( map to DPCD 201h[0] )

( setting value for DPCD 000h )

( setting value for DPCD 001h )

ITE Tech. INC.

-20- 2013/11/12

Page 24

RegNoAuxHSLT

7

0: Requires AUX CH handshake to sync.

R/W 0

RegMaxDwnSpread

6 0:

No down spread

R/W 1

RegEnhFrameCap

5

0: Enhanced framing symbol sequence disabled.

R/W 1

RegMaxLaneCnt

4:0 T

he maxi

mum number of lanes that sink device can

R/W 00100

Reserved

7

------------------------------------------

RO

RegOUISupport

6

0: OUI not supported

R/W 0

Reg8B10BSupport

5 This bit set to

1 when DP receiver support the main

R/W 1

RegFmtConv

4

0: this branch device does not have a format

R/W 0

RegDSPortType

3:2 I

ndicates the downstream port type of port 0

R/W 0

RegDSPortPret

1 Set to 1 when this device has downstream port

R/W 00

RegNORP

0

Number of rece

iver ports

R/W 1

Reg1ATPrecPort

7

0: port 1 is used for main isochronous stream

R/W 0

Reg1LEDIDPret

6

0: receiver port 1 has no local EDID

R/W 0

Reg0ATPrecPort

5

0: port 0 is used for main isochronous stream

R/W 0

Reg0LEDIDPret

4

0: receiver port 0 has no local EDID

R/W 1

RegDSPortCnt

3:0 T

he number of downstream ports

R/W 0000

25 Reg0BufSize

7:0 P

ort 0’s buffer size = ( value+1 ) * 32 Bytes/lane

R/W 00000000

26 Reg1BufSize

7:0 Port 1

’

s buffer size = ( value+1 ) * 32 Bytes/lane

R/W 0

0000000

Reserved

7:4 ------------------------------------------

RO

RegDSPort0HPD

3

0: Downstream port is not HPD aware

R/W 0

RegDSPort0Type

2:0 000: DisplayPort 001: Analog VGA

R/W 000

Reserved

7

------------------------------------------

RO

RegDSPortStChg

6

Set

to 1 when any of the downstream ports has

R/W 0

RegSinkCnt

5:0 T

otal number of the sink devices within th

is device

R/W 000000

2C RegSinkOUI

[7:0] 7:0 SINK_IEEE_OUI 7:0

R/W 00000000

2D RegSinkOUI

[15:8]

7:0 SINK_IEEE_OUI 15:8

R/W 00000000

2E RegSinkOUI

[23:16]

7:0 SINK_IEEE_OUI 23:16

R/W 00000000

Re

gI2CMasterSel

7

0: I2C request feed from Aux Channel

R/W 0

RegDebugMode

6:5 00: normal mode

R/W 00

Reg1usCntNo

4:0 C

ounter value for 1us

R/W 11011

30 RegBusHoldT

7:0 I2C Bus Hold Timer

R/W 00001000

22

IT6506 PROGRAMMING GUIDE

1: Does not require AUX CH handshake to sync.

( setting value for DPCD 003h[6] )

1: 0.5% down spread

( setting value for DPCD 003h[0] )

1: Enhanced framing symbol sequence enabled.

( setting value for DPCD 002h[7] )

support.

( setting value for DPCD 002h[4:0] )

1: OUI supported

link channel coding specification as specified in

ANSI X3.230-1994, clause 11

23

24

27

conversion block

1: this downstream port has a format conversion

block

00: Display Port

01: Analog VGA or analog video over DVI-I

10: DVI or HDMI

11: Others

1: port 1 is used for secondary isochronous stream

of main stream received in the preceding port

1: receiver port 1 has a local EDID

1: port 0 is used for secondary isochronous stream

of main stream received in the preceding port

1: receiver port 0 has a local EDID

1: Downstream port is HPD aware

010: DVI 011: HDMI

100: others without EDID support

101~111 : Reserved

2B

2F

ITE Tech. INC.

changed status

and those conneted to the downstream ports of this

device

1: I2C request feed from uP

11: simulation only mode

-21- 2013/11/12

Page 25

RegRdStretch

7

1: Stretch I2C clock after mot=0 rd

R/W 0

RegMonTxSense

6

0: Not monitor TxSense signal

R/W 1

RegRdRpyLenSel

5

0: read replay length equal to ready data length in

R/W 1

RegWrRpyLenSel

4

0: write replay length only include the length

R/W 1

RegStrClrEn

3

0: internal stretch signal cleared w

hen new request

R/W 1

RegHdrRpySel

2 0:

ACK header when receive header and the

R/W 1

RegI2CAbort

1

I2C Abort request by uP

R/W 0

RegI2CFifoClr

0

I2C FIFO Clear

R/W 0

32 RegI2CTOutSel

7:0 I2C TimeOut counter value

R/W 01000000

Reserved

7

------------------------------------------

RO

Ref_BusHang

6

I2C bus h

ang RO

Ref_Stus_ArbLose

5

I2C bus arbitration lose

RO

Ref_Stus_WaitBus

4

I2C wait bus

RO

Ref_Stus_NoACK

3

I2C no ack

RO

Ref_Stus_Done

2

I2C request done

RO

Ref_Active

1

I2C bus actived

RO

Ref_WaitBus

0

I2C in wait bus state

RO

RegI2C

EnRpStr

7

0: disable I2C repeat start

R/W 1

RegAUXINSel

6

0: delay auxin From auxrxctrl

R/W 0

RegDPCDReset

5

0: Normal

R/W 0

RegdisSelAudID

4

Disable select Audio Stream ID

R/W 0

Reg_newpkt_sel

3

New packet select

R/W 0

RegCmd_Filttap

2 Setting for I2C salve

R/W 0

RegCmd_Filttype

1 Setting for I2C salve

R/W 0

RegCmd_Deglitch

0 Setting for I2C salve

R/W 0

RegNoInfothresh

7:4 No InfoFrame threshold

R/W 1000

RegNoVideo

3 Software video mute value

R/W 0

RegNoVideoEn

2 Software video mute enable

R/W 0

RegAmute

1 Software audio mute value

R/W 0

RegAmuteEn

0 Software audio mute enable

R/W 0

RegMajor_thresh

7:5 Majority allow continuous error threshold

R/W 100

RegECC_thresh

4:2 E

rror correction allow continuous error threshold

R/W 100

RegDisECC

1 Disable secondary data RS ECC

R/W 0

RegInvFieldEn

0 Video field top signal invert enable

R/W 0

37 Reg_PktRec_type

7:0 G

eneral pack

et type select

R/W 00000000

38 RegSelAudID

7:0 Audio stream ID select

R/W 00000000

3F LSPkt_Type

[7:0] 7:0 R

eceived packet type[7:0] pulse

R1C

Reserved

7:2 ------------------------------------------

RO

LSPkt_Type

[9:8] 1:0 R

eceived packet type[9:8] pulse

R1C

41 LSAVIPktID

7:0 AVI InfoFrame packet ID

RO

42 LSAVIDataCnt

[7:0] 7:0 AVI InfoFrame data byte count[7

:0] RO

LSAVIDPV

er 7:2 AVI InfoFrame DP support version

RO

LSAVIDataCnt

[9:8] 1:0 AVI InfoFrame data byte count[9:8]

RO

44 LSAVI1PB

7:0 AVI InfoFrame packet payload byte 1

RO

45 LSAVI

2PB

7:0 AVI InfoFrame packet payload byte 2

RO

31

33

IT6506 PROGRAMMING GUIDE

1: Monitor TxSence signal

FIFO

1: read replay length equal to Tx request length

between two requests.

1: write replay length include the total bytes have

been written from the write request start

coming.

1: internal stretch signal not cleared when new

request coming.

request is not address only request.

1: Not ACK header when receive header and the

request is not address only request.

34

35

36

40

1: enable I2C repeat start

1: delay auxin From clkbuf

1: Reset DPCD FIFO

Maximum: 100

per lane

Maximum: 100

43

43

ITE Tech. INC.

-22- 2013/11/12

Page 26

46 LSAVI

3PB

7:0 AVI InfoFrame pack

et payload byte 3

RO

47 LSAVI

4PB

7:0 AVI InfoFrame packet payload byte 4

RO

48 LSAVI

5PB

7:0 AVI InfoFrame packet payload byte 5

RO

49 LSAVI

6PB

7:0 AVI InfoFrame packet payload byte 6

RO

4A LSAVI

7PB

7:0 AVI InfoFrame packet payload byte 7

RO

4B LS

AVI8PB 7:0 AVI InfoFrame packet payload byte 8

RO

4C LSAVI

9PB

7:0 AVI InfoFrame packet payload byte 9

RO

4D LSAVI1

0PB

7:0 AVI InfoFrame packet payload byte 10

RO

4E LSAVI1

1PB

7:0 AVI InfoFrame packet payload byte 11

RO

4F LSAVI

12PB

7:0 AVI InfoFram

e packet payload byte 12

RO

50 LSAVI1

3PB

7:0 AVI InfoFrame packet payload byte 13

RO

51 LSSPDPktID

7:0 SPD InfoFrame packet ID

RO

52 LSSPDDataCnt

[7:0] 7:0 SPD InfoFrame data byte count[7:0]

RO

LSSPDDPVer

7:2 SPD InfoFrame DP support version

RO

LSSPDDataCnt

[9:8] 1:0 SPD InfoFrame data byte count[9:8]

RO

54 LSSPD25PB

7:0 SPD InfoFrame packet payload byte 25

RO

55 LSAudPktID

7:0 Audio InfoFrame packet ID

RO

56 LSAudDataCnt

[7:0] 7:0 Audio InfoFrame data byte count[7:0]

RO

LSAudDPVer

7:2 Audio InfoFrame DP support version

RO

LSAudDataCnt

[9:8] 1:0 Audio InfoFrame data byte count[9:8]

RO

58 LSAud1PB

7:0 Audio InfoFrame packet payload byte 1

RO

59 LSAud

2PB

7:0 Audio InfoFrame packet payload byte 2

RO

5A LSAud

3PB

7:0 Audio InfoFrame

packet payload byte 3

RO

5B LSAud

4PB

7:0 Audio InfoFrame packet payload byte 4

RO

5C LSAud

5PB

7:0 Audio InfoFrame packet payload byte 5

RO

5D LSMpegPktID

7:0 Mpeg InfoFrame packet ID

RO

5E LSMpegDataCnt

[7:0] 7:0 Mpeg InfoFrame data byte count[7:0]

RO

LSMpegDPVer

7:2 Mpeg InfoFrame DP support version

RO

LSMpegDataCnt

[9:8] 1:0 Mpeg InfoFrame data byte count[9:8]

RO

60 LSMpeg1PB

7:0 Mpeg InfoFrame packet payload byte 1

RO

61 LSMpeg

2PB

7:0 Mpeg InfoFrame packet payload byte 2

RO

62 LSMpeg

3PB

7:0 Mpeg InfoFrame packet payload byte 3

RO

63 LSMpeg

4PB

7:0 Mpeg InfoFrame packet payload byte 4

RO

64 LSMpeg

5PB

7:0 Mpeg InfoFrame packet payload byte 5

RO

65 LSGenPkt_0HB

7:0 General packet header byte 0

RO

66 LSGenPkt_1HB

7:0 General packet

header byte 1

RO

67 LSGenPkt_

2HB

7:0 General packet header byte 2

RO

68 LSGenPkt_

3HB

7:0 General packet header byte 3

RO

69 LSGenPkt_0pb

7:0 General packet payload byte 0

RO

6A LSGenPkt_

1pb

7:0 General packet payload byte 1

RO

6B LSGenPkt_

2pb

7:0 General packet payload byte 2

RO

6C LSGenPkt_

3pb

7:0 General packet payload byte 3

RO

6D LSGenPkt_

4pb

7:0 General packet payload byte 4

RO

6E LSGenPkt_

5pb

7:0 General packet payload byte 5

RO

6F LSGenPkt_

6pb

7:0 General packet payload byte 6

RO

70 LSGenPkt_

7pb

7:0 General packet payload byte 7

RO

71 LSGenPkt_

8pb

7:0 General packet payload byte 8

RO

72 LSGenPkt_

9pb

7:0 General packet payload byte 9

RO

73 LSGenPkt_

1

0pb 7:0 General packet payload byte 10

RO

74 LSGenPkt_

11pb

7:0 General packe

t payload byte 11

RO

75 LSGenPkt_

12pb

7:0 General packet payload byte 12

RO

76 LSGenPkt_

13pb

7:0 General packet payload byte 13

RO

77 LSGenPkt_

14pb

7:0 General packet payload byte 14

RO

78 LSGenPkt_

15pb

7:0 General packet payload byte 15

RO

79 LS

GenPkt_

16pb

7:0 General packet payload byte 16

RO

7A LSGenPkt_

17pb

7:0 General packet payload byte 17

RO

7B LSGenPkt_

18pb

7:0 General packet payload byte 18

RO

7C LSGenPkt_

19pb

7:0 General packet payload byte 19

RO

7D LSGenPkt_

2

0pb 7:0 General pack

et payload byte 20

RO

7E LSGenPkt_

21pb

7:0 General packet payload byte 21

RO

7F LSGenPkt_

22pb

7:0 General packet payload byte 22

RO

80 LSGenPkt_

23pb

7:0 General packet payload byte 23

RO

IT6506 PROGRAMMING GUIDE

53

57

5F

ITE Tech. INC.

-23- 2013/11/12

Page 27

81 LSGenPkt_

24pb

7:0 General packet payload byte 24

RO

82 L

SGenPkt_

25pb

7:0 General packet payload byte 25

RO

83 LSGenPkt_

26pb

7:0 General packet payload byte 26

RO

84 LSGenPkt_

27pb

7:0 General packet payload byte 27

RO

85 LSAudTStpPktID

7:0 Audio time stamp packet ID

RO

86 LSAudTStpDCnt

[7:0] 7:0 Audio tim

e stamp data byte count[7:0]

RO

LSAudTStpDPVer

7:2 A

udio time stamp DP support version

RO

LSAudTStpDCnt

[9:8] 1:0 Audio time stamp data byte count[9:8]

RO

88 LSAudStrID

7:0 Audio stream packet ID

RO

Reserved

7

--------------------------------

----------

RO

LSAudStrCType

6:3 Audio stream coding type

RO

LSAudStrChCnt

2:0 Audio stream channel count

RO

LSMVid

[7:0] 7:0 Mvid value[7:0] ( don

’

t care if novideo or video not

RO

8B LSMVid

[15:8]

7:0 Mvid value[15:8]

RO

8C LSMVid

[23:

16] 7:0 Mvid value[23:16]

RO

LSNVid

[7:0] 7:0 Nvid value[7:0] ( don

’

t care if novideo or vide not

RO

8E LSNVid

[15:8]

7:0 Nvid value[15:8]

RO

8F LSNVid

[23:16]

7:0 Nvid value[23:16]

RO

90 LSMaud

[7:0] 7:0 Maud value[7:0] ( don

’

t care if audm

ute ) RO

91 LSMaud

[15:8]

7:0 Maud value[15:8]

RO

92 LSMaud

[23:16]

7:0 Maud value[23:16]

RO

93 LSNaud

[7:0] 7:0 Naud value[7:0] ( don

’

t care if audmute )

RO

94 LSNaud

[15:8]

7:0 Naud value[15:8]

RO

95 LSNaud

[23:16]

7:0 Naud value[23:16]

RO

LSAu

dID 7:0 Audio stream real

-

time ID, include :

RO

97 LSHTotal

[7:0] 7:0 H total [7:0]

RO

98 LSHTotal

[15:8]

7:0 H total [15:8]

RO

LSHStart

[7:0] 7:0 H start [7:0] from Hsync start edge to H active

start

RO

LSHStart

[15:8]

7:0 H start [15:8] from Hsync start edge to H active

RO

9B LSHWidth

[7:0] 7:0 M

ain stream attribute data

- H active width [7:0]

RO

9C LSHWidth

[15:8]

7:0 M

ain stream attribute data

-

H active width [15:8]

RO

9D LSVTotal

[7:0] 7:0 M

ain stream attribute data

-

V total [7:0]

RO

9E LSVTotal

[15:8]

7:0 M

ain stream attribute data

-

V total [15:8]

RO

LSVStart

[7:0] 7:0 M

ain stream attribute data

-

V start [7:0] from Vsync

RO

L

SVStart

[15:8]

7:0 M

ain stream attribute data

-

V start [15:8] from

RO

A1 LSVHeight

[7:0] 7:0 M

ain stream attribute data

-

V active height [7:0]

RO

A2 LSVHeight

[15:8]

7:0 M

ain stream attribute data

-

V active height [

15:8] RO

A3 LSHSyncWidth

[7:0] 7:0 M

ain stream attribute data

-

H Sync Width [7:0]

RO

LSHSyncPolarity

7 Main stream attribute data

-

H Sync polarity

RO

LSHSyncWidth

[14:8]

6:0 M

ain stream attribute data

-

H Sync Width[14:8]

RO

A5 LSVSyncWidth

7:0 Main stream attribute data

-

V Sync Width [7:0]

RO

LSVSyncPolarity

7 Main stream attribute data

-

VSync polarity

RO

LSVSyncWidth

6:0 M

ain stream attribute data

-

V Sync Width[14:8

] RO

LSVdBPC

7:5 M

ain stream attribute data

-Bit depth per color /

RO

LSVdYUVColor

4 Main stream attribute data

-

YCbCr Colorietry

RO

IT6506 PROGRAMMING GUIDE

87

89

8A

8D

96

99

9A

9F

A0

ready )

ready )

Audio InfoFrame

Audio time stamp

Audio stream

edge

start edge

start edge to V active start edge

Vsync start edge to V active start edge

A4

A6

A7

ITE Tech. INC.

component

000 = 6 bits

001 = 8 bits

010 = 10 bits

011 = 12 bits

100 = 16 bits

101, 110, 111 = Reserved

0: ITU-R BT601-5

1: ITU-R BT709-5

-24- 2013/11/12

Page 28

LSVdRange

3 Main stream attribute data

-

Dynamic r

ange

RO

LSVdPxlFormat

2:1 M

ain stream attribute data

-Component format

RO

LSCLKSync

0 Main stream attribute data

-

Synchronous clock

RO

Reserved

7:3 ------------------------------------------

RO

LSStereoVdAttr

2:1 M

ain stream attribute data

-

Stereo video attribute

RO

LSVdIFrameEven

0 Main stream attribute data

-

Interlaced vertical total

RO

viditemcomp

7 Video format 5 attribute data compare bit

-

debug

RO

LSdiffVidFormat

6 Video main stream attribute data change

RO

LSHDCPSyncDet

5

HDCP SYNC DETECT

RO

LSAudMute

4

AudioMute_Flag

RO

LSNoVideo

3

NoVide

oStream_Flag

RO

LSVdFrameMd

2

Interlace_Flag

RO

LSVdFieldTop

1

FieldID_Flag

RO

LSVBlank

0

VerticalBlanking_Flag

RO

B0 RegOtpCtrl

7:0 Otp encryption word selection for EMemory data

R/W 00101010

B1 RegOtpXor

7:0 Otp XOR value for EMemory data

R/W 10100101

RegEMemWeakRd

7

EMemory weak read

R/W 1

RegEMemRWEn

6

EMemory Read/Write enable

R/W 1

RegMasterSel

5

EMemory control master selection.

R/W 0

RegROMBIST

4

ROM BIST enable

R/W 0

RegEnEMem

3

EMemory enable

R/W 1

RegPwrOnRdBksv

2

Automatically read Bksv when system power on

R/W 1

RegDisDecryp

1

HDCP decryption disable

R/W 0

RegCPDesired

0

HDCP enable

R/W 0

RegDDCReq

7:4 Ememory DDC request command type.

R/W 0000

RegEMemLoad

3:0 EMemory load bit number.

R/W 0010

RegDDCHeader

7:0 Emem

ory DDC Header.

R/W 00000000

B5 RegDDCReqOffset

7:0 EMemory DDC Read Offset address.

R/W 00000000

B6 RegDDCRe

q

Byte 7:0 EMemory DDC request Byte Number.

R/W 00000000

RegCRSymLockMax

7:0 Max number of locked symbol for Clock Recovery.

R/W 01000000

A8

IT6506 PROGRAMMING GUIDE

0: VESA range ( from 0 to the maximum )

1: CEA range

00: RGB

01: YCbCr 4:2:2

10: YCbCr 4:4:4

11: Reserved

0: Link clock and stream clock asynchronous

1: Link clock and stream clock synchronous

00: No stereo video transported

01: for progressive vide, the next frame is RIGHT

eye, for interlaced video, TOP field is RIGHT eye

and BOTTOM field is LEFT eye

10: reserved and must not be used

11: for progressive video, the next frame is LEFT

eye, for interlaced video, TOP field is LEFT eye and

BOTTOM field is RIGHT eye

even

0: number of lines per interlaced frame ( consisting

of two fields ) is an odd number

1: number of lines per interlaced frame ( consisting

of two fields ) is an even number

A9

B2

B3

B4

0: HDCP circuit.

1: Register control. (RegB3[7:4]~RegB6)

(BIST function is not implemented,

this bit is useless)

0000: DDC request is valid.

Others: invalid.

This setting extends the write enable pulse width

for Ememory write.

Unit: 1T I2C CLK.

11100000: EMemory DDC Read Bank0.

11100010: EMemory DDC Read Bank1.

Others: invalid.

B7

ITE Tech. INC.

Note: Due to the double size of bus width, the

-25- 2013/11/12

Page 29

IT6506 PROGRAMMING GUIDE

actual value is equal to the setting * 2.

RegCRSymLockMin

7:0 Min number of locked symbol for Clock Recovery.

R/W 00100000

RegEQSymLockMax

7:0 Max number of locked symbol for Channel

R/W

01000000

RegEQSymLockMin

7:0 Min number of locked symbol for Channel

R/W 00100000

RegCRTimer

[7:0] 7:0 CR timeout Timer [7:0]

R/W 10100100

RegEQTimer

[7:0] 7:0 EQ timeout Timer [7:0]

R/W 10100000

RegSymLockMax

7:6 Max number of symbol lock for decreasing the

R/W 00

RegDisTxSense

5

Disable 1.1a Tx Sense function

R/W 0

RegEnLaneSwp 4 Enable lane swap

R/W 0

RegEQTimer

[10:8]

3:1 EQ timeout Timer [10:

8] R/W 001

RegCRTimer

[8] 0 CR timeout Timer [8]

R/W 0

RegEQFalCRMax

7:4 Max number of lost lock symbol in EQ phase

.

R/W 0000

RegSymUnLockMax

3:0 Max number of lost lock symbol in normal operation

R/W 0000

RegCDRSel

7

AFE configuration value selection for Clock

R/W 1

Reserved

6 R/W 0

RegSymAlignMax

5:4 Max

number of

symbol alignment

for decreasing

R/W 00

RegSymUnAlgnMax

3:0 Max number of lost symbol alignment in normal

R/W 0001

RegHPDIrqPeriod

[7:0] 7:0 HPD Interrupt pulse period [7:0].

R/W 10001010

RegHPDIrqPeriod

[15:8]

7:0 HPD Interrupt period [15:8]

R/W 01011010

B8

B9

BA

BB

BC

BD

C0

Note: Due to the double size of bus width, the

actual value is equal to the setting * 2.

Equalization.

Note: Due to the double size of bus width, the

actual value is equal to the setting * 2.

Equalization.

Note: Due to the double size of bus width, the

actual value is equal to the setting * 2.

Unit: 1 LSCLK period

The number of the valid CR symbol must reach

RegCRSymLockMax within this time period.

Unit: 1 LSCLK period

The number of the valid EQ symbol must reach

RegCRSymLockMax within this time period.

number of lose symbol lock

If the number of lost lock symbol exceeds this

setting, CR_DONE in DPCD will be cleared.

Unit: 16 times.

Default value 0000 = 16 times.

(after a successful Link Training).

If the number of lost lock symbol exceeds this

setting, CR_DONE, CHANNEL_EQ_DONE and

SYMBOL _LOCKED in DPCD will be cleared.

Unit: 16 times.

Default value 0000 = 16 times.

C1

C2

C3

ITE Tech. INC.

Recovery

1: analog CDR, 0:digital CDR

the number of lost symbol alignment in normal

operation (after a successful Link Training).

When the number of symbol alignment reaches this

setting, subtract 1 from the number of lost symbol

alignment.

00: 2^10

01: 2^12

10: 2^14

11: 2^16

operation (after a successful Link Training).

If the number of lost symbol alignment exceeds this

setting, LANE_ALIGN_STATUS_UPDATED in DPCD

will be cleared.

Unit: 1 time.

Default value 0001 = 1 time.

RegHPDIrqPeriod[11:0] is the time base.

Unit: 37.04ns

Default value 101010001010 is 100us.

RegHPDIrqPeriod[15:12] is the time counter.

-26- 2013/11/12

Page 30

Unit: time base defined in [11:0]

Reserved

7:6 ------------------------------------------

RegLnkTrnFail

5

Link Training fail status

RO

RegTxSense

4

Tx Sense status

RO

RegTxPwrSense

3

Tx power is on

RO

RegTxConnected

2

Tx is connected

RO

RegLnkTrnDn

1

Link Training done s

tatus RO

RegLnkTrnBusy

0

Link Training busy status

RO

RegEnLaneNo

7:6 Lane

enable

in PHY test

R/W 00

RegEnPHYTest

5

Enable PHY test

R/W 0

RegEnHPDOut

4

Enable HPD output

R.W 0

RegEnCRWait

3

Enable wait

function in CR

R/W 0

RegEnEQOpt

2

Enable optimization in EQ

R/W 0

RegEnCROpt

1

Enable optimization in CR

R/W 0

RegAutoDSkwEn

0

Enable inter

-

lane and H/L byte De

-

Skew R/W 0

RegCRTimeBase[3:0]

7:4 Time base for CR wait function.

R/W 1000

RegCRWaitCnt

3:0 Time counter for CR wait function

R/W 0001

RegCRTimeBase[11:4]

7:0 Time base f

or CR wait function.

R/W 10101110

RegSetLnkStUpd

7

Force LINK_STATUS_UPDATED in DPCD

R/W 0

RegDBounceTime

6:3 Tx sense and Tx connected de

-

bounce time

R/W 0000

RegDisTrnVELmt

2

Disable Link Training 1.2V limitation

R/W 0

RegEnEQTimer

1

Enable EQ timeout timer

R/W 0

RegEnCRTimer

0

Enable CR timeout timer

R/W 0

RegSetRepeater

2

Enable HDCP repeater function

R/W 0

RegForceVReady

1

Force V

’ Ready in DPCD

R/W 0

RegForceCPRdy

0

Force CP Ready in DPCD

R/W 0

D0

7:0

R/W 00000101

7:4

R/W 0000

3 R/W 1

2:0

R/W 000

7:6

R/W 00

5 R/W 0

RegAttrSet

4

Set main stream attribute from

RegD3 ~ RegE2

R/W 0

3 R/W 0

2 R/W 0

1:0

R/W 00

D3 RegHWidth

[7:0] 7:0 H active width [7:0]

R/W 00000000

D4 RegHWidth

[15:8]

7:0 H active width [15:8]

R/W 00000000

D5 RegHTotal

[7:0] 7:0 H total [7:0]