Page 1

®

www.BDTIC.com/Intersil

ISL97632

Data Sheet February 22, 2008

White LED Driver with Digital Dimming

The ISL97632 represents an efficient and highly integrated

PWM boost LED driver that is suitable for 1.8” to 3.5” LCDs

that employ 2 to 6 white LEDs for backligh ti n g. With

integrated Schottky diode, OVP, and dynamic digital

dimming capability , the ISL97632 provides a simple, reliable,

and flexible solution to the backlight designers.

The ISL97632 features a simple single-wire digital interface

that provides a 5-bit dimming control. The dimming signal

adjusts the FB voltage and therefore the LED brightness in a

DC manner in 32 linear steps. An EN pin can be used to

provide a zero brightness setting or shutdown power saving

function.

The ISL97632 is available in the 8 Ld TDFN (2mmx3mm)

package. There are 14V , 18V, and 26V OVP options that are

suitable for 3, 4, and 6 LEDs backlight applications

respectively. The ISL97632 is specified for operation over

the -40°C to +85°C ambient temperature at input voltage

from 2.4V to 5.5V.

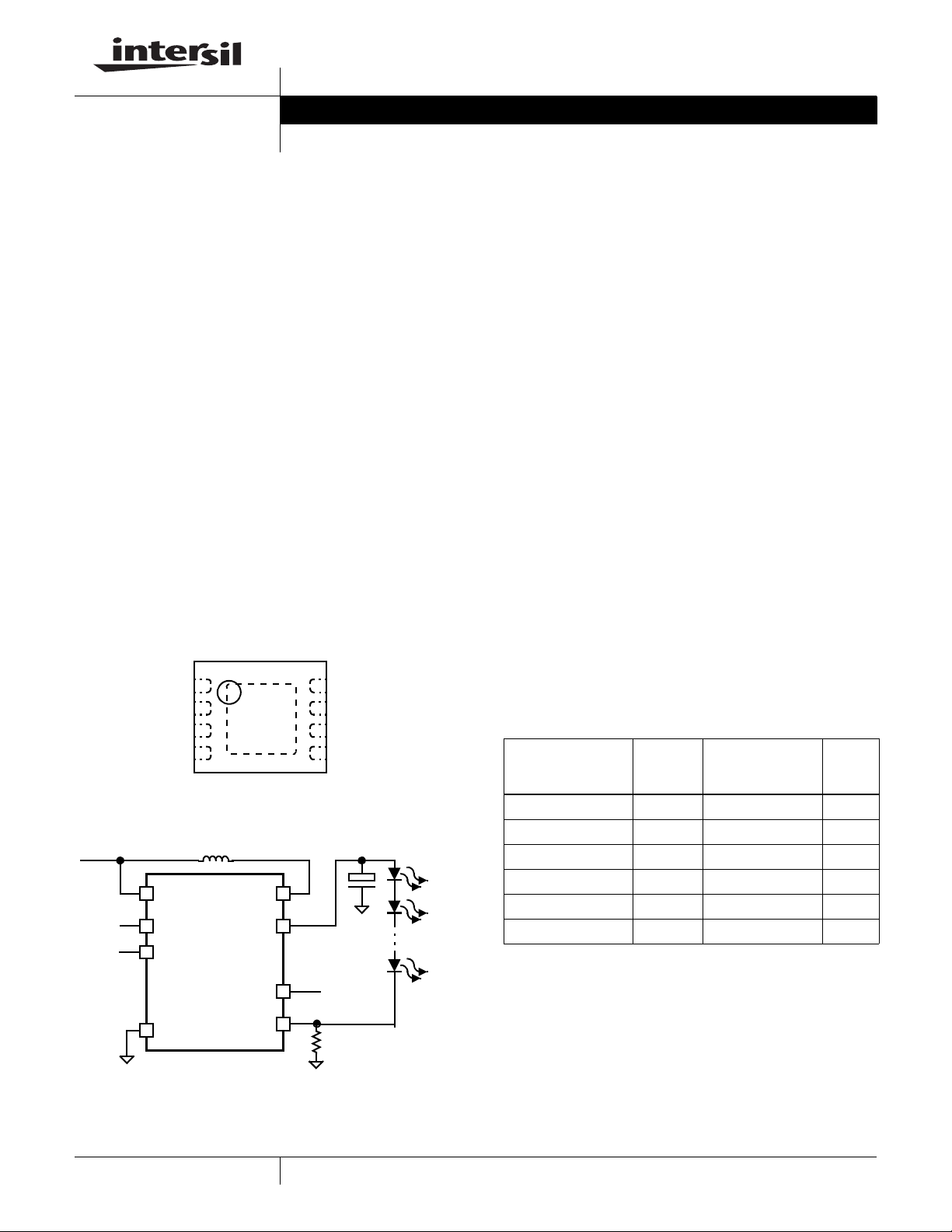

Pinout

ISL97632

(8 LD 2x3 TDFN)

TOP VIEW

GND

VIN

EN

SDIN

1

2

3

4

LX

8

VOUT

7

FBSW

6

FB

5

Typical Application Circuit

VIN

EN

SDIN

GND

10µH or 22µH

LX

VOUT

FBSW

FB

VIN

FN9239.3

Features

• 5-Bit Digital Dimming Control

• Drives up to 6 LEDs in Series

• OVP (14V , 18V and 26V for 3, 4, and 6 LEDs applications)

• Integrated Schottky Diode

• 2.4V to 5.5V input

• 86% Efficiency

• 1.4MHz Switching Frequency Allows Small LC

• Enable for Shutdown Function or Zero Brightness Setting

• 1µA Shutdown Current

• Internally Compensated

• 8 Ld TDFN (2mmx3mm)

• Pb-Free (RoHS Compliant)

Applications

• LED backlighting for

- Cell phones

- Smartphones

-MP3

-PMP

- Automotive Navigation Panel

- Portable GPS

Ordering Information

PACKAGE

PART NUMBER

(Note)

ISL97632IRT14Z-T* ELB 8 Ld 2x3 TDFN L8.2x3A

ISL97632IRT14Z-TK* ELB 8 Ld 2x3 TDFN L8.2x3A

ISL97632IRT18Z-T* ELC 8 Ld 2x3 TDFN L8.2x3A

ISL97632IRT18Z-TK* ELC 8 Ld 2x3 TDFN L8.2x3A

ISL97632IRT26Z-T* ELD 8 Ld 2x3 TDFN L8.2x3A

ISL97632IRT26Z-TK* ELD 8 Ld 2x3 TDFN L8.2x3A

*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ

special Pb-free material sets; molding compounds/die attach

materials and 100% matte tin plate PLUS ANNEAL - e3 termination

finish, which is RoHS compliant and compatible with both SnPb and

Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/JEDEC J STD-020.

PART

MARKING

TAPE AND REEL

(Pb-Free)

PKG.

DWG.#

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2006-2008. All Rights Reserved

Page 2

ISL97632

www.BDTIC.com/Intersil

Absolute Maximum Ratings (T

Input Voltage (V

LX Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to 28V

FBSW Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to 28V

All Other Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to 6V

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to 6V

IN

= +25°C) Thermal Information

A

Thermal Resistance (Typical, Note 1) θ

TDFN Package (Notes 1, 2). . . . . . . . . 70 10.5

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . .+125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Lead Temperature (S oldering 10s) . . . . . . . . . . . . . . . . . . . .+300°C

(°C/W) θJC (°C/W)

JA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed over temperature of -40°C to +85°C unless otherwise stated. Typical va lues are for

information purposes only at TJ = TC = TA = +25°C.

NOTE:

1. θ

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

JA

Tech Brief TB379.

2. For θ

Electrical Specifications V

PARAMETER DESCRIPTION CONDITION MIN TYP MAX UNIT

R

t

LOGIC-LOAD

t

LOGIC-HIGH

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

= VEN = 3V

IN

V

IN

I

IN

Fsw Switching Frequency 1,300 1,450 1,600 kHz

DMAX Maximum Duty Cycle 90 95 %

I

LIM

R

SW(LX)

ILEAK LX Switch Leakage Current VLX = 28V 1 μA

VFB Feedback Voltage Serial interface setting = 15 (center) 90 95 100 mV

IFB FB Pin Bias Current VFB = 95mV 1 μA

SW(FBSW)

V

DIODE

OVP Overvoltage Protection ISL97632IRT14Z 14 V

VIL Logic Low Voltage 0.6 V

VIH Logic High Voltage 1.5 V

t

LOGIC

t

LOGIC

Supply Voltage 2.4 5.5 V

Supply Current EN = 3V, enabled, not switching 0.8 1.5 mA

EN = 0V, disabled 1 μA

LX Current 400 470 mA

LX Switch ON-Resistance ILX = 100mA 900 mΩ

Serial interface setting = S (S = 0,1..31) 9.8 + 5.68 x S mV

Serial interface setting = 0

FBSW Switch ON-Resistance 10 Ω

Schottky Diode Forward

Voltage

1 Timing Range for Logic 1 SDIN = low 15 45 μs

0 Timing Range for Logic 0 SDIN = low 90 120 μs

Timing Range for Load SDIN = low 215 μs

Minimum Valid SDIN High

Time

IDIODE = 100mA, TA = +25°C 600 850 mV

ISL97632IRT18Z 18 V

ISL97632IRT26Z 26 28 V

SDIN = high 3 μs

9.8 mV

2

FN9239.3

February 22, 2008

Page 3

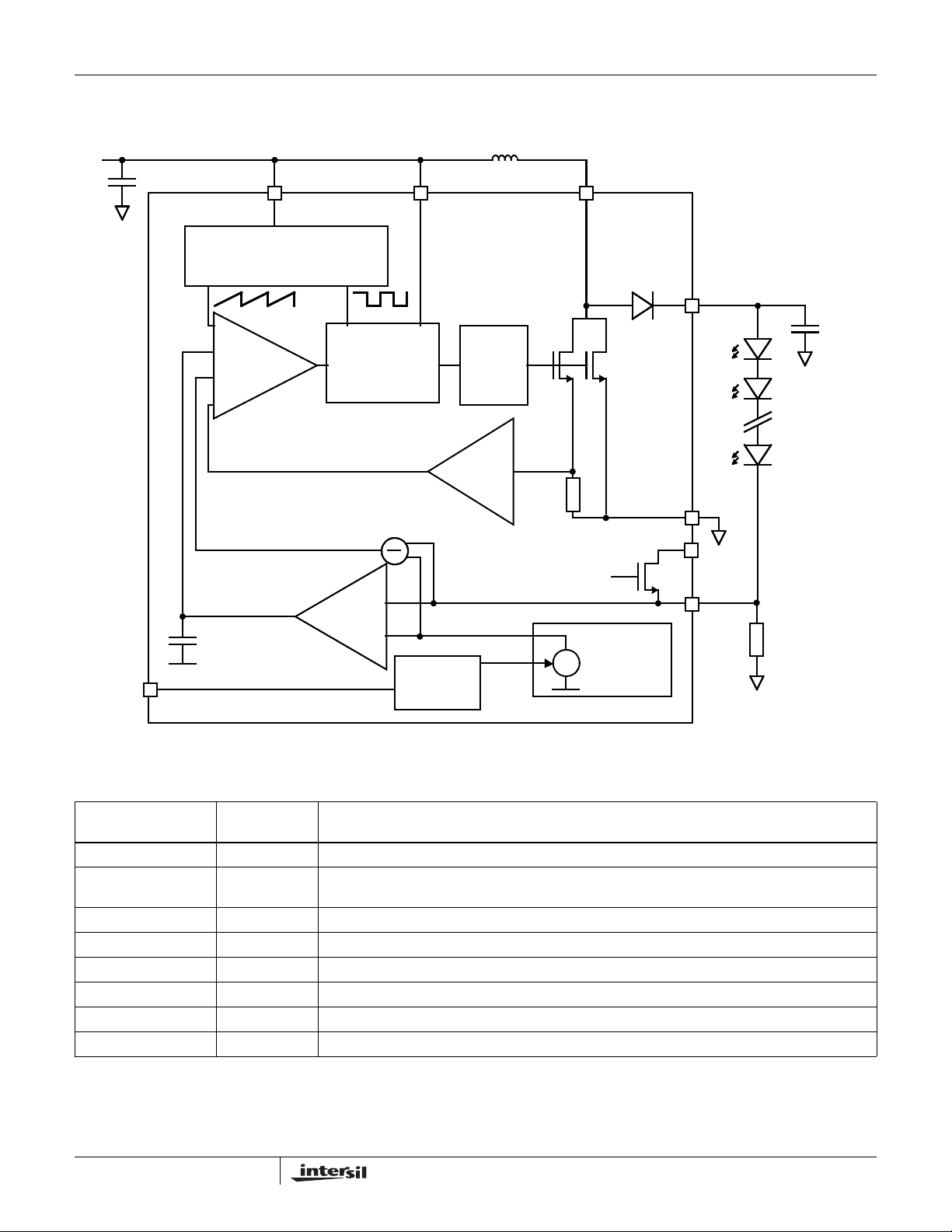

Block Diagram

www.BDTIC.com/Intersil

VIN (2.4V to 5.5V)

CIN

ISL97632

L

VIN EN LX

1.4MHZ OSCILLATOR AND RAMP

GENERATOR

PWM

COMPARATOR

GM AMP

COMPENSATION

SDIN

PWM LOGIC

CONTROLLER

GM

AMPLIFIER

CURRENT

10 - 186mV

SERIAL

INTERFACE

ISL97632

FET

DRIVER

SENSE

EN

BANDGAP

REFERENCE

GENERATOR

V

OUT

GND

FBSW

FB

2 to 6 LEDs

RSET

C

OUT

Pin Descriptions

PIN

NUMBER

1 GND Ground Pin. Connect to local ground.

2 VIN Input Supply Pin. Connect to the input supply voltag e, t he ind uctor a nd t he inp ut sup ply decoup ling

3 EN Enable Pin. Connect to enable signal to turn-on or off the device. Active High.

4 SDIN Single-Wire XSD Digital Interface.

5 FB Feedback Pin. Connect to the cathode of bottom LED and the sense resistor.

6 FBSW Optional FB Disconnect Switch.

7 VOUT Output Pin. Connect to the ano de o f t he t op L ED and t he o utpu t f ilte r ca pacitor.

8 LX Switching Pin. Connect to inductor.

PIN

NAME DESCRIPTION

capacitor.

3

FN9239.3

February 22, 2008

Page 4

Single-Wire Serial Interface

www.BDTIC.com/Intersil

30µs 100µs 220µs

'1' '0' '1' '0' '0' 'LOAD'

0 200 400 600 800 1000 1200 µs

FIGURE 1. SINGLE-WIRE XSD INTERFACE

The ISL97632 uses a simple single-wire serial interface for

programming the output brightness of the LEDs. A 5-bit

interface is used to give a total of 32 levels of output

brightness. The interface uses a normally high connection

for use with open-drain driving schemes and Intersil’s

proprietary XSD bus. When held low for between 15µs and

45µs, the interface registers a logic 1. When held low for

between 90µs and 120µs the interface registers a logic 0.

When held low for greater tha t 215µs, the i nterface load s the

last 5 bits into the brightness control register and updates

the brightness level. The required minimu m high time is 3µs.

This simple single-wire programming is summarized as

follow:

ISL97632

• Logic 0 = Negative pulse >90µs and <120µs

• Logic 1 = Negative pulse >15µs and <45µs

• Load = Negative pulse >215µs

Figure 1 shows an example of programming a binary code of

10100 and load it in to the device serial register.

The serial interface is automatically reset to 0 when the

device is disabled, or enters UVLO. Therefore, when the part

is enabled, the output brightness is automatically set to the

minimum level.

4

FN9239.3

February 22, 2008

Page 5

Typical Performace Curves

www.BDTIC.com/Intersil

ISL97632

90

4.2V IN 4 LEDs OUT (15µH)

85

80

75

70

65

EFFICIENCY (%)

60

55

50

3.6V IN 4 LEDs OUT (15µH)

4.2V IN 4 LEDs OUT (22µH)

3.6V IN 4 LEDs OUT (22µH)

0 5 10 15 20 25 30 35 40 45

3.6V IN 4 LEDs OUT (10µH)

4.2V IN 4 LEDs OUT (10µH)

I

(mA)

OUT

FIGURE 2. EFFICIENCY vs LED CURRENT FIGURE 3. QUIESCENT CURRENT vs VIN (ENAB = HI)

20.08

20.04

20.00

(mA)

O

I

19.96

19.92

0 5 10 15 20 25 30

FIGURE 4. LOAD REGULATION (V

V

OUT

(V)

= 4V) FIGURE 5. LINE REGULATION

IN

1.0

0.8

0.6

0.4

Iq (mA)

0.2

0

- 0.2

0

19.76

19.74

19.72

19.70

(mA)

O

19.68

I

19.66

19.64

19.62

2.53.03.54.04.55.05.5

1234 5

V

(V)

IN

V

(V)

IN

40

R

35

30

25

20

(mA)

O

I

15

10

5

0

= 4.7Ω

SET

0 5 10 15 20 25 30 35

CODE = DECIMAL

FIGURE 6. ILED vs PROGRAMMING CODES

5

FN9239.3

February 22, 2008

Page 6

ISL97632

www.BDTIC.com/Intersil

Detailed Description

The ISL97632 uses a constant frequency, current mode

control scheme to provide excellent line and load regulation.

There are three OVP models for driving 3, 4, and 6 LEDs and

their OVP thresholds

respectively . The ISL97632 ope rate s from a n input volt ag e of

2.4V to 5.5V and ambient temperature from -40°C to +85°C.

The switching frequency is around 1.45MHz and allows the

driver circuit to employ small LC components. The forward

current of the LED is set using the R

state mode, the LED current is given by Equation 1:

V

FB

--------------------

I

LED

==

S()

R

where S is the 5-bit Serial Interface Setting or Digital code

from 0 to 31 programmed in the XSD single-wire interface.

The default setting is 0 and the VFB is at minimum.

Dimming Cont rol

The ISL97632 powers up to provide minimium current. By

programming the digital code with the Intersil’s XSD singlewire interface as shown in Figure 1, the current can be

changed linearly with the digital code from 0 to 31. Figure 6

shows LED current versus the programming codes.

Overvoltage Protection

The ISL97632 comes with overvoltage protection. The

OVP trip points are at 14V, 18V, and 26V for

ISL97632IRT14Z, ISL97632IRT18Z, and

ISL97632IRT26Z respectively. The maximum numbers of

LEDs and OVP threshold are shown in Table 1. When the

device reaches the OVP, the LX stops switching, disabling

the boost circuit until V

threshold. At this point, LX will be allowed t o switch agai n.

The OVP event will not cause the device to shutdown

PART NO. OVP

ISL97632IRT14Z 14V 3 70mA

ISL97632IRT18Z 18V 4 50mA

ISL97632IRT26Z 26V 6 30mA

There are three OVP options so that the 3 LEDs

application should use the 14V OVP device and the 6 LEDs

application should use the 26V OVP device. An output

capacitor that is only rated for the required voltage range can

therefore be used which will optimize the component costs in

some cases.

Shut-Down

An active high EN pin is normally on but this pin can be used

as a shutdown power saving function or zero brightness

setting. When taken low the EN pin places the ISL97632 into

power down mode down where the supply current is

reduced to less than 1µA. The EN pin cannot be used as

PWM input as the part resets to 0 whenever EN is low. To

are set at 14V, 18V, and 26V

S()

9.8mV 5.68mV S×+

--------------------------------------------------------

SET

R

SET

falls about 7% below the OVP

OUT

TABLE 1.

MAX NO. OF

resistor. In the steady

SET

(EQ. 1)

LEDS MAX ILED

resume previous setting, the device needs to be

reprogrammed.

Output Disconnect

The ISL97632 features a FBSW feedback disconnect switch

that can be used in between the LED and Rset for an

optional short-circuit protection. For example, the user may

build an external short circuit detection to monitor the V

If the V

goes low due to one or more LEDs which are

OUT

OUT

shorted, the circuit can release the EN and FBSW switch to

disconnect the LEDs.

Components Selection

The input capacitance is typically 0.22µF to 4.7µF. The

output capacitor should be in the range of 0.22µF to 1µF.

X5R or X7R type of ceramic capacitors of the appropriate

voltage rating are recommended.

When choosing an inductor, make sure the average and

peak current ratings are adequate by using the following

equations (80% efficiency assumed):

I

LAVG

I

LPKILAVG

V

INVOUTVIN

---------------------------------------------------

Δ

=

I

L

⋅⋅

LV

⋅

0.8 V

IN

1

-- -

2

–()⋅

OUTfOSC

Δ⋅+=

I

L

(EQ. 2)

(EQ. 3)

(EQ. 4)

I

⋅

LEDVOUT

---------------------------------

=

Where:

• ΔI

is the peak-to-peak inductor current ripple in Amps

L

• L is the inductance in H.

is the switching frequency, typically 1.45MHz

•f

OSC

The ISL97632 supports a wide range of inductance values

(10µH~82µH). For lower inductor values or lighter loads, the

boost inductor current may become discontinuous. For high

boost inductor values, the boost inductor current will be in

continuous mode.

In addition to the inductor value and switching frequency, the

input voltage, the number of LEDs and the LED current also

affect whether the converter operates in continuous

conduction or discontinuous conduction mode. Both operating

modes are allowed and normal. The discontinuos conduction

mode yields lower efficiency due to higher peak current.

Compensation

The product of the output capacitor and the load create a

pole while the inductor creates a right half plane zero. Both

attributes degrade the phase margin but the ISL97632 has

an internal compensation network that ensures the device

operates reliabily under the specified conditions. The

internal compensation and the highly integrated functions of

the ISL97632 make it a design friendly device to be used in

high volume high reliability applications.

.

6

FN9239.3

February 22, 2008

Page 7

ISL97632

www.BDTIC.com/Intersil

Applications

Efficiency Improvement

Figure 2 shows the efficiency measurements. The choice of

the inductor has a significant impact on the power efficiency.

As shown in Equation 4, the higher the inductance, the lower

the peak current therefore the lower the conduction and

switching losses. On the other hand, it has also a higher

series resistance. Nevertheless, the efficiency improvement

from lowering the peak current is greater than the impact of

the resistance increase with larger value of inductor.

Efficiency can also be improved for systems that have high

supply voltages. Since the ISL97632 can only supply from

2.4V to 5.5V, V

voltage for the boost circuit as shown in Figure 7 and the

efficiency improvement is shown in Figure 8.

Vs = 12V

C1

1µ

V

= 2.7V TO 5.5V

IN

0.1µ

C2

FIGURE 7. SEPERATE HIGH INPUT VOL TAGE FOR HIGHER

90

85

80

75

EFFICIENCY (%)

70

FIGURE 8. EFFICIENCY IMPROVEMENT WITH 9V AND 12V

8 LEDs Operation

For medium size LCDs that need more than 6 low power

LEDs for backlighting, such as a Portable Media Player or

Automotive Navigation Panel displays, the voltage range of

the ISL97632 is not sufficient. However, the ISL97632 can

be used as an LED controller with an external protection

must be seperated from the high supply

IN

C3

L1

1 2

22µ

VIN

ISL97632

EN

SDIN

EFFICIENCY OPERATION

VS = 12V

0

5101520

INPUTS

LX

VOUT

FBSW

FB

GND

VS = 9V

ILED (mA)

0.22µ

R1

VIN = 4V

6 LEDs

L1 = 22µH

R1 = 4Ω

25 30

4Ω

D1

D2

D3

D4

D5

D6

25mA

MOSFET connected in cascode fashion to achieve higher

output voltage. A conceptual 8 LEDs driver circuit is shown

in Figure 9. A 60V logic level N-Channel MOSFET is

configured such that its drain ties between the inductor and

the anode of schottky diode, its gate ties to the input, and its

source ties to the ISL97632 LX node connecting to the drain

of the internal switch. When the interna l sw it ch turns on, it

pulls the source of M1 down to ground, and LX conducts as

normal. When the internal switch turns off, the source of M1

will be pulled up by the follower action of M1, limiting the

maximum voltage on the ISL97632 LX pin to below Vin, but

allowing the output voltage to go much higher than the

breakdown limit on the LX pin. The switch current limit and

maximum duty cycle will not be changed by this setup, so

input voltage will need to be carefully considered to make

sure that the required output voltage and current levels are

achievable. Because the source of M1 is effectively floating

when the internal LX switch is off, the drain-to-source

capacitance of M1 may be sufficient to capacitively pull the

node high enough to breaks down the gate oxide of M1. To

prevent this, VOUT should be connected to VIN, allowing the

internal schottky to limit the peak voltage. This will also hold

the VOUT pin at a known low voltage, preventing the built in

OVP function from causing problems. This OVP function is

effectively useless in this mode as the real output voltage is

outside its intended range. If the user wants to implement

their own OVP protection (to prevent damage to the output

capacitor, they should insert a zener from vout to the FB pin.

In this setup, it would be wise not to use the FBSW to FB

switch as otherwise the zener will have to be a high power

one capable of dissipating the entire LED load power. Then

the LED stack can then be connected directly to the sense

resistor and via a 10k resistor to FB. A zener can be placed

from Vout to the FB pin allowing an over voltage event to pull

up on FB with a low breakdown current (and thus low power

zener) as a result of the 10k resistor.

V

= 2.7V TO 5.5V

IN

C1

1µ

C2

0.1µ

FIGURE 9. CONCEPTUAL 8 LEDS HIGH VOLTAGE DRIVER

L1

12

2.2µ

VOUT

VIN

EN

SDIN

ISL97632

FBSW

GND

LX

FB

M1

R1

D0

10BQ100

FQT13N06L

SK011C226KAR

6.3Ω

C3

4.7µ

D1

D2

D3

D4

D5

D6

D7

D8

SEPIC Operation

For applications where the output voltage is not always

above the input voltage, a buck or boost regulation is

needed. A SEPIC (Single Ended Primary Inductance

7

FN9239.3

February 22, 2008

Page 8

ISL97632

www.BDTIC.com/Intersil

Converter) topology, (shown in Figure ), can be considered

for such an application. A single cell Li-Ion battery

operating a cellphone backlight or flashlight is one

example. The battery voltage is between 2.5V and 4.2V

depending on the state of charge. On the other hand, the

output may require only one 3V to 4V medium power LED

for illumination because the light guard of the backlight

assembly is optimized or it is a cost efficiency trade off

reason.

In fact, a SEPIC configured LED driver is flexible enough to

allow the output to be well above or below the input voltage,

unlike the previous example. Another example is when the

number of LEDs and input requirements are different from

platform to platform, a common circuit and PCB that fit all the

platforms, in some cases, may be beneficial enough that

it

outweights the disadvantage of adding additional component

cost. L1 and L2 can be a coupled inductor in one package.

VIN = 2.7V to 5.5V

C1

1µ

C2

0.1µ

1

VIN

EN

SDIN

L1

22µ

2

LX

VOUT

FBSW

FB

GND

C3

V

A

R1

V

B

1µ

1Ω

L2

22µ

C4 0.22µ

D1

boost regulator operation, except the lowest reference point

is at -V

V

. The output is approximated as:

IN

D

------------------

=

OUTVIN

1D–()

(EQ. 5)

where D is the on-time of the PWM duty cycle.

The convenience of SEPIC comes with some trade off in

addition to the additional L and C cost s. The ef ficiency is

usually lowered because of the relatively large efficiency

loss through the Schottky diode if the output voltage is low.

The L2 series resistance also contributes additional loss.

Figure 11 shows the efficiency measurement of a single LED

application as the input varies between 2.7V and 4.2V.

Note, V

is considered the level-shifted LX node of a

B

standard boost regulator. The higher the input voltage, the

lower the V

voltage will be during PWM on period. The

B

result is that the efficiency will be lower at higher input

voltages because the SEPIC has to work harder to boost up

to the required level. This behavior is the opposite to the

standard boost regulator’s and the comparison is shown in

Figure 11.

76

72

VIN = 2.7V

FIGURE 10. SEPIC LED DRIVER

The simplest way to understand SEPIC topology is to think

about it as a boost regulator in which the input voltge is level

shifted downward at the same magnitude and the lowest

reference level starts at -V

rather than 0V.

IN

The SEPIC works as follows; assume the circuit in Figure 10

operates normally when the ISL97632 internal switch opens

and it is in the PWM off state after a short duration where few

LC time constants elapsed, the circuit is considered in the

steady-state within the PWM off period that L1 and L2 are

shorted. V

charged to V

switch closes and the circuit is in the PWM on state, V

is therefore shorted to the ground and C3 is

B

with VA = VIN. When the ISL97632 internal

IN

is

A

now pulled to ground. Since the voltage in C3 cannot be

changed instantenously, V

becomes -V

opens, V

. The next cycle when the ISL97632 switch

IN

boosts up to the targetted output like the standard

B

is shifted downward and

B

68

EFFICIENCY (%)

64

60

0 5 10 15 20

FIGURE 11. EFFICIENCY MEASUREMENT OF A SINGLE LED

SEPIC DRIVER

VIN = 4.2V

1 LED

L1 = L2 = 22µH

C3 = 1µF

R1 = 4.7Ω

ILED (mA)

PCB Layout Considerations

The layout is very important for the converter to function

properly . R

and GND pins. Longer traces to the LEDs are acceptable.

Similarly , th e supply decoupl ing cap and the output filter ca p

should be as close as possible to the VIN and VOUT pins.

The heat of the IC is mainly dissipated through the thermal

pad of the package. Maximize the copper area conn ected to

this pad if possible. In addition, a solid ground plane is always

helpful for the EMI performance.

must be located as close as possible to the FB

SET

8

FN9239.3

February 22, 2008

Page 9

ISL97632

www.BDTIC.com/Intersil

Thin Dual Flat No-Lead Plastic Package (TDFN)

(DATUM A)

NX (b)

5

INDEX

AREA

SEATING

(DATUM B)

6

INDEX

AREA

NX L

8

A

6

C

PLANE

(A1)

D

TOP VIEW

SIDE VIEW

D2

D2/2

12

N

N-1

e

(Nd-1)Xe

REF.

BOTTOM VIEW

2X

A3

NX b

5

C

L

E

A

87

E2/2

0.10

2X

E2

ABC0.15

//

0.15

NX k

CB

0.10

0.08

L

L8.2x3A

8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

MILLIMETERS

SYMBOL

A 0.70 0.75 0.80 A1 - - 0.05 A3 0.20 REF -

b 0.20 0.25 0.32 5,8

D 2.00 BSC D2 1.50 1.65 1.75 7,8

C

C

E 3.00 BSC E2 1.65 1.80 1.90 7,8

e 0.50 BSC -

k0.20 - - -

L 0.30 0.40 0.50 8

N 8 2

Nd 4 3

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

2. N is the number of terminals.

3. Nd refers to the number of terminals on D.

4. All dimensions are in millimeters. Angles are in degrees.

5. Dimension b applies to the metallized terminal and is measured

between 0.25mm and 0.30mm from the terminal tip.

6. The configuration of the pin #1 identifier is optional, but must be

located within the zone indicated. The pin #1 identifier may be

either a mold or mark feature.

7. Dimensions D2 and E2 are for the exposed p ads which provide

BAMC

improved electrical and thermal performance.

8. Nominal dimensions are provided to assist with PCB Land

Pattern Design efforts, see Intersil Technical Brief TB389.

NOTESMIN NOMINAL MAX

Rev. 0 6/04

SECTION "C-C"

FOR EVEN TERMINAL/SIDE

CC

e

TERMINAL TIP

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implic atio n or other wise u nde r any p a tent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

9

FN9239.3

February 22, 2008

Loading...

Loading...