Intersil ISL6262CRZ, ISL6262IRZ Schematics

®

ISL6262

Data Sheet May 15, 2006

Two-Phase Core Regulator for IMVP-6

Mobile CPUs

The ISL6262 is a two-phase buck converter regulator

implementing Intel® IMVP-6 protocol, with embedded gate

drivers. The two-phase buck converter uses two interleaved

channels to effectively double the output voltage ripple

frequency and thereby reduce output voltage ripple

amplitude with fewer components, lower component cost,

reduced power dissipation, and smaller real estate area.

The heart of the ISL6262 is R

Robust Ripple Regulator modulator. Compared with the

traditional multiphase buck regulator, the R

has the fastest transient response. This is due to the R

modulator commanding variable switching frequency during

a load transient.

Intel Mobile Voltage Positioning (IMVP) is a smart voltage

regulation technology, which ef fectively reduces power

dissipation in Intel Pentium processors. To boost battery life,

the ISL6262 supports DPRSLRVR (deeper sleep),

DPRSTP# and PSI# functions and maximizes the efficiency

via automatically enabling different phase operation modes.

At heavy load operation of the active mode, the regulator

commands the two phase continuous conduction mode

(CCM) operation. While the PSI# is asserted at the medium

load in the active mode, the ISL6262 smoothly disables one

phase and operates in a one-phase CCM. When the CPU

enters deeper sleep mode, the ISL6262 enables diode

emulation to maximize the efficiency at the light load.

A 7-bit digital-to-analog converter (DAC) allows dynamic

adjustment of the core output voltage from 0.300V to 1.500V .

A 0.5% system accuracy of the core output voltage over

temperature is achieved by the ISL6262.

A unity-gain differential amplifier is provided for remote CPU

die sensing. This allows the voltage on the CPU die to be

accurately measured and regulated per Intel IMVP-6

specifications. Current sensing can be realized using either

lossless inductor DCR sensing or precision resistor sensing.

A single NTC thermistor network thermally compensates the

gain and the time constant of the DCR variations.

3

Technology™, Intersil’s

3

Technology™

3

FN9199.2

Features

• Precision Two-phase CORE Voltage Regulator

- 0.5% System Accuracy Over Temperature

- Enhanced load line accuracy

• Internal Gate Driver with 2A Driving Capability

• Dynamic Phase Adding/Dropping

• Microprocessor Voltage Identification Input

- 7-Bit VID Input

- 0.300V to 1.500V in 12.5mV Steps

- Support VID Change on-the-fly

• Multiple Current Sensing Schemes Supported

- Lossless Inductor DCR Current Sensing

- Precision Resistive Current Sensing

• Thermal Monitor

• User Programmable Switching Frequency

• Differential Remote CPU Die Voltage Sensing

• Static and Dynamic Current Sharing

• Overvoltage, Undervoltage, and Overcurrent Protection

• Pb-Free Plus Anneal Available (RoHS Compliant)

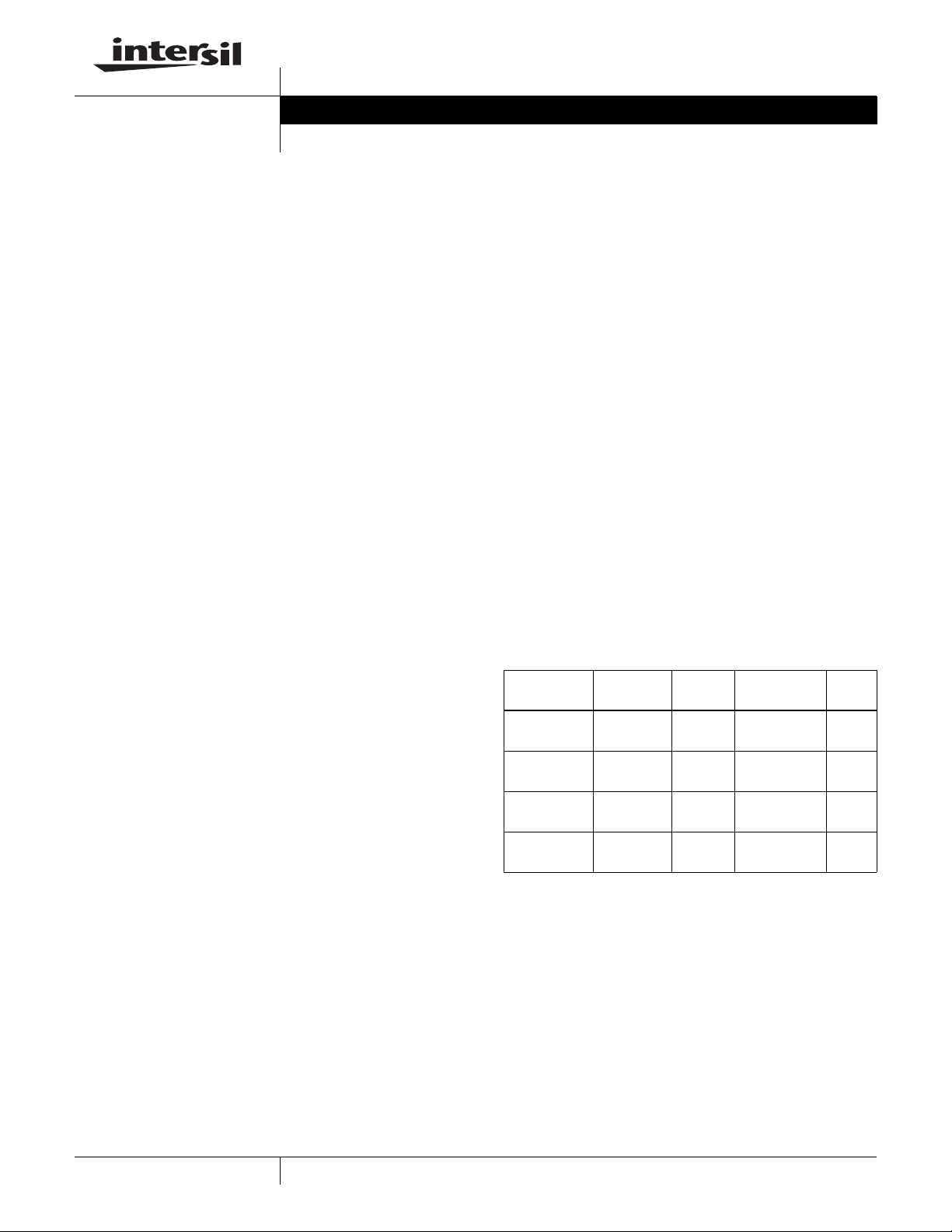

Ordering Information

PART

NUMBER

ISL6262CRZ

(Note)

ISL6262CRZ-T

(Note)

ISL6262IRZ

(Note)

ISL6262IRZ-T

(Note)

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

PART

MARKING

ISL6262CRZ -10 to 100 48 Ld 7x7 QFN

ISL6262CRZ -10 to 100 48 Ld 7x7 QFN

ISL6262IRZ -40 to 100 48 Ld 7x7 QFN

ISL6262IRZ -40 to 100 48 Ld 7x7 QFN

TEMP.

(°C) PACKAGE

(Pb-free)

(Pb-free)

(Pb-free)

(Pb-free)

PKG.

DWG. #

L48.7x7

L48.7x7

L48.7x7

L48.7x7

1

Copyright Intersil Americas Inc. 2005-2006. All Rights Reserved. R

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

3

Technology™ is a trademark of Intersil Americas Inc.

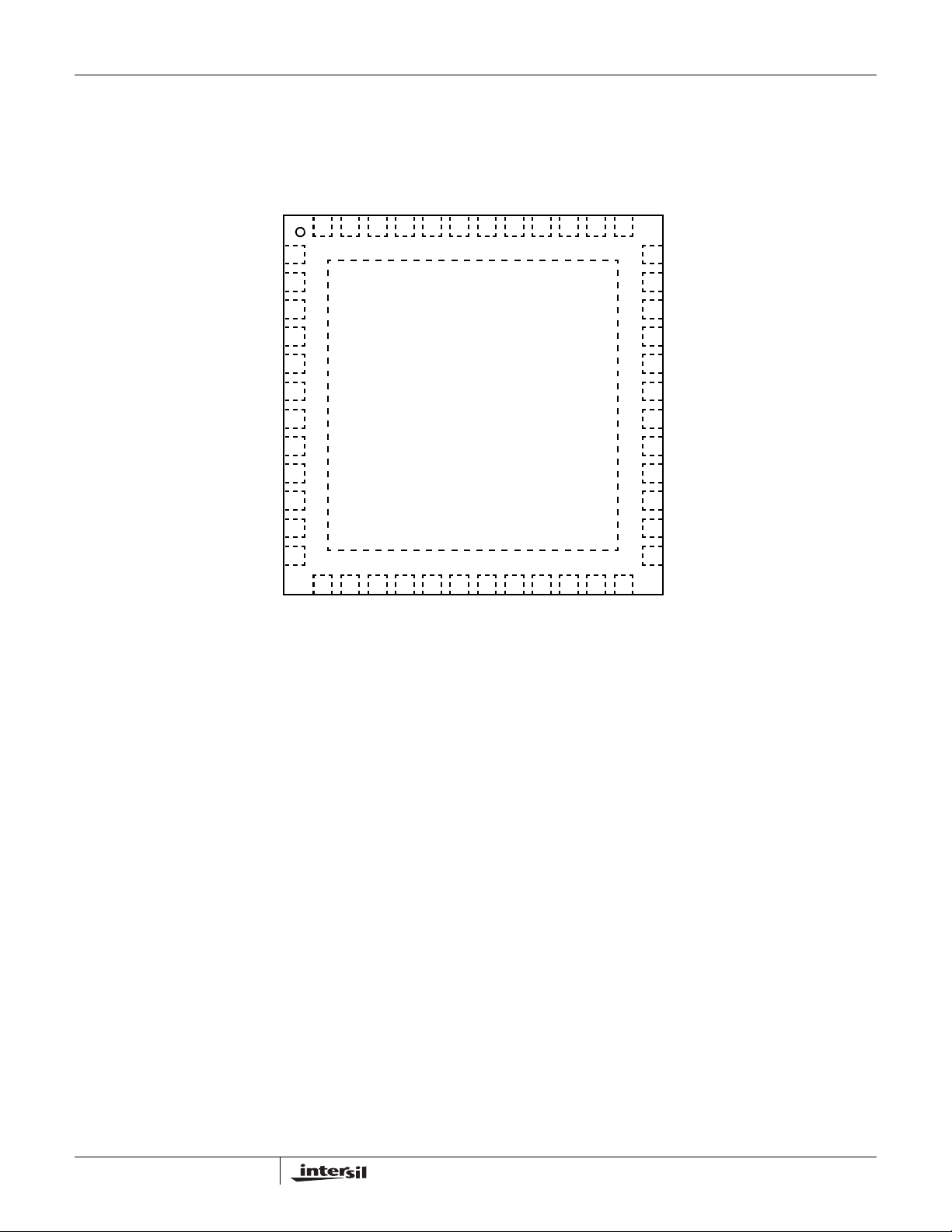

Pinout

ISL6262

ISL6262 (7x7 QFN)

TOP VIEW

3V3

CLK_EN#

DPRSTP#

DPRSLPVR

VR_ON

VID6

VID5

VID4

VID3

VID2

VID1

48 47 46 45 44 43 42 41 40 39 38 37

VID0

PGOOD

PSI#

PGD_IN

RBIAS

VR_TT#

NTC

SOFT

OCSET

VW

COMP

FB

FB2

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

RTN

VSEN

VDIFF

DFB

DROOP

GND PAD

(BOTTOM)

VO

VIN

VSUM

GND

VDD

36

BOOT1

35

UGATE1

34

PHASE1

33

PGND1

LGATE1

32

31

PVCC

30

LGATE2

29

PGND2

PHASE2

28

UGATE2

27

BOOT2

26

NC

25

ISEN2

ISEN1

2

FN9199.2

May 15, 2006

ISL6262

Absolute Maximum Ratings Thermal Information

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 -+7V

Battery Voltage, VIN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +25V

Boot1,2 and UGATE1,2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +30V

ALL Other Pins. . . . . . . . . . . . . . . . . . . . . . . . -0.3V to (VDD +0.3V)

Open Drain Outputs, PGOOD, VR_TT# . . . . . . . . . . . . . . -0.3 -+7V

Recommended Operating Conditions

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

Battery Voltage, VIN. . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V to 21V

Ambient Temperature. . . . . . . . . . . . . . . . . . . . . . . . -10°C to 100°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . -10°C to 125°C

Ambient Temperature, Industrial . . . . . . . . . . . . . . . -40°C to 100°C

Junction Temperature, Industrial . . . . . . . . . . . . . . . -40°C to 125°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

1. θ

JA

Tech Brief TB379.

2. For θ

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

Thermal Resistance (Typical)

θJA

°C/W θJC°C/W

QFN Package (Notes 1, 2). . . . . . . . . . 29 4.5

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . 150°C

Maximum Storage Temperature Range. . . . . . . . . . -65°C to 150°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300°C

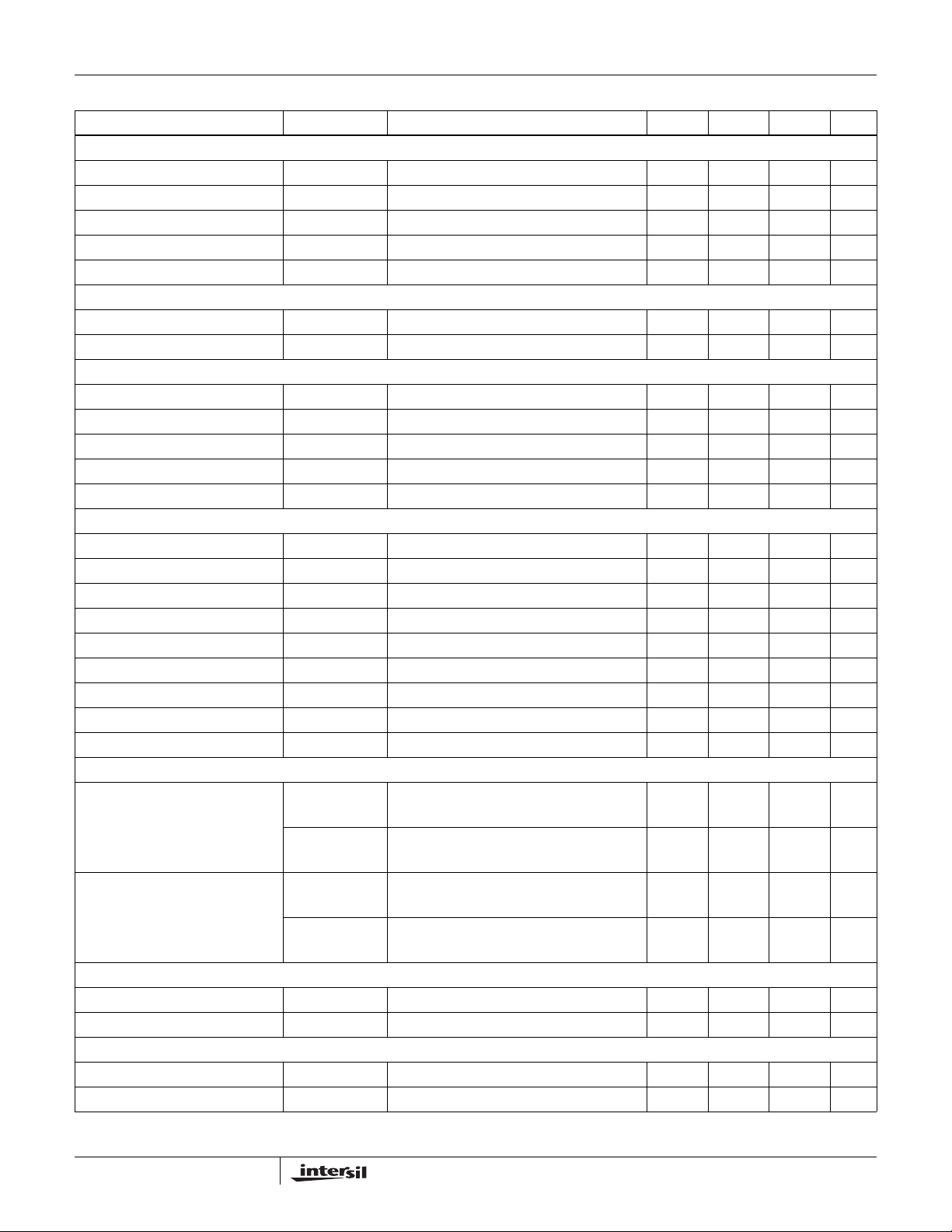

Electrical Specifications V

= 5V, TA = -40°C to 100°C, Unless Otherwise Specified.

DD

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

INPUT POWER SUPPLY

+5V Supply Current I

VDD

VR_ON = 3.3V - 3.1 3.6 mA

VR_ON = 0V - - 1 µA

+3.3V Supply Current I

Battery Supply Current at VIN pin I

3V3

VIN

POR (Power-On Reset) Threshold POR

POR

No load on CLK_EN# - - 1 µA

VR_ON = 0V, VIN = 25V, - - 1 µA

VDD Rising - 4.35 4.5 V

r

VDD Falling 3.9 4.1 - V

f

SYSTEM AND REFERENCES

System Accuracy %Error

(V

cc_core

ISL6262CRZ

No load, closed loop, active mode,

)

TA = 0°C to 100°C, VID = 0.75-1.5V -0.5 - 0.5 %

VID = 0.5-0.7375V -8 - 8 mV

VID = 0.3-0.4875V -15 - 15 mV

%Error

(V

cc_core

ISL6262IRZ

)

= -40°C to 100°C, VID = 0.75-1.5V -0.8 - 0.8 %

T

A

VID = 0.5-0.7375V -10 - 10 mV

VID = 0.3-0.4875V -18 - 18 mV

RBIAS Voltage R

Boot Voltage V

Maximum Output Voltage V

V

RBIAS

BOOT

CC_CORE

(max)

CC_CORE

(min)

R

= 147kΩ 1.45 1.47 1.49 V

RBIAS

1.188 1.2 1.212 V

VID = [0000000] - 1.5 - V

VID = [1100000] - 0.3 - V

VID Off State VID = [1111111] - 0 - V

CHANNEL FREQUENCY

Nominal Channel Frequency f

SW

R

= 3.9kΩ, 2 channel operation,

FSET

V

= 2V

comp

-300-kHz

Adjustment Range 200 - 500 kHz

3

FN9199.2

May 15, 2006

ISL6262

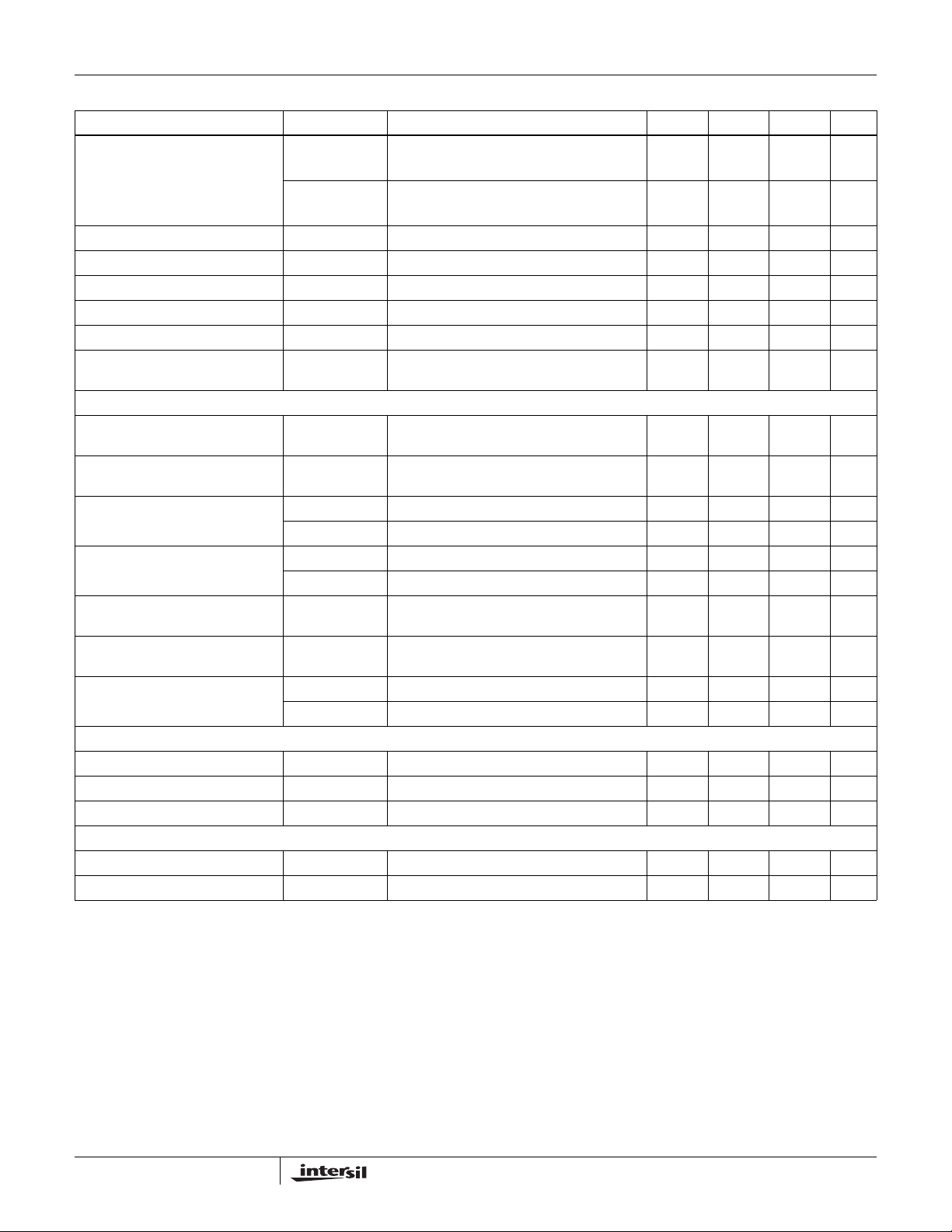

Electrical Specifications V

= 5V, TA = -40°C to 100°C, Unless Otherwise Specified. (Continued)

DD

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

AMPLIFIERS

Droop Amplifier Offset -0.3 - 0.3 mV

Error Amp DC Gain A

V0

Error Amp Gain-Bandwidth Product GBW C

Error Amp Slew Rate SR C

FB Input Current I

IN(FB)

= 20pF - 18 - MHz

L

= 20pF - 5 - V/µs

L

-90-dB

- 10 150 nA

ISEN

Imbalance Voltage --1mV

Input Bias Current -20-nA

SOFT-START CURRENT

Soft-Start Current I

Soft Geyserville Current I

Soft Deeper Sleep Entry Current I

Soft Deeper Sleep Exit Current I

Soft Deeper Sleep Exit Current I

SS

GV

C4

C4EA

C4EB

|SOFT - REF|>100mV ±170 ±200 ±230 µA

DPRSLPVR = 3.3V -47 -41 -35 µA

DPRSLPVR = 3.3V 35 41 47 µA

DPRSLPVR = 0V 170 200 230 µA

-47 -41 -35 µA

GATE DRIVER DRIVING CAPABILITY

UGATE Source Resistance R

UGATE Source Current I

UGATE Sink Resistance R

UGATE Sink Current I

LGATE Source Resistance R

LGATE Source Current I

LGATE Sink Resistance R

LGATE Sink Current I

UGATE to PHASE Resistance R

SRC(UGATE)

SRC(UGATE)VUGATE_PHASE

SNK(UGATE)

SNK(UGATE)VUGATE_PHASE

SRC(LGATE)

SRC(LGATE)VLGATE

SNK(LGATE)

SNK(LGATE)VLGATE

p(UGATE)

500mA Source Current - 1 1.5 Ω

= 2.5V - 2 - A

500mA Sink Current - 1 1.5 Ω

= 2.5V - 2 - A

500mA Source Current - 1 1.5 Ω

= 2.5V - 2 - A

500mA Sink Current - 0.5 0.9 Ω

= 2.5V - 4 - A

-1.1-kΩ

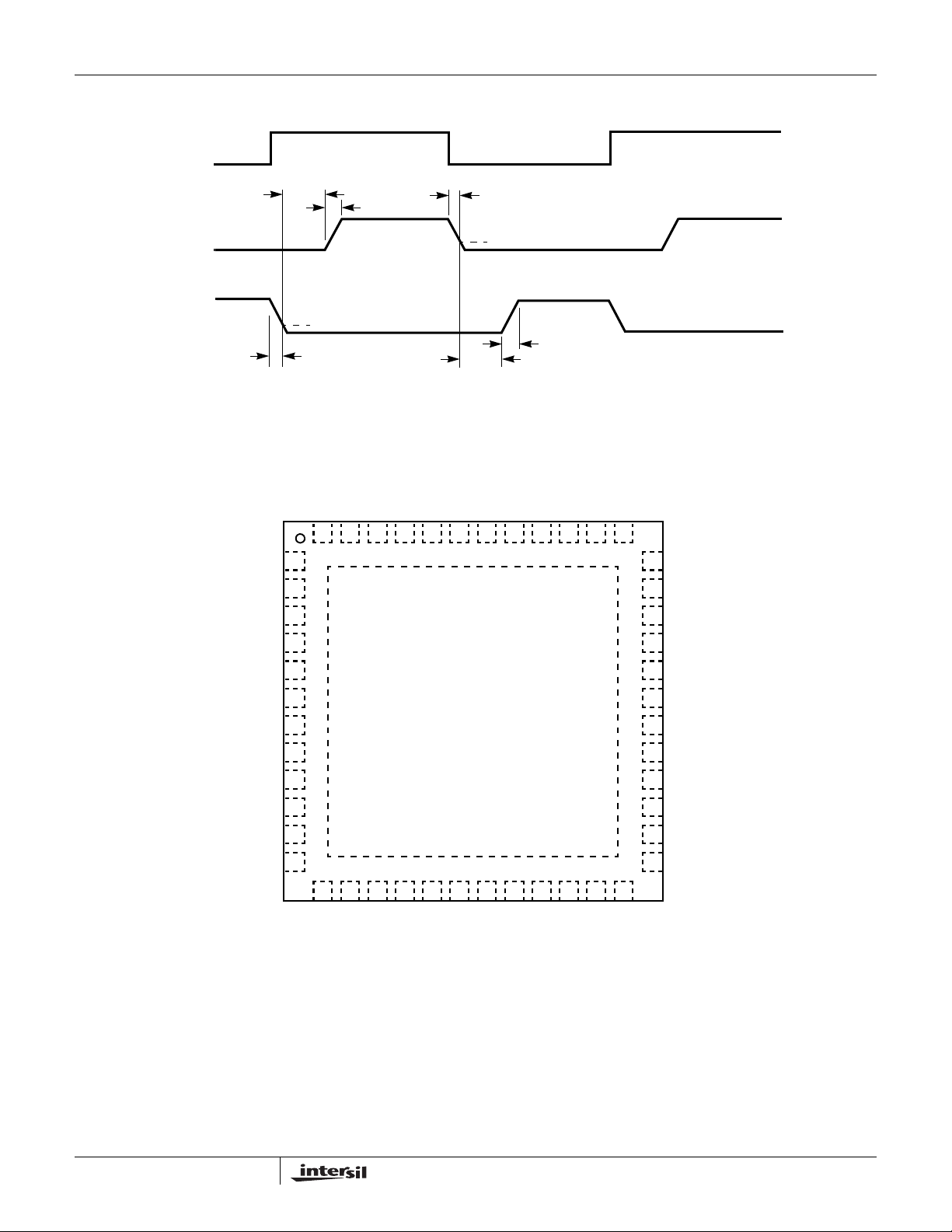

GATE DRIVER SWITCHING TIMING (refer to timing diagram)

UGATE Turn-On Propagation Delay t

ISL6262CRZ

PDHU

t

PDHU

T

= -10°C to 100°C

A

PV

= 5V, Outputs Unloaded

CC

PV

= 5V, Outputs Unloaded 18 30 44 ns

CC

20 30 44 ns

ISL6262IRZ

T

LGATE Turn-On Propagation Delay t

ISL6262CRZ

PDHL

t

PDHL

= -10°C to 100°C

A

PV

= 5V, Outputs Unloaded

CC

PV

= 5V, Outputs Unloaded 5 15 30 ns

CC

71530ns

ISL6262IRZ

BOOTSTRAP DIODE

Forward Voltage V

Leakage V

= 5V, Forward Bias Current = 2mA 0.43 0.58 0.72 V

DDP

= 16V - - 1 µA

R

POWER GOOD and PROTECTION MONITOR

PGOOD Low Voltage V

PGOOD Leakage Current I

OL

OH

I

= 4mA - 0.11 0.4 V

PGOOD

P

= 3.3V -1 - 1 µA

GOOD

4

FN9199.2

May 15, 2006

ISL6262

Electrical Specifications V

= 5V, TA = -40°C to 100°C, Unless Otherwise Specified. (Continued)

DD

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

PGOOD Delay t

ISL6262CRZ

pgd

t

pgd

T

= -10°C to 100°C

A

5.5 6.8 8.1 ms

CLK_EN# Low to PGOOD High

CLK_EN# Low to PGOOD High 5.3 6.8 8.1 ms

ISL6262IRZ

Overvoltage Threshold O

Severe Overvoltage Threshold O

VH

VHS

VO rising above setpoint > 1ms 160 200 240 mV

VO rising above setpoint > 0.5µs 1.675 1.7 1.725 V

OCSET Reference Current I(Rbias) = 10µA 9.8 10 10.2 µA

OC Threshold Offset DROOP rising above OCSET > 120µs -3.5 - 3.5 mV

Current Imbalance Threshold Difference between ISEN1 and ISEN2 > 1ms - 7.5 - mV

Undervoltage Threshold

UV

f

VO falling below setpoint for > 1ms -365 -300 -240 mV

(VDIFF-SOFT)

LOGIC INPUTS

VR_ON, DPRSLPVR and PGD_IN

V

IL

--1V

Input Low

VR_ON, DPRSLPVR and PGD_IN

Input High

Leakage Current of VR_ON and

PGD_IN

Leakage Current of DPRSLPVR I

DAC(VID0-VID6), PSI# and

DPRSTP# Input Low

DAC(VID0-VID6), PSI# and

V

IH

I

IL

I

IH

IL_DPRSLP

I

IH_DPRSLP

V

IL

V

IH

2.3 - - V

Logic input is low -1 0 - µA

Logic input is high at 3.3V - 0 1 µA

DPRSLPVR input is low -1 0 - µA

DPRSLPVR input is high at 3.3V - 0.45 1 µA

--0.3V

0.7 - - V

DPRSTP# Input High

Leakage Current of DAC(VID0-

VID6), PSI# and DPRSTP#

I

IL

I

IH

Logic input is low -1 0 - µA

Logic input is high at 1V - 0.45 1 µA

THERMAL MONITOR

NTC Source Current NTC = 1.3 V 53 60 68 µA

Over-Temperature Threshold V(NTC) falling 1.165 1.18 1.205 V

VR_TT# Low Output Resistance R

TT

I = 20mA - 5 9 Ω

CLK_EN# OUTPUT LEVELS

CLK_EN# High Output Voltage V

CLK_EN# Low Output Voltage V

OH

OL

3V3 = 3.3V, I = -4mA 2.9 3.1 - V

I

CLK_EN#

= 4mA - 0.18 0.4 V

5

FN9199.2

May 15, 2006

ISL6262 Gate Driver Timing Diagram

PWM

t

PDHU

UGATE

t

RU

ISL6262

t

FU

1V

LGATE

t

FL

1V

Functional Pin Description

PSI#

RBIAS

NTC

SOFT

VW

1

2

3

4

5

6

7

8

9

PGOOD

PGD_IN

VR_TT#

OCSET

t

t

PDHL

3V3

CLK_EN#

DPRSTP#

DPRSLPVR

VR_ON

VID6

VID5

48 47 46 45 44 43 42 41 40 39 38 37

GND PAD

(BOTTOM)

RL

VID4

VID3

VID2

VID1

VID0

36

BOOT1

35

UGATE1

34

PHASE1

33

PGND1

LGATE1

32

31

PVCC

30

LGATE2

29

PGND2

PHASE2

28

COMP

10

FB

11

FB2

12

13 14 15 16 17 18 19 20 21 22 23 24

RTN

VSEN

VDIFF

DROOP

PGOOD - Power good open-drain output. Will be pulled up

externally by a 680Ω resistor to VCCP or 1.9kΩ to 3.3V .

PSI# - Low load current indicator input. When asserted low,

indicates a reduced load-current condition, and product goes

into single phase operation.

PGD_IN - Digital Input. When asserted high, indicates

VCCP and VCC_MCH voltages are within regulation.

6

UGATE2

27

BOOT2

26

NC

25

VO

DFB

VSUM

VIN

VDD

GND

ISEN2

ISEN1

RBIAS - 147K resistor to VSS sets internal current

reference.

VR_TT# - Thermal overload output indicator with open-drain

output. Over temperature pull-down resistance is 10Ω.

NTC - Thermistor input to VRTT# circuit and a 60µA current

source is connected internally to this pin.

FN9199.2

May 15, 2006

ISL6262

SOFT - A capacitor from this pin to GND pin sets the

maximum slew rate of the output voltage. The SOFT pin is

the non-inverting input of the error amplifier.

OCSET - Overcurrent set input. A resistor from this pin to

VO sets DROOP voltage limit for OC trip. A 10µA current

source is connected internally to this pin.

VW - A resistor from this pin to COMP programs the

switching frequency (exa. 4.42kΩ ≅ 300kHz).

COMP - This pin is the output of the error amplifier.

FB - This pin is the inverting input of error amplifier.

FB2 - There is a switch between FB2 pin and the FB pin.

The switch is closed in single-phase operation and is

opened in two phase operation. The components connecting

to FB2 is to adjust the compensation in single phase

operation to achieve optimum performance.

VDIFF - This pin is the output of the differential amplifier.

VSEN - Remote core voltage sense input.

RTN - Remote core voltage sense return.

DROOP - Output of the droop amplifier. The voltage level on

this pin is the sum of Vo and the programmed droop voltage

by the external resistors.

DFB - Inverting input to droop amplifier.

VO - An input to the IC that reports the local output voltage.

LGATE1 - Lower-side MOSFET gate signal for phase 1.

PGND1 - The return path of the lower gate driver for

phase 1.

PHASE1 - The phase node of phase 1. This pin should

connect to the source of upper MOSFET.

UGATE1 - Upper MOSFET gate signal for phase 1.

BOOT1 - This pin is the upper gate driver supply voltage for

phase 1. An internal boot strap diode is connected to the

PVCC pin.

VID0, VID1, VID2, VID3, VID4, VID5, VID6 - VID input with

VID0 is the least significant bit (LSB) and VID6 is the most

significant bit (MSB).

VR_ON - Digital input enable. A high level logic signal on

this pin enables the regulator.

DPRSLPVR - Deeper sleep enable signal. A high level logic

indicates the micro-processor is in Deeper Sleep Mode and

also indicates a slow C4 entry or exit rate with 41µA

discharging or charging the SOFT cap.

DPRSTP# - Deeper sleep slow wake up signal. A low level

logic signal on this pin indicates the micro-processor is in

deeper sleep mode.

CLK_EN# - Digital output for system PLL clock. Goes active

10µs after PGD_IN is active and Vcore is within 10% of Boot

voltage.

VSUM - This pin is connected to the summation junction of

channel current sensing.

VIN - Battery supply voltage. It is used for input voltage

feedforward to improve the input line transient performance.

VSS - Signal ground. Connect to local controller ground.

VDD - 5V control power supply.

ISEN2 - Individual current sharing sensing for channel 2.

ISEN1 - Individual current sharing sensing for channel 1.

N/C - Not connected. Grounding this pin to signal ground in

the practical layout.

BOOT2 - This pin is the upper gate driver supply voltage for

phase 2. An internal boot strap diode is connected to the

PVCC pin.

UGATE2 - Upper MOSFET gate signal for phase 2.

PHASE2 - The phase node of phase 2. This pin should

connect to the source of upper MOSFET.

PGND2 - The return path of the lower gate driver for

phase 2.

LGATE2 - Lower-side MOSFET gate signal for phase 2.

3V3 - 3.3V supply voltage for CLK_EN#.

PVCC - 5V power supply for gate drivers.

7

FN9199.2

May 15, 2006

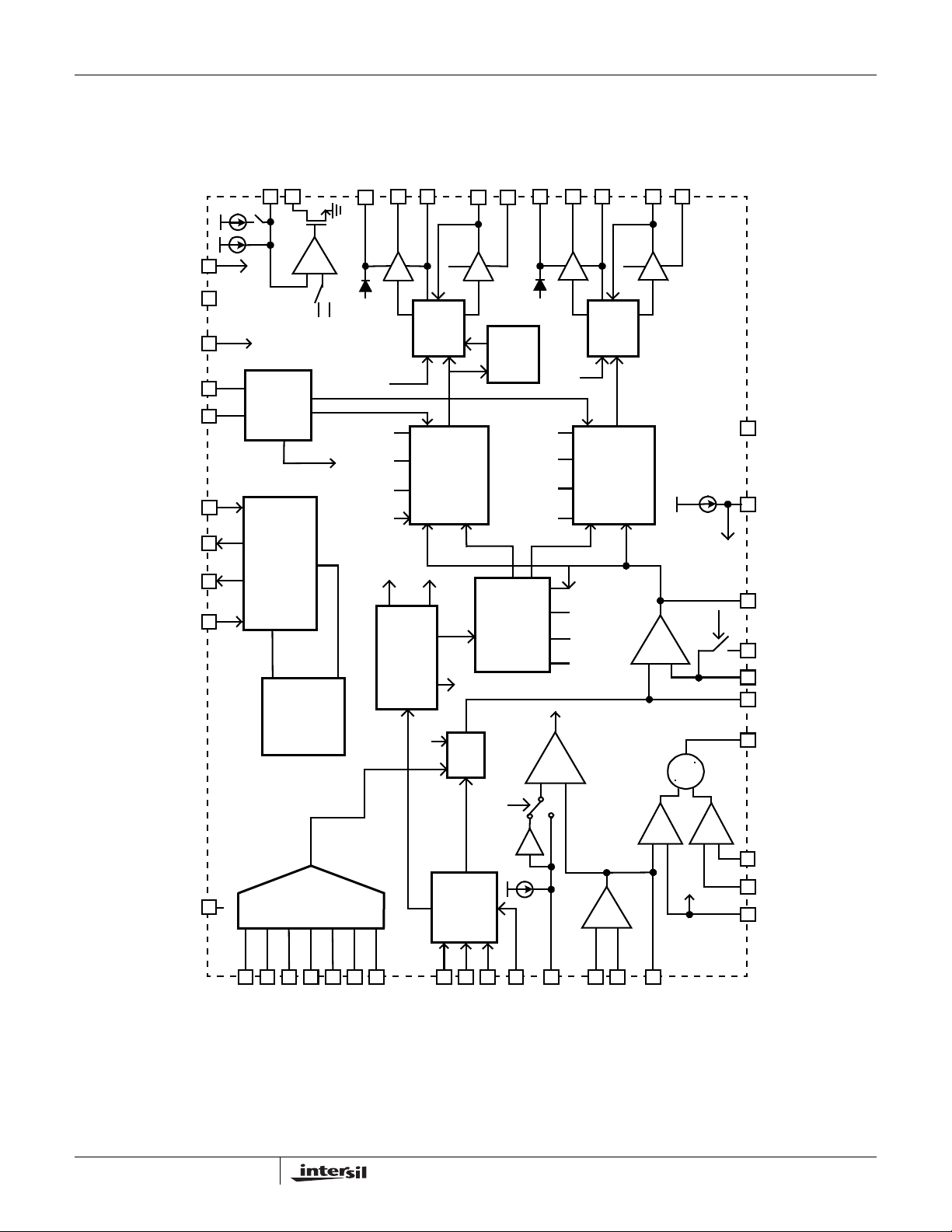

Functional Block Diagram

ISL6262

PVCC

VDD

VIN

ISEN2

ISEN1

3V3

PGOOD

CLK_EN#

PGD_IN

6µA

54µA

PVCC

VIN

NTC

VR_TT#

1.18V

CURRENT

BALANCE

PGOOD

MONITOR

AND LOGIC

P

FLT

FAULT AND

PGOOD

LOGIC

-

I_BALF

GOOD

+

1.2V

BOOT1

PVCC

VSOFT

VIN

OC

CH1

CH1 CH2

CONTROL

UGATE1

FLT

PHASE

LOGIC

VO

PHASE1

PVCC

DRIVER

LOGIC

MODULATOR

SINGLE

PHASE

SOFT

LGATE1

PGND1

PVCC

ULTRA-

SONIC

TIMER

VSOFT

CH2

PHASE

SEQUENCER

SINGLE

PHASE

BOOT2

VIN

OC

-

PHASE2

UGATE2

DRIVER

LOGIC

FLT

MODULATOR

Vw

VO

VIN

OC

+

PVCC

VSOFT

LGATE2

E/A

+

PGND2

SINGLE

PHASE

-

+

GND

VW

Vw

COMP

FB2

FB

SOFT

VDIFF

+

RBIAS

DPRSLPVR

0.5

10µA

DPRSTP#

DROOP

OCSET

VID0

VID1

DAC

VID2

DACOUT

VID3

VID4

VID5

REQUEST

MODE CHANGE

VID6

MODE

CONTROL

PSI#

VR_ON

FIGURE 1. SIMPLIFIED FUNCTION BLOCK DIAGRAM OF ISL6262

8

1

+

-

+

DFB

VSUM

DROOP

1

VO

-

+

RTN

VSEN

VO

FN9199.2

May 15, 2006

-

ISL6262

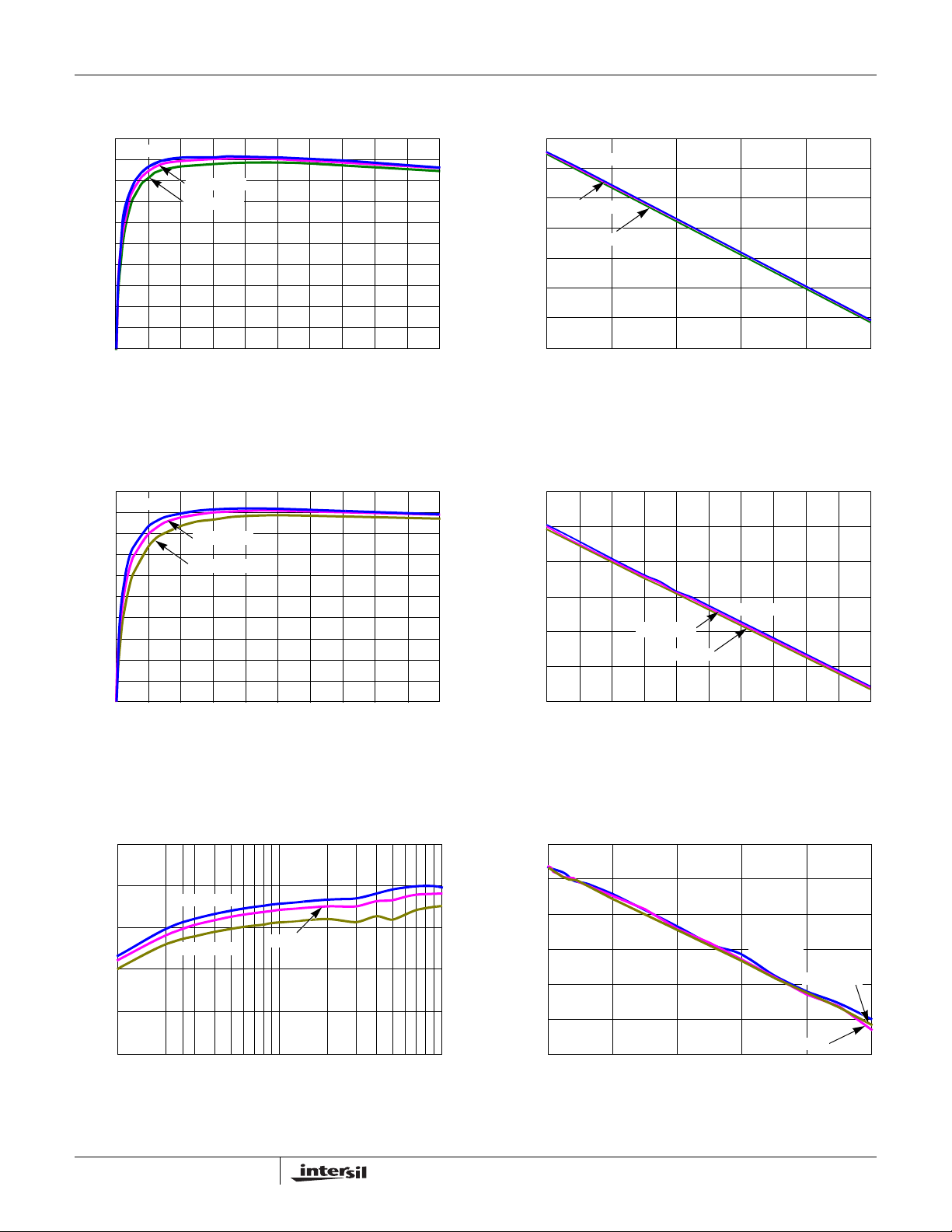

Typical Performance Curves 300kHz, DCR Sense, 2xIRF7821/2xIRF7832 Per Phase

100

VIN = 8.0V

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0 5 10 15 20 25 30 35 40 45 50

VIN = 12.6V

V

= 19.0V

IN

I

OUT

(A)

FIGURE 2. ACTIVE MODE EFFICIENCY , 2 PHASE, CCM,

PSI# = HIGH, VID = 1.15V

100

VIN = 8.0V

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

02468101214161820

VIN = 12.6V

VIN = 19.0V

I

OUT

(A)

FIGURE 4. ACTIVE MODE EFFICIENCY , 1 PHASE, CCM,

PSI# = LOW, VID = 1.15V

1.16

VIN = 8.0V

VIN = 12.6V

= 19.0V

V

IN

01020304050

I

(A)

OUT

(V)

OUT

V

1.14

1.12

1.10

1.08

1.06

1.04

1.02

FIGURE 3. ACTIVE MODE LOAD LINE, 2 PHASE, CCM,

PSI# = HIGH, VID = 1.15V

1.16

1.15

1.14

(V)

1.13

OUT

V

1.12

1.11

1.10

0 4 6 8 10 20

2 12141618

VIN = 12.6V

VIN = 19.0V

I

OUT

VIN = 8.0V

(A)

FIGURE 5. ACTIVE MODE LOAD LINE, 1 PHASE, CCM,

PSI# = LOW, VID = 1.15V

100

90

80

70

EFFICIENCY (%)

60

50

0.1 1 10

VIN = 8.0V

VIN = 19.0V

VIN = 12.6V

I

(A)

OUT

FIGURE 6. DEEPER SLEEP MODE EFFICIENCY , 1 PHASE,

DCM MODE, VID = 0.7625V

9

0.765

0.76

0.755

(V)

0.75

OUT

V

0.745

0.74

0.735

0246810

I

OUT

VIN = 8.0V

VIN = 19.0V

VIN = 12.6V

(A)

FIGURE 7. DEEPER SLEEP MODE LOAD LINE, 1 PHASE,

DCM MODE, VID = 0.7625V

FN9199.2

May 15, 2006

Loading...

Loading...